## Control Design for Electronic Power Converters

Carolina Albea-Sanchez

#### ▶ To cite this version:

Carolina Albea-Sanchez. Control Design for Electronic Power Converters. Automatic. Institut National Polytechnique de Grenoble - INPG; Universidad de Sevilla, 2010. English. NNT: . tel-00539077

# HAL Id: tel-00539077 https://theses.hal.science/tel-00539077

Submitted on 24 Nov 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITE DE GRENOBLE INSTITUT POLYTECHNIQUE DE GRENOBLE

#### THESE EN COTUTELLE INTERNATIONALE

pour obtenir le grade de

DOCTEUR DE L'Université de Grenoble délivré par l'Institut polytechnique de Grenoble et de L'Université de Sevilla (Espagne)

Spécialité: AUTOMATIQUE-PRODUCTIQUE

préparée au Département Automatique du GIPSA-lab

dans le cadre de **l'Ecole Doctorale** Electronique, Electrotechnique, Automatique, Traitement du Signal

> et au laboratoire Departamento de Ingeniería de Sistemas y Autimática

> > présentée et soutenue publiquement

par

## Carolina ALBEA-SÁNCHEZ

le 27/09/2010

#### **TITRE**

## **Control Design for Electronic Power Converters**

#### **DIRECTEURS DE THESE**

M. Carlos Canudas de Wit Directeur de Recherche CNRS

M. Francisco Gordillo Álvarez Professeur, Universidad de Sevilla

#### **JURY**

| M. Javier Aracil Santoja   | Professeur, Universidad de Sevilla,              | Président   |

|----------------------------|--------------------------------------------------|-------------|

| M. Wilfrid Perruquetti     | Professeur, Ecole Centrale de Lille,             | Rapporteur  |

| M. Enric Fossas Colet      | Professeur, Université Politècnica de Catalunya, | Rapporteur  |

| M. Laurent Fesquet         | Maitre de Conférence de l'INPG,                  | Examinateur |

| M. Luis, Martinez Salamero | Professeur, Université de Tarragona,             | Examinateur |

### PhD Thesis

# **Control Design for Electronic Power Converters**

*By* Carolina Albea Sánchez

Supervised by

Carlos Canudas de Wit and Francisco Gordillo

# **Contents**

| Al | knowl  | edgeme  | ents                                       | vii |

|----|--------|---------|--------------------------------------------|-----|

| No | otatio | n       |                                            | ix  |

| 1  | Intr   | oductio | n                                          | 1   |

|    | 1.1    | Introdu | uction to power converters                 | 1   |

|    |        | 1.1.1   | Converters classification                  | 2   |

|    |        | 1.1.2   | DC-DC converters                           | 2   |

|    |        | 1.1.3   | DC-AC converter                            | 3   |

|    |        | 1.1.4   | AC-DC converter                            | 3   |

|    |        | 1.1.5   | AC-AC converter                            | 4   |

|    | 1.2    | Resear  | rch motivation                             | 4   |

|    |        | 1.2.1   | Boost inverter                             | 4   |

|    |        | 1.2.2   | DC-DC Vdd-Hopping converter                | 5   |

|    | 1.3    | Main    | objectives                                 | 6   |

|    |        | 1.3.1   | Controlling a boost inverter               | 7   |

|    |        | 1.3.2   | Controlling a DC-DC Vdd-hopping converters | 7   |

|    | 1.4    | Thesis  | structure                                  | 8   |

| Ι | Con  | Controlling a DC-AC Boost Converter |                                                  |    |  |  |

|---|------|-------------------------------------|--------------------------------------------------|----|--|--|

| 2 | Intr | oductio                             | n                                                | 11 |  |  |

|   | 2.1  | Boost                               | inverter                                         | 12 |  |  |

|   |      | 2.1.1                               | System description                               | 13 |  |  |

|   | 2.2  | Contro                              | ol problem objectives                            | 16 |  |  |

|   |      | 2.2.1                               | Control law                                      | 17 |  |  |

|   |      | 2.2.2                               | Adaptive control                                 | 20 |  |  |

|   |      | 2.2.3                               | Attraction domain                                | 21 |  |  |

| 3 | Con  | trol of t                           | the DC-AC boost converter by energy shaping      | 23 |  |  |

|   | 3.1  | Norma                               | alized average model                             | 23 |  |  |

|   | 3.2  | Energy                              | y shaping control for generation of oscillations | 25 |  |  |

|   |      | 3.2.1                               | Approach overview                                | 25 |  |  |

|   |      | 3.2.2                               | Controller design                                | 27 |  |  |

|   |      | 3.2.3                               | Control law for the full system                  | 29 |  |  |

|   |      | 3.2.4                               | Simulation results                               | 30 |  |  |

|   | 3.3  | Synchi                              | ronization problem                               | 33 |  |  |

|   |      | 3.3.1                               | Boost inverter synchronization                   | 33 |  |  |

|   |      | 3.3.2                               | Synchronization with the electrical grid         | 38 |  |  |

|   | 3.4  | Conclu                              | asion                                            | 39 |  |  |

| 4 | Ada  | ptive co                            | ontrol                                           | 41 |  |  |

|   | 4.1  | Design                              | n of an adaptive control                         | 41 |  |  |

|   |      | 4.1.1                               | Adaptation law                                   | 43 |  |  |

|    |       | 4.1.2    | Error equation                                          | 43 |

|----|-------|----------|---------------------------------------------------------|----|

|    |       | 4.1.3    | Stability properties                                    | 44 |

|    | 4.2   | Stabilit | ty considerations of the full closed-loop system        | 45 |

|    |       | 4.2.1    | Tuned system                                            | 45 |

|    |       | 4.2.2    | Closed-loop system                                      | 46 |

|    |       | 4.2.3    | Singular perturbation form                              | 47 |

|    |       | 4.2.4    | Slow sub-system                                         | 49 |

|    |       | 4.2.5    | Boundary layer fast subsystem                           | 49 |

|    |       | 4.2.6    | Simulations                                             | 52 |

|    | 4.3   | Conclu   | isions                                                  | 52 |

| 5  | Estin | mation ( | of the attraction domain                                | 57 |

|    | 5.1   | Proble   | m statement                                             | 58 |

|    | 5.2   | An app   | proach of estimation of the attraction domain           | 59 |

|    |       | 5.2.1    | Sum of squares optimization                             | 62 |

|    | 5.3   | Applic   | ation to the boost inverter                             | 63 |

|    | 5.4   | Conclu   | isions                                                  | 65 |

|    |       |          |                                                         |    |

| II | Co    | ontroll  | ing a DC-DC Vdd-Hopping converter                       | 67 |

| 6  | Intro | oduction | n                                                       | 69 |

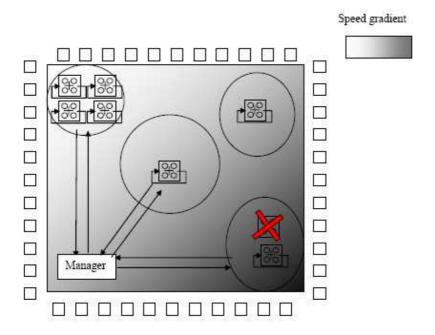

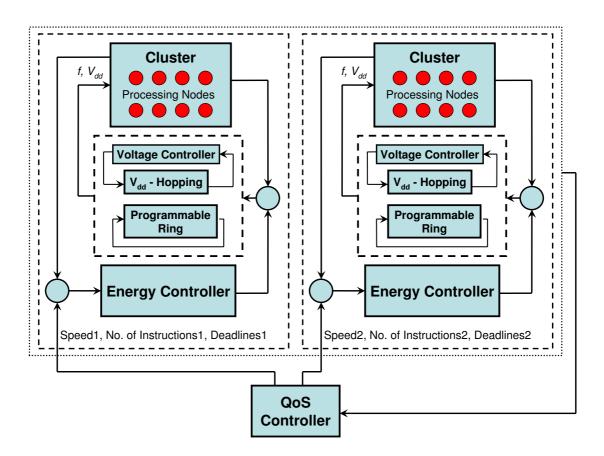

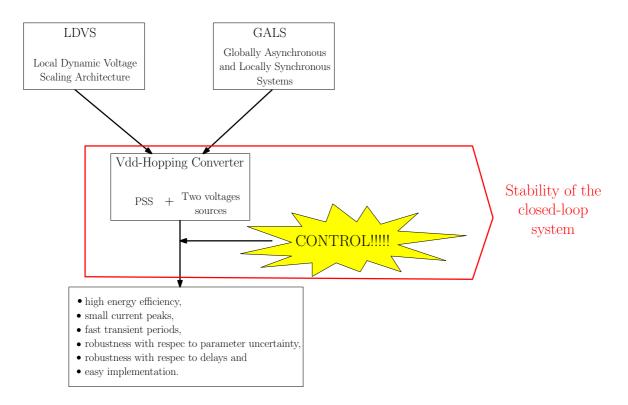

|    | 6.1   | Optimi   | ization of the energy consumption in SoCs               | 71 |

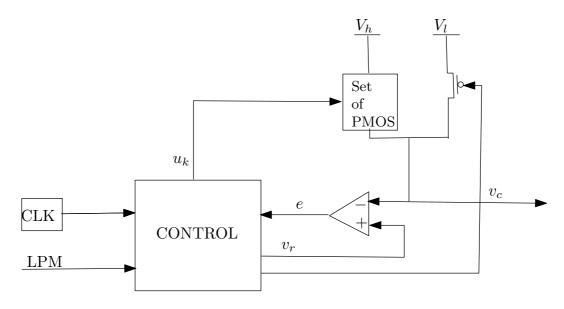

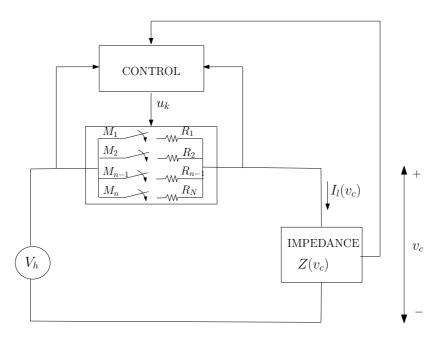

|    | 6.2   | Vdd-H    | opping DC-DC converter                                  | 72 |

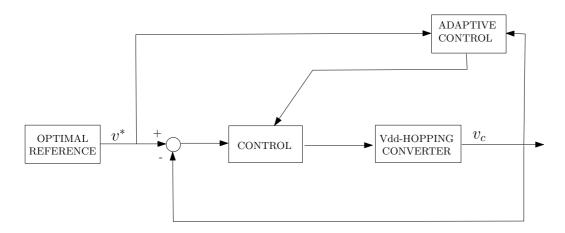

|    | 6.3   | Non-li   | near control application to Vdd-Hopping DC-DC converter | 74 |

|   |      | 6.3.1    | High-performance controllers                                   | 75  |

|---|------|----------|----------------------------------------------------------------|-----|

|   |      | 6.3.2    | Energy-aware controller                                        | 76  |

|   |      | 6.3.3    | Approximate stability analysis for the energy-aware controller | 77  |

|   |      | 6.3.4    | Advanced energy-aware controller                               | 78  |

| 7 | Higl | 1-perfoi | mance control for the DC-DC Vdd-Hopping converter              | 81  |

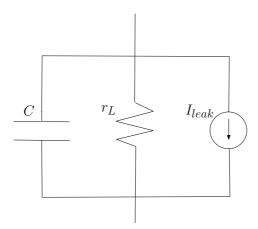

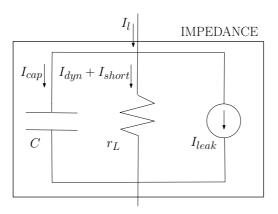

|   | 7.1  | Mathe    | matical model of Vdd-Hopping mechanism                         | 82  |

|   |      | 7.1.1    | Mathematical model for control design                          | 82  |

|   | 7.2  | Contro   | ol laws                                                        | 85  |

|   |      | 7.2.1    | Control proposed in [99]                                       | 85  |

|   |      | 7.2.2    | Controller No. 1: linear controller                            | 86  |

|   |      | 7.2.3    | Controller No.2: feedback linearization                        | 89  |

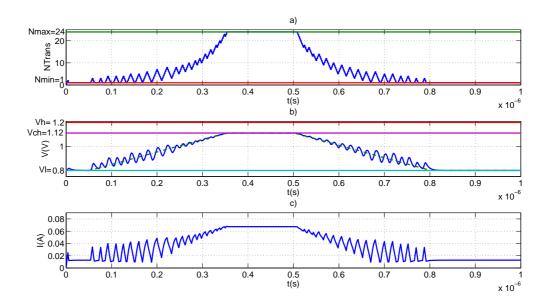

|   |      | 7.2.4    | Controller No.3: Lyapunov-based design                         | 90  |

|   | 7.3  | Perform  | mance evaluation                                               | 93  |

|   |      | 7.3.1    | Energy evaluation                                              | 94  |

|   |      | 7.3.2    | Summary                                                        | 95  |

|   | 7.4  | Advan    | ced Lyapunov's controller                                      | 97  |

|   |      | 7.4.1    | Optimal voltage reference computation                          | 98  |

|   |      | 7.4.2    | Adaptive feedback control design                               | 103 |

|   | 7.5  | Simula   | ation of the advanced Lyapunov's controller                    | 104 |

|   | 7.6  | Conclu   | asion                                                          | 106 |

| 8 | Ene  | rgy-awa  | are controller for the Vdd-Hopping converter                   | 109 |

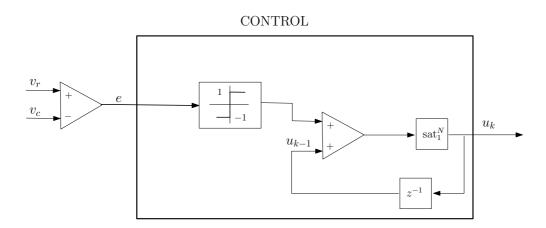

|   | 8.1  | Contro   | ol design without current-peak managing                        | 110 |

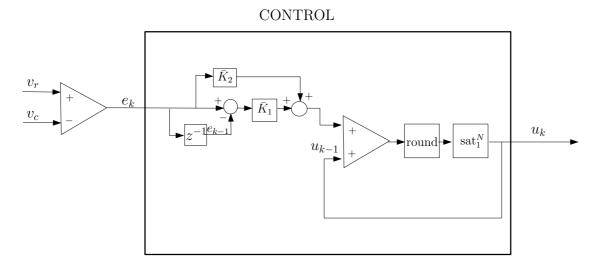

|    | 8.2  | Control redesign with current-peak managing                                                      | 110 |

|----|------|--------------------------------------------------------------------------------------------------|-----|

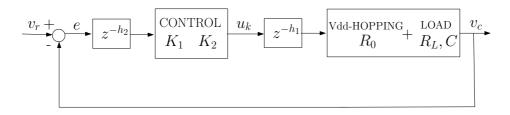

|    |      | 8.2.1 Time discretization                                                                        | 112 |

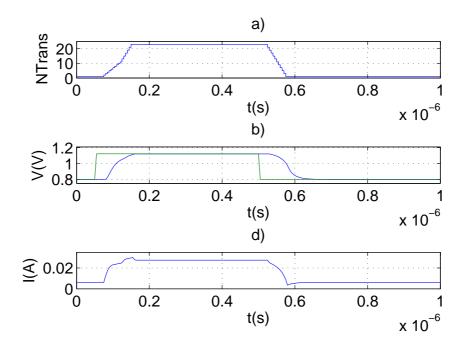

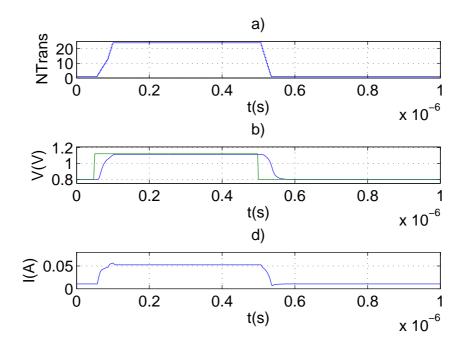

|    |      | 8.2.2 Simulation of ENARC controller in the Vdd-Hopping system                                   | 113 |

|    | 8.3  | Conclusions                                                                                      | 115 |

| 9  | Appı | roximate stability analysis of the DC-DC Vdd-Hopping converter                                   | 117 |

|    | 9.1  | Stability with control (7.10)                                                                    | 118 |

|    | 9.2  | Stability with control (8.6)                                                                     | 121 |

|    | 9.3  | Conclusions                                                                                      | 127 |

| 10 | Sub- | optimal control considering delays and parameter uncertainties                                   | 129 |

|    | 10.1 | Problem statement                                                                                | 131 |

|    |      | 10.1.1 Alternative representation for the saturated control (10.2) and the error equation (10.1) | 132 |

|    |      | 10.1.2 State-space representation                                                                | 133 |

|    |      | 10.1.3 Stability and disturbance rejection problem                                               | 133 |

|    | 10.2 | $H_{\infty}$ control design                                                                      | 134 |

|    |      | 10.2.1 Descriptor model transformation                                                           | 134 |

|    |      | 10.2.2 Condition for state-space representation                                                  | 135 |

|    |      | 10.2.3 Control design                                                                            | 136 |

|    | 10.3 | Robust control tuning                                                                            | 137 |

|    | 10.4 | Sub-optimal control result                                                                       | 139 |

|    | 10.5 | Simulation Results                                                                               | 140 |

|    |      | 10.5.1 Uncertain clock frequency                                                                 | 140 |

|    |      | 10.5.2 Uncertain PMOS resistance                                                                 | 140 |

| Lis | st of P | Publications                         | 152 |

|-----|---------|--------------------------------------|-----|

|     | 12.2    | Future work                          | 150 |

|     | 12.1    | Conclusions and contribution summary | 147 |

| 12  | Cone    | clusions and future work             | 147 |

|     | 10.7    | Conclusions                          | 145 |

|     | 10.6    | Evaluation of the tuning methods     | 143 |

|     |         | 10.5.3 Uncertain load parameter      | 140 |

# Aknowledgements

The period of this thesis brought me valuable new experiences in both a scientific and personal perspective. This thesis would not have been possible without the constant support and motivation of many people.

Firstly, I would like to express my sincere gratitude to my two supervisors, the Professor Francisco Gordillo at the 'Universidad de Sevilla' (Spain), in the Nonlinear Control group from the 'Departmento de Ingenía de Sistemas y Automática'; and the Director of Research Carlos Canudas de Wit at the CNRS (France), in the NeCS team from the 'Département d'Automatique de GIPSA-Lab' at the 'Institut Polytechnique de Grenoble' and at the 'Institut National de Recherche en Informatique et en Automatique de Grenoble' (France). Their wide knowledge and their experience have been of great value for me. Their encouraging and personal guidance have provided a good background for the present thesis.

Many thanks to the Professor Wildfrid Perruquetti at the 'l'Ecole Central de Lille' (France), and the Professor Enric Fossas Colet at the 'Universit Politècnica de Catalunya' (Spain), for accepting to review my work as well as for participating in my jury committee. Their constructive suggestions on the thesis are really appreciated for me. I am grateful that in the midst of their activities, they accepted these tasks.

I am also grateful the Professor Javier Aracil at the 'Universidad de Sevilla' (Spain), the Maitre de Conference Laurent Fesquet at the 'Institut Polytechnique de Grenoble' (France) and the Professor Luis Martinez Salamero at the 'Université de Tarragona' (Spain), for their commitment to take part in my jury committee.

During this period, I have collaborated with many colleagues, from PhD students, teachers to professors for whom I have great regard, and I wish to extend my warmest thanks to all those who have helped me from a professional and personal point of view. Especially to Alicia, Mirko, Antonio, Isa, Pablo, Alejandro, Jörn, Guilherme, Vicente, Fabio, Manolo Gil, Manolo Vargas, Manolo Ruiz, Jose Ángel, Manolo Lopez, Javier, Eduardo, Paco Rubio, Paco Salas, Carlos Vivas, Fernando, Asun, Amparo and David in the 'Departmento de Ingenía de Sistemas y Automática', at the 'Universidad de Sevilla'. And thanks to Luc, Lara, Sylvain, Riccardo, Nicolas, Emilie, Gabriel, Denis, Wenjuan, Brandon, Katerina, John-Jairo,

Gregory, Daniel, Nicolas and Olivier in the 'Département d'Automatique de GIPSA-Lab' at the 'IInstitut Polytechnique de Grenoble' and at the 'Institut National de Recherche en Informatique et en Automatique de Grenoble'.

I am grateful to the secretaries and librarians in the automatic departments from Spain, (Manolo, Antonio, Silvia) and France, (Virginie, Marie-Rose, Marie-Therese, Patricia, Myriam, Elodie) for helping me to run smoothly and for assisting me in many different ways.

I wish to thank my best friends from Spain, JuanMa, Maribel, Olga, compañeros de ISF, Manolo, Sonia, and from France, Johana, Mikel, Luis, Eduardo, for helping me through difficult periods, and for providing to me their friendship, entertainment and attention.

My warm special thanks to my family, especially to my mother Marilo, my sister Myrian, Domingo and my father Pepín, for their consideration of my research abroad. And my deep lovely thanks to Alexandre for its emotional supports. Without their encouragement and understanding it would have been impossible for me to finish this work.

Lastly, I offer my regards and blessings to all of those who supported me in any respect during the completion of the project.

# **Notation**

The following symbols and conventions will be used consistently throughout the thesis.

```

identically equal

\neq

not identically equal

\approx

approximately equal

defined as

<(>)

less (greater) than

\leq (\geq)

less (greater) than or equal to

\ll (\gg)

much less (greater) than

\pm

plus and minus

\forall

for all

\in

belongs to

\subset

subset of

intersected with

such as

tend to

x^T

the transpose of a vector x

\infty

infinity

Σ

summation

|x|

the absolute value of x

the norm of a vector x

||x||

the p-norm of a vector x

||x||_p

closed interval from a to b

[a,b]

the set from 1 to N

\{1,2,...,N\}

discrete variable

discrete-time delay or parameter, i.e., x_{k-1} = q^{-1}x_k

\mathbb{R}^n

the n-dimensional Euclidean space

\mathbb{R}^+

the semi-positive-dimensional Euclidean space

\mathbb{N}

the set of natural numbers

\mathbb{Z}

the set of integer numbers

```

| Re z                                                                                                                               | the real part of a complex variable z                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| (x,y)                                                                                                                              | metric space                                                                                                            |

| $I_n$                                                                                                                              | n-dimensional identity matrix                                                                                           |

| $\operatorname{diag}[a_1,,a_n]$                                                                                                    | a diagonal matrix with diagonal elements $a_1$ to $a_n$                                                                 |

| $O(\cdot)$                                                                                                                         | order of magnitude notation                                                                                             |

| $f: S_1 \rightarrow S_2$                                                                                                           | a function $f$ mapping a set $S_1$ into a set $S_2$                                                                     |

| $\frac{\partial f}{\partial x}$                                                                                                    | the Jacobian matrix                                                                                                     |

| $f: S_1 \to S_2$ $\frac{\partial f}{\partial x}$ $\dot{y}$ $\frac{d}{dt}$ $\lambda_{min}(P)$ $P > 0$                               | the first derivative of y with respect to time                                                                          |

| $\frac{d}{d}$                                                                                                                      | the first derivative of y with respect to time                                                                          |

| $\lambda_{min}^{dt}(P)$                                                                                                            | the minimum eigenvalue of symmetric matrix P                                                                            |

| P > 0                                                                                                                              | a positive definite matrix                                                                                              |

| $P \ge$                                                                                                                            | a positive semidefinite matrix P                                                                                        |

| e                                                                                                                                  | neperian number                                                                                                         |

| S                                                                                                                                  | the Laplace variable                                                                                                    |

| sign                                                                                                                               | sign function                                                                                                           |

| max                                                                                                                                | maximum                                                                                                                 |

| min                                                                                                                                | minimum                                                                                                                 |

| exp                                                                                                                                | exponential function                                                                                                    |

| sin                                                                                                                                | sine                                                                                                                    |

| cos                                                                                                                                | cosine                                                                                                                  |

| dist(p, M)                                                                                                                         | the distance from a point p to a set M                                                                                  |

| $\lim_{x\to c} f(x)$                                                                                                               | limit of $f(x)$ as x approaches $c$                                                                                     |

|                                                                                                                                    |                                                                                                                         |

| $\operatorname{sat}_m^M(x)$                                                                                                        | is defined as $\begin{cases} M & \text{if}  x > M \\ x & \text{if}  m \le x \le M \\ m & \text{if}  x < m. \end{cases}$ |

| <i>m</i> 、                                                                                                                         | m if $x < m$ .                                                                                                          |

| $\mathscr{C}o$ is the convex hull of a set                                                                                         | •                                                                                                                       |

| round(x)                                                                                                                           | is the nearest integer to x                                                                                             |

| $\zeta^+$                                                                                                                          | denotes $\zeta(k+1)$                                                                                                    |

| $\zeta^-$                                                                                                                          | denotes $\zeta(k)$                                                                                                      |

| $\Delta \zeta 	riangleq \zeta^+ - \zeta^-$                                                                                         | the value of $\zeta$ in two consecutive sampling time                                                                   |

| Fo is the convex hull of a set $\operatorname{round}(x)$ $\zeta^+$ $\zeta^ \Delta \zeta \triangleq \zeta^+ - \zeta^ \mathscr{L}_2$ | is the space of $\{x\}$ with the norm: $  x  _2^2 \triangleq \sum_{k=0}^{\infty} x^T x < \infty$                        |

| $H_{\infty}$                                                                                                                       | H-infinite method                                                                                                       |

|                                                                                                                                    | designation of the end of definition                                                                                    |

|                                                                                                                                    | designation of the end of proof                                                                                         |

| [xx]                                                                                                                               | see reference number xx in the bibliography                                                                             |

|                                                                                                                                    |                                                                                                                         |

#### **Acronyms**

BVP Boundary Value Problem DC Direct current DVS Dynamic Voltage Scaling **ENARC ENergy Aware Controller** Globally-Asynchronous and Locally Synchronous Systems **GALS** HPF High Pass Filter IVP Initial Value Problem LDVS Local Dynamic Voltage Scaling LMI Linear Matrix Inequalities LPF Low Pass Filter PC Personal Computer PHC PHase Controller Proportional-Integral PΙ

PLL Phase-Lock Loop PMOS P-channel Metal-Oxide-Semiconductor field-effect transistor

PSS Power Supply Selector QoS Quality of Service SDP Semidefinite Program

AC Alterning current

SMPC Switched-Mode Power Converter

SoC System on ChipSOS Sum Of SquaresTHD Total Harmonic Distortion

VLSI Very Large Scaling Integration

VHDL-AMS Verilog Hardware Description Language-Analog and Mixed-Signal

# Chapter 1

# Introduction

### 1.1 Introduction to power converters

Power converters are electronic circuits associated to the conversion, control, and conditioning of electric power. The power range can be from milliwatts, mobile phone, for example, to megawatts, in electric power transmission systems. Reliability of the power converters become a key industrial focus. Electronic devices and control circuit must be highly robust in order to achieve a high useful life. A special accent must be set on the total efficiency of the power electronic circuits. Firstly, because of the economic and environmental value of wasted power and, secondly, because of the cost of energy dissipated that it can generate. Even a small improvement in converter power efficiency translates to improved profitability of the investment in the electronic market [33, 100].

Among all electronic converters, the most common technology is switched-mode power converters (SMPC) [118]. They convert the voltage input to another voltage signal, by storing the input energy temporarily and then releasing that energy to the output at a different voltage. This switched-mode conversion has a particular interest due to the fact that it can switch at high frequency in a very efficient way. Power is controlled (even modified) by controlling the timing that the electronic switches are "on" and "off".

A much greater emphasis is required on achieving high-power efficiency in low-power level electronic technology, since few low-power circuits can tolerate a power efficiency less than 85%. Converters are used in these circuits in order to change the supply voltage in the blocks of the System on Chips (SoCs) according to performance requirements, for power efficiency reasons. Research have been focused on developing electronic circuits that can be employed as switches. e.g. approximating ideal closed or open switches, as the Vdd-hopping converter [98].

#### 1.1.1 Converters classification

Power converters control the flow of power between two systems by changing the character of electrical energy: from direct current to alternating current, from one voltage level to another voltage, or in some other way.

Here, some important way to classify the power converters are described. The aim of this section is not to make a rigorous converter classification, either to make a state of the art, because it is not the purpose of this thesis. It is only desired to understand some properties of these kind of circuits.

The most common classification of power conversion systems is based on the waveform of the input and output signals, in the case whether they are alternating current (AC) or direct current (DC) [33], thus:

- DC to DC.

- DC to AC. Inverter.

- AC to DC. Rectifier.

- AC to AC. Transformer.

At the same time, the devices within converters can be switched in different ways [72, 79, 100]. If the devices switch at the line frequency (normally, 50Hz or 60HZ), they can be *line frequency converters* (naturally commutated converters) or *high-frequency switching* (forced-commutated converters).

Depending on the character of the input source, they may be *voltage-source converters* or *current-source converters*. Moreover, converters may be of low, medium or high voltage and/or current level. Another sort of classification may be performed according to the size of the output signal obtained from the input signal; if the converter accomplishes a lower output signal it is well known as *step-down*, and if it obtains a larger signal, it is known as *step-up* [2].

#### 1.1.2 DC-DC converters

DC-DC converters are electronic circuits that change the DC operating voltage or current. They have recently aroused the interest in the current market due to its wide range of applicability. Normally, they are designed in order to transfer power from the input to the output

in one direction. However, in the case of switches topologies, the power moving may be also bidirectional, being very useful to develop new converter topologies for other applications, as can be an inverter topology [25].

They have a particular interest in low-power circuits, as cellular phone and personal computers (PCs). This sort of technology are composed of many sub-circuits that require an own voltage level from an external supply (higher, lower or even negative) or battery. DC-DC converters have a special role in these kind of systems, since they can be employed to change the voltage from a partial lowered battery voltage thereby. This is based on the Dynamic Voltage Scaling technic (DVS) [27, 89, 136]. The main idea of DVS is to vary the supply voltage in order to consume a minimal amount of energy. This fact improves the power efficiency and saves space in spite of using multiple batteries to accomplish the same voltage level [82].

#### 1.1.3 DC-AC converter

DC-AC converters, or commonly named inverters, can obtain a certain amplitude and frequency of the AC voltage and/or current without using normally an intermediate DC stage. This electrical device is a power electronic oscillator [118]. An electronic oscillator is just an electric circuit that produces a repetitive signal, as a sine-wave output signal. Generally, they are SMPCs.

These kind of circuits require an efficient control for the switches devices that, in many occasions, can be quite complex due to system structure. Therefore, to design a suitable control law currently is a subject of much research [22, 107].

#### 1.1.4 AC-DC converter

The process that converts AC to DC is known as rectification, hence, these converters are also called rectifier. Among others applications, they are used in power supplies and detector of radio signals.

The rectification can be half-wave or full-wave. In the first case (half-wave rectification), only one half of the input waveform can be employed to reach the desired output. Therefore, only this half AC wave (positive or negative) is converted. The efficiency will depend of the kind of application. It is clear, that it is not useful for power transfer. The full-wave rectification can convert the whole of the input waveform to achieve the constant output signal. It becomes more efficient [59, 137].

4 1.2. Research motivation

#### 1.1.5 AC-AC converter

AC-AC converters are employed to transform an AC input signal to another AC output signal with an arbitrary amplitude. Likewise, depending on the converter complexity, the frequency can be changed as well. The efficiency of these kind of systems depends on the type of circuit employed. It is clear that a higher power density and reliability will be obtained with a conversion in one single stage [139].

#### 1.2 Research motivation

A lot of research has recently been focused on converters due to the increasing deal of interest in power electronics. This is mainly caused by their broad applicability domain that includes battery-operating portable equipment, computers, appliances, vehicles, industrial electronic equipment, uninterruptible power supplies, telecommunication systems and much more. This current research is specially focused on finding highly-efficient converter topologies for every system application and, on designing control mechanisms that accomplishes the converter objectives. On this way, one or more electrical parameters can be regulated with a high reliability and efficiency, e.g., the supply voltage of an appliance, the temperature of an oven, the speed of a motor, the supply voltage within calcul node of a SoCs [41,141].

Tackling the control problem in detail for every converter is out of the scope of a thesis. That is why, among all variety of converters, this thesis is focused on providing a control solution for two converters topologies, which have some interesting properties and applications. The converters that will be dealt with are: firstly, a switch inverter topology; and secondly, a DC-DC converter for low power application.

#### 1.2.1 Boost inverter

As was said before, inverters are devices that obtain a current output signal capables from passing through zero. The inverters are generally SMPCs, and their topologies are derived from coupling one or more basic switch topologies. Among them, it can be found the boost-buck inverter [95], the buck-boost inverter [90], the buck inverter [127], the boost inverter [25].

The first part of this thesis is focused on a boost inverter. Its interest is due to its step-up property, which is achieved through a signal stage. In this case, two DC-DC boost converters are connected with a load between them, thus it has a bidirectional current [25].

In this system, four switches have to be controlled by two control signals, in order to control the two output voltages of each DC-DC boost converter. Not only the voltage amplitude must be controlled, but the phase of both signal must also be controlled to achieve the specified output voltage.

Several control laws have been designed for this converter from other authors [25, 126, 149], applying different control strategies. In this thesis, a novel control strategy based on energy shaping for generation of oscillations is employed [16,58], being the control objective a limit cycle. The novelty of this method is that it does not need to track any reference signal to achieve an oscillatory character in the output signal.

#### 1.2.2 DC-DC Vdd-Hopping converter

The second part of the thesis is focused on a DC-DC converter employed in low-power applications. As mentioned, the demand for high efficiency DC-DC converters is increasing dramatically, especially in battery-operated devices such as cellular phones and personal computers.

In SoCs, to extend battery life has a particular role. By employing DC-DC converters based on power-saving, power efficiency in SoCs can be significantly increased, thereby extending battery life. The goal of these efficiency DC-DC converters is to adapt dynamically the supply voltage of the chip according to the required performance level. This is the DVS idea mentioned before. Numerous DC-DC converters employed for this aim have been proposed over the years to increase the power efficiency of an SoCs. The most commonly used topologies in DC-DC converters in low-power electronics are: continuous buck converters [119, 143, 153], boost converters [36], buck-boost [125, 142] converters and charge pump [125], among others. However, while converters may decrease conduction losses, additional losses can be added if switched devices are employed. In low-power applications where a high-efficiency is required, other different topologies far from switched-mode are employed.

In [98], a discrete DC-DC converter was proposed based on the 'Vdd-Hopping' technique. This method is expired in scaling the voltage supply  $V_{dd}$  in a discrete way, delivering two small voltage levels according to the optimum  $V_{dd}$  required for every performance [75, 106, 128]. Hence its name of 'DC-DC Vdd-Hopping converter'. Therefore, this technique replaces the continuous adjustable voltage, just to two set-points [83], so that it reaches a high-efficiency and reduced size. Likewise, it is a very simple system, becoming easily controllable [55].

This converter is employed in a French gouvernement project, with a very ambitious objective: 'to reduce the size of the SoCs to 32nm'. For this, a new technology must be

1.3. Main objectives

| Converter             | Power level   | Conversion | Scales      | Model order |

|-----------------------|---------------|------------|-------------|-------------|

| Boost Inverter        | More suitable | DC-AC      | normal      | $4^{th}$    |

|                       | for medium    |            |             |             |

|                       | and high      |            |             |             |

|                       | power         |            |             |             |

| Vdd-Hopping Converter | Low power     | DC-DC      | micro- or   | $1^{st}$    |

|                       |               |            | nano-scales |             |

**Table 1.1**: Main differences between boost inverter and Vdd-Hopping converter

developed, since the currently technology applied to 45nm can not be employed for physical reasons. Here, the control may take a particular role since, a suitable control law can achieve the equilibrium and the demanded requirements, as well. For instance, it has to achieve the highest efficiency (among other goals) to achieve the global project objective.

## 1.3 Main objectives

The two selected converters have different natures and applications, and hence, they may have different control objectives. They covers a wide range of the power converter domain. The boost inverter normally is applied to medium and high power level for normal scales; and DC-DC Vdd-hopping converter is used in low-power technology for micro-scales or nano-scales. Likewise, conversions are DC-to-DC, and DC-to-AC. The DC-AC converter is based on the switched-mode classical topology, as is the boost inverter; and the DC-DC converter has a topology far from the common structures. The complexity of the systems are quite different, from a 1<sup>st</sup>-order model in the DC-DC converter to a 4<sup>th</sup>-order. Table 1.1 summarizes these differences.

That does not mean that these two applications completely cover all power converter domain. In fact, there are other features that have not been taken into account, as is the different natural- or forced-commuted characteristic, the input sources, the level of the output signal, among others.

These two converter applications, as for its work context as for its different characteristics, have some different control objectives.

#### 1.3.1 Controlling a boost inverter

The first application is focused on controlling an SMPC boost inverter. This converter is particularly interesting because it does not only allow to generate an alternating current, but it can also obtain an output voltage larger than the input signal. It has a high efficiency due to its switching character. Nevertheless, it has a non-minimum phase, 4<sup>th</sup>-order model. In addition, the desired behavior is not an equilibrium point but a limit cycle.

Due to all the mentioned boost inverter characteristics, the main objective is to design a control law that guarantees not only the convergence to the desired limit cycle, but also the stability of it, with the particularity that no external reference is applied to the system. Likewise, the system has to accomplish right performance not only for known loads, but also for unknown loads. Another important aim is to estimate a set of initial voltage and current values, for which the system variables tend to the desired limit cycles when the control law before is applied to the boost inverter.

If all these objectives are achieved, a control system guarantees a stable and robust behavior from an initial condition, which is within an estimated attraction region. And, in addition, the system is autonomous in the sense that no reference signals are needed.

### 1.3.2 Controlling a DC-DC Vdd-hopping converters

This is a low-power converter with a high-efficiency. Furthermore, it has nice properties, for instance, it has a 1<sup>st</sup>-order and its control objective is an equilibrium. Nevertheless, in low-power technology, this level of efficiency may not become enough if certain requirements are demanded (e.g. high energy-efficiency, small current peaks and reduced space) to achieve a certain objective. For this, to design a control law focused on achieving an optimal energy-efficiency may be an attractive control problem in order to reach this objective. Indeed, the control problem of the Vdd-Hopping converter in this thesis comes directly demanded by the industry. Concretely, it is included in a French national project called ARAVIS, sponsored by the global competitive cluster Minalogic<sup>1</sup>.

The main control objective of this converter is to guarantee that the system reaches the desired equilibrium point, achieving certain required features as: high-efficiency, stability, low computational cost, robustness with respect to parameter uncertainties and robustness with respect to delays due to synchronization and computation issues [45]. In this way, the control law must be designed taken these objectives into account.

<sup>&</sup>lt;sup>1</sup>http://www.minalogic.com/

8 1.4. Thesis structure

#### 1.4 Thesis structure

This thesis, as is noted above, is composed of two parts. Part I covers Chapters 2 to 5 while Part II covers Chapter 6 to 10. Conclusions are drawn in Chapter 11.

The first part deals with controlling the boost inverter. In Chapter 2, the model of the double boost converter (boost inverter) is presented. Likewise, the objectives are specified in details, just as a particular solution is proposed in order to resolve the raised problem. Chapter 3 shows the general idea of producing oscillating behavior by means of the generation of a limit cycle through energy shaping. This idea yields a controller for the boost inverter, but it is shown that the behavior is not acceptable due to a lack of synchronization. Therefore, a phase controller is added to achieve the synchronization of an isolated boost inverter as well as the synchronization of the boost inverter with a pre-specified signal. Chapter 4 deals with the unknown-load case, which is solved by means of an adaptation mechanism design. A stability analysis for the full-system is also studied by using singular perturbation analysis. Chapter 5 is devoted to develop a method of estimating an attraction domain. This method deals with control and state constraints. It is employed to provide an estimated attraction domain for the boost inverter.

The second part of the thesis is focused on controlling the DC-DC Vdd-Hopping converter. In Chapter 6, a summary of the ARAVIS project work context, where this research is included, is performed. Likewise, the control objectives required for this DC-DC converter in the ARAVIS project are defined. In Chapter 7, a set of controllers are presented and discussed. From the control solution that offers the best performance, a controller is developed in order to achieve the control objectives. For this, optimal control theory as well as adaptation methods are applied. Nevertheless, it has an important drawback, its implementation is not simple, thus it is not suitable in the ARAVIS project. Next, another controller is developed in Chapter 8. This proposed control solution is developed from the simplest control implementation of the set of controllers presented in Chapter 7. This controller presents good properties for the project. In Chapter 9, a rigorous stability analysis is developed for the closed-loop system with this last controller. Chapter 10 presents an optimal tuning mechanism for the control constants in order to deal with delays and parameter uncertainties. This development copes with resolving a  $H_{\infty}$  problem, proposing some Linear Matrix Inequalities (LMIs) developed from Lyapunov Krasovskii method.

# Part I

**Controlling a DC-AC Boost Converter**

# Chapter 2

# Introduction

DC-DC power converters have a very large presence in all kind of electronic circuits, from industrial applications (spacecraft power systems, DC motor drives, telecommunication equipment) to personal applications (PCs, office equipment, electrical appliance). These systems provide a regulated DC voltage level  $(V_o)$  from an unregulated DC voltage level  $(V_{in})$ .

High efficiency is the most important requirement for DC-DC converters in a wide range of load power, since it directly affects the battery lifetime [42]. It can be achieved using 'switched-mode'. A switched-mode power converter (SMPC) is characterized by rapidly switching on and off some devices, transferring a rate of energy from the input to the output. This rate of energy is controlled by a duty cycle<sup>1</sup> to minimize the dissipated energy. The switching effect is achieved by transistors, which dissipates little power when it is outside of its active region. In addition, SMPCs have an inductor, whose main function is to limit the current slew rate through the power switch. This action help to limit the otherwise high peak current. Moreover, the inductor stores the energy, which can be recovered in the discharge phase [43,118]. This approach is also used in alternating current (AC) applications.

The basic components of the switching circuit can be rearranged to form a:

- 1. **Buck converter.** It is a step-down: the output voltage is lower than the input voltage.

- 2. **Boost converter.** It is a step-up: the output voltage is larger than the input voltage.

- 3. **Buck-boost converter.** It can be a step-down or a step-up. Its main characteristic is that it inverts the polarity of the voltage.

- 4. **Cuk converter.** It has the same features that a buck-boost converter, with other different configuration.

<sup>&</sup>lt;sup>1</sup>Duty cycle is the fraction of time that a system is operated.

12 2.1. Boost inverter

5. **SEPIC converter.** It can be a step-down or a step-up, but it does not invert the voltage polarity.

From these topologies other converters can be obtained [96, 100].

A buck or boost topology, by oneself, can not achieve alternating current. Physical reasons prevent the output current signal from passing through zero. Hence, some topologies have been proposed in order to obtain the alternating current condition.

Traditionally, DC-AC converters (or inverters) are based on the buck topology. Nevertheless, this kind of configurations obtain an AC output voltage lower in amplitude than the input voltage [90]. In applications that require a boosting output, this problem is solved by using two-stages. One-stage to change the signal from DC to AC, and the other stage, to raise the amplitude [121]. These topologies have the drawback of needing more space and dissipating more energy since they use more components.

In [25], a new inverter was proposed composed of two boost converter. It is known as boost inverter. This inverter has as main advantage that it generates an AC output voltage from a lower DC voltage in a single stage. As side effect, it has a higher efficiency and a better signal quality with respect to the traditional buck inverters [126, 147]. These nice properties are only achieved with a suitable controller. Hence, to design an appropriate control law has an important relevance for these kind of circuits.

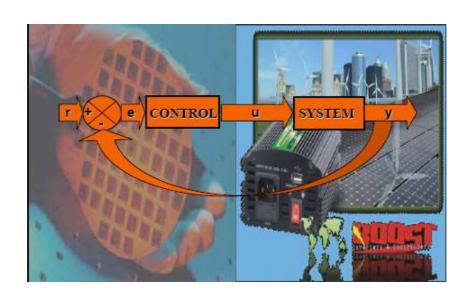

The boost inverter may be used in diverse applications, as for example in photovoltaic system market. The solar cells can charge a battery up with a DC voltage of 48V. When they are used in domestic installations, a standard domestic AC power is required as power supply [15, 29]. Therefore, a boost inverter provides in these kind of applications a better benefit. Its structure allows to isolate as well as to increase the voltage. Moreover, it ensures that the power conversion is done with reduced energy losses [3, 4]. Figure 2.1 represents a domestic photovoltaic installation.

#### 2.1 Boost inverter

A boost circuit is usually employed as a DC-DC converter, being especially interesting because it generates an output voltage larger than its input voltage, i.e., it is a voltage elevator. In [46, 48], there is a proposition of using this boost circuit as a way to convert DC voltage into an oscillating voltage. However, alternating current cannot be generated with this converter, since the output current cannot change its sign. For this, an inverter is yielded by duplicating the boost circuit [25].

Figure 2.1: Domestic photovoltaic installation.

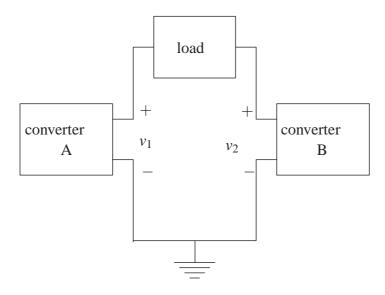

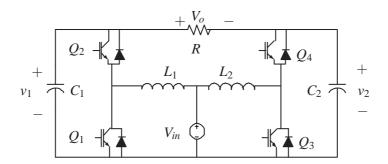

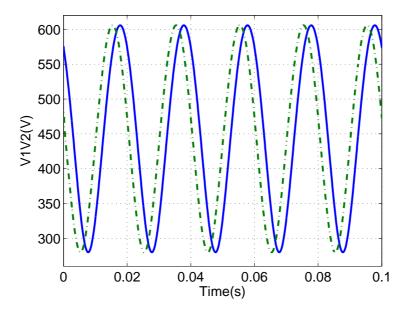

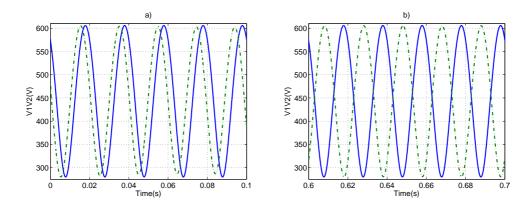

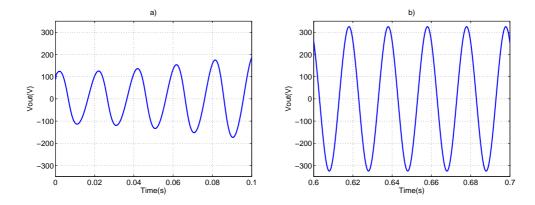

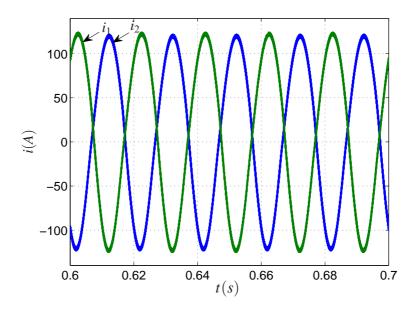

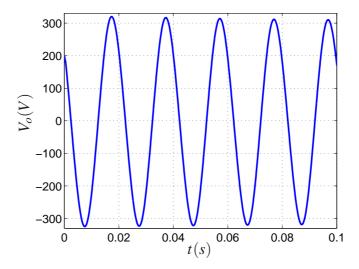

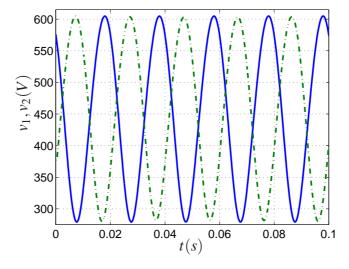

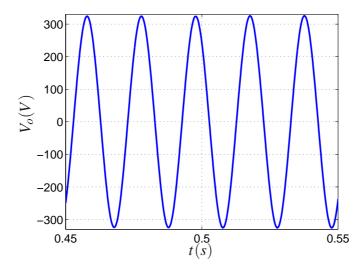

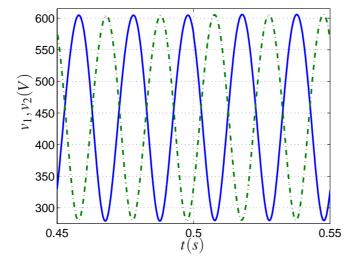

The boost inverter is made up of two DC-DC converters<sup>2</sup> and a load connected differentially across them, having a bidirectional current (see Fig. 2.2). Each converter produces a DC-biased sine wave output,  $v_1$  and  $v_2$ , so that each source generates a unipolar voltage. Voltages  $v_1$  and  $v_2$  should present a phase shift equal to  $180^\circ$ , to maximize the voltage excursion across the load. In this way, to generate an oscillatory signal without bias is possible. The circuit implementation is shown in Fig. 2.3.

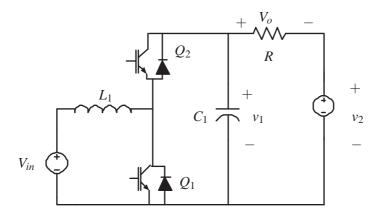

In order to simplify the analysis, a part of the boost inverter is replaced by a constant voltage source as is shown in Fig. 2.4. Once the desired results are obtained, they are extrapolated to the full inverter. Note that, this replacement shows more clearly the bidirectional current of each boost DC-DC converter.

### 2.1.1 System description

Now, some assumptions about the boost inverter are presented.

Assume that:

<sup>&</sup>lt;sup>2</sup>Throughout this part of the thesis, each part of the boost inverter will be referred as 'boost DC-DC converter' since each part is a normal boost converter that is commonly used as a DC-DC converter. Nevertheless, it should be taken into account that, in the boost inverter, each part does not act as a DC-DC converter.

14 2.1. Boost inverter

Figure 2.2: Basic representation of the boost inverter.

Figure 2.3: Boost inverter model.

Figure 2.4: Boost inverter model with replacement of a voltage source.

- all the components are ideal and the currents of the converter are continuous,

- the power supply is constant and known,

- the converter operates at a high-switching frequency,

- the inductances  $L_1 = L_2$ , and the capacitances  $C_1 = C_2$ , are known and symmetric,

- $v_1$  and  $v_2$  are positive and sinusoidal voltages.

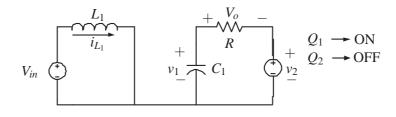

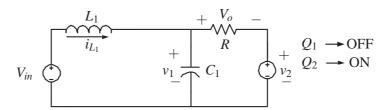

The circuit shown in Fig. 2.4 is driven by the transistor ON/OFF inputs,  $Q_i$ . This yields two modes of operation illustrated in Fig. 2.5. Formally, this circuit generates a switched model. For control purposes, it is common to use an average model described in terms of the mean current and voltage levels [97]. This averaging process may reach an averaged, smooth, nonlinear, continuous-time ordinary differential equation (ODE), as will be seen below.

Figure 2.5: Operation modes.

If the control variable, q, is defined as q = 0 when  $Q_1 = \text{OFF}$  and  $Q_2 = \text{ON}$ , and q = 1, when  $Q_1 = \text{ON}$  and  $Q_2 = \text{OFF}$ , the converter dynamic equations are

$$L_1 \frac{di_{L_1}}{dt} = -v_1 + qv_1 + V_{in} (2.1)$$

$$C_1 \frac{dv_1}{dt} = i_{L_1} - qi_{L_1} - \frac{v_1}{R} + \frac{v_2}{R}.$$

(2.2)

Now,  $\underline{u}_1 = 1 - q$  is taken as the control action in equations (2.1)–(2.2); obtaining

$$L_1 \frac{di_{L_1}}{dt} = -\underline{u}_1 v_1 + V_{in} \tag{2.3}$$

$$C_1 \frac{dv_1}{dt} = \underline{u}_1 i_{L_1} - \frac{v_1}{R} + \frac{v_2}{R},\tag{2.4}$$

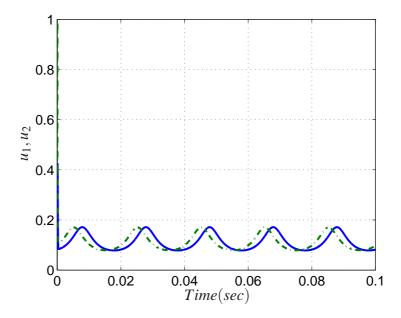

where  $\underline{u}_1$  is the control variable, which can only take two values  $\underline{u}_1 \in \{0,1\}$ . However, it is usual to consider its average value  $u_1(t) = \frac{1}{T} \int_t^{T+t} \underline{u}_1(s) ds$  where T is the switching period [97]. Therefore,  $u_1$  is a continuous variable defined as  $u_1 \in [0,1]$ .

The full inverter structure according to Fig. 2.3 is

$$L_1 \frac{di_{L_1}}{dt} = -u_1 v_1 + V_{in} (2.5)$$

$$C_1 \frac{dv_1}{dt} = u_1 i_{L_1} - \frac{v_1}{R} + \frac{v_2}{R}$$

(2.6)

$$L_2 \frac{di_{L_2}}{dt} = -u_2 v_2 + V_{in} (2.7)$$

$$C_2 \frac{dv_2}{dt} = u_2 i_{L_2} + \frac{v_1}{R} - \frac{v_2}{R},\tag{2.8}$$

where  $u_2$  controls the other part of the full system (remember that this part has been replaced by a constant voltage source).

The main difficulty of system (2.5)–(2.8) copes with its control, because of:

- system nonlinearities. The control signals multiply the state variables. This kind of system are more difficult to study [76].

- The linear part of system (2.5)–(2.8) is nonminimum phase because it has poles in the positive semiplane. Therefore, it is not stable in open-loop [131].

- It is 4<sup>th</sup> order, which is a relatively high order.

- The current signal is indirectly controlled. An alternating current signal can be achieved by a suited control-law that controls the voltage output [48].

- A phase shift of 180° is not necessarily achieved. In order to reach a right performance with this inverter, both voltages signals must present this phase shift [25].

- Boost inverter is a double oscillator, thus it does not present two equilibrium points but two limit cycles.

- The control law variables are saturated because of duty-cycle signals [25].

- Loads in this kind of systems are unknown or/and slowly variable [63].

### 2.2 Control problem objectives

As mentioned before, the main objective for the boost inverter is to generate alternating current. Hence, it can produce an oscillating voltage centered around zero, and thus, it can

achieve negative voltages. Its main drawback, however, is its control due to the complexity of the system structure.

The general control objectives for the boost inverter, which are common in switching electronics converters, are:

- 1. to generate a stable output voltage with an amplitude equal to the desired voltage. Furthermore, in certain applications, it is required that the output voltage has a prespecified phase;

- 2. to ensure the performance for unknown or/and slowly variable loads;

- 3. in the case that the control law does not guarantee global stability, to study an attraction domain composed of all initial conditions that ensure a convergency to the system right performance. This estimation of the region of attraction is important for the design of the starting phase.

In this thesis, these general objectives can be achieved for a particular solution made up of some proposed specific objectives:

- 1. to design a suitable control law for the duty cycle by using energy shaping, without introducing reference signals;

- 2. to achieve an anti-synchronization<sup>3</sup> between the voltage signals of each side of the circuit;

- 3. to propose an adaptive control to deal with unknown and/or slowly varying loads and,

- 4. to estimate an attraction domain for the resulting system.

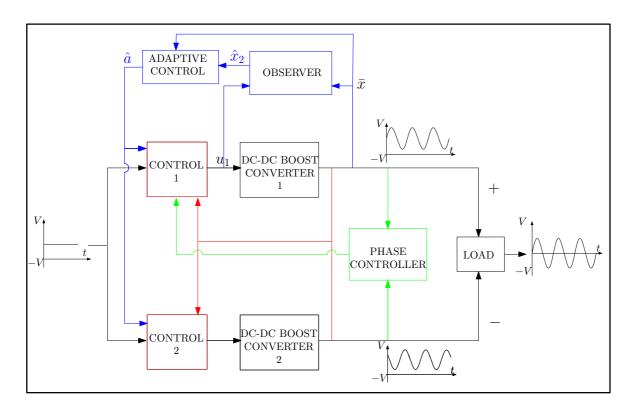

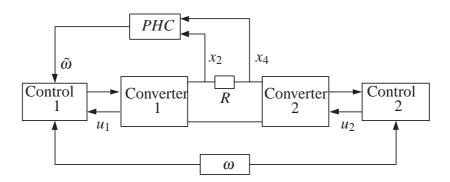

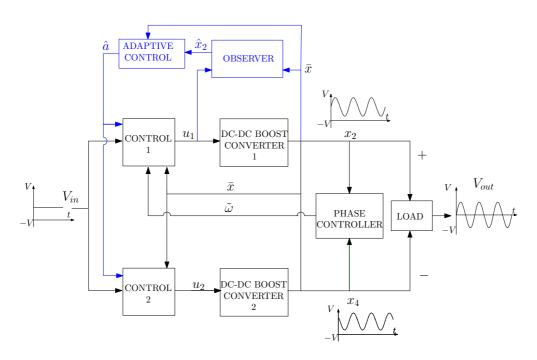

Figure 2.6 shows a block diagram of the solution proposed in this thesis for the boost inverter control problem. Note that the user has to specify the desired amplitude and frequency of the output voltage, as well as that the initial conditions belong to an estimated attraction domain to ensure the system convergency.

#### 2.2.1 Control law

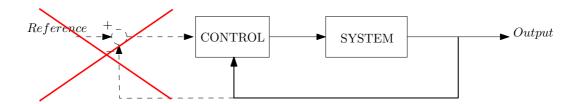

The control of switched-mode inverter is usually accomplished by tracking a reference (sinusoidal) signal [20,35,126,150]. The use of this external signal makes the closed-loop system

$<sup>^3</sup>$ In this thesis it is said that two sinusoidal signals of the same frequency are anti-synchronized, or in antiphase, when the phase shift between them is equal to  $180^\circ$ .

**Figure 2.6**: General control problem.

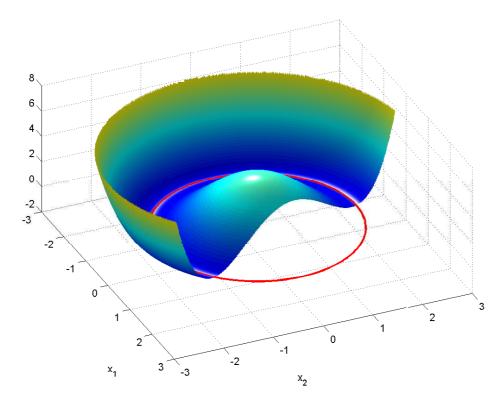

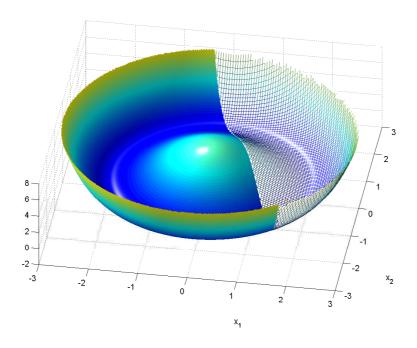

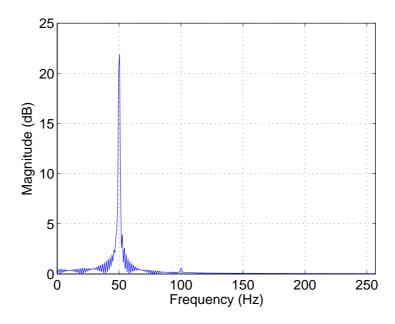

non-autonomous in such a way that its analysis is more involved than if it were autonomous. In these kind of systems, the control objective can be seen as the generation of a stable limit cycle defined by a given amplitude and frequency. Figure 2.7 shows the control objective, which corresponds to the valley of a certain surface with a 'Mexican-hat' shape [115]. If a control law is able to produce such a limit cycle, alternating current will be generated without the need to introduce a time-dependent reference signal. The generation of limit cycles to produce self-oscillations has been successfully applied to electro-mechanical systems [56, 57]. Applications to electronic devices are [16, 58], where a three-phase UPS and a boost converter are controlled using this method. The idea behind [19, 73] is similar but there a sliding mode controller is proposed.

In Chapter 3, this approach is applied to a nonlinear boost inverter [11]. Several approaches have been applied to control this topology of inverter. For instance, in [25, 126], sliding mode method is applied and, in [148], the control is based on passivity. Nevertheless, these methods need a reference signal.

Therefore, the main contribution in this part of the thesis is to control the boost inverter without using any reference signal, i.e., the system becomes autonomous [24, 150]. Figure 2.8 shows the autonomous structure that replaces the standard feedback control loop. This is a sub-control problem, since both current and voltage signals are controlled by the same control variable.

Figure 2.7: Desired energy function: Mexican-hat shape.

Figure 2.8: Autonomous feedback control loop.

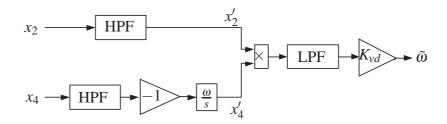

It is shown that the direct application of the approach proposed in [16] and [58] does not fulfill the objective due to the lack of anti-synchronization between both parts of the circuit. In order to achieve anti-synchronization, a phase controller (PHC) in an external loop is added to the previous control law. This approach is also applied to synchronize<sup>4</sup> the output with a given signal. An example of such a configuration is the synchronization of the boost inverter with the electrical grid (as in the photovoltaic case) in order to achieve a satisfactory power factor, which is shown in Fig. 2.6.

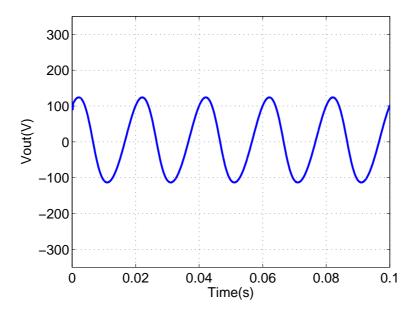

The circuit performance is validated in the simulation of a practical case presented in this chapter.

Previous results were extended to the case that the load is not purely resistive but it is inductive, as is usually the case in industrial applications. In [10], the extension to the controller based on energy shaping method considering an inductive load was presented, taking also into account the PHC.

### 2.2.2 Adaptive control

Previously, a control law satisfying previous requirements was designed in Chapter 3. It has been supposed that the load is known and constant. However, it is well known in industrial applications that the load can be unknown or suffer perturbations. This problem in switched-mode converters is usually dealt with by using adaptation mechanisms along with other techniques such as feedback stabilization [63], input-output feedback linearization [64], backstepping [123, 135], grid-point modeled [102], sliding modes [28, 134, 145], predictive control [94] or fuzzy logic control [40]. In [108], an adaptive control is obtained for a part of the DC-DC boost converter, which is controlled using the oscillation generation approach mentioned before. This adaptive controller is computed using passivity arguments. This approach is not easily applicable to the boost inverter because its model is more involved than the converter of [108].

In Chapter 4, the goal is to design a load-adaptation mechanism for the boost inverter controlled by energy shaping methodology. In order to estimate the load, a state observer is designed for any system variable even when the state variables are measured (Fig. 2.6). This provides a fast, successful adaptation of the load parameter [7]. This approach is applied by simulation to a real industrial case.

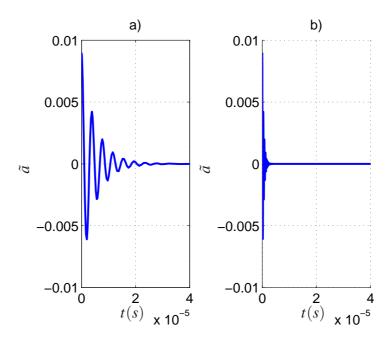

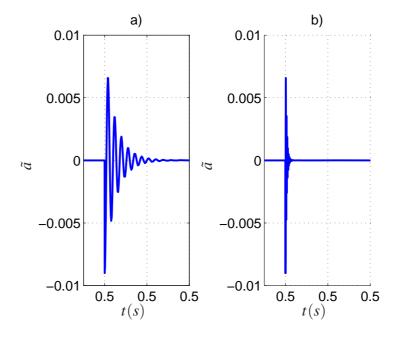

The stability of the full system is analyzed by singular perturbation analysis, [76,78]. For the sake of simplicity, the phase controller is not considered in this analysis. The resulting adaptive control is tested by simulations.

$<sup>^4</sup>$ In this thesis it is said that two sinusoidal signals of the same frequency are synchronized when the phase shift between them is equal to  $0^{\circ}$ .

The extension to case of unknown and non-purely resistive load using the adaptation mechanism before is published in [12]. In this application two parameters of the load are adapted at the same time.

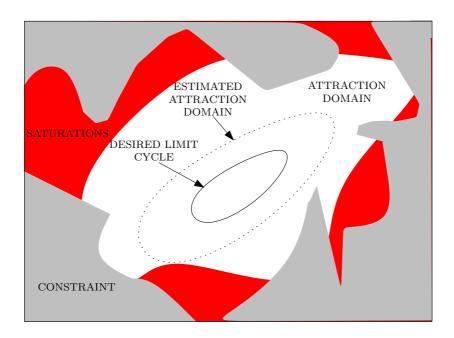

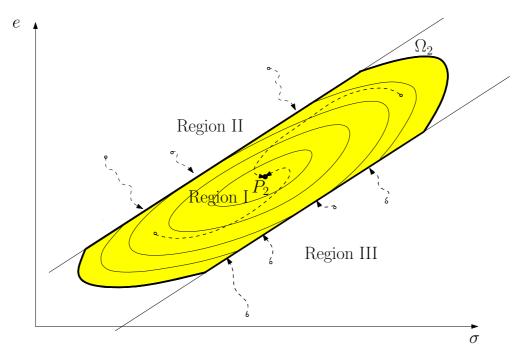

### 2.2.3 Attraction domain

In Chapter 3, a control law for the boost inverter is designed satisfying its main objectives. Ideally, the designed control law guarantees global stability by means of a Lyapunov function. In practice, however, the control law does not achieve global stability due to two reasons: firstly, the ideal control signal cannot be implemented globally due to control signal saturation; and secondly, the circuit imposes physical constraints on certain state variables: the capacitor voltages, for example, cannot be negative. Consequently, it is necessary to estimate an attraction region for the boost inverter. This attraction region is composed of all initial conditions of the system that guarantee the convergency to the right behavior. There is a starting phase, which is very common in this kind of systems [13, 91, 156], that must bring the state of the system into a point inside this region. The attraction domain estimation problem presents several difficulties. The main drawback is the complexity of the control law, which is a rational function with a high degree polynomial numerator. Moreover, it is necessary to highlight that the desired behavior does not correspond to an equilibrium point but to a limit cycle. Therefore, to obtain an estimated attraction domain for the boost inverter can be quite involved.

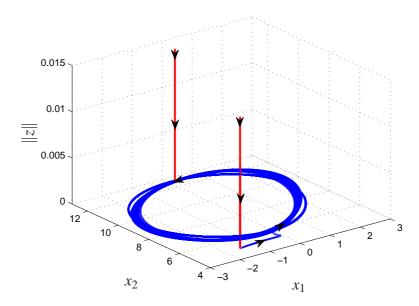

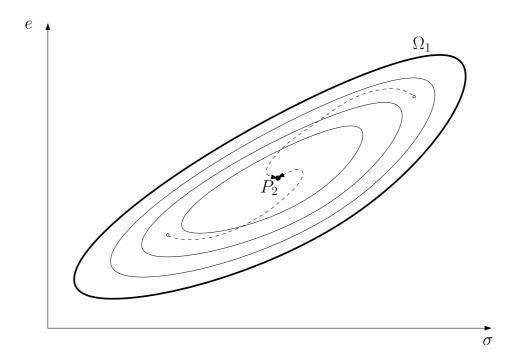

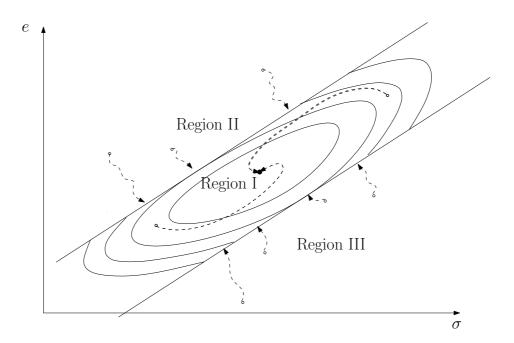

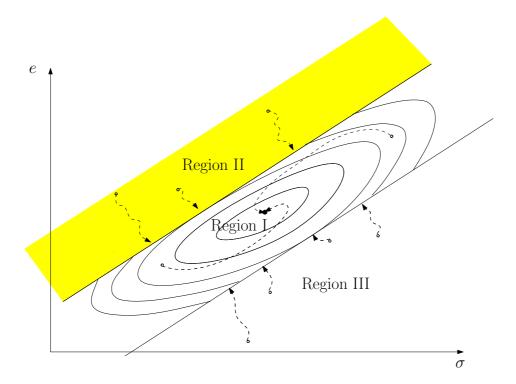

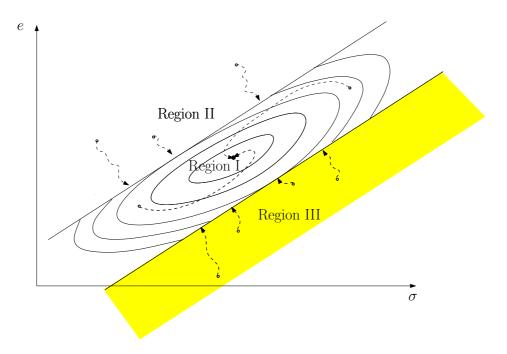

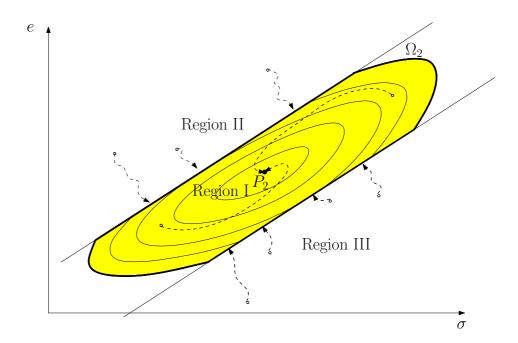

There exist many published methods to estimate the region of attraction (see, for example [54, 76] and the references therein). One example of this kind of methods is based on Lyapunov theory, in which closed Lyapunov-function level surfaces are employed to determine approximate sort of 'conservative' estimations for the region of attraction [76] (see Fig. 2.9). These methods often employ polynomial systems [85, 124, 146].

Chapter 5 presents a method of estimating an attraction domain, considering state and control-signal constraints. This approach can be applied to a class of system, whose local system stability was previously guaranteed by a Lyapunov function, as is the problem proposed here. By means of employing this Lyapunov function to estimate a 'conservative' attraction domain, a simple computational approach can be generated, although the model and/or control law have a relative high degree and complexity. In order to apply the method, the closed-loop system must be in a polynomial form, in such a way that the problem is transformed in a sum of squares (SOS) optimization problem [117].

This method is applied to estimate an attraction domain for the boost inverter. It is remarked, that the computed attraction region obtained from this Lyapunov function considers physical system constraints, containing control law saturations. The application of this method is very simple and satisfactory results are obtained.

Figure 2.9: System attraction domain with constraints.

# **Chapter 3**

# Control of the DC-AC boost converter by energy shaping

This chapter exposes a novel control strategy for nonlinear boost inverter. Boost inverter is nonminimum phase  $4^{th}$  order nonlinear system, which has not an equilibrium point but a limit cycle. The control objective is not only to obtain a right system performance, but also to guaranty the system stability. In addition, it is necessary to mention that it is a sub-control problem. The control law has to control voltage as well as current signal.

The idea behind is based on generating an autonomous stable oscillator. The interesting advantage of this method is that an external reference signal is not needed. This aim is achieved by using energy-shaping methodology with a suitable Hamiltonian function which defines the desired system behavior [44]. This approach guaranties the system stability.

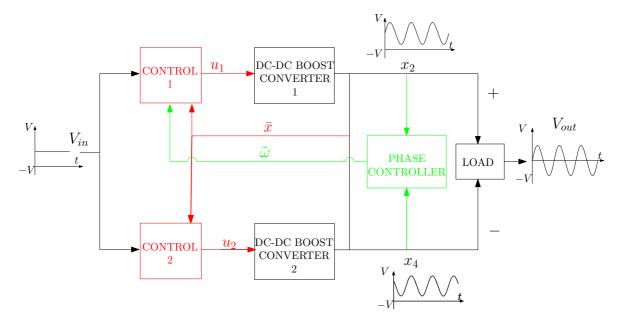

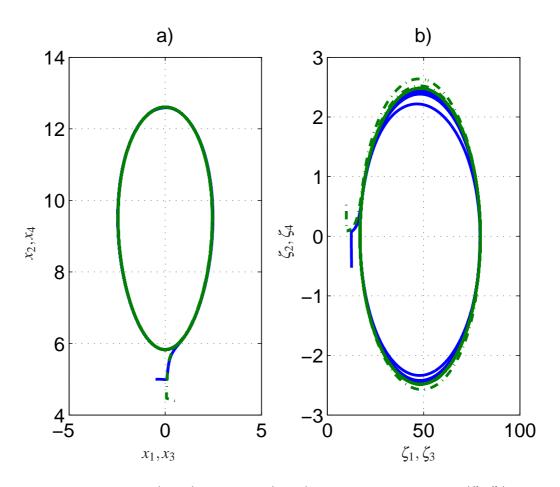

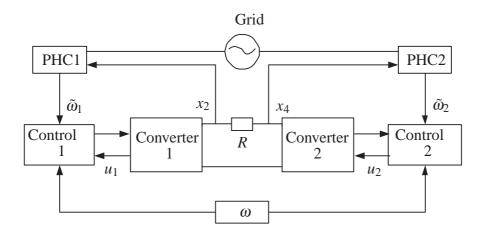

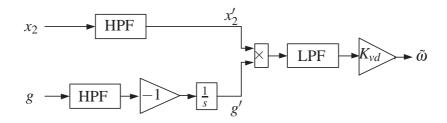

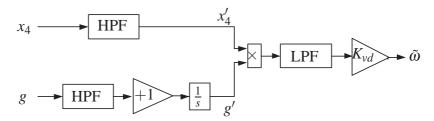

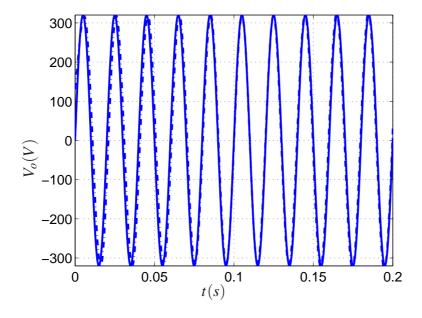

The only missed thing in the developed controller is to synchronize the voltage signals with a phase shift of 180°. This is important in order to obtain the desired response. For this, a phase controller is added to the control law in order to achieve 180°-synchronization between both parts of the circuit, as is shown in Fig. 3.1. In addition, this idea is used to synchronize the voltage output with a pre-specified signal, e.g. synchronization with the electrical grid. The resulting control is tested by means of simulations.

# 3.1 Normalized average model

Assume system (2.3)–(2.4) is only subject to a resistive load. In order to simplify the control study, a known change of variable is employed [18, 133], in order to achieve a normalize

Figure 3.1: Controlled boost inverter with PHC.

model:

$$x_{1} = \frac{1}{V_{in}} \sqrt{\frac{L_{1}}{C_{1}}} i_{L_{1}}$$

$$x_{2} = \frac{v_{1}}{V_{in}}$$

(3.1)

$$x_2 = \frac{v_1}{V_{in}} \tag{3.2}$$

$$x_3 = \frac{1}{V_{in}} \sqrt{\frac{L_1}{C_1}} i_{L_2} \tag{3.3}$$

$$x_4 = \frac{v_2}{V_{in}} \tag{3.4}$$

where  $x_1$  and  $x_3$  are the averaged currents and  $x_2$  and  $x_4$  are the averaged voltages. The normalized time scale is

$$\tilde{t} = \omega_n t \tag{3.5}$$

with

$$\omega_n = \frac{1}{\sqrt{L_1 C_1}},\tag{3.6}$$

which yields

$$\dot{x}_1 = -u_1 x_2 + 1 \tag{3.7}$$

$$\dot{x}_2 = u_1 x_1 - a x_2 + a x_4, \tag{3.8}$$

$$\dot{x}_3 = -u_2 x_4 + 1 \tag{3.9}$$

$$\dot{x}_4 = u_2 x_3 + a x_2 - a x_4, \tag{3.10}$$

where  $a = \frac{1}{R} \sqrt{\frac{L_1}{C_1}}$ . Note that  $\omega_n$  is the natural frequency and a is twice the damping.

**Remark 3.1**  $\dot{x}_1$ ,  $\dot{x}_2$ ,  $\dot{x}_3$  and  $\dot{x}_4$  are time derivatives of  $x_1$ ,  $x_2$ ,  $x_3$  and  $x_4$ , respectively, with respect to  $\tilde{t}$ .

As mentioned in the chapitre before, for simplicity, the simplified boost inverter (2.3)–(2.4) is dealt with and, later, the results are extrapolated to the full system.

Focussing on the simplified system. If  $u_1$  is eliminated in (3.7)–(3.8), next equation is obtained

$$x_1(1-\dot{x}_1) = x_2(\dot{x}_2 + ax_2 - ax_4). \tag{3.11}$$

This equation is an implicit equation, which relates the state variables  $(x_2, x_4)$  and their time derivatives and does not depend on the control signal u. Note that  $x_4$  can be considered an exogenous input in system (3.7)–(3.8). Equation (3.11) can be understood as the internal dynamic of the system. If  $\dot{x}_1 = 0$  and  $\dot{x}_2 = 0$  is performed, the equilibrium manifold is  $x_1 = ax_2(x_2 - x_4)$ . In this way, the internal dynamic of system (3.7)–(3.8) given by (3.11) acts as a constraint on the system states.

From Eq. (3.11), it is possible to see that given  $x_4$ , and only controlling  $x_1$ , variable  $x_2$  can be indirectly controlled<sup>1</sup>. Moreover, the stability of the system is maintained [48].

# 3.2 Energy shaping control for generation of oscillations

# 3.2.1 Approach overview

The generation of alternating current in electronic converters can be achieved by generating a stable limit cycle without the need to introduce a reference signal. To do this, an oscillatory target system may be defined and by matching its equations and system equations (3.7)–(3.8) a control law can be obtained. In order to define the target system, consider the following energy-like function

$$H_0(\eta_1, \eta_2) = \frac{1}{4} \Gamma_1^2(\eta_1, \eta_2),$$

(3.12)

where  $\eta_1$  and  $\eta_2$  are state variables and  $\Gamma_1(\eta_1, \eta_2) \triangleq \omega^2(\eta_1 - \eta_{10})^2 + (\eta_2 - \eta_{20})^2 - \mu$ . Parameters  $\omega$ ,  $\eta_{10}$ ,  $\eta_{20}$  and  $\mu > 0$  should be chosen so that the closed curve  $\Gamma_1 = 0$  defines the desired behavior. This curve is an ellipse centered at point  $(\eta_{10}, \eta_{20})$ . A dynamical system can be defined such that this closed curve is its limit set. This can be reached by

<sup>&</sup>lt;sup>1</sup>For the full system, it is had:  $x_1(1-\dot{x}_1)=x_2(\dot{x}_2+a(x_2-x_4))$  and  $x_3(1-\dot{x}_3)=x_4(\dot{x}_4+a(x_4-x_2))$ . Thus, controlling  $x_1$  and  $x_3$ , the desired behaviors for  $x_2$  and  $x_4$  can be obtained.

adopting  $H_0$  as a Hamiltonian function [16, 108], and defining the Hamiltonian dynamical system

$$\begin{bmatrix} \dot{\eta}_1 \\ \dot{\eta}_2 \end{bmatrix} = \begin{bmatrix} -k_{a_1} & \frac{1}{\Gamma_1} \\ -\frac{1}{\Gamma_1} & -k_{a_2} \end{bmatrix} \begin{bmatrix} \frac{\partial H_0}{\partial \eta_1} \\ \frac{\partial H_0}{\partial \eta_2} \end{bmatrix}, \tag{3.13}$$

which, after using (3.12), results in

$$\dot{\eta}_1 = (\eta_2 - \eta_{20}) - k_{a_1} \omega^2 (\eta_1 - \eta_{10}) \Gamma_1 \tag{3.14}$$

$$\dot{\eta}_2 = -\omega^2(\eta_1 - \eta_{10}) - k_{a_2}(\eta_2 - \eta_{20})\Gamma_1. \tag{3.15}$$

Taking into account that

$$\dot{H}_0 = -\Gamma_1^2 \left( k_{a_1} \omega^4 (\eta_1 - \eta_{10})^2 + k_{a_2} (\eta_2 - \eta_{20})^2 \right) \le 0, \tag{3.16}$$

by using the LaSalle invariance principle it can be seen that, for all initial conditions except the center of the ellipse, the trajectories of the system tend to the curve  $\Gamma_1 = 0$ . Figure 3.2 shows this energy-like function.

**Figure 3.2**: Desired energy function: mexican-hat.

The behavior of the target system ( $\Gamma_1 = 0$ ) corresponds to the desired sinusoidal behavior for the DC-AC converter. Constants  $\omega$ ,  $\eta_{10}$ ,  $\eta_{20}$  and  $\mu$  are design parameters for the frequency, bias and amplitude of the desired behavior, while  $k_{a_1}$  and  $k_{a_2}$  define the speed of the transient response.

Note that  $\dot{\eta}_1$  and  $\dot{\eta}_2$  are in this case time derivatives of  $\eta_1$  and  $\eta_2$  with respect to  $\tilde{t}$ , in order to work with the normalized averaged model (3.7)–(3.8).

### 3.2.2 Controller design

System (3.7)–(3.8) can not be directly transformed to the form of system (3.14)–(3.15), but this can be done using the new change of coordinates given below:

$$\zeta_1 = \frac{x_1^2 + x_2^2}{2} \tag{3.17}$$

$$\zeta_2 = x_1 - ax_2^2 + ax_2x_4 + \zeta_{20} \tag{3.18}$$

where  $\zeta_{20}$  is an offset term that will be a tuning parameter. From (3.17)–(3.18), it is easy to see that

$$\dot{\zeta}_1 = \zeta_2 - \zeta_{20} \tag{3.19}$$

$$\dot{\zeta}_2 = 1 + 2a^2x_2^2 - 3a^2x_4x_2 + a^2x_4^2 + ax_2\dot{x}_4 - u_1(x_2 + 2ax_1x_2 - ax_4x_1). \tag{3.20}$$

It is not easy to obtain simple relationships  $x_1 = f(\zeta_1, \zeta_2)$  and  $x_2 = f(\zeta_3, \zeta_4)$  from (3.17)–(3.18) due to the quadratic terms. Nevertheless, this change of variables is a diffeomorphism if and only if  $x_2 + 2ax_1x_2 - ax_4x_1 \neq 0$ , as follows from the inverse function theorem. In Chapter 5 it will be seen that this constraint restricts the domain of attraction of the desired limit cycle when the controller obtained below is applied.

Looking at target system structure (3.14)–(3.15) and comparing it with (3.19)–(3.20) the choice  $k_{a_1} = 0$  is obvious, resulting in the target system

$$\dot{\zeta}_1 = \zeta_2 - \zeta_{20} \tag{3.21}$$

$$\dot{\zeta}_2 = -\omega^2(\zeta_1 - \zeta_{10}) - k_1 \Gamma_1(\zeta_2 - \zeta_{20}), \tag{3.22}$$

where, for sake of simplicity,  $k_{a_2}$  has been denoted as  $k_1$ . The attraction of curve  $\Gamma = 0$  can still be proved by the LaSalle invariance principle.

The control law, u, that matches (3.19)–(3.20) and (3.21)–(3.22) is

$$u_1 = \frac{1 + 2a^2x_2^2 - 3a^2x_4x_2 + a^2x_4^2 + ax_2\dot{x}_4 + k_1\Gamma_1(\zeta_2 - \zeta_{20}) + \omega^2(\zeta_1 - \zeta_{10})}{x_2 + 2ax_1x_2 - ax_4x_1}.$$

(3.23)

Indeed,  $u_1$  varies dependently on x, as can be noted from Eq. (3.17)– (3.18). This controller has several problems. First, the denominator in (3.23) may be zero (this is the same necessary condition for (3.19)–(3.20) to be a diffeomorphism). Furthermore, in other cases, the resulting  $u_1$  can violate the constraint  $0 \le u_1 \le 1$ . In Chapter 5, an estimation for the region of attraction of the desired limit cycle will be obtained by taking these problems into account. It is assumed that a starting strategy will bring the state of the system into this region of attraction [13,91,156].

Parameters  $\eta_{10}$ ,  $\eta_{20}$  and  $\mu$  have to be defined as a function of the desired behavior. For this, it is necessary to obtain an analytical expression of the desired objective curve in plane  $x_1 - x_2$ . Assume that the desired time evolutions for  $x_2$  and  $x_4$  are

$$x_2^* = A\sin\omega t + B \tag{3.24}$$

$$x_4^* = -A\sin\omega t + B, (3.25)$$

where A, B and  $\omega$  take pre-specified values to obtain the desired evolution for  $v_1$  and  $i_{L_1}$  using (3.1)–(3.4), (3.5) and (3.6). In addition, note that these desired evolutions allow us to remove the bias in the output. The origin of time in (3.24)–(3.25) is arbitrary in such a way that no phase shift value is imposed (signal synchronization will be achieved below). Assume that the desired steady state for  $x_1$  can be approximated by

$$x_1^* = a\alpha_0 + \alpha_1 \cos \omega t + \beta_1 \sin \omega t \tag{3.26}$$

This assumption is very common in the field of electronics [20, 37, 48, 60].

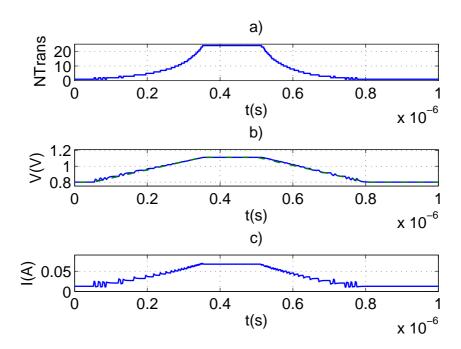

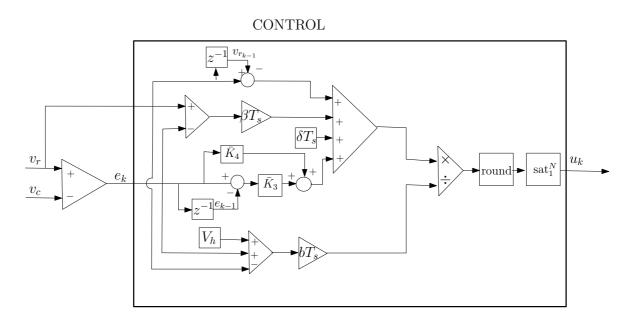

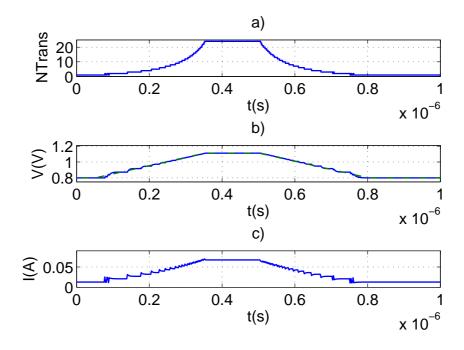

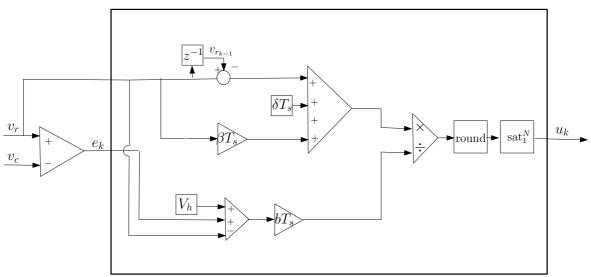

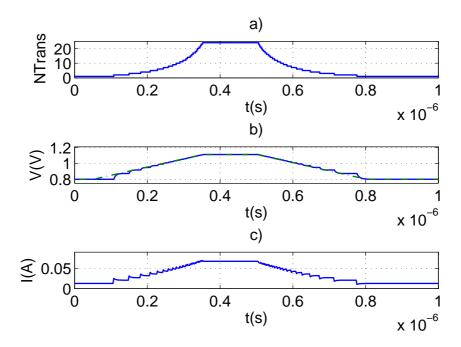

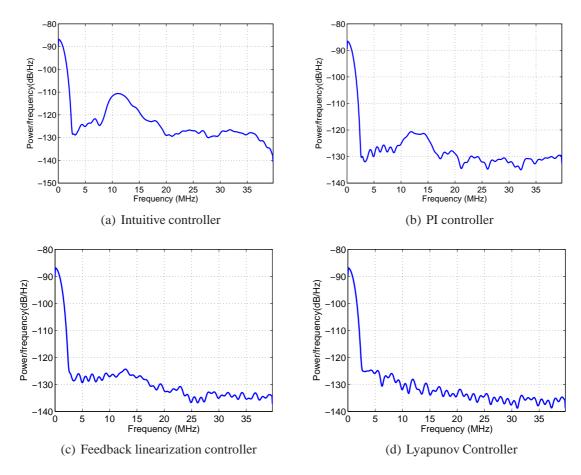

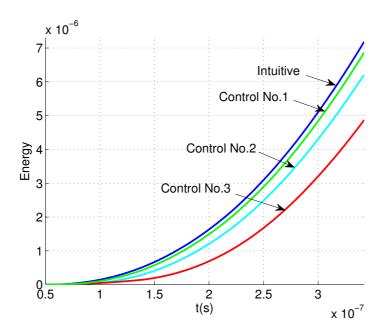

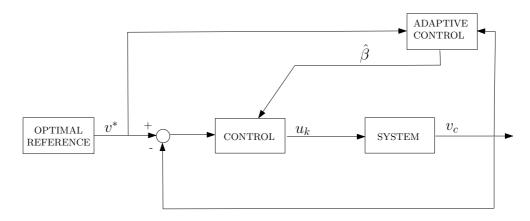

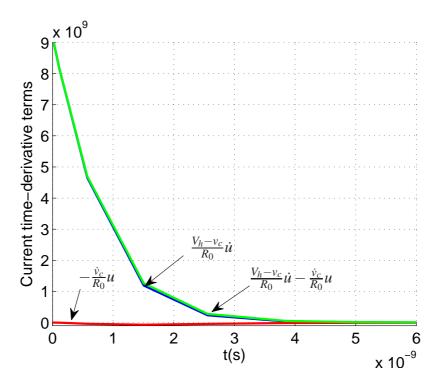

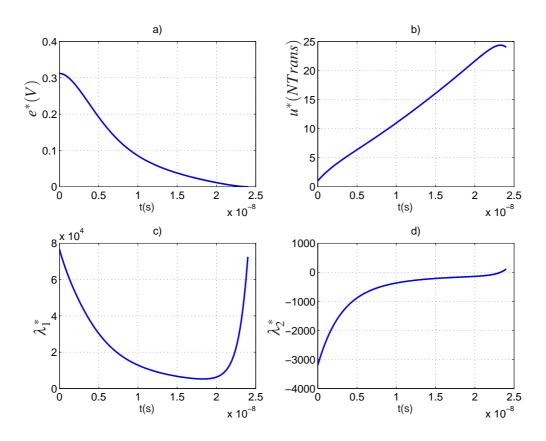

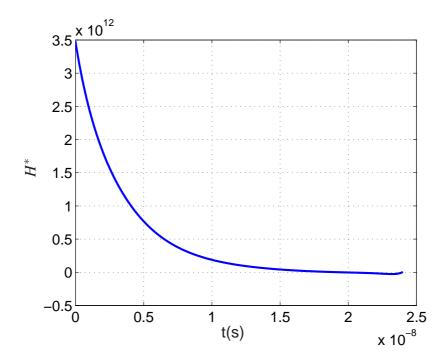

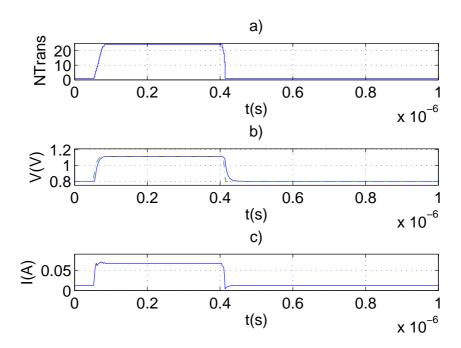

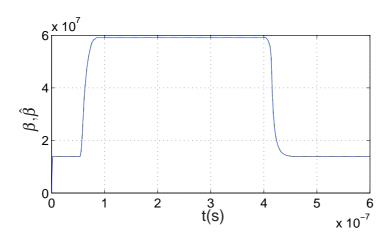

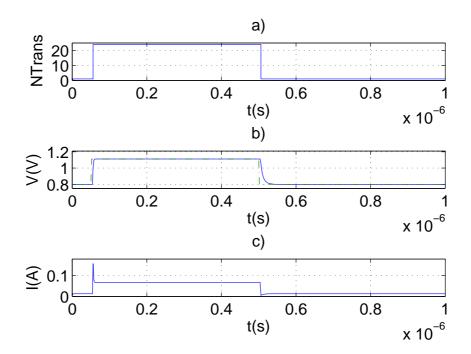

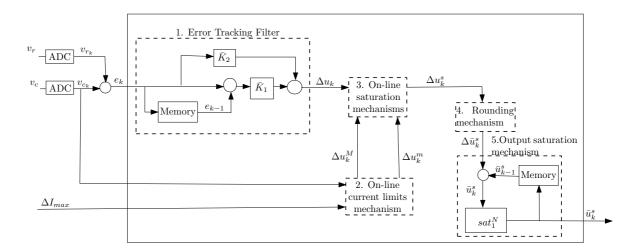

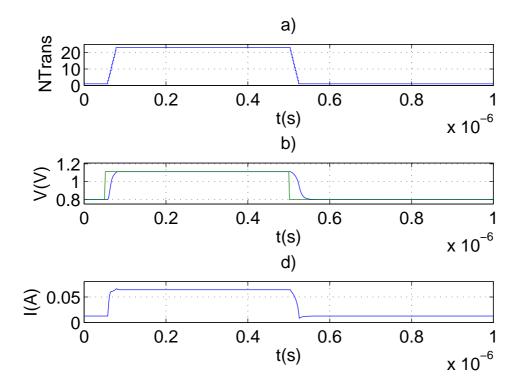

By substituting (3.24)–(3.25) and (3.26) in (3.11)