# 42, A Component-Based Approach to Virtual Prototyping of Heterogeneous Embedded Systems

Tayeb Bouhadiba

### ▶ To cite this version:

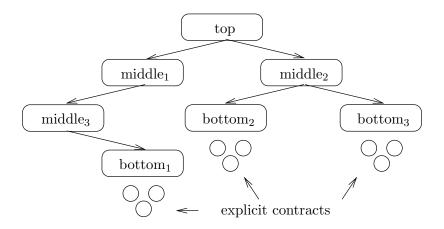

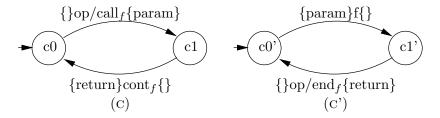

Tayeb Bouhadiba. 42, A Component-Based Approach to Virtual Prototyping of Heterogeneous Embedded Systems. Computer Science [cs]. Institut National Polytechnique de Grenoble - INPG, 2010. English. NNT: . tel-00539648

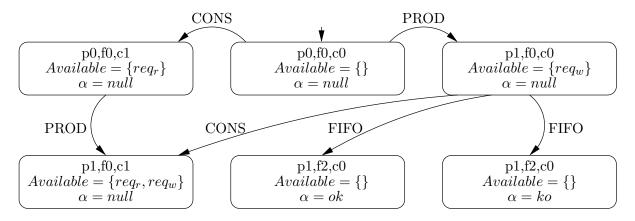

## HAL Id: tel-00539648 https://theses.hal.science/tel-00539648v1

Submitted on 24 Nov 2010

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

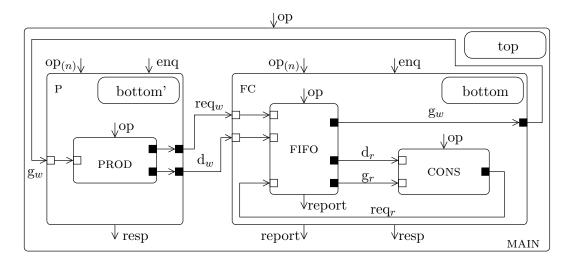

#### UNIVERSITE DE GRENOBLE

| No | a | ttr | ibı | ıé | pai | r la | a b | ibl | iot | hè | que |

|----|---|-----|-----|----|-----|------|-----|-----|-----|----|-----|

|    |   |     |     |    |     |      |     |     |     |    |     |

|    |   |     |     |    |     |      |     |     |     |    |     |

#### THESE

pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITE DE GRENOBLE

Spécialité : Informatique

préparée au Laboratoire VERIMAG

dans le cadre de l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

présentée et soutenue publiquement

par

### Tayeb Sofiane BOUHADIBA

le 15 Septembre 2010

# 42, Une Approche à Composants pour le Prototypage Virtuel des Systèmes Embarqués Hétérogènes

42, A Component-Based Approach to Virtual Prototyping of Heterogeneous Embedded Systems

Directrice de thèse: Florence MARANINCHI

JURY:

Marc Pouzet Pr. **ENS Paris** Rapporteur et Président Lionel Seinturier Pr. Université de Lille Rapporteur Jean-Bernard Stefani INRIA Rhône-Alpes D.RExaminateur Florence Maraninchi Pr. Grenoble INP Directrice de thèse

# REMERCIEMENTS

Les travaux qui sont présentés dans cette thèse n'auraient pu être possible sans l'aide de plusieurs personnes. Ne pouvant citer tout le monde, je tiens à remercier tous ceux qui ont contribué, de près ou de loin à l'aboutissement de cette thèse.

Je tiens en particulier à remercier ma directrice de thèse Florence MARANINCHI pour son encadrement, ses précieux conseils, pour tout ce que j'ai pu apprendre au travers des  $42^{\infty}$  discussions et pour m'avoir permis de développer mes idées.

C'est un honneur pour moi que Marc Pouzet, Lionel Seinturier et Jean-Bernard Stefani aient accepté de faire partie de mon jury de thèse. Un grand merci à eux pour avoir sacrifié un moment précieux de leur temps afin de lire et juger ma thèse.

Je remercie aussi les membres de l'équipe Synchrone du laboratoire Verimag. Leur disponibilité pour répondre à mes multiples questions m'ont beaucoup aidé à approfondir ma culture dans divers domaines. Une mention spéciale pour les membres du Bureau N°9, les anciens et les nouveaux.

Je reste reconnaissant à tout ceux qui ont pris le temps de relire (un bout de) ma thèse pour me rapporter des erreurs ou des correctifs. 42milles merci à Florence, David, Stéphane, Giovanni, Thomas, Kevin, Matthieu, Nicolas, Julien, Selma, Sophie, Laurie et tous ceux que j'ai pu oublié.

Il ne faut pas oublier l'ensemble du personnel administratif, merci à toute l'équipe qui entoure Christine pour leur travail remarquable. Aussi, un grand merci pour notre administrateur système Jean-Nöel (alias  $\mathbf{root}$ ) qui veille à maintenir le système au point, et qui m'a souvent rattrapé le paralysant rm -rf \*.

Je remercie encore les membres du laboratoire Verimag avec qui j'ai eu le plaisir de partager beaucoup d'activités extra-scientifiques, que ce soit pour prendre un café, faire ski, jouer au foot

Je ne peux pas oublier mes amis et cousins Ahmed, Amine(s), Chicho, Farah, Farid, Hichem, Kader, Khaled, Tamtam,... pour le temps d'un petit coup de fil, d'une discussion, d'une escapade ou d'une partie de PES. Les moments que j'ai partagé avec eux sont inoubliables et m'ont beaucoup aidé a tenir le coup.

Enfin, je pense que je ne serais pas arrivé là sans l'aide précieuse de ma famille côté BOUHADIBA, BOUKBIR et BENBERNOU. Un grand merci à mes parents pour m'avoir toujours soutenu durant mes études et m'avoir offert la possibilité de continuer et d'aller aussi loin. Merci à vous Sosso, Radia et Imène, les coups de fil et visites de mes sœurs m'ont toujours apporté un énorme réconfort.

Enfin, je terminerai mes remerciements par celle qui partage ma vie. Merci à toi Ismahène pour le soutien que tu m'a apporté durant cette thèse et pour avoir partagé les moments difficiles par lesquels j'ai pu passé.

# Contents

| 1' | Intr         | roduct                                         | ion (In French)                                        | 9  |  |  |  |  |

|----|--------------|------------------------------------------------|--------------------------------------------------------|----|--|--|--|--|

| 1  | Introduction |                                                |                                                        |    |  |  |  |  |

|    | 1.1          | 1 Embedded Systems and Their Development Cycle |                                                        |    |  |  |  |  |

|    | 1.2          | Comp                                           | onent-based Virtual Prototyping and Challenges         | 16 |  |  |  |  |

|    | 1.3          | Summ                                           | nary of the Contributions                              | 17 |  |  |  |  |

|    | 1.4          | Outlin                                         | ne                                                     | 17 |  |  |  |  |

| 2  | Bac          | kgrou                                          | $\mathbf{nd}$                                          | 19 |  |  |  |  |

|    | 2.1          | Model                                          | ls of Computation for Discrete Concurrent Systems      | 20 |  |  |  |  |

|    |              | 2.1.1                                          | Synchronous Models and Languages                       | 20 |  |  |  |  |

|    |              | 2.1.2                                          | Asynchronous Models                                    | 25 |  |  |  |  |

|    | 2.2          | Virtua                                         | al Prototypes of HW Platforms for SW Development       | 27 |  |  |  |  |

|    |              | 2.2.1                                          | Modeling Hardware Platforms                            | 27 |  |  |  |  |

|    |              | 2.2.2                                          | Executing Embedded SW on a Virtual Prototype of the HW | 30 |  |  |  |  |

|    | 2.3          | Comp                                           | onents and Contracts                                   | 32 |  |  |  |  |

|    |              | 2.3.1                                          | Components                                             | 32 |  |  |  |  |

|    |              | 2.3.2                                          | Specifying Components                                  | 33 |  |  |  |  |

|    |              | 2.3.3                                          | Design By Contract                                     | 34 |  |  |  |  |

|    | 2.4          | Valida                                         | ation                                                  | 35 |  |  |  |  |

|    |              | 2.4.1                                          | Formal Specification of Properties                     | 35 |  |  |  |  |

|    |              | 2.4.2                                          | Validation by Simulation                               | 36 |  |  |  |  |

|    |              | 2.4.3                                          | Runtime Verification                                   | 36 |  |  |  |  |

|    |              | 2.4.4                                          | Static Verification                                    | 36 |  |  |  |  |

| 3  | Ove          | erview                                         | of the 42 Model                                        | 39 |  |  |  |  |

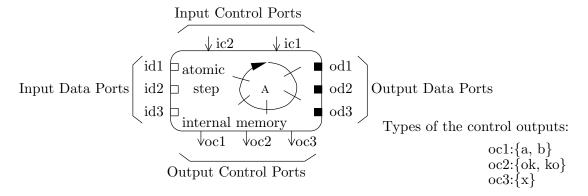

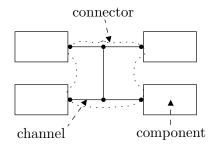

|    | 3.1          | Basic                                          | Elements of the 42 Model                               | 40 |  |  |  |  |

|    |              | 3.1.1                                          | Basic Components                                       | 40 |  |  |  |  |

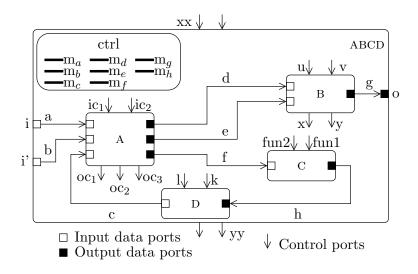

|    |              | 3.1.2                                          | Composed Components                                    | 42 |  |  |  |  |

|   |     | 3.1.3                     | Discussion on the Memory Associated with the 42 Model  | 45   |  |  |  |  |  |  |

|---|-----|---------------------------|--------------------------------------------------------|------|--|--|--|--|--|--|

|   | 3.2 | Specif                    | ying Components                                        | 46   |  |  |  |  |  |  |

|   |     | 3.2.1                     | Implicit Specifications                                | 47   |  |  |  |  |  |  |

|   |     | 3.2.2                     | Explicit Specifications: Rich Control Contracts for 42 | 47   |  |  |  |  |  |  |

|   |     | 3.2.3                     | Components Introspection                               | 50   |  |  |  |  |  |  |

|   | 3.3 | Consis                    | stency Issues                                          | 51   |  |  |  |  |  |  |

|   | 3.4 | Using                     | the 42 Modeling Approach                               | 52   |  |  |  |  |  |  |

|   |     | 3.4.1                     | Reasoning on Components with the 42 Model              | 52   |  |  |  |  |  |  |

|   |     | 3.4.2                     | Main Usage of 42 Control Contracts                     | 53   |  |  |  |  |  |  |

|   | 3.5 | Imple                     | mentation                                              | 55   |  |  |  |  |  |  |

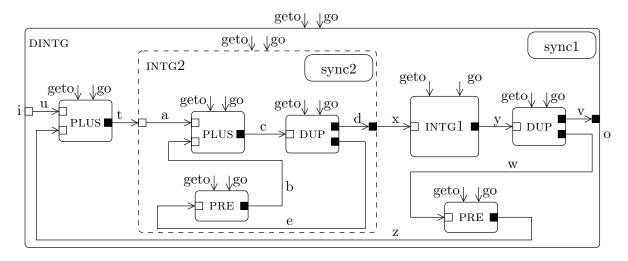

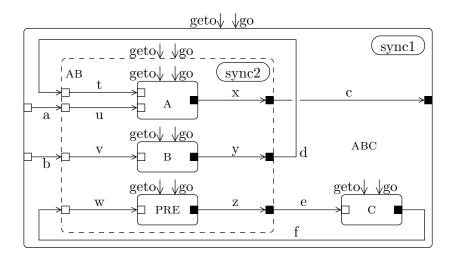

| 4 | Mo  | deling                    | Examples with 42 Components                            | 57   |  |  |  |  |  |  |

|   | 4.1 | Exam                      | ples with Implicit Specifications                      | 58   |  |  |  |  |  |  |

|   |     | 4.1.1                     | Mono-Clock Synchronous Programs or Circuits            | . 58 |  |  |  |  |  |  |

|   |     | 4.1.2                     | Simulation of Asynchronous Systems                     | 64   |  |  |  |  |  |  |

|   |     | 4.1.3                     | Hardware/Software Modeling                             | 67   |  |  |  |  |  |  |

|   |     | 4.1.4                     | Kahn Process Networks                                  | 70   |  |  |  |  |  |  |

|   |     | 4.1.5                     | Globally Asynchronous Locally Synchronous Systems      | 72   |  |  |  |  |  |  |

|   | 4.2 | Exam                      | ples with Explicit Contracts                           | 75   |  |  |  |  |  |  |

|   |     | 4.2.1                     | Mono-Clock Synchronous Programs or Circuits            | 75   |  |  |  |  |  |  |

|   |     | 4.2.2                     | Multi-Cycle Synchronous Programs or Circuits           | 79   |  |  |  |  |  |  |

|   |     | 4.2.3                     | Using Contracts to Describe Asynchronous Systems       | 85   |  |  |  |  |  |  |

| 5 | For | Formal Definition of 42 9 |                                                        |      |  |  |  |  |  |  |

|   | 5.1 | Comp                      | onents and Composing Components                        | 92   |  |  |  |  |  |  |

|   |     | 5.1.1                     | Components and the Architecture Description Language   | 92   |  |  |  |  |  |  |

|   |     | 5.1.2                     | Controllers                                            | 93   |  |  |  |  |  |  |

|   |     | 5.1.3                     | Combining Components                                   | 93   |  |  |  |  |  |  |

|   | 5.2 | 42 Co                     | ntrol Contracts                                        | 95   |  |  |  |  |  |  |

|   |     | 5.2.1                     | Original Form of Control Contracts                     | 95   |  |  |  |  |  |  |

|   |     | 5.2.2                     | Expanded Form of Control Contracts                     | 96   |  |  |  |  |  |  |

|   |     | 5.2.3                     | The Master/Slave Relation                              | 97   |  |  |  |  |  |  |

|   | 5.3 | Forma                     | al Definition of Consistency                           | 98   |  |  |  |  |  |  |

|   |     | 5.3.1                     | Contracts Vs Basic Components                          | 98   |  |  |  |  |  |  |

|   |     | 5.3.2                     | Contracts Vs Controllers                               | 99   |  |  |  |  |  |  |

| 6 | Exp | oloiting                  | g 42 Control Contracts                                 | 103  |  |  |  |  |  |  |

|   | 6.1 | Contr                  | acts and Consistency Checking                                 | 103 |

|---|-----|------------------------|---------------------------------------------------------------|-----|

|   |     | 6.1.1                  | Checking Component Implementation                             | L04 |

|   |     | 6.1.2                  | Checking Controller Micro-steps                               | 105 |

|   | 6.2 | Dedu                   | icing the Controller from the Contracts                       | 105 |

|   |     | 6.2.1                  | Static Code Generation for Synchronous Controllers            | 106 |

|   |     | 6.2.2                  | Asynchronous Simulation Controllers as Contracts Interpreters | L07 |

| 7 | Har | $\operatorname{dware}$ | e Simulation and Software Execution 1                         | 19  |

|   | 7.1 | Proto                  | typing Hardware Using 42                                      | 120 |

|   |     | 7.1.1                  | An Example System-on-a-Chip                                   | 120 |

|   |     | 7.1.2                  | Modeling the Hardware Architecture with 42                    | 122 |

|   |     | 7.1.3                  | Contract-Based Simulation                                     | 125 |

|   | 7.2 | Softwa                 | are Execution                                                 | 126 |

|   |     | 7.2.1                  | Using Wrappers for Hardware/Software Simulation               | 126 |

|   |     | 7.2.2                  | Checking Software Implementation                              | 129 |

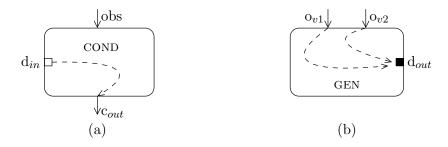

|   | 7.3 | Forma                  | alizing SystemC-TLM with 42 Components                        | 130 |

|   |     | 7.3.1                  | Structural Correspondence Between 42 and SystemC              | 132 |

|   |     | 7.3.2                  | Executable Contracts For SystemC-TLM Components               | 133 |

|   |     | 7.3.3                  | Typical Uses of the Approach                                  | 135 |

|   |     | 7.3.4                  | Comments                                                      | l41 |

| 8 | Rel | ated V                 | Vork 1                                                        | 43  |

|   | 8.1 | Comp                   | onent Models and MoCCs                                        | 144 |

|   |     | 8.1.1                  | Ptolemy                                                       | 144 |

|   |     | 8.1.2                  | General Discussions on Design and Expressiveness of Models    | 147 |

|   |     | 8.1.3                  | Reactive Modules                                              | 148 |

|   |     | 8.1.4                  | An Academic Approach to Software Components: Fractal          | 150 |

|   |     | 8.1.5                  | Coordination of Component Activities with Reo                 | 152 |

|   | 8.2 | Specif                 | fication Languages and Contracts                              | 153 |

|   |     | 8.2.1                  | Formal Specification of Behaviors                             | 153 |

|   |     | 8.2.2                  | Contracts for Hardware Components                             | 155 |

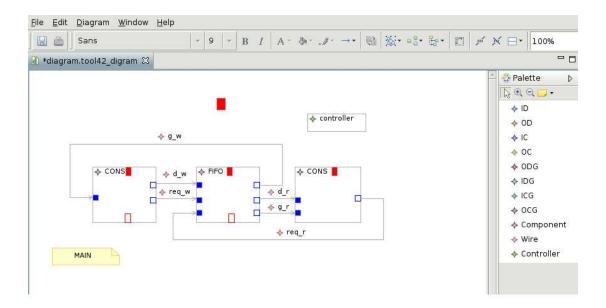

| 9 | АТ  | Tool fo                | r the 42 Component Model 1                                    | .57 |

|   | 9.1 | Writin                 | ng Components and Architectures                               | 158 |

|   |     | 9.1.1                  | Basic Components                                              | 158 |

|   |     | 9.1.2                  | Composed Components                                           | 160 |

|   |     | 9.1.3                  | Controllers                                                   | 160 |

|       | 9.1.4     | Contracts                             | . 161 |  |  |  |  |  |

|-------|-----------|---------------------------------------|-------|--|--|--|--|--|

| 9.2   | An Ex     | ecution Engine to Perform Simulations | . 161 |  |  |  |  |  |

|       | 9.2.1     | Instantiation of Systems              | . 162 |  |  |  |  |  |

|       | 9.2.2     | Simulation                            | . 163 |  |  |  |  |  |

|       | 9.2.3     | A Graphical Interface                 | . 163 |  |  |  |  |  |

| 10 Co | nclusio   | n & Prospects                         | 165   |  |  |  |  |  |

| 10.1  | 1 Summary |                                       |       |  |  |  |  |  |

|       | 10.1.1    | Contributions                         | . 165 |  |  |  |  |  |

| 10.2  | 2 Prospe  | $\operatorname{ects}$                 | . 166 |  |  |  |  |  |

|       | 10.2.1    | Semantical Aspects                    | . 166 |  |  |  |  |  |

|       | 10.2.2    | The Language of Control Contracts     | . 167 |  |  |  |  |  |

|       | 10.2.3    | Towards Non-Functional Properties     | . 167 |  |  |  |  |  |

| 10.3  | 8 Public  | eations Related to 42                 | . 168 |  |  |  |  |  |

| 10'Co | nclusio   | n & Perspectives (In French)          | 169   |  |  |  |  |  |

# Chapter 1'

# Introduction (In French)

### 1'.1 Les Systèmes Embarqués et leur Cycle de Développement

Les systèmes embarqués sont des systèmes informatiques omniprésents dans notre vie quotidienne. Les domaines où ils sont utilisés varient des systèmes critiques (avionique, centrales nucléaires, transport, etc.) à l'électronique grand publique (appareils photo, smartphones, etc.).

Comparés aux ordinateurs personnels, la particularité des systèmes embarqués réside dans leur architecture matérielle. En effet, l'architecture matérielle d'un système embarqué est souvent dédiée à celui-ci, et change d'une application à une autre. Les choix de conception du matériel sont guidés par la fonctionnalité du système, ainsi que par des propriétés non-fonctionnelles telle que la consommation en énergie.

Dans un système embarqué, les parties matérielles et logicielles sont fortement couplées. De ce fait, il est indispensable de les concevoir ensemble. Cependant, trouver une solution optimale pour de tels systèmes est difficile à cause des différents paramètres qui doivent être pris en compte (vitesse de calcul, consommation d'énergie, taille de la mémoire, surface disponible, etc.). Un autre paramètre à prendre en compte est la fabrication de la partie matérielle, qui est souvent disponible très tard dans le cycle de développement. En conséquence, la conception des système embarqués repose sur des techniques de *prototypage virtuel*.

Un prototype virtuel est un modèle exécutable d'un système. La modélisation nous permet d'étudier un système, très tôt, avant que le système ne soit disponible. En plus : 1) si le langage de spécification utilisé pour écrire les modèles est exécutable, nous pouvons observer le comportement du système réel en faisant des simulations ; 2) si les modèles sont formellement définis, nous avons la possibilité de vérifier quelques propriétés du système en appliquant les méthodes de validation formelle ; 3) le système final peut être généré automatiquement depuis son modèle ; cette technique est souvent appelée développement (conception, etc.) dirigés par les modèles.

Ecrire des modèles pour systèmes embarqués est parfois difficile. Une des causes de cette difficulté est l'hétérogénéité des systèmes embarqués: Ils sont composés de matériel et de logiciel ; le matériel peut contenir des composants analogiques et numériques ; les composants d'un système sont extrêmement concurrents, le modèle de concurrence peut varier du pure synchrone au pure asynchrone ; etc. En plus de l'hétérogénéité inhérente aux systèmes embarqués euxmême, une autre forme d'hétérogénéité apparaît dans le flot de conception : la conception de ces systèmes implique une expertise dans plusieurs domaines de l'ingénierie incluant l'électronique, l'automatique, l'informatique, etc. Dans chaque domaine, il existe une multitude d'outils et de formalismes pour répondre aux questions cruciales relatives à ce domaine. Chaque formalisme ou outil a ses propres notions pour modéliser les aspects relatifs à la concurrence, et le temps.

Pour palier à l'hétérogénéité des systèmes embarqués, un environnement de modélisation doit permettre la modélisation des composants hétérogènes du système. De plus, il doit permettre de décrire différents types de concurrence, de communication, de temps, de synchronisation, etc. Ces notions, sont définies par la notion de MoCC (Model of Computation and Communication).

Une autre notion relative aux travaux effectués dans cette thèse est celle des composants pour les systèmes embarqués. Les approches basées sur les composants ont fait leur apparition en réponse à la complexité croissante des systèmes embarqués et aux contraintes de temps de mise sur la marché. Dans l'industrie électronique (la partie matérielle), la notion de composants existe depuis bien longtemps. En effet, les IPs (Intellectual Properties) sont des composants électroniques prêts à l'usage. Ils sont vendus sous forme de composants physiques (prêts à être intégrés dans une plateforme matérielle), ou sous forme de spécifications synthétisables (doivent être intégrées durant le flot de conception). La notion de composant pour le matériel est assez générique grâce à l'adoption du MoCC universel pour les circuits synchrone.

Dans l'industrie du logiciel, les approches à composants sont nombreuses. Cependant, la notion de composant pour le logiciel n'est pas aussi générique que celle des composants pour le matériel. Ceci est dû à la multitude de *MoCCs* où ils peuvent être utilisés (threads, processus, programmes, programmation par événements, etc.)

### 1'.2 Le Prototypage par Composants et ses Challenges

Les questions qui ont motivées la définition du modèle 42 sont relatives à la notion de composants pour la modélisation et la simulation des systèmes embarqués hétérogènes, incluant les parties matérielles et logicielles. Les modèles pour le matériel sont intrinsèquement composants, du fait que le matériel est déjà partitionné en blocs. Pour le logiciel, plusieurs approches à composants ont été proposées. Cependant, un des challenges pour la modélisation des systèmes embarqués est de modéliser à la fois les composants matériels, les composants logiciels, ainsi que l'interaction entre eux, dans le même environnement.

Comme mentionné plus haut, une des utilisations possibles des modèles est de fournir un support pour la simulation. Plusieurs outils, qu'ils soient à usage académique ou industriel, ont été développés pour la simulation des systèmes embarqués. Ces outils ont montré leur efficacité à fournir des modèles de simulation de systèmes complexes comme les systèmes-sur-puce [Ghe06], réseaux-sur-puce [CCG+04], réseaux de capteurs [LFLL06], etc. De part notre expérience avec ces outils, nous somme arrivés à l'observation suivante : dans la plupart des outils, il existe une sorte de modèle à composants. Dans Ptolemy [EJL+03] par exemple, la notion de composants est claire et bien définie. Cependant, ce n'est pas le cas pour toutes les approches. Dans SystemC/TLM [Ghe06] par exemple, l'approche de modèlesation est clairement modulaire, mais elle ne repose que sur des directives de conception de modèles. De plus, la plupart des outils ne proposent pas de moyens pour réfléchir sur les modèles préalablement ; leur intérêt est de fournir des modèles de simulation. Un axe de recherche serait de définir un environnement de modélisation rigoureux, indépendant de tout langage ou formalisme existant, qui peut être utilisé conjointement avec les outils existants.

Cet environnement de modélisation doit adopter une approche par composants à cause de la complexité des systèmes à modéliser. Pour cela, il doit fournir une définition claire de ce qu'est un composant pour les systèmes embarqués, et doit appliquer le principe du FAMAPSAP (Forget As Much As Possible As Soon As Possible). Ce que nous entendons par FAMAPSAP est l'analyse systématique des détails qui peuvent être encapsulés et les détails qui doivent être exposé par un composant.

Pour récapituler, les challenges suivants ont motivé la définition de 42:

- fournir un environnement, indépendant de tout langage ou formalisme, pour la modélisation par composants de systèmes matériels/logiciels.

- fournir un support pour une définition claire de la notion de composants, et aider à appliquer le FAMAPSAP.

- fournir un support pour l'intégration de modèles existants, issus d'outils hétérogènes, dans un environnement de prototypage virtuel ouvert.

#### 1'.3 Résumé des Contributions

L'approche 42 est inspirée par Ptolemy : les système sont composés d'agents connectés entre eux pour échanger des données et un contrôleur pour déterminer ce qui se passe dans les connections, et comment les composants/agents sont activés. La grande différence avec Ptolemy est que les contrôleurs 42 sont décrits par des programmes utilisant un petit ensemble de primitives de base.

Nos contributions sont les suivantes :

- La définition (partiellement publiée dans [MB07]) d'une approche de modélisation basée sur les composants, ayant les propriétés suivantes : hiérarchie, indépendante de tout langage, spécification de composants en utilisant des contrats, exécutabilité des contrats, séparation du contrôle des données pour appliquer le principe du FAMAPASAP.

- Un ensemble assez riche d'exemples de modélisation pour montrer l'expressivité du modèle 42 pour la modélisation de différents *MoCCs* (voir chapitre 4).

- Un exemple de modélisation d'un système matériel/logiciel pour montrer l'utilisation des contrats 42 pour fournir des modèles de simulation de plateformes matérielles afin d'exécuter le logiciel embarqué (publié dans [BM09]).

- Un cas d'étude complet (publié dans [BMF09]) de l'utilisation de 42 avec des approches à composants existantes ; SystemC/TLM [Ghe06] dans notre exemple. L'exemple montre : l'intérêt de décrire des composants SystemC/TLM par des interfaces et contrats 42 ; la possibilité de générer de composants 42 depuis des langages existants ; la possibilité de simuler des systèmes décrits par des composants 42 et de composants SystemC/TLM.

- Un outil pour la conception est la simulation de modèles écrits en 42. Cet outil permet d'importer des composant existants issus d'autres approches, comme ça a été fait pour le cas de SystemC/TLM.

#### 1'.4 Plan de la Thèse

Le contenu de cette thèse est inspiré des publication autour de 42 [MB07, BM09, BMF09]. Il est organisé comme suit :

Le Chapitre 2 "Background" est un ensemble de notions de base et de pratiques existantes dans divers domaines, qu'ils soient relatifs aux systèmes embarqués en particulier ou au génie logiciel en général. La plupart des idées présentes dans 42 sont inspirées des ces notions et pratiques. Ce chapitre sert de référence pour détailler l'ensemble de ces idées. Dans le reste de thèse, à chaque fois où nous rencontrons une de ces notions, nous mettons un pointeurs vers la section qui la détaille dans ce chapitre.

Le Chapitre 3 "Overview" est un aperçu des éléments de base de 42. Ce chapitre introduit la notion de composants et les moyens de spécifications que nous proposons pour les décrire. Ces spécifications peuvent être implicites, explicites (i.e., les contrats de contrôle), ou un mixe

entre les deux. Ce chapitre inclut aussi une brève présentation de quelques points adressés par 42 qui seront détaillés dans les chapitres suivants.

Le Chapitre 4 "Modeling Examples with 42 Components" est composé d'une série d'exemples de modélisation. Il décrit des guidelines pour l'écriture des composants pour quelques MoCCs et comment ces MoCCs peuvent être décrits par des contrôleurs 42. Le chapitre est partagé en deux grandes sections : la première section regroupe les exemples où les composants sont associés à des spécifications implicites. Dans la deuxième section, nous montrons comment utiliser les contrats de contrôle pour donner des informations explicites sur le comportement des composants 42.

Le Chapitre 5 "Formal Definition of 42" présente une définition formelle de 42. Nous y décrivons formellement les composants 42, l'assemblage de composants, les contrats, etc. Dans ce chapitre, nous décrivons aussi les programmes des contrôleurs au travers d'une sémantique opérationnelle, qui nous permettra par la suite de déduire le comportement de composants composites du comportement de leurs sous-composants et les programmes associés au contrôleur. Ce chapitre traite aussi les différentes notions de compatibilités entre composants, contrats, et contrôleurs.

Le Chapitre 6 "Exploiting 42 Control Contracts" est un chapitre dédié à l'utilisation des contrats de contrôle pour décrire le comportement des composants 42. En particulier, il donne des exemples de MoCCs où les contrôleurs peuvent être déduits directement des informations fournies par les contrats des composants et les dépendances de données entre les composants.

Le Chapitre 7 "Hardware Simulation and Software Execution" regroupe deux cas d'étude complets de l'usage de 42 dans le contexte du prototypage virtuel des systèmes-surpuce. Dans un premier temps, nous montrons comment utiliser 42 pour écrire des prototypes virtuels de plateformes matérielles. Ces prototypes serviront par la suite de support pour le développement et l'exécution du logiciel embarqué. Le deuxième cas d'étude montre l'intérêt d'utiliser 42 conjointement avec des approches existantes. Nous avons choisi d'utiliser 42 avec SystemC/TLM vu que SystemC/TLM est l'un des standards dans l'industrie pour le prototypage virtuel des systèmes-sur-puce. L'intérêt de notre approche est de donner une description claire des composants TLM, ainsi que de fournir des modèles de simulation légers pour observer les synchronisations des composants TLM.

Le Chapitre 8 "Related Work" discute les choix que nous avons proposé pour 42 en comparaison aux approches qui existent déjà. Les approches décrites ne sont pas toutes dédiés aux systèmes embarqués. Pour chaque approche, nous donnons une brève présentation et nous discutons les similitudes et différences avec 42.

Le Chapitre 9 "A Tool for the 42 Component Model" décrit un outil que nous avons développé autour de 42. Cet outil implémente les éléments de base du modèle 42 et a permis de simuler l'intégralité des exemples qui sont présentés dans cette thèse.

Le Chapitre 10' "Conclusion & Prospects" conclut la thèse et présente quelques remarques et directions pour les travaux futurs autour de 42.

#### Suggestions pour le lecteur

- Le Chapitre 2, *Background*, décrit quelques notions et pratiques que le lecteur peut ne pas connaître. Vous pouvez ignorer ce chapitre dans le cas où vous connaissez déjà son contenu. Dan les autres chapitres, à chaque fois que nous avons besoin de détailler une des notions contenues dans le chapitre *Background*, un pointeur est mis vers la section concernées.

- Le Chapitre 3, *Overview*, doit être lu entièrement. Il donne un aperçu du modèle 42 et les éléments de base à retenir pour comprendre les exemples présentés dans la thèse.

- Si vous êtes intéressé, plus particulièrement par le MoCC synchrone, nous vous suggérons de lire la section 4.1.1 pour comprendre l'approche de modélisation des systèmes synchrones en 42. Ensuite, la section 4.2.1 pour comprendre comment les contrats sont utilisés pour décrire des composants synchrones. La section 4.2.2 présente la modélisation des systèmes synchrone multi-cycle. Enfin, la section 6.2.1 décrit comment générer des contrôleurs implémentant le MoCC synchrone depuis les contrats des composants.

- Si vous êtes intéressé, plus particulièrement par le MoCCs asynchrone, nous vous suggérons de lire la section 4.1.2 pour comprendre le principe de modélisation des MoCCs asynchrones en 42. Ensuite, la section 4.2.3 pour voir l'intérêt des contrats pour décrire les composants asynchrones. Enfin, la section 6.2.2 décrit la génération de contrôleurs implémentant des MoCCs asynchrones depuis les contrats des composants.

# Chapter 1

# Introduction

### 1.1 Embedded Systems and Their Development Cycle

Embedded systems are computer systems that are omnipresent in our everyday life. The domains where they may be used range from safety critical systems (avionics, nuclear plants, transportation, etc.) to consumer electronics (digital cameras, smartphones, etc.).

Compared to personal computer systems, the particularity of embedded systems lies in their hardware architecture. The hardware platform of embedded systems is often dedicated and differs from an application to another. The design choices of the hardware are guided by the functionality of the system and its required non-functional properties like energy consumption.

As hardware and software are tightly coupled, it is often unavoidable to design them together. However, finding an optimal solution is hard, because of the various parameters that should be taken into account, including computation speed, energy consumption, memory size, available surface, etc. Moreover, the hardware part may be available very late in the design cycle. Therefore, the design approach of embedded systems relies on *virtual prototyping*.

A virtual prototype is nothing more than an executable model of the embedded system. The use of models has numerous advantages: 1) When the specification language used for writing models is executable, one may predict the behavior of the future product by means of *simulations*; 2) When models are formally defined, there may be a possibility of asserting properties of the system by means of *formal validation*; 3) The final product may also be derived from the information provided by its model. This set of techniques is often referred to as *model-based development (design, etc.)*.

The difficulty of writing models comes from the intrinsic heterogeneity of embedded systems: they are composed of hardware and software, the hardware part may contain analog and digital circuits, the objects composing the systems are extremely concurrent and the concurrency model varies from pure synchrony to pure asynchrony, etc. In addition, heterogeneity appears during the design phase: the design of embedded systems involves some expertise from various domains including hardware engineering, control engineering, software engineering, etc. In each domain, there are several formalisms that answer crucial questions relevant to that domain. Each formalism has a proper understanding of the notions related to concurrency and timing aspects.

Hence, to cope with the heterogeneity of embedded systems, a modeling framework should encompass the modeling of the heterogeneous parts of a system. Moreover, it should be able to describe various types of concurrency models, communication mechanisms, timing aspects, synchronizations, etc. These notions are defined by the so-called *Model of Computation and Communication (MoCC)*.

Another important notion is that of *components* for the design of embedded systems. Because of the complexity of the systems and the increasing time-to-market constraints, component-based approaches have seen their emergence. In the hardware industry, the notion of component is relatively old. *Intellectual Properties (IPs)* are off-the-shelf hardware components bought as physical blocks (to be plugged directly in the hardware platform), or as synthesizable specifications (to be integrated during the design phase). The notion of component in the hardware domain benefits a lot from the universal MoCC of synchronous circuits.

On the other hand, component-based approaches in the software industry are numerous. However, the notion of components for software is less generic than that for hardware because of the variety of MoCCs in which they may be used (threads, processes, event-driven, programs, etc.).

### 1.2 Component-based Virtual Prototyping and Challenges

The questions that motivated the design of the 42 approach are related to the notion of components in the modeling and simulation of heterogeneous embedded systems, including hardware and software parts. The models of hardware are intrinsically component-based, they benefit a lot from the hardware partitioning as blocks. For software, numerous component-based modeling approaches were proposed. However, one of the challenges for modeling embedded systems lies in modeling hardware and software as well as their interactions in the same framework.

As already mentioned, one of the uses of models is to perform simulations. For that purpose, plenty of academic and industrial tools were designed. They showed their effectiveness in simulating complex systems such as systems-on-a-chip [Ghe06], networks-on-a-chip [CCG<sup>+</sup>04], sensor networks [LFLL06], etc. Our experience with these tools raised the following observation: in most the tools, there exist (some sort of) a component model. In Ptolemy [EJL<sup>+</sup>03] for instance, the notion of components is clear and well-defined. However, this is not the case for other approaches like SystemC/TLM [Ghe06], where the modeling approach is clearly modular but relies on guidelines. Moreover, the only purpose of these tools is simulation. They do not propose a means for reasoning on models beforehand. For that purpose, some work has to be done in order to define a rigorous modeling framework independent from any language and usable jointly with the existing tools.

Such a modeling framework should be component-based because of the complexity of the systems to be modeled. For that purpose, it should have a clear definition of the notion of components for embedded systems and should enforce the FAMAPASAP (Forget As Much As Possible As Soon As Possible) principle. It should provide tools for the systematic analysis of the details that can be hidden vs the details that must be exposed by a component.

To summarize, the following challenges motivated the design of 42:

- provide a language-independent component-based framework for modeling hardware/soft-ware systems.

- provide support for a clean definition of components, and help enforcing the FAMAPASAP principle.

- provide support for integration of existing modeling and simulation tools in open virtual prototyping environments.

### 1.3 Summary of the Contributions

42 is inspired by Ptolemy: systems are made of agents connected to each other for exchanging data, and a controller determines what happens on the connections, and how the components/agents are activated. The essential difference with Ptolemy is that the controller is described as little programs in terms of more basic primitives.

The main contributions are the following:

- The complete definition (partially published in [MB07]) of a component-based modeling approach with the following properties: hierarchy, language-independent, explicit specifications with contracts, executability of contracts, separation of control and data to enforce the FAMAPASAP principle.

- A rich suite of examples, which demonstrate the expressiveness of 42 for modeling various MoCCs (see chapter 4).

- A simple hardware/software model to demonstrate the combined use of 42 contracts together with the embedded software for simulation (published in [BM09]).

- A complete case-study (published in [BMF09]) on the use of 42 together with an existing component-based approach, namely SystemC/TLM [Ghe06] for systems-on-a-chip. It demonstrates: the interest of the 42 interfaces and contracts; the possibility of generating 42 objects from an existing language; the possibility of simulating a system made of 42 components and SystemC/TLM components.

- A toolset for the design and simulation of 42 models. It is capable of importing existing components from other approaches. This has been applied to SystemC/TLM and Lustre.

#### 1.4 Outline

The content of the thesis is inspired from the publications [MB07, BM09, BMF09] of the work dedicated to 42. The thesis is organized as follows:

Chapter 2 "Background" is a collection of basic notions. The reader may notice that most of the ideas presented in 42 are borrowed from the current practices of some approaches from distinct domains. We refer to these ideas during the presentation of 42.

**Chapter 3 "Overview"** is an overview of the basic elements of 42. It introduces the notion of components, and how they may be described by means of specifications. These specifications may be *implicit*, *explicit* (i.e., *control contracts*), or a mixture of both. It also includes brief presentations of some points tackled by 42.

Chapter 4 "Modeling Examples with 42 Components" is a suite of modeling examples. It illustrates some guidelines for modeling components and describing MoCCs. The examples are grouped into two sections. In the first section, we describe modeling examples based on implicit specifications of components. In the second one, we show how control contracts may be used in order to give explicit information about components.

Chapter 5 "Formal Definition of 42" presents the formal definitions of 42 elements. Namely, we define the notion of components, assemblies, the controllers implementing MoCCs, compositions, contracts, etc.

Chapter 6 "Exploiting 42 Control Contracts" illustrates the benefits of having control contracts associated with the components. In particular, it illustrates how some controllers may be deduced from the contracts of the components, and how the contracts may be executed.

Chapter 7 "Hardware Simulation and Software Execution" tackles two interesting uses of 42 in the context of systems-on-a-chip. First, we describe how 42 may be used in order to model virtual and executable prototypes of hardware platforms for the development of the embedded software. Second, we present first steps towards the formalization of SystemC/TLM with 42. SystemC/TLM being the de-facto standard in the industry for modeling systems-on-a-chip. However, it lacks in semantics.

Chapter 8 "Related Work" discusses the choices we made for 42 compared to various approaches, not all of them dedicated to embedded systems. We present each of them and discuss the differences/similarities with 42.

Chapter 9 "A Tool for the 42 Component Model" describes a prototype implementing the basic elements of 42. All the examples presented in this thesis were simulated with this prototype.

Chapter 10' "Conclusion & Prospects" is dedicated to concluding remarks and some directions for future work.

#### Suggestions for Readers

- Chapter 2, *Background*, is a collection of ideas that you may or may not know about. If you already know, you may skip it, we refer to the sections of this chapter when needed.

- Chapter 3, *Overview*, has to be read entirely. It provides an overview of all the aspects to be understood before reading the examples.

- If you are interested, in particular, in the synchronous MoCC, we suggest you read Section 4.1.1 for a global understanding of the modeling approach of synchronous systems with 42; then Section 4.2.1 to see how contracts may be useful for describing synchronous components; Section 4.2.2 presents the modeling of multi-cycle programs; finally, Section 6.2.1 describes how controllers implementing the synchronous MoCC are generated from the contracts.

- If you are interested, in particular, in the asynchronous MoCC, we suggest you read Section 4.1.2 for a global understanding of the approach; Section 4.2.3 to see how contracts may be useful for describing asynchronous components; finally, Section 6.2.2 describes how controllers implementing the asynchronous MoCC are generated from the contracts.

## Chapter 2

# BACKGROUND

Introduction (En) This chapter is presented as a collection of basic notions one should know about when reading the presentation of 42. We first introduce the most important discrete MoCCs for modeling concurrent systems. Then, we present virtual prototyping of the hardware in order to develop the software of systems-on-a-chip. 42 is a component based-approach, hence, we recall some aspects of components and their specification in software and hardware industry. At the end we give a brief presentation of the validation techniques used during the design of systems.

#### Contents

| 2.1 | Mod             | lels of Computation for Discrete Concurrent Systems 20    |

|-----|-----------------|-----------------------------------------------------------|

|     | 2.1.1           | Synchronous Models and Languages                          |

|     | 2.1.2           | Asynchronous Models                                       |

| 2.2 | $\mathbf{Virt}$ | ual Prototypes of HW Platforms for SW Development 27      |

|     | 2.2.1           | Modeling Hardware Platforms                               |

|     | 2.2.2           | Executing Embedded SW on a Virtual Prototype of the HW 30 |

| 2.3 | Con             | ponents and Contracts                                     |

|     | 2.3.1           | Components                                                |

|     | 2.3.2           | Specifying Components                                     |

|     | 2.3.3           | Design By Contract                                        |

| 2.4 | Vali            | dation                                                    |

|     | 2.4.1           | Formal Specification of Properties                        |

|     | 2.4.2           | Validation by Simulation                                  |

|     | 2.4.3           | Runtime Verification                                      |

|     | 2.4.4           | Static Verification                                       |

|     |                 |                                                           |

Introduction (Fr) La définition du modèle à composant 42 est inspirée de plusieurs notions existantes, que ce soit dans le domaine des systèmes embarqués, ou en génie logiciel en général. Dans ce chapitre, nous présentons les notions à connaître avant d'aborder la description de 42. Dans un premier temps, nous allons introduire des modèles de calcul discrets pour la modélisation des systèmes concurrents. Ensuite, nous présentons les techniques de prototypage virtuel de systèmes matériels, pour le développement de logiciel embarqué. Nous décrirons ensuite les notions de composants et de spécifications pour les composants logiciels et matériels. Nous terminerons par une description des techniques de validation de systèmes complexes.

### 2.1 Models of Computation for Discrete Concurrent Systems

The design of embedded systems is subject to several constraints. The size of an embedded system is small compared to the size of a general purpose computer system. It often has limited resources in terms of computation speed, memory, energy, etc. The context in which an embedded system may be used varies from consumer electronics (phones, PDA, etc.), to safety critical systems (air plains, nuclear plants, etc.) in which bugs may cause considerable damage. All of these constraints make embedded systems complex, and impose careful decisions on their design.

#### 2.1.0.1 The Design of Embedded Systems Requires Models

Due to their complexity, the design of embedded systems requires a modeling phase to understand the interaction between its various components, and the interaction of the system with its environment. Modeling may be used for:

- simulating the behavior of the future system.

- validating the system (testing, formal verification, etc.).

- analyzing the system with respect to timing, energy consumption, etc.

- designing a starting point of a *Model-Based Development* approach.

A model is a simplification of another entity, which can be a physical thing or another model. The model contains exactly those characteristics and properties of the modeled entity which are relevant for a given task. A model is minimal with respect to a task if it does not contain any other characteristics than those relevant for the task [Jan03].

A model is an abstraction of the entity being modeled, it exposes the relevant information we want to observe. Hence, an entity may be represented with various models depending on the use of the model. For instance, a model dedicated to performance analysis may be completely distinct from a model dedicated to functional validation.

#### 2.1.0.2 Models of Computation and Communication

An embedded system is made of concurrent components that interact to expose the behavior of the whole system. The concurrency model varies from pure *Synchrony* (e.g., digital circuits) to pure *Asynchrony* (e.g., distributed systems).

To associate a complete system with its model, one has to define a model of each component of the system and define the concurrency model. That is, defining how components evolve together, and how they communicate. This amounts to providing the semantics of the MoCC (Model of Computation and Communication) governing the system.

The notion of time is relevant to the semantics of a MoCC. Time may be considered as continuous (where components are described with models based on differential equations), or discrete. In  $Hybrid\ systems$  the MoCC deals with the two notions. What follows will describe the main  $discrete\ MoCCs$ .

#### 2.1.1 Synchronous Models and Languages

Synchronous languages [BCE<sup>+</sup>03] are well suited to design reactive systems [Hal92, HLR92]; that is, systems with permanent interaction with their environment. A reactive system repeatedly

gets its inputs (reading sensors for instance) from the environment and produces the outputs (controlling an actuator for instance). A reactive system should compute fast enough in order not to miss relevant events (inputs).

The Notion of Clocks In synchronous systems, there is a notion of logical clock that indicates when the system should read the inputs to compute the outputs. At each clock tick, the computation of the outputs involve the parallel reaction of all the components of the system. Each of them computes its outputs based on the inputs it is provided with. In a real system, the clock would be associated with the arrival of some event (from the environment) that may, or may not, be related to physical time. For instance, the timer signal in a computer system (time), a train reaching a beacon (distance), etc., may define a clock for a synchronous system.

**Communication** The communication mechanism between synchronous components is the *synchronous broadcast*. At each clock tick, a component sends some values through it outputs and does not need to know whether one or several components are waiting for these values. Sending is non-blocking.

Instantaneous Computation Synchronous components are supposed to read inputs and compute outputs instantaneously (i.e., during the same clock cycle). In practice, instantaneous computation of the outputs is not feasible. However, the requirement for reactive systems is that the reaction is sufficiently fast in order not to miss incoming events. The code produced by synchronous languages compilers is quite simple, it may be used for Worst Case Execution Time analysis [Rin00]. Hence, it is possible to check that the system reacts to all incoming events if we have some knowledge about their arrival frequency.

Interesting Uses Besides the design of reactive systems, several techniques were developed around the synchronous languages for the purpose of modeling, simulation and validation of safety critical systems.

The modeling of embedded systems often requires asynchrony and non-determinism. It is well known that synchronous formalisms can be used to model asynchronous parallelism [Mil83]. In fact, the synchronous paradigm may be used to model all kinds of intermediate behaviors, between pure synchrony and pure asynchrony.

Synchronous languages propose some operators to prevent a component from reacting (e.g., Clocks in Lustre and Signal, the suspend statement in Esterel, activation conditions in SCADE, etc.). Thanks to such operators, one can decide that components do not execute at the same clock cycles, hence, they are asynchronous (see 4.2.2.8 for illustration). The most interesting instance of this principle is the so-called quasi-synchronous approach [CMP01], to describe systems made of several processors that are not explicitly synchronized. Their respective clocks may differ, but not in a completely unknown way. These systems are modeled by a quite liberal constraint on the clocks, namely: there are never more than two ticks of one clock between two ticks of the other one.

The purpose of modeling asynchrony by means of a synchronous formalism is to benefit from the validation approaches developed around synchronous languages [HM06]. Such an approach has been applied to several case studies from the industry [JHR+07, GG03]. Moreover, recent work have been devoted to the use of synchronous formalisms for the analysis of non-functional properties such as energy consumption [LFLL06], and performance analysis in stream processing systems [AM10, ALM10].

In the sequel we present some languages for the design of synchronous systems.

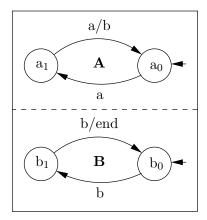

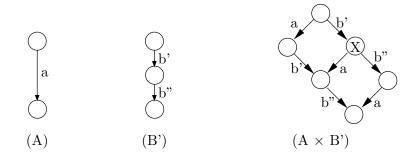

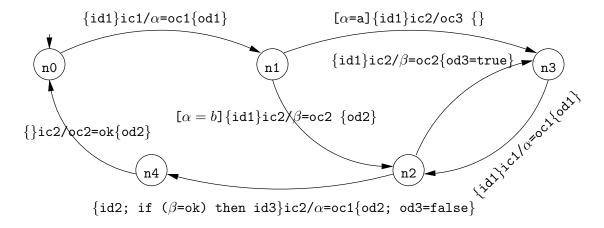

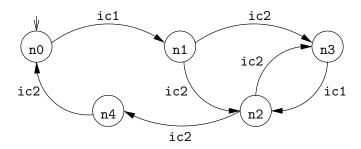

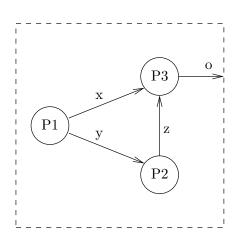

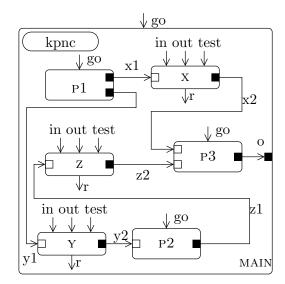

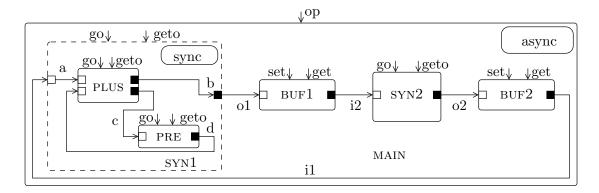

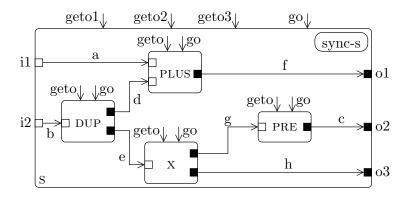

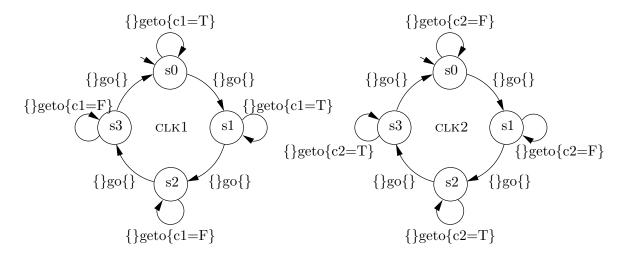

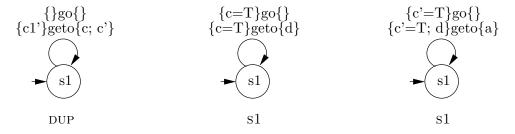

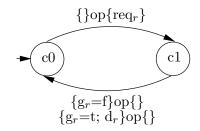

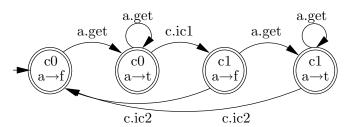

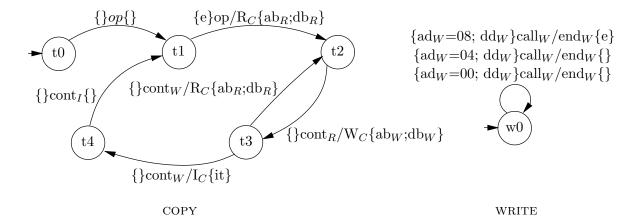

Fig. 2.1: A Boolean Mealy machines

Fig. 2.2: The modeling of a modulo-4 a-counter with Boolean Mealy machines

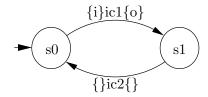

#### 2.1.1.1 Automata-Based Models

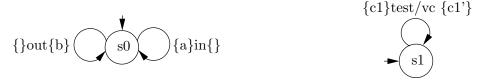

We present in this section an example of modeling synchronous systems by means of Mealy machines. Mealy machines are automata (precisely transducers) in which the computation of the outputs depends on the state of the automaton, and the current values of the inputs. In the rest of the section, we borrow the syntax from the synchronous language Argos to describe the example. In the category of automata-based languages, one may refer to SyncCharts [And04] also.

Figure 2.1 illustrates a *Boolean Mealy machine*: a Mealy machine where the inputs (a in the figure) and the outputs (b in the figure) are of Boolean type. Each transition of the automaton is labeled with inputs/outputs. The behavior of the machine is as follows:

- At state  $a_0$ , if it receives a then it does not emit b, and moves to state  $a_1$ . Otherwise, if it receives  $\overline{a}$  (which stand for he negation of a), it does not emit b and does not change state.

The loops over the states that does not emit some outputs are often omitted (see Figure 2.2).

A Modeling Example Figure 2.2 illustrates the modeling of a modulo-4 a-counter<sup>1</sup> with two Boolean Mealy machines. A was described previously in Figure 2.1. Notice that the loops over the states are made implicit. B exposes the same behavior, but it has b as input and end as output. As b is the output of A, there exists a communication between A and B.

At each step, each component (i.e., A and B) takes one transition depending on its inputs. The outputs of the transition are broadcasted to all the components running in parallel. The behavior of the parallel reaction of the two automata is as follows:

Initially, the global state is  $a_0b_0$  which encodes 0. The first occurrence of a moves the global

<sup>&</sup>lt;sup>1</sup>The example is inspired by the presentation of Argos in [MR01]

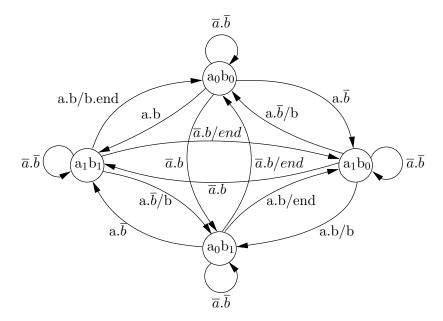

Fig. 2.3: The synchronous product of the Mealy machines A and B of Figure 2.2

Fig. 2.4: (1): Encapsulating and (2): hiding the signal b in the product of Figure 2.3

state to  $a_1b_0$  which encodes 1: A takes a transition and changes state; B takes the implicit transition and does not change its state. The second occurrence of a moves the global state to  $a_0b_1$  encoding 2: A changes its state and emits b. At the same step, B takes its transition and changes its state because its input b is emitted.

The Synchronous Product Figure 2.3 describes the synchronous product of the Boolean Mealy machines of Figure 2.2. It is also a Boolean Mealy machine, where the inputs (resp., outputs) are the union of the inputs (resp., outputs) of the two components. Each transition of the product corresponds to exactly one transition of each of the components. Notice that the synchronous product does not make any synchronization between components.

**Encapsulation** The encapsulation is parameterized by a set of signal names. It is used to restrict the scope of a signal, and to force synchronization between components. For instance, the signal b of Figure 2.2 which is the output of A and the input of B may be used to synchronize A and B. In this case, b becomes a local signal.

Figure 2.4 illustrates the steps of encapsulating the synchronous product of Figure 2.3. Firstly, we remove some transitions (illustrated by (1) in Figure 2.4). Secondly, as the encapsulated signals are local, we hide their names in the labels (illustrated by (2) in Figure 2.4).

The transition that are removed during the encapsulation are those that do not fit in the two following rules:

- A local signal which is supposed to be present has to be emitted in the same reaction. Transitions like a.b,  $\overline{a}.b$ , etc., are removed.

- A local signal that is supposed to be absent should not be emitted in the same reaction. Transitions like  $a.\bar{b}/b$  are removed.

#### 2.1.1.2 Synchronous Programming Languages

Among the languages designed for synchronous programming, one would refer to the imperative style language Esterel [BG92], and the declarative languages Lustre [HCRP91], and Signal [GG87].

In this section, we present the synchronous language Lustre, to which a lot of work has been devoted, in order to develop techniques for program verification [RHR91, GH06, Gon07], sequential and distributed code generation [Gir94], etc.

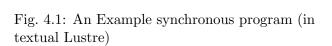

```

node integrator(i : int)

returns (o : int) ;

let

o = i -> pre(o) + i ;

tel.

```

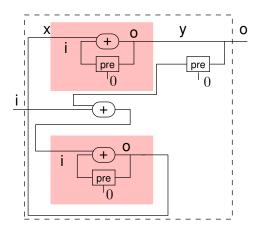

Fig. 2.5: An integrator written in textual Lustre and its graphical representation

Figure 2.5 is an example of a program written in Lustre, and its graphical representation as it would be described in the commercial tool Scade<sup>2</sup>.

A program written in Lustre is called a node. The interface of a node exposes the set of its inputs and outputs (i and o in the example). Lustre is a data-flow declarative language; this means that the internal variables, the inputs and the outputs are flows of values.

When there is only the global clock (mono-clock synchronous programs), at each instant of the global clock, each flow is given a value. The value of a flow is defined as a function of other flows. The function may be a basic operator (i.e., +, -, \*, etc) or a node; which means that a node may be used to design a new node in Lustre.

Cyclic Dependencies and the Delay Operator Because of the dependencies of the flows, at each instant, there is an order in which the values of the flows are computed. The architecture of a Lustre program as it would be described by its graphical representation, defines a partial order on the dependencies of the flows. Programs containing cyclic dependencies are rejected by the Lustre compiler as there is no way to compute an order of computation. Figure 2.6 illustrates the case where there exists a cycle between the flow o and itself. Such a program is rejected.

The pre operator introduces a delay. In Figure 2.5, the statement  $o = i \rightarrow i + pre(o)$  means that o takes the value of i at the first instant ( $\rightarrow$ ) is the initialization operator), and for all the instants  $n_k$  such that k > 0 the value of o is the value of the input i plus the previous value of o (i.e., the value of o at instant  $n_{k-1}$ ). This statement exposes a cycle (o depends on itself),

<sup>&</sup>lt;sup>2</sup>SCADE is a commercial tool for the design of safety critical systems; it is based on Lustre

```

node cycle(i : int) returns (o : int) ;

let

o = i -> o + i ;

tel

```

Fig. 2.6: A cyclic dependency in a Lustre program: the flow o depends on itself

but is still correct because of the delay. The value of o depends on its previous value. In Lustre, every cycle must be cut with a **pre** operator.

Clocks and Clock Manipulation Operators Lustre may be used to describe systems with several clocks in addition to the global clock. Clocks are associated with flows (i.e., the variables of a Lustre program) to define the presence or the absence of a value of the flow at a given instant. In Lustre any Boolean flow may define a clock for another flow.

| X                | 0    | 1     | 2    | 3     | 4     | 5     | 6    | 7    |

|------------------|------|-------|------|-------|-------|-------|------|------|

| CLK              | true | false | true | false | false | false | true | true |

| Y = X when $CLK$ | 0    |       | 2    |       |       |       | 6    | 7    |

| Z = current Y    | 0    | 0     | 2    | 2     | 2     | 2     | 6    | 7    |

Fig. 2.7: The when/current operators in Lustre

Lustre provides some primitives to manipulate clocks. The operator when is a *sampling operator*. It is used to define a slower flow from a faster one. In Figure 2.7, the declaration Y = X when CLK says that the flow Y takes the value of the flow X each time the flow CLK has the value true. Hence, CLK is the clock associated with the flow Y.

The operator current is a *projection operator*. The operator is used to get a faster flow from a slower one. For instance Z = current Y says that the flow Z takes the value of the flow Y if Y is present, otherwise it takes the value of Y the last time it was present.

#### 2.1.2 Asynchronous Models

When modeling embedded systems, there is often a need for describing systems where components evolve asynchronously. Contrary to synchronous ones, asynchronous systems are systems where there is no common clock that may be shared between components. Asynchronous systems range from threads on a mono-processor systems to large scale multi-computer systems.

On a mono-processor system, several processes or threads may run (in parallel) thanks to time-sharing schedulers, and may access a shared memory. On multi-computer systems, processes run in real parallelism, and may synchronize by message-passing.

#### 2.1.2.1 Modeling Asynchronous Behaviors without Communication

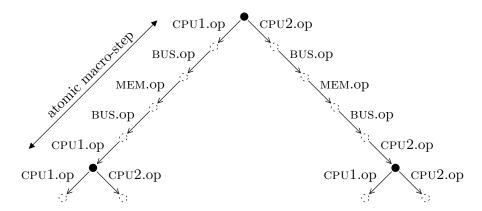

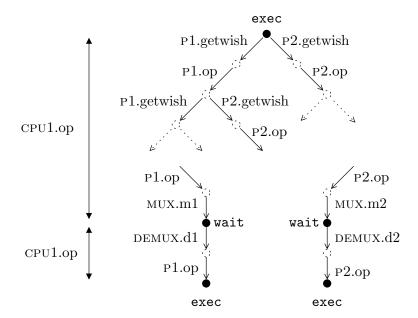

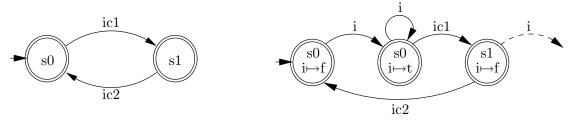

The general modeling of asynchronous systems relies on *interleaving* semantics. That is, for a whole system, an execution step corresponds to one execution step of one of its components.

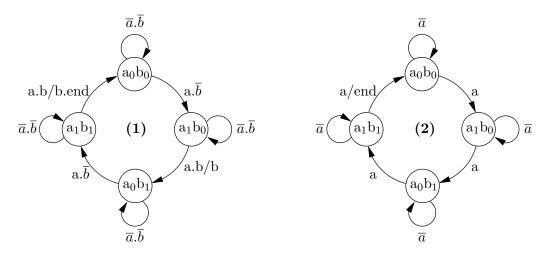

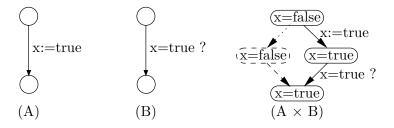

Figure 2.8 describes two automata (A) and (B) that may model the behavior of processes for instance. The states of the automata model the state of the processes. Each transition corresponds to an action (or a set of actions) of the process and is considered to be atomic. In other words, nobody running in parallel can observe the internal states of (A) during action a.

On the figure,  $(\mathbf{A} \times \mathbf{B})$  describes the asynchronous product of  $(\mathbf{A})$  and  $(\mathbf{B})$ . The asynchronous product produces the states that are potentially reachable when the two automata are run in

Fig. 2.8: Asynchronous models without communication

parallel.

**A Note on Granularity** Figure 2.9 recalls the importance of atomicity in such asynchronous models, based on interleaving semantics. Suppose we replace the automaton (**B**) of Figure 2.8 with the automaton (**B'**), where the transition **b** is no longer atomic, it is split into to atomic actions **b'** and **b''**.

Now, the global behaviors are those of automaton  $(A \times B')$ , in which new states appear. The a transition from state X means that in (B'), the intermediate state between b' and b'' is observable by (A).

Fig. 2.9: Fine granularity of atomic executions exposes more states

Choosing the granularity of atomic transitions is an intrinsic modeling problem. When modeling the behaviors of two threads on a mono-processor with a preemptive scheduler, the only possible choice is to consider the atomicity as given by the execution platform: instructions in the processor are atomic (non interruptible by the scheduler). Hence a thread is described by a detailed automaton, with explicit states between machine instructions. The model is appropriate for checking parallel programs that use low-level synchronization mechanisms like semaphores of atomic read-write machine instructions.

However, in high-level models, the notion of atomicity may be of a coarser granularity. In transaction-level models (see Section 2.2.1.1), typically, the granularity reflects the fact that we do not need to observe the precise interleavings of the component behaviors. We only need to observe the interleavings at a granularity given by the explicit synchronizations between the components.

#### 2.1.2.2 Modeling Asynchronous Behaviors with Shared Memory

Figure 2.10 illustrates the modeling of communicating asynchronous processes. As the processes may not be alive at the same time, they communicate through a shared Boolean variable  ${\tt x}$  initialized to false.

The process A assigns true to the variable x. The process B may not execute its transition until x has the value true.

The states of the asynchronous product include the state of the memory location relevant for the two processes. Here, the variable **x**.

Due to the communication between the processes, the left path of the product (dashed lines) is not possible. Notice that we still rely on interleaving semantics, but some of the states in the asynchronous product are no longer reachable.

Fig. 2.10: Asynchronous models with shared memory

# 2.2 Virtual Prototypes of Hardware Platforms for Software Development

The development of embedded systems has to take into account the design of the hardware part, and the software that may run on the hardware platform.

Modeling the hardware platform is an important phase in the design of an embedded system. There are plenty of tools that allow for the design of virtual prototypes of the hardware at various levels of abstraction.

Beside the fact that virtual prototypes of the hardware may be used for accurate simulation, design verification, and automatic generation of the hardware platform, software developers need virtual prototypes of the hardware to start developing the embedded software. The fact is that the hardware part of embedded systems is often changing from a system to another. Hence, software developers may not rely on programming models to write the software, they need executable prototypes of the real hardware on which the software would run.

In this section we discuss some tools for the modeling of the hardware and how such models would be used as a virtual execution platform for software development.

#### 2.2.1 Modeling Hardware Platforms

The behavior of the hardware may be modeled at several abstraction levels. At each abstraction level, timing aspects are defined precisely, approximately, or even inexistent. An abstraction level also defines the notion of granularity in the observable simulation states and the data exchanges.

Low Level of Abstraction Models HDLs (Hardware Description Languages), allow for the modeling of the hardware at RT-Level (Register Transfer Level). Tools like Verilog [ver] and VHDL [vhd92] propose a textual language to specify hardware. Programs written in such languages may be simulated with a precise notion of time; they are also used as input to automatic generation of the hardware layer. The synchronous languages Lustre [RH92] and Esterel [Ber92] together with SystemC [sysa] may also be used to describe hardware at the RTL level.

High Level of Abstraction Models Other approaches target the modeling of hardware at higher levels of abstraction. They may abstract away from the details that do not matter with regards to the modeling purposes. For instance, AADL (Architecture Analysis and Design Language) [FLVC05] is a component-based approach for modeling (not only) hardware architectures. The details exposed by the models written in AADL allow to perform architecture exploration and some timing analysis related to data flows.

SysML [Wei08], an extension of UML, has also been proposed to tackle specific modeling problems. It may be used for modeling of hardware at a high level of abstraction. For the moment it is not executable, and the semantics is not formalized, so it is of limited use.

Metropolis [BWH<sup>+</sup>03] is a formally defined methodology for the development of embedded systems. Abstract hardware models may be designed with Metropolis; they provide an API for the software development.

In the same category one can refer to approaches like SystemC/TLM [Ghe06], SystemVerilog [SYSb], SpecC [GZD+00], etc.

What Kind of Models do Software Developers Need Instead of waiting for the hardware platform to be manufactured, software developers use a virtual and executable prototype of the hardware to start developing the software. The main motivation is to decrease time-to-market.

It is possible to use the RTL model as an executable model of the hardware. However, in addition to the late availability of the RTL model, the hardware/software co-simulation is too slow to allow for effective development of the software. The low co-simulation speed is due to the quantity of details exposed by the RTL model.

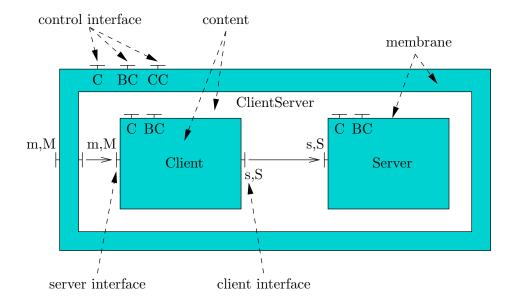

To cope with the slow simulation speed, new abstraction levels have emerged. For instance, *Transaction Level Modeling (TLM)* [Ghe06] uses a component-based approach, in which hardware blocks are described by *modules*; the communication between the hardware blocks over the real bus is abstracted by the so-called *transactions*.

TLM allows several abstraction levels, from cycle-accurate to pure functional models. They are better suited than RTL models for early development of the embedded software, because the high level of abstraction allows a faster simulation.

In the sequel we present the  $Programmer's\ View\ (PV)$  abstraction level of TLM by means of an example written in SystemC/TLM.

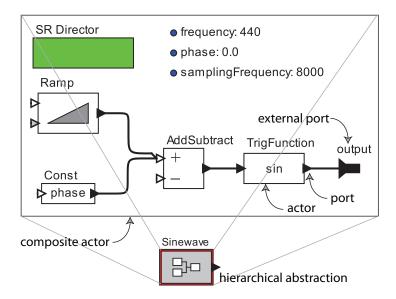

#### 2.2.1.1 TLM Programmer's View with SystemC

SystemC [sys06] is a C++ library used for the description of SoCs at different levels of abstraction, from cycle accurate to purely functional models. It comes with a simulation environment, and has become a *de-facto* standard. SystemC offers a set of primitives for the description of parallel activities representing the physical parallelism of the hardware blocks. The TLM/PV level of abstraction is implemented in SystemC by defining specific TLM libraries and templates. TLM 2.0 has been standardized by the Open SystemC Initiative (OSCI).

The success of SystemC comes from its C/C++ part: it is widely known, it is a general-purpose programming language, so there are no restrictions on what the designer can write, and it makes it possible to build tools for the co-simulation of SystemC code with C, assembly code, RTL models, etc. The dark side of the picture is that SystemC models are quite hard to analyze formally (SystemC, being based on C++, has no formal semantics, and SystemC models may implement relatively simple things by complex integer manipulations, which make simple properties undecidable in the general case). Therefore the main activity with a SystemC model is simulation.

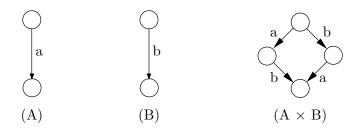

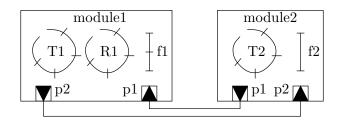

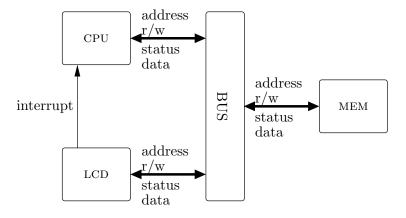

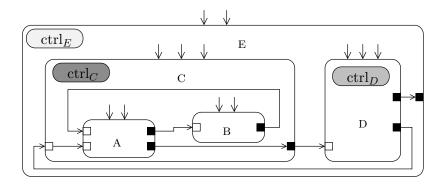

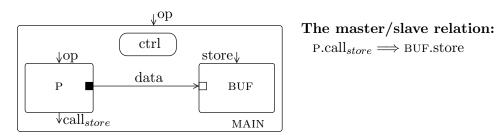

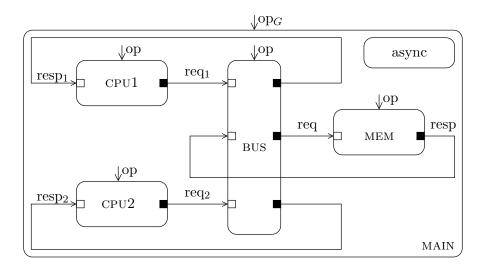

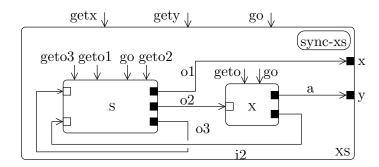

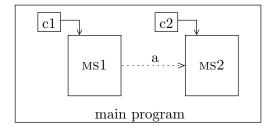

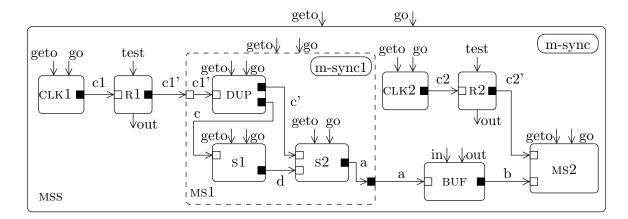

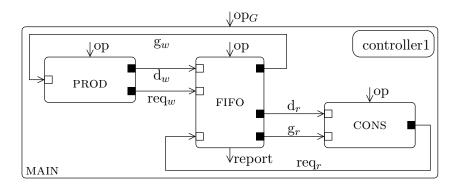

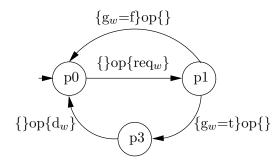

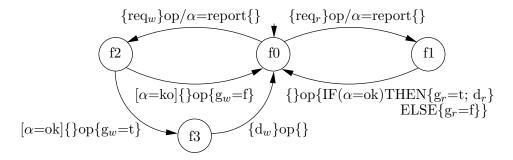

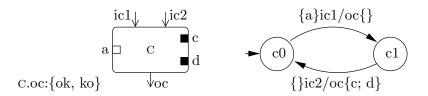

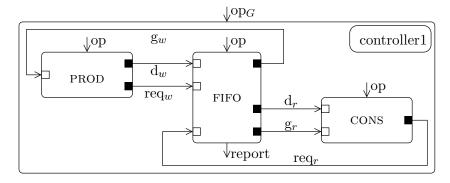

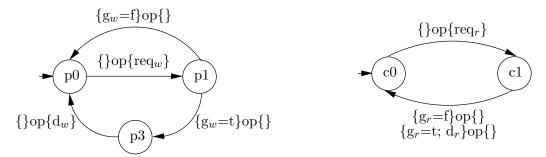

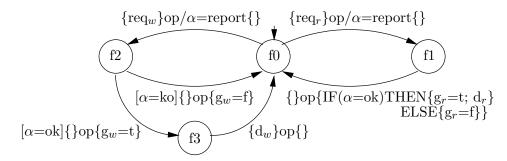

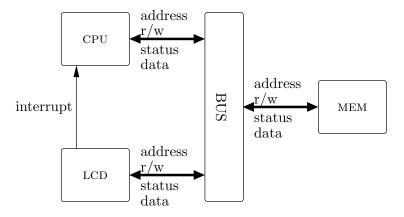

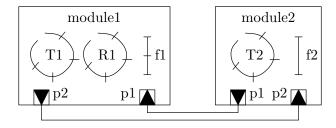

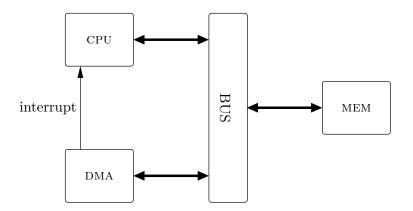

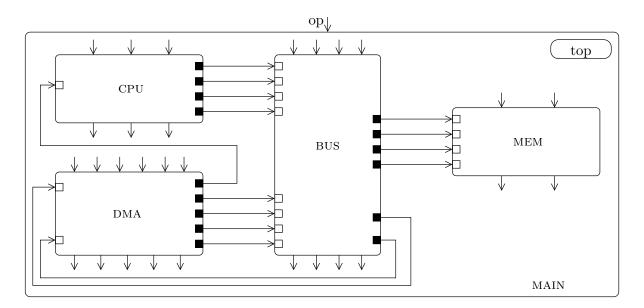

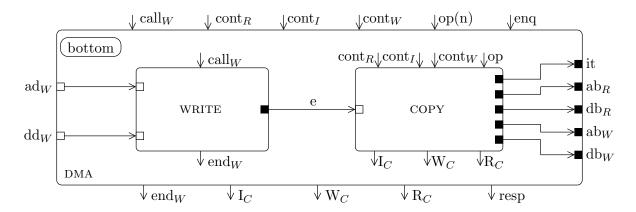

Fig. 2.11: Example of SystemC/TLM (architecture)

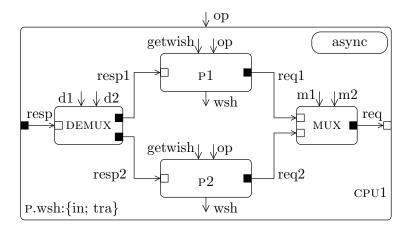

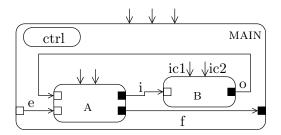

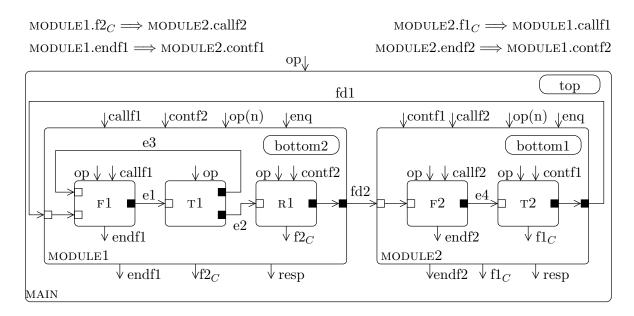

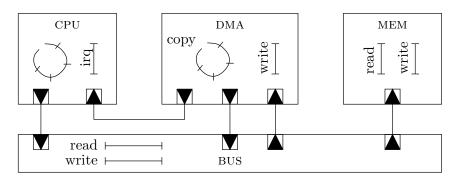

**SystemC Modules** A TL-Model is based on an *architecture*, i.e., a set of components that expose *ports*, and connections between them, as shown on Figure 2.11. The components, also called *modules*, represent some physical entities that behave *in parallel* in the real system to be modeled (typically: a bus, a CPU, a memory, etc.).

Components communicate through the ports by means of *transactions*. The direction of the arrow shown on a port determines the role of the port during transactions. On Figure 2.11, p2 in module1, and p1 in module2, are *initiator* ports of the transactions; p1 in module1, and p2 in module2, are *target* ports.

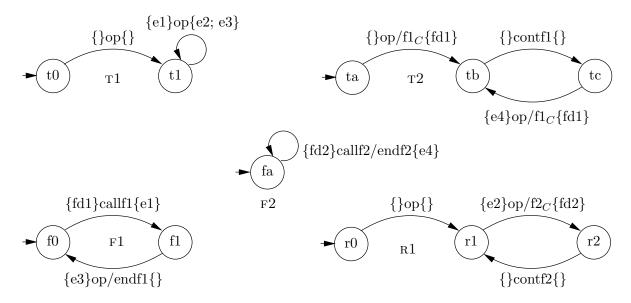

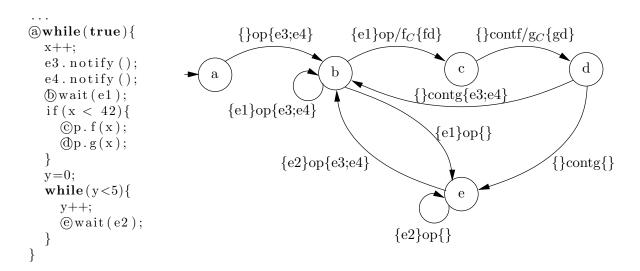

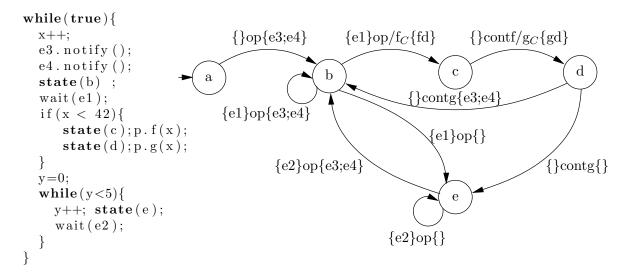

A Module is Composed of Threads and Functions The behavior of a component is given by a set of threads (represented by circles with steps on Figure 2.11), and a set of functions (represented by straight lines with steps), both programmed in full C++ (see Figure 2.13). module1 has two threads T1 and R1, and one function f1, while module2 has a single thread T2 and a function f2. The threads are active code, to be scheduled by the global scheduler; the functions are passive code, offered to the other components, and that will be called from a thread or function of another component; the functions are attached to the target ports of the module (f1 is attached to p1 in module1). Inside such a module, the processes and the functions may share events in order to synchronize with each other. Events can be notified, or waited for. In module1 (Figure 2.13) there are three events e1, e2, e3.

The SystemC Scheduler All the threads are managed globally by a non-deterministic scheduler. The SystemC scheduler is non-preemptive: a running thread has to yield, by performing a wait on an event or on time. For instance, for the thread T1 of module1, the only point where the thread yields is wait(e1). The execution of a++; e2.notify(); a++; e3.notify(); is therefore atomic.

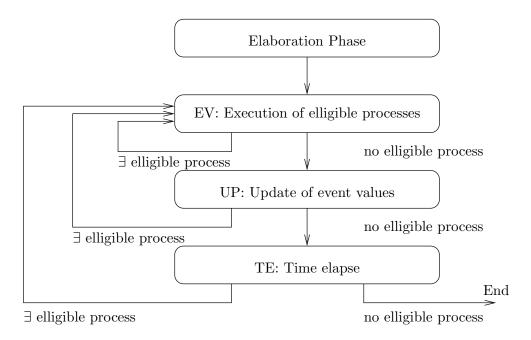

Figure 2.12  $^3$  is a sketch of the algorithm of the SystemC scheduler. After the elaboration phase, where the set of modules and communication channels are instantiated, the scheduler executes the phases presented below; a more concise description would be found in [sys06, Cor08]:

- EV Is the evaluation phase. The scheduler executes the eligible processes in a non-deterministic order. Processes yield back control by waiting for an event or time to elapse. Notified events may render some processes eligible. These processes are executed during the same phase. When there is no eligible process, the scheduler enters the update phase (UP).

- **UP** During the evaluation phase, SystemC objects may request to be activated at the update phase. For instance, some communication channels may request the scheduler to call their *update* function to update their values. Some events may be notified during this phase. Then the scheduler re-executes the EV phase.

<sup>&</sup>lt;sup>3</sup>The figure is taken from [Bou07]

Fig. 2.12: The SystemC scheduler

**TE** When no process still eligible after the update phase, the scheduler lets time elapse until reaching the earliest delay waited for by processes. The corresponding processes are made eligible, and the scheduler enters a new evaluation phase.

Some TLM Guidelines According to the TLM-PV guidelines, communications between modules cannot use the event mechanism, because this would be meaningless w.r.t. the physical parallelism to be modeled. The only possible communications are called transactions, implemented by blocking function calls; the link between a caller and the callee is established through the architecture. On Figure 2.13, the thread T2 of module2 initiates a transaction on its port p1 (written p1.f1(c)). This is a call to the function f1 in module1 (which is attached to the target port p1 of module1), because the initiator port p1 of module2 is connected to the target port p1 of module1. When the call is executed (T2 being running), the control flow is transferred to module1, until f1 terminates; then the control flow returns to module2, and the execution continues until the next yielding point (wait(e4) in the example). Since function f1 in module1 waits for the event e3, it yields if e3 is not present; this means that thread T2 in module2 may yield because of a wait statement in the function it has called in another module.

An example atomic sequence is the following: the scheduler elects thread R1, which is at line 12; it executes b++ and then calls f2 via the port p2; the body of f2 in module2 is executed entirely, and the control returns to module1; the thread R1 loops, executes b++ at line 11, and stops on wait(e2) at line 11.

#### 2.2.2 Executing Embedded Software on a Virtual Prototype of the Hardware

As explained previously, hardware virtual prototypes are used by software developers to write the embedded software. The virtual prototype provides an execution platform for the software. This means that the software should execute together with the model of the hardware.

Suppose we (as software developers) are provided with the virtual prototype of the hardware platform described by Figure 2.14. The virtual prototype contains a model of the memory, the

```

void module1::T1(){

void module2::T2(){

19

int a = 0;

int c;

2

20

while (true) {

while (true) {

3

21

p1.f1(c);

wait (e1);

c++;

22

4

a++; e2.notify();

wait (e4);

c++;

5

23

6

a++; e3. notify();

24

}}

25

7

void module1::R1(){

26

8

int b = 0;

void module2 :: f2 (int x) {

9

27

while (true) {

cout << x;

10

28

b++; wait (e2);

e4. notify();

11

29