### Temps Logique pour l'ingénierie dirigée par le modèles Frédéric Mallet

### ▶ To cite this version:

Frédéric Mallet. Temps Logique pour l'ingénierie dirigée par le modèles. Modeling and Simulation. Université Nice Sophia Antipolis, 2010. tel-00541140

### HAL Id: tel-00541140 https://theses.hal.science/tel-00541140

Submitted on 29 Nov 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ NICE-SOPHIA ANTIPOLIS

École Doctorale STIC

## Habilitation à Diriger des Recherches

### Spécialité: **INFORMATIQUE**

par

## Frédéric MALLET

# Logical Time in Model-Driven Engineering

Soutenue publiquement le 26 novembre 2010 devant le jury composé de:

| Rapporteurs  | М.       | Robert<br>Suzanne<br>Jean-Pierre | France<br>Graf<br>Talpin | Professor CSU<br>DR CNRS/HDR<br>DR INRIA/HDR |

|--------------|----------|----------------------------------|--------------------------|----------------------------------------------|

| Président    | М.       | François                         | Terrier                  | DR CEA/Professor                             |

| Examinateurs | М.<br>М. | Charles<br>Robert                | André<br>de Simone       | Professor UNS<br>DR INRIA/HDR                |

Laboratoire I3S, salle de conférences

# Preface

In this document, I introduce some work realized over the last few years in collaboration with the team-project Aoste and other people with various backgrounds. AOSTE is a joint team between I3S and INRIA, bi-localized in Sophia Antipolis and Rocquencourt. It builds on previous experience by research scientists from the former TICK and OSTRE INRIA teams, and the I3S SPORTS team from the University of Nice-Sophia antipolis. Aoste tackles several topics in the design methodologies for real-time embedded systems. Here design means altogether:

- High-Level Modeling ;

- Transformation and Analysis ;

- Implementation onto Embedded platforms.

To cover this vast spectrum of subjects we need to specialize the type of formalisms considered. Aoste focuses on synchronous reactive systems, such as Esterel/SyncCharts, and on the AAA methodology. Part of our activity is devoted to enrich the Model Based Design approach with a proper UML modeling diagrams and profiles with elements allowing for efficient modeling and embedding of synchronous designs. The main idea was to extend the Unified Modeling Language (UML) so as it could be used for the design of embedded and real-time systems. UML provides a broad range of diagrams to cover all aspects of a system (*e.g.*, requirements, object models, functional models, state machines, data flows, deployment). It allows extensions through the definition of profiles and seems to be a good front-end to capture models. These models need a precise semantics and depending on the analysis context the same diagrams may be interpreted with a different semantics. To allow interoperability of models, the expected interpretation must not be left outside the model and should rather be made explicit within the model.

Following some collaborations with the CEA-List and Thalès Research & Technology, we have had the opportunity to contribute to the definition of the UML profile for Modeling and Analysis of Real-Time and Embedded systems (MARTE) by the Object Management Group (OMG). The main part of this contribution was to lead the definition of its model and allocation models. Inspired by our background in synchronous reactive systems, we setup in 2005 to define a language, called the Clock Constraint Specification Language (CCSL), as a support to make explicit the causal and chronological relations between events of a system. Even though it was devised as a companion language for UML/MARTE models, CCSL has been developed independently and is now defined as a model (rather than a language) that can complement not only UML models but also non-UML ones (*e.g.*, ecore-based).

The first part of this document describes CCSL. The remaining two parts give usage examples of CCSL for modeling (Part II) and for verification (Part III).

# Acknowledgement

I must say that, as most research works, this work would not have been possible without the help and contribution of several administrative, engineering and research staff and students. So I want to thank every one that felt concerned by this work at some point or another.

I am greatly in debt to the referees and members of my examination committee. In a time where the administrative duties are overwhelming I know how demanding it may be to read and report on dissertations. I am grateful that they took some of their time to do it for me and to be part of my committee.

I also want to thank the Aoste team members, current and paste, for being good sparring partners and our assistants for helping me through the administrative maze. Special thanks to Charles, for his great work in defining CCSL, for his huge contribution to this work and for having always been very helpful and ready to discuss. Many thanks to Robert for, as team leaders should do, providing the resources required to foster research activity (research tracks, fundings and collaboration partners).

I have special thoughts for Fernand who has followed my work since the beginning of my Master. He has been of a great support to decrypt and synthesize the tremendous work of philosophers and physicists who have, for ages, tried to grasp the essential nature of time.

> To my parents, To Iris, To Luc & Vincent.

# Contents

| Pr       | eface | e                                                                                                          | i   |

|----------|-------|------------------------------------------------------------------------------------------------------------|-----|

| Ac       | cknov | wledgement                                                                                                 | iii |

| Ι        | Lo    | gical Time at/as design time                                                                               | 1   |

| 1        | Bac   | kground                                                                                                    | 3   |

|          | 1.1   | Models of Computation and Communication                                                                    | 3   |

|          | 1.2   | Events, causality, exclusion                                                                               | 6   |

|          | 1.3   | Tag structures                                                                                             | 8   |

|          | 1.4   | Logical time and logical clocks                                                                            | 11  |

| <b>2</b> | The   | Clock Constraint Specification Language                                                                    | 13  |

|          | 2.1   | Instants, clocks and time structures                                                                       | 13  |

|          | 2.2   | Clock constraints                                                                                          | 16  |

|          |       | 2.2.1 Coincidence-based clock constraints                                                                  | 16  |

|          |       | 2.2.2 Derived coincidence-based clock constraints                                                          | 17  |

|          |       | 2.2.3 Precedence-based clock constraints                                                                   | 18  |

|          |       | 2.2.4 Derived precedence-based clock constraints                                                           | 19  |

|          |       | 2.2.5 Mixed constraints                                                                                    | 20  |

|          |       | 2.2.6 TimeSquare $\ldots$ | 22  |

|          | 2.3   | UML for Real-Time and Embedded systems                                                                     | 23  |

|    |              | 2.3.1   | UML, SPT, Marte                                                                       | 23 |

|----|--------------|---------|---------------------------------------------------------------------------------------|----|

|    |              | 2.3.2   | Marte Time profile                                                                    | 25 |

|    |              | 2.3.3   | UML and formal methods $\ldots$                                                       | 27 |

|    |              | 2.3.4   | UML and synchronous languages                                                         | 28 |

|    |              | 2.3.5   | SysML/Marte                                                                           | 29 |

|    | 2.4          | The fu  | uture of MARTE Time Model                                                             | 31 |

| 3  | Hov          | v does  | CCSL compare ?                                                                        | 33 |

|    | 3.1          | Petri I | Nets                                                                                  | 34 |

|    |              | 3.1.1   | Time Petri nets                                                                       | 34 |

|    |              | 3.1.2   | Encoding CCSL operators in Time Petri nets                                            | 35 |

|    | 3.2          | Proces  | ss networks                                                                           | 38 |

|    |              | 3.2.1   | Synchronous Data Flow                                                                 | 38 |

|    |              | 3.2.2   | A CCSL library for SDF                                                                | 39 |

|    |              | 3.2.3   | Discussion and perspectives $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 40 |

|    | 3.3          | Polych  | aronous languages                                                                     | 42 |

|    |              | 3.3.1   | Signal                                                                                | 42 |

|    |              | 3.3.2   | Encoding CCSL operators in Signal                                                     | 43 |

|    |              | 3.3.3   | Hierarchization of CCSL clock constraints $\ldots \ldots \ldots \ldots$               | 47 |

|    | 3.4          | Perspe  | ectives                                                                               | 48 |

| II | $\mathbf{N}$ | Iodeli  | ing                                                                                   | 51 |

| 4  | The          | e autor | notive domain                                                                         | 53 |

|    | 4.1          | An AI   | DL for automotive software: East-ADL2                                                 | 53 |

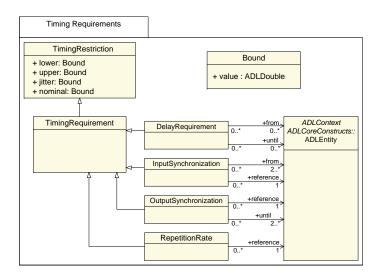

|    |              | 4.1.1   | Timing Requirements                                                                   | 54 |

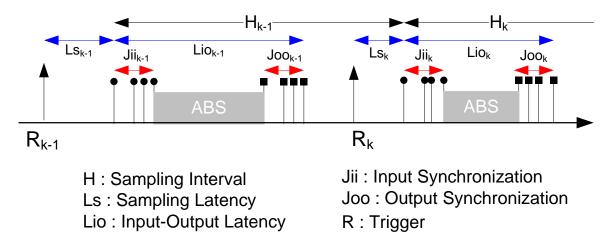

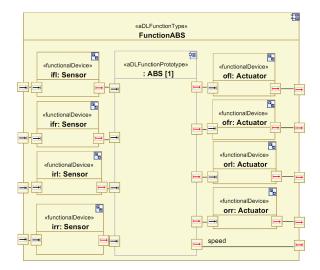

|    |              | 4.1.2   | Example: An ABS controller                                                            | 56 |

|    | 4.2          | A CCS   | SL library for East-ADL                                                               | 57 |

|    |              | 4.2.1   | Applying the UML profile for Marte                                                    | 57 |

|    |              | 4.2.2   | Repetition rate                                                                       | 58 |

|    |              | 4.2.3   | Delay requirements                                                                    | 59 |

|    |              |         |                                                                                       |    |

|   | 4.3 | Analysis of East-ADL specification           | 60            |

|---|-----|----------------------------------------------|---------------|

|   | 4.4 | Perspectives                                 | 61            |

| 5 | The | avionic domain                               | 33            |

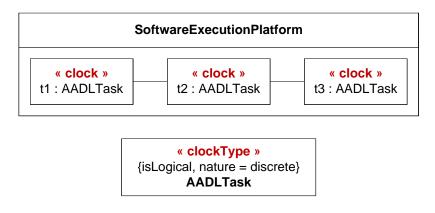

|   | 5.1 | Architecture & Analysis Description Language | 64            |

|   |     | 5.1.1 Modeling elements                      | 64            |

|   |     | 5.1.2 AADL application software components   | 64            |

|   |     | 5.1.3 AADL execution platform components     | 65            |

|   |     | 5.1.4 AADL flows                             | 65            |

|   |     | 5.1.5 AADL ports                             | 66            |

|   | 5.2 | From AADL to UML Marte                       | 66            |

|   |     | 5.2.1 Two layers or more                     | 66            |

|   |     | 5.2.2 AADL application software components   | 68            |

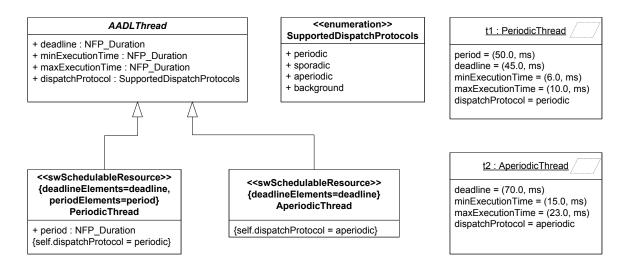

|   |     | 5.2.3 Modeling ports                         | 69            |

|   | 5.3 | Describing AADL models with Marte            | 69            |

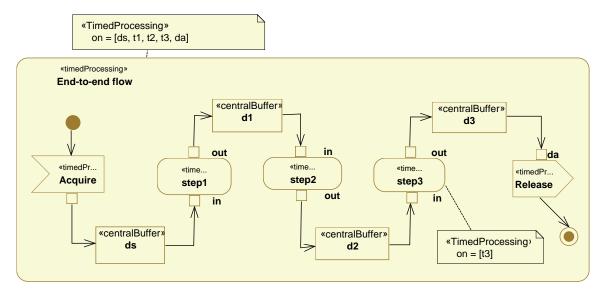

|   |     | 5.3.1 AADL flows with Marte                  | 69            |

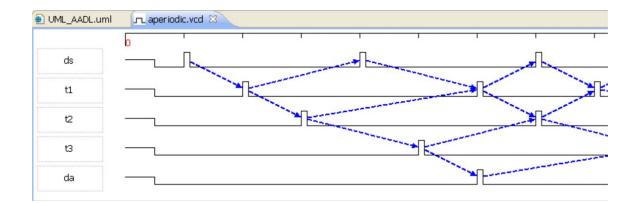

|   |     | 5.3.2 Five aperiodic tasks                   | 71            |

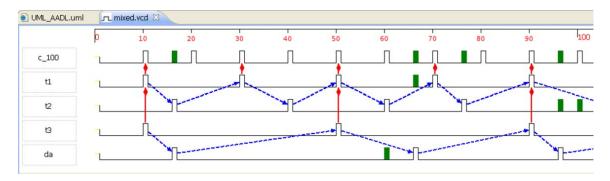

|   |     | 5.3.3 Mixing periodic and aperiodic tasks    | 72            |

|   | 5.4 | Perspectives                                 | 74            |

|   |     |                                              |               |

| Π | IV  | Verification 7                               | $\mathbf{'5}$ |

| 6 | Bui | ding language-specific observers for CCSL    | 77            |

|   | 6.1 | The generation process                       | 77            |

|   | 6.2 |                                              | 80            |

|   |     |                                              | 80            |

|   |     | 6.2.2 In VHDL                                | 80            |

|   | 6.3 | Relation observers                           | 81            |

|   |     | 6.3.1 In Esterel                             | 82            |

|   |     | 6.3.2 In VHDL                                | 82            |

|   | 6.4 | Generators                                   | 83            |

|    |     | 6.4.1 In Esterel                    | 84  |

|----|-----|-------------------------------------|-----|

|    |     | 6.4.2 In VHDL                       | 85  |

|    | 6.5 | Perspectives                        | 86  |

| 7  | Ver | ifying Esterel implementations      | 87  |

|    | 7.1 | Example: a digital filter           | 87  |

|    | 7.2 | CCSL specification                  | 88  |

|    | 7.3 | Running simulations with TimeSquare | 91  |

|    | 7.4 | Analysis with Esterel observers     | 92  |

| 8  | Ver | ifying VHDL implementations         | 95  |

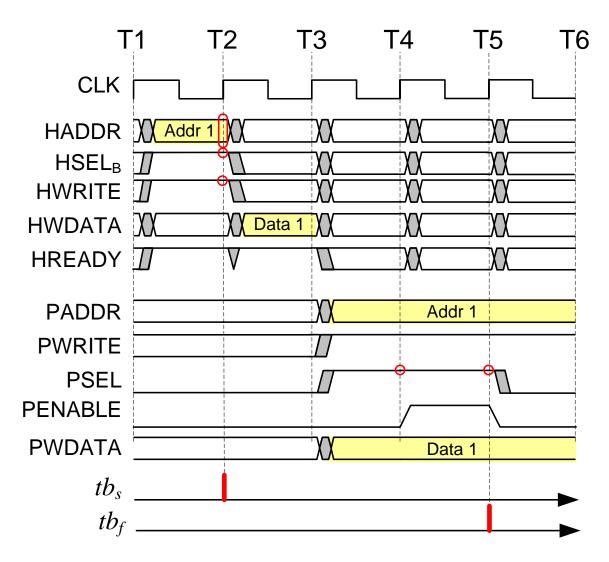

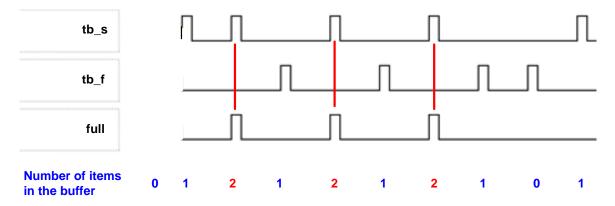

|    | 8.1 | Example: an AMBA AHB to APB Bridge  | 95  |

|    | 8.2 | CCSL specification                  | 96  |

|    | 8.3 | Analysis with VHDL observers        | 99  |

|    |     |                                     |     |

| I۱ | / ( | Conclusion                          | 103 |

| Bibl | iogra | phy |

|------|-------|-----|

|------|-------|-----|

106

# List of Figures

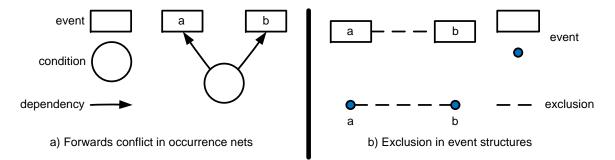

| 1.1 | Exclusion in occurrence nets and event structures                                           | 6  |

|-----|---------------------------------------------------------------------------------------------|----|

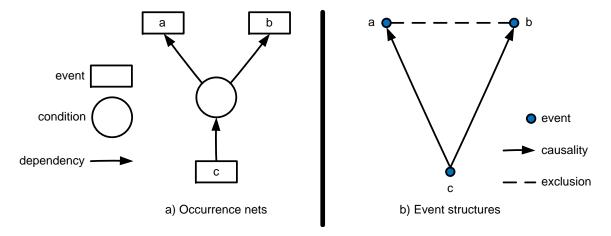

| 1.2 | Causality and exclusion                                                                     | 7  |

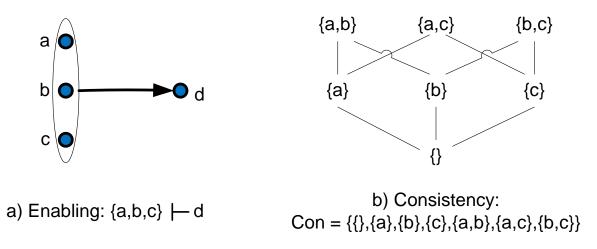

| 1.3 | Enabling and consistency.                                                                   | 8  |

| 1.4 | Tag structure by example                                                                    | 10 |

| 1.5 | Logical clocks by example                                                                   | 10 |

| 2.1 | Graphical representation of instant relations                                               | 15 |

| 2.2 | Coincidence-based clock constraint                                                          | 17 |

| 2.3 | Precedence-based clock constraint                                                           | 19 |

| 2.4 | Sampling constraints                                                                        | 21 |

| 2.5 | SysML parametric diagrams                                                                   | 30 |

| 3.1 | Precedence and alternation in Time Petri net                                                | 35 |

| 3.2 | B is<br>PeriodicOn A period=P offset= $\delta$                                              | 36 |

| 3.3 | Operator defer: $B \equiv A \$_C 2 \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 37 |

| 3.4 | CCSL alternates<br>With encoded as an automaton $\hdots$                                    | 43 |

| 4.1 | The metamodel of East-ADL Timing Requirements                                               | 55 |

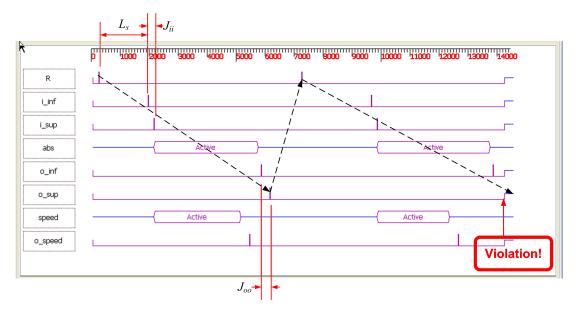

| 4.2 | Timing requirements for the ABS                                                             | 56 |

| 4.3 | Example of the ABS                                                                          | 57 |

| 4.4 | Executing the East-ADL specification of the ABS with TimeSquare $\ .$ .                     | 60 |

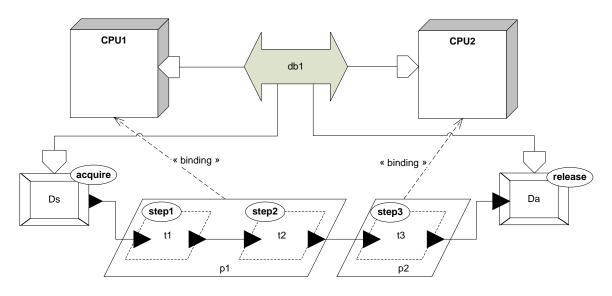

| 5.1 | The example in AADL                                                                         | 64 |

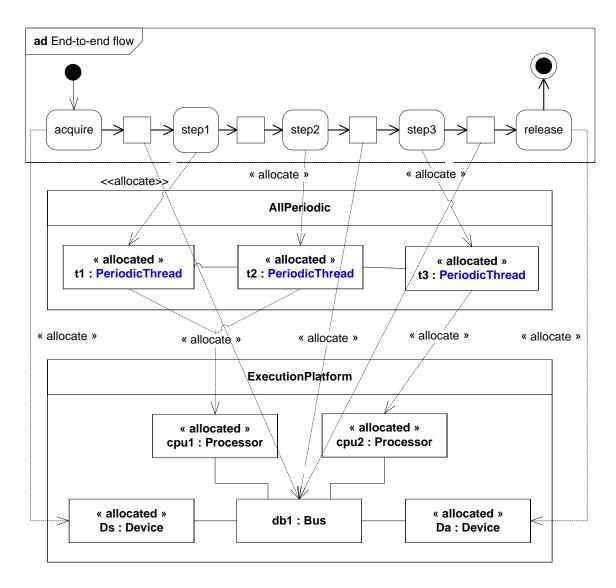

| 5.2 | Three-layer approach with Marte                                                             | 67 |

| 5.3 | A UML/Marte library for AADL threads                                                        | 68 |

| 5.4 | End to end flows with UML Marte                                        | 70  |

|-----|------------------------------------------------------------------------|-----|

| 5.5 | AADL thread activation conditions denoted as CCSL clocks $\ . \ . \ .$ | 71  |

| 5.6 | Five aperiodic tasks.                                                  | 71  |

| 5.7 | Mixing periodic and aperiodic tasks.                                   | 73  |

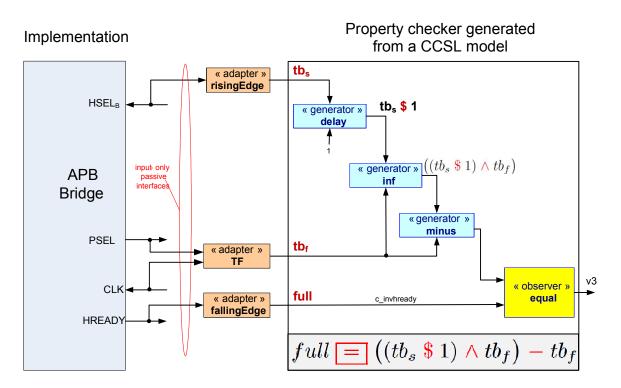

| 6.1 | The observation network structurally reflects the CCSL model           | 79  |

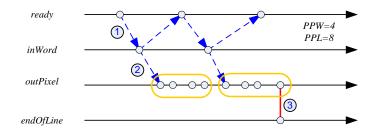

| 7.1 | Some time constraints on the DF behavior                               | 89  |

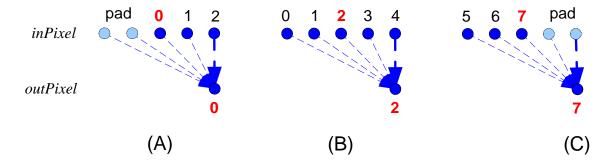

| 7.2 | Pixel dependency                                                       | 90  |

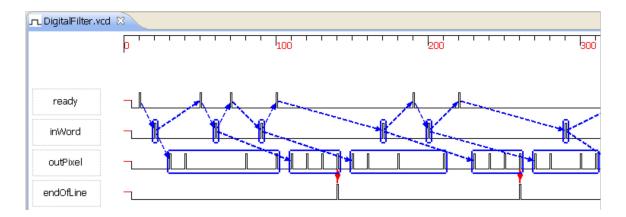

| 7.3 | One acceptable solution generated by TimeSquare                        | 92  |

| 8.1 | A typical write transfer through the bridge                            | 97  |

| 8.2 | Sample Execution of Constraint 3 on CCSL Simulator                     | 100 |

# Part I

# Logical Time at/as design time

CCSL has arisen from different inspiring models in an attempt to abstract away the data and the algorithms and to focus on events and control. Even though CCSL was initially defined as the time model of the UML profile for MARTE, it has now become a full-fledged domain-specific modeling language for capturing causal, chronological and timed relationships. It is intended to be used as a complement of other syntactic models that capture the data structure, the architecture and the algorithm.

Chapter 1 introduces the background and the historical models of concurrency that have inspired the construction of CCSL. Chapter 2 introduces CCSL and its relationships to the UML and MARTE. Chapter 3 compares CCSL to related concurrent models.

## Chapter 1

## Background

### **1.1** Models of Computation and Communication

Embedded systems are built by assembling various kinds of concurrent components : hardware or software. For hardware components, the concurrency is physical because components actually run in parallel; hardware description languages consider components as concurrent processes that communicate through shared signals. Embedded software is increasingly a composition of concurrent processes and departs from traditional software engineering by making explicit the concurrency and by offering mechanisms to model the time. For software components, the concurrency is potential and mainly due to the dependency or rather independence between data (and control) processed by algorithms. In both cases, the components interact in a variety of ways, not limited to the simple transfer of control of the classical synchronous message-passing mechanism predominantly used in software engineering. Components represent computations (or communications) and their interaction are governed by so-called Models of Computation<sup>1</sup> and Communication (MoCC) [Lee00, Jan03]. The heterogeneity of modern systems requires the joint use of several MoCCs and a

<sup>&</sup>lt;sup>1</sup>Computational models have been developed as early as the 1930s, Turing Machines are examples. The term "Model of Computation" came in use much later in the 1970s. The use of "Model of Computation and Communication" is even more recent (2000s). It underlines the actual effort to design computations and communications separately.

framework to combine them [EJL<sup>+</sup>03]: state machines for control-dominant aspects, data-flow for data-intensive processing, discrete-event to deal with mainly aperiodic systems, time-triggered or synchronous when predictability is required.

Following Petri's view, computations (processes) are often represented in terms of their events, on which they synchronize, and their effect on local states <sup>2</sup>.

Untimed (causal) models focus on the causal dependency and conflicts between events. The word *event* refers either to one occurrence of a certain 'atomic' action or to the set of all the occurrences of this action, depending on the level considered. Atomicity, meaning here instantaneous or without duration, also largely depends on the abstraction level; what is considered as indivisible at a certain level-because its duration is negligible compared to other actions-may have a complex structure when refined. Examples of untimed models include Petri's *Transition Nets* [Pet87], where a transition represents a set of all the occurrences of a given action, *occurrence nets* and *event structures* [NPW81], where each transition represents a single occurrence. It also includes untimed *process algebras* like CCS [Mil80] or CSP [Hoa78], that consider processes as primitive elements and not only events. In that context, event names denote an event *class* and there may be many occurrences of events in a single class. A major difference with causal nets resides in the communications. Communications in causal nets are through events of mutual synchronization, whereas process calculi use (synchronous or asynchronous) channels.

While untimed models mainly deal with *causality*, timed models deal with *sequentialization* [KK98], *i.e.*, an action must occur before another one in some sequentialization, in some temporal ordering of events. Causality clearly induces sequentialization, if a causes b, then b must never be observed before a in any sequentialization. However, causality is not the only reason for sequentialization. There may be some extra-functional reasons: it has been decided that an event should occur periodically every 10 ms because of some (arbitrary or not) reasons, because of the way the sampling mechanism was designed, because by doing so, there will only be some harmonic

$<sup>^{2}</sup>$ Strachey and Scott assumed a view as a function acting in a continuous fashion between datatypes, but the event-based view is closer to our preoccupations.

task sets and some scheduling algorithms would apply. Extra-functional considerations are essential for embedded systems and time is one of the property that must be taken into account, especially in safety-critical hard real-time systems. Time has deliberately been ignored by untimed models, not only to simplify the designs and reasoning but also because it was considered purely extra-functional and so, had to be treated independently of the logical correctness of the design.

"Another detail which we have deliberately chosen to ignore is the exact timing of occurrences of events. The advantage of this is that designs and reasoning about them are simplified, and furthermore can be applied to physical and computing systems of any speed and performance. In cases where timing of responses is critical, these concerns can be treated independently of the logical correctness of the design. Independence of timing has always been a necessary condition to the success of high-level programming languages."

#### C.A.R. Hoare, Communicating Sequential Processes, 2005.

However, in parallel computations, time is not solely a performance issue as it is in sequential computations, but it can alter the functional behavior. In a systemon-chip with multiple time domains for instance, the relative frequency between the processor clock and the bus clock has an impact on the global functional behavior. In real-time systems, it is sometimes preferable to send approximate data rather than sending them too late (*e.g.*, video processing), this means altering the actual function performed not to miss a deadline. It is sometimes preferable not to send a data when we know it will arrive too late, *e.g.*, to save resources. Time constraints that have an impact on the logical correctness should therefore be integrated into the model. When addressing these problems where time is part of the functional specification, time is qualified as *logical* [Lam78], as opposed to physical. It does not necessarily means that the actual timing must be included in the model but that at least the relative orderings must be considered.

The purpose of this work is to propose a model that combines causal and time aspects.

### **1.2** Events, causality, exclusion

Let us consider a set E of event occurrences. We do not say what events are, they can be anything performed by a process as time goes on. Two primitive relations are considered between events: *exclusion* and *causal dependency*.

For various reasons, some events may exclude some others. It may be because physically two values cannot be at the same time at some place or because they compete for the same resource. Forwards conflicts in occurrence nets (see Fig. 1.1-a) are simple examples that induce an *exclusion*. a and b shares the same condition, so if a occurs then b will never occur and vice-versa. In, Figure 1.1-b, the relation is directly denoted by the dashed line connecting two events. The upper right figure denotes events as in place/transition nets. The lower right figure is more concise.

Figure 1.1: Exclusion in occurrence nets and event structures

Some events may cause others. Causality is not really the right English word, it rather denotes a necessity [Win08]. In that context, a causes b does not mean that if a occurs then b must occur, but rather that b cannot occur, unless a has already occurred. In the following, we abusively use the terminology causality or causal dependency to remain consistent with other works on the topic. Figure 1.2-a illustrates the causal dependency on an occurrence net: events a and b cannot occur unless c has already occurred. Figure 1.2-b abstracts away the shared condition and directly represents the causal dependency with a plain arrow directed from the cause to the effect. It must be acknowledged that this kind of causality is purely logical and not temporal (as might wrongly suggest the present perfect). It does not say anything about the date at which the events occur but only specifies the logical ordering in which events must occur. It differs from the (temporal) precedence relation introduced later.

Figure 1.2: Causality and exclusion

There have been many presentations and variants of event structures. In [NPW79], elementary event structures are simply a partially ordered set  $(E, \leq)$ , where E is a set of events (occurrences) and  $\leq \subset E \times E$  is a partial ordering over E, called the *causality relation*. Assuming that in physical systems, there is an upper bound on the speed at which causality travels, a property of *finite causes* is considered:  $\forall e \in E, \{e' \in E | e' \leq e\}$  is finite. In event structures, a conflict relation  $\# \subset E \times E$ , a symmetrical and irreflexive relation on E, is added. The axiom of conflict heredity is stated as follows:  $\forall e, e', e'' \in E, (e \# e' \wedge e' \leq e'') \Rightarrow e \# e''$ .

Later [Win86], the binary relations are replaced by N-ary relations. The enabling relation generalizes the causality relation and stands for events that have multiple causes (AND-Causality [Gun92]) (see Fig. 1.3-a). A consistency predicate,  $Con \subset Fin(E)$  over the finite subsets of E, generalizes the binary conflict relation by picking out some events that can occur together. Figure 1.3-b shows the domain of configurations for a simple consistency predicate. a is not directly in conflict with neither b nor c, since  $\{a, b\} \in Con \land \{a, c\} \in Con$  but a will never occur when both b and c have occurred. Ultimately, a, b, c cannot all occur:  $\{a, b, c\} \notin Con$ . The binary exclusion implies the following simple rule on the consistency predicate:  $(a\#b) \Rightarrow (\forall X \in Con)(\{a, b\} \notin X).$

Figure 1.3: Enabling and consistency.

Flow event structures [BC88] are a more flexible notion of event structures obtained by relaxing the axiom of conflict heredity, the finite cause property and by replacing the causal dependency by a weaker (irreflexive) relation, the *flow* relation, denoted  $\prec$ .

### **1.3** Tag structures

The notion of Tag Systems has been initially introduced in the Lee and Sangiovanni-Vincentelli's (LSV) tagged-signal model [LS98]. LSV is a denotational approach where a system is modeled as a set of behaviors. Behaviors are sets of events. Each event is characterized by a data value and a tag. It departs from the work on event structures by not relying on the category theory to be more accessible. The parallel composition of systems consists in taking the intersection of their corresponding sets of behaviors. Tag Systems gave rise to Tag Structures [BCC<sup>+</sup>08] and to Tag Machines [BCCSV05]. Tag structures aim at providing a compositional theory of heterogeneous reactive systems. They restrain the generality of tag systems and give more structure to the behaviors, which become finite sets of signals, signals being sequences of events. They also introduce the concept of stretching to allow certain deformations of the tags for behaviors. The stretching mechanism allows an entire characterization of the MoCCs. Parallel composition is allowed through the *fibered* product of tag structures and requires an appropriate algebra. More formally, a tag structure is a triple  $\langle \mathcal{T}, \leq, \Phi \rangle$ , where:

- $\mathcal{T}$  is a set of tags and  $(\mathcal{T}, \leq)$  is a partial order;

- $\Phi$  is a set of increasing total functions  $\phi : \mathcal{T} \to \mathcal{T}$ , the set of stretching functions.

This work departs from the event structures by considering timed systems. Tags are time stamps. For instance, the tag structure  $\langle \mathbb{N}, \leq, \{id\} \rangle$ , where  $\leq$  is the usual total order on natural numbers, can be used in modeling synchrony. Tags indicate the reaction indices. The tag structure  $\langle \mathbb{R}_+, \leq, \{id\} \rangle$  can be used in modeling timetriggered systems. Tags become real-time dates.

The stretching function  $\Phi$  allows deformations of the tags. When  $\Phi = \{id\}$  no deformations are allowed and the structure is rigid. When, for instance,  $\Phi$  is the set of all dilating increasing functions, *i.e.*, functions  $\phi$  such that  $\phi(\tau) \geq \tau$  for all  $\tau \in \mathcal{T}$ , then the tags represent the earliest possible dates for execution of events.

Tag structures then consider a set of variables  $\mathcal{V}$ . A behavior  $\sigma$  considers a finite subset  $V \subset \mathcal{V}$  with domain D and is a mapping defined as follows:

$$\sigma \in V \to \mathbb{N} \to (\mathcal{T} \times D)$$

meaning that, for each  $v \in V$ , the  $n^{th}$  occurrence of v in behavior  $\sigma$  has tag  $\tau \in \mathcal{T}$ and value  $x \in D$ . For a given variable and a given behavior the *clock* is extracted. The clock of v in  $\sigma$  is the first projection of the map  $\sigma(v)$  and must be an increasing (order-preserving) function  $f : \mathbb{N} \to \mathcal{T}$ , *i.e.*,  $f(\leq_{\mathbb{N}}) \subseteq \leq_{\mathcal{T}}$ .

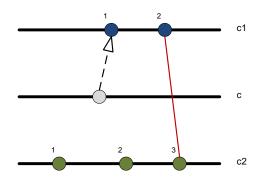

Figure 1.4 shows an example, where values are not displayed.  $\mathcal{T}$  is a set of tags and the solid arrows denote the partial order  $\leq$ . Each bold line represents a behavior for a given variable. The dashed lines are the clocks for this behavior, the blue (upper) ones for variable v1 and the red (lower) ones for variable v2. Note that, the third event of v2 in  $\sigma$  has the same tag than the second event of v1 in  $\sigma$ . The two events occur at the same time, they are *coincident*.

Figure 1.4: Tag structure by example

We consider that *clocks* are central in such a model as they are in synchronous languages. We propose a time model that abstracts away the values and focuses on the clocks themselves. Figure 1.5 shows the same example with logical clocks. The clock *c*1 represents the clock of  $\sigma(v1)$ , whereas *c*2 represents the clock of  $\sigma(v2)$ . Clock *c* is introduced to capture the lonely tag not used in any of these two behaviors. The plain vertical connection (in red) denotes a coincidence. The two instants (circles) represent occurrences of events that are *a priori* independent. Forcing a simultaneous occurrence of the events is done by mapping them to the same tag in the tag structure model and by adding a *coincidence* relation in our model. The dashed arrow denotes the precedence relationship that gives the ordering between the occurrences of the two events. In this model, our clock is more an element of  $2^{\mathcal{T}}$  with a proper total order relation rather than a mapping to  $\mathcal{T}(\mathcal{T}^{\mathbb{N}})$  as in tag structures.

Figure 1.5: Logical clocks by example

The next section discusses further the notions of logical time and clocks independently of any specific model.

### 1.4 Logical time and logical clocks

Tag structures go beyond event structures by considering tags, which provide a support to model timed systems. The word *time* is used here in a very broad sense where the relative ordering between events primes over the actual date. This *logical time* is widely used in models dedicated to embedded, real-time, reactive systems and in particular it is the time model in use in synchronous languages [BCE<sup>+</sup>03]. Discrete-time *logical clocks* (or simply logical clocks) represent/measure the logical time. Clocks that refer to the "physical time" or real-time are called *chronometric clocks*. Logical clocks as originally defined by Lamport [Lam78] are a special case introduced as a support to build a distributed synchronization algorithm.

Logical time is sometimes qualified as multiform. Indeed, when renouncing to represent the physical time only, the same model can be used to represent chronological relationships between events on different natures. Chronology being the order in which a series of events occur. The events can be ticks of a processor or cycles of a communication bus, but also ticks emit by sensor that measures the rotation degree of a crankshaft in an engine or the sending of a message between two components.

(Logical) clocks are central in synchronous languages and play an important role in tag structures. We propose a model called the Clock Constraint Specification Language (CCSL) dedicated to building logical clocks and expressing relations on clocks. CCSL is described in the following chapter.

CHAPTER 1. BACKGROUND

# Chapter 2

# The Clock Constraint Specification Language

The Clock Constraint Specification Language (CCSL) has initially been introduced as a companion language for the UML profile for MARTE (Modeling and Analysis of Real-Time and Embedded systems). It has then become a domain-specific language (DSL) on its own and it is now developed independently. It aims at being a specification language to equip syntactic models (UML-based or other DSLs) with a timed causality model that explicitly expresses the causal and chronological relationships amongst events of the modeled systems.

The initial intent of MARTE being to cover both design and analysis, a large set of CCSL constraints have been introduced for convenience on top of a relatively small set of kernel primitives. Section 2.1 introduces the CCSL time model. Section 2.2 discusses some fundamental coincidence and precedence constraints. Then, Section 2.3 presents the integration of this model into UML, through MARTE stereotypes.

### 2.1 Instants, clocks and time structures

CCSL focuses on the events and their occurrences and abstracts away the values. This is a major difference with other related models (Signal, Tag structures), which usually

consider an event as a pair value/time stamp. In CCSL, the value may be added as an annotation and never influences the scheduling in any way. CCSL deals with sets of event occurrences  $\mathcal{I}$ , called instants to avoid the possible confusion between the events and their occurrences. On these events we build a *time structure*  $\langle \mathcal{I}, \prec, \equiv \rangle$  by considering the two primitive binary relations: strict precedence (denoted  $\prec$ ) and the *coincidence* (denoted  $\equiv$ ).  $\prec$  is irreflexive and transitive, it is only a partial relation and therefore is not asymmetric, there can be instants that are not related to each other. The coincidence is a direct emanation of synchronous languages.  $\equiv$  is a partial equivalence relation, *i.e.*, reflexive, transitive and symmetric. The coincidence is the major difference with the general net theory and the event structures because it forces one instant to occur when another has occurred or prevents an event from occurring when another one is not ready. The coincidence is universal, no referential can tell apart two coincident instants. Petri's model (following the relativity theory) restricts coincidence to single points in space-time. In CCSL, the coincidence relationship "melts" a priori independent points (instants) to reflect design choices and thus is a foundational relation.

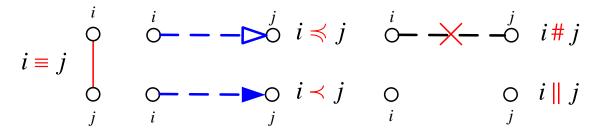

From these two relations, we build three more: exclusion (denoted #), precedence (denoted  $\preccurlyeq$ ) and independence (denoted  $\parallel$ ). The exclusion is when the instants can never be coincident. Note, that this definition of exclusion is weaker than the exclusion of event structures (see section 1.2), since it does permanently prevent the other event from occurring but just prevents them from being coincident. The precedence is the union of the strict precedence and the coincidence. It is the equivalent of the causality relation in event structures and  $\preccurlyeq$  is a partial pre-order, *i.e.*, it is reflexive and transitive but neither antisymmetric, nor asymmetric. If  $a \preccurlyeq b$  and  $b \preccurlyeq a$  then a is not necessarily identical to b but is coincident with it ( $a \equiv b$ ). The graphical representation of instant relations is given in Figure 2.1.

All these relations are defined on instants (event occurrences). However, in a specification, it is more likely to talk about the events themselves and therefore we define a *clock* c as a totally ordered set of instants  $\mathcal{I}_c$ .  $\langle \mathcal{I}_c, \preccurlyeq _c \rangle$  is a total order<sup>1</sup>.  $\preccurlyeq _c$  is

$<sup>^1\</sup>mathrm{Colors}$  distinguish the total order on clocks in blue from the partial order on the time structure in red

Figure 2.1: Graphical representation of instant relations

antisymmetric since no two instants of a given clock can be coincident without being identical. We chose the word clock, instead of events or signals to avoid confusion with these highly overridden words. The word comes from the synchronous languages, in which the clock is a pure signal (without values). It represents events, but the word event is sometimes used to denote the occurrences and sometimes to denote the classes of occurrences. Additionally, event also exists in UML and we therefore needed another word. Note that the set of instants can be either dense or discrete. A *discrete-time clock* is a clock c with a discrete set of instants  $\mathcal{I}_c$ . Since  $\mathcal{I}_c$  is discrete, it can be indexed by natural numbers in a fashion that respects the ordering on  $\mathcal{I}_c$ : let  $\mathbb{N}^* = \mathbb{N} \setminus \{0\}$ , idx :  $\mathcal{I}_c \to \mathbb{N}^*$ ,  $\forall i \in \mathcal{I}_c$ , idx(i) = k if and only if i is the  $k^{\text{th}}$  instant in  $\mathcal{I}_c$ . c[k] is defined so as  $\forall k \in \mathbb{N}^*$ , idx(c[k]) = k. °i is the unique immediate predecessor of i in  $\mathcal{I}_c$ . For simplicity, we assume a virtual instant (called birth) the index of which is 0, and which is considered as the immediate predecessor of the first instant.

From a set of clocks C, we build a time structure  $\langle \mathcal{I}, \prec, \equiv \rangle$  such that

- $\mathcal{I} = \bigcup_{c \in C} \mathcal{I}_c$

- $\prec = \bigcup_{c \in C} \prec_c$ , where  $\prec_c$  is the reflexive reduction of  $\preccurlyeq_c$  for a clock c

- $\equiv = Id_{\mathcal{I}}$

Instant relations are then extended to clock relations, which usually represent infinitely many instant relations at once. The following section explains how, given a set of clocks and its underlying time structure, we augment it by considering a given specification, a set of clock relations *Rel*.

### 2.2 Clock constraints

Specifying a full time structure using only instant relations is not realistic, all the more so since a clock usually has an infinite number of instants therefore forbidding an enumerative specification of instant constraints. Instead of defining individual instant pairings, a clock constraint specifies generic associations between (infinitely) many instants of the constrained clocks.

In this section we define the most general clock constraints and we introduce some usual constraints, derived from the basic ones. The clock constraints are classified in three main categories: 1) coincidence-based constraints, 2) precedence-based constraints, and 3) mixed constraints.

Actually, most constraints only partially constrain the systems and therefore several time structures are possible. So a specification induces a set of time structures that share the same set of instants  $\mathcal{I}$ . For one given time structure TS,  $\mathcal{I}_{TS} = \mathcal{I}$ denotes its set of instants,  $\prec_{TS}$  is its precedence relation and  $\equiv_{TS}$  its coincidence relation.

#### 2.2.1 Coincidence-based clock constraints

Coincidence-based clock constraints are classical in synchronous languages and can then be very easily specified with such languages.

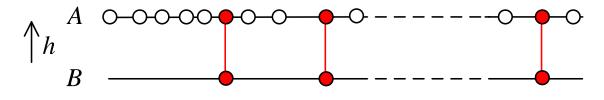

**Sub-Clocking** is the most basic coincidence-based clock constraint relationship. Let a, b be two clocks. The clock relation b isSubClockOf a imposes b to be a subclock of a. Intuitively, this means that each instant in b is coincident with exactly one instant in a (Figure 2.2). More formally, a time structure  $TS = \langle \mathcal{I}, \prec_{TS}, \equiv_{TS} \rangle$ satisfies the clock relation b isSubClockOf a if and only if there exists an injective mapping  $h: \mathcal{I}_b \to \mathcal{I}_a$  such that :

(1) h is order preserving:

$$(\forall i, j \in \mathcal{I}_b) \ (i \ \preccurlyeq _b j) \implies (h(i) \ \preccurlyeq _a h(j))$$

(2) an instant of  $\mathcal{I}_b$  and its image are coincident:

$$(\forall i \in \mathcal{I}_b) \ i \equiv {}_{TS} \ h(i)$$

Figure 2.2: Coincidence-based clock constraint

In what follows, this constraint is denoted as  $b \subseteq a$ , read "b is a sub-clock of a" or equivalently "a is a super-clock of b".

#### 2.2.2 Derived coincidence-based clock constraints

h can be specified in many different ways.

**Equality**  $a \equiv b$  is the symmetric relation that makes the two clocks a and b "synchronous": h is a bijection and the instants of the two clocks are pair-wise coincident. It is strictly equivalent to  $b \equiv a$ .

Other coincidence-based *clock expressions* allow the creation of a new clock, subclock of a given clock (denoted *new clock*  $\triangleq$  *defining expression*). Three such clock expressions are presented hereafter. **Restriction**  $b \triangleq a$  restricted To P where a is a given clock, b is a new clock, and P is a predicate on  $\mathcal{I}_a \times \mathcal{I}_b$ , such that

$$(\forall i \in \mathcal{I}_A, \forall j \in \mathcal{I}_B) \ i \equiv h(j) \iff P(i,j) = \mathsf{true}$$

**Filtering**  $b \triangleq a$  filteredBy w, where a and b are discrete-time clocks, and w is a binary word. For filtering, the associated predicate is such that

$$(\forall i \in \mathcal{I}_a, \forall j \in \mathcal{I}_b) (P(i, j) = \mathsf{true} \iff \mathrm{idx}_a(i) = w \uparrow \mathrm{idx}_b(j))$$

where  $w \uparrow k$  is the index of the  $k^{\text{th}}$  1 in w. The use of infinite k-periodic binary words in this kind of context has previously been studied in N-Synchronous Kahn networks [CDE<sup>+</sup>06]. This constraint is frequently used in clock constraint specifications and is denoted  $A \checkmark w$  in this document. It allows the selection of a subset of instants, on which other constraints can then be enforced.

In what follows, a (periodic) binary word is denoted as  $w = u(v)^{\omega}$ , where u is called the *transient* part of w and v its *periodic* part. The power  $\omega$  means that the periodic part is repeated an unbounded number of times. So,  $u(v)^{\omega}$  denotes  $u.v.v.\cdots v.\cdots$ .

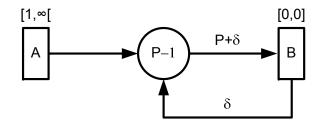

**Periodicity** Defining the periodicity of discrete clocks consists in using a binary word with a single 1 in the periodic part. b isPeriodicOn a period p offset d defines a periodic clock b. The same clock can be built with a filtering  $b \triangleq a \lor 0^d \cdot (1.0^{p-1})^{\omega}$ . In this expression, for any bit  $x, x^0$  stands for the empty binary word. Note that this is a very general definition of periodicity that does not require a to be chronometric contrary to the usual definition.

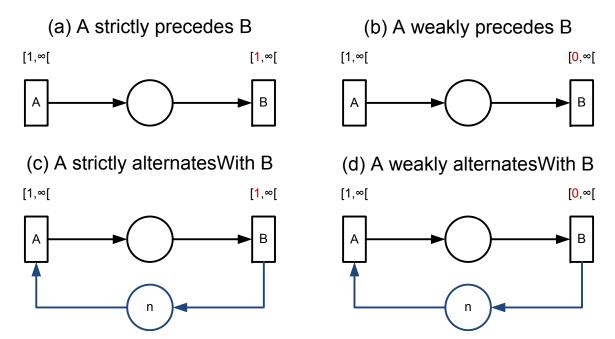

#### 2.2.3 Precedence-based clock constraints

Precedence-based clock constraints are easy to specify with concurrent models like Petri nets but are not usual in synchronous languages. A discussion on main differences with Time Petri nets can be found in some of our previous work [MA09]. **Precedence** The clock constraint Precedence consists in applying infinitely many precedence instant relations. Two forms can be distinguished: the strict precedence *a* strictly precedes *b*, and the non strict precedence *a* precedes *b*. Intuitively, this means that each instant in *b* follows one instant in *a* (Fig. 2.3). More formally, a time structure  $TS = \langle \mathcal{I}, \prec_{TS}, \equiv_{TS} \rangle$  satisfies the clock relation *a* precedes *b* if and only if there exists an injective mapping  $h: \mathcal{I}_b \to \mathcal{I}_a$  such that :

(1) h is order preserving:

$(\forall i,j \in \mathcal{I}_b) \ (i \ \preccurlyeq _b j) \implies (h(i) \ \preccurlyeq _a h(j))$

(2) an instant of  $\mathcal{I}_b$  and its image are ordered:

$(\forall i \in \mathcal{I}_b)(h(i) \preccurlyeq _{TS} i)$  for the non strict precedence  $(\forall i \in \mathcal{I}_b)(h(i) \prec _{TS} i)$  for the strict precedence

Figure 2.3: Precedence-based clock constraint

#### 2.2.4 Derived precedence-based clock constraints

When a and b are discrete clocks, the precedence relationship gives rise to more specific constraints. Three often used precedence constraints are discussed here.

**Discrete precedence** A time structure TS satisfies a strictly precedes b (denoted  $a \prec b$ ) iff

$$(\forall i \in \mathcal{I}_b)(k = \mathrm{idx}_b(i)) \implies a[k] \prec_{TS} b[k]$$

There also exists a weak form (denoted  $a \leq b$ ) of this constraint where  $\prec_{TS}$  is replaced by  $\preccurlyeq_{TS}$ .

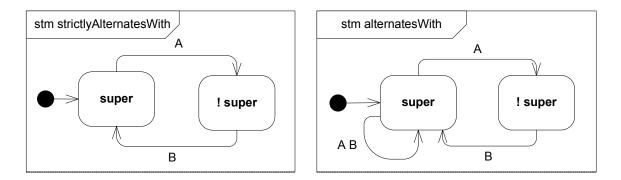

**Alternation** A time structure TS satisfies a alternatesWith b (denoted  $a [\sim] b$ ) iff:

$(a \triangleleft b) \land (b \triangleleft a')$ , where  $a' \triangleq a \lor 0.1^{\omega}$

The equivalent following specification uses instant relations instead of clock relations,  $(\forall i \in \mathcal{I}_a)(k = \operatorname{idx}_a(i)) \implies (a[k] \prec_{TS} b[k] \land b[k] \prec a[k+1]).$

**Synchronization** A time structure TS satisfies a synchronizesWith b (denoted  $a \bowtie b$ ) iff

$$\begin{pmatrix} a \Join b' \end{pmatrix} \land \begin{pmatrix} b \leftthreetimes a' \end{pmatrix}$$

where  $a' \triangleq a \lor 0.1^{\omega}$ , and  $b' \triangleq b \lor 0.1^{\omega}$

This constraint can also be expressed using instant relations:

$$(\forall k \in \mathbb{N}^*)(a[k] \preccurlyeq T_S b[k+1]) \land b[k] \preccurlyeq T_S A[k+1]).$$

Precedences used in the definition of *Alternation* and *Synchronization* can be nonstrict precedences, thus there exist four different variants of these clock relations. Another extension considers instants by "packets". For instance, a by  $\alpha$  strictly precedes b by  $\beta$ (denoted  $a/\alpha \prec b/\beta$ ) is a short notation for

$$\left(a_{f} \Join b_{s}\right)$$

where  $a_{f} \triangleq a \checkmark \left(0^{\alpha-1}.1\right)^{\omega}$ , and  $b_{s} \triangleq b \checkmark \left(1.0^{\beta-1}\right)^{\omega}$

#### 2.2.5 Mixed constraints

Mixed constraints combine coincidences and precedences. They are used to synchronize clock domains in globally asynchronous and locally synchronous models.

#### 2.2. CLOCK CONSTRAINTS

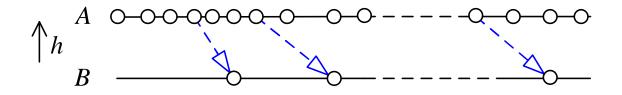

**Sampling** The commonest constraint of this kind is the *Sampling* constraint.  $c \triangleq a$  sampledOn b, where b and c are discrete clocks and a can be either discrete or dense, constraints the clocks a, b and c so that c is a sub-clock of b that ticks only after a tick of a (Fig. 2.4). A time structure TS satisfies  $c \triangleq a$  sampledOn b iff

$$(\forall i_c \in \mathcal{I}_c)(\exists i_b \in \mathcal{I}_b)(\exists i_a \in \mathcal{I}_a)(i_c \equiv {}_{TS} i_b) \land (i_a \preccurlyeq {}_{TS} i_b) \land (^\circ i_b \prec {}_{TS} i_a)$$

Figure 2.4: Sampling constraints

A time structure TS satisfies the strict form  $c \triangleq a$  strictly sampledOn b iff:  $(\forall i_c \in \mathcal{I}_c)(\exists i_b \in \mathcal{I}_b)(\exists i_a \in \mathcal{I}_a)(i_c \equiv TS i_b) \land (i_a \prec TS i_b) \land (\circ i_b \preccurlyeq TS i_a)$

**Delay** A slight variation of the sampling is the *Delay* constraint.  $c \triangleq a$  delayedFor N b (also denoted  $c \triangleq a \$_b N$ ) samples the clock a on the  $N^{th}$  occurrence of the discrete clock b. c is necessary discrete and is a subclock of b. a can be either discrete or dense.

Note that this operator is polychronous, contrary to usual synchronous delay operators (pre in Lustre, \$ in Signal). There is also a binary variant of this ternary operator denoted \$ and which is equivalent to a delay when a is synchronous with b.  $c \triangleq a$  \$ N is equivalent to  $c \triangleq a$  \$\_a N.

#### 2.2.6 TimeSquare

Most constraints only partially constrain the system, which means that several (possibly infinitely many) time structures may satisfy a set of constraints. Timesquare has been built to implement CCSL and provide support for the analysis of CCSL specifications. Several kinds of analyses are possible. Given a set of clocks and a set of constraints, the clock calculus engine can find one possible time structure that satisfies all the constraints. Actually, this is done in simulation and the time structure is only built partially up to the current simulation point. Since it is not always possible to choose a single time structure in a deterministic way the simulation may be non determinate. The clock calculus relies on CCSL structural operational semantics (SOS) to run the simulation. A description of the SOS semantics is available in [And09]. The CCSL constraints are encoded as a set of Boolean equations that determines at each step, which clock can is enabled and which one is not. With non deterministic specifications several solutions (each of which may involve several clocks) may be valid. A simulation policy is then used to pick one solution and fire the associated clocks. Depending on which clocks were fired, the rewriting rules allows to process a new set of boolean equations. This ends the current simulation step and the simulation engine proceeds to the next one. Several simulation policies are offered. For instances, the *random policy* randomly chooses one possible solution amongst the set of solutions. The *minimum policy* chooses a consistent solution where the number of firing clocks is minimal. The *maximum policy* chooses a consistent solution where the number of firing clocks is maximal.

Another kind of analyses is also possible. Given a time structure (*e.g.*, defined as a by-product of the execution of some code) and a CCSL specification, one can verify whether the time structure satisfies all the constraints in the specification. This aspect is described further in the third part of this document. The time structure is given by an existing implementation of the system on which we have no control. The implementation forces some clocks to tick while preventing others to be fired. Our observer-based verification technique can be used to check that the implementation satisfies all the constraints of the specification.

TimeSquare has been implemented as a set of Eclipse plugins and is available for

download at http://www.inria.fr/sophia/teams/aoste/dev/time\_square. Time-Square is protected by the APP (Agence pour la protection des programmes).

### 2.3 UML for Real-Time and Embedded systems

#### 2.3.1 UML, SPT, Marte

The Unified Modeling Language (UML) [OMG09b] is a general-purpose modeling language specified by the Object Management Group (OMG). It proposes graphical notations to represent all aspects of a system from the early requirements to the deployment of software components, including design and analysis phases, structural and behavioral aspects. As a general-purpose language, it does not focus on a specific domain and maintains a weak, informal semantics to widen its application field. However, when targeting a specific application domain and especially when building trustworthy software components or for critical systems where life may be at stake, it is absolutely required to extend the UML and attach a formal semantics to its model elements. The simplest and most efficient extension mechanism provided by the UML is through the definition of profiles. A UML profile adapts the UML to a specific domain by adding new concepts, modifying existing ones and defining a new visual representation for others. Each modification is done through the definition of annotations (called stereotypes) that introduce domain-specific terminology and provide additional semantics. However, the semantics of stereotypes must be compatible with the original semantics (if any) of the modified or extended concept.

The UML profile for Modeling and Analysis of Real-Time and Embedded systems (MARTE [OMG09a]) extends the UML with concepts related to the domain of real-time and embedded systems. It supersedes the UML profile for Schedulability, Performance and Time (SPT [OMG05]) that was extending the UML 1.x and that had limited capabilities. MARTE has three parts: *Foundations*, *Design* and *Analysis*.

The foundation part is itself divided into five chapters: *CoreElements*, *NFP*, *Time*, *Generic Resource Modeling* and *Allocation*. *CoreElements* defines configurations and modes, which are key parameters for analysis. In real-time systems, preserving the non-functional (or extra-functional) properties (power consumption, area, financial cost, time budget...) is often as important as preserving the functional ones. The UML proposes no mechanism at all to deal with non-functional properties and relies on mere String for that purpose. NFP (Non Functional Properties) offers mechanisms to describe the quantitative as well as the qualitative aspects of properties and to attach a unit and a dimension to quantities. It defines a set of predefined quantities, units and dimensions and supports customization. NFP comes with a companion language called VSL (Value Specification Language) that defines the concrete syntax to be used in expressions of non-functional properties. VSL also recommends syntax for user-defined properties. Time is often considered as an extra-functional property that comes as a mere annotation after the design. These annotations are fed into analysis tools that check the conformity without any actual impact on the functional model: e.q., whether a deadline is met, whether the end-to-end latency is within the expected range. Sometimes though, time can also be of a functional nature and has a direct impact on what is done and not only when it is done. All these aspects are addressed in the time chapter of MARTE [AMdS07]. The next section elaborates on the time profile.

The design part has four chapters: High Level application modeling, Generic component modeling, Software Resource Modeling, and Hardware Resource Modeling. The first chapter describes real-time units and active objects. Active objects depart from passive ones by their ability to send spontaneous messages or signals, and react to event occurrences. Passive objects can only answer to the messages they receive. The three other parts provide a support to describe resources used and in particular the execution platform on which the application may run. A generic description of resources is provided, including stereotypes to describe communication media, storages and computing resources. Then this generic model is refined to describe software and hardware resources along with their non-functional properties.

The analysis part also has a chapter that defines generic elements to perform model-driven analysis on real-time and embedded systems. This generic chapter is specialized to address schedulability analysis and performance analysis. The chapter on schedulability analysis is not specific to a given technique and addresses various formalisms like the classic and generalized Rate Monotonic Analysis (RMA), holistic techniques, or extended timed automata. This chapter provides all the keywords usually required for such analyses. In Chapter 5 of this document, we follow a rather different approach and instead of focusing on syntactic elements usually required to perform schedulability analysis (periodicity, task, scheduler, deadline, latency), we show how we can use MARTE time model and its companion language CCSL to build libraries of constraints that reflect the exact same concepts. Finally, the chapter on performance analysis, even if somewhat independent of a specific analysis technique, emphasizes on concepts supported by the queueing theory and its extensions.

MARTE extends the UML for real-time and embedded systems but should be refined by more specific profiles to address specific domains (avionics, automotive, silicon) or specific analysis techniques (simulation, schedulability, static analysis). The three examples addressed here consider different domains and/or different analysis techniques to motivate the demand for a fairly general time model that has justified the creation of MARTE time subprofile.

#### 2.3.2 Marte Time profile

Time in SPT is a *metric* time with implicit reference to physical time. As a successor of SPT, MARTE supports this model of time. UML 2, issued after SPT, has introduced a model of time called *SimpleTime* [OMG09b, Chap. 13]. This model also makes implicit reference to physical time, but is too simple for use in real-time applications and was, right from the beginning, expected to be extended in dedicated profiles.

MARTE goes beyond SPT and UML 2. It adopts a more general time model suitable for system design. In MARTE, Time can be *physical*, and considered as *dense*, but it can also be *logical*, and related to user-defined clocks. Time may even be *multiform*, allowing different times to progress in a non-uniform fashion, and possibly independently to any (direct) reference to physical time.

In MARTE, time is represented by a collection of *Clocks*. Each clock specifies a totally ordered set of instants (see Section 2.1). There may be dependence relationships between instants of different clocks. In practice, clocks should be associated

with events whose occurrence should be constrained or with events used to constrain others. In UML, TimeEvent is specialization of Event stating that this special kind of events can carry a time stamp. Our intent is to allow any kind of event to carry a time stamp. For instance, the goal would be to constrain the way a message is sent or received, a behavior starts or finishes its execution. Therefore time (or causality) must be orthogonal to the various events and not a special kind of events.

The MARTE Time profile defines two stereotypes ClockType and Clock to represent the concept of clock. ClockType gathers common features shared by a family of clocks. The ClockType fixes the nature of time (dense or discrete), says whether the represented time is linked to physical time or not (respectively identified as chronometric clocks and logical clocks), chooses the type of the time units. A Clock, whose type must be a ClockType, carries more specific information such as its actual unit, and values of quantitative (resolution, offset, etc.) or qualitative (time standard) properties, if relevant.

TimedElement is another stereotype introduced in MARTE. A timed element is *explicitly bound* to at least one clock, and thus closely related to the time model. For instance, a TimedEvent, which is a specialization of TimedElement extending UML Event, has a special semantics compared to usual events: it can occur only at instants of the associated clock. In a similar way, a TimedValueSpecification, which extends UML ValueSpecification, is the specification of a set of *time values* with explicit references to a clock, and taking the clock's unit as time unit. Thus, in a MARTE model of a system, the stereotype TimedElement or one of its specializations is applied to model elements which have an influence on the specification of the temporal behavior of this system.

The MARTE Time subprofile also provides a model library named TimeLibrary. This model library defines the enumeration TimeUnitKind which is the standard type of time units for chronometric clocks. This enumeration contains units like s (second), its submultiples, and other related units (minute, hour...). The library also predefines a clock type (IdealClock) and a clock (idealClk) whose type is IdealClock. idealClk is a dense chronometric clock with the second as time unit. This clock is assumed to be an ideal clock, perfectly reflecting the evolutions of physical time. idealClk should be

imported in user's models with references to physical time concepts (*i.e.*, frequency, physical duration, etc.).

#### 2.3.3 UML and formal methods

The UML is a general-purpose modeling language. Its semantics is described in English in the OMG specification. Several aspects are left unspecified in so-called *semantic variation points* to allow user-defined adaptations for addressing domain-specific issues. There have been many efforts to use the UML in formal environments to address critical systems or domains where formal verification is mandatory. A brief classification is attempted hereafter even though it is usually acknowledged [BLMF00] that building a full taxonomy is difficult:

- 1. The first kind consists in using a formal language to build UML expressions and/or constraints. Since, UML does not enforce any specific syntax for expressions and constraints, any language can be used. Even though the Object Constraint Language (OCL) [OMG06] may seem the most natural choice, formal languages (e.g., Z [GL00], Labelled Transition Systems [SCK09]) are also used to specify invariants in UML use cases or pre-conditions/post-assertions on UML operations. Then, scenarios (UML interaction diagrams) or behaviors (state machines or activities) are statically analyzed [CPC<sup>+</sup>04, GBR07, YFR08] to check whether the use case invariants and the post-assertions hold.

- 2. The second kind of approaches is *transformational*. It consists in transforming every UML model element into a model element of a formal language (for instances, Petri Nets [Stö05] or  $\pi$ -calculus [YsZ03]). After transformation, various analyses become possible, like symbolic model-checking [Esh06].

- 3. In the third kind, the semantics resides in annotations (stereotypes). For instance, the semantics of Concurrent Sequential Processes [Hoa78] can be given to a UML state machine provided that a UML profile for Concurrent Sequential Processes [FGL<sup>+</sup>08] is defined.

4. In the fourth kind, only a subset of the UML is allowed to make it suitable for a specific domain, *e.g.*, the UML state machines can be reduced to timed automata [AD94] thus giving access to a whole family of formal tools [BDL<sup>+</sup>06].

In all cases, the semantics remains outside the model and therefore the model may be interpreted differently by another tool or another user. The purpose of CCSL is to provide a domain-specific language (DSL) to build an explicit semantic model that would be linked into the model itself to define its time/causal semantics. Our approach is not specific to UML models and can be used with domain-specific models as well. We propose to use the MARTE time model and its companion language CCSL (Clock Constraint Specification Language) to build the semantic model.

#### 2.3.4 UML and synchronous languages

Synchronous languages [Hal92, BCE<sup>+</sup>03] are well-suited to formal specification and analysis of reactive system behavior. They are even more relevant with safety-critical applications where lives may be at stake. However, to cover a complete design flow from system-level specification to implementation, synchronous languages need to interoperate with other, more general, specification languages. One of the candidates is the UML associated with SysML, the UML profile for systems engineering [Wei08, OMG08]. This is very tempting since synchronous languages internal formats rely on state machines or data flow diagrams both very close to UML state machines and activities. Moreover, SyncCharts [And96] are a synchronous, formally well-founded, extension of UML state machines and are mathematically equivalent to Esterel [Ber00], one of the three major synchronous languages. As for SysML, it adds two constructs most important for specification: requirements and constraint blocks (see 2.3.5).

There have been attempts to bridge the gap between the UML and synchronous languages. Some [LD06] choose to import UML diagrams into Scade, a synchronous environment that combines *Safe State Machines* (SSM—a restriction of SyncCharts) together with block diagrams, the semantics of which is based on Lustre. Others [BRG<sup>+</sup>01] prefer to define an operational semantics of UML constructs with a synchronous language, like SIGNAL. In both cases, the semantics remains outside the UML and within proprietary tools. Other tools, from the same domain, would interpret the same models with a completely different semantics, not necessarily compatible. Therefore, it is impossible to exchange diagrams between tools, not only because of syntactical matters but also for semantic reasons. Different environments are then competing rather than being complementary. To provide full interoperability between tools of the embedded domain, the UML absolutely requires a timed causality model. The UML Profile for MARTE has introduced a time model with that purpose (see 2.3.1). Its companion language, CCSL is advertised as a pivot language to make explicit the interactions between different models of computations [MAdS08], like Ptolemy directors [EJL<sup>+</sup>03]. It offers a rich set of constructs to specify time requirements and constraints.

#### 2.3.5 SysML/Marte

The UML profile for System Engineering (SySML) [OMG08] is an adopted OMG Specification to be used at the system level. SySML is based on a selected subset of UML constructs, called UML4SysML, and provides few new extensions amongst which *Refinement* and *Parametric* diagrams. The former helps making explicit system-level requirements and tracing their proposed implementations. The latter should be used to represent "non-causal" relationships amongst values of the system and possibly making explicit within the model, physical laws required for the design. "non-causal" is used here to denote equations in which variables are not assigned a particular role or direction. In  $F = m \times \gamma$ , no distinction is made between F, m and  $\gamma$ . A causal or functional interpretation would have considered m and  $\gamma$  as inputs and F as an output.

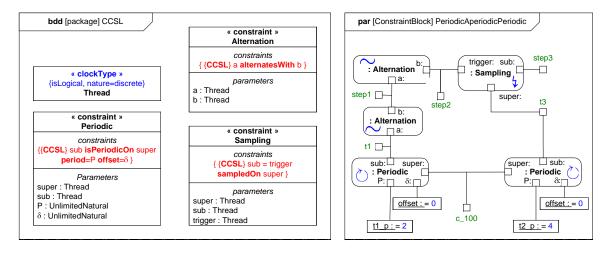

So, we can use this SySML construct to represent laws related to time, whether physical or logical. SySML recommends building a new "Constraint Block" for each new law and uses these blocks in so-called *parametric diagrams* to apply a law to relevant design values. In CCSL, there is a small number of identified relations among logical clocks. Consequently, we can easily construct a library of CCSL-specific constraint blocks. Figure 2.5 shows a CCSL specification expressed using SySML constraint

blocks and parametric diagrams.

Figure 2.5: SysML parametric diagrams

The left-hand side part is an excerpt of the library. Three constraint blocks (Periodic, Alternation, Sampling) have been defined for each of the three CCSL relations introduced previously. Each constraint block has three compartments. The bottom one, called *parameters* contains typed *formal* parameters. The middle compartment, called *constraints*, contains the constraint itself that applies on the parameters. In our case, the constraint is defined in CCSL. However, this library is built once and for all, so end-users need not being entirely familiar with the concrete syntax and only need to be familiar with underlying concepts.

The right-hand side part models the following CCSL specification as a SySML parametric diagram:

```

t1 isPeriodicOn c_100 period=2 offset=0 // periodic thread t1

t3 isPeriodicOn c_100 period=4 offset=0 // periodic thread t3

t1 alternatesWith step1 // t1 executes step1

step1 alternatesWith step2 // step2 starts when step1 finishes

step3 = step2 sampledOn t3 // step3 samples the result from step2

```

In such a diagram, boxes are properties extracted from the model. Some of the properties are clocks (t1, step1 ...), some others have integer values (offset,  $t1_p$  ...). These properties may come from different diagrams and different blocks. The

rounded rectangles are usages of constraint blocks. Their ports, which represent parameters, are connected with properties using non-causal connectors. Being noncausal means that there is no input or output, whichever value is known causes the other to update. For instance, considering Alternation, if b is known, one can deduce (partially) a but if a is known, then one can deduce (partially) b. This example is further presented in Chapter 5.

# 2.4 The future of MARTE Time Model

MARTE v1.0 has been adopted in November 2009 and the first revision committee should release MARTE v1.1 by the end of 2010. The major modification in revision v1.1 concerning the time model is to authorize the stereotype «clock» to extend the metaclass «Event». The intent of this modification is to make it clear that any event of any kind (Call, Time, Send, ...) can be used as a logical time base in time specifications. They are no major modifications anticipated for release v1.2, but we shall continue our effort to disseminate MARTE and to increase the tool support. A second important requirements is to maintain and enhance the compatibility with SySML. The objective of next year being to provide SySML with a lighter time model that would be compatible with MARTE. SySML users do not seem ready to accept a textual language (like CCSL). Working with predefined domain-specific libraries as explained in Section 2.3.5 is one possible solution. An alternative would be to provide a better integration with the OMG's Object Constraint Language (OCL), more and more used, by offering a logically timed OCL. Timed OCL extensions already exist [F02] but propose to extend OCL with temporal logics constructs which is rather different from our objective.

# 32 CHAPTER 2. THE CLOCK CONSTRAINT SPECIFICATION LANGUAGE

# Chapter 3

# How does CCSL compare ?

This chapter compares CCSL to other closely related concurrent models: Petri Nets, Process networks, Signal. The comparison to Petri Nets and to Signal has been published at ISORC'09 [MA09] and the work on using the hierarchization mechanism has been published in the workshop MOBE-RTS [YTB<sup>+</sup>10]. The comparison to process networks have been accepted to be published in September 2010 in the proceedings of FDL 2010.

## 3.1 Petri Nets

#### 3.1.1 Time Petri nets

MARTE Time model conceptually differs from Petri's work on concurrency theory [Pet87]. Petri's theory restricts coincidence to single points in space-time. In our model, the foundational relationship *coincidence* gathers *a priori* independent points (instants) to reflect design choices.

Petri nets have well-established mathematical foundations and offer rich analysis capabilities. They support true concurrency and can be used to specify some of our clock relations. However it is not possible to force two separate transitions to fire "at the same time", *i.e.*, to express coincidence. Thus, we use Time Petri net, the Merlin's extension [Mer74] that associates a time interval (two times a and b, with  $0 \le a \le b$  and b possibly unbounded) with each transition. Times a and b, for transition t, are relative to the moment  $\theta$  at which the transition was last enabled. tmust not fire before time  $\theta + a$  and must fire before or at time  $\theta + b$  unless it is disabled (in case of conflicts) by the firing of another transition. Even with this extension, the specification of CCSL constraints is far from straightforward.

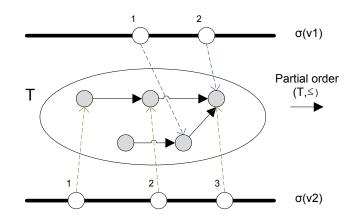

In our representation, each MARTE discrete-time pure clock  $c = \langle \mathcal{I}_c, \prec_c \rangle$  is represented as a single transition  $c_t$  (called *clock transition*) of a Time Petri net. Instants of a clock are *firings* of the related transition. For a given initial marking and for a given firing sequence, there is an injective function  $firing : CT \times \mathbb{N}^* \to \mathbb{N}$ , where CTis the set of clock transitions.  $firing(c_t, i)$  is the time at which, the clock transition  $c_t$ fires for the  $i^{\text{th}}$  time in the firing sequence. We consider a Time Petri net as equivalent to a CCSL clock constraint, iff for all possible firing sequences and all clock transitions (other transitions do not matter), firing preserves the ordering (Eq. 3.1).

$$(\forall c1, c2 \in C)(\forall k1, k2 \in \mathbb{N}^{\star})$$

$$((c1[k1] \preccurlyeq c2[k2])$$

$$(3.1)$$

$$\Leftrightarrow (firing(c1_t, k1) \leq firing(c2_t, k2))$$

where  $c1_t$  (resp.  $c2_t$ ) is the clock transition associated with clock c1 (resp. c2). Note that, even though Time Petri nets can handle continuous time, we restrict our comparison to discrete-time clocks and therefore we consider the transition firing time as a natural number ( $\in \mathbb{N}$ ).

### 3.1.2 Encoding CCSL operators in Time Petri nets

#### Precedence

CCSL strict precedence has a straightforward equivalent in Time Petri net (Fig. 3.1(a)). Note that the time interval  $[1, \infty]$  of A prevents multiple firing of transition A at the same time. This condition can be weakened if needed. However, the time interval  $[1, \infty]$  for B ensures the strictness of the relation: the  $i^{th}$  occurrence of B is strictly after the  $i^{th}$  occurrence of A in any valid behavior. The weak form of the precedence (depicted in Figure 3.1(b)) weaken the lower bound to allow simultaneous occurrences. In both cases, the place in-between the two transitions prevents B from ticking faster than A.

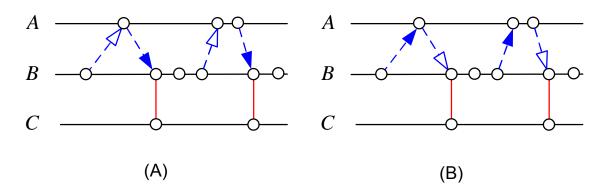

Figure 3.1: Precedence and alternation in Time Petri net

At the initial state (time=0) no transitions are enabled, only time can evolve. Then, transition A is enabled but there is no upper bound for its firing. Transition B will not become enabled before A fires. When A eventually fires, B becomes immediately enabled for the weak form and can fire "synchronously" with A. In the strict form, because of the time interval  $[1, \infty[, B \text{ must wait one instant before being enabled. Still, there is no upper bound.$

Clearly both models are not bounded, only A can tick leading to (infinite) accumulation of tokens in the intermediate place. Alternation bounds the model by adding a cycle (see Fig. 3.1(c)-(d)). The number n of tokens in the newly introduced place gives the maximum advance A can have on B: default is 1.

#### Subclocking