# Transient-Fault Robust Systems Exploiting Quasi-Delay Insensitive Asynchronous Circuits

Rodrigo Possamai Bastos

#### ▶ To cite this version:

Rodrigo Possamai Bastos. Transient-Fault Robust Systems Exploiting Quasi-Delay Insensitive Asynchronous Circuits. Micro and nanotechnologies/Microelectronics. Institut National Polytechnique de Grenoble, July 9, 2010. English. NNT: 2010INPG0070. tel-00541344

# HAL Id: tel-00541344 https://theses.hal.science/tel-00541344

Submitted on 30 Nov 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITE DE GRENOBLE INSTITUT POLYTECHNIQUE DE GRENOBLE

| Nº       | att | ribi | ué į     | par      | la | bib      | lio | thè | que | 9 |

|----------|-----|------|----------|----------|----|----------|-----|-----|-----|---|

| <u> </u> | _   |      | <u> </u> | <u> </u> | l  | <u> </u> | l   | l   |     |   |

#### THESE EN COTUTELLE INTERNATIONALE

pour obtenir le grade de

DOCTEUR DE L'Université de Grenoble délivré par l'Institut polytechnique de Grenoble et de l'Université Fédérale du Rio Grande do Sul

Spécialité : Micro et Nano Electronique

préparée au laboratoire TIMA (France)

dans le cadre de l'Ecole Doctorale Electronique, Electrotechnique, Automatique et Traitement du Signal

et aux laboratoires de l'Instituto de Informática (Brésil)

dans le cadre du Programa de Pós-Graduação em Microeletrônica

présentée et soutenue publiquement

par

#### **Rodrigo POSSAMAI BASTOS**

à Grenoble, le 9 Juillet 2010

## Transient-Fault Robust Systems Exploiting Quasi-Delay Insensitive Asynchronous Circuits

Directeurs de thèse : Marc RENAUDIN (France), Ricardo REIS (Brésil) Co-directeurs de thèse : Gilles SICARD (France) et Fernanda KASTENSMIDT (Brésil)

#### **JURY**

- M. Skandar BASROUR

- M. Christian PIGUET

- M. Matteo SONZA REORDA

- M. Marc RENAUDIN

- M. Ricardo REIS

- M. Gilles SICARD

- M. Gustavo WILKE

- , Président

- , Rapporteur

- , Rapporteur

- , Directeur de thèse

- , Directeur de thèse

- , Co-directeur de thèse

- , Examinateur

# **CONTENTS**

| LIST  | OF ABBREVIATIONS                                                 | 7  |

|-------|------------------------------------------------------------------|----|

| LIST  | OF FIGURES                                                       | 9  |

| LIST  | OF TABLES                                                        | 11 |

| ABS   | TRACT                                                            | 13 |

| RÉSI  | JMÉ                                                              | 15 |

| 1 IN  | ITRODUCTION                                                      | 17 |

| 2 A   | SYNCHRONOUS CIRCUITS                                             | 19 |

| 2.1   | Classes of Asynchronous Circuits                                 | 22 |

|       | Quasi-Delay Insensitive Asynchronous Circuits                    |    |

| 2.2.1 | Communication Protocol                                           | 25 |

| 2.2.2 | Data Codification                                                | 26 |

| 2.2.3 | Logic Synthesis                                                  |    |

| 2.3   | Conclusions                                                      | 30 |

| 3 TF  | RANSIENT-FAULT EFFECTS ON INTEGRATED CIRCUITS                    | 33 |

| 3.1   | Transient Faults Induced by Environmental Perturbations          | 34 |

| 3.2   | Types of Transient-Fault Effects                                 |    |

| 3.2.1 | Harmful Effects of Transient Faults on Synchronous Circuits      |    |

| 3.2.2 | Harmful Effects of Transient Faults on QDI Asynchronous Circuits |    |

| 3.2.3 | Harmless Effects of Transient Faults                             |    |

| 3.2.4 | Failures: the Effects of Soft Errors                             |    |

| 3.2.5 | Harmful Effects of Multiple-Transient Faults                     |    |

| 3.2.6 | Harmful Effects of Long-Duration Transient Faults                |    |

| 3.3   | Conclusions                                                      | 39 |

| 4 E   | VALUATING TRANSIENT-FAULT EFFECTS AT LOGICAL LEVEL               | 41 |

| 4.1   | Method for Logical-Level Evaluation of Transient-Fault Effects   |    |

| 4.1.1 | Modelling the Transient-Fault Effects                            |    |

| 4.1.2 | Dynamic of Fault-Injection Simulations                           |    |

| 4.1.3 | Evaluation Metrics                                               |    |

| 4.1.4 | Reducing the Total Number of Simulations                         |    |

| 4.1.5 | The Method on Case-Study Circuits                                |    |

| 4.2   | Conclusions                                                      | 53 |

| 5 ASYNCHRONOUS CIRCUITS AS ALTERNATIVE FOR MITIGATION OF LONG-DURATION TRANSIENT FAULTS IN DEEP-SUBMICRON TECHNOLOGIES | 55        |

|------------------------------------------------------------------------------------------------------------------------|-----------|

| 5.1 Natural Detection of Failures                                                                                      | 56        |

| 5.1.1 Ability of QDI Asynchronous Systems                                                                              |           |

| 5.1.2 Inability of Synchronous Systems                                                                                 |           |

| 5.2 Mitigation of Multiple-Transient Faults                                                                            |           |

| 5.3 Mitigation of Long-Duration Transient Faults                                                                       |           |

| 5.4 A Case-Study Analysis                                                                                              |           |

| 5.5 Conclusions                                                                                                        | 61        |

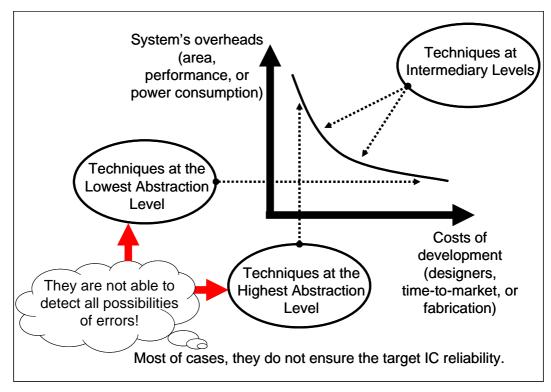

| 6 TECHNIQUES FOR TRANSIENT-FAULT MITIGATION                                                                            |           |

| 6.1 Techniques at Logical and RT Abstraction Levels                                                                    |           |

| 6.1.1 Classic Spatial Redundancies                                                                                     |           |

| 6.1.2 Temporal Redundancies                                                                                            |           |

| 6.1.3 Spatial Redundancies by Gate Duplication                                                                         |           |

| 6.1.4 Spatial Redundancies by Codification                                                                             |           |

| 6.1.5 Techniques Dedicated to QDI Asynchronous Circuits                                                                |           |

| 6.2.1 Spatial Redundancies by Transistors                                                                              |           |

| 6.2.2 Robust Memory Cells                                                                                              |           |

| 6.3 Costs of Mitigation Techniques at Different Abstraction Levels                                                     |           |

| 6.4 Conclusions                                                                                                        |           |

| 7 EVALUATING TRANSIENT-FAULT EFFECTS ON C-ELEMENT'S IMPLEMENTATIONS                                                    | 77        |

| 7.1 Traditional C-element's Implementations                                                                            | <b>78</b> |

| 7.2 Method for Electrical-Level Evaluation of Transient-Fault Effects                                                  |           |

| 7.2.1 Modelling the Transient Faults                                                                                   | 79        |

| 7.2.2 Situations of Transient-Fault Vulnerability                                                                      | 80        |

| 7.2.3 Perturbation Charge of a Circuit Node                                                                            |           |

| 7.3 Making Transient-Fault Robust the C-element                                                                        |           |

| 7.4 Evaluations of the C-element's Implementations                                                                     |           |

| 7.4.1 Simulation Experiments                                                                                           |           |

| 7.4.2 Simulation Results and Evaluations                                                                               |           |

| 7.5 Conclusions                                                                                                        |           |

| AUTHOR'S REFERENCES                                                                                                    |           |

|                                                                                                                        |           |

| REFERENCES                                                                                                             | 99        |

| APPENDIX A SISTEMAS ROBUSTOS A FALHAS TRANSIENTES EXPLORANDO CIRCUITOS ASSÍNCRONOS QUASE-INSENSÍVEIS AOS ATRASOS11     | 14        |

| APPENDIX B SYSTEMES ROBUSTES AUX FAUTES TRANSITOIRES EXPLOITANT LA LOGIQUE ASYNCHRONE QUASI-INSENSIBLE AUX DELAIS      | 27        |

## LIST OF ABBREVIATIONS

ASIC Application Specific Integrated Circuit

CAD Computer-Aided Design

CMOS Complementary Metal-Oxide-Semiconductor

CPU Central Processor Unit

CPO Circuit's Primary Output

CWSP Code Word State Preserving

DES Data Encryption Standard

DIMS Delay-Insensitive Minterm Synthesis

DNA Deoxyribonucleic Acid

dSE Direct Soft Error

DWC Duplication with Comparison

EDA Electronic Design Automation

EDAC Error Detection and Correction

EEATS Electronique, Electrotechnique, Automatique & Traitement du Signal

EMI Electromagnetic Interference FDN Failure Detectable Naturally

FPGA Field Programmable Gate Array

FNN Failure Non-detectable Naturally

FTN Faults Tolerated Naturally

HC Hamming Code

HCMOS High-density Complementary Metal-Oxide-Semiconductor

HDL Hardware Description Language

IC Integrated Circuit

INPG Institut National Polytechnique de Grenoble

iSE Indirect Soft Error

LDT Long-Duration Transient

MBU Multiple-Bit Upset

MDD Multi-valued Decision Diagram

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

NOC Network-on-Chip

PDA Personal Digital Assistant

PGMicro Pós-Graduação em Microeletrônica

PPGC Programa de Pós-Graduação em Computação

QDI Quasi-Delay Insensitive RAM Random Access Memory

RFID Radio Frequency Identification

ROM Read Only Memory

RT Register Transfer

SDF Standard Delay Format

SE Soft Error

SEO Signal of End Operation

SEE Single Event Effect

SER Soft Error Rate

SET Single-Event Transient

SEU Single Event Upset

SOC System-on-Chip

SOI Silicon-on-Insulator

SRAM Static Random Access Memory

TIMA Laboratoire de Techniques de l'Informatique et de la Microélectronique

pour l'Architecture des systèmes intégrés

TR Time Redundancy

TMR Triple Modular Redundancy

UFRGS Universidade Federal do Rio Grande do Sul

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VLSI Very Large Scale Integration

# **LIST OF FIGURES**

| Figure 2.1: The different classes of circuits in accord with the logic redundancy and  | the  |

|----------------------------------------------------------------------------------------|------|

| number of timing assumptions                                                           |      |

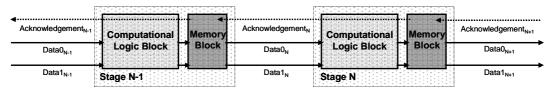

| Figure 2.2: Communication between stages of a QDI asynchronous system                  | 25   |

| Figure 2.3: Four-phase protocol for a communication between stages                     | 26   |

| Figure 2.4: Dual-rail data codification by three states                                | 27   |

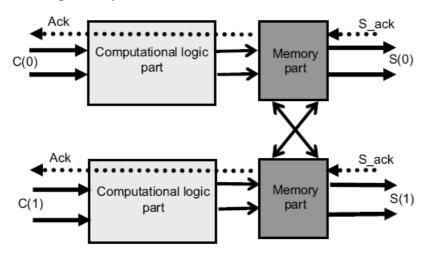

| Figure 2.5: A structure of a QDI system by analogy to a synchronous system             |      |

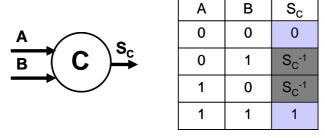

| Figure 2.6: Function of a 2-input C-element gate                                       | 28   |

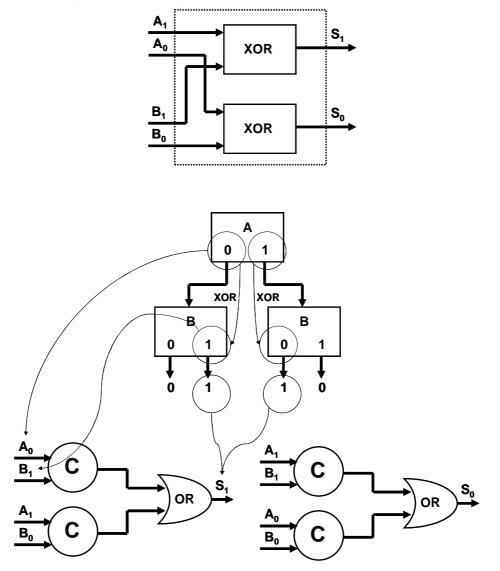

| Figure 2.7: MDD-based logic synthesis of a delay-insensitive dual-rail XOR function    |      |

| for the four-phase protocol                                                            |      |

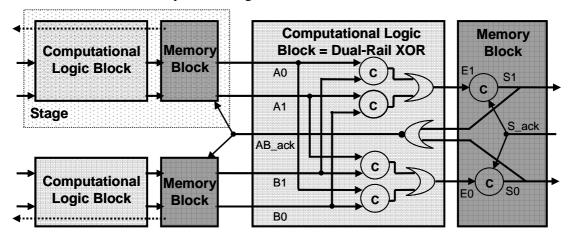

| Figure 2.8: A QDI system operating through the four-phase protocol                     | 30   |

| Figure 3.1: A generic hardware module to represent either a synchronous systems of     | r a  |

| QDI asynchronous                                                                       |      |

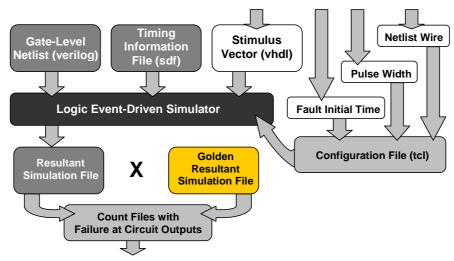

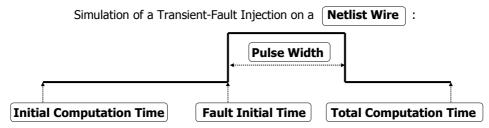

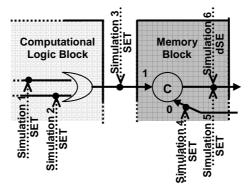

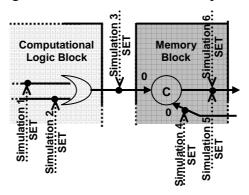

| Figure 4.1: Simulation scheme of a SET on an IC-design netlist                         | 43   |

| Figure 4.2: Modelling of a SET fault on a netlist's wire                               | 43   |

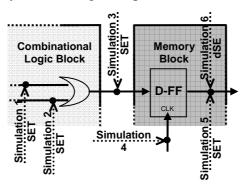

| Figure 4.3: Fault-injection simulations into a synchronous circuit                     | 44   |

| Figure 4.4: Fault-injection simulations into a QDI asynchronous circuit with different |      |

| logic values at its C-element's inputs                                                 | 44   |

| Figure 4.5: Fault-injection simulations into a QDI asynchronous circuit with equal l   | ogic |

| values at its C-element's inputs                                                       | 44   |

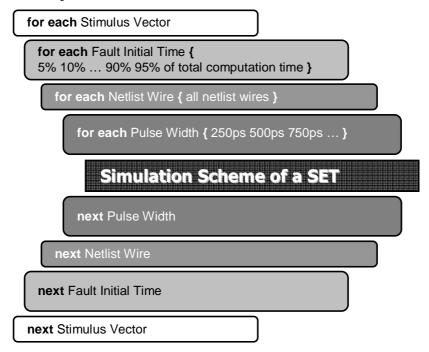

| Figure 4.6: Simulation methodology for injection of SETs                               | 45   |

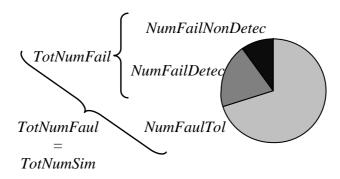

| Figure 4.7: The total number of injected transient faults and their consequences       | 47   |

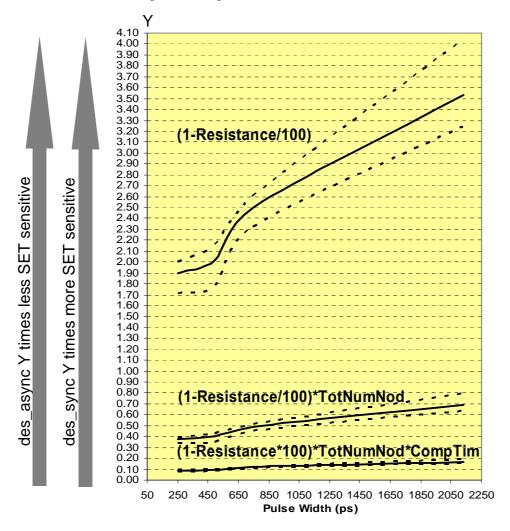

| Figure 4.8: Estimating a methodology's evaluation metric (Sensitivity)                 | 49   |

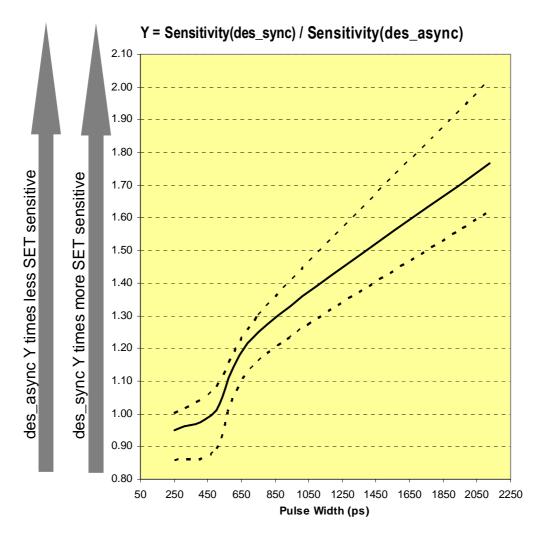

| Figure 4.9: Circuits' Sensitivities in terms of the ratio des_sync / des_async         | 50   |

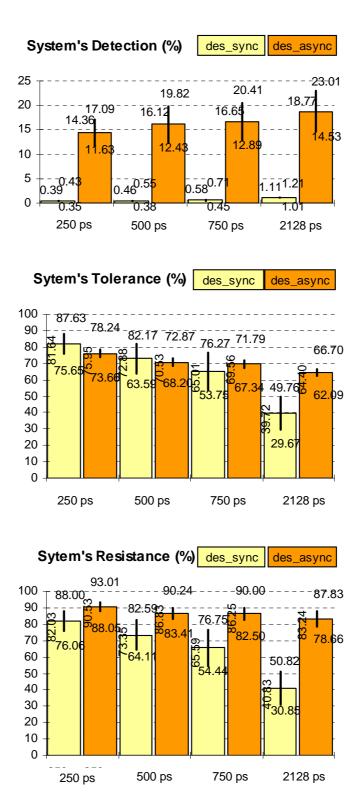

| Figure 4.10: System-robustness percentages                                             | 51   |

| Figure 4.11: Circuits' Sensitivities by considering between des_async and des_sync     |      |

| area factor of 2 and computation time factor of 1                                      |      |

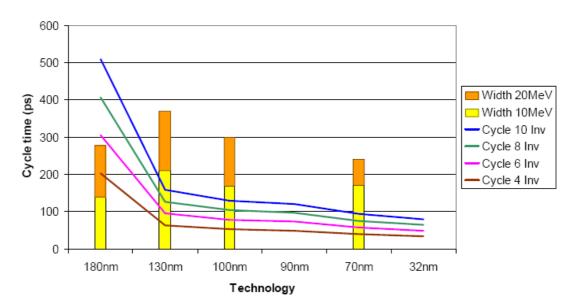

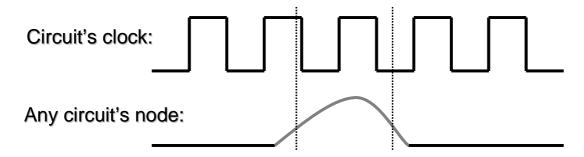

| Figure 5.1: Transient-fault width vs. clock's cycle time scaling (LISBOA, 2009)        |      |

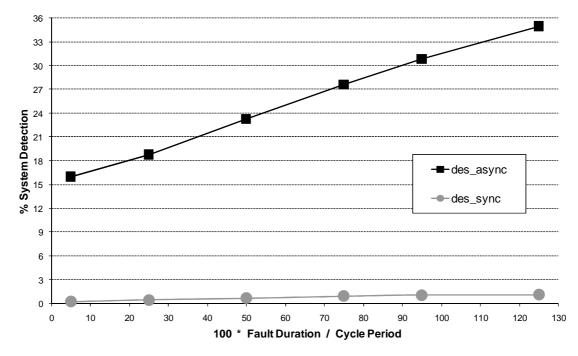

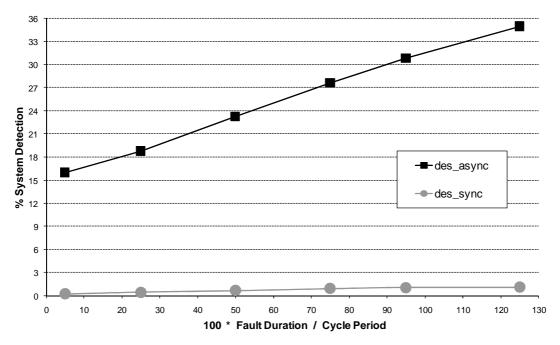

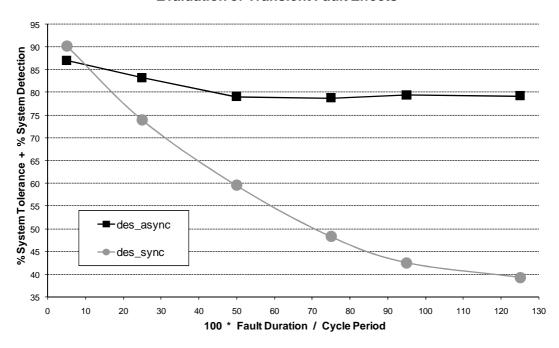

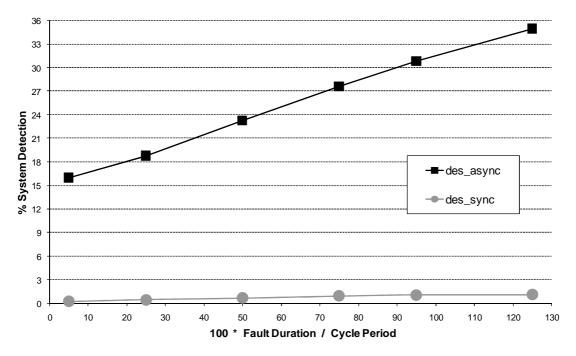

| Figure 5.2: A case study on a DES crypto-processor: system's ability for detection i   |      |

| function of transient fault durations                                                  |      |

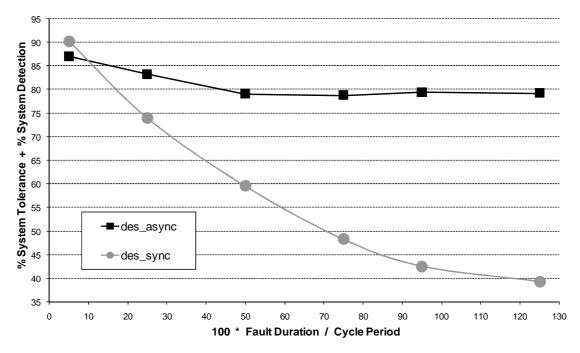

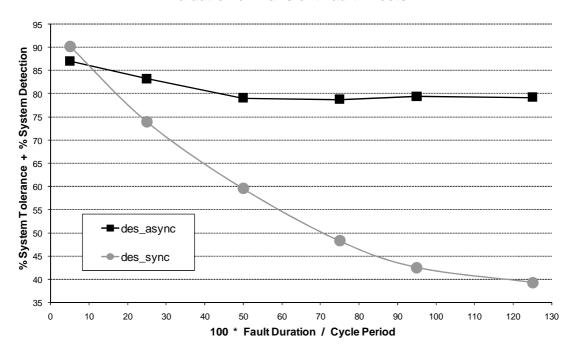

| Figure 5.3: The stronger natural ability of a QDI asynchronous system for mitigation   |      |

| LDT faults in deep-submicron technologies                                              |      |

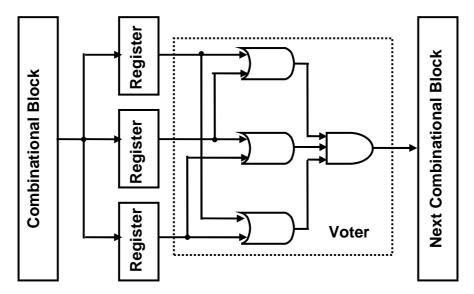

| Figure 6.1: TMR scheme applied on a 1-bit register                                     | 65   |

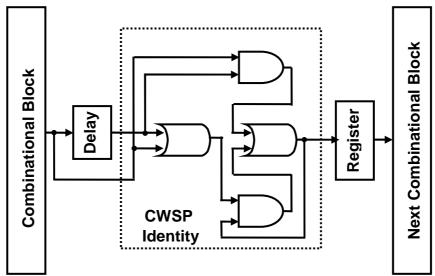

| Figure 6.2: TR+CWSP scheme applied on a 1-bit register                                 |      |

| Figure 6.3: TR+CWSP scheme working on a 1-bit register                                 |      |

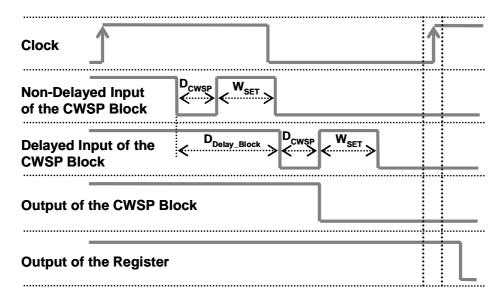

| Figure 6.4: CWSP elements at logical abstraction level (NICOLAIDIS, 1999)              | 67   |

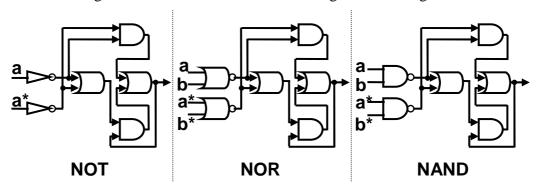

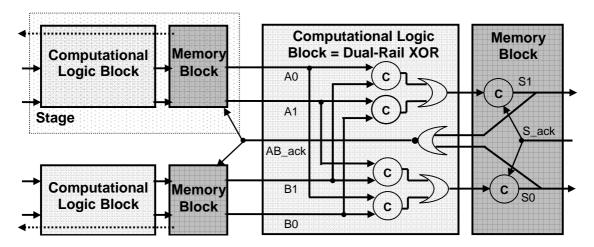

| Figure 6.5: Duplication-based technique for computational logic of a QDI system        |      |

| (MONNET, 2005-b)                                                                       | 70   |

| Figure 6.6: Synchronization Technique for two bits of a data word in a QDI system          |            |

|--------------------------------------------------------------------------------------------|------------|

| (MONNET, 2005-b)                                                                           | 70         |

| Figure 6.7: CWSP elements at electrical abstraction level (NICOLAIDIS, 1999)               | 71         |

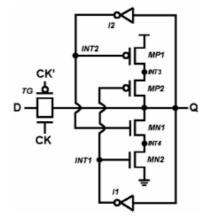

| Figure 6.8: A robust latch (OMAÑA, 2007)                                                   | 72         |

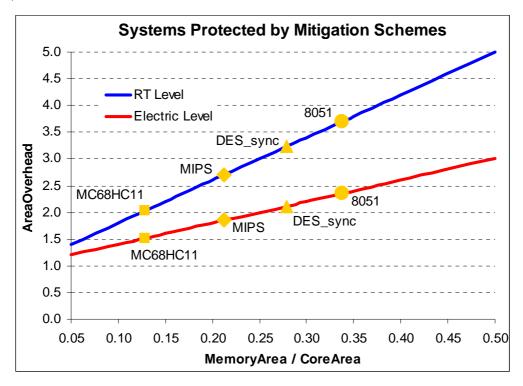

| Figure 6.9: Costs of mitigation techniques at different abstraction levels                 | 73         |

| Figure 6.10: Area costs of traditional mitigation techniques in function of the memory     | <b>y</b> - |

| core area ratio                                                                            | 74         |

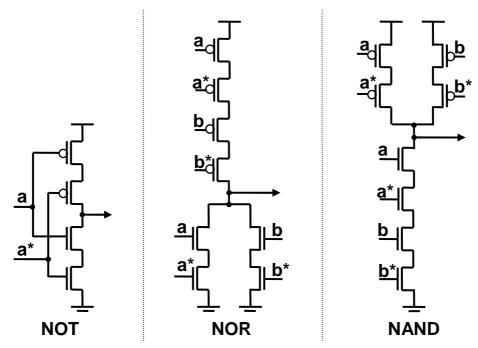

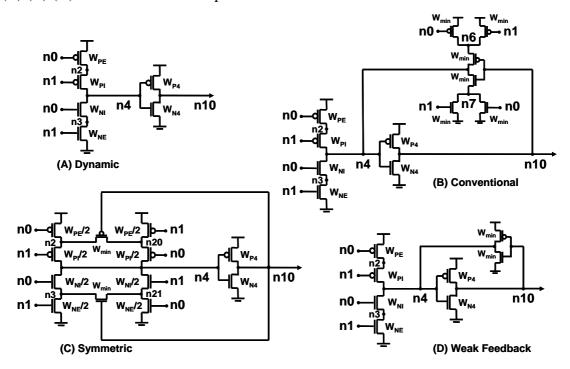

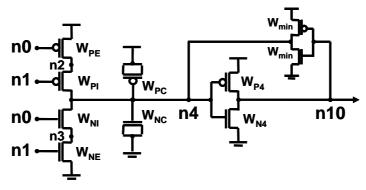

| Figure 7.1: The traditional C-element's implementations                                    | 78         |

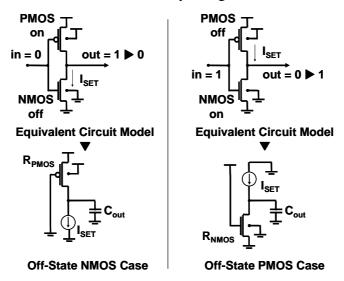

| Figure 7.2: Modelling the perturbation-induced transient current $I_{SET}$ that temporally |            |

| discharges (off-state NMOS case) or charges (off-state PMOS case) the node out             | 80         |

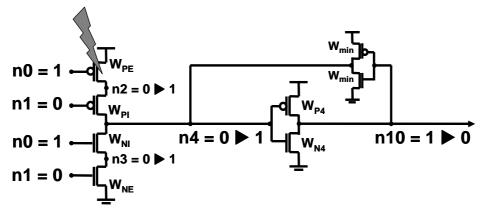

| Figure 7.3: Nodes' logic states of the weak-feedback C-element version under a             |            |

| situation of transient-fault vulnerability                                                 | 80         |

| Figure 7.4: The explicit-capacitor version of a weak-feedback C-element                    | 83         |

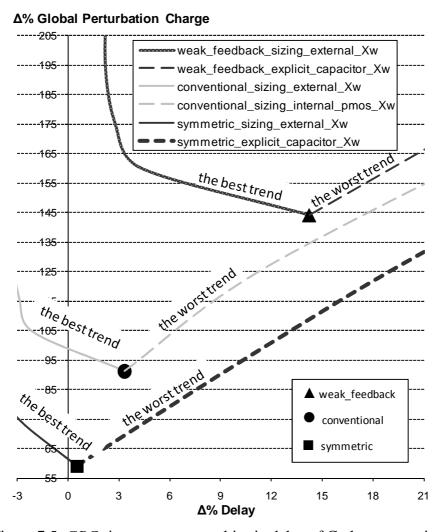

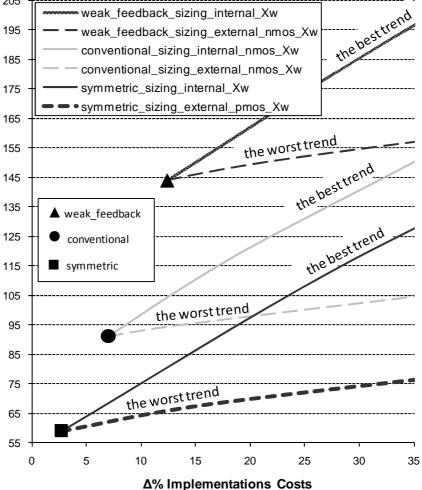

| Figure 7.5: $GPC_V$ increases vs. penalties in delay of C-element versions                 | 86         |

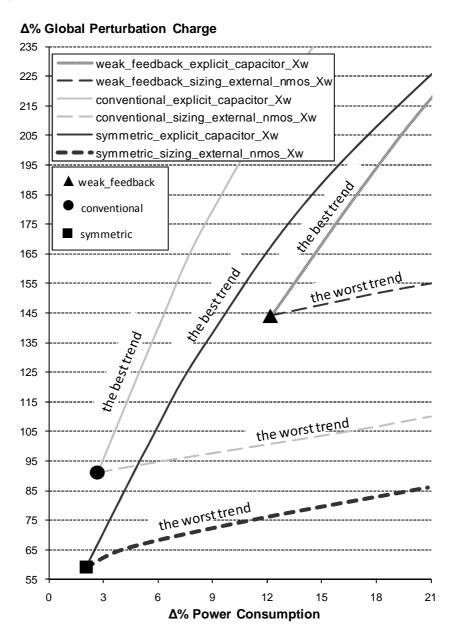

| Figure 7.6: $GPC_V$ increases vs. power-consumption overheads                              | 87         |

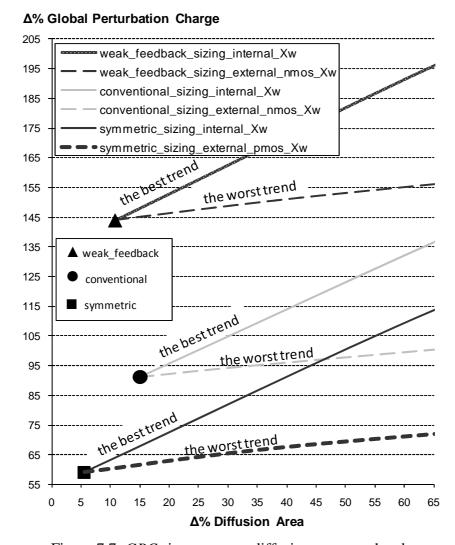

| Figure 7.7: <i>GPC<sub>V</sub></i> increases vs. diffusion-area overheads                  | 88         |

| Figure 7.8: $GPC_V$ increases vs. C-element implementation costs                           | 89         |

|                                                                                            |            |

# **LIST OF TABLES**

| Table 3.1: Possible primary outputs of a module perturbed by transient faults                                                                                                      | 39  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.2: Summary of transient-fault effects on synchronous and QDI asynchronous                                                                                                  |     |

| circuits                                                                                                                                                                           | 40  |

| Table 5.1: Possible CPOs of a system perturbed by transient faults                                                                                                                 | 57  |

| Table 7.1: Situations of transient-fault vulnerabilities on the traditional C-element's                                                                                            |     |

| versions                                                                                                                                                                           | 81  |

| Table 7.2: Diffusion widths W <sub>N4</sub> , W <sub>P4</sub> , W <sub>NI</sub> , W <sub>PI</sub> , W <sub>NE</sub> , W <sub>PE</sub> W <sub>NC</sub> , and W <sub>PC</sub> of the |     |

| NMOS and PMOS transistors in robust C-element cells                                                                                                                                | 83  |

| Tabela 1: Possiveis CPOs de um sistema perturbado por falhas transientes 1                                                                                                         | 119 |

| Tableau 1: Possibles CPOs d'un système perturbé par fautes transitoires                                                                                                            | 132 |

#### **ABSTRACT**

Recent deep-submicron technology-based ICs are significantly more vulnerable to transient faults. The arisen errors are thus also more critical than they have ever been before. This thesis presents a further novel benefit of the Quasi-Delay Insensitive (QDI) asynchronous circuits in terms of reliability: their strong natural ability to mitigate long-duration transient faults that are severe in modern synchronous circuits. A methodology to evaluate comparatively the transient-fault effects on synchronous and QDI asynchronous circuits is presented. Furthermore, a method to obtain the transient-fault mitigation ability of the QDI circuits' memory elements (i.e., the C-elements) is also proposed. Finally, mitigation techniques are suggested to increase even more the C-elements' transient-fault attenuation, and thus also the QDI asynchronous systems' robustness.

**Keywords:** Design of robust or fault-tolerant systems, QDI asynchronous circuits, transient faults, soft errors, evaluation of transient-fault effects.

## Systèmes Robustes aux Fautes Transitoires Exploitant la Logique Asynchrone Quasi-Insensible aux Délais

#### **RESUME**

Les technologies nanoélectroniques récentes font que les circuits intégrés deviennent de plus en plus vulnérables aux fautes transitoires. Les erreurs engendrées sont aussi plus critiques que jamais auparavant. Cette thèse présente un nouvel avantage en termes de fiabilité des circuits asynchrones quasi-insensibles aux délais (QDI): Leurs fortes résistances naturelles aux fautes transitoires de longue durée qui sont graves pour les circuits synchrones actuels. Une méthodologie pour évaluer comparativement les effets des fautes transitoires sur les circuits synchrones et asynchrones QDI est présentée. En outre, une méthode pour obtenir la résistance aux fautes transitoires des éléments mémorisants spécifiques aux circuits QDI (les portes de Muller) est également proposée. Enfin, des techniques de tolérance ont été étudiées pour augmenter encore plus la robustesse des portes de Muller aux fautes transitoires, et donc aussi la robustesse des systèmes asynchrones QDI.

**Mots clés:** Conception de systèmes robustes ou tolérants aux fautes, circuits asynchrones QDI, fautes transitoires, soft errors, évaluation des effets aux fautes transitoires.

#### 1 INTRODUCTION

The IC fabrication technology's evolution has allowed in last years the use of nanometer scales to design semiconductor devices. Deeper-submicron technologies enable thus the development of sophisticated electronic systems in small scale, high density, high performance, and low power consumption.

On the other hand, the close proximity to the physical limits of the semiconductors and the high complexity of such deep-submicron technology-based designs impose considerable challenges to the IC reliability. The circuits indeed suffer harmful effects that in older technologies were practically negligible.

There are many challenges imposed by deep-submicron technologies to the circuit reliability. Several types of faults can thus occur in a circuit given its larger vulnerability. Today nanoelectronic circuits are indeed more sensitive to variations of fabrication process as well as environmental factors like temperature, radiations, and electrical noise. IC-based systems are so more vulnerable to two effects of such variations: timing alterations of the circuit delays and transient voltage modifications.

Such effects, in terms of voltage transients and delay variations, have motivated many researches due to the severity of their consequences for the systems. In fact, these effects, known respectively as transient faults and delay faults, can provoke errors in circuit's functional operations. If propagated, theses errors can lead the circuit to produce inconsistent results at its primary outputs, and so making a system's failure scenario.

Normally, delay faults are arisen from fabrication process variations, however they can also be induced by environmental factors. On the contrary, transient faults are generated due to environmental or intentional-perturbation events. A single perturbation event on an IC can produce a transient fault so-called as single-event transient (SET). Moreover, there are lower-probability cases in which multiple-perturbation events or even a single event can create multiple-transient faults. The worst transient-fault effects on ICs are memory-bit flips that are non-permanent errors in memory cells named as soft errors (SEs). If transient faults accomplish upsetting various memory cell's bits, the phenomenon is thus known as multiple-bit upset (MBU).

The transient and delay faults have even more severe effects in deeper-submicron technologies where the circuit's delays are inherently shorter. In these technologies, it is possible that fault's durations are comparable or even longer than the clock cycle's periods. In addition, most of the existing mitigation techniques require very-high power, performance, and area overheads to deal with such long-duration transient (LDT) faults, hence new solutions to protect the circuits are necessary (LISBOA, 2007-a). LDT faults

have clearly a much higher probability of not being masked, and therefore they also stand a greater chance of producing a system's failure.

In fact, such a higher error probability is due to the limitation of the clock period that is thus fundamental for the severity of transient and delay faults. On the other hand, the clock is a particularity of the traditional synchronous circuits which suffer thus much more with the worse LDT consequences than clockless circuits. Hence, designing circuits that are not controlled by a global clock but only by their internal data flow can result in systems that are more robust against such LDT faults. It is the case of the asynchronous circuits, and specially their most important class: the Quasi-Delay Insensitive (QDI) circuits.

Essentially, QDI circuits are composed of C-elements, so-called Muller gates. Such an element, which has a dual-behavior, works either as a buffer or as a memory cell. These special gates ensure the QDI property and permit the synchronization between circuit's stages, where a handshaking protocol is applied by a multi-rail data path.

The multi-rail data codification and the asynchronous handshaking communication of QDI systems make the detection and correction of errors easier (MONNET, 2007-a). The absence of a clock tree allows them to emit less electromagnetic interference (PANYASAK, 2004), and makes them more secure against malicious power analysis (BOUESSE, 2005). Moreover, such a clockless property also leads to increased energy savings (RIOS, 2008), and achieving high performance at the expense of using less than twice larger area than their synchronous counterparts. A QDI circuit is also inherently robust against delay faults on most of its paths due to its natural QDI property (LAFRIEDA; MANORAR, 2004). In addition, its C-elements are fundamental to implement more robust systems. In fact, even in synchronous systems, C-elements are often used to filter transient faults, and so protecting the circuits against SEs (NICOLAIDIS, 1999; MITRA et al, 2005; FAZELI et al, 2007). Then, QDI systems' Celements improve the circuit's ability for masking transient faults (MONNET, 2007-a). Such inherent characteristics of QDI asynchronous designs ensure a high systems' reliability without implementing costly hardware-based mitigation mechanisms which in synchronous designs are practically indispensable to obtain similar immunity level.

As QDI asynchronous circuits are undeniably quite robust against delay faults, the goal of this thesis was exploiting such a class of circuits in order to obtain more transient-fault robust systems.

In this thesis, chapter 2 shows the benefits and features of the QDI asynchronous systems. Chapter 3 outlines the different transient-fault effects on ICs. In Chapter 4, a novel method is proposed to evaluate at logical level the transient-fault effects as on synchronous circuits as on QDI asynchronous circuits. Chapter 5 presents and discusses a new QDI asynchronous systems' benefit in comparison with synchronous systems: their better natural ability for mitigation of LDT faults in deep-submicron technologies. In chapter 6, hardware-based transient-fault mitigation techniques and their costs to protect synchronous circuits at different abstraction levels are discussed. Furthermore, chapter 7 evaluates innovatively the transient-fault effects on traditional C-element's implementations and also presents for the first time the best C-element's options to further improve the QDI asynchronous systems' robustness. Finally, chapter 8 highlights the main contributions of this thesis as well as the ideas to be discussed in future works.

#### 2 ASYNCHRONOUS CIRCUITS

Even nowadays the largest part of ICs in electronics equipments are based on an oscillator to start, process, and finalize all of their operations. Such electronics systems are synchronous circuits at a frequency of a signal well determined to reach all circuit parts. However, in the last years, there are already systems in which their different internal circuits operate without the need of the pace of a global clock. These circuits then so-called asynchronous or clockless use their own data flow to locally govern the computation and communication between parts of the system.

The asynchronous communication activity between circuit blocks, and even among systems with their environments, had a significant increase (BRZOZOWKI; SEGER 1995). Indeed, the technological evolutions and their more complex ICs have required asynchronous activities to face with design challenges. Synchronous blocks which operate on different frequencies need asynchronous interfaces to efficiently exchange data (SUTHERLAND, EBERGEN, 2002). In the last years, the use of asynchronous approaches has also been targeted for electronics applications or embedded systems. Asynchronous systems are thus mostly applied to achieve low power consumption, reliability, robustness, and security. Then, applications such as smart cards, RFIDs, pagers, PDAs, power management chips, electronics for automation and avionics, sensor networks, cell phones, metering, medical, mobile, and battery-powered devices are very feasible. In addition, high-performance applications like processors for simulation, audio, video, images, signals, graphics, servers, and workstations may also be designed by asynchronous logic (GEER, 2005; TIEMPO, 2009).

Asynchronous systems are not only applications for ICs. Synthetic biology uses engineering principles to design genetic circuits. Such biological circuits constructed from DNA (deoxyribonucleic acid) are inserted into bacteria to perform various tasks (NGUYEN et al, 2007). As there is not a global clock, genetic circuits are inherently asynchronous. Thus, asynchronous design techniques are also applied for many applications of the synthetic biology, which contributes directly, for instance, in the production of drugs to combat malaria (NGUYEN et al, 2007).

In fact, all digital systems, essentially, can be viewed as asynchronous (BRZOZOWKI; SEGER 1995). Some fundamental concepts related to asynchronous circuits support the operational characteristics of the synchronous (FLETCHER, 1980). A synchronous circuit is designed based on rules of a particular project and operated under special assumptions of its environment (BRZOZOWKI; SEGER 1995). Its combinational circuits process their logic functions asynchronously within a clock period. In addition, its hearts, the flip-flops, are structurally asynchronous sequential machines that operate within the time conditions of set-up and hold. Several other

asynchronous machines, such as, latches and Muller C-elements, are also components for the design of synchronous systems.

The concepts of asynchronous circuits are suggested since the middle of the last century when there was the development of the first asynchronous machines (FLETCHER, 1980). However, synchronous approaches prevailed in the microelectronics industry due to the simplicity in the design implementation of the control and logic circuit (FRAGOSO, 2005). Such a dominion nowadays is accomplished by the maturity of commercial CAD tools dedicated to synchronous. Although synchronous methods could be adapted for asynchronous (KONDRATYEV; LWIN, 2002), they are optimized for synchronous. There is, therefore, a larger complexity for the implementation of asynchronous designs by using such synchronous-dedicated tools. Moreover, the resulting asynchronous circuits are poorly optimized. In fact, these tools are not prepared to implement a local organization for asynchronous communications between circuit blocks. Then, implementations of asynchronous protocols are not optimized resulting thus in high overheads in terms of area and total computation time.

On the other hand, a coordination of asynchronous actions also determines additional hardware mechanisms and, therefore, costs in terms of area. Indeed, even using an efficient synthesis method for asynchronous designs, the area of an asynchronous system reaches the order of twice the size of an equivalent synchronous system. However, this is practically the only cost paid to obtain the many inherent advantages of an asynchronous system. The absence of a fixed rhythm of a global clock allows several important benefits that are discussed in the following paragraphs (SUTHERLAND, EBERGEN, 2002; FRAGOSO, 2005; SPARSO, 2006; FLETCHER, 1980; HAUCK, 1995; BRZOZOWKI; SEGER 1995):

- Sutherland and Ebergen (2002) observe that the efforts required to coordinate asynchronous actions are small. An asynchronous system indeed may, on average, be **faster** than a synchronous, especially in irregular IC designs in which slower actions are infrequent. In fact, the data paths of asynchronous circuits operate in the pace of their gate and wire delays. Thus, operations more complex and less frequent take more time than average, and simple and frequent ones take less. On the other hand, synchronous systems are always in the pace of the longest circuit path. In addition, a margin to cope with variations of the clock (jitter and skew), and manufacturing and environmental irregularities must be also considered (GEER, 2005). Therefore, simple tasks in synchronous circuits run slower to follow the pace of the more complex ones;

- In clocked systems, the delay differences between data paths of their circuits generate the so-called static hazards (FLETCHER, 1980), which are tolerated by using a global clock. Otherwise, such a kind of spurious switching is not allowed in asynchronous design. By nature, indeed, asynchronous systems have no static hazards. Therefore, dynamic power is not wasted. In addition, as there is not a clock, a clock-distribution circuit is not required. Consequently, **lower power consumptions** (GAGELDONK, 1998) are feasible. In fact, nowadays complex synchronous chips, like microprocessors, have clock-tree circuits that represent a good part of the system's area (SUTHERLAND, EBERGEN, 2002). About 30% of the power consumed by such chips is due to the clock and its distribution circuit. Furthermore, as the clock is always working, the chip heats even though

it is not doing anything useful. Clockless systems, otherwise, allow easily disable blocks of the circuit to reduce the power consumption;

- The need nowadays to distribute uniformly the clock signal in all parts of the chips, which are faster and denser, has required synchronous designs even more sophisticated in order to avoid different latching times within the clock-skew problem. Given such a technological trend, asynchronous approaches arise as an interesting alternative to avoid elaborate clock-tree designs in complex circuits:

- Synchronization by a clock also requires more careful designs with signals from

a system's asynchronous interface. An inadequate sampling of such signals can

put the synchronous circuit indefinitely in meta-stable states (FLETCHER, 1980;

HAUCK, 1995; BRZOZOWKI; SEGER 1995; MYERS, 2001). In contrast,

asynchronous systems by nature can wait the interfaces to meet stable conditions

in order to start a correct computation, and thus avoiding the metastability

phenomenon;

- The clock also limits the modularity of a synchronous system, which requires special interfaces to perform communications with other systems of different operation frequencies (SUTHERLAND, EBERGEN, 2002; FRAGOSO, 2005). Asynchronous modules are much more flexible because their circuits do not have to share a common rhythm, therefore, they easily allow designs of SOCs and NOCs;

- The absence of a clock's fixed rhythm allows also **lower emissions of electromagnetic interferences** (EMI) (SUTHERLAND, EBERGEN, 2002; PANYASAK, 2004). In contrast, synchronous systems emit stronger electromagnetic signals at its clock frequency and harmonics. Besides being able to produce internal noise in its own circuit, such signals can also interfere with televisions, cellular phones, aircraft navigation systems, and any electronics equipment operating at the same frequency band;

- More recently, asynchronous systems, especially the Quasi-Delay Insensitive class (QDI Circuits), are suggested as a qualified alternative to design robust and secure circuits. This topic is discussed at greater length in the following sections of this chapter.

Given such many advantages, asynchronous applications certainly will evolve even more in the IC market, especially when the various methods optimized for the asynchronous design, like those in (VIVET, 2001; RIGAUD, 2002; MAURINE et al, 2003; DINH-DUC, 2003; FOLCO et al, 2005; FRAGOSO, 2005; BALSA, 2009; TIEMPO, 2009), conquer more popular commercial dimensions. However, these asynchronous qualities already encourage several efficient commercial applications which perhaps still are little known by the scientific community and industry.

Asynchronous ICs indeed are already in commercial mass production (SUTHERLAND, EBERGEN, 2002). The electronics company Sharp already released asynchronous media chips devoted to edit graphics, video, and audio. Asynchronous microcontrollers are used in pagers sold by Philips Electronics. Some synchronous processors from Sun Microsystems include asynchronous blocks to organize information from memory chips. Other hybrid applications are proposed but based on the idea of globally asynchronous and locally synchronous designs (CHAPIRO, 1984;

IYER; MARCULESCU, 2002; TEEHAN, 2007). The Handshake Solutions and ARM companies developed asynchronous cores for devices such as smart cards, consumer electronics, and automotive applications (GEER, 2005). In addition, the Fulcrum Microsystems offers asynchronous chips of high performance for networks, storage devices, and embedded systems. The Theseus Logic company developed a low-power and low-noise asynchronous version of a Freescale's 8-bit microcontroller. It is for signal-processing or battery-powered applications. Moreover, such a company with a medical-equipment provider, the Medtronic, also produced asynchronous chips for defibrillators and pacemakers. The French company Tiempo presents its asynchronousbased solutions for applications of smart cards, RFIDs, cellular phones, mobile handsets, power management, automobile, avionics, and medical systems. Tiempo's products include IP cores of microcontrollers, microprocessors, and crypto-processors, as well as an asynchronous-dedicated EDA tool (TIEMPO, 2009). Besides these and other companies, there are several asynchronous-dedicated research groups at educational institutions like the California Institute of Technology, the University of Manchester, the University of Tokyo, and the TIMA Laboratory in Grenoble.

According to the aim of this work, the following sections present the main characteristics of this important asynchronous option to design, especially, low-power, reliable, robust, and secure circuits.

#### 2.1 Classes of Asynchronous Circuits

An asynchronous system has, as a natural feature, a well-coordinated activity of its data switching (KONDRATYEV; LWIN, 2002). The computation flow is not modelled with the aid of a clock but with the implementation of logic redundancy in parts of the circuit. It thus prevents spurious switching, the hazards, which arise from the delay differences in the gates and wires of the system. On the other hand, the design of a synchronous system does not require, within a clock period, an exact timing sequence coordination of the circuit's switching activity. The design implementation, therefore, requires less redundancy.

In the past decades, these features related to the lower design complexity and smaller circuit area were very important for the synchronous design achieving today such a maturity. However, given the current technological trends that require more robust systems, the larger redundancy in asynchronous have made such circuits very attractive.

The use of redundancy to ensure the correct circuit behaviour (i.e., a hazard-free circuit) in any delay distribution of gates and wires can be costly and even impractical (KONDRATYEV; LWIN, 2002). Therefore, certain timing assumptions are necessary to enable implementations of any function type. Such timing assumptions have different locality degrees that can be since matching delays on wire branches of some circuit's forks (as in Quasi-Delay Insensitive asynchronous systems, the QDI circuits) to balance all circuit's data paths (as in synchronous circuits) (KONDRATYEV; LWIN, 2002).

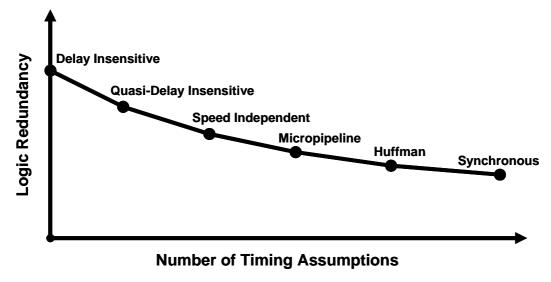

The different classes of circuits can thus be summarized by Figure 2.1 (VIVET, 2001; KONDRATYEV; LWIN, 2002). The figure's vertical axis shows the redundancy degree of the class, therefore the robustness degree as well as the complexity. The horizontal axis indicates the number of timing assumptions, then also the degree of non-locality and slack of the constraints on the assumptions. As greater as the number of timing assumptions is, slacker timing constraints must be set and thus the circuits are

simpler (FRAGOSO, 2005). However, they are less robust, less modular, and the timing assumptions are more difficult to meet (KONDRATYEV; LWIN, 2002).

Figure 2.1: The different classes of circuits in accord with the logic redundancy and the number of timing assumptions

The **Huffman circuits** (HUFFMAN, 1954-a; HUFFMAN, 1954-b), which are also known as asynchronous sequential machines, are the origin of the asynchronous systems and therefore they well represent their fundamental mode. Such circuits consist of a set of combinational gates, which compute the next state and circuit outputs, and a set of feedback lines, which store the circuit states (ALMUKHAIZIM, 2008). Their inputs must remain at a steady state for a minimum time that ensures the circuit stabilization. The classic examples of Huffman circuits are the flip-flops, which must conserve the time of set-up and hold to stabilize their outputs. Other asynchronous sequential machines more complex are feasible, but they will be even more sensitive to the delays of their gates and wires. Therefore, they are sensitive to delay variations beyond the limits set by the designer, because they use a model known as bounded delay. The circuits will be thus more sensitive to physical failures and more vulnerable to fabrication defects (defined in chapter 3). The same bounded delay is also used in synchronous circuits, so they are also subject to these vulnerabilities.

The Micropipeline circuits (SUTHERLAND, 1989) are asynchronous architectures that, as the pipelines of synchronous approaches, compute and store data. The global clock is replaced by a local-synchronization structure based on handshake. It is used to control the elastic data pipeline in the circuit stages (FRAGOSO, 2005). The control circuit operates independently of its gate and wires delays, so it uses an unbounded-delay model. It means that no upper limit to the values of its delays is needed or established, since there is an asynchronous communication by handshake between its stages (HAUCK, 1995). Furthermore, the bounded-delay model is also used on the Micropipeline circuits, but only on the architecture's data path to circumvent the hazard problem in its computation logic. Micropipeline circuits are thus also subject to those vulnerabilities discussed in last paragraph for Huffman circuits.

The **Speed Independent circuits** (MILLER, 1961) use the unbounded-delay model on all their gates, but the delays of all their wires are simply negligible or assumed smaller than their smaller gate delays (HAUCK, 1995). Nowadays the wire delays are

increasingly more critical in complex systems based on deep-submicron technologies, therefore Speed Independent circuits are not recommended (FRAGOSO, 2005).

On the other hand, the **Delay Insensitive circuits** (DI circuits) (WESLEY, 1967; UDDING, 1986), which are built similarly to the Speed Independent ones, have no timing assumption. Therefore, all gate and wire delays use the unbounded-delay model. DI circuits would be thus the ideal ones to avoid physical failures and tolerating fabrication defects, since they operate correctly under whatever delay condition in their gates and wires. However, Martin (1990) highlighted that the implementation of DI circuits is very limited and non-practical. In addition, he also presented the minimum timing assumptions, which have the constraints with the least slack, to make practicable the implementation of any circuit. In fact, Martin (1990) proved that the required timing assumptions, called isochronic forks, are indeed those which characterize a QDI circuit. Therefore, the class of the QDI circuits impose themselves as the most feasible.

### 2.2 Quasi-Delay Insensitive Asynchronous Circuits

The **Quasi-Delay Insensitive circuits** (QDI circuits) beyond using the unbounded-delay model (discussed in the previous section) in all their gates, they also use it in **quasi**-all their wires. The only timing assumptions of the QDI circuits are localized in branches of some critical forks. In fact, such forks need be isochronic (i.e., they need to have branches with similar delays) to enable the implementation of any circuit with the quasi-delay insensitivity feature. The only timing-assumption requirement is thus to have a negligible delay difference between the branches of isochronic forks. It must indeed be negligible compared to the smallest gate delays of the circuit (MARTIN, 1990). Therefore, the branches of isochronic forks are the only wires in a QDI circuit that do not use the unbounded-delay model.

The use of this unbounded-delay model results in a circuit that is no sensitive to the delays of its gates and almost all its wires. The circuit thus has the QDI property. It has no determined time to compute a certain input logic state, since all gates and almost all wires can have any delay value. Therefore, the circuit's inputs have to remain stable also for an undetermined period of time in order to correctly compute the circuit's logic functions. Only after the end of the logic computation, the circuit's inputs can be stimulated again with a new logic state. On the contrary, a certain synchronous system's stage needs to have the logic state of its inputs kept by a certain determined time to enable a correct computation. Stimulating a new logic state at its inputs is authorized only after such a determined time, which is defined by the inverse of the maximum system's clock frequency.

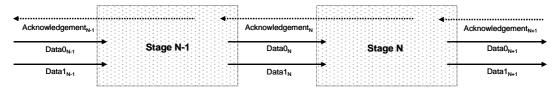

On the other hand, in a QDI system generalized in Figure 2.2, each one of its stages need abstract the absence of a clock and the unbounded-delay model in order to enable the stimulus of a new logic state at their inputs. As this delay model considers that there is not a determined time for a correct computation of a certain input logic state X of a stage N, an emitter stage N-1 would have no guarantee that stage N has finished the computation of state X. Hence, the emitter stage N-1 need to be informed by some artifice. Otherwise, it could disturb the computation end of state X by means of sending prematurely a certain new state Y. The QDI system need thus locally coordinate its communication actions between the parts (stages) of its circuit. Therefore, a small additional circuit is implemented to detect changes at stage's outputs and indicating to

the emitter stage, by means of an acknowledgment signal, the computation end of a state X. Thus, the correct computation of a state X and a new state Y are achievable.

Figure 2.2: Communication between stages of a QDI asynchronous system

Such an acknowledgment signal to the emitter stage need be always consistent to ensure the QDI property of a system. Therefore, the circuit design of a QDI system's stage need also ensure that

- no hazards occur on any stage's logic and

- whatever logic state transition at stage's inputs results in some logic state change at stage's outputs.

Ensuring such conditions, eventual false acknowledgements to the emitter stage are avoided because there are no hazards. In fact, these conditions eliminate any stage's input logic transition that does not generate logic state changes at stage's outputs. Hence, the outputs of a receiver stage will not fail to acknowledge an input transition. It ensures, therefore, the feasibility to observe all possible input logic transitions of a receiver stage by means of its output transitions. Finally, it also ensures an accurate acknowledgement to the emitter stage that becomes enabled to send a new logic state to the receiver stage's inputs. Evidently, it is ensured because any output logic transition of the receiver stage means, in theory, a correct computation of a logic state at its inputs. Consequently, only ensuring these conditions there will be a guarantee that the emitter stage will not stay without knowing about the computation end of the receiver stage.

To implement such conditions, three design mechanisms are used:

- a communication protocol between system's stages that implements a handshake by request and acknowledgement to start a certain computation and indicating its end;

- a data codification that allows the stage to detect a computation request as well identifying its end; and

- circuits of the logic functions synthesized in a certain way that do not allow the hazard generation.

#### 2.2.1 Communication Protocol

The communication between stages of a QDI system is organized by a protocol. It allows agreeing a handshake by request and acknowledgment to control the data flow and the computation. Therefore, any action produced by an emitter stage to modify the input logic state of a receiver stage is necessarily authorized before by the receiver stage's outputs.

A traditional protocol uses two phases to achieve a cycle for computation of a certain logic state X and authorization of a new one Y. However, the protocol that is currently further used in QDI systems consists of four phases. This protocol guarantees a simpler implementation (FRAGOSO, 2005; MONNET, 2007-a) because the detection

of its phases is performed by logical level rather than transition events, as it is done in the two-phase protocol.

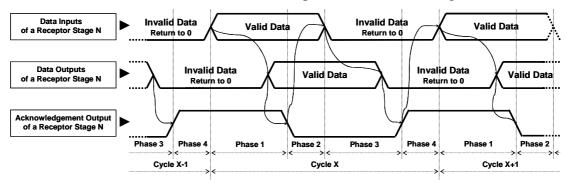

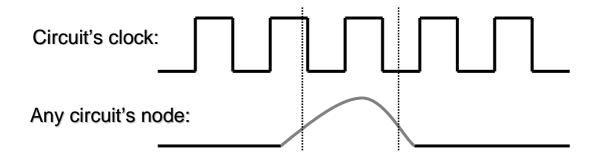

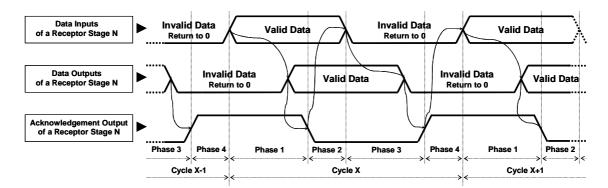

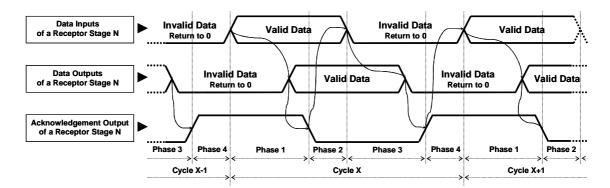

Figure 2.3 illustrates the four phases of such a protocol. In the first phase, **Phase 1**, valid data are detected at the inputs of the receiver stage N that computes and generates, by using its data outputs, a signal of acknowledgment at the computation end. In **Phase 2**, the acknowledgment is detected by the emitter stage N-1 that sends zero to all data inputs of the receiver stage N. Such returns to zero level are known as invalid data that are defined by a codification discussed in the next section. In **Phase 3**, the invalid data are detected by the receiver stage N that generates again the signal of acknowledgment. Finally, **Phase 4**, such an acknowledgment is detected by the emitter stage N-1 that is thus authorized to send new valid data to the inputs of the receiver stage N.

Figure 2.3: Four-phase protocol for a communication between stages

#### 2.2.2 Data Codification

A QDI system's stage detects the presence of new input data only by its own data switching. However, implementing such a mechanism requires necessarily a data codification based on more than one wire to represent a data bit, i.e., a multi-rail codification. The request to begin a new computation and the information of data validity can thus be included in its own data (FRAGOSO, 2005).

Otherwise, by implementing a codification that has only one wire per data bit (i.e., single rail), the use of a specific additional signal to characterize the request would be needed. In addition, the bounded-delay model would have to be used in the circuit's data path to thus ensure an end of the data computation before the end of the request signal. In fact, a fixed delay in such a request signal would have to be defined for it goes along with the computation of the slowest circuit logic. Therefore, the circuit would not be a QDI, but a Micropipeline. Furthermore, in case of using a single-rail codification without the aid of any request signal, a new logic state equal to the current state at data inputs could not be detected without the implementation of a data packet. Moreover, interpreting the beginning of the packet would require a memory bank in each stage. In order to avoid the computation time in such a package interpretation, a data codification using more than one wire per data bit would make easier not only the implementation of the logic circuit responsible to identify a request but also the circuit for acknowledgment generation.

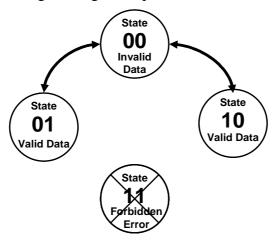

The minimum data codification, which is thus the most traditional one, uses two wires per data bit, i.e., it is the dual-rail codification. Based on two wires per data bit, four states of data codification are available (00, 01, 10, and 11) to express two logic values of a data bit (0 or 1) (MONNET, 2007-a).

For a two-phase protocol, the four states are used to ensure the codification of all possible transition events of a data bit (0=>0, 0=>1, 1=>0, and 1=>1) (FRAGOSO, 2005). The least significant bit's value of a codification state expresses the logic value of the data. In addition, a new computation request is detected by the modification of the codification state's parity ("codification state 00" => parity even, logic value 0; "state 01" => odd, value 1; "state 10" => odd, value 0; "state 11" => even, value 1). Owing to such particularities, the implementation of this protocol is more complex and less used.

For a four-phase protocol, only three states are required to code a valid-data logic value 0, another 1, and a return to zero defined as an invalid data. A fourth state is thus considered as forbidden or not used (FRAGOSO, 2005). This dual-rail data codification by three states is illustrated in Figure 2.4. This approach ensures that the transition from a certain state to another is always done by modifying only a single bit of the codification state (MONNET, 2007-a). Hazards, therefore, are not tolerated because any spurious switching could lead the circuit to an unwanted codification state. On the other hand, the generation of the acknowledgment signal can be easily implemented by a simple NOR gate monitoring the stage's outputs.

Figure 2.4: Dual-rail data codification by three states

Even if the dual-rail codification is the most used in the design of QDI circuits, other codifications based on N wires to represent a data bit are also feasible. In case of dual rail, two wires (N=2) are thus used to represent a data bit. However, only one wire (M=1) must be equal to logic level 1 to code a logic value of a data bit. To implement a QDI circuit, any codification is possible for a data bit represented by N wire(s) at which M of such wire(s) must be equal to logic level 1 to code a logic value. Unfortunately, such codifications known as M-out-of-N increase the circuit design complexity.

Codifications M-out-of-N are redundant by nature, so they ensure a greater data bit robustness to voltage variations due to environmental or intentional perturbation events. For instance, by using codification 1-out-of-2 (dual rail), if one of the data bit wires erroneously switching to a complementary logic state (as from 00 to 01; 01=>00; 01=>11; 00=>10; 10=>00; and 10=>11), the chance of the resulting erroneous state being the forbidden state 11 is 2 / 6. Under correct circuit operation, this forbidden state will never be used, therefore it can be monitored by a simple AND gate as a form of error detection scheme. As the circuit has such a redundancy able to detect errors, it is thus also more robust.

#### 2.2.3 Logic Synthesis

The structure of a QDI system can be better understood by the blocks in Figure 2.5. This illustration indeed shows a direct analogy to the typical stages of a synchronous system (MONNET, 2007-a). The memory blocks in this figure would represent the registers (groups of flip-flops) in a synchronous system. In addition, the computational blocks would implement the combinational logic in the synchronous system. However, the implementations of such blocks in a QDI system obviously have a different construction, they use actually a particular gate known as C-element, or also Muller gate (MULLER, 1959).

Figure 2.5: A structure of a QDI system by analogy to a synchronous system

In fact, the C-element is a key component in QDI asynchronous circuits to ensure the QDI property. The basic function of a C-element, Figure 2.6, is comparing the logic states at its inputs. Basically, if the inputs are identical, the state at its output will be updated with such an input state. The C-element in this condition will work like a buffer gate. On the other hand, when its inputs are not identical, the output state will be preserved. Then, the C-element will work like a memory cell. There are several circuit variations of the C-element implementation that may have, for example, more than two inputs. The traditional circuit implementations of a C-element are presented in chapter 7.

Figure 2.6: Function of a 2-input C-element gate

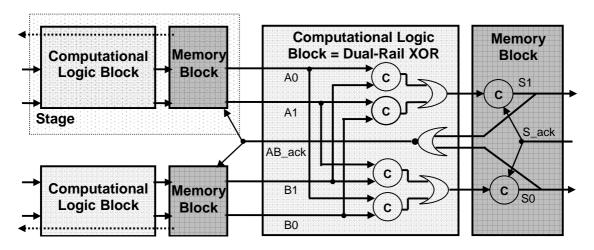

Based on this particular C-element operation and the data codification M-out-of-N (like the dual rail) associated to a communication protocol, the computational blocks in Figure 2.5 can be synthesized as hazard-free logic functions (i.e., as delay insensitive functions). The generation of a computational logic circuit operating according with the four-phase protocol, for instance, can be made by any synthesis method traditionally used in the design of synchronous circuits. The classic expression resulting from the logic synthesis, the sum of minterms, can be used to map the logic circuit (SPARSO, 2006). However, the ANDs of the mini-terms are replaced by C-elements. Such a method is thus known as Delay-Insensitive Minterm Synthesis (DIMS). The simplest method for the synthesis of logic functions in codification M-out-of-N uses the so-called MDDs (Multi-valued Decision Diagrams) (BREGIER, 2007). As an example, Figure 2.7 illustrates the MDD-based synthesis of a dual-rail XOR function for the four-phase protocol (RIOS, 2008). More complex logic functions are also feasible using the same method. As complex as the function is, smaller area overheads are achieved although

the circuits' areas continue to be greater than the conventional single-rail implementations (SPARSO, 2006).

Figure 2.7: MDD-based logic synthesis of a delay-insensitive dual-rail XOR function for the four-phase protocol

Figure 2.7 shows that the computational logic blocks of a QDI system, like in Figure 2.5, consist basically of C-elements and ORs. Unlike combinational blocks in a synchronous system, the computational blocks of a QDI system contains memory elements, since the C-elements can store logic states. However, such memory elements when used in computational blocks are not intended to store the result of a computation. They indeed implement a rendezvous behaviour and thus make the synchronization of different signals (MONNET, 2007-a). The C-element's memory property is required only to ensure the QDI property of the computational block.

In stages of a QDI asynchronous system, C-elements are not only used in the design of a computational blocks' part. They, moreover, also implement the system's memory blocks in accordance with the communication protocol and the data codification. Figure 2.8 illustrates three stages of a QDI system operating through the four-phase protocol. The memory blocks are implemented by half-buffers (RENAUDIN, 2000) characterized by two C-elements. By using its memory function, the C-elements aid the stages in

retaining their output states until a computation end. They thus also aid in coordinating the actions between each system's stage.

Figure 2.8: A QDI system operating through the four-phase protocol

#### 2.3 Conclusions

This chapter discusses the different classes of circuits and details specially the QDI asynchronous systems. It shows that the inherent redundancy of such QDI systems makes possible additional characteristics in terms of robustness and security which are significantly better than those in synchronous systems. The following paragraphs summarize these natural benefits:

- QDI systems have better resistance to attacks based on analysis of the power consumption (e.g., differential power analysis, DPA) than their synchronous counterparts. In fact, the data codification, the communication protocol, and the local control rather than a global clock make the electrical activity of these circuits with weaker current peaks. Hence, the correlations to obtain confidential data through a DPA attack are more difficult. These natural features permit thus improve the security properties of cryptographic devices used in confidential systems (BOUSSE et al, 2004; BOUSSE et al, 2005; BOUSSE, 2005; RENAUDIN et al, 2004; RENAUDIN; MONNET, 2006);

- As asynchronous systems generate weaker current peaks due to the absence of a clock edge, they emit less EMI (Electromagnetic Interference) and so there is a reduction of errors related as to noise within the circuits as to interference with nearby devices (PANYASAK, 2004; GEER, 2005);

- The QDI property makes them **largely robust by nature to timing variations** arisen from fabrication defects, environmental or intentional perturbation events (MONNET et al, 2006-c; MONNET 2007-a) that are further discussed in chapter 3. A QDI asynchronous system automatically adapts itself to such timing variations, which are known as delay faults. In theory, delay faults of any duration are tolerated. Only those on branches of isochronic forks, which represent a small part of the wires, are not tolerated;

- QDI circuits are potentially more able to tolerate any kind of transient fluctuation. The use of C-elements and a communication protocol allows particular masking forms of certain transient-fault effects. Such harmless effects of transient faults are further discussed in chapter 3. In addition, asynchronous

- systems are not vulnerable to perturbations on a clock-distribution circuit as the synchronous systems are due to attacks by malicious fault injection (MONNET et al, 2006-c; MONNET 2007-a) or even occurrence of natural transient faults;

- In QDI systems, the multi-rail codification schemes and the asynchronous communication by handshake between computation stages make **easier** the **detection and correction of soft errors** (KUANG et al., 2010). Multi-rail codifications allow the system identifying theoretically inexistent logic states (forbidden states) and, therefore, enable it detecting soft errors. Moreover, with a little additional circuitry and the assistance of the asynchronous handshake, the system can make a recomputation to correct the detected soft error before propagating it to a next circuit's computation stage.

# 3 TRANSIENT-FAULT EFFECTS ON INTEGRATED CIRCUITS

An IC performs several operations to achieve functional goals of a system. In fact, ICs implement functions providing results in accordance with input stimuli. In nornal conditions, the circuits are stimulated through operational events controlled by their applications. However, perturbation events arisen from internal or external sources can stimulate along the circuit's lifetime the occurrence of faults (ABRAMOVICI; BREUER; FRIEDMAN, 1990). The presence of a **fault** in an IC's functional element can lead it to produce incorrect operations. The occurrence of such an **error** scenario in one of the IC's elements can still perturb the system as a whole. A **failure** of the system's functional goals is illustrated by the generation of inconsistent results at IC's primary outputs (LAPRIE, 1998).

Abramovici (1990) classifies types of faults, errors, and failures in the design of a circuit. The **design errors** are thus due to faults during the circuit design, for example, incomplete or inconsistent specifications, incorrect mapping between different abstraction levels of design, or violations of design rules. There are also those **fabrication errors** which occur during the circuit's fabrication procedures as a direct consequence of some human fault in the design implementation, for instance, wrong configuration of factory's equipments or the mistaken selection of materials or components. On the other hand, there are those **fabrication defects** which are the result of imperfections or variations in the fabrication process, such as, short or open circuits, improper doping profiles, bad alignment of the layout's masks, etc. Fabrication defects give rise to stuck-at faults, which retain permanently the logic of circuit's bits. Furthermore, such defects can also generate delay faults that are delay variations of circuit's wires (internal connections) or gates.

Abramovici (1990) also classifies the **physical failures** that can occur during the circuit's lifetime. Such failures are indeed as instantaneous as short or long-term consequences of transient, intermittent or permanent faults that are induced by perturbation events arisen from environmental or intentional sources:

- Environmental perturbation events: variations of environmental factors in terms of temperature, humidity, or vibration, as well any kind of natural radiation (particles from cosmic rays or radioactive materials) or even artificial radiation (electromagnetic emission from electronics equipments, external or internal electrical noise in the circuits);

- **Intentional perturbation events**: malicious fault injections by radiation (light flashes, sources of particles or laser), by voltage variation of circuit's pins (power, clock, inputs), or even by temperature variation. All of these injection

types work as a form of attack to break secret information in confidential systems (RENAUDIN et al, 2004; MONNET, 2007-a).

The recent many technological advances in ICs have induced several researches concerning the circuits' susceptibility to faults, especially the transient faults.

In reality, the concern about the transient faults due to environmental perturbations in ICs always existed. However, until the end of 20th century, before the emergence of deep-submicron technologies, related researches were very focused on circuits located in hostile environments. Evaluations of such faults in circuits and suggestions to protect them were mostly developed for space and physics applications. With the recent deep-submicron technologies, the circuits are today designed through tiny transistors which thus determine smaller capacitances on their nodes. Moreover, the reduced voltages generate lower currents and charges to supply them. All of these advances decrease the circuit's noise margin which along with the viability of higher clock's frequency and higher density makes them more vulnerable to faults (LIMA, 2003-b; KARNIK; HAZUCHA; PATEL, 2004; KASTENSMIDT; CARRO; REIS, 2006). Hence, related researches have also become more and more important in other ICs' applications, including therefore IC-based systems at ground level.

Furthermore, also due to technological advances, there is a growing need to ensure the confidentiality in the communication of information between systems. This concern indeed always existed on systems for banking, military, and government services that require the preservation and protection of their secret information (MONNET, 2007-a). However, in recent years the data communication between systems has remarkably increased with the advances in the cellular telephony and Internet. Banking services and electronic commerce through the world wide web of computers, as applications that require security, are more and more common by using, for instance, smartcards (MONNET, 2007-a). The confidentiality of such electronics transactions is ensured by implementing secure systems based on cryptography algorithms. Nevertheless, on the other hand, cryptanalysis methods have also evolved considerably in terms of efficiency to break such secure systems. Novel classes of attacks, like the differential fault analysis (DFA), are developed based, for instance, by injecting non-invasive transient faults in system's circuits.

In accordance with the goals of this thesis, this chapter discusses briefly the transient faults induced by environmental perturbation events during the circuit's lifetime. Furthermore, the physical failures arisen from the different types of transient-fault effects on synchronous and QDI asynchronous circuits are also detailed. Such discussions render also the consequences of transient faults due to intentional perturbation events, which indeed create very similar transient voltage modifications in the circuits (MONNET, 2007-a).

#### 3.1 Transient Faults Induced by Environmental Perturbations

Many recent researches indicate that transient faults in ICs are induced mostly by environmental perturbations arisen from radiation sources.

About radiation, the physics explains as the process of propagating radiant energy in the form of waves or particles. The radiation-induced particles can hit with atoms of semiconductor devices transferring them their energy by means of ionizing or nonionizing processes. Depending on the energy and flow of the particles, the effects of such energy transfers to devices can be transient, permanent, cumulative, or even destructive (O'BRYAN et al, 1998; LABEL et al, 2000; LIMA, 2000-c; SROUR; MARSHALL; MARSHALL, 2003).

The radiation-induced transient effects on ICs are caused specially by alpha particles (released by radioactive impurities) and more importantly neutrons from cosmic rays. Such types of environmental perturbations events can produce in silicon chips ionizing processes that deposit charges on circuit's nodes. The amount of ionization and current arisen in the semiconductor devices is directly proportional to the energy lost by the radiation-induced particles (LIMA, 2003-b; KARNIK; HAZUCHA; PATEL, 2004). In fact, a current pulse generated by the charge deposition is considered a transient fault that reflects also a transient voltage fluctuation at the circuit's node (KRISHNAMOHAN, MAHAPATRA, 2004). It is well-known as a transient arisen from a single perturbation event (e.g., a particle flow in a certain circuit's node), and so-called as a single event transient (SET).

If the energy and flow of the radiation-induced particles are enough to deposit a charge that creates a significant transient effect on a node, a volatile memory element of the circuit may be perturbed (MASSENGILL et al, 2000). In this wrong way, a memory element's bit would be logically inverted featuring the well-known single event upset (SEU), which by its non-permanent and non-recurring nature is also called as soft error (SE).

These transient effects highlighted in previous paragraphs are also known as soft effects arisen from a single event: the soft single event effects (Soft SEE).

## 3.2 Types of Transient-Fault Effects

The primary harmful transient-fault effects on systems are basically the generation of soft errors highlighted in previous section and chapter 1. The most basic model to represent a soft error is abstracted at logical level of a system design. The simple logic inversion of a memory bit accurately models the characteristics of such an error.

On the other hand, soft errors give rise to secondary harmful transient-fault effects which are the failures presented at primary outputs of systems' modules.

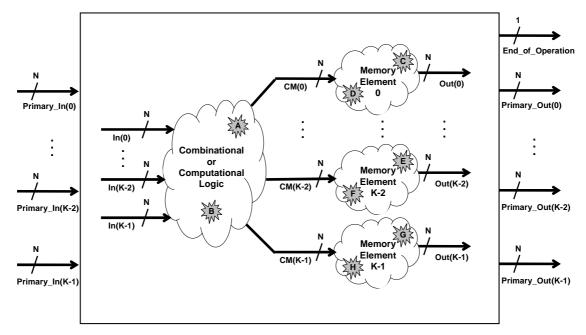

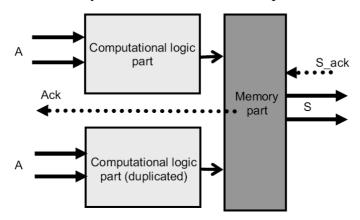

Figure 3.1, which generalizes a module of whatever system, is used in the following sections to illustrate further details of such transient-fault effects on synchronous systems or on QDI asynchronous. The illustrated module abstracts RT-level blocks characterized by K-bit registers and also combinational or computational macrocells of K bits. The K-bit registers are represented by memory macrocells of N bits.

In synchronous systems, such memory macrocells are single rail, then N=1, and typically represent flip-flops. While in QDI asynchronous systems, they are usually dual rail, so N=2, and represent C-elements. The combinational macrocells for synchronous systems are logic gates, and the computational macrocells for QDI asynchronous systems are C-elements as well logic gates. In fact, in accordance with chapter 2, such C-elements in computational macrocells do not work as registers but like AND gates that prevent the generation of hazards.

Figure 3.1: A generic hardware module to represent either a synchronous systems or a QDI asynchronous

All analysis in this chapter 3 assumes that such a module in Figure 3.1 is stimulated at its K-bit primary inputs by a certain data X. The module requires a number I of iterations along the time to process such a data X. After these I iterations, the module will provide at its K-bit primary outputs a result Y from its functional operations on the data X. Moreover, the module will also provide by a certain specific primary output an indication signal (i.e., End\_of\_Operation in Figure 3.1) for the end of such a result Y's computation. In fact, It is used to indicate to another module the result Y's availability at its K-bit primary outputs.

The module thus needs I execution cycles (i.e., I iterations) to accomplish its function. In a synchronous system, an execution cycle is a clock period, while in a QDI asynchronous system, it is the time required to perform, for example, the four protocol's phases illustrated in Figure 2.3. Hence, the module's operating frequency is defined multiplying I by the inverse of the total computation time due to the I iterations. Such a frequency for an asynchronous system is an average, while for a synchronous, it is constant in accordance with the clock rhythm.

#### 3.2.1 Harmful Effects of Transient Faults on Synchronous Circuits

The effects of transient faults on synchronous circuits are well defined by many works (KARNIK; HAZUCHA; PATEL, 2004). Depending on the circuit part that a transient fault is induced, different consequences arise on a synchronous system like that abstracted in Figure 3.1. In fact, there are three cases based on occurrences of single transient faults (i.e., SETs as explained in chapter 1 and previous section 3.1):

Case (1): A SET occurring on a D-flip-flop that implements a memory macrocell: the worst effect is a **direct soft error** (**dSE**). It means the flip-flop's output is wrongly inverted until a next system's event that updates such a memory. If the SET starts during the latching window (set-up and hold times), the worst case is also a dSE;

- Case (2): A SET on a D-latch which implements also a memory macrocell: the worst situation is a dSE when the latch is not enabled. Otherwise, when the latch is enabled, the worst effect is a SET propagation to the latch's output;

- Case (3): A SET on a combinational logic macrocell: the worst effect is the combinational circuit propagates the SET up to the input of a memory circuit (flip-flop or latch) generating an **indirect Soft Error (iSE)**. Furthermore, the SET can reach a non-registered primary output (i.e., a module's output that ends nor by a memory macrocell but by a combinational logic), and so the SET propagates to another module;

## 3.2.2 Harmful Effects of Transient Faults on QDI Asynchronous Circuits

A simple QDI asynchronous circuits' analysis in terms of computational and memory blocks allows a direct analogy with combinational and memory blocks in synchronous circuits (MONNET; RENAUDIN; LEVEUGLE, 2005-b). Therefore, transient-fault effects on synchronous circuits, discussed in previous section in accordance with Figure 3.1, are easily transposed to QDI circuits by only including the C-element's concepts:

- Case (4): A SET occurring on a C-element that implements part of a memory macrocell: the worst effect is a dSE when the C-element has different values at its inputs. This is because the C-element would work as a memory circuit. In contrast, when its inputs have the same value, the worst consequence is a SET appearing at its output, since the C-element would work like a buffer;

- Case (5): A SET on a computational logic macrocell: such a situation is similar to case (3) detailed in the previous section for synchronous circuits, even though the memory macrocells consists of C-elements. Observe however that computational macrocells' C-elements under transient faults never result in dSE because they do not work as logic state registers of a system's module. In fact, it may generate iSE in memory macrocell's C-elements that characterize the module's registers.

#### 3.2.3 Harmless Effects of Transient Faults