# Program Transformations and Memory Architecture Optimizations for High-Level Synthesis of Hardware Accelerators

Alexandru Plesco

### ▶ To cite this version:

Alexandru Plesco. Program Transformations and Memory Architecture Optimizations for High-Level Synthesis of Hardware Accelerators. Other [cs.OH]. Ecole normale supérieure de lyon - ENS LYON, 2010. English. NNT: . tel-00544349

# HAL Id: tel-00544349 https://theses.hal.science/tel-00544349

Submitted on 7 Dec 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

$N^o$  d'ordre: 589

Nº attribué par la bibliothèque: \_\_ENSL589

## THÈSE

# en vue d'obtenir le grade de Docteur de l'Université de Lyon ÉCOLE NORMALE SUPÉRIEURE DE LYON

spécialité: Informatique Laboratoire de l'Informatique du Parallélisme École Doctorale de Mathématiques et Informatique Fondamentale

présentée et soutenue publiquement le 27 Septembre 2010 par Monsieur **Alexandru PLESCO**

#### Titre:

Transformations de programmes et optimisations de l'architecture mémoire pour la synthèse de haut niveau d'accélérateurs matériels

#### Co-Directeurs:

Monsieur Christophe Alias Monsieur Alain Darte Monsieur Tanguy RISSET

### Après avis de:

Monsieur Frédéric PÉTROT (Rapporteur) Monsieur Patrice QUINTON (Rapporteur)

#### Devant la commission d'examen formée de:

| Monsieur Steven Derrien (Examinateur)            |     |

|--------------------------------------------------|-----|

| Monsieur Ronan Keryell (Examinateur)             |     |

| Monsieur Frédéric Pétrot (Président/Rapporteur)  |     |

| Monsieur Patrice Quinton (Examinateur/Rapporteur | r)  |

| Monsieur Tanguy RISSET (Examinateur/Co-directe   | ur) |

$N^o$  order: 589

$N^o$  assigned by the library: \_\_ENSL589

### PhD THESIS

# for the grade of Doctor of Université de Lyon ÉCOLE NORMALE SUPÉRIEURE DE LYON

field: Computer Science

# Laboratoire de l'Informatique du Parallélisme École Doctorale de Mathématiques et Informatique Fondamentale

presented and defended the 27 of September, 2010

by Mr. Alexandru PLESCO

#### Title:

Program Transformations and Memory Architecture Optimizations for High-Level Synthesis of Hardware Accelerators

#### **Supervisors:**

Mr. Christophe Alias Mr. Alain Darte Mr. Tanguy Risset

### With the approval of:

Mr. Frédéric PÉTROT (Reviewer) Mr. Patrice QUINTON (Reviewer)

#### With the dissertation committee composed of:

| Mr. | Alain    | Darte   | (Member/Supervisor)  |

|-----|----------|---------|----------------------|

| Mr. | Steven   | Derrien | (Member)             |

| Mr. | Ronan    | Keryell | (Member)             |

| Mr. | Frédéric | Pétrot  | (President/Reviewer) |

| Mr. | Patrice  | Quinton | (Member/Reviewer)    |

| Mr. | Tanguy   | RISSET  | (Member/Supervisor)  |

Alexandru Plesco: Program Transformations and Memory Architecture Optimizations for High-Level Synthesis of Hardware Accelerators, Doctorate, © September 27, 2010

Supervisors:

Christophe Alias

Alain Darte

Tanguy Risset

Faculty:

Computer Science

Department:

Laboratoire de l'Informatique du Parallélisme

University:

ÉCOLE NORMALE SUPÉRIEURE DE LYON

Location:

Lyon, France

Time Frame:

September 27, 2010

Version 1.0

### $\label{eq:continuous} Ohana \text{ means family.}$ Family means no body gets left behind, or forgotten.

— Lilo & Stitch

Dedicated to the loving memory of Lidia Plesco.  $1960-2009 \label{eq:lovenormal}$

Consider Columbus:

He didn't know where he was going.

When he got there he didn't know where he was.

When he got back he didn't know where he had been.

And he did it all on someone else's money.

(LINUX FORTUNE)

# Acknowledgments

Many thanks to my supervisors for their moral support as well as for their help that made this thesis possible.

Thanks to Christophe ALIAS who joined forces during the last year of the thesis and who helped very much during the work and writing of the last chapter of this thesis.

Thanks to Alain DARTE for his guidance during the whole thesis, for his help and persistence that helped pass through seemingly unsolvable problems and many thanks for his major help during the writing of this thesis.

Thanks to Tanguy RISSET for proposing the internship on high level synthesis that I was searching for, for helping me find and apply for thesis scholarship, for helping me with the work and writing of Chapter 3 of this thesis, and for helping to find and apply for an ATER position that gave me time to finalize all the works on this thesis.

Many thanks to jury members for their time and pertinent remarks that helped me improve this writing.

Special thanks to my girlfriend Andreea CHIS for being with me on sunny days and especially during rainy ones.

Thanks to my family who made me who I am, and who supported me till the last moment of this thesis and to my precious mother that I miss a lot and who was with me till the last moments of her life.

Thanks to all the members of the LIP laboratory at ENS Lyon and TC laboratory at INSA Lyon that made the work here pleasant and fun.

Thanks to Bogdan PASCA and Christophe ALIAS for all the time passed in front of a white board during "tea breaks".

Thanks to my friends and everyone else that I didn't mention here for their help and support.

# Abstract

A wide category of sold products including telecommunication and multimedia propose more and more advanced features and functionalities. These functionalities come at a cost of increased design complexity. For performance and power budget issues, these features can be accelerated using dedicated hardware accelerators. To meet the required time-to-market and development price, traditional hardware design methodologies are not sufficient and the use of high-level synthesis (HLS) tools is an appealing alternative. These tools are now getting more mature for generating hardware accelerators with an optimized internal structure, thanks to efficient scheduling techniques, resource sharing, and finite-state machines generation. However, interfacing them with the outside world, i.e., integrating the automatically-generated hardware accelerators within the complete design, with optimized communications, so that they achieve the best throughput, remains a very hard task, reserved to expert designers. The leitmotiv of this thesis was to study and to develop source-to-source strategies to improve the design of these interfaces, trying to consider the HLS tool as a back-end for more advanced front-end transformations.

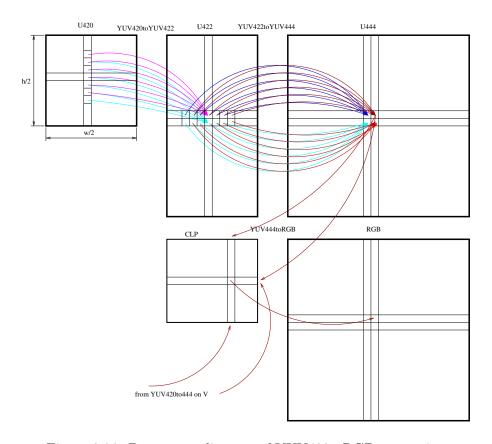

In the first part of the thesis, as a case study, we designed by hand, in VHDL, an intelligent glue logic to interface an accelerator, for matrix-matrix multiplication, generated by the MMAlpha HLS tool. Using data dependence information, we implemented double-buffering and blocking techniques on a scratchpad-like local SRAM memory to exploit data reuse. This increased significantly the performance of the system but required also a significant engineering effort. We then showed, on several multi-media applications and with another HLS tool, Spark, that the same benefit could be obtained with a preliminary semi-automatic source-to-source (here C-to-C) transformations step. For that, we used an advanced state-of-the-art compiler front-end, based on the Open64 compiler and the WRaP-IT framework for polyhedral transformations. Significant improvements were shown in particular on the synthesis of part of the video color space conversion from MediaBench II benchmarks, for which data was fed through a processor cache memory. This study demonstrated the importance of loop transformations as a pre-processing step to HLS tools, but also the difficulty to use them depending on the HLS tool features to express external communications.

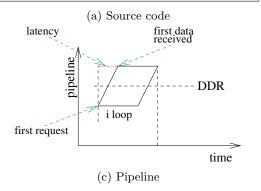

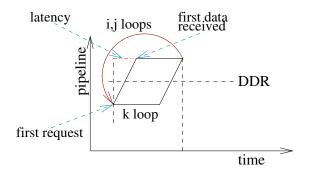

In the second part of the thesis, using the C2H HLS tool from Altera, which can synthesize hardware accelerators communicating to an external DDR-SDRAM memory, we showed that it is possible to automatically restructure the application code, to generate adequate communication processes in C, and to compile them all with C2H, so that the resulting application is highly-optimized, with full usage of the memory bandwidth. These transformations and optimizations, which combine techniques such as double buffering, array contraction, loop tiling, software pipelining, among others, were incorporated in an automatic source-to-source transformation tool, called Chuba, based on the polyhedral model representation. Our study shows that high-level synthesis (HLS) tools can indeed be used as back-end optimizers for front-end optimizations, as it is the case for standard compilation with high-level transformations developed on top of assembly-code optimizers. We believe this is the way to go for making HLS tools viable.

**Keywords:** High-level synthesis tools, hardware accelerators, DDR SDRAM, optimized communications, HPC, source-to-source program transformations, reconfigurable architectures, FPGA.

# Résumé

Une grande variété de produits vendus, notamment de télécommunication et multimédia, proposent des fonctionnalités de plus en plus avancées. Celles-ci induisent une augmentation de la complexité de conception. Pour satisfaire un budget de performance et de consommation d'énergie, ces fonctionnalités peuvent tre accélérées par l'utilisation d'accélérateurs matériels dédiés. Pour respecter les délais nécessaires de mise sur le marché et le prix de développement, les méthodes traditionnelles de conception de matériel ne sont plus suffisantes et l'utilisation d'outils de synthèse de haut niveau (HLS) est une alternative intéressante. Ces outils sont maintenant plus aboutis et permettent de générer des accélérateurs matériels possédant une structure interne optimisée, grce à des techniques d'ordonnancement efficaces, de partage des ressources et de génération de machines d'états. Cependant, les interfacer avec le monde extérieur, c'est-à-dire intégrer des accélérateurs matériels générés automatiquement dans une conception complète, avec des communications optimisées pour atteindre le meilleur débit, reste une tche très ardue, réservée aux concepteurs experts. Le leitmotiv de cette thèse était d'étudier et d'élaborer des stratégies source-à-source pour améliorer la conception de ces interfaces, en essayant d'envisager l'outil HLS comme back-end pour des transformations front-end plus avancées.

Dans la première partie de la thèse, comme étude de cas, nous avons conu à la main, en VHDL, une logique intelligente permettant l'interfaage d'un accélérateur, calculant la multiplication de deux matrices, généré par l'outil de synthèse MMAlpha. En utilisant des informations sur les dépendances de données, nous avons implanté des techniques de double tampon et de calcul/transfert par bloc (pavage), pour des mémoires locales SRAM de type scratchpad, pour améliorer la réutilisation des données. Ceci a permis d'augmenter de manière significative les performances du système, mais a également exigé un effort important de développement. Nous avons ensuite montré, sur plusieurs applications de type multimédia, avec un autre outil de HLS, Spark, que le mme avantage pouvait tre obtenu avec une étape préliminaire semi-automatique de transformations source-à-source (ici de C vers C). Pour cela, nous avons utilisé le front-end d'un compilateur avancé, basé sur le compilateur Open64 et l'outil WRaP-IT de transformations polyédriques. Des améliorations significatives ont été présentées, en particulier pour la synthèse de la conversion de l'espace couleur (extrait d'un benchmark de MediaBench II), dont les données étaient transmises via une mémoire cache. Cette étude a démontré l'importance des transformations des boucles comme étape de pré-traitement pour les outils HLS, mais aussi la difficulté de les utiliser en fonction des caractéristiques de l'outil HLS pour exprimer les communications externes.

Dans la deuxième partie de la thèse, en utilisant l'outil C2H HLS d'Altera qui peut synthétiser des accélérateurs matériels communiquant avec une mémoire externe DDR-SDRAM, nous avons montré qu'il était possible de restructurer automatiquement le code de l'application, de générer des processus de communication adéquats, <u>écrits entièrement en C</u>, et de les compiler <u>avec C2H</u>, afin que l'application résultante soit hautement optimisée, avec utilisation maximale de la bande passante mémoire. Ces transformations et optimisations, qui combinent des techniques telles que l'utilisation de double tampon, la contraction de tableaux, le pavage, le pipeline logiciel, entre autres, ont été intégrées dans un outil de transformation automatique source-à-source, appelé Chuba et basé sur la représentation du modèle polyédrique. Notre étude montre que ainsi qu'il est possible d'utiliser

certains outils HLS comme des optimiseurs de niveau back-end pour les optimisations effectuées au niveau front-end, comme c'est le cas pour la compilation standard o des transformations de haut niveau sont développées en amont des optimiseurs au niveau assembleur. Nous pensons que ceci est la voie à suivre pour que les outils HLS deviennent viables.

**Mots-clés :** synthèse de haut niveau, accélérateurs matériels, DDR SDRAM, optimisations des communications, HPC, transformations de programme source-à-source, architectures reconfigurables, FPGA.

# **Publications**

Some ideas and figures have appeared previously in the following publications:

Christophe Alias, Alain Darte, and Alexandru Plesco. Optimizing DDR-SDRAM communications at C-level for automatically generated hardware accelerators. An experience with the Altera C2H HLS tool. In 21st IEEE International Conference on Application-specific Systems, Architectures and Processors (ASAP'10). IEEE Computer Society, July 2010

Alexandru Plesco and Tanguy Risset. Coupling loop transformations and high-level synthesis. In SYMPosium en Architectures nouvelles de machines (SYMPA'08), Fribourg, Switzerland, February 2008

# Contents

| 1 | Intr | roduction                                                                   | 1  |

|---|------|-----------------------------------------------------------------------------|----|

| 2 | Rela | ated works in high-level synthesis                                          | 5  |

|   | 2.1  | Hardware description languages and early HLS                                | 5  |

|   |      | 2.1.1 Conventional low-level hardware description languages                 | 5  |

|   |      | 2.1.2 Early attempts in high-level synthesis                                | 7  |

|   | 2.2  | Advances in high-level synthesis                                            | 7  |

|   |      | 2.2.1 Low-level hardware constructs                                         | 8  |

|   |      | 2.2.2 Configuration files and compiler directives                           | 10 |

|   |      | 2.2.3 Class libraries, template architectures, etc                          | 13 |

|   |      | 9                                                                           | 15 |

|   |      |                                                                             | 16 |

|   | 2.3  | o v                                                                         | 17 |

|   |      | 2.3.1 Transformations that change the computation order                     | 19 |

|   |      | 2.3.2 Transformations that change the memory access order and its size      | 26 |

|   | 2.4  | Conclusions                                                                 | 29 |

| 3 | Tio  | htly-coupled architectures with cache: experiments with MMAlpha & Spark     | 21 |

| U | 3.1  |                                                                             | 31 |

|   | 3.2  | A case study for a matrix-matrix multiplication design generated by MMAlpha | 34 |

|   | 0.2  | 3.2.1 Algorithm description                                                 | 34 |

|   |      | 3.2.2 Implementation                                                        | 37 |

|   |      | •                                                                           | 43 |

|   | 3.3  |                                                                             | 44 |

|   | 3.3  | •                                                                           | 45 |

|   |      | 3.3.2 Loop transformations in HLS, in the context of Spark                  | 51 |

|   |      | 3.3.3 First example: edge detection                                         | 54 |

|   |      |                                                                             | 59 |

|   | 3.4  | - '                                                                         | 64 |

| 4 | Loc  | al SRAM with external DDR: Altera C2H flow                                  | 65 |

| _ | 4.1  |                                                                             | 65 |

|   | 4.2  |                                                                             | 67 |

|   |      | *                                                                           | 68 |

|   |      | • • •                                                                       | 69 |

|   |      |                                                                             | 70 |

|   |          | 4.2.4 Pragmas for aliasing and connections                                     |

|---|----------|--------------------------------------------------------------------------------|

|   | 4.3      | Motivating examples with DDR accesses                                          |

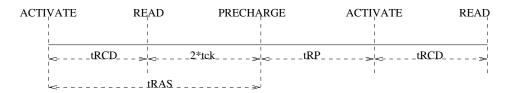

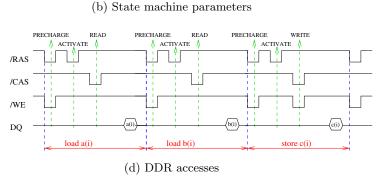

|   |          | 4.3.1 DDR-SDRAM principles                                                     |

|   |          | 4.3.2 Examples                                                                 |

|   |          | 4.3.3 Optimizing DDR accesses                                                  |

|   | 4.4      | First attempts toward a solution                                               |

|   |          | 4.4.1 Blocking                                                                 |

|   |          | 4.4.2 Juggling                                                                 |

|   |          | 4.4.3 Conclusions                                                              |

|   | 4.5      | A solution with multiple communicating accelerators                            |

|   |          | 4.5.1 Architecture description                                                 |

|   |          | 4.5.2 Hardware accelerator implementations                                     |

|   |          | 4.5.3 Experimental results                                                     |

|   |          | 4.5.4 Coarse-grain software pipelining                                         |

|   |          | 4.5.5 Automation of code transformations                                       |

|   |          |                                                                                |

| 5 | Aut      | comation of code transformations 121                                           |

|   | 5.1      | Introduction                                                                   |

|   |          | 5.1.1 Preliminaries                                                            |

|   |          | 5.1.2 Overview of the method                                                   |

|   | 5.2      | Communication coalescing                                                       |

|   |          | 5.2.1 Specification                                                            |

|   |          | 5.2.2 An exact solution for computing the Load and Store sets                  |

|   | 5.3      | Local memory management                                                        |

|   |          | 5.3.1 Array contraction                                                        |

|   |          | 5.3.2 Mapping global memory to local memory                                    |

|   | 5.4      | Code generation                                                                |

|   |          | 5.4.1 General organization                                                     |

|   |          | 5.4.2 Generation of load, compute, and store kernels                           |

|   | 5.5      | Experimental results                                                           |

|   | 5.6      | Conclusion                                                                     |

| c | <b>C</b> |                                                                                |

| 6 | Con      | aclusion 151                                                                   |

| 7 | Apr      | pendix 165                                                                     |

|   | 7.1      | MMAlpha                                                                        |

|   |          | 7.1.1 Reference code XUP                                                       |

|   |          | 7.1.2 Alphahard code of the matrix-matrix multiplication                       |

|   | 7.2      | Spark + WRaP-IT                                                                |

|   | •        | 7.2.1 Oprofile results                                                         |

|   |          | 7.2.2 Original source code                                                     |

|   |          | 7.2.3 WRaP-IT code transformations                                             |

|   | 7.3      | Altera C2H                                                                     |

|   |          | 7.3.1 Manually-transformed DMA double-buffering implementation                 |

|   |          | 7.3.2 Manually-transformed vector-sum double-buffering implementation 184      |

|   |          | 7.3.3 Manually-transformed matrix-multiply double-buffering implementation 189 |

|   |          |                                                                                |

# Acronyms

**ALU** arithmetic logic unit

**ALUT** Altera look-up table

**ANSI** American National Standards Institute

ANSI-C C standard published by American National Standards Institute

**API** Application Programming Interface

**ASH** Application-Specific Hardware

**ASIC** application-specific integrated circuit

**Avalon-MM** Avalon MM

Avalon-ST Avalon ST

В

**BRAM** block select RAM

$\mathbf{C}$

CAD computer-aided design

C C programming language

**CSP** communicating sequential processes

**C++** C++

CWB CyberWorkBench

**COMU** communication and interface unit

**CABA** cycle accurate and bit accurate

**CLooGVHDL** CLooGVHDL

**C2H** C-to-Hardware Acceleration

**CPU** central processing unit

CAS column address strobe

**CL** CAS latency

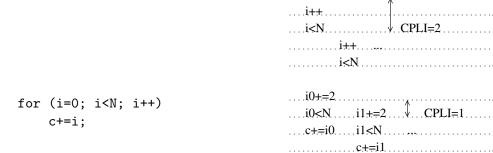

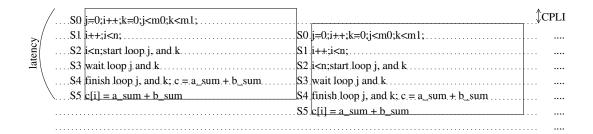

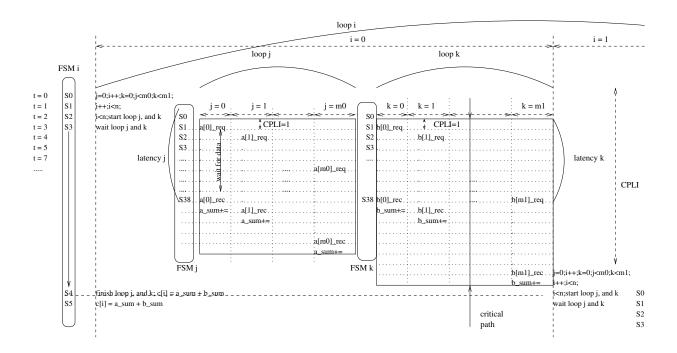

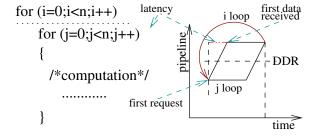

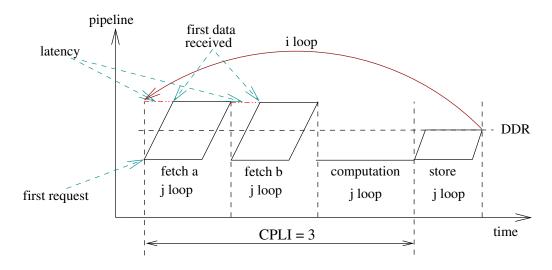

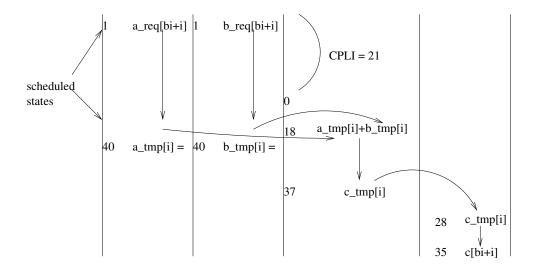

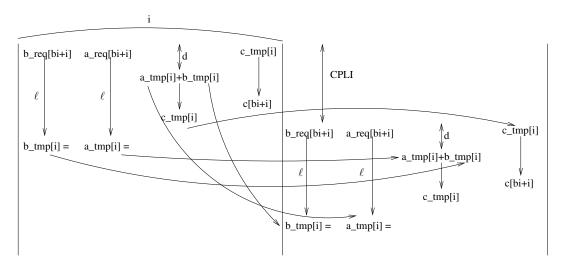

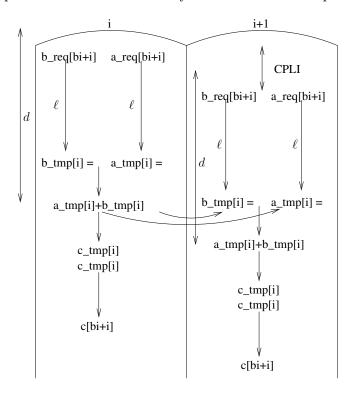

**CPLI** cycles per loop iteration

**CLB** configurable logic block

**CDFG** control/data flow graph

**CODEC** coder-decoder

D

**DDP** draft data-path

**DSP** digital signal processing

**DFG** data flow graph

**DRAM** dynamic RAM

**DDR** double data rate SDRAM

**DDR SDRAM** double data rate SDRAM

**DMA** direct memory access

**DSOCM** data-side OCM

**DIMM** dual in-line memory module

$\mathbf{E}$

**EDA** electronic design automation

**EDIF** Electronic Design Interchange Format

**ESL** electronic system level

**EDK** embedded development kit

F

**FSM** finite state machine

FPGA field programmable gate array

FHM fast hardware model

**FIFO** First In, First Out

G

**GLD** gate-level description

**GCC** GNU Compiler Collection

**GPP** general purpose processor

**GUI** graphical user interface

GALS globally asynchronous locally synchronous

Η

**HLS** high-level synthesis

**HMMU** hardware memory management unit

**HA** hardware accelerator

**HDL** hardware description language

**HW** hardware

**HPC** high-performance computing

**HPF** High Performance Fortran

**HTG** hierarchical task graph

T

**IP** intellectual property

**IR** intermediate representation

IC integrated circuit

ICD integrated circuit design

**I/O** Input/Output

**IDE** integrated development environement

**ISA** instruction set architecture

**ISPS** instruction set processor specification

II initiation interval

J

JEDEC joint electron device engineering council

JTAG joint test action group

$\mathbf{L}$

LDP logic design phase

LIS latency insensitive systems

М

**MEMU** memory unit

MMU memory management unit

MM memory-mapped

Ν

**NPA** non-programmable accelerators

0

**OOP** object-oriented programming

Open64 Open64

**OPB** on-chip peripheral bus

**OCM** on-chip memory

**ORC** Open Research Compiler

Ρ

PU processing unit

**PLB** processor local bus

R.

**RTL** register transfer level

**RAM** random access memory

**ROM** read only memory

**RISC** reduced instruction set computing

R/W read/write

S

**SW** software

**SOPC** system on a programmable chip

**SOC** system on chip

**S2S** source-to-source

**SSA** static single assignment form

**SCOP** static control part

**SRAM** static RAM

**SDRAM** synchronous DRAM

**ST** streaming interface

SystemC SystemC

**SIMD** single instruction, multiple data

**SSE** streaming SIMD extensions

Τ

**TLM** transaction-level modeling

**TLM-T** TLM with timing

U

**UML** Unified Modeling Language

**USP** user specification phase

V

VHSIC very-high-speed IC

VHDL VHSIC hardware description language

**Verilog** Verilog

**VLSI** very-large-scale integration

**VLIW** very large instruction word

W

WHIRL Open64 intermediate representation

WRaP-IT WHIRL Represented as Polyhedra

**WCET** worst-case execution time

Χ

**XNF** Xilinx netlist format

**XUP** Xilinx university program

# Chapter 1

# Introduction

Recent trends in embedded system design have brought new concepts such as platform-based design, network on chip, and higher levels of specification formalisms. Using predefined hardware blocks, also known as intellectual property (IP) re-use, is now widely considered as the main way of improving design efficiency. Embedded software design, i.e., the design and optimization of the software, takes now a major part of the time of a system on chip (SOC) design (for example the complete design of a smartphone), which includes the design of the architecture and of the applications that will be running on it. However, for widely-sold products such as telecommunication and multimedia devices, the design of dedicated hardware accelerators (IP design) is still mandatory because it provides better trade-offs between performances (especially in terms of power consumption) and cost (chip area).

The increasing complexities of accelerated algorithms and of demands of processing power have led integrated circuit (IC) manufacturers to an ever increasing IC size and complexity. Using traditional languages such Verilog or VHDL <sup>1</sup> to specify a complex IC design becomes a very tedious and error-prone task. In order to minimize this design effort, the abstraction level of the specification languages was increased. The tools developed to synthesize a circuit from such a high-level abstraction have been called HLS tools.

For many years, HLS has been foreseen as the solution to accelerate dedicated hardware design. Ideally, HLS should enable the automatic generation of efficient hardware designs from functional specifications expressed in some high-level programming language. We think that HLS failed, up to now, to integrate the industrial design flow because it was not mature enough to solve important technical problems:

- A huge design space to explore: the potential parallelism and the variety of target architecture technologies imply the use of multi-criteria optimizations. Some choices must be made by the designer to reduce the design space.

- Interface design: in many HLS tools, the process of integration of the generated hardware accelerator into the system is either manual or based on template-based interfaces that do not take into account the data transfer pattern of the accelerator.

- The memory bottleneck: the memory size and the memory traffic have become major components in the chip power consumption. Optimizing data accesses is even more difficult than optimizing parallelism exploitation.

- Data reuse: while some high-performance compilers have very efficient code transformation

<sup>1.</sup> In VHSIC hardware description language (VHDL), VHSIC stands for very-high-speed IC.

techniques to increase the data reuse in central processing unit (CPU) with caches, HLS tools usually leave these transformations and optimization decisions to the user.

In recent years HLS has become a necessity, mainly because the exponential increase in the number of gates per chip far outstrips the productivity of human designers. Besides, applications that need hardware accelerators usually belong to domains, like telecommunications, multimedia and game platforms, where fast turn-around and time-to-market minimization are paramount.

Today, synthesis tools for field programmable gate arrays (FPGAs) or application-specific integrated circuits (ASICs) come in many shapes. At the lowest level, there are proprietary synthesis and place and route tools, whose input is a VHDL or Verilog specification at the structural level or register transfer level (RTL). The direct use of these tools will always be difficult and restricted to expert hardware designers. Indeed, a structural description is completely different from an usual algorithmic language description, as it is written in term of interconnected basic operators. Also, synthesis tools have trouble handling loops. This is particularly true for logic synthesis systems, where loops are systematically unrolled (or considered as sequential) before synthesis. More generally, a VHDL design is at a too low level to allow the designer to perform, easily, higher-level code optimizations. This is especially true on multi-dimensional loops and arrays, which are of paramount importance to exploit parallelism, pipelining, and perform memory optimizations.

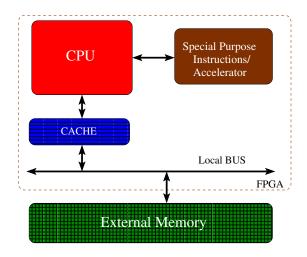

In the last decade, important efforts have been made to make possible the generation of lowlevel VHDL specification from higher-level specifications. Two main approaches can be identified. The first one is the bottom-up approach. Different tools such as the "behavioral compiler" from Synopsys [18] tried to synthesize from a common language such as VHDL with added behavioral abstractions. However, this approach failed to establish itself as the solution since it did not diminish sufficiently the design effort and it did not increase the synthesis quality enough for pushing the designers to learn and use it. The other approach is a top-down approach. A lot of works considered a very commonly used and known language like such as C programming language (C) or C++ (C++). To increase the quality of the synthesis results, the languages support extensions for low-level hardware constructs and compiler directives that are used by the user to guide the synthesis process. At the beginning, these languages had very little success mostly due to poor synthesis results. However, later on, more advanced languages such as Handel-C [16] and tools appeared, both in academia, such as Spark [78], Gaut [90], Ugh [28], Nisc [9], and in industry such as C2H [2], Catapult [8], Impulse-C [7], Pico Express [11], to quote but a few. These tools are now quite efficient for generating finite-state machines, for exploiting instruction-level parallelism, operator selection, resource sharing, and even for performing some form of software pipelining, for one given kernel. In other words, we believe that it now start to be acceptable to rely on them for optimizing the heart of accelerators, i.e., the compute part of it. In other words, HLS tool may be considered as the equivalent of back-end optimizers in standard (software) compilers.

However, this is only part of the complete design. In general, the designer seeks a pipelined solution with optimal throughput, where the mediums for data accesses (either to local memory or for outside communications) are saturated, in other words, a solution where bandwidth is the limiting factor. The HLS tool should then instantiate the necessary hardware and schedule computations inside the hardware accelerator so that data are consumed and produced at the highest possible rate. But, for most tools, the designer has still the responsibility to decompose the application into smaller communicating processes, to define the adequate memory organization or communicating buffers, and to integrate all processes in one complete design with suitable synchronization mechanisms. This task is extremely difficult, time-consuming, and error-prone. Some designers

even believe that relying on today's HLS tools to get the adequate design is just impossible and they prefer to program directly in VHDL. Indeed, some HLS tools do not consider the interface with the outside world at all: data are assumed to be given on input ports, available for each clock cycle, possibly with a timing diagram to be respected [77, 63]. Then, the user has to design all the necessary glue (explicit communications, scheduling of communications, synchronizations) in VHDL or with ad-hoc libraries and structures [70][47, Chap. 9]. Some other tools, for example Ugh and CatapultC [28, 8], can rely on First In, First Out (FIFO)-based communication. The designer still needs to define the FIFO sizes, the number of data packed together in a FIFO slot (to provide more parallelism), and to prefetch data to hide memory latencies. Finally, some tools, such as C2H, also allow direct accesses to an external memory and is (sometimes) able to pipeline them. But, again, the designer has to perform preliminary code transformations to change the computations order and the memory organization to hide the latency and exploit the maximal bandwidth.

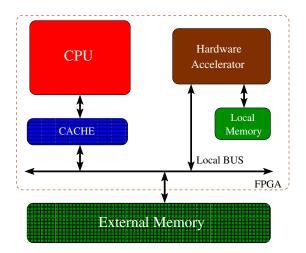

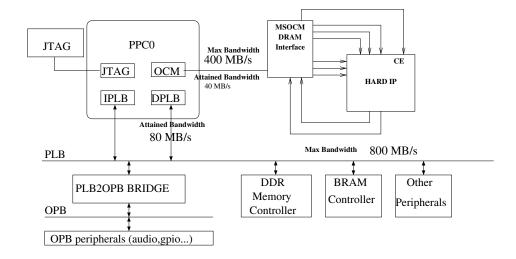

The leitmotiv of this thesis consists in optimizing the design of the interface that connects the accelerator to the outside world. As we know, most of the time the performance of a hardware accelerator is limited by the data availability. Thus, optimizing the data availability can increase its performance. The first part of this work (Chapter 3) concerns a situation where the generated hardware accelerator can take advantage of an existing cache in the architecture, directly or indirectly. The second part (Chapter 4) explores the situation where the hardware accelerator can and has to access directly an external double data rate SDRAM (DDR) memory.

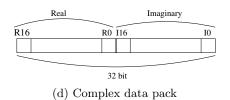

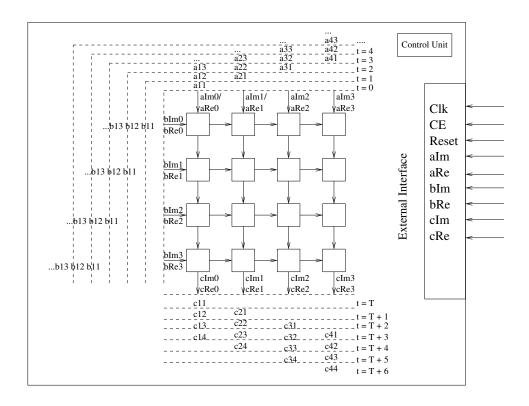

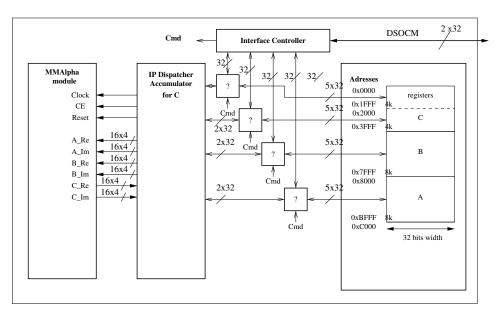

In the first part of Chapter 3, instead of using a template interface (limited by nature) to the outside world, we build a glue logic that contains the interface and a local memory architecture. Data access information from the application is used to find the possible data reuse. We manually generated a local memory architecture that conform to this data reuse information. The whole logic is connected to the processor and we analyze specific aspects of this type of connection. This study is done with the HLS tool MMAlpha for a particular application, the matrix-matrix multiplication of complex numbers, and is exposed in the first part of Chapter 3. It demonstrates, on one particular example, how difficult is the interfacing problem and what is the potential loss of performance of such an interface in a complete system.

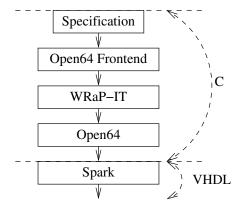

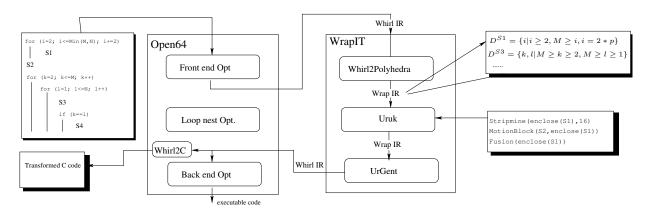

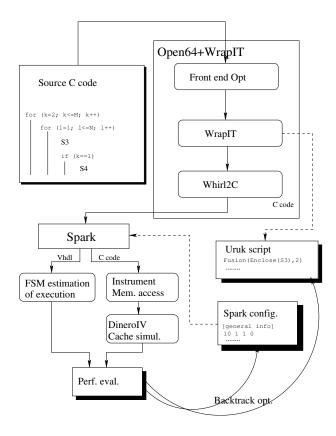

In general, and not only for the tool we used (MMAlpha), designing such a glue logic by hand is a very time-consuming and error-prone process, and performances are not always as good as expected. Another solution to improve the data availability is to transform the input code of the HLS tool to increase the data reuse. But transforming the code by hand is not an easy task either. Such transformation could be implemented in the HLS tool itself. However, this would require an advanced knowledge of its intermediate representation (IR) and, anyway, most of the time, these tools are provided in binary format, so such a transformation stage cannot be integrated. Instead, in the second part of Chapter 3, we present a source-to-source automatic code transformation methodology based on the WRaP-IT loop transformation library and scripting language Uruk. Being source-to-source, this methodology can be used in front of any tool whose input is a specification in C, so as to perform, as a pre-processing step, some of the loop transformations that are mandatory to get the code in a suitable form to go through the HLS tool and get acceptable performances. Our study focuses on one particular HLS tool, Spark, and on optimizing the memory communications and data reuse. This requires a local memory where the reused data can be stored. As Spark is not able to generate local memories, we use the cache available on the platform to control the data accesses. But our study goes beyond the two particular tools we use (Spark and WRaP-IT, itself integrated in Open64): it demonstrates that HLS can be coupled with software compilation to achieve even better results than HLS tools alone can do. This does not eliminate the need for loop transformations fully integrated in the HLS tool (some may be mandatory, depending on its design flow), but it lets the user control and apply some of them in a semi-automatic way at source level.

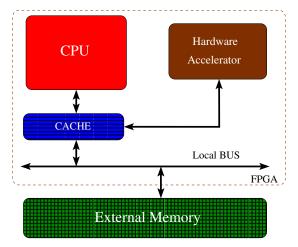

In Chapter 3, the performance improvements were obtained mostly thanks to data reuse, either by exploiting an available cache or by designing a local memory architecture. Designing such a memory architecture by hand is not only difficult but it is also not very flexible. Since, as mentioned earlier, HLS tools are getting more mature to generate compute-parts of applications, one should indeed be able to apply various code transformations at source level so as to optimize data transfers and reuse, and to rely on the HLS tool itself to synthesize the result of these transformations, including the required glue (if any). We believe that being able to automatically generate an efficient interface for an automatically-generated accelerator is a sine qua non condition for making HLS tools a usable thus viable solution to hardware design, in the same way a traditional front-end compiler can perform high-level optimizations on top of any assembly-code optimizer. It is no longer acceptable that the user spends so much time to interface the accelerator obtained by HLS as if, today, when compiling C to assembly code, the user had to spend a lot of time connecting the different pieces of automatically-generated assembly code. The challenge here is thus to be able to perform code optimizations at C level that are directly beneficial when used in front of an HLS tool, with no modification of the tool itself.

In Chapter 4, we show that such a memory architecture and interface can be generated automatically, using the HLS tool itself, in a form of "meta-compilation", at least with the HLS tool we consider. Our study is done with the C2H Altera tool, for accelerators with external accesses to a DDR memory, always keeping in mind that any code transformation we perform can be automated. We first analyze C2H and we identify the features that make DDR optimizations feasible or hard to perform. We then communicating processes, and of software pipelining that can lead to fully-optimized DDR accesses. The idea is to keep the bandwidth saturated as much as possible, orchestrating communications and computations in a pipelined fashioned, using local memories to store data before they are consumed.

In Chapter 5, we present a method to derive automatically from a naive kernel written in C, a set a C functions implementing the pipelined communicating accelerators optimized for C2H, as proposed in chapter 4. Original techniques are defined to minimize the communications with the DDR, manage the local memory and generate the final code. The user must delimit the kernel to be optimized and specify several other parameters with compiler directives. The method has been fully implemented and the first experiments gives promising results. We believe that our technique can also be used to optimize loop-based programs for GPUs (graphics processing units).

To summarize, this thesis manuscript is organized as follows. After this short introduction, Chapter 2 presents the related works in HLS and code transformations, in particular those related to HLS based on the C language. In Chapter 3, we present the manually-designed local memory architecture and interface for the example of MMAlpha, then the source-to-source methodology we experimented in front of the HLS tool Spark. In Chapter 4, we present our various attempts to optimize the DDR accesses with the Altera C2H tool and the solution we found with the constraint that it can be automated. In Chapter 5, we show that the process we designed can be make automatic, with adequate program analysis, program transformations, and code generation. Chapter 6 raises some conclusions and perspectives.

# Chapter 2

# Related works in high-level synthesis

The ever increasing complexity of the circuits imposed a transition from low-level hardware languages, used in traditional hardware design, to languages with a higher level of abstraction such as C used in high-level synthesis (HLS) tools. The use of a higher abstraction level eases the design process, making it more flexible. However, as observed in the first generation of HLS tools, the synthesis quality was far from manual-level designs [91]. As the circuit complexity increased, the use of HLS became mandatory to get a better time to market. To raise the quality of synthesis results, the synthesis tools were extended with some add-ons. One of them is the extension of the input language with low-level hardware constructs. Unfortunately, such constructs could be only understood by hardware designers eliminating the software developers from the potential users. Another approach is to use configuration files to drive the synthesizer at a coarse-grain level. A better approach is to use compiler directives that can guide the synthesizer at a very fine grain so that the generated design approaches the desired one. There are many other approaches like class libraries and template/draft architecture definition methods that can be used to guide the HLS tool. In this chapter, we describe these different approaches together with their advantages and disadvantages. The goal of this chapter is not to be exhaustive, this would be impossible, but to give an idea of the evolution of HLS tools and of their underlying ideas, focusing mainly on tools based on variants of the C language. We also describe, in the form of a catalog, some code transformations (in particular loop transformations) that can be useful for HLS.

# 2.1 Hardware description languages and early HLS

### 2.1.1 Conventional low-level hardware description languages

One of the most used abstraction of hardware circuits is RTL (register transfer level) [14]. It has the lowest abstraction level for defining a synchronous digital circuit in terms of logical operations. The circuit structure is defined by hardware registers and logical operators. They are connected by signals that perform transfers of data. RTL description is very close to the gate-level description (GLD) and is very well suited for the logic design phase of the integrated circuit design (ICD). One of the advantages of using such an abstraction is that the user have the full control of the system being implemented. However, as the designed systems became more complex, the amount of designer work used to describe complex and large digital systems became not economically viable.

To circumvent this problem, languages like structural VHDL [14, 17] were proposed. VHDL is used as a design language for FPGAs and ASICs. It was originally developed at the US Department

of Defense in order to document the behavior of the ASICs (described as RTL) that supplier companies were included in equipment. It was revolutionary when it was introduced. VHDL has a syntax mainly based on the ADA programming language, along with an added set of constructs to handle hardware parallelism. While it can be used for basic RTL description, the language incorporates higher-level constructs. One can describe multiple entities and their corresponding architecture implementations. Each architecture can use multiple components described elsewhere in entities. It is more flexible than RTL and provides IP. However, recent increase in hardware complexity has shown that manual structural VHDL coding is very time-consuming and error-prone. Behavioral VHDL has a higher level of abstraction than structural VHDL. The main difference is that a design described in behavioral VHDL is not always synthesizable as opposed to structural VHDL, i.e., it is not always possible to derive automatically a layout with a synthesis tool.

Another hardware description language (HDL) language used to model electronic systems is Verilog [14, 15]. It was invented by Phil Moorby at Automated Integrated Design Systems (later renamed to Gateway Design Automation) in 1985 as a hardware modeling language. Gateway Design Automation was later purchased by Cadence Design Systems in 1990. Cadence now has full proprietary rights to Gateway's Verilog and the Verilog-XL simulator logic simulators. As opposed to VHDL designers that opted for a RTL syntax (at least in the earlier versions of VHDL standard), the designers of Verilog wanted a language with a syntax similar to the C programming language so that it would be familiar to engineers and readily accepted. The language has a pre-processor like C, and the major control keywords such as if, while, etc., are similar. The formatting mechanism in the printing routines and the language operators (and their precedence) are also similar. Like VHDL, the language differs from a conventional programming language in that the execution of statements is not strictly linear. A Verilog design consists of a hierarchy of modules. Modules are defined with a set of input, output, and bidirectional ports. Internally, a module contains a list of wires and registers. Concurrent and sequential statements define the behavior of the module by defining the relationships between the ports, wires, and registers. Sequential statements are placed inside a begin/end block and executed in sequential order within the block. But all concurrent statements and all begin/end blocks in the design are executed in parallel. A module can also contain one or more instances of another module to define sub-behaviors.

Even though the VHDL language has higher level constructs and a higher behavioral level of abstraction, Verilog is still used worldwide much more than VHDL. Assuming that the user has zero knowledge in either languages, Verilog is the easiest to understand. VHDL is less intuitive for multiple reasons. One of the reasons is that it is strongly typed. This feature makes it robust and powerful for the advanced user. However, this is only after a longer learning phase. Another reason is that there are many ways to model the same circuit (especially those with large hierarchical structures). The VHDL roots are based on ADA. Verilog has more similarities with C because its constructs are based half on C and half on ADA. For this reason, an existing C programmer may prefer Verilog over VHDL.

Independently on the programming language (VHDL or Verilog), designing systems with an ever increasing complexity using these languages becomes more expensive, tedious, and error-prone. We must take into account the fact that the success of a language depends a lot on its understanding simplicity and similarities with well-known and greatly-used programming languages.

#### 2.1.2 Early attempts in high-level synthesis

The concept of high-level synthesis started in early 1974 when Mario Barbe from Carnegie Mellon University noticed that one could compile (synthesize) an instruction set processor specification (ISPS) into hardware [47, Page 15]. Later, HLS was defined as a process of automatic (or semi-automatic) generation of hardware from an algorithmic description. Since then, there were many attempts to synthesize circuits from different types of input specifications. In this section, we first quickly recall different attempts and mention their advantages and disadvantages.

In order to increase the acceptance of the HLS tools, some industry electronic design automation (EDA) such as Synopsys focused on increasing the abstraction level of existing languages instead of trying to synthesize efficiently from higher-level specifications. As we mentioned earlier, the specification written in behavioral VHDL or Verilog is not always synthesizable. The "behavioral compiler" from Synopsys addressed this issue. This reduced the design effort of RTL synthesis designers. However, on the other hand, software and algorithm designers were still unable to use this tool because it still required a huge hardware design knowledge. Another disadvantage of behavioral synthesis was the rather poor and unpredictable quality of results. The design was very difficult to validate because its timing behavior was very dependent on the synthesis tool optimizations. This had a major impact on the HLS tool acceptance.

One of the first attempts in HLS to synthesize from a high-level specification was the work of Snow in late 80's during his thesis [47, Page 17]. He was one of the first to propose the use of control/data flow graph (CDFG) as an input specification to the synthesis system. In later year, Emil Gircyz in his thesis proposed the use of the ADA language to model hardware [47, Page 17], which is, as previously mentioned, the predecessor of the VHDL language.

In the domain-specific category, Cathedral and Cathedral-II [57] were the most well-known. The tools were used for digital signal processing (DSP)-oriented specifications. The specification language was called Silage and it was developed by IMEC. Silage is a pure behavioral language without any structural biases. It was oriented to describe DSP algorithms. However, the domain specialization was not appropriate for the majority of ASIC designers. Early ASIC designers indeed concentrated on control logic rather than on dataflow and signal processing. The designs were mostly written by hand in an rather poorly-structured random logic.

These high-level synthesis attempts failed to establish themselves in the hardware design cycle of many engineers. Most of them were only starting to move from schematic system design to the HDL methodology. Learning new and much different languages such as Silage, together with their different design methodologies, was not an easy task and was not considered as a good investment. Another important drawback of the first HLS tools were the very poor quality of the generated results compared to the manual approach. This was mainly due to the simplicity of the optimizing algorithms used.

## 2.2 Advances in high-level synthesis

In this section, we present some advances in high-level synthesis. We mostly focus on tools that synthesize from a C-like language, since C is very popular among hardware and software designers. We present different types of synthesis approaches used to increase the synthesis easiness and quality. We also try to classify the tools according to these different approaches, following their most important feature. But, of course, these tools usually incorporate multiple approaches and this classification may therefore seem a bit artificial, on some aspects. For a more detailed information,

one may consult the books of Diniz et al. [41] and of Coussy et al. [47], and the article "High-Level Synthesis: Past, Present, and Future" [91].

The first work that addressed the designers language familiarity problem was the work of Stroud et al [102]. They introduced a new C-like language called Cones. This was the very first time an input to the high-level synthesis system was a C-like language. The input specification was synthesized by the Cones HLS tool. It is an automated synthesis system that takes a behavioral circuit description written in C and generates a gate-level implementation. Its name is based on the logic cone that is formed by inputs and outputs connected by arrows representing data dependences. Each function is synthesized independently. It has input and output variable definitions. Cones supports a subset of C that includes if, switch, and for constructs. It also provides macros to handle array of inputs, outputs, memory elements, and temporary variables. Memory elements are defined explicitly with no memory controller or scheduler to fetch them. Cones can be used with single-clock, single-edge <sup>1</sup> synchronous designs, or purely combinatorial ones. Even though the language was very familiar to designers, being only able to synthesize combinatorial designs limited its usability.

#### 2.2.1 Low-level hardware constructs

One of the problems with the synthesis from a high-level language like C was the unexpected synthesis results. To guide the HLS tool, hardware constructs were introduced in the language.

Ku and De Micheli from Stanford University addressed this issue of synthesizing sequential circuits and developed Hardware [58, 84, 64] as an input to the Olympus synthesis system. It has a C-like syntax and it represents a behavioral HDL with support for declarative and procedural semantics. It supports the notion of concurrent processes, message passing, timing constraints, resource constraints, hardware structure, and hierarchy. It supports adjusting the degree of parallelism by grouping specific operations using different types of parentheses defined in the language. External interfacing is done thanks to port passing or message passing using channel mechanisms.

Another C-like language that has hardware constructs is SpecC [14, 64, 62]. It was developed by Gajski et al.'s at University of California, Irvine. As HardwareC, it is based on C and it offers special extensions (keywords) to cover the needs of embedded designs. In addition to low-level hardware constructs, it also provides constructs for finite state machines (FSMs), concurrency, pipelining, and structure. As such, the SpecC language provides a minimal set of orthogonal constructs that covers the concepts identified in embedded systems. Systems written in the complete language must be refined into the synthesizable subset. Channels are used for synchronization and communication between modules. Unlike previously-presented synthesis tools, SpecC was designed with system integration in mind. The obtained architecture contains a software processor and a custom hardware. A part of the initial algorithm will run on the software processor and the rest will run on custom hardware. The two parts communicate using a generated interface.

Another more advanced language with hardware constructs is Handel C [14, 16, 64]. Developed at Oxford University Computing Laboratory, it was adopted by Agility [1] until Mentor Graphics acquired its assets [14]. It is a programming language designed for compiling programs into hardware images of FPGAs or ASICs. It uses much of the syntax from C standard published by American National Standards Institute (ANSI-C) with addition of explicit parallelism. By default, the written instructions will be executed in a sequential order. To execute a part of the code in parallel, one must use the par keyword. In this case, the instructions that have to be executed

<sup>1.</sup> Digital designs can use the two edges of the clock, i.e., the rising and the falling one. When only one is used, the design is called single-edge.

in parallel will be executed at the same instant in time by separate pieces of hardware. The language also provides channel communications in order to synchronize parallel branches of a program. Handel-C semantics is inherited from the communicating sequential processes (CSP) formalism. It also imposes a restriction that a single variable can be written by only one parallel branch and may be read by several parallel branches. The variables can be mapped to memory elements such as random access memory (RAM) and read only memory (ROM) by using type extensions and cannot be accessed more than one element at a time, otherwise the compiler will generate an error. Before the start of the main function, the clock at which the main function will run needs to be defined. More than one main function can be defined if different parts of a program need to run with different clocks. Handel-C comprises all common expressions necessary to describe complex algorithms, but lacks processor-oriented features like pointers and floating-point arithmetic. The programs are mapped into hardware at the netlist level, currently in Xilinx netlist format (XNF) or Electronic Design Interchange Format (EDIF) format.

Another C-like language, designed at Sharp, Bach C [82] based on the C language had fewer low-level constructs. It has extensions to support explicit parallelism, communication between parallel processes, and a bit-width specification of data types and arithmetic. The semantics of the language is untimed so that users specify the hardware behavior without worrying about when operations will take place. It supports arrays but not pointers. The input specification was synthesized by Bach which was developed at Sharp Corporation in 2001. Sharp has also developed a simulation and debugging environment for Bach C, and a high-level synthesis tool for turning Bach C programs into RTL-VHDL. The algorithm described in Bach C is partitioned into the hardware (HW) (hardwired logic) and software (SW) parts. The SW part can be executed on an ARM7. The HW part is compiled into RTL circuits using the Bach synthesizer, meeting the given constraints. The compiler uses a logic-synthesis tool to estimate the delay and area of each functional unit in the design. It has some issues. HW/SW partitioning has to be done by hand. Performance, area, and power consumption cannot be evaluated at the level of Bach C. The HW/SW interface circuit is generated automatically and represents a AMBA bus. IP reuse is done manually by manual modifications in the VHDL code [82].

Finally, another language that restricted the number of low-level constructs was the language Transmogrifier C [71, 14]. It was developed at the University of Toronto and is a restricted subset of the ANSI-C programming language with a minimum number of extensions. The communication is performed by using Input/Output (I/O) ports defined in the language as low-level constructs and directives. It does not support multiply, divide, pointers, arrays, structure, and recursion. It is used by the Transmogrifier C HLS system. Now Transmogrifier C is called FPGAC and is an open-source project. Its usability is rather limited because of its very restricted subset of the C language and because it targets only the platforms based on the Xilinx XC4000 series FPGAs.

The HLS systems presented above were able to synthesize synchronous and much more complex circuits compared to systems like Cones. However, this does not come for free. To be able to optimize the synthesis results, the designers were forced to guide the HLS tool using very low-level constructs. Most of these constructs could be understood by only the hardware designers, eliminating the software designers from the possible users. One of the main disadvantages of low-level hardware constructs was that the designer was usually forced to completely rewrite its specification written in C in order to get it synthesized by the HLS tool. Poor quality, variable and unpredictable synthesis results, together with the difficulty to manage low-level hardware constructs were some of the main factors that perished the success of these tools.

#### 2.2.2 Configuration files and compiler directives

The previous section mentioned some HLS tools that defined hardware constructs in the language in order to inform the HLS tool of some hardware specific attributes. As explained earlier, this however limited the code reuse between the hardware and software parts in a hardware/software co-design. There are multiple solutions to this problem.

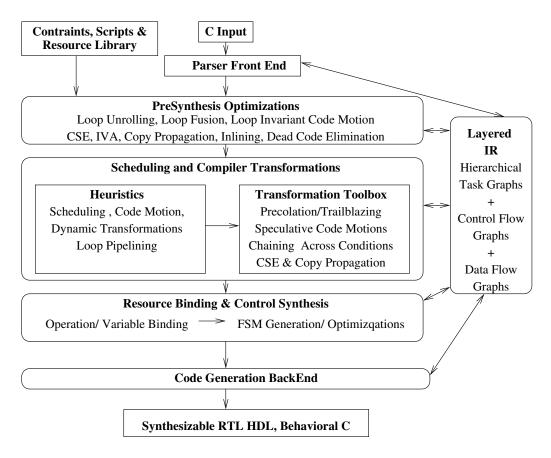

Configuration files The first solution is to use a configuration file that guides the HLS tool. This solution is for example used by the HLS tool Spark [78]. It was designed as a continuation of the MI-CRO project 00-037 (2001) and was developed at the University of California, San Diego, funded by Semiconductor Research Corporation and Intel. It takes behavioral ANSI-C code as input and generates synthesizable register-transfer level VHDL. Spark does not accept code that contains pointers, function recursion, and irregular control-flow jumps. It uses hierarchical task graphs and dataflow graphs as the internal representation of the program. In a pre-synthesis phase, using parameters from the configuration file to tune heuristics, Spark applies several optimization techniques and coarse-level code restructuring as function inlining, loop unrolling, loop fusion, common sub-expression elimination (CSE), copy propagation, dead code elimination, loop-invariant code motion, induction variable analysis (IVA), and operation strength reduction. After this presynthesis phase follows a scheduler phase, which is organized in two parts. The first part contains heuristics that perform scheduling and the second part contains a toolbox of synthesis and compiler transformations such as percolation and trailblazing (code motions techniques), speculative code motions, chaining across conditions, and other. The resource allocation has to be done by the designer who has to specify in the configuration file the amount of available hardware elements and their timing information. All these transformations have a very important impact on maximizing the parallelism and performance of the final system. After the scheduling phase follows the control generation phase that minimizes interconnects between units and generates a FSM that implements the controller. Finally, a back-end code generation pass generates synthesizable a RTL VHDL description that can be synthesized by commercial tools. We will use this tool in Chapter 3.

A similar methodology was used for the HLS tool C2Verilog. It was introduced in 1998 by CompiLogic that was later bought by Synopsys in 2001 [101, 64]. The compiler accepts pointers, structure, arrays, loops, and function calls. Each function is synthesized independently and each function parameter is translated into an input and returned into an output port. The compiler can be informed, by the graphical user interface (GUI), of different global settings such as bit widths, multiplication and divider options, etc. In order to tune the performance of the system, the designer has to iterate through different compiler options, logic synthesis preferences and, if a finer grain change is required, using direct C code modifications.

Another example of tool that uses configuration files is CyberWorkBench (CWB), which was designed internally at NEC. It includes synthesis, verification, and hardware software co-simulation. The input language is an extension of ANSI-C and is called BDL or Cyber-C or SystemC. The basic concept of the framework is the all-modules-in-C and all-processes-in-C. Everything is expressed by means of the C language. The tool can perform such fusion, array expansion, loop pipelining (also called loop folding). The tool automatically instantiates a CPU, its corresponding bus interface, and the connection to the hardware modules.

Finally, it is worth mentioning AutoPilot, an electronic system level (ESL) synthesis system of AutoESL [3, 47], which uses configuration files containing user constraints and directives to guide the synthesis process. Based on the UCLA xPilot system [44], it can automatically synthesize an input code written in an untimed or partially timed C, C++, or SystemC (SystemC) code.

The tool is based on a commercial C/C++ compiler and can automatically perform optimizations such as constant propagation, dead code elimination, common sub-expression elimination, strength reduction, if-conversion, loop unrolling, loop flattening, loop fusion, intra and inter-procedural analysis, bit-width analysis and optimization, and pipelining. The synthesis process takes into account user constraints such as latency, throughput, and resources defined in the configuration file. Dynamic pointers, dynamic memory allocations, and function recursions are not supported.

To summarize, configuration files can express very general requirements of the designer. Compared to low-level hardware constructs, the use of configuration files does not change the code allowing a much more flexible hardware/software partitioning. However, even though some HLS tools have a very powerful internal optimization framework, the results are not always acceptable by the designer. Communicating with the tool with a rather limited tuning of the internally predefined heuristics is not always sufficient to obtain a design with the required performances and characteristics. Using a configuration file, the designer cannot express fine-grain specifications such as, for example, which loop to parallelize. The only solution is to change the code, in an iterative manner and by hand, and to check the obtained results, which is very tedious and error prone.

Compiler directives Instead of configuration files, used for coarse-grain configuration of the synthesis process, one can use compiler directives (pragmas). Compiler directives can describe code optimizations at a much finer grain. Also, as for configuration files, code compatibility is ensured with pragmas: a code written using pragmas can be synthesized to a dedicated hardware or compiled as a software for a standard processor. The compiler will then ignore pragmas that it does not understand without generating an error. At the same time, an advantage of using pragmas over low-level hardware constructs is the flexibility of the code. To change the behavior of a specific part of a code, one just has to write a pragma instead of changing the structure of the code, which would be error prone. We present below some of the tools that use compiler directives.

One tool that uses, in the input language specifications, compiler directives to guide the synthesizer is Impulse C [14]. It was developed by Impulse Accelerated Technologies for their Impulse C compiler. It represents a subset of the ANSI-C. The programming model is a variant of CSP. The synthesizer accepts multiple predefined pragmas such as NONRECURSIVE used to inform the optimizer that a given array variable cannot be scalarized, PIPELINE used to inform the synthesizer that the loop should be pipelined, and so on. From its subset of C, the Impulse C compiler generates an FPGA hardware accelerator using HDL. The architecture is generated from the CSP description described in the C language. It is more dataflow and streaming oriented, with processes accepting data, performing computations on it, and sending them after. The inter-process communications are performed using streams or shared memories.

Anther commercial tool that accepts pragmas to guide the synthesizer is Nios II C2H [22, 21]. It is a tool developed by Altera Corporation that synthesizes hardware accelerator co-processing modules to the Nios II soft-core processor. The design starts with an algorithmic description written in ANSI-C that is supposed to be executed on the processor. Some parts of the code (that are separated in functions) can be selected to be implemented in hardware. The C2H compiler will automatically redirect all calls to a hardware function to its hardware implementation. The calls to the hardware accelerator can be blocking or non-blocking. In the blocking call implementation, the processor waits in a while loop reading the state of the status register of the accelerator. In the non-blocking call, the designer must register an interruption routine. The compiler supports most C constructs such as pointers, arrays, structures, global and local variables, loops and subfunction calls. Each syntax element is mapped in a straightforward way into a hardware element

thus, in particular, with no resource sharing. Each loop or function is translated into a separate state machine that is synchronized to the upper hierarchy one. As opposed to Impulse C, the compiler will automatically pipeline the loops based on its data dependence analysis. There are also multiple pragmas defined in the input language specification that can be used to define, for the compiler, the connections of variables to memories, the blocking and non-blocking function executions, etc. The compiled hardware accelerator is integrated into the system on a programmable chip (SOPC) builder system and is connected to the rest of the system by means of the Altera's Avalon interconnect. The hardware accelerator supports parallel scheduling, which is performed automatically based on the data dependences, instead of using pragmas as in Handel-C. In a state machine, multiple constructs can be scheduled for parallel execution. The constructs can be simple statements but also other state machines. The hardware accelerator can access the (external) memory directly by using master port connections. The accesses are then pipelined in order to reduce the memory latency penalty. We will use this tool in Chapter 4.

One of the tools that does not really accept directives written in the code but, nevertheless, can specify code optimizations at a fine-grain level, using GUI or Tcl scripts, is Catapult C [14, 47]. Previously called PrecisionC, it is a ESL commercial HLS tool of Mentor Graphics. It takes as input ANSI-C/C++ and SystemC and generates an RTL description. The interface generation is done by parsing the C++ arguments and generating Catapult C supports multi-level clock gating, multi-block systems, loop unrolling, loop fusion, and loop pipelining. The Catapult C language supports pointers, classes, templates, and operator overloading. It uses some user memory directives to specify, for example, to split the mapping of an array into multiple memories. The input code should be statically determinable.

Instead of using compiler directives, one can also use code labels and a separate configuration file to inform the compiler about the required code transformations. This is used in the academic HLS tool CLooGVHDL (CLooGVHDL). It accepts a C description and generates a VHDL design. The tool is built on the side of the WHIRL Represented as Polyhedra (WRaP-IT) tool. The input C code is parsed by the Open64 (Open64) compiler. Its intermediate representation, whirl, is fed into the WRaP-IT tool that performs polyhedral loop transformations. CLooGVHDL accepts the so-called VIM-scripts and the CLooG outputs to generate a HW architecture, composed of functional computational blocks, loop control, internal FIFOs and memories, and a pre-fetch request module with synchronization points [61, 59]. However, CLooGVHDL is just a toy HLS tool, which does not include any complex optimizations or parallel execution. As explained in Section 2.3, our work in Chapter 3 uses WRaP-IT too, but in front of a more complete HLS tool, namely Spark.

As this brief survey shows, compiler directives are very useful in HLS. The designer does not have to change the C code that was written for a software part to get it synthesized into hardware: the user can just add, during the synthesis process, pragmas to the code. Unlike low-level hardware constructs, the code can still be compiled in software. For example, when using C2H, if a function is compiled into software, hardware pragmas are ignored by the software compiler. Actually, in practice, to get efficient designs, the process is a bit more complicated. In addition to pragmas, the C code may need to be rewritten in a particular way so that the hardware design generated by the HLS tool delivers adequate performance. But it can still be compiled into software, which is, in particular, very useful for verification and simulation. Also, compared to the configuration files, pragmas can specify at a much smaller grain the designer's requirements (when needed).

#### 2.2.3 Class libraries, template architectures, etc.

Class libraries Another approach used to guide the synthesis tool to a suitable synthesis result is by using class libraries. These libraries allow the designer to use extension to an existing programming language, such as specialized data-types with corresponding methods or functionalities. We present below several HLS tools of this category.

Gaut [47] is an academic and open-source HLS tool dedicated to the synthesis of DSP applications. The synthesis starts with an algorithmic description written in C with Mentor Graphics class libraries that allow designers to specify bit-accurate data types such as ac\_int and ac\_fixed that represent bit-accurate integers and bit-accurate fixed-point data types. The compilation unit is based on GCC<sup>2</sup>. During the compilation phase, several code optimizations are performed such as dead code elimination, value range propagation, redundancy elimination, loop-invariant code motion, loop peeling, loop fusion, partial loop unrolling. The designer can specify the variable location (memory, register or both (dynamic)) using the so-called locality-threshold parameter so as to minimize the cost of storage elements. The user is guided by a lifetime variables histogram and the frequency of utilization. Using design constraints specified by the user, Gaut generates a hardware accelerator that is composed of a pipelined processing unit (PU), a memory unit (MEMU), and a communication and interface unit (COMU) based on latency insensitive systems (LIS). The synchronous components are encapsulated into combinational logic that drives them only when all the inputs are valid and all outputs can be stored. Gaut generates scripts used to simulate the result using cycle accurate and bit accurate (CABA) simulation and TLM with timing (TLM-T).

Ocapi [99, 64] is another tool that uses the class libraries mechanism. It supports simulation, verification, and synthesis. The object-oriented features of the C++ language allow the mix between high-level description of the components and a detailed cycle-accurate simulation. This approach also reduces considerably the simulation time compared to a RTL-level simulation.

A very popular framework that uses the class libraries methodology is SystemC. It has as origin the Scenic project from Synopsys [72] designed to create a language based on C++ that would allow RTL synthesis and would be able to generate executable modules of hardware system. SystemC is used mostly for hardware simulation. However, recent compilers such as Forte's Cynthesizer can perform hardware synthesis from SystemC. It provides C++ high-level constructs as classes and macros, and also low-level ones such as structural hierarchy, delta cycles <sup>3</sup>, 4-state logic, virtual platform modeling. The designer can simulate concurrent processes using C++ syntax [14]. Forte's Cynthesizer, one of the HLS tools that use SystemC, is a high-level design product of Forte Design Systems [6]. It accepts SystemC-transaction-level modeling (TLM) design description as input and generates an RTL design. The user can use high-level C++ constructs like encapsulation, construction of custom data types, templates, etc. The tool also supports a few directives used to control the loop pipelining and unrolling.

One can also mention C-to-Silicon, the commercial HLS tool from Cadence, which uses input specifications based on class libraries. It accepts C, C++, and SystemC as input specification. The compiler synthesizes the design up to the physical level in order to generate accurate timings. The tool also incorporates a verification module. The design is translated into a so-called fast hardware model (FHM) that runs almost as fast as an untimed C-model [4].

Finally, the commercial tool Synphony C Compiler from Synopsys [12] is also based on class

<sup>2.</sup> GNU Compiler Collection (GCC)

<sup>3.</sup> Hardware simulation is performed using delta cycles. At a specific delta cycle are executed only hardware instances for which some signals have changed their state at the previous delta cycle.

libraries. It uses C/C++ constructs for synthesis. The tool has the key capability of automatically inserting, in the hardware design, clock gating in order to save power.

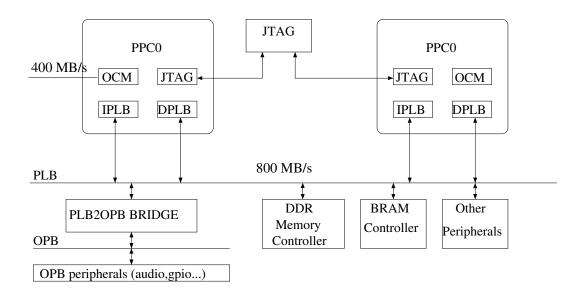

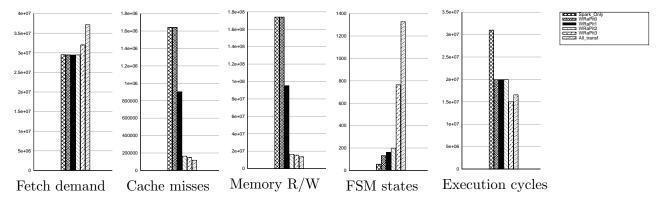

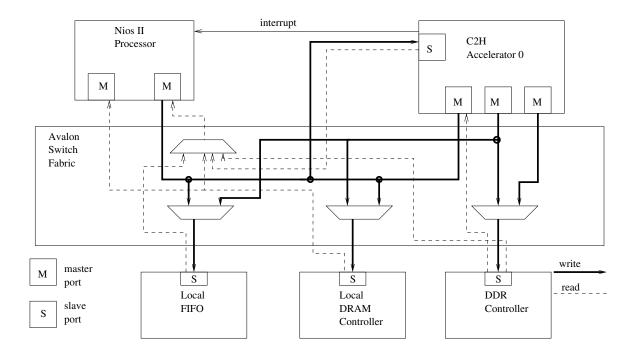

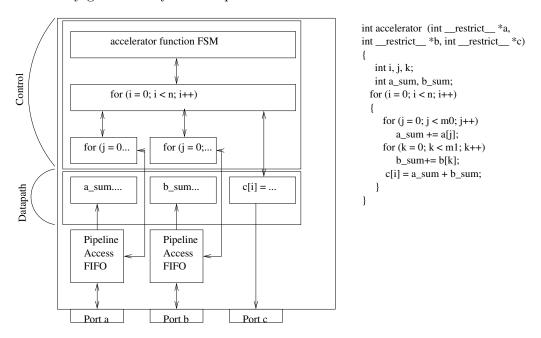

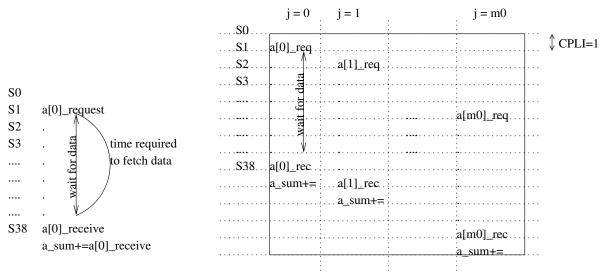

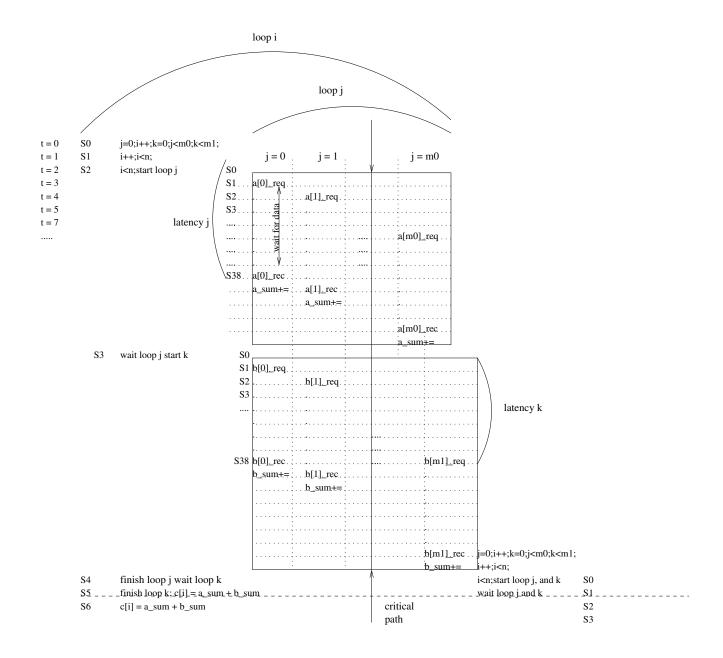

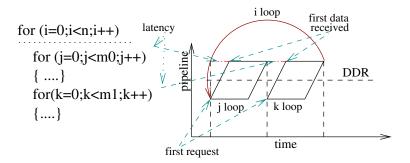

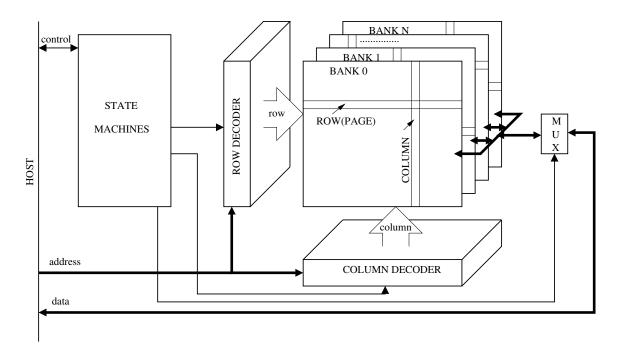

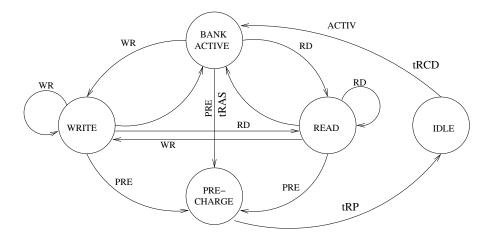

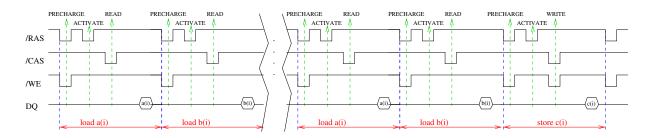

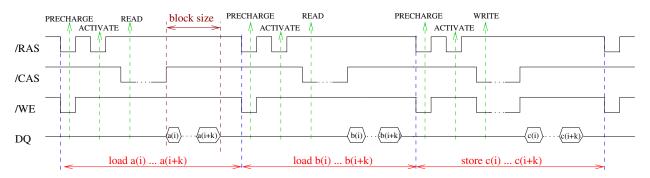

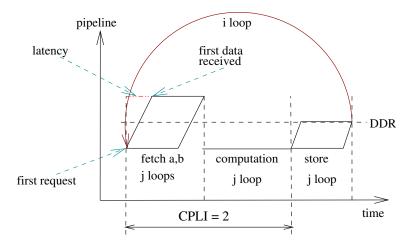

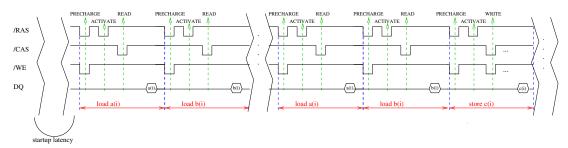

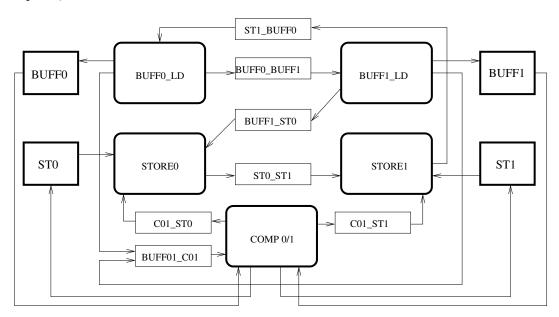

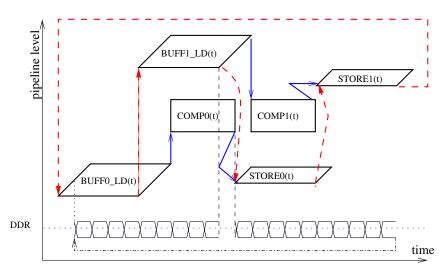

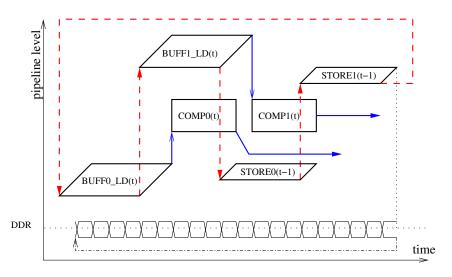

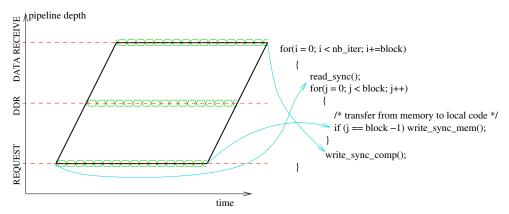

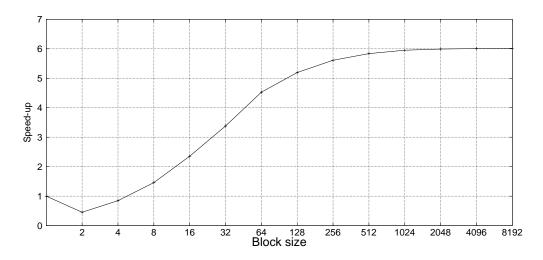

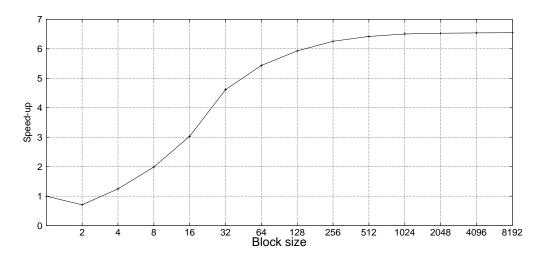

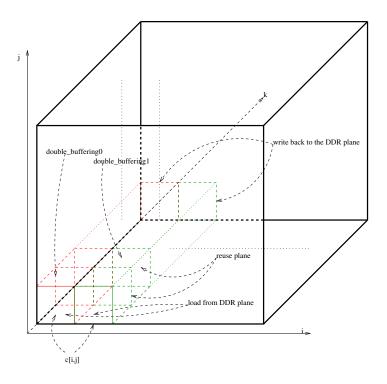

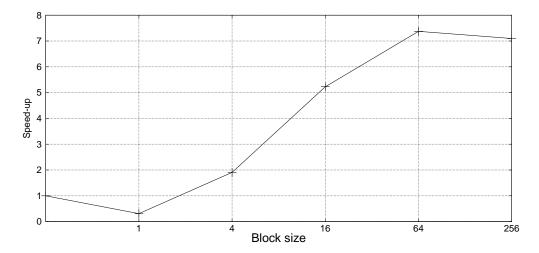

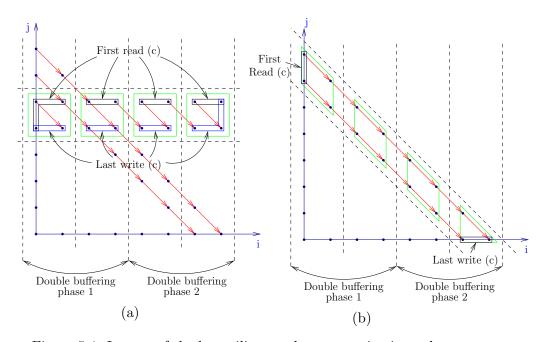

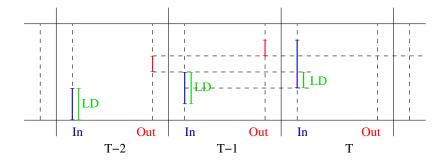

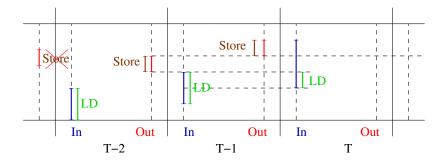

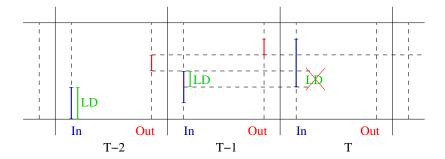

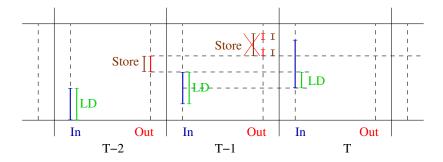

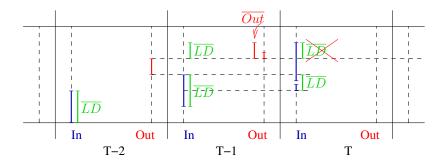

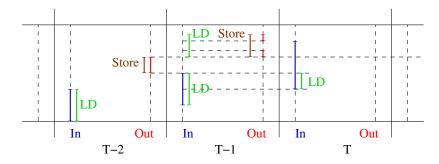

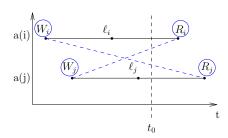

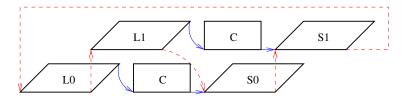

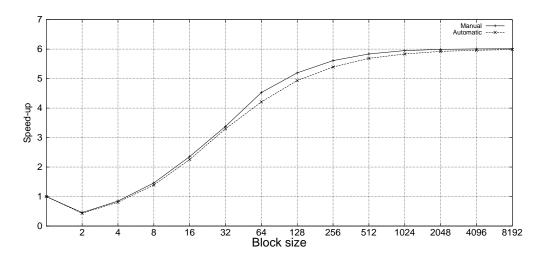

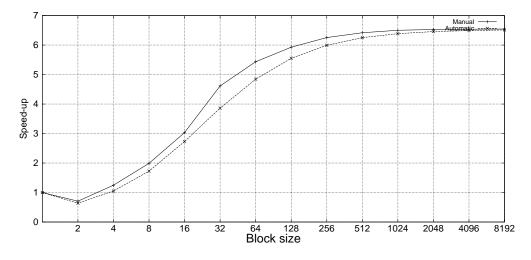

All HLS tools we just mentioned use class libraries in their input specifications. These class libraries are used to extend the original language specification. This has multiple advantages. One of the major advantage is the very fast simulation time when the required level of simulation does not need to be as accurate as VHDL simulation. Another advantage of these class libraries is the very easy hardware/software partitioning as well as a very rapid and painless co-simulation and co-verification. Unfortunately, all this comes at a cost. Because of the required use of these class libraries, the majority of the code is not directly usable. The user has to pass through painful transformation phases from its original specification into one that uses these class libraries.