# Program Transformations and Memory Architecture Optimizations for High-Level Synthesis of Hardware Accelerators

Alexandru PLESCO Ph.D. Defense

Supervisors: Christophe Alias, Alain Darte, Tanguy Risset

Compsys Team

Laboratoire de l'Informatique du Parallélisme (LIP)

École Normale Supérieure de Lyon

France

September 27, 2010

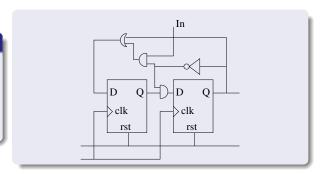

#### Description level

- Schematics, RTL

- Structural VHDL

- Behavioral VHDL

- Verilog

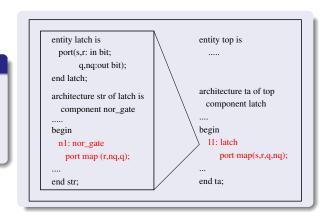

#### Description level

- Schematics, RTL

- Structural VHDL

- Behavioral VHDL

- Verilog

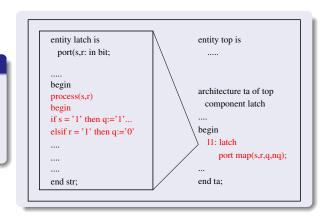

#### Description level

- Schematics, RTL

- Structural VHDL

- Behavioral VHDL

- Verilog

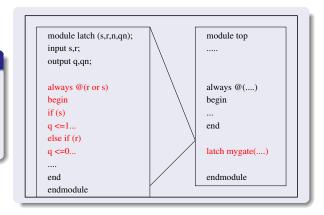

#### Description level

- Schematics, RTL

- Structural VHDL

- Behavioral VHDL

- Verilog

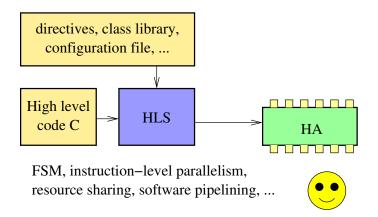

# High-Level Synthesis (HLS)

#### Increasing complexities of accelerated algorithms:

- Telecommunication equipment (3G, 4G, ...)

- Multimedia devices (Video/audio CODECS, ...)

- High performance computing (encryption, simulation, ...)

- ➡ Increasing demands in processing power

# High-Level Synthesis (HLS)

#### Increasing complexities of accelerated algorithms:

- Telecommunication equipment (3G, 4G, ...)

- Multimedia devices (Video/audio CODECS, ...)

- High performance computing (encryption, simulation, ...)

- ➡ Increasing demands in processing power

- + Short time to market

- + Development effort

- ➡ HLS tools become mandatory to meet design constraints

→ Optimize memory accesses, data reuse, and interconnections

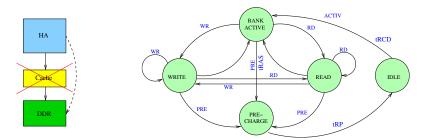

# Outline

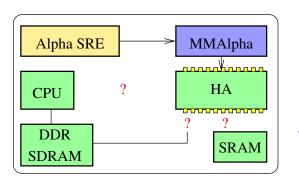

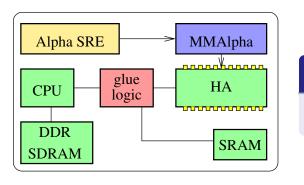

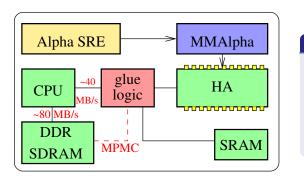

### MMAlpha

- Slave HA

- Synchronous interface

- Regular control inside HA (dataflow)

Glue logic: interface + memory manager for

- data reuse

- burst transfers

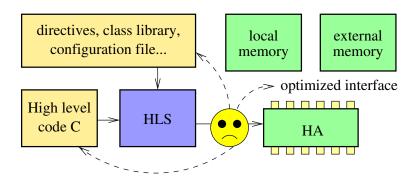

#### Problems

- Small bandwidth

- Multi-port memory controller?

- Important design and programming effort

#### Problems

- Small bandwidth

- Multi-port memory controller?

- Important design and programming effort

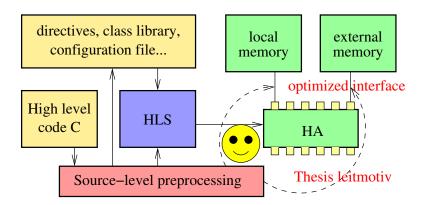

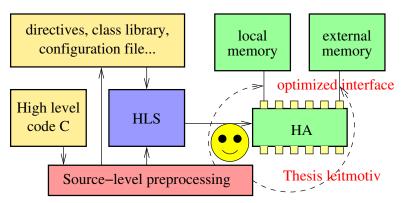

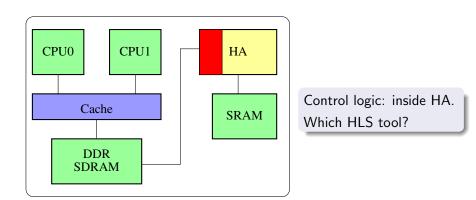

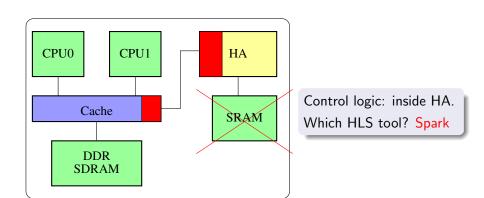

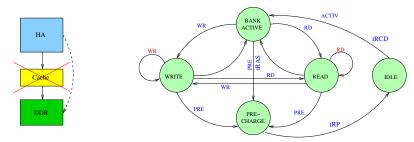

## Moving the glue logic inside the HA

# Moving the glue logic inside the HA

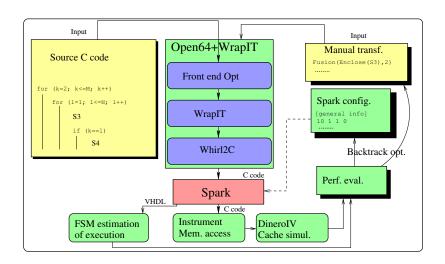

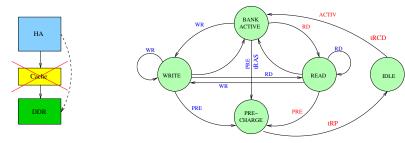

# Design with Spark and WRaP-IT

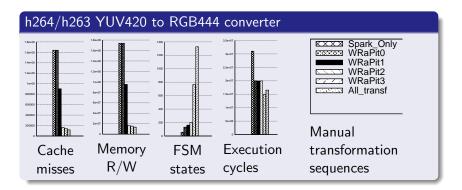

## Experimental results

- increases the cache hit ratio

- decreases the memory bandwidth requirements

- increases the number of FSM states (may degrade frequency)

- decreases the total execution time

# Try to improve HLS tools with high-level transformations

#### **Experiments with MMAlpha**

- Parallel (systolic) architecture.

- Data should be available at MMAlpha ports, fed by FIFOs.

- Need to implement (in VHDL) a complex memory controller.

- ➡ Improved performances but still (very) limited by bandwidth.

# Try to improve HLS tools with high-level transformations

#### **Experiments with MMAlpha**

- Parallel (systolic) architecture.

- Data should be available at MMAlpha ports, fed by FIFOs.

- Need to implement (in VHDL) a complex memory controller.

- **▶** Improved performances but still (very) limited by bandwidth.

#### **Experiments with Spark**

- Accelerator to be connected to a CPU, possibly with a cache.

- I/O pins: 1 dedicated pin per data bit

- Apply loop transformations: optimize transfers and reuse.

- **▶** Loop transformations appeared to be useful.

# Try to improve HLS tools with high-level transformations

#### **Experiments with MMAlpha**

- Parallel (systolic) architecture.

- Data should be available at MMAlpha ports, fed by FIFOs.

- Need to implement (in VHDL) a complex memory controller.

- **▶** Improved performances but still (very) limited by bandwidth.

#### **Experiments with Spark**

- Accelerator to be connected to a CPU, possibly with a cache.

- I/O pins: 1 dedicated pin per data bit

- Apply loop transformations: optimize transfers and reuse.

- **▶** Loop transformations appeared to be useful. **But**:

- How to interface? No way to reuse pins.

- Thus performances improvements could only be simulated.

- Frequency sometimes lower.

# Outline

# Goal of this study: use HLS tools as a back-end compiler

- Show that high-level transformations are useful and needed.

- Focus on accelerators limited by bandwidth: optimize throughput and put necessary hardware for computations.

- Optimize transfers at C level.

- Compile any new functions with the same HLS tool.

- Try to consider HLS tools the same way back-end compilers are used, in standard compilation, by front-end optimizers.

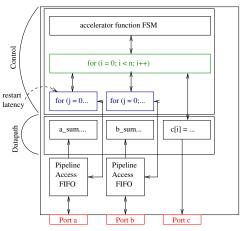

#### Syntax-directed translation to hardware

- Hierarchical FSMs: stalls to wait for the longest inner FSM.

- Access to external memory through arrays and pointers.

- One local memory for each local array.

#### Syntax-directed translation to hardware

- Hierarchical FSMs: stalls to wait for the longest inner FSM.

- Access to external memory through arrays and pointers.

- One local memory for each local array.

### **Software pipelined loops →** Optimize CPLI (initiation interval)

- Basic software pipelining with rough data dependence analysis.

- Latency-aware pipelined DDR accesses (with internal FIFOs).

#### Syntax-directed translation to hardware

- Hierarchical FSMs: stalls to wait for the longest inner FSM.

- Access to external memory through arrays and pointers.

- One local memory for each local array.

### **Software pipelined loops →** Optimize CPLI (initiation interval)

- Basic software pipelining with rough data dependence analysis.

- Latency-aware pipelined DDR accesses (with internal FIFOs).

#### Full interface within the complete system

- Accelerator initiated as a (blocking or not) function call.

- Memory mapped connection ports with Avalon interconnect.

#### Syntax-directed translation to hardware

- Hierarchical FSMs: stalls to wait for the longest inner FSM.

- Access to external memory through arrays and pointers.

- One local memory for each local array.

### **Software pipelined loops →** Optimize CPLI (initiation interval)

- Basic software pipelining with rough data dependence analysis.

- Latency-aware pipelined DDR accesses (with internal FIFOs).

#### Full interface within the complete system

- Accelerator initiated as a (blocking or not) function call.

- Memory mapped connection ports with Avalon interconnect.

#### A few compilation pragmas

- restrict: pointer does not alias with any other pointer.

- arbitration share: how many accesses without re-arbitration.

### Nested finite state machines and pipelined accesses

```

void acc(int *a, int *b, int *c) {

int i, j, k, a_sum, b_sum;

for(i=0; i<n; i++) {

for(j=0; j<m; j++)

a_sum += a[j];

for(j=0; j<p; j++)

b_sum += b[j];

c[i] = a_sum + b_sum;

}

</pre>

```

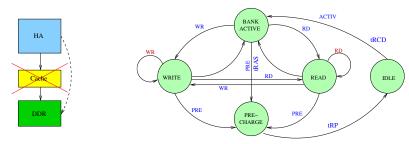

DDR-400 128Mbx8, size of 16MB, CAS 3, at 200MHz.

DDR-400 128Mbx8, size of 16MB, CAS 3, at 200MHz.

• Successive reads to the same row: 1 data every 10ns.

DDR-400 128Mbx8, size of 16MB, CAS 3, at 200MHz.

- Successive reads to the same row: 1 data every 10ns.

- Successive reads with a row change: 1 data every 80ns.

DDR-400 128Mbx8, size of 16MB, CAS 3, at 200MHz.

- Successive reads to the same row: 1 data every 10ns.

- Successive reads with a row change: 1 data every 80ns.

- **▶** For accelerators exploiting full bandwidth, frequent changes of rows kill the throughput. Need to use "burst" communications.

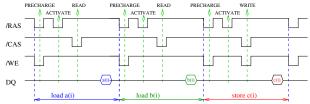

### Simple example: vector sum

Non-optimized version: time gaps + data thrown away.

### Simple example: vector sum

```

int vector_sum (int* __restrict__ a, int* __restrict__ b,

int* __restrict__ c, int n) {

int i;

for (i = 0; i < n; i++) c[i] = a[i] + b[i];

return 0;

block size PRECHARGE

READ

PRECHARGE

WRITE

READ

/RAS

/CAS

/WE

DQ

load a(i) ... a(i+k)

load b(i) ... b(i+k)

store c(i) ... c(i+k)

```

Optimized block version: reduces gaps, exploits burst.

### Strip-mining and loop distribution

Loop distribution: too large local memory.

Unrolling: too many registers.

```

for (i=0; i<MAX; i=i+BLOCK) {

for(j=0; j<BLOCK; j++) a_tmp[j] = a[i+j]; //prefetch

for(j=0; j<BLOCK; j++) b_tmp[j] = b[i+j]; //prefetch

for(j=0; j<BLOCK; j++) c_tmp[i+j] = a_tmp[j] + b_tmp[j];

for(j=0; j<BLOCK; j++) c[i+j] = c_tmp[i+j]; //store

}</pre>

```

### Strip-mining and loop distribution

Loop distribution: too large local memory. Unrolling: too many registers.

```

strip-mining + loop distribution.

```

```

for (i=0; i<MAX; i=i+BLOCK) {

for(j=0; j<BLOCK; j++) a_tmp[j] = a[i+j]; //prefetch

for(j=0; j<BLOCK; j++) b_tmp[j] = b[i+j]; //prefetch

for(j=0; j<BLOCK; j++) c_tmp[i+j] = a_tmp[j] + b_tmp[j];

for(j=0; j<BLOCK; j++) c[i+j] = c_tmp[i+j]; //store

}</pre>

```

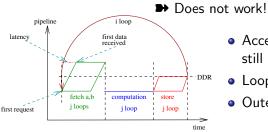

- Accesses to arrays a and b still interleaved!

- Loop latency penalty.

- Outer loop not pipelined.

### Introduce false dependences

```

for (i=0; i<MAX; i=i+BLOCK) {</pre>

for(j=0; j<BLOCK; j++) tmp = BLOCK; a_tmp[j] = a[i+j];</pre>

for(j=0; j<tmp; j++) b_tmp[j] = b[i+j];</pre>

for(j=0; j<BLOCK; j++) c_{tmp}[i+j] = a_{tmp}[j] + b_{tmp}[j];

for(j=0; j<BLOCK; j++) c[i+j] = c_tmp[i+j];</pre>

pipeline

first data

i loop

DDR

fetch a

fetch b

computation

store

j loop

j loop

i loop

i loop

first request

time

```

**▶** Still pay loop latency penalty and poor outermost loop pipeline.

# Emulating nested loops with a single loop & an automaton

```

i=0; j=0; bi=0;

for (k=0; k<4*MAX; k++) {

if (j==0) a_tmp[i] = a[bi+i];

else if (j==1)

b_{tmp[i]} = b[bi+i];

else if (j==2)

c_{tmp}[i] = a_{tmp}[i] + b_{tmp}[i];

else c[bi+i] = c_tmp[i];

if (i<BLOCK-1) i++;

else {

i=0:

if (j<3) j++;

else {j=0; bi = bi + BLOCK;}

```

- CPLI = 21! Problem with dependence analyzer and software pipeliner.

- Better behavior (CPLI=3) with case statement: by luck.

- Further loop unrolling to get CPLI = 1: too complex.

# Emulating nested loops with a single loop & an automaton

```

i=0; j=0; bi=0;

for (k=0; k<4*MAX; k++) {

if (j==0) a_tmp[i] = a[bi+i];

else if (j==1)

b_{tmp[i]} = b[bi+i];

else if (j==2)

c_{tmp}[i] = a_{tmp}[i] + b_{tmp}[i];

else c[bi+i] = c_tmp[i];

if (i<BLOCK-1) i++;

else {

i=0:

if (j<3) j++;

else {j=0; bi = bi + BLOCK;}

```

- CPLI = 21! Problem with dependence analyzer and software pipeliner.

- Better behavior (CPLI=3) with case statement: by luck.

- Further loop unrolling to get CPLI = 1: too complex.

- But DDR accesses still interleaved: bad throughput!

## Emulating nested loops, regrouping transfers

- No more interleaving between arrays a and b;

- CPLI not equal to 1, unless *restrict* pragma added: but leads to potentially wrong codes.

How to decrease CPLI and generalize to more complex codes?

# Decompose into communication & computation processes

- Pipeline computation and communication.

- Force suitable order of DDR requests.

- Overlap computation and communication.

- Play with flow/anti dependences.

# Decompose into communication & computation processes

- Pipeline computation and communication.

- Force suitable order of DDR requests.

- Overlap computation and communication.

- Play with flow/anti dependences.

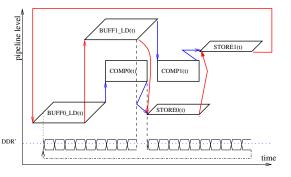

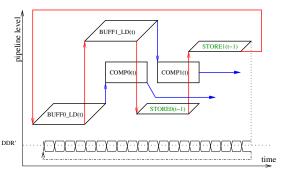

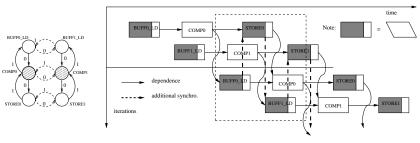

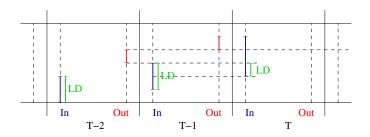

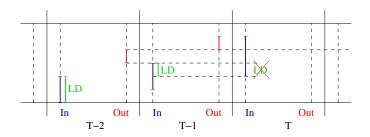

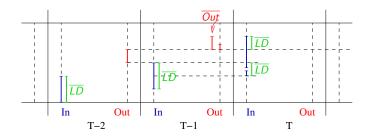

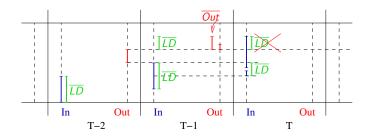

## Coarse-grain software pipelining

### Semantically, "as if":

- BUFF0\_LD(t) at 4t, BUFF1\_LD(t) at 4t + 2.

- COMP0(t) at 4t + 2, COMP1(t) at 4t + 4.

- STORE0(t) at 4t + 5, STORE1(t) at 4t + 7.

Here, STORE0(t-1) finished before COMP0(t).

**▶** Similar to "double buffering"

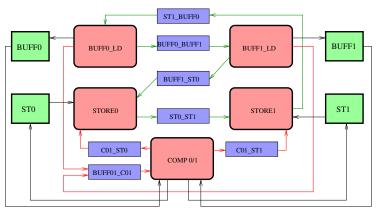

## General architecture organization: typical example

Use dedicated FIFOs of size 1 for synchronizations. Data transfers done through explicit memory accesses.

### How to synchronize at C-level?

#### Need two kinds of synchronizations

- Sequential access to shared resource (computation or DDR).

- Data-flow: wait for data to arrive.

```

pipeline depth

for (t=0; t<iter_space; t+=db_iter) {

DATA RECEIVE

dummy read +=*st1 buff0 read;

for(r=0,tmp=dummy\_read; r < r\_sup; r++)

if (s==0) {

compute local and global addresses for array a

and scan the iteration space of array a;

if end of iteration space: s++;

} else if (s==1) { same as s==0 for array b; }

DDR

transfer data from DDR to local memory;

if (r == r \sup -1) {*buff0 buff1 write = 0; tmp = 0; }

REQUEST

*buff0_c01_write = tmp;

external linearized loop control;

__ time

```

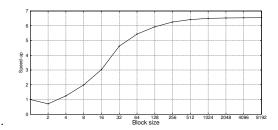

# Experimental results: typical examples

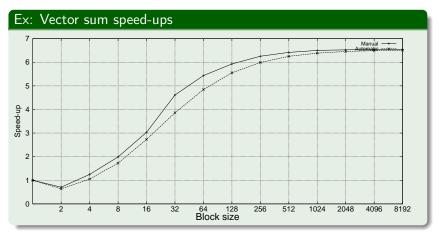

Typical speed-up vs block size figure (pS accurate simulation).

- SA: system alone.

- VS0 & VS1: vector sum direct & optimized version.

- MM0 & MM1: matrix-matrix multiply direct & optimized.

| Kernel | Speed-up | ALUT  | Dedicated | Total     | Total block | DSP block      | Max Frequency |

|--------|----------|-------|-----------|-----------|-------------|----------------|---------------|

|        |          |       | registers | registers | memory bits | 9-bit elements | (MHz > 100)   |

| SA     | 1        | 5105  | 3606      | 3738      | 66908       | 8              | 205.85        |

| VS0    | 1        | 5333  | 4607      | 4739      | 68956       | 8              | 189.04        |

| VS1    | 6.54     | 10345 | 10346     | 11478     | 269148      | 8              | 175.93        |

| MM0    | 1        | 6452  | 4557      | 4709      | 68956       | 40             | 191.09        |

| MM1    | 7.37     | 15255 | 15630     | 15762     | 335196      | 188            | 162.02        |

## Outline

# Polyhedral model

###

- Affine (parameterized) loop bounds and accesses

- Iteration domain, iteration vector

- Instance-wise analysis

- Affine transformations

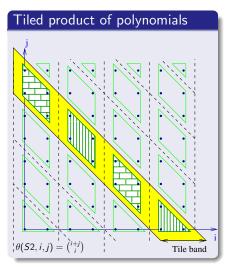

# Polyhedral model: tiling

- Tile: atomic block operation

- Increases granularity of computations

- Tile band: double buffering

- n loops transformed into n tile loops + n block loops

- Expressed from permutable loops (function  $\theta$ )

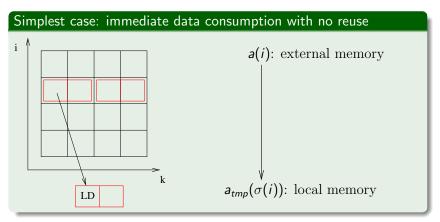

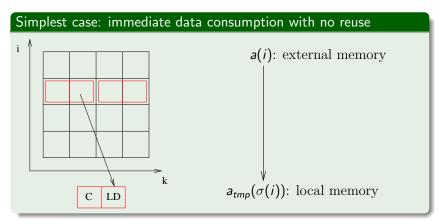

### Overview of the method

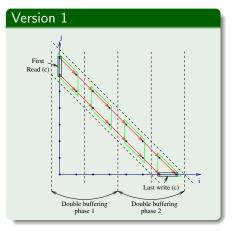

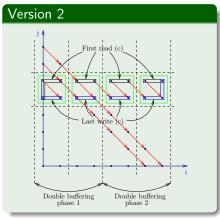

Derive automatically the C2H-compliant C functions for the pipelined accelerators: load, store and compute. Blocks obtained by loop tiling, pipelined in a "double-buffering" scheme.

- Communication coalescing prefetches data out of tile, following rows, and exploits data reuse

- **2** Local memory management defines memory elements, reduces size, and computes access functions

- Ode generation generates final C code in a linearized form while optimizing accesses to the DDR

### Overview of the method

Derive automatically the C2H-compliant C functions for the pipelined accelerators: load, store and compute. Blocks obtained by loop tiling, pipelined in a "double-buffering" scheme.

- Communication coalescing prefetches data out of tile, following rows, and exploits data reuse

- 2 Local memory management defines memory elements, reduces size, and computes access functions

- Ode generation generates final C code in a linearized form while optimizing accesses to the DDR

### Overview of the method

Derive automatically the C2H-compliant C functions for the pipelined accelerators: load, store and compute. Blocks obtained by loop tiling, pipelined in a "double-buffering" scheme.

- Communication coalescing prefetches data out of tile, following rows, and exploits data reuse

- Local memory management defines memory elements, reduces size, and computes access functions

- Code generation generates final C code in a linearized form while optimizing accesses to the DDR

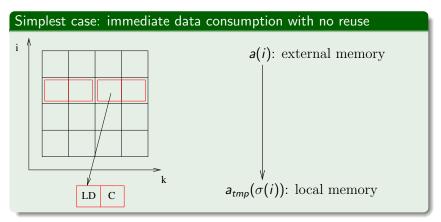

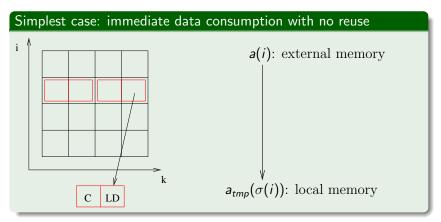

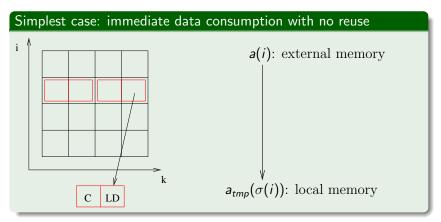

## Loop tiling: impact on communication

**Load**  $\sim$  FirstRead  $\cap$  tile domain **Store**  $\sim$  LastWrite  $\cap$  tile domain FirstRead/LastWrite  $\sim$  Array dataflow analysis

#### Valid load

(i) Load at least what is needed but not previously produced:

$$\bigcup_{t \leq \mathcal{T}} \left\{ \operatorname{In}(t) \setminus \operatorname{Out}(t' < t) \right\} \subseteq \operatorname{Load}(t \leq \mathcal{T})$$

(ii) Do not overwrite live data:

$$\operatorname{Out}(t < T) \cap \operatorname{Load}(T) = \emptyset$$

#### Exact load

(i) Load exactly what is needed but not previously produced:

$$\forall T, \cup_{t \leq T} \{ \operatorname{In}(t) \setminus \operatorname{Out}(t' < t) \} = \operatorname{Load}(t \leq T)$$

(ii) All loads must be disjoint:

$$\operatorname{Load}(T) \cap \operatorname{Load}(T') = \emptyset, \forall T \neq T'$$

### Valid approximated load

(i) Load at least the exact amount of data:

$$\cup_{t \leq \mathcal{T}} \left\{ \overline{\operatorname{In}}(t) \setminus \underline{\operatorname{Out}}(t' < t) \right\} \subseteq \operatorname{Load}(t \leq \mathcal{T})$$

(ii) Do not overwrite possible live data:

$$\overline{\mathrm{Out}}(t < T) \cap \mathrm{Load}(T) = \emptyset$$

### Valid approximated load

(i) Load at least the exact amount of data:

$$\bigcup_{t \leq \mathcal{T}} \left\{ \overline{\operatorname{In}}(t) \setminus \underline{\operatorname{Out}}(t' < t) \right\} \subseteq \operatorname{Load}(t \leq \mathcal{T})$$

(ii) Do not overwrite possible live data:

$$\overline{\mathrm{Out}}(t < T) \cap \mathrm{Load}(T) = \emptyset$$

## General organization

#### Iteration over tiles

```

void Load0() {

for (T_1 = ...)

3

for (T_{n-1} = ...) {

5

for (T_n = L(T_1, ..., T_{n-1});

6

T_n < U(T_1, \ldots, T_{n-1});

7

T_n += 2) {

8

//Synchronize from Store1()

9

//Load(T_1, ..., T_n) + sync. to Load1()

10

//Synchronize to Compute()

11

}}...}}

void Load1() {...}

12

void Store0() {...}

13

void Store1() {...}

14

15

void Compute() {...}

```

- Similar for functions Load1, Store0, Store1, Compute

- Loop nests: linearized

- Synchronizations

- Code generation ensures spatial data locality for optimized DDR access

## Kernel code generation

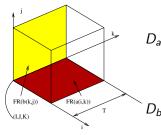

$$D_a: \left\{ \begin{array}{l} T \cdot I \leq i \leq T \cdot I + (T-1) \\ j = T \cdot J \\ T \cdot K \leq k \leq T \cdot K + (T-1) \end{array} \right. : LD(a(i,k))$$

$$D_b: \begin{cases} i = T \cdot I \\ T \cdot J \leq j \leq T \cdot J + (T-1) \\ T \cdot K \leq k \leq T \cdot K + (T-1) \end{cases} : LD(b(k,j))$$

## Linearized loops $\implies$ use Boulet-Feautrier with $(D_a, \theta_a), (D_b, \theta_b)$

$$\theta_a(i,j,k)=(0,i,k)$$

Arrays are read one after the other  $\theta_b(i,j,k)=(1,k,j)$  Scan arrays row by row

### Manually- vs. automatically-transformed

Method implemented in  $\mathrm{CHUBA}$  (array contraction:  $\mathrm{BeE}$ )

| Kernel                                    | Speed-up | ALUT  | Dedicated | Total     |

|-------------------------------------------|----------|-------|-----------|-----------|

|                                           |          |       | registers | registers |

| System alone                              |          | 4406  | 3474      | 3606      |

| DMA direct implementation                 | 1        | 4598  | 3612      | 3744      |

| DMA transformed manually (1K tile)        | 5.95     | 9665  | 10244     | 10376     |

| DMA transformed manually (8K tile)        | 6.01     | 9853  | 10517     | 10649     |

| DMA automatic (8K tile)                   | 5.98     | 11052 | 12133     | 12265     |

| Vector sum direct implementation          | 1        | 5333  | 4607      | 4739      |

| Vector sum transformed manually (1K tile) | 6.50     | 10345 | 10346     | 11478     |

| Vector sum transformed manually (8K tile) | 6.54     | 10881 | 11361     | 11493     |

| Vector sum automatic (8K tile)            | 6.51     | 11632 | 13127     | 13259     |

| Kernel                                    | Total block | DSP block      | Max Freq. |

|-------------------------------------------|-------------|----------------|-----------|

|                                           | memory bits | 9-bit elements | (MHz)     |

| System alone                              | 66908       | 8              | 205.85    |

| DMA direct implementation                 | 66908       | 8              | 200.52    |

| DMA transformed manually (1k tile)        | 203100      | 8              | 167.25    |

| DMA transformed manually (8k tile)        | 1120604     | 8              | 162.55    |

| DMA automatic (8k tile)                   | 1120348     | 48             | 167.87    |

| Vector sum direct implementation          | 68956       | 8              | 189.04    |

| Vector sum transformed manually (1k tile) | 269148      | 8              | 175.93    |

| Vector sum transformed manually (8k tile) | 1645404     | 8              | 164       |

| Vector sum automatic (8k tile)            | 1644892     | 48             | 159.8     |

| Kernel                                    | C        | ALUT  | Dedicated | Total     |

|-------------------------------------------|----------|-------|-----------|-----------|

| Kernei                                    | Speed-up | ALUI  |           |           |

|                                           |          |       | registers | registers |

| System alone                              |          | 4406  | 3474      | 3606      |

| DMA direct implementation                 | 1        | 4598  | 3612      | 3744      |

| DMA transformed manually (1K tile)        | 5.95     | 9665  | 10244     | 10376     |

| DMA transformed manually (8K tile)        | 6.01     | 9853  | 10517     | 10649     |

| DMA automatic (8K tile)                   | 5.98     | 11052 | 12133     | 12265     |

| Vector sum direct implementation          | 1        | 5333  | 4607      | 4739      |

| Vector sum transformed manually (1K tile) | 6.50     | 10345 | 10346     | 11478     |

| Vector sum transformed manually (8K tile) | 6.54     | 10881 | 11361     | 11493     |

| Vector sum automatic (8K tile)            | 6.51     | 11632 | 13127     | 13259     |

| Kernel                                    | Total block | DSP block      | Max Freq. |

|-------------------------------------------|-------------|----------------|-----------|

|                                           | memory bits | 9-bit elements | (MHz)     |

| System alone                              | 66908       | 8              | 205.85    |

| DMA direct implementation                 | 66908       | 8              | 200.52    |

| DMA transformed manually (1k tile)        | 203100      | 8              | 167.25    |

| DMA transformed manually (8k tile)        | 1120604     | 8              | 162.55    |

| DMA automatic (8k tile)                   | 1120348     | 48             | 167.87    |

| Vector sum direct implementation          | 68956       | 8              | 189.04    |

| Vector sum transformed manually (1k tile) | 269148      | 8              | 175.93    |

| Vector sum transformed manually (8k tile) | 1645404     | 8              | 164       |

| Vector sum automatic (8k tile)            | 1644892     | 48             | 159.8     |

| Kernel                                    | Speed-up | ALUT  | Dedicated | Total     |

|-------------------------------------------|----------|-------|-----------|-----------|

|                                           |          |       | registers | registers |

| System alone                              |          | 4406  | 3474      | 3606      |

| DMA direct implementation                 | 1        | 4598  | 3612      | 3744      |

| DMA transformed manually (1K tile)        | 5.95     | 9665  | 10244     | 10376     |

| DMA transformed manually (8K tile)        | 6.01     | 9853  | 10517     | 10649     |

| DMA automatic (8K tile)                   | 5.98     | 11052 | 12133     | 12265     |

| Vector sum direct implementation          | 1        | 5333  | 4607      | 4739      |

| Vector sum transformed manually (1K tile) | 6.50     | 10345 | 10346     | 11478     |

| Vector sum transformed manually (8K tile) | 6.54     | 10881 | 11361     | 11493     |

| Vector sum automatic (8K tile)            | 6.51     | 11632 | 13127     | 13259     |

| Kernel                                    | Total block | DSP block      | Max Freq. |

|-------------------------------------------|-------------|----------------|-----------|

|                                           | memory bits | 9-bit elements | (MHz)     |

| System alone                              | 66908       | 8              | 205.85    |

| DMA direct implementation                 | 66908       | 8              | 200.52    |

| DMA transformed manually (1k tile)        | 203100      | 8              | 167.25    |

| DMA transformed manually (8k tile)        | 1120604     | 8              | 162.55    |

| DMA automatic (8k tile)                   | 1120348     | 48             | 167.87    |

| Vector sum direct implementation          | 68956       | 8              | 189.04    |

| Vector sum transformed manually (1k tile) | 269148      | 8              | 175.93    |

| Vector sum transformed manually (8k tile) | 1645404     | 8              | 164       |

| Vector sum automatic (8k tile)            | 1644892     | 48             | 159.8     |

| Kernel                                    | Speed-up | ALUT  | Dedicated | Total     |

|-------------------------------------------|----------|-------|-----------|-----------|

|                                           |          |       | registers | registers |

| System alone                              |          | 4406  | 3474      | 3606      |

| DMA direct implementation                 | 1        | 4598  | 3612      | 3744      |

| DMA transformed manually (1K tile)        | 5.95     | 9665  | 10244     | 10376     |

| DMA transformed manually (8K tile)        | 6.01     | 9853  | 10517     | 10649     |

| DMA automatic (8K tile)                   | 5.98     | 11052 | 12133     | 12265     |

| Vector sum direct implementation          | 1        | 5333  | 4607      | 4739      |

| Vector sum transformed manually (1K tile) | 6.50     | 10345 | 10346     | 11478     |

| Vector sum transformed manually (8K tile) | 6.54     | 10881 | 11361     | 11493     |

| Vector sum automatic (8K tile)            | 6.51     | 11632 | 13127     | 13259     |

| Kernel                                    | Total block | DSP block      | Max Freq. |

|-------------------------------------------|-------------|----------------|-----------|

|                                           | memory bits | 9-bit elements | (MHz)     |

| System alone                              | 66908       | 8              | 205.85    |

| DMA direct implementation                 | 66908       | 8              | 200.52    |

| DMA transformed manually (1k tile)        | 203100      | 8              | 167.25    |

| DMA transformed manually (8k tile)        | 1120604     | 8              | 162.55    |

| DMA automatic (8k tile)                   | 1120348     | 48             | 167.87    |

| Vector sum direct implementation          | 68956       | 8              | 189.04    |

| Vector sum transformed manually (1k tile) | 269148      | 8              | 175.93    |

| Vector sum transformed manually (8k tile) | 1645404     | 8              | 164       |

| Vector sum automatic (8k tile)            | 1644892     | 48             | 159.8     |

### Contributions

- Focus on memory optimizations and interface generation.

- Demonstrates importance of source-to-source optimizations (script + use of transformation tool) in front of HLS tools.

- To our knowledge, first process to automate communications and integrate hardware accelerators, entirely at C level.

- Identifies important needs for synchronization mechanisms at source level and for better pragmas (e.g., restrict for pairs).

- Analysis and transformations appear to be very similar to optimizations needed for GPUs.

- Starting point for using HLS tools as back-end compilers?

## Perspectives

### Many opportunities for improvements.

- Design more domain-specific code generation.

- Define compilation directives at C level for hardware synthesis.

- Design customized memories and inter-processes buffers.

- Exploit schedule with slacks for GALS pipelined designs.

- . . .