# System-Level Synthesis of Ultra Low-Power Wireless Sensor Network Node Controllers: A Complete Design-Flow

Muhammad Adeel Ahmed Pasha

## ▶ To cite this version:

Muhammad Adeel Ahmed Pasha. System-Level Synthesis of Ultra Low-Power Wireless Sensor Network Node Controllers: A Complete Design-Flow. Computer Science [cs]. Université Rennes 1, 2010. English. NNT: . tel-00553143

# HAL Id: tel-00553143 https://theses.hal.science/tel-00553143

Submitted on 6 Jan 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre : 4297 ANNÉE 2010

# THÈSE / UNIVERSITÉ DE RENNES 1

sous le sceau de l'Université Européenne de Bretagne

pour le grade de

## **DOCTEUR DE L'UNIVERSITÉ DE RENNES 1**

Mention: Traitement du Signal et Télécommunications

**Ecole doctorale: Matisse**

présentée par

# Muhammad Adeel Ahmed PASHA

Préparée à l'unité de recherche : CAIRN/IRISA-UMR 6074

Nom développé de l'unité : Institut de Recherche en Informatique et

Systèmes Aléatoires de Rennes

Composante universitaire : S.P.M.

Synthèse de haut-niveau de contrôleurs ultra-faible consommation pour des réseaux de capteurs: un flot de conception complet

System-Level Synthesis of Ultra Low-Power Wireless Sensor Network Node Controllers: A Complete Design-Flow

## Thèse soutenue à l'IRISA Rennes

le 15 décembre 2010

devant le jury composé de:

## **Tanguy RISSET**

Président

Professeur, INSA Lyon, Lyon

#### Cécile BELLEUDY

Examinateur

Maître de Conférences, Université de Nice, Sophia Antipolis

### **Christian PIGUET**

Rapporteur

Professeur, EPFL, Lausanne, Suisse

## Frédéric PETROT

Rapporteur

Professeur, ENSIMAG, Grenoble

#### **Olivier SENTIEYS**

Directeur

Professeur, Université de Rennes 1, Lannion

#### Steven DERRIEN

Co-directeur

Maitre de Conférences, Université de Rennes 1, Rennes

# Acknowledgments

First of all, countless thanks to Almighty Allah, Who has given me knowledge and courage to carry out this work. Secondly, I would like the readers to keep all the below-mentioned people in mind while reading this dissertation, without them this success would not have been possible.

I would like to begin by thanking my Ph.D. advisors, Olivier Sentieys and Steven Derrien, for their guidance, understanding, patience, always believing in my capabilities and most importantly, their friendship during my Ph.D. at IRISA Rennes. They provided me different flavors of care as they were my bosses, advisors, friends and brothers from time to time. They have always helped me to not only grow as a researcher and developer but also an independent thinker and a better human being. It is my honour to have worked with them.

I would also like to thank all my colleagues of CAIRN research team and administration staff at IRISA for creating such a pleasant work environment and for being there for me. In particular many thanks to Kevin Martin, Antoine Floch, Erwan Raffin, Laurent Perraudeau, Antoine Morvan, Naeem Abbas, Amit Kumar, Jeremie Guidoux, Loic Cloatre, Florent Berthelot, Georges Adouko, Maxime Naullet, Charles Wagner, François Charot, Christophe Wolinski, Patrice Quinton and Ludovic L'Hours with whom I worked closely and had many fruitful discussions. Many thanks to my colleagues at Lannion as well including Olivier Berder, Daniel Menard, Daniel Chillet, Sebastian Pillement, Emmanuel Casseau, Philippe Quemerais, Thomas Anger, Arnaud Carer, Vivek T.D., Shafqat Khan and others. I would also like to pay special thanks to CAIRN team-assistants Celine, Elise and Nadia for their support.

Most importantly I would like to thank my parents, Abdul Hameed and Latifan Bibi, for their faith in me, encouraging me to be as ambitious as I wanted and supporting me in all my endeavors. It was under their watchful eye that I gained so much drive and ability to tackle challenges head on. A very special thanks goes to my siblings, nephews and nieces as well for being there for me all the time and cheering me up.

I thank all my friends in France and in Pakistan for motivating me and regularly wishing me good luck. I am very grateful to all of them who made me feel at home, cared for and allowed me to worry only about my studies during my stay in France. I would also like to thank my teachers at Centre d'Etude de Langue of Colmar and at University of Nice Sophia-Antipolis.

Finally I would like to express my indebtedness to all the jury members for spending their precious time to read and accept my work.

This dissertation is dedicated to the light of useful knowledge that enlightens our lives.

# Résumé

Les réseaux de capteurs sont une technologie dont l'évolution est très rapide et avec un grand nombre d'applications potentielles dans des domaines variés (e.g. en médecine, en surveillance de l'environnement ou de structures, ou encore en contexte militaire). La conception d'une plateforme matérielle pour un nœud de capteur est un véritable défi car elle est soumise à des contraintes sévères. Par exemple, comme les nœuds doivent être de taille et de coût limités, il doivent comporter une capacité limitée d'énergie et ils s'appuient donc sur des sources d'énergie non rechargeables (e.g. piles) ou récupérées dans l'environnement (e.g. cellules photovoltaïques). Comme le réseau doit de plus pouvoir fonctionner sans intervention pendant une très longue durée (des mois voire des années), la consommation d'énergie est souvent considérée comme la contrainte la plus forte. De nos jours, ces dispositifs s'appuient principalement sur des microcontrôleurs à très faible consommation disponibles commercialement. Ces processeurs offrent des puissances de calcul raisonnable pour des coûts et une consommation limités. Cependant, ils ne sont pas nécessairement complètement adaptés au contexte des réseaux de capteurs car basés sur une structure de calcul monolithique et généraliste.

Dans cette thèse, nous proposons un flot de conception depuis le niveau système pour une approche alternative et originale se basant sur le concept de micro-tâches matérielles avec coupure de la tension d'alimentation (power gating). Dans cette approche les parties calcul et contrôle d'un nœud de capteur sont constituées d'un ensemble de micro-tâches matérielles qui sont activées selon un principe événementiel, chacune étant dédiée à une tâche spécifique du système, telle que le relevé de paramètres, la couche MAC, le routage ou le traitement des données. En combinant la spécialisation du matériel avec la coupure d'alimentation, nous réduisons de façon significative les énergies dynamique et statique d'un dispositif. Suivant la philosophie de nombreux environnements logiciels de programmation des réseaux de capteurs, notre flot de conception utilise l'association d'un langage spécifique (DSL pour Domain Specific Language) pour les spécifications système (interactions entre micro-tâches, gestion des événements et des ressources partagées, etc.) et de C-ANSI pour spécifier le comportement de chaque micro-tâche. Partant de ces spécifications et en utilisant des approches MDE (Model Driven Engineering) et des techniques de compilation reciblables, notre flot génère une description VHDL synthétisable de l'ensemble du sous-système de contrôle et de calcul d'un nœud de capteur.

Dans un but de validation expérimentale de l'approche, nous accomplissons tout d'abord des simulations au niveau transistor à l'aide de SPICE pour étudier les performances des coupures d'alimentation dans notre système. Ces coupures dynamiques au cours de l'exécution sont possibles avec des temps de commutation très faibles, de l'ordre de la centaine de nano-secondes. Ceci améliore les temps de réveil et de mise en veille d'au moins 50% en comparaison avec les microcontrôleurs à faible consommation. Un cas d'étude sur une application en réseau de capteurs a été spécifié puis synthétisé à l'aide de notre flot de conception matériel en un ensemble de micro-tâches associées à un moniteur système. Les résultats montrent que des gains en énergie dynamique d'un à deux ordres de grandeur sont possibles en comparaison avec des implémentations à base de microcontrôleurs comme le MSP430. De la même façon, des gains d'un ordre de grandeur en énergie statique sont également obtenus grâce à la réduction de l'espace mémoire et à l'utilisation de la coupure des tensions d'alimentation.

# Abstract

Wireless Sensor Networks (WSN) are a fast evolving technology having a number of potential applications in various domains of daily-life, such as structural and environmental monitoring, medicine, military surveillance, robotic explorations etc. Engineering a WSN node hardware platform is known to be a tough challenge, as the design must enforce many severe constraints. For example, since WSN nodes must have small form-factors and limited production cost, it is not possible to provide them with large energy sources. In most cases they must rely on non-replenishing (e.g. battery) or self-sufficient (e.g. solar cells) sources of energy. As WSN nodes may have to work unattended for long durations (months if not years), their energy consumption is often the most critical design parameter. Moreover, as a WSN node remains idle during most of its life-time (with a duty cycle of less than 1%), special measures have to be taken to avoid the high static energy dissipation. WSN node devices have until now been designed using off-the-shelf low-power microcontroller units (MCUs) (such as the MSP430, the ARM-Cortex-M0 or the ATMega128L). These MCUs provide a reasonable processing power with low power consumption at an affordable cost. However, they are not necessarily well-suited for WSN node design as they are based on a general purpose compute engine.

In this thesis, we propose a complete system-level design-flow for an alternative approach based on the concept of power-gated hardware micro-tasks. In this approach, computation and control part of a WSN node is made of several hardware micro-tasks that are activated on an event-driven basis, each of them being dedicated to a specific task of the system (such as event-sensing, low-power MAC, routing, and data processing etc.). By combining hardware specialization with power-gating, we can drastically reduce both dynamic and static energy of the WSN node. Following the philosophy of many WSN software frameworks, our design-flow uses a combination of a textual Domain Specific Language (DSL) for system-level specifications (interactions between micro-tasks, event management, shared resources management etc.) and ANSI-C for specifying the behavior of each micro-task. Starting from these specifications and by using Model Driven Engineering (MDE) and retargetable compilation techniques, we are able to generate a synthesizable VHDL description of the whole computation and control subsystem of a WSN node. This VHDL description provides a direct path to ASIC/FPGA implementation.

For experimental validation of the approach, first of all, we performed SPICE transistor-level simulations to study the feasibility of using power-gating in our system. We found that the power-gating scheme happens to have very short switching-time delays, in the orders of a few hundred of nano-seconds. This improves the wake-up response time by at least 50% when compared to low-power MCUs such as the MSP430. A case-study example of a WSN application was conceived and by using our design-flow, VHDL codes for different hardware micro-tasks and system monitor were obtained. The synthesis results show that dynamic power savings by one to two orders of magnitude are possible w.r.t. MCU-based implementations. Similarly, static power savings of one order of magnitude are also obtained due to the reduction in data memory size and power-gating.

# Contents

| C | onter | $_{ m nts}$ |                                                                   | i  |

|---|-------|-------------|-------------------------------------------------------------------|----|

| 0 | Rés   | umé é       | tendu                                                             | 1  |

|   | 0.1   | Résea       | ux de capteurs sans fil                                           | 1  |

|   |       | 0.1.1       | Architecture d'un nœud de capteur                                 | 2  |

|   |       | 0.1.2       | Contraintes de conception d'un nœud de capteur                    | 3  |

|   | 0.2   | Optim       | nisation de puissance d'un nœud de capteur                        | 4  |

|   |       | 0.2.1       | Conception VLSI orientée faible consommation                      | 4  |

|   |       | 0.2.2       | Microcontrôleurs faible consommation                              | 5  |

|   | 0.3   | Une a       | pproche combinant power gating et spécialisation                  | 6  |

|   |       | 0.3.1       | Micro-tâches matérielles                                          | 7  |

|   |       | 0.3.2       | Modèle au niveau système proposé                                  | 7  |

|   |       | 0.3.3       | Modèle d'exécution et flot de conception logiciel                 | 10 |

|   | 0.4   | Contri      | ibutions                                                          | 13 |

|   | 0.5   | Résult      | tats expérimentaux                                                | 13 |

|   |       | 0.5.1       | Temps de commutation du power gating                              | 14 |

|   |       | 0.5.2       | Gains en puissance dynamique de l'approche à base de micro-tâches | 14 |

|   |       | 0.5.3       | Estimation de la consommation du moniteur système                 | 16 |

| 1 | Intr  | oducti      | ion                                                               | 19 |

|   | 1.1   | Wirele      | ess Sensor Network (WSN)                                          | 19 |

|   |       | 1.1.1       | WSN node architecture                                             | 20 |

|   |       | 1.1.2       | WSN node design constraints                                       | 21 |

|   | 1.2   | Power       | optimization of a WSN node                                        | 22 |

|   |       | 1.2.1       | Low-power VLSI design                                             | 22 |

|   |       | 1.2.2       | Low-power MCUs                                                    | 22 |

|   | 1.3   | Propo       | sed approach: combination of power-gating and hardware special-   |    |

|   |       | ization     | 1                                                                 | 23 |

|   |       | 1.3.1       | Power-gated micro-task                                            | 24 |

|   |       | 1.3.2       | Proposed system model                                             | 25 |

|   |       | 1.3.3       | Customized execution model and software design-flow               | 27 |

|   | 1.4   | Contri      | ibutions                                                          | 30 |

|   | 1.5   | Thesis      | s organization                                                    | 30 |

ii Contents

| <b>2</b> | WS  | N nod | e architectures and low-power microcontrollers 3          | 33       |

|----------|-----|-------|-----------------------------------------------------------|----------|

|          | 2.1 | WSN   | basics                                                    | 33       |

|          | 2.2 | WSN   | node architectures                                        | 34       |

|          |     | 2.2.1 | Computation subsystem                                     | 35       |

|          |     | 2.2.2 | Communication subsystem                                   | 35       |

|          |     | 2.2.3 | Sensing subsystem                                         | 36       |

|          |     | 2.2.4 | Power supply subsystem                                    | 36       |

|          | 2.3 | Power | dissipation analysis of a WSN node                        | 37       |

|          | 2.4 | WSN   | platforms                                                 | 38       |

|          |     | 2.4.1 | The Mica mote family                                      | 38       |

|          |     | 2.4.2 | BTnodes                                                   | 39       |

|          |     | 2.4.3 | Telos                                                     | 39       |

|          |     | 2.4.4 | PowWow                                                    | 39       |

|          |     | 2.4.5 | WiseNet                                                   | 39       |

|          |     | 2.4.6 | ScatterWeb                                                | 39       |

|          | 2.5 | Emerg | gence of low-power microcontrollers                       | 40       |

|          |     | 2.5.1 | Power optimization at VLSI circuit level                  | 40       |

|          |     |       | 2.5.1.1 Clock gating                                      | 42       |

|          |     |       | 2.5.1.2 Voltage scaling                                   | 44       |

|          |     |       | 2.5.1.3 Transistor sizing                                 | 44       |

|          |     |       | 2.5.1.4 Power gating                                      | 45       |

|          |     | 2.5.2 | Commercial low-power MCUs                                 | 46       |

|          |     | 2.5.3 | WSN-specific sub-threshold controllers                    | 48       |

|          |     |       | 2.5.3.1 SNAP/LE processor                                 | 48       |

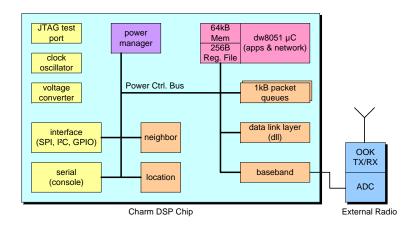

|          |     |       | 2.5.3.2 Accelerator-based WSN processor                   | 49       |

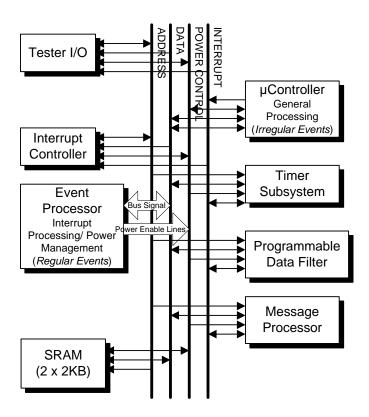

|          |     |       | 2.5.3.3 Charm processor                                   | 51       |

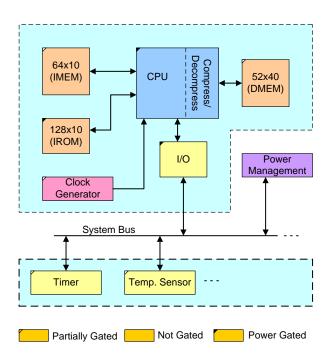

|          |     |       | 2.5.3.4 Phoenix processor                                 | 51       |

|          |     |       | 2.5.3.5 BlueDot                                           | 52       |

|          |     | 2.5.4 | Conclusion                                                | 52       |

|          | TT. |       |                                                           |          |

| 3        | _   |       | v ii i e                                                  | 55       |

|          | 3.1 | _     |                                                           | 55       |

|          |     | 3.1.1 | 9                                                         | 56       |

|          |     | 3.1.2 | 9                                                         | 57       |

|          |     |       | 9                                                         | 57       |

|          |     | 9 1 9 |                                                           | 58       |

|          |     | 3.1.3 | 9                                                         | 58       |

|          |     |       | 9                                                         | 58       |

|          |     |       |                                                           | 59       |

|          |     |       |                                                           | 59       |

|          |     |       | 3.1.3.4 Mixed Integer Linear Programming (MILP)-based ap- | 20       |

|          |     | 914   | •                                                         | 60       |

|          |     | 3.1.4 | , •                                                       | 60<br>80 |

|          |     |       | 3.1.4.1 Interval-graph based allocation                   | 60       |

Contents

|   |     |        | Left-Edge Algorithm (LEA): 61                              |

|---|-----|--------|------------------------------------------------------------|

|   |     |        | 3.1.4.2 Conflict-graph based allocation 61                 |

|   |     |        | Heuristic <i>clique</i> partitioning [137]: 61             |

|   |     |        | Graph coloring algorithm:                                  |

|   | 3.2 | Power- | -aware HLS tools                                           |

|   |     | 3.2.1  | SCALP                                                      |

|   |     | 3.2.2  | Interconnect-Aware Power Optimized (IAPO) approach 63      |

|   |     | 3.2.3  | LOPASS                                                     |

|   |     | 3.2.4  | HLS-pg                                                     |

|   | 3.3 | -      | pools targeting other design constraints                   |

|   | 0.0 | 3.3.1  | Multi-mode HLS                                             |

|   |     | 3.3.2  | Word-length aware HLS                                      |

|   |     | 3.3.3  | Datapath-specification-based HLS                           |

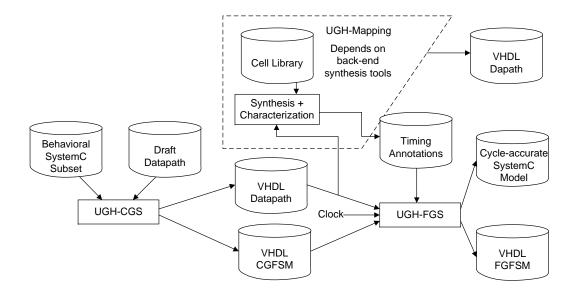

|   |     |        | 3.3.3.1 User Guided HLS (UGH)                              |

|   |     |        | 3.3.3.2 No Instruction-Set Computer (NISC) 66              |

|   |     | 3.3.4  | Commercial tools and their application domain              |

|   | 3.4 |        | eation Specific Instruction-set Processor (ASIP) design 67 |

|   |     | 3.4.1  | Methodology for complete ASIP design                       |

|   |     | 3.4.2  | Methodology for partial ASIP design                        |

|   |     | 3.4.3  | Instruction selection                                      |

|   |     |        | 3.4.3.1 DAG-based instruction selection 71                 |

|   |     |        | Simulated annealing:                                       |

|   |     |        | Genetic Algorithm (GA):                                    |

|   |     |        | Constraint Satisfaction Problem (CSP):                     |

|   |     |        | 3.4.3.2 Tree-based instruction selection                   |

|   |     |        | Dynamic programming:                                       |

|   |     |        | Bottom-Up Rewrite System (BURS) generator: 73              |

|   |     | 3.4.4  | Register allocation                                        |

|   | 3.5 |        | ng tools in ASIP design                                    |

|   |     | 3.5.1  | ICORE                                                      |

|   |     | 3.5.2  | Soft-core generator                                        |

|   | 3.6 |        | al discussion                                              |

|   |     |        |                                                            |

| 4 | Har |        | micro-task synthesis 79                                    |

|   | 4.1 | Notion | n of hardware micro-task                                   |

|   |     | 4.1.1  | Potential power benefits                                   |

|   |     |        | 4.1.1.1 Simplified architecture                            |

|   |     |        | 4.1.1.2 Exploiting the run-to-completion semantic 82       |

|   |     |        | 4.1.1.3 Micro-task granularity                             |

|   |     |        | 4.1.1.4 Simplified access to shared resources              |

|   |     | 4.1.2  | Generic architecture                                       |

|   | 4.2 | Propos | sed design-flow for micro-task generation                  |

|   |     | 4.2.1  | Compiler front-end                                         |

|   |     | 4.2.2  | Instruction selection and mapping                          |

|   |     |        |                                                            |

iv

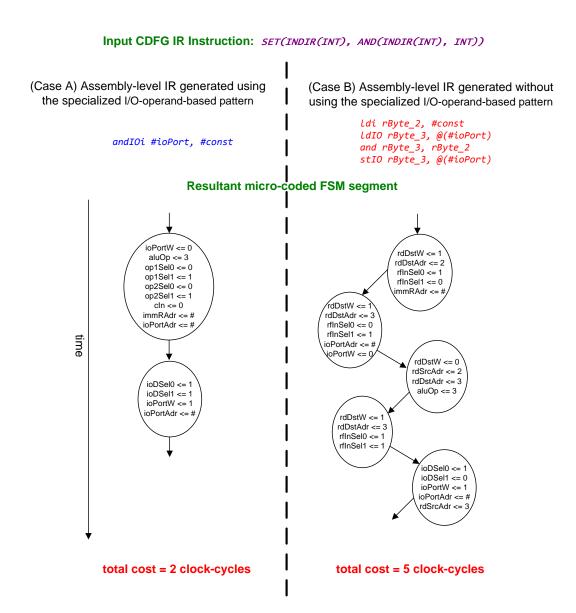

|   |     | 4.2.2.1 Customized BURG-generator                                | 89         |

|---|-----|------------------------------------------------------------------|------------|

|   |     | $P, the pattern: \dots \dots \dots \dots \dots \dots$            | 89         |

|   |     | $S, the replacement symbol: \dots \dots \dots \dots \dots$       | 90         |

|   |     | C and $A$ , the cost and the action:                             | 90         |

|   |     | 4.2.3 Bitwidth adaptation                                        | 93         |

|   |     | 4.2.4 Register allocation                                        | 94         |

|   |     | 4.2.5 Hardware generation                                        | 95         |

|   |     | 4.2.5.1 Datapath generation                                      | 95         |

|   |     | 4.2.5.2 FSM generation                                           | 96         |

|   |     | 4.2.5.3 Code generation                                          | 98         |

|   |     | 4.2.6 Comparison to traditional design-flows of ASIP and HLS     | 98         |

|   | 4.3 | An illustrative example of micro-task synthesis                  | 00         |

|   |     | 4.3.1 Resultant dynamic power and energy savings                 | 01         |

| _ | _   |                                                                  |            |

| 5 |     |                                                                  | 05         |

|   | 5.1 | P                                                                |            |

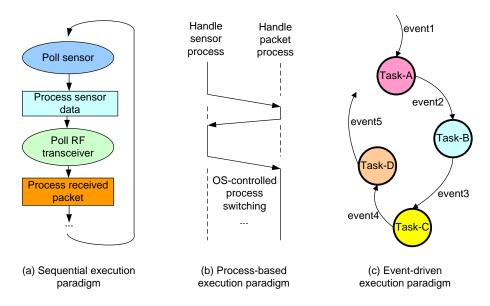

|   |     | 5.1.1 Sequential approach                                        |            |

|   |     | 5.1.2 Process-based approach                                     |            |

|   | T 0 | 5.1.3 Event-driven approach                                      |            |

|   | 5.2 | System-level execution model                                     |            |

|   | 5.3 | WSN-specific OS                                                  |            |

|   |     | 5.3.1 TinyOS                                                     |            |

|   |     | 5.3.2 Contiki                                                    |            |

|   |     | 5.3.3 MANTIS OS                                                  |            |

|   |     | 5.3.4 LIMOS                                                      |            |

|   | 5.4 | 5.3.5 SenOS                                                      |            |

|   | 0.4 | 5.4.1 Events and commands                                        |            |

|   |     | 5.4.1 Events and commands                                        |            |

|   |     | 5.4.3 Task hierarchy                                             |            |

|   |     | 5.4.4 Memory management                                          |            |

|   | 5.5 | System monitor (SM)                                              |            |

|   | 5.6 | Design-flow for the SM generation                                |            |

|   | 0.0 | 5.6.1 System specification                                       |            |

|   |     | 5.6.2 Model transformation                                       |            |

|   |     | 5.6.3 Extraction of guard expression for micro-task activation 1 |            |

|   |     | 5.6.4 Hardware generation                                        |            |

|   |     | 5.6.5 C-simulator generation for early system validation         |            |

|   | 5.7 | · · ·                                                            | 21         |

|   | -   |                                                                  |            |

| 6 | _   | •                                                                | <b>2</b> 3 |

|   | 6.1 |                                                                  | 23         |

|   | 6.2 | An illustrative WSN application                                  |            |

|   |     | 6.2.1 Existing WSN applications                                  | 25         |

Contents

|    |       | 6.2.2   | WSN ap     | plication benchmarks                          |  |       | 127 |

|----|-------|---------|------------|-----------------------------------------------|--|-------|-----|

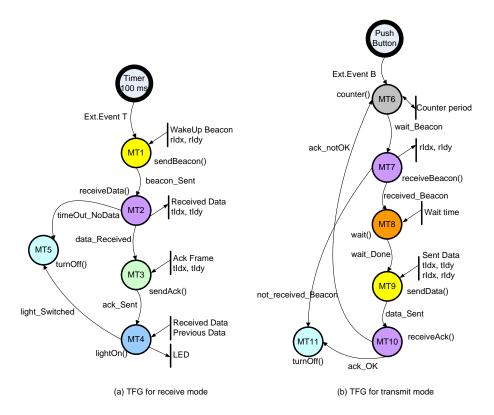

|    |       | 6.2.3   | The case   | study                                         |  |       | 127 |

|    |       |         | 6.2.3.1    | Tasks running in transmit mode                |  |       | 128 |

|    |       |         | 6.2.3.2    | Tasks running in receive mode $\dots \dots$ . |  |       | 129 |

|    | 6.3   | Dynan   | nic power  | gains                                         |  |       | 130 |

|    |       | 6.3.1   | Extraction | on of cycle count                             |  |       | 131 |

|    |       | 6.3.2   | Approxim   | nate energy efficiency                        |  |       | 131 |

|    | 6.4   | Design  | space ex   | ploration for datapath bitwidth               |  |       | 134 |

|    |       | 6.4.1   | 8-bit vs.  | 16-bit micro-task                             |  |       | 134 |

|    | 6.5   | Power   | estimatio  | n of hardware system monitor                  |  |       | 135 |

|    |       | 6.5.1   | Dynamic    | power consumption                             |  |       | 135 |

|    |       | 6.5.2   | Static po  | wer and area overhead                         |  |       | 137 |

|    | 6.6   | Effects | of low di  | ty-cycle and overall energy gain              |  | <br>• | 138 |

| 7  | Con   | clusior | and fut    | ure perspectives                              |  |       | 141 |

|    | 7.1   | Work i  | n progres  | 5                                             |  |       | 143 |

|    | 7.2   | Future  | perspect   | ves                                           |  |       | 144 |

| Pe | erson | al pub  | lications  |                                               |  |       | 147 |

| Li | st of | acrony  | ms and     | abbreviations                                 |  |       | 149 |

| Bi | bliog | graphy  |            |                                               |  |       | 153 |

| Li | st of | Figure  | es         |                                               |  |       | 165 |

| Li | st of | Tables  | 3          |                                               |  |       | 169 |

# Chapter 0

# Résumé étendu

## 0.1 Réseaux de capteurs sans fil

Les réseaux de capteurs sont une technologie dont l'évolution est très rapide et avec un grand nombre d'applications potentielles dans des domaines variés de notre vie quotidienne, e.g. en médecine, en surveillance de l'environnement ou de structures, en robotique ou encore en contexte militaire. Les avancées dans les technologies de l'électronique numérique, de la microélectronique ou de la micromécanique MEMS (Micro-Electro-Mechanical-Systems) ont facilité le développement de nœuds de capteur à faible coût, faible encombrement et faible consommation qui communiquent sans-fil de façon efficace sur de faibles distances. Par conséquent, le domaine émergent des réseaux de capteurs combine la mesure, le calcul et la communication de données dans un unique et minuscule nœud dit "de capteur". Ces systèmes contenant des milliers voire des dizaines de milliers de tels nœuds sont anticipés afin de révolutionner la façon dont l'humain travaille et vit.

Le principal challenge dans le domaine des réseaux de capteurs est de faire face aux difficultés liées aux contraintes sévères de ressources et d'énergie liées au nœud de capteur. Les processeurs contrôlant le nœud ne contiennent que quelques kilo-octets de mémoire et doivent cependant implémenter des protocoles réseaux complexes. Plusieurs contraintes émergent du fait que ces composants seront produits en grand nombre et doivent être de petite taille et peu chers. Chaque nouvelle génération de technologie silicium amène un plus grand nombre de transistors sur une même surface et résulte donc en deux scénarios distincts: (i) plus de fonctionnalités peuvent être placées sur un composant à surface constante ou (ii) la taille du composant et sa consommation peuvent être réduites pour la même fonctionnalité.

La plus forte des contraintes et aussi la plus complexe à respecter dans ce domaine des réseaux de capteurs est celle de la consommation d'énergie ou de puissance. La faible taille d'un nœud de capteur et ses besoins en autonomie limitent de façon très forte la réserve d'énergie disponible sur un de ces dispositifs. Ceci induit des limitations en termes de puissance de calcul et de mémoire disponibles et conduit à des problématiques représentant un véritable challenge en termes d'architectures. De nombreux dispositifs,

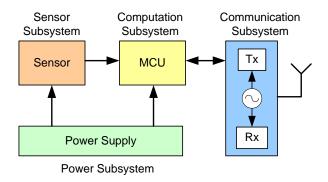

Figure 1: Architecture générale d'un nœud de capteur.

tels que les téléphones cellulaires et autres "smartphones", réduisent leur consommation d'énergie en utilisant des composants matériels spécialisés — ou  $Application\ Specific\ Integrated\ Circuits\ (ASIC)$  — qui procurent des implémentations faible consommation des protocoles de communications et algorithmes de traitement nécessaires.

A ce jour, une des forces des réseaux de capteurs est leur supposées flexibilité et universalité. Cependant, si on observe de façon plus précise leur conception actuelle, le besoin de flexibilité et de programmabilité est essentiellement poussé vers les couches hautes et applicatives, ce qui de plus ne représente qu'une faible fraction de la charge de calcul du nœud, alors que la plus grosse partie de celle-ci est dédiée à la pile de protocole de communication, en particulier vers les couches basses. Notre opinion est donc qu'il est intéressant d'explorer une approche de spécialisation du matériel dans la conception d'un nœud du réseau, de façon à respecter les exigences de très faible énergie. Afin de réduire cette consommation dans un dispositif, nous devons tout d'abord étudier son architecture générique et rechercher ses "points chauds". L'architecture générique d'un nœud de capteur est discutée dans la prochaine section.

### 0.1.1 Architecture d'un nœud de capteur

Les nœuds de capteur sont des dispositifs à faible consommation fortement embarqués constitués de blocs de calcul et de mémorisation (e.g. un microcontrôleur (MCU) connecté à une mémoire RAM et/ou flash) associés à des composants de communication sans-fil (RF transceiver) et à des capteurs/actionneurs. Comme les nœuds doivent être de taille et de coût limités, il doivent comporter une capacité limitée d'énergie [138]. Dans la plupart des cas, ils s'appuient donc sur des sources d'énergie non rechargeables (e.g. piles) ou récupérées dans l'environnement (e.g. cellules photovoltaïques).

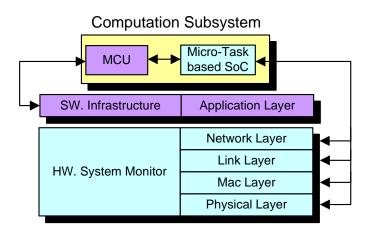

La figure 1 présente l'architecture d'un nœud de capteur générique. Il est constitué de quatre sous-systèmes: alimentation, communication, contrôle et calcul, et capteurs. Le sous-système d'alimentation est constitué d'une batterie (ou d'une pile) et d'un convertisseur DC-DC. Le sous-système de communication constitué d'un émetteur-récepteur radio pour les communications sans-fil entre objets. La plupart des plate-formes utilise une antenne unique omnidirectionnelle, cependant des techniques de

coopération MIMO (Multiple-Input and Multiple-Output) peuvent également être déployées [99]. Le sous-système de calcul est typiquement composé de mémoire permettant de stocker le programme ou les données, et d'un microcontrôleur pour contrôler le système et traiter les données. Le dernier sous-système lie le nœud avec le monde physique et dispose d'un ensemble de capteurs et/ou d'actionneurs dépendant de l'application considérée. Il contient également des convertisseurs analogique-numérique pour convertir les signaux captés en données numériques utilisables pas le calculateur. Pour concevoir de tels dispositifs avec des ressources fortement limitées, les concepteurs d'architecture doivent faire face à des contraintes difficiles qui seront discutées dans la prochaine section.

## 0.1.2 Contraintes de conception d'un nœud de capteur

Concevoir ces nœuds de capteur est un réel challenge, car plusieurs fortes contraintes sont imposées qui, de plus, sont souvent étroitement liées. Les principales métriques utiles à cette conception sont décrites ci dessous.

- La *consommation d'énergie* (ou de puissance) est le plus grand challenge à atteindre car le réseau doit pouvoir fonctionner sans intervention pendant une très longue durée (des mois voire des années).

- La *robustesse* est également un critère important pour les réseaux de capteurs car elle permet de garantir le fonctionnement correct du r'eseau dans son ensemble. Chaque nœud doit donc être conçu pour être le plus robuste possible afin de tolérer et donc de s'adapter à des pannes de nœuds voisins.

- La *sécurité* au niveau de l'application est une autre métrique à considérer et les dispositifs doivent souvent embarquer des algorithmes relativement complexes d'authentification ou de chiffrement des données.

- Les *débits et portées de communication* sont des éléments clés dans la conception des nœuds. Augmenter la portée et le débit a cependant un impact significatif sur la consommation de puissance des partie radio et calcul.

- La *charge de calcul* est une autre métrique clé qui influence directement la consommation d'énergie du dispositif. Cependant, augmenter la puissance de calcul peut aussi permettre de réduire l'énergie du sous-système radio.

- Le *coût et la taille* de chaque nœud a un impact direct et significatif sur la facilité et le coût du déploiement du réseau de capteurs complet ainsi que sur la capacité de la source d'énergie disponible sur les dispositifs.

Comme discuté précédemment, les réseaux de capteurs sont déployés en général en grand nombre et ils doivent donc être petits et peu coûteux. Dans le même temps, comme il n'est pas possible de les équiper avec de grande sources d'énergie voire d'accéder à un rechargement de cette source, la très faible consommation est donc

4 Résumé étendu

leur contrainte majeure de conception. De plus, sachant que les nœuds sont inactifs ou en attente pendant la majeure partie de leur durée de vie (rapport cyclique de fonctionnement inférieur à 1%), l'énergie induite par les pertes statiques des composants (courants de fuite) doit être plus particulièrement réduite.

Si le profil de consommation d'un nœud de capteur est analysé sur l'ensemble de ses sous-systèmes, les blocs de communication et de calcul représentent bien sur la majeure partie du budget énergétique [116, 30]. Dans ce travail de thèse, nous ciblons par conséquent l'optimisation de la consommation des sous-systèmes de contrôle et de calcul. En effet, nous soutenons que les gains en énergie ou en puissance obtenus par notre approche sur ces blocs ouvrent des possibilités vers des protocoles de communication ou schémas de modulation plus complexes et plus coûteux en termes de puissance de calcul, ce qui, au final, permettra de fournir une meilleure qualité de service, une puissance radio plus faible et une meilleure efficacité d'utilisation de la bande passante du réseau. La réduction de puissance des sous-systèmes de contrôle et de calcul peut bénéficier d'optimisations à différents niveaux de conception du dispositif, tels que le niveau application, la micro-architecture ou le niveau de conception de circuits VLSI (Very Large Scale Integrated).

Dans les paragraphes suivants, nous présentons et discutons les techniques de réduction de la consommation adaptées au domaine des réseaux de capteurs i.e. micro-architecture et conception VLSI.

# 0.2 Optimisation de puissance d'un nœud de capteur

Depuis un peu plus d'une décennie, les problèmes d'estimation de réduction de la consommation électrique dans les circuits VLSI sont l'objet d'un grand nombre de travaux de recherche. Une grand partie de ces travaux se sont notamment intéressés à la conception de microarchitectures faible consommation pour microcontrôleurs embarqués. Cette section a pour objectif d'offrir au lecteur une synthèse des techniques utilisées dans ce domaine.

#### 0.2.1 Conception VLSI orientée faible consommation

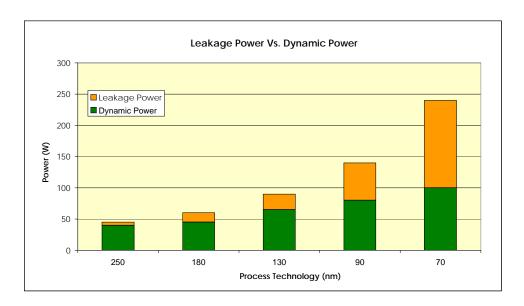

La consommation électrique dans un circuit VLSI découle de deux phénomènes: la puissance dynamique, provoquée par les charges et décharges des capacités (découlant des changements d'états du circuit) et la puissance statique causée par les courants de fuites entre la tension d'alimentation et la masse.

Quand un circuit est en mode actif, la puissance qu'il dissipe est très largement dominée par sa composante dynamique, et peut-être considérée comme étant approximativement proportionnelle à sa fréquence d'horloge. Pour les réseaux de capteurs, les choses sont assez différentes car les nœuds peuvent rester inactifs pendant de longue périodes (taux d'activité souvent inférieur à 1%). Dans ce contexte, il n'est plus raisonnable d'ignorer la contribution de la puissance statique dans le bilan énergétique global.

Il existe de nombreuses techniques permettant de réduire la puissance dynamique dans un circuit (*clock gating*, contrôle de la tension d'alimentation, etc.), celles-ci pou-

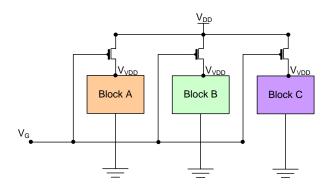

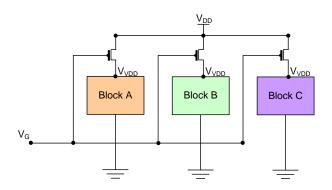

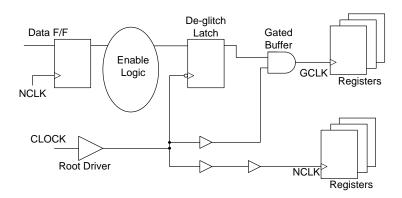

Figure 2: Un exemple d'utilisation du power gating.

vant être appliquées à différents étapes du flot de conception. La plupart d'entre elles sont cependant peu adaptées au contexte des réseaux de capteurs car elles ont souvent pour effet secondaire d'augmenter le nombre de transistors du circuit, augmentant ainsi indirectement sa puissance statique, avec un bilan global pouvant de fait devenir négatif.

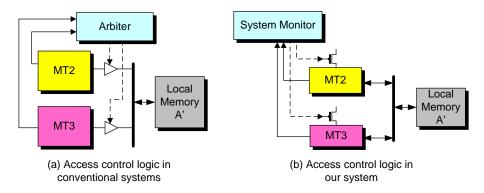

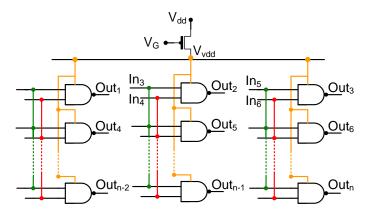

La technique de la coupure des alimentations – ou power gating –, dont le principe consiste à couper l'alimentation d'un composant inactif [12, 87], est toutefois une exception à cette règle. Le power gating, si utilisé à bon escient, permet donc de réduire de fait à la fois la puissance dynamique et la puissance statique, ce qui en fait une technique particulièrement attrayante pour des circuits dont les périodes d'activité sont limitées.

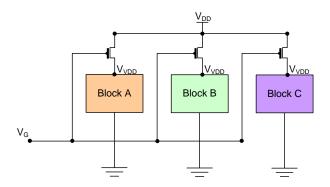

La technique consiste à ajouter un sleep transistor entre la source d'alimentation  $V_{DD}$  globale et celle du composant, créant ainsi une alimentation virtuelle notée  $V_{VDD}$ , comme illustré sur la figure 2. Ce sleep transistor, lorsqu'il est ouvert, permet de réduire les courants de fuites du composant à leurs niveaux minimums

### 0.2.2 Microcontrôleurs faible consommation

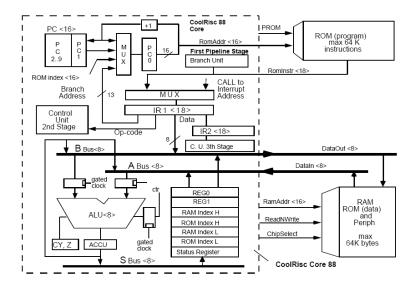

Les microcontrôleurs à très faible consommation actuellement disponibles sur le marché (e.g. MSP430, CoolRISC and ATmega128L) partagent de très nombreuses caractéristiques : un chemin de données simple (8/16-bits), un faible nombre d'instructions (seulement 27 instructions pour le MSP430), et surtout de nombreux modes de fonctionnement qui permettent d'adapter dynamiquement le comportement du processeur en jouant sur des compromis entre gain en consommation et réactivité. Ces processeurs sont conçus pour une gamme d'application assez large et ne sont donc pas spécifiquement conçus pour des réseaux de capteurs. De fait, parce qu'il sont conçus sur la base d'un micro-architecture généraliste et monolithique, ils ne sont pas forcement bien adaptés à la nature très particulière (basée événements) de la charge de calcul de ces nœuds.

La plupart des plateformes matérielles utilisées dans des infrastructures de réseaux de capteurs utilisent des processeurs commerciaux de ce type. Par exemple, la plate6 Résumé étendu

forme Mica2 [25], qui a été très largement utilisée par la communauté, est basée sur un microcontrôleur ATmega128L de la société Atmel. Le même contrôleur a également été utilisé par les concepteurs de la plateforme eXtreme Scale Mote (XSM) [30]. Les autres plateformes (Hydrowatch [39], PowWow [64]) utilisent quand à elles des processeurs MSP430 [129] de la société Texas Instruments, tandis que la plateforme WiseNet est basée sur un processeur CoolRISC [33] de la société EM Microelectronic.

Bien que les niveaux de puissance dynamique relevés (et plus particulièrement en Joules/instruction) pour ces processeurs puissent sembler extrêmement faibles au regard de processeurs embarqués plus classiques (ex: MSP430), ces gains nous semblent cependant loin de ce qui pourrait être obtenu en combinant des approches exploitant la spécialisation et le parallélisme.

Le problème de ces approches est qu'elles impliquent des surcoût importants en termes de coût silicium, qui eux-mêmes induisent des niveaux de puissance statique in-acceptables pour des applications de type réseaux de capteurs. Dans la section suivante, nous proposons donc une approche qui exploite la spécialisation en vue d'améliorer les niveaux de puissance dynamique dissipés, tout en contrôlant très finement le niveau de puissance statique en utilisant la technique de power-gating.

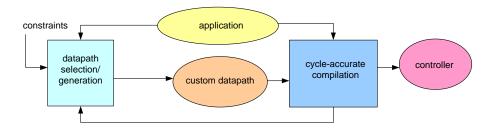

# 0.3 Une approche combinant power gating et spécialisation

Nous pensons qu'une approche à base de spécialisation matérielle offre une piste intéressante pour améliorer l'efficacité énergétique des parties calcul et contrôle embarquées dans un nœud de réseau de capteurs. Plutôt que d'exécuter l'applicatif et le système d'exploitation sur un processeur programmable, nous proposons de générer automatiquement, pour chacune des tâches du système, une micro-architecture matérielle taillée sur mesure. Une telle approche permet une réduction drastique de la puissance dynamique dissipée par chaque nœud. De plus, lorsque combinée avec des techniques de power gating, elle permet également de maitriser le niveau de puissance statique.

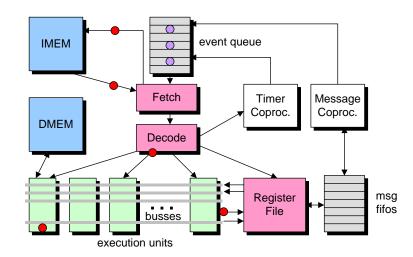

Dans notre approche, l'architecture matérielle du calculateur embarqué dans le nœud consiste en un ensemble de *micro-tâches* matérielles fonctionnant de manière concurrente, et activées en fonction de l'arrivé de tel ou tel événement.

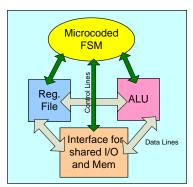

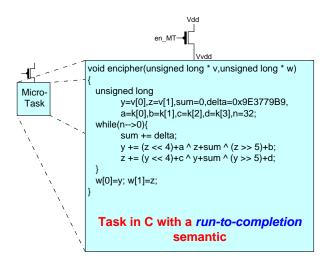

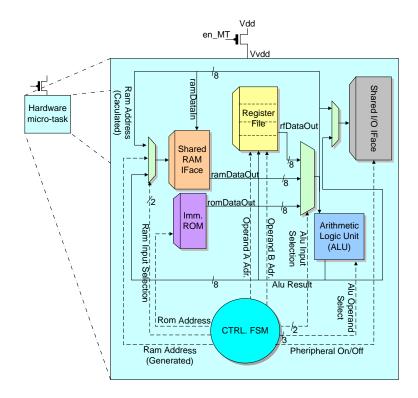

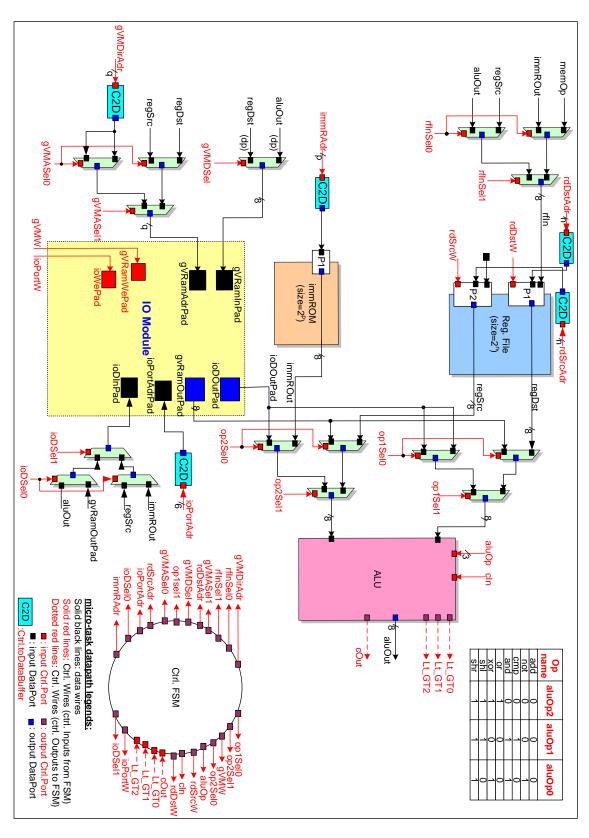

Chacune de ces micro-tâches est chargée d'une fonctionnalité bien définie (interfaçage avec les capteurs, contrôleur MAC, routage, etc.), et est mise en œuvre sur une micro-architecture minimaliste, organisée autour d'un chemin de données dédié lui-même contrôlé par une machine à états. Cette micro-architecture est générée directement à partir d'une spécification de son comportement en C, grâce à l'adaptation d'un flot de compilation reciblable pour processeur spécialisé ASIP et d'un outil de génération de description RTL dédié à ce type d'architectures.

En combinant la spécialisation matérielle avec des techniques de réduction de puissance statique (power gating), nous pouvons réduire de manière très significative la puissance globale (et l'énergie) dissipée par le système [103].

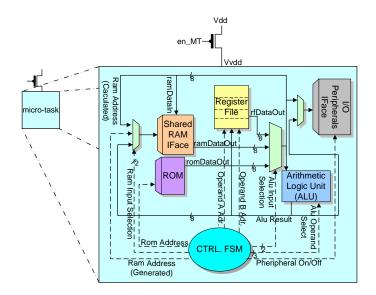

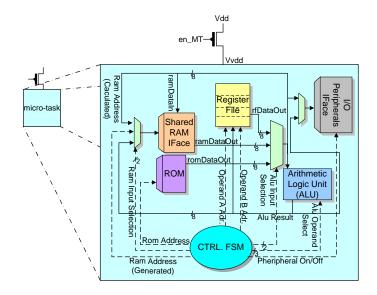

Figure 3: Architecture d'une micro-tâche matérielle generique.

#### 0.3.1 Micro-tâches matérielles

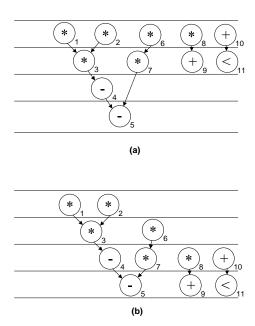

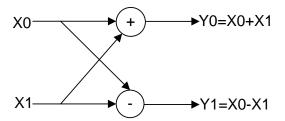

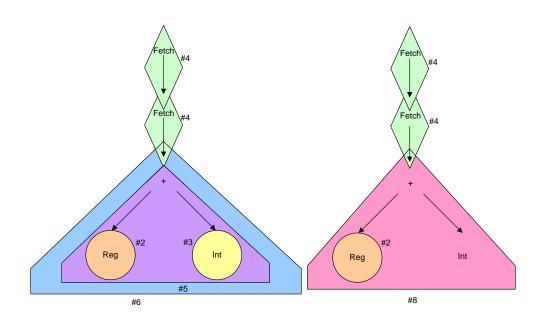

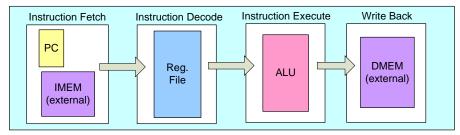

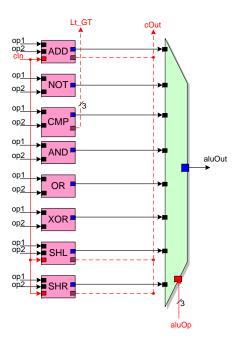

Notre approche repose sur cette notion de micro-tâche matérielle spécialisée, qui exécute une partie des traitements du nœud. A la différence d'un processeur à jeu d'instructions, la fonctionnalité d'une micro-tâche est figée et mise en œuvre sous la forme d'une machine à états pilotant un chemin de données spécialisé. Cette mise en œuvre rend l'architecture beaucoup plus compacte (pas besoin de décodeur d'instructions, pas de mémoire de programme, etc.) et permet de dimensionner précisément tant les ressources de stockage (file de registres, ROM, RAM) que les ressources de calcul (ALU simplifiée en fonction des calculs mis en œuvre par la micro-tâche).

Chacune de ces micro-tâches peut accéder à une mémoire de données (éventuellement partagée avec d'autres tâches) ainsi qu'à des périphériques au travers d'un bus d'E/S (ex: SPI link vers un émetteur RF tel que le CC2420 [131]).

La figure 3 représente la micro-architecture d'une tâche matérielle (ici avec un chemin de données sur 8 bits). Les lignes en pointillé représentent les signaux de contrôle générés par la machine à états de contrôle, tandis que les lignes en trait continu représentent le flot de données entre les opérateurs, les ressources de stockage, etc. Une description plus détaillée de l'organisation d'une micro-tâche matérielle sera donnée en section 4.1.2.

## 0.3.2 Modèle au niveau système proposé

Dans cette sous-section, nous détaillons l'architecture système d'un nœud basé sur le principe de micro-tâches, dont le fonctionnement est illustré dans les paragraphes qui suivent au travers d'un exemple d'application très simple (mesure et transmission de température).

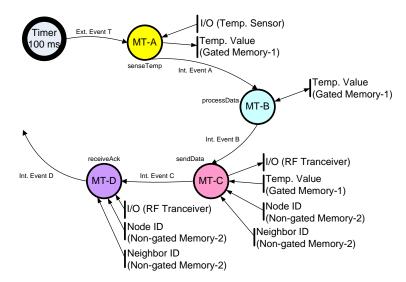

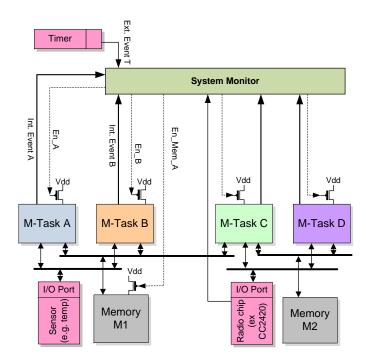

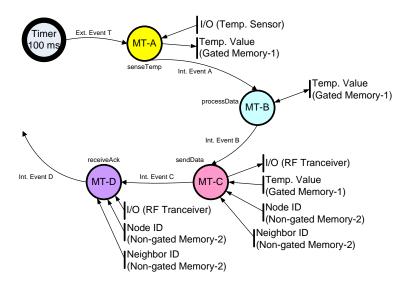

Figure 4: Graphe de tâches d'une application de relevé et envoi de température.

## Graphe de tâche de l'application

Considérons une application dans laquelle nous devons : lire à intervalle régulier la mesure de température effectuée par un capteur au travers de son interface d'E/S, analyser et traiter cette valeur, l'envoyer au nœud voisin, puis enfin recevoir un acquittement de ce même voisin. Le graphe de tâche de cette application est représenté figure 4 et consiste en un ensemble de quatre micro-tâches qui echangent des données brutes et des données de contrôle.

#### Architecture

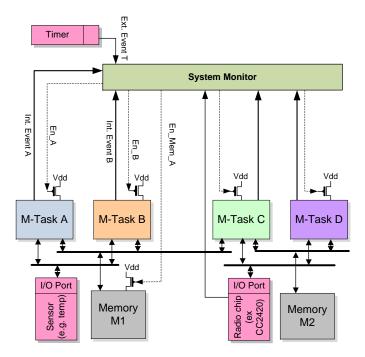

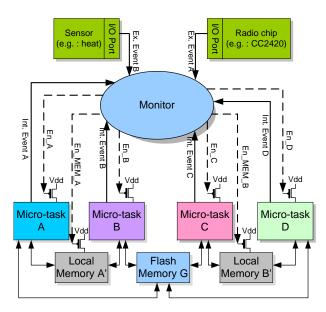

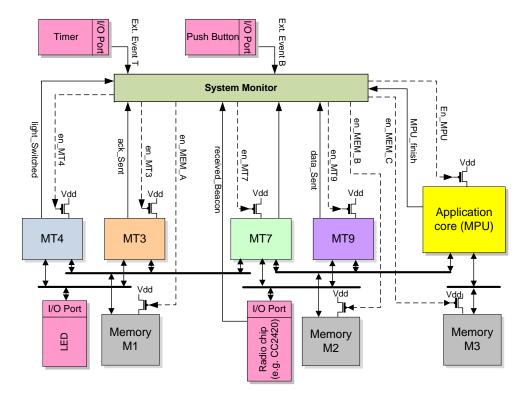

Le figure 5 représente une vue système d'une plateforme matérielle basée sur l'approche *micro-tâche*, et dont l'application cible (graphe de tâches) est celle proposée plus haut. Un tel système est formé:

- d'un ensemble de *micro-tâches* matérielles, contrôlées par un mécanisme de *power gating*, et qui accèdent à un ensemble de ressources partagées (RF, capteurs) et mémoires (gated/non-gated). Chacune de ces micro-tâches étant chargée d'une tâche spécifique (mesure de températuren traitement de données, etc.);

- d'un moniteur système (SM) qui contrôle l'activation de toutes les micro-tâches matérielles. Le moniteur système est chargé du contrôle de l'alimentation de toutes les micro-taches ainsi que des mémoires en fonction de leur utilisation;

- des périphériques capables de déclencher des événements (radio, timer, etc.) qui seront transmis au moniteur système.

Figure 5: Vue niveau système d'un nœud de capteur basé sur l'approche à base de micro-tâches matérielles.

# Fonctionnement d'un nœud de capteur basé sur l'approche micro-tâches matérielles

L'interaction entre le moniteur système (SM) et les micro-tâches matérielles reste relativement simple. Le SM échange des informations de contrôle avec chaque micro-tâche, au travers de signaux de contrôle (comme par exemple les signaux  $En\_A, En\_B, En\_Mem\_1$ , etc., représentés figure 1.5), de signaux d'événements internes (Int. Event A, Int. Event B etc., comme indiqué figure 1.5) et d'événements externes, issus des périphériques (Ext. Event T, etc.).

A titre d'exemple nous détaillons ci-dessous le comportement du système mettant en œuvre l'exemple du graphe de tâches de la figure 4.

- Tout d'abord le SM détecte que l'événement externe Ext. Event T vient de se produire, et envoie un signal de réveil à la micro-tâche M-Task A au travers la commande En\_A ainsi qu'à la mémoire Memory 1 (non alimentée à cet instant) au travers de la commande En\_Mem\_1. Une fois M-Task A réveillée, celle-ci va interroger le capteur de température en y accédant au travers de son bus d'E/S. Une fois lue et traité, cette valeur sera stockée dans la mémoire Memory 1, la micro-tâche M-Task A envoie alors au SM un événement interne Int. Event A lui indiquant qu'elle a terminé son travail.

- A la reception du signal Int. Event A, le SM coupe l'alimentation de M-Task A

10 Résumé étendu

en désactivant la commande  $En\_A$ , et réveille la micro-tâche M- $Task\,B$  qui est en charge de la seconde tâche du graphe de tâches de la figure 4, et dont le rôle est de réaliser un traitement sur la température précédemment relevée et stockée dans  $Memory\,1$ , puis de réécrire la valeur modifiée en lieu et place de la précédente valeur en mémoire. La tâche M- $Task\,B$  envoie alors un événement interne  $Int.Event\,B$  au SM pour lui indiquer qu'à son tour elle a terminé son travail.

- A la réception du signal Int.Event B, le SM coupe l'alimentation de M-Task B et réveille la micro-tâche M-Task C dont le rôle est de transmette la donnée stockée en Memory 1 au nœud le plus proche. Pour réaliser cette tâche M-Task C a également besoin de la mémoire permanente Memory 2 utilisée par le nœud pour stocker son identifiant (ID) ainsi que sa table de routage. M-Task C effectue alors un calcul de voisinage et envoie un paquet au plus proche voisin en accédant au composant radio par son interface SPI. M-Task C envoie à son tour un évenement interne Int.Event C au SM pour lui indiquer qu'elle a terminé son travail.

- Lorsqu'il reçoit  $Int.Event\ C$ , le MS coupe l'alimentation de  $MTask\ C$  à l'aide de la commande  $En\_C$  et réveille la tâche M- $Task\ D$  chargée de la réception de l'acquittement du message par le voisin. Puisque  $Memory\ 1$  n'est pas nécessaire à l'exécution de M- $Task\ D$ , elle est également désactivée par le SM grâce à la commande  $En\_Mem\_1$  line. Finalement, une fois l'acquittement reçu par le nœud, à l'issue de l'exécution de M- $Task\ D$ , le SM coupe l'alimentation de la quatrième et dernière tâche de l'application (sur réception de l'événement interne  $Int.Event\ D$ ). De fait, l'ensemble des composants de la plateforme (à l'exception du SM et de la mémoire  $Memory\ 2$ ) n'est plus alimenté. La puissance statique du système est alors réduite à son minimum.

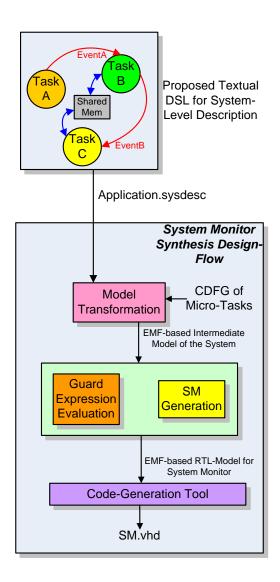

## 0.3.3 Modèle d'exécution et flot de conception logiciel

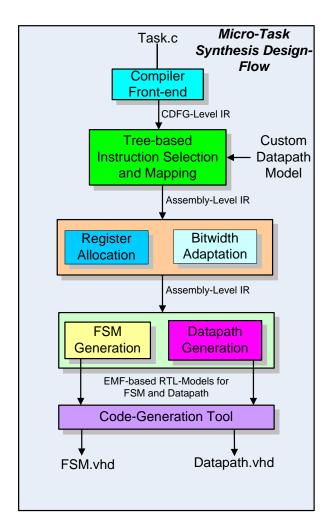

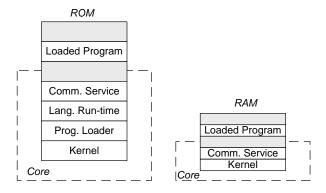

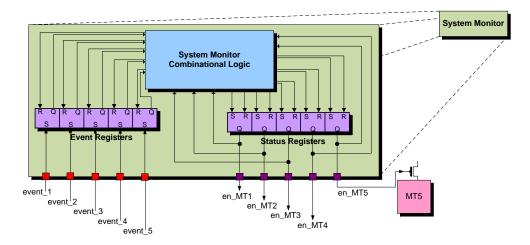

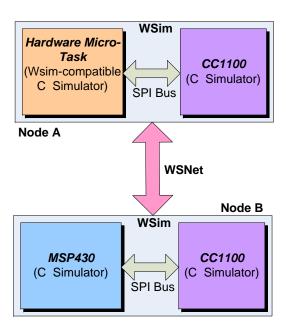

Une grade partie de ce travail de thèse a porté sur le développement de l'outil LoMiTa (ultra Low-power Micro-Tasking), un flot complet de conception pour plateformes matérielles dédiées [104, 105]. S'inspirant de la plupart des infrastructures pour réseaux de capteurs, ce flot se base sur l'utilisation d'un langage dédié pour la spécification système (interactions entre les tâches, gestion des événements, gestion des ressources partagées) et sur la spécification du comportement des tâche en langage C-ANSI. A partir de ces spécifications, nous sommes capables de générer du VHDL synthétisable de la plateforme dans son ensemble (micro-tâches + moniteur système), permettant une implantation directe sur ASIC ou FPGA.

Il nous semble important de préciser que notre but n'est pas de proposer un nouveau modèle de calcul pour des plate-formes de réseau de capteurs, notre approche se veut plutôt comme proposant un modèle d'exécution simple, qui soit bien adapté à ce que nous pensons être une solution architecturale innovante pour les nœuds d'un réseau de capteurs.

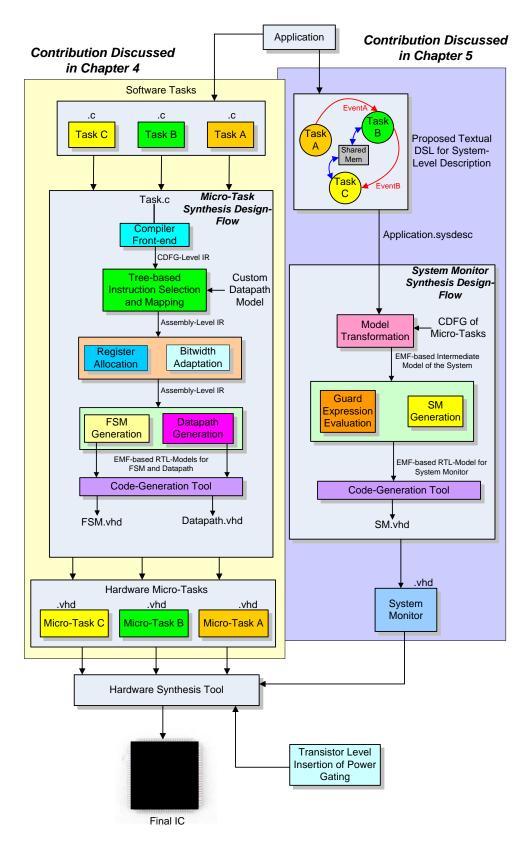

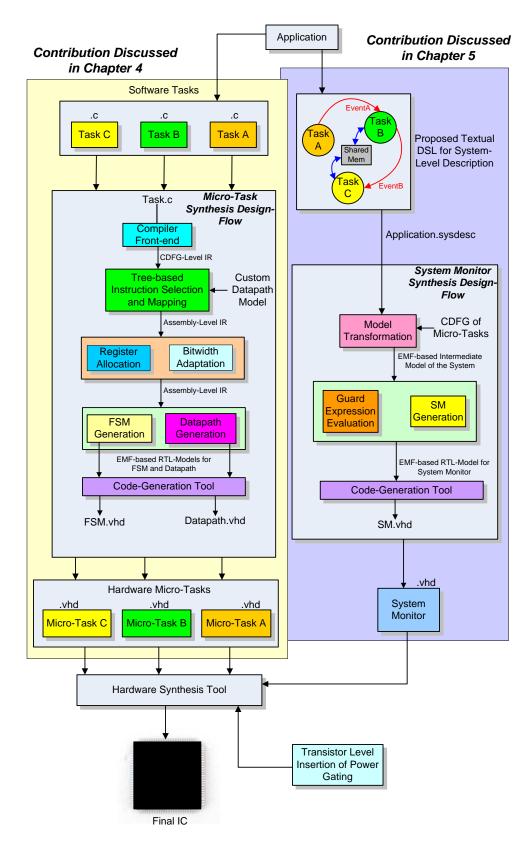

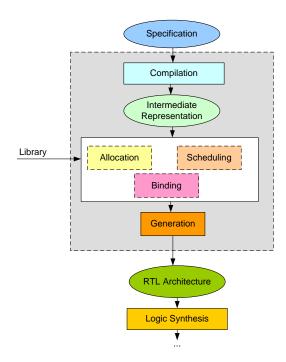

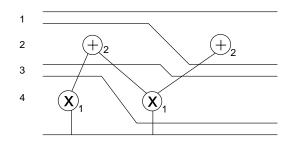

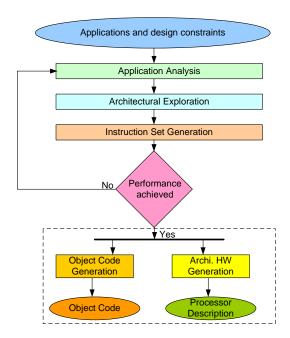

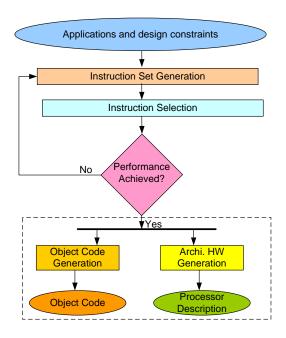

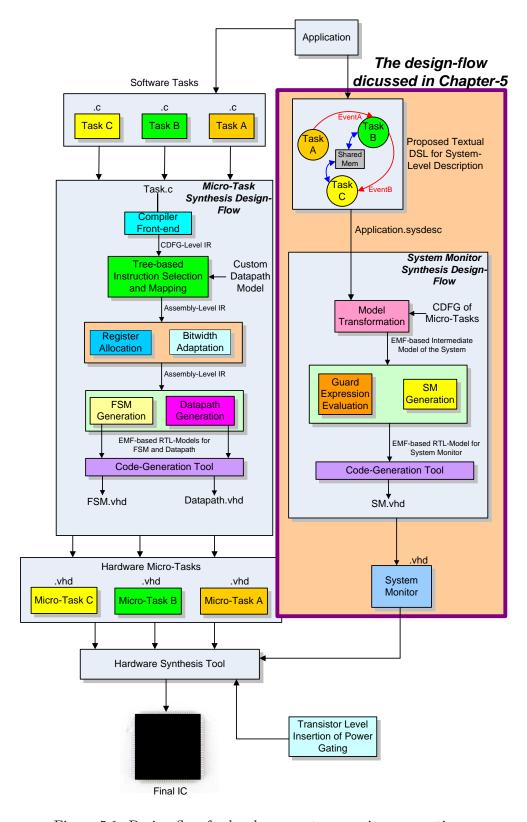

Nous présentons ci-dessous une vue globale de notre flot de conception à base de micro-tâches, celui-ci peut se décomposer en deux parties (c.f. figure 6):

- un outil de synthèse de matériel qui est utilisé pour générer la spécification VHDL de la micro-tâche à partir de sa spécification en ANSI-C;

- Un flot système qui se sert d'une spécification de la plate-forme et de son graphe de tâches (exprimé à l'aide d'un langage dédié) et génère la description VHDL du moniteur système.

La mise en oeuvre de notre flot de conception exploite les outils et principes du Model Driven Engineering (MDE), et plus particulièrement de l'infrastructure Eclipse Modeling Framework (EMF) [134], ainsi que les nombreux outils et technologies qui lui sont associés.

Nous avons ainsi défini un méta-modèle pour décrire et manipuler des microarchitectures spécifiées au niveau RTL sous la forme de machine à états commandant des chemins de données (modèle FSM+Datapath). Ce méta-modèle est ensuite utilisé pour générer le code VHDL et SystemC des microarchitectures ainsi modélisées. En complément de ce méta-modèle, nous avons également utilisé les possibilités de l'outil MDE Xtext pour définir un langage dédié dont le but est de faciliter la spécification au niveau système de la plateforme (tâche, E/S, mémoires, etc.).

12 Résumé étendu

Figure 6: Flot de conception système LoMiTa

Contributions 13

#### 0.4 Contributions

Les contributions de cette thèse sont décrites ci dessous.

• Nous proposons un flot de conception original pour la génération de plateformes matérielles pour réseaux de capteurs très faible consommation. Ce flot se base sur la notion de micro-tâche matérielle et permet la génération d'une description d'une plate-forme complète. Dans ce flot, le comportement de chaque tâche est spécifié an C ANSI et est mappé sur une micro-architecture dédiée, grâce à une version adaptée d'un compilateur reciblable.

- Nous montrons également dans cette approche que les techniques à base de power gating permettent d'obtenir des temps de commutation très courts, de l'ordre de quelques dixièmes de miro-secondes, et ce même pour des micro-tâches de taille importante. Ces propriétés permettent d'améliorer le temps de réponse d'au minimum 50% par rapport à des solutions basées sur des microcontrôleurs de type MSP430.

- Nous proposons également un langage dédié (DSL) qui peut-être utilisé pour spécifier la vue système de la plateforme et qui permet de générer une description synthétisable de l'ensemble du système et en particulier le moniteur système qui est utilisée pour contrôler l'activation et la désactivation des micro-tâches matérielles.

- Notre approche permet d'obtenir des gains en puissance dynamique d'environ deux ordres de grandeur par rapport à des solution existantes à base de micro-contrôleurs programmables.

- Nous avons utilisé notre flot de conception pour effectuer une étape d'exploration de l'espace de conception dans le but d'évaluer les différents compromis en surface/performance pouvant être obtenus en modifiant certains paramètres de la micro-architecture, et en particulier la largeur du chemin de données. Là encore nous avons comparé les résultats obtenus avec ceux obtenus pour une microcontrôleur comme le MSP430.

- Nous avons validé notre flot sur une application simple (mais réaliste) et montré que l'approche était tout à fait appropriée au domaine applicatif des réseaux de capteurs.

# 0.5 Résultats expérimentaux

Cette section présente l'ensemble des expérimentations effectuées et les résultats obtenus. Après une description des gains obtenus en termes de temps de réponse et de réveil de notre technique de *power gating* à grain fin, nous présentons les réductions de puissances dynamique et statique obtenus par notre concept de micro-tâches matérielles, en les comparant avec des implémentations à base de microcontrôleurs. Finalement, le

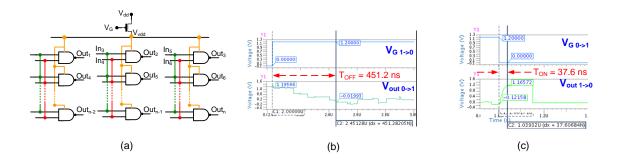

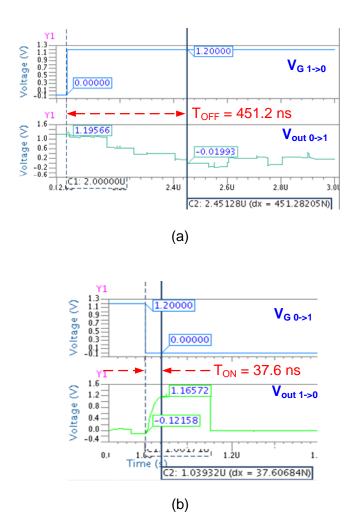

Figure 7: Modèle à base de portes NAND parallèles utilisé pour exécuter les simulations au niveau transistor à l'aide de SPICE et temps de réveil et de mise en veille mesurés pour n=3000.

coût en surface et le gain en puissance statique du système complet est analysé via la synthèse du moniteur système. Tous ces résultats sont obtenus en utilisant notre flot de conception complet, tel que proposé et développé dans cette thèse.

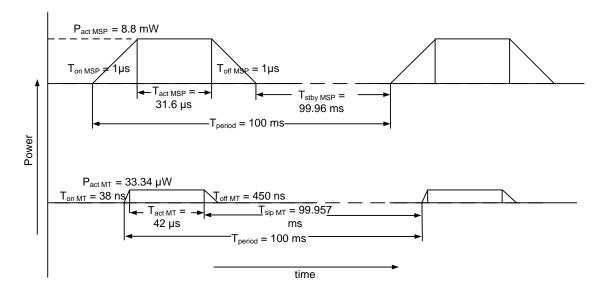

## 0.5.1 Temps de commutation du power gating

Pour vérifier l'applicabilité du *power gating* dans l'architecture que nous proposons, nous utilisons un modèle similaire à celui utilisé par Hu et al. [59]. Cependant, comme les auteurs ne donnent pas de valeurs quantitatives des temps de commutation pour une technologie CMOS spécifique, nous avons accompli plusieurs expérimentations.

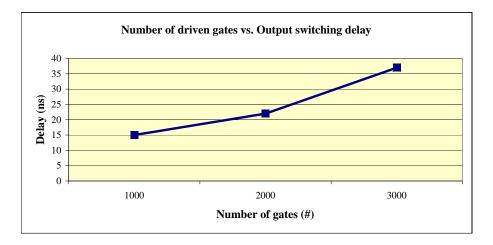

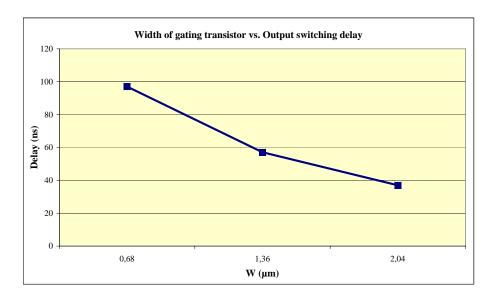

Pour cela, l'outil *Eldo* de Mentor Graphics a été utilisé pour les simulations SPICE avec une technologie CMOS 130 nm et une tension d'alimentation de 1.2 V. Nous avons utilisé un modèle à base de portes NAND parallèles (cf. figure 7 (a)). Un bloc logique de 3000 portes équivalentes, comparable en termes de surface de silicium avec la plus complexe des micro-tâches présentes dans notre système, a été simulé. Les figures 7 b et 7 c) montrent de temps d'allumage (réveil) de 37.6 ns et de coupure (mise en veille) de 451 ns entre les modes "éteint" et "actif". Ces temps doivent être comparés avec ceux du MSP430 qui offre un temps de réveil de 1  $\mu$ s [129]. Ceci montre que le *power gating* est applicable dans notre système et une réduction de plus de 50% du temps de réveil peut être gagnée par rapport aux implémentations à base de microcontrôleurs.

## 0.5.2 Gains en puissance dynamique de l'approche à base de microtâches

Pour explorer les gains en consommation de notre approche, plusieurs tâches applicatives représentatives ont été extraites de benchmarks récents en réseaux de capteurs, tels que SenseBench [97] et WiSeNBench [96]. De plus, pour couvrir les applications orientées contrôle, plusieurs tâches de gestion des réseaux de capteurs dans un système d'exploitation ont été utilisées: calcul de l'adresse du prochain nœud dans un protocole de routage géographique multi-sauts (calcNeigh), protocole de transfert sur

|              |        |        |           | MSP   | 430     |       |         |

|--------------|--------|--------|-----------|-------|---------|-------|---------|

| Nom          | Nb.    | Cycles | Temps     | Pu    | issance | Eı    | nergie  |

| Tâche        | Instr. | Horl.  | $(\mu s)$ | (1    | mW)     |       | (nJ)    |

|              |        |        |           | tiMSP | openMSP | tiMSP | openMSP |

| crc8         | 30     | 81     | 5.1       | 8.8   | 0.96    | 44.9  | 4.9     |

| crc16        | 27     | 77     | 4.8       | 8.8   | 0.96    | 42.2  | 4.6     |

| tea-decipher | 152    | 441    | 27.5      | 8.8   | 0.96    | 242   | 26.4    |

| tea-encipher | 149    | 433    | 27.0      | 8.8   | 0.96    | 237.6 | 26      |

| fir          | 58     | 175    | 10.9      | 8.8   | 0.96    | 96    | 10.4    |

| calcNeigh    | 110    | 324    | 20.2      | 8.8   | 0.96    | 177.7 | 19.4    |

| sendFrame    | 132    | 506    | 31.6      | 8.8   | 0.96    | 278   | 30.3    |

| receiveFrame | 66     | 255    | 15.9      | 8.8   | 0.96    | 139.9 | 15.2    |

Table 1: Consommation de puissance et d'énergie du MSP430 pour différentes tâches applicatives issues de benchmarks (@ 16 MHz).

bus SPI pour interfaçage avec un composant radio tel que le CC2420 (sendFrame et receiveFrame). Toutes ces tâches sont traitées via notre flot de conception qui génère les descriptions matérielles correspondantes aux micro-tâches.

Une technologie CMOS 130 nm et une tension d'alimentation de 1.2 V sont utilisées pour les résultats de synthèse. Les estimations de consommation statique et dynamique résultent d'une simulation au niveau portes à une fréquence d'horloge de 16 MHz. Les puissances estimées sont comparées avec celles dissipées par (i) tiMSP: un microcontrôleur MSP430F21x2 dont les informations sont extraites depuis la datasheet constructeur (8.8 mW @ 16 MHz en mode actif), ce qui inclut les mémoires et les périphériques, et (ii) openMSP, une version open-source du MSP430 (0.96 mW @ 16 MHz) synthétisée dans la même technologie 130 nm et n'incluant que le cœur et aucune mémoire ni périphérique.

Nous escomptons que la puissance dissipée réelle du cœur du MSP430 associé à sa mémoire programme se trouve entre ces deux résulats et faisons donc la comparaison avec ces deux versions.

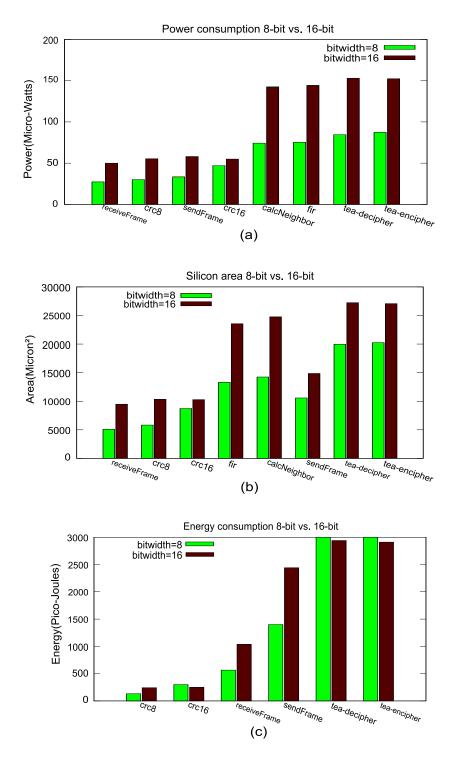

Les résultats sont donnés dans les tableaux 1 à 3 où le tableau 1 donne le nombre de cycles et d'instructions pour les deux versions du MSP430 MCU. Les tableaux 2 et 3 montrent quant à eux les gains en puissance et en énergie obtenus par notre architecture à base de micro-tâches matérielles pour des chemins de données de 8 et 16 bits respectivement. On observe que notre approche obtient des gains en énergie entre un et deux ordres de grandeur pour les différents benchmarks.

En ce qui concerne la puissance statique, les micro-tâches consomment en moyenne 6 octets de mémoire. Quand cette mémoire est synthétisée dans une technologie 130 nm (sans optimisation spécifique), elle consomme seulement  $18\,\mathrm{nW}$  de puissance statique. Par opposition, le MSP430 consommant approximativement  $1.54\,\mu\mathrm{W}$  en statique, notre approche permet de gagner un rapport d'environ un ordre de grandeur en consommation statique par rapport aux implémentations à base de microcontrôleurs.

|              | Micro-tâches 8-bits |           |           |         |           |            |                      |             |  |

|--------------|---------------------|-----------|-----------|---------|-----------|------------|----------------------|-------------|--|

| Nom          | Nb.                 | Temps     | Puissance | Energie | Gain P.   | Gain E.    | Surface              | Nb. portes  |  |

| Tâche        | Etats               | $(\mu s)$ | $(\mu W)$ | (pJ)    | (x) P1/P2 | (x) E1/E2  | $(\mu \mathrm{m}^2)$ | Nand equiv. |  |

| crc8         | 71                  | 4.4       | 30.09     | 132.4   | 292/32    | 339/37     | 5831.7               | 730         |  |

| crc16        | 103                 | 6.4       | 46.92     | 300.3   | 187/20.4  | 140.5/15.3 | 8732.5               | 1092        |  |

| tea-decipher | 586                 | 36.6      | 84.5      | 3090    | 104/11.4  | 78/8.55    | 19950                | 2494        |  |

| tea-encipher | 580                 | 36.2      | 87.3      | 3160    | 101/11    | 75/8.2     | 20248                | 2531        |  |

| fir          | 165                 | 10.3      | 75.3      | 775.6   | 116/12.8  | 123.8/13.4 | 13323.7              | 1666        |  |

| calcNeigh    | 269                 | 16.8      | 74.3      | 1248.2  | 118/12.9  | 142.4/15.5 | 14239.4              | 1780        |  |

| sendFrame    | 672                 | 42        | 33.3      | 1400.3  | 264/28.8  | 198.5/21.7 | 10578                | 1323        |  |

| receiveFrame | 332                 | 20.7      | 27.3      | 565     | 322/35    | 247.6/26.7 | 5075.3               | 635         |  |

Table 2: Gain en puissance et en énergie pour des micro-tâches 8 bits par rapport au MSP430 (@ 16 MHz, 130 nm). P1 et E1 sont les gains en puissance et en énergie par rapport à la version tiMSP tandis que P2 et E2 sont les gains en puissance et en énergie par rapport à la version openMSP.

|              | Micro-tâches 16 bits |           |           |         |            |            |                      |             |  |

|--------------|----------------------|-----------|-----------|---------|------------|------------|----------------------|-------------|--|

| Nom          | Nb.                  | Temps     | Puissance | Energie | Gain P.    | Gain E.    | Surface              | Nb. portes  |  |

| Tâche        | Etats                | $(\mu s)$ | $(\mu W)$ | (pJ)    | (x) P1/P2  | (x) E1/E2  | $(\mu \mathrm{m}^2)$ | Nand equiv. |  |

| crc8         | 71                   | 4.4       | 55.3      | 242.6   | 159.6/17.4 | 185.1/20.2 | 10348                | 1294        |  |

| crc16        | 73                   | 4.56      | 55.0      | 251.0   | 159.8/17.4 | 168.1/18.3 | 10280                | 1285        |  |

| tea-decipher | 308                  | 19.2      | 152.8     | 2940    | 57.6/6.2   | 82/9       | 27236                | 3405        |  |

| tea-encipher | 306                  | 19.1      | 152.3     | 2910    | 57.8/6.3   | 81/8.93    | 27069                | 3384        |  |

| fir          | 168                  | 10.5      | 144.2     | 1514    | 61.02/6.7  | 63.4/6.9   | 23547                | 2944        |  |

| calcNeigh    | 269                  | 16.8      | 142.4     | 2392    | 61.8/6.7   | 74.3/8.1   | 24745                | 3094        |  |

| sendFrame    | 672                  | 42        | 58.1      | 2440    | 151.5/16.5 | 114/12.4   | 14863                | 1858        |  |

| receiveFrame | 332                  | 20.7      | 50.0      | 1036    | 175.8/19.2 | 135/14.7   | 9485                 | 1183        |  |

Table 3: Gain en puissance et en énergie pour des micro-tâches 16 bits par rapport au MSP430 (@ 16 MHz, 130 nm). P1 et E1 sont les gains en puissance et en énergie par rapport à la version tiMSP tandis que P2 et E2 sont les gains en puissance et en énergie par rapport à la version openMSP.

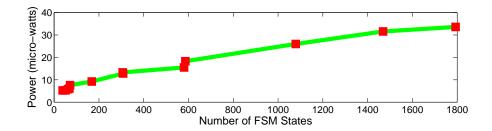

#### 0.5.3 Estimation de la consommation du moniteur système

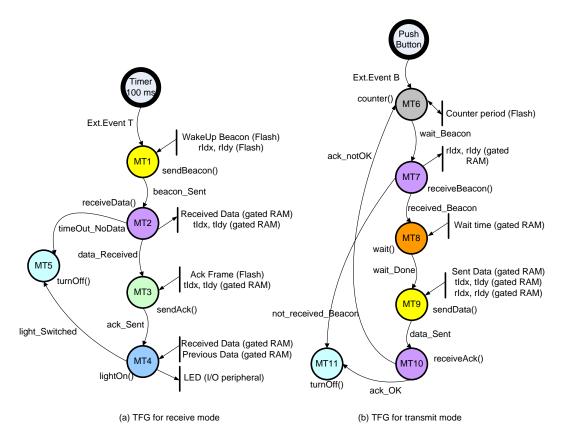

Pour comparer les consommations d'énergie et le potentiel surcoût en surface du moniteur système (SM), une description sous forme de graphe de tâches est présentée à la figure 4 et est exprimée à l'aide de notre DSL. Celui ci est ensuite traité avec notre flot de conception et une description VHDL du moniteur système qui contrôle l'activation et la désactivation des quatre micro-tâches et de la mémoire partagée est générée.

Ce code VHDL est ensuite synthétisé pour une bibliothèque de cellules CMOS standards en 130 nm afin d'obtenir les consommations statique et dynamique et le coût en surface de silicium. Les résultats montrent que le SM consomme  $5.15\,\mu\mathrm{W}$  de puissance dynamique (@ 16 MHz et  $1.2\,\mathrm{V}$ ) et 296 nW de puissance statique. La partie statique peut être réduite jusqu'à 80 nW si des cellules faible consommation alimentées à  $0.3\,\mathrm{V}$  sont utilisées pour les registres présents dans l'architecture. D'un point de vue de la surface de silicium, le SM consomme seulement  $754\,\mu\mathrm{m}^2$  (pour un graphe simple), soit environ 1% de la surface d'un cœur MSP430 synthétisé dans la même technologie.

En résumé, notre approche basée sur des micro-tâches matérielles fournit une réduction d'environ 50% dans les temps de commutation entre les modes de veille et d'activité, et des gains d'un à deux ordres de grandeur en énergie dynamique et d'un ordre de grandeur en énergie statique, par comparaison avec des implémentations logicielles sur des microcontrôleurs à très faible consommation tels que le MSP430.

# Chapter 1

# Introduction

## 1.1 Wireless Sensor Network (WSN)

Wireless Sensor Networks (WSNs) is a fast evolving technology having a number of potential applications in various domains of daily-life, such as structural-health and environmental monitoring, medicine, military surveillance, robotic explorations etc. Advancements in Micro-Electro-Mechanical-Systems (MEMS) technology, wireless communications, and digital electronics have facilitated the development of low-cost, low-power, multi-functional sensor nodes that are small in size and communicate efficiently over short distances. Thus the emerging field of WSN combines sensing, computation, and communication into a single tiny device (WSN node). WSN Systems of 1000s or even 10,000s of such nodes are anticipated that can revolutionize the way we live and work.

The core design challenge in WSN is coping with the harsh resource constraints placed on the individual node devices. Embedded processors controlling the WSN nodes have only kilo-Bytes of memory and they must implement complex networking protocols. Many constraints evolve from the fact that these devices will be produced in a large number and must be small and inexpensive. As Moore's law still remains applicable, we get nearly double the number of transistors in same surface area with newer process technology. This results in two scenarios (i) more functionalities can be added to a device for the same given area or (ii) size of the device gets smaller for the same given functionalities. This size reduction is also helpful for the devices to be produced as inexpensively as possible.

The most difficult resource constraint to meet is power consumption. As physical size decreases, so does energy capacity of a WSN node. Underlying energy constraints end up creating computational and storage limitations that lead to a new set of architectural issues. Many devices, such as cell phones and pagers, reduce their power consumption through the use of specialized communication hardware in Application Specific Integrated Circuits (ASICs) that provide low-power implementations of the necessary communication protocols.

To date, the strength of WSN systems is supposed to be their flexibility and uni-

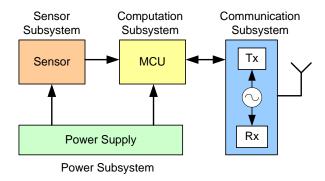

Figure 1.1: General architecture of a WSN node.

versality. However, when looking more carefully to actual design practices, we observe that the need for flexibility/programmability is essentially geared toward the user application layer, which happens to represent only a small fraction of a WSN node's processing workload. Whereas most of the processing workload is almost dedicated to the communication protocol stack. Hence, in our opinion, it is worth-studying to explore the hardware specialization approach in WSN node design as well to meet the ultra low-power requirement. In order to reduce the power consumption in a WSN node, we first need to look at the generic node architecture to find out the hotspots for power consumption. The generic architecture of a WSN node is discussed in the next section.

#### 1.1.1 WSN node architecture

WSN nodes are low-power embedded devices consisting of processing and storage components (a Microcontroller Unit (MCU) connected to a RAM and/or flash memory) combined with wireless communication capabilities (RF transceiver) and some sensors/actuators. Since these nodes must have small form-factors and limited production cost, it is not possible to provide them with large energy sources [138]. In most cases they must rely on non-replenishing (e.g. battery) or self-sufficient (e.g. solar cells) sources of energy.

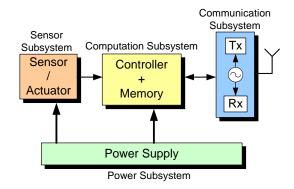

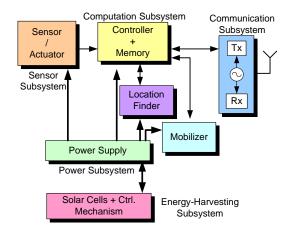

Figure 1.1 presents the system architecture of a generic sensor node. It is composed of four major subsystems: power supply, communication, control and computation, and sensing. The power supply subsystem consists of a battery and a DC-DC converter and has the purpose to power-up the node. The communication subsystem consists of a radio transceiver for wireless communication. Most of the platforms use a single omni-directional antenna however, cooperative "Multiple-Input and Multiple-Output (MIMO)" technology has also been deployed [99]. The processing subsystem is typically composed of memory to store application program codes and data, and of a microcontroller to control the system and process the data. The last subsystem links the sensor node to the region of interest and has a group of sensors and actuators that depend on the WSN application. It also has an Analog-to-Digital Converter (ADC) to

convert the analog data sensed by the sensors to digital data that can be used by the processing subsystem. To design such architecture with limited resources, the designers are faced with some tough constraints that are discussed in the following section.

#### 1.1.2 WSN node design constraints

Designing a WSN node is a challenging task, since the designers must deal with many stringent design constraints and metrics that are often interrelated. Here we will briefly discuss some of the metrics that are considered while designing a WSN node.

- **Power** is the biggest design challenge to meet while designing individual sensor nodes to implement the applications that require multi-year life-time.

- *Robustness* also becomes an important parameter in WSN node design to support correct functioning of the network. Each node must be designed to be as robust as possible to tolerate and adapt to neighborhood node failures.

- **Security** at application-level is another metric to be considered while designing a node. The individual nodes must be capable of performing relatively complex encryption and authentication algorithms.

- Communication bit-rate and range are key design metrics for a WSN node as well. An increase in the communication range (and bit-rate) has a significant impact on the power consumption (and computational requirement) of the node.

- Computation workload is another key design metric and it directly influences a node's power consumption. The more a node would be computationally-intensive, the more would be its overall power/energy budget.

- Cost and size The physical size and cost of each individual sensor node has a significant and direct impact on the ease and cost of deployment as well as the size of the energy source available to it.

As discussed earlier, since WSN nodes are deployed in huge numbers, they must be of small form-factor and inexpensive. Besides, it is not possible to equip them with large power sources. Hence, ultra low-power becomes the most critical design metric for a WSN node. It is also supported by the fact that WSN nodes may have to work unattended for long durations due to a large number of deployed nodes or a difficult access to them after deployment.

If we analyze the power profile of a WSN node, among all the subsystems (Section 1.1.1), communication and computation subsystems consume bulk of a node's available power-budget [116, 30]. In this work, we are targeting the power optimization of the computation and control subsystem of a WSN node. Indeed, we believe that power and energy savings obtained through our approach could open possibilities for more computationally demanding protocols or modulation schemes which, as a result, would provide better Quality-of-Service (QoS), lower transmission energy and higher

22 Introduction

network efficiency. Power reduction for computation and control subsystem can benefit from optimizations at several levels of a WSN node design (such as application design, micro-architecture design, logic synthesis and Very Large Scale Integrated (VLSI) circuit design).

We will discuss the power reduction techniques adapted at two different levels of a WSN node design, i.e. micro-architectural level and VLSI circuit level as they are the two levels targeted by our approach.

#### 1.2 Power optimization of a WSN node

In the last decade, there have been a large number of research results dealing with power optimization in VLSI circuits. A lot of research has also been done to optimize power at micro-architectural level such as evolution of low-power MCUs. This section briefly covers some of these power optimization techniques.

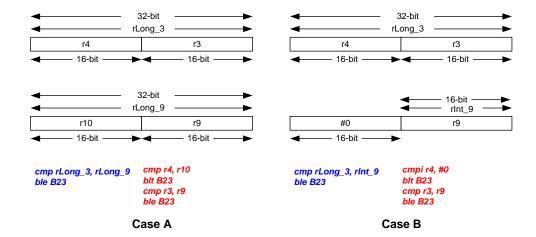

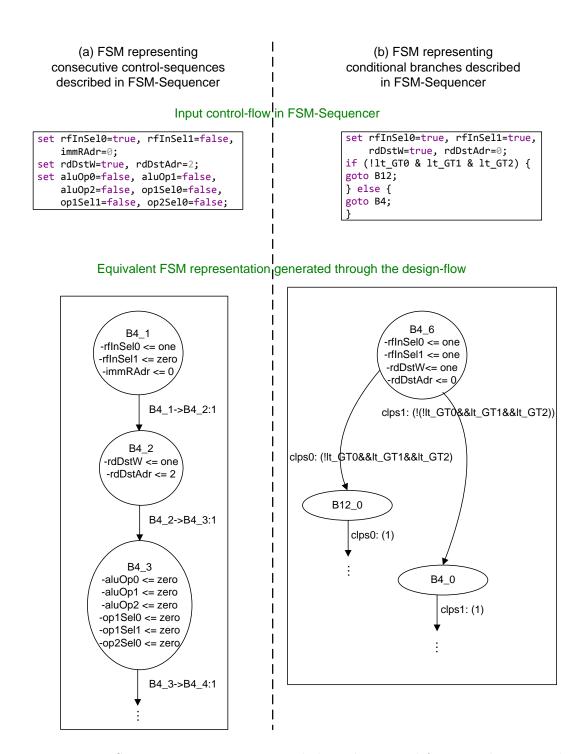

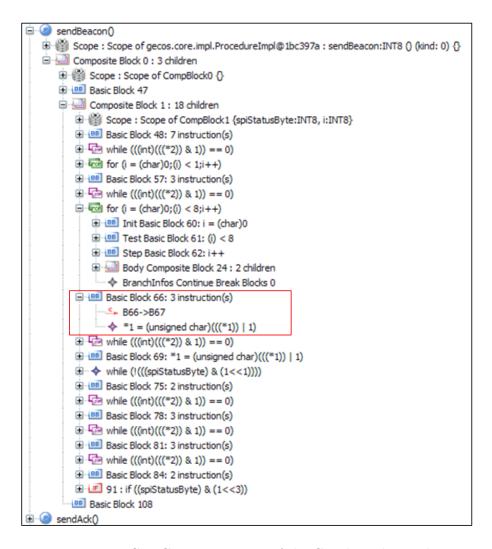

#### 1.2.1 Low-power VLSI design