### Blocs nuls dans la hiérarchie mémoire

Julien Dusser

### ▶ To cite this version:

Julien Dusser. Blocs nuls dans la hiérarchie mémoire. Réseaux et télécommunications [cs.NI]. Université Rennes 1, 2010. Français. NNT: . tel-00557080

### HAL Id: tel-00557080 https://theses.hal.science/tel-00557080

Submitted on 18 Jan 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

$N^{\circ}$  d'ordre : 4305 ANNÉE 2010

### THÈSE / UNIVERSITÉ DE RENNES I

sous le sceau de l'Université Européenne de Bretagne

pour le grade de

### DOCTEUR DE L'UNIVERSITÉ DE RENNES I

Mention: Informatique

École doctorale Matisse

présentée par

### Julien Dusser

préparée à l'unité de recherche IRISA, UMR6074 Institut de Recherche en Informatique et Systèmes Aléatoires IFSIC

## Blocs nuls dans la hiérarchie mémoire

# Thèse soutenue à Rennes le 16 décembre 2010

devant le jury composé de :

Olivier SENTIEYS / président Professeur à l'Université de Rennes I, ENSSAT – Lannion

Pascal SAINRAT / rapporteur Professeur à l'Université de Toulouse III, IRIT – Toulouse

Jean-Michel Muller / examinateur Directeur de recherches au CNRS, LIP, École Normale Supérieure de Lyon

André SEZNEC / directeur de thèse Directeur de recherche à INRIA, INRIA Rennes – Bretagne Atlantique

membre invité:

### Isabelle Puaut

Professeur à l'Université de Rennes I, IRISA – Rennes

Hofstadter's Law: It always takes longer than you expect, even when you take into account Hofstadter's Law.

Douglas Hofstadter [49]

### Remerciements

Je remercie Olivier Sentieys, professeur à l'Université de Rennes 1, de m'avoir fait l'honneur de présider ce jury.

J'exprime ma profonde gratitude à Pascal Sainrat, professeur à l'Université Paul Sabatier et Olivier Temam, directeur de recherche à l'INRIA, pour avoir accepté d'être les rapporteurs de cette thèse.

Je tiens également à remercier Jean-Michel Muller, directeur de recherches au CNRS, et Isabelle Puaut, professeur à l'Université de Rennes 1, d'avoir participé à mon jury.

Je remercie André Seznec pour m'avoir accueilli au sein des équipes CAPS puis ALF et pour avoir dirigé ma thèse tout au long de ces quatre années. Je lui suis profondément reconnaissant pour son attention, sa disponibilité, ses conseils avisés et sa vision éclairée du futur de l'architecture des processeurs.

Je remercie également Éric, Erven et Pierre pour les discussions passionnées à la cafète, ainsi que Benjamin, Damien, David, Guillaume, Jean-François, Junjie, Nathanaël, Ricardo, Thomas et tous les autres membres passés et présents des équipes ALF et CAPS.

Je remercie ma famille ainsi que mes amis qui m'ont toujours apporté leur soutien durant cette thèse.

Enfin, je remercie de tout cœur Bénédicte pour son soutien, ses relectures, les nombreuses kɔ.ʁɛk.sjɔ̃ ɔʁ.tɔ.gʁa.fik ainsi que pour l'organisation du pot.

# Table des matières

| Re | emerc  | iements  | S                                               | 5  |

|----|--------|----------|-------------------------------------------------|----|

| Ta | ıble d | es matic | ères                                            | 7  |

| In | trodu  | ction    |                                                 | 11 |

|    | Con    | tributio | ns                                              | 12 |

|    | Orga   | anisatio | n du document                                   | 13 |

| 1  | Con    | ipressio | on de données au sein de la hiérarchie mémoire  | 15 |

|    | 1.1    | Algori   | ithmes de compression de données sans perte     | 15 |

|    |        | 1.1.1    | Codage d'Huffman                                | 16 |

|    |        | 1.1.2    | LZ77 et ses variantes                           | 16 |

|    |        | 1.1.3    | Frequent Pattern Compression                    | 18 |

|    |        | 1.1.4    | X-Match et ses variantes                        | 19 |

|    |        | 1.1.5    | Élimination des mots nuls                       | 20 |

|    | 1.2    | Comp     | ression des caches                              | 20 |

|    |        | 1.2.1    | Propositions de Yang, Zhang et Gupta            | 20 |

|    |        | 1.2.2    | Proposition de <i>Alameldeen et Wood</i>        | 21 |

|    |        | 1.2.3    | Filtrage des mots d'une ligne de cache          | 22 |

|    |        | 1.2.4    | Zero-Value Cache d'Islam et Stenström           | 22 |

|    | 1.3    | Comp     | ression sur le bus mémoire                      | 23 |

|    | 1.4    | Comp     | ression de la mémoire principale                | 23 |

|    |        | 1.4.1    | Compression logicielle                          | 23 |

|    |        |          | 1.4.1.1 Structure                               | 23 |

|    |        |          | Cache de taille statique                        | 24 |

|    |        |          | Cache de taille adaptative                      | 25 |

|    |        |          | 1.4.1.2 Adaptations du système d'exploitation   | 25 |

|    |        | 1.4.2    | Compression matérielle                          | 25 |

|    |        |          | 1.4.2.1 IBM Memory eXpansion Technologies (MXT) | 26 |

|    |        |          | Architecture                                    | 26 |

|    |        |          | Performances                                    | 29 |

8 Table des matières

|   |      |        | Limitations                                                           |

|---|------|--------|-----------------------------------------------------------------------|

|   |      |        | 1.4.2.2 Proposition d'Ekman et Stenström 2                            |

|   |      |        | Architecture                                                          |

|   |      |        | Performances                                                          |

|   |      |        | Limitations                                                           |

|   |      |        | 1.4.2.3 Autres propositions                                           |

|   |      |        | Mesures de <i>Kjelsø</i> , <i>Gooch et Jones</i>                      |

|   |      |        | Proposition de <i>Benini</i> , <i>Bruni</i> , <i>Macii et Macii</i> 3 |

|   |      |        | Brevet de <i>Moore</i>                                                |

|   |      |        | Compression du code                                                   |

|   |      |        | 1.4.2.4 Formalisation de l'architecture des mémoires com-             |

|   |      |        | pressées                                                              |

|   |      |        | 1.4.2.5 Adaptations du système d'exploitation                         |

|   |      | 1.4.3  | Machines virtuelles                                                   |

| _ | 3.6  | 1 1    |                                                                       |

| 2 |      |        | utilisation des blocs nuls                                            |

|   | 2.1  |        | e du nombre d'accès à des blocs nuls                                  |

|   | 2.2  |        | ion de l'utilisation de blocs nuls au cours de l'exécution 4          |

|   | 2.3  | -      | e de la provenance des blocs nuls                                     |

|   |      | 2.3.1  | 403.gcc                                                               |

|   |      | 2.3.2  | 410.bwaves                                                            |

|   |      | 2.3.3  | 416.gamess                                                            |

|   |      | 2.3.4  | 434.zeusmp                                                            |

|   |      | 2.3.5  | 436.cactus                                                            |

|   |      | 2.3.6  | 437.leslie3d                                                          |

|   |      | 2.3.7  | 450.soplex                                                            |

|   |      | 2.3.8  | 458.sjeng                                                             |

|   |      | 2.3.9  | 459.GemsFDTD                                                          |

|   | 2.4  | Synthè | se                                                                    |

| 3 | Zoro | -Conto | nt Augmented Cache 5                                                  |

| J | 3.1  |        | ecture du Zero-Content Augmented Cache                                |

|   | 3.1  | 3.1.1  | Structure                                                             |

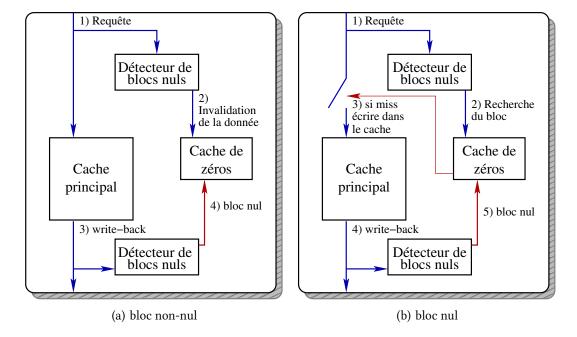

|   |      | 3.1.1  | Accès en lecture                                                      |

|   |      | 3.1.2  | Accès en écriture                                                     |

|   |      | 3.1.3  | Coût matériel                                                         |

|   |      | 3.1.4  | Consommation électrique                                               |

|   |      | 3.1.6  | Position du cache de zéros dans la hiérarchie mémoire                 |

|   |      | 3.1.0  | 3.1.6.1 Au niveau du cache L1                                         |

|   |      |        | 3.1.6.2 Au niveau du cache L2                                         |

|   |      |        | 3.1.6.3 Au niveau du cache L3                                         |

|   |      |        | J.1.0.J AU III VEAU UU CACHE LJ                                       |

Table des matières 9

|   |     |        | 3.1.6.4     | A plusieurs niveaux simultanément 5                     |

|---|-----|--------|-------------|---------------------------------------------------------|

|   |     | 3.1.7  | Politique   | e de remplacement                                       |

|   |     | 3.1.8  | Utilisati   | on avec une mémoire compressée 5                        |

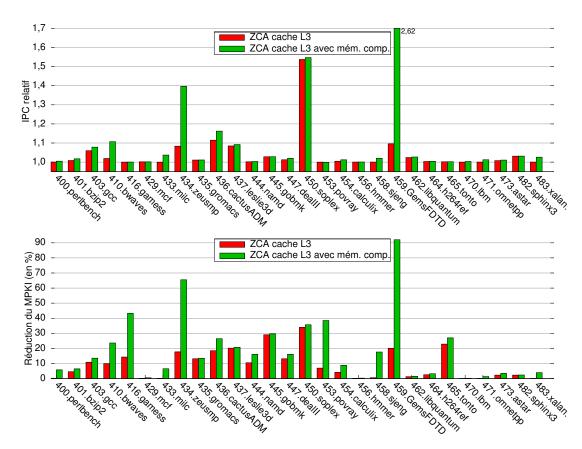

|   | 3.2 | Évalua | ation des p | performances 6                                          |

|   |     | 3.2.1  | Infrastru   | acture de simulation 6                                  |

|   |     |        | 3.2.1.1     | Applications simulées 6                                 |

|   |     |        | 3.2.1.2     | Architecture simulée 6                                  |

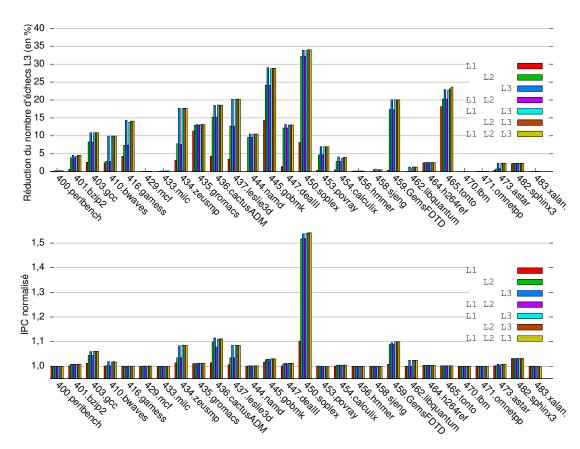

|   |     | 3.2.2  | Position    | du cache de zéros dans la hiérarchie mémoire 6          |

|   |     |        | 3.2.2.1     | Zero-Content Augmented Cache placé en L1, L2 ou L3 6    |

|   |     |        | 3.2.2.2     | Zero-Content Augmented Cache placé à plusieurs ni-      |

|   |     |        |             | veaux                                                   |

|   |     | 3.2.3  | Zero-Co     | ontent Augmented Cache au niveau L3 6                   |

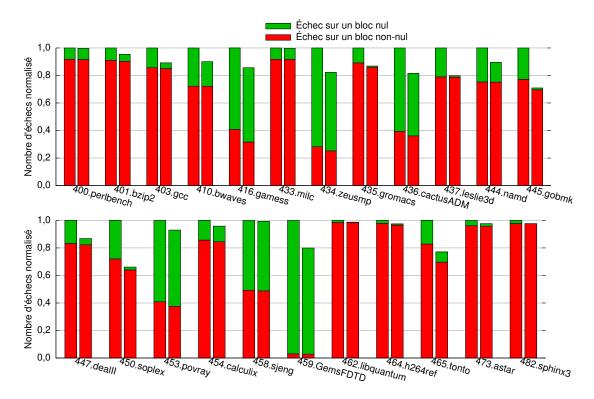

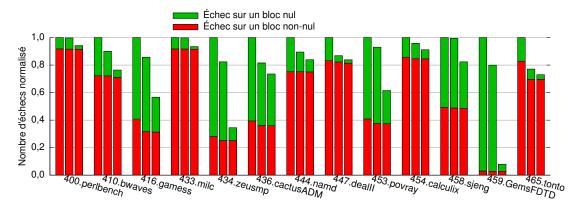

|   |     |        | 3.2.3.1     | Composition des échecs 6                                |

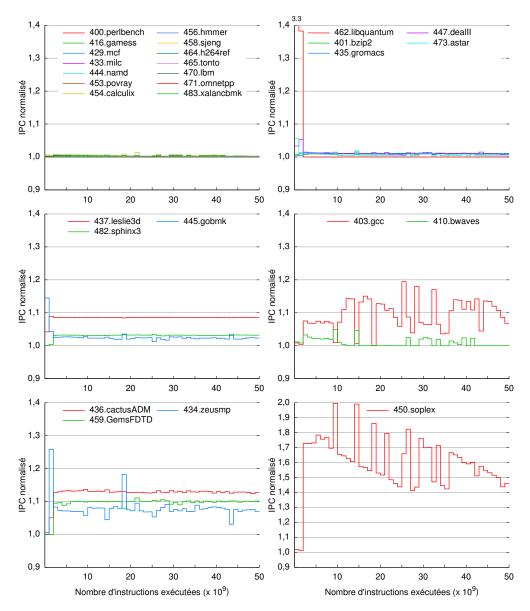

|   |     |        | 3.2.3.2     | Évolution des performances au cours de la simulation 6  |

|   |     |        | 3.2.3.3     | Évaluation avec une mémoire compressée 6                |

|   |     |        | 3.2.3.4     | Localité spatiale des blocs nuls 6                      |

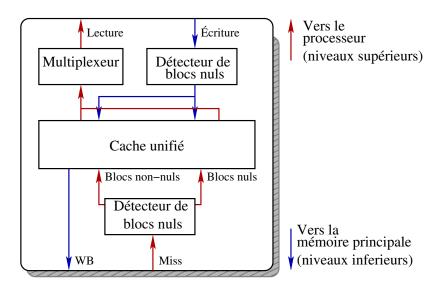

|   | 3.3 | Fusion | du cache    | de zéros au sein du cache principal                     |

|   |     | 3.3.1  | Le cas d    | es TLB                                                  |

|   |     | 3.3.2  | Architec    | cture du cache de zéros unifié                          |

|   |     |        | 3.3.2.1     | Terminologie                                            |

|   |     |        | 3.3.2.2     | Structure                                               |

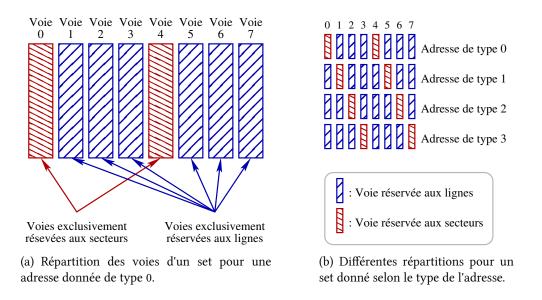

|   |     |        | 3.3.2.3     | Répartition des voies                                   |

|   |     |        | 3.3.2.4     | Politique de remplacement                               |

|   |     | 3.3.3  | Perform     | ances                                                   |

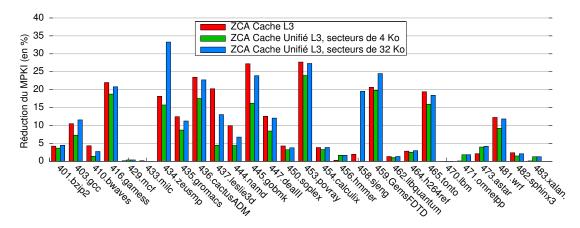

|   |     |        | 3.3.3.1     | Taille des secteurs                                     |

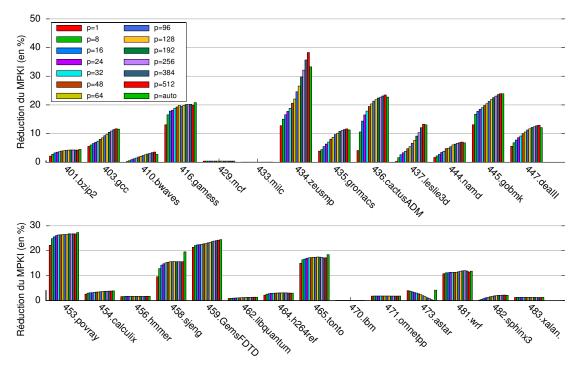

|   |     |        | 3.3.3.2     | Politique de remplacement                               |

|   | 3.4 | Concl  | usion       |                                                         |

|   |     |        |             |                                                         |

| 4 | Mén |        | ompressé    |                                                         |

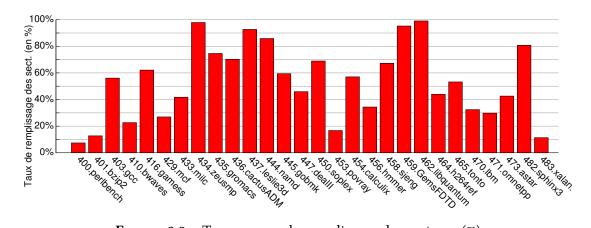

|   | 4.1 | Taux o |             | ompressibles en mémoire                                 |

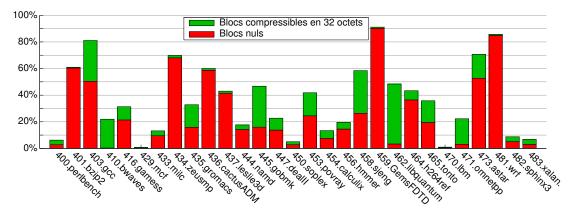

|   |     | 4.1.1  |             | blocs nuls                                              |

|   |     | 4.1.2  |             | blocs compressibles avec FPC                            |

|   | 4.2 | Decou  | -           | -Compressed Memory                                      |

|   |     | 4.2.1  | Archited    | ture                                                    |

|   |     |        | 4.2.1.1     | Structure                                               |

|   |     |        |             | Accès en lecture                                        |

|   |     |        | 1           | Accès en écriture                                       |

|   |     |        | 4.2.1.2     | Coût de stockage des structures de contrôle 8           |

|   |     |        | 4.2.1.3     | Contrôleur de mémoire compressée 8                      |

|   |     |        | 4.2.1.4     | Amélioration de la distribution des blocs nuls 8        |

|   |     |        | 4.2.1.5     | Amélioration par rapport aux propositions antérieures 8 |

1. Table des matières

|         |          | Par rapport à la compression logicielle                   | 89  |

|---------|----------|-----------------------------------------------------------|-----|

|         |          | Par rapport à la technologie IBM MXT                      | 89  |

|         |          | Par rapport à la proposition d' <i>Ekman et Stenström</i> | 89  |

|         | 4.2.2    | Évaluation des performances                               | 90  |

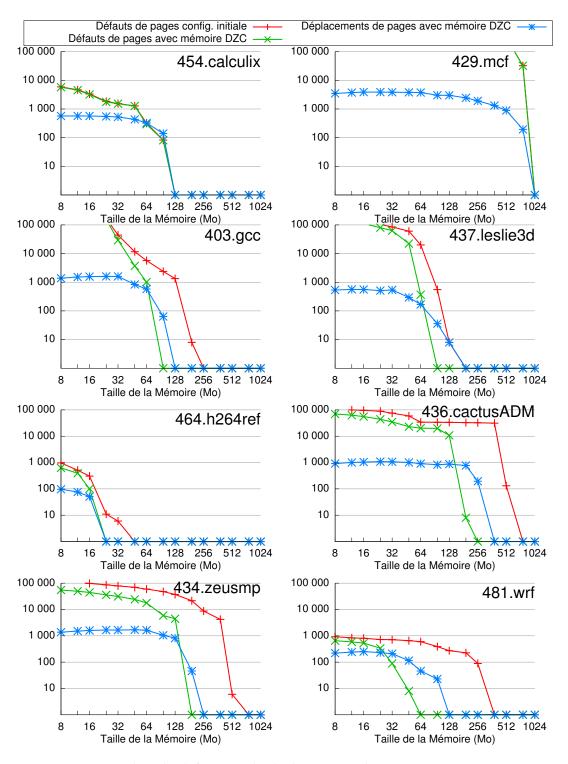

|         |          | 4.2.2.1 Métriques choisies                                | 90  |

|         |          | Défauts et déplacements de pages                          | 90  |

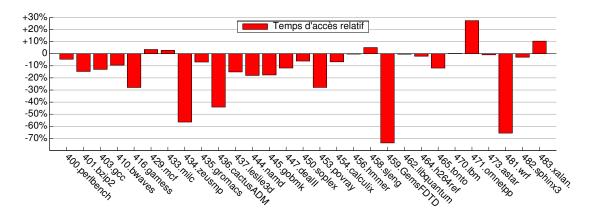

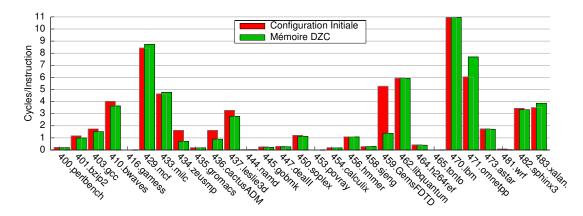

|         |          | Temps moyen d'accès mémoire                               | 91  |

|         |          | 4.2.2.2 Méthode expérimentale                             | 91  |

|         |          | Environnement de simulation                               | 91  |

|         |          | Configuration                                             | 92  |

|         |          | Politique de remplacement de pages                        | 92  |

|         |          | Déplacement de pages lors des écritures                   | 93  |

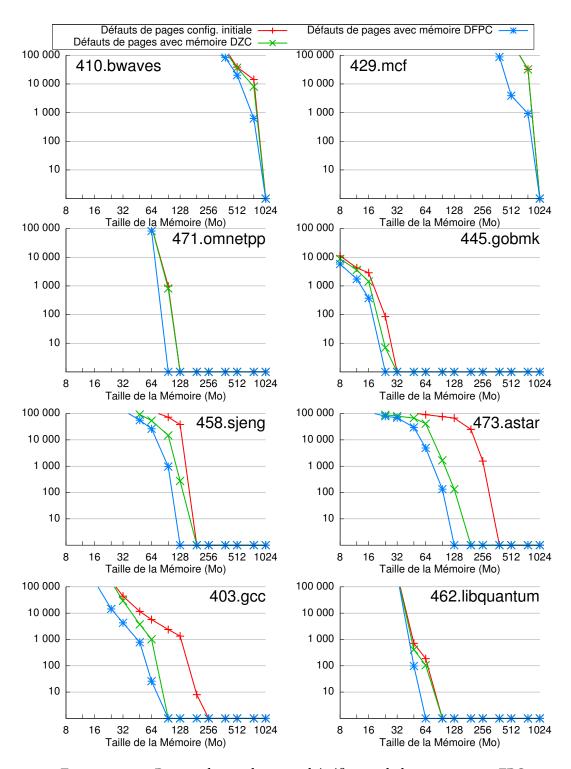

|         |          | 4.2.2.3 Résultats                                         | 93  |

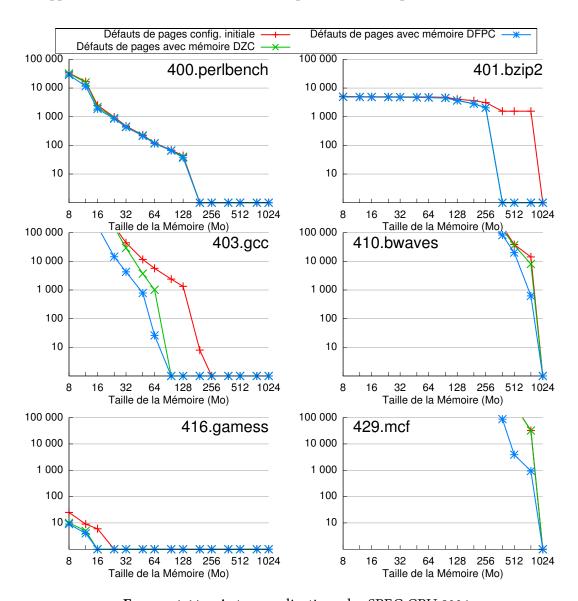

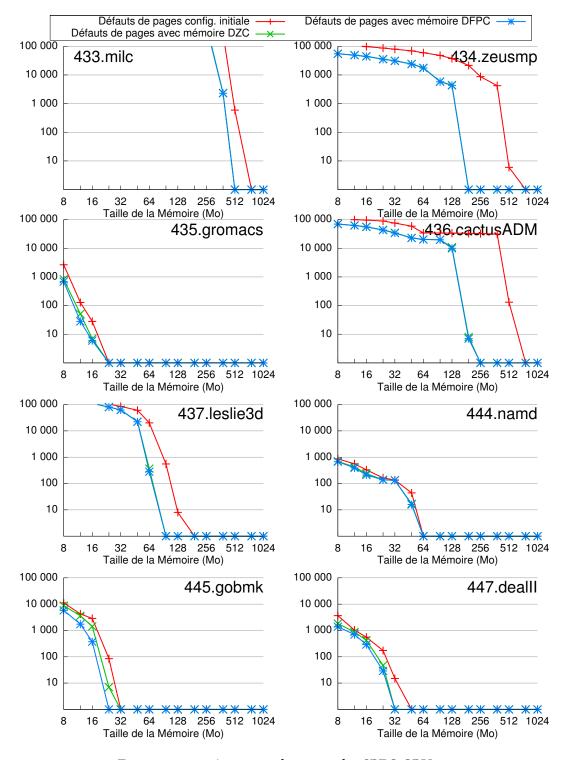

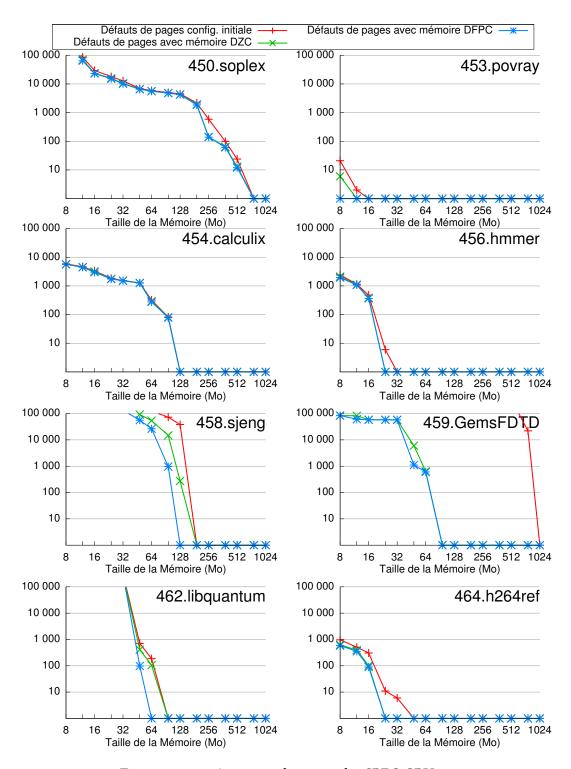

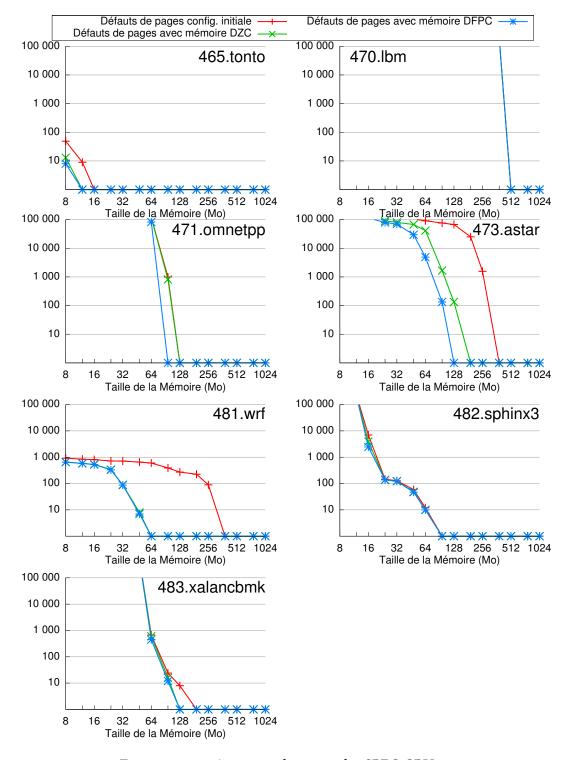

|         |          | Nombre de défauts de pages                                | 93  |

|         |          | Déplacements de pages                                     | 95  |

|         |          | Temps moyen d'accès mémoire                               | 95  |

|         |          | 4.2.2.4 Conclusions                                       | 99  |

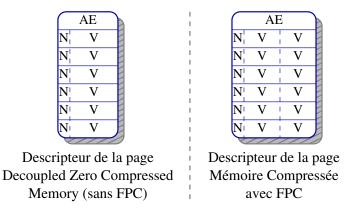

| 4.3     | Mémo     | oire découplée avec compression FPC                       | 99  |

|         | 4.3.1    | Architecture                                              | 99  |

|         |          | 4.3.1.1 Coût de stockage des structures de contrôle       | 100 |

|         | 4.3.2    | Évaluation des performances                               | 101 |

| 4.4     | Concl    | usion                                                     | 103 |

| 4.5     | Annex    | xes                                                       | 104 |

| Conclu  | sion     |                                                           | 109 |

| Bibliog | raphie   |                                                           | 111 |

| Table d | es figur | res                                                       | 125 |

### Introduction

Le processeur et la mémoire sont deux composants intimement liés qui représentent le cœur des ordinateurs. Ce duo est apparu en 1945 avec le premier ordinateur programmable. Depuis, chacun de ces composants a considérablement évolué, nécessitant des changements radicaux dans la façon de les interconnecter.

La première grande évolution touchant le lien entre le processeur et la mémoire, est due à l'augmentation de la fréquence. Cette augmentation a créé un véritable fossé entre le nombre de cycles nécessaires pour accéder à une donnée stockée dans un registre et pour accéder à une donnée stockée en mémoire principale. En effet, au début des années 1980, un accès mémoire ne nécessitait qu'une poignée de cycles. De nos jours, le temps d'accès à la mémoire est beaucoup plus court mais il n'a pas réduit dans les mêmes proportions que le temps de cycle des processeurs. Ainsi, la durée d'un accès mémoire se compte désormais en centaines de cycles. Les mémoires cache sur un puis plusieurs niveaux, ainsi que l'exécution dans le désordre, ont alors vu le jour. Les mémoires cache permettent de stocker près du processeur de petites quantités de données, et donc de diminuer leur la latence d'accès. Cependant, le temps moyen d'accès demeurant toujours trop important, l'introduction de l'exécution dans le désordre a permis de masquer une partie de la latence d'accès. En effet, lors de l'attente d'un accès à la mémoire, l'exécution dans le désordre permet d'exécuter d'autres instructions. Le principal rôle de la hiérarchie mémoire consiste alors à diminuer la latence d'accès.

La deuxième grande évolution touchant particulièrement le lien entre le processeur et la mémoire est due à l'augmentation du nombre de cœurs sur un composant. En effet, depuis le début des années 2000, devant l'impossibilité d'augmenter la fréquence au delà de 4 GHz, les constructeurs ont choisi d'augmenter le nombre de cœurs. Cette augmentation se traduit par un partage d'une partie de la hiérarchie mémoire entre différents cœurs d'exécution. Généralement, le premier niveau de cache est privé, c'est-à-dire réservé à un cœur. Mais, plus l'on descend dans la hiérarchie mémoire, plus le nombre de cœurs partageant un niveau est important. Cela conduit à une saturation de la bande passante entre les différents niveaux de la hiérarchie mémoire. Cette saturation est renforcée par la gestion simultanée de plusieurs processus par cœur (Simultaneous MultiThreading, SMT). Dans un futur proche, si le nombre de cœurs continue à augmenter, la bande passante mémoire va devenir le principal goulot d'étranglement. Dans

12 Introduction

ce contexte, un rôle majeur de la hiérarchie mémoire consiste à filtrer les accès afin de diminuer leur nombre et d'éviter ainsi une saturation complète de la bande passante mémoire.

Dans cette thèse, nous proposons des mécanismes permettant une gestion efficace de la hiérarchie mémoire, réduisant la latence d'accès, l'occupation du bus mémoire et augmentant sa capacité. La compression des données transitant dans la hiérarchie mémoire est la solution que nous avons retenue. En effet, de nombreuses études ont montré que les données traversant la hiérarchie mémoire sont fortement compressibles. Nos propres constatations montrent que les blocs de données complètement nuls représentent la majeure partie des données compressibles. Nous proposons donc des modifications peu coûteuses de l'architecture de la hiérarchie mémoire permettant d'exploiter la présence de ces blocs.

### Contributions

Dans ce document, nous analysons les données contenues dans les différents niveaux de la hiérarchie mémoire, et nous constatons la présence d'un nombre important de blocs de la taille d'une ligne de cache complètement nuls, et ce pour de nombreuses applications. Nous montrons que la présence de ces blocs nuls ne résulte pas de simples phénomènes d'initialisation, mais que les blocs nuls sont utilisés tout au long de l'exécution de ces applications. La présence de ces blocs nuls nous permet de faire deux propositions d'architectures. Notre première proposition se situe au niveau du dernier niveau de cache et la seconde au niveau de la mémoire principale.

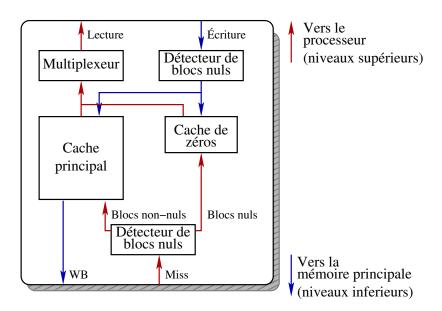

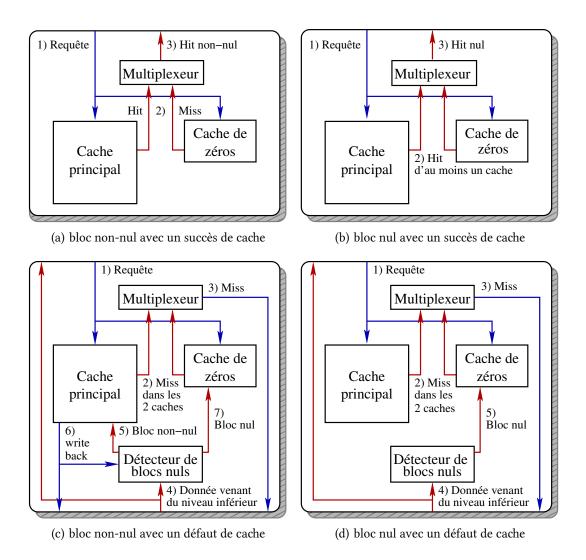

Notre première contribution est le *Zero-Content Augmented Cache*. Il s'agit d'une modification du dernier niveau de cache permettant d'exploiter le nombre important de blocs nuls présents en mémoire. Nous proposons d'utiliser un cache spécialisé dans le stockage des blocs nuls conjointement avec le cache traditionnel. Ce cache, appelé cache de zéros, permet non seulement de stocker à moindre coût une grande quantité de blocs nuls, mais aussi de libérer de la place dans le cache principal. Un bloc nul est représenté dans le cache de zéros par un seul bit. Ainsi, quelques kilo-octets de stockage physique seulement permettent de stocker plusieurs méga-octets de blocs nuls.

Notre seconde contribution est la *Decoupled Zero-Compressed Memory*. Il s'agit d'une proposition de compression matérielle de la mémoire principale dans laquelle seuls les blocs nuls sont compressés. Cette architecture de mémoire compressée permet de réduire significativement la taille de la mémoire physique nécessaire pour faire tenir le *working-set* de nombreuses applications. Cette proposition utilisée simultanément avec un *Zero-Content Augmented Cache* permet une diminution importante du nombre d'accès mémoire et une augmentation significative des performances.

Introduction 13

### Organisation du document

Ce document de thèse se compose de quatre chapitres : un état de l'art, puis une analyse de l'utilisation des blocs nuls au sein de la hiérarchie mémoire, suivie de notre proposition de cache spécialisé pour stocker les blocs nuls, et enfin notre proposition de mémoire compressée exploitant elle aussi la présence de blocs nuls.

L'état de l'art présente la compression de données au sein de la hiérarchie mémoire. Dans ce chapitre, nous commençons par décrire le fonctionnement des algorithmes de compression les plus fréquemment utilisés. Ensuite, nous abordons la compression de données dans la hiérarchie mémoire par une étude des propositions de cache de donnés compressées. À l'issue de cette étude, nous descendons dans la hiérarchie mémoire pour examiner les différentes propositions de mémoires principales compressées : la compression logicielle, la compression matérielle et, à mi-chemin entre les deux, la compression de données au sein des machines virtuelles Java.

Le deuxième chapitre consiste en une analyse détaillée de la présence de blocs nuls au sein de la hiérarchie mémoire. En effet, la présence d'une proportion significative de blocs nuls tout au de l'exécution de l'application peut au premier abord surprendre. Nous mesurons donc de façon approfondie le taux de blocs nuls dans les accès aux différents niveaux de la hiérarchie mémoire. Dans une deuxième partie, nous évaluons l'évolution de ce taux au cours de l'exécution de leurs utilisations afin de nous assurer que ces blocs nuls ne sont pas de simples phénomènes d'initialisation. Enfin, dans une troisième partie, nous montrons pourquoi des applications lisent et écrivent des blocs nuls à travers l'étude de leurs codes sources.

Le troisième chapitre présente notre première contribution architecturale : le *Zero-Content Augmented Cache*. Il s'agit d'une proposition de modification du dernier niveau de cache afin de stocker efficacement les blocs nuls. Nous présentons successivement sa structure, son fonctionnement et une analyse détaillée des performances. À l'issue de cette évaluation, nous proposons une modification permettant de réduire drastiquement le surcoût de notre proposition.

Le quatrième, et dernier, chapitre présente notre deuxième contribution : la *Decoupled Zero-Compressed Memory*. Celle-ci permet de compresser la mémoire principale en ne stockant pas les blocs nuls. Dans ce chapitre, nous évaluons le taux de blocs nuls présents dans la mémoire principale. Ensuite, nous présentons la structure et le fonctionnement de la *Decoupled Zero-Compressed Memory*. Pour finir, nous proposons de modifier cette mémoire afin de considérer un algorithme de compression plus complexe que la simple compression des blocs nuls.

# Chapitre 1

# État de l'art de la compression de données au sein de la hiérarchie mémoire

Depuis les années 1990, de nombreuses études ont montré que les données présentes dans la hiérarchie mémoire sont fortement compressibles. Il a par exemple été observé pour de nombreuses applications que plus de la moitié des octets présents en mémoire sont des zéros. De nombreuses propositions d'architectures visant à compresser les données au sein de la hiérarchie mémoire ont alors été proposées.

Dans ce chapitre, nous allons décrire les différents travaux relatifs à la compression de données dans la hiérarchie mémoire. Dans un premier temps, nous présenterons rapidement le fonctionnement des algorithmes de compression de données sans perte les plus fréquemment rencontrés. Dans un deuxième temps, nous explorerons les différentes propositions de mémoires compressées. Et pour finir, nous nous intéresserons à la compression de la mémoire principale, qu'elle soit matérielle ou logicielle.

# 1.1 Algorithmes de compression de données sans perte

Il existe deux principaux types de compression de données : la compression sans perte et la compression avec pertes. Seule la compression sans perte est envisageable pour une hiérarchie mémoire. En effet, le changement d'un seul bit dans la zone de code d'une application suffit à changer une instruction en une autre pouvant provoquer ainsi une sortie en erreur ou un résultat incorrect. Par exemple, en assembleur x86, l' $opcode\ 0 \times 74$  est un je alors que  $0 \times 75$  est l'instruction contraire, c'est-à-dire un jne. Le remplacement de l'un par l'autre change radicalement l'exécution.

Dans cette section, nous allons présenter succinctement deux types principaux d'algorithmes de compression sans perte : les algorithmes de codage entropique et les algorithmes de compression à dictionnaire.

### 1.1.1 Codage d'Huffman

Les premiers véritables algorithmes de compression sont publiés en 1948 et 1952. Il s'agit d'algorithmes de codage. Les premiers algorithmes sont le codage de Shannon-Fano [83, 37], et codage de Huffman [51]. Contrairement au codage de Shannon-Fano, le codage de Huffman est un codage optimal, c'est-à-dire qu'il n'existe pas de modification de ce codage permettant d'obtenir un message plus court. Depuis, des dizaines d'autres algorithmes ont vu le jour, chacun adapté à des contraintes particulières ou à un format de données spécifique.

Dans le *codage de Huffman*, la donnée d'entrée est découpée en symboles. Le codage consiste à affecter les codes les plus courts aux symboles les plus fréquents. Une table de correspondance symbole  $\mapsto$  code est obtenue en construisant un arbre binaire à partir des fréquences des différents symboles. La donnée compressée est obtenue en remplaçant chaque symbole par le code correspondant. La table inverse est utilisée pour la décompression.

Si le *codage de Huffman* est appliqué sur des données brutes, le taux de compression obtenu est généralement faible. En effet, l'efficacité des algorithmes de codage dépendent fortement du format des données à compresser. Ils nécessitent de définir une méthode permettant de découper la donnée en mots, et d'établir des statistiques de fréquences des différents mots.

Le codage de Huffman est généralement utilisé dans des méthodes de compression hybrides, après une transformation avec ou sans perte. Cette transformation permet d'obtenir un format régulier, dont on peut ensuite extraire des mots qui possèdent une répartition non-aléatoire. Le codage permet alors d'exploiter cette répartition. Les formats de compression de fichiers gzip et bzip2 sont conçus de cette façon. gzip utilise une compression par dictionnaire (LZ77) suivie d'un codage de Huffman. Quant à bzip2, il utilise le codage de Huffman après une transformée de Burrows-Wheeler [20].

En raison de la nécessité de transformer et d'examiner préalablement les données, les algorithmes de codage sont peu utilisés dans la compression de données dans la hiérarchie mémoire. Ils sont plutôt adaptés à une compression hors-ligne.

#### 1.1.2 LZ77 et ses variantes

L'algorithme LZ77 proposé en 1977 par *Lempel et Ziv* est un algorithme de compression à dictionnaire. Le dictionnaire est construit dans une fenêtre coulissante qui se déplace sur les données à compresser. Le dictionnaire contient alors les dernières données rencontrées.

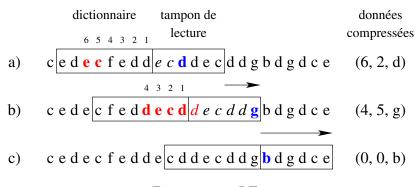

**FIGURE 1.1 – LZ77**

La fenêtre coulissante est composée de deux parties : le dictionnaire et le tampon de lecture. Lorsqu'une suite de caractères du tampon de lecture est compressée, elle est recherchée dans le dictionnaire. La donnée compressée est composée d'un triplet comprenant la position dans le dictionnaire, la longueur de la chaîne trouvée et le premier caractère différent.

L'exemple de la figure 1.1 illustre le fonctionnement de *LZ77*. À l'étape a, la chaîne ecddec est recherchée dans le dictionnaire. Le motif de *deux* caractères ec est trouvé en position *six*. La sortie compressée est donc (6, 2, d). La fenêtre est décalée de trois positions. À l'étape b, la chaîne decddg est recherchée. Le motif de *cinq* caractères decdd est trouvé en position *quatre*, sachant que le motif peut être partiellement récursif. La sortie compressée est alors (4, 5, g). La fenêtre est décalée de six positions. A l'étape c, la chaîne bdgdce est recherchée. Aucune correspondance n'est trouvée. La sortie est alors (0, 0, b).

Cette dernière étape de l'exemple illustre bien l'un des points faibles de LZ77: l'encodage des nouvelles valeurs. Elles sont en effet représentées par le triplet  $(0, 0, \times)$ , qui occupe beaucoup plus d'espace que le caractère ajouté. LZSS [85] est une variante de LZ77 qui permet de ne pas stocker le triplet dans ce cas de figure. Un marqueur permet de désactiver la compression sur un passage.

LZ77 est à l'origine de multiples travaux dérivés. Parmi les plus utilisés on peut citer LZ78 [105] et sa variante LZW [93]. Ces deux algorithmes utilisent un dictionnaire implicite. Contrairement à LZ77, le dictionnaire est créé d'après les données à venir et non pas d'après les données déjà compressées. En 1991, Ross Williams a proposé LZRW [94]. Il s'agit d'une variante très optimisée, plus simple et utilisant moins de mémoire. Elle permet une compression en 13 instructions par octet et une décompression en 4 instructions par octet. De multiples autres variantes existent, parmi lesquelles : LZJB, LZMA, LZO, LZT, LZWL, LZX et ROLZ. Ces variantes permettent de répondre à diverses contraintes de vitesse de compression (ou de décompression), de complexité ou d'efficacité.

Quelque soit la variante, les algorithmes de type LZ77 présentent tous une efficacité limitée sur les données de petites tailles. En effet, si le bloc de données à compresser

est petit, le dictionnaire a une taille réduite, et peu de motifs vont être retrouvés dans ce dictionnaire. Ces algorithmes nécessitent aussi un temps d'initialisation assez long, le dictionnaire étant initialement vide. Les premiers motifs ne seront alors pas compressés. Franaszek, Robison et Thomas [43] ont analysé l'évolution du taux de compression de LZ77 en fonction de la taille de la donnée. En dessous de 512 octets, le taux de compression est fortement dégradé. La taille minimale idéale semble être comprise entre 512 octets et 1,5 Ko.

En conclusion, ces algorithmes sont, certes, adaptés à la compression de données dans la hiérarchie mémoire car ils sont rapides, et présentent un bon taux de compression, mais leur efficacité est conditionnée à la taille des blocs de données qui doivent atteindre au moins 1 Ko. Ils sont donc plus adaptés à une compression logicielle des données pour archivage.

### 1.1.3 Frequent Pattern Compression

L'algorithme de compression Frequent Pattern Compression [8] (FPC) proposé par Alameldeen et Wood en 2004 est également un algorithme à dictionnaire. Cependant, contrairement au codage de Huffman, il utilise un dictionnaire statique prédéfini qu'il n'est donc pas nécessaire de stocker. Pour leur version destinée à la compression dans le cache L2, Alameldeen et Wood proposent d'utiliser un dictionnaire à huit motifs pour représenter des mots de 32 bits.

| Avant compress           | Après compression |         |          |        |

|--------------------------|-------------------|---------|----------|--------|

| Motif                    | Valeur            | Préfixe | Valeur   | Taille |

| mot nul                  | 00000000          | 000     | _        | 3      |

| mot de 4 bits            | SSSSSSSa          | 001     | a        | 7      |

| mot de 8 bits signé      | SSSSSSab          | 010     | ab       | 11     |

| mot de 16 bits signé     | SSSSabcd          | 011     | abcd     | 19     |

| mot de 16 bits           | 0000abcd          | 100     | abcd     | 19     |

| 2 mots de 8 bits signés  | SSabSScd          | 101     | abcd     | 19     |

| 4 mots de 8 bits répétés | abababab          | 110     | ab       | 11     |

| mot non-compressé        | abcdefgh          | 111     | abcdefgh | 35     |

**TABLE 1.1 –** FPC à huit motifs. Les champs *valeur* sont notés en hexadécimal. S est l'extension du bit de signe (soit 0x0, soit 0xF).

L'entrée est parcourue par mot de 32 bits. Chacun de ces mots est recherché parmi les motifs et est remplacé par le couple (préfixe, valeur) correspondant. Les motifs doivent être adaptés à l'*endianness* de la machine.

Ainsi, par exemple, la chaîne hexadécimale de 16 octets 00000085, 00000000, ffffffc5, 0bfffff0 est compressée en quatre paires (011, 0085), (000, -), (010, c5), (111, 0bfffff0). Elle occupe alors 19+3+11+35=68 bits.

| Avant compre         | Apı      | rès compression | on       |        |

|----------------------|----------|-----------------|----------|--------|

| Motif                | Valeur   | Préfixe         | Valeur   | Taille |

| mot nul              | 00000000 | 00              | _        | 2      |

| mot de 8 bits        | 000000ab | 01              | ab       | 10     |

| mot de 16 bits signé | SSSSabcd | 10              | abcd     | 18     |

| mot non-compressé    | abcdefgh | 11              | abcdefgh | 34     |

Table 1.2 – FPC à quatre motifs proposé par Ekman et Stenström

Ekman et Stenström [34] ont mesuré les performances de l'algorithme FPC pour la compression de la mémoire principale. Ils ont observé que les motifs les plus importants étaient ceux correspondant aux mots nuls et partiellement nuls. Dans leurs mesures, une compression FPC simplifiée avec quatre motifs offrait un taux de compression très proche d'un FPC à huit motifs. Ils ont montré que FPC permet d'obtenir un taux de compression  $^1$  d'environ 50% pour des blocs de 64 octets.

### 1.1.4 X-Match et ses variantes

L'algorithme de compression X-Match a été proposé en 1996 par *Kjelsø*, *Gooch et Jones* [56]. Comme *LZ77*, cet algorithme construit un dictionnaire au fur et à mesure de la compression. Une nouvelle entrée est ajoutée au dictionnaire pour chaque nouveau mot rencontré.

Lors de la compression, la donnée d'entrée est découpée en mots de quatre octets. Un par un, les mots sont ensuite recherchés dans le dictionnaire. Si une entrée du dictionnaire a au moins deux octets identiques avec le mot recherché, celui-ci est alors considéré comme compressible. Dans le cas contraire, le mot ne sera pas compressé.

Un mot non-compressé est représenté par la paire (1, *mot non-compressé*), il occupera donc 33 bits de stockage.

Un mot compressé est représenté par le quadruplet (0, position dans le dictionnaire, position des caractères trouvés dans le mot, caractères restants). Ce quadruplet occupe entre 5 et 32 bits, selon le nombre de caractères communs entre le mot à compresser et le mot trouvé dans le dictionnaire.

Afin de stocker efficacement les suites de zéros, les auteurs proposent une version légèrement modifiée de l'algorithme, nommée X-RL. Cependant, la complexité matérielle de la compression augmente sérieusement. *Ahn, Yoo et Kang* proposent eux aussi de petites modifications de X-Match. Celles-ci permettent des gains substantiels de compressibilité [6] sans trop augmenter la complexité de l'algorithme.

<sup>1.</sup> Le taux de compression est défini par  $au = \frac{Taille\; non\text{-}compressée}{Taille\; non\text{-}compressée}$

Comme la majorité des algorithmes construisant un dictionnaire au fur et à mesure de la compression, cet algorithme est particulièrement adapté aux blocs de données de quelques kilo-octets. Si la taille de bloc descend en dessous de 1 Ko, le taux de compression se dégrade sérieusement.

### 1.1.5 Élimination des mots nuls

En 1997, *Rizzo* [74] a constaté qu'une grande partie des mots de 32 bits présents en mémoire sont des mots nuls. Il a proposé un mécanisme de compression adapté à la compression des mots nuls au sein d'une page de 4 Ko.

La page est découpée en deux parties, une partie stockant les mots non-nuls et une partie contenant une table de bits (*bitmap*). La table de bits est utilisée pour indiquer pour chaque mot s'il est nul ou non-nul. S'il est non-nul, la valeur est lue dans la première partie de la page.

Après compression, il constate que la partie correspondant à la table de bits, contient elle aussi de nombreux zéros. Il utilise alors le même mécanisme sur la seconde partie de la page, avec une taille de mot de 8 bits. Le gain d'espace supplémentaire ainsi obtenu s'explique par la présence de blocs nuls d'au moins trente-deux octets.

Le taux de compression  $^{2}$  obtenu ainsi est important mais moins bon que FPC, il se situe autour de 40%.

### 1.2 Compression des caches

Une dizaine de propositions de caches compressés ont été faites [59, 58, 92, 101, 103, 100, 23, 7, 70, 71, 89]. Cependant, la compression des données à l'intérieur du cache pose de nombreuses difficultés : L'efficacité de l'algorithme sur de petits blocs, la latence de décompression et le stockage des blocs compressés.

Parmi les propositions, nous allons décrire les plus avancées, à savoir celles de *Yang, Zhang et Gupta*, puis celle d'*Alameldeen et Wood* et pour finir celle de *Qureshi, Suleman et Patt.*

### 1.2.1 Propositions de Yang, Zhang et Gupta

En 2000 et 2003, Yang, Zhang et Gupta ont publié trois propositions différentes de caches compressés [101, 103, 100]. Ils sont partis des observations de Lipasti [64] et Gabbay [46] qui ont remarqué que de nombreuses instructions produisent régulièrement les mêmes valeurs. Ils proposent alors de stocker ces valeurs fréquentes dans une table dédiée et de remplacer la valeur par l'index dans la table, l'index étant généralement codé sur trois bits.

Dans la publication [103], Zhang, Yang et Gupta proposent de diminuer le nombre d'échecs d'un cache direct mapped. Ils suggèrent d'ajouter un Frequent Value Cache à

<sup>2.</sup> cf. note 1 page précédente

coté du cache principal. Le *Frequent Value Cache* est un cache compressé qui ne stocke que les index des mots compressés, les mots non-compressés n'étant pas stockés. Afin de ne pas dégrader les performances sur les mots non-compressés, le *Frequent Value Cache* est utilisé comme un *victim cache*. Lors de l'éjection d'un bloc du cache principal, une entrée est ajoutée au *Frequent Value Cache*. Ainsi, ce dernier ne peut qu'améliorer les performances. Lors d'un succès, l'entrée est invalidée dans le *Frequent Value Cache* et insérée dans le cache principal. De ce fait, la donnée n'est jamais présente simultanément dans les deux caches. Cette proposition permet de diminuer le nombre d'échecs.

Dans la publication [101], Yang, Zhang et Gupta proposent une autre architecture de cache compressé. Chaque ligne du cache compressé peut accueillir soit un bloc noncompressé soit deux blocs compressés. Si au moins la moitié des mots d'un bloc sont des valeurs fréquentes, il peut être stocké compressé. La demi-ligne stocke alors les valeurs non-fréquentes. L'index des valeurs fréquentes est stocké, quant à lui, dans un champs additionnel de trois bit par mot. Cette proposition permet d'augmenter la quantité de données stockées, mais elle a un coût important. Elle nécessite de doubler le nombre de tags et aussi d'ajouter un champ de trois bits par mot. La latence de décompression qui risque d'avoir un impact sur les performances n'est pas mesurée.

Dans la publication [100], *Yang et Gupta* proposent d'utiliser les *valeurs fréquentes* pour diminuer la consommation électrique du cache. Pour les valeurs fréquentes, seuls le tag et quatre bits sont lus au lieu du tag et trente-deux bits. Pour les *valeurs non-fréquentes*, la latence d'accès est augmentée d'un cycle.

### 1.2.2 Proposition de Alameldeen et Wood

Alameldeen et Wood ont mesuré que lors de l'utilisation d'un cache compressé avec FPC, les performances peuvent aussi bien augmenter de 18% que diminuer de 17% selon l'application [7]. Cette dégradation est due à la latence de décompression qui n'est pas toujours compensée par le gain d'espace obtenu dans le cache. Ce sont principalement les applications tenant dans le cache qui sont concernées. Afin de résoudre ce problème, Alameldeen et Wood proposent en 2004 d'utiliser un mécanisme adaptatif [7, 98].

La compression est réalisée à l'aide d'un cache associatif par ensemble de huit voies mais qui ne dispose d'un espace de stockage que de quatre voies. Ainsi, pour chaque *set* le cache contient huit *tags*, mais seulement quatre à huit blocs selon leurs compressibilités.

Un prédicteur est utilisé pour déterminer l'efficacité de la compression. La position de la ligne dans la LRU permet de détecter un succès dû à la compression. En effet, si un bloc placé après la quatrième position provoque un succès, il y aurait eu un échec sur ce bloc sans compression. Si le nombre de succès dus à la compression ne permet pas de couvrir la latence de décompression, le prédicteur peut alors choisir de ne pas compresser un bloc. Dans ce cas, les tags sont quand même mis à jour pour continuer à évaluer l'efficacité de la compression. La dégradation des performances est alors limitée à 0,4%.

### 1.2.3 Filtrage des mots d'une ligne de cache

Les caches utilisent la localité spatiale des accès. Ainsi, si un mot a été accédé, les autres mots de la même ligne ont alors une forte probabilité d'être accédés eux aussi. Cependant, pour certaines applications, la localité spatiale n'est pas toujours réelle. Ce phénomène est d'autant plus présent que la ligne est proche de la position LRU [71]. En 2007, deux propositions visant à filtrer les blocs non-utilisés ont été faites [71, 70]. *Qureshi, Suleman et Patt* proposent d'utiliser pour chaque *set* la voie du L2 destinée à stocker la ligne LRU afin de stocker les mots utiles de plusieurs blocs. *Pujara et Aggarwal* proposent, quant à eux, d'effectuer le filtrage sur toutes les lignes du cache de données de niveau 1.

La compression est obtenu en stockant des mots issus d'autres lignes dans l'espace libéré par le filtrage. Aucune décompression n'est nécessaire : il n'y a donc pas d'impact sur la latence d'accès. Les difficultés principales viennent de l'augmentation de la complexité de la structure du cache, des *tags* supplémentaires à gérer, et de la prédiction des mots non-utilisés.

### 1.2.4 Zero-Value Cache d'Islam et Stenström

Cette proposition de Zero-Value Cache [54] a été publiée simultanément avec notre Zero-Content Augmented Cache qui sera détaillée au chapitre 3. Nos deux propositions suggèrent d'utiliser un cache spécialisé dans le stockage de données nulles. Cependant, la taille des blocs nuls considérés et la structure du cache sont radicalement différents. Néanmoins, cela montre l'intérêt de traiter efficacement les blocs nuls au sein de la hiérarchie mémoire.

En 2009, *Islam et Stenström* ont constaté qu'une part non-négligeable des *loads* accèdent a des mots nuls [54]. Ils ont mesuré sur les SPEC CPU 2000 un taux de mots nuls compris entre 5 et 59% avec une moyenne à 18%. Ces mesures sont effectuées avec SimpleScalar, SimPoint et un jeu d'instructions Alpha. Nos propres mesures effectuées avec Pin et un jeu d'instructions x86 montrent un taux plus faible, compris entre 5 et 28% avec une moyenne proche de 9%.

Le Zero-Value Cache proposé par Islam et Stenström vise le premier niveau de la hiérarchie mémoire. Un petit cache est utilisé afin de traquer les octets nuls dernièrement accédés. Ainsi, lors d'un load le cache est accédé, si tous les octets du mot lu sont nuls alors le Zero-Value Cache peut répondre à la requête.

La difficulté principale de la gestion d'un cache de premier niveau est la granularité variable des accès à une même donnée. En effet, les processeurs modernes proposent plusieurs instructions *load* et *store* de 1, 2, 4 ou 8 octets. Il est donc nécessaire de garder un bit par octet et non un bit par mot afin de gérer les données nulles.

### 1.3 Compression sur le bus mémoire

Afin d'améliorer la bande passante mémoire, quelques propositions de compression des données transitant sur le bus mémoire ont été faites [26, 38, 21, 55, 14, 25]. Les adresses et les données sont compressées avant d'être envoyées sur le bus et décompressées dès la réception. La majorité des ces propositions utilisent le fait que seuls les bits de poids faibles ont une forte entropie. Les bits de poids fort sont, quant à eux, souvent identiques.

La première proposition est celle de *Citron et Rudolph* [26], publiée en 1995. Ils proposent d'utiliser un dictionnaire pour les bits de poids forts afin de diminuer la largeur du bus. À chaque extrémité du bus, un dictionnaire est maintenu d'après les dernières valeurs transférées. Lors d'un transfert, si une entrée de même valeur que les bits de poids forts à transférer est trouvée, alors seuls l'index dans le dictionnaire et les bits de poids faibles sont transférés. Sinon, la donnée est transférée en plusieurs cycles. Ainsi, ils ont mesuré que pour 90% des transferts un bus de 16 bits utilisant ce mécanisme de compression permet de transférer en un cycle autant de données qu'un bus de 32 bits.

### 1.4 Compression de la mémoire principale

Les propositions de compression de la mémoire principale peuvent être classées en trois catégories : logicielles, matérielles et machines virtuelles.

### 1.4.1 Compression logicielle

On dénombre de nombreuses propositions utilisant une compression logicielle sur la mémoire principale. *Wilson* en 1991 [95] est le premier à suggérer de compresser les pages non-récemment utilisées. En 1993, *Douglis* propose une structure complète de mémoire compressée [30]. Ensuite, de nombreuses autres propositions ont suivi. En décembre 2009, *compcache* [27], un mécanisme de mémoire compressée a été intégré dans la version officielle du noyau Linux 2.6.33.

#### 1.4.1.1 Structure

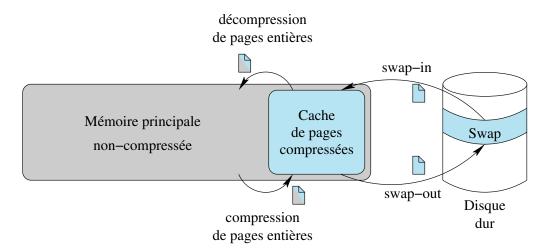

Toutes les propositions utilisant une compression logicielle de la mémoire ont la même structure. La figure 1.2 page suivante présente cette structure. Une partie de la mémoire, appelée cache compressé, est réservée afin de stocker les pages compressées. Seul ce cache est compressé, le reste de la mémoire n'est pas modifié. Lors d'un accès à une donnée dans ce cache compressée la page complète est décompressée dans l'espace non-compressé. Le gain de performance obtenu vient du temps de décompression de la

**FIGURE 1.2** – Compression logicielle de la mémoire. Un cache compressé est réservé au sein de la mémoire principale.

page qui est inférieur au temps d'accès au disque dur, et de la forte compressibilité des pages mémoire.

Cependant, la taille du cache compressé est difficile à établir. *Douglis* a constaté qu'un cache trop petit ne permet pas de stocker suffisamment de pages pour être efficace [30]. Inversement, si le cache compressé est trop gros de nombreuses pages qui auraient tenu en mémoire non-compressée vont être stockées dans le cache. Le temps d'accès à ces pages va alors augmenter.

Les propositions de mémoire compressée en logiciel peuvent être classées en deux catégories : celles dont la taille du cache compressé est déterminée statiquement et celles dont la taille du cache compressé s'adapte à son efficacité.

### Cache de taille statique

On dénombre assez peu de propositions de compression logicielle de la mémoire avec un cache compressé de taille fixe. Les principales propositions sont [75] et [22].

Roy, Kumar et Prvulovic proposent dans [75] d'utiliser un drivers Linux afin de réaliser un cache compressé. La principale limitation est la difficulté de trouver une taille de cache qui satisfasse toutes les applications.

*Cervera, Cortes et Becerra* proposent dans [22] de réserver seulement quelques mégaoctets afin de créer un tampon vers un *swap* compressé. Ce tampon permet de regrouper plusieurs pages compressées au sein d'un bloc du disque dur. Ainsi, lors du chargement d'un bloc depuis le disque dur, un mécanisme de *prefetch* apparaît.

### Cache de taille adaptative

Les propositions de compression logicielle avec un cache de taille variable sont beaucoup plus nombreuses. On peut principalement citer les publications : [30, 96, 29, 47, 91, 48, 102, 12, 13]

Toutes ces propositions sont fondamentalement très proches. Chacune propose d'utiliser une nouvelle structure de données pour stocker le cache compressé, ou bien une nouvelle heuristique pour déterminer sa taille, ou encore d'utiliser un nouvel algorithme de compression plus rapide.

### 1.4.1.2 Adaptations du système d'exploitation

Dans les propositions précédentes, l'utilisation d'une mémoire compressée de façon logicielle nécessite une modification assez profonde du système.

Le système d'exploitation doit être adapté pour ne pas éjecter les pages vers le périphérique de stockage de masse, mais plutôt vers le cache compressé en mémoire. De plus, ce cache doit aussi être géré : sa taille doit être contrôlée et des pages compressées doivent être éjectées vers le périphérique de stockage de masse. Tous les prototypes reposent sur un noyau Linux modifié.

### 1.4.2 Compression matérielle

Contrairement à la compression logicielle de la mémoire, la compression matérielle permet de compresser toute la mémoire, et non pas seulement un cache dans lequel les pages sont stockées compressées. Ainsi, le processeur accède directement aux données compressées sans qu'il y ait besoin de les recopier préalablement dans une zone noncompressée.

Les contraintes appliquées à l'algorithme de compression ne sont pas les mêmes que pour une compression logicielle de la mémoire. Tous les blocs étant compressés, à chaque accès les blocs de données compressés doivent être décompressés. Il est en conséquence primordial que l'algorithme de compression permette une décompression très rapide. Par contre, l'exigence d'efficacité de l'algorithme est beaucoup plus faible puisqu'il est appliqué sur l'ensemble de la mémoire, et non simplement sur une partie de celle-ci.

Afin de garantir les accès aléatoires, la mémoire est découpée en blocs de taille fixe qui sont ensuite compressés. La taille de ces blocs, une fois compressés, est variable. Cela rend leur stockage difficile. Ce stockage est rendu encore plus complexe par l'évolution possible de la taille des blocs lors d'une réécriture. Cela rend nécessaire un nouveau niveau d'adressage.

Parmi les différentes propositions, deux se distinguent particulièrement : la technologie IBM MXT qui a été commercialisée [90] et une proposition d'*Ekman et Stenström* [34].

### 1.4.2.1 IBM Memory eXpansion Technologies (MXT)

IBM a proposé au début des années 2000 des serveurs équipés de la technologie MXT [90] permettant de compresser la mémoire principale. Le premier objectif de l'utilisation de cette technologie était de diminuer le prix de vente [84]. En effet, diviser par deux la quantité de mémoire présente permettait de réduire le prix d'un tiers.

#### Architecture

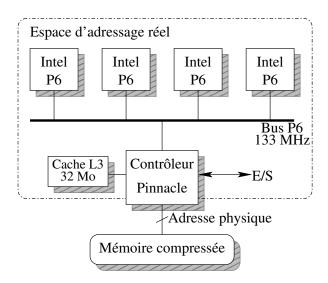

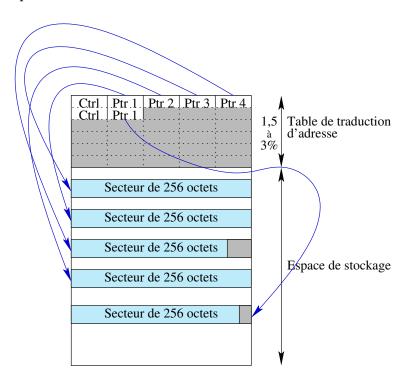

FIGURE 1.3 - Architecture IBM MXT

La mémoire compressée IBM MXT, décrite dans la figure 1.3, repose sur un contrôleur mémoire nommé *Pinnacle* dont le fonctionnement est décrit dans les publications [41, 90, 39, 42]. Il est capable de gérer l'accès à la mémoire compressée. Deux espaces d'adressage sont définis : l'espace des adresses réelles et l'espace des adresses physiques. La traduction d'adresse se fait dans le contrôleur. Afin de masquer le plus possible les latences de compression et de décompression, un cache L3 de 32 Mo contenant des lignes de 1 Ko est ajouté. Il est composé de mémoire SDRAM DDR, plus rapide que la mémoire principale compressée qui est composée de simple SDRAM [90].

La compression est effectuée dans le contrôleur Pinnacle qui intègre une version parallèle [43] de l'algorithme LZ77 [104]. Elle est appliquée à des blocs de 1 Ko qui sont compressés en 0, 1, 2, 3 ou 4 secteurs de 256 octets.

Afin de pouvoir adresser la mémoire compressée, une table de traduction, représentée sur la figure 1.5 page ci-contre, est stockée non-compressée. Elle occupe 16 octets par bloc de 1 Ko. Chaque entrée, représentée sur la figure 1.4 page suivante, est composée d'un champ de contrôle et de quatre pointeurs de 30 bits permettant d'adresser les différents secteurs où est stocké le bloc compressé.

| 8 bits           | 30 bits    | 30 bits    | 30 bits    | 30 bits    |

|------------------|------------|------------|------------|------------|

| Champ de contôle | Pointeur 1 | Pointeur 2 | Pointeur 3 | Pointeur 4 |

|                  |            |            |            |            |

16 octets

FIGURE 1.4 – Une entrée de la table de traduction. Elle est composée d'un champ de contrôle et de quatre pointeurs vers les secteurs où est stocké le bloc compressé.

FIGURE 1.5 – Organisation de la mémoire. Une partie de l'espace sert à stocker les pointeurs de secteurs.

Plus le contenu de la mémoire est compressible, plus elle contient de lignes, et plus il faut agrandir cette table. Cette dernière occupe donc environ 1,5% de la mémoire pour un taux de compression de 0% et 3,1% de la mémoire pour un taux de 50%.

Dans le but d'optimiser l'utilisation de l'espace physique, deux techniques ont été proposées. On peut facilement les comparer à celles actuellement utilisées dans les systèmes de fichiers.

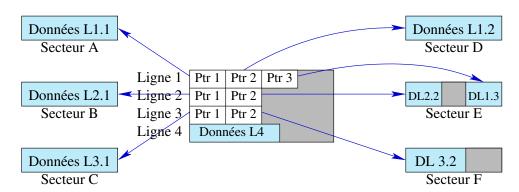

Si le bloc une fois compressé utilise 120 bits ou moins, il peut être stocké dans les quatre champs réservés aux pointeurs. Sur la figure 1.6 page suivante, la ligne 4 est stockée de cette façon. Aucun secteur n'est donc alloué. Pour comparaison, dans les systèmes de fichiers ext4 et NTFS, les petits attributs de fichiers sont directement stockés respectivement dans les *inodes* [36] et dans la *MFT* [68].

FIGURE 1.6 – Optimisation de l'espace de stockage. Les lignes 1 et 2 partagent le même secteur E. La ligne 4 est stockée directement dans la table.

Si le dernier secteur dans lequel est stocké le bloc compressé est rempli à moins de 50%, il peut accueillir la fin d'un autre bloc compressé de la même page. Sur la figure 1.6, c'est le cas pour les lignes 1 et 2. Pour comparaison, cette technique appliquée aux systèmes de fichiers est appelée *Tail packing*. Elle est utilisée notamment par *Reiser4* [72].

Le choix d'une taille de bloc de 1 Ko résulte d'un compromis. Dans l'article présentant la version parallèle de LZ77 de *Franaszek*, *Robison et Thomas* [43], une analyse de l'évolution du taux de compression en fonction de la taille des blocs est effectuée. En dessous de 512 octets, le taux de compression est fortement dégradé. Au dessus de 1, 5 Ko, le taux de compression est stable. Les blocs doivent donc être suffisamment larges pour obtenir un bon taux de compression avec LZ77 (et LZSS). Inversement, sur la question de l'accès aux données compressées, une taille de bloc trop importante entraîne une grande latence de décompression. La taille choisie est donc un compromis entre le taux de compression et le temps d'accès.

La taille des secteurs fixée à 256 octets résulte également d'un compromis [41, 42]. L'utilisation de petits secteurs permet d'éviter la fragmentation de l'espace disponible. Ils ont cependant un coût de gestion très important, car il faut adresser chacun d'entre eux. En effet, l'utilisation de plus petits secteurs impliquerait plus de secteurs, plus de pointeurs, et des pointeurs plus longs. L'espace réservé à la table de traduction augmenterait donc, réduisant l'espace disponible pour les données compressées. Par ailleurs, de larges structures sont difficiles à faire tenir en cache et augmentent la latence de traduction d'adresse.

Afin d'améliorer le support de l'espace compressé, des modifications sont appliquées au système d'exploitation. Ces modifications se présentent sous la forme d'un driver pour Windows 2000, ou d'une modification du noyau Linux. Elles sont décrites par *Abali et al.* dans [3, 1, 2]. *Franaszek, Heidelberger et Wazlowski* [40] proposent quant à eux une analyse de la gestion de l'espace libre. Le système est initialisé avec une taille de mémoire principale de deux fois la taille de la mémoire physique réellement présente.

La principale modification consiste, lorsque le taux de compression est trop faible, à éjecter des pages vers le périphérique de stockage de masse afin de diminuer la pression sur la mémoire compressée.

#### **Performances**

L'analyse de performances réalisée par *Abali et al.* [4] montre que pour certaines applications cette architecture réussit presque à doubler la taille de la mémoire, c'est-à-dire que le *working-set* que peut contenir la mémoire MXT est de deux fois la taille de la mémoire physique. La vitesse d'exécution de six applications parmi les SPEC CPU 2000 s'améliore même de 4 à 8%. Une application de base de données interne à IBM est aussi testée. Elle montre une réduction impressionnante de 66% du temps d'exécution.

Cependant, d'autres applications des SPEC CPU 2000 s'exécutent jusqu'à 10% plus lentement. Aucun détail n'est donné sur l'application de base de données ni sur le jeu de données réellement stockées. Les gains semblent en réalité provenir de la forte compressibilité des données manipulées et des mauvaises performances de l'application avec une mémoire non-compressée. De plus, il s'avère qu'une partie importante des gains de performances vient de l'utilisation d'un cache L3 non-compressé de 32 Mo constitué de mémoire SDRAM DDR plus rapide que la mémoire SDRAM.

#### Limitations

Le principal facteur limitant de cette architecture est la granularité des accès à la mémoire principale. L'impact des soixante-quatre cycles de latence de décompression des blocs de 1 Ko masque en partie les gains de la compression. Certaines applications accédant à de nombreuses petites structures telles que des listes chaînées risquent aussi de saturer la bande passante mémoire.

### 1.4.2.2 Proposition d'Ekman et Stenström

Début 2005, *Ekman et Stenström* ont tout d'abord proposé de hiérarchiser la mémoire principale sur deux niveaux [33]. D'après leurs mesures, si le premier niveau occupe 30% de la taille de la mémoire principale et que le deuxième niveau est plus lent d'un facteur dix, l'impact sur les performances n'est que de 1, 2%. Ainsi, le deuxième niveau plus lent peut être constitué de mémoire moins chère, ou même une mémoire compressée. Cette approche ressemble à l'architecture IBM MXT précédemment décrite avec un cache SDRAM DDR de 32 Mo.

La même année, *Ekman et Stenström* ont fait une proposition de mémoire compressée matériellement [34]. Celle-ci se démarque principalement de l'approche d'IBM par l'utilisation de petits blocs de 64 octets.

#### Architecture

Ekman et Stenström sont partis de l'observation de Yang et Gupta [100] qu'une large partie des pages, des blocs et des mots sont nuls. Les mesures effectuées par Ekman et Stenström d'après des instantanés de la mémoire montrent qu'en moyenne 30% des blocs de 64 octets sont complètement nuls, et que 55% des octets sont nuls. Une version simplifiée de l'algorithme FPC proposé par Alameldeen et Wood [7, 8] est alors utilisée. Le taux de compression moyen sur les applications choisies est d'environ 0, 5.

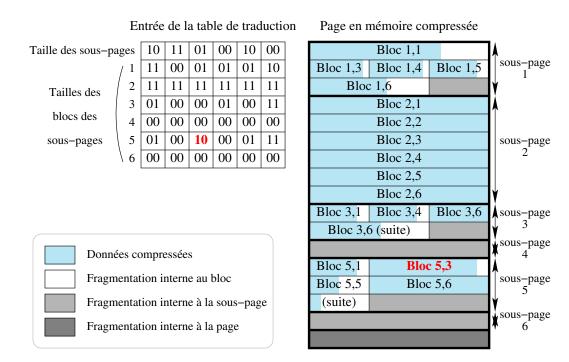

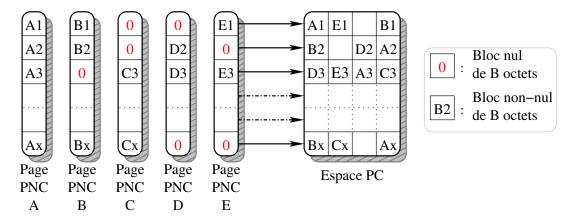

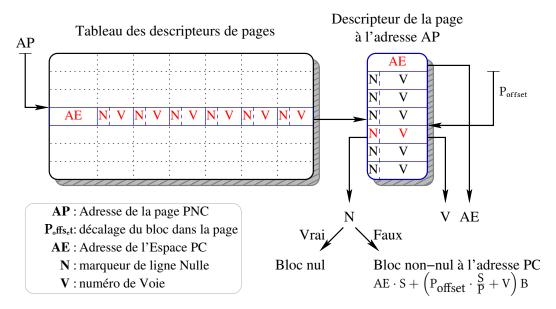

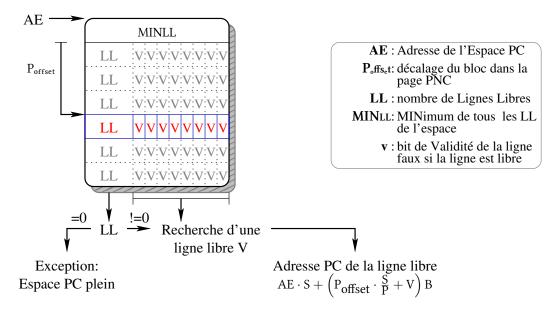

Lorsqu'un bloc de données est compressé, quatre tailles S sont considérées : 0, 22, 44 ou 64 octets. Ces tailles sont codées sur deux bits dans une table de traduction d'adresses. Une taille de 0 indique un bloc nul. Le bloc n'est alors pas alloué en mémoire.

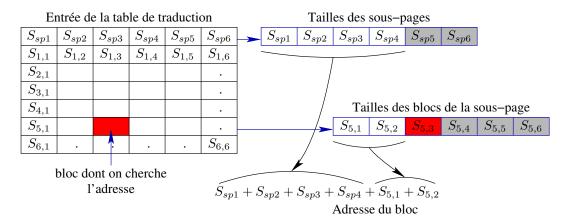

La principale complexité de la gestion de blocs de 64 octets est l'impossibilité d'associer un pointeur de 32 bits par bloc (6, 25% de l'espace mémoire serait utilisé pour la table d'indexation). Ekman et Stenström proposent de stocker les blocs contigus de façon séquentielle. Ainsi, la position  $P_x$  du bloc x peut se déduire d'après les tailles des blocs précédents.  $P_x = \sum_{i=0}^{x-1} S_i$ . Mais, afin de réduire le nombre d'additions nécessaires au calcul d'adresse, les pages sont divisées en sous-pages dont les tailles sont elles codées sur deux bits. Ekman et Stenström proposent d'utiliser quatre tailles de sous-pages : 256, 512, 768 et 1024 octets. La figure 1.7 page ci-contre représente le découpage des pages en sous-pages et blocs.

Le calcul de l'adresse d'un bloc est illustré sur la figure 1.8 page 32. L'adresse correspond à la somme des tailles des sous-pages précédentes et des blocs précédents au sein de la sous-page.

La gestion du changement de la taille d'un bloc compressé est assez délicate. Lorsque la taille d'un bloc compressé augmente et qu'il n'existe pas suffisamment d'espace libre après le bloc, tous les blocs suivants sont décalés, et éventuellement les sous-pages suivantes. La complexité de ce décalage est réellement importante, surtout si le bloc se situe en début de page. De plus, si la page est trop petite, elle doit être déplacée et allouée ailleurs.

Inversement, lorsque la taille d'un bloc compressée diminue, un décalage est également nécessaire. Mais celui-ci peut être interrompu si besoin, en contrepartie d'une fragmentation interne plus importante. Cependant, la fragmentation de l'espace libre au sein des blocs, des sous-pages et des pages permet d'absorber une partie des décalages.

Afin d'accélérer la recherche d'un bloc compressé, la table de traduction d'adresses est mise en cache au niveau du TLB. Cette structure occupe le double de la taille du TLB. Elle est accédée pour tout accès au L2.

#### **Performances**

L'utilisation de cette architecture permet de réduire en moyenne de 30% l'espace mémoire occupé par les applications simulées. Ce taux de compression de 30%, est donc

FIGURE 1.7 – Disposition des sous-pages et des blocs au sein d'une page. 4 tailles de sous-page et quatre tailles de bloc compressé sont possibles. La taille 00 correspondant à une taille nulle, le bloc n'est pas stocké dans la page.

largement inférieur au taux de compression de 50% permis par FPC. Ceci est dû à la fragmentation de l'espace libre. Les performances mesurées en Instructions Par Cycle (IPC) sont plutôt inférieures à celles d'une configuration sans mémoire compressée. L'écart est compris entre +0,5% (speedup) et -4,5% (speeddown) avec une moyenne à -0,5%.

#### Limitations

Cependant, l'architecture proposée n'est pas possible à mettre en œuvre telle que proposée car elle souffre de quatre défauts principaux.

Tout d'abord, la gestion des blocs dont la taille augmente est difficile. De nombreux décalages sont nécessaires. *Ekman et Stenström* proposent de les faire par accès DMA. Cela risque tout de même de saturer la bande passante mémoire.

Ensuite, l'espace libre est fortement fragmenté. Certes, la fragmentation permet souvent de diminuer le nombre de décalages nécessaires lorsque la taille d'un bloc augmente. Mais cela diminue d'autant l'efficacité de la compression.

De plus, l'éviction lors d'une réécriture différée d'un bloc du dernier niveau de cache semble avoir été oubliée. Lorsqu'un bloc est évincé, aucun accès TLB n'est réalisé. Il est donc impossible d'accéder au cache de la table de traduction d'adresse. Il faut donc au moins faire un aller-retour en mémoire pour obtenir la traduction d'adresse.

Figure 1.8 – Traduction d'adresse.  $S_{sp_i}$  est la taille de la sous-page i et  $S_{i,j}$  est la taille du je bloc de la ie sous-page. Exemple avec le calcul de l'adresse du  $3^e$  bloc de la  $5^e$  sous-page obtenu grâce aux tailles des 4 sous-pages et des 2 blocs précédents.

Enfin, cette architecture ne peut pas être utilisée sur un multiprocesseur. Les adresses qui transitent sur le bus sont des adresses en mémoire compressée. Il est impossible d'assurer la cohérence car l'adresse d'un bloc dépend de la taille des blocs le précédant. Pire, les blocs nuls n'ont pas d'adresse. Ils sont stockés directement dans la table de traduction. Pour la même raison, les entrées-sorties ne peuvent pas se faire en DMA.

En conclusion, il ressort de ces observations que la principale modification nécessaire à une mise en œuvre du schéma d'*Ekman et Stenström* permettant la traduction d'adresse lors des éjections du cache et lors des entrées-sorties est d'effectuer la traduction d'adresse dans le contrôleur mémoire et non dans le TLB.

#### 1.4.2.3 Autres propositions

#### Mesures de Kjelsø, Gooch et Jones

En 1996, *Kjelsø*, *Gooch et Jones* ont mesuré la compressibilité de la mémoire et ont proposé un compresseur matériel permettant d'obtenir un taux de compression de 0,5 avec une décompression plutôt rapide. Cependant, la compression est appliquée à des pages entières. La latence de décompression est donc critique. Ils ne proposent pas de mécanisme permettant la gestion des pages compressées.

### Proposition de Benini, Bruni, Macii et Macii

Benini, Bruni, Macii et Macii ont proposé [14, 15] en 2002 puis en 2004 d'utiliser une mémoire compressée afin de réduire la consommation des processeurs embarqués. Une partie de la mémoire est dédiée aux blocs compressés. Si le bloc de taille L une fois

compressé a une taille inférieure à un seuil S, il est stocké dans un emplacement de taille S. Le gain provient de  $S \leq L$ . Une seule taille de bloc est supportée, ce qui simplifie beaucoup la gestion des blocs compressés.

L'architecture proposée n'augmente pas l'espace disponible pour les applications, mais elle diminue la taille des communications. Les gains sur la consommation sont compris entre 7 et 26%.

#### Brevet de Moore

En 2003, *Moore* a déposé un brevet [66] sur une architecture dans laquelle la mémoire physique est compressée. S'agissant d'un brevet, peu de détails ont été présentés sur le fonctionnement de l'architecture, et aucun résultat n'a été communiqué. Le but de la compression est de diminuer l'utilisation de la bande passante mémoire. Il place la gestion de la mémoire compressée au sein du contrôleur mémoire.

### Compression du code

De très nombreuses propositions de compression de la zone de code des applications ont été faites. Elles sont principalement destinées à des architectures embarquées. La compression permet d'atteindre deux objectifs : diminuer le coût de fabrication et augmenter l'autonomie. La compression permet de diminuer la taille et donc le coût de l'EEPROM (ou mémoire flash) dans laquelle est stocké le programme. Elle permet aussi d'économiser de l'énergie. Si le processeur charge moins d'instructions, ou s'il fait moins d'accès à la mémoire principale, le système est plus économe en énergie et l'autonomie s'en trouve augmentée.

Dans certains cas, l'exécutable est complètement décompressé juste avant l'exécution [45, 28, 67, 16, 9, 44, 35]. Dans ce cas, l'objectif consiste seulement à diminuer la taille du code. La décompression peut être faite en logiciel.

Dans d'autres propositions [97, 19, 62, 61, 17, 99], le décodage peut s'effectuer par ligne de cache. Ces architectures permettent en général de diminuer la consommation d'énergie de la hiérarchie mémoire. La décompression est faite dans ce cas par un décompresseur matériel situé entre le cache et la mémoire.

Il existe même des publications [50, 60, 18] proposant d'effectuer le codage instruction par instruction. Dans ce cas, une architecture sans cache peut tout de même utiliser une mémoire compressée.

On peut aussi noter les jeux d'instructions *Thumb* [5] et *Thumb-2* présents sur certains processeurs ARM. Des instructions 16 bits représentant des instructions 32 bits avec des restrictions sur les opérandes sont utilisées pour diminuer la taille du code et l'utilisation de la bande passante mémoire.

La compression de code présente beaucoup moins de contraintes que la compression des données. Le code peut être compressé hors-ligne, par exemple lors de la compilation

ou juste après. Il n'y a donc pas de restriction sur la complexité de l'algorithme de compression qui peut être très lent. Seule la décompression qui est faite à l'exécution doit être rapide. Elle est généralement effectuée par un décompresseur matériel. De plus, aucune écriture n'est réalisée pendant l'exécution. Il n'y a donc pas de changement de taille des blocs compressés à gérer.

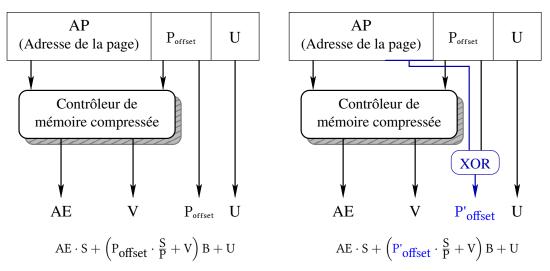

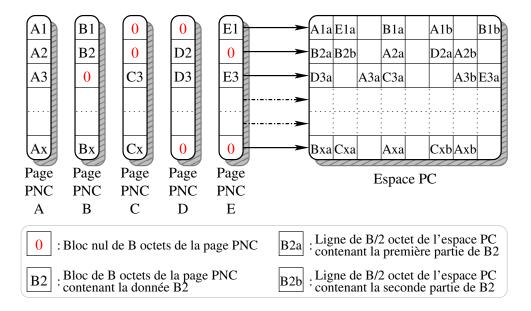

### 1.4.2.4 Formalisation de l'architecture des mémoires compressées

Afin de faire la synthèse des propositions précédemment décrites, nous allons définir l'architecture minimale commune aux mémoires compressées matériellement.

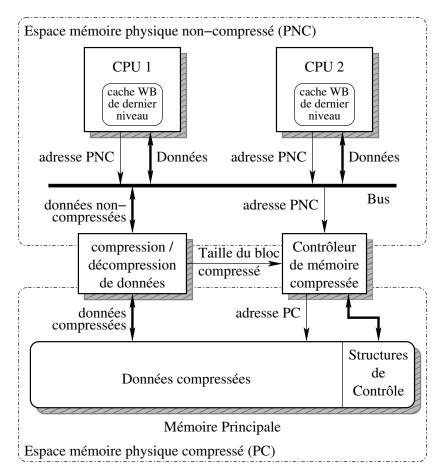

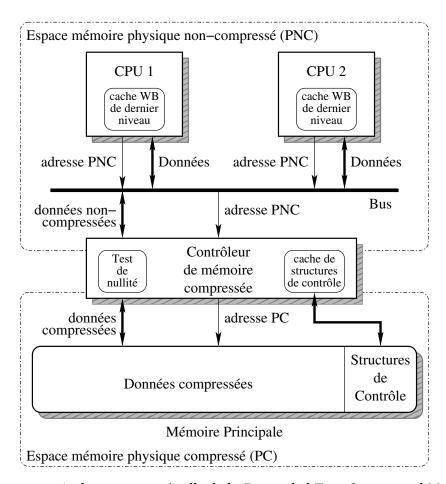

Tout d'abord, il convient de distinguer *deux domaines d'adressage*, que nous nommerons l'espace mémoire physique non-compressé (PNC) et l'espace mémoire physique compressé (PC). Toutes les transactions vues par le processeur ou par les entrées-sorties doivent être dans l'espace mémoire physique non-compressé. Le contrôleur de mémoire compressée assure la conversion des adresses de l'espace physique non-compressé en adresses dans l'espace physique compressé. Nous noterons ces adresses respectivement adresses PNC et adresses PC.

La figure 1.9 page ci-contre illustre ce modèle pour un multiprocesseur à bus partagé. Les processeurs n'ont accès qu'à des adresses PNC. La traduction s'effectue au niveau du contrôleur de mémoire compressée afin d'éviter les problèmes rencontrés par la solution proposée par *Ekman et Stenström*. Ce modèle convient aussi à un système distribué avec des paires d'espaces compressés et non-compressés.

### 1.4.2.5 Adaptations du système d'exploitation

D'après les propositions précédentes, le système doit être légèrement adapté lors de l'utilisation d'une mémoire compressée.

La compression matérielle de la mémoire ne demande que très peu de support du système d'exploitation. Celui-ci doit seulement être modifié pour éjecter des pages lorsque la mémoire compressée est pleine. Le taux de compression étant variable, la saturation n'arrive pas toujours au même instant. Le système d'exploitation doit donc avoir un compteur, ou doit recevoir un signal lui indiquant la saturation de mémoire.

### 1.4.3 Machines virtuelles

Récemment des travaux [24, 77, 76] ont montré une forte compressibilité des données dans les machines virtuelles Java. Ce taux de compression élevé a deux origines principales : l'allocation de tableaux et la copie de tableaux.

Lors de la création d'un tableau, une zone mémoire contiguë est implicitement allouée et initialisée à zéro. Toutes les cellules inutilisées du tableau occupent alors de l'espace. *Sartor et al.* ont alors proposé [77, 76] d'utiliser un niveau d'indirection supplémentaire et de découper le tableau *Arraylet* de taille fixe. Un *Arraylet* vide global est

**FIGURE 1.9** – Architecture matérielle des mémoires compressées. Les processeurs ne voient que des adresses dans l'espace non compressé (adresses PNC).

alors défini et partagé par tous les tableaux. Lors d'une écriture réelle par l'application sur l'*Arraylet* vide, celui-ci est recopié ailleurs.

Une fonctionnalité semblable existe déjà en C dans la *glibc* depuis de nombreuses années. La pagination est alors utilisée. Lors d'un appel à *calloc()*, un espace virtuel de la taille de la zone demandée est alloué mais une page physique seulement est réservée <sup>3</sup> et mise à zéro. Toutes les pages virtuelles pointent alors sur cette unique page physique. Lors d'une écriture un mécanisme de Copy-On-Write est utilisé. Grâce à la pagination, l'indirection est faite au niveau de la traduction d'adresse virtuelle en adresse physique, et l'*Arraylet* n'est autre qu'une page.

<sup>3.</sup> Une seule page physique est allouée, mais le reste de l'espace nécessaire est reservé dans le swap. Cela permet d'éviter la destruction de l'application par l'Out-Of-Memory-Killer lors d'une écriture

La deuxième source de redondance des données identifiée par *Sartor et al.* est la copie de tableau. Java ne prévoit pas de mécanisme de Copy-On-Write sur une partie d'un tableau. Le découpage des tableaux en *Arraylet* permet alors d'effectuer un Copy-On-Write et de ne copier qu'une partie des tableaux. La encore la glibc propose ce mécanisme depuis de nombreuses années grâce à la pagination. Lors d'un appel à *memcpy*, les pages communes à la donnée source et destination ne sont pas dupliquées mais marqués comme Copy-On-Write.

## Chapitre 2

## Mesure de l'utilisation des blocs nuls

Dans ce document, nous allons proposer des modifications de la hiérarchie mémoire permettant d'exploiter la présence de blocs nuls. Nous avons choisi une taille de bloc identique à la taille d'une ligne de cache, ici 64 octets. Ce choix permet une gestion aisée des blocs nuls puisqu'il n'est pas nécessaire d'utiliser de tampon pour adapter les différentes tailles de bloc manipulées.

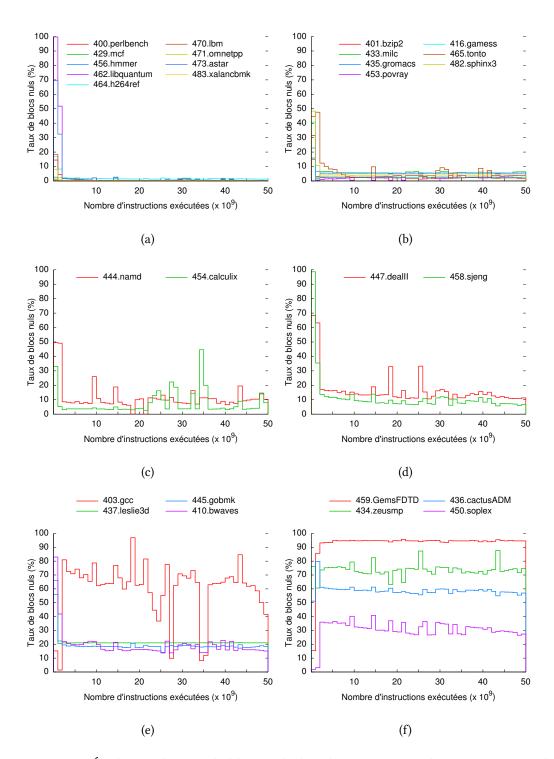

Dans ce chapitre, nous commençons par évaluer la proportion de blocs de 64 octets complètement nuls dans les accès aux différents niveaux de caches et à la mémoire. Dans un deuxième temps, nous mesurons l'évolution de ce taux tout au long de l'exécution. Pour finir, nous analyserons pourquoi des applications accèdent à des blocs nuls. Pour cela, nous allons regarder la provenance de ces blocs dans le code source de quelques applications des SPEC CPU 2006.

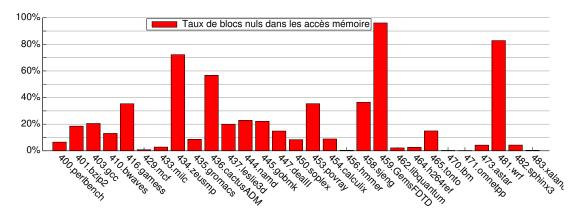

#### 2.1 Mesure du nombre d'accès à des blocs nuls

A l'aide du simulateur Sesc [73], nous avons mesuré le nombre d'accès à des blocs nuls pour les applications des suites SPEC CPU 2000 et 2006. Ces mesures ont été effectuées lors de l'exécution des cinquante premiers milliards d'instructions. Par souci de concision, seuls les résultats des applications des SPEC CPU 2006 sont détaillés. En effet, nos mesures ont montré que les applications des SPEC CPU 2000 adoptent toutes un comportement que l'on retrouve dans au moins l'une des applications des SPEC CPU 2006. Enfin, l'application 481.wrf se termine prématurément lors de son exécution dans Sesc, mais les mesures effectuées avec le simulateur Simics au chapitre 4 montrent qu'elle utilise de nombreux blocs nuls et qu'elle a un comportement proche de 459.GemsFDTD.

Nous avons choisi une durée de simulation suffisamment longue pour que les effets de l'initialisation soient négligeables. Nous le vérifierons dans la section 2.2. La hiérarchie mémoire que nous avons simulée est composée de trois niveaux de caches avec un L1

d'instruction de 64 Ko, un L1 de donnée de 32 Ko, un L2 unifié de 256 Ko et un L3 unifié de 1 Mo. La mémoire principale est choisie suffisamment grande pour contenir toute l'application et ses données.

L'environnement de simulation se base sur Sesc, un simulateur *cycle accurate* MIPS. Il sera décrit plus en détail dans la section 3.2.1 page 60 du chapitre sur le *Zero-Content Augmented Cache*.

|                | I     | DL1  |    |       | L2   |    |       | L3   |    | Mémoire |      |    |

|----------------|-------|------|----|-------|------|----|-------|------|----|---------|------|----|

| Application    | ANPKI | APKI | %  | ANPKI | APKI | %  | ANPKI | APKI | %  | ANPKI   | APKI | %  |

| 400.perlbench  | 0,1   | 346  | 0  | 0,0   | 6,4  | 1  | 0,0   | 1,1  | 4  | 0,0     | 0,6  | 6  |

| 401.bzip2      | 4,0   | 297  | 1  | 0,3   | 12,9 | 3  | 0,3   | 7,0  | 4  | 0,3     | 3,1  | 8  |

| 403.gcc        | 96,7  | 294  | 33 | 10,5  | 20,3 | 52 | 6,8   | 13,7 | 50 | 1,3     | 6,3  | 20 |

| 410.bwaves     | 101,4 | 292  | 35 | 2,7   | 13,9 | 19 | 1,4   | 4,6  | 30 | 1,4     | 4,6  | 30 |

| 416.gamess     | 7,0   | 301  | 2  | 0,3   | 5,4  | 6  | 0,0   | 0,1  | 22 | 0,0     | 0,0  | 46 |

| 429.mcf        | 0,3   | 372  | 0  | 0,3   | 53,0 | 1  | 0,3   | 43,4 | 1  | 0,3     | 39,1 | 1  |

| 433.milc       | 3,7   | 404  | 1  | 1,6   | 24,5 | 7  | 1,6   | 24,2 | 7  | 1,6     | 24,2 | 7  |

| 434.zeusmp     | 108,5 | 258  | 42 | 16,3  | 22,9 | 71 | 5,0   | 6,9  | 73 | 4,4     | 6,1  | 73 |

| 435.gromacs    | 2,3   | 350  | 1  | 0,4   | 8,4  | 5  | 0,1   | 1,6  | 6  | 0,1     | 0,6  | 9  |

| 436.cactusADM  | 127,2 | 545  | 23 | 3,5   | 6,4  | 55 | 2,9   | 4,9  | 59 | 2,8     | 4,7  | 59 |

| 437.leslie3d   | 50,2  | 280  | 18 | 5,4   | 21,9 | 25 | 3,4   | 15,7 | 22 | 2,9     | 14,2 | 20 |

| 444.namd       | 0,2   | 282  | 0  | 0,0   | 8,6  | 0  | 0,0   | 0,2  | 15 | 0,0     | 0,1  | 23 |

| 445.gobmk      | 10,5  | 293  | 4  | 0,9   | 9,8  | 9  | 0,4   | 1,9  | 21 | 0,2     | 0,7  | 24 |

| 447.dealII     | 24,8  | 306  | 8  | 1,6   | 5,7  | 27 | 0,3   | 2,2  | 15 | 0,2     | 1,2  | 18 |

| 450.soplex     | 65,4  | 255  | 26 | 9,6   | 37,2 | 26 | 9,3   | 31,4 | 30 | 8,4     | 24,8 | 34 |

| 453.povray     | 0,4   | 349  | 0  | 0,0   | 8,5  | 0  | 0,0   | 0,2  | 3  | 0,0     | 0,0  | 42 |

| 454.calculix   | 1,9   | 294  | 1  | 0,2   | 5,6  | 3  | 0,1   | 3,0  | 4  | 0,1     | 0,7  | 12 |

| 456.hmmer      | 0,1   | 326  | 0  | 0,0   | 7,3  | 0  | 0,0   | 4,2  | 0  | 0,0     | 3,7  | 0  |