# Study of Active Filters Topologies for Telecommunications Applications

Cristian Andriesei

#### ▶ To cite this version:

Cristian Andriesei. Study of Active Filters Topologies for Telecommunications Applications. Micro and nanotechnologies/Microelectronics. Université de Cergy Pontoise, 2010. English. NNT: . tel- 00560292

# HAL Id: tel-00560292 https://theses.hal.science/tel-00560292

Submitted on 27 Jan 2011

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# PhD THESIS

#### prepared at

ETIS UMR 8051 Laboratory, Ecole Nationale Supérieure de l'Electronique et de ses Applications, Cergy-Pontoise University & Centre National de la Recherche Scientifique, FRANCE

SCS laboratory, Technical University "Gheorghe Asachi" / ETTI,

Iași, ROMANIA

and presented at

Cergy-Pontoise University

Technical University "Gheorghe Asachi" of Iași

A dissertation submitted on

December 2<sup>nd</sup>, 2010

in partial fulfilment of the requirements for the degree of

**Doctor in Sciences and Techniques**Specialized in Electronics

# Study of Active Filters Topologies for Telecommunications Applications

#### Cristian ANDRIESEI

Advisors Pr. Liviu GORAŞ, University of Iaşi, Romania

Pr. Farid TEMCAMANI, ENSEA, Cergy, France

Reviewers Pr. Gheorghe BREZEANU, University of Bucharest, Romania

Pr. Jean-Marie PAILLOT, University of Poitiers, France

Examiners Pr. Daniel PASQUET, ENSEA, Cergy, France

Dr. Cédric DUPERRIER, ENSÉA, Cergy, France

Dr. Bruno DELACRESSONNIERE, ENSEA, Cergy, France (co-advisor)

To the memory of my father April, 2010

You see, wire telegraphy is a kind of very, very long cat. You pull his tail in New York and his head is meowing in Los Angeles. Do you understand this? And radio operates exactly the same way: you send signals here; they receive them there. The only difference is that there is no cat.

Albert Einstein, 1879–1955

# Study of Active Filters Topologies for Telecommunications Applications

Ву

#### Cristian ANDRIESEI

#### **ABSTRACT**

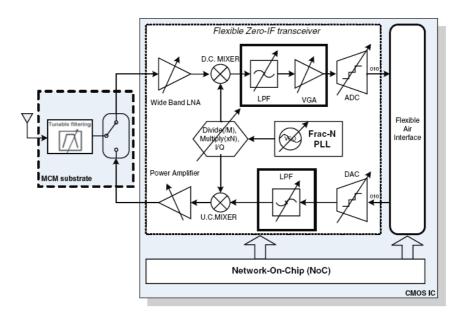

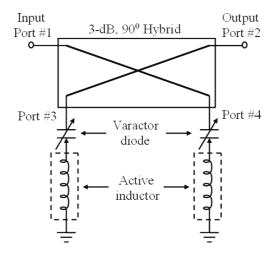

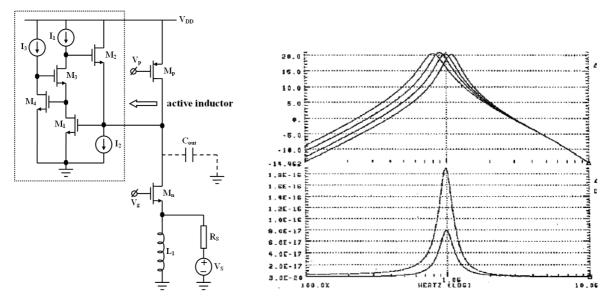

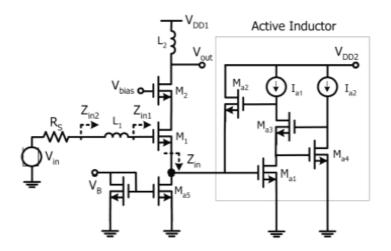

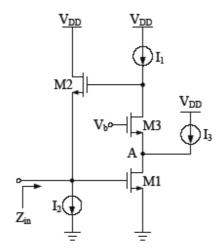

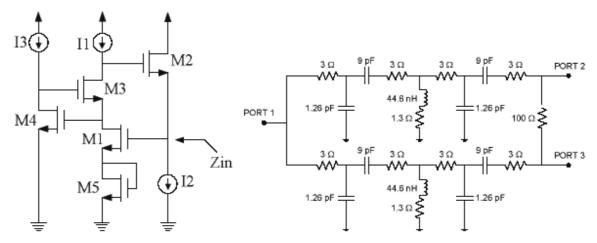

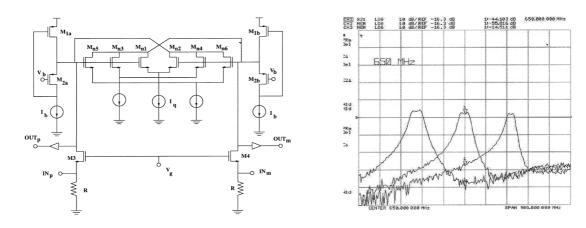

The scope of this thesis is to propose solutions to improve the performances of the CMOS transistor only simulated inductors (TOSI) aiming RF filtering applications. We are interested in TOSI architectures because they prove better performances than the classical  $g_m$ –C filters, being superior with respect to the number of transistors, power consumption, frequency capability and chip area. Furthermore, TOSI architectures have many potential applications in RF design.

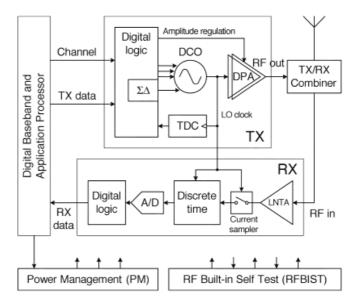

In the general context of the multi-standard trend followed by wireless transceivers, TOSI based RF filters may offer the possibility of implementing reconfigurable devices. However, satisfying the telecommunications requirements is not an easy task therefore high order TOSI based filters should be implemented. Consequently, using good second order TOSI cells is a matter of the utmost importance and we propose a novel quality factor tuning principle which offers an almost independent tuning of self resonant frequency and quality factor for simulated inductors. An improved TOSI architecture with increased frequency capability is also reported.

Thesis Supervisors: Liviu Goraș, Farid Temcamani and Bruno Delacressonnière

## **Acknowledgments**

This thesis may have been written well enough, had sufficient number of relevant references, transmit interesting ideas and valuable information or maybe not but what this thesis has to prove is the intellectual maturity and design experience I have attained during this doctoral program and mandatory for any research based post doctoral activity (educational research or in industry). Consequently, I express first my acknowledgements to my Romanian adviser, Prof. Liviu Goraş, for his guidance, patience, effort, enthusiasm and support of any kind to create a perfect research climate while conducting the research activity. The same appreciation goes to the French advisers, Mr. Farid Temcamani and Bruno Delacressonnière for their guidance, valuable advices and effort in having this thesis finished.

My acknowledgements go also to the older team ECIME for receiving me in France. I would also like to express my gratitude to Prof. Myriam Ariaudo for her advice in choosing this research direction but also for making this co–tutelle de thèse possible.

I would like to thank Siemens PSE Romania and the Romanian Higher Education Research National Council for providing financial support that had made my research work easier and this thesis finished.

I thank also Prof. Adriana Sîrbu, Tecla Goraş and Valeriu Munteanu for their support in my educational activity.

I am grateful to the older SCS team (including Marius, Emilian and Sergiu) for the nice working atmosphere and knowledge gathered there. I thank also Camelia for her encouragement and infinite sense of humor.

Finally, I thank my family for their constant support, care, love and understanding.

# **TABLE OF CONTENTS**

| List of Tables                                                                                                                     |   |

|------------------------------------------------------------------------------------------------------------------------------------|---|

| Abbreviations and Symbols                                                                                                          |   |

| 1. INTRODUCTION                                                                                                                    |   |

| 1.1 Motivation                                                                                                                     |   |

| 1.2 Thesis Outline                                                                                                                 |   |

| 2. WIRELESS TELECOMMUNICATIONS STANDARDS AND RF TRANSCEIVERS                                                                       |   |

| 2.1 Introduction                                                                                                                   |   |

| 2.2 Telecommunications Standards and Frequency Allocation 2.2.1 2G/3G/4G Mobile Systems 2.2.2 Wireless LAN Standards (IEEE 802.11) |   |

| 2.2.2 Wireless LAN Standards (IEEE 802.11)                                                                                         |   |

| 2.2.4 Zigbee Standard (IEEE 802.15.4)                                                                                              |   |

| 2.2.5 GPS Applications                                                                                                             |   |

| 2.2.6 WiMAX Applications                                                                                                           |   |

|                                                                                                                                    |   |

| 2.3 RF Front-ends Receivers and Multistandard Trend                                                                                |   |

| 2.3.1 Super–heterodyne Transceiver                                                                                                 |   |

| 2.3.3 Low-IF Receiver                                                                                                              |   |

| 2.3.4 Software Defined Radio (SDR) Architectures                                                                                   |   |

| 2.3.5 SAW-less Wireless Transceivers                                                                                               |   |

| 2.4 CONCLUSION                                                                                                                     |   |

| 2.5 REFERENCES                                                                                                                     |   |

| 3. GYRATOR BASED TRANSISTOR ONLY SIMULATED INDUCTORS FOR RF DESIG                                                                  | N |

| 3.1 Introduction                                                                                                                   |   |

| 3.2 Gyrator model                                                                                                                  |   |

| 3.2.1 Ideal Gyrator and its Applications in Circuit Design                                                                         |   |

| 3.2.2 Gyrator Practical Implementations                                                                                            |   |

| 3.2.3 The Gyrator Power Transfer                                                                                                   |   |

| 3.2.4 Gyrator and the Series/Parallel Simulated Inductor Equivalent Model                                                          |   |

| 3.2.5 The Effect of the Parasitic Capacitors on the Simulated Inductor                                                             |   |

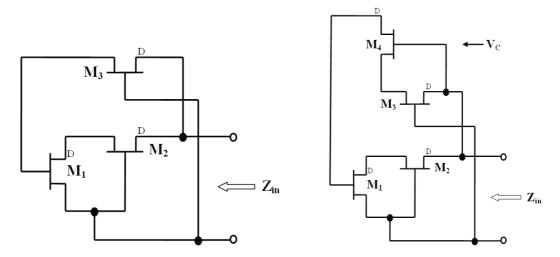

| 3.3 Proposed TOSI Architectures for RF Design                                                                                      |   |

| 3.3.1 TOSI Concept                                                                                                                 |   |

| 3.3.2 TOSI Architectures using MESFET Transistors                                                                                  |   |

| 3.3.3 CMOS TOSI Architectures                                                                                                      |   |

| 3.4 TOSI Based Preselective Filter Solutions                                                                                       | 1 |

| 3.4.1 2 <sup>nd</sup> Order TOSI Based Filters                                                                                     | 1 |

| 3.4.2 RF Filters with Multiple TOSI Cells                                                                                          | 1 |

| 3.5 CONCLUSION                                                                                                                     | 1 |

| 3.6 REFERENCES                                             | 115 |

|------------------------------------------------------------|-----|

| 4. FREQUENCY RESPONSE IMPROVEMENT OF CMOS TOSIs            | 123 |

| 4.1 Introduction                                           | 123 |

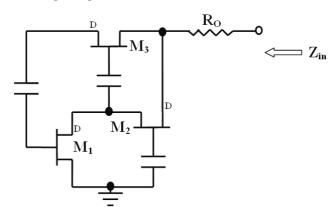

| 4.2 Simulated Inductor Equivalent Passive Model            | 124 |

| 4.2.1 CMOS Transistor Small-Signal Models                  | 124 |

| 4.2.2 RLC TOSI Passive Equivalent Model                    | 129 |

| 4.2.3 Improved RLC TOSI Equivalent Passive Model           | 132 |

| 4.3 Frequency Enhancement Solutions                        | 135 |

| 4.3 Frequency Enhancement Solutions                        | 135 |

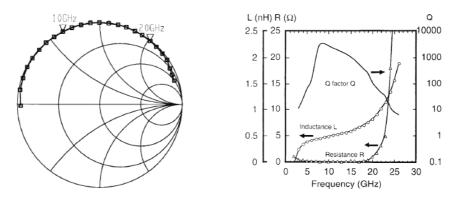

| 4.3.2 Proposed Method for $\omega_0$ –Q Independent tuning | 137 |

| 4.4 Simulated Inductor with Improved Frequency Response    | 159 |

| 4.4.1 Active Inductor with Supplementary Gate Resistance   | 159 |

| 4.4.2 Active Inductor with Improved Biasing Scheme         | 164 |

| 4.5 CONCLUSION                                             | 166 |

| 4.6 REFERENCES                                             | 168 |

| 5. Conclusion and Future Work                              | 170 |

# **List of Tables**

| Table 1 Overview of analog cellular mobile radio (1G)                              | 25  |

|------------------------------------------------------------------------------------|-----|

| Table 2 Overview of digital cellular mobile radio (2G)                             | 25  |

| Table 3 Overview of the most important 3G wireless standards                       | 26  |

| Table 4 WLAN standard and its implemented amendments                               | 28  |

| Table 5 Bluetooth Standard Specifications                                          | 30  |

| Table 6 Comparison of WiMAX and other broadband technologies [2.44]                | 33  |

| Table 7 Three ways of implementing UWB systems                                     | 34  |

| Table 8 Three ways of implementing UWB systems                                     | 35  |

| Table 9 Maximum values of the DC blocking capacitors (pF)                          | 146 |

| Table 10 TOSI Frequency enhancement with gate resistance                           | 161 |

| Table 11 The influence of the floating voltages on the frequency–Q interdependence | 160 |

## **Abbreviations and Symbols**

1G First Generation Wireless Technology

3G Third Generation Wireless Technology

3GPP 3<sup>rd</sup> Generation Partnership Project

4G Fourth Generation Wireless Technology

AC Alternating current

ADC Analog-to-Digital Converter AES Advanced Encryption Standard

AM Amplitude Modulation

AMPS Advanced Mobile Phone System

ASIC Application—Specific Integrated Circuit

BAW Bulk Acoustic Wave

BB Baseband BiCMOS Bipolar CMOS

BOK Bi-Orthogonal Keying

BPF Bandpass Filter

BPSK Bipolar PSK

CCK Complementary code keying CCO Current controlled oscillator

CD Common Drain

CDMA Code division multiple access

CG Common Gate

CMOS Complementary metal-oxide semiconductor

CS Common Source

DAC Digital—to—Analog Converter DCR Direct Conversion Receiver

DC Direct current

DCS Digital Cellular Service

DECT Digital Enhanced Cordless Telecommunications

DL Downlink

DoD Department of Defense

DPSK Differential PSK DQPSK Differential QPSK

DSP Digital Signal Processor

DSSS Direct—sequence spread spectrum

EDGE Enhanced Data rates for GSM Evolution

EGSM Extended GSM

ESA European Space Agency

ETACS Extended Total Access Communication System

FCC Federal Communications Commission

FDD Frequency—division duplexing FDMA Frequency division multiple access

FDNR Frequency Dependent Negative Resistance

FET Field-effect transistor

FHSS Frequency-Hopping Spread Spectrum

FM Frequency Modulation

FPGA Field–Programmable Gate Array

FSK Frequency–Shift Keying

GaAs Gallium arsenide

GFSK Gaussian Frequency–Shift Keying

GIC General Impedance Converter

GLONASS Global Navigation Satellite System

GMSK Gaussian MSK

GNSS Global Navigation Satellite Systems

GPRS General Packet Radio Service

GPS Global Positioning System

GSM Global Systems for Mobile Communications

HPSK Hybrid PSK

HSDPA High—Speed Downlink Packet Access (3.5G)

IEEE Institute of Electrical and Electronics Engineers

IM3 Third-Order Inter-Modulation

IMEC Interuniversity Microelectronics Centre

IIP2 Second-order Intermodulation Intercept Point

IIP3 Third-order Input Intercept Point

Third-order Intermodulation Intercept Point

IP3 Third–order Intercept Point IF Intermediate Frequency

IMT2000 International Mobile Telecommunications—2000

IS-95 Interim Standard 95 (cdmaOne)

ISM Industrial, Scientific, and Medical

LAN Local area network

LNA Low noise amplifier

LO Local Oscillator

M-BOK M-ary BOK

MEMS Micro-Electro-Mechanical Systems

MESFET Metal Semiconductor FET MIMO Multiple-Input, Multiple-Output

MMIC Monolithic Microwave Integrated Circuits

NF Noise Figure

NIC Negative Impedance Converter

NMOS n-channel MOSFET

NMT Nordic Mobile Telephony

NRZ Non-return-to-zero

OFDM Orthogonal frequency—division multiplexing

OFDMA Orthogonal Frequency—Division Multiple Access

OQPSK Offset QPSK

OTA Operational Transconductance Amplifier

PA Power Amplifier

PCS Personal Communications System

PDC Personal Digital Cellular PMOS p-channel MOSFET PSK Phase Shift Keying QAM Quadrature amplitude modulation QPSK Quadrature Phase Shift Keying

Rx Receiver

SAW Surface Acoustic Wave

SDD-Al SourceDegenerated Differential Active Inductor

SDR Software defined radio

SiGe Silicon—germanium

SMR Specialized mobile radio

SNR Signal—to—noise ratio

TACS Total Access Communication System

TAI Tunable Active Inductor

TDD Time Division Duplexing

TDM Time Division Multiplexing

TDMA Time Division Multiple Access

THD Total Harmonic Distorsion

TOI Third—order Intercept Point

TOSI Transistor only simulated inductor

UL Uplink

UMTS Universal Mobile Telecommunications System

UWB Ultra Wide Band

VCO Voltage—controlled oscillator

VHF Very High Frequency (30 MHz–300 MHz)

WCDMA Wideband CDMA

WiMAX Worldwide Interoperatibility for Microwave Access

WLAN Wireless Local Area Network

WPAN Wireless personal area network

WWiSE World Wide Spectrum Efficiency

# 1. INTRODUCTION

#### 1.1 Motivation

The telecommunications market requirements and continuous technology development impose a continuous research for both baseband and RF transceiver sides. During the last three decades, telecommunications transceivers evolved from entirely analog 1G terminals (AM and FM transmitters) to multistandard wireless devices with mixed digital baseband - analog front-end parts, the fourth generation (4G) being expected. On the transceiver side, the filtering part (active and passive) had an important contribution to the transceiver reconfigurability and smaller size. However, if the analog baseband filtering does not impose problems in implementing reconfigurable terminals, the RF passive filtering still represents a challenge. Thus, the surface acoustic wave (SAW) RF filters used in any wireless transceiver are external, bulky and offer no frequency tuning opportunity therefore, decreasing the customer satisfaction degree against size and device portability. Although SAW filters are cheap, the final cost for a multi-standard terminal is greatly increased since at least 8 such filters are used for different filtering operations. Many passive (MEMS), pseudo-passive (Q-enhanced LC) and active (g<sub>m</sub>-C) solutions have been proposed until now in literature but no one can beat the excellent frequency performances offered by the SAW filters. A promising small size, low power entirely active implementation makes use of transistor only simulated inductors (TOSI) which have the main benefit of being reconfigurable devices. These architectures are addressed in this research.

#### 1.2 Thesis Outline

The content of this thesis, presented in a very concise form, covers three different topics as follows.

Since filtering in telecommunications is envisaged, Chapter 2 is entirely dedicated to the telecommunications field. The first section is a brief description at basic level (due to size constraints) of telecommunications standards, covering frequencies up to 5 GHz. The interest in this regard are the frequency allocation and attenuation requirements for particular applications since these represent key aspects for the RF filtering design. Other

standard specifications regard different transceiver blocks, like the modulation scheme which becomes important for the power amplifier design but also the low noise amplifier. An overview of the wireless transceiver architectures is presented in the second section. Since hundreds of papers and tens of books have been reported in literature covering the transceiver architectures and design, an overview of RF transceivers is beyond the scope of this thesis. Only a concise, clear and up to date review of RF transceivers in a form that synthesizes the relevant information from a great number of sources but also describe the current multi–standard trend is given.

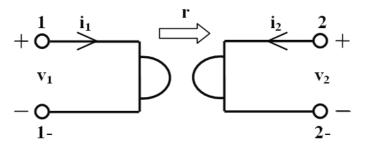

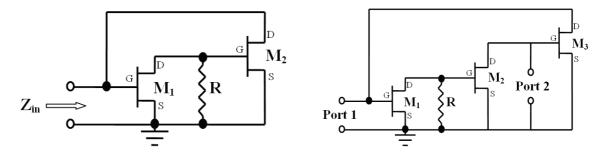

Chapter 3 covers the gyrator concept and is intended to be a 'state of the art' regarding the concept of 'transistor only simulated inductor'. All TOSI architectures reported in literature and mentioned in this thesis envisage applications in the GHz range thanks to their frequency capability. These capacitorless simulated inductors represent promising architectures for RF filtering applications and not only, since their successful use in implementing CCOs, LNAs and bandpass amplifiers has been reported in literature.

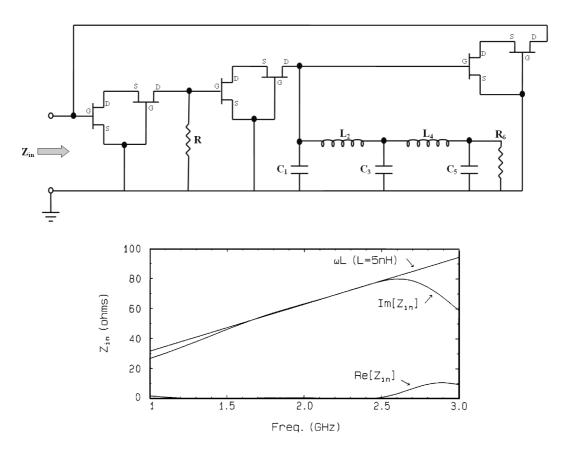

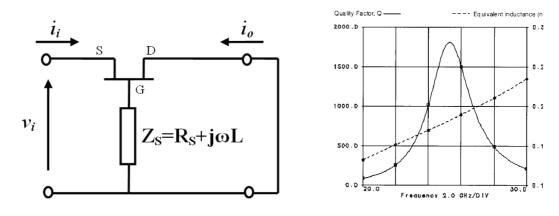

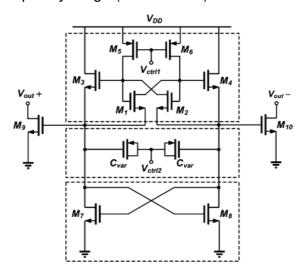

A more detailed insight into CMOS simulated inductors is provided in Chapter 4 where the TOSI frequency behavior is addressed. The main contributions for this research are presented in this final chapter.

A final conclusion is drawn at the end of this thesis in Chapter 5.

# 2. WIRELESS TELECOMMUNICATIONS STANDARDS AND RF TRANSCEIVERS

#### 2.1 Introduction

In this introductory chapter, the most common wireless telecommunications standards in the frequency band up to 5 GHz are presented. Since a detailed presentation of each standard is beyond the scope of this thesis, more details can be found in the references. The reason of introducing this review chapter is that any engineering problem on RF transceivers design requires a corresponding insight on the telecommunications standard at least at basic level.

Two reasons imposed taking into consideration the frequency of 5 GHz as the maximum frequency:

- 1) The widest spread wireless implemented standards aiming civilian applications which represent also the most important part of the telecommunications market are represented by GSM/3G, WiMAX, WLAN and GPS applications, all operating in the lower microwave spectrum. The first UWB frequency band belongs to this spectrum too.

- 2) Much research has been devoted for developing different RF Front-ends, aiming the low frequency microwave applications. Thus, at least 350 papers submitted to different journals and conferences, dedicated to different wireless transceiver architectures, may be counted from 1990 to 2010.

The continuous expanding of the CMOS technology compared to other technologies (GaAs, SiGe) [2.1]...[2.5] due to its low cost, small size but also the increasing cut-off frequency, facilitated the implementation of high speed digital circuits and competitive RF CMOS circuits. However, this is not the case for higher frequencies, aiming radar applications (22–29 / 76.5 / 77–81 GHz), where RF CMOS technology is inferior to SiGe BiCMOS in terms of cut-off frequency and sensitivity to parasitics and layout configurations [2.6]. In any case, the continuous technology scaling will help CMOS technology to surpass these issues when it reaches the quantum limit, expected to be 2036 [2.7]. It is difficult to say how the RF circuits will be designed in twenty six years but if the software defined radio (SDR) becomes reality then a mixing between SDR and perhaps quantum computing may constitute an exciting transceiver.

Most papers proposed until now in the literature and dedicated to CMOS RF applications envisage frequencies up to 5 GHz (0.35 µm, 0.18 µm) but there are RF circuits implemented in smaller CMOS processes (130 nm, 95 nm, 65 nm) working at higher frequencies [2.8]...[2.13], as well. Through a careful design of the baseband part by implementing efficient algorithms (coding and modulation) to fulfill the system level design requirements in terms of SNR, fading and interference minimization, the RF analog part is also minimized [2.14]. An important contribution to the transceiver design is added by an efficient antennas system design that can simplify the overall circuit design (at circuit level) while improving the coverage and network capacity [2.15]...[2.18] (at system level). In other words, through a conjugate effort of telecommunications engineers and RF/analog designers, the transceivers performances are significantly improved and the path of truly inexpensive global multistandard terminals is opened.

Regarding the spectrum allocation, there are many differences between the frequencies bands allocated to the same standard over the world thus raising many problems when designing worldwide reconfigurable devices. The spectrum allocation in Europe for telecommunications applications is given in [2.19] being very difficult to be reproduced here due to its irregular allocation.

A very short review of wireless standards in the 5 GHz band is presented in the following sections together with a detailed overview of different transceiver architectures.

## 2.2 Telecommunications Standards and Frequency Allocation

#### 2.2.1 2G/3G/4G Mobile Systems

The mobile telecommunications represent an important part of the telecommunications market with billions of users over the world (3 billions in 2008 and 4 billions in 2009) and even increasing benefits. They knew a continuous expanding history, beginning with the first generation analog system 1G, continuing with digital generation (2G) and achieving 3G nowadays thus opening the path for the future 4G networks. A brief review [2.20]...[2.22] of the spectrum allocation and parameters for 1G and 2G mobile implementations is presented in the following tables (Table 1 and 2).

While 2G systems were focused on voice data transmission only, the third generation 3G systems give the opportunity of simultaneous transfer of both voice (telephone call) and non-voice data while by offering low cost and high-speed Internet

services (WLAN) through mobile connectivity (downloading information, e-mail, instant messaging).

| Parameter        | C 450        | NMT 450     | NMT 900     | TACS    | ETACS   | AMPS    |

|------------------|--------------|-------------|-------------|---------|---------|---------|

| Original country | Germany      | Scandinavia | Scandinavia | GB      | GB      | USA     |

| Standardized by  | DBP Telecom  |             |             | CRAG    | CRAG    | FCC     |

| Introduced in    | 1985         | 1981        | 1986        | 1984    |         | 1983    |

| Uplink [MHz]     | 450.3-454.74 | 453–457.5   | 890–915     | 890–915 | 872–905 | 824-849 |

| Downlink [MHz]   | 461.3–465.74 | 463–467.5   | 935–960     | 935–960 | 917–950 | 869-894 |

| Channel spacing  |              |             |             |         |         |         |

| [KHz]            | 20           | 25 (20)     | 25 (12.5)   | 25      | 25      | 30      |

| Access method    | FDMA         | FDMA        | FDMA        | FDMA    | FDMA    | FDMA    |

| Modulation       | FM           | FM          | FM          | FM      | FM      | FM      |

| Cell diameter    |              | 15–40 km    | 2–20 km     |         |         |         |

**Table 1** Overview of analog cellular mobile radio (1G)

| Standard          | Digital cellular telephony (voice/data) |                             |  |  |

|-------------------|-----------------------------------------|-----------------------------|--|--|

|                   | GSM                                     | cdmaOne                     |  |  |

|                   | GSM850                                  |                             |  |  |

|                   | DL(869-894)-UL(824-849)                 | DL(869-894)-UL(824-849)     |  |  |

|                   | GSM900                                  |                             |  |  |

| Frequency         | DL(935-960)-UL(890-915)                 |                             |  |  |

| Range (MHz)       | GSM1800 (DCS)                           |                             |  |  |

|                   | DL(1805-1880)-UL(1710-1785)             |                             |  |  |

|                   | GSM1900 (PCS)                           |                             |  |  |

|                   | DL(1930-1990)-UL(1850-1910)             | DL(1930-1990)-UL(1850-1910) |  |  |

|                   | PDC 800                                 |                             |  |  |

|                   | DL(810-888)-UL(893-958)                 |                             |  |  |

|                   | PDC1500                                 |                             |  |  |

|                   | DL(1477-1501)-UL(1429-1453)             |                             |  |  |

|                   | GMSK                                    |                             |  |  |

| Modulation        | DQPSK (PDC)                             | QPSK/OQPSK                  |  |  |

|                   | 8-PSK (EDGE only)                       |                             |  |  |

| Multiple access   | TDMA/FDMA                               | CDMA/FDMA                   |  |  |

| Duplex (UL/DL)    | FDD                                     | FDD                         |  |  |

| Channel bandwidth | 200 KHz / 25 KHz (PDC)                  | 1.25 MHz                    |  |  |

|                   | 14.4 kbit/s                             | 14.4 kbit/s (IS-95-A)       |  |  |

| Peak data rate    | 53.6–114 kbit/s (GPRS)                  | 115.2 kbit/s (IS-95-B)      |  |  |

|                   | 384 kbit/s (EDGE)                       |                             |  |  |

**Table 2** Overview of digital cellular mobile radio (2G)

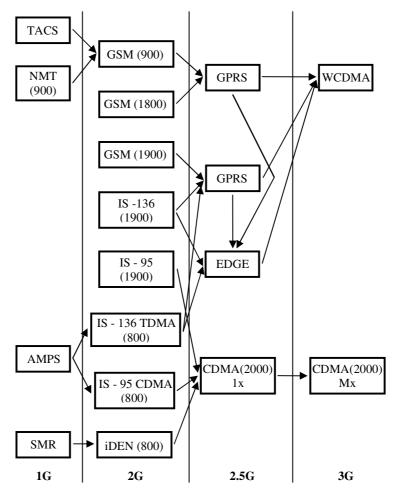

The main supplementary services specific to 3G networks are: Mobile TV, Video Conferencing, Tele-medicine, Location Based Services and Video on Demand. The evolution of mobile technology from the second phase to the third one (with specifications regulated by IMT-2000), is represented by the chart given in Fig. 2.1 while the allocated spectrum is given in Table 3.

Fig. 2.1 IMT-2000 Specs

| G <sub>4</sub> 1 1 | Digital cellular telephony (voice/data) |                             |             |  |

|--------------------|-----------------------------------------|-----------------------------|-------------|--|

| Standard           | cdma2000                                | WCDMA                       | WCDMA       |  |

|                    |                                         | 3GPP/FDD                    | 3GPP/TDD    |  |

| Frequency          | 450; 700                                |                             | 2010-2025   |  |

| range              | 800; 900                                | DL(2110-2170);UL(1920-1990) | 1900-1920   |  |

| (MHz)              | 1700; 1800                              | DL(1930-1990);UL(1850-1910) | 1930-1990   |  |

|                    | 1900; 2100                              | DL(1805-1880);UL(1710-1785) | 1850-1910   |  |

|                    |                                         |                             | 1910-1930   |  |

| Modulation         | QPSK, OQPSK                             | UL: Dual BPSK               | UL+DL: QPSK |  |

|                    | HPSK                                    | DL: QPSK, 16QAM             | DL: 8PSK    |  |

| Multiple           | CDMA                                    | CDMA/FDMA                   | TDD         |  |

| access             |                                         |                             |             |  |

| Duplex             | FDD                                     | FDD                         | FDD         |  |

| Channel            | 1.25 MHz                                | 5 MHz                       | 5 MHz       |  |

| bandwidth          |                                         |                             |             |  |

| Peak               | 307.7 kbit/s                            | 2 Mbit/s                    | 2 Mbit/s    |  |

| data               | (CDMA2000 1x)                           | 10 Mbit/s                   | 10 Mbit/s   |  |

| rate               | 2.4 Mbit/s                              | (HSDPA)                     | (HSDPA)     |  |

Table 3 Overview of the most important 3G wireless standards

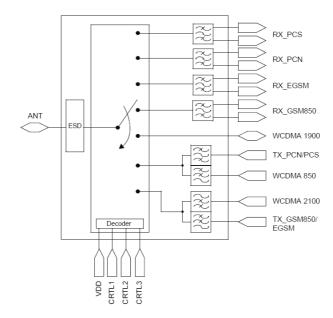

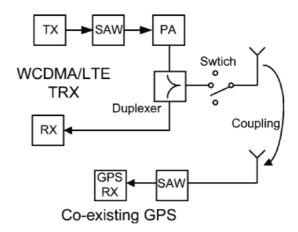

Different 3G bands (8 frequency bands) are regulated over the world a thing that makes the design of multistandard mobile terminals much more difficult. In Europe, the 2100 MHz (W–CDMA) frequency band is established as UMTS band, with 1920–1980 MHz for uplink and 2110–2170 MHz for downlink. The knowledge of these frequencies is of utmost importance when designing RF transceivers aiming 2G, 2.5G and 3G multistandard mobile terminals. It is obvious that regarding the RF filtering part for these mobile transceivers a large number of SAW RF preselective filters are used, with negative effects on the final product cost. Moreover, the out-of-band attenuation requirements in the case of mobile transceivers are more stringent than for other wireless standards. Beside the filtering issue, supplementary problems are rising on the transceiver part since different modulation schemes and power requirements are particular to each telecommunications standard with negative effects on the transmitter linearity, mainly in the case of the power amplifier. From this point of view, the practical design of a multistandard transceiver is by far not an easy task.

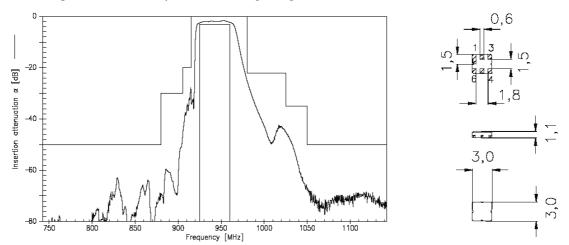

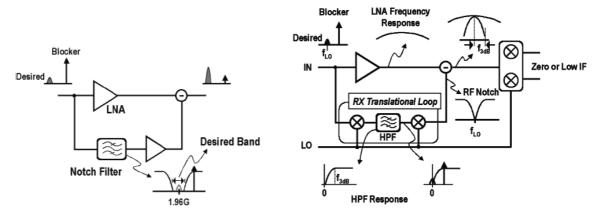

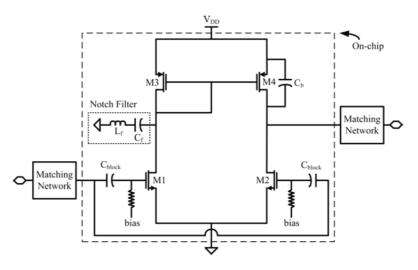

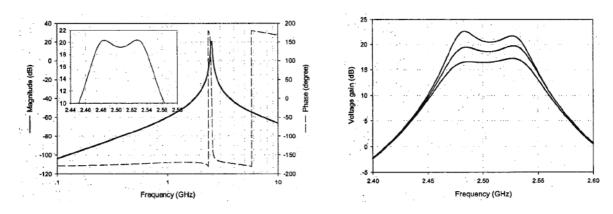

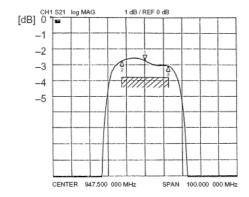

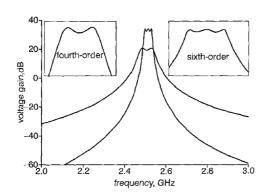

The frequency response of a SAW filter [2.23] satisfying the EGSM spectrum requirements for the frequency band 925–960 MHz ( $f_0$ =942.5 MHz) is shown in Fig. 2.2, not easy to obtain. Such frequency characteristic, not easy to obtain, should be envisaged if an active implementation is researched. The filter is  $50\Omega$  input and output matched. Other filtering solutions are presented in [2.24].

Fig. 2.2 B4141 SAW EGSM filter frequency response and chip size (mm) [2.23]

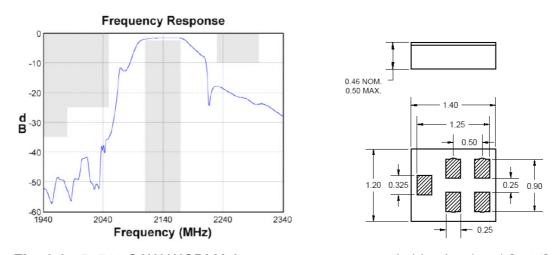

The frequency response of a SAW filter [2.24] satisfying the WCDMA spectrum requirements for the frequency band 2110–2170 MHz ( $f_0$ =2140 MHz) is shown in Fig. 2.3. The filter is single–ended 50 $\Omega$  input matched and has balanced output (100  $\Omega$ ).

**Fig. 2.3** 856562 SAW WCDMA frequency response and chip size (mm) [2.24] Design guidelines for SAW and BAW filters are given in [2.25] and [2.26] respectively.

#### 2.2.2 Wireless LAN Standards (IEEE 802.11)

A wireless LAN (WLAN) is a telecommunications system that offers network service access to portable wireless devices using radio waves [2.27]...[2.32]. It consists of a network hardware backbone, along with a series of detached components, like computer desktops, computer laptops, personal digital assistants (PDAs), cell phones, security cameras, printers. This network can be deployed as a stand-alone network or together with a wired network. As any other wireless standard, being wired offers opportunities but has also drawbacks when talking about interference.

The WLAN technology is regulated by the IEEE 802.11 family of specifications established by the WLAN Group [2.27]. There are four implementations of the IEEE 802.11 wireless LAN Standard, each one evolving from the basic IEEE 802.11 specifications and being defined by its frequency band and modulation scheme. A short review of these modulations is presented in Table 4:

| WLAN               | Year of      | Frequency   | Modulation    | Maximum   |

|--------------------|--------------|-------------|---------------|-----------|

| Standard           | Introduction | Band        | Scheme        | Data Rate |

| IEEE 802.11        | 1999         | 2.4 GHz     | OFDM          | 1-2  Mb/s |

| IEEE 802.11a (USA) | 1999         |             |               |           |

| IEEE 802.11h (EU)  | 2003         | 5 GHz       | OFDM          | 54 Mb/s   |

| IEEE 802.11j (JAP) | 2004         |             |               |           |

| IEEE 802.11b       | 1999         | 2.4 GHz     | DSSS/CCK      | 11 Mb/s   |

| IEEE 802.11g       | 2003         | 2.4 GHz     | DSSS/OFDM/CCK | 54 Mb/s   |

| IEEE 802.11n       | Not ratified | 2.4 / 5 GHz | MIMO - OFDM   | 540 Mb/s  |

**Table 4** WLAN standard and its implemented amendments

When designing RF WLAN transceivers, the followings aspects must be taken into consideration:

- a) the increasing demand for portable multistandard devices existent on the market;

- b) a superior amendment (IEEE 802.11n) must support the inferior amendments;

- c) the use of previous modulation scheme makes the practical design much easier;

- d) multiple antennas (as in the case of IEEE 802.11n) strongly ameliorates the data rate (a supplementary antenna simply doubles the data rate);

- e) OFDM modulation scheme makes difficult the transceiver design.

A throughout study of a WLAN multistandard transceiver designed to support IEEE 802.11a/b/g/n standards is presented in [2.31].

Finally, it is interesting to note that choosing a suitable topology for a wireless transceiver is not an easy task. Thus, regarding the last amendment (IEEE 802.11n), about 61 proposals have been submitted to IEEE but only two have been selected (from WWiSE and TGn Sync) [2.33]. The first scheme was able to transmit data at rates of 135 Mb/s while the second up to 315 Mb/s. No one has gained the majority voting support so that a mixing between all these proposed schemes was chosen for implementation. Devices supporting the IEEE 802.11n wireless network already appeared on the market.

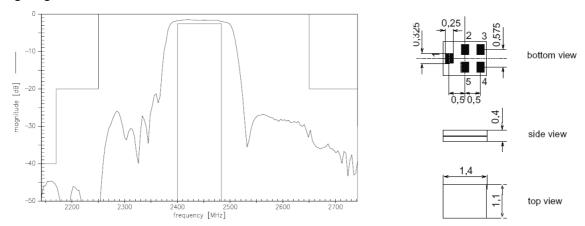

The frequency response of a SAW filter satisfying the WLAN (IEEE 802.11 b/g) spectrum mask requirements for the frequency band 2400–2483.5 MHz ( $f_0$ =2441.75 MHz) is showed in Fig. 2.4. Much more relaxed attenuation requirements are required for WLAN applications than for mobile ones. This standard should be complied with when designing RF active filters.

Fig. 2.4 B9410 SAW WLAN filter frequency response and chip size (mm) [2.23]

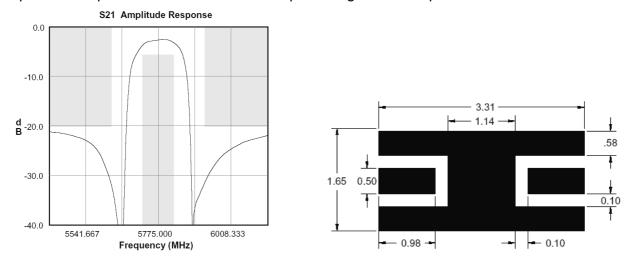

BAW RF filters are used for higher frequencies instead of SAW ones. The frequency response of a BAW filter satisfying the WLAN (IEEE 802.11a) spectrum mask

requirements for a centre frequency of 5775 MHz is shown in Fig. 2.5. The filter is  $50\Omega$  input and output matched. The filter occupies a significant chip area.

Fig. 2.5 880369 BAW WLAN filter transfer function and chip size (mm) [2.24]

#### 2.2.3 Bluetooth Standard (IEEE 802.15.1)

Bluetooth is the name given to a telecommunication system that facilitates wireless communications between portable and/or fixed electronic devices [2.34]...[2.38]. From the very beginning the idea behind Bluetooth was to avoid cables for short range communications (less than 10 m). Working in the 2.4 GHz ISM band (2.4–2.4835 GHz), like WLAN devices (IEEE 802.11b/g), Bluetooth transceivers are designed to work in noisy environments due to the free interference FHSS frequency hoping scheme with low power and cost requirements. It is obvious that working in the ISM band, the main source of interference for Bluetooth systems is represented by the WLAN b/g transceivers. As in the case of the previously mentioned WLAN standard, Bluetooth knew a continuous development, as shown in Table 5:

| Bluetooth<br>Version        | Year of Regulation | Frequency<br>Band (GHz)                                                                                          | Modulation Scheme                                                    | Data Rate<br>(Mb/s)       |

|-----------------------------|--------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------|

| Core v1.0<br>[2.34]         | Dec. 1999          | 2.4 – 2.4835 (EU <sup>*)</sup> , USA)<br>2.471 – 2.497 (JAP)<br>*) 2.445 – 2.475 (ESP)<br>*) 2.446 – 2.4835 (FR) | GFSK                                                                 | 1 Ms/s <sup>1)</sup>      |

| Core v2.0<br>+EDR<br>[2.35] | Nov. 2004          | 2.4 GHz Band                                                                                                     | GFSK <sup>2)</sup><br>π/4–DQPSK <sup>3)</sup><br>8DPSK <sup>3)</sup> | 1<br>2<br>3 <sup>4)</sup> |

| Core v3.0                   | Apr. 2009          | 2.4 GHz Band                                                                                                     | BR/EDR                                                               | 1–3 <sup>5)</sup>         |

| Core v4.0                   | Dec. 2009          | 2.4 GHz Band                                                                                                     | BR/EDR                                                               | 1–3 <sup>6)</sup>         |

Table 5 Bluetooth Standard Specifications

1) Practically max. 721 kb/s (v1.2)

2) Basic Rate (BR)

3) Enhanced Data Rate (EDR)

4) Practically max. 2.1 Mb/s

<sup>5)</sup> 24 Mb/s theoretical data rate by using WiFi – 802.11 resources [2.37]

6) 24 Mb/s theoretical data rate, low power devices (one year battery life) [2.38]

#### 2.2.4 Zigbee Standard (IEEE 802.15.4)

**Zigbee** is a specification for high level short–range radio frequency communication protocols using small, simple, less expensive low power and data rate digital radios based on the IEEE 802.15.4 standard for WPAN. This standard aims to fit the market that is not filled by other wireless technologies. The standard specifications [2.39] have been regulated by ZigBee Alliance [2.40]. Instead of working in a single band as Bluetooth does, its spectrum is spread over three different frequencies, depending on local spectrum regulations: 2450 MHz band (16 channels – worldwide), 915 MHz band (10 channels – USA/Australia) and 869 MHz band (1 channel – EU). Until now only the highest regulated frequency was used but the standard is continuously expanding over the world. The spreading scheme is DSSS, BPSK is used for lower bands and OQPSK for 2.4 GHz band.

ZigBee products are used currently in different applications like:

- wireless control (home automation): audio/video), smart lighting;

- monitoring applications: security systems, water/fire/smoke detectors;

- telecommunications applications: secured networks;

- personal/hospital care;

- toys.

Through its very low power requirements (up to 5 years battery life), network capabilities (self-organizing and self-healing dynamic mesh network) and size (thousands of devices per network) but also its secure communications (by using 8-bit microcontroller implantable AES-128 encryption algorithm), ZigBee proves to be a reliable wireless technology [2.41]. Through its excellent performances in low signal-to-noise ratio environments it proves greater performances than any other wireless technology (GSM/3G, Bluetooth/WiFi).

#### 2.2.5 GPS Applications

The second technological major achievement in the human history after the practical implementation of telecommunications systems may be considered the Global Navigation Satellite Systems (GNSS) that enable any user to know his position on Earth thanks to satellite systems. The first fully operational localization system is the American Global Positioning System (GPS), developed by the Department of Defense (DoD). The second one, partially available due to financial constraints is GLONASS, developed by the former Soviet Union now used rather as a back-up system to American GPS than a fully functional one. Both systems were developed as military applications and although they are currently accessible to civilians, they remain under army control (national defense departments) which also supports their costs. EU and ESA agreed in 2002 to implement an entirely European localization system, named Galileo, thought as complementary to the American GPS systems and expected to be operative in 2012. The first GALILEO satellite (Giove-A) was put into orbit in 2005 (Kazakhstan). The cost required for the second generation (the addition of four satellites and the development of the Galielo ground network) reached €950 million while the third phase (putting the rest of Galilleo satellites on the orbit) is expected to cost €3.6 billion. The high interest of different private companies in supporting the implementation of any GNSS systems is not surprising since the market of satellite navigation products and services knew an average annual increase of 25% even during crisis times. Although road applications represent an important GNSS market, many different areas makes use of this system. Thus, the main emerging GNSS applications are: Location Based Services, Road applications, Aviation, Maritime, Rail, Oil and Gas, Precision Agriculture, Fisheries, Survey and maritime engineering, Science, Electricity Networks, Social, Customs and Justice Affairs.

The satellite frequencies were chosen as a compromise between the required satellite transmission power and ionospheric errors, the errors significantly decreasing for frequencies higher than 1 GHz. This is also the reason why all GNSS bands are established between 1 and 2 GHz. The most important frequency bands are L1 and L2 while the modulation is BPSK. For the sake of generality, the GPS systems are working in the frequencies bands L2 (1215–1240 MHz) and L1 (1559–1610 MHz) and in future the band E5A (1164–1188 MHz) is to be reserved. L1 is expected to be used by Galileo together with E5A–B bands (1164–1215 MHz).

An overview (including design issues) of the GPS/Galielo RF Frontends proposed in literature until now is made in [2.42] while a good review of satellite systems is presented in [2.43].

#### 2.2.6 WiMAX Applications

If two thirds of the entire world's population uses portable terminals to communicate instantly, the Internet users do not surpass 20% of the world's population although more of the productivity gains in today's economies are due to the Internet and ecommerce. The emerging countries are the most affected from this point of view due to economic problems, lack of infrastructure, affordability of personal computers and so on. The next step after designing 3G mobile and WLAN networks is the practical implementation of **mobile Internet** considered a revolutionary step. The purpose of WiMAX [2.44]...[2.46], based on IEEE.802.16 standards specifications, is to enable mobile Internet from the physical layer to the network layer. This novel technology makes use of OFDMA as multiple access method and MIMO, both to optimize coverage and spectral efficiency. A comparison between this novel technology and the previous broadband solutions already implemented over the world is presented in Table 6.

| Parameter    | Fixed WiMAX       | Mobile WiMAX      | HSPA          | Wi-Fi             |

|--------------|-------------------|-------------------|---------------|-------------------|

| Standards    | IEEE 802.16-      | IEEE 802.16e-     | 3GPP release  | IEEE 802.11       |

|              | 2004              | 2005              | 6             | a/g/n             |

| Frequency    | 3.5 GHz and       | 2.3 GHz, 2.5 GHz, | 800/900/1800/ | 2.4 GHz,          |

|              | 5.8 GHz initially | 3.5 GHz initially | 1900/2100     | 5 GHz             |

|              |                   |                   | MHz           |                   |

| Multiplexing | TDM               | TDM/OFDMA         | TDM/CDMA      | CSMA              |

| Modulation   | QPSK, 16 QAM,     | QPSK, 16 QAM,     | QPSK,         | BPSK, QPSK,       |

|              | 64 QAM            | 64 QAM            | 16 QAM        | 16 QAM, 64        |

|              |                   |                   |               | QAM               |

| Bandwidth    | 3.5/7MHz -        | 3.5, 7, 5, 10 and |               | 10MHz for a/g     |

|              | 3.5GHz            | 8.75 MHz          | 5 MHz         | 20/40MHz for /n   |

|              | 10MHz – 5GHz      |                   |               |                   |

|              |                   |                   |               | < 100 ft indoors; |

| Coverage     | 3-5 miles         | < 2 miles         | 1 – 3 miles   | <1000 ft          |

|              |                   |                   |               | outdoors          |

**Table 6** Comparison of WiMAX and other broadband technologies [2.44]

#### 2.2.7 Wireless USB Applications

Wireless USB applications are in fact practical implementations of the UWB standard (IEEE 802.15.3a) [2.47]...[2.49]. UWB refers to any radio or wireless device

where the occupied bandwidth is greater than 25% of the center frequency or greater than 1.5 GHz. This facilitates that a great number of users communicate using UWB technology. An ultra wideband communication consists of transmitting very short pulses with low energy where, the impulse radio UWB is a carrier–less radio technology (no mixer needed), therefore the practical implementation being quite simple. However, since UWB systems operate in a very large bandwidth shared with other telecommunications standards, interferences always exists mainly for frequencies lower than 5 GHz (WiMAX, WLAN) and must be minimized. The radiation mask regulated by FCC imposes a maximum radiation level of –41.3 dBm/MHz in the frequency range 3.1–10.6 GHz. According to this, there are three architectures that fulfill the power requirements, as presented in Table 7 [2.49].

| Standard                                           | OFDM          | DS-UWB             | TD/FDMA pulses     |

|----------------------------------------------------|---------------|--------------------|--------------------|

| Bands                                              | 3–13          | 2                  | 3–13               |

| Bandwidths                                         | 3x528 -       | 1.5 GHz            | 3x550 -            |

|                                                    | 13x528 MHz    | 3.6 GHz            | 13x550 MHz         |

| Frequency ranges                                   | 3.1-4.8       | 3.1-5.15           | 3.1–5              |

| [GHz]                                              | 4.8–10.6      | 5.825-10.6         | 4.9–10.6           |

| Modulation                                         | OFDM-QPSK     | M–BOK, QPSK        | M–BOK, QPSK        |

| Modulation<br>Efficiency<br>(10 <sup>-3</sup> BER) | 6.8 dB        | 4.1–6.8 dB         | 6.1–6.8 dB         |

| Error correction                                   | Convolutional | Convolutional and  | Convolutional and  |

|                                                    |               | Reed-Solomon codes | Reed–Solomon codes |

**Table 7** Three ways of implementing UWB systems

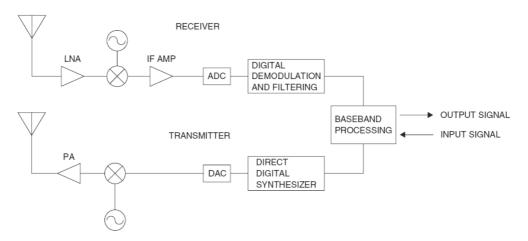

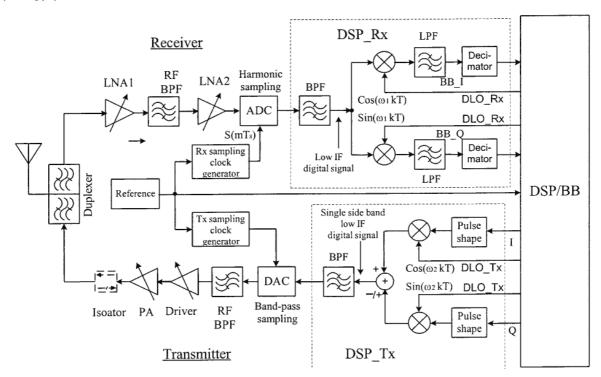

#### 2.3 RF Front-ends Receivers and Multistandard Trend

The RF front-end is part of the overall radio receiver—transmitter or transceiver system and is represented by all blocks between the antenna and the digital baseband part. The front-end receiver task is to extract the original information from the transmitted radio waves while at the transmitter part to convert the baseband signal into an appropriate form supported by the telecommunications channel and also recognized by the receiver.

Any published microwave book includes one or more chapters dedicated to wireless transceivers meaning that a basic knowledge on RF part is compulsory when dealing with radio signals. This justifies a further review of wireless transceivers architectures generally used in telecommunications systems while the filtering part is emphasized. Several RF resources have been used for this section [2.50]...[2.62]. Moreover, hundreds

of articles envisaging different implementations of RF transceivers for one or more wireless standards (wideband or reconfigurable architectures) have been published in the literature until now. It is obvious that choosing one transceiver architecture may enhance the device performances therefore making the design of a particular RF block much easier or even may offer the opportunity to avoid certain blocks if the overall performances are not negatively influenced. The RF designers but also the companies behind them will do all the best to simplify the RF circuit and implement different methods in baseband to avoid some bulky or expensive RF blocks, thus decreasing the overall product cost and making the circuit design easier. An example in this case is the choosing of a particular modulation scheme. As presented in Table 8, the modulation scheme is very important for the power amplifier (PA) linearity [2.63].

| <b>Modulation scheme</b> | Parameter             | Crest factor (dB) |

|--------------------------|-----------------------|-------------------|

|                          | 16 occupied channels  | 10.5              |

| Wideband CDMA            | 32 occupied channels  | 11.1              |

|                          | 64 occupied channels  | 12.2              |

|                          | 128 occupied channels | 13.6              |

|                          | $\alpha = 0.20$       | 4.86              |

|                          | $\alpha = 0.25$       | 4.55              |

| π/4-DQPSK                | $\alpha = 0.30$       | 4.23              |

|                          | $\alpha = 0.35$       | 3.87              |

|                          | $\alpha = 0.40$       | 3.38              |

|                          | $\alpha = 0.50$       | 3.21              |

|                          | $\alpha = 0.20$       | 6.03              |

|                          | $\alpha = 0.25$       | 5.92              |

| 16-QAM                   | $\alpha = 0.30$       | 5.66              |

|                          | $\alpha = 0.35$       | 5.40              |

|                          | $\alpha = 0.40$       | 5.18              |

|                          | $\alpha = 0.50$       | 4.94              |

| GSM EDGE (8-PSK)         |                       | 3.21              |

**Table 8** Three ways of implementing UWB systems

In the table above, "crest factor", "peak ratio", "peak to average ratio" and "peak to mean ratio" are *methods of defining the statistics of a modulated signal in a manner which an amplifier designer can understand and interpret* [2.63]. The "crest factor" (CF) is defined as the ratio of the peak to r.m.s. amplitude of a signal while "peak-to-mean ratio" (PMR=CF<sup>2</sup>) is the ratio of the peak power to r.m.s. power of a signal. Therefore, the minimization of a multicarrier signal crest factor is envisaged when choosing a modulation scheme with a significant impact upon the power rating of the PA and its linearity. Baseband coding by implementing different codes like *Shapiro–Rudin sequences*,

maximal—length sequences, Barker codes, Newman or Schoeder phases, block coding, selected mapping and partial transmit sequences, the RF efficiency is greatly improved.

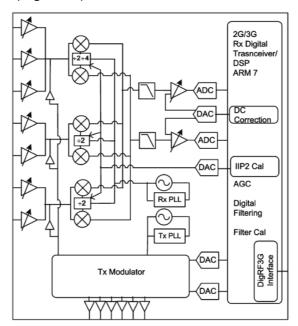

In the following, a brief review of the RF wireless transceiver architectures is presented, identifying, among others, the filtering issue. Since there are many references on this topic, a minimum condensed bibliography has been reported. Only CMOS circuits have been envisaged since this is the main technology used for RF circuits design aiming the lower microwave spectrum.

It is worth noting that instead of using voltages and currents, as they are employed for baseband circuits (analog/digital) design, power concepts are used in RF. Since the transceiver operates with low power input signals, this is usually expressed in dBm where the reference load resistance is considered 50  $\Omega$  if not otherwise stated.

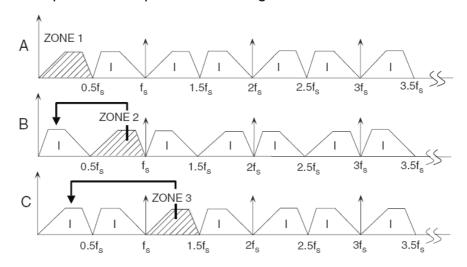

The development of different transceivers schemes has an intrinsic reason: the technological impossibility of filtering a particular channel of hundred KHz or MHz directly in the RF domain in the GHz domain. Otherwise, RF preselective filters with very large quality factors are needed. In other words, the decision of choosing a particular architecture is determined in fact by the filtering possibilities. In the following sections a review of all RF transceiver types is presented.

## 2.3.1 Super-heterodyne Transceiver

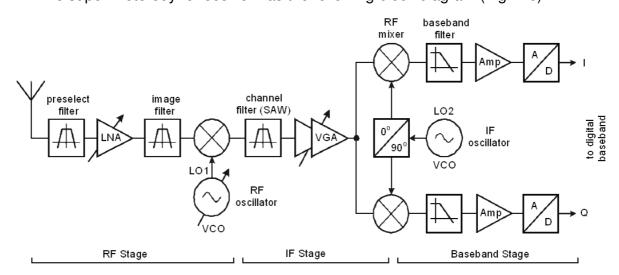

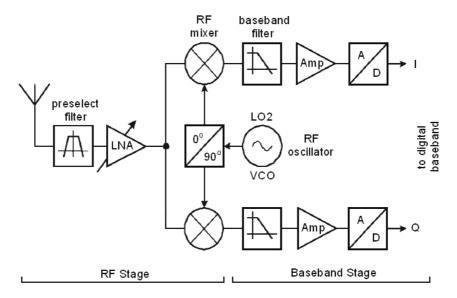

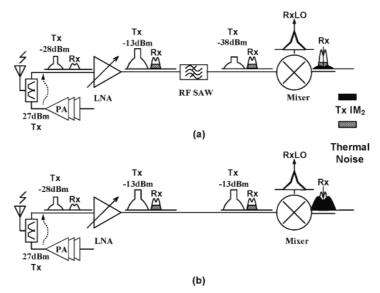

The super-heterodyne receiver has the following block diagram (Fig. 2.6).

Fig. 2.6 Block diagram of the super-heterodyne receiver architecture

This architecture translates the desired signal band from higher frequencies (GHz domain) at a much smaller frequency (called intermediate frequency – IF), much lower

than the channel carrier frequency. The translation is carried out by a mixer, usually seen as an analog multiplier but passive mixers may be used as well. Channel select filtering is usually performed at the IF where relaxed requirements are imposed to SAW filters with respect to relative bandwidth. Several factors are taken into consideration when choosing the IF: (1) system requirements, (2) the radio frequency band (RF), (3) the usage of neighboring frequency bands, (4) possible interferer signals, (5) possible mixing products and (6) the availability of IF SAW filters.

This is a well-known architecture for its best overall system performance, still regarded the most reliable RF architecture for single band transceivers. However, it becomes useless for multi-band (reconfigurable) terminals due to the fixed IF section. Furthermore, consecutive amplification and filtering yield very high sensitivity and selectivity in the RF, IF and baseband part. This results in good image and interferer rejection, high channel selection and lower power consumption since the linearity constraints are more relaxed. These make it suitable for UMTS where the spectrum is more optimized compared to GSM cellular systems.

The main drawback is represented mainly by the increased number of blocks. It is obvious that the overall cost of such architecture using a large number of components is noticeable increased. Making use of two local oscillators (LO) and synthesizers together with three SAW filters is an important aspect. In addition, the LO and IF filter have different specifications, particular to world regions where the standard is regulated. Consequently, the design becomes more difficult and much effort is required for IF frequency planning to avoid spurious signals.

Different versions of heterodyne receivers have been developed: dual–IF receiver, image—reject receiver, wideband—IF receiver and digital—IF receiver. The dual—IF receiver makes use of two or more intermediate frequencies to optimize the trade—off between image—rejection and channel selection. In the case of image—reject receiver, the signal and its image are processed differently in order to achieve cancellation of the image. The wideband—IF receiver with double conversion suits best high level integration requirements. However, the large number of components (mainly of mixers) increases the power consumption making it a difficult choice. In digital—IF receivers the IF stage is digitized using high frequency ADCs. Digital IF signal processing avoids all problems encountered by the analog IF like I/Q amplitude and phase mismatch yielding to excellent image rejection. However, high performance ADCs results in high power consumption.

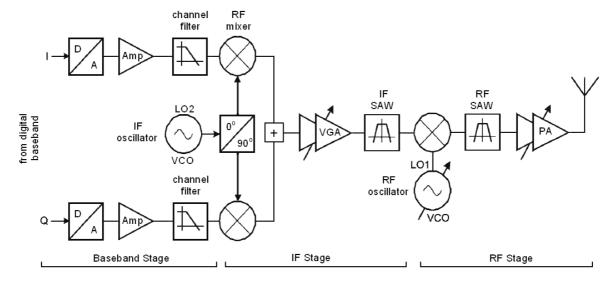

The super-heterodyne transmitter is shown in Fig. 2.7.

In a heterodyne transmitter, the baseband is converted to RF signal in two steps. By using variable power amplifiers in the RF part, the overall power consumption can be reduced, depending on the particular standard requirements. The intermediate filter (IF SAW) reduces the noise and spurs in adjacent channels.

Fig. 2.7 Super-heterodyne transmitter architecture

The super-heterodyne transceiver is not suitable for multi-standard application due to its large number of building blocks and consequently the final cost but also its difficult IF frequency planning. The filtering part cannot be neglected since it consists of five SAW filters (3 for the receiver and 2 for the transmitter). The practical implementation of such circuit in practical multi-standards wireless devices is not possible until all filtering blocks are actively implemented.

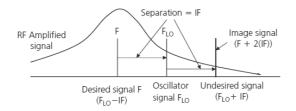

A main drawback of heterodyne receivers is represented by the image frequency interference which is related to the mixing process. Considering that the frequency obtained at the mixer output port is equal to  $f_{IF}=f_{LO}\pm f_{RF}$ , the desired intermediate frequency signal ( $f_{IF}=f_{RF}-f_{LO}$ ) is the difference one while the <u>image frequency</u> is the sum ( $f_{LO}+f_{RF}$ ) and must be removed (Fig. 2.8).

Fig. 2.8 Mixing process [2.61]

However, if a signal with the frequency  $f_{RF}$ — $2f_{IF}$  is applied to the input, the mixer generates the same image frequency (denoted as  $f_{IF}$ =F+2(IF)) therefore corrupting the desired intermediate frequency signal. This is the reason why a supplementary image—reject filter is used before the mixer which represents also the main drawback of this architecture.

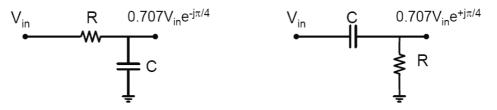

To avoid the image problem, two image—reject receivers have been proposed as alternatives for heterodyne systems. One of them is the Hartley architecture (Fig. 2.9). The simplest phase shifter is implemented as RC–CR bridges (Fig. 2.10). This receiver topology is sensitive to amplitude balance and phase quadrature between two paths, the last being dependent on the parasitics and passive component matching.

Fig. 2.9 Hartley receiver

Fig. 2.10 Phase shifter used in Hartley receiver

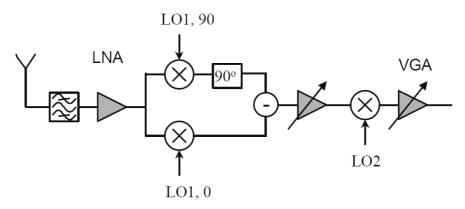

The Weaver architecture is the second alternative to heterodyne receivers (Fig. 2.11). This architecture utilizes an additional pair of mixers to perform the phase shifting prior to IF combination therefore achieving greater image rejection despite temperature and process variations. These constitute the main advantage over Hartley topology although the gain and phase mismatches between the signal paths still represent a critical problem. However, the use of the second set of mixers brings new concern for a second image which must be addressed using proper frequency planning and filtering. If the signal is converted directly to BB by the second mixer than this image problem is avoided.

Fig. 2.11 Weaver receiver architecture

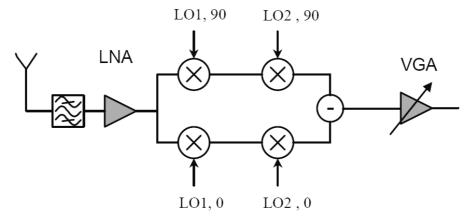

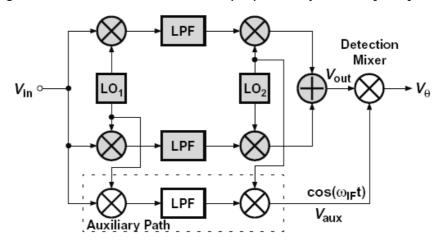

For the both configurations, low–pass filters are used after the mixing process. A self–calibrating Weaver architecture has been proposed by Razavi [2.64] – Fig. 2.12.

Fig. 2.12 Self-calibrating Weaver architecture [2.64]

## 2.3.2 Direct Conversion Architecture

The block diagram of the homodyne receiver, known also as direct conversion receiver or simply DCR, is presented in Fig. 2.13. The idea behind this configuration is to translate the desired signal band from higher frequencies (RF input signal) directly into the baseband where it is easier recovered. The channel filtering is implemented in this case by a low–pass filter which, being active, allows bandwidth tuning and thus the receiver can be configured as multi–standard architecture. Due to its simplicity, the need for frequency planning (time consuming and hard to validate) is avoided. Although direct conversion transceivers have worse performances compared to super–heterodyne transceivers (used in military applications), they are preferred for civilian applications since they are cheaper.

Fig. 2.13 Direct conversion receiver architecture

The circuit shown in Fig. 2.13 works as follows. The RF input signal is received by the antenna (modern wireless transceivers have multiple antennas) and the resulted signal is applied to a high quality factor passive external filter (usually SAW filter). This pre–select filter rejects the out–of–band interferences and image frequencies. Since only one filter is needed for this architecture, it must have a high quality factor. A common method of implementing wireless transceivers is to use duplexers instead of filters which separate the transmission and receiver paths which reject also the transmission leakage power. The signal is further amplified by a low noise amplifier (LNA), ideally designed with a high gain since it is the first RF front-end component. Currently, several successive identical LNAs are used in modern receivers in order to achieve higher gains (~ 60–80 dB) and thus maximizing the SNR ratio. By filtering and amplifying the input signal, the noise (not only the thermal one) that sets the transceiver sensitivity but also by other out of band RF signals (sources of interference), is lowered sufficiently compared to the signal level.

After maximizing the SNR level with LNA stage(s), the input RF signal is mixed (on a diode or FET mixer) with a reference signal generated by a local oscillator (LO) whose frequency,  $f_{LO}$ , is equal to that of the carrier  $f_{RF}$ . After the mixer, two signals are obtained: one with the frequency  $f_{RF} = 2f_{RF}$  and a second one in the baseband. In other words, the image frequency, a potential problem in super–heterodyne topology, coincides with the desired signal (IF = 0). The original signal is simply recovered through a corresponding low frequency filtering in KHz (switched capacitor filters) or MHz domain ( $g_m$ –C filters),

according to the standard specifications. After low-pass filtering, the signal is amplified and applied to an analog to digital converter (ADC), the signal being further digitally processed. As in the previous scheme, two orthogonal signals are received therefore the transmission efficiency being increased.

The main advantage of this architecture is that any supplementary local oscillator or mixer, required by heterodyne receiver to translate the information from IF to baseband, is not needed. Therefore, the design becomes simpler and smaller cost is achieved. Furthermore, the front—end is less affected by the individual nonlinearity and noise which, together with the possibility of channel bandwidth tuning, make this architecture well suited for multi—band and multi—mode application.

However, there are several drawbacks for this architecture as mentioned in the following.

- 1. The local oscillator must generate a signal synchronized to the exact carrier frequency, a requirement that makes the design more difficult. If they do not have identical frequencies, the signal cannot be recovered in BB.

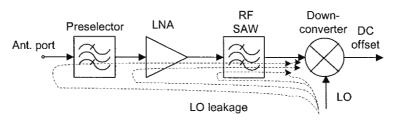

- 2. DCR receivers are very sensitive to spurious LO leakage that can generate large DC offsets (self interference). A large DC offset compromise the amplification of the next low–pass filter amplifier that becomes saturated. The leakage problem is caused by the inherent LO leakage existing due to the weak isolation between LO port and LNA input. This problem characterizes any super–heterodyne receiver but due to its principle, the direct conversion architecture is much more affected by this problem.

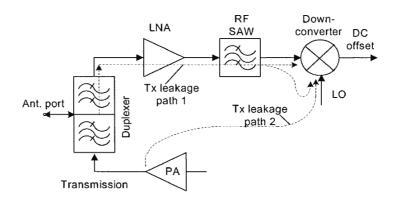

The first type of leakage manifests when a fraction of reference signal (generated by LO), arrives to LNA input through capacitive and substrate coupling and mixes with the original LO generating a supplementary DC offset (self mixing) as shown in Fig. 2.14. The second type is encountered when a small part of the received input RF signal applied to LNA or mixer leaks to the LO port and mixes with the input signal at the mixer stage. This type of leakage is described in Fig. 2.15.

Fig. 2.14 DC offset caused by LO mixing [2.53]

Fig.2.15 DC offset caused by the transmission leakage self–mixing [2.53]

The third one refers to the time variant self-mixing. In the case of moving objects (car, train), the reference signal generated by the local oscillator may leak to the antenna and be radiated in space. Being reflected back to the receiver, it mixes with LO and generates a time variable offset, thus making difficult the correct recovering in BB. Moreover, through this type of leakage, this transceiver acts as a source of interference for other transceivers working in the same frequency range since the "noise" signal generated by this LO-antenna leakage becomes baseband signal or DC offset for others. The pre-select filter selects the entire bandwidth allocated to a particular standard and thus any receiver, working at a particular time on a specific channel, receives also other in-band signals (emitted be other transmitters) which are in fact interferences.

However, this leakage problem can be minimized by applying the following methods:

- a) Careful transceiver design (RF design level), including the possibility of implementing near zero DCR where the signal is recovered at very low frequencies but not 0, thus exploiting that mixers have not the same carrier frequency but with the requirement of using higher frequency ADCs. However, the use of high frequencies ADC does not represent a problem since even GHz bandwidth ADCs are currently on the market.

- b) Maintaining good isolation between the LO and the RF part at a layout level, also including the possibility of using a high reverse isolation LNA. A LNA gain of 20 dB is high enough to increase the LNA isolation. The insertion loss of RF bandpass filter (and of preselector) further enhances the isolation. However, the implementation of differential LNAs or circuit independent single ended LNAs strongly ameliorates the LNA isolation and decreases the leakage.

- c) Efficient bit representation (using NRZ or bipolar encoding) of the BB signal before being modulated so that, after demodulation, little energy is near DC.

- d) AC coupling in baseband simply avoids this problem but adds new drawbacks since this coupling decreases the signal energy around DC and introduces group delay distortion near the DC further reducing the SNR and affecting receiver sensitivity. An alternative is to filter out the DC component (high-pass filtering) if the baseband spectrum is predominantly away from DC as in the case of WLAN a/g spectrum but not applicable otherwise (Blutetooth case where the spectrum is concentrated at very low frequencies).

- 3. As the down-converted RF signal is usually of low amplitude and low frequency (near 0 Hz), flicker noise (1/f) from the mixer output decreases the SNR. This depends on what telecommunications standard is implemented, the GSM one being more sensitive to this noise due to its small bandwidth.

- 4. Second order intermodulation distortion becomes significant for this architecture, two mechanisms being responsible: RF self-mixing and device nonlinearity and mismatches. When designing a high performance direct conversion transceiver, higher IIP2 compression points must be envisaged. For example, in the case of UMTS frequency division duplexing system a minimum IIP2 value of 48 dBm is required. The use of high quality factor RF bandpass filters relaxes the IIP2 receiver requirements.

The concept of direct conversion transceiver was introduced in 1924 and adopted for the first time in 1932, as a replacement for heterodyne transceivers. However, they have seen limited use in the past, for over half a century, due to implementation complexities when building it with discrete components. A well known example of direct conversion receiver built with discrete components is the amplitude demodulator. Owing to the technological advancements during the last decades, this architecture has been widely adopted (first time for GSM standard in 90's) and now it represents an attractive solution for reconfigurable multistandard 3G/4G transceivers due to its simplicity, low cost, small size and low power consumption. In other words, the technological trend of using direct conversion transceivers in RF wireless terminal is a positive one, proving to be different of what Razavi expected in 1998 [2.50]. Moreover, the DCR architecture is more suitable for multistandard applications employing wide channel bandwidth since this mitigates the classical DCR problems like flicker noise and DC offset. The first analog systems used a bandwidth of 25 KHz, GSM uses 200 KHz while currently WCDMA systems make use of 5 MHz bandwidth. It is obvious that multimedia services require large bandwidths a fact that makes direct conversion architectures an attractive choice for the coming generations of cellular receivers. From this point of view, the main advantage of DCR structure over

super-heterodyne architecture is that the latter becomes quite complex for multi-standard applications due to the great required number of mixers, local oscillators and filters negatively affecting the overall cost. However, an important drawback for these transceivers that still remains is the use of RF filters (before LNA) which are external, bulky and, though cheap, the final cost for using between 8 and 12 RF filters or even more when implementing a multi-standard device is greatly increased, taking into consideration the billions of mobile devices sold over the world. A considerable effort may be put in future for designing SAW-less homodyne transceivers or integrating RF filters in an active reconfigurable topology.

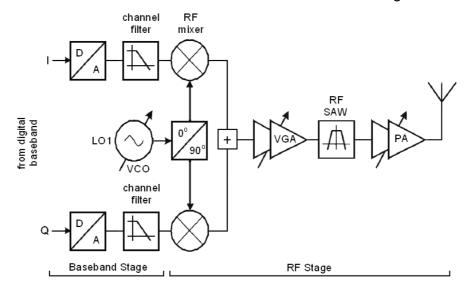

The architecture of direct conversion transmitter is shown in Fig. 2.16.

Fig. 2.16 Direct conversion transmitter

The advantage of the direct conversion transmitter consists in the rejection of the IF path with its SAW filter leading to high integration level and lower cost. Using a single mixer and VCO, fewer mixing products and lower level spurious signals are generated in the output spectrum. All these make this architecture suited for multi–band multi–mode operation. However, it seems that the power consumption is comparable to a heterodyne receiver, despite its high integration level.

It is worth mentioning that for the receiver part, the baseband analog circuits establish the overall receiver gain (approximately 75%) in opposite to the transmitter part where more than 90% of its gain is in the RF part from I/Q modulator to the power amplifier (PA). Furthermore, the direct conversion transmitter has fewer drawbacks than the receiver counterpart, therefore being easier to be implemented. However, direct

conversion transmitter architectures make use of the same SAW filter introduced in between power amplifier and driver amplifier, in order to minimize the out-of-band and spurious emissions for the receiver part. From this point of view, the single gain of a direct conversion transmitter over the super-heterodyne transmitter consists in it's LO. This is the reason why much profit is obtained rather with the receiver part than the transmitter one for a direct conversion scheme.

A clear drawback of this architecture is the mechanism of *injection locking/pulling*. It refers to the fact that the LO is disturbed by the up–converter or power amplifier and consequently causes spurious signals and noise in the transmit spectrum. If the PA is turned on and off periodically as in the case of 3G systems (3GPP–TDD), the problem worsens. Other challenges consist in high I/Q phase accuracy, high linearity and noise performance for the RF blocks, higher LO–RF isolation, low noise floor requirements as well as output spectrum purity.

#### 2.3.3 Low-IF Receiver

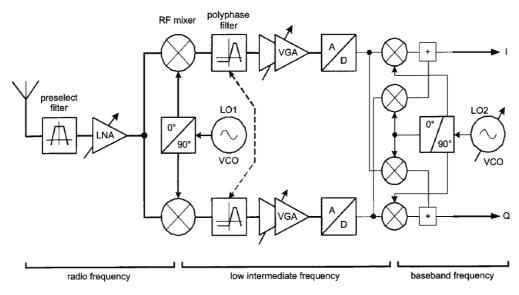

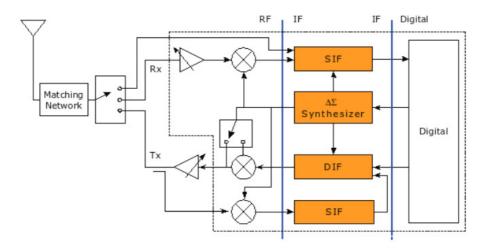

The architecture of a Low–IF receiver is shown in Fig. 2.17.

Fig. 2.17 Low-IF receiver architecture

It represents in fact a compromise between the heterodyne and the homodyne architectures. In this case, the signal is quadrature down-converted to a very low IF (for example hundreds of kHz i.e. the order of one channel spacing) by exploiting the mixing properties of a complex mixer (used to multiply two complex signals). Such mixer only

mixes the positive RF frequencies with a negative LO frequency thus achieving an active image rejection.

The low–IF allows the use of low–Q channel select filter while avoiding the dc–offset problems encountered in zero–IF. The complex signal applied to the mixer input is generated in a complex form by the polyphase filters which act as an allpass filter for positive frequencies and band–stop one for negative frequencies. This is superior to zero–IF architectures since is not sensitive to dc–offset, LO leakage and intermodulation product of third order (IM3). However, due to the limited matching between I and Q generators, limited image rejection is achieved while asymmetric poly–phase filters used to enhance the image rejection introduce insertion loss and cause noise degradation. This architecture is more suitable for telecommunications applications with low adjacent channel power or with exceptions for image frequencies like GSM, Bluetooth or DECT. It envisages rather the receiver side than the transmitter one and thus a mixing between heterodyne transmitter and low–IF receiver may be used as well.

# 2.3.4 Software Defined Radio (SDR) Architectures

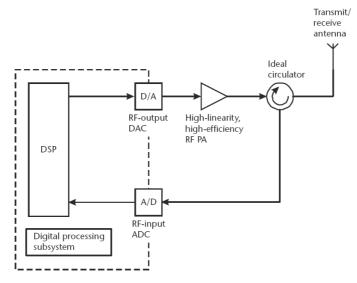

SDR represents an ideal revolutionary concept regarding the RF design. In a SDR transceiver the signal is entirely processed by means of software control. They are known also as *digital transceivers*. The basic idea is to place the ADC/DAC pair in the RF frontend near the antenna as possible which means more digital/software processing instead of analog RF processing. Often thought in terms of baseband DSPs, hence the term *software radio*, by making use of FPGAs, ASICs, parallel processor arrays and other techniques, the SDR transceiver is a flexible software based radio architecture, increasingly adopted and researched. It may be obvious that an important application of these SDR architectures would be represented by military communications where the opportunity of changing not only the scrambling or encryption codes (avoiding the communications interception) but also the modulation format, channel bandwidth, data rate and voice codec type is of high interest.

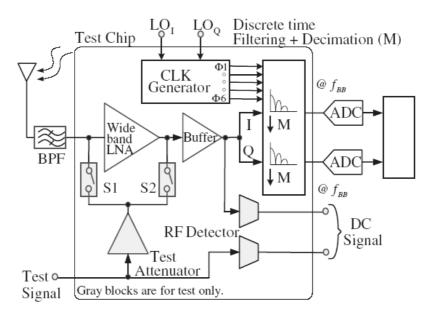

The ideal SDR architecture is shown in Fig. 2.18. As it can be noticed, by extensively minimizing the analog RF part, all stringent requirements are imposed to ADCs and DACs which must have wide dynamic range and high sampling rates (of many GHz) with a negative impact on the power consumption. In this case, the converter must

work at an RF sampling frequency higher than twice the greatest carrier of the frequency of interest while the samples are processed by a programmable signal processor.

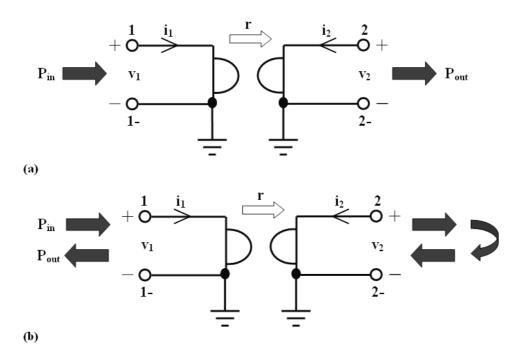

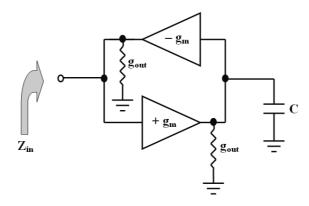

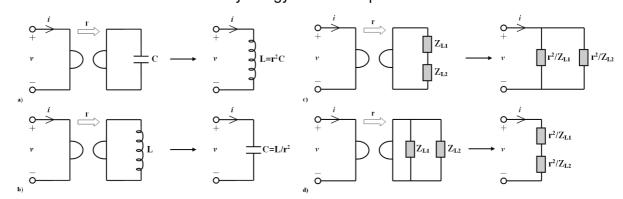

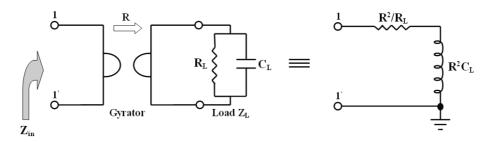

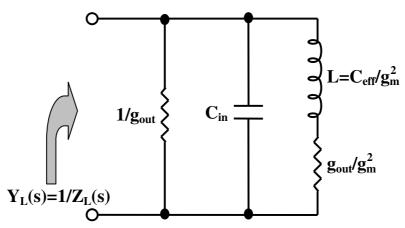

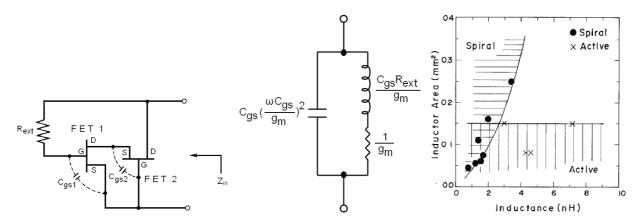

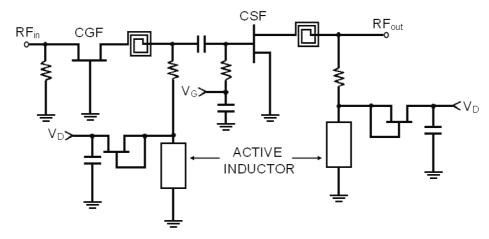

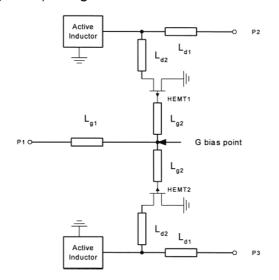

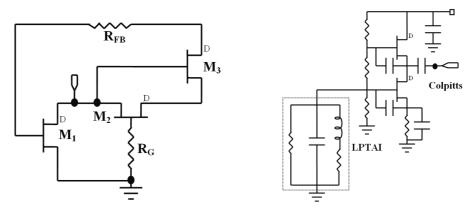

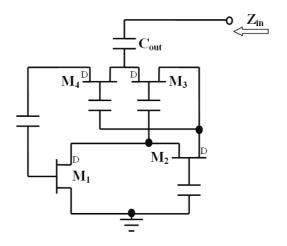

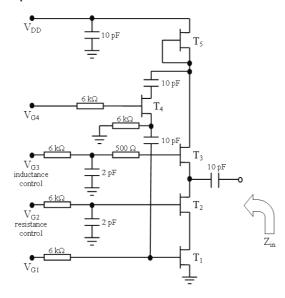

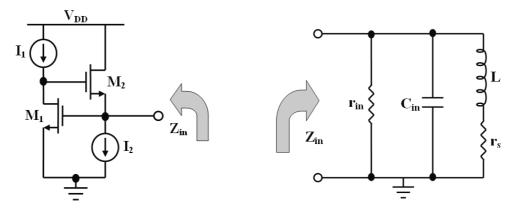

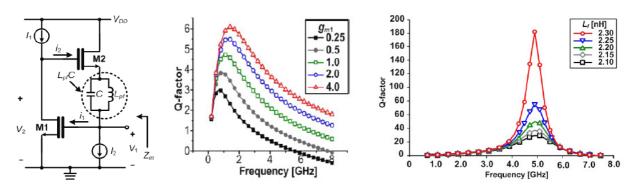

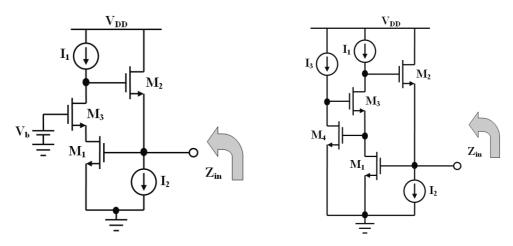

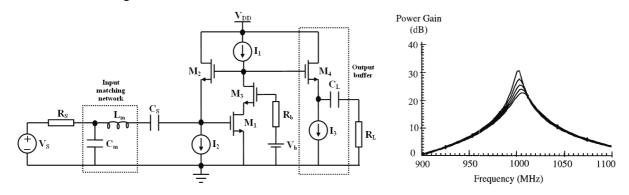

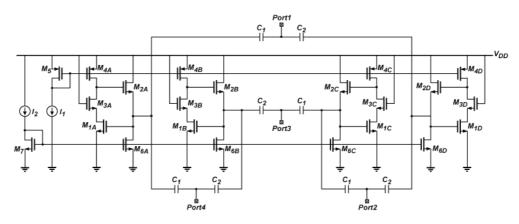

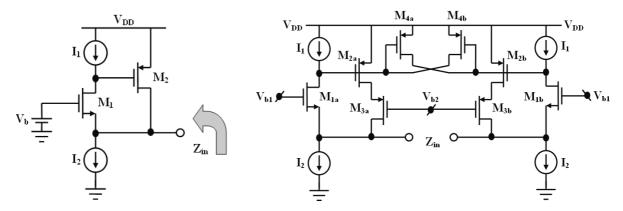

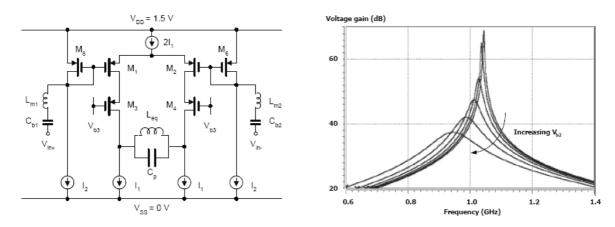

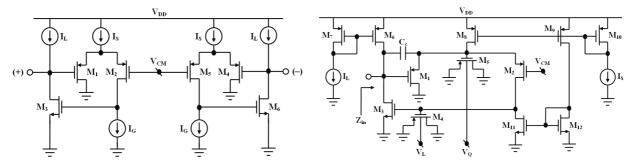

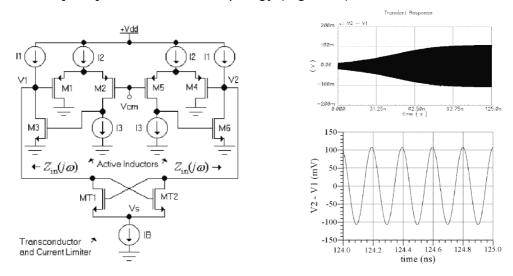

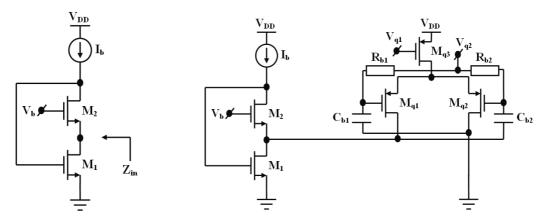

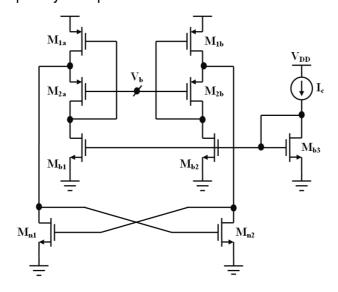

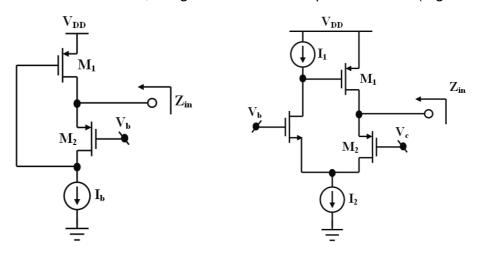

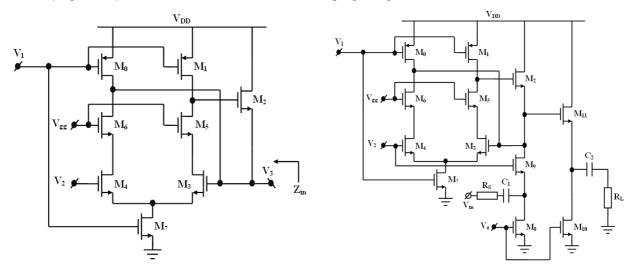

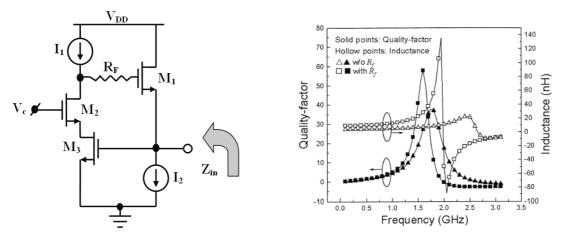

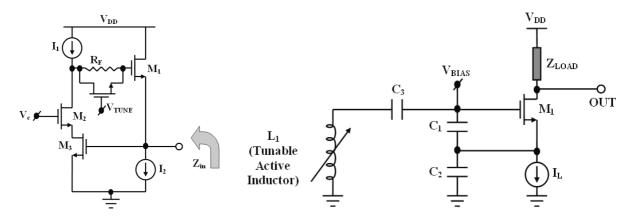

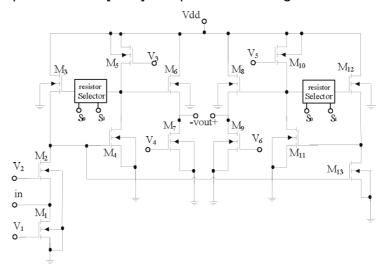

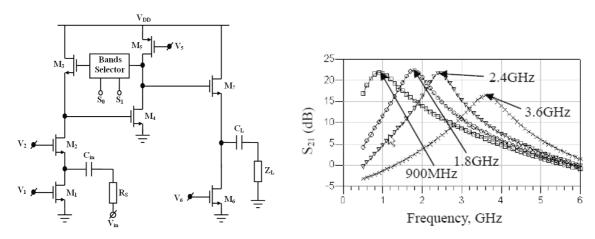

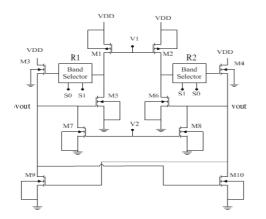

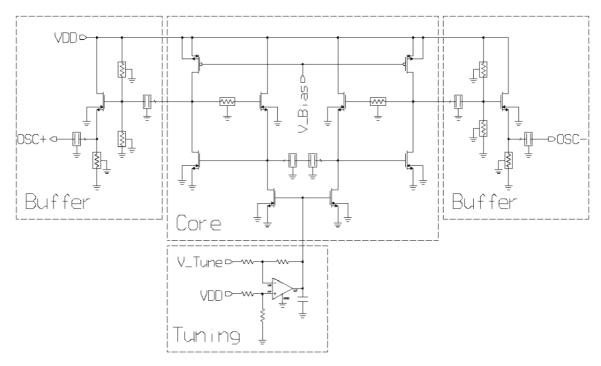

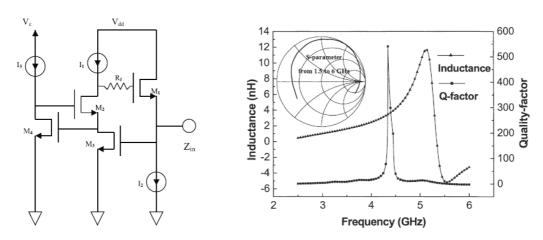

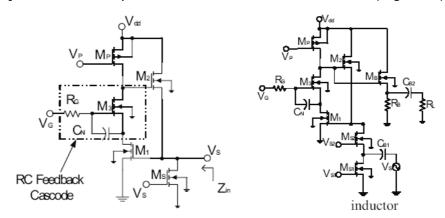

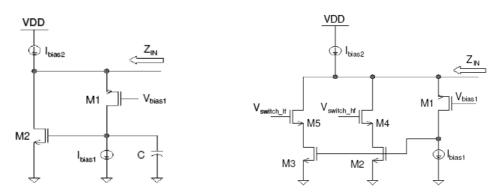

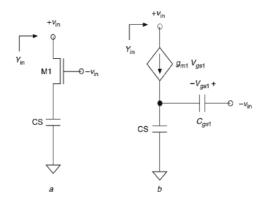

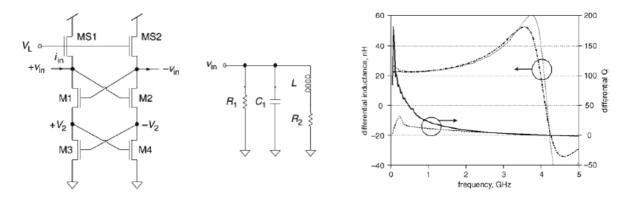

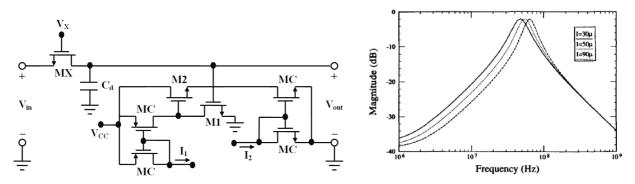

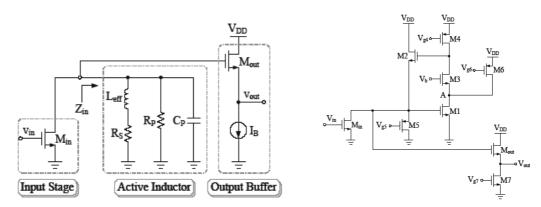

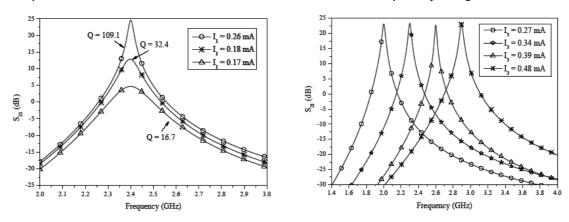

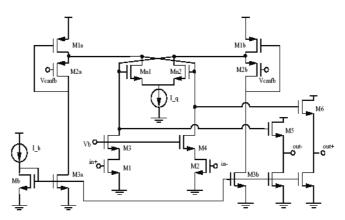

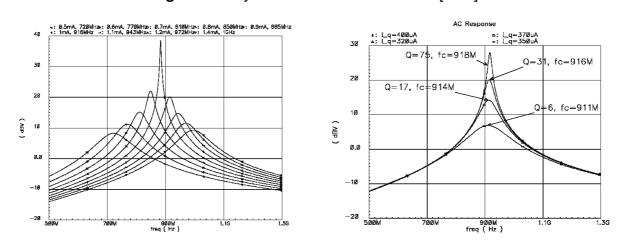

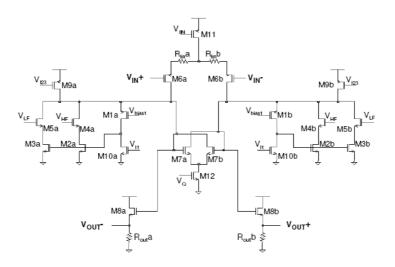

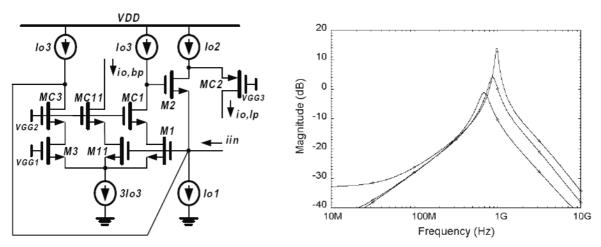

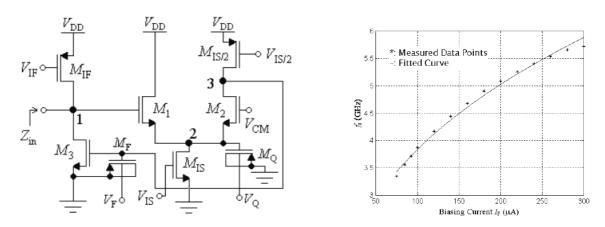

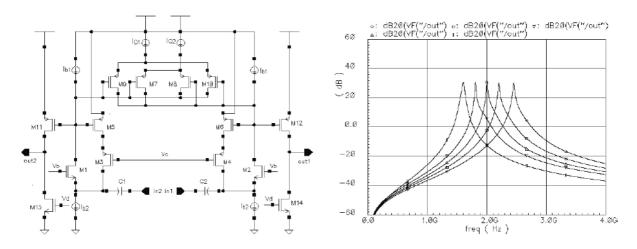

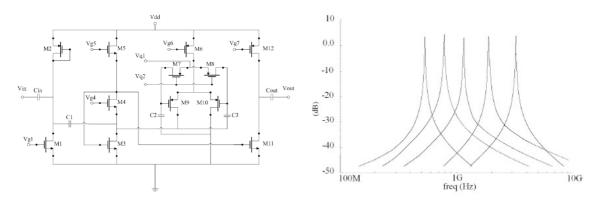

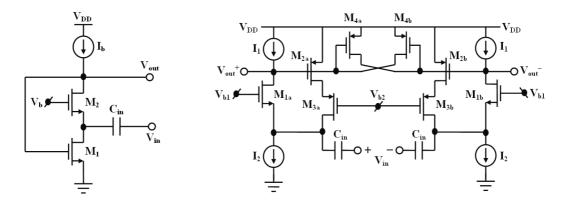

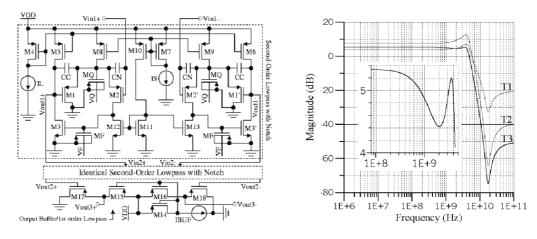

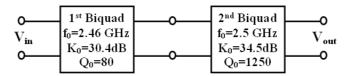

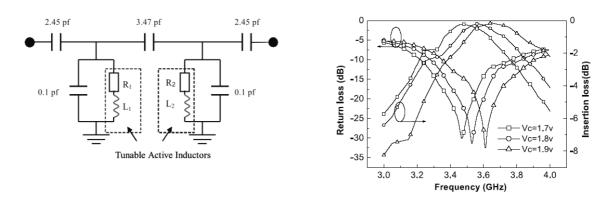

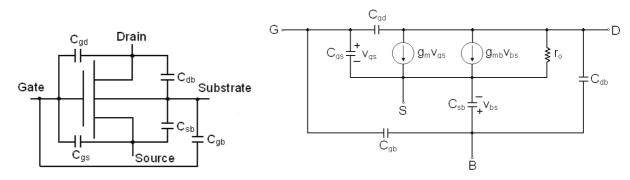

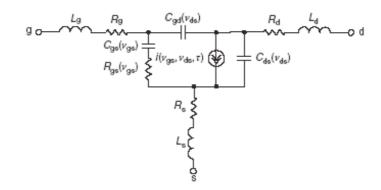

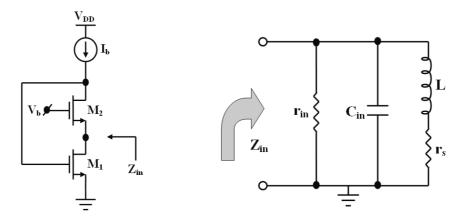

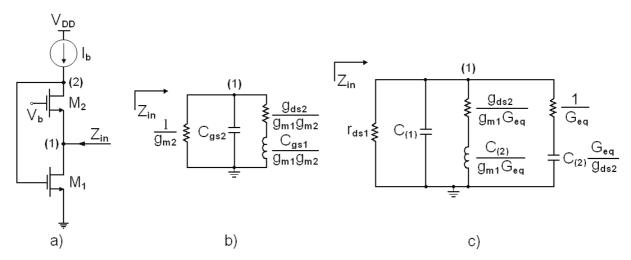

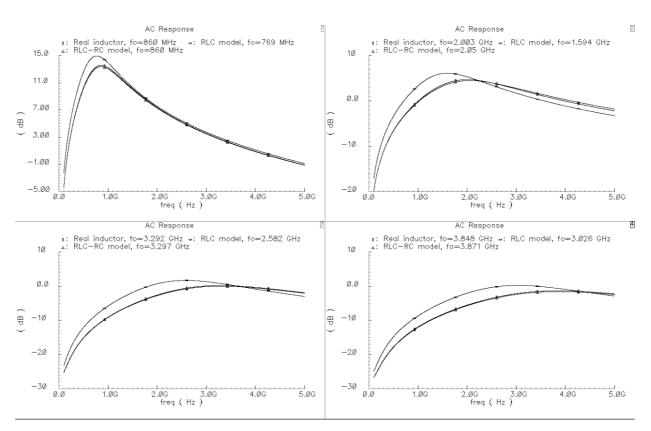

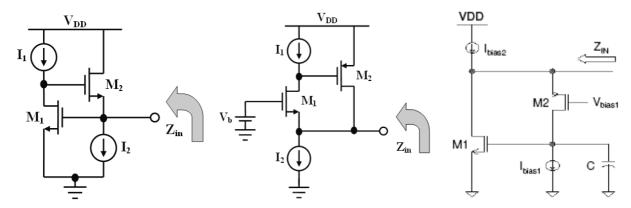

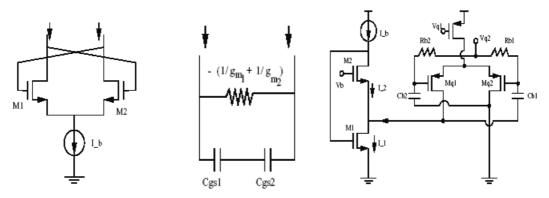

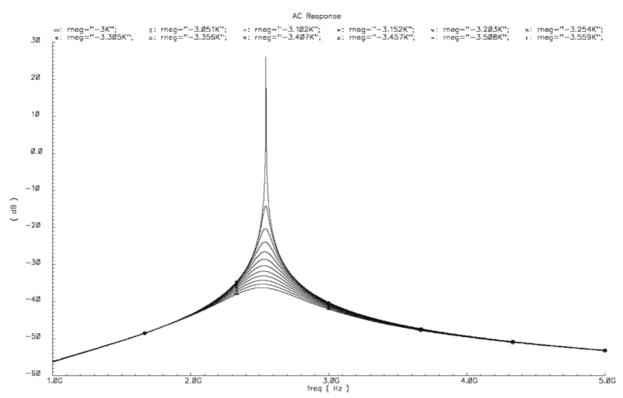

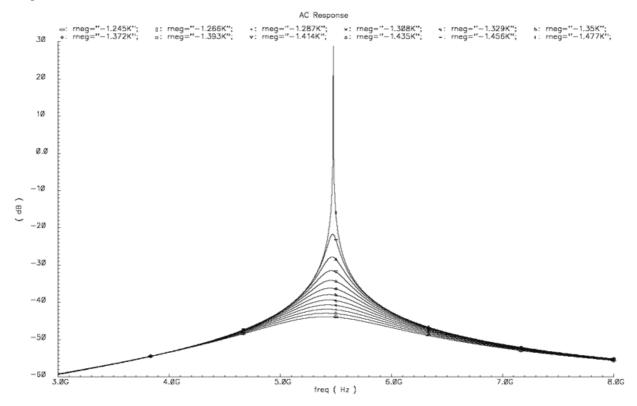

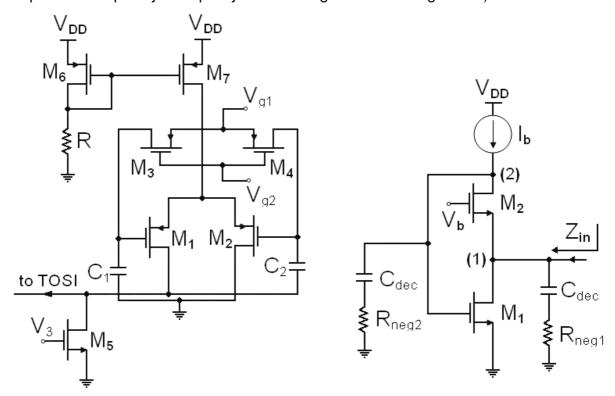

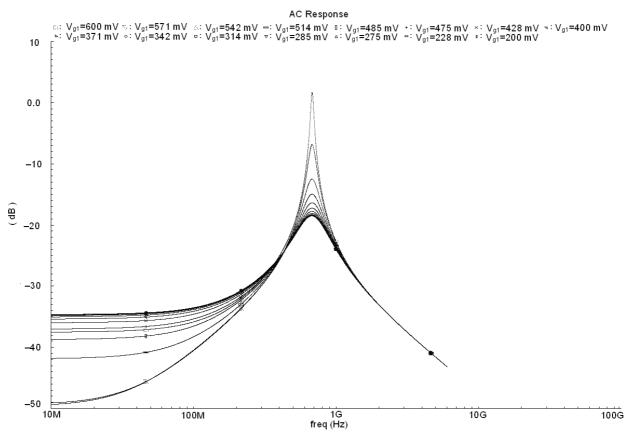

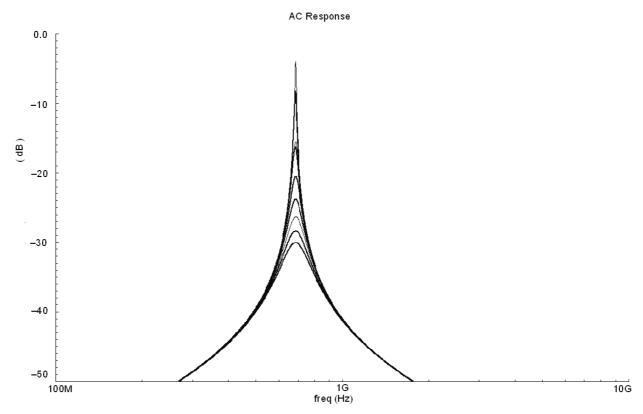

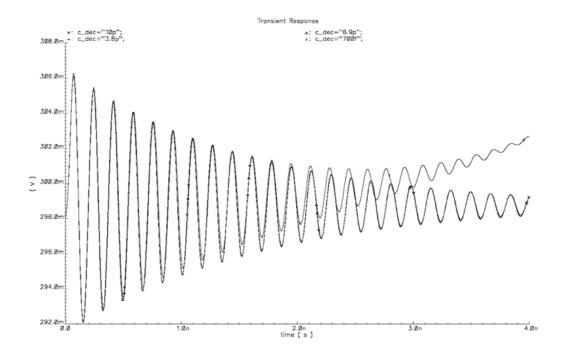

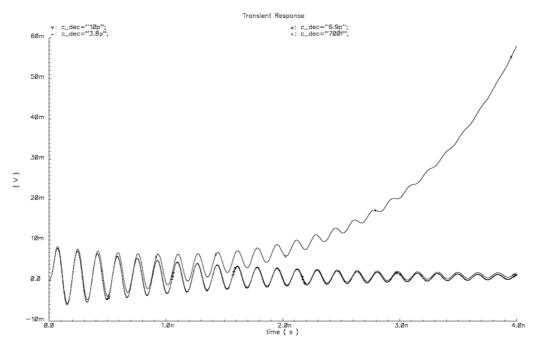

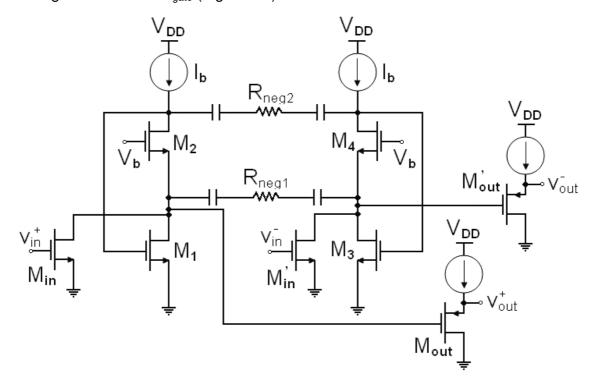

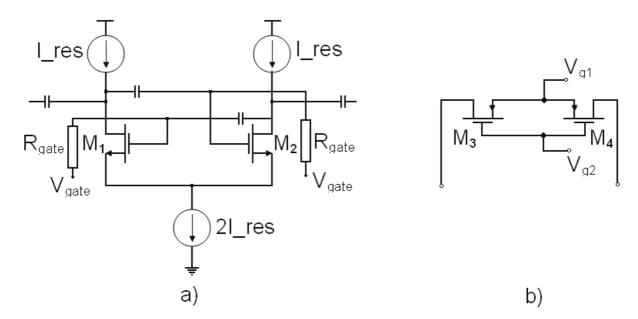

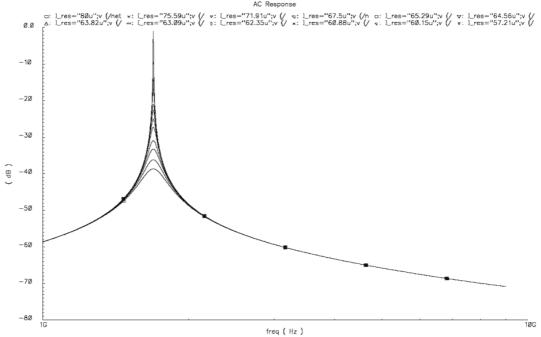

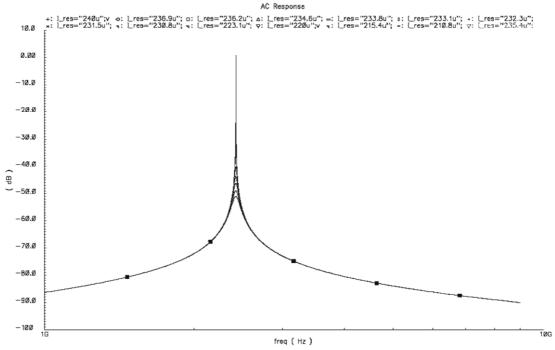

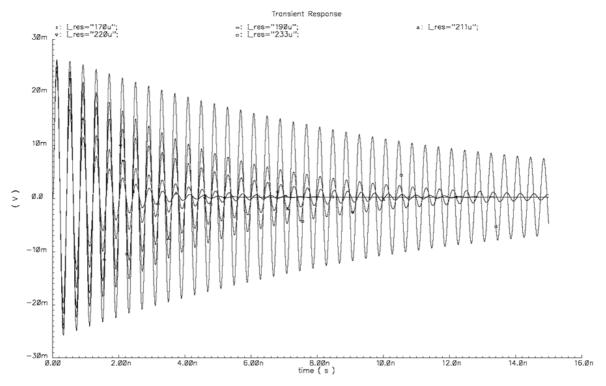

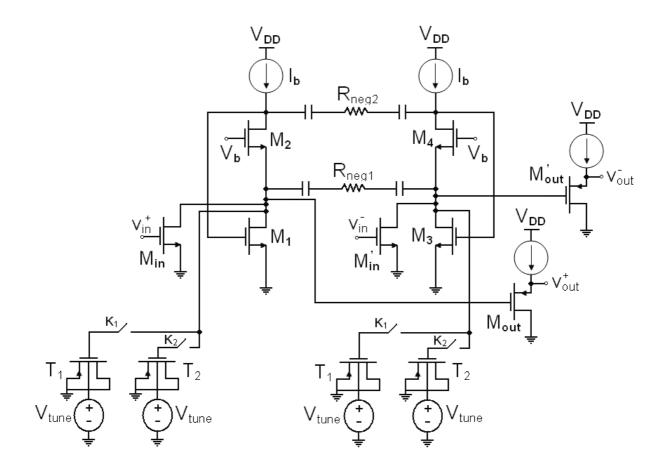

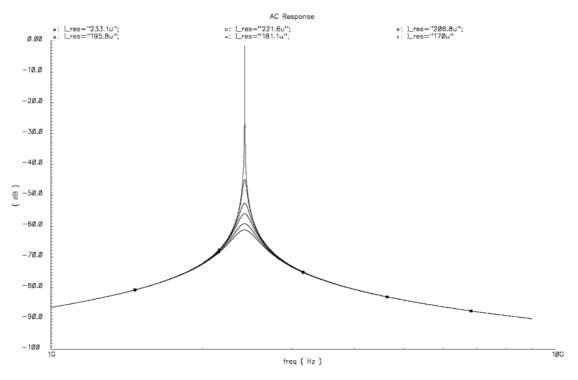

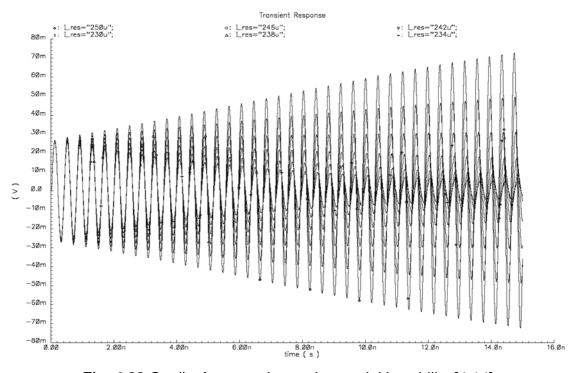

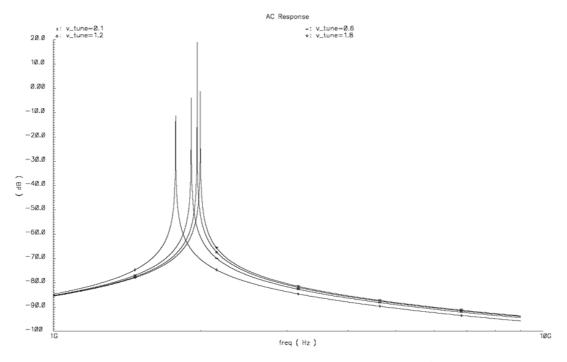

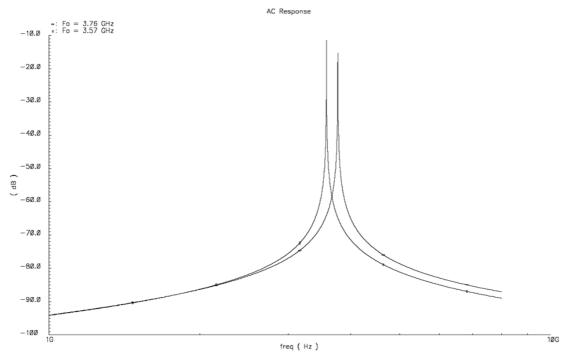

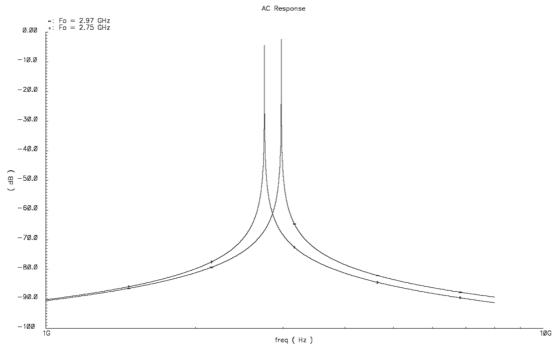

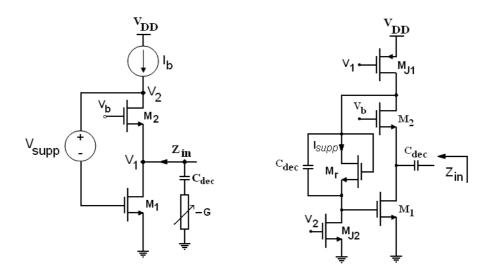

Fig. 2.18 Ideal SDR architecture