# Modélisation flux de données et optimisation pour architecture multi-cœurs de motifs répétitifs

Jonathan Piat

#### ▶ To cite this version:

Jonathan Piat. Modélisation flux de données et optimisation pour architecture multi-cœurs de motifs répétitifs. Informatique [cs]. INSA de Rennes, 2010. Français. NNT: . tel-00564522

### HAL Id: tel-00564522 https://theses.hal.science/tel-00564522

Submitted on 9 Feb 2011

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

sous le sceau de l'Université européenne de Bretagne

pour obtenir le titre de

DOCTEUR DE L'INSA DE RENNES

Spécialité : Traitement du signal et des images

Modélisation flux de données et optimisation pour architecture multi-cœurs de motifs répétitifs

## Jonathan Piat

**ECOLE DOCTORALE:** *MATISSE* LABORATOIRE: IETR

#### Thèse soutenue le 16.09.2010

devant le jury composé de :

#### **Mohamed Akil**

Professeur des universités, ESIEE Paris, France/ rapporteur

#### Pierre Boulet

Professeur des universités, LIFL Villeneuve d'Ascq, France / rapporteur

#### Shuvra S. Bhattacharyya

Professeur des universités, UMD College Park, USA / examinateur

#### Steven Derrien

Maître de conférence, IFSIC Rennes, France / examinateur

#### **Olivier Deforges**

Professeur des universités, INSA Rennes, France / directeur de thèse

#### Mickaël Raulet

Ingénieur de recherche, INSA Rennes, France / encadrant

## Acknowledgements

The work in the thesis is the result of a three-year work at the INSA of Rennes. I really enjoyed spending time working at the lab, and I would like to thank the people that made it possible.

First, I want to thank my supervisor, Pr. Olivier Deforges, for making this work possible and for the time he spent correcting my mistakes in this thesis. I also would like to thanks my co-advisors, Mickaël Raulet and Pr Jean-François Nezan, for giving me support and freedom in my work. I address special thanks to Mickaël Raulet for his contribution and Olivier Déforges' work with correcting my orthography. Thanks to Shuvra S. Bhattacharyya who helped a lot on the research and publications. His contributions during the last two years were valuable and helped me to overcome a lot of difficulties in my work. Thanks to, Pr. Mohamed Akil and Pr. Pierre Boulet, for being the reviewers of this thesis. Moreover, thanks to Steven Derrien and Pr. Shuvra S. Bhattacharyya for their participation as member of the jury.

Spending three years on the same topic would have affected my mental health without following colleagues help on both work and ambiance (not listed in any order of importance): Maxime Pelcat, Mathieu Wipliez, Médéric Blestel, Jérôme Gorin, Fabien Racapé, Emilie Bosc, Pierre Laurent Lagalaye, Mathieu Urvoy, Yohan Pitrey. Being passionate by embedded systems, robotic, and general electronic I found great geek-mates at the lab that helped me full filing my geekyness needs: Sylvain Haese, Eric Bazin, Clément Strauss, François Pasteau, Xavier Perraud. Thanks to Jocelyne Trermier, Denis Simon, Frédéric Garesche and all the technical and administrative staff of the INSA of Rennes. Special thanks to Emilie Besse for enlightening our workdays by presenting the news with her natural softness.

Those three years would not have been possible without a personal and social life. Thanks to Emilie Malenfant for sharing my life the past seven years, bearing with my meaningless technical conversation, standing by my mess and for her support in good and bad times. Thanks to her family for being close and supportive. This work would not have been possible without my family whose presence the last twenty seven years helped constructing the person I am. Thanks to my missing dad, whose positive influence has undoubtedly guided me to this point (and beyond).

## Table des matières

| 1  | Fr                                    | ench    | Summary                                         | 1          |  |  |

|----|---------------------------------------|---------|-------------------------------------------------|------------|--|--|

| 1  | Introduction                          |         |                                                 |            |  |  |

|    | 1.1 Contributions du travail de thèse |         |                                                 |            |  |  |

|    |                                       | 1.1.1   | Prototypage rapide                              | 4          |  |  |

|    |                                       | 1.1.2   | Reconfigurable Video Coding                     | 5          |  |  |

|    |                                       | 1.1.3   | Bit-Stream Description Language                 | 5          |  |  |

|    |                                       | 1.1.4   | Organisation de la thèse                        | 5          |  |  |

| 2  | Eta                                   | t de l' | art                                             | 7          |  |  |

|    | 2.1                                   | Proto   | typage rapide                                   | 7          |  |  |

|    |                                       | 2.1.1   | Introduction                                    | 7          |  |  |

|    |                                       | 2.1.2   | Systèmes de calculs distribués                  | 7          |  |  |

|    |                                       | 2.1.3   | Modèle de calcul flux de données                | 8          |  |  |

|    |                                       | 2.1.4   | Ordonnancement multiprocesseurs                 | 9          |  |  |

|    | 2.2                                   | Trans   | formation des nids de boucles                   | 9          |  |  |

|    |                                       | 2.2.1   | Boucles imbriquées et ordre séquentiel          | 9          |  |  |

|    |                                       | 2.2.2   | Dépendance de données dans les nids de boucles  | 10         |  |  |

|    |                                       | 2.2.3   | Transformation des nids de boucles              | 12         |  |  |

|    |                                       | 2.2.4   | Partitionnement des répétitions                 | 14         |  |  |

| 3  | Contributions 1                       |         |                                                 |            |  |  |

|    | 3.1                                   | Repré   | sentation hiérarchique dans le modèle SDF       | 17         |  |  |

|    | 3.2                                   | Génér   | ration de code pour le prototypage rapide       | 18         |  |  |

|    | 3.3                                   | Optin   | nisation des nids de boucles dans le modèle SDF | 20         |  |  |

| 4  | Cor                                   | ıclusio | n et propositions de travail                    | <b>2</b> 3 |  |  |

| ΙΙ | В                                     | ackgr   | round                                           | 25         |  |  |

| 5  | Int                                   | roduct  | ion                                             | 27         |  |  |

|   | 5.1 | Overvi          | ew                                                                                                                                            | 7 |  |  |  |  |

|---|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|

|   | 5.2 |                 | butions of this Thesis                                                                                                                        | 9 |  |  |  |  |

|   |     | 5.2.1           | Rapid Prototyping Framework                                                                                                                   | 9 |  |  |  |  |

|   |     | 5.2.2           | Reconfigurable Video Coding                                                                                                                   | 3 |  |  |  |  |

|   |     | 5.2.3           | Bit-Stream Description Language                                                                                                               | 4 |  |  |  |  |

|   | 5.3 | Outlin          | e of this Thesis                                                                                                                              | 6 |  |  |  |  |

| 6 | Bac | kgrour          | ad and related work 3'                                                                                                                        | 7 |  |  |  |  |

|   | 6.1 | .1 Introduction |                                                                                                                                               |   |  |  |  |  |

|   | 6.2 | Paralle         | el computing systems                                                                                                                          | 7 |  |  |  |  |

|   | 6.3 | Data I          | Flow model of computation $\dots \dots \dots$ | 1 |  |  |  |  |

|   |     | 6.3.1           | <u>Introduction</u>                                                                                                                           | 1 |  |  |  |  |

|   |     | 6.3.2           | Data Flow paradigm introduction 4                                                                                                             | 2 |  |  |  |  |

|   |     | 6.3.3           | Synchronous Data Flow (SDF) 4                                                                                                                 | 4 |  |  |  |  |

|   |     | 6.3.4           | Homogeneous Synchronous Data Flow (HSDF) 4                                                                                                    | 7 |  |  |  |  |

|   |     | 6.3.5           | Boolean-controlled Data Flow (BDF) 4                                                                                                          | 7 |  |  |  |  |

|   |     | 6.3.6           | Cyclo-Static Synchronous Data Flow (CSDF) 4                                                                                                   | 9 |  |  |  |  |

|   |     | 6.3.7           | Parameterized Synchronous Data Flow (PSDF) 5                                                                                                  | 1 |  |  |  |  |

|   |     | 6.3.8           | Conclusion                                                                                                                                    | 3 |  |  |  |  |

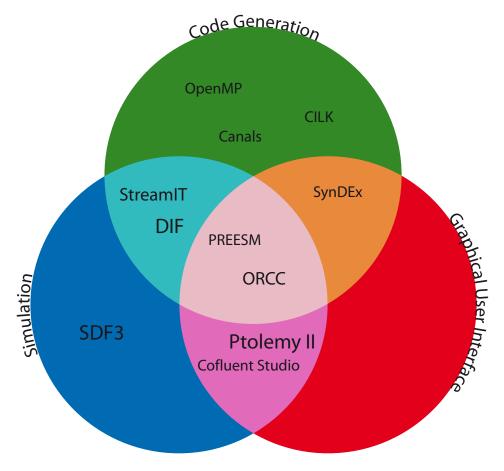

|   | 6.4 | Applie          | ation modeling tools                                                                                                                          | 4 |  |  |  |  |

|   |     | 6.4.1           | Introduction                                                                                                                                  | 4 |  |  |  |  |

|   |     | 6.4.2           | Dataflow Interchange Format                                                                                                                   | 4 |  |  |  |  |

|   |     | 6.4.3           | SDF3 5                                                                                                                                        | 5 |  |  |  |  |

|   |     | 6.4.4           | Ptolemy II                                                                                                                                    | 6 |  |  |  |  |

|   |     | 6.4.5           | StreamIt                                                                                                                                      | 6 |  |  |  |  |

|   |     | 6.4.6           | PREESM                                                                                                                                        | 7 |  |  |  |  |

|   |     | 6.4.7           | SynDEx data-flow model                                                                                                                        | 8 |  |  |  |  |

|   |     | 6.4.8           | Canals                                                                                                                                        | 8 |  |  |  |  |

|   |     | 6.4.9           | CAL Actor Language                                                                                                                            | 9 |  |  |  |  |

|   |     | 6.4.10          | MCSE specification model                                                                                                                      | 9 |  |  |  |  |

|   |     | 6.4.11          | Conclusion                                                                                                                                    | 0 |  |  |  |  |

|   | 6.5 | Multi-          | processor scheduling                                                                                                                          | 1 |  |  |  |  |

|   | 6.6 | Conclu          | <u>usion</u>                                                                                                                                  | 2 |  |  |  |  |

| 7 | Nes | ted loc         | ops Partitioning 6'                                                                                                                           | 7 |  |  |  |  |

|   | 7.1 | Introd          | uction                                                                                                                                        | 7 |  |  |  |  |

|   | 7.2 |                 | Loops representation                                                                                                                          | 7 |  |  |  |  |

|   | 7.3 |                 | Loops execution optimization                                                                                                                  |   |  |  |  |  |

|   | 7.4 |                 | Loops partitioning by iteration domain projection $\dots \dots 7$                                                                             | 1 |  |  |  |  |

|    | Nested Loops partitioning by iteration domain tiling | 73                                                                  |            |  |

|----|------------------------------------------------------|---------------------------------------------------------------------|------------|--|

|    | 7.6                                                  | Conclusion                                                          | 75         |  |

| II | I F                                                  | Research Work                                                       | <b>7</b> 9 |  |

| 8  | Hie                                                  | rarchy Representation in Synchronous Data Flow Graphs               | 81         |  |

|    | 8.1                                                  | Introduction                                                        | 81         |  |

|    | 8.2                                                  | Existing hierarchy representation in Synchronous Data Flow Graphs . | 83         |  |

|    |                                                      | 8.2.1 Repetition based hierarchy                                    | 83         |  |

|    |                                                      | 8.2.2 Parameter based hierarchy                                     | 85         |  |

|    | 8.3                                                  | Interface based hierarchy                                           | 86         |  |

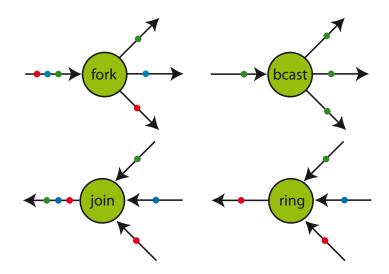

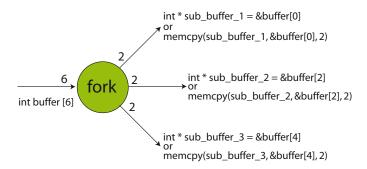

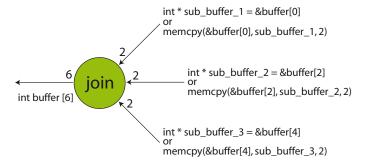

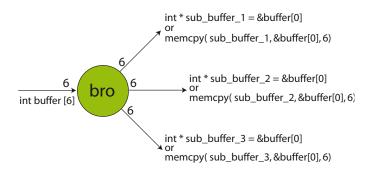

|    |                                                      | 8.3.1 Special nodes                                                 | 86         |  |

|    |                                                      | 8.3.2 Hierarchy deadlock-freeness                                   | 87         |  |

|    |                                                      | 8.3.3 Hierarchy scheduling                                          | 89         |  |

|    |                                                      | 8.3.4 Hierarchy behavior                                            | 90         |  |

|    |                                                      | 8.3.5 Hierarchy improvements                                        | 91         |  |

|    | 8.4                                                  | Application case study                                              | 91         |  |

|    |                                                      | 8.4.1 IDCT2D description                                            | 92         |  |

|    |                                                      | 8.4.2 Structural analysis                                           | 92         |  |

|    | 8.5                                                  | Conclusion                                                          | 93         |  |

| 9  | Mul                                                  | lti-core code generation of Interface based Synchronous Data-       |            |  |

|    | flow                                                 |                                                                     | 95         |  |

|    | 9.1                                                  | Introduction                                                        | 95         |  |

|    | 9.2                                                  | Multi-threaded execution model                                      |            |  |

|    | 9.3                                                  | C code generation procedure                                         |            |  |

|    | 9.4                                                  | Graph optimization for code generation                              |            |  |

|    | 9.5                                                  | Buffer optimization and allocation                                  |            |  |

|    | 9.6                                                  | Hierarchical actor port management                                  |            |  |

|    | 9.7                                                  | Actor prototypes instantiation                                      | 108        |  |

|    | 9.8                                                  | In loop actors instantiation                                        | 108        |  |

|    | 9.9                                                  | Special vertices instantiation                                      | 109        |  |

|    | 9.10                                                 | Inter Processor Communication instantiation                         | 110        |  |

|    | 9.11                                                 | xml to C transformation                                             | 112        |  |

|    | 9.12                                                 | Code generation example                                             | 114        |  |

|    | 9.13                                                 | Conclusion                                                          | 116        |  |

| ΤO | LOO]  | p partitioning techniques for Interface based Synchronous D           | a-    |

|----|-------|-----------------------------------------------------------------------|-------|

|    | taflo | $\mathbf{ow}$                                                         | 121   |

|    | 10.1  | Introduction                                                          | . 121 |

|    | 10.2  | Iteration domain projection technique                                 | . 122 |

|    |       | 10.2.1 Distance vector extraction from interface-based SDF            | . 123 |

|    |       | 10.2.2 SDF network synthesis using analysis results                   | . 124 |

|    |       | 10.2.3 The matrix vector product example                              | . 124 |

|    | 10.3  | Iteration domain tiling                                               | . 128 |

|    |       | 10.3.1 Limitations                                                    | . 129 |

|    |       | $10.3.2~{ m SDF}$ network synthesis from partitioned iteration domain | . 129 |

|    |       | 10.3.3 The matrix vector product example                              | . 132 |

|    | 10.4  | Conclusion                                                            | . 132 |

| 11 | Con   | nclusion, Current Status and Future Work                              | 137   |

|    | 11.1  | Conclusion                                                            | . 137 |

|    | 11.2  | Current Status                                                        | . 138 |

|    | 11.3  | Future Work                                                           | . 138 |

| Gl | ossaı | ${f ry}$                                                              | 144   |

Première partie

French Summary

## Chapitre 1

## Introduction

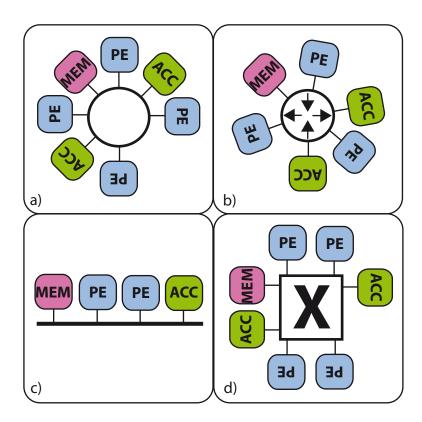

Devant la demande croissante en puissance de calcul, des applications de traitement du signal et notamment, des applications d'encodage/décodage d'images fixes et vidéos, il est de plus en plus courant de faire appel à la puissance des architectures multi-coeurs/multiprocesseurs. Ce type d'architecture présente une puissance potentielle importante, mais la complexité d'implémentation d'une application est élevée. En effet, ce type d'architecture peut, selon le contexte, faire appel à des types de processeurs différents tels que DSP ou GPU mais aussi à des coeurs généralistes (x86, ARM ...). Ces coeurs de processeur sont interconnectés au travers de réseaux de communication présentant des topologies adaptées.

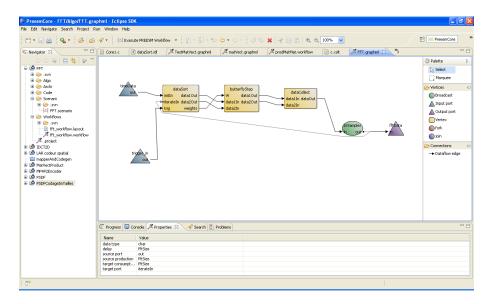

Afin de parvenir rapidement à une implémentation fiable et efficace sur ce type d'architecture, il est nécessaire de faire appel à des outils de prototypage rapide tel que PREESM, PEaCe ou SynDEx qui proposent des méthodes automatiques pour parvenir à une solution d'implantation d'un algorithme sur une architecture parallèle rapidement. Ces outils s'appuient sur un modèle d'application de type flux de données, qui modélise l'application au travers des dépendances de données qui existent entre les acteurs qui la compose. Un acteur est un élément opératoire qui consomme des données, effectue un calcul et produit des données. Ces acteurs sont connectés au sein d'un réseau au travers d'arcs qui symbolisent les dépendances de données.

L'outil PREESM est l'un des fruits de cette thèse et s'appuie sur le modèle Synchronous Data Flow, ou modèle Flux de Données Synchrone. Ce modèle spécifie pour chaque tâche le nombre de données produites et consommées par chaque acteur pour une exécution de celui-ci. Ces informations permettent d'extraire un ordre total d'exécution des acteurs qui composent le réseau ainsi que la mémoire requise pour la communication entre les acteurs. Dans le modèle flux de données, il existe une représentation hiérarchique du réseau qui permet de spécifier le comportement de chaque acteur au travers d'un réseau flux de données. Dans le modèle SDF (Synchronous

4 Introduction

Data Flow), la technique du clustering permet d'extraire une représentation hiérarchique à partir d'une représentation à plat, mais il n'existe pas de modèle spécifique de hiérarchie qui permette la spécification d'un réseau SDF ou chaque acteur peut lui même être spécifié par un réseau SDF.

La première contribution de cette thèse est de définir un tel modèle de hiérarchie en spécifiant des règles qui assurent la composition (comme définit précédemment). De ce fait, il est possible d'extraire un ordonnancement du réseau de plus haut niveau indépendamment de l'ordonnancement des réseaux qui spécifient le comportement des acteurs. Ce modèle s'approche, par son interprétation, du découpage en fonctions et blocks possible dans le code C.

Une autre contribution de cette thèse est la partie génération de code C de l'outil PREESM. Cette génération de code a pour but de délivrer un code C dans un format compréhensible et structuré. De plus, la flexibilité de la méthode de génération permet à l'utilisateur de configurer la technique d'allocation mémoire et de facilement s'adapter à différents types de matériels et OS. Il est également envisageable de générer du code dans un langage autre que le C avec peu de modifications.

Enfin, une dernière contribution établit l'utilisation de méthodes d'extraction de parallélisme dans les nids de boucles appliquées au domaine de la modélisation flux de données synchrone. Ce type de transformation permet d'extraire du parallélisme d'une description factorisée de l'application tout en conservant un nombre réduit de sommets à ordonnancer.

Durant cette thèse, j'ai également participé à des contributions dans le domaine du codage vidéo. En effet, l'équipe "<image"> de l'IETR est impliquée dans l'encodage/décodage d'images fixes et de vidéos. L'équipe participe depuis peu au standard MPEG-RVC, et j'ai été impliqué dans des travaux connexes. La première contribution concerne la validation de bit-stream dans RVC. J'ai participé au développement de l'outil de validation, et j'ai apporté ma contribution à une publication sur la procédure de validation d'un bit-stream. J'ai, également, participé au portage sur plateforme ARM d'un décodeur vidéo reconfigurable. Ce décodeur utilise la technologie LLVM pour implémenter un décodeur reconfigurable à partir d'une description d'un réseau d'acteurs CAL. Une description plus complète de l'environnement des contributions est décrite ci-après.

#### 1.1 Contributions du travail de thèse

#### 1.1.1 Prototypage rapide

Les travaux contenus dans cette thèse sont des contributions au logiciel de prototypage rapide PREESM (Parallel Real-tile Embedded Executive Scheduling Me-

thod). Le prototypage rapide vise à établir rapidement un prototype d'une application donnée pour une architecture donnée. Ce prototype est généré à partir de descriptions haut niveau de l'architecture et l'application. A partir de ces spécifications haut niveau, le logiciel se charge d'établir un partitionnement de l'application sur les coeurs de l'architecture cible. Il génère, ensuite, un ordonnancement pour chaque coeur. L'objectif final est de générer, à partir de cet ordonnancement, du code compilable et exécutable. Le logiciel prend donc en charge une majeure partie de la complexité afin de faciliter le travail du programmeur.

#### 1.1.2 Reconfigurable Video Coding

Le standard RVC définit par MPEG, s'attache à décrire les actions qui composent un décodeur générique pour en dresser une bibliothèque et pouvoir configurer dynamiquement un décodeur. Les acteurs sont appelés "<Functionnal Units"> (Unités fonctionnels ou FU) et sont instanciés dans un réseau qui définit les échanges de données entre FU. A partir de cette description, il est alors possible de créer dynamiquement une structure de décodage vidéo. Le langage de spécification des acteurs est RVC-CAL.

#### 1.1.3 Bit-Stream Description Language

Dans le cadre du standard RVC, il est nécessaire d'être capable de décrire la structure du flux d'informations d'entrée du décodeur. En effet, le seul élément non standard dans l'ensemble des codecs, est la structure du flux. Afin de valider la structure du flux, il est nécessaire d'avoir recours au standard BSDL qui fournit la syntaxe de description du flux et en décrire la structure dans un fichier de type xslt. Il est également possible de générer dynamiquement un acteur capable d'interpréter ce flux et ainsi l'utiliser dans le cadre de RVC. J'ai travaillé, dans ce contexte, sur les outils qui permettent d'obtenir la description BSDL d'un flux à partir d'une séquence, et la séquence à partir d'une description BSDL. J'ai également participé à la rédaction d'un article sur la méthode de validation de la structure d'un flux.

#### 1.1.4 Organisation de la thèse

La suite de cette thèse s'organise comme suit :

- Cette première partie présente un résumé substantiel du travail effectué en français

- Une deuxième partie dresse un état de l'art en anglais des éléments nécessaires à la compréhension de la suite du document

- Une troisième partie en anglais présente les travaux de recherche effectués.

6 Introduction

## Chapitre 2

## Etat de l'art

#### 2.1 Prototypage rapide

#### 2.1.1 Introduction

Le prototypage rapide s'attache à fournir un ensemble d'étapes automatisées qui permettent, à partir d'une description haut niveau de l'application et de l'architecture, de générer une solution optimisée d'implantation. Les outils de prototypage rapide répondent à la problématique d'implantation d'algorithmes complexes sur des architectures parallèles. Ces architectures embarquent un nombre variable de processeurs, ainsi que différents moyens de communication entre ces processeurs. Le modèle d'application utilisé doit fournir suffisamment d'informations pour extraire du parallélisme sans dénaturer le comportement de l'application. Le modèle flux de données symbolise une application par les dépendances de données qui existe entre ces constituants. A l'aide de ce modèle, il est ainsi aisé d'extraire le parallélisme intrinsèque et différentes informations permettant l'optimisation mémoire et l'ordonnancement.

#### 2.1.2 Systèmes de calculs distribués

Un système de calcul distribué est caractérisé par plusieurs éléments :

- Application cible : un système de calcul distribué est avant tout caractérisé par l'application cible. On distinguera deux grands types d'applications : dominés par le contrôle ou dominés par les données. En effet, une application dominée par le contrôle devra, par exemple, présenter un temps de réaction faible, tandis qu'une application dominée par les données devra être capable d'un important débit et d'une puissance de calcul.

- Consommation/Performance: Les choix architecturaux sont, dans le cas des

8 Etat de l'art

applications mobiles, guidés par le choix du meilleur rapport consommation/performance. En effet, une architecture parallèle offre plus de possibilités pour

améliorer ce rapport. La multiplication des coeurs, permet (selon l'application)

de baisser la fréquence de ceux-ci et ainsi limiter les pertes joules.

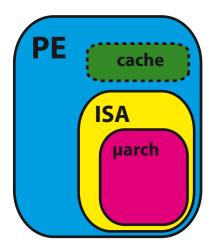

- Elément de calcul : L'élément de calcul, est, dans le cas des architectures multi-coeurs, un coeur du système. Un système multi-coeurs est donc généré par l'interconnexion de multiples éléments de calculs homogènes ou hétérogènes.

Cet élément de calcul est caractérisé par le jeu d'instructions qu'il prend en charge et sa microarchitecture. La microarchitecture définit la manière dont est implémenté le jeu d'instruction. L'efficacité de l'élément de calcul dépend grandement de sa microarchitecture.

- Système mémoire : Le système mémoire de l'architecture est caractérisé par : le système de cache, l'interconnexion des éléments de calcul, et la gestion de la cohérence.

- Accélérateurs, Périphériques : Les accélérateurs et périphériques sont des composants non programmables (configurables) de l'architecture. Ces composants effectuent des tâches dédiées avec une grande efficacité et en parallèle des éléments de calcul. Le DMA (Direct Memory Access) peut, par exemple, effectuer des transferts de mémoire à mémoire sans intervention d'un élément de calcul.

Les éléments donnés ci-dessus permettent de caractériser de manière précise un système de calcul distribué de type multi-coeurs. Pour un système de type multi-processeurs, pour lequel la division des coeurs et à la fois logique et spatiale, il est également nécessaire de caractériser le système de communication entre les processeurs. En effet, dans un système multi-coeurs, les éléments de calcul résident dans un seul composant physique. Dans le cas d'un système multiprocesseurs, plusieurs éléments physiques sont connectés par un medium. Ce type d'interconnexion présente des caractéristiques différentes de l'interconnexion sur puce.

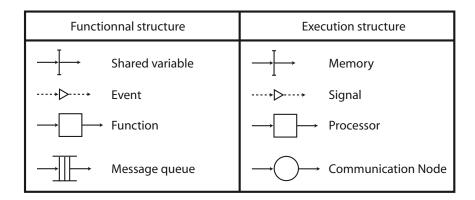

#### 2.1.3 Modèle de calcul flux de données

Les modèles de calcul flux de données s'attachent à décrire le comportement d'une application au travers des dépendances de données qui existent entre les tâches qui la composent. La description flux de données repose sur trois éléments :

- Acteur : Un acteur représente une entité de calcul de l'application.

- Jeton de données : Un jeton de données est l'élément d'une donnée atomique que s'échangent les acteurs.

- Arc : Un arc connecte deux acteurs. Un acteur produit des données sur l'arc que l'acteur/consommateur peut ensuite consommer.

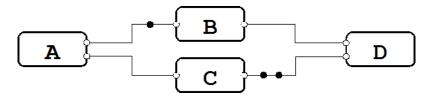

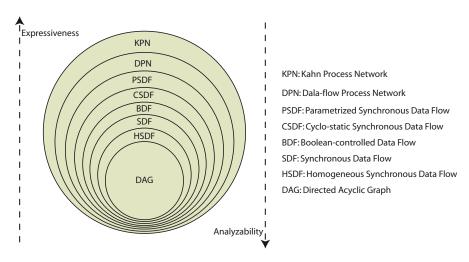

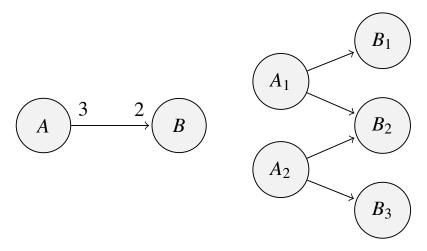

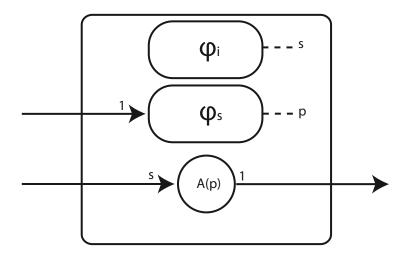

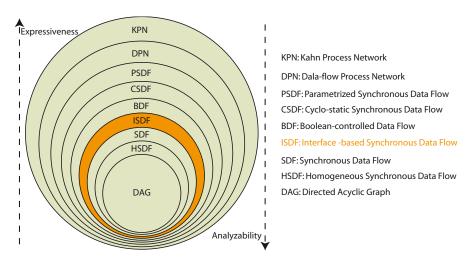

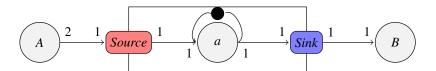

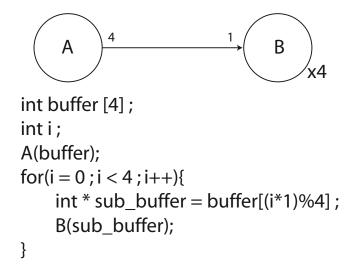

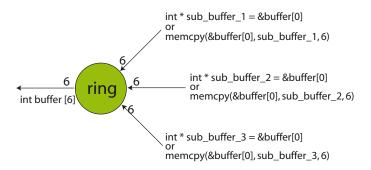

Figure 2.1 – Réseau d'acteurs échangeant des jetons de données

L'interconnexion des acteurs au travers des arcs constitue un réseau. Le modèle flux de données le plus générique est appelé Kahn Process Network (KPN). Dans ce modèle, les acteurs sont connectés par l'intermédiaire de FIFO (First In First Out) unidirectionnels non limités. Le modèle Data flow Process Network limite le modèle KPN en associant aux acteurs des règles de déclenchement (Firing rules). Ces règles spécifient les séquences de données d'entrée permettant l'exécution de l'acteur. D'autres modèles tels que le SDF restreignent l'expressivité en associant pour chaque arc trois nombres entiers représentant le nombre de jetons produits (production rate), le nombre de jetons consommés (consumption rate) et le nombre de jetons initialement présents sur l'arc. Ce modèle permet de déterminer un ordonnancement de l'application avant exécution et ainsi garantir son bon fonctionnement à l'exécution et une consommation mémoire bornée.

#### 2.1.4 Ordonnancement multiprocesseurs

Grâce à un modèle des caractéristiques de l'architecture multi-coeurs et un modèle flux de données de l'application; il est possible de déterminer la meilleure implémentation de l'application sur l'architecture. Pour y parvenir il est, tout d'abord nécessaire, de répartir les acteurs qui composent la description flux de données sur les différents opérateurs de l'architecture. Cette opération est appelée : allocation. Ensuite, il faut, pour chaque processeur, décrire l'ordonnancement des acteurs et organiser les communications entre opérateurs. Cette implémentation cherche à optimiser un ou plusieurs critères d'exécution tel que le temps d'exécution (cadence ou latence), l'empreinte mémoire et/ou la consommation électrique.

#### 2.2 Transformation des nids de boucles

#### 2.2.1 Boucles imbriquées et ordre séquentiel

**Definition** On désigne par « nid de boucles » une structure composée de plusieurs boucles imbriquées.

10 Etat de l'art

Cette définition peut être restreinte dans le cas des nids de boucles dit parfaits ou parfaitement imbriqués.

**Definition** On désigne par « nid de boucles parfait » un nid de boucles pour lequel le code de chaque boucle ne contient qu'une autre boucle à l'exception de la boucle la plus interne.

Exemple de nid de boucles imparfait :

```

\begin{array}{l} \textbf{for} \ \ i_1 \ := \ l_1 \ \ \textbf{to} \ \ u_1 \ \ \textbf{do} \\ \textbf{for} \ \ i_2 \ := \ l_2(i_1) \ \ \textbf{to} \ \ u_2(i_1) \ \ \textbf{do} \\ & \dots \\ \textbf{for} \ \ i_n \ := \ l_n(i_1, i_2, ..., i_{n-1}) \ \ \textbf{to} \ \ u_n(i_1, i_2, ..., i_{n-1}) \ \ \textbf{do} \\ S \ : \{Instruction1\} \\ & \dots \\ \{Instructionk\} \\ \textbf{end} \\ \textbf{end} \\ \textbf{end} \end{array}

```

Figure 2.2 - Example de nid de boucles imparfait

Chaque boucle définit un vecteur d'itération (ex : i=0 to N) et l'imbriquement des boucles définit un domaine d'itération de dimension égale à la profondeur du nid (le nombre de boucles imbriquées). Dans notre exemple, ce nid de boucles définit un domaine dans  $Z^n$  inclus dans le polyèdre  $l_1 \leq i_1 \leq u_1, l_2(i_1) \leq i_2 \leq u_2(i_1)...l_n(i_1,i_2,...,i_{n-1}) \leq i_n \leq u_n(i_1,i_2,...,i_{n-1})$ . Le programme exécute chaque opération notée S entourée par une boucle pour toutes les valeurs I du vecteur d'itération dans un ordre séquentiel noté  $<_{seq}$  définit par l'ordre lexicographique du vecteur d'itération.

$$S(I) <_{seg} S(J) \leftarrow I <_{lex} J$$

#### 2.2.2 Dépendance de données dans les nids de boucles

#### Types de dépendances

Les catégories de dépendances identifiées par Bernstein et résumées dans leur livre par Alain Darte, Yves Robert et Frédéric Vivien [AYF00], sont de trois types : Les dépendances de flot, anti-dépendances et dépendances en sortie. Il y a une dépendance de données entre S(I) et T(J) si les deux opérations accèdent au même emplacement mémoire et si au moins un accès est une écriture. La dépendance est dirigée comme dans l'ordre séquentiel, c'est-à-dire qu'il y a dépendance de  $S(I) \to T(J)$

si dans l'ordre séquentiel on à  $S(I) <_{seq} T(J)$ . Les trois types de dépendances sont ici :

- **Dépendance de flot**: Si l'accès à l'emplacement mémoire commun est une écriture pour S(I) et une lecture pour T(J) et qu'il n'y a aucun accès en écriture sur l'emplacement entre S(I) et T(J) dans l'ordre séquentiel.

- Anti-dépendance : Si l'accès à l'emplacement mémoire commun est une lecture pour S(I) et une écriture pour T(J) et qu'il n'y a aucun accès en écriture sur l'emplacement entre S(I) et T(J) dans l'ordre séquentiel.

- **Dépendance en sortie :** Si S(I) et T(J) sont deux écritures consécutives au même emplacement mémoire.

#### Représentation des dépendances

Les vecteurs de dépendances expriment dans le domaine D des itérations la dépendance entre deux itérations. Le calcul de ces vecteurs se fait par analyse du code des boucles du nid.

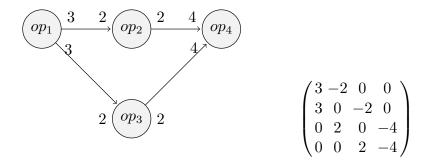

FIGURE 2.3 - Exemple de nid de boucles

Dans l'exemple de nid de boucles (figure 2.3) décrit ici, on peut établir quatre vecteurs de dépendances. Le premier décrit la dépendance existant entre l'instruction  $S_1$  et l'instruction  $S_3$ , ce vecteur décrira donc une dépendance de flot.

$$S_1 \to S_3 \ d_1 = \left(\begin{array}{c} 0\\2 \end{array}\right)$$

Ce vecteur est obtenu par égalité sur les indices, pour cela on pose l'égalité sur les indices d'itération entre l'instruction  $S_1$  et l'instruction  $S_3$ , ce qui nous donne.

12 Etat de l'art

$i_3 = i_1 - 2$  et  $j_3 = j_1$ , la dépendance étant une dépendance de flot le vecteur est orienté de  $S_3$  vers  $S_1$  on a donc  $i_1 = i_3 + 2$  et  $j_3 = j_1$ , ce qui nous donne le vecteur de dépendance. Sur l'exemple, les autres vecteurs de dépendance sont :

$$S_{3} \rightarrow S_{2} \ d_{2} = \begin{pmatrix} 1 \\ -6 \end{pmatrix}$$

$$S_{2} \rightarrow S_{1} \ d_{3} = \begin{pmatrix} 1 \\ 5 \end{pmatrix}$$

$$S_{1} \rightarrow S_{4} \ d_{4} = \begin{pmatrix} 0 \\ 1 \end{pmatrix}$$

$$S_{4} \rightarrow S_{1} \ d_{5} = \begin{pmatrix} 1 \\ -4 \end{pmatrix}$$

Conventence and large

Ces vecteurs sont largement utilisés dans les méthodes de transformation de nid de boucles ou d'ordonnancement.

#### 2.2.3 Transformation des nids de boucles

#### Types de transformation

Afin de maximiser le parallélisme exploitable dans un nid boucles, il est nécessaire de passer par une étape de transformation, rendant explicite le parallélisme implicite. Une transformation est dite légale si elle respecte les dépendances entres les itérations d'un nid boucles et donc si le résultat de l'exécution de la boucle transformée est conforme au résultat attendu. Les transformations peuvent prendre plusieurs formes.

**Distribution :** Ce type de transformation vise à distribuer un nid de boucles mal structuré afin de faire apparaître au moins une boucle forall.

Fusion : Ce type de transformation a pour but de fusionner le corps de plusieurs boucles en une seule. Cela a pour effet d'augmenter la localité des données et de minimiser les communications.

Déroulement de la boucle : Dans cette transformation on déroule les itérations de la boucle afin de faire apparaître un parallélisme maximum.

Partitionnement : On cherche ici à scinder les boucles afin de faire apparaitre des sous ensembles disjoints.

Transformation uni-modulaire : Dans une transformation uni-modulaire on change l'ordre dans lequel les vecteurs d'itérations sont énumérés. Le nouveau vecteur

d'itération est déterminé par le produit du vecteur d'itération originel avec une matrice uni-modulaire. I' = TI.

#### Méthode de l'hyperplan

Cette méthode de transformation de boucles dite méthode de l'hyperplan ou méthode de Lamport [Lam74] consiste à chercher à transformer un nid de boucles en un nid de boucles pour lequel un certain nombre de boucles internes peuvent être exécutés en parallèle. Le cas optimal est le cas où toutes les boucles internes peuvent être effectuées en parallèle.

```

\begin{array}{l} \mathbf{for} \ t := 0 \ \mathbf{to} \ t_N \ \mathbf{do} \\ \mathbf{for} \ i_2 := l_2(i_1) \ \mathbf{to} \ u_2(i_1) \ \mathbf{do} \\ & \dots \\ \mathbf{for} \ p \in E(t) \ \mathbf{do} \ \mathbf{in} \ \mathbf{parallel} \\ P(p) \\ \mathbf{end} \\ \mathbf{end} \\ \mathbf{end} \end{array}

```

Figure 2.4 — Nid de boucles transformées pour permettre l'exécution en parallèle des itérations de la boucle la plus interne

Dans ce nid la boucle externe correspond à une itération. E(t) est l'ensemble des itérations calculées à l'itération t et P(p) représente l'ensemble des boucles exécutées en parallèles correspondant au vecteur d'itération p. La complexité du partitionnement repose sur la recherche d'une fonction de séquencement. Dans la recherche du partitionnement, il faut faire attention à ce que les dépendances soient respectées afin de garantir l'intégrité du calcul. Lamport [Lam74] propose de se restreindre au cas de fonctions de séquencement linéaire au point du domaine C'est-à-dire qu'il cherche à déterminer une famille d'hyperplans affines parallèles,H(t) tel que l'ensemble des points calculés à l'instant t soit  $E(t) = H(t) \cap D$  l'intersection de l'hyperplan et du domaine. Le passage d'un hyperplan à un autre  $H(t) \to H(t+1)$  se fait par translation de l'hyperplan d'un vecteur  $\pi$  appelé vecteur de temps. Dans le cas d'une boucle uniforme, les vecteurs de dépendances sont positifs, il est aisé de construire un vecteur de temps solution. Il suffit pour cela de déterminer un vecteur  $\pi$  tel que pour tout vecteur de dépendance d on ait  $\pi d > 1$ . Les points p calculés à l'instant t forment l'hyperplan définit par  $E(t) = \{p; Ap \leq b; [\pi p] = t\}$ , et on peut calculer le temps de calcul total d'exécution de la boucle ainsi contractée en calculant t pour le dernier point du domaine  $t_{execution} = \pi p_{max}$

Lamport propose de faire de la façon suivante, : soit  $D = (d_1, ..., d_m)$  la matrice

14 Etat de l'art

des vecteurs de dépendances, de taille  $n \times m$  ou n est la profondeur du nid et m est le nombre de vecteurs de dépendances. On suppose D organisé selon l'ordre lexicographique croissant (de la dépendance la plus courte à la dépendance la plus longue). Soit  $k_1$  la première composante non nulle de  $d_1$  le premier vecteur de D. Comme  $d_1$  est positif,  $d_{1,k_1} \geq 0$ . On pose  $\pi_{k_1}$  et  $\pi_k = 0$  pour  $k_1 \neq k \neq n$ . Soit maintenant  $k_2$  l'indice de la première composante non nulle de  $d_2$ . Comme  $d_1$  est lexico graphiquement plus petit que  $d_2$ ,  $k_2 \leq k_1$ . On pose  $\pi_k = 0$  pour  $k_2 < k < k_1$ , et on prend pour  $\pi_{k_2}$  le plus petit entier positif tel que  $\pi d_2 > 0$ , en modifiant éventuellement  $\pi_{k_1}$  si  $k_2 = k_1$ . En réitérant le processus on obtient le vecteur de temps solution.

Pour des nids de boucles uniformes, plusieurs cas particuliers de la méthode de l'hyperplan ont été proposés, chacun d'eux privilégie un certain type de vecteur de temps.

#### 2.2.4 Partitionnement des répétitions

#### Méthode de projection

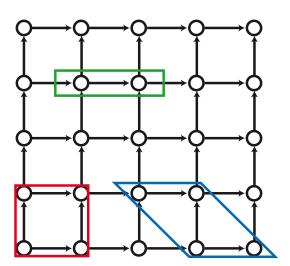

Cette méthode propose de résoudre le problème du partitionnement des applications en utilisant l'algèbre linéaire. En effet, le but de cette méthode est de produire automatiquement un réseau systolique calculant un problème exprimé par un système d'équations récurrentes uniformes. L'idée générale est de profiter de la cyclicité et de l'uniformité des dépendances pour obtenir un réseau dans lequel la circulation de données est synchrone et formée de cellules modulaires. Les calculs sont répartis sur le réseau par une fonction d'allocation linéaire et séquencés par une fonction de temps.

**Principe**: La construction du réseau se fait par projection du domaine de calcul selon un vecteur s primitif choisi en fonction de la taille du réseau à générer et la position des entrées-sorties. Le choix du vecteur s doit également respecter les contraintes temporelles imposées par le vecteur temporel  $\tau$ .

Le domaine de calcul de l'équation récurrente se fait dans le domaine D définissant le polyèdre  $D = \{x | Ax \leq b\}$  dans  $Z^n$ .

Les dépendances sont représentées par une matrice correspondant aux vecteurs valuant les arrêtes du graphe réduit de l'équation récurrente :  $D = (d_i, ..., d_n)$

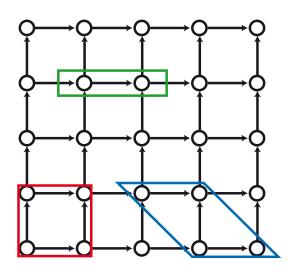

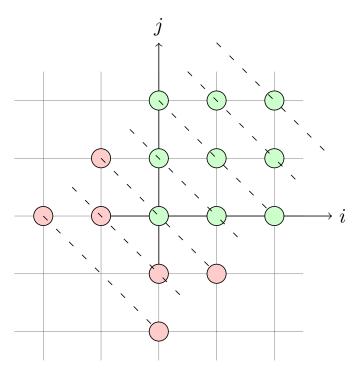

Figure 2.5 – Exemple de domaine d'itération et plusieurs solutions de projection

#### Méthode de pavage

La méthode de pavage (ou tiling) cherche à grouper plusieurs points de calcul du domaine d'itération afin de les exécuter de manière atomique. Cette technique s'assure que le calcul d'un block ne nécessite pas de communication afin de minimiser le coût des synchronisations entre blocs de calcul.

Principe: Cette méthode repose sur la construction d'une « tuile » dont la forme englobe plusieurs points du domaine d'itération. Une fois la forme de la tuile déterminée, celle-ci peut être mise à l'échelle afin d'optimiser le volume de calcul de chaque tuile et le volume de communication aux interfaces de la tuile. Cette tuile, dite tuile canonique est ensuite translatée par un vecteur de temps valide afin de paver l'intégralité du domaine.

16 Etat de l'art

Figure 2.6 – Exemple de domaine d'itération et plusieurs solutions de pavage.

## Chapitre 3

## Contributions

## 3.1 Représentation hiérarchique dans le modèle SDF

Le modèle SDF dispose de plusieurs modes de représentation hiérarchique :

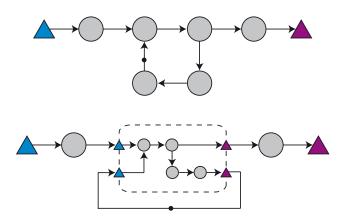

- Clustering : Ce mode de représentation hiérarchique s'attache à regrouper plusieurs acteurs d'une représentation SDF afin qu'ils puissent être exécutés de manière atomique. Cet ensemble d'acteurs est appelé cluster, et peut être représenté et traité comme un acteur unique. Ce regroupement s'appuie sur un ensemble de règles qui garantissent l'exécution atomique du cluster sans perturber le comportement de l'application. Cette hiérarchie part d'une représentation à plat pour en extraire des niveaux de hiérarchie.

- Parameterized SDF: Le modèle PSDF s'attache à décrire la structure d'applications dont le comportement de sous-systèmes varie à l'exécution. Dans ce modèle, la topologie de ces sous-systèmes est décrite à l'aide de facteur de production/consommation et d'acteurs paramétrés. Ces paramètres sont résolus à l'exécution par l'intermédiaire de deux acteurs spécifiques. L'acteur init est exécuté pour chaque instanciation du sous-système et il peut affecter les paramètres qui conditionnent l'ordonnancement du réseau parent du sous-système. L'acteur sub<sub>init</sub> peut affecter les paramètres qui n'affectent que la topologie du sous-système et/ou le comportement des acteurs. Ce type de hiérarchie s'appuie sur la sémantique du modèle SDF tout en ajoutant une couche de paramétrage du modèle qui est résolu à l'exécution. Ce paramétrage augmente l'expressivité du modèle tout en augmentant sa complexité et en diminuant sa vérificabilité.

Ces deux modèles permettent de spécifier de manière hiérarchique une application. Le clustering construit automatiquement la représentation hiérarchique en partant d'une représentation à plat de l'application. Le modèle PSDF permet de décrire des applications dont le comportement de certains sous-systèmes peut varier 18 Contributions

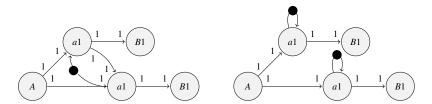

à l'exécution. Nous proposons un modèle qui respecte la sémantique SDF et son caractère statique, tout en permettant la spécification hiérarchique de l'application (voir [PBR09]). Cette hiérarchie ne serait pas extraite d'une représentation à plat comme dans le clustering, mais permettrait au concepteur de raffiner une représentation gros grain en spécifiant le comportement de certains acteurs au travers d'une représentation SDF. Afin de permettre cette spécification, il est nécessaire de définir les propriétés du modèle permettant la composition de spécifications SDF. Ce modèle s'appuie sur l'ajout d'interfaces aux sous-systèmes SDF pour garantir la cohérence entre les niveaux de hiérarchie. Le comportement de ces interfaces s'appuie sur un ensemble de règles qui garantissent l'atomicité du sous-système et qui assurent l'indépendance en terme d'ordonnancement des différents niveaux de hiérarchie.

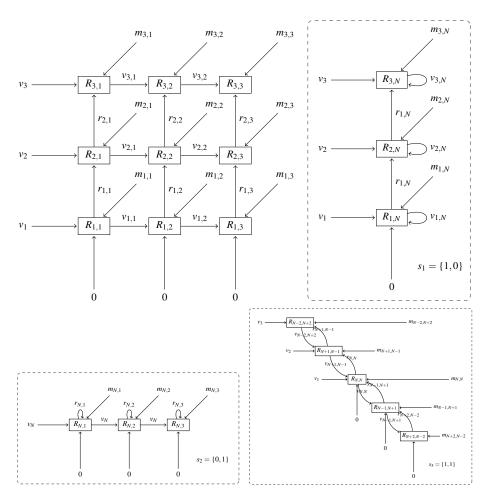

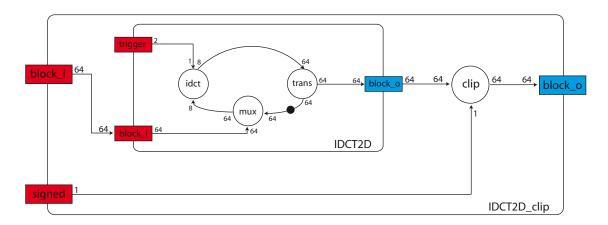

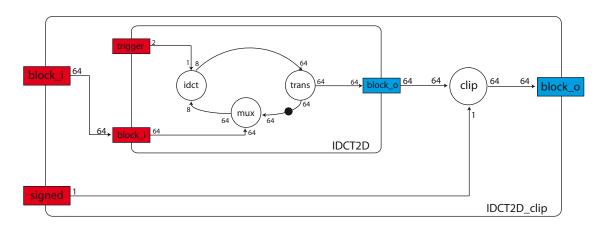

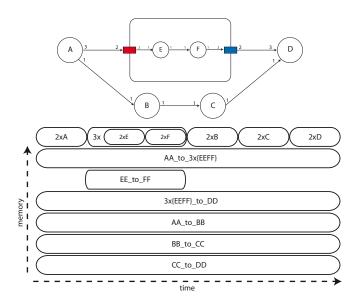

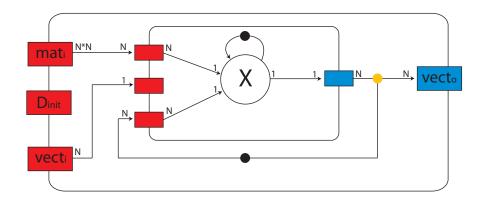

FIGURE 3.1 – Exemple d'application d'IDCT2D utilisant le modèle hiérarchique

Cette hiérarchie permet d'impliquer le designer dans le processus de composition de la hiérarchie et ainsi de structurer cette hiérarchie selon la hiérarchie existant dans la sémantique des données et/ou des opérations. De plus, ce type de hiérarchie autorise des optimisations mémoires et opératoires basées sur les choix du designer. Enfin, la hiérarchie spécifiée par l'utilisateur peut être utilisée pour générer le code de l'application dans une forme structurée et facilement interprétable par le designer.

#### 3.2 Génération de code pour le prototypage rapide

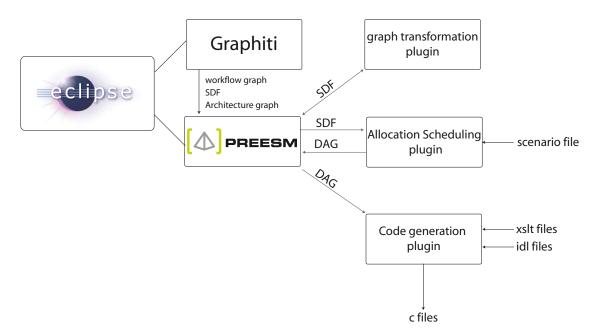

Une des contribution de cette thèse consiste à générer du code multiprocesseur à partir du modèle de hiérarchie décrit précédemment (voir [PBPR09]). Cette génération de code cible les architectures multi-coeur embarqués grâce à une allocation mémoire statique et une empreinte de code réduite. Cette génération de code est implémentée dans l'outil PREESM développée depuis 2007 à l'Institut d'Electronique et de Télécommunication de Rennes dans l'équipe image et télédétection. Cet

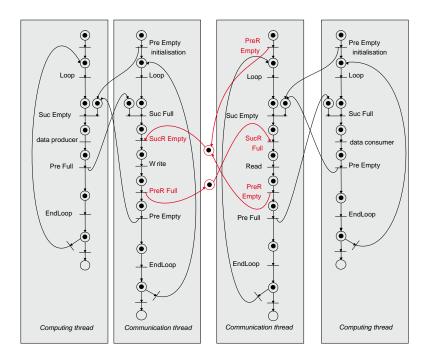

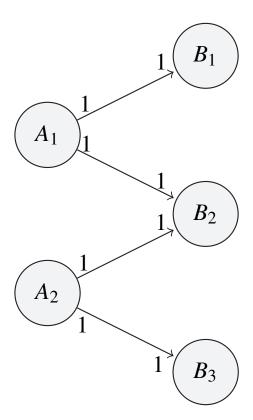

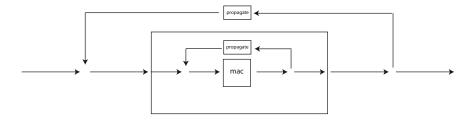

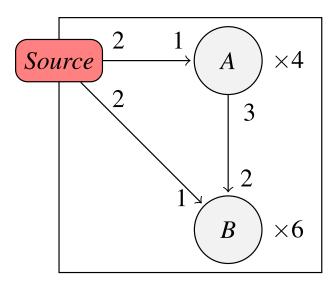

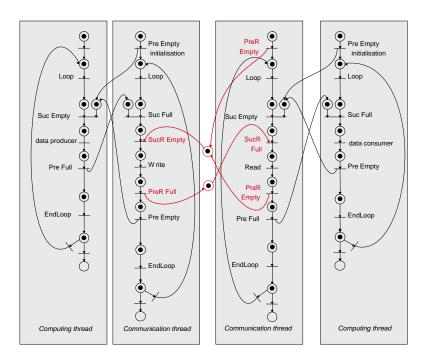

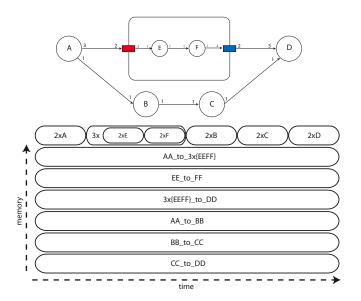

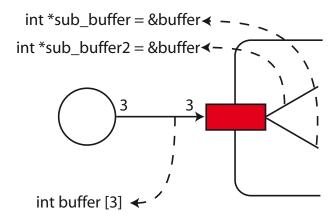

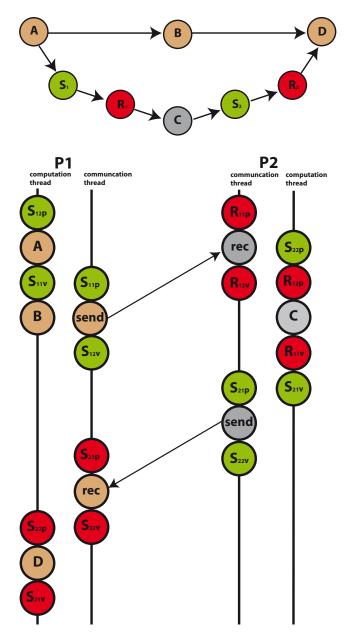

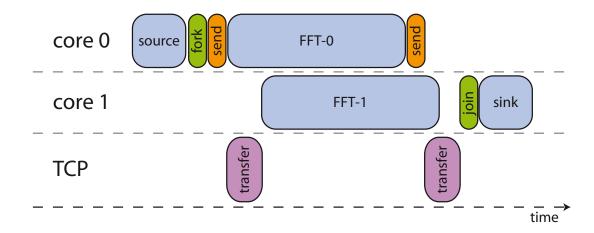

outil s'appui sur l'environnement de développement Eclipse pour proposer un outil de prototypage rapide couvrant les étapes de spécification de l'application (plugin Graphiti), spécification de l'architecture, prototypage automatique et génération de code. Le prototypage de l'application sur l'architecture spécifié ce fait par une suite de traitements séquentiels sur les informations d'entrée pour terminer par générer du code multiprocesseur compilable pour les différents processeurs/coeurs de l'architecture. Cette suite de traitement est dirigée par l'utilisateur, par l'intermédiaire d'un workflow qui spécifie les traitements à appliquer, sélectionnés dans une bibliothèque, et les dépendances de données entre traitement. La génération de code est la dernière phase de cette suite de traitement et vise à produire du code optimisé pour l'architecture dans un format compréhensible par l'utilisateur. Cette génération de code implémente un modèle d'exécution dans lequel chaque processeur/coeur exécute plusieurs processus légers synchronisés par un protocole basé sur l'utilisation de sémaphores. Un processus léger exécute l'ordonnancement des acteurs sur le processeur. Pour chaque bus de communication utilisé, un processus léger gère l'ordonnancement des communications. Le processus de calcul et synchronisé aux différents processus de communication par des sémaphores indiquant pour un envoi la disponibilité de la donnée et pour l'envoi, et la disponibilité de la donnée pour le calcul, et pour une réception de données, la disponibilité de la donnée pour le calcul, et la disponibilité de la donnée pour la réception (voir figure 3.2).

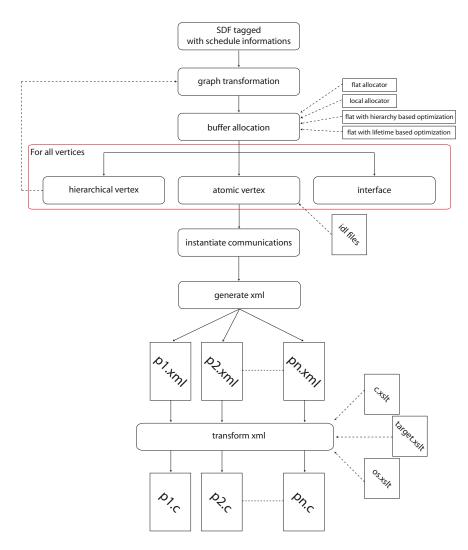

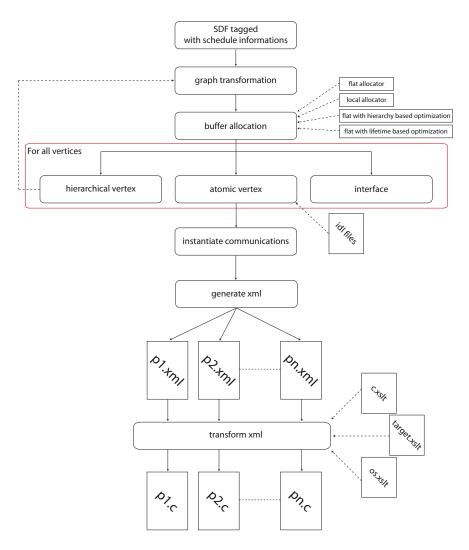

Cette génération se découpe en plusieurs phases :

Ce découpage en phase permet la séparation des problématiques pour traiter chacune d'elles de manière optimale. Pour une meilleure adaptabilité, la phase d'allocation mémoire bénéficie d'une bibliothèque extensible de politiques d'allocation permettant de s'adapter aux contraintes mémoire de l'application et d'évaluer différents algorithmes d'optimisation mémoire.

La génération de code produit un code générique dans une syntaxe xml qu'il est ensuite possible de transformer en une syntaxe spécifique pour cibler l'architecture en utilisant la technologie XSLT (Xml Syntax Language Transformation). Cette transformation utilise trois types de ressources:

- Transformations spécifiques au Système d'exploitation : transformations spécifiques aux appels systèmes et primitives de synchronisation.

- Transformations spécifiques à l'architecture : transformations spécifiques à l'utilisation des ressources matérielles de l'architecture.

- Transformations spécifiques au langage : transformations spécifiques à la syntaxe du langage.

Le code ainsi généré cible un composant de l'architecture et cette génération de code peut facilement être étendue pour supporter d'autres langages, systèmes 20 Contributions

FIGURE 3.2 — Réseau de petri symbolisant la synchronisation des processus de calcul et de communication

d'exploitation, architectures.

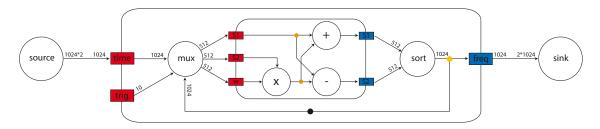

# 3.3 Optimisation des nids de boucles dans le modèle SDF

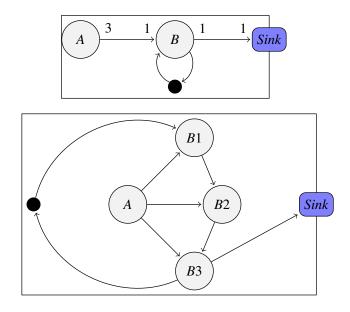

La spécification d'application en utilisant le modèle de hiérarchie basée sur les interfaces décrit précédemment, permet une spécification compacte et factorisée. Cette compacité présente, facilite la saisie par l'utilisateur tout en permettant la même compacité dans la génération de code. Le principal inconvénient de ce modèle réside dans le fait qu'une majorité du parallélisme existant dans l'application reste enfoui dans les niveaux de hiérarchie et ne peut être exploité par l'allocation. Pour pallier à ce défaut, il est possible d'effectuer une mise à plat de la hiérarchie et ainsi remonter le parallélisme enfoui au plus haut niveau, le rendant ainsi exploitable par l'allocation. Cependant, dans le cadre de motifs répétés un grand nombre de fois, cette mise à plat de la hiérarchie, s'accompagne d'une explosion du nombre d'acteur à allouer/ordonnancer. La complexité de l'allocation/ordonnancement dépendant principalement du nombre d'acteur, l'augmentation du nombre de sommet

FIGURE 3.3 – Etapes de la génération de code

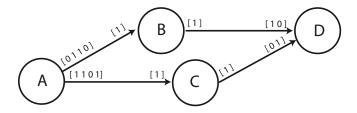

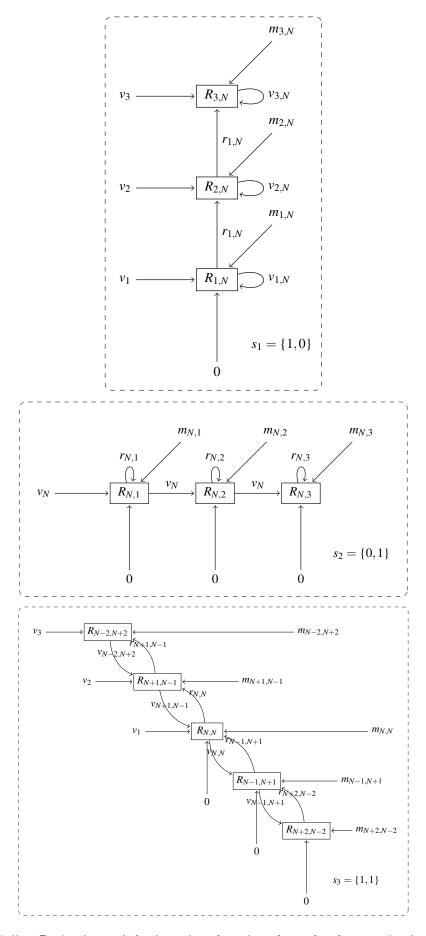

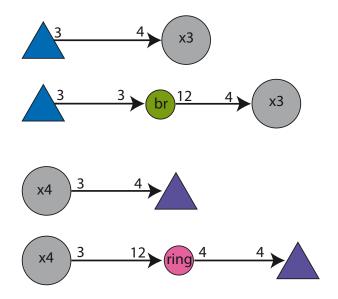

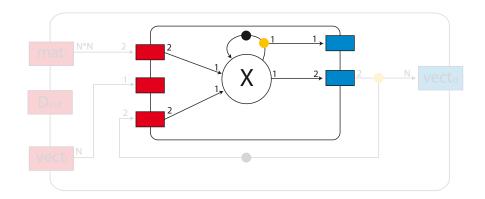

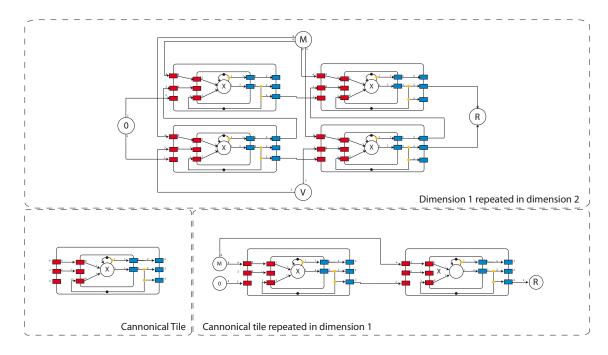

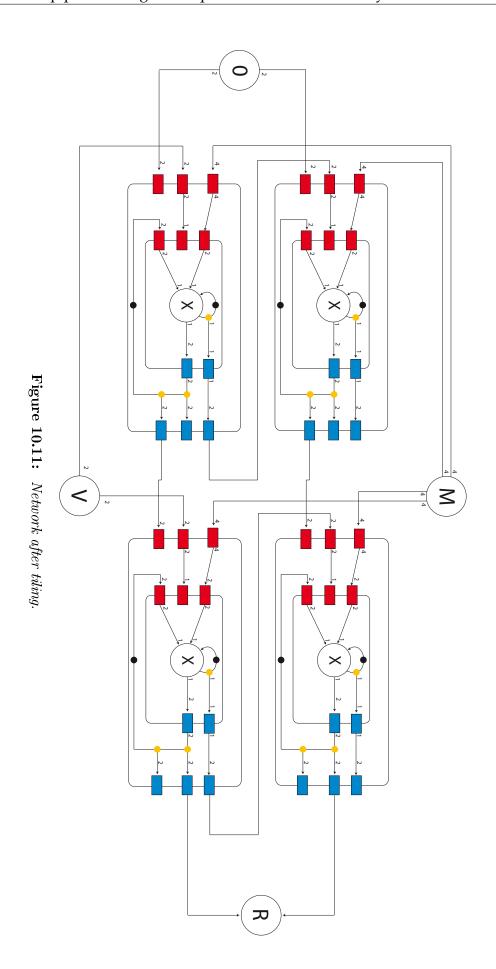

s'accompagne d'une augmentation de la complexité et donc du temps nécessaire à cette étape. Lors de cette thèse, ont été développées des techniques de partitionnement des motifs répétitifs dans le modèle SDF en utilisant l'analogie existante avec la structure des motifs de boucles imbriqués (voir [PBR10]).

Dans un premier temps, il a été nécessaire de déterminer comment extraire les vecteurs de distance d'itération de la représentation hiérarchique. L'extraction de ces vecteurs repose sur l'interprétation des jetons de données initialement présent sur les arcs. Une fois ces vecteurs extraits, les techniques de projection et pavage peuvent être utilisées. Lors de cette thèse, il a également été déterminé comment générer le nouveau réseau d'acteurs à partir des données de pavage ou de projection. Ces deux techniques permettent toutes deux d'extraire du parallélisme de la représentation hiérarchique. Cependant la technique de pavage permet plus de flexibilité. En effet, pour la technique de projection, la taille du réseau d'acteur produit, dépend des

22 Contributions

dimensions du domaine d'itération. Dans le cas de la technique de pavage, la taille du réseau produit, dépend uniquement de la taille de la tuile de pavage choisie.

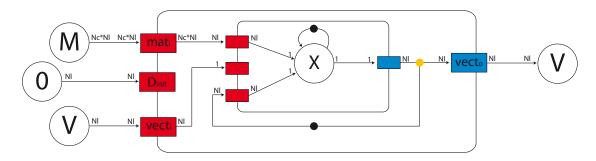

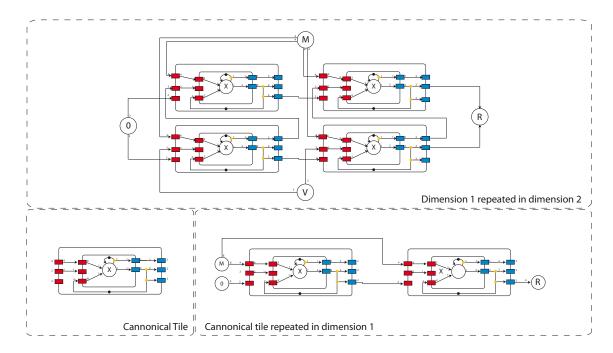

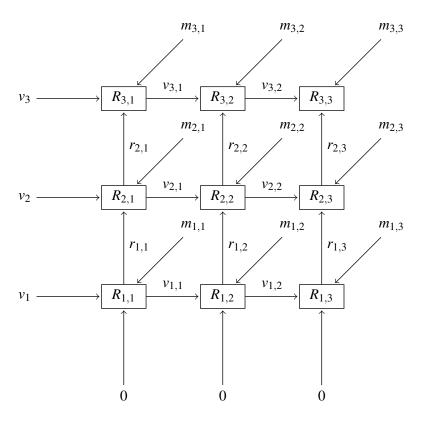

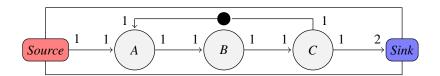

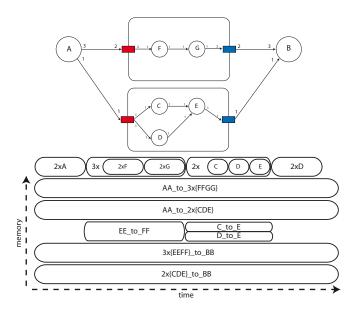

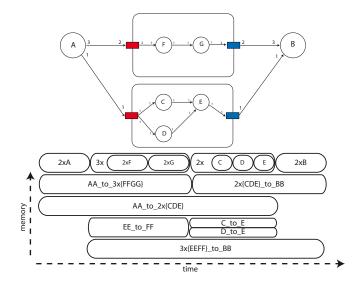

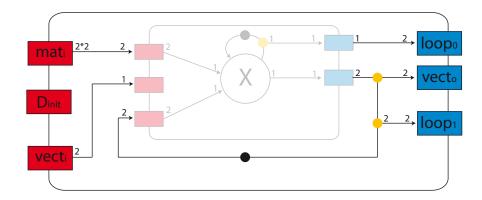

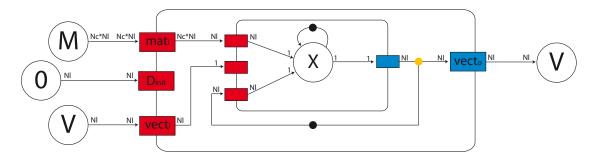

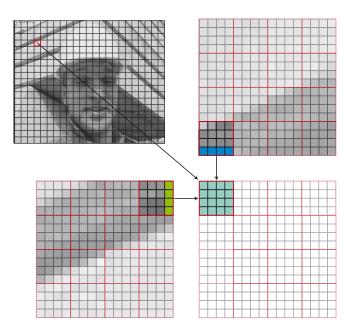

Figure 3.4 – Exemple de produit matrice vecteur en présentation SDF factorisée

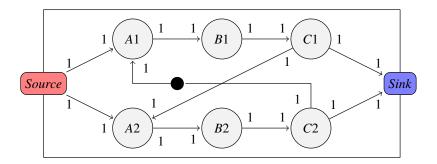

Figure 3.5 - Procédure de pavage du produit matrice vecteur

## Chapitre 4

## Conclusion et propositions de travail

Le travail effectué lors de cette thèse contribue majoritairement au logiciel PREESM. Le modèle de hiérarchie présenté, permet la spécification de motifs factorisés dans une approche descendante. Cette approche autorise le concepteur à décrire le comportement de l'application à gros grain pour ensuite raffiner cette description. Des méthodes de transformation telles que celles présentées permettent d'extraire le parallélisme existant à grain fin. Ces techniques capitalisent sur les méthodes existantes pour les transformations de boucles imbriquées afin de générer une description exprimant du parallélisme de manière optimale. Afin de couvrir l'intégralité de la chaine de prototypage, j'ai aussi développé la génération de code tirant partie du modèle de description hiérarchique pour produire une description factorisée et tirant partie de la hiérarchie pour optimiser l'allocation mémoire.

Les résultats de cette thèse peuvent être appliqués dans d'autres domaines flux de données et notamment au langage CAL. En effet, il serait possible d'extraire des comportements SDF au sein de la description CAL et ensuite leur faire bénéficier des transformations proposées. Le modèle SDF étant purement statique, il pourrait aussi être intéressant d'utiliser le modèle PSDF dans le cadre du prototypage rapide. Ce modèle est en cours d'implémentation dans l'environnement PREESM et pourrait bénéficier des transformations proposées dans cette thèse et également d'une génération de code optimisée.

Une autre perspective serait de supporter des modèles de workflow itératifs dans PREESM et ainsi proposer au concepteur d'automatiser la procédure de prototypage rapide pour générer une implémentation de l'application sur l'architecture donnée qui réponde à des critères quantitatifs donnés.

En définitive le travail développé dans cette thèse s'inscrit dans une construction logique pour l'implémentation d'une chaîne de prototypage rapide. De plus, ce travail est supporté par une implémentation open-source. Ce logiciel est notamment utilisé par l'entreprise Texas Instrument pour le prototypage d'applications multi-coeurs

pour plateformes multi-dsp. Nous espérons, dans l'avenir, attirer d'autres utilisateurs et contributeurs afin d'améliorer cet outil.

# Part II Background

## Chapter 5

## Introduction

#### 5.1 Overview

Since applications such as video coding/decoding or digital communications with advanced features are becoming more complex, the need for computational power is rapidly increasing. Telecom standards such as Long Term Evolution (LTE) bring the computing requirement of the base station at a high level. Applications such as Reconfigurable Video Coding aims at creating a video codec with multi-standard capabilities, thus copping with multiple levels of complexity and time constraints.

In order to satisfy software requirements, the use of parallel architectures is a common answer. Depending on the target application, those parallel architectures can make use of a wide variety of processor cores and communication media. On one hand, in mobile applications, the power requirement being tight, System On Chip (SOC) designers prefer to make use of specialized cores that give the best performance for a reduced set of instructions. On the other hand one might want to use general purpose cores, that handle most of the applications with an average power/performance ratio. Thus some architectures make use of heterogeneous core types to best fit any application requirements. For example mobile applications usually make use of general purpose cores to handle most user interfaces and basic functions, and use DSP core or GPU for signal processing, video decoding or gaming. Communication media are of great importance on multi-core architectures, as most of the parallel performance rely on the ability cores have to exchange data at fast rates. Multiple kind of interconnection topologies exist, each fitting a given purpose at a given cost. The multiplicity of cores and interconnections greatly increases the complexity and time necessary to port an application on a given architecture. Moreover, once porting of the application has been realized, one cannot benefit of it to target a new architecture and has to start from scratch.

To reduce the software development efforts for such architectures, it is neces-

28 Introduction

sary to provide the programmer with efficient tools capable of automatically solving communications and software partitioning/scheduling concerns. The complexity introduced by the wide range of available architectures and the increasing number of cores make the optimal implantation of an application hard to reach by hand. Moreover the stability of the application has to be early proved in the development stage to ensure the reliability of the final product. Tools such as PeaCE [SOIH97], Syn-DEx [GS03] or PREESM [PRP+08] aim at providing solutions to problems described earlier, by assisting the designer through automated steps leading to a reliable final prototype in a short time. This kind of tools is called rapid prototyping frameworks.

Most of these tools use as an entry point a model of the application associated to a model of the architecture. Data flow model is indeed a natural representation for data-oriented applications since it represents data dependencies between the operations allowing to extract parallelism. In this model the application is described as a graph in which nodes represent computations and edges carry the stream of data-tokens between operations. A well known data flow model is the Synchronous Data Flow (SDF) that enables to specify the number of tokens produced/consumed on each outgoing/incoming edges for one firing of a node. Edges can also carry initialization tokens, called delay. That information allows to perform analysis on the graph to determine whether or not there exist a schedule of the graph, and if so to determine an execution order of the nodes and application's memory requirements at compile-time. In basic SDF representation, hierarchy is used either as a way to represent clusters of nodes in the SDF graph or as parameterized sub-systems. One contribution of this thesis is to describe a hierarchy type allowing the designer to describe sub-graph in a classical top down approach. Relevant information can also be extracted from this representation in order to ease the graph scheduling and to lead to a better implementation. The goal of tools such as PREESM is to provide the programmer with a multi-core implementation of the application in a language, a compiler or synthesizer can take. Another contribution of this thesis is to describe the generation of the C code that implements the computed multi-processor schedule in PREESM. The described C code generation method presents a high level of flexibility for the users and generates optimized C code in a comprehensible format.

When dealing with multi-dimensional problems such as image video encoding/decoding, the use of nested loops is a relevant answer to the application modeling. This kind of loop structure is used to hierarchically describe an algorithm, each nested level of hierarchy representing the application in a lower dimension space. For example, an image encoding application can be described at the picture level as a loop over the lines of the image. The line level is itself described as a loop over the blocks of the line, and the block level as a loop over the pixels of the blocks. This

kind of representation can expose little parallelism from the hierarchy point of view, but a lot at the lowest hierarchy. In order to find a trade-off between too much and not enough parallelism extraction from the application description, PREESM integrates an SDF graphs transformation step that aims at extracting a given level of parallelism in concordance with available parallelism on the target architecture. This step also aims at decreasing the scheduling complexity by providing a factorized representation of the application. This step can take advantage of nested loops transformations algorithm inspired by methods such as iteration domain projection and iteration domain tiling to extract a given level of parallelism.

This thesis also led to other contributions in the domain of video coding. The image group inside the IETR lab, is highly involved into still image and video coding/decoding applications. Recently the team got involved into the MPEG-RVC standard, and as a consequence I was involved into related work. The first contribution concerns bit-stream validation for RVC. I was involved into the programming of the validation tool, and I contributed to two publications [LPM09, RPLM08] on the bit-stream validation procedure. I also helped at porting a reconfigurable video decoder on an ARM architecture. This reconfigurable video decoder [GWP+10] makes use of LLVM (Low Level Virtual Machine) to implement a decoder reconfigurable using description of a CAL network. Those other contributions will not be described in depth in this thesis but an overview of their context is given in the following.

### 5.2 Contributions of this Thesis

# 5.2.1 Rapid Prototyping Framework

The recent evolution of digital communication systems (voice, data and video) has been become more and more complex. Over the last two decades, low data-rate systems (such as dial-up modems, first and second generation cellular systems, 802.11 Wireless local area networks) have been replaced or augmented by systems capable of data rates of several Mbps, supporting multimedia applications (such as DSL, cable modems, 802.11b/a/g/n wireless local area networks, 3G, WiMax and ultra-wideband personal area networks).

As communication systems have evolved, the resulting increase in data rates has necessitated a higher system algorithmic complexity. A more complex system requires greater flexibility in order to deal with different protocols in different environments. Additionally, there is an increased need for the system to support multiple interfaces and multi-component devices. Consequently, this requires the optimization of device parameters over varying constraints such as performance, area and power. Achieving this device optimization requires a good understanding of the ap-

30 Introduction

plication complexity and the choice of an appropriate architecture to support this application.

An embedded system commonly contains several processor cores in addition to hardware co-processors. The embedded system designer needs to distribute a set of signal processing functions onto a given hardware with predefined features. The functions are then executed as software code on target architectures; this action will be called a deployment in this paper. A common approach to implement a parallel algorithm is the creation of a program containing several synchronized threads in which execution is driven by the scheduler of an operating system. Such implementation does not meet the hard timing constraints required by real-time applications and the memory consumption constraints required by embedded systems [Lee06]. One-time manual scheduling developed for single-processor applications is also not suitable for multiprocessor architectures: manual data transfers and synchronizations quickly become very complex, leading to a waste of time and potential deadlocks. Furthermore, the task of finding an optimal deployment of an algorithm mapped onto a multi-component architecture is not straightforward. When performed manually, the result is generally a sub-optimal solution. These issues raise the need for new methodologies, which allow the exploration of several solutions, to achieve a more optimal result.

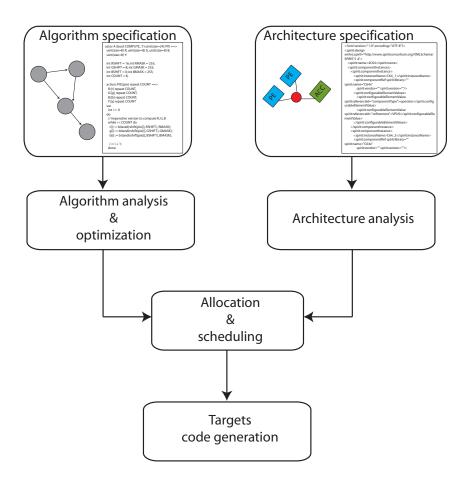

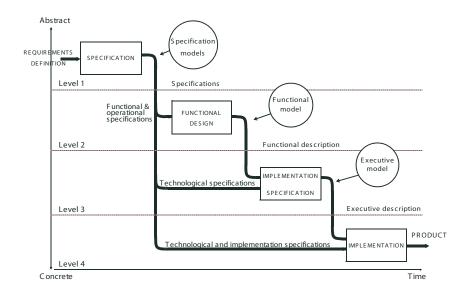

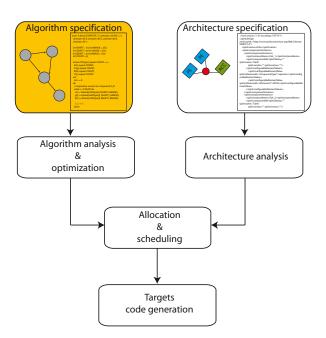

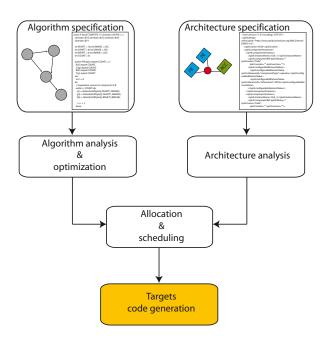

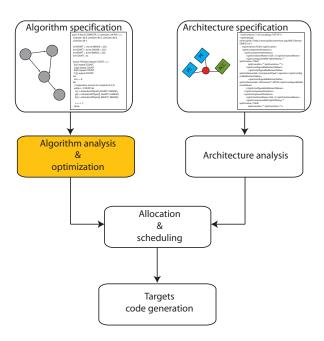

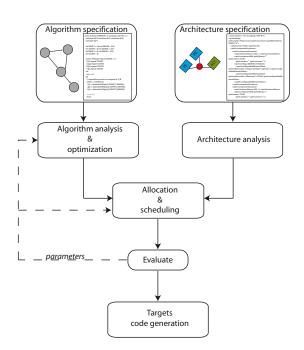

Several features must be provided by a fast prototyping process: description of the system (hardware and software), automatic mapping/scheduling, simulation of the execution and automatic code generation. Based on [PAN08][PBRP09][PMAN09] a more complete rapid prototyping framework was created. This complete framework is composed of three complementary tools based on Eclipse [ecl] that provide a full environment for the rapid prototyping of real-time embedded systems: Parallel and Real-time Embedded Executives Scheduling Method (PREESM), Graphiti and Synchronous Data Flow for Java (SDF4J). This framework implements the methodology Algorithm-Architecture Matching (AAM) [GS03]. The focus of this rapid prototyping activity is currently static code mapping/scheduling but dynamic extensions are planned for future versions of the tool. Such tools rely on a design flow which takes an algorithm transformations, architecture analysis, allocation and scheduling, to finally generate code adapted to the target as depicted in 5.1.

From the graph descriptions of an algorithm and of an architecture, PREESM can find the right deployment, can provide simulation information and can generate a framework code for the processor cores [PAN08]. These rapid prototyping tasks can be combined and parameterized in a workflow. In PREESM, a workflow is defined as an oriented graph representing the list of rapid prototyping tasks to

Figure 5.1: A Rapid Prototyping Frame (RPF) work design flow.

execute on the input algorithm and architecture graphs in order to determine and simulate a given deployment. A rapid prototyping process in PREESM consists of a succession of transformations. These transformations are associated in a data-flow graph representing a workflow that can be edited in a Graphiti generic graph editor. The PREESM input graphs may also be edited using Graphiti. The PREESM algorithm models are handled by the SDF4J library. The framework can be extended by modifying the workflows or by connecting new plug-ins (for compilation, graph analyses, and so on).

There exist numerous solutions to partition algorithms onto multi-core architectures. If the target architecture is homogeneous (all cores of the architectures share the same properties), several solutions exist which generate multi-core code from

32 Introduction

C with additional information (OpenMP [opeb], CILK [BJK+95a]). In the case of heterogeneous architectures, languages such as OpenCL [opea] and the Multicore Association Application Programming Interface (MCAPI [mca]) define ways to express parallel properties of a code. However, they are not currently linked to efficient compilers and runtime environments. Moreover, compilers for such languages would have difficulty in extracting and solving the bottlenecks of the implementation that appear inherently in graph descriptions of the architecture and the algorithm.

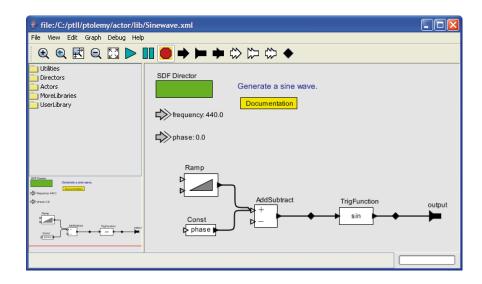

The Poly-Mapper tool from PolyCore Software [pol] offers similar functionalities to PREESM but, in contrast to PREESM, its mapping/scheduling is manual. Ptolemy II [Lee01] is a simulation tool that supports many models of computation. However, it also has no automatic mapping and currently its code generation for embedded systems focuses on single-core targets. Another family of frameworks existing for data flow based programming is based on CAL [EJ03b] language like OpenDF [BBE+08]. OpenDF employs a more dynamic model than PREESM but its related code generation does not currently support efficient automatic mapping on multi-core embedded systems.

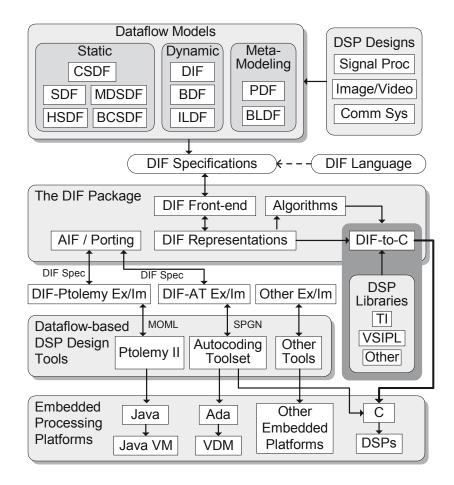

Closer to PREESM are the Model Integrated Computing (MIC [KSLB03]), the Open Tool Integration Environment (OTIE [Bel06]), the Synchronous Distributed Executives (SynDEx [GLS99]), the Dataflow Interchange Format (DIF [HKK+04]), and SDF for Free (SDF3 [SGB06]). Both MIC and OTIE can not be accessed online. According to the literature, MIC focuses on the transformation between algorithm domain-specific models and metamodels, while OTIE defines a single system description that can be used during the whole signal processing design cycle.

DIF is designed as an extensible repository of representation, analysis, transformation and scheduling of data-flow language. DIF is a Java library which allows the user to go from graph specification using the DIF language to C code generation. However, the hierarchical Synchronous Data Flow (SDF) model used in the SDF4J library and PREESM is not available in DIF.

SDF3 is an open source tool implementing some data-flow models and providing analysis, transformation, visualization, and manual scheduling as a C++ library. SDF3 implements the Scenario Aware Data Flow (SADF [TGS+08]), and provides Multiprocessor System-on-Chip (MP-SoC) binding/scheduling algorithm to output MP-SoC configuration files.

SynDEx and PREESM are both based on the AAM methodology [GS03] but the tools do not provide the same features. SynDEx is not open source, has its own model of computation that does not support schedulability analysis and target code generation is possible but not provided with the tool. Moreover, the architecture model of SynDEx is at a too high level to take into account bus contentions and DMA

used in modern chips (multi-core processors of MP-SoC) in the mapping/scheduling.

The features that differentiate PREESM from the related works and similar tools are:

- the tool is an open source and accessible online <sup>1</sup>,

- the algorithm description is based on a single well-known and predictable model of computation,

- the mapping and scheduling are totally automatic,

- the functional code for heterogeneous multi-core embedded systems can be generated automatically,

- the algorithm model provides a helpful hierarchical encapsulation thus simplifying the mapping/scheduling [PBPR09].

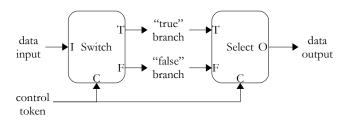

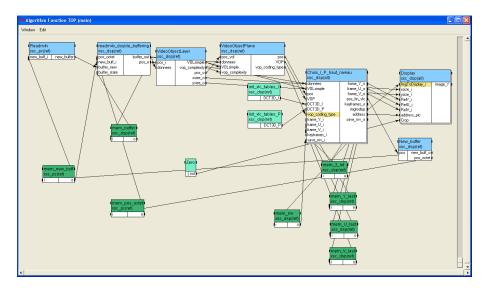

## 5.2.2 Reconfigurable Video Coding

MPEG-1, MPEG-2, MPEG-4...). The specification of the standards usually relies on a monolithic implementation using C/C++ imperative language. This specification lacks flexibility, and does not allow to use the combination of coding algorithms from different standards enabling to achieve specific design or performance trade-offs and thus fill, case by case, the requirements of specific applications.

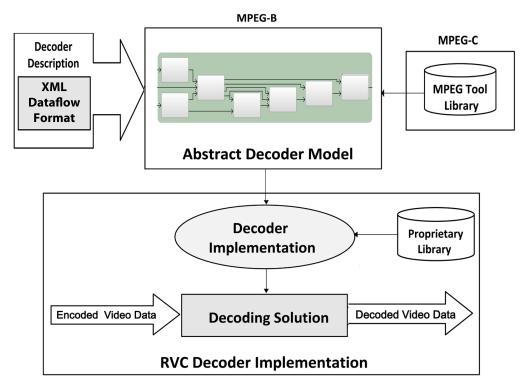

RVC is an MPEG standard that aims at specifying coder/decoder by combining together Functionnal Units (FUs) modeling video coding tools, from the MPEG standard library written in CAL. Those FUs are extracted from existing MPEG standards (MPEG-2, MPEG-4, MPEG-4 AVC, ...). The RVC framework includes:

- The standard Video Tool Library is a repository of video coding tools. Those tools are described using RVC-Cal, that specify the algorithmic behavior and the inputs/outputs of the unit.

- The Functional unit Network Language aims at describing the decoder configuration as a network of FUs from the VTL.

- The MPEG-21 Bitstream Description Language provides an xml syntax that can be used in a schema to describe the bitsream structure that a RVC decoder as to decode. A BSDL schema may be used to generate the parser to be used in the decoder network as a RVC-CAL actor.

The RVC standard relies on the CAL Actor Language for actor specification. This data flow language was developed as a sub-project of the ptolemy project at the university of California at Berkeley. A subset of the CAL language called RVC-CAL was adopted as a specification language for the FUs of the MPEG RVC library. This language allows low level actor behavior specification as CAL actor

<sup>1.</sup> http://preesm.sf.net

34 Introduction

Figure 5.2: The reconfigurable Video Coding Framework.

that is a computational entity with input and output ports, states and parameters. An actor behavior is described through multiple actions that define the computation performed. An action consumes sequences of input tokens, and produces sequences of output tokens. Actor can communicate together by sending and receiving tokens on a CAL actors network.

## 5.2.3 Bit-Stream Description Language

MPEG-B part 5 is an ISO/IEC international standard that specifies BSDL [Int] (Bitstream Syntax Description Language), a language based on XML Schema aiming at describing the structure of a bitstream with an XML document named BS Description. For instance, in the case of a MPEG-4 AVC video codec [iso04], a BS Schema describes the structure common to all possible conformant MPEG-4 AVC video bitstreams, whereas a BS description describes a single MPEG-4 AVC encoded bitstream as an XML document. Figure 5.3 shows the BSDL Schema associated with the BSDL description in Figure 5.4. BSDL uses XML to describe the structure of video coded data. An encoded video bitstream can be described as a sequence of binary symbols of arbitrary length – some symbols contain a single bit, while others contain many bytes. For these binary symbols, the BSDL description indicates values in a human – and machine – readable format for example, using hexadecimal values (as for startCode in Figure 5.3), integers, or strings. It also organizes the

symbols into a hierarchical structure that reflects the data semantic interpretation.

In other words, the BSDL description level of granularity can be fully customized to the application requirements [TKJM<sup>+</sup>07]. BSDL was originally conceived and designed to enable adaptation of scalable multimedia content in a format-independent manner [J. 07]. In the RVC framework, BSDL is used to fully describe the entire bitstream – each elementary bit has its corresponding value in a Variable Length Decoding (VLD) table. As a result, the corresponding BS schema must specify all components of the syntax at a finer granularity level than the ones developed and used for adaptation of scalable content. In this context BSDL does not replace the original data, but instead provides additional information (or metadata) to support an application for parsing and processing the binary content. Finally, BSDL does not mandate the names of the elements in the BSDL Description; the application assigns names that provide meaningful semantics for the description at hand. Figure 5.3 is an example of a BSDL description for video in MPEG-4 AVC format.

In the RVC framework, BSDL is preferred over Flavor [Ele97] because:

- it is stable and already defined by an international standard;