### Enjeux de conception des architectures GPGPU: unités arithmétiques spécialisées et exploitation de la régularité Caroline Collange

#### ▶ To cite this version:

Caroline Collange. Enjeux de conception des architectures GPGPU: unités arithmétiques spécialisées et exploitation de la régularité. Réseaux et télécommunications [cs.NI]. Université de Perpignan, 2010. Français. NNT: tel-00567267

### HAL Id: tel-00567267 https://theses.hal.science/tel-00567267

Submitted on 19 Feb 2011

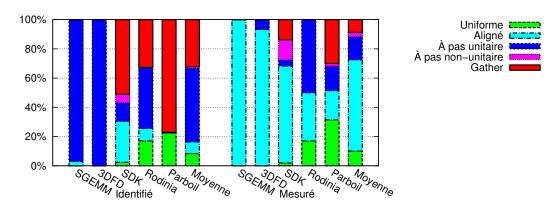

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### Université de Perpignan Via Domitia

Laboratoire ELIAUS : Électronique, Informatique, Automatique et Systèmes

### **THÈSE**

Présentée le 30 novembre 2010 par

Caroline COLLANGE

pour obtenir le grade de :

#### DOCTEUR DE L'UNIVERSITÉ DE PERPIGNAN Spécialité INFORMATIQUE

Au titre de l'école doctorale 305 : E<sup>2</sup>

Enjeux de conception des architectures GPGPU : unités arithmétiques spécialisées et exploitation de la régularité

soutenue devant la commission d'examen formée de

| M.:  | Dominique | LAVENIER    | Président    |

|------|-----------|-------------|--------------|

| MM.: | Daniel    | ETIEMBLE    | Rapporteurs  |

|      | Mateu     | SBERT       |              |

| MM.: | Florent   | DE DINECHIN | Examinateurs |

|      | Ronan     | KERYELL     |              |

|      | Marc      | DAUMAS      | Directeur    |

|      | David     | DEFOUR      | Co-directeur |

GPU shader engines are not your family's vector processor Neither Uncle Seymour (Cray) Nor Uncle Steve (Wallach) Andy Glew [Gle09]

#### Remerciements

Je tiens à remercier l'ensemble de mon jury de thèse pour avoir accepté de venir jusqu'à Perpignan pour m'écouter et me transmettre leurs commentaires. Merci à Dominique Lavenier pour avoir accepté de présider ce jury, et à Daniel Etiemble et Mateu Sbert pour leur relecture attentive du manuscrit. Merci également à Florent de Dinechin et Ronan Keryell pour leurs questions et nombreuses remarques constructives.

Je remercie Marc Daumas pour avoir assumé la tâche délicate et parfois ingrate de diriger cette thèse. Merci à David Defour pour m'avoir accompagné scientifiquement et humainement depuis mon stage de fin de Master. Merci David pour ton soutien sans faille, et pour avoir toléré mon entêtement dans nos discussions scientifiques.

Je remercie également les chercheurs de tous horizons avec qui j'ai eu la chance et le plaisir de travailler. Un grand merci à Mark pour avoir m'avoir accordé une confiance et un soutien sans faille dès mon premier stage à Lehigh, et pour m'avoir fait partager sa passion pour les « règles à calcul électroniques ». Merci également à Arnaud pour son soutien et les discussions enrichissantes que nous avons mené. Merci à Jorge, à Yogi et à Yao pour leurs contributions respectives à ce travail.

Un autre grand merci aux membres de l'équipe DALI – Philippe, Bernard, David D. et David P., Christophe, Matthieu, Guillaume pour leur aide et pour les discussions constructives que j'ai pu mener avec chacun. Merci à mes co-bureaux successifs Nicolas, Pascal, Éric, Arnault, Laurent, puis David et Álvaro à Lyon pour avoir toujours maintenu une ambiance conviviale dans le bureau. Merci aussi à Benaoumeur, Mourad, Ali et Chen pour leurs encouragements.

Je tiens aussi à remercier tous les membres de l'équipe Arénaire qui m'ont accueilli lors de ma rédaction de thèse. Je remercie Florent pour son soutien continu malgré ma trahison (partir à Perpignan), mon prédécesseur Nicolas L. pour m'avoir transmis patiemment sa riche expérience aussi bien à Perpignan qu'à Lyon, Nathalie et Claude-Pierre pour leurs commentaires constructifs avant ma soutenance, Damien, Gilles, Guillaume, Jean-Michel, Nicolas B., Serge, Vincent, Adrien, Álvaro, Andy, Bogdan, Christophe, David, Diep, Erik, Ioana, Ivan, Xavier pour leur soutien.

Merci à tous ceux que j'ai eu l'occasion de croiser durant et/ou avant ma thèse et qui m'ont apporté leurs encouragements, notamment Jérémie, Stef, Pierre, Mehdi, Nicolas Estibals, Nicolas Brunie, Marthe et certainement d'autres que j'oublie.

Je remercie Cyril Z. pour la confiance qu'il m'a accordée en m'invitant en stage à Devtech, et pour m'y avoir abrité des tracas administratifs. Merci à Paulius pour son encadrement et ses conseils, ainsi qu'à l'ensemble de Devtech pour leur accueil. Merci à Norbert pour avoir su répondre à toutes les questions que je me posais et d'autres encore, et à Tim M. pour son soutien. Je remercie également les membres d'ARG et notamment Ronny et James pour leurs commentaires sur mon travail.

Merci également aux membres du forum NVIDIA, et notamment à Greg Diamos pour les discussions enrichissantes. Coin aussi aux X86-Adv et autres canards du forum CPC, à qui je dois les données de la figure 1.7 mais aussi et surtout beaucoup d'inspiration.

Merci aux membres de Vélo en Têt, avec qui j'ai pu pratiquer des activités aussi diverses que la peinture et la mécanique. Merci enfin à mes parents pour leur soutien. J'adresse mes plus plates excuses aux personnes que j'ai oubliées.

| 1 | État | de l'ar  | t du calcul sur GPU                                | 11 |

|---|------|----------|----------------------------------------------------|----|

|   | 1.1  | Enviro   | nnements logiciels                                 | 11 |

|   |      | 1.1.1    | API graphiques                                     | 12 |

|   |      | 1.1.2    | Le modèle de programmation                         | 14 |

|   |      | 1.1.3    | JIT ou micro-architecture?                         | 16 |

|   |      | 1.1.4    | Travaux indépendants                               | 18 |

|   | 1.2  | Archite  | ecture                                             | 18 |

|   |      | 1.2.1    | Architectures considérées                          | 18 |

|   |      | 1.2.2    | Applications cibles                                | 19 |

|   |      | 1.2.3    | Une architecture orientée débit                    | 20 |

|   |      | 1.2.4    | Une perspective historique                         | 21 |

|   |      | 1.2.5    | Le modèle d'exécution : SIMT                       | 22 |

|   |      | 1.2.6    | Mémoires externes                                  | 23 |

|   |      | 1.2.7    | Mémoires internes                                  | 24 |

|   |      | 1.2.8    | Unités spécialisées pour le rendu graphique        | 26 |

|   | 1.3  | Enjeux   | ζ                                                  | 28 |

|   |      | 1.3.1    | Approche statique ou approche dynamique?           | 28 |

|   |      | 1.3.2    | Matériel spécialisé ou implémentation logicielle ? | 32 |

| 2 | Étuc | de de ca | s : l'architecture Tesla                           | 35 |

|   | 2.1  | Jeu d'i  | instructions                                       | 36 |

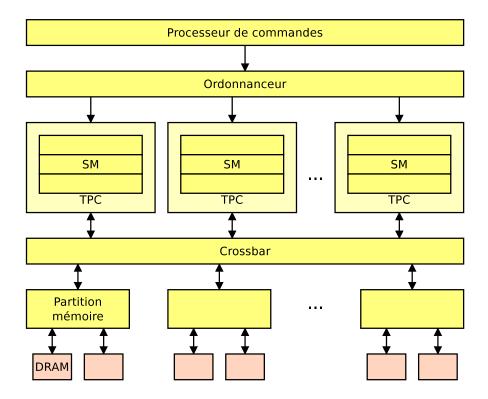

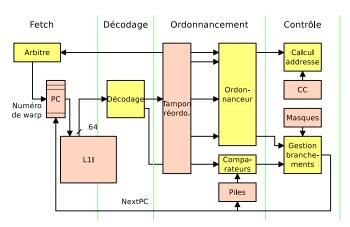

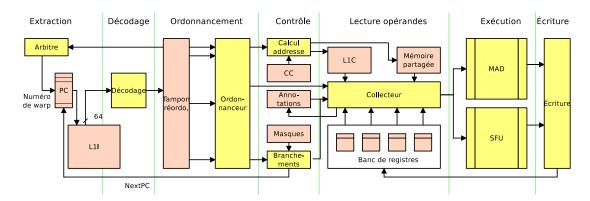

|   | 2.2  | Organi   | isation générale                                   | 38 |

|   | 2.3  | Gestio   | n des tâches                                       | 40 |

|   |      | 2.3.1    | Processeur de commandes                            | 40 |

|   |      | 2.3.2    | Ordonnancement à gros grain                        | 41 |

|   | 2.4  | SM       |                                                    | 42 |

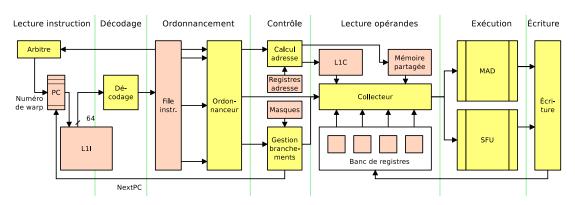

|   |      | 2.4.1    | Lecture des instructions                           | 42 |

|   |      | 2.4.2    | Ordonnancement des warps                           | 43 |

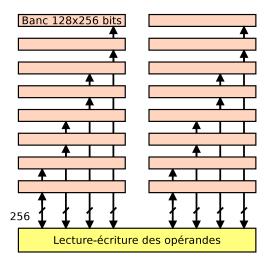

|   |      | 2.4.3    | Banc de registres                                  | 45 |

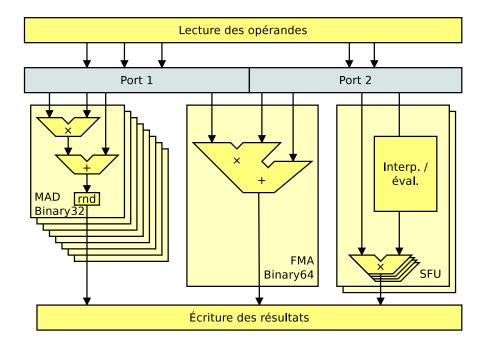

|   |      | 2.4.4    | Unités d'exécution                                 | 47 |

|   | 2.5  | Hiérar   | chies mémoire                                      | 48 |

|   |      | 2.5.1    | Mémoires internes                                  | 49 |

|   |      | 2.5.2    | Mémoires niveau cluster                            | 52 |

|   |      | 2.5.3     | Traduction d'adresse                         |

|---|------|-----------|----------------------------------------------|

|   |      | 2.5.4     | Réseau d'interconnexion et ROP               |

|   |      | 2.5.5     | Contrôleur mémoire                           |

|   | 2.6  | Gestion   | n de l'énergie                               |

|   |      | 2.6.1     | Protocole de test                            |

|   |      | 2.6.2     | Tests applicatifs                            |

|   |      | 2.6.3     | Ordonnancement                               |

|   |      | 2.6.4     | Instructions                                 |

|   |      | 2.6.5     | Mémoire                                      |

|   | 2.7  | Conclu    | sion                                         |

| 3 | Expl | loiter le | s spécificités arithmétiques du GPU 61       |

|   | 3.1  | Introdu   | action à l'arithmétique virgule flottante    |

|   |      | 3.1.1     | Système de représentation                    |

|   |      | 3.1.2     | Unités de calcul                             |

|   |      | 3.1.3     | Modélisation et analyse d'erreurs 65         |

|   | 3.2  | Test de   | es unités de calcul                          |

|   |      | 3.2.1     | Historique                                   |

|   |      | 3.2.2     | Architecture                                 |

|   |      | 3.2.3     | Caractéristiques des unités arithmétiques 67 |

|   |      | 3.2.4     | Évolution des fonctionnalités arithmétiques  |

|   | 3.3  |           | rner les unités graphiques                   |

|   |      | 3.3.1     | Application: transferts radiatifs            |

|   |      | 3.3.2     | Détourner le pipeline graphique              |

|   |      | 3.3.3     | Résultats                                    |

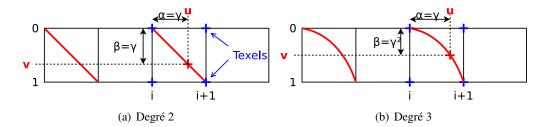

|   | 3.4  |           | tion de fonction par filtrage                |

|   |      | 3.4.1     | Détourner l'unité de textures                |

|   |      | 3.4.2     | Application: système logarithmique           |

|   |      | 3.4.3     | Résultats et validation                      |

|   | 3.5  |           | nétique d'intervalles sur GPU                |

|   |      | 3.5.1     | Arithmétique d'intervalles                   |

|   |      | 3.5.2     | Simuler les modes d'arrondis manquants       |

|   |      | 3.5.3     | Arrondis dirigés corrects                    |

|   |      | 3.5.4     | Résultats                                    |

| 4 |      |           | lateur d'architecture CUDA 99                |

|   | 4.1  |           | teurs d'architectures parallèles             |

|   | 4.2  |           | nnement de simulation                        |

|   |      | 4.2.1     | Pilote                                       |

|   | 4.3  | 4.2.2     | Modules                                      |

|   | 4.3  |           | ation fonctionnelle                          |

|   | 4.4  |           | lisation de la simulation                    |

|   | 4.5  |           | tion et applications                         |

|   | 46   | Liornot   | origotion 10°                                |

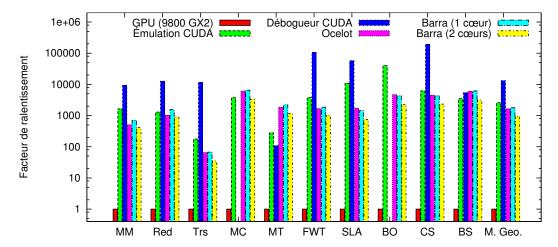

|    |        | 4.6.1   | Vitesse de simulation                               | . 107 |

|----|--------|---------|-----------------------------------------------------|-------|

|    |        | 4.6.2   | Précision                                           | . 109 |

| 5  | Tire   | -       | de la régularité parallèle                          | 113   |

|    | 5.1    | Introdu | uction                                              | . 114 |

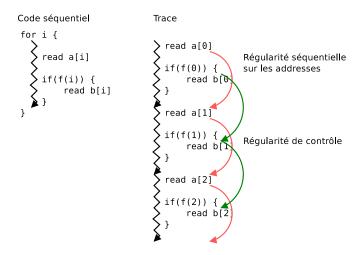

|    |        | 5.1.1   | Régularité séquentielle                             | . 114 |

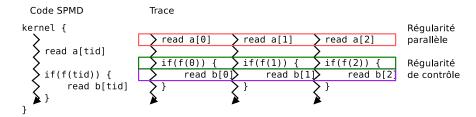

|    |        | 5.1.2   | Régularité parallèle                                | . 115 |

|    |        | 5.1.3   | Sources de régularité                               | . 116 |

|    |        | 5.1.4   | Applications                                        | . 117 |

|    | 5.2    | Régula  | arité séquentielle                                  | . 118 |

|    |        | 5.2.1   | Caches conventionnels sur GPU                       | . 118 |

|    |        | 5.2.2   | Caches de valeurs                                   | . 119 |

|    |        | 5.2.3   | Implications                                        | . 119 |

|    | 5.3    | Régula  | arité de contrôle                                   | . 120 |

|    |        | 5.3.1   | Problématique                                       | . 120 |

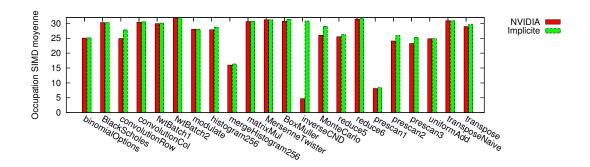

|    |        | 5.3.2   | Reconvergence implicite                             | . 122 |

|    |        | 5.3.3   | Validation                                          | . 123 |

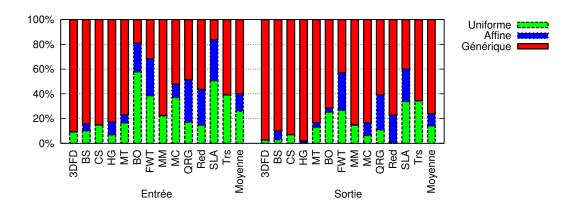

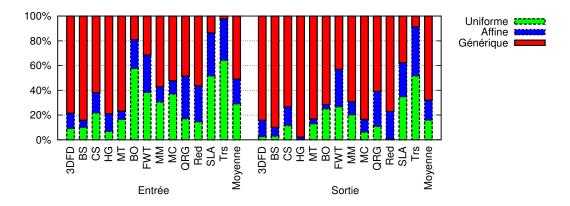

|    | 5.4    | Vecteu  | urs uniformes et affines                            | . 125 |

|    |        | 5.4.1   | Intérêt                                             | . 126 |

|    |        | 5.4.2   | Scalarisation                                       | . 127 |

|    |        | 5.4.3   | Gestion du flot de contrôle                         | . 129 |

|    |        | 5.4.4   | Problèmes et solutions                              | . 130 |

|    |        | 5.4.5   | Résultats                                           | . 132 |

|    | 5.5    | Consé   | quences sur l'architecture et la micro-architecture | . 137 |

|    |        | 5.5.1   | Approche statique                                   | . 137 |

|    |        | 5.5.2   | Approche dynamique                                  | . 137 |

|    |        | 5.5.3   | Conséquences sur les unités de calcul               | . 140 |

|    | 5.6    | Partag  | e de tables pour l'évaluation de fonctions          | . 142 |

| Bi | bliogr | aphie   |                                                     | 161   |

### Introduction

Les microprocesseurs superscalaires se sont progressivements imposés depuis les années 1990 dans la quasi-totalité des segments de marché liés au calcul : ordinateurs personnels, serveurs, supercalculateurs, voire informatique embarquée [HPAD07]. Ils ont été suivis par les processeurs multi-cœurs au cours des années 2000. Leur production de masse permet des économies d'échelle qui rendent leur emploi plus économique que celui d'alternatives spécialisées.

L'évolution des performances de ces architectures se heurte cependant à plusieurs limites. D'une part, les gains permis par le parallélisme d'instructions s'amenuisent à mesure de son exploitation. Le parallélisme de tâches que les multi-cœurs exploitent en complément présente quant-à-lui des difficultés de programmation. D'autre part, le fossé de performance entre les unités de calcul et la mémoire s'accroît de manière continuelle, et devient de plus en plus difficile à combler tout en présentant au logiciel l'illusion d'une unique mémoire cohérente. Enfin, l'énergie consommée et dissipée par les processeurs représente le nouveau facteur limitant la performance, devant la surface de silicium et la vitesse de commutation des transistors [ABC<sup>+</sup>06].

En parallèle au développement des multi-cœurs, on constate l'émergence des processeurs graphiques (GPU) dédiés au rendu d'images de synthèse. Conçus à l'origine comme des accélérateurs spécialisés, ils sont devenus des architectures parallèles à grain fin entièrement programmables. Leur rôle est complémentaire à celui des processeurs généralistes. Alors que les superscalaires multi-cœur sont optimisés pour minimiser la latence de traitement d'un faible nombre de tâches séquentielles, les GPU sont conçus pour maximiser le débit d'exécution d'applications présentant une grande quantité de parallélisme.

Le marché de masse que constitue le jeu vidéo a permis de concevoir et de produire en volume des GPU dont la puissance de calcul est nettement supérieure à celle des processeurs multi-cœurs [MM05].

Cette puissance disponible à faible coût a suscité l'intérêt de la communauté scientifique qui y a vu l'occasion d'exploiter le potentiel des GPU pour d'autres tâches que le rendu graphique. Ainsi, les GPU ont été proposés pour accélérer des applications de calcul scientifique haute performance, telles que des simulations physiques, ou des applications multimédia, telles que du traitement d'image et de vidéo [OLG<sup>+</sup>07, GLGN<sup>+</sup>08].

Les constructeurs de GPU ont vu dans ces travaux académiques une opportunité de s'ouvrir au marché du calcul scientifique, et ont commencé à intégrer des fonctionnalités matérielles non liées au rendu graphique dans leurs processeurs respectifs [LNOM08, NVI09b]. Ce double engouement pour le calcul généraliste sur processeur graphique (GPGPU) soulève plusieurs questions.

Les GPU sont décrits dans la littérature tantôt comme des architectures totalement nouvelles [LNOM08], tantôt comme des architectures parallèles classiques qui n'auraient de nouveau que le vocabulaire qui leur est associé [VD08, Kan08]. Ces deux visions extrêmes ne représentent chacune qu'une part de la réalité. En effet, de nombreux aspects des GPU actuels sont hérités des architectures SIMD [HPAD07]. On peut notamment retrouver des similarités dans la façon dont est conçue l'architecture, dans les langages et environnements de programmation utilisés, ainsi que dans les algorithmes parallèles suivis. En contrepartie, les GPU ont aussi adopté des éléments issus du rendu graphique, voire des idées nouvelles. Quelles sont les connaissances et méthodes issues des processeurs SIMD qui sont également applicables aux GPU, et quelles sont les différences qu'il faut prendre en compte? Nous tenterons de répondre à ces questions en dressant un état de l'art des environnements de programmation et des architectures dédiées au GPGPU au début du chapitre 1.

Les différents constructeurs de GPU ont des points de vue différents sur le niveau d'abstraction à considérer pour les architectures et les langages de programmation. Par exemple, AMD met l'accent sur la simplicité et l'efficacité du matériel en déléguant les tâches d'ordonnancement au compilateur, tandis que les architectures NVIDIA fournissent des mécanismes matériels transparents pour masquer la complexité interne. De même, ces constructeurs proposent des environnements de programmation se plaçant à différents niveaux d'abstraction. Doit-on adopter des mécanismes d'optimisation statiques ou dynamiques ? Nous évaluerons les avantages et les inconvénients de chaque approche dans la suite du premier chapitre.

Les programmeurs ont accès uniquement à une vue partielle des mécanismes mis en œuvre en matériel, ainsi qu'aux interactions entre le programme, le compilateur et l'architecture. Les principaux environnements de programmation pour GPU se comportent comme des boîtes noires, ce qui rend l'optimisation du code délicate. Ainsi, le manque de documentation précise semble être l'un des principaux griefs des programmeurs sur GPU à l'encontre des constructeurs [VD08, WPSAM10]. Nous désirons également comprendre et étudier les enjeux de conception des GPU. Pour répondre à ces deux questions, nous chercherons à déterminer plus précisément le fonctionnement des architectures actuelles au travers de tests synthétiques que nous appliquerons au cours du chapitre 2.

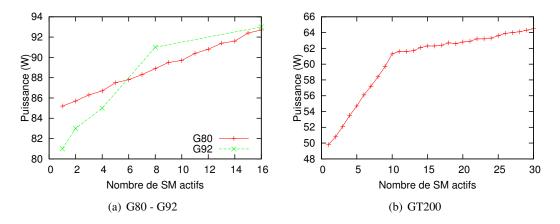

Les architectures parallèles promettent des gains en efficacité énergétique par rapport aux processeurs superscalaires. Ainsi, Nebulae, le deuxième supercalculateur du classement Top500 de juin 2010 construit à base de GPU fournit une puissance de calcul de 1,27 petaflops sous le test Linpack pour une consommation annoncée à 2,5 MW. Par comparaison, son concurrent direct Jaguar à base de processeurs multi-cœurs atteint 1,75 petaflops pour une consommation de 7 MW [Mer10]. Cependant, il est difficile de quantifier précisément l'impact que les décisions de programmation et de conception auront sur la consommation. Nous présenterons des mesures de consommation afin d'orienter ces choix à la fin du chapitre 2.

Les GPU disposent d'unités spécialisées pour effectuer des tâches liées au rendu graphique, telles que les unités de rastérisation, de filtrage de textures ou de fusion de fragments. Celles-ci permettent des gains en performance, mais surtout en consommation. Par exemple, le système sur puce NVIDIA Tegra 2 destiné aux appareils multimédia mobiles emploie des accélérateurs spécialisés distincts pour l'encodage vidéo, le décodage vidéo, le traitement d'images et de son et le rendu graphique, alors que ses processeurs généralistes ARM Cortex-A9 n'incluent délibérément pas d'extensions SIMD virgule-flottante [NVI10c]. La définition même d'une unité

spécialisée semble exclure toute utilisation en dehors de son domaine d'application. Qu'en est-il réellement ? Nous explorerons des possibilités de détourner ces unités pour effectuer des calculs associés à plusieurs applications non-graphiques au cours du chapitre 3.

Les unités de calcul généralistes en virgule flottante des GPU différent également par rapport à celles des CPU, voire entre générations et entre constructeurs de GPU. Nous ferons une étude détaillée du comportement arithmétique d'une génération de GPU au moyen de tests synthétiques, et présenterons un récapitulatif des spécificités des unités arithmétiques de l'ensemble des GPU de ces cinq dernières années.

Cette étude nous révélera que les unités arithmétiques des GPU offrent des fonctionnalités supplémentaires par rapport à leurs équivalents sur les CPU les plus répandus. Nous tirerons parti de certaines de ces possibilités pour construire une bibliothèque d'arithmétique d'intervalles efficace dans la suite du chapitre 3.

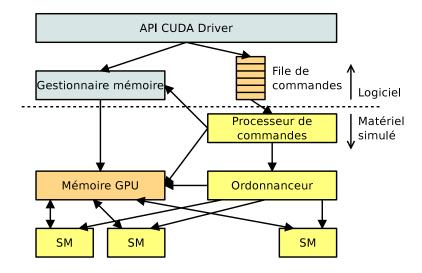

Les GPU représentent une architecture encore en mutation. Leur étude du point de vue de l'architecture des ordinateurs est nécessaire pour effectuer des choix de conception pertinents. Elle requiert un modèle réaliste du matériel permettant l'exploration micro-architecturale. Nous présenterons au chapitre 4 un simulateur de l'architecture NVIDIA Tesla qui est à même de répondre à ce besoin.

Les faibles performances que les GPU obtiennent sur du code parallèle irrégulier constitue le principal reproche que leurs détracteurs leur accordent [Pfi08]. Cette faiblesse des GPU constitue aussi leur force : l'exploitation de régularité présente dans les applications parallèles est une des raisons qui explique l'efficacité des architectures GPU. Faire évoluer les GPU pour les rendre aussi souples que les CPU scalaires ferait perdre une grande partie de leur efficacité sur les applications régulières. L'enjeu consiste plutôt à établir un compromis entre la flexibilité et l'exploitation de la régularité. Au delà des mécanismes d'exécution existants, nous chercherons à explorer certains de ces compromis et nous considérerons davantage de moyens de tirer parti de la régularité dans le chapitre 5.

La régularité de contrôle représente une première manifestation de la régularité. Les systèmes matériels existants nécessitent d'inclure des informations particulières au niveau du jeu d'instructions pour communiquer les points d'indépendance de contrôle. Nous considérerons un mécanisme transparent identifiant la régularité de contrôle de manière dynamique qui permette de s'affranchir de ces informations. Ainsi, l'impact sur le jeu d'instructions et sur le compilateur est éliminé.

La régularité sur les données se manifeste par de de la redondance dans les calculs et en mémoire. Nous déterminerons dans la suite du chapitre 5 des moyens d'éliminer cette redondance en exploitant la régularité. La détection peut être réalisée en matériel à l'exécution ou lors de la compilation. Cette optimisation vise aussi bien une réduction de la consommation qu'une amélioration des performances.

## État de l'art du calcul sur GPU

Le domaine du calcul généraliste sur GPU est actuellement en phase de transition depuis des prototypes de recherche vers une utilisation dans l'industrie. Il reste moins bien maîtrisé que la programmation sur des architectures séquentielles, voire des architectures parallèles plus conventionnelles. Programmer efficacement un GPU réclame une compréhension du fonctionnement des couches logicielles impliquées autant que de celui des architectures matérielles sous-jacentes.

Ainsi, les deux questions qui se posent sont les suivantes.

- Comment exploiter la puissance de calcul des GPU pour accélérer des applications de calcul généraliste?

- Comment concevoir un GPU capable d'exécuter efficacement aussi bien les tâches graphiques que les tâches généralistes ?

Pour répondre à la première question, nous présenterons dans la section 1.1 une étude comparée des outils de programmation existants, en mettant en perspective leur évolution dans le temps.

La seconde question fera l'objet d'une étude des architectures GPU au travers d'exemples actuels dans la section 1.2. Nous en extrairons les principaux enjeux qui sous-tendent la conception d'un GPU.

### 1.1 Environnements logiciels

Le GPU est conçu à l'origine comme un coprocesseur spécialisé dédié à accélérer les calculs intervenant dans le rendu interactif d'images de synthèse. Il prend place au sein d'un système *hôte*, constitué d'un ou plusieurs CPU, d'un espace mémoire partagé et d'autres périphériques.

En tant que périphérique de calcul, le GPU utilise un environnement d'exécution et un pilote de périphérique. Un programme utilisant le GPU sera divisé en deux parties : un programme principal exécuté par le processeur hôte, dont une des tâches consistera à configurer le GPU, et éventuellement un ou plusieurs *noyaux de calcul* exécutés par le GPU.

Les modèles de programmation associés aux noyaux de calcul GPU sont tous dérivés du modèle SPMD (Single Program, Multiple Data). Le code du noyau est exécuté de manière

concurrente par un grand nombre de *threads*, de l'ordre de la dizaine de milliers. Tous les threads exécutent le code du même noyau. Afin de distinguer les threads entre eux, chacun dispose d'un *identifiant* unique. Ainsi, le noyau correspond au corps d'une boucle parallèle, tandis que l'identifiant du thread correspond au compteur de la boucle parallèle.

Les distinctions entre les modèles de programmation résident dans les possibilités offertes concernant la communication et les synchronisations entre threads, leur souplesse et leur granularité. La thèse de Göddeke fournit une vue d'ensemble des environnements GPGPU dans son chapitre 3 [Gö10].

Nous considérerons ici les environnements basés sur les bibliothèques de rendu graphique historiques, puis les environnements dédiés à la programmation généralistes.

#### 1.1.1 API graphiques

La manière traditionnelle de configurer et programmer un GPU consiste passer par l'intermédiaire d'environnements de programmation dédiés au rendu graphique. Les environnements de programmation graphique actuellement utilisés sont Direct3D de Microsoft [Mica] et les implémentations de la norme OpenGL du consortium Khronos [OGL].

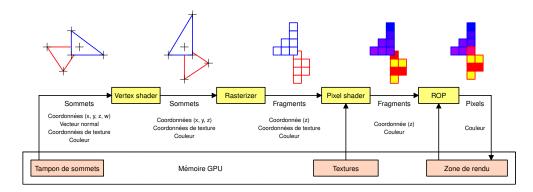

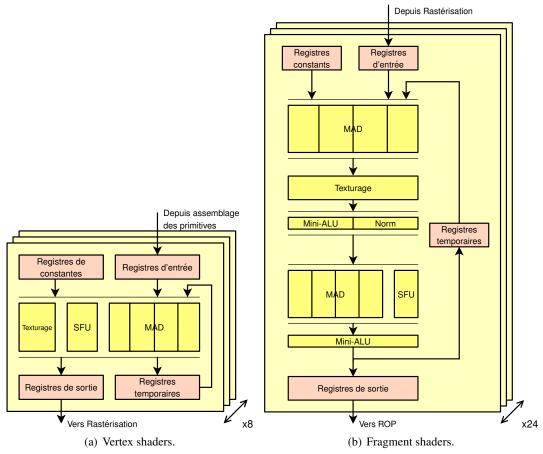

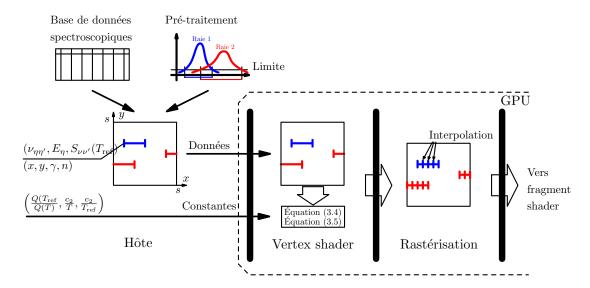

Le pipeline graphique Les algorithmes de rendu graphique direct opèrent selon une succession d'étapes. Nous considérerons ici le pipeline de rendu graphique de l'environnement d'OpenGL 2.0 et Direct3D 9, tel qu'il existait en 2005. Notons que des étapes supplémentaires que nous n'aborderons pas liées à l'instanciation dynamique de primitives et à la tessalation ont été introduites ultérieurement. Les étapes de ce pipeline de rendu sont représentées sur la figure 1.1.

FIGURE 1.1 – Pipeline de rendu graphique Direct3D 9.

Les données en entrée provenant du CPU sont des listes de *sommets* composant des *primitives* géométriques, telles que des triangles ou des lignes. Des *attributs* sont associés à chaque sommet pour représenter ses coordonnées dans l'espace, sa couleur, ses coordonnées de texture ou son vecteur normal.

Un premier programme nommé vertex shader est appliqué de manière indépendante à

chaque sommet. Il se charge de modifier les attributs, typiquement en appliquant des transformations géométriques, afin de calculer les coordonnées du sommet dans l'espace de l'écran.

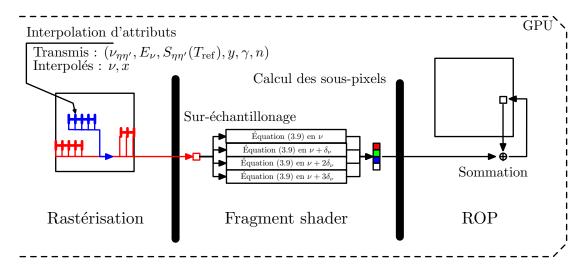

Les primitives sont ensuite assemblées à partir des sommets les composant. L'unité de *rastérisation* détermine les pixels (ou *fragments*) couverts par chaque primitive.

Des attributs de fragments correspondant aux attributs de sortie du vertex shader sont calculés par interpolation entre les valeurs des attributs des sommets de la primitive. Les coordonnées de chaque fragment sont fixées définitivement à cette étape.

La seconde étape programmable, le *fragment shader* ou *pixel shader* consiste à calculer la couleur résultante de chaque fragment.

Ces deux types de shader peuvent lire depuis des images rangées en mémoire, nommées *textures*. Le processus d'accès à la texture est dit *échantillonnage*.

Enfin, le fragment doit rejoindre l'image de destination. Une étape d'arbitrage et de fusion est réalisée par les unités ROP (Raster Operations). Il permet de gérer les situations d'occlusion et de transparence qui se présentent lorsque plusieurs fragments se trouvent aux mêmes coordonnées.

**Détournement des API graphiques** Les deux fonctionnalités qui ont permis la programmation généraliste sur GPU sont d'une part, la possibilité d'effectuer le rendu dans une zone mémoire, puis de réutiliser cette zone comme texture dans une étape ultérieure, et d'autre part, les unités de shaders programmables.

De nombreuses techniques ont été mises au point afin d'exprimer les algorithmes parallèles classiques tels que les réductions, les calculs de préfixes ou les tris de manière graphique. Owens et al. présentent un état de l'art détaillé de ces techniques [OLG<sup>+</sup>07].

Les calculs généralistes sont typiquement effectués dans le fragment shader. Chaque fragment représente alors un thread indépendant. L'identifiant du thread est constitué par ses coordonnées dans la zone de rendu. Le nombre de threads à exécuter est déterminé par les dimensions d'un rectangle à dessiner, qui englobe généralement l'ensemble de la zone de rendu. Les lectures en mémoire sont opérées par des échantillonnages de textures, ce qui permet d'adresser des valeurs arbitraires dans un table. En revanche, les écritures doivent s'opérer uniquement aux coordonnées de destination dans la zone de rendu, c'est-à-dire au pixel correspondant à l'identifiant du thread.

Devoir détourner les modèles de programmation et les environnements dédiés au rendu graphique rend la programmation complexe. Des langages de plus haut niveau ont été développés pour pallier à cette difficulté, notamment le langage du projet Brook [BFH<sup>+</sup>04]. Néanmoins, ces langages ne résolvent pas les problèmes que posent les contraintes logicielles et matérielles sur la souplesse de programmation.

Les contraintes logicielles proviennent du surcoût qu'engendre l'utilisation d'un environnement dédié au rendu graphique pour effectuer les calculs. Au niveau matériel, l'absence de gestion matérielle du *scatter*, c'est-à-dire la possibilité d'écrire à une adresse arbitraire en mémoire est restée un frein au développement du GPGPU.

Afin de contourner la pile logicielle graphique et permettre l'opération scatter, ATI (au-jourd'hui AMD) a développé l'environnement CTM [PSG06]. Il permet l'accès direct au GPU au niveau assembleur. Cependant, la difficulté de programmation due au positionnement bas-

niveau du langage lui a valu un succès mitigé auprès des développeurs. Cette expérience a fait apparaître la nécessité d'offrir une pile logicielle complète.

L'impossibilité d'effectuer des communications locales à grain fin limite également l'efficacité de ces approches. De fait, la génération suivante d'environnements de développement a intégré des langages de plus haut niveau, ainsi que des mémoires locales partagées en matériel.

#### 1.1.2 Le modèle de programmation

L'arrivée de l'environnement de développement CUDA de NVIDIA a marqué un pas significatif dans la démocratisation du GPGPU [NVI10b]. Cet environnement combine un modèle de programmation relativement accessible au travers d'un langage niveau C, et une architecture matérielle permettant les lectures et écritures mémoire arbitraires et offrant un accès à des mémoires locales et des synchronisations entre threads.

L'API CAL d'AMD est basée sur des concepts similaires, et fournit une fondation sur laquelle peuvent s'appuyer des langages de plus haut niveau tels que Brook+, une version reprise par AMD du projet Brook [AMD09a].

Ces API propriétaires ont inspiré des normes permettant la portabilité des applications entre les GPU des différents constructeurs. L'environnement OpenCL du consortium Khronos établit un norme multi-plate-forme principalement inspiré par CUDA [Mun09]. Microsoft inclut également les Compute Shaders dans son environnement de programmation graphique Direct3D à partir de la version 11 [Mica]. Cette interface est quant-à-elle plus proche de CAL.

Tous ces environnements ont pour point commun d'être basés sur un modèle de programmation similaire. Ce modèle tire son inspiration du modèle *bulk-synchronous programming* (BSP), qui considère des sections parallèles où les threads sont indépendants, séparées par des barrières de synchronisation globales [Val90]. Cependant, les synchronisations globales sont trop intrusives pour permettre le passage à l'échelle.

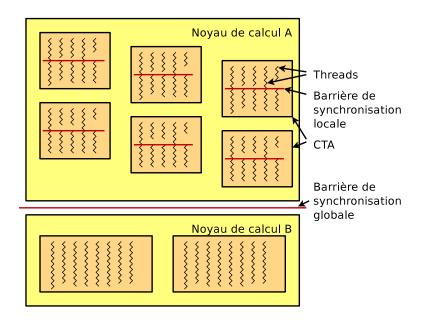

Le modèle de programmation des environnements GPU distingue deux niveaux d'ordonnancement imbriqués, qui fonctionnent chacun suivant le modèle BSP à sa propre échelle (figure 1.2).

Le programmeur découpe le domaine des threads de manière régulière en blocs nommés CTA (Cooperative Thread Arrays). Il peut placer des barrières de synchronisation locales entre tous les threads d'un CTA, et utiliser une mémoire locale à chaque CTA, nommée mémoire partagée. Cette mémoire est allouée de manière statique.

Entre l'exécution de deux noyaux de calcul, il est possible d'opérer une synchronisation globale.

Notons qu'il n'existe pas de consensus sur la terminologie liée à ce modèle. En effet, chaque acteur du calcul sur GPU a adopté son propre vocabulaire. La table 1.1 récapitule les principales différences. Ainsi, des expressions telles que « local memory » peuvent avoir un sens totalement différent suivant le contexte. Nous nous basons dans cette thèse sur une version francisée de la nomenclature NVIDIA.

TABLE 1.1 - Correspondance entre les terminologies des principaux constructeurs

| NVIDIA                            | AMD                          | Intel            | OpenCL             | Ce document       |

|-----------------------------------|------------------------------|------------------|--------------------|-------------------|

| Thread                            | Thread                       | Strand / Channel | Work item          | Thread            |

| Warp                              | Wavefront                    | Thread / Vector  |                    | Warp              |

| CTA/Block                         | Thread group                 | Fiber            | Work group         | CTA               |

| Scalar processor (SP) / CUDA Core | SPU                          | Lane             | Processing Element | SP                |

| Streaming multiprocessor (SM)     | SIMD processor               | Core / EU        | Compute Unit       | SM                |

| Shared memory                     | Local data share (LDS)       |                  | Local memory       | Mémoire partagée  |

| Local memory                      |                              |                  | Private memory     | Mémoire locale    |

| Global memory                     | Local memory / Global buffer |                  | Global memory      | Mémoire globale   |

| Stream                            | Onene                        |                  | Command queue      | File de commandes |

| Kernel                            | Kernel                       |                  | Program            | Noyau de calcul   |

FIGURE 1.2 – Répartition des threads en CTA dans le modèle SIMT.

#### 1.1.3 JIT ou micro-architecture?

Les environnements de développement pour GPU que nous avons abordés sont des systèmes complets. Ils regroupent à la fois un langage, un compilateur, une interface de bibliothèque (API), un pilote et une architecture matérielle. Cela représente une intégration verticale.

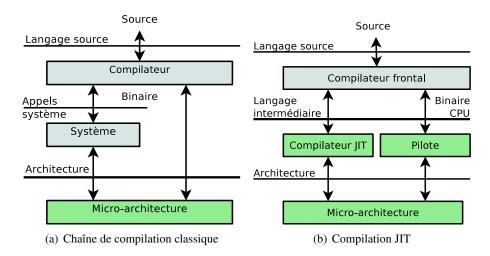

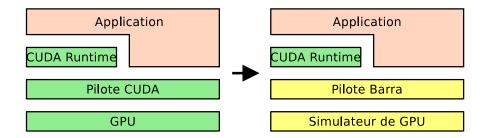

Or, dans une chaîne de compilation traditionnelle, les langages, compilateurs et systèmes d'exploitation forment un écosystème qui n'est pas lié au matériel. Le fabricant de processeurs se doit de définir et documenter précisément *l'architecture*, qui forme l'interface entre le logiciel et le matériel. Ainsi, on effectue la distinction entre l'architecture, qui définit le jeu d'instructions et sa sémantique, et la micro-architecture, qui est l'implémentation d'une architecture donnée. Dans le cadre classique, l'architecture est aussi l'interface entre les applications et le système (figure 1.3(a)).

Dans le cadre des GPU, l'architecture a moins de poids. L'interface entre les applications et le système est constituée par un langage intermédiaire (HLSL assembly pour Direct3D [Micb], NVIDIA PTX pour CUDA [NVI10d], AMD IL pour CAL [AMD09a]), voire un langage de haut-niveau (GLSL pour OpenGL, C pour OpenCL). Le constructeur maîtrisant l'ensemble de la chaîne de compilation, il n'est pas tenu de documenter la façon d'accéder au matériel. AMD et Intel publient des documentations succinctes du jeu d'instructions et des registres de configuration de leurs GPU respectifs [AMD09b, Int09b] et NVIDIA fournit aux développeurs une documentation simplifiée du jeu d'instructions Tesla depuis août 2010. Ces efforts de documentation sont cependant loin d'égaler ceux des jeux d'instructions des CPU [Int10a].

L'organisation des couches logicielles est similaire à celle des environnements fonctionnant à base de compilation à la volée (JIT) tels que Sun/Oracle Java ou Microsoft .Net. En addition, le code s'exécutant sur CPU communique avec le pilote du GPU par une des API graphiques ou

FIGURE 1.3 – Compilation statique et compilation JIT.

GPGPU que nous avons abordées précédemment (figure 1.3(b)). Par exemple, CUDA fournit l'accès aux fonctionnalités de base par l'API *CUDA Driver*, et offre une API de plus haut niveau nommée *CUDA Runtime*. Une telle organisation présente à la fois des opportunités et des difficultés.

**Opportunités** D'une part, cette organisation permet de maintenir la compatibilité ascendante sans conséquence sur le matériel. Les constructeurs ont la possibilité de modifier le jeu d'instructions des GPU d'une génération sur l'autre. La compatibilité avec les applications existantes est conservée, car celles-ci seront recompilées à la volée.

D'autre part, les applications existantes peuvent profiter des améliorations du compilateur à chaque mise à jour des pilotes. Cet aspect est particulièrement manifeste dans le cadre des applications graphiques. Par exemple, chaque mise à jour des pilotes graphiques s'accompagne d'une annonce de gains de performance dans les jeux récents.

Cette approche minimise aussi les conséquences d'éventuels bogues matériels. Par exemple, le bogue de la division du Pentium d'Intel en 1995 a nécessité le retour des processeurs affectés, coûtant au constructeur près de 500 millions de dollars [Coe95]. Du côté des GPU, la documentation du R600 d'AMD mentionne un bogue causant l'exécution incorrecte d'un mode d'adressage indirect [AMD09d]. Ce problème pourtant sérieux a pu être contourné par logiciel et serait passé entièrement inaperçu s'il n'avait pas été documenté.

Enfin, ce modèle permet la génération dynamique de code spécialisé. Cette technique est utilisée par des applications graphiques.

**Difficultés** En retour, le processus de compilation et d'exécution est opaque. L'environnement ne fournit pas de retour précis sur l'efficacité de la compilation et de l'exécution. Il est donc difficile d'effectuer des optimisations fines spécifiques à l'architecture.

La recompilation à la volée fait perdre également en déterminisme. Des régressions accidentelles en termes de performance et de fonctionnalités sont toujours possibles. De plus,

une nouvelle version de l'environnement peut rendre visible des erreurs de programmation qui étaient tolérées auparavant, brisant la compatibilité avec des programmes existants. L'application CUDA Badaboom s'est par exemple révélée incompatible avec les GPU basés sur l'architecture Fermi [Bad10].

#### 1.1.4 Travaux indépendants

La disponibilité d'environnements bas-niveau tels que CUDA a encouragé l'émergence de travaux académiques et industriels se basant sur ces environnements. On trouve notamment des outils de compilation, des langages de plus haut niveau et des environnements d'exécution.

Parmi ceux-ci, Ocelot est un environnement de compilation pour les programmes CUDA qui opère sur une représentation intermédiaire basée sur le langage PTX [DKYC10]. Il inclut un environnement d'exécution reproduisant les fonctionnalités de l'API CUDA Runtime. Les noyaux de calcul peuvent être émulés sur CPU par un interpréteur de la représentation intermédiaire, traduits à la volée vers un code CPU par LLVM [LA04], ou exécutés sur GPU.

Cet environnement offre un ensemble de structures de données permettant la transformation et l'analyse de code, tels que des graphes de flot de contrôle et de données et une allocation de registres virtuels sous forme SSA. Il fournit également des étapes de compilation telles qu'une allocation de registres au niveau PTX, et permet de générer des traces et des statistiques à partir de l'interpréteur.

L'objectif principal du projet est de fournir une machine virtuelle assurant la compilation JIT pour diverses architectures. Alors que l'environnement CUDA n'utilise le JIT que pour assurer la portabilité, Ocelot prévoit d'utiliser les données retournées par l'analyse dynamique de performances pour optimiser la compilation.

#### 1.2 Architecture

Un GPU doit être à même d'exécuter efficacement un champ d'applications plus large que le strict rendu graphique. Ces applications ont pour point commun de permettre l'exploitation de parallélisme de données. Une architecture parallèle optimisée pour le débit permet de les exécuter efficacement.

#### 1.2.1 Architectures considérées

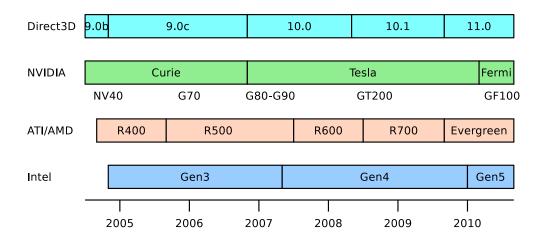

Nous ferons référence dans la suite de cette thèse à un certain nombre de GPU commerciaux. Nous considérerons les gammes des constructeurs NVIDIA, AMD et Intel commercialisés entre 2005 et 2010. La chronologie de ces architectures est représentée sur la figure 1.4. Les nouvelles générations de GPU coïncident généralement avec les révisions de l'API Microsoft Direct3D.

Les noms des produits qui s'appuient sur ces GPU sont les gammes GeForce, Quadro et Tesla <sup>1</sup> de NVIDIA, les gammes Radeon, FireGL et FirePro/FireStream d'AMD et GMA

<sup>1.</sup> Le nom Tesla présenté sur la figure 1.4 correspond au nom de code associé à une architecture, et n'a pas de relation directe avec le nom commercial Tesla désignant la gamme destinée au calcul scientifique du même constructeur. Lorsque nous utiliserons le nom Tesla par la suite, nous ferons référence à l'architecture.

Architecture 19

FIGURE 1.4 – Générations successives des architectures GPU NVIDIA, AMD et Intel considérées ici, mis en relation avec les versions de Microsoft Direct3D.

d'Intel.

Nous classerons également le projet Larrabee d'Intel parmi les GPU [SCS<sup>+</sup>08]. Bien qu'aucune version commerciale ne soit disponible à ce jour et que le projet de coprocesseur graphique Larrabee ait été suspendu au profit de l'architecture parallèle MIC [Int10b], les enjeux de conception de cette architecture sont similaire à ceux des GPU actuels. En effet, nous avons affaire dans les deux cas à une architecture parallèle généraliste initialement optimisée pour le rendu graphique.

#### 1.2.2 Applications cibles

L'application historique des GPU est la synthèse d'images en temps réel pour les jeux vidéo. Le poids de ce marché a permis de justifier l'investissement dans la conception de co-processeurs spécialisés (ASIC) basés sur des technologies de l'état de l'art.

En parallèle de l'augmentation de la puissance de calcul, l'industrie du jeu vidéo tend à réclamer plus de flexibilité. Cela a conduit entre autre à l'adoption des unités de shader programmables. Des programmeurs de jeux réclament encore aujourd'hui une flexibilité accrue, et la possibilité de s'abstraire du modèle de pipeline graphique traditionnel [Swe09]. Ainsi, les fonctionnalités récemment introduites visant la programmation généraliste peuvent également profiter aux moteurs de rendu des jeux vidéo.

Les *shaders* utilisés dans les moteurs de rendu actuels peuvent s'avérer plus complexes en termes de dépendances, d'instructions et de contrôle de flot que des applications GPGPU régulières telles que de l'algèbre linéaire. Ainsi, les modèles d'exécution de Direct3D et OpenGL imposent un ordre de traitement des primitives strictement séquentiel [SWND07]. Par ailleurs, Norman Rubin mettait en évidence en 2008 une évolution exponentielle de la longueur des shaders, et une utilisation accrue de structures de contrôle [Rub08].

La diversification des applications que ciblent les GPU est de fait inévitable. Une architecture GPU est aujourd'hui conçue dès l'origine pour exécuter efficacement un panel d'applica-

tions présentant du parallélisme de données et de la régularité :

- le rendu 3D interactif pour les jeux vidéo,

- le rendu pour applications de conception assistée par ordinateur et de modélisation,

- les applications multimédia (image, son, vidéo),

- les éléments de jeux vidéo non liés au rendu (physique),

- le calcul scientifique.

#### 1.2.3 Une architecture orientée débit

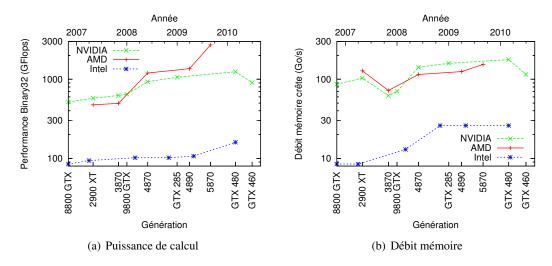

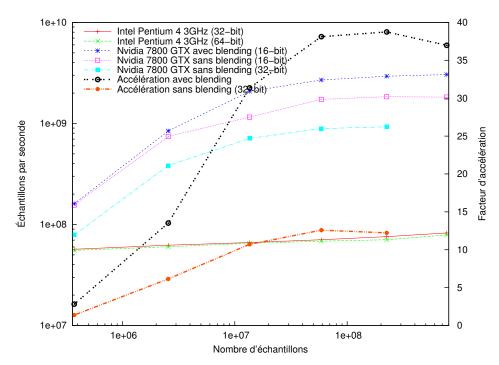

Considérons les puissances de calcul et les débits mémoire crêtes des architectures GPU de ces trois dernières années, comparés aux CPU de même génération sur la figure 1.5. Les processeurs comparés ici sont tous issus du segment haut de gamme du marché grand public.

FIGURE 1.5 – Comparaison des puissances de calcul et débits mémoire crête des GPU NVIDIA et AMD, et des CPU Intel.

La performance crête des GPU reste supérieure d'un facteur 8 à 10 par rapport à celle des CPU. La tendance est à une augmentation de 25 % par an sur les CPU Intel, contre respectivement +35 % et +105 % par an sur les GPU NVIDIA et AMD. Le fossé des performances crêtes tendrait donc à se creuser dans l'immédiat. L'élargissement des unités SIMD et la généralisation de l'opérateur de multiplication-addition fusionnée (FMA) qu'offriront les extensions de jeux d'instructions tels qu'AVX pourraient compenser cette tendance [Int09a].

L'évolution du débit de la mémoire externe est plus modeste. Si l'on ne considère pas l'impact de l'intégration du contrôleur mémoire, il augmente de 20 % par an sur les CPU. Celui des GPU est plus élevé d'un facteur 6 à 7, et évolue dans les mêmes proportions. Cette tendance étant dépendante des contraintes technologiques liées à la DRAM, il est peu probable qu'il y ait d'évolution sur ce point dans un futur proche.

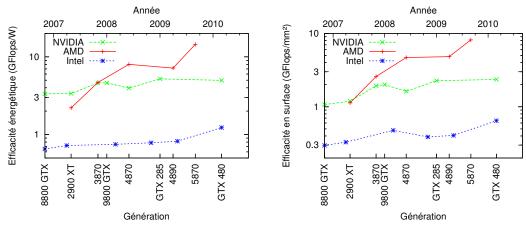

Normalisons maintenant les valeurs de performances crêtes par la consommation et la surface figure 1.6. Les valeurs de consommation sont issues de l'enveloppe thermique (TDP)

Architecture 21

- (a) Puissance crête normalisée par la consommation

- (b) Puissance crête normalisée par la surface

FIGURE 1.6 – Comparaison de l'efficacité théorique en énergie et en surface des GPU NVIDIA et AMD, et des CPU Intel.

fournie par le constructeur <sup>2</sup>. L'écart de performances entre les deux types d'architectures se réduit pour atteindre un facteur de 4 à 9. L'évolution de l'efficacité énergétique des architectures NVIDIA est similaire à celle des multi-cœurs (+15 %/an).

Plusieurs raisons expliquent ces différences de performances crêtes :

- l'exploitation du parallélisme de données par le GPU pour masquer les latences, tandis que le CPU se base sur le parallélisme d'instructions qui est plus coûteux à extraire au-delà d'un certain point [HPAD07],

- l'accent mis sur le calcul virgule flottante sur le GPU, aux dépens des formats entiers et à virgule fixe,

- le profil de réutilisation des données dans les applications sur GPU qui rend envisageable

l'utilisation de caches de faible taille, libérant des ressources pour des unités d'exécution,

- la régularité des applications considérées, qui permet de simplifier les mécanismes de contrôle.

#### 1.2.4 Une perspective historique

La conception du GPU tel qu'on le connaît aujourd'hui a été influencée par des travaux sur les architectures parallèles dans les années 1990. De nombreux aspects associés aux GPU se retrouvent dans cette littérature. Par exemple, l'organisation interne des registres et unités d'exécution de l'architecture NVIDIA Tesla est étonnamment proche de celle du projet Torrent-0 développé à Berkeley à la fin des années 1990 [Asa98].

Les architectures parallèles peuvent être classées grossièrement en plusieurs catégories, comprenant notamment :

<sup>2.</sup> Notons que l'enveloppe thermique des CPU n'inclut pas la consommation de la mémoire, ni celle du contrôleur mémoire sur les processeurs Core 2. En revanche, celle des GPU inclut la consommation sur l'ensemble de la carte graphique. Cette différence à l'avantage des CPU n'affecte pas les tendances globales.

le modèle SIMD, qui consiste à exécuter chaque instruction simultanément sur plusieurs unités de calcul sur des données différentes,

le modèle MIMD, où plusieurs instructions indépendantes sont exécutées sur autant d'unités de calcul [Fly72].

Les architectures de type SIMD opèrent sur des registres vectoriels. Pour permettre un traitement différencié entre les composantes individuelles de ces registres, les jeux d'instructions offrent de la prédication et des opérations *gather* et *scatter* [Asa98]. Ces mécanismes opèrent respectivement sur le contrôle et sur les données.

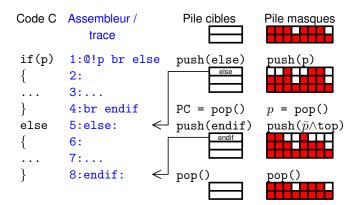

La prédication simule un flot de contrôle différencié sur chaque voie SIMD en permettant de désactiver de manière sélective le calcul sur certaines composantes d'un vecteur. Elle peut être complétée par des mécanismes à base de piles ou de compteurs pour gérer des structures de contrôle imbriquées arbitraires [LP84, Ker92].

L'opération *gather* prend en entrée un vecteur d'adresses mémoire et se charge de récupérer l'ensemble des données pointées par ces adresses pour les placer chacune dans la composante correspondante du registre vectoriel destination. L'opération *scatter* fonctionne de façon analogue sur les écritures mémoire, en répartissant un vecteur de données à des emplacements décrits par un vecteur d'adresses [Asa98].

Néanmoins, les GPU actuels présentent d'autres spécificités que les machines parallèles traditionnelles pour répondre à des contraintes différentes. D'un côté, la densité de logique à surface de silicium constante a été multipliée par 30 en dix ans, permettant l'intégration de supercalculateurs complets sur une puce. En revanche, la latence des accès à la mémoire externe n'a pas connu de tel saut quantitatif [Pat04]. La consommation des circuits devient également le principal facteur limitant, devant la surface de silicium. Ainsi, les architectures parallèles de la génération suivante ont opté pour une organisation hiérarchique et adopté de nombreux mécanismes destinés à optimiser les mouvements de données [KDR+02, KBH+04].

#### 1.2.5 Le modèle d'exécution : SIMT

Le modèle de programmation présenté section 1.1.2 considère des CTA composés chacun d'un nombre de threads de l'ordre de la centaine. Les threads peuvent effectuer des communications et des synchronisations à grain fin à l'intérieur de chaque CTA.

Les CTA étant indépendants entre eux, ils peuvent être ordonnancés librement sur un ensemble de multiprocesseurs, ou SM. Chaque SM se charge d'exécuter les threads d'un ou plusieurs CTA. L'ordonnancement des CTA sur les SM est laissé à la liberté de l'environnement, permettant d'ajuster l'équilibre entre parallélisme et localité en fonction de la cible matérielle. Le modèle de programmation garantit que tous les threads d'un CTA seront en vie simultanément sur un cœur unique.

Chaque SM offre une mémoire partagée à faible latence qui est partitionnée de manière statique entre les CTA en cours d'exécution. Cette mémoire permet les communications entre les threads au sein d'un CTA.

Une solution naïve consisterait à concevoir chaque SM comme un processeur MIMD, composés de cœurs indépendants exécutant chacun un ou plusieurs threads. Cette approche nécessite de répliquer la logique de contrôle : caches d'instructions, mécanismes de lecture et de décodage d'instructions. Or, les applications que nous considérons exhibent de la régularité

Architecture 23

d'instructions : plusieurs threads peuvent être synchronisés de manière à exécuter la même instruction au même moment.

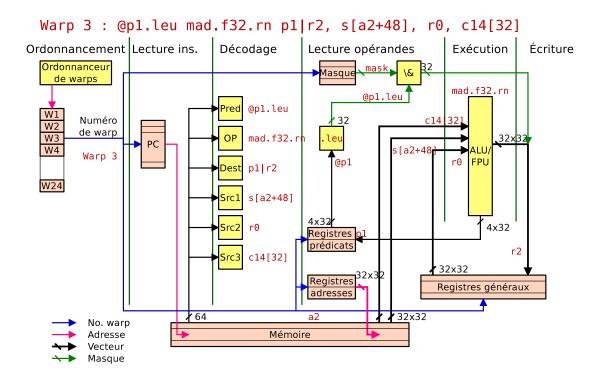

Une telle instruction opérant pour le compte de plusieurs threads peut être traitée comme une instruction SIMD, à la manière des architectures décrites dans la section précédente. Ainsi, le modèle SIMT (single instruction, multiple threads) rassemble les threads d'un CTA en groupes de taille fixe nommés *warps*. Les threads d'un warp restent mutuellement synchronisés, et partagent le même mécanisme de lecture et de décodage d'instructions.

Le modèle SIMT est similaire au MIMD du point de vue du programmeur : des mécanismes d'exécution transparents exécuteront cependant le code sur des unités SIMD. À la différence des architectures SIMD conventionnelles, la vectorisation s'effectue lors de l'exécution plutôt qu'à la compilation.

D'un autre point de vue équivalent, les instructions opèrent toutes sur des vecteurs. Les instructions de lecture/écriture mémoire deviennent alors des instructions gather/scatter. Les instructions de comparaison et de branchement reproduisent de manière transparente une exécution proche d'un modèle MIMD.

Toujours selon ce point de vue, le jeu d'instructions n'offre aucune instruction de calcul scalaire, ni de registre scalaire, ni même d'opération de lecture ou écriture mémoire; il est entièrement vectoriel. C'est paradoxalement cette généralisation vectorielle qui permet à ce type d'architecture d'exposer un modèle de programmation SPMD et d'être qualifiée de *scalaire* par NVIDIA [LNOM08].

Dans ce modèle, les données sont naturellement manipulées sous la forme de structures de tableaux (SoA), par opposition aux architectures SIMD à vecteurs courts capables de traiter des données sous forme de tableaux de structure (AoS). En SIMT, ce sont les opérations gather et scatter qui permettent d'effectuer les conversions entre SoA et AoS.

#### 1.2.6 Mémoires externes

Les applications traditionnelles de rendu graphique opèrent sur des jeux de données plus importants que la quantité de mémoire qu'il est possible d'intégrer sur une puce.

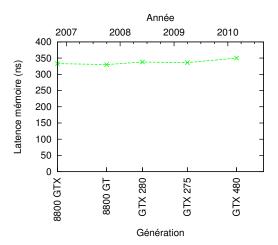

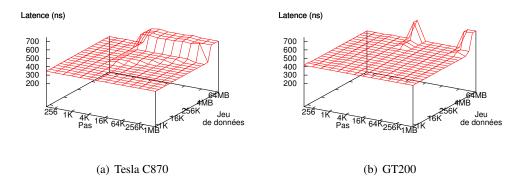

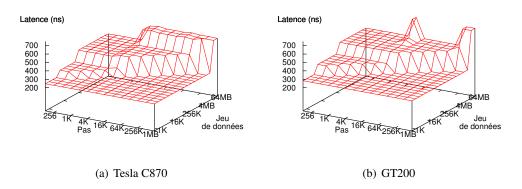

De fait, l'architecture des GPU met l'accent sur la bande passante vers la mémoire graphique. Ces optimisations se font généralement au détriment de la latence. En effet, considérons figure 1.7 les latences mémoires mesurées sur plusieurs générations de GPU NVIDIA. Nous observons que la latence reste stable autour de 340 ns, avec une légère augmentation de 2 % par an. Par comparaison, la latence mémoire d'un CPU avec contrôleur intégré est de l'ordre de 50 ns, soit inférieure d'un facteur 7, et décroît de 6 % par an [Pat04].

Les processeurs graphiques des années 1980 à 1990 utilisaient des technologies de mémoires à double ports (VRAM), puis des mémoires exotiques supportant directement l'accélération des opérations graphiques 2D (SGRAM). Ces solutions sont devenues obsolètes en raison de l'augmentation de la vitesse des SDRAM, des avancées des contrôleurs mémoire, de la régularité moindre des accès et de facteurs économiques. Ainsi, les mémoires actuelles (GDDR5) sont basées sur la même technologie que les mémoires conventionnelles telles que la DDR3, mais bénéficient d'optimisations quantitatives pour améliorer leur vitesse au détriment du coût et des marges d'erreur. Les normes et protocoles employés étant très proches, l'avantage de cette approche est qu'un même contrôleur mémoire peut être aisément conçu pour être

FIGURE 1.7 – Évolution des latences mesurées sur les GPU NVIDIA.

compatible avec les mémoires DDR2 et DDR3 employées sur les cartes graphiques d'entrée de gamme.

Les débits mémoire mis en œuvre sont comparables à ceux des architectures serveur multiprocesseur mais les enjeux sont différents. Dans le cas des GPU, les exigences sur la capacité sont plus réduites, mais les contraintes sur les coûts de production sont plus fortes.

Ainsi, les configurations mémoire choisies visent à maximiser la largeur des bus, tout en minimisant le nombre de puces. La capacité mémoire obtenue est principalement un effet secondaire des exigences en termes de débit. La largeur des bus mémoire de tous les GPU haut de gamme considérés varie entre 256 et 512 bits.

#### 1.2.7 Mémoires internes

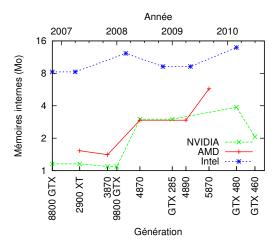

La figure 1.8 représente l'évolution de la taille des mémoires internes des mêmes architectures que précédemment. Les valeurs présentées incluent les bancs de registres et les caches.

Contrairement à une idée reçue, un GPU n'est pas constitué majoritairement d'unités de calcul, mais inclut également des quantités conséquentes de mémoires internes. La taille des bancs de registres et caches est en progression constante, et se rapproche des tailles des caches des CPU.

En effet, nous avons observé au travers des figures 1.5(b) et 1.7 que la bande passante mémoire  $b_m$  des GPU était en augmentation tandis que la latence  $t_m$  restait stable. Or, le volume de données en vol dans le pipeline mémoire  $d_m$  s'exprime par le produit entre la latence et le débit moyens, selon la loi de Little sur les files d'attentes [Lit61]:

$$d_m = b_m t_m. (1.1)$$

Les GPU s'appuient sur le parallélisme de données pour masquer les latences. Le nombre de threads en vol  $n_{\rm threads}$  est proportionnel au nombre de transactions mémoire en vol :

$$n_{\text{threads}} = \frac{d_m}{p \cdot d_{\text{trans}}},\tag{1.2}$$

Architecture 25

FIGURE 1.8 – Évolution de la capacité des mémoires internes des GPU et CPU.

où  $d_{\rm trans}$  est la taille d'une transaction et p le nombre de transactions en vol par thread, obtenues en exploitant le parallélisme d'instructions.

Or, si chaque thread nécessite un contexte d'exécution de taille  $d_c$ , alors la taille totale des mémoires internes sera de :

$$d_{\text{total}} = \frac{d_c b_m t_m}{p \cdot d_{\text{trans}}}.$$

(1.3)

La taille du contexte  $d_c$  est dépendante de la complexité de l'application, du taux de partage entre threads et du ratio entre puissance de calcul et débit mémoire.

Par exemple, considérons les mesures de débit effectuées par Volkov sur GT200 en fixant la taille de transaction  $d_{\rm trans}$  à 8 octets et en faisant varier p et  $n_{\rm threads}$  [Vol10b]. Les résultats obtenus montrent que pour atteindre 85 % du débit crête avec p=1, il est nécessaire de maintenir au moins 9600 threads en vol. Dans ces conditions, chaque thread doit se limiter à un contexte de 250 octets.

L'exploitation du parallélisme de données a donc un impact négatif sur la localité.

Des solutions possibles sont d'extraire davantage de parallélisme d'instructions pour augmenter p, augmenter la granularité des communications  $d_{\rm trans}$ , ou ajuster dynamiquement l'équilibre entre le nombre de threads  $n_{\rm threads}$  et la taille de leur contexte d'exécution  $d_c$ . Nous verrons par la suite que ces trois solutions sont employées par les GPU actuels.

La mémoire interne est majoritairement constituée de bancs de registres. Ces mémoires doivent fournir une bande passante importante, mais tirent avantage de la régularité de l'ordonnancement des threads. Nous étudierons une telle structure plus en détail dans la section 2.4.3.

Pour permettre des communications à faible latence entre threads, les cœurs disposent de mémoires locales contrôlées de manière logicielle.

Enfin, des caches permettent d'assurer les rôles combinés de mémorisation de données locales, de tampon d'envoi et de réception sur la mémoire externe et de tampon de communication entre threads. Ils permettent aussi la mémorisation de tableaux locaux accédés avec indirection ou de taille dynamique telle que la pile d'appel. Leur gestion est assurée de manière

transparente par le matériel, et ils permettent d'unifier et d'équilibrer les ressources mémoire entre chaque type d'usage. Cependant, ils ont un coût en énergie, latence et surface supérieur aux mémoires spécialisées, à bande passante équivalente.

L'architecture Fermi et le projet Larrabee affichent une tendance au déplacement des données locales depuis le banc de registres vers le cache L1.

#### 1.2.8 Unités spécialisées pour le rendu graphique

**Rastérisation** L'étape de *rastérisation* consiste à identifier les fragments recouverts par une primitive. Les environnements graphiques imposent que l'ordre de traitement des primitives soit respecté. En effet, les opérations de fusion des fragments en cas de recouvrement ne sont pas nécessairement associatives, et le résultat dépendra de l'ordre de traitement des primitives.

Cette opération est donc effectuée de manière séquentielle sur la plupart des GPU, une primitive après l'autre. La difficulté de parallélisation a justifié son implémentation en matériel sur tous les GPU commercialisés. Fermi parallélise cette opération en découpant l'espace de la zone de rendu en tuiles [Tri10]. Larrabee est décrit comme suivant une approche hiérarchique en logiciel [Abr09].

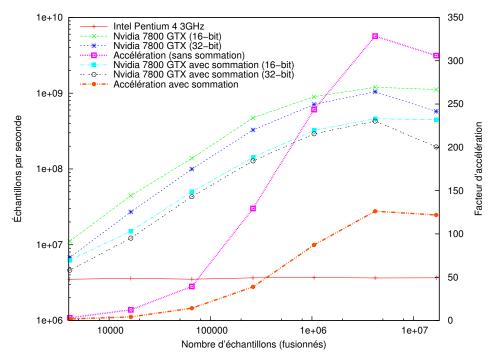

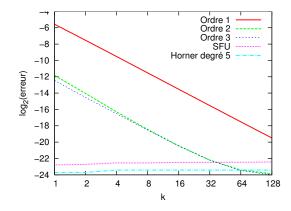

**Filtrage de textures** Le placage de texture consiste à disposer une image, ou *texture* sur la face d'un objet géométrique, en tenant compte de la perspective. On appelle *texels* les éléments de couleur dans le plan de la texture, et pixels ceux du plan de l'écran.

La problématique consiste à calculer la couleur de chaque pixel en fonction du ou des texels le recouvrant. Un filtre est appliqué afin d'éviter les effets de crénelage ou de repliement. Le filtrage est assisté par une unité matérielle sur tous les GPU car jugé trop coûteux à réaliser en logiciel [For09].

Les textures telles qu'elles sont exposées dans les langages graphiques et GPGPU sont paramétrables par plusieurs attributs. Une texture peut être définie comme un tableau uni-, bi-ou tri-dimensionnel, et sera respectivement indexée au moyen d'une, deux ou trois coordonnées de textures. Chaque texel contient un vecteur de 1 à 4 composantes, chacune d'elles pouvant être représentée dans l'un des nombreux formats virgule fixe ou virgule flottante disponibles.

Lorsqu'aucun filtre n'est appliqué, l'unité de filtrage de textures retourne la valeur du texel le plus proche des coordonnées calculées.

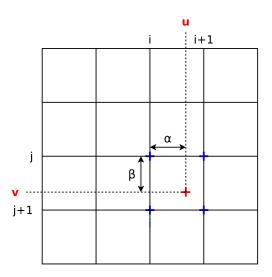

Le mode de filtrage de base disponible en matériel est le filtrage bilinéaire. Il effectue une interpolation entre les quatre texels encadrant les coordonnées, selon le schéma représenté figure 1.9.

Soit T une texture bi-dimensionnelle de  $N \times M$  texels accédée par des coordonnées de textures u et v telles que  $u \in [0,N]$  et  $v \in [0,M]$ . L'unité de filtrage renvoie la valeur V suivante :

$$V = (1 - \alpha) \cdot (1 - \beta) \quad T[i, j] + (1 - \alpha) \cdot \beta \qquad T[i + 1, j] + \alpha \cdot (1 - \beta) \qquad T[i, j + 1] + \alpha \cdot \beta \qquad T[i + 1, j + 1],$$

$$(1.4)$$

Architecture 27

FIGURE 1.9 – Filtrage bilinéaire d'une texture à deux dimensions.

avec  $i, j \in \mathbb{Z}$  et  $\alpha, \beta \in [0, 1[$  calculés tels que  $u = i + \alpha + \frac{1}{2}$  et  $v = j + \beta + \frac{1}{2}$   $^3$ .

De nombreux autres modes de filtrage sont supportés de manière logicielle ou matérielle. Nous nous limiterons ici à l'utilisation du filtrage bilinéaire 2D à coordonnées non normalisées.

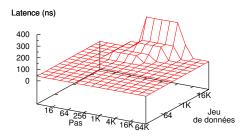

Cache de textures Le rôle d'un cache traditionnel est d'exploiter la localité spatiale et la localité temporelle offertes par un code séquentiel. Il part du principe qu'un thread accédera successivement à des adresses égales ou proches dans un intervalle de temps court.

Dans le cas d'une architecture parallèle à grain fin, la localité se manifeste entre threads adjacents. Par exemple, un *fragment shader* pourra appliquer une texture pour les informations de couleur, une autre pour les informations de relief (*displacement map*), et une troisième pour les informations d'éclairement (*light map*). Chacune de ces textures réside à un emplacement différent dans la mémoire : il n'existe pas de localité entre les accès successifs aux textures. En revanche, les pixels adjacents accéderont à des texels proches dans chacune des textures. Les textures étant généralement bi-dimensionnelles, le mode d'adressage et la structure du cache sont adaptés à la localité spatiale dans un espace 2D.

Dans ce contexte, il peut être avantageux de maintenir une synchronisation artificielle entre les warps pour limiter la compétition sur le cache. Des techniques basées sur l'ajout de barrières de synchronisation ont été développées pour améliorer l'efficacité du cache de textures [MLC<sup>+</sup>08].

La gestion de la cohérence mémoire s'effectue de manière manuelle, par invalidation explicite des caches. Cette approche se justifie par la taille réduite des caches et la faible localité temporelle. Dans la pratique, la mémoire de textures est considérée comme accessible en lec-

<sup>3.</sup> Le décalage d'un demi-texel appliqué aux coordonnées est dû au problème classique des piquets de clôture : les coordonnées de texture u et v peuvent atteindre respectivement les valeurs N et M, alors que le dernier texel est situé en (N-1,M-1).

ture seule pendant tout le temps d'exécution d'un noyau de calcul sur le GPU.

**ROP** L'unité ROP se charge de l'arbitrage entre les fragments situés aux mêmes coordonnées. Le test d'occlusion détermine quel fragment masque l'autre dans le cas de fragments opaques. Le fragment le plus proche est déterminé au moyen d'un tampon de profondeur (*Z-buffer*) contenant la valeur de profondeur de la dernière valeur écrite dans la zone de rendu aux coordonnées considérées.

Elle gère également les effets de transparence, en permettant d'effectuer une interpolation paramétrable entre la couleur en mémoire et la couleur du fragment à fusionner. L'équation d'interpolation est de la forme suivante :

$$x' = \alpha x + \beta y \tag{1.5}$$

où  $\alpha$  et  $\beta$  sont des vecteurs constants, x est la couleur précédemment en mémoire, y la couleur à écrire et x' la nouvelle valeur de couleur.

#### 1.3 Enjeux

Si les générations actuelles de GPU partagent un certain nombre de points communs, tels que ceux que nous avons abordés dans la section précédente, les GPU des différents constructeurs possèdent chacun leurs spécificités propres. Ainsi, il n'existe pas actuellement de consensus sur la direction à privilégier en ce qui concerne l'évolution future de ces architectures.

#### 1.3.1 Approche statique ou approche dynamique?

Dimensions de parallélisme Tout comme les processeurs multi-cœurs, les GPU tirent parti du parallélisme à plusieurs niveaux de granularité. Considérons table 1.2 une comparaison quantitative des mécanismes d'extraction du parallélisme mis en œuvre dans les différents GPU ainsi qu'un CPU. Les types de parallélisme exploités sont le parallélisme de tâches (TLP), le parallélisme de données (DLP, prépondérant dans le cadre des GPU), et le parallélisme d'instructions (ILP). Les architectures GPU considérées sont celles que nous avons abordé section 1.2.1. L'architecture Intel Nehalem est présente dans les CPU Intel Core i7 en 2009.

Du grain le plus gros au grain le plus fin, les mécanismes permettant l'extraction de ces formes de parallélisme sont :

- l'exécution concurrente de tâches sur plusieurs cœurs ou SM dotés de mécanismes d'exécution indépendants (CMP),

- le multithreading à basculement sur événement (SoEMT), consistant à basculer d'un warp à l'autre lorsqu'un événement à latence longue survient,

- le multithreading à grain fin (FGMT), consistant à entrelacer l'exécution de différents warps au sein des unités d'exécution, permettant de masquer les latences courtes,

- l'exécution en pipeline d'une même instruction sur des données différentes,

- l'exécution en parallèle d'une même instruction sur des données différentes (SIMD),

- le démarrage en parallèle de plusieurs instructions indépendantes par cycle (degré superscalaire ou VLIW).

Enjeux 29

TABLE 1.2 – Comparaisons des dimensions de chaque mécanisme parallèle des architectures GPU.

| Architecture | CMP | Multith | reading | Vecteurs i | mplicites | V. explicites | Degré SS |

|--------------|-----|---------|---------|------------|-----------|---------------|----------|

|              |     | SoEMT   | FGMT    | Pipeline   | SIMD      | SIMD          |          |

| Tesla        | 30  | 1       | 32      | 4          | 8         | 1             | 1        |

| Fermi        | 16  | 1       | 48      | 2          | 16        | 1             | 2/3+1    |

| Evergreen    | 20  | 6       | 4       | 4          | 16        | 1             | 5        |

| GenX         | 12  | 1       | 4       | 1 ou 2     | 8 ou 2    | 1 ou 4        | 1        |

| Larrabee     | 24  | 8       | 4       | 1          | 1         | 16            | 1+1      |

| Nehalem      | 4   | 1       | 2       | 1          | 1         | 4             | 3+3      |

| Parallélisme | TLP |         |         | DLP        |           |               | ILP      |

TABLE 1.3 – Classification des mécanismes d'extraction du parallélisme entre statique et dynamique.

| Architecture | Multithreading (TLP) | Vecteurs<br>(DLP) | Superscalaire (ILP) |

|--------------|----------------------|-------------------|---------------------|

| Tesla/Fermi  | Dynamique            | Dynamique         | Mixte               |

| Evergreen    | Mixte                | Dynamique         | Statique            |

| GenX         | Dynamique            | Mixte             | Statique            |

| Larrabee     | Mixte                | Statique          | Mixte               |

| Nehalem      | Dynamique            | Statique          | Dynamique           |

Ces mécanismes peuvent également se partager entre techniques statiques et techniques dynamiques. La table 1.3 présente un tel classement. Ainsi, si l'on retrouve les mêmes niveaux de granularité de parallélisme dans toutes les architectures, les approches suivies pour extraire le parallélisme varient entre méthodes statiques et méthodes dynamiques. Considérons maintenant tour à tour chacune des trois granularités de parallélisme.

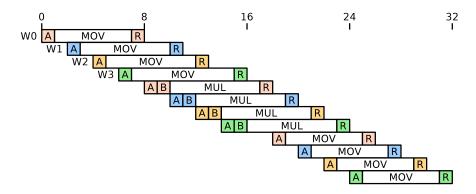

**Ordonnancement des warps** Maintenir plusieurs warps en parallèle par SM en les faisant partager les mêmes unités de calcul permet de masquer les latences sans pour autant affecter le débit d'exécution crête. Ces latences sont de deux types : des latences courtes et prévisibles pour les instructions de calcul, et des latences longues et non-déterministes pour les lectures en mémoire.

Une technique consiste à mettre en œuvre des mécanismes distincts pour masquer les latences longues et les latences courtes. Ainsi, les architectures d'AMD et Larrabee se basent sur du multithreading à basculement sur événement pour masquer les latences mémoire. Ce choix vise à effectuer un compromis dynamique entre parallélisme et localité.

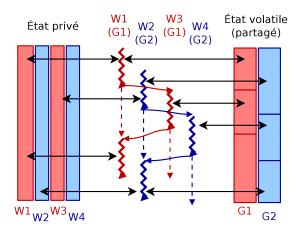

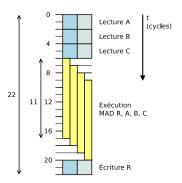

En effet, il est possible de partager des ressources entre les warps inactifs. Considérons un exemple sur la figure 1.10. Quatre warps W1 à W4 sont répartis en deux groupes G1 et G2. Les warps de deux groupes différents peuvent être exécutés simultanément par du multithreading à

grain fin. Le basculement entre deux warps d'un même groupe intervient lors des opérations à latence longue. Comme ces basculements de contextes sont uniquement permis en des points connus du compilateur, il est possible de scinder le contexte associé aux warps (registres) entre une partie privée et une partie partagée. La partie privée survit aux basculements de contexte, tandis que la partie partagée est écrasée par les données du ou des autres warps du groupe.

FIGURE 1.10 – Exemple d'ordonnancement à deux niveaux.

Ce type de multithreading à basculement sur événement nécessite l'intervention du compilateur sur toutes les architectures considérées. Il peut éventuellement être réalisé de manière logicielle comme sur Larrabee. Les décisions se rapportant à la sauvegarde du contexte d'exécution lors des basculements de contexte incombent au compilateur et sont établies de manière statique.

À l'inverse, le multithreading à grain fin est géré entièrement en matériel, de manière dynamique. Notons que les architectures NVIDIA se reposent uniquement sur ce multithreading dynamique, tandis que les autres architectures GPU suivent une approche mixte.

**Extraction de vecteurs** Nous effectuons une distinction dans la table 1.2 entre les mécanismes basés sur des vecteurs implicites de type SIMT et les vecteurs explicites visibles au niveau architectural. Les vecteurs implicites sont contrôlés par le matériel de manière dynamique, tandis que l'exploitation des vecteurs explicites nécessite un travail de vectorisation préalable de la part du compilateur voire du programmeur. Les GPU basés sur le SIMT suivent l'approche dynamique, tandis que les CPU et Larrabee dépendent d'une vectorisation statique.

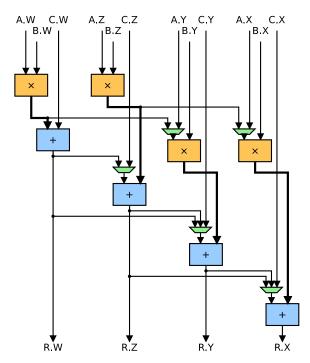

**Parallélisme d'instructions** Les GPU exploitent également du parallélisme d'instructions. Les architectures NVIDIA et Intel Larrabee sont de type superscalaire dans l'ordre, tandis que l'architecture AMD est un processeur de type VLIW. Dans ce dernier cas, l'effort de conception est déporté sur le compilateur [Leu02].

Une technique appliquée par tous les GPU pour recouvrir les latences mémoire est de rendre les lectures de textures asynchrones par rapport aux calculs, en permettant à un warp

Enjeux 31

de continuer à exécuter des calcul non-dépendants d'une lecture mémoire en cours. Ce recouvrement peut être explicite dans le jeu d'instruction comme dans le cas des architectures AMD [AMD09b], ou être géré dynamiquement par un *scoreboard* à l'instar des architectures NVIDIA [CMOS08].

De manière plus originale, le jeu d'instructions d'Evergreen présente des aspects se rapprochant d'architectures *transport triggered* [Cor97]. Contrairement à un VLIW traditionnel où chaque instruction d'un groupe gouverne une unité indépendante, les unités de calcul d'Evergreen sont disposées en cascade (figure 1.11). Les connexions entre ces unités sont paramétrables par des champs dans le mot d'instruction [AMD09b]. Les chemins de données représentés en gras sur la figure 1.11 sont les résultats exacts des multiplications flottantes. Des unités de calcul de minimum/maximum, négation et valeur absolue (non présentes sur le schéma) peuvent également être utilisées. Ainsi, des opérations arithmétiques relativement complexes peuvent être décrites au moyen d'une unique instruction.

De tels mécanismes d'extraction de l'ILP sont rendus possibles par la tolérance à la latence des instructions et à la localité dans le cache d'instructions qu'apporte le modèle SIMT.

FIGURE 1.11 – Organisation générale de l'unité virgule flottante VLIW de l'architecture Evergreen.

Enfin, notons que les frontières entre les trois formes de mécanismes d'extraction du parallélisme que nous avons présentées peuvent devenir floues. Ainsi, la notion de warp pourrait être amenée à s'effacer pour laisser place à des techniques plus flexibles pour grouper des instructions depuis différents threads, à mi-chemin entre le multithreading traditionnel et le SIMT [Fun08, Gle09].

#### 1.3.2 Matériel spécialisé ou implémentation logicielle?

Les spécificités des GPU actuels sont-elles amenées à se résorber, où bien seront-elles intégrées à des processeurs généralistes? La tendance ayant accompagné l'évolution des GPU jusqu'à aujourd'hui est de remplacer des unités spécialisées en unités programmables. Cette tendance à la généricité s'illustre par l'apparition des vertex shaders et des fragment shaders puis leur unification, ainsi que les autres types de shaders introduits par Direct3D 10 et 11.

De même, des unités spécialisées sont délaissées au profit d'unités génériques pour permettre la consolidation des ressources de calcul, même lorsque cela n'est pas requis par l'API graphique. Par exemple, l'architecture Evergreen effectue les interpolations d'attributs en utilisant les unités de calcul généralistes [AMD09b], contrairement aux générations antérieures qui disposaient d'unités dédiées [AMD09c].

Le projet Larrabee met également l'accent sur cette approche de généralisation, en proposant de réaliser la plupart des étages du pipeline de rendu graphique de manière logicielle, y compris la rastérisation [SCS<sup>+</sup>08]. Seul le filtrage de textures bénéficie d'une unité matérielle spécialisée.

Les avantages de cette approche sont une souplesse de programmation accrue et la possibilité d'un équilibrage de charge dynamique adapté à chaque application. Cependant, le rendement énergétique d'une unité dédiée reste bien meilleur que celui d'une implémentation logicielle.

La tendance pourrait donc s'inverser, alors que la consommation énergétique devient un enjeu plus important que la surface de silicium. Notons que l'ensemble des GPU actuels intègrent des processeurs spécialisés pour le décodage vidéo. Les GPU destinés au marché embarqué disposent également d'architectures spécialisés avec notamment des vertex shaders et fragment shaders séparés [NVI10c].

#### Conclusion