### UNIVERSITÉ DE GRENOBLE

### **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Micro et Nano Electronique

Arrêté ministériel : 7 août 2006

Présentée par

### Hatem Mohamed Zakaria Radwan

Thèse dirigée par Laurent Fesquet et codirigée par Marc Renaudin

préparée au sein du Laboratoire TIMA dans l'École Doctorale « Electronique, Electrotechnique, Automatique et Traitement du Signal »

Architecture Asynchrone pour L'Efficacité Energétique et L'Amélioration du Rendement en Fabrication dans les Technologies Décananométriques: Application à un Système sur Puce Multi-Cœurs

Thèse soutenue publiquement le « 24 Février 2011 », devant le jury composé de :

### M. Michel ROBERT

Professeur des Universités, LIRMM, Président

### M. Olivier SENTIEYS

Professeur des Universités, ENSSAT, Rapporteur

### M. Habib MEHREZ

Professeur des Universités, Laboratoire LIP6, Rapporteur

### M. Laurent Fesquet

Maitre de Conférences, TIMA, Directeur de thèse

### M. Marc Renaudin

Directeur Technique, TIEMPO, Co-encadrant

### M. Carlos Canudas-de-Wit

Directeur de Recherche, GIPSA-Lab, CNRS, Membre

### M. Mario Diaz Nava

Directeur Technique, STMicroelectronics, Invité

# Asynchronous Architecture for Power Efficiency and Yield Enhancement in the Decananometric Technologies: Application to a Multi-Core System-on-Chip

By

Hatem Zakaria

**France**, 2011

To ...

My dear Wife and lovely child, Ali

My Parents, Sisters and Brother

My lovely country Egypt

# ACKNOWLEDGMENT

This thesis arose in part out of years of research that has been done within the Concurrent Integrated Systems group (CIS) of the TIMA laboratory in Grenoble. By that time, I have worked with a great number of people whose contribution in assorted ways to the research and the making of the thesis deserved special mention. It is a pleasure to convey my gratitude to them all in my humble acknowledgment.

In the first place I would like to record my gratitude to Dr. Laurent Fesquet for his supervision, advice, and guidance from the very early stage of this research as well as giving me extraordinary experiences throughout the work. Above all and the most needed, he provided me unflinching encouragement and support in various ways. His truly scientist intuition has exceptionally enriched my growth as a scientist want to be.

I greatly indebted to my co-supervisor Dr. Marc Renaudin for all his precious support, consistent encouragement and valuable guidance thought the start of my thesis. I owe an enormous debt of gratitude to him, for the confidence that he accorded to me by accepting to participate in the supervision of my thesis.

I am grateful to the thesis jury members for their precious time which they have scarified for me. Thanks to Prof. Michel Robert, for the interest he gave to this work by agreeing to be the president of my thesis jury. I am also thankful to the thesis reviewers, Prof. Olivier Sentieys and Prof. Habib Mehrez, the interest they have shown towards my work has brought an outside perspective on enriching the subject. Their constructive suggestions on the thesis are really appreciated for me. I am grateful that in the midst of their activities, they accepted these tasks. My thanks also go to Dr. Carlos Canudas-de-Wit and Dr. Mario Diaz Nava, for their commitment to take part in my jury committee.

My deep regards for Dr. Gilles Sicard, for his precious friendly attitude and his immediate help for many administrative issues. I am also grateful to Mr. Alexandre Chagoya, the responsible of service design and test at CIME Nanotech. He always provided me with the needed help and software tools for my work. I also thank all the

administrative staff of the TIMA laboratory and the EEATS, who have always been gentle with me and helped me to get things done very smoothly.

Collective and individual acknowledgments are also owed to my colleagues in CIS group whose present somehow perpetually refreshed, helpful, and memorable. Many thanks go in particular to Eslam and Oussama for their friendship, brotherhood and continual support in work and life. Thanks to Taha, Hakim, Franck and Gregory for the great discussions and open minded attitude. I cannot finish without thanking also Khaled, Saeed, Jeremie, Florant, Alexandre, Hawraa, Olivier, Mathieu, David and Rodrigo. Special thanks also go to all my colleagues in the ARAVIS Minalogic project, those from INRIA, CEA-Leti and STMicroelectronics for their appreciated discussions and valuable remarks all over my PhD work.

My warm special thanks to my family, for their consideration of my research abroad. Without their encouragement, inseparable support and prayers it would have been impossible for me to finish this work. My Father, in the first place is the person who put the fundament my learning character, showing me the joy of intellectual pursuit ever since I was a child. My Mother is the one who sincerely raised me with her caring and gently love. My sisters and brother, who inspired my life with the real meaning of the family. My dearest and lovely kid, Ali who is the real source of happiness in my life, he actually suffered a lot because of my busyness.

Words fail me to express my appreciation to my wonderful and beautiful wife, whose prayers, dedication, love, continual support and persistent confidence in me, has taken the load off my shoulder. I owe her for being unselfishly let her intelligence, passions, and ambitions collide with mine.

All gratitude to my dearest teachers and professors those did great efforts to drive me up to the scientific level which I have now. Special thanks for Dr. Abdel Aziz El-Bassiouni who always keep encouraging and supporting me to do the best.

**Hatem ZAKARIA**

Grenoble, France February 2011

# **Abstract**

Continuous scaling of CMOS technology push circuit designs towards multi-core complex SoCs. Unfortunately with the nanometric technologies, the integrated system performances after fabrication will not be fully predictable. Indeed, the process variations really become huge at the chip scale. Therefore the design of such complex SoCs in the nanoscale technologies is now constrained by many parameters such as the energy consumption and the robustness to process variability. This implies the need of efficient algorithms and built-in circuitry able to adapt the system behavior to the workload variations and, at the same time, to cope with the parameter variations which cannot be predicted or accurately modeled at design time. In this context, this thesis work addresses the design of Globally Asynchronous Locally Synchronous "GALS" based Network-on-Chip "NoC" architectures in the upcoming CMOS technologies. A novel methodology to dynamically control the speed of different voltage-frequency NoC islands according to the process variability impact on each domain is proposed. This control technique can improve the performances, the energy consumption, and the yield of future SoC architectures in a synergistic manner. The control methodology is based on the design of an asynchronous programmable self-timed ring where the controller takes into account the dynamic workload and the process variability effects. The controller especially considers the operating frequency limit which does not exceed the maximum locally allowed value for a given clock domain. With such an approach, it is no more required to separately guaranty the timing performances for each node at design time. This drastically relaxes the fabrication constraints and helps the yield enhancement.

# **Table of Contents**

| List of F | igur | res                                                 | ΧÌ |

|-----------|------|-----------------------------------------------------|----|

| List of T | able | es                                                  | XV |

| Chapter   | 1.   | Introduction                                        | 1  |

| 1.1       | Co   | ntext and Motivations                               | 1  |

| 1.2       | The  | esis Outline                                        | 3  |

| Part-I    |      | GALS Paradigm                                       | 5  |

| Chapter   | 2.   | <b>Asynchronous Circuits</b>                        | 7  |

| 2.1       | Inti | roduction                                           | 7  |

| 2.2       | As   | ynchronous Circuits Principles                      | 9  |

| 2.3       | Ha   | ndshaking Protocols                                 | 11 |

| 2.4       | The  | e Muller's C-Element                                | 13 |

| 2.5       | The  | e Muller's Pipeline                                 | 14 |

| 2.6       | Cla  | ssification of Asynchronous Circuits                | 16 |

| 2.7       | Pip  | eline and Rings: Token Game                         | 17 |

| 2.8       | Co   | nclusions                                           | 19 |

| Chapter   | 3.   | Self Timed Rings                                    | 21 |

| 3.1       | Int  | roduction                                           | 21 |

| 3.2       | Rin  | ng Structure                                        | 22 |

| 3.        | 2.1  | Ring Connectivity                                   | 22 |

| 3.        | 2.2  | Definitions and Notations                           | 23 |

| 3.3       | Rin  | ng Modeling                                         | 24 |

| 3.        | 3.1  | The Charlie Effect                                  | 25 |

| 3.        | 3.2  | The Drafting Effect                                 | 26 |

| 3.        | 3.3  | The Charlie Model                                   | 26 |

| 3.        | 3.4  | Timed VHDL Models                                   | 29 |

| 3.4       | Oso  | cillation Frequency Calculation of Self-Timed Rings | 30 |

| 3.5       | Pro  | grammable Self-Timed Rings                          | 34 |

| 3.        | 5.1  | PSTR Architecture                                   | 34 |

| 3.        | 5.2  | PSTR Design Flow                                    | 37 |

| 3.6       | Pro  | ogrammable Stoppable Oscillator (PSO)               | 40 |

| 3.7       | Imp  | plementation and Results                            | 46 |

|      | _    |      |                                                 |

|------|------|------|-------------------------------------------------|

|      |      | 7.1  | Analog Results                                  |

|      |      | 7.2  | Frequency vs. Supply Voltage                    |

| _    |      | 7.3  | Sensitivity to Process Variability              |

| Ź    | 3.8  | Cor  | nclusions                                       |

| Chaj | pter | 4.   | PSTR Case Study in a GALS System                |

| 2    | 2.1  | Intr | oduction                                        |

| 2    | 2.2  | Mu   | lti Clock Challenges and GALS Scheme            |

| 2    | 2.3  | Dat  | a Synchronization in GALS Systems               |

|      | 2.   | 3.1  | GALS Wrapper with Pausible Clocking             |

|      | 2.   | 3.2  | FIFO Solutions                                  |

|      | 2.   | 3.3  | Boundary Synchronization                        |

| 2    | 2.4  | App  | plication of PSTR for GALS Data Synchronization |

|      | 2.   | 4.1  | Circuit Design                                  |

|      | 2.   | 4.2  | Simulation Results                              |

|      | 2.   | 4.3  | Multipoint Interconnection Schemes              |

| 2    | 2.5  | Cor  | nclusions                                       |

| Par  | t-II |      | CMOS Power Reduction and Design for Yield       |

| Cha  | ptei | · 5. | Power Saving Techniques                         |

| 5    | 5.1  | Intr | oduction                                        |

| 5    | 5.2  |      | rces of CMOS Power Consumption                  |

|      | 5.   | 2.1  | Leakage Power                                   |

|      | 5.   | 2.2  | Switching Power                                 |

|      | 5.   | 2.3  | Short-Circuit Power                             |

| 5    | 5.3  | Sta  | tic Power Reduction Techniques                  |

|      | 5.   | 3.1  | Multi-Threshold                                 |

|      | 5.   | 3.2  | Body Biasing                                    |

|      | 5.   | 3.3  | Power Gating                                    |

| 5    | 5.4  | Dyı  | namic Power Reduction Techniques                |

|      | 5.   | 4.1  | Clock Gating                                    |

|      | 5.   | 4.2  | Dynamic Voltage and Frequency Scaling           |

| 5    | 5.5  | Cla  | ssification of DVFS Algorithms                  |

|      | 5    | 5.1  | Intra-Task DVFS                                 |

|      | ٥.   |      |                                                 |

|      |      | 5.2  | Inter-Task DVFS                                 |

| 5    |      | ·-   | Inter-Task DVFS                                 |

| Chapter  | 6.   | Controlling Uncertainty and Handling the Process Variability | 95  |

|----------|------|--------------------------------------------------------------|-----|

| 6.1      | Intr | oduction                                                     | 95  |

| 6.2      | Rel  | ated Work Contributions                                      | 97  |

| 6.3      | Pro  | cess Variability Robust NoC Architecture                     | 98  |

| 6.       | 3.1  | Overall Architecture                                         | 102 |

| 6.       | 3.2  | Sensing the Computational Activity                           | 105 |

| 6.       | 3.3  | DC-DC Converter                                              | 106 |

| 6.       | 3.4  | Frequency Controller                                         | 106 |

| 6.4      | No   | C Control Method                                             | 107 |

| 6.       | 4.1  | Fast Predictive Control                                      | 110 |

| 6.       | 4.2  | Tracking Efficiency                                          | 112 |

| 6.       | 4.3  | Digital Controller Algorithm                                 | 114 |

| 6.5      | Sim  | nulation Results                                             | 116 |

| 6.       | 5.1  | Load Modeling                                                | 116 |

| 6.       | 5.2  | Workload Tracking Efficiency                                 | 117 |

| 6.       | 5.3  | Robustness to Process Variability                            | 118 |

| 6.6      | Cor  | nclusions                                                    | 119 |

| Chapter  | 7.   | Designing Process Variability Robust DVFS Control            | 121 |

| 7.1      | Intr | oduction                                                     | 121 |

| 7.2      | Cas  | se Study: MIPS R2000                                         | 122 |

| 7.3      | Ana  | alysis of MIPS R2000 Critical Path Delay Variations          | 123 |

| 7.4      | PST  | ΓR Programmability to Manage MIPS R2000 Variations           | 126 |

| 7.       | 4.1  | PSTR 45nm CMOS Delay Parameters                              | 126 |

| 7.       | 4.2  | PSTR Architecture                                            | 127 |

| 7.       | 4.3  | PSTR Configuration                                           | 128 |

| 7.5      | Dig  | rital Controller Design                                      | 129 |

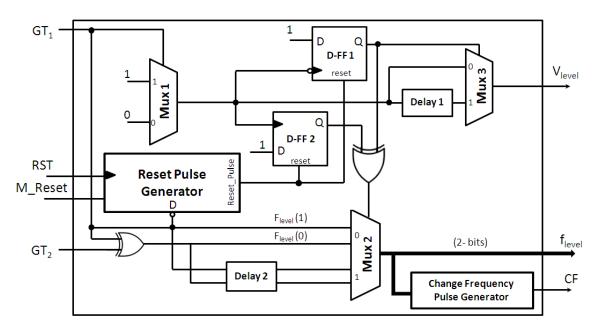

| 7.       | 5.1  | Overall Architecture                                         | 129 |

| 7.       | 5.2  | Speed Set Point Update                                       | 131 |

| 7.       | 5.3  | Voltage and Frequency Selection                              | 133 |

| 7.6      | Sim  | nulation Results                                             | 135 |

| 7.7      | Cor  | nelusions                                                    | 143 |

| Chapter  | 8.   | Conclusion and Perspectives                                  | 145 |

| Publicat | ions |                                                              | 149 |

| Referen  | ces  |                                                              | 151 |

# LIST OF FIGURES

| Figure | Title                                                                                                         | Page |

|--------|---------------------------------------------------------------------------------------------------------------|------|

| 2.1    | Basic Structure of a Synchronous Circuit.                                                                     | 9    |

| 2.2    | Basic Structure of an Asynchronous Circuit.                                                                   | 10   |

| 2.3    | A Two-Phase Protocol.                                                                                         | 12   |

| 2.4    | A Four-Phase Protocol.                                                                                        | 13   |

| 2.5    | The Muller's C-element: Symbol and Truth Table.                                                               | 14   |

| 2.6    | The Muller Pipeline.                                                                                          | 15   |

| 2.7    | Gates and Wires Delay Model for a Circuit Fragment.                                                           | 16   |

| 2.8    | Basic Elements of an Asynchronous Circuit.                                                                    | 17   |

| 2.9    | A Possible State of a Five Stage Pipeline.                                                                    | 18   |

| 2.10   | A Sequence of Data Transfers in a Ring.                                                                       | 19   |

| 3.1    | A Ring Stage.                                                                                                 | 23   |

| 3.2    | A Self-Timed Ring.                                                                                            | 23   |

| 3.3    | Modes of Operation in Self-Timed Rings.                                                                       | 24   |

| 3.4    | "week feedback" Implementation of a Muller C-element.                                                         | 25   |

| 3.5    | A Ring Stage Chronogram.                                                                                      | 27   |

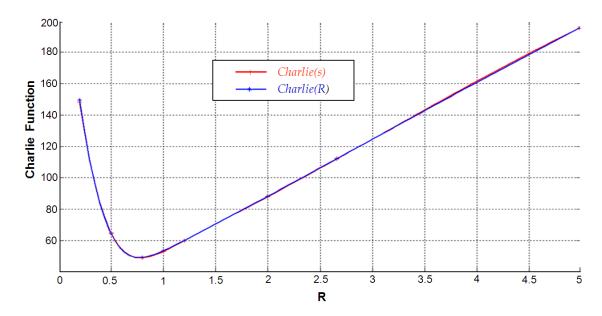

| 3.6    | Charlie Diagram at Constant y.                                                                                | 28   |

| 3.7    | Charlie Diagram at Constant s.                                                                                | 29   |

| 3.8    | VHDL Simulation Results for two Different Configurations of 11-Stages Self-Timed Ring without Charlie Effect. | 30   |

| 3.9    | VHDL Simulation Results for two Different Configurations of 11-Stages Self-Timed Ring with Charlie Effect.    | 30   |

| 3.10   | Charlie Diagram at Constant y for two Different Operating Conditions.                                         | 31   |

| 3.11   | Charlie $(R)$ against Charlie $(s)$ Diagrams with respect to $R$ .                                            | 33   |

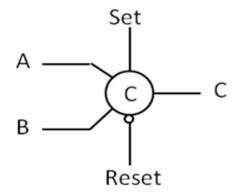

| 3.12 | Muller Gate with Set/Reset.                                      | 35 |

|------|------------------------------------------------------------------|----|

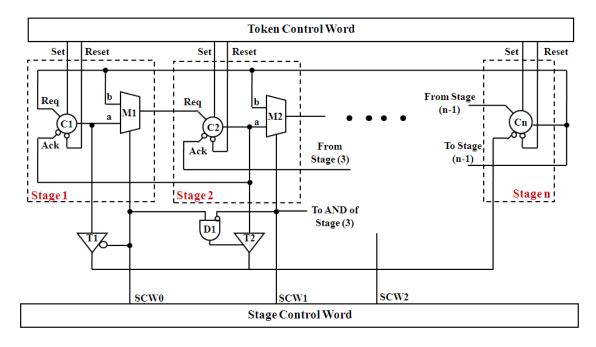

| 3.13 | Programmable Self-Timed Ring.                                    | 36 |

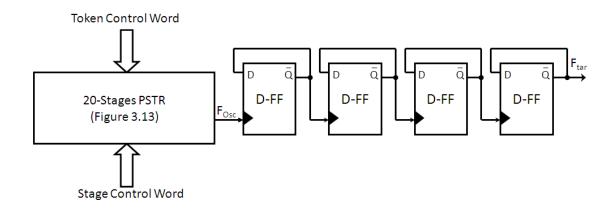

| 3.14 | PSTR with External D-F.Fs for Targeting Low Frequencies.         | 38 |

| 3.15 | Design Flow for PSTR Oscillators.                                | 39 |

| 3.16 | The Interface between Micro-Processor and PSO.                   | 40 |

| 3.17 | Programmable/Stoppable Oscillator.                               | 41 |

| 3.18 | PSO Control Unit.                                                | 42 |

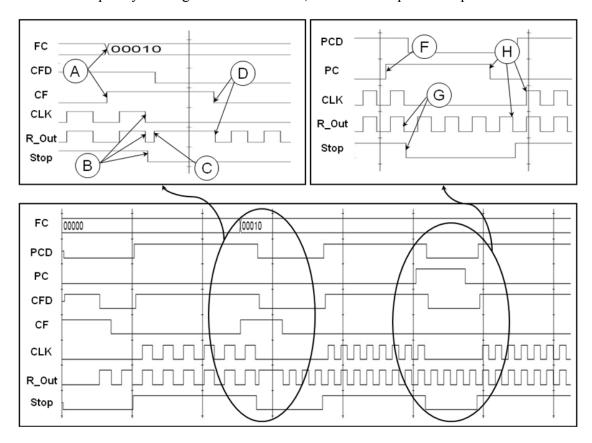

| 3.19 | Timing Diagram of the PSO.                                       | 45 |

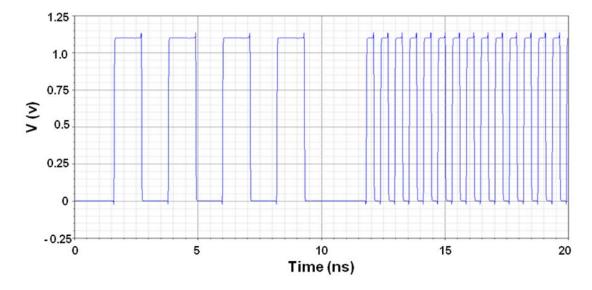

| 3.20 | Analog Results of the PSO.                                       | 46 |

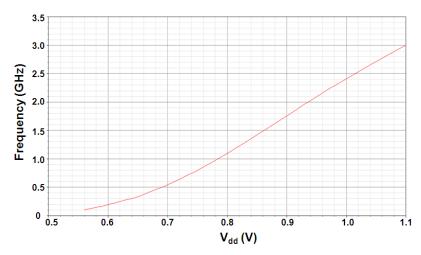

| 3.21 | PSTR Output Frequency Change with respect to the Supply Voltage. | 49 |

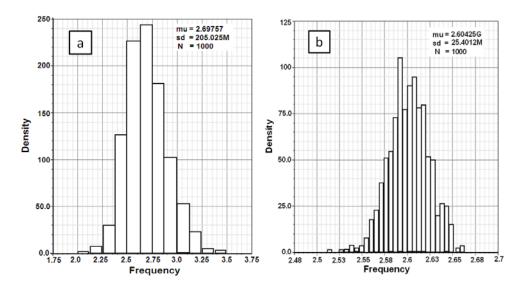

| 3.22 | Process Variations of PSTR.                                      | 49 |

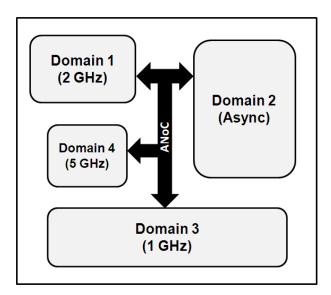

| 4.1  | GALS Architecture.                                               | 55 |

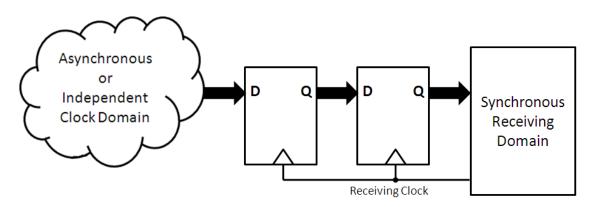

| 4.2  | Double-Latching Synchronization Scheme.                          | 56 |

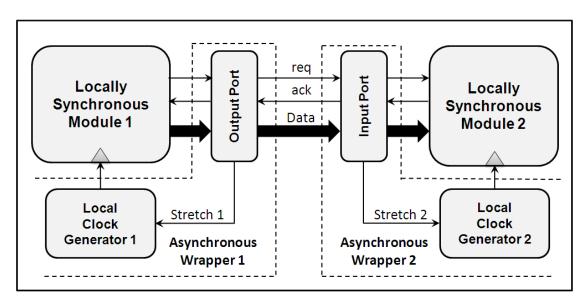

| 4.3  | GALS System with Pausible Clocking.                              | 57 |

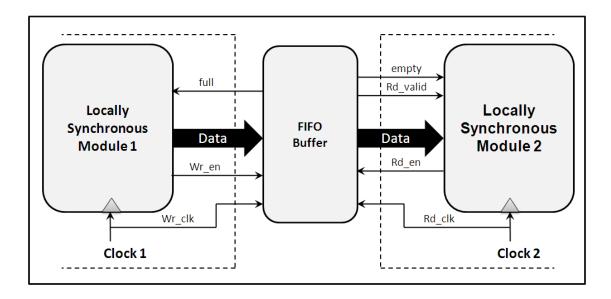

| 4.4  | Typical FIFO Based GALS System.                                  | 58 |

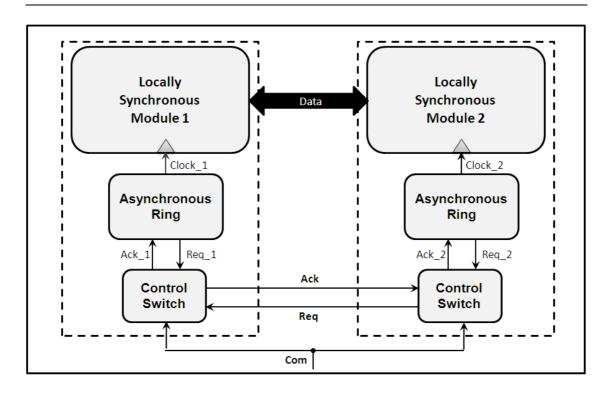

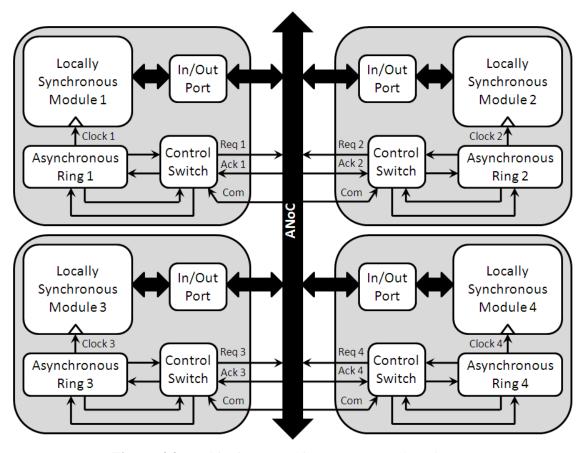

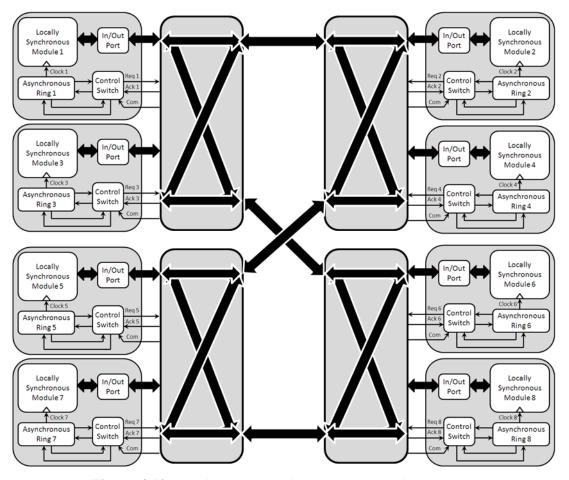

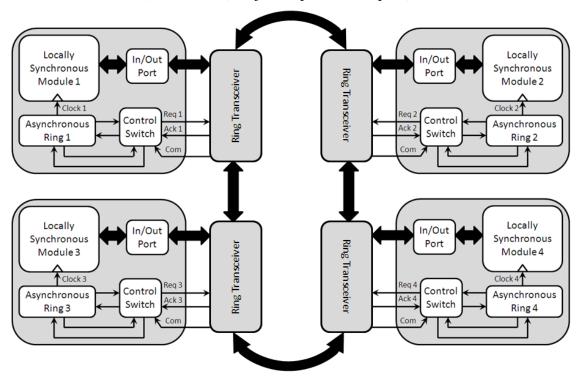

| 4.5  | PSTR Based GALS System.                                          | 62 |

| 4.6  | Control Switch Interconnections with the Asynchronous Ring.      | 63 |

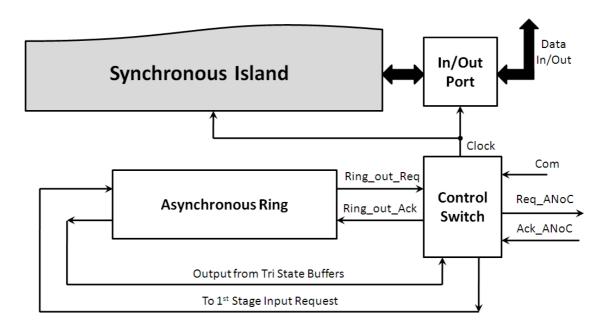

| 4.7  | Control Switch.                                                  | 64 |

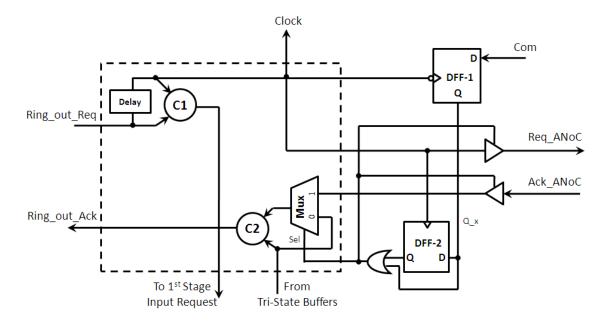

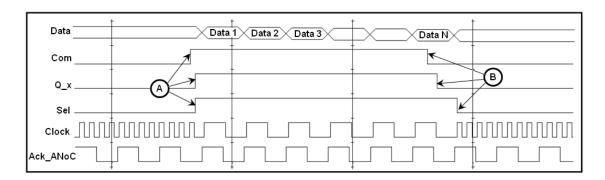

| 4.8  | Timing Diagram of the Control Switch.                            | 66 |

| 4.9  | Multipoint GALS interconnects (Shared Bus).                      | 67 |

| 4.10 | Multipoint GALS interconnects (Switch Network).                  | 68 |

| 4.11 | Multipoint GALS interconnects (Ring Structure).                  | 69 |

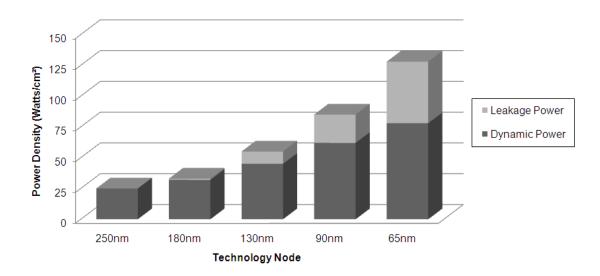

| 5.1  | Static vs. Dynamic Power with Process Migration.                 | 75 |

| 5.2  | Using Bias to Control Threshold Voltages.                        | 78 |

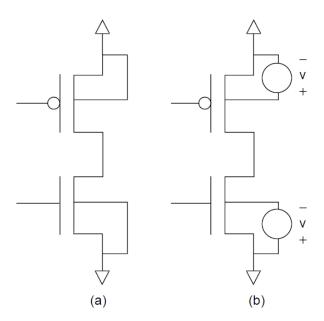

| 5.3  | Fine Grain Power Gating with an Inverter.                                                                                                           | 80  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

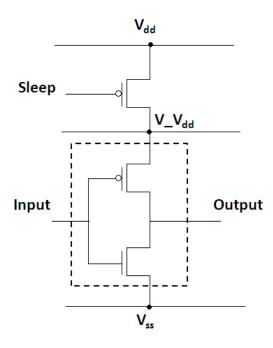

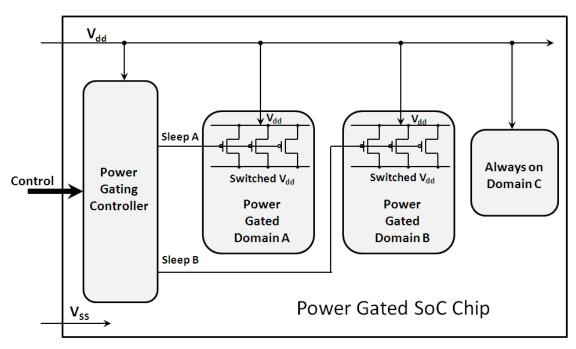

| 5.4  | Coarse-Grain Power Gating.                                                                                                                          | 81  |

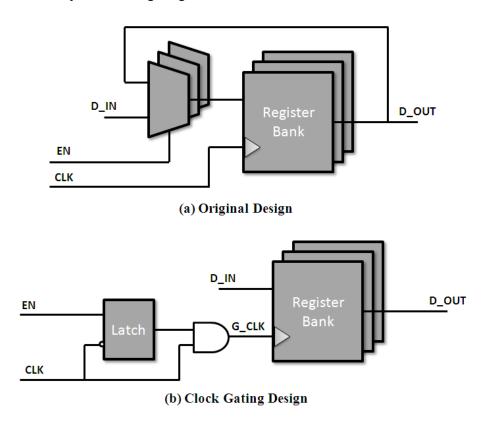

| 5.5  | Clock Gating.                                                                                                                                       | 83  |

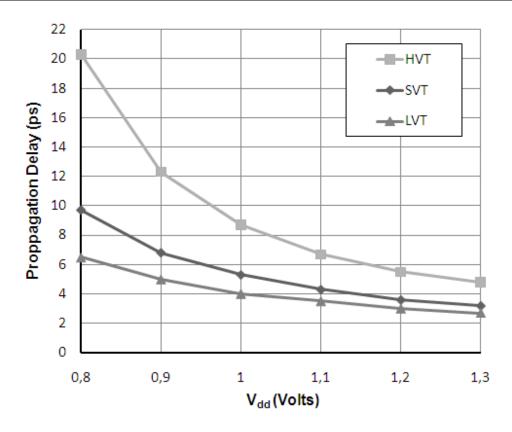

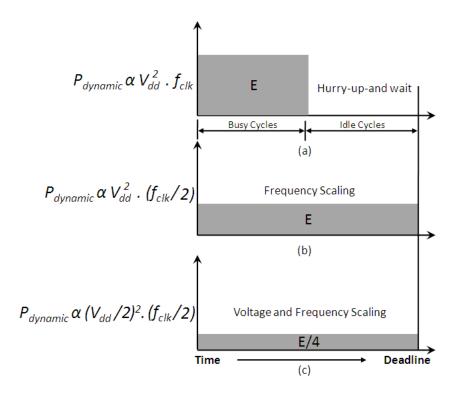

| 5.6  | Propagation Delay vs. $V_{dd}$ for an Inverter Gate in STMicroelectronics 45nm CMOS Process using HVT, SVT and LVT libraries.                       | 85  |

| 5.7  | Energy Consumption vs. Power Consumption.                                                                                                           | 86  |

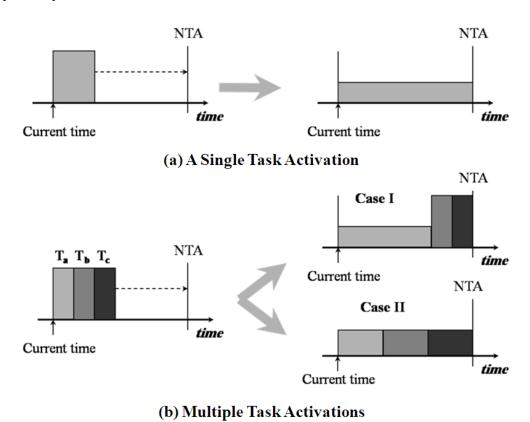

| 5.8  | Examples of Stretching to NTA.                                                                                                                      | 90  |

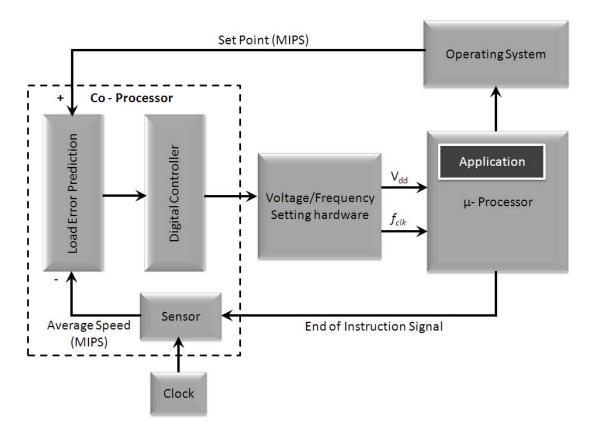

| 5.9  | Voltage/Frequency Control Simplified Architecture.                                                                                                  | 93  |

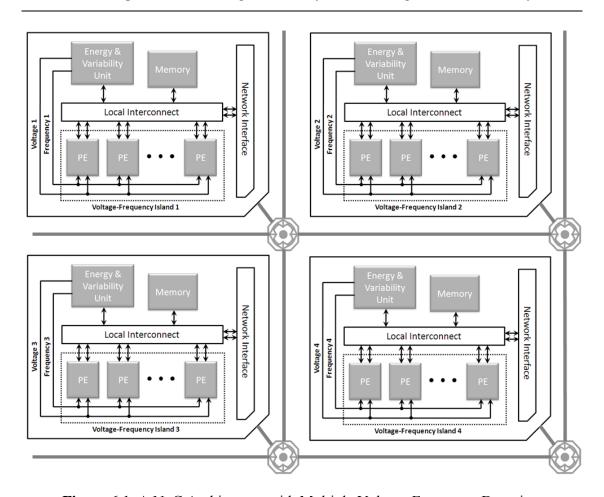

| 6.1  | A NoC Architecture with Multiple Voltage-Frequency Domains.                                                                                         | 96  |

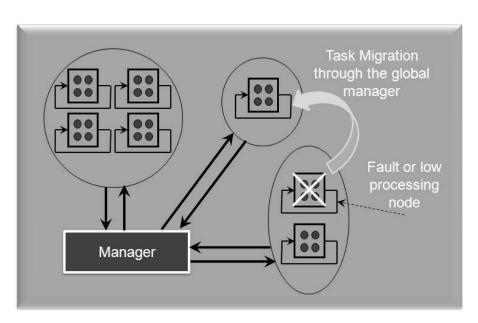

| 6.2  | Fabrication Yield Control by Distributing Tasks over Different Processing Nodes in a GALS System.                                                   | 98  |

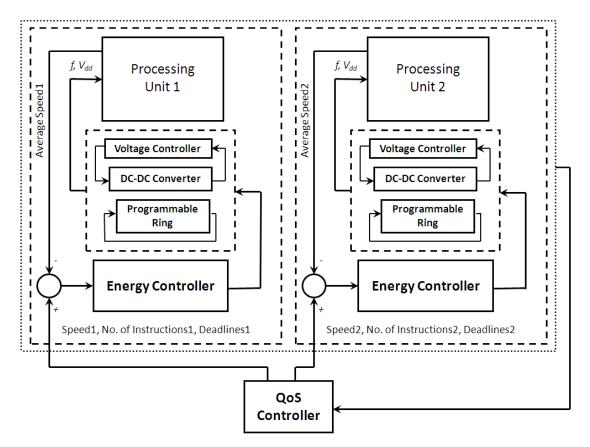

| 6.3  | Energy/Performance Control Simplified Architecture.                                                                                                 | 101 |

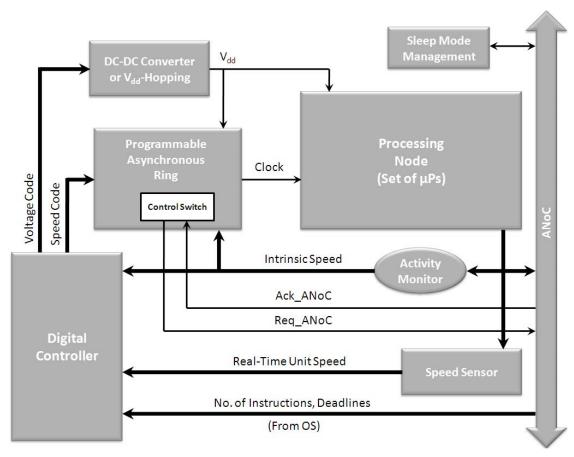

| 6.4  | Energy/Performance Management Architecture for a Voltage-Frequency Island in a GALS-NoC System.                                                     | 103 |

| 6.5  | Chronogram of V <sub>dd</sub> -Hopping.                                                                                                             | 106 |

| 6.6  | Different Computational Speed Set Point Buildings and their Impact on<br>the Energy Consumption (i.e. the Penalizing High Voltage Running<br>Time). | 109 |

| 6.7  | Flow Chart of the Digital Controller Algorithm.                                                                                                     | 115 |

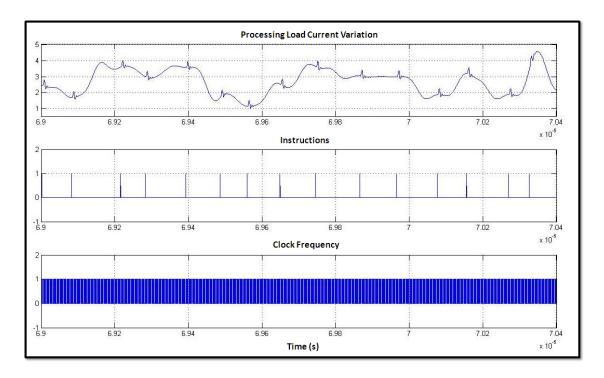

| 6.8  | Simulink Simulation for the Processing Node Load Model showing its Current Variations with respect to Different Processing Instructions.            | 116 |

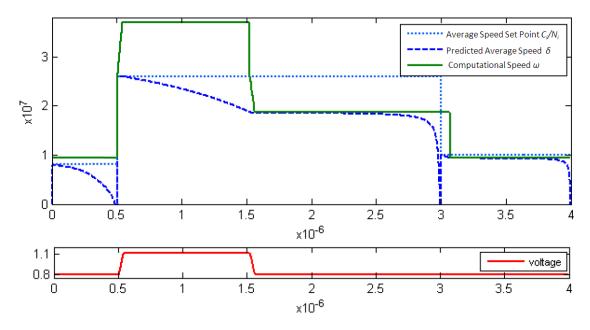

| 6.9  | Matlab Simulation Result of the Digital Controller.                                                                                                 | 117 |

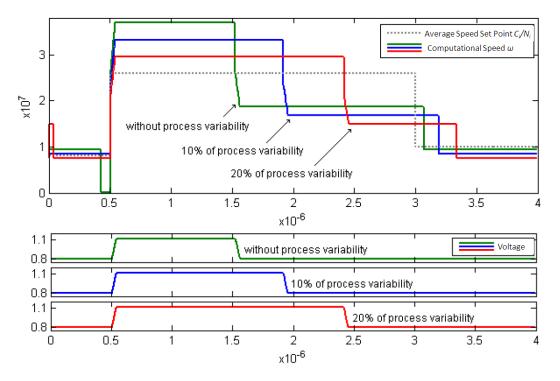

| 6.10 | Matlab Simulation Results to Test the System Robustness with Different Degrees of the Process Variability Effect.                                   | 118 |

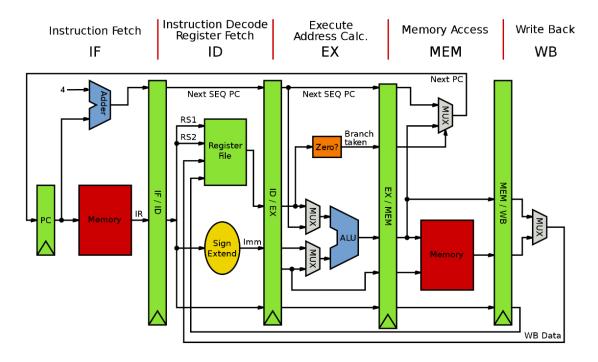

| 7.1  | Internal Architecture of the Pipelined MIPS (5 Stages).                                                                                             | 122 |

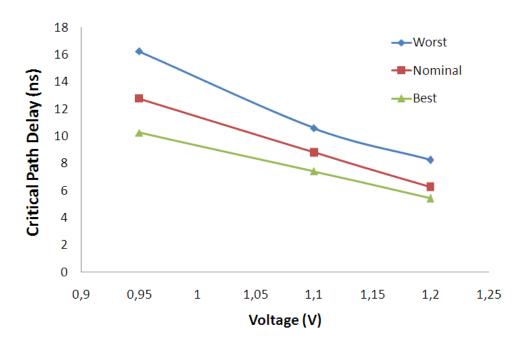

| 7.2  | MIPS R2000 Critical Path Delay Variation with Respect to Supply Voltage at Three Different PVT Corners.                                             | 123 |

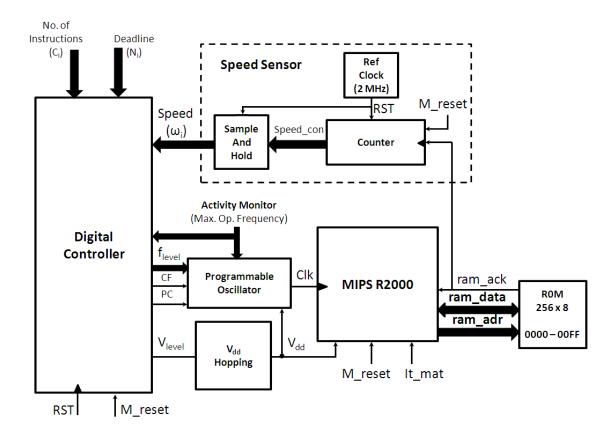

| 7.3  | Process Variability Robust Energy/Performance Management Architecture (MIPS R2000 Case Study).                                     | 125 |

|------|------------------------------------------------------------------------------------------------------------------------------------|-----|

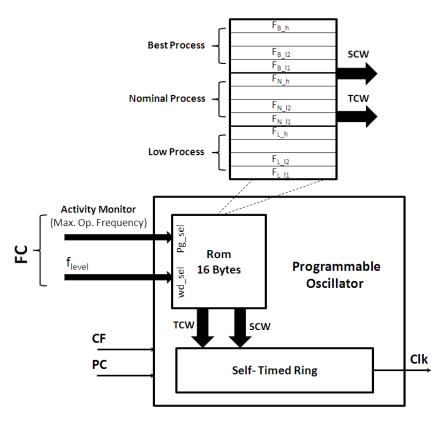

| 7.4  | Memory Mapping of the Programmable Oscillator.                                                                                     | 127 |

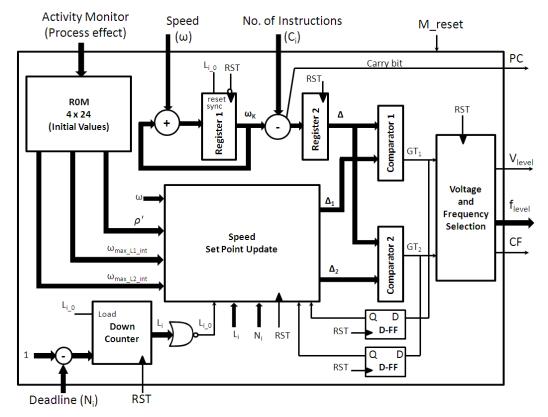

| 7.5  | Digital Controller Architecture.                                                                                                   | 129 |

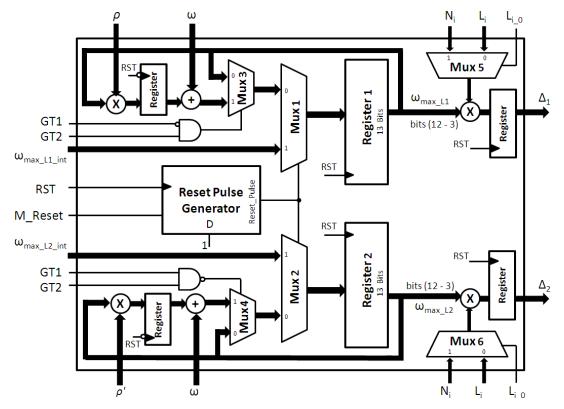

| 7.6  | Speed Set Point Update Unit.                                                                                                       | 131 |

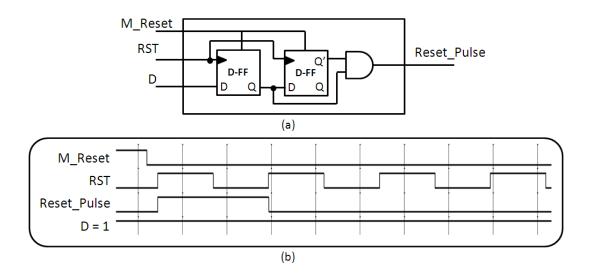

| 7.7  | Reset Pulse Generator Architecture and Timing Diagram.                                                                             | 133 |

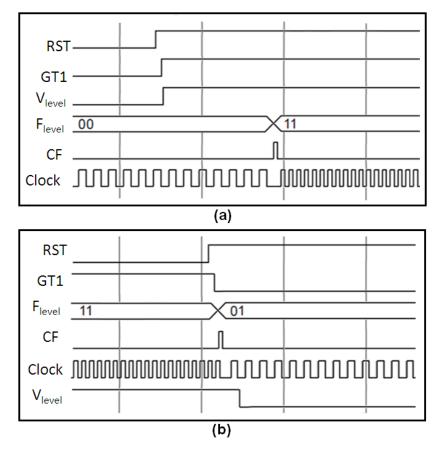

| 7.8  | Voltage and Frequency Selection Unit.                                                                                              | 134 |

| 7.9  | Timing Diagram of the Voltage and Frequency Selection Unit.                                                                        | 134 |

| 7.10 | Change Frequency Pulse Generator.                                                                                                  | 135 |

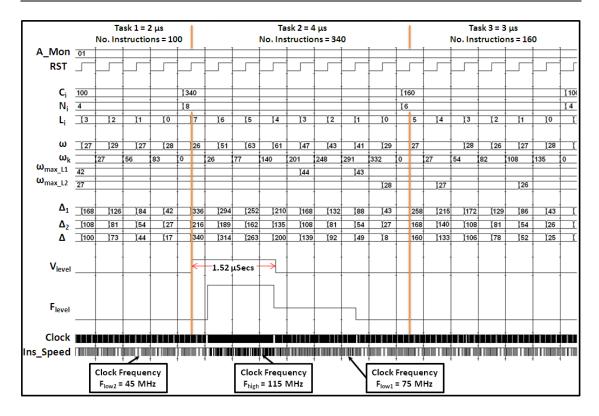

| 7.11 | Timing Diagram of the Digital Controller Behaviour with 3 Different MIPS R2000 Workloads under Nominal Process Variability Effect. | 137 |

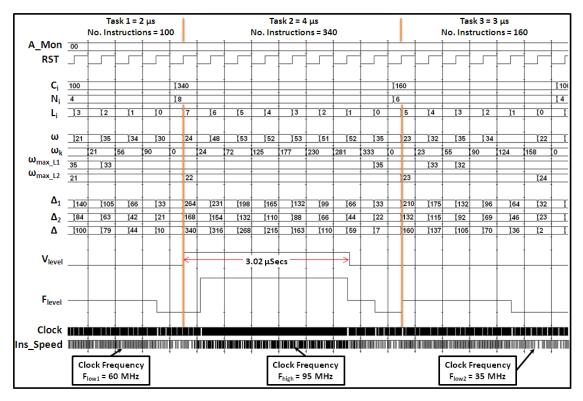

| 7.12 | Timing Diagram of the Digital Controller Behaviour with 3 Different MIPS R2000 Workloads under Worst Process Variability Effect.   | 138 |

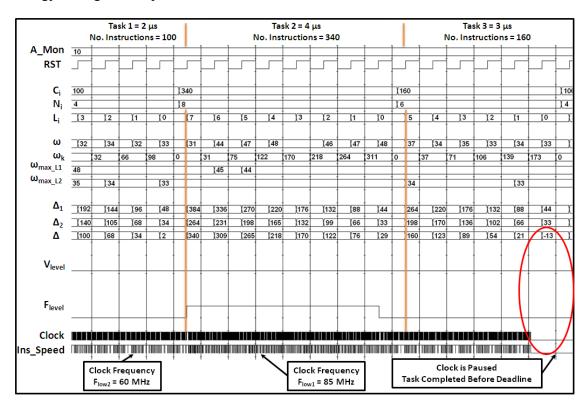

| 7.13 | Timing Diagram of the Digital Controller Behaviour with 3 Different MIPS R2000 Workloads under Best Process Variability Effect.    | 139 |

# LIST OF TABLES

| Table | Description                                                                                                                                                 | Page |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.1   | Results for Different Programming Strategies.                                                                                                               | 47   |

| 4.1   | Properties of GALS Systems.                                                                                                                                 | 60   |

| 5.1   | Classification of DVFS Algorithms.                                                                                                                          | 91   |

| 7.1   | MIPS R2000 Optimum Clock Frequencies Required to Compensate for the Process Variability Impact on 45nm CMOS Technology.                                     | 124  |

| 7.2   | Extracted Delay Values of the Asynchronous PSTR Functional Parameters on STMicroelectronics 45nm CMOS.                                                      | 126  |

| 7.3   | PSTR Programmability to Manage Process Variations of the 45nm CMOS Technology on the MIPS R2000.                                                            | 128  |

| 7.4   | A Comparison between Energy-Efficient and Normal Average Based DVFS Control with Respect to a System without DVFS at Different Process Variability Corners. | 140  |

| 7.5   | Power, Energy and Cross Sectional Area of Each Part in the DVFS Architecture shown in Figure 7.3.                                                           | 142  |

| 7.6   | Performance Analysis of the Whole Energy-Efficient GALS-NoC DVFS Control System under Nominal Process Variability Impact.                                   | 142  |

# **Chapter 1**

## Introduction

### 1.1 Context and Motivations

With increased levels of integration in scaled technologies, complex systems containing (large number of processors, on-chip memories, IPs, complex clock trees, I/O control units, etc.) have become a reality. As recognized by the International Technology Roadmap for Semiconductors (ITRS), dealing with on-chip communications and power management problems require a drastic departure from the classic design methodologies [SEM 06]. Therefore novel on-chip communication architectures that use a Network-on-Chip (NoC) approach have emerged as a scalable alternative to traditional bus-based or point-to-point communication solutions [DAL 01] and [LEE 07].

By eliminating global wires, the NoC approach provides the needed modularity and performance, while facilitating design reuse. Moreover, the NoC approach offers a matchless platform for implementing the globally asynchronous locally synchronous (GALS) design paradigm [CHA 84] and [MUT 00]. This makes the clock distribution and timing closure problems more manageable. In addition, a GALS design style fits nicely with the concept of different voltage-frequency domains, which provides better power-performance tradeoffs than its single voltage, single clock frequency counterpart [DIE 03] and [BER 05], while taking advantage of the natural partitioning and mapping of applications onto the NoC platform. However, the implementation of GALS systems makes mandatory the synchronization of the communicating clock domains frequencies and phases in order to guarantee that data is reliably transferred among them [BEI 06].

In addition to this huge increase in system complexity, the systems designed in nanoscale technologies suffer from systematic and random variations in process, voltage, and temperature (PVT), particularly from the 45nm CMOS technologies and beyond. As

a result, the integrated system performances after fabrication will not be fully predictable. Indeed, within die variations play an increasingly important role in system power consumption and performance as the technology scales down [BOR 03].

Since designers cannot rely on the accuracy of the nominal parameter values, there is a tremendous need for on-line techniques that can cope with such dynamic variations [REB 09] and [MIE 08]. More precisely, there is a need for efficient algorithms and built-in circuitry able to adapt the system behavior to workload variations and, at the same time, cope with the parameter variations which cannot be predicted or accurately modeled at design time.

Not surprisingly, designing appropriate dynamic voltage and frequency scaling (DVFS) control algorithms for run-time control of different voltage-frequency domains in a GALS system is a matter of great importance. While this problem has been addressed before by a number of authors [OGR 08], [WU 04] and [NIY 05], no attention has been given to add the feature of controlling the impact of manufacturing process variations to the capabilities of the DVFS controllers.

Starting from these overarching ideas, ARAVIS project (Architecture avancée Reconfigurable et Asynchrone pour la Video et la radio logicielle Intégrée Sur puce) sponsored by Minalogic, looks for architecture and design solutions that allow the production of embedded computational platforms in its scalability limit. It proposes a generalization of certain techniques in order to obtain a solution to the technology variability problem in 32nm, which will represent an input toward the development of a new paradigm. The ARAVIS project is focused on three technology keys:

- 1- Reconfigurable structure with respect to applicability requirements. It can be accomplished by programming the flexible interconnections between the clustered nodes of the SoC computational unit [PIN 01].

- 2- GALS paradigm in order to release the communication constraints between remote points.

- 3- Dynamic management of the power consumption and activity with respect to constraints are achieved by control theory application [HEL 04].

This thesis is included as a part of the ARAVIS project context. It specifically focuses on the design of GALS-based NoC architectures in the upcoming CMOS technologies. Activity monitors are disseminated into each voltage-frequency island to locally evaluate the process quality in terms of its relative speed with respect to the other processing nodes. A novel methodology to dynamically control the speed of different voltage-frequency GALS-NoC islands according to the process variability impact on each domain is proposed. This control technique can improve the performances, the energy consumption, and the yield of future SoC architectures in a synergistic manner.

The proposed control methodology is based on the design of an asynchronous programmable self-timed ring where the controller takes into account the dynamic workload and the process variability effects. The controller especially considers the operating frequency limit which does not exceed the maximum locally allowed value for a given clock domain. With such an approach, it is no more required to separately guaranty the performance for each node. This drastically relaxes the fabrication constraints and helps the yield enhancement.

### 1.2 Thesis Outline

This thesis dissertation is mainly split into two main parts: GALS Paradigm (Part-I) and CMOS Power Reduction and Design for Yield (Part-II).

This first part comprises the chapters 2 to 4. In Chapter 2 an introduction of the asynchronous circuits is introduced. Asynchronous circuit classes are discussed stating the different handshaking protocols. In addition to this, token and bubble rules were also presented to facilitate the discussion of data flow in asynchronous circuits. This helps to understand the basic principle of operation of self-timed rings.

In Chapter 3, we propose a design for a Programmable/Stoppable Oscillator (PSO) which is based on self-timed ring to exploit its interesting characteristics (programmability, accuracy and robustness against process variability). Through a handshaking protocol, the oscillator is communicating with the synchronous processor to ensure a proper switching from one frequency to another. The oscillator is designed in order to avoid the presence of glitches and truncated clock periods.

As we consider GALS-NoC architectures, low latency high throughput asynchronous communication mechanisms between synchronous blocks will be obligatory. Therefore in Chapter 4, we make use of the previously designed programmable self-timed ring to propose a new scheme based on the use of asynchronous handshake circuits to safely synchronize these clocks. This circuit design gathers the small area and the low power consumption advantages of the pausible clocking GALS with the high throughput advantage of the FIFO-based GALS.

The second part of the thesis contains the chapters 5 to 7. The necessary concepts needed to understand and well characterize the main sources of CMOS power dissipation in the nanometric era are declared in Chapter 5. Moreover, in this chapter we investigate different low power solutions that are needed to reduce the impact of each contributing part to the total CMOS power consumption. As DVFS is recognized as one of the most effective power reduction techniques, therefore its different algorithms and its architecture are detailed.

In Chapter 6, a novel DFVS architecture that dynamically adapts the speed of each voltage-frequency island in a GALS system is proposed. The DVFS control principal not only considers the dynamic workload variations, but also ensures that the operating frequency does not exceed the maximum allowed value for a given process variability effect. The control methodology is based on the use of the asynchronous PSO with a fast predictive feedback controller.

Chapter 7 addresses the problem of designing the proposed process variability robust DVFS control methodology. MIPS R2000 presents our processing load case study. The PSO was programmed and configured to compensate for MIPS R2000 variations on STMicroelectronics 45nm CMOS technology. Moreover, the digital controller part of the DVFS was completely designed and tested on different process variability corners.

Finally the conclusion of the thesis and the prospects are discussed in Chapter 8.

# Part – I GALS Paradigm

# Chapter 2

# **Asynchronous Circuits**

### 2.1 Introduction

In recent years there has been tremendous growth in the silicon integration capacity. Starting from the 45 nm technology and beyond, designers face various problems in power consumption, process variability, environment-parameters (Process, Voltage, and Temperature) "PVT" variations and Electromagnetic Interference "EMI". As synchronous design style is based on global timing assumptions determined by the clock. Coping with this assumption, especially with the recent technologies, is challenging from two points of views. First, the increase of process variability implies inefficient increase in timing doubt while designing. Second, clock trees are gradually consuming more power and needing more effort for managing. Therefore, different solutions are presented for these challenges as multi-clock systems and clock gating. However, Asynchronous circuits show an efficient alternative solution for these problems [REN 03] and [BEE 02].

Asynchronous circuits use handshaking between their components in order to perform the necessary synchronization, communication, and sequencing of operations. This results in a behavior that is similar to systematic fine-grain clock gating and local clocks that are not in phase and whose period is determined by actual circuit delays; i.e. registers are only clocked where and when needed. This behavior gives asynchronous circuits the following interesting features [SPA 01], [BER 99], and [MAR 97]:

### (1) Low power consumption

Because asynchronous circuits do not need any clock signals, the power spent on clock switching in a synchronous chip is avoided. Additionally, the signal transitions in asynchronous circuits will automatically stop when there is no data. Therefore, asynchronous circuit design has zero standby dynamic power consumption), [BER 94].

### (2) No global-signal distribution and clock skew problems

Since asynchronous circuit designs have simple handshake interfaces and local timing, the difficulties of clock distribution and clock skew faced by synchronous designs are removed from asynchronous designs.

### (3) Low emitted EMI noise

In a synchronous design, flip-flop transitions follow a certain clock frequency so that the energy spent on signal transitions concentrates within the very narrow bands around the clock frequency. Thus, the synchronized signal switching activities will produce substantial electrical noise. Whereas, the switching activities in an asynchronous circuit are correlated loosely because there is no universal timing pace, hence, they produce a more distributed noise spectrum and a lower peak noise value, [PAV 98].

### (4) Average-case performance

In a synchronous design, the operating speed is limited by the worst-case, called critical path in the circuits. However, in asynchronous circuits, the operating speed is determined by actual local latencies in the circuits rather than global worst-case latency. In most of cases, the average-case of latencies are smaller than the worst-case latency, hence, asynchronous designs can achieve better operating speed performance, [WIL 91] and [WIL 95].

### (5) Robust and adaptive

A synchronous circuit is sensitive to the delay variations caused by the process variability effects and environment-parameters variations (i.e. clock signal, supply voltage, and operating temperature) related with the manufacturing process and application surrounding. Whereas, the loose timing requirement of asynchronous circuits allow them to operate correctly under large variations caused by different manufacturing processes and application environment, [NIE 94] and [SPA 01].

### (6) Better modularity

The modularity of asynchronous circuits is almost perfect. It is due to the locality of control and the use of a well-specified communication protocol by all operators. It is indeed easy to construct a complex system involving pre-existing blocks, [SPA 01].

According to the previously mentioned asynchronous circuit advantages, research and industry are progressively more motivated to the introduction of asynchronous technology into products and design flows. On the other hand there are also some drawbacks of the asynchronous circuit implementation. The asynchronous control logic that implements the handshaking normally causes an overhead in terms of silicon area, circuit speed, and power consumption. It is therefore important to ask whether or not the investment pays off, i.e. whether the use of asynchronous technique results in a considerable improvement over the synchronous one or not [SPA 01].

### 2.2 Asynchronous Circuits Principles

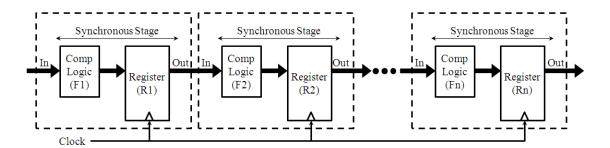

In synchronous design style, depicted in Figure 2.1, synchronous circuits are composed of combinational function blocks and registers. The circuit activity is controlled by a global clock which triggers at the same time the memorization of the complete state of the circuit. As a new state is sampled and placed in the registers, the combinational circuits start the computation of the next state to be sampled at the next clock edge. The clock signal is fixed so that all functional blocks correctly complete their operations and their data outputs are stable and ready to be sampled. That implies a global timing assumption which is applied to the whole circuit: the longest combinational path (critical path) must not exceed the clock period. Synchronization in asynchronous circuits is done by replacing the clock signal with some form of handshaking between adjacent registers; for example the request-acknowledge based handshake protocol shown in Figure 2.2 [MYE 01] and [SPA 01].

Figure 2.1: Basic Structure of a Synchronous Circuit.

Asynchronous circuits are composed of communicating stages which computation is controlled by the presence of data at their inputs and outputs. Their behavior is much similar to the data-flow model, [REN 03]. Let's consider one asynchronous stage described in Figure 2.2. It receives data from its input port, the functional block computes it, and sends the result through a register to its output port. Data communication over its ports are not controlled by an external signal, like a clock, but by a communication protocol implemented within the control part of the stage itself. Such protocols require a bi-directional exchange of information between senders and receivers called handshake protocols.

Figure 2.2: Basic Structure of an Asynchronous Circuit.

The communication protocol is the basis of the sequencing rules of asynchronous circuits. The first rule is that an asynchronous stage starts the computation if and only if all the data required for the computation are available. Once the result can be stored in the register, the asynchronous stage releases the input ports. It outputs the result through the output port if and only if this port is available, i.e. released by the next stage connected to it, at the end of the previous communication. The implementation of the communication protocol in each stage is the price to pay to get rid of the clock and be able to control the sequencing locally, [REN 03].

Each asynchronous stage can implement functions with very different granularity: bit-level functions, word-level arithmetic functions or even complex algorithms. However, they always have the following three main characteristics, [YUN 96], [REN 96], [CUM 94], and [WIL 94]:

- 1. All their channels respect a unified communication protocol.

- 2. They all compute the input data set at the highest speed and place the result at its output as soon as possible (minimum forward latency), while, the synchronous circuits forward latency may not vary with the data computed. The forward latency is constrained by the clock period.

- 3. They also all have a maximum throughput which corresponds to the maximum frequency at which the module can process the incoming data (maximum cycle time). This characteristic is not the inverse of the forward latency because the asynchronous stage has to release the communication channels before accepting the next data set. With asynchronous circuits, we have to consider the forward and reverse phases to compute the throughput (Notice that is not a trivial relation because this depends on the employed handshaking protocol).

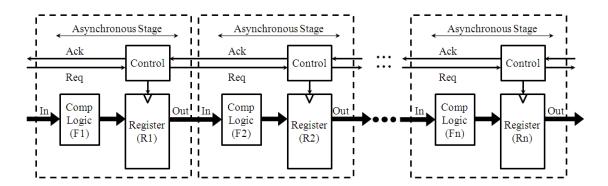

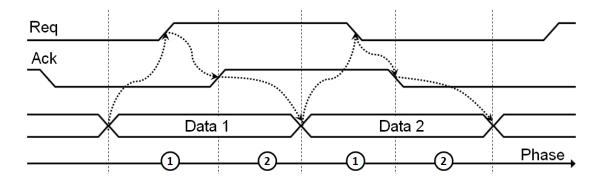

### 2.3 Handshaking Protocols

To implement a bidirectional signaling in asynchronous circuits, two communication protocols are commonly used: the two-phase protocol, also called NRZ (Non Return to Zero) or "half-handshake" and four-phase protocol, also known as RZ (Return to Zero) or "full-handshake". Both protocols are respectively shown in Figure 2.3 and Figure 2.4. In both cases, it should be noted that any event on a signal from the transmitter stage is reset by an event on a signal from the receiver stage, and vice versa. This mechanism ensures the insensitivity to the processing time of the operator. In these protocols, the only importance is in the occurrence of events locally between the transmitter and the receiver, and not in their relative time, or their respective orders in relation to the transmitter input or the receiver output. The choice of communication protocol affects the characteristics of the board layout (Area, speed, power consumption, robustness, etc...), [REN 03] and [SPA 01].

The two phase protocol has the minimum required sequence of information exchange per communication. Signaling in the 2-phase protocol is event-based since data

detection and acknowledgment are done by means of rising and falling edges of signals. The two phases are as follows:

*1<sup>st</sup> Phase*: The transmitter generates a transition on the request signal. The receiver detects the incoming data and once the reception process is completed, it generates a transition on the acknowledgement signal.

$2^{nd}$  *Phase*: The transition on the acknowledgement signal is detected by the transmitter and depending upon the availability, the new data is transmitted.

Figure 2.3: A Two-Phase Protocol.

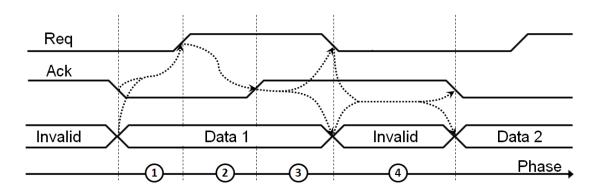

Four phase protocols are level-based. These protocols require a return to zero phase for both the data and the acknowledgement as shown in Figure 2.4. The sequencing between two asynchronous stages in the four phase protocol is done in the following manner:

1<sup>st</sup> Phase: The transmitter issues data and sets the request signal high.

$2^{nd}$  *Phase*: The receiver absorbs the data and sets the acknowledgement high.

3<sup>rd</sup> Phase: The transmitter responds by taking request low (at which point data is no longer valid).

$4^{th}$  *Phase*: The receiver acknowledges this by taking acknowledge low. At this point the transmitter may initiate the next communication cycle.

Figure 2.4: A Four-Phase Protocol.

Despite of the apparent effectiveness of the two-phase protocol (i.e. faster and less power consuming), but actually it is not always the case because event-based logic is more costly than level-based in terms of CMOS implementation. Moreover, very effective optimizations can be done at the logic and architectural levels when using four-phase protocols. Generally speaking two-phase protocols are preferred when slow components (with large forward latencies) are involved in the cycle time. On the contrary, four-phase protocols are mostly used within the circuit due to the symmetry of its phases, where the designer is free of balancing component latencies to optimize the circuit performances [REN 03], [SPA 01], and [REN 00].

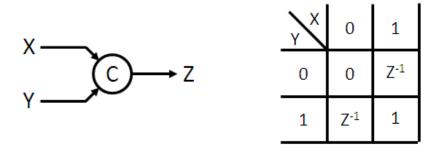

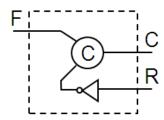

### 2.4 The Muller's C-element

In a synchronous circuit the checking role is to define points in time where signals are stable and valid. In between the clock ticks, signals may exhibit hazards and may have multiple transitions till the combinational circuits stabilize. This does not matter from the functional point of view. Conversely, asynchronous control circuits shown in Figure 2.2 have a different behavior. The absence of the clock means that, in many situations signals are required to be valid all the time, that every signal transition has a meaning. As a result, hazards and races must be avoided. A circuit that is better in this respect is the Muller's C-element shown in Figure 2.5, [RIG 02], and [MAR 86]. Actually, it is a state holding element works in the following principle: When both inputs are 0 the output is set to 0, and when both inputs are 1 the output is set to 1. For other input combinations the output does not change. Consequently, an observer seeing the

output change from 0 to 1 may conclude that both inputs are now at 1; and similarly, an observer seeing the output change from 1 to 0 may conclude that both inputs are now 0. Combining this with the observation that all asynchronous circuits rely on handshaking that involves cyclic transitions between 0 and 1, it should be clear that the C-element is indeed a fundamental component that is extensively used in asynchronous circuits.

**Figure 2.5**: The Muller's C-element: Symbol and Truth Table.

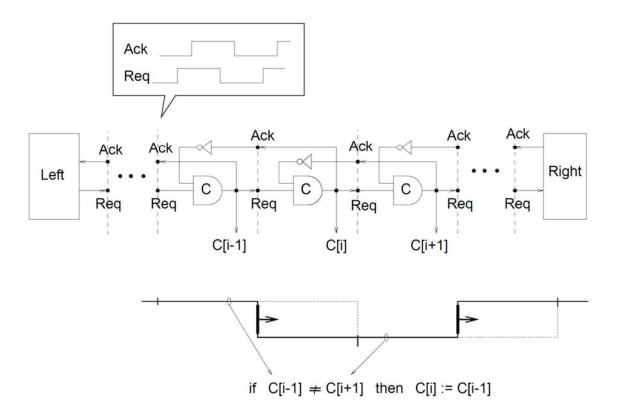

### 2.5 The Muller's Pipeline

Figure 2.6 shows a circuit that is built from C-elements and inverters. The circuit is known as a Muller's pipeline, [GUN 93] and [MUL 59]. Variations and extensions of this circuit form the control backbone of almost all asynchronous circuits. This Muller's pipeline is a way to transmit the handshakes. After all of the C-elements have been initialized to 0, the left environment may start handshaking. To understand what happens let's consider the ith C-element, C[i]: It will propagate a 1 from its predecessor, C[i-1], only if its successor, C[i+1], is 0. In a similar way it will propagate a 0 from its predecessor if its successor is 1. It is often useful to think of the signals propagating in an asynchronous circuit as a sequence of waves, as illustrated at the bottom of figure 2.6. Viewed this way, the role of a C-element stage in the pipeline is to propagate these waves in a carefully controlled way that maintains the integrity of each wave.

On any interface between C-element pipeline stages an observer will see correct handshaking, but the timing may differ from the timing of the handshaking on the left hand environment. Once a wave has been injected into the Muller pipeline, it will propagate with a speed that is determined by the actual delays in the circuit. Eventually the first handshake (request) injected by the left hand environment will reach the right hand environment. If the right hand environment does not respond to the handshake, the pipeline will eventually fill. If this happens the pipeline will stop handshaking with the left hand environment. In addition to this elegant behavior, the pipeline has a number of beautiful symmetries. Firstly, it does not matter if 2-phase or 4-phase handshaking is used. The difference is in how the signals are interpreted and the circuit is used. Secondly, the circuit operates equally well from right to left, with reversing the role of the request and acknowledge signals. Finally, the circuit has the interesting property that it works correctly regardless of delays in gates and wires. The Muller pipeline is delayinsensitive.

Figure 2.6: The Muller Pipeline.

### 2.6 Classification of Asynchronous Circuits

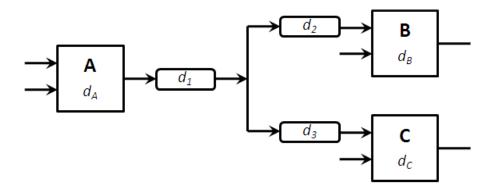

Asynchronous circuits can be classified as being speed-independent, delay insensitive or self-timed depending on gate and wire delays assumptions that are required to guarantee their functional correctness [PAN 02], and [EBE 91]. Figure 2.7 facilitate the illustration of this concept. The figure shows three gates: A, B, and C, where the output signal from gate A is connected to inputs on gates B and C.

**Figure 2.7**: Gates and Wires Delay Model for a Circuit Fragment, the output of Gate A forks to inputs of gates B and C.

### *Speed-Independent (SI)*:

This class of circuits operates correctly assuming that positive, bounded but unknown delays in gates and ideal zero-delay wires, [EBE 91]. Referring to Figure 2.7 this means arbitrary  $d_A$ ,  $d_B$ , and  $d_C$ , but  $d_I = d_2 = d_3 = 0$ . Assuming ideal zero-delay wires is not very realistic in today's semiconductor processes.

### Delay-Insensitive (DI):

This class of circuits operates correctly with positive, bounded but unknown delays in wires as well as in gates. Referring to Figure 2.7 this means arbitrary  $d_A$ ,  $d_B$ ,  $d_C$ ,  $d_1$ ,  $d_2$ , and  $d_3$ . Such circuits are obviously extremely robust. At the gate level, only circuits composed of C-elements and inverters can be delay-insensitive, and their functionality is limited. This is why delay-insensitive circuits are usually built out of modules which require some delay assumptions internally. Circuits that are delay-

insensitive with the exception of some carefully identified wire forks, where  $d_2 = d_3$  are called *Quasi-Delay-Insensitive* (QDI). Such wire forks where signal transitions occur at the same time at all end points are called "isochronic forks", [BER 92] and [MAR 90]. At the gate level, this assumption enables the design of circuits made of single-output gates.

#### Self-Timed Circuits:

Speed independency and delay-insensitivity as introduced above are mathematically well defined prosperities under the unbounded gate and wire delay model, [SPA 01]. Circuits whose correct operation relies on more elaborate and/or engineering timing assumptions are simply called self-timed. In the next chapter a full description of self-timed rings and their programmability will be presented.

The different circuit classes SI, DI, QDI and self-timed are not mutually exclusive ways to build complete systems, but useful abstractions that can be used at different levels of design, [SPA 01] and [HAU 95]. In most practical designs they are mixed. For example, in the Amulet processors SI design is used for local asynchronous controllers, and DI is used for high-level composition, [GAR 00]. Therefore, the careful choice of handshake protocol and circuit implementation style is among the factors to optimize an asynchronous digital system.

### 2.7 Pipelines and Rings: Token Game

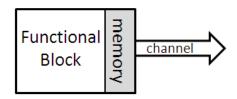

At architectural level, in order to ease the token flow discussion it is assumed that an asynchronous circuit is composed of functional blocks (combinational circuits), memory elements (registers) and channels (request, acknowledgment, and data signals). Figure 2.8 shows the basic elements of an asynchronous circuit.

Figure 2.8: Basic Elements of an Asynchronous Circuit.

A token is carrying information and is stored in a memory element. A token is represented by a filled circle next to the memory element it is stored in. When using a 4-phase protocol, the asynchronous data-path processes a stream of alternating valid and return to zero tokens. When a 2-phase protocol is used, there are only valid tokens, but apart from that everything is the same. Data flow information is controlled by two rules, [REN 03]:

Token rule: a memory may receive and store a new token from its predecessor if and only if it has a bubble.

Bubble rule: a memory becomes empty (bubble) if and only if its successor has received and stored the token that it was holding.

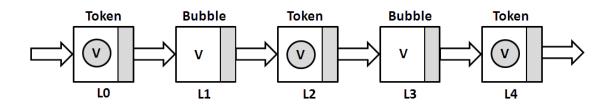

Figure 2.9 shows a snapshot of a simple five stage pipeline, which is implemented using 2-phase protocol. The valid value in L1 and L3 has just been copied into L2 and L4 respectively. This means that L1 and L3 are now holding old duplicates of the values now stored in L2 and L4. Such old duplicates are called "bubbles", and the newest valid values are called "tokens". To distinguish tokens from bubbles, tokens are presented with a circle around the value. Bubbles can be viewed as a medium: a bubble allows a token to move forward, and in supporting this, the bubble moves backward one step.

**Figure 2.9**: A Possible State of a Five Stage Pipeline.

Any circuit should have one or more bubbles; otherwise it will be in a deadlock state. This is a matter of initializing the circuit properly. Furthermore, as we will see in the next chapter, the number of bubbles also has a significant impact on performance.

Figure 2.10: A Sequence of Data Transfers in a Ring.

In a pipeline with at least three stages, it is possible to connect the output of the last stage to the input of the first stage, forming a ring in which data tokens can circulate autonomously, [SPA 01]. Assuming the ring is initialized as shown in Figure 2.10 at time  $t_0$  with two valid tokens and a bubble, the steps of the circulation process are shown in Figure 2.10, at time  $t_1$ ,  $t_2$  and  $t_3$ . Rings are the backbone structure of circuits that perform iterative computations. The cycle time of the ring in Figure 2.10 is 3 steps (the state at  $t_3$  is identical to the state at  $t_0$ ).

Next chapters of the thesis show how programmable versions of 2-phase self-timed rings could be used, in order to: Firstly, synchronize the data transfer between different clock domains in a GALS system, while avoiding metastability problems. Secondly, manage not only the energy consumption but also the process variability in complex integrated system (System on Chip often denoted SoC).

#### 2.8 Conclusions

Problems with the clock in synchronous circuit design are becoming more and more complex, which open the path to the design of asynchronous circuits. Unlike the global clock mechanism used in synchronous circuits, timing in asynchronous circuits is done locally through a bidirectional signaling between all elements of the circuit. This signaling is established via communication channels using a specified handshaking

protocol (2-phase or 4-phase). Asynchronous circuits are classified into different types according to their gate and wire delays assumptions that are required to guarantee their functional correctness. Asynchronous circuits make the design of distributed finite state machines as well as data paths much easier than before, as there is no need to know the global state of the system to make things communicate and synchronize, where it is the case with synchronous circuits. Token and bubble rules were presented to facilitate the discussion of data flow in asynchronous circuits. This also helps to understand the basic principle of operation of self-timed rings, which will be presented in details within the next chapter.

# **Chapter 3**

# **Self-Timed Rings**

#### 3.1 Introduction

Ring oscillators are one of the most essential building blocks in many digital and communication systems. They are used in to generate and distribute timing signals which synchronize processing unit operations. Programmable versions of these ring oscillators have a variety of applications. In Dynamic Voltage and Frequency Scaling "DVFS" systems, they are used to dynamically manage the energy consumption of a complex system integrated on a chip. This is done with the regular adaption of the processing unit clock frequency according to the computational needs, as will be shown in Chapter 5. In Globally Asynchronous Locally Synchronous "GALS" systems programmable ring oscillators are also required in order to adjust the clock frequency for each clock domain, where each domain has its own local clock frequency, as will shown in Chapter 4. With the rapid increase in the process variability effects on the system behavior due to the shrinking of the integrating technology, one must carefully choose the operational ring oscillator. This oscillator should have robust behavior under different environmental and process variability effects.

Adjustable clocks can be derived from different kinds of clock generators. For example, these clocks can be derived from analog Voltage Controlled Oscillators "VCO", which are a part of a Phase Locked Loop "PLL". However, VCO have a limited operating range and a required stabilization time when changing the frequency [BOY 06]. Another solution is to use a standard clock divider, but this will make the time resolution coarser, due to counting integer periods of the input frequency [STO 03]. In addition, they give regular time step which implies irregular frequency step (usually frequency step follows "1/x" curve).

Asynchronous self-timed rings are considered promising solution for generating clocks. In [FAI 04] they are efficiently used to generate high-resolution timing signals. Their robustness against process variability in comparison to inverter rings is proven in [HAM 08]. They are efficiently used as a data driven clocks in [MUL 07]. Moreover, for a given number of stages self-timed rings can be reconfigured easily by controlling their initialization (i.e. their number of tokens and bubbles; explain in the sequel), while in the contrary, inverter-ring frequency is fixed [FAI 04]. Furthermore, as events propagate between adjacent stages in self-timed rings according to a simple request/acknowledge handshake signals, we can make use of these handshakes in synchronizing the data transfer between different clock domains in a GALS system while avoiding metastability problems, as will be shown in Chapter 4.

This chapter proposes a design for a Programmable/Stoppable Oscillator which is based on asynchronous self-timed ring to exploit its interesting characteristics. Through a handshaking protocol, the oscillator is communicating with the synchronous processor to insure a proper switching from one frequency to another. The oscillator is designed in order to avoid the presence of glitches and truncated clock periods. A new methodology for calculating the ring oscillation period will also be presented.

# 3.2 Ring Structure

Various kinds of implementations of a self-timed ring exist and the underlying token and bubble notions depend on the communication protocol (e.g. 2-phase or 4-phase communication protocol). In this context, it is important to clearly define the structure and the token and bubble notions.

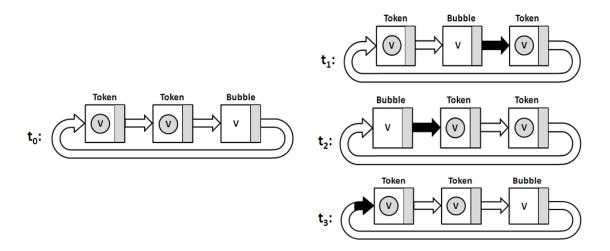

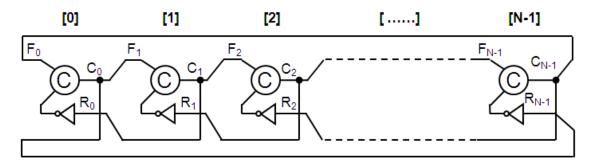

#### 3.2.1 Ring Connectivity

Figure 3.1 shows the structure of the ring stage. It is composed of a Muller C-element and an inverter. In each stage, the input which is connected to the previous stage is marked F (Forward) and the input which is connected to the following stage is marked R (Reverse), C denotes the output of the stage. Figure 3.2 shows an example of a ring composed of self-timed handshaking N-stages, [MUL 59].

Figure 3.1: A Ring Stage

Figure 3.2: A Self-Timed Ring.

#### 3.2.2 Definitions and Notations

We choose the 2-phase communication protocol as defined in [SUT 89], which allows us to derive the token and bubble concepts of the self-timed ring as follows:

- Stage<sub>i</sub> contains a token if its output C<sub>i</sub> is not equal to the output C<sub>i+1</sub> of stage<sub>i+1</sub>.

C<sub>i</sub> ≠ C<sub>i+1</sub> ⇔ Stage<sub>i</sub> ← Token

- Stage<sub>i</sub> contains a bubble if its output  $C_i$  is equal to the output  $C_{i+1}$  of stage<sub>i+1</sub>.

$$C_i = C_{i+1} \Leftrightarrow Stage_i \leftarrow Bubble$$

The numbers of tokens and bubbles are denoted by  $N_T$  and  $N_B$  respectively. Because a token is defined with respect to the value of two adjacent stages,  $N_T$  is an even number whatever the number of stages. Moreover, each stage of the ring contains either a token or a bubble, so  $N_T + N_B = N$ , where N is the number of the ring stages. As self-timed rings have a 2-phase pipeline structure, the data flow through its adjacent stages is the same as it was previously discussed in Chapter 2. If a token is present in stage<sub>i</sub>, it will propagate to stage<sub>i+1</sub>, if and only if stage<sub>i+1</sub> contains a bubble. The bubble of stage<sub>i+1</sub> will

move backward to stage<sub>i</sub>. This implies a transition on stage<sub>i+1</sub>. In Figure 2.10 an example was shown for these token/bubble movements in a three stage self-timed ring, which contains two tokens and one bubble. With the previous notations, the necessary and sufficient condition for a token to propagate from stage<sub>i-1</sub> to stage<sub>i</sub> can be expressed as:

$$C_{i-1} \neq C_i = C_{i+1}$$

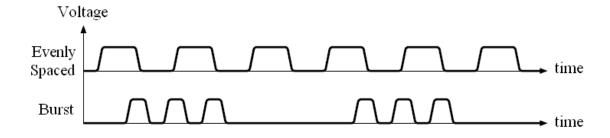

From these propagation rules, we can derive the requirements to obtain an oscillating asynchronous self-timed ring. By definition, the number of tokens in a ring must be even and at least one bubble is necessary to enable tokens to move. The minimal number of stages is hence 3. Self-timed rings produce two different modes of oscillation: "Evenly spaced" or "Burst" modes, see Figure 3.3. In the evenly spaced mode, the events inside the ring are equally spaced in time. In the burst mode, the events are non-uniformly spaced in time. In our application, we only target the evenly spaced mode.

**Figure 3.3**: Modes of Operation in Self-Timed Rings.

#### 3.3 Ring Modeling

The key to understand the temporal properties of self-timed rings lies in finding an appropriate model for the ring. The ideal model will be one that captures the non-linear timing dependencies of real circuits while still being simple enough to provide insight into the causes of bursting and uniformly spaced behavior. Two key effects have been identified as being responsible of the ring behavior, the Charlie effect, [EBE 98] and [ZEB 05], and the Drafting effect [WIN 01], [WIN 02], and [FAI 04].

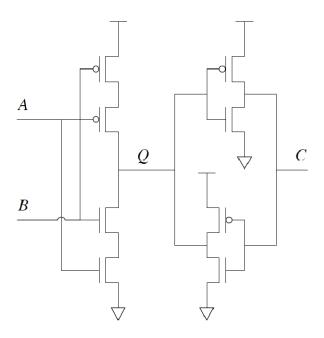

#### 3.3.1 The Charlie effect

The deep observation of the C-element temporal behavior shows that the separation time between input events has a direct impact on the propagation delay: "the closer the input events; the longer the propagation time". This phenomenon is called "Charlie effect" in reference to Charles E. Molnar. The analysis of the C-element structure can explain these variations in the propagation time. Figure 3.4 shows a conventional implementation of the C-element referenced as "week feedback", [SHA 98]. It can be divided into two stages: the input stage which calculates the output value when both inputs are identical and the output stage which stores this value in other cases.

**Figure 3.4**: "week feedback" Implementation of a Muller C-element.

The Charlie effect appears in the input stage transistors when both N-channel and P-channel transistors must move simultaneously from the cut-off state to the saturation state, or vice versa. This occurs when the events on both inputs of the C-element are close. To understand this phenomenon, we propose an example. Consider a scenario where both A and B make a 0 to 1 transitions, and A changes after B. If A changes a long time after B, then the P-channel transistor controlled by B will be in its cut-off region, and the N-channel transistor controlled by B will be *fully conducting* as A changes.

Furthermore, the node between the two N-channel transistors will be close to ground potential. This allows a relatively fast transition on signal Q and therefore on the output C. on the other hand, if A changes only slightly after B, then the transistors controlled by B will both be *partially conducting* as A changes. This result in a greater delay from the transition of A to the transition of C. Similar effects occur if A changes before B.

### 3.3.2 The Drafting effect

Similarly, there is an impact of the time elapsed between two successive output communications on the propagation delay: the closer the successive transitions; the shorter the propagation delay. This phenomenon is called the "Drafting effect". This effect is opposite to the Charlie effect which has a tendency to slow the spread of tokens, while the Drafting effect tends to accelerate several tokens in sequence. This effect which appears on the output stage of the Muller C-element is due to the output capacitance of the stage. When a commutation occurs just after the previous one, the output has not enough time to reach neither  $V_{\rm dd}$  nor GND before its new commutation which causes a faster transition (i.e. shorter propagation delay).

#### 3.3.3 The Charlie Model

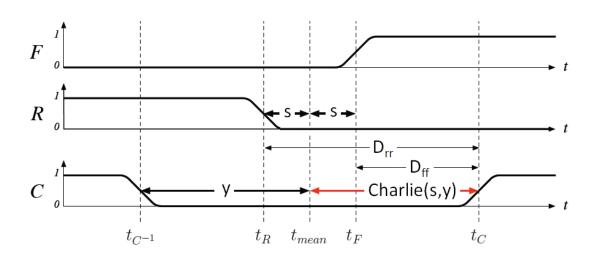

The Charlie model represents the ring stage propagation delay as a function of two variables, *s* and *y* as shown in Figure 3.5 where:

- *s* is the half separation time between input events:

$$s=\frac{t_F-t_R}{2}$$

- y is the time between the previous output commutation and the mean input time.

$$y = \frac{t_F + t_R}{2} - t_{C^{-1}} = t_{mean} - t_{C^{-1}}$$

Figure 3.5: A Ring Stage Chronogram.

The Charlie model is also adjusted by a set of five parameters that correspond to the physical characteristics of the stage implementation (dimensions of the Muller Celement and inverter transistors). These parameters are noted as:

- $D_{ff}$  the static forward propagation delay.

- $D_{rr}$  the static reverse propagation delay.

- $D_{charlie}$  the amplitude of the Charlie effect.

- A the duration of the drafting effect.

- B the amplitude of the drafting effect.

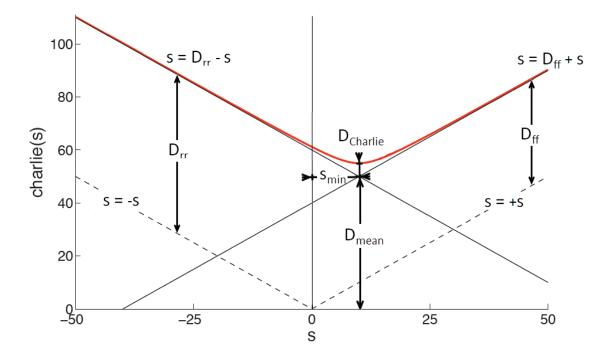

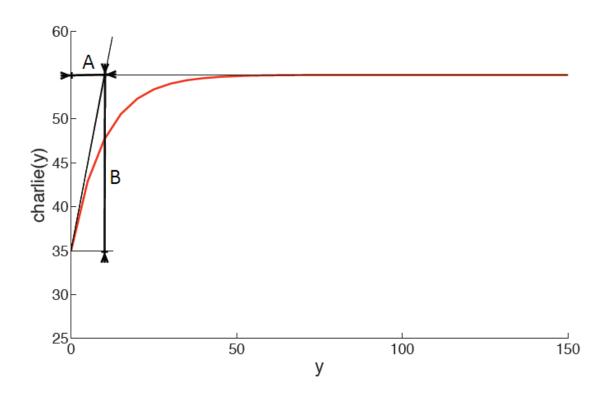

The shape of the Charlie model at constant y corresponds to a parabola defined by the asymptote lines  $D_{ff} + s$  and  $D_{rr} - s$  (see Figure 3.6). Noting that the minimum value of this parabola, which is called "valley" of Charlie model, corresponds to the longest propagation delay where the influence of the Charlie effect is the maximum. Similarly, the shape of the Charlie model at constant s follows the exponential form of charging a capacitance through a resistance (see Figure 3.7). Therefore, the analytical formulation of the Charlie model can be expressed as:

Charlie

$$(s, y) = \underbrace{D_{mean} + \sqrt{D_{charlie}^2 + (s - s_{min})^2}}_{Charlie} - \underbrace{B_{prafting}^{-\frac{y}{A}}}_{Drafting}$$

(3.1)

with:

$$\begin{cases} D_{mean} = \frac{D_{rr} + D_{ff}}{2} \\ s_{min} = \frac{D_{rr} - D_{ff}}{2} \end{cases}$$

Finally, the commutation instant  $t_C$  can be expressed with respect to the input commutation instants ( $t_F$  and  $t_R$ ) and the Charlie model as:

$$t_C = (t_F + t_R)/2 + charlie(s, y)$$

(3.2)

**Figure 3.6**: Charlie Diagram at Constant y.

**Figure 3.7**: Charlie Diagram at Constant *s*.

#### 3.3.4 Timed VHDL Models

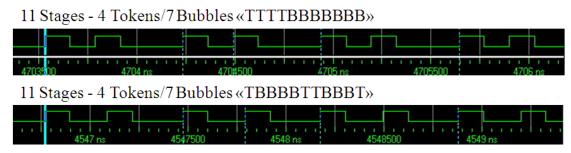

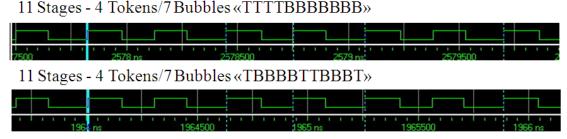

Without modeling the Charlie effect and by simulating the same self-timed ring with the same number of tokens and bubbles, but with different spatial token distributions, digital simulation (VHDL Model) shows different steady state waveform. However, Analog simulation shows exactly the same steady state waveform. An explanation of this incorrect behavior of the digital simulation is due to the absence of Charlie effect in the model, [YAH 09]. To confirm this explanation, we simulate an 11-stage ring without modeling the Charlie effect. We first configured it by the following Token/Bubble pattern ("TTTTBBBBBBBBB"). The steady state output was a burst mode oscillation. When the ring is initialized with ("TBBBBTTBBBT"), the steady state output becomes evenly spaced. This wrongly concludes that the initial spatial distribution of the Tokens/Bubbles could affect the oscillation mode, which is not true. These simulation results are shown in Figure 3.8.

**Figure 3.8**: VHDL Simulation Results for two Different Configurations of 11-Stages Self-Timed Ring without Charlie Effect.

The same simulation is now performed using Muller gates models which are taking the Charlie effect into consideration. Figure 3.9 shows that they give identical steady state behavior and both are oscillating in evenly spaced mode as it was expected.

**Figure 3.9**: VHDL Simulation Results for two Different Configurations of 11-Stages Self-Timed Ring with Charlie Effect.

The conclusion is that including the Charlie effect inside our digital model is mandatory to have a correct behavior of the ring model. As the design and analysis phases need so many simulations, our digital model saves us a lot of time compared to standard analog simulations.

# 3.4 Oscillation Frequency Calculation of Self-Timed Rings

In this section, we propose a simple methodology for calculating the oscillation frequency of the self-timed ring oscillator. The new method allows us to estimate the oscillation period in function of the stage temporal parameters and the number of bubbles and tokens. In [HAM 08] a behavioral model of asynchronous ring is proposed. The proposed behavioral model offers interesting prospects regarding timing information. It needs to calculate the half separation time between inputs *s*. To do so, it uses state graph

to iteratively catch the timing evolution inside the ring. That seems a bit complex if the goal is only estimating the oscillation frequency. Consequently, it seems very useful to find a simple relation between *s* and the number of bubbles and tokens. In [FAI 04], the authors give a relation between the period, the stage delay and the separation time. In this model the Drafting effect can be neglected because its effect is very small compared to the Charlie effect in the period calculation. With our terminology we can express this relation as:

$$T = 4 \times D + 4 \times |s| = 4 \times (D + |s|) = 4 \times Charlie(s)$$

(3.3)

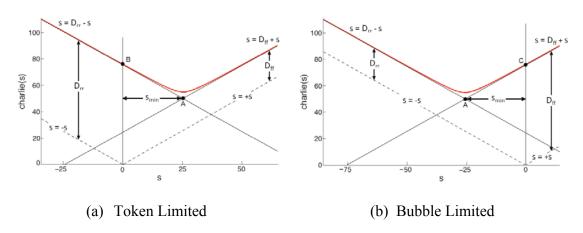

Where D = Charlie(s) - |s| is the stage delay from the last arriving input (i.e.  $D_{ff}$  in Figure 3.5). The period of the self-timed ring oscillators depends on the ratio  $R = {}^{N_T}/{N_B}$ . For the same ratio, we have the same oscillation whatever the number of stages. This is why we think that there is a direct relation between s and R. To estimate s we can use the Charlie diagram at constant s shown in Figure 3.6 at two different operating conditions. First, when the operating point of the asynchronous self-timed ring is in the *token limited* region, where  ${}^{N_T}/{N_B} \ge {}^{D_{ff}}/{D_{rr}}$  i.e.  $s \le s_{min}$ . Second, when the operating point of the asynchronous self-timed ring is in the *bubble limited* region where  ${}^{N_T}/{N_B} \le {}^{D_{ff}}/{D_{rr}}$  i.e.  $s \ge s_{min}$ , the two operating conditions are shown in Figure 3.10.

**Figure 3.10**: Charlie Diagram at Constant y for two Different Operating Conditions.

At point "A" shown in Figure 3.10 (a) the ring is oscillating at its maximum frequency, [WIN 01]:

$$R = N_T/N_B = D_{ff}/D_{rr}$$

and  $s = s_{min} = (D_{rr} - D_{ff})/2$  Lemma 1

At points B and C shown in Figures 3.10 (a) and (b) respectively:

$$s = 0 \rightarrow R = 1$$

Lemma 2

Lines (A-B) and (A-C) are applied when  ${}^{N_T}/N_B \ge {}^{D_{ff}}/N_T$  and  ${}^{N_T}/N_B \le {}^{D_{ff}}/N_T$  respectively. From *Lemma 1* and by dividing *s* by  $D_{rr}$ :

$$\frac{2s}{D_{rr}} = \frac{D_{rr} - D_{ff}}{D_{rr}} \qquad \Rightarrow \qquad s = \frac{D_{rr}}{2} (1 - R) \tag{3.4}$$

If we prove that Equation 3.4 is correct for point B then we can assume that it is correct for the line (A-B). At point B, s = 0 and from Lemma 2, R = 1. Substituting R = 1 into Equation 3.4, results in s = 0 which is correct. This means that Equation 3.4 is correct for the line (A-B). This could be mathematically formulated as:

If

$$R = \frac{N_T}{N_R} \ge \frac{D_{ff}}{D_{rr}} \qquad \text{then} \quad s = \frac{D_{rr}}{2} (1 - R)$$

(3.5a)

By the same way, from Lemma 1 and by dividing s by  $D_{ff}$ , we can prove that:

If

$$R = \frac{N_T}{N_B} \le \frac{D_{ff}}{D_{rr}}$$

then  $s = \frac{D_{ff}}{2} (\frac{1}{R} - 1)$  (3.5b)

These equations allow us to calculate s without going through the behavioral model. Therefore, we can introduce a new function called Charlie(R), which expresses the value of the function of Charlie according to the ratio R. This equation can be obtained by replacing s, from Equation 3.5, into Equation 3.1. The result is shown in Equation 3.6.

If

$$R = \frac{N_T}{N_B} \ge \frac{D_{ff}}{D_{rr}}$$

then

Charlie (R) =

$$\frac{D_{rr} + D_{ff}}{2} + \sqrt{\left(D_{Charlie}^2 + \left(\frac{D_{rr}}{2}\left(R - \frac{D_{ff}}{D_{rr}}\right)\right)^2\right)}$$

(3.6a)

If

$$R = \frac{N_T}{N_R} \le \frac{D_{ff}}{D_{rr}}$$

then

Charlie (R) =

$$\frac{D_{rr} + D_{ff}}{2} + \sqrt{\left(D_{Charlie}^2 + \left(\frac{D_{ff}}{2}\left(\frac{1}{R} - \frac{D_{rr}}{D_{ff}}\right)\right)^2\right)}$$

(3.6b)

To show the accuracy of Equation 3.6, we compared the Charlie values extracted from the VHDL simulation which is based on *Charlie* (s) Equation 3.1. These values are plotted against the corresponding R in Figure 3.11. The same curve is plotted using *Charlie*(R), Equation 3.6. The figure shows that the two plots are identical with an error which is less than 1%.

**Figure 3.11**: *Charlie (R)* against *Charlie (s)* Diagrams with respect to *R*.

The importance of this Charlie(R) diagram is that it allows us to have a clear idea about the oscillation period with respect to  $R = N_T / N_B$ . For designers it is easier, even obvious to interpret the Charlie diagram with the R parameter than the Charlie diagram with the s parameter. In case of the burst mode, s is not the same for all stages and s which is computed by Equation 3.5 is the average value. Equation 3.7 shows how the oscillation period can be calculated using Charlie(R).

$$T = 4 \times Charlie(R) \tag{3.7}$$

If we neglect Charlie effect in Equation 3.6, and by substituting the result in Equation 3.7:

If

$$R = \frac{N_T}{N_B} \ge \frac{D_{ff}}{D_{rr}}$$

then  $T = 2 \times D_{rr}(R+1)$  (3.8a)

If

$$R = \frac{N_T}{N_R} \le \frac{D_{ff}}{D_{rr}}$$

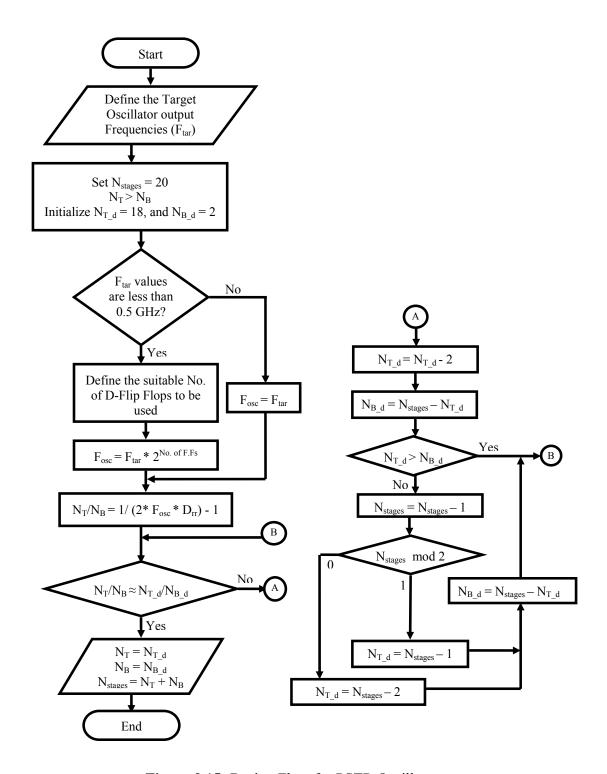

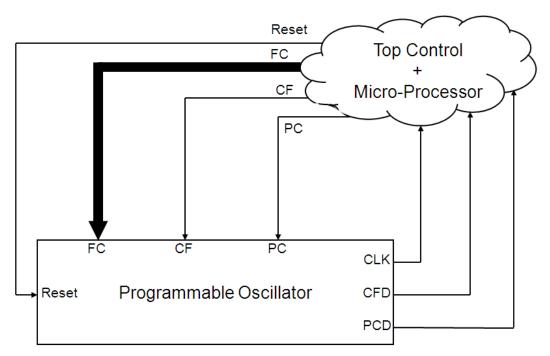

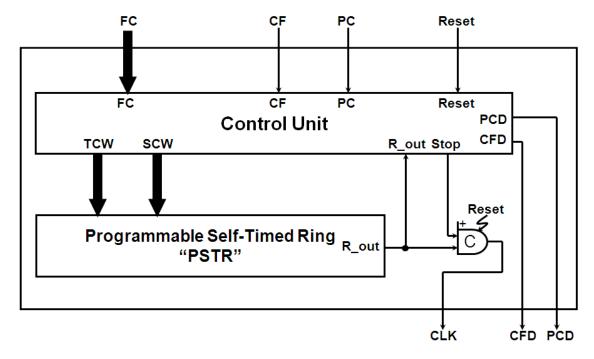

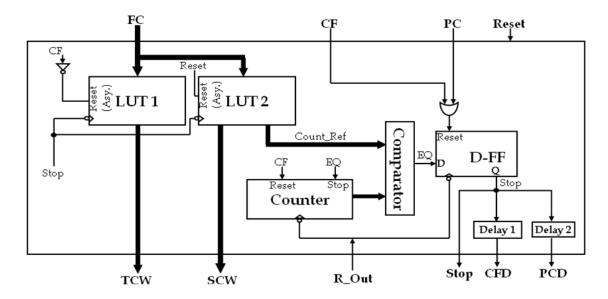

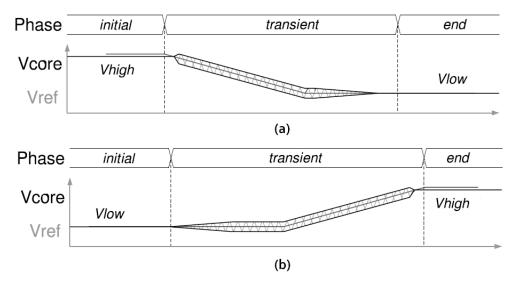

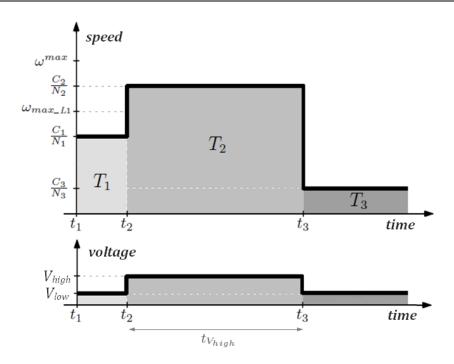

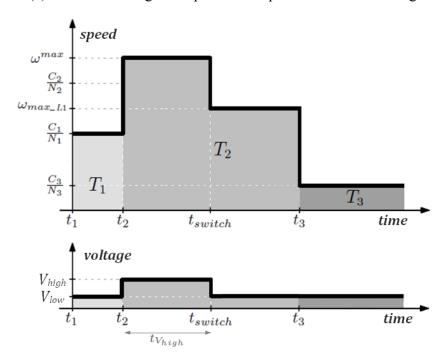

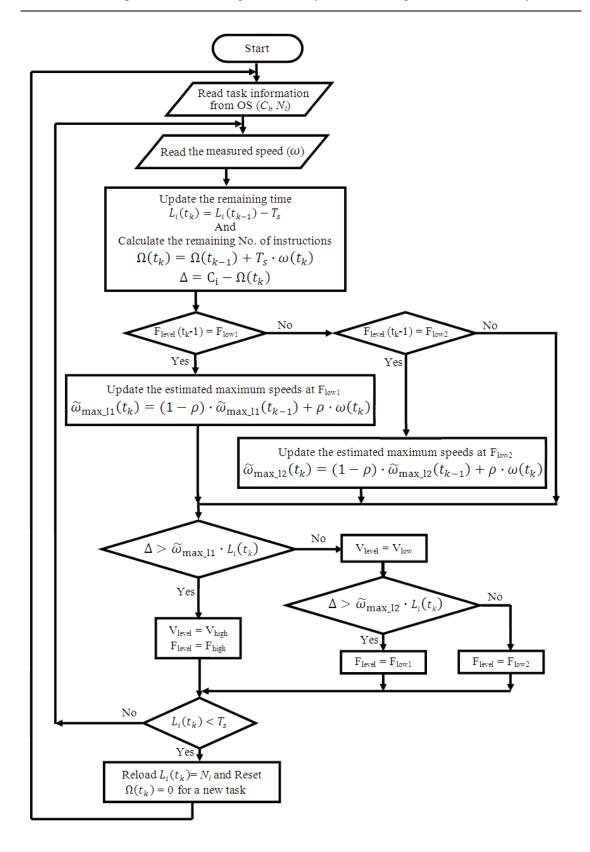

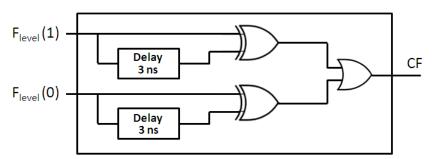

then  $T = 2 \times D_{ff} \left(\frac{1}{R} + 1\right)$  (3.8b)