### Commande faible coût pour une réduction de la consommation d'énergie dans les systèmes électroniques embarqués

Sylvain Durand

#### ▶ To cite this version:

Sylvain Durand. Commande faible coût pour une réduction de la consommation d'énergie dans les systèmes électroniques embarqués. Autre. Université de Grenoble, 2011. Français. NNT: 2011 GRENT006. tel-00586620v2

#### HAL Id: tel-00586620 https://theses.hal.science/tel-00586620v2

Submitted on 20 Mar 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### PhD Thesis

# REDUCTION OF THE ENERGY CONSUMPTION IN EMBEDDED ELECTRONIC DEVICES WITH LOW CONTROL COMPUTATIONAL COST

#### UNIVERSITÉ DE GRENOBLE

#### **THÈSE**

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Automatique et Productique

Arrêté ministérial: 7 août 2006

Présentée par

#### Sylvain DURAND

Thèse dirigée par Nicolas MARCHAND et Daniel SIMON

préparée au sein du centre de recherche INRIA Grenoble Rhône-Alpes, du laboratoire GIPSA-Lab, département automatique et de l'école doctorale Électronique, Électrotechnique, Automatique et Traitement du Signal

# Reduction of the energy consumption in embedded electronic devices with low control computational cost

Thèse soutenue publiquement le **17 janvier 2011**, devant le jury composé de :

Mazen ALAMIR, Président

Directeur de Recherche CNRS, GIPSA-Lab (Grenoble, France)

Patrick BOUCHER, Rapporteur

Professeur des Universités, Supélec (Paris, France)

Maurice HEEMELS, Rapporteur

Professor, Eindhoven University of Technology (Eindhoven, Pays-Bas)

Arben CELA, Examinateur

Maître de Conférences, ESIEE (Paris, France)

Jose-Fermi GUERRERO-CASTELLANOS, Examinateur

Profesor Investigador, BUAP (Puebla, Mexique)

Suzanne LESECQ, Examinatrice

Ingénieure de Recherche, CEA-Leti (Grenoble, France)

Laurent FESQUET, Invité

Maître de Conférences, TIMA (Grenoble, France)

Daniel SIMON, Directeur de thèse

Chargé de Recherche INRIA, INRIA Rhône-Alpes (Grenoble, France)

Nicolas MARCHAND, Co-Directeur de thèse

Chargé de Recherche CNRS, GIPSA-Lab (Grenoble, France)

à Cécile.

### Aknowledgments

This thesis arose in part of research that has been done within the NECS group in the INRIA RHÔNE-ALPES research center and the control department of the GIPSA-LAB, in Grenoble. This experience would not have been possible without the support of many people. This page is dedicated to them.

First of all, I greatly indebted my two supervisors, Nicolas Marchand and Daniel Simon, for the confidence they accorded to me. Their encouraging and personal guidance have provided a good background for the present thesis.

I am also grateful to the jury members for the precious time they have spent for me. Thanks to Prof. Mazen Alamir, for the interest he gave to this work by agreeing to be the president of my jury. I am also thankful to the reviewers, Prof. Maurice Heemels and Prof. Patrick Boucher. Their constructive suggestions on the thesis are really appreciated for me. My thanks also go to Dr. Arben Cela for his commitment to take part in my jury.

Many thanks to Dr. Laurent Fesquet for his wide contribution in my research works, for his patience when explaining the micro-electronics aspects or the asynchronous paradigm, and his understanding on the control issues. I also thank him for accepting the invitation to be in my jury committee. Furthermore, I wish to extend my thanks to all those who have helped me in the ARAVIS project. In particular Hatem and Anne-Marie who contribute in merging my work in a low and high level respectively. I do not forget the numerous WP2 meetings too, with Carolina, Carlos, Yvain, Sylvain, Fabien, and all other people from TIMA, CEA-LETI, INRIA and STMICROELECTRONICS. I also thank Brigitte from the LJK for her collaboration in the TATIE project.

I would like to express my deep regards to Dr. J-Fermi Guerrero Castellanos. I will not forget how I was well received during "mi estancia en Puebla", his availability at the university to discuss on valuable ideas and his friendly attitude the weekend to visit his beautiful country. Thanks also for agreeing to deem my work and for his courage when being present in my jury committee in video conference at three in the morning in Mexico. I do not forget his family too, especially his father Prof. Willy and his wife Esmeralda. I also thank Jonathan and the other Mexican students for their attempt to get my Spanish. Eventually, my special thanks to Betsa and her family for their warm welcome in Pachuca and their friendship.

I wish to thank Prof. Suzanne Lesecq for giving me the opportunity of a post-doc in order to test my control strategies on a practical nanometric SoC. I am grateful for her acceptance to take part in my jury committee too.

During this period, I have worked with many other colleagues for whom I have great regard and I wish to extend my warmest thanks to all those who have helped me from a professional and personal point of view. Especially to Luc for our great discussions, Émilie, Gabriel, Lara, Nicolas, Valentina, Alexandre, Alain, Kateřina, Florine, Federica, Jonathan, Riccardo, Wenjuan and other people from the NECS team, Antoine, Lizeth, Charles, Corentin, Irfan and others from the GIPSA-LAB.

I am also thankful to the secretaries, librarians and any administrative and technical support, in particular Élodie, Myriam and Florence in INRIA, Marie-Thérèse, Patricia, Virginie and Olivier in GIPSA-LAB, for helping and assisting me in many different ways.

My special thanks to my family and friends who support me through difficult period and for providing to me their friendship, entertainment and attention. In particular, I would like to thank Sébastien and Cyril who encouraged me in this direction. I also thank my brother Nicolas for accommodating me when I had a party in Grenoble. Finally, I wish to thank Cécile, Patricia, Denise and Suzanne who hand-made the "pot de thèse" which was perfect.

Lastly, my deep lovely thanks go to my wife Cécile for her emotional supports and her continual and confident encouragement. I dedicate this work to her.

| $\mathbf{T}_{A}$ | ΓABLE OF CONTENTS                                                                                     | 9      |

|------------------|-------------------------------------------------------------------------------------------------------|--------|

| St               | SUMMARY OF THE THESIS (IN FRENCH)                                                                     | 15     |

| $\mathbf{A}$     | A Problématiques de recherche                                                                         | 17     |

| В                | B Gestion du compromis énergie performance                                                            | 19     |

|                  | B.1 Context et motivations                                                                            | 19     |

|                  | B.2 Le système monocœur                                                                               | 20     |

|                  | ${\bf B.2.1}  {\bf Commande \ intuitive \ de \ la \ fréquence \ et \ du \ niveau \ de \ tension \ .}$ |        |

|                  | B.2.2 Commande de la vitesse de calcul                                                                |        |

|                  | B.2.3 Commande complètement discrète                                                                  |        |

|                  | B.3 Le système multicœur                                                                              |        |

|                  | B.4 Résultats de simulation                                                                           | 25     |

| $\mathbf{C}$     | C Commande déclenchée par événements                                                                  | 27     |

|                  | C.1 Context et motivations                                                                            | 27     |

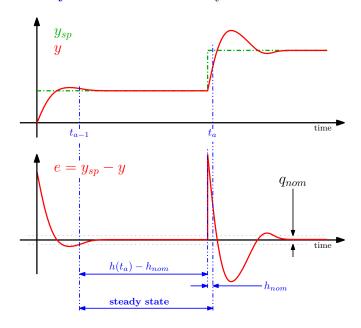

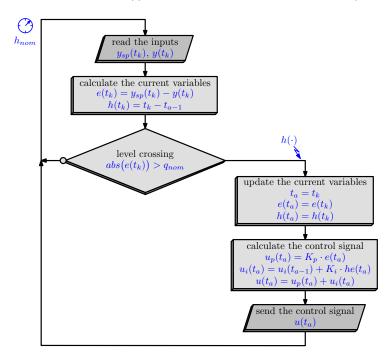

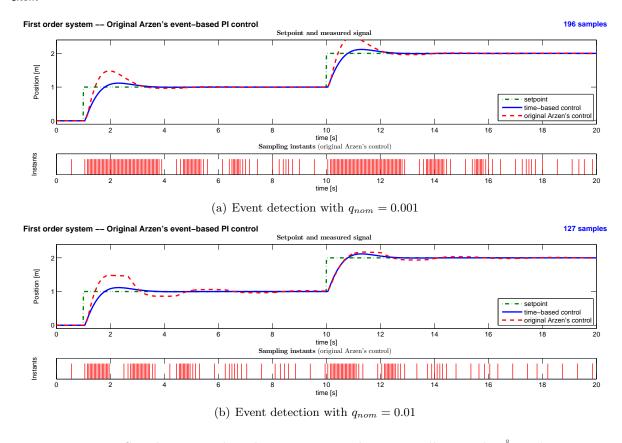

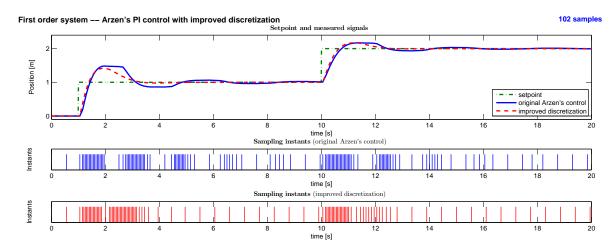

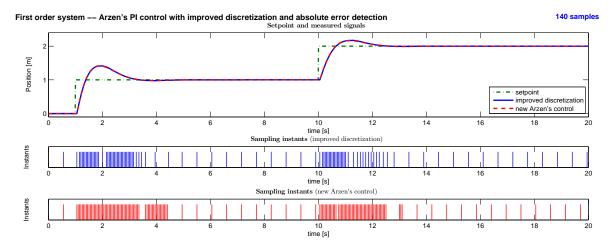

|                  | C.2 Commande PID et détection d'événement par franchissement de nivea                                 | u 28   |

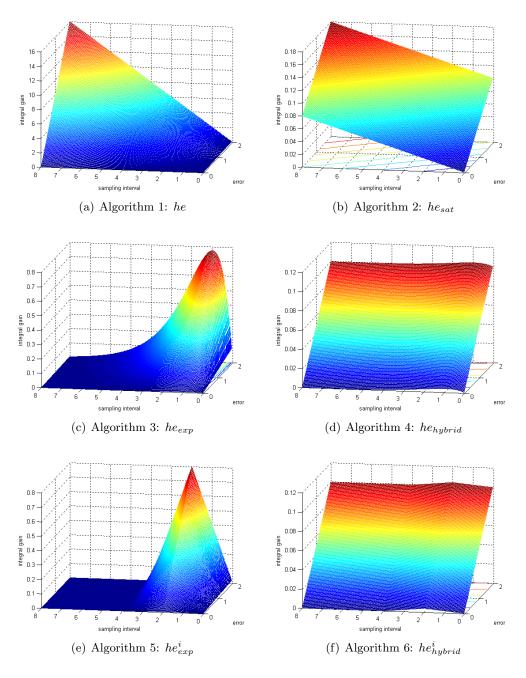

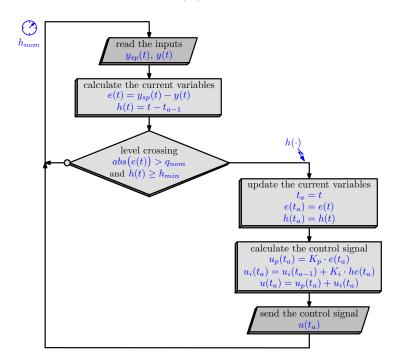

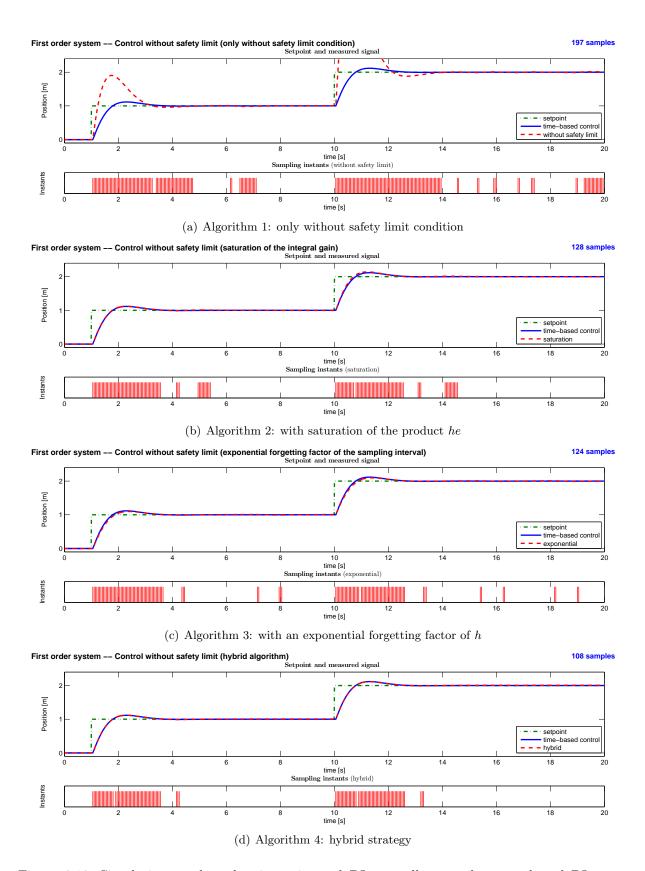

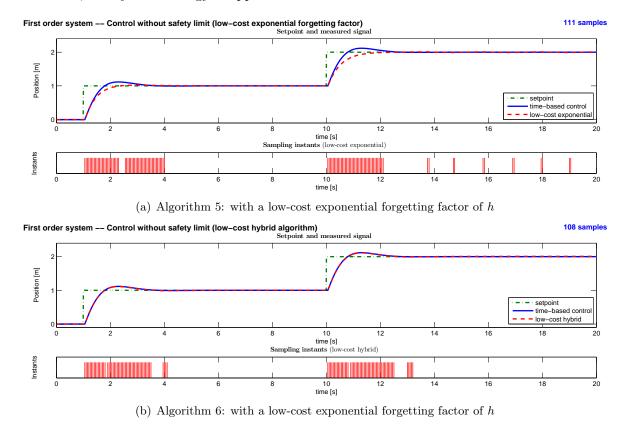

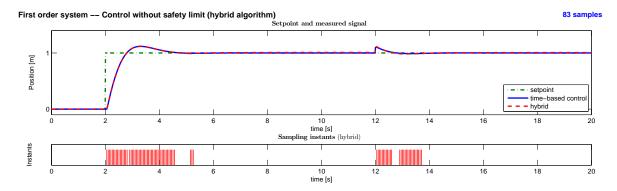

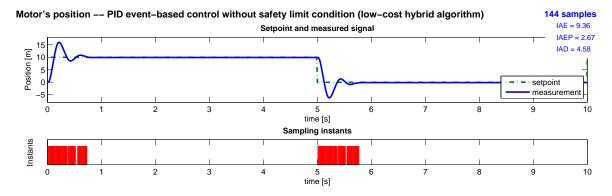

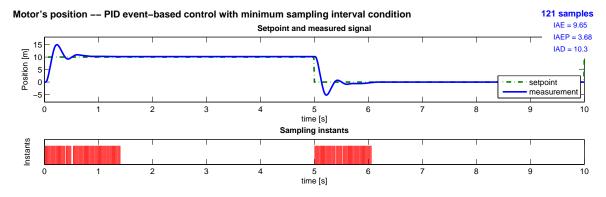

|                  | C.2.1 Commande sans limite de sécurité                                                                | 29     |

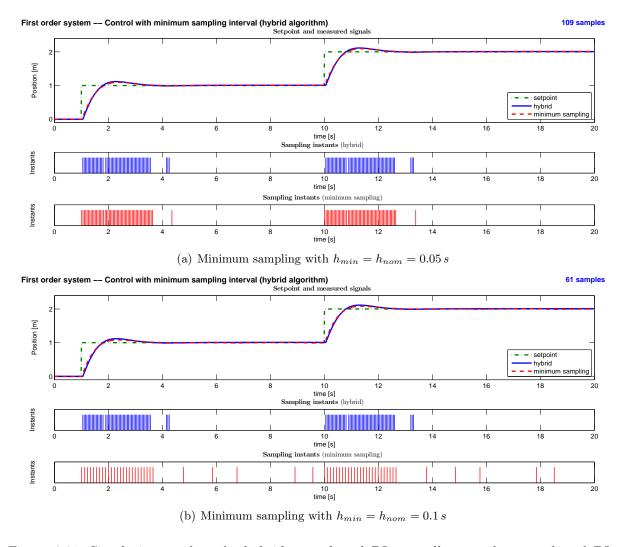

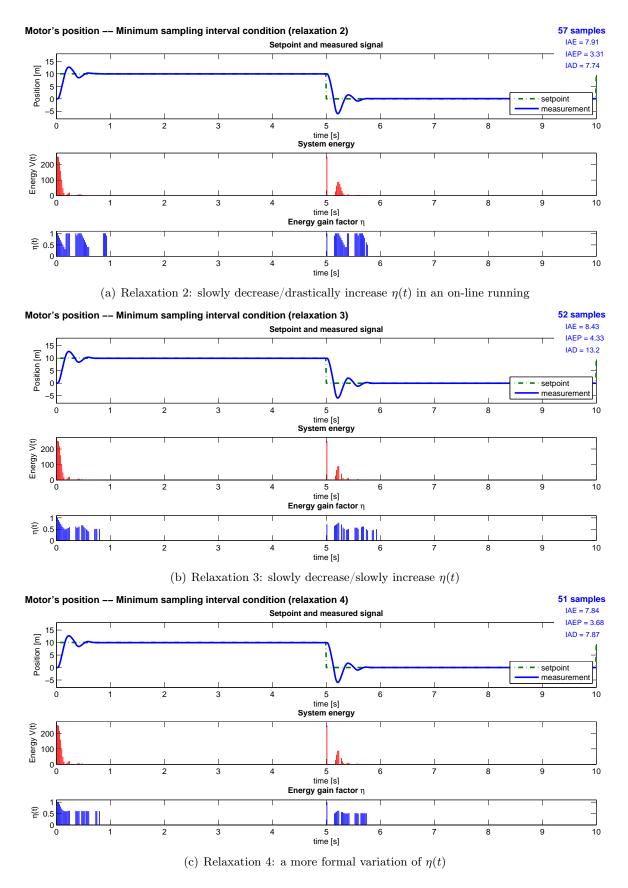

|                  | C.2.2 Commande avec condition d'échantillonnage minimum                                               | 30     |

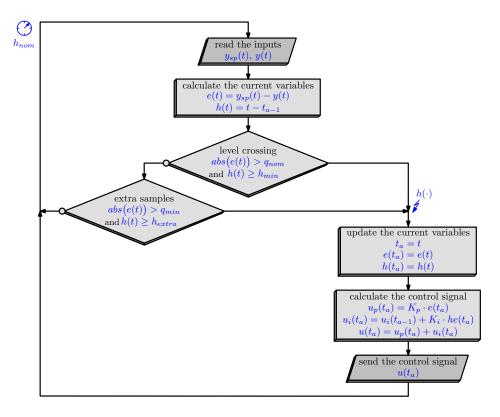

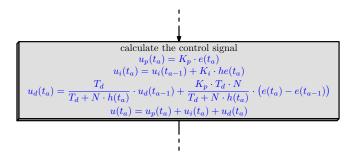

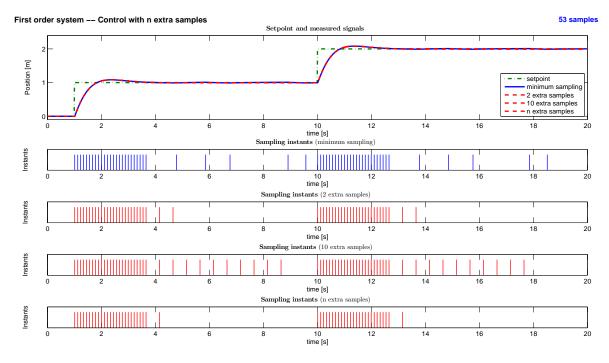

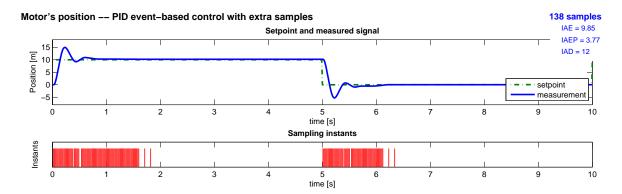

|                  | C.2.3 Commande avec échantillons supplémentaires                                                      | 31     |

|                  | C.2.4 Résultats de simulation                                                                         | 31     |

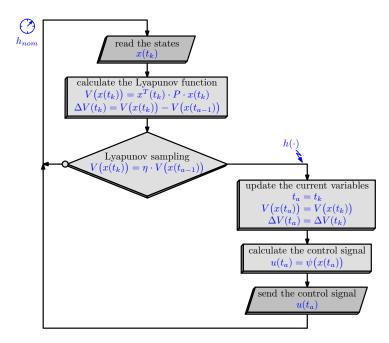

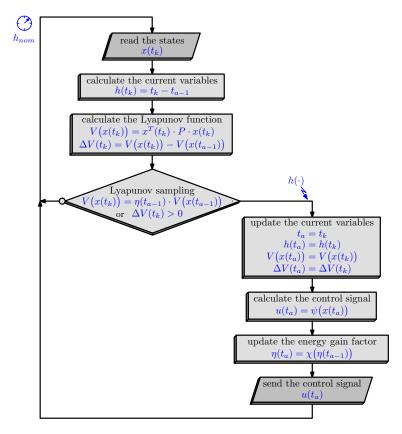

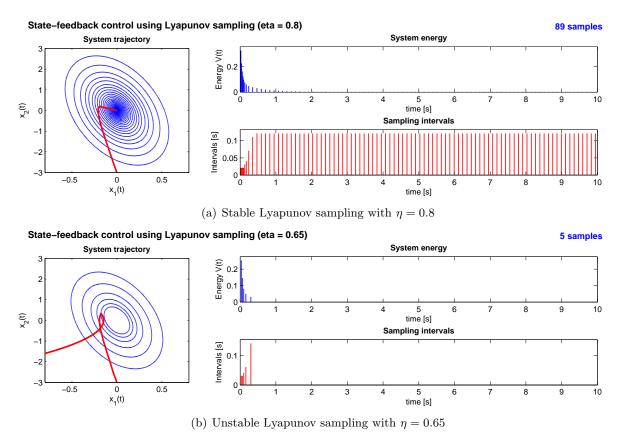

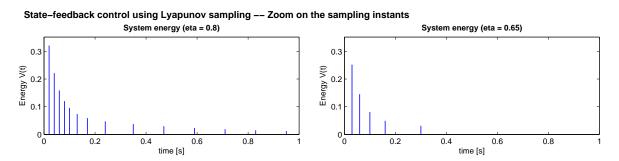

|                  | C.3 Retour d'état et échantillonnage déclenché par une fonction de Lyapur                             | nov 31 |

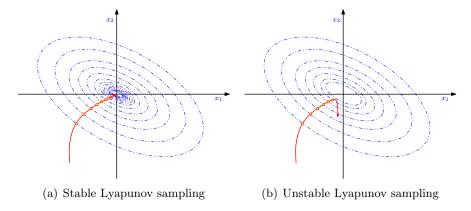

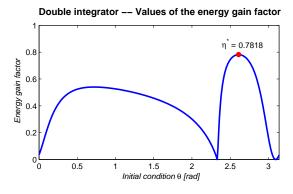

|                  | C.3.1 Échantillonnage déclenché sur fonction de Lyapunov                                              | 31     |

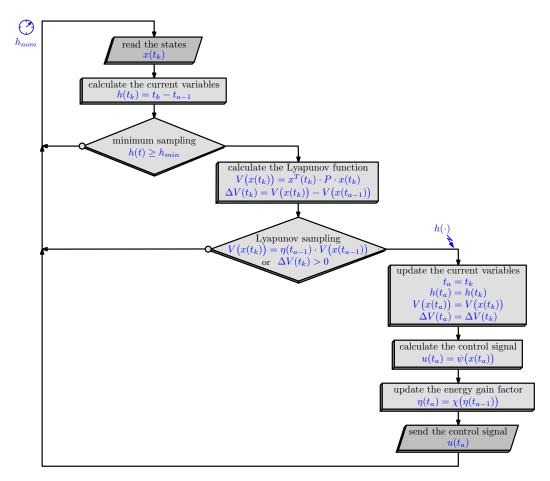

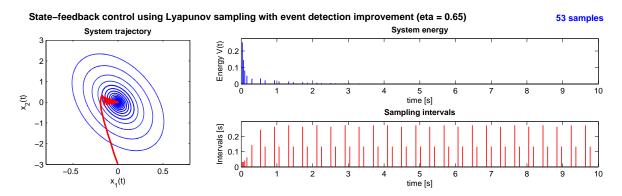

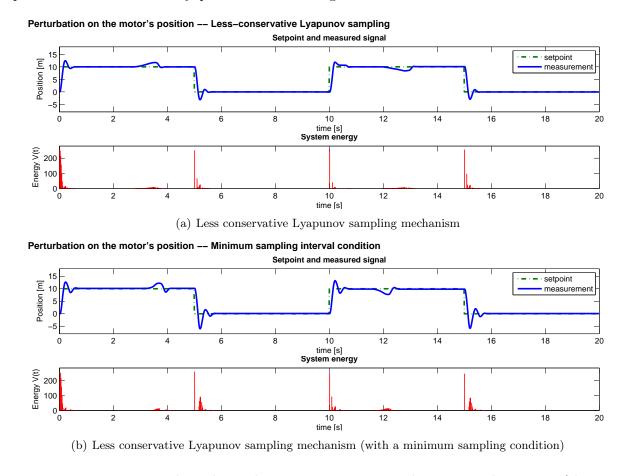

|                  | C.3.2 Simplification du mécanisme d'échantillonnage                                                   | 32     |

|                  | C.3.3 Commande avec condition d'échantillonnage minimum                                               | 33     |

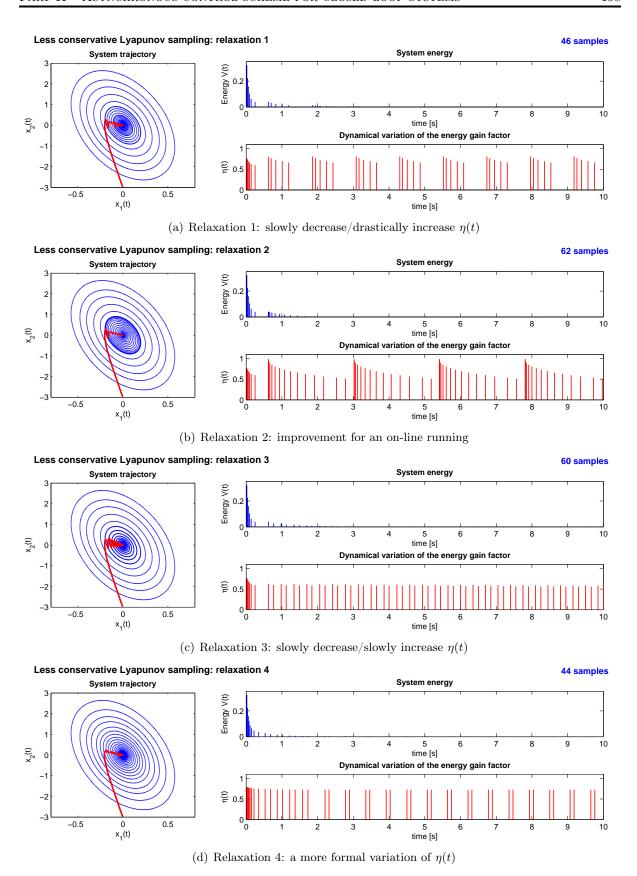

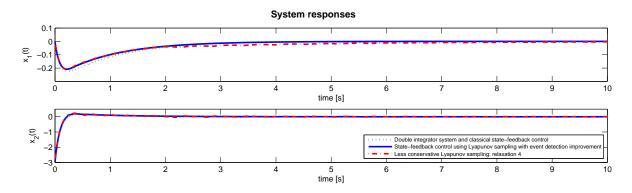

|                  | C.3.4 Résultats de simulation                                                                         | 33     |

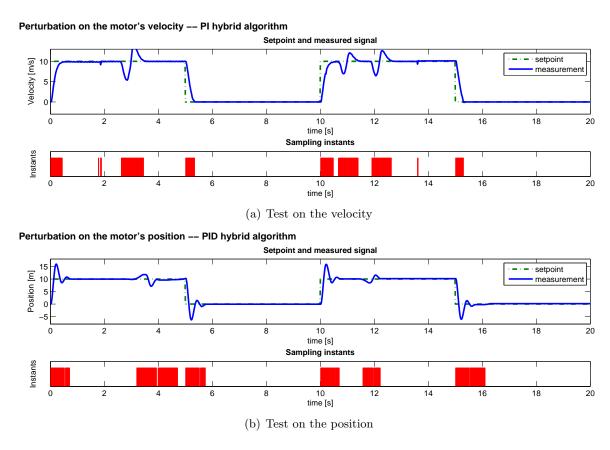

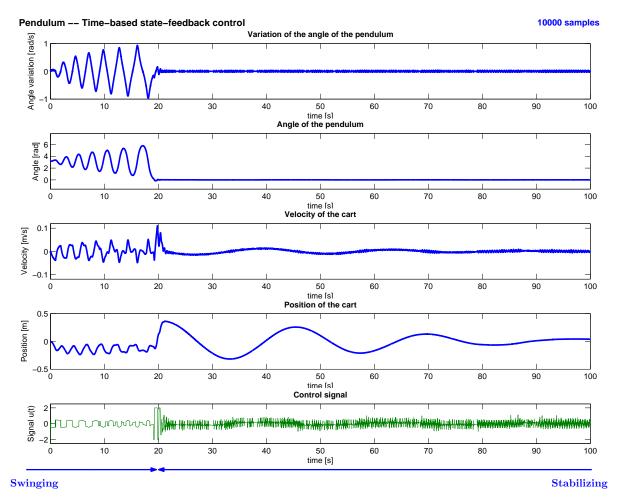

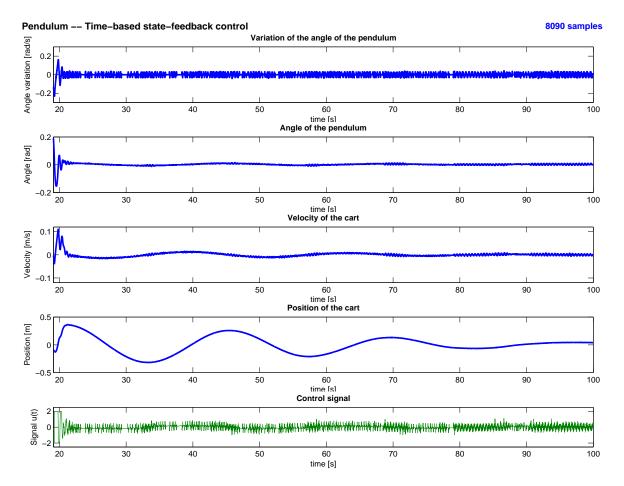

|                  | C.4 Résultats expérimentaux                                                                           | 33     |

| $\mathbf{G}$     | GENERAL INTRODUCTION                                                                                  | 35     |

| _                | Research problematic and proposed solutions                                                           | 37     |

|                  | Structure of the thesis                                                                               |        |

|                  |                                                                                                       |        |

|                  | Part I<br>Energy-performance tradeoff in electronic systems                                           | 43     |

| 1                | Context and motivations                                                                               | 45     |

| _                | 1.1 Micro and nano-electronics                                                                        |        |

|                  | 1.2 Problems in nanometric technologies                                                               |        |

|                  | 1.3 Suggested solutions                                                                               |        |

|                  | 1.3.1 Power management techniques                                                                     |        |

|                  | 1.3.2 Focus on the energy-performance tradeoff                                                        |        |

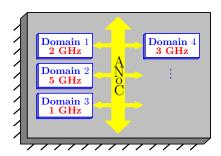

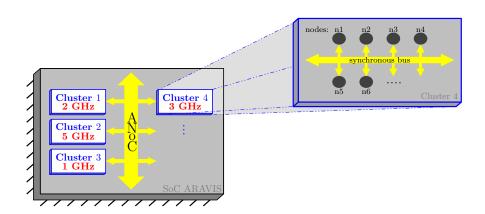

|                  | 1.3.3 Globally asynchronous locally synchronous paradigm                                              |        |

|                  | 1.4 Handling the process variability                                                                  |        |

|                  | 1.4.1 Essential feedback control loops in nanotechnologies                                            |        |

|                  | 1.4.2 Study case: The ARAVIS project                                                                  |        |

| 2 | Cor | ου 1 · · · · · · · · · · · · · · · · · ·                                         | 61        |

|---|-----|----------------------------------------------------------------------------------|-----------|

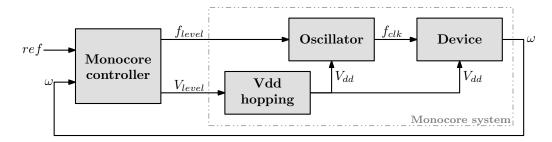

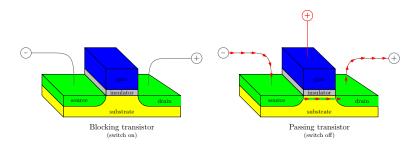

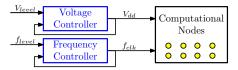

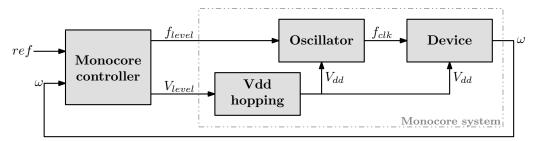

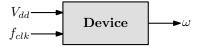

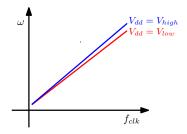

|   | 2.1 | A single voltage scalable device to control                                      | 62        |

|   |     | 2.1.1 The electronic device                                                      | 62        |

|   |     | 2.1.2 The actuators                                                              | 63        |

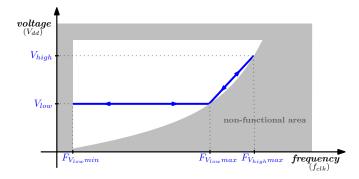

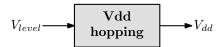

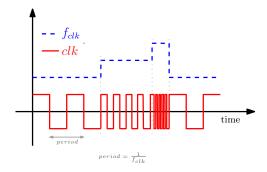

|   |     | 2.1.2.1 The Vdd-hopping to control the supply voltage                            | 64        |

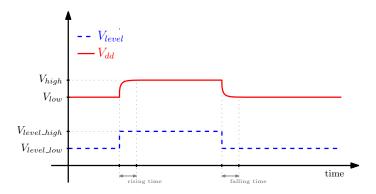

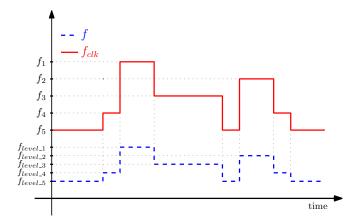

|   |     | 2.1.2.2 The oscillator to control the clock frequency                            | 65        |

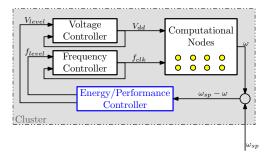

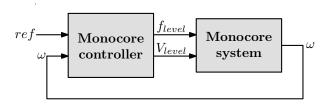

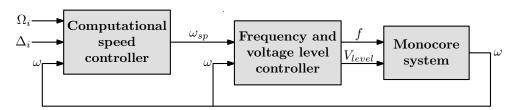

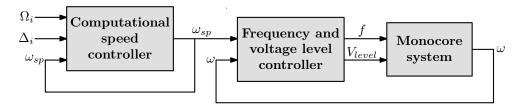

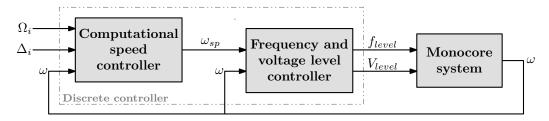

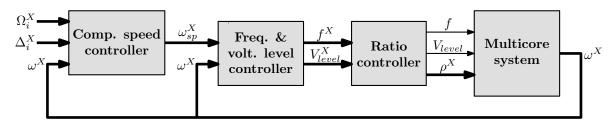

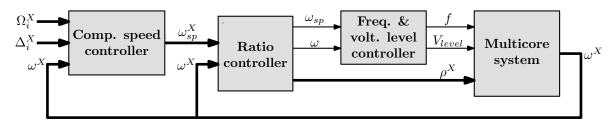

|   |     | 2.1.3 The monocore controller                                                    | 66        |

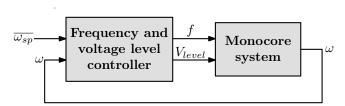

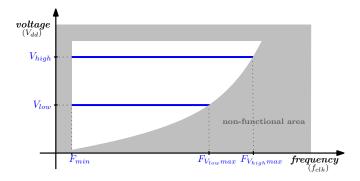

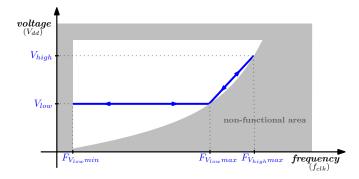

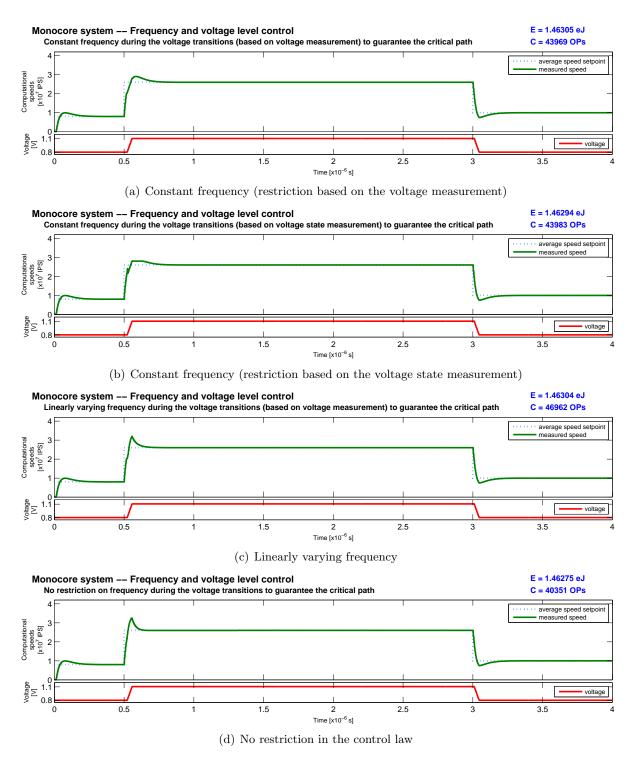

|   | 2.2 | Frequency and voltage level control                                              | 68        |

|   |     | 2.2.1 Frequency control                                                          | 68        |

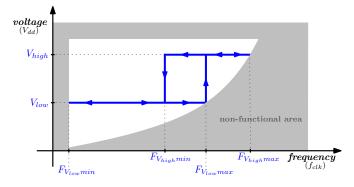

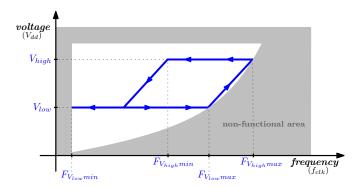

|   |     | 2.2.2 Voltage level control                                                      | 71        |

|   |     | 2.2.3 Guarantee of the maximum delay over the critical path                      | 73        |

|   |     | 2.2.3.1 Frequency restriction during the voltage transitions                     | 74        |

|   |     | 2.2.3.1 Voltage measurement for a maximum gain                                   | 74        |

|   |     | 2.2.3.3 Self-management from the oscillator                                      | 75        |

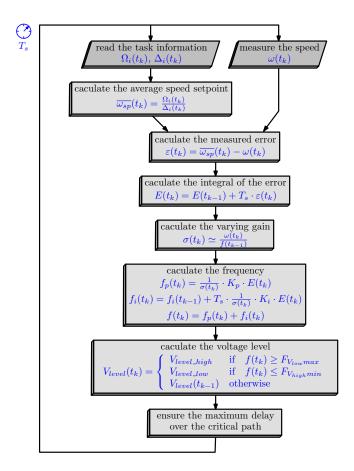

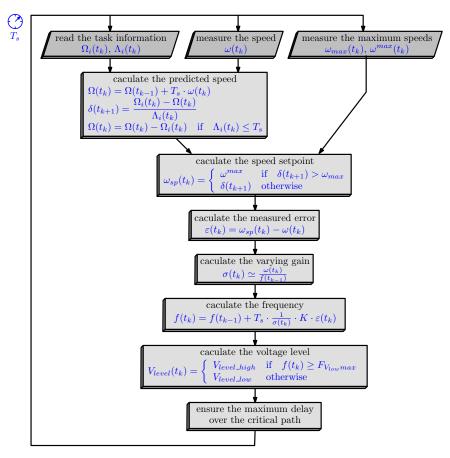

|   |     | 2.2.4 Control algorithm                                                          | 75        |

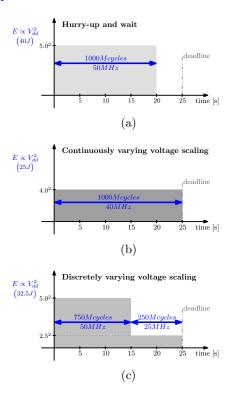

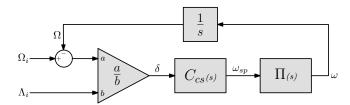

|   | 2.3 | 9                                                                                | 76        |

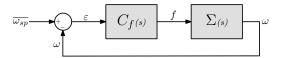

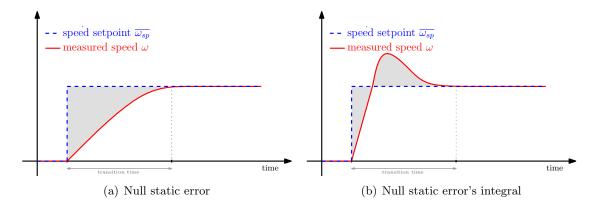

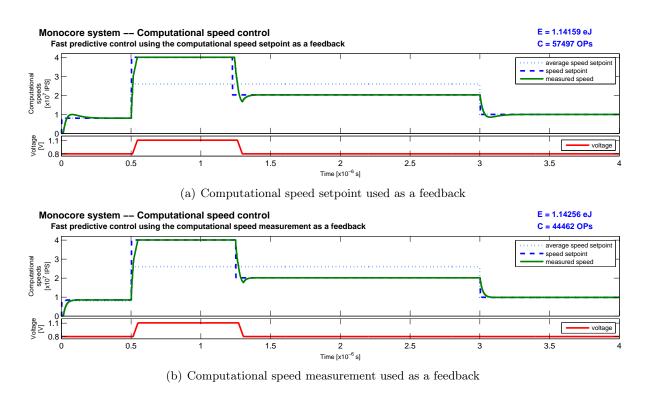

|   | 2.3 | Computational speed control                                                      |           |

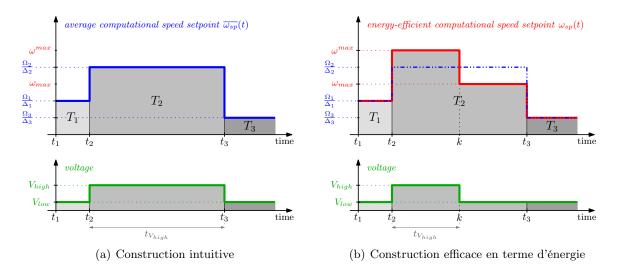

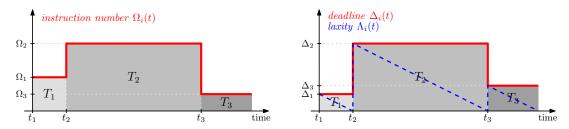

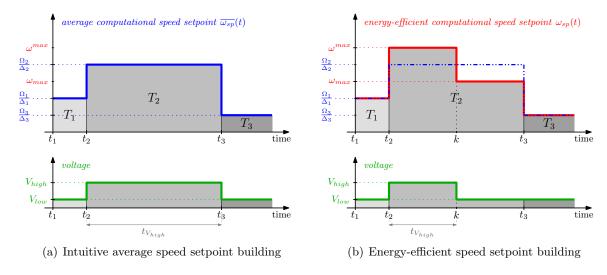

|   |     | 2.3.1 Computational speed setpoint building                                      | 77        |

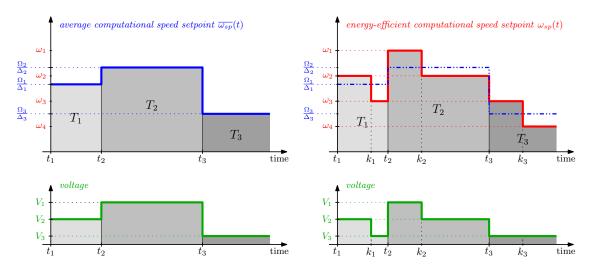

|   |     | 2.3.1.1 The intuitive average speed setpoint                                     | 78        |

|   |     | 2.3.1.2 A more energy-efficient reference                                        | 78        |

|   |     | 2.3.2 Fast predictive control using the measured speed as a feedback             | 79        |

|   |     | 2.3.3 Fast predictive control using the speed setpoint as a feedback             | 81        |

|   |     | 2.3.4 Measurement of the maximum computational speeds                            | 82        |

|   |     | 2.3.5 Frequency and voltage level controller for the new setpoints               | 82        |

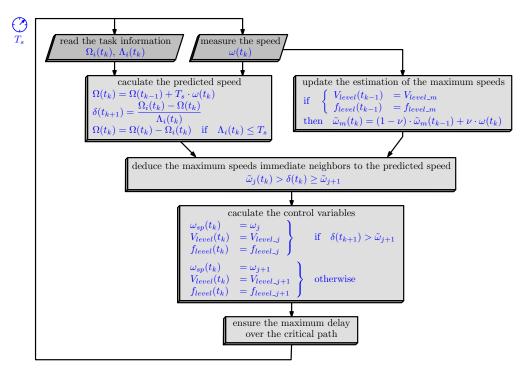

|   |     | 2.3.6 Control algorithm                                                          | 84        |

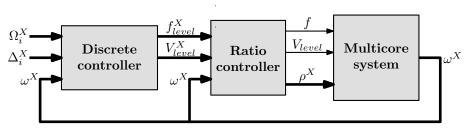

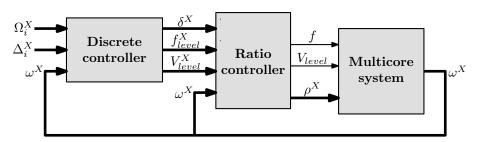

|   | 2.4 | Fully discrete control scheme                                                    | 85        |

|   |     | 2.4.1 Energy-efficient setpoint for a $M$ -voltage level mechanism $\dots \dots$ | 86        |

|   |     | 2.4.2 Extension of the fast predictive control                                   | 88        |

|   |     | 2.4.3 Clock-gating control                                                       | 89        |

|   |     | 2.4.4 Estimation of the maximum computational speeds                             | 90        |

|   |     | 2.4.5 Control algorithm                                                          | 91        |

|   | 2.5 | Simplification of the algorithms for a low control computational cost            | 92        |

|   | 2.6 | Intuitive stability analysis                                                     | 94        |

|   | 2.7 | Synthesis                                                                        | 94        |

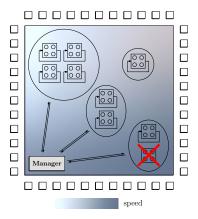

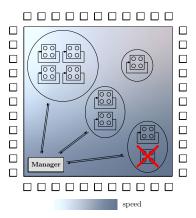

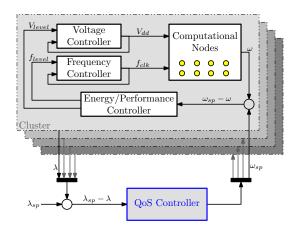

| 3 | Glo | obal control in multicore systems                                                | 97        |

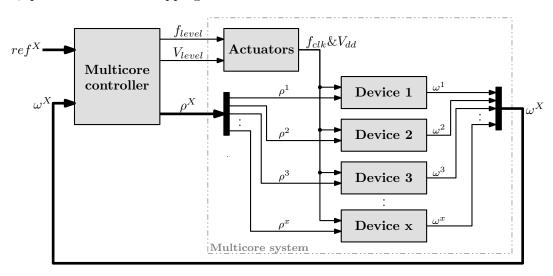

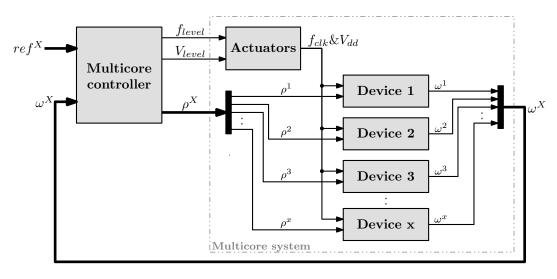

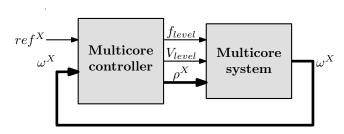

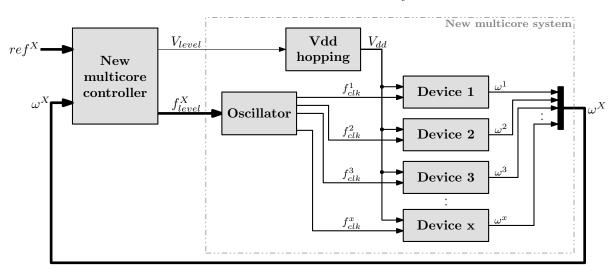

| U | 3.1 | Several chips working together in the same power domain                          | 98        |

|   | 0.1 | 3.1.1 A certain degree of freedom thanks to some frequency ratios                | 99        |

|   |     | 3.1.2 The multicore controller                                                   | 99        |

|   | 3.2 |                                                                                  | وو<br>00ا |

|   | 0.2 |                                                                                  | L00       |

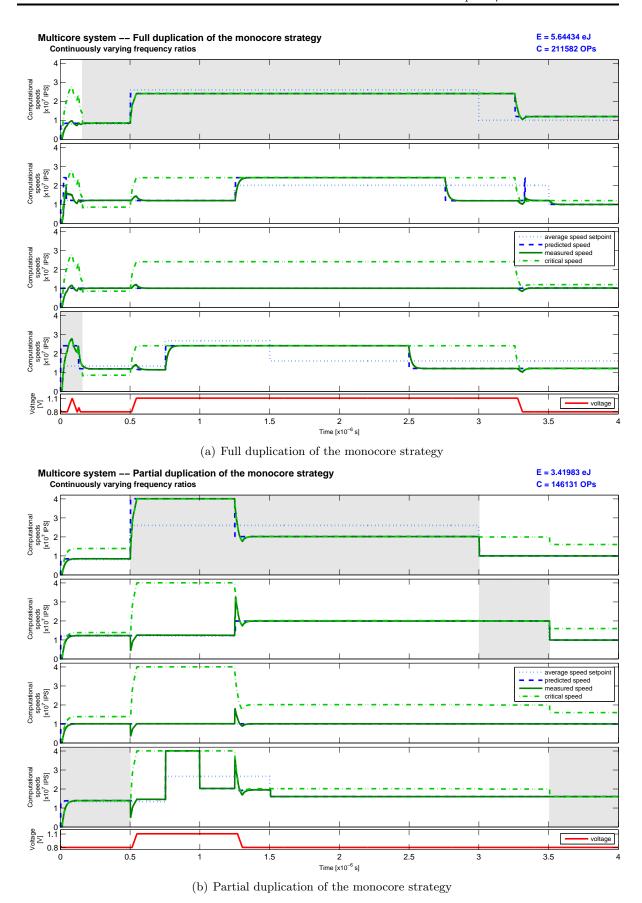

|   |     | 3.2.1 Pull duplication of the monocore control strategy                          |           |

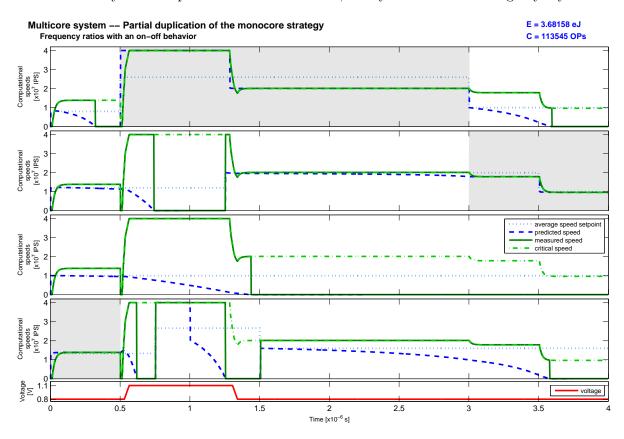

|   |     |                                                                                  |           |

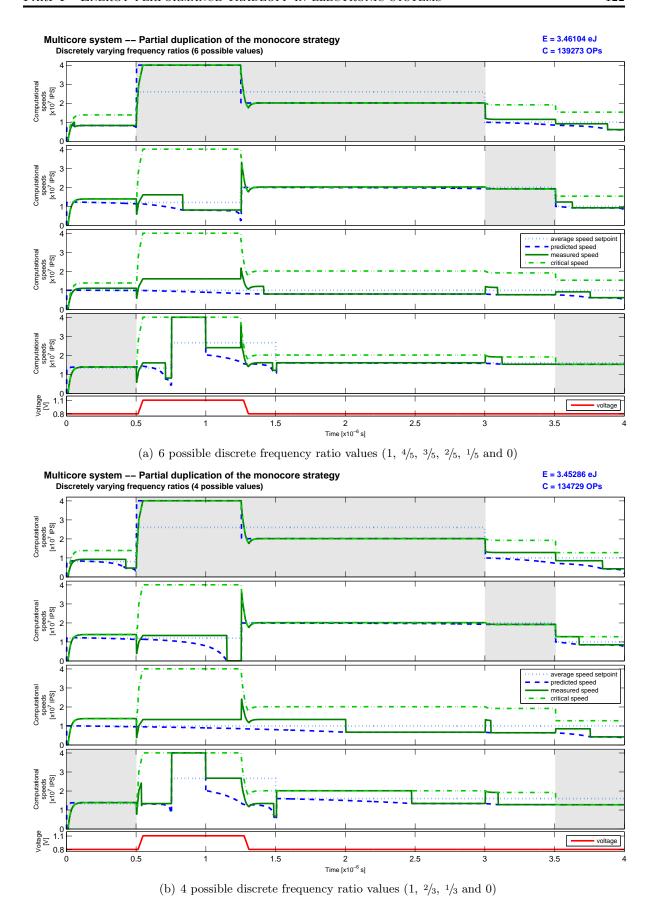

|   |     | 3.2.3 Discrete values of the frequency ratios                                    |           |

|   | 0.0 | 3.2.4 Fully discrete control scheme                                              |           |

|   | 3.3 | Several chips working with their own clock                                       |           |

|   | 3.4 | Synthesis                                                                        | .07       |

| 4 | Sim | nulation results 1                                                               | 09        |

|   | 4.1 | Presentations                                                                    | 110       |

|   |     | 4.1.1 Recap of the different control strategies                                  | 10        |

|   |     | 4.1.2 Controlled systems                                                         |           |

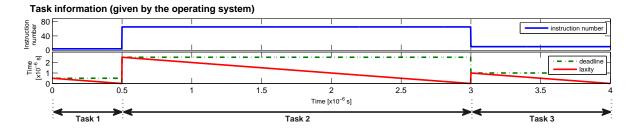

|   |                                               | 4.1.3 Test benches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                    |

|---|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

|   | 4.2                                           | 4.1.4 Indexes of performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                    |

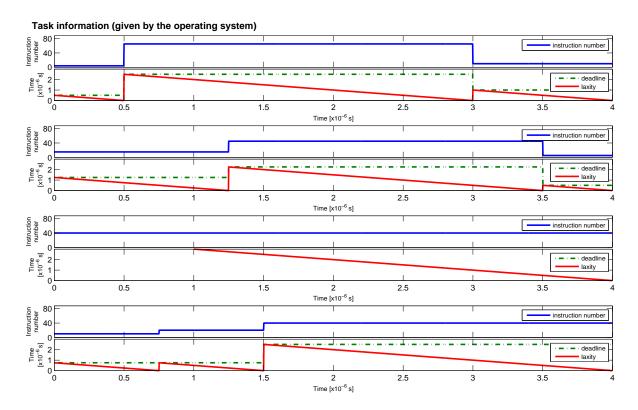

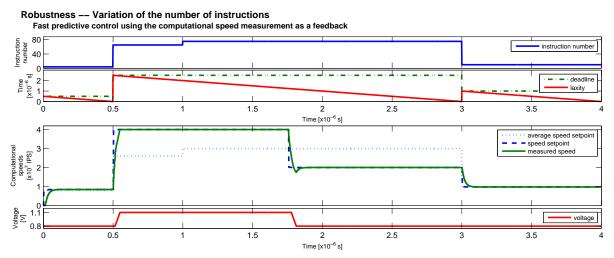

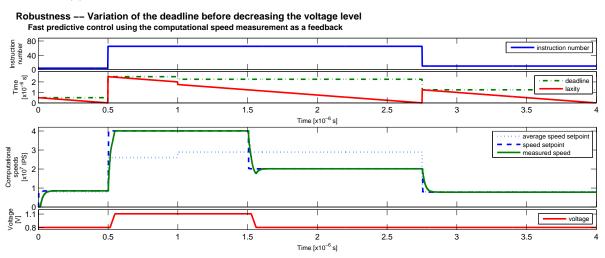

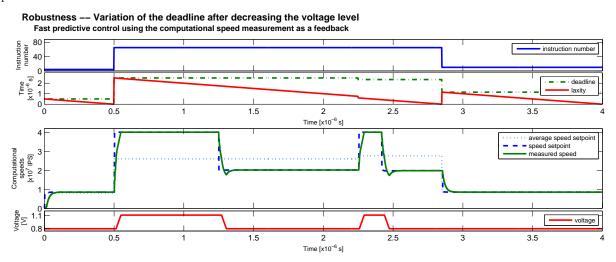

|   | 4.2                                           | Computational speed control to build a more energy-efficient setpoint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                    |

|   | 4.0                                           | 4.3.1 Fast predictive control law                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                    |

|   |                                               | 4.3.1 Past predictive control law                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                    |

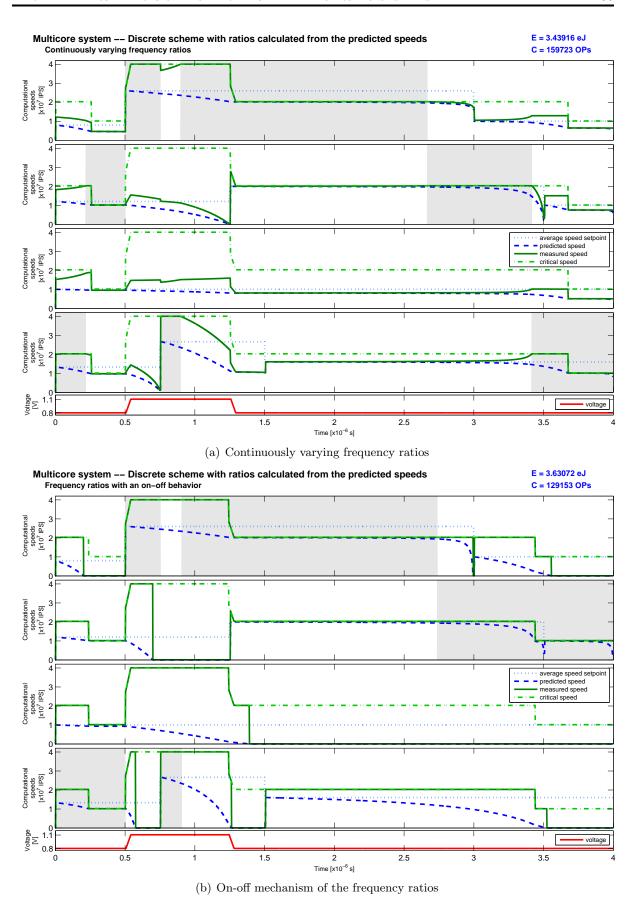

|   |                                               | 4.3.3 Duplication of the monocore strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                    |

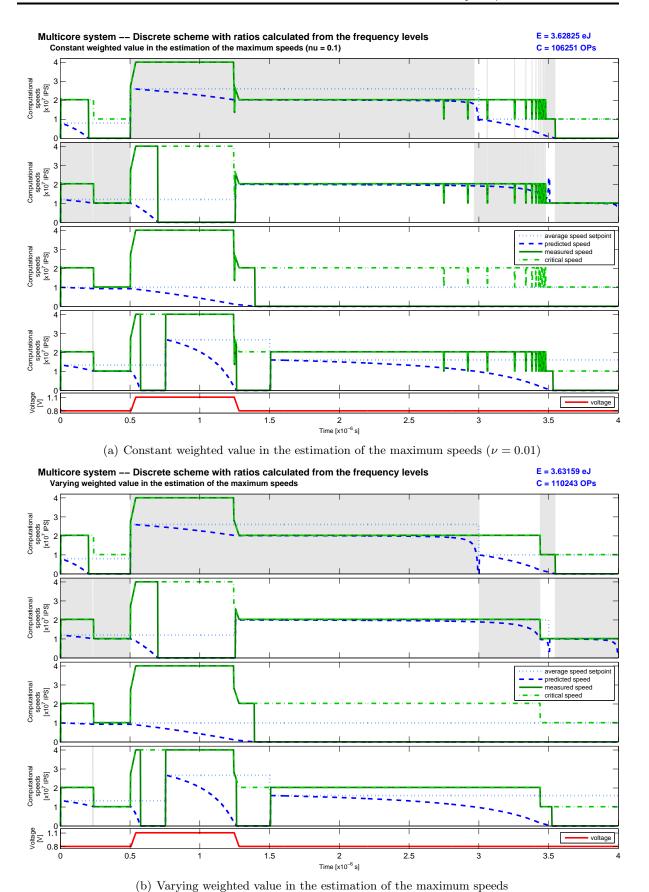

|   |                                               | 4.3.4 Discrete values of the frequency ratios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                    |

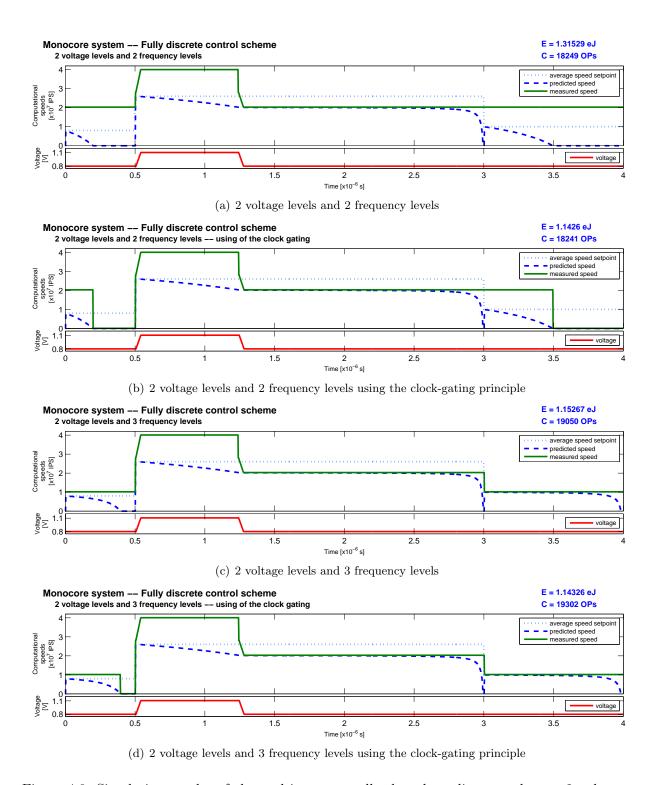

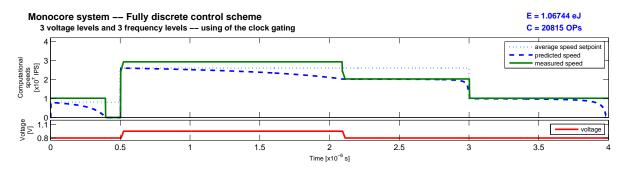

|   | 4.4                                           | Fully discrete control scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                    |

|   | 4.4                                           | 4.4.1 Results with small numbers of voltage and frequency levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                    |

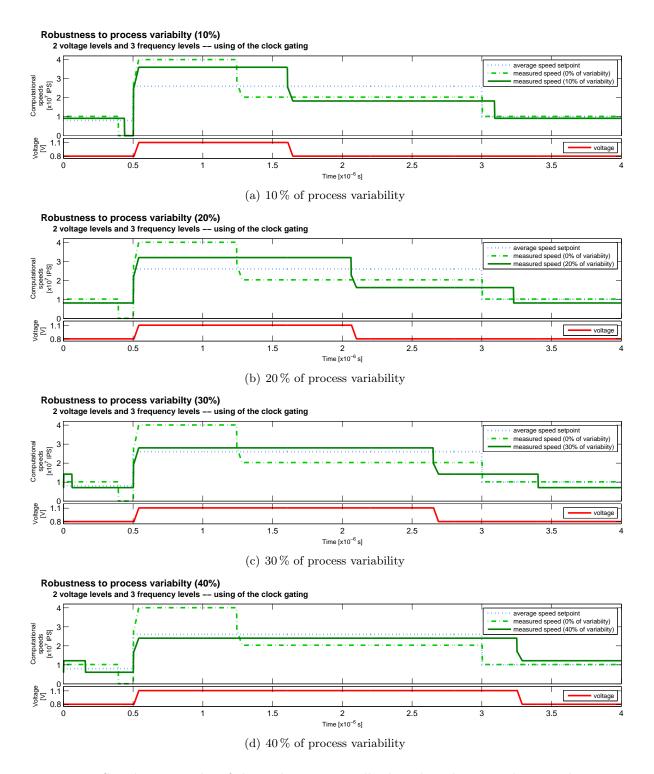

|   |                                               | 4.4.1 Results with small numbers of voltage and frequency levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                    |

|   |                                               | 4.4.2 Robustness to process variability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                    |

|   | 4.5                                           | Performance analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                    |

|   | 4.6                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                    |

|   | 4.0                                           | Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 132                                                                                                              |

|   | art I                                         | T<br>CHRONOUS CONTROL SCHEME FOR CLOSED-LOOP SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 135                                                                                                                |

|   |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                    |

| 5 |                                               | ntext and motivations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 137                                                                                                                |

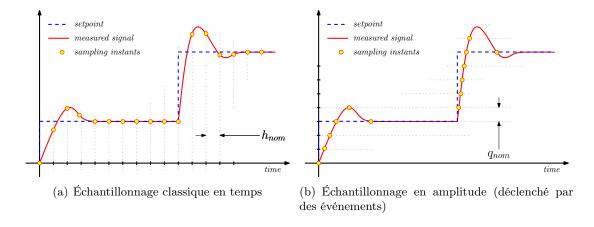

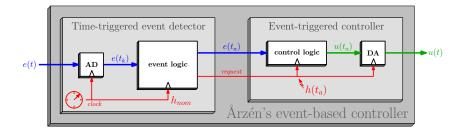

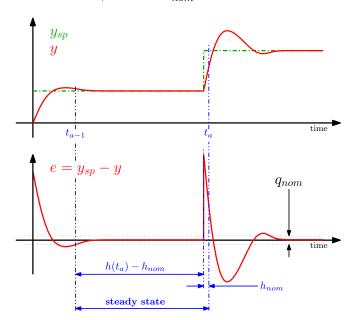

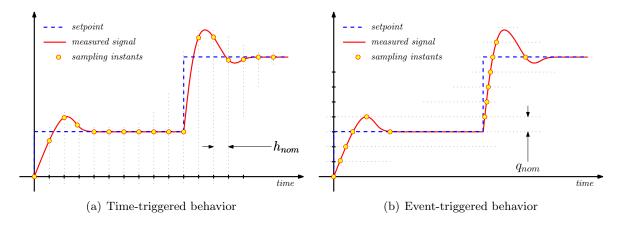

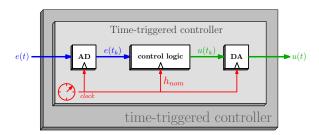

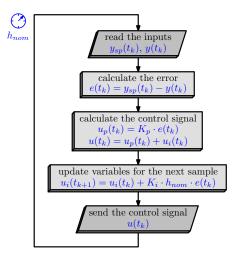

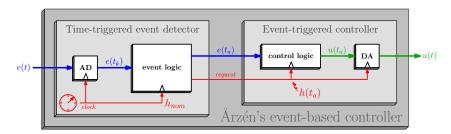

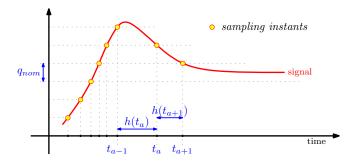

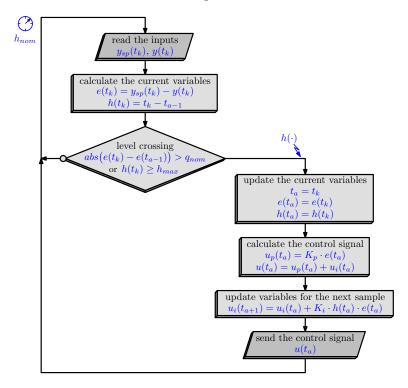

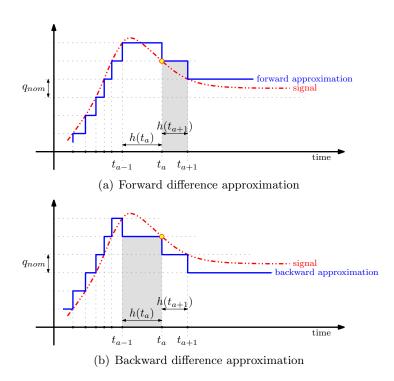

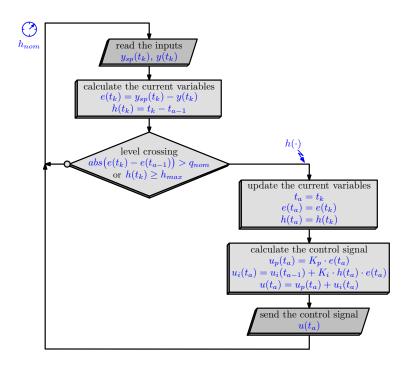

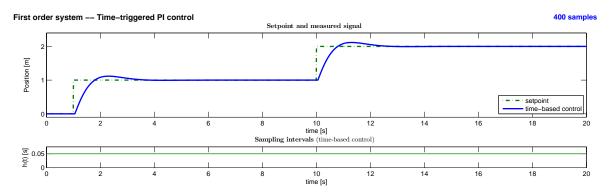

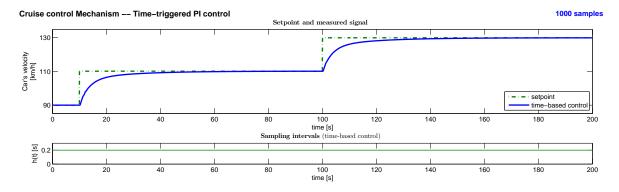

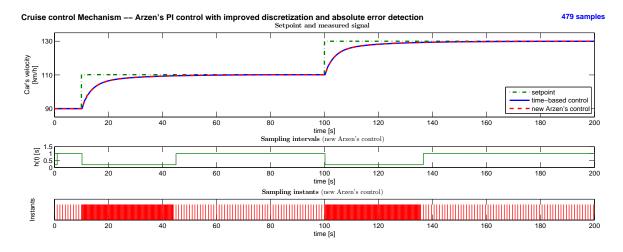

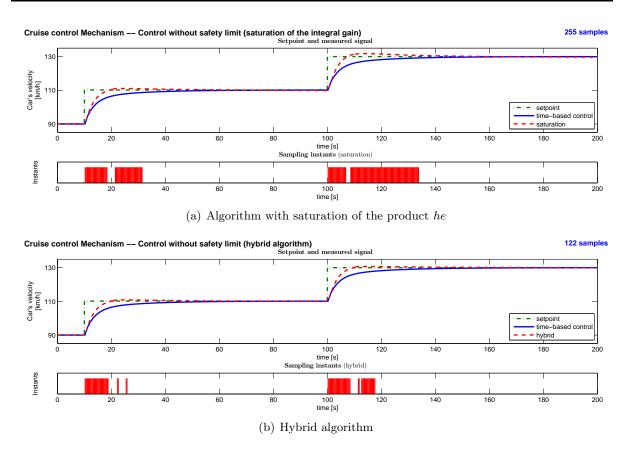

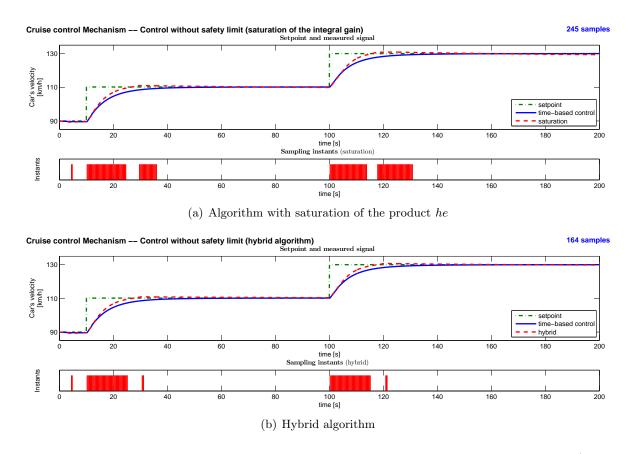

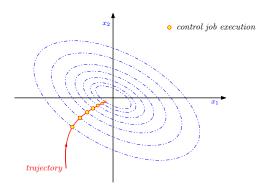

|   | 5.1                                           | Time-based vs. event-based sampling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                    |

|   | 5.2                                           | Event-driven sampling as an opportunity for embedded systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                    |

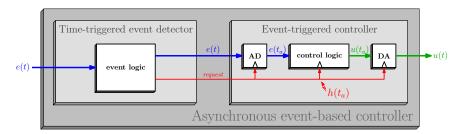

|   |                                               | 5.2.1 Asynchronous needs in the different communities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                    |

|   |                                               | F 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.40                                                                                                               |

|   |                                               | 5.2.2 Difficulties to untie some well-established paradigms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                    |

|   |                                               | 5.2.2 Difficulties to unitie some well-established paradigms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                    |

| 6 |                                               | 5.2.3 Study case: The TATIE project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 140<br><b>143</b>                                                                                                |

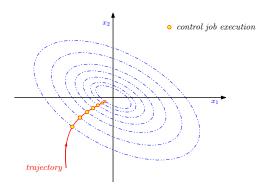

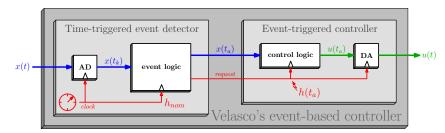

| 6 | <b>Eve</b> 6.1                                | 5.2.3 Study case: The TATIE project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ul><li>140</li><li>143</li><li>144</li></ul>                                                                      |

| 6 |                                               | 5.2.3 Study case: The TATIE project                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <ul><li>140</li><li>143</li><li>144</li><li>144</li></ul>                                                          |