# An inverse method for the synthesis of timing parameters in concurrent systems

Etienne André

#### ▶ To cite this version:

Etienne André. An inverse method for the synthesis of timing parameters in concurrent systems. Computers and Society [cs.CY]. École normale supérieure de Cachan - ENS Cachan, 2010. English. NNT: 2010DENS0044. tel-00595268

### HAL Id: tel-00595268 https://theses.hal.science/tel-00595268

Submitted on 24 May 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

présentée à l'École Normale Supérieure de Cachan

en vue de l'obtention du grade de

#### Docteur de l'École Normale Supérieure de Cachan

par Étienne André

Spécialité informatique

# An Inverse Method for the Synthesis of Timing Parameters in Concurrent Systems

Soutenue le 8 décembre 2010 devant un jury composé de

Eugene ASARIN Examinateur

Bernard BERTHOMIEU Rapporteur

Franck CASSEZ Rapporteur

Emmanuelle Encrenaz-Tiphene Co-directrice de thèse Laurent Fribourg Co-directeur de thèse

Marta KWIATKOWSKA Examinatrice Kim G. LARSEN Examinateur

## **Abstract**

This thesis proposes a novel approach for the synthesis of delays for timed systems. When verifying a real-time system, e.g., a hardware device or a communication protocol, it is important to check that not only the functional but also the timed behavior is correct. This correctness depends on the values of the delays of internal operations and of the environment.

Formal verification methods guarantee the correctness of a timed system for a given set of delays, but do not give information for other values of the delays. Checking the correctness of for various values of those delays can be difficult and time consuming. It is thus interesting to consider that these delays are parameters. The problem then consists in synthesizing "good values" for those parameters, i.e., values for which the system is guaranteed to behave well.

We are here interested in the synthesis of parameters in the framework of timed automata, a model for verifying real-time systems. Our approach relies on the following inverse method: given a reference valuation of the parameters, we synthesize a constraint on the parameters, guaranteeing the same time-abstract linear behavior as for the reference valuation. This gives a criterion of robustness to the system. By iterating this inverse method on various points of a bounded parameter domain, we are then able to partition the parametric space into good and bad zones, with respect to a given property one wants to verify. This gives a behavioral cartography of the system.

This method extended to probabilistic systems allows to preserve minimum and maximum probabilities of reachability properties. We also present variants of the inverse method for directed weighted graphs and Markov Decision Processes. Several prototypes have been implemented; in particular, IMITATOR II implements the inverse method and the cartography for timed automata. It allowed us to synthesize parameter values for several case studies such as an abstract model of a memory circuit sold by the chipset manufacturer ST-Microelectronics, and various communication protocols.

**Keywords**: verification, model checking, timed systems, parametric timed automata, synthesis of parameters, hardware verification, probabilistic timed automata, randomized protocols.

ii Abstract

## Résumé

Cette thèse propose une nouvelle approche pour la synthèse de valeurs temporelles dans les systèmes temporisés. Lorsque l'on vérifie un système temps-réel, comme un circuit ou un protocole de communication, il est important de vérifier non seulement l'aspect fonctionnel, mais également temporisé. La correction du système dépend de valeurs temporelles internes et de l'environnement.

Les méthodes formelles de vérification garantissent la correction d'un système temporisé pour un ensemble de valeurs temporelles, mais ne donnent pas d'information pour d'autres valeurs. Vérifier la correction d'un système pour de nombreuses valeurs peut s'avérer long et difficile. Il est alors intéressant de les considérer comme paramètres. Le problème consiste alors à synthétiser des valeurs de ces paramètres pour lesquelles le système est correct.

Nous nous intéressons ici à la synthèse de paramètres dans le cadre des automates temporisés. Notre approche est basée sur la méthode inverse suivante : à partir d'une instance de référence des paramètres, nous synthétisons une contrainte sur les paramètres, garantissant le même comportement que pour l'instance de référence, abstraction faite du temps. Il en résulte un critère de robustesse pour le système. En itérant cette méthode sur des points dans un domaine paramétrique borné, nous sommes alors à même de partitionner l'espace des paramètres en bonnes et mauvaises zones par rapport à une propriété à vérifier. Ceci nous donne une cartographie comportementale du système.

Cette méthode s'étend aisément aux systèmes probabilistes. Nous présentons également des variantes de la méthode inverse pour les graphes orientés valués et les processus de décision markoviens. Parmi les prototypes implémentés, IMITATOR II implémente la méthode inverse et la cartographie pour les automates temporisés. Ce prototype nous a permis de synthétiser de bonnes valeurs pour les paramètres temporels de plusieurs études de cas, dont un modèle abstrait d'une mémoire commercialisée par le fabricant de puces ST-Microelectronics, ainsi que plusieurs protocoles de communication.

**Mots-clés** : vérification, model-checking, systèmes temporisés, automates temporisés paramétrés, synthèse de paramètres, vérification de circuits, automates temporisés probabilistes, protocoles de communication.

iv Résumé

### Remerciements

Je remercie en premier lieu mes directeurs de thèse Emmanuelle ENCRENAZ et Laurent FRIBOURG pour les pistes de recherche qu'ils ont su me conseiller au cours de ces trois années, pour leurs conseils avisés, pour nos discussions parfois contradictoires et toujours bénéfiques.

Je tiens également à remercier Bernard Berthomieu et Franck Cassez pour m'avoir fait l'honneur de relire ma thèse, et y avoir apporté des commentaires constructifs. I would also like to thank Eugene Asarin, Marta Kwiatkowska and Kim G. Larsen to have done me the great honor of accepting to take part to my jury.

Un grand merci également à plusieurs personnes qui m'ont, d'une manière ou d'une autre, encouragé à entreprendre une thèse : Patrice QUINTON en premier lieu pour ses conseils très judicieux, Sébastien FERRÉ et Mireille DUCASSÉ pour m'avoir accordé leur confiance et leur soutien pendant mon Master 2, et enfin Arnaud GOTLIEB pour ses encouragements.

Cette thèse n'aurait pu exister dans sa forme actuelle sans les personnes avec qui j'ai eu l'occasion de travailler au cours de ces trois années. En tant que membre du projet VALMEM, j'ai eu la chance de bénéficier d'une étude de cas réaliste et très motivante en la mémoire SPSMALL, grâce aux travaux des autres membres du projet que sont, outre mes deux directeurs de thèse, Abdelrezzak BARA, Pirouz BAZARGAN-SABET, Remy CHEVALLIER, Dominique LE DU et Patricia RENAULT. Cette étude de cas a, par sa complexité, motivé plusieurs techniques développées dans cette thèse, et notamment la réalisation de IMITATOR II. Merci également à Ulrich KÜHNE pour avoir poursuivi le développement d'IMITATOR II, et à Romain SOULAT pour avoir expérimenté de nouvelles techniques permettant ainsi l'analyse de deux modèles de la mémoire SPS-MALL (et pour avoir martyrisé passion de longues nuits durant). I also thank Jeremy SPROSTON for reading my thesis and suggesting numerous interesting enhancements.

Évidemment, merci au LSV pour la très bonne ambiance qui y règne, et qui permet d'y réaliser une thèse dans d'excellentes conditions. Et puis, comme vi Remerciements

il est d'usage de glisser dans cet exercice obligé quelques allusions *private* que personne ne comprendra ou ne lira jamais, probablement pas même les personnes concernées, merci aux occupants de la salle Renodo pour leurs (bruyantes) parties de travail collaboratif du temps où ils tentaient encore de rivaliser avec moi, merci à la RATP de m'avoir permis de réaliser *Ticket II*, qui aura égayé le mur en face de moi à défaut de m'enrichir, merci à mon presque voisin de bureau pour m'avoir emmené à la découverte des paysages ferroviaires d'Asie centrale au beau milieu de l'hiver et de ma thèse et au grand dam de nos encadrants respectifs, merci à Valérie pour avoir contribué à développer nos capacités créatrices et nous avoir fait découvrir tout Paris à pied, merci à mes piments pour avoir consciencieusement poussé, même dans les moments difficiles que représente l'hiver cachannais, merci à ceux (et surtout celles) qui les ont arrosés – et puis, *last but not least* comme on dit, merci à mon vélo. Enfin, merci à mes parents sans qui je ne serais pas là (c'est une tautologie). 最後,非常感謝黃磊長久以來的支持和幫助。

## **Contents**

| Ał | ostra | ct       |                                   |   | i    |

|----|-------|----------|-----------------------------------|---|------|

| Re | ésum  | é en fra | ançais                            |   | iii  |

| Re | emer  | ciemen   | nts                               |   | V    |

| Li | st of | Algorit  | hms                               |   | хi   |

| Li | st of | Figures  | <b>S</b>                          |   | XV   |

| Li | st of | Tables   |                                   | 2 | xvii |

| 1  | Intr  | oducti   | on                                |   | 1    |

|    | 1.1   | The G    | ood Parameters Problem            |   | 2    |

|    | 1.2   | Conte    | xt                                |   | 6    |

|    |       | 1.2.1    | Classical Problems                |   | 6    |

|    |       | 1.2.2    | Formal Techniques of Verification |   | 7    |

|    | 1.3   | Organ    | nization of the Thesis            |   | 9    |

| 2  | Pre   | liminaı  | ry Definitions                    |   | 11   |

|    | 2.1   | Const    | raints                            |   | 12   |

|    |       | 2.1.1    |                                   |   | 12   |

|    |       |          | Parameters                        |   | 13   |

|    |       | 2.1.3    |                                   |   | 13   |

|    | 2.2   |          | d Automata                        |   | 15   |

|    |       | 2.2.1    |                                   |   | 15   |

|    |       | 2.2.2    |                                   |   | 15   |

|    |       | 2.2.3    | Parametric Timed Automata         |   | 22   |

|    | 2.3   |          | ood Parameters Problem            |   | 32   |

|    | 2.4   |          | ed Work                           |   | 32   |

|    |       | 2.4.1    | 1                                 |   | 33   |

|    |       | 2.4.2    | Timed Automata                    |   | 34   |

viii Contents

|   |             | 2.4.3 Time Petri Nets                                |

|---|-------------|------------------------------------------------------|

|   |             | 2.4.4 Hybrid Systems                                 |

|   |             | 2.4.5 Discussion                                     |

| 3 | An l        | overse Method for PTAs 3                             |

| Ū | 3.1         | The Inverse Problem                                  |

|   |             | 3.1.1 A Motivating Example                           |

|   |             | 3.1.2 The Problem                                    |

|   | 3.2         | The Inverse Method Algorithm                         |

|   | o. <u>_</u> | 3.2.1 Principle                                      |

|   |             | 3.2.2 A Toy Example                                  |

|   |             | 3.2.3 Remarks on the Algorithm                       |

|   | 3.3         | Results                                              |

|   |             | 3.3.1 Correctness                                    |

|   |             | 3.3.2 Termination                                    |

|   |             | 3.3.3 Properties                                     |

|   |             | 3.3.4 Discussion                                     |

|   | 3.4         | Application to the Flip-flop Example                 |

|   | 3.5         | Variants of the Inverse Method 6                     |

|   |             | 3.5.1 Variant with State Inclusion in the Fixpoint 6 |

|   |             | 3.5.2 Variant with Union of the Constraints 6        |

|   |             | 3.5.3 Discussion on the Variants 6                   |

|   | 3.6         | Related Work                                         |

|   |             | 0. 4                                                 |

| 4 |             | Studies 7                                            |

|   | 4.1         | Tools                                                |

|   |             | 4.1.1 IMITATOR                                       |

|   |             | 4.1.2 IMITATOR II                                    |

|   | 4.2         | SR-Latch                                             |

|   | 4.3         | AND-OR                                               |

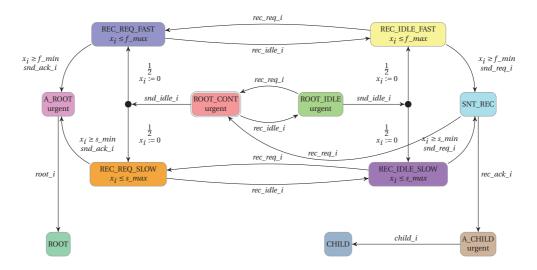

|   | 4.4         | IEEE 1394 Root Contention Protocol                   |

|   | 4.5         | Bounded Retransmission Protocol                      |

|   | 4.6         | Latch Circuit                                        |

|   | 4.7         | SPSMALL Memory                                       |

|   |             | 4.7.1 Description                                    |

|   |             | 4.7.2 A Short History                                |

|   |             | 4.7.3 Manually Abstracted Model                      |

|   |             | 4.7.4 Automatically Generated Model 10               |

|   |             | 4.7.5 Larger Models                                  |

|   | 4.8         | Networked Automation System                          |

|   | 4.9         | Summary of the Experiments                           |

Contents ix

|                          | 4.10 | Tools  | Related to IMITATOR II                    |

|--------------------------|------|--------|-------------------------------------------|

| 5 Behavioral Cartography |      |        | l Cartography 113                         |

|                          | 5.1  | Beyor  | nd the Inverse Method                     |

|                          | 5.2  |        | ehavioral Cartography Algorithm           |

|                          | 5.3  |        | rties                                     |

|                          | 5.4  | _      | Studies                                   |

|                          |      | 5.4.1  | Implementation                            |

|                          |      | 5.4.2  | SR-Latch                                  |

|                          |      | 5.4.3  | Flip-flop                                 |

|                          |      | 5.4.4  |                                           |

|                          |      | 5.4.5  | Summary of the Experiments                |

|                          | 5.5  | Relate | ed Work                                   |

|                          |      |        |                                           |

| 6                        |      |        | to Probabilistic Systems 137              |

|                          | 6.1  |        | ivating Example                           |

|                          | 6.2  |        | bilistic Timed Automata                   |

|                          |      | 6.2.1  | Timed Probabilistic Systems               |

|                          |      | 6.2.2  |                                           |

|                          |      | 6.2.3  |                                           |

|                          | 6.3  |        | nverse Problem for PPTAs                  |

|                          | 6.4  |        | sion of the Inverse Method                |

|                          | 6.5  | Case S | Studies                                   |

|                          |      | 6.5.1  |                                           |

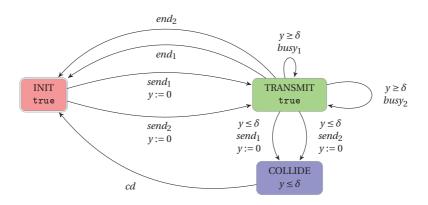

|                          |      | 6.5.2  | CSMA/CD Protocol                          |

|                          |      | 6.5.3  |                                           |

|                          | 6.6  | Carto  | graphy of PPTAs                           |

|                          |      | 6.6.1  | Principle of the Extension                |

|                          |      | 6.6.2  | Example: Root Contention Protocol         |

|                          | 6.7  | Relate | ed Work                                   |

| 7                        | An 1 | nverse | Method for Weighted Graphs 169            |

| •                        | 7.1  |        | ted Weighted Graphs                       |

|                          |      | 7.1.1  | The Floyd–Warshall Algorithm              |

|                          |      | 7.1.2  | The Problem                               |

|                          |      | 7.1.3  | An Inverse Method for Weighted Graphs 178 |

|                          |      | 7.1.4  | Properties                                |

|                          |      | 7.1.5  | Implementation and Case Studies           |

|                          | 7.2  |        | ov Decision Processes                     |

|                          | 1.2  | 7.2.1  |                                           |

|                          |      |        | The Inverse Problem for MDPs              |

|                          |      |        |                                           |

| X              | Contents |

|----------------|----------|

| · <del>-</del> |          |

|    |                  | 7.2.3 An Inverse Method for MDPs      |                |  |

|----|------------------|---------------------------------------|----------------|--|

|    |                  | 7.2.4 Properties                      |                |  |

|    |                  | 7.2.5 Implementation and Applications |                |  |

|    | 7.3              | Related Work                          | <del>}</del> 9 |  |

| 8  | Con              | clusion and Perspectives 20           | 1              |  |

|    | 8.1              | Summary                               | )1             |  |

|    | 8.2              | Future Research                       | )3             |  |

| Bi | Bibliography 207 |                                       |                |  |

| A  | Clas             | sical Notions 22                      | 21             |  |

|    | A.1              | LTL                                   | 21             |  |

|    | A.2              | CTL                                   | 22             |  |

|    | A.3              | Time-Abstract Bisimulation            | 24             |  |

| No | otatio           | ns 22                                 | 25             |  |

| Gl | ossaı            | y 22                                  | 27             |  |

| In | dex              | 22                                    | 29             |  |

| Ré | sum              | substantiel 23                        | 31             |  |

## List of Algorithms

| 1  | Inverse method algorithm $IM(\mathcal{A}, \pi)$                      |

|----|----------------------------------------------------------------------|

| 2  | Variant $IM^{\subseteq}(\mathcal{A},\pi)$ of the inverse method 61   |

| 3  | Variant $IM^{\cup}(\mathcal{A},\pi)$ of the inverse method 65        |

| 4  | Optimization of <i>IM</i> for IMITATOR II                            |

| 5  | Simpler way to describe $IM(\mathcal{A}, \pi)$                       |

| 6  | Behavioral cartography algorithm $BC(\mathcal{A}, V_0)$              |

| 7  | Floyd–Warshall algorithm $FW(\mathcal{G})$                           |

| 8  | Parametric Floyd–Warshall algorithm $PFW(\mathcal{G}, \pi_0)$ 179    |

| 9  | Algorithm of value determination $VD(\mathcal{M}, v)$ 189            |

| 10 | Algorithm of policy iteration $PI(\mathcal{M})$                      |

| 11 | Parametric value determination $pVD(\mathcal{M}, v)$ 194             |

| 12 | Inverse method algorithm for MDPs $pPI(\mathcal{M}, \pi_0, v_0)$ 196 |

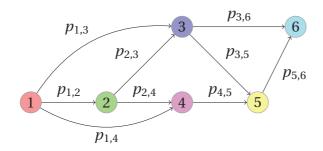

## **List of Figures**

| 1.1  | Flip-flop circuit (left) and its environment (right)                                               | 3  |

|------|----------------------------------------------------------------------------------------------------|----|

| 2.1  | An example of Timed Automaton                                                                      | 17 |

| 2.2  | Example of Network of Timed Automata                                                               | 18 |

| 2.3  | Example of concrete run for a TA                                                                   | 19 |

| 2.4  | Example of trace associated to a concrete run for a TA                                             | 20 |

| 2.5  | Example of trace set of a TA                                                                       | 21 |

| 2.6  | An example of Parametric Timed Automaton                                                           | 23 |

| 2.7  | Example of Network of Parametric Timed Automata                                                    | 25 |

| 2.8  | Example of symbolic run for a PTA                                                                  | 28 |

| 2.9  | Example of trace associated to a symbolic run of a PTA                                             | 29 |

| 2.10 | Example of trace set of a PTA                                                                      | 29 |

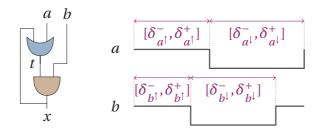

| 2.11 | A "NOT" gate (left) and its environment (right)                                                    | 30 |

| 2.12 | PTA modeling a "NOT" gate using one interval of delays                                             | 31 |

| 2.13 | PTA modeling a "NOT" gate using a bi-bounded inertial model                                        | 32 |

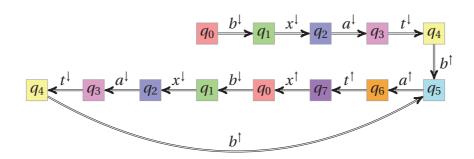

| 3.1  | Trace set of the flip-flop circuit under $\pi_0$                                                   | 41 |

| 3.2  | A toy PTA                                                                                          | 44 |

| 3.3  | PTA showing the necessity of the fixpoint of <i>IM</i>                                             | 45 |

| 3.4  | Trace set of $\mathscr{A}[\pi_0]$                                                                  | 45 |

| 3.5  | Trace set of $\mathscr{A}[\pi]$ , for any $\pi \models K'_0 \dots \dots \dots \dots \dots$         | 46 |

| 3.6  | PTA explaining the intersection of constraints returned by $\mathit{IM}$                           | 46 |

| 3.7  | An example of PTA for which <i>IM</i> does not terminate                                           | 52 |

| 3.8  | PTA showing the non-confluence of algorithm $\mathit{IM}$                                          | 52 |

| 3.9  | PTA showing the non-CTL-equivalence of $IM$                                                        | 55 |

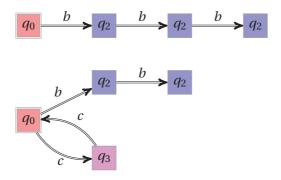

| 3.10 | A PTA $\mathcal{A}_{var}$ for comparing the variants of $IM$                                       | 70 |

| 3.11 | Trace set of $\mathcal{A}_{var}$ under $\pi_0$                                                     | 70 |

| 3.12 | Over trace set of $\mathscr{A}_{var}[\pi]$ for $\pi \models K^{\subseteq}$                         | 71 |

| 3.13 | Possible trace sets of $\mathcal{A}_{var}[\pi]$ for $\pi \models K^{\cup} \dots \dots \dots \dots$ | 71 |

| 3.14 | Comparison of the constraints synthesized for $\mathcal{A}_{var}$                                  | 72 |

xiv List of Figures

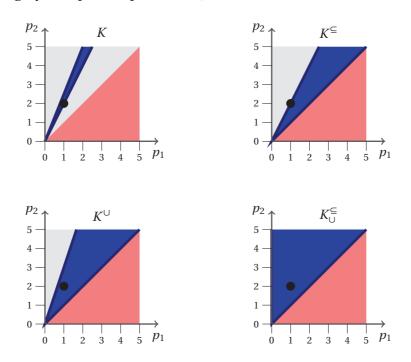

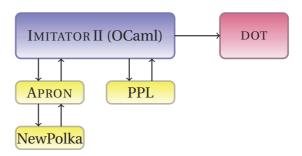

| 4.1  | ${\tt IMITATOR}$ II inputs and outputs in inverse method mode                      | 79  |

|------|------------------------------------------------------------------------------------|-----|

| 4.2  | IMITATOR II internal structure                                                     | 80  |

| 4.3  | Example of trace set automatically output by Imitator II                           | 81  |

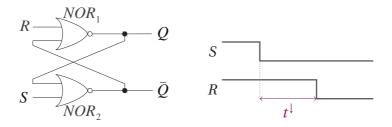

| 4.4  | SR latch (left) and environment (right)                                            | 85  |

| 4.5  | Trace set for the SR latch under $K_0$                                             | 86  |

| 4.6  | AND–OR circuit (left) and its environment (right)                                  | 86  |

| 4.7  | Trace of the AND–OR circuit under $\pi_0$                                          | 88  |

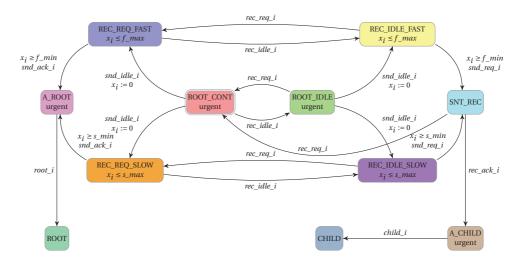

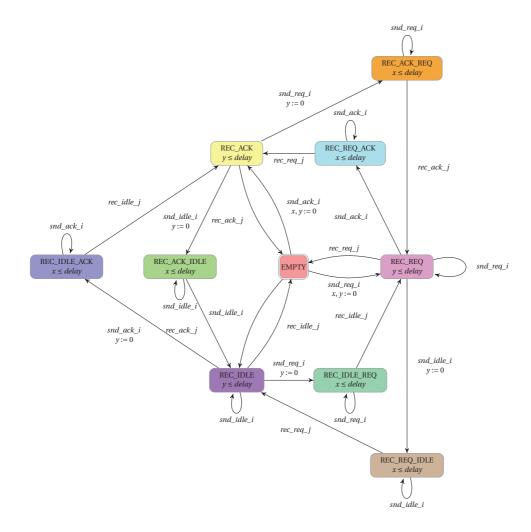

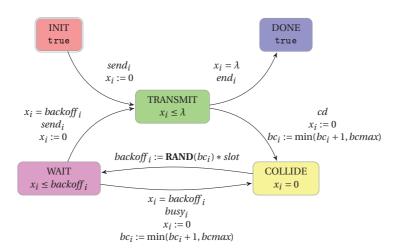

| 4.8  | PTA modeling node $i$ in the Root Contention Protocol $\ldots \ldots$              | 90  |

| 4.9  | PTA modeling wire $i$ in the Root Contention Protocol                              | 91  |

| 4.10 | Trace set of the RCP output by Imitator II                                         | 92  |

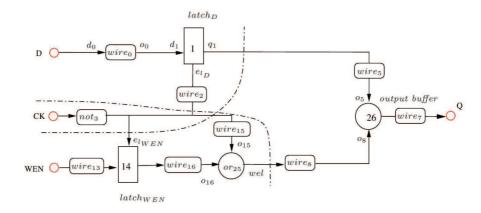

| 4.11 | A latch circuit                                                                    | 94  |

| 4.12 | Environment for the latch circuit                                                  | 95  |

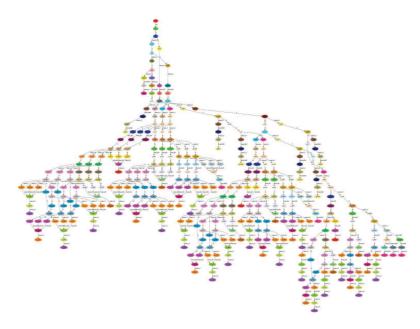

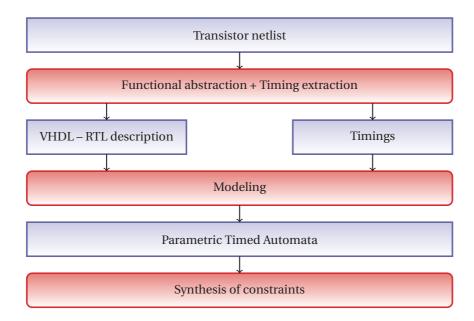

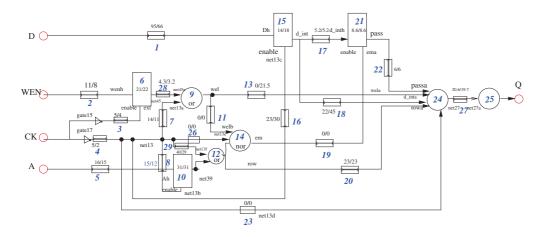

| 4.13 | Methodology of the VALMEM project                                                  | 97  |

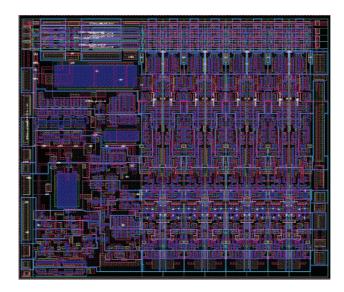

| 4.14 | Transistor representation of the SPSMALL memory                                    | 98  |

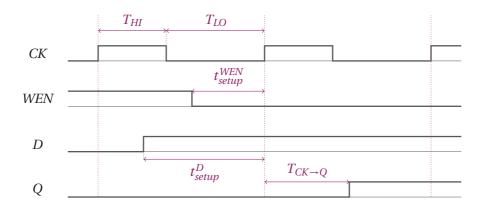

| 4.15 | Environment for the <i>write</i> operation of SPSMALL                              | 99  |

| 4.16 | Abstract model of the SPSMALL memory (write operation)                             | 101 |

| 4.17 | PTAs modeling the write operation of SPSMALL                                       | 102 |

| 4.18 | Abstract model of the SPSMALL memory                                               | 105 |

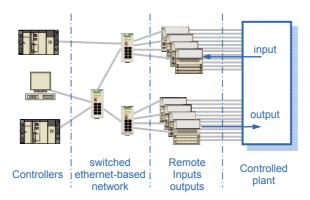

| 4.19 | Example of Networked Automation Systems (NAS)                                      | 107 |

| 5.1  | IMITATOR II inputs and outputs in cartography mode                                 | 119 |

| 5.2  |                                                                                    | 120 |

| 5.3  | Trace set of tile 1 for the SR latch                                               |     |

| 5.4  | Trace set of tile 2 for the SR latch                                               |     |

| 5.5  | Trace set of tile 3 for the SR latch                                               |     |

| 5.6  | Trace set of tile 4 for the SR latch                                               |     |

| 5.7  | Trace set of tile 5 for the SR latch                                               |     |

| 5.8  | Trace set of tile 6 for the SR latch                                               |     |

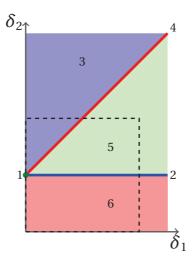

| 5.9  | Behavioral cartography of the SR latch according to $\delta_1$ and $\delta_2$      | 123 |

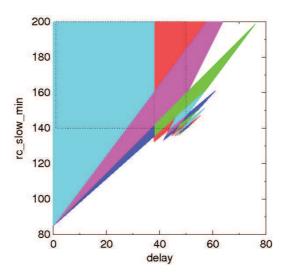

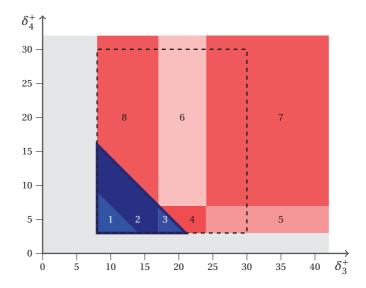

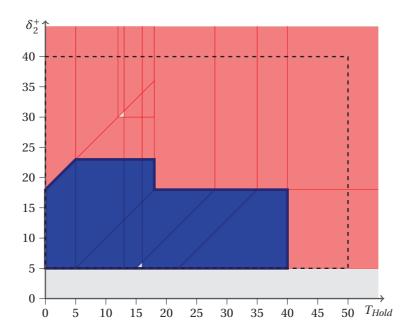

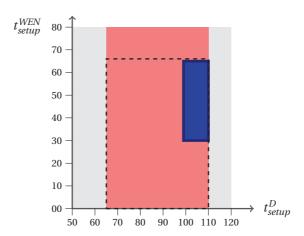

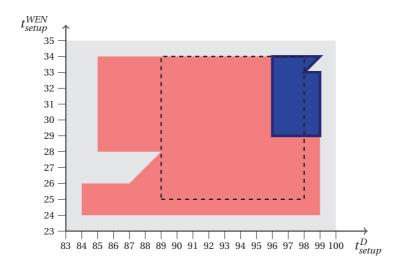

| 5.10 | Behavioral cartography of the flip-flop according to $\delta_3^+$ and $\delta_4^+$ | 125 |

|      | Trace set of tile 3 for the flip-flop case study                                   |     |

|      | Trace set of tile 7 for the flip-flop case study                                   |     |

|      | Environment for the flip-flop circuit with $D = 0 \dots \dots \dots$               |     |

|      | Behavioral cartography of the flip-flop for parameters $T_{Hold}$ and $\delta_2^+$ |     |

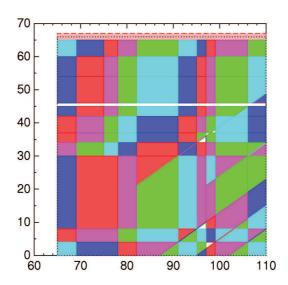

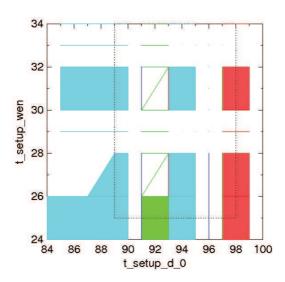

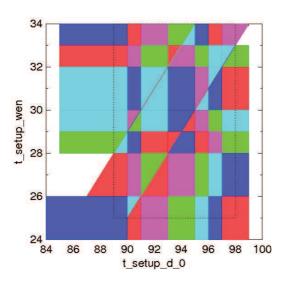

|      | Cartography of the SPSMALL memory                                                  |     |

|      | Cartography of the SPSMALL memory (after partition)                                |     |

|      | Cartography of the SPSMALL memory (generated model)                                |     |

|      | Cartography of the SPSMALL memory (full coverage)                                  |     |

|      | Cartography of the generated model of the SPSMALL memory (af-                      |     |

|      |                                                                                    | 133 |

List of Figures xv

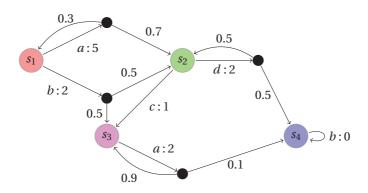

| 6.1  | Example of probabilistic timed automaton                                                                                                                 | 42  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.2  | Examples of probabilistic timed automata satisfying neither de-                                                                                          |     |

|      | terminism on actions nor reset unicity (left) and satisfying both                                                                                        |     |

|      | (right)                                                                                                                                                  | 43  |

| 6.3  | Example of path                                                                                                                                          | 46  |

| 6.4  | A probabilistic timed automaton containing a deadlock 1                                                                                                  | 47  |

| 6.5  | Example of PPTA                                                                                                                                          | 49  |

| 6.6  | Example of trace                                                                                                                                         | 50  |

| 6.7  | Example of non-probabilistic version of a PPTA                                                                                                           | 52  |

| 6.8  | PPTA modeling node $i$ in the Root Contention Protocol 1                                                                                                 | 56  |

| 6.9  | CSMA/CD Medium                                                                                                                                           | 58  |

| 6.10 | CSMA/CD Station $i$                                                                                                                                      | 59  |

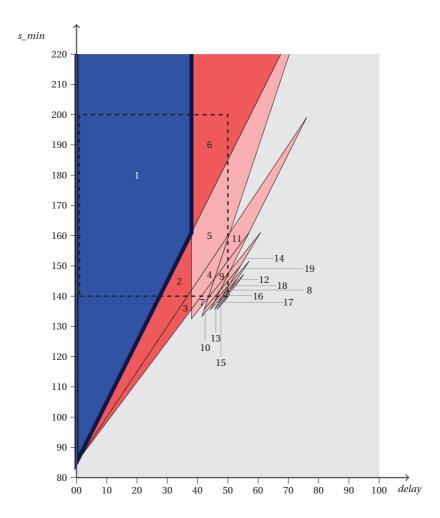

| 6.11 | Behavioral cartography of the Root Contention Protocol accord-                                                                                           |     |

|      | ing to <i>delay</i> and $s_min \dots 1$                                                                                                                  | 64  |

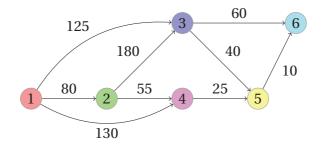

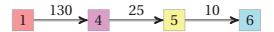

| 7.1  | An example of Directed Weighted Graph                                                                                                                    | 72  |

| 7.2  | Example of path of a DWG                                                                                                                                 |     |

| 7.3  | An example of PDWG                                                                                                                                       |     |

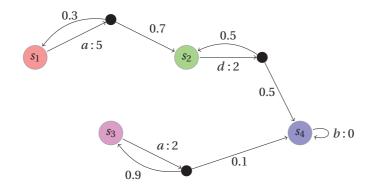

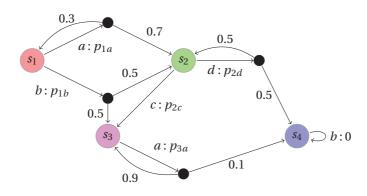

| 7.4  | An example of Markov Decision Process                                                                                                                    |     |

| 7.5  | Our example of MDP associated to policy $v \dots $ | 89  |

| 7.6  | An example of Parametric Markov Decision Process                                                                                                         | 93  |

| A.1  | LTL semantics for infinite words over $2^{AP}$                                                                                                           | 222 |

xvi List of Figures

## **List of Tables**

| 3.1 | Locations of the flip-flop circuit                                                                 |

|-----|----------------------------------------------------------------------------------------------------|

| 4.2 | Value of the signals for each of the locations of the SR-latch 85  Locations of the AND–OR circuit |

|     | Summary of experiments for the cartography algorithm                                               |

| 6.1 | Results of PRISM for the RCP                                                                       |

| 6.2 | Results of Prism for the CSMA/CD                                                                   |

| 6.3 | Results of PRISM for the IEE 802.11 Protocol                                                       |

## Chapter 1

## Introduction

When did everything start having an expiration date?

Chungking Express (Wong Kar-wai)

The importance of computer systems has dramatically increased in the last decades. Critical systems, involving human lives, need to be perfectly reliable, with a total absence of any inappropriate behavior, such as failures or unexpected sequences of actions. One can test a given system to check the absence of inappropriate behaviors for a given environment, by directly executing the system for this environment; however, although testing a system can show the absence of bad behavior for a given execution, no guarantee is given in the general case, for different scenarios of the environment. Moreover, if there is some nondeterminism in the execution, the correctness of a test case does not give any guarantee, even exactly for the same environment. As a consequence, testing can be used in order to find possible errors in a system, but usually not to show its correctness. This is why formal verification is needed, allowing to prove the correctness of a system with respect to some properties, using mathematical models and proofs.

When considering timed systems, i.e., systems involving time elapsing between actions, correctness also takes timing constraints into account. In a real-time environment, i.e., for systems working in a highly interactive environment, such as hardware devices or telecommunication protocols, it is not sufficient to prove that the system behaves well: one also needs to prove that this good behavior always occurs within a given interval of time. For example, when designing the computer system of a car, one can formally prove that, in case of a collision, the airbag will *eventually* inflate. However, one easily understands

that this proof is not enough, and that one should prove that the airbag will inflate within a given amount of time (hopefully short) after the collision occurred. In other words, timed systems have to meet not only constraints on the order of the events, but also quantitative constraints on delays between these events.

Moreover, in a concurrent environment where several timed systems interact with each other, an action occurring too late (or, more generally, at a wrong time) in a subsystem can change the global behavior of the whole system, and have dramatic consequences. For example, the Therac-25 machine, a radiation therapy machine, severely injured and killed several patients in the 1980s because the patients were given by mistake high overdoses of radiation. Beside numerous bugs in the software code and in the development process, one of the causes for this dramatic malfunctioning was a race condition, i.e., an unexpected ordering of actions leading to unpredictable behaviors. The bug in the software allowing this race condition was difficult to detect by simple testing, because it occurred only after a specific sequence of actions within a short amount of time, and the engineers having tested the system were not familiar enough with the machine for them to perform this sequence of actions quickly enough.

#### 1.1 The Good Parameters Problem

When designing a real-time system, it is not sufficient to prove the correctness for some given delays: one also wants to know for which delays the behavior of the system is correct. Checking the correctness of the system for various values of those delays can be difficult and time consuming. It is therefore interesting to reason parametrically, by considering that these delays are *unknown constants*, or *parameters*. The problem then consists in synthesizing good values for those parameters, i.e., values for which the system is guaranteed to behave well. This can be done by synthesizing a *constraint* on these parameters guaranteeing a correct behavior.

This thesis faces the following good parameters problem, as mentioned in [FJK08] in the framework of hybrid systems: "given a timed system involving delays, find values for those delays seen as parameters within a bounded domain for which the system behaves well".

Finding suitable values for the timing delays is of interest for guaranteeing a good behavior in a concurrent timed system. This allows a notion of robustness: one can guarantee that the values *around* a given value of the delays will not impact the overall behavior of the system, or will still guarantee a (possibly different) good behavior. Moreover, it allows the optimization of some of the

timing delays, without changing the overall behavior of the system.

However, this problem is generally difficult for concurrent timed systems. Such systems involve both a functional behavior (i.e., sequences of actions, possibly concurrent) and a timed behavior (i.e., durations between two actions). As a consequence, abstracting either time or functionalities leads in general to too imprecise results. Simple heuristics do generally not apply to this framework: for example, in order to minimize the response (or computation) time of a system, one may want to minimize every (or some) intermediate timing delay. However, it is unfortunately well known (in particular, in hardware verification) that diminishing an intermediate timing delay can actually *increase* the global response or computation time. As a consequence, one should consider *all* possibilities. First, this may not be possible if one considers real-valued timing delays, because this would result in an infinite number of models to verify. Second, even with suitable abstractions allowing to group interval of values together, this may result in the explosion of the state-space if the considered model is too precise.

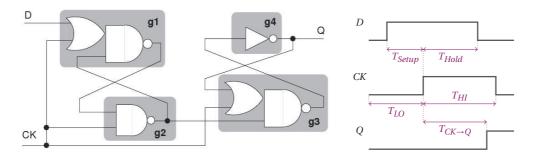

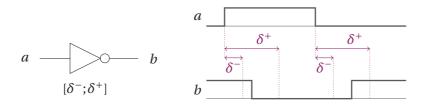

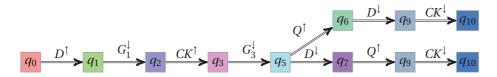

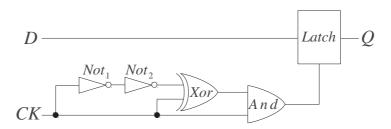

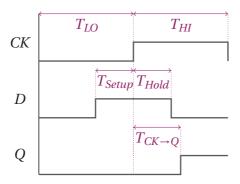

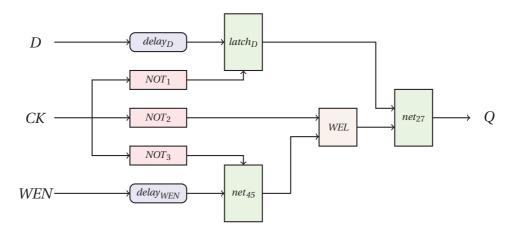

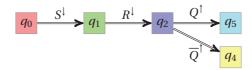

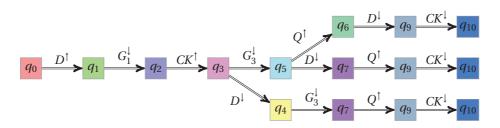

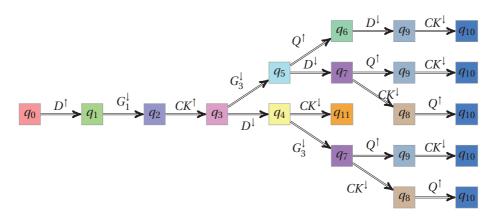

**A Motivating Example.** As an example, consider the asynchronous "D flip-flop" circuit described in [CC07] and depicted in Figure 1.1 left. It is composed of 4 gates ( $G_1$ ,  $G_2$ ,  $G_3$  and  $G_4$ ) interconnected in a cyclic way, and an environment involving two input signals D and CK. The global output signal is Q.

Figure 1.1: Flip-flop circuit (left) and its environment (right)

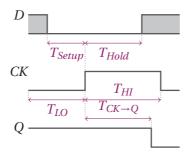

We consider a bi-bounded inertial model for gates (see [BS95, MP95]), where any change of the input may lead to a change of the output (after some delay). As a consequence, each gate  $G_i$  has a timing delay in the parametric interval  $[\delta_i^-, \delta_i^+]$ , with  $\delta_i^- \leq \delta_i^+$ . There are 4 other timing parameters (viz.,  $T_{HI}, T_{LO}, T_{Setup}$ , and  $T_{Hold}$ ) used to model the environment. The output signal of a gate  $G_i$  is denoted by  $g_i$  (note that  $g_4 = Q$ ). The rising (resp. falling) edge of signal D is denoted by  $D^{\uparrow}$  (resp.  $D^{\downarrow}$ ) and similarly for signals  $CK, Q, g_1, \ldots, g_4$ .

We consider an environment starting from D = CK = Q = 0 and  $g_1 = g_2 = 0$

$g_3 = 1$ , with the following ordered sequence of actions for inputs D and CK:  $D^{\uparrow}$ ,  $CK^{\uparrow}$ ,  $D^{\downarrow}$ ,  $CK^{\downarrow}$ , as depicted in Figure 1.1 right.

We consider that the behavior of this circuit is correct if, for this environment, the rise of signal Q (i.e., action  $Q^{\uparrow}$ ) always occurs before the fall of signal CK (i.e., action  $CK^{\downarrow}$ ).

The question that now arises is: what are the possible values for these 12 timing parameters such that the circuit behaves in a correct way? As said above, this is a difficult problem, in the sense that testing all the possible values for those parameters is simply not possible.

We will develop in this thesis techniques allowing to answer this question.

**Timed Automata.** We will here mostly focus on the good parameters problem in the framework of timed automata [AD94]. Timed automata are an extension of the class of standard finite-state automata, making use of clocks, which are real-valued variables evolving linearly at the same rate. Those clocks are compared with the delays of the system in constraints that must be verified in order to stay in a state of the automaton, or in order to take a transition. One can also reset some clocks when firing transitions. The model of timed automata has been widely used in order to study and verify hardware devices or communication protocols. However, timed automata can verify the correctness of a system only for one given set of values for the timing parameters.

When facing the problem of synthesis of parameters ensuring the correctness of the system, one needs to consider *parametric* timed automata [AHV93]. Parametric timed automata are an extension of timed automata to the parametric case, allowing in the constraints the use of parameters in place of constants.

**Contributions.** We propose here a novel approach for solving the good parameters problem in the framework of parametric timed automata. This approach relies on the following *inverse method*: given a reference valuation of the parameters, we synthesize a constraint on the delays viewed as parameters, guaranteeing the same time-abstract behavior as for the reference valuation. Roughly speaking, this time-abstract behavior only relies on actions, and not on the time elapsing between actions. This method has two main advantages. First, it gives a criterion of *robustness* by ensuring the correctness of the system for other values for the parameters around the reference valuation. This is of interest when implementing a system: indeed, the exact model with (for example) integer values for timing delays that has been formally verified will necessarily be implemented using values which will not be exactly the ones that have been verified. Second, it allows the system designer to *optimize* some delays without changing the overall functional behavior of the system.

By iterating this inverse method on various points of a bounded parameter domain, we are then able to separate parameter zones into zones for which the time-abstract behavior of the system is uniform. This gives a *behavioral cartography* of the system. One can then partition those zones into good zones and bad zones, with respect to a given property one wants to verify. The main interest is that this cartography does not depend on the property one wants to verify: only the partition into good and bad zones actually does. As a consequence, when verifying other properties, it is sufficient to check the property for only one point in each zone in order to get the new partition.

Two versions of prototypes have been implemented; in particular, IMITATOR II implements the inverse method, and its behavioral cartography algorithm, in the framework of timed automata. This prototype allowed us to synthesize values for the parameters of several case studies such as abstractions of a memory circuit sold by the chipset manufacturer ST-Microelectronics, or communication protocols.

Both this inverse method and the behavioral cartography algorithm naturally extend to probabilistic timed automata. In this framework, the constraint synthesized guarantees that, for any valuation of the parameters of a constraint synthesized by the inverse method, the minimum (resp. maximum) probabilities of reaching a given state will be the same. Besides the advantages inherited from the non-probabilistic framework, the main practical advantage of this extension is that it allows the *rescaling* of constants. Indeed, when verifying properties on probabilistic timed systems, for example using the PRISM model checker [HKNP06], the verification time and memory may highly depend on the size of the constants of the system. As a consequence, it can sometimes be extremely difficult (or even impossible) to compute probabilities for the "official" constants of a case study, and one has to rescale them in an approximate way, without much guarantee of correctness. By synthesizing a constraint guaranteeing the equality of reachability properties, one may safely rescale the constants of the system, and compute the probabilities for smaller constants (within the constraint).

The underlying principle of the inverse method is not strongly related to the framework of timed automata, and may also be applied to other formalisms. As a consequence, we generalize the synthesis of parameters in two untimed frameworks, namely Directed Weighted Graphs and Markov Decision Processes. In that case, the parameters do not necessarily correspond to timing delays. We extend the inverse method to those two frameworks as follows. First, in the framework of Directed Weighted Graphs, we synthesize a constraint on the costs of the system seen as parameters guaranteeing that the path of optimal cost between any two nodes of a graph will remain the same, for any valuation of the parameters satisfying that constraint. Second, in the framework of

Markov Decision Processes, which allow to consider untimed probabilistic systems, we synthesize a constraint on the costs seen as parameters guaranteeing that the optimal policy of the system remains the same, for any valuation of the parameters satisfying that constraint. Prototypes have been implemented.

#### 1.2 Context

This thesis focuses on the verification and synthesis of parameters in the framework of real-time systems. This problem has applications in various domains such as software analysis, hardware analysis, or networking protocols, and can be used for industrial applications in the medical industry, aeronautics, biology, etc. We develop hereafter some of the classical problems and techniques related to this problem.

#### 1.2.1 Classical Problems

**Computation of Response Time.** When verifying a real-time system, one of the major problems is the computation of the *response time* of the system. This classical problem consists, given an environment, i.e., a scenario for the inputs of the system, in computing the time between the change of the inputs and the change of a given output. This computation of response time is critical in particular when considering the verification of hardware, and more specifically of asynchronous circuits. An approach to compute the response time of a system is the Time Separation of Events (see, e.g., [CDY01] for an extensive survey). As said in [CDY01]: "The behavior of asynchronous and concurrent systems is naturally described in terms of events and their interactions. A fundamental problem in analyzing such systems is to determine bounds on the time separation of events. Stated informally, we seek answers to questions such as: How late can event i occur after event j? for arbitrary events i and j. The problem of computing time separation bounds is compounded in practice by statistical variations in manufacturing and operating conditions that introduce uncertainties in component delays. Consequently, finding bounds on time separation of events in the presence of uncertain component delays is an important practical problem." The system can be represented under the form of an (oriented) timing constraint graph [CSD97], where nodes represent events, and the directed edges represent dependencies between them. Various techniques have been proposed to solve this problem, either exact or using approximations (see, e.g., [CDY01, EF08] for a survey).

1.2. Context 7

**Worst-Case Execution Time.** A strongly related problem is the *worst-case exe* cution time (WCET) of some computation of a hardware device. It corresponds to the maximum length of time it takes to execute a given task on this device, and thus gives an upper bound on the execution time. Although it is wellknown that giving an upper bound on the execution of a program (in the general sense) is impossible, one can compute such an upper bound on real-time systems, which can be seen as a restricted form of programming [WEE<sup>+</sup>08]. In most cases, the state space is too large to exhaustively explore all possible executions and thus determine the exact worst-case execution time. As a consequence, one needs to define methods using abstractions or overapproximations, with the smallest possible loss of precision. Various techniques can be used; among them, one can first cite static program analysis [CC77, NNH99], which creates an abstraction of the device while avoiding to actually execute it. Second, (exact) simulation is a classical technique to estimate execution time for hardware verification using an exact model. A survey on techniques for WCET analysis can be found in [WEE+08], providing in particular a thorough overview of dedicated tools.

#### 1.2.2 Formal Techniques of Verification

Testing the correctness of a system by simulation is often performed when verifying the correctness of a system in practice. However, simulation and testing techniques only consider specific environments, and cannot give guarantees on *all* the possible executions. As a consequence, those techniques are generally inadequate for the verification of critical systems. One needs formal techniques, involving formal semantics, modeling languages, specification languages, and verification algorithms.

**Model Checking.** The model checking approach considers a system and a property to check on the system, and builds on the one hand a mathematical model of the system, and on the other hand a mathematical model for the property [EC80, CE82]. Techniques are then applied, allowing to *automatically* check whether the mathematical model of the system satisfies the mathematical model of the property. If yes, we say that the system meets the specification. Mathematical models for systems can be oriented graphs, i.e., automata and their extension (including timed automata [AD94]), as well as Petri nets [Pet62, Mer74] or process algebra. Properties can also be modeled by various structures, such as extensions of automata (including timed automata) or logics, including temporal logics (e.g., [Pnu77, CE82, ACD93]).

**Temporal Logics.** Temporal logics are extensions of propositional logic, allowing to specify the behavior of a reactive system over time using temporal modalities. Those logics allow to specify *order* on events, but generally not to introduce timing constraints specifying the time value at which an event must occur. Temporal logics allow in particular the specification of properties such as reachability (possibility that a certain event occurs), safety (impossibility that a certain set of events occurs), liveness (ultimate occurrence of a certain event) or fairness (occurrence infinitely often of a certain event). Temporal logics can be either *linear* or *branching*.

Linear Temporal Logic (LTL) is a logic introduced by Pnueli [Pnu77]. It is linear in the sense that it considers that time steps have only one (discrete) successor. Therefore, it is possible to express ordering of events on single paths, and not on tree structures: LTL expresses *path-based properties*. Various variants and extensions of LTL have been studied (see, e.g., [GPSS80, LPZ85, Lam94]). The logic LTL is widely used in the framework of model checking, and various algorithms have been proposed. An efficient model checker allowing to check properties expressed using LTL is Spin [Hol03].

We now consider *branching* temporal logics. Whereas linear temporal logics focus on infinite sequence on states, branching logics focus on infinite trees of states. As a consequence, properties specified using branching temporal logics can express the notion of *choice*, in the sense that one can express the different possible futures of a given state. In particular, CTL [CE82] is a widely used branching temporal logic. As for LTL, CTL is widely used in the framework of model checking, and various algorithms have been proposed. Model checkers include SMV [McM93] (which stands for Symbolic Model Verifier) and NuSMV [CCG<sup>+</sup>02]. It can be shown that the expressiveness of LTL and CTL is incomparable, i.e., some properties can be expressed using LTL only, and some others using CTL only (see, e.g., [BK08] for a survey).

We can consider that temporal logics such as LTL and CTL are *time-abstract* logics, in the sense that they only focus on the order of events, and not on the precise time at which they occur. One can then extend the temporal logics with *time*, thus obtaining *timed* temporal logics. Those logics do not only check that constraints on the order of the events are satisfied, but also that quantitative constraints on delays between these events are satisfied. A famous example of timed temporal logic is the timed CTL (TCTL) logic [ACD93], which allows to express properties specifying both a branching behavior and interval of time within which events may occur. The TCTL logic is widely used in the framework of timed model checking, in particular to verify properties on models expressed using timed automata. Powerful model checkers for (fragments of) TCTL include UPPAAL [LPY97] and KRONOS [Yov97].

**Formalisms for Modeling Timed Systems.** Structures for the modeling and the verification of real-time systems include Time Petri Nets [Mer74], Timed Automata, Time Separation of Events using timing constraint graphs [CSD97], and various extensions. We provide a survey on various formalisms for the modeling of timed systems in Section 2.4.

## 1.3 Organization of the Thesis

This thesis is structured as follows.

In Chapter 2, we recall the major formalisms used in this thesis. We first recall the notion of clocks, parameters and constraints. We then recall timed automata, and their extension to parametric timed automata. We also formally state the good parameters problem we intend to solve in this thesis in the framework of parametric timed automata. We finally justify our choice of the formalism of timed automata, and present its specificities with respect to other timed formalisms (in particular Time Petri Nets).

In Chapter 3, we introduce the inverse method, which allows to generalize the behavior of a timed automaton by synthesizing a constraint on the parameters guaranteeing the same time-abstract behavior.

In Chapter 4, we present our implementation, the tool IMITATOR II, and we apply our method to various case studies of asynchronous hardware circuits and communication protocols.

In Chapter 5, we show how an iteration of the inverse method can solve the good parameters problem for parametric timed automata, by computing a behavioral cartography of the system. We also apply this algorithm to various case studies using IMITATOR II.

In Chapter 6, we extend our inverse method, and the behavioral cartography, to the framework of probabilistic timed automata. In that case, we synthesize a constraint guaranteeing the same values for the minimum and maximum probabilities of reachability properties.

In Chapter 7, we introduce variants of the inverse method for two different frameworks: Directed Weighted Graphs, and Markov Decision Processes.

We finally conclude and present directions of future research in Chapter 8. Related work is mentioned at the end of each chapter.

**VALMEM Project.** This thesis has been done in the framework of the ANR VALMEM project "Functional and Timed Validation of Embedded Memories Using Formal Methods", grant ANR-06-ARFU-005, involving the LIP6 laboratory (Université Pierre et Marie Curie), the LSV laboratory (École Normale Supérieure de Cachan), and the chipset manufacturer ST-Microelectronics.

Many techniques developed in this thesis have been actually designed in order to be able to synthesize constraints to guarantee the good behavior of various models and abstractions of the SPSMALL memory, which is a memory circuit sold by ST-Microelectronics. Due to its internal complexity, this memory has been a very interesting motivation throughout my thesis.

**Joint Work.** Most of this work is a joint work with Laurent Fribourg and Emmanuelle Encrenaz. Thomas Chatain collaborated on the inverse method for parametric timed automata (Chapter 3). Jeremy Sproston collaborated on the extension of the inverse method to the framework of probabilistic timed automata (Chapter 6). The fixpoint of the inverse method benefited from discussion with Laurent Doyen. The counter-example showing the non-CTL equivalence of the inverse method was proposed by Jeremy Sproston.

The analysis of the SPSMALL memory (Section 4.7) has been done in the framework of the ANR VALMEM project involving (besides Emmanuelle Encrenaz, Laurent Fribourg and me) Remy Chevallier (from ST-Microelectronics), Abdelrezzak Bara, Pirouz Bazargan-Sabet, Dominique Le Du and Patricia Renault (from LIP 6). The analysis of the SIMOP Networked Automation System (Section 4.8) has been done in the framework of the SIMOP project in the framework of Institut Farman (Fédération de Recherche CNRS, FR3311), with the contribution of Olivier De Smet, Bruno Denis and Silvain Ruel (LURPA, École Normale Supérieure de Cachan).

When coming to the design and the implementation of the tool IMITATOR II (Chapter 4), Ulrich Kühne implemented several modifications allowing to decrease the computation time. Bertrand Jeannet has been of great help when linking the tool with the APRON library. Daphné Dussaud implemented the graphical output of the cartography. Romain Soulat has been a great contributor of IMITATOR II by applying the tool to various case studies; in particular, he applied the cartography algorithm implemented in IMITATOR II to the SPS-MALL memory, using a very helpful optimization of his own.

## Chapter 2

## **Preliminary Definitions**

You're entering a world of pain.

The Big Lebowski (Joel and Ethan Coen)

In this chapter, we present the formalism used throughout this thesis. We focus on a way to model timed systems by means of timed automata [AD94]. Timed automata are an extension of standard finite-state automata allowing the use of clocks, i.e., real-valued variables increasing linearly at the same rate. Such clocks can be compared with constants in constraints that allow (or not) to stay in a location ("invariants") or to take a transition ("guards"). At each transition, it is possible to reset some of the clocks of the system. This formalism allows the parallel composition of several timed automata, which behave like a single one, and thus provides the designer with a powerful and intuitive way to represent timed systems. Above all, the main theoretical advantage of timed automata relies in its decidability results. In particular, it has been shown that the reachability of a state is decidable. Moreover, various *timed* temporal logics (e.g., [ACD93]) have been designed, and various decidability results have been shown (e.g., [ACD93, HRSV02, WY03]). Finally, it is important to note that the model of Timed Automata is very sensitive to the size of the automata and the number of automata in parallel, thus often leading to the state-space explosion problem. However, powerful tools, such as the UPPAAL [LPY97] model checker, have been designed allowing to model and verify very efficiently timed systems modeled by Timed Automata.

We are interested in this thesis in synthesizing values for timing parameters of a system, guaranteeing a good behavior. As a consequence, we will use a parametric extension of timed automata. Those *parametric timed automata* [AHV93] allow in guards and invariants the use of parameters (in the

sense of unknown constants) in place of rational constants. Unfortunately, for most interesting problems, parametric timed automata lose the decidability results proved for timed automata. In particular, the reachability of a state is not decidable (although semi-algorithms do exist, i.e., if the algorithm terminates, then the result is correct). Moreover, parametric timed automata are even more sensitive to the state space explosion problem, because of the addition of the parameters. In practice, this comes also from the fact that the data structures used to represent parametric timed automata are far less efficient than the ones used for timed automata (typically Difference Bound Matrices, proposed in [BM83] for the analysis of Time Petri Nets, and introduced in [Dil90] for Timed Automata). Structures allowing to handle parametric timed models include Parametric Difference Bound Matrices (an extension of DBMs, proposed in [HRSV02]), SAT-solvers, SMT-solvers and polyhedra. Avoiding the explosion of the state space, and finding cases for which analyses are decidable for parametric timed automata, are actually some of the motivations for this thesis.

We will also state formally in this chapter the good parameters problem in the framework of parametric timed automata. This problem can be considered as the central problem of this thesis.

**Plan of the chapter.** We first recall in Section 2.1 the notion of linear constraints on the clocks and the parameters. We then describe in Section 2.2 the formalism of Timed Automata, and its extension to Parametric Timed Automata. We introduce in Section 2.3 the good parameters problem that we will intend to solve in this thesis. We finally give in Section 2.4 a survey of formalisms used to model timed systems, and justify our choice for dense time representation and parametric timed automata.

#### 2.1 Constraints

#### **2.1.1** Clocks

Let  $\mathbb{R}_{\geq 0}$  be the set of non-negative real numbers.

Throughout this thesis, we assume a fixed set  $X = \{x_1, ..., x_H\}$  of *clocks*. A *clock* is a variable  $x_i$  with value in  $\mathbb{R}_{\geq 0}$ . All clocks evolve linearly at the same rate.

We define a *clock valuation* as a function  $w: X \to \mathbb{R}_{\geq 0}$  assigning a non-negative real value to each clock variable. We will often identify a valuation w with the point  $(w(x_1), \ldots, w(x_H))$ .

2.1. Constraints

Given a constant  $d \in \mathbb{R}_{\geq 0}$ , we use X + d to denote the set  $\{x_1 + d, \dots, x_H + d\}$ . Similarly, we write w + d to denote the valuation such that (w + d)(x) = w(x) + d for all  $x \in X$ .

#### 2.1.2 Parameters

Throughout this thesis, we assume a fixed set  $P = \{p_1, ..., p_M\}$  of *parameters*, i.e., unknown constants.

A parameter valuation  $\pi$  is a function  $\pi: P \to \mathbb{R}_{\geq 0}$  assigning a nonnegative real value to each parameter. There is a one-to-one correspondence between valuations and points in  $(\mathbb{R}_{\geq 0})^M$ . We will often identify a valuation  $\pi$  with the point  $(\pi(p_1), ..., \pi(p_M))$ .

#### 2.1.3 Constraints

**Definition 2.1** (Linear inequality). Let V be a set of variables of the form  $V = \{v_1, \ldots, v_N\}$ . A *linear inequality on the variables of* V is an inequality e < e', where  $e < \{<, \le\}$ , and e, e' are two linear terms of the form

$$\sum_{1 \le i \le N} \alpha_i v_i + d$$

where  $v_i \in V$ ,  $\alpha_i \in \mathbb{Q}_{\geq 0}$ , for  $1 \leq i \leq N$ , and  $d \in \mathbb{Q}_{\geq 0}$ .

Note that we define the coefficients of the linear inequalities as *positive rationals*. It would of course be equivalent to define them as *positive integers*, as it is sometimes the case in the literature.

We assume in the following that all inequalities are linear, and we will simply refer to linear inequalities as *inequalities*.

**Definition 2.2** (Negation of an inequality). Let V be a set of variables of the form  $V = \{v_1, ..., v_N\}$ . Given an inequality J on the variables of V of the form e < e' (resp.  $e \le e'$ ), the *negation* of J, denoted by  $\neg J$ , is the linear inequality  $e' \le e$  (resp. e' < e).

**Definition 2.3** (Convex linear constraint). Let V be a set of variables of the form  $V = \{v_1, \ldots, v_N\}$ . A *convex linear constraint on the variables of* V is a conjunction of inequalities on the variables of V.

We assume in the following that all constraints are both convex and linear, and we will simply refer to convex linear constraints as *constraints*.

**Definition 2.4** (Constraint on the clocks). An *inequality on the clocks* is an inequality on the set of variables X. A *constraint on the clocks* is a constraint on the set of variables X.

**Definition 2.5** (Constraint on the parameters). An *inequality on the parameters* is an inequality on the set of variables P. A *constraint on the parameters* is a constraint on the set of variables P.

**Definition 2.6** (Constraint on clocks and parameters). An *inequality on the clocks and the parameters* is an inequality on the set of variables  $X \cup P$ . A *constraint on the clocks and the parameters* is a constraint on the set of variables  $X \cup P$ .

Throughout this thesis, we will denote by  $\mathcal{K}_X$  the set of all constraints on the clocks, by  $\mathcal{K}_P$  the set of all constraints on the parameters, and by  $\mathcal{K}_{X \cup P}$  the set of all constraints on the clocks and the parameters.

In the sequel, the letter J will denote an inequality on the parameters, the letter D will denote a constraint on the clocks, the letter K will denote a constraint on the parameters, and the letter C will denote a constraint on the clocks and the parameters.

**Semantics of Constraints.** Given a constraint D on the clocks and a clock valuation w, D[w] denotes the expression obtained by replacing each clock x in D with w(x). A clock valuation w satisfies constraint D (denoted by  $w \models D$ ) if D[w] evaluates to true.

Given a parameter valuation  $\pi$  and a constraint C on the clocks and the parameters,  $C[\pi]$  denotes the constraint on the clocks obtained by replacing each parameter p in C with  $\pi(p)$ . Likewise, given a clock valuation w,  $C[\pi][w]$  denotes the expression obtained by replacing each clock x in  $C[\pi]$  with w(x). We say that a parameter valuation  $\pi$  satisfies a constraint C, denoted by  $\pi \models C$ , if the set of clock valuations that satisfy  $C[\pi]$  is nonempty. We use the notation  $< w, \pi > \models C$  to indicate that  $C[\pi][w]$  evaluates to true.

Given two constraints  $C_1$  and  $C_2$  on the clocks and the parameters, we say that  $C_1$  is *included in*  $C_2$ , denoted by  $C_1 \subseteq C_2$ , if  $\forall w, \pi : \langle w, \pi \rangle \models C_1 \Rightarrow \langle w, \pi \rangle \models C_2$ . We have that  $C_1 = C_2$  if and only if  $C_1 \subseteq C_2$  and  $C_2 \subseteq C_1$ .

Similarly to the semantics of constraints on the clocks and the parameters, we say that a parameter valuation  $\pi$  *satisfies* a constraint K on the parameters, denoted by  $\pi \models K$ , if the expression obtained by replacing each parameter p in K with  $\pi(p)$  evaluates to true. Given two constraints  $K_1$  and  $K_2$  on the parameters, we say that  $K_1$  is *included in*  $K_2$ , denoted by  $K_1 \subseteq K_2$ , if  $\forall \pi : \pi \models K_1 \Rightarrow \pi \models K_2$ . We have that  $K_1 = K_2$  if and only if  $K_1 \subseteq K_2$  and  $K_2 \subseteq K_1$ . We will consider true as a constraint on the parameters, corresponding to the set of all possible values for P.

Given a constraint C on the clocks and the parameters, we denote by  $\exists X : C$  the constraint on the parameters obtained from C after elimination of the clock variables, i.e.,  $\{\pi \mid \exists w : \langle w, \pi \rangle \models C\}$ .

2.2. Timed Automata

#### 2.2 Timed Automata

#### 2.2.1 Labeled Transition Systems

We first introduce labeled transition systems, which will be used later in this section to represent the semantics of timed automata.

**Definition 2.7** (LTS). A *labeled transition system (LTS)* over a set of symbols  $\Sigma$  is a triple  $\mathcal{L} = (S, S_0, \Rightarrow)$ , with S a set of *states*,  $S_0 \subset S$  a set of *initial states*, and  $\Rightarrow \in S \times \Sigma \times S$  a *transition relation*. We write  $s \stackrel{a}{\Rightarrow} s'$  for  $(s, a, s') \in \Rightarrow$ . A *run* (of length m) of  $\mathcal{L}$  is a finite alternating sequence of states  $s_i \in S$  and symbols  $a_i \in \Sigma$  of the form  $s_0 \stackrel{a_0}{\Rightarrow} s_1 \stackrel{a_1}{\Rightarrow} \cdots \stackrel{a_{m-1}}{\Rightarrow} s_m$ , where  $s_0 \in S_0$ . A state  $s_i$  is *reachable* if it belongs to some run r.

#### 2.2.2 Timed Automata

We introduce here timed automata as defined in [AD94]. Timed automata are an extension of standard finite-state automata allowing the use of clocks, i.e., real-valued variables increasing linearly at the same rate.

#### **Syntax**

**Definition 2.8** (Timed Automaton). A *Timed Automaton (TA)*  $\mathscr{A}$  is a 6-tuple of the form  $\mathscr{A} = (\Sigma, Q, q_0, X, I, \rightarrow)$ , where

- $\Sigma$  is a finite set of actions,

- *Q* is a finite set of locations,

- $q_0 \in Q$  is the initial location,

- X is a set of clocks,

- I is the invariant, assigning to every  $q \in Q$  a constraint I(q) on the clocks, and

- $\rightarrow$  is a step relation consisting of elements of the form  $(q, g, a, \rho, q')$ , also denoted by  $q \stackrel{g,a,\rho}{\rightarrow} q'$ , where  $q, q' \in Q$ ,  $a \in \Sigma$ ,  $\rho \subseteq X$  is a set of clock variables to be reset by the step, and g (the step guard) is a constraint on the clocks.

Note that we use a more permissive definition of the constraints used in guards and invariants than in the original definition of TAs (see [AD94]). Indeed, we allow the use of conjunctions of any linear inequalities on the clocks, whereas the original definition usually considers conjunctions of comparisons of a single clock with a constant. This more permissive definition has usually an impact on the decidability (the addition of clock values within a constraint leads to undecidability [AD94]), but this has no impact in this thesis, mainly because of the use of *parametric* timed automata, where the parameters bring themselves undecidability in the general case.

Timed Automata are often extended in practice with *discrete variables*, which can be used in guards and transitions, updated within the transitions, and sometimes even used as a factor for clocks. However, in most cases, there represent only syntactic sugar for the discrete space (i.e., locations). As a consequence, we will not use them in any theoretical part of this thesis. Note nevertheless that our implementation (see Chapter 4) allows the use of such discrete variables.

The graphical representation of a TA  $\mathscr{A}$  is an oriented graph where vertices correspond to locations, and edges correspond to actions of  $\mathscr{A}$ . We follow the following conventions for the graphical representation of timed automata: locations are represented by nodes, above of which the invariant of the location is written; transitions are represented by arcs from one location to another location, labeled by the associated guard, the action name and the set of clocks to be reset (guards and invariants equal to true will be omitted). The initial location is usually represented with a double circle.

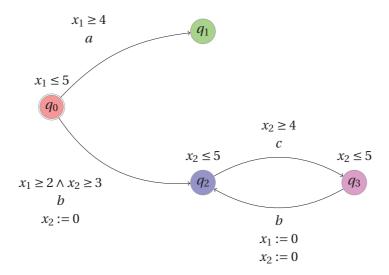

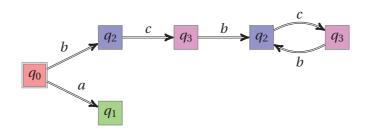

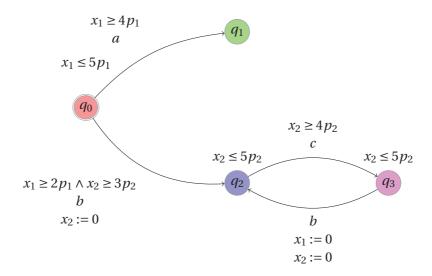

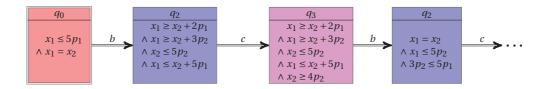

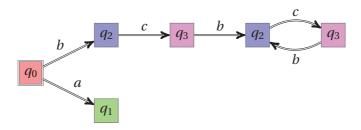

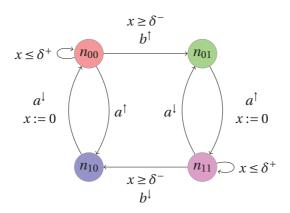

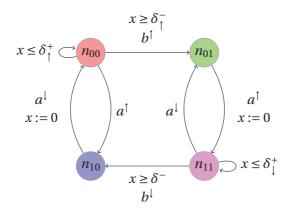

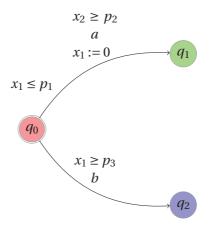

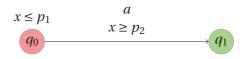

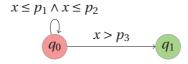

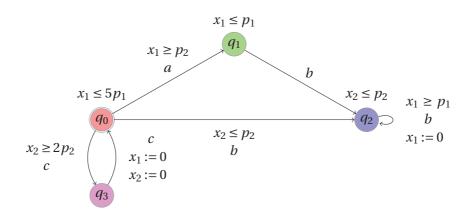

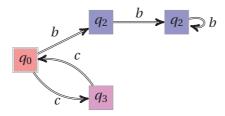

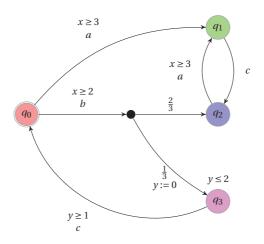

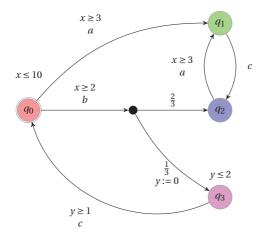

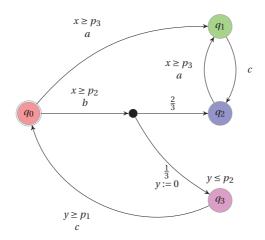

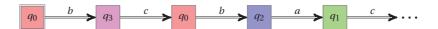

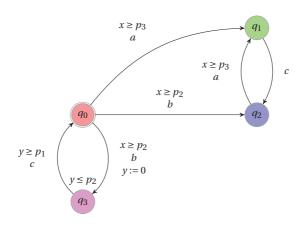

*Example* 2.9. We give in Figure 2.1 an example of Timed Automaton containing 4 locations (viz.,  $q_0$ ,  $q_1$ ,  $q_2$  and  $q_3$ ), 3 actions (viz., a, b and c) and 2 clocks (viz.,  $x_1$  and  $x_2$ ). The initial location is  $q_0$ .

In this TA,  $q_0$  has invariant  $x_1 \le 5$ ,  $q_1$  has invariant true, and both  $q_2$  and  $q_3$  have invariant  $x_2 \le 5$ . The transition from  $q_0$  to  $q_1$  has guard  $x_1 \ge 4$  through action a; no clock is reset. The transition from  $q_0$  to  $q_2$  has guard  $x_1 \ge 2 \land x_2 \ge 3$  through action b, and resets clock  $x_2$ . The transitions between  $q_2$  and  $q_3$  can be explained similarly.

#### **Parallel Composition of TAs**

We now introduce the notion of network of timed automata, and show in the following definition how N TAs can be composed into a single TA.

П

Figure 2.1: An example of Timed Automaton

**Definition 2.10** (Network of TAs). Let  $N \in \mathbb{N}$ . For all  $1 \leq i \leq N$ , let  $\mathcal{A}_i = (\Sigma_i, Q_i, (q_0)_i, X_i, I_i, \rightarrow_i)$  be a TA. The sets  $Q_i$  and  $X_i$  are mutually disjoint. A *network of timed automata* (NTA) is  $\mathcal{A} = \mathcal{A}_1 \| \dots \| \mathcal{A}_N$ , where  $\|$  is the operator for parallel composition defined in the following way. This NTA corresponds to the TA  $\mathcal{A} = (\Sigma, Q, q_0, X, I, \rightarrow)$  where

- $\Sigma = \bigcup_{i=1}^{N} \Sigma_i$ ,

- $Q = \prod_{i=1}^{N} Q_i$ ,

- $q_0 = \langle (q_0)_1, \dots, (q_0)_N \rangle$ ,

- $X = \biguplus_{i=1}^{N} X_i$ ,

- $I(\langle q_1, ..., q_N \rangle) = \bigwedge_{i=1}^N I_i(q_i)$  for all  $\langle q_1, ..., q_N \rangle \in Q$ ,

and  $\rightarrow$  is defined as follows. For all  $a \in \Sigma$ , let  $T_a$  be the subset of indices  $i \in 1,...,N$  such that  $a \in \Sigma_i$ . For all  $a \in \Sigma$ , for all  $\langle q_1,...,q_N \rangle \in Q$ , for all  $\langle q'_1,...,q'_N \rangle \in Q$ ,  $(\langle q_1,...,q_N \rangle, g,a,\rho,\langle q'_1,...,q'_N \rangle) \in \rightarrow$  if:

- for all  $i \in T_a$ , there exist  $g_i$ ,  $\rho_i$  such that  $(q_i, g_i, a, \rho_i, q_i') \in \rightarrow_i$ ,  $g = \bigwedge_{i \in T_a} g_i$ ,  $\rho = \bigcup_{i \in T_a} \rho_i$ , and,

- for all  $i \notin T_a$ ,  $q'_i = q_i$ .

Note that the requirement that the set of clocks of each of the TAs in parallel be mutually disjoint is not a strong requirement from a theoretical point of view in this thesis. However, it is almost always met in practice.

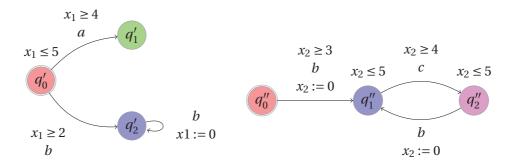

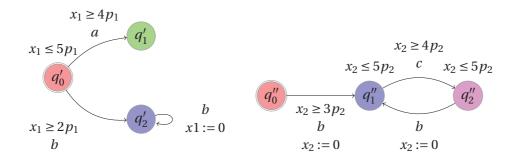

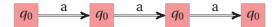

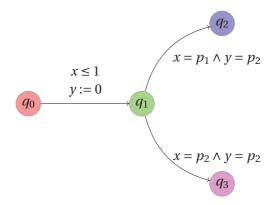

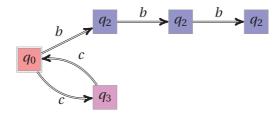

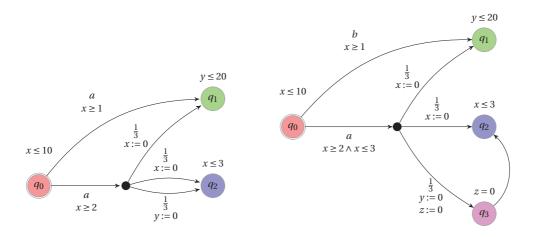

*Example* 2.11. We give in Figure 2.2 an example of Network of 2 TAs. The left one (say,  $\mathcal{A}'$ ) contains 3 locations (viz.,  $q'_0$ ,  $q'_1$ , and  $q'_2$ ), 2 actions (viz., a and b) and 1 clock  $x_1$ . The right one (say,  $\mathcal{A}''$ ) contains 3 locations (viz.,  $q''_0$ ,  $q''_2$ , and  $q''_3$ ), 2 actions (viz., b and b) and 1 clock b.

Figure 2.2: Example of Network of Timed Automata

Then, the composition of those 2 TAs in parallel (viz.,  $\mathscr{A}' \| \mathscr{A}''$ ) corresponds to the TA from Example 2.9, where  $q_0 = (q_0', q_0'')$ ,  $q_1 = (q_1', q_0'')$ ,  $q_2 = (q_2', q_1'')$  and  $q_3 = (q_2', q_2'')$ .

#### **Semantics**

The semantics of TAs is given under the form of a LTS, where states are couples made by a location and a valuation for each clock.

**Definition 2.12** (Semantics of TAs). Let  $\mathscr{A} = (\Sigma, Q, q_0, X, I, \rightarrow)$  be a Timed Automaton. The *concrete semantics of*  $\mathscr{A}$  is the LTS  $(S, S_0, \Rightarrow)$  over  $\Sigma$  where

$$S = \{(q, w) \in Q \times (X \to \mathbb{R}_{\geq 0}) \mid w \models I(q)\},\$$

$$S_0 = \{(q_0, w) \mid w \models I(q_0) \land w = (w_0, ..., w_0) \text{ for some } w_0\}$$

and the transition predicate  $\Rightarrow$  is specified by the following three rules. For all  $(q, w), (q', w') \in S, d \ge 0$  and  $a \in \Sigma$ ,

$$-(q,w) \xrightarrow{a} (q',w')$$

if  $\exists g, \rho : q \xrightarrow{g,a,\rho} q'$  and  $w \models g$  and  $w' = \rho(w)$ ;

$$-(q, w) \xrightarrow{d} (q', w')$$

if  $q' = q$  and  $w' = w + d$ ;

$$-(q,w) \stackrel{a}{\Rightarrow} (q',w') \text{ if } \exists d,w'': (q,w) \stackrel{a}{\rightarrow} (q',w'') \stackrel{d}{\rightarrow} (q',w').$$

We consider with the definition of  $S_0$  that all clocks are initially set to 0, or have evolved linearly in the bounds given by  $I(q_0)$ . A state (resp. run) in the concrete semantics will be referred to as a *concrete state* (resp. *concrete run*).

A concrete run is represented by a directed graph where states are depicted within nodes containing the name of the location and the value of each of the clocks, and transitions are depicted using edges labeled with the name of the action.

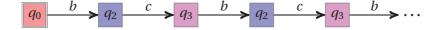

*Example* 2.13. Consider again the timed automaton  $\mathscr{A}$  of Example 2.1. Then Figure 2.3 depicts an example of concrete run for  $\mathscr{A}$ .

Figure 2.3: Example of concrete run for a TA

This run is obtained as follows: one starts from the initial location  $q_0$  where both clocks have evolved during 3 time units. Then, we take action b, reset  $x_2$  and spend 4 time units in  $q_2$ . Then, we take action c, and spend 0.5 time unit in  $q_3$ . Then, we take action b, reset both clocks and spend 4.2 time units in  $q_2$ . Then, we take action c, and spend 0.8 time units in  $q_3$ , and so on.

The power of timed automata relies in the fact that one can construct a finite partition of the infinite space of clock valuations. In particular, this construction is suitable to perform reachability analysis.

The main theoretical advantage of Timed Automata relies in its decidability results. In particular, it has been shown that the reachability of a state is decidable. Moreover, various *timed* temporal logics (e.g., [ACD93]) have been designed, and various decidability results have been shown (e.g., [ACD93, HRSV02, WY03]).

#### **Traces**