# Etude de régulateurs linéaires et à découpage intégrés : Application à la téléphonie portable

Cécile Hamon

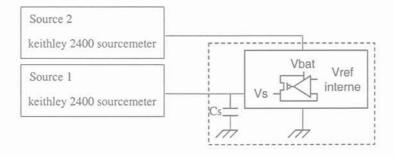

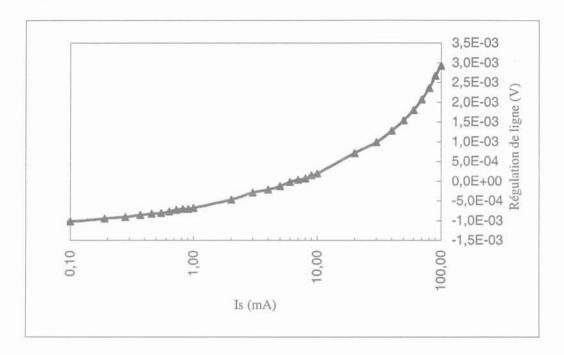

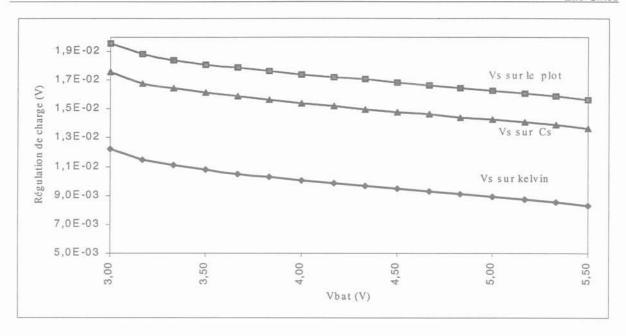

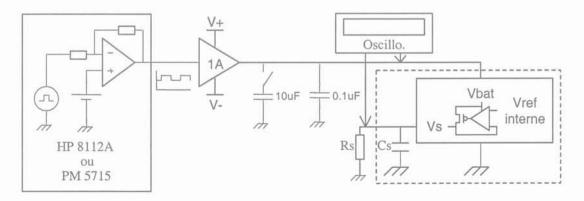

#### ▶ To cite this version:

Cécile Hamon. Etude de régulateurs linéaires et à découpage intégrés : Application à la téléphonie portable. Sciences de l'ingénieur [physics]. Université de Grenoble, 2001. Français. NNT : . tel-00599163

# HAL Id: tel-00599163 https://theses.hal.science/tel-00599163

Submitted on 8 Jun 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITE GRENOBLE I - JOSEPH FOURIER

## 1\_\_\_\_\_\_

## THESE

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITE GRENOBLE I

Discipline : Génie électrique

Présentée et soutenue publiquement

Par

Cécile HAMON

Le 27 Septembre 2001

# ETUDE DE REGULATEURS LINEAIRES ET A DECOUPAGE INTEGRES : APPLICATION A LA TELEPHONIE PORTABLE

Directeurs de thèse :

J.P. FERRIEUX

Y. LEMBEYE

#### JURY

M. F Ndagijimana Président

M. JP Chante Rapporteur

M. JL Sanchez Rapporteur

M. JP Ferrieux Directeur de thèse

M. Y Lembeye Directeur de thèse

M. C Bernard Industriel

Thèse préparée au sein du Laboratoire d'Electrotechnique de Grenoble et de STMicroelectronics

## REMERCIEMENTS

Ces travaux ont été effectués au sein de STMicroelectronics à Grenoble, en étroite collaboration avec le Laboratoire d'Electrotechnique de Grenoble. Je tiens à remercier **Patrick Bernard** d'avoir initié ce projet.

Je suis très reconnaissante envers les membres de mon jury :

- Monsieur Jean-Pierre Chante, Professeur à l'INSA de Lyon et rapporteur pour avoir apporté toute son attention à cette étude.

- Monsieur Jean-Louis Sanchez, Directeur de Recherches au CNRS de Toulouse et fervent utilisateur de téléphone portable, qui a également accepté d'être rapporteur.

- Monsieur Fabien Ndagijimana, Professeur à l'Université Joseph Fourier, qui a assuré la présidence de ce jury.

- Monsieur Jean-Paul Ferrieux, Professeur à l'Université Joseph Fourier qui a dirigé

ma thèse et à qui je tiens à exprimer toute ma reconnaissance pour ses conseils, sa

disponibilité et ses réponses scientifiques.

- Monsieur Yves Lembeye, Maître de Conférences à l'Université Joseph Fourier qui a également encadré mes travaux en m'initiant aux joies du découpage et qui a toujours été à mon écoute.

- Monsieur Christophe Bernard, ingénieur de STMicroelectronics, qui a également pris le temps nécessaire pour répondre à mes questions et me conseiller. Merci beaucoup.

Je tiens à remercier tout particulièrement **Alexandre Pons** pour tout ce qu'il a fait pour moi pendant ces trois ans. Alex, tu as été là pour me faire découvrir le monde « intégré » de la régulation linéaire, me conseiller et m'encourager, alors mille fois merci pour ta patience, ta générosité, et ta bonne humeur.

L'étude sur les alimentations à découpage n'aurait pu se faire sans les explications et l'aide précieuse de **David Chesneau** et **Christophe Premont** (cou couleur 3 sur 89.4), je tiens donc à les remercier pour cela, tout comme **Philippe Goubier** « Goubs » pour le travail qu'il a effectué sur les pompes de charges et qui m'a permis d'appréhender ce sujet.

La réussite de mes travaux est également due à toutes les personnes qui se sont occupées de la réalisation du layout de mes cellules ou qui m'y ont initié, **Delphine Bouchereau** (Vive Super Mulot!), **Frank Tellier** (A quand les pizzas?) et **Fabienne Grigis** (Reine des vérifications).

Je tiens également à affirmer toute ma considération à tous ceux qui m'ont expliqué et aidé lors de la caractérisation des mes cellules, Jean Redolfi qui m'a fait une place dans son équipe dès que j'en ai eu besoin, Sébastien Cany, Florence Caranana, Gaël Jaffrain, Anne-Laure Combe et Bernard Billion qui ont toujours pris le temps de répondre à mes nombreuses questions. Il va sans dire que je dois beaucoup à Pierre Daude et que je suis fière d'avoir été « son élève ».

Merci également aux nombreuses personnes de la CAD et de «l'assistance informatique» qui étaient toujours présentes pour me dépanner, ainsi qu'aux déménageurs pour leur efficacité et leur promptitude.

Les moments que j'ai passés au sein du Laboratoire d'Electrotechnique de Grenoble ont été un réel plaisir et j'ai une pensée particulière pour les anciens thésards, thésards actuels et stagiaires avec qui j'ai passé de très bons moments dans la salle EPTE. Parmi ceux-ci, Guillaume Verneau, mais aussi tant d'autres qui m'ont aidée et conseillée en toute occasion...Merci beaucoup pour les fleurs, elles sont magnifiques.

Merci beaucoup à toutes les personnes que j'ai rencontrées et avec qui j'ai eu énormément de plaisir à discuter (et à travailler) : Sylvie, Mickaëlle (Vive le Kouign aman libre), Christian (Meuuuhh), Philippe, Régis, Joël, Alex... et toutes les autres personnes que j'ai côtoyées mais que je n'ai pu citer ici.

Il ne faut pas oublier les amis qui sont venus me soutenir lors de ma présentation : Thierry, Roger, Olivier, Vincent, Charles, Fred, Manu, Christophe...

Je remercie également du fond du cœur mes parents et mes familles pour m'avoir soutenue et encouragée depuis le tout début. Mes derniers remerciements vont à **Christophe** : « Merci pour ton sourire et nos éclats de rire, particulièrement pendant ces trois années ».

Avant que vous ne commenciez la lecture de ce manuscrit, je vous livre ma perle préférée parmi celles que j'avais immanquablement écrites :

« Les téléphones potables »

# TABLE DES MATIERES

| REMERCIEMENTS                                                            | i  |

|--------------------------------------------------------------------------|----|

|                                                                          |    |

| INTRODUCTION                                                             | 7  |

|                                                                          |    |

| 1 GENERALITES                                                            | 13 |

| 1 GENERALITES                                                            | 10 |

| Introduction                                                             | 13 |

| INTRODUCTION                                                             | 1. |

| 1.1 Presentation Des Besoins                                             | 13 |

|                                                                          |    |

| 1.2 Presentations Des Trois Types De Regulateur De Tension               | 15 |

| 1.2.1 REGULATEURS LINEAIRES                                              | 15 |

| 1.2.1.1 Principe de fonctionnement général des régulateurs linéaires     | 15 |

| 1.2.1.2 Cas des régulateurs de tension de type LDO                       | 16 |

| 1.2.2 ALIMENTATION A DECOUPAGE DE TYPE SMPS                              | 17 |

| 1.2.2.1 Principe de fonctionnement des hacheurs                          | 18 |

| 1.2.3 POMPE DE CHARGE, CP                                                | 19 |

| 1.3 Les Technologies                                                     | 20 |

| 1.3.1 Composants Semi-Conducteurs                                        | 20 |

| 1.3.1.1 Présentation des familles de technologie                         | 20 |

| 1.3.1.2 Composants disponibles, cas de la technologie CMOS analogique 5V | 21 |

| 1.3.2 Composants Externes                                                | 25 |

| 1.3.2.1 Pourquoi cette étude ?                                           | 25 |

| 1.3.2.2 Batteries                                                        | 26 |

| 1.3.2.3 Condensateurs                                                    | 33 |

| 1.3.2.3.1 Condensateurs en céramique multicouches                        | 34 |

| 1.3.2.3.1.1 Diélectrique de type 1                                       | 35 |

| 1.3.2.3.1.2 Diélectrique de type 2                                       | 35 |

| 1.3.2.3.2 Condensateurs en tantale                                       | 39 |

| 1.3.2.4 Inductances                                                      | 43 |

| Conclusion                                                               | 46 |

| 2 LDO CMOS                                                                                             | 51         |

|--------------------------------------------------------------------------------------------------------|------------|

| Introduction                                                                                           | 51         |

| 2.1 POURQUOI UTILISER UNE TECHNOLOGIE CMOS ?                                                           | 52         |

| 2.2 VOCABULAIRE ASSOCIE                                                                                | 52         |

| 2.2.1 Drop-out, Tension De Dechet                                                                      | 53         |

| 2.2.2 COURANT DE SORTIE MAXIMUM (EN FONCTIONNEMENT NORMAL)                                             | 53         |

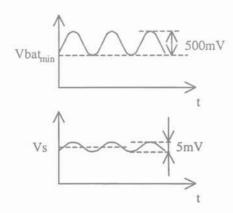

| 2.2.3 REJECTION DE L'ALIMENTATION                                                                      | 54         |

| 2.2.4 Consommation 2.2.5 Rendement                                                                     | 55         |

| 2.2.6 REGULATION DE LIGNE                                                                              | 55<br>55   |

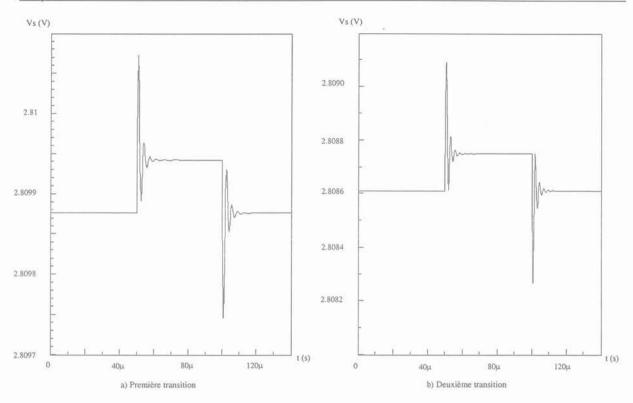

| 2.2.7 REGULATION DE LIGNE  2.2.7 REGULATION DE LIGNE TRANSITOIRE                                       | 55         |

| 2.2.8 REGULATION DE CHARGE                                                                             | 56         |

| 2.2.9 REGULATION DE CHARGE TRANSITOIRE                                                                 | 56         |

| 2.2.10 Precision Sur La Tension De Sortie                                                              | 57         |

| 2.2.11 PROTECTION CONTRE LES COURTS-CIRCUITS                                                           | 57         |

| 2.2.12 TEMPS D'ETABLISSEMENT DE LA TENSION DE SORTIE                                                   | 57         |

| 2.2.13 Bruit                                                                                           | 58         |

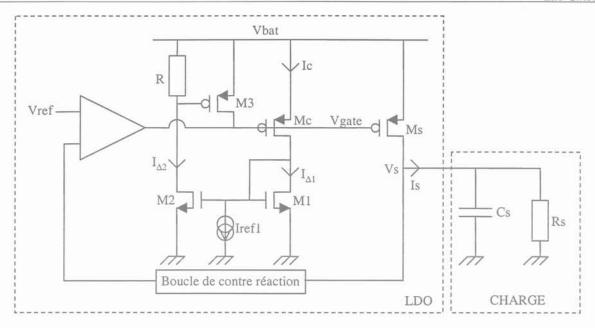

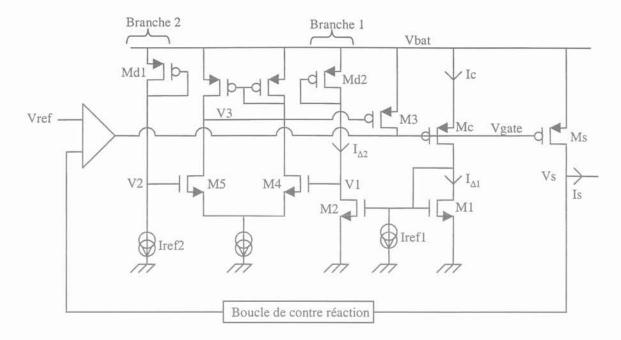

| 2.3 REALISATION                                                                                        | 58         |

| 2.3.1 L'AMPLIFICATEUR                                                                                  | 59         |

| 2.3.2 LA BOUCLE DE CONTRE REACTION                                                                     | 66         |

| 2.3.3 Mos De Sortie                                                                                    | 69         |

| 2.4 COMPENSATION DYNAMIQUE                                                                             | 71         |

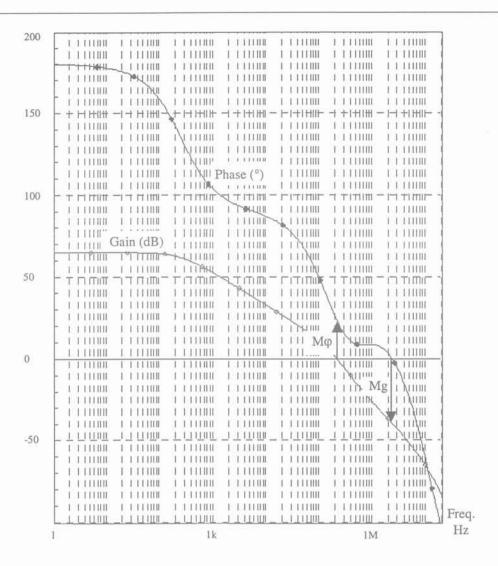

| 2.4.1 RAPPEL SUR LA STABILITE DES SYSTEMES BOUCLES                                                     | 71         |

| 2.4.1.1 Critères de stabilité                                                                          | 72         |

| 2.4.1.2 Degré de stabilité                                                                             | 72         |

| 2.4.2 PRINCIPE DE COMPENSATION D'UN REGULATEUR LINEAIRE 2.4.2.1 Définition des pôles sans compensation | 74<br>74   |

| 2.4.2.1 Définition des pôles sans compensation 2.4.2.2 LDO avec un condensateur externe                | 75         |

| 2.4.2.3 LDO avec compensation Miller                                                                   | 77         |

| 2.4.2.3.1 Rappel sur la compensation Miller                                                            | 77         |

| 2.4.2.3.2 Zéro Miller                                                                                  | 78         |

| 2.4.3 APPLICATION AU LDO EN TECHNOLOGIE CMOS                                                           | 78         |

| 2.4.3.1 Définitions des pôles et des zéros                                                             | 78         |

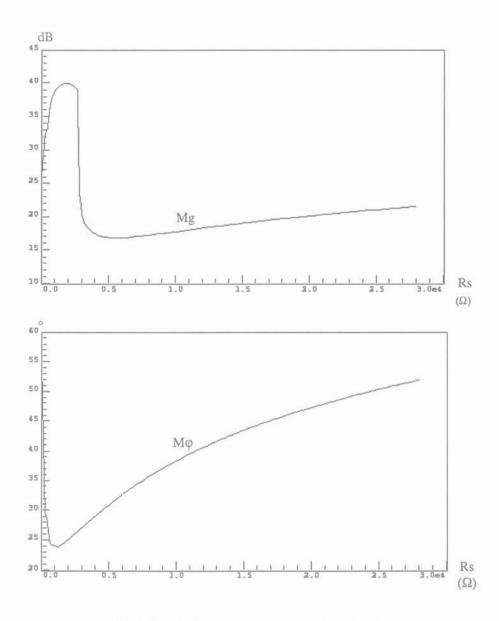

| 2.4.3.2 Déplacement des pôles en fonction du courant de sortie dans notre cas                          | 83         |

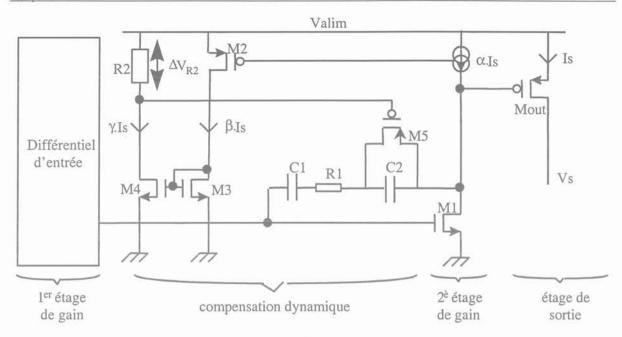

| 2.4.3.3 Méthode développée pour la compensation du LDO CMOS                                            | 88         |

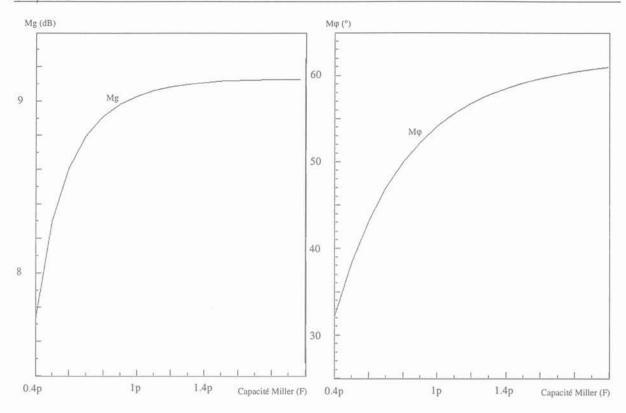

| 2.4.3.3.1 Variation du condensateur Miller                                                             | 88         |

| 2.4.3.3.2 Commande                                                                                     | 89         |

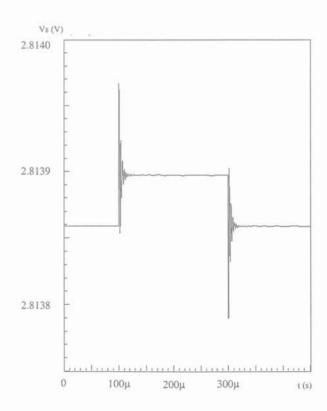

| 2.4.3.3.3 Simulations de vérification                                                                  | 91         |

| 2.5 PROTECTION CC                                                                                      | 94         |

| 2.5.1 ASSERVISSEMENT EN COURANT CLASSIQUE                                                              | 94         |

| 2.5.2 Nouvelle Protection Contre Les Courts-Circuits - Partie Statique                                 | 96         |

| 2.5.3 PARTIE DYNAMIQUE                                                                                 | 100        |

| 2.5.4 PRE POLARISATION EN PDN 2.5.5 IMPRECISION DU COURANT DE REFERENCE                                | 102<br>103 |

| 2.5.6 SIMULATIONS DE VERIFICATION                                                                      | 103        |

171

Etude analytique de la stabilité

3.3.4.3

| 3.4   | INTRODUCTION AUX POMPES DE CHARGES                               | 177 |

|-------|------------------------------------------------------------------|-----|

| 3.4.1 | PRINCIPE DE FONCTIONNEMENT DES ALIMENTATIONS A POMPES DE CHARGES | 178 |

| 3.4.2 | STRUCTURE ×1, ×2 – DOUBLEUR DE TENSION                           | 180 |

| 3.4.3 | ETUDE D'UNE STRUCTURE AUTORISANT PLUSIEURS RAPPORTS DE TENSION   | 181 |

| Con   | CLUSION                                                          | 188 |

| CON   | NCLUSION GENERALE                                                | 191 |

| ANN   | TEXES                                                            | 195 |

| BIBI  | LIOGRAPHIE                                                       | 223 |

# **INTRODUCTION GENERALE**

Le marché des équipements portables connaît une croissance importante et, bien que cette croissance ne soit pas toujours régulière, le besoin de systèmes électroniques, de plus en plus miniaturisés et autonomes, ira grandissant.

Un des facteurs clés de ces systèmes portables, à l'image de la téléphonie mobile, est l'autonomie qui dépend essentiellement de la source d'énergie, mais aussi de la façon dont sont gérés la tension et le courant qu'elle délivre, facteurs relatifs à l'alimentation et à son rendement. Le deuxième critère important pour le concepteur est bien sûr la compacité où l'alimentation est un maillon souvent considéré comme perturbateur. En effet, les dimensions et le poids des téléphones portables sont non seulement des points particulièrement critiques, mais le coût du silicium impose des dimensions de circuits intégrés de plus en plus petites.

La gestion de l'énergie au sein de ces systèmes est devenue un véritable challenge où, d'une part, on trouve généralement une batterie dont la tension évolue au cours de l'utilisation et, d'autre part, des circuits de fonctionnalités diverses avec des tensions d'alimentation régulées, parfois supérieures à celle de la batterie.

C'est dans ce contexte que mes travaux de thèse se sont déroulés entre la société STMicroelectronics et le Laboratoire d'Electrotechnique de Grenoble. L'objectif à long terme est la conception d'un régulateur, le plus dense possible, avec des performances de rendement et de régulation satisfaisantes.

Nous nous sommes tout d'abord concentrés sur les régulateurs linéaires et plus particulièrement les LDO (Low Drop Out) dont l'inconvénient généralement mis en avant, le faible rendement, est contrebalancé par un faible niveau de bruit.

L'alternative naturelle à cette classe de régulateurs sont les alimentations à découpage qui procurent en plus la possibilité d'élévation et d'inversion de la tension de batterie. Bien

que ces systèmes à découpage présentent en théorie un très bon rendement, les contraintes liées à la technologie en basse tension font que celui-ci peut être comparable à celui des régulateurs linéaires. De plus, ils nécessitent des éléments inductifs additionnels difficilement intégrables.

Les systèmes à pompe de charges seront abordés, de façon moins approfondie, à la fin de ce mémoire. Egalement basés sur le principe du découpage, ils sont un compromis entre les deux précédents principes et permettent, moyennant des pertes supplémentaires, d'éviter l'utilisation des composants inductifs.

Le mémoire de thèse se décompose en trois parties principales :

Un chapitre général situe le contexte de l'étude en présentant brièvement les différents types de régulateurs de tension, leur principe de fonctionnement ainsi qu'un premier aperçu global sur leurs points forts et leurs inconvénients. Nous décrirons ensuite la façon dont se compose une famille de technologies pour les composants internes des circuits intégrés réalisés par STMicroelectronics, puis nous détaillerons les caractéristiques des composants électriques disponibles dans la technologie CMOS analogique qui sera employée pour la réalisation de nos cellules. Comme la conception des régulateurs est dépendante des composants externes à ceux-ci, nous terminerons cette partie par une description des différentes possibilités que nous pouvons rencontrer, d'une part en ce qui concerne la batterie, et d'autre part pour les composants électriques non intégrables tels que certains condensateurs et les inductances.

La partie relative à la conception d'un régulateur linéaire de type LDO débute par une explication sur le besoin d'utiliser dorénavant une technologie CMOS analogique pour la réalisation de cette fonction. Elle continue ensuite par la définition du vocabulaire spécifique à la régulation de tension, vocabulaire qui sera utilisé tout au long de cet exposé. A partir de là, nous présenterons la réalisation finalement obtenue, ce qui permettra d'approfondir par la suite les points clés sur lesquels notre étude s'est portée : l'étude de la stabilité du LDO ainsi que la méthode de protection contre les courts-circuits. En effet l'optimisation des performances électriques statiques et dynamiques du régulateur n'est pas une chose aisée car il est souvent difficile d'améliorer une caractéristique de régulation sans pour autant dégrader la stabilité du système. Nous expliquerons donc le principe de compensation habituellement utilisé pour les LDO, puis nous verrons qu'avec la technologie CMOS analogique que nous avons employée, nous avons dû développer une méthode toujours basée sur ce principe, mais qui permet une adaptation en fonction du courant de sortie du régulateur, facilitant ainsi la

stabilisation pour une plus grande plage de courant de sortie. Pour le second point, la protection contre les courts-circuits, nous débuterons aussi par la description de la méthode classiquement utilisée, puis nous présenterons l'amélioration que nous y avons apportée. Une réalisation sur silicium du LDO conçu nous a permis de finaliser cette étude par des mesures qui ont permis de retrouver les résultats des simulations précédemment évoquées. Les méthodes de mesures et leurs résultats font l'objet du dernier paragraphe de ce chapitre.

Un dernier chapitre traite des régulateurs de tension à découpage et des alimentations à pompes de charges.

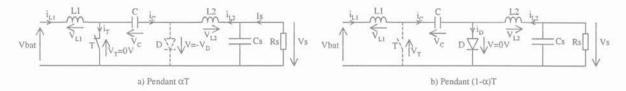

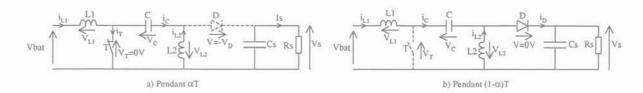

Après avoir expliqué l'intérêt et le besoin de concevoir des régulateurs de tension à partir de telles architectures, nous rappellerons brièvement le principe de commutation, ainsi que les lois de l'électronique de puissance qui sont à la base du découpage. Nous pourrons ainsi aborder le fonctionnement de plusieurs structures de cœur d'alimentation à découpage, ce qui nous permettra de déterminer celle qui répond le mieux à nos contraintes d'intégration.

Nous analyserons ensuite le comportement statique de la structure retenue afin d'en déterminer les pertes et la dégradation de rendement inhérente. Un dernier aspect de ce type de régulateur de tension concerne l'étude de son comportement en fréquence, et plus particulièrement de sa stabilité. Pour cela, nous développerons le calcul de sa fonction de transfert, que nous analyserons. Nous pourrons ainsi proposer une solution de compensation qui sera validée par des simulations.

Nous terminerons ce chapitre par une introduction sur le fonctionnement et le calcul des rendements théoriques des alimentations à pompes de charges.

Nous conclurons par une discussion sur les améliorations envisageables dans une perspective d'intégration et d'amélioration de certaines performances.

# CHAPITRE 1 GENERALITES

#### INTRODUCTION

| 1.1 Presentation Des Be | ESOINS |

|-------------------------|--------|

|-------------------------|--------|

- 1.2 Presentation Des Trois Types De Regulateur De Tension

- 1.2.1 REGULATEURS LINEAIRES

- 1.2.2 ALIMENTATION A DECOUPAGE DE TYPE SMPS

- 1.2.3 POMPE DE CHARGE, CP

- 1.3 LES TECHNOLOGIES

- 1.3.1 Composants Semi-Conducteurs

- 1.3.2 Composants Externes

#### CONCLUSION

# 1 GENERALITES

#### INTRODUCTION

Ce chapitre présente le contexte de l'étude, depuis l'utilité des régulateurs de tension, jusqu'à la description des technologies de fabrication que nous rencontrerons tant du point de vue des composants semi-conducteurs que des composants discrets et de la batterie.

Pour cela, nous verrons tout d'abord la présentation des besoins et le rôle des régulateurs de tension dans une application de systèmes portables tels que les téléphones mobiles. Nous exposerons ensuite pour trois types de régulateurs de tension, leur principe de fonctionnement, leurs avantages et leurs inconvénients ainsi que l'utilisation plus spécifique qui en est faite. Nous parlerons ensuite de la technologie utilisée dans notre cas pour la fabrication du circuit intégré en décomposant la famille à laquelle elle appartient, puis en donnant les principales caractéristiques des composants électriques dont elle dispose. Nous terminerons par un descriptif des technologies actuelles et futures de composition des éléments dits externes aux régulateurs, la batterie, certains condensateurs et les inductances.

#### 1.1 Presentation Des Besoins

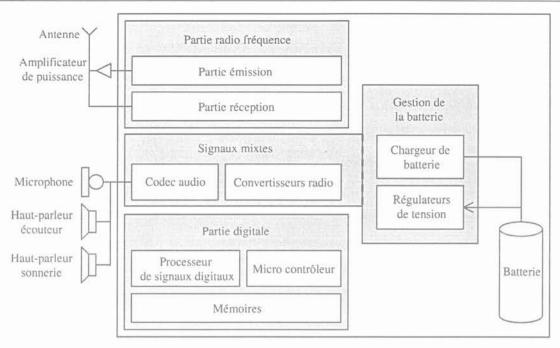

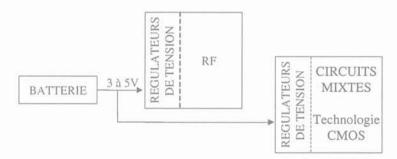

A l'heure actuelle, l'électronique des téléphones portables est constituée de plusieurs circuits intégrés. La figure F1.1-1 en donne la répartition. Le premier circuit sert à l'émission et à la réception de données par l'antenne, ses contraintes sont donc liées aux transferts par radio fréquence. Le deuxième circuit gère les parties digitales, mémoires, micro-contrôleur et processeur de signaux, son coût est le facteur prépondérant. Le troisième circuit intègre les circuits mixtes analogique/digital et les fonctions de gestion de la batterie. Comme les contraintes sont très différentes pour chacun de ces circuits, ceux-ci sont fabriqués dans une technologie qui leur est propre et adaptée à leurs fonctions.

F1.1-1: Répartition des circuits intégrés d'un téléphone portable Chaque partie grise correspond à un circuit intégré regroupant plusieurs fonctions Chacun de ces circuits est fabriqué à partir de technologies différentes

Comme pour tous les systèmes portables, l'alimentation de ces différents circuits se fait au moyen d'une batterie unique. Or les tensions d'alimentation des circuits intégrés sont propres à chaque technologie employée pour sa fabrication. De plus, la tension que délivre cette source unique varie au cours du temps à cause de sa décharge, et subit des perturbations dues aux rayonnements électromagnétiques externes ou internes sur sa connectique, alors que les circuits intégrés demandent à être alimentés par une tension fixe et non perturbée.

Le rôle des régulateurs de tension va donc être de générer plusieurs tensions régulées, c'est-à-dire propres et constantes dans le temps, à partir de l'unique tension variable et perturbée que délivre la batterie rechargeable pour alimenter un ensemble de circuits électroniques.

F1.1-2 : Répartition simplifiée des circuits intégrés et des tensions d'alimentation d'un téléphone portable

Pour cela nous pouvons utiliser différents types de régulateur, ceux à faible tension de déchet, LDO, qui fonctionnent en linéaire et ceux dont le principe est la commutation entre source et charge à l'aide de composants intermédiaires, à savoir les alimentations à découpage, SMPS, et les alimentations à pompe de charges, CP.

Les besoins partent de la réduction des coûts et de la miniaturisation qui passent par le développement de nouvelles structures intégrées telles que des régulateurs de tension en technologie purement CMOS ou de nouvelles fonctionnalités comme abaisser et élever la tension avec un seul et même régulateur.

#### 1.2 Presentations Des Trois Types De Regulateur De Tension

#### 1.2.1 REGULATEURS LINEAIRES

#### 1.2.1.1 Principe de fonctionnement général des régulateurs linéaires

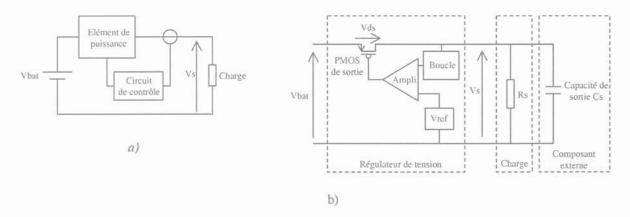

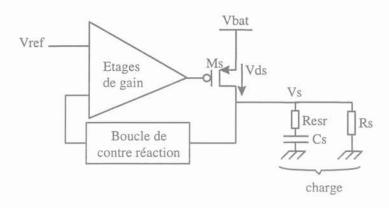

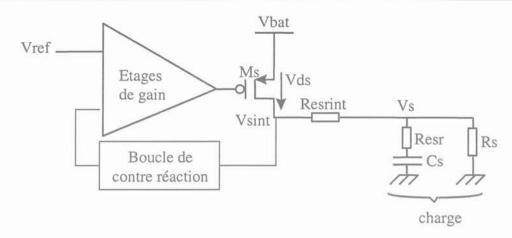

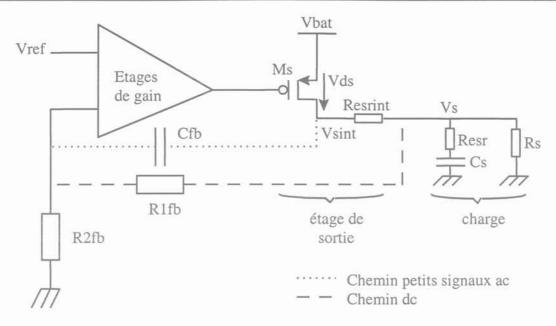

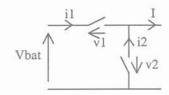

Le régulateur linéaire doit fournir une tension fixe quels que soient sa tension d'alimentation et son courant de sortie. Le principe utilisé pour répondre à ce besoin est illustré par la figure F1.2-1 :

F1.2-1: Principe (a) et réalisation (b) des régulateurs linéaires

La comparaison entre la tension de sortie Vs et la tension de référence Vref permet de contrôler le transistor de sortie et ainsi d'ajuster la tension Vs. On parle de régulation linéaire car l'élément de puissance est commandé en continu.

En effet, toute variation du potentiel d'alimentation Vbat ou du courant de sortie, donc de la charge Rs, se traduit par une variation de la tension de sortie Vs qui est transmise par la boucle de contre réaction sur l'entrée de l'amplificateur. Lorsque le régulateur fonctionne correctement, la variation du potentiel de cette entrée entraîne le retour du potentiel Vs à sa valeur nominale. La tension de sortie Vs est ainsi régulée.

Prenons l'exemple d'un cas où la boucle de contre réaction a une fonction de transfert unitaire, la fonction de transfert globale du régulateur linéaire s'écrit sous la forme suivante :

$$Vs = \frac{H_D}{1 + H_D} \cdot Vref = \frac{1}{1 + 1/H_D} \cdot Vref$$

où  $H_D$  est la fonction de transfert de la chaîne directe.

Si le gain de H<sub>D</sub> (gain de l'amplificateur) est grand, nous retrouvons alors Vs=Vref.

La figure F1.2-1 montre que la tension de sortie Vs est toujours inférieure à la tension de batterie Vbat d'une valeur égale à la tension Vds du transistor de sortie. Ainsi les régulateurs linéaires fonctionnent uniquement en abaisseur de tension.

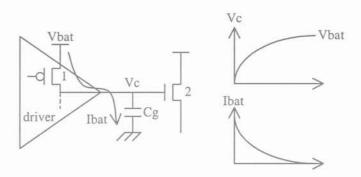

#### 1.2.1.2 Cas des régulateurs de tension de type LDO

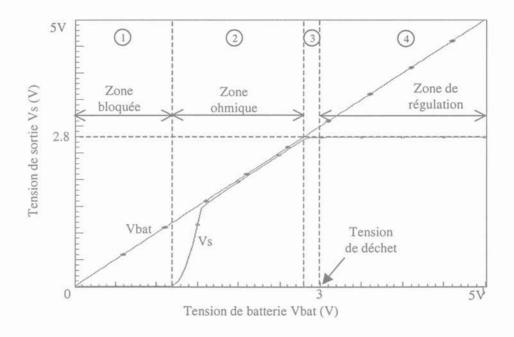

Parmi la catégorie des régulateurs linéaires, nous nous intéresserons dans cette étude uniquement aux régulateurs linéaires de type LDO (Low Drop Out), ce sont des régulateurs de tension qui permettent d'obtenir une tension régulée Vs très proche de leur tension d'alimentation Vbat.

En effet, pour la téléphonie mobile comme pour tous les systèmes portables, l'autonomie de la batterie est un critère primordial. Pour que celle-ci soit la plus longue possible, il faut pouvoir utiliser la tension qu'elle délivre sur la plus grande plage possible.

Actuellement les circuits intégrés demandent des tensions d'alimentation d'environ 2.8V alors que les technologies de fabrication des batteries permettent d'utiliser des tensions pour des valeurs légèrement supérieures, descendant jusqu'à 3V. La différence de potentiels introduite par le régulateur entre sa tension d'alimentation et sa tension de sortie doit pouvoir rester faible, aux alentours de 200mV, si nous voulons pouvoir utiliser toute la capacité de la batterie. Seuls les régulateurs linéaires de type LDO répondent à ce critère.

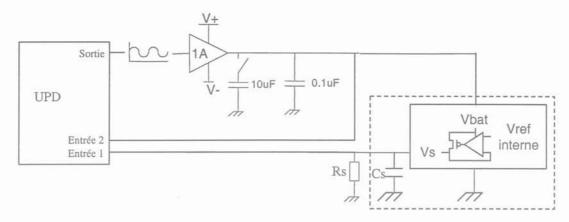

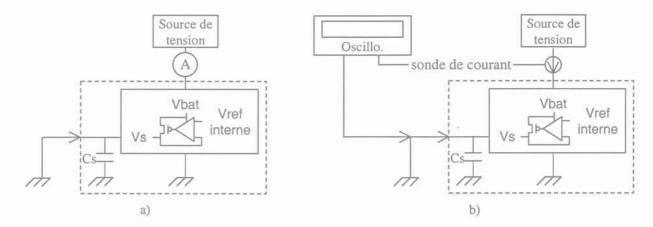

La figure F1.2-1 donne aussi une brève description de la réalisation des régulateurs de tension de type LDO :

La tension de référence Vref est délivrée par une cellule incluse dans le circuit intégré. L'amplificateur se compose le plus souvent de plusieurs étages de gain. La boucle de contre réaction peut être montée en gain ou en suiveur selon les besoins. La charge en sortie du régulateur représente la somme des impédances d'entrée des circuits alimentés par le régulateur.

Par rapport aux autres alimentations à découpage que nous décrirons par la suite, l'avantage de ces régulateurs de tension est qu'ils n'utilisent qu'un seul composant externe, un condensateur (fig. F1.2-1), ceci engendre un coût faible en prix et en place sur la carte pour les composants qui sont ajoutés au régulateur. De plus, comme la commande de la régulation se fait en continu, il n'y a pas d'ondulation sur la tension de sortie Vs, et aucune perturbation due à un découpage.

Leur principal inconvénient reste toutefois d'avoir un rendement médiocre puisque la tension Vds, tension drain/source du transistor de sortie, ne pourra jamais atteindre 0V en fonctionnement normal. Même en théorie, nous ne pourrons pas atteindre un rendement de 100%.

Les LDO dont la consommation et la réjection d'alimentation sont faibles sont principalement utilisés pour alimenter les mémoires. Ceux qui possèdent une forte réjection d'alimentation et une faible tension Vds alimentent les circuits mixtes et les parties processeur de signaux, tandis que ceux qui possèdent une forte réjection d'alimentation et qui ne génèrent que très peu de bruit sont utilisés pour alimenter les circuits de radio fréquence. La technologie utilisée pour la fabrication de ces régulateurs de tensions va dépendre de ces caractéristiques.

#### 1.2.2 ALIMENTATION A DECOUPAGE DE TYPE SMPS

SMPS est l'acronyme de Switch Mode Power Supply. Il correspond aux alimentations à découpage qui utilisent le principe de la commutation pour contrôler le transfert d'énergie à rendement théorique unitaire.

Il existe deux grands groupes, ceux à commutation naturelle [Ferrieux99 – Chapitre III] et ceux à commutation commandée. Les alimentations à commutation naturelle emploient généralement le principe de la résonance qui impose des composants passifs supplémentaires. Par ailleurs le gain sur les pertes par commutation est amoindri par un supplément de pertes

par conduction, inconvénient qui prend de l'importance dans les systèmes basses tensions. Nous limiterons donc notre étude aux alimentations à commutations commandées.

Par ailleurs, la présence de transformateurs n'est pas indispensable compte-tenu des niveaux de tension. Nous nous limiterons donc aux structures non isolées.

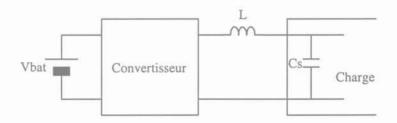

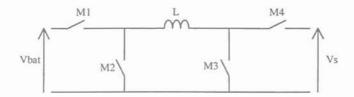

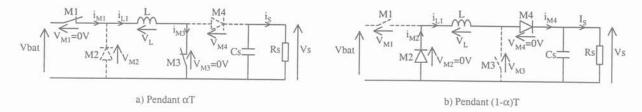

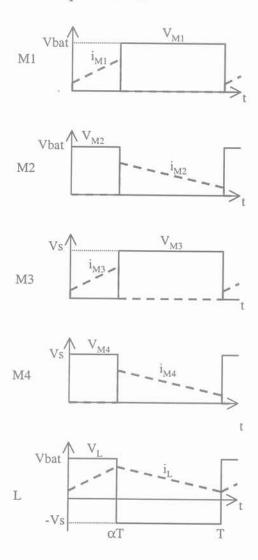

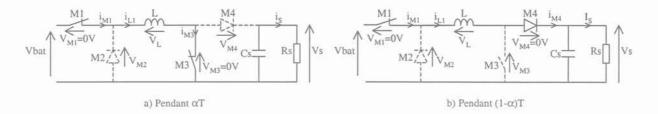

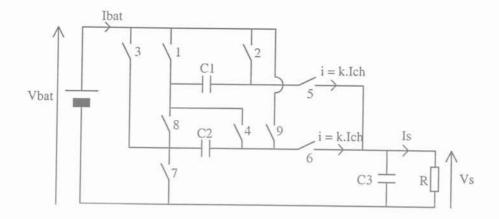

#### 1.2.2.1 Principe de fonctionnement des hacheurs

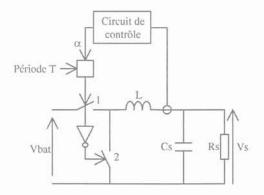

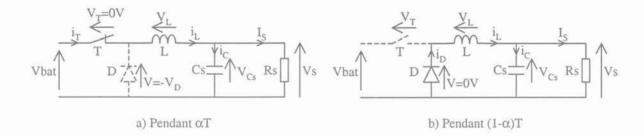

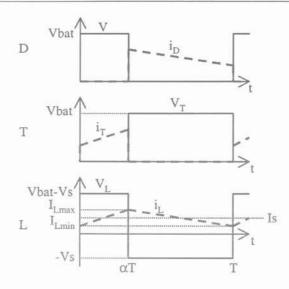

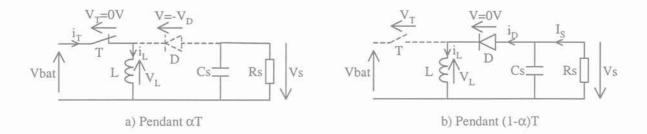

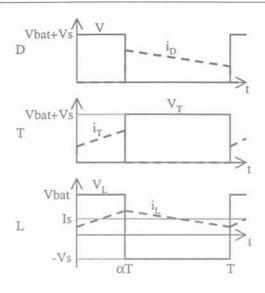

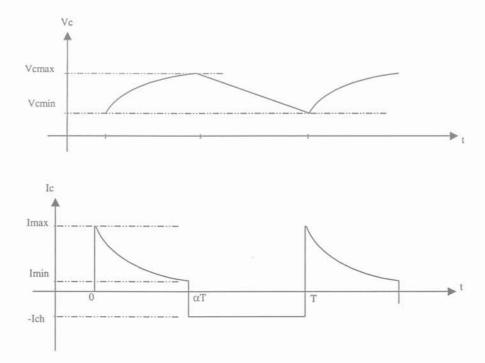

Les hacheurs fonctionnent sur le principe du découpage. Pendant une partie de la période de travail, la batterie fournit de l'énergie à un élément de stockage (inductance ou condensateur). Au cours du temps restant, l'énergie stockée est transférée en sortie du régulateur.

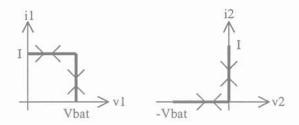

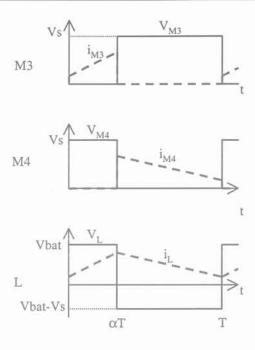

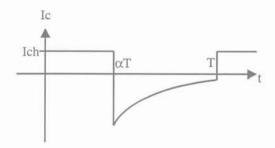

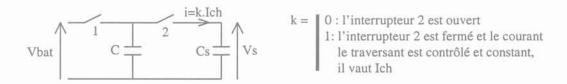

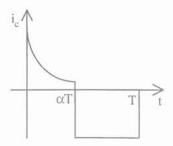

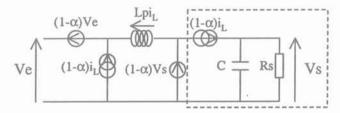

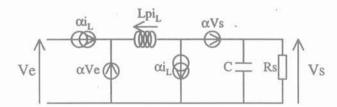

Il existe de multiples configurations qui permettent aussi bien d'abaisser, d'élever ou d'inverser la tension de sortie par rapport à la tension d'entrée. Certaines de ces configurations seront étudiées au cours du troisième chapitre. La figure F 1.2-2 illustre le principe utilisé dans le cas particulier d'un hacheur série qui permet d'abaisser la tension.

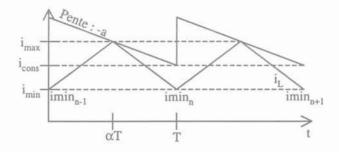

Pendant une fraction  $\alpha$  de la période T, l'interrupteur 1 est fermé et l'interrupteur 2 est ouvert. La batterie fournit alors de l'énergie à l'inductance L et à la charge Rs. Pendant le restant de la période T, c'est l'interrupteur 2 qui est fermé et l'interrupteur 1 qui est ouvert. L'inductance L se décharge alors dans la charge Rs. La tension de sortie Vs est ajustée en agissant sur le rapport cyclique  $\alpha$ . Dans le cas le plus classique, le circuit de contrôle permet de générer  $\alpha$  à partir d'une comparaison entre la tension de sortie Vs et une tension de référence.

F 1.2-2 : Principe de fonctionnement d'une alimentation à découpage Cas d'un hacheur série (Buck)

Le premier avantage de ces SMPS est de pouvoir, selon leur configuration, abaisser, élever ou inverser la tension. De plus, ils possèdent, en théorie, un bon rendement car si les éléments sont idéaux, il n'y a pas de perte.

Par contre, le découpage induit des perturbations lors des commutations ainsi qu'une ondulation sur la tension de sortie ce qui limite la régulation. A ajouter à cela, ces régulateurs demandent au moins deux composants externes pour fonctionner : un condensateur et une inductance. Ce dernier composant est particulièrement coûteux aussi bien en prix qu'en volume sur la carte.

Les SMPS sont le plus souvent utilisés pour alimenter les circuits intégrés des microcontrôleurs et de la partie processeur de signaux.

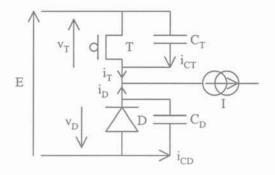

#### 1.2.3 POMPE DE CHARGE, CP

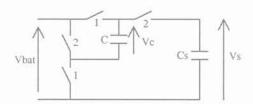

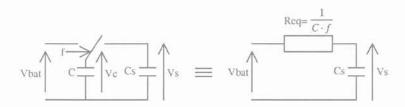

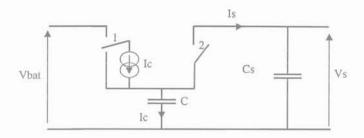

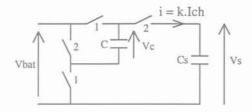

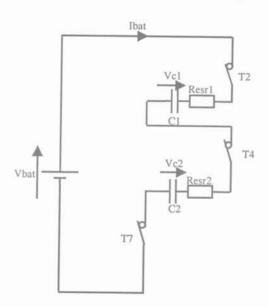

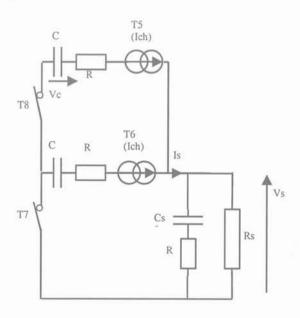

Pendant une partie du temps du temps de travail, la tension Vbat est fournie à un condensateur, pendant un autre moment cette énergie est transférée au condensateur de sortie et à la charge du régulateur.

Prenons l'exemple du cas le plus courant, le doubleur de tension, fig. F 1.2-3. Lorsque les interrupteurs 1 sont fermés, le condensateur C se charge à Vbat. Ensuite les interrupteurs 2 se ferment et le condensateur Cs se charge alors sous la tension Vc en série avec la tension Vbat, soit une tension de 2·Vbat.

F 1.2-3: Principe de fonctionnement du doubleur de tension

La charge et la décharge de ces condensateurs se fait nécessairement avec des pertes dans les semi-conducteurs, contrairement aux alimentations à découpage, puisqu'il n'y a pas de composants inductifs.

Un asservissement permet de réguler la tension de sortie Vs en jouant soit sur les durées des temps de commutation, soit sur l'impédance des transistors qui servent à réaliser les fonctions interrupteurs.

Tout comme les SMPS, les pompes de charge permettent d'obtenir une tension de sortie inférieure, supérieure ou inversée par rapport à leur tension d'entrée sans pour autant avoir recours à l'utilisation d'une inductance. Par contre, il faut souvent plus d'un seul condensateur en externe et le rendement reste inférieur à celui obtenu avec un SMPS. Le découpage risque dans ce cas encore d'induire des perturbations sur l'environnement.

A cause du mauvais rendement obtenu dans le cas d'un abaisseur, les alimentations à pompe de charges sont essentiellement utilisées en élévateur de tension, donc pour tous les circuits qui demandent une tension d'alimentation assez élevée telle que 3 ou 4.8V pour les cartes SIM.

#### 1.3 LES TECHNOLOGIES

Ce paragraphe se divise en deux parties, la première concerne la technologie utilisée pour la fabrication des circuits intégrés et la deuxième expose les différentes solutions technologiques qui sont actuellement disponibles chez les fabricants de batterie et de composants externes.

#### 1.3.1 Composants Semi-Conducteurs

La technologie utilisée pour la conception des cellules des circuits intégrés est une donnée qui est imposée. Nous allons donc voir quelles sont les contraintes qu'elle engendre, quels sont les composants disponibles et quels sont leurs principaux paramètres.

### 1.3.1.1 Présentation des familles de technologie

Il existe plusieurs familles de technologie, chacune est déterminée par la dimension minimale qu'elle autorise et qui correspond à la longueur minimale de grille d'un transistor MOS. Chaque famille se divise ensuite en sous classes qui correspondent à des technologies à vocations différentes :

- Pour les circuits purement digitaux la technologie est la plus simple, technologie CMOS,

- En y ajoutant des options, on peut concevoir des circuits analogiques avec une technologie CMOS. Il faut alors entre 15 et 18 masques pour leurs fabrications,

- A partir de cette dernière technologie, on peut de nouveau ajouter des masques et obtenir des transistors bipolaires, c'est la technologie BiCMOS qui est habituellement utilisée pour les circuits analogiques standards. Il faut alors prévoir

- entre 22 et 26 masques, mais cette technologie dispose entre autres de transistors bipolaires de type NPN avec une fréquence de transition f<sub>t</sub> de 5.5GHz,

- Enfin la technologie la plus complète permet de concevoir les circuits de radiofréquence, c'est la technologie BiCMOS RF. Elle propose un transistor bipolaire de type NPN avec une ft de 16GHz, mais elle demande entre 23 et 27 masques.

Dans cette liste chacune des technologies est parfaitement compatible avec celle qui la précède.

Actuellement les régulateurs de tension sont conçus dans une technologie BiCMOS analogique à partir d'une famille caractérisée par une longueur de grille minimale de  $0.5\mu$ . Ses principaux autres paramètres sont donnés dans le tableau T 1.3-1 et peuvent dépendre de la classe de tension d'alimentation du circuit, 3 ou 5V. Nous noterons toutefois que la longueur de grille minimale passe à  $0.6\mu$  dans le cas des applications à 5V, ce qui correspond aux circuits des régulateurs de tension.

| ,                                                   | Applications à 3V  | Applications à 5V  |

|-----------------------------------------------------|--------------------|--------------------|

| Nombre de niveaux de métaux                         | 3                  | 3                  |

| Nombre de niveaux de polysilicium                   | 2                  | 2                  |

| Tension d'alimentation maximum                      | 3.6V               | 5.5V               |

| Température d'utilisation (température de jonction) | De –40 à<br>+125°C | De –40 à<br>+125°C |

T 1.3-1: Paramètres de la technologie 0.5µ

Certaines options technologiques supplémentaires permettent d'obtenir des composants qui tiennent des tensions d'alimentations plus élevées, mais ceci aux dépens du coût du circuit.

## 1.3.1.2 Composants disponibles, cas de la technologie CMOS analogique 5V

Les figures F1.3-1 et F1.3-2 donnent les symboles et les constitutions, respectivement, des transistors NMOS et PMOS. Ce sont des composants latéraux, les zones actives, source et drain, se situent sur le même côté de la puce.

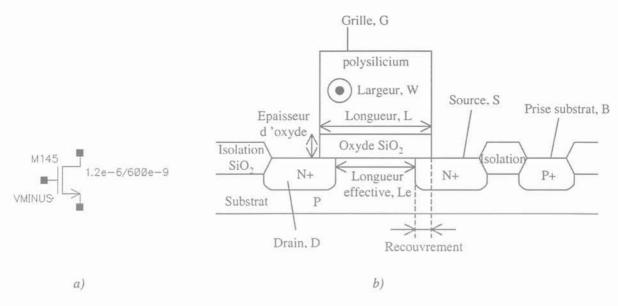

F1.3-1 : Transistor NMOS a) Symbole électrique, b) Vue en coupe

La vue en coupe du transistor NMOS, fig. F1.3-1, fait apparaître le phénomène de recouvrement. Dans la suite de l'étude tout ce que l'on nommera longueur des transistors sera relatif à la longueur dessinée, L, par opposition à la longueur électrique ou longueur effective, Le. Le substrat est le même pour tout le circuit. Il est polarisé à 0V, les autres zones doivent donc être polarisées avec des tensions supérieures ou égales pour ne pas avoir de fuites par les diodes entre ces zones et le substrat.

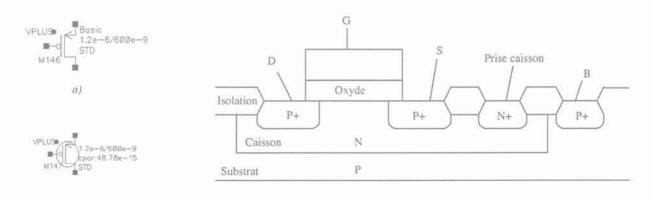

Sur la figure F1.3-2, on note que les symboles des transistors PMOS isolé et non isolé diffèrent mais leurs constitutions restent les mêmes. Il suffit juste de polariser le caisson convenablement pour respecter l'isolation entre le caisson et le substrat.

b) c)

F1.3-2 : Transistor PMOS a) Symbole du transistor non isolé, b) Symbole du transistor isolé, c) Vue en coupe

La figure F1.3-3 rappelle la caractéristique électrique d'un transistor NMOS, courant drain/source Ids en fonction de la tension drain/source Vds pour différentes tensions grille/source Vgs. Les deux zones, linéaire et saturée, sont régies par des équations électriques différentes. Dans la zone saturée, le transistor se comporte comme une source de courant commandée en tension.

F1.3-3: Caractéristique électrique d'un transistor NMOS Courant Ids en fonction de la tension Vds pour plusieurs Vgs

Le tableau T 1.3-2 regroupe les principaux paramètres technologiques des transistors MOS 5V.

|                       | Conditions                 | NMOS      | PMOS       |

|-----------------------|----------------------------|-----------|------------|

| Epaisseur d'oxyde     |                            | 120Å      | 120Å       |

| T11374                | W=10μ, L=10μ               | 600mV     | -630mV     |

| Tension de seuil Vt   | W=10μ, L=0.6μ              | 640mV     | -610mV     |

| Courant de fuite      | L=0.6µ, Vgs=0V,  Vds =5V   | 1pA/μm    | -1pA/μm    |

| Courant de saturation | L=0.6µ,  Vgs =5V,  Vds =5V | 0.52mA/μm | -0.25mA/μm |

| Kb                    | W=10μ et L=10μ             | 0.65√V    | 0.7√V      |

T 1.3-2: Paramètres technologiques des transistors MOS 5V

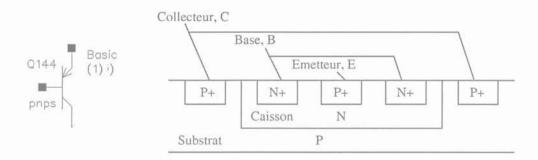

La technologie CMOS analogique dispose également d'un transistor bipolaire vertical de type PNP qui utilise le substrat comme collecteur. La figure F1.3-4 en donne le symbole et la vue en coupe. Sa fréquence de transition  $f_t$  est de 300MHz pour un courant de collecteur Ic de 400 $\mu$ A.

F1.3-4: Coupe d'un transistor bipolaire substrat

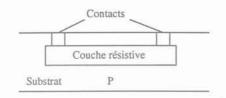

Les résistances sont faites à partir de couches planes plus ou moins résistives selon leur nature, fig. F1.3-5. Pour les valeurs les plus élevées, entre  $1\Omega$ à  $1M\Omega$ , on utilise du polysilicium à  $1000\Omega$ /carré, ou une zone diffusée à  $1300\Omega$ /carré. Pour les très faibles valeurs de résistance, on utilise des métaux dont la résistivité par carré est de quelques  $m\Omega$ . Ces résistances ont une dépendance en température qui varie selon leur nature, les coefficients sont négatifs pour le polysilicium, et positifs pour les résistances diffusées. Mais les résistances en polysilicium permettent d'obtenir une variation faible de leurs valeurs en fonction de la tension qui leur est appliquée alors que les résistances diffusées y sont beaucoup plus sensibles.

F1.3-5: Coupe d'une résistance

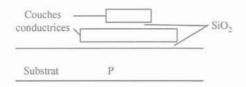

La technologie CMOS permet aussi d'utiliser des condensateurs dont les valeurs peuvent raisonnablement atteindre plusieurs dizaines de pico Farad à partir d'une capacité surfacique de 1150pF/mm<sup>2</sup>. Comme le montre la figure F1.3-6, elles sont constituées de deux couches conductrices planes séparées par une couche isolante.

F1.3-6: Coupe d'un condensateur

#### 1.3.2 Composants Externes

Ce que nous définirons dans la suite de l'étude comme des composants externes, sont les éléments non intégrés qui ont une influence sur la conception des régulateurs. Le premier est bien sûr la batterie, les autres sont les composants qui ne peuvent pas être intégrés, soit parce que leurs valeurs sont trop importantes comme pour certains condensateurs, soit parce qu'ils ne sont pas disponibles dans la technologie à partir de laquelle le circuit intégré est fabriqué, c'est le cas des inductances.

#### 1.3.2.1 Pourquoi cette étude ?

Les composants externes imposent des contraintes sur la conception car, comme nous le verrons plus en détail lors des chapitres sur les LDO et sur les alimentations à découpage, les condensateurs et les inductances externes influencent énormément la conception des régulateurs de tension en intervenant directement sur la stabilité et les pertes de ces systèmes. En effet, les composants réels correspondants ne sont pas idéaux, ils possèdent des éléments parasites. Les variations de valeur de ces éléments parasites ou des composants eux-mêmes, que ce soient selon la température, la fréquence ou la tension qui est appliquée sur leurs bornes, ne sont pas négligeables.

Après avoir regardé quelles sont les différentes technologies de batteries, quelles sont les tensions qu'elles délivrent et donc quelles sont les contraintes en tension d'alimentation des régulateurs, nous chercherons à connaître les éléments parasites des condensateurs et des inductances externes ainsi que leurs variations. Nous ne regarderons pas de cas précis car il y a beaucoup de différences selon le type de composants et ceux-ci ne sont que très rarement connus lorsque l'étude de l'application débute. Une modélisation précise ne serait pas adaptée, nous tenterons seulement de mettre en avant les grandes lignes de ces variations.

#### 1.3.2.2 Batteries

La batterie impose une contrainte, la tension qu'elle délivre, sur l'alimentation des régulateurs de tension. Une technologie de fabrication de batterie correspond à une certaine valeur de tension. Pour obtenir une tension d'alimentation des circuits intégrés suffisante, on peut être amené à mettre plusieurs cellules unitaires en série.

Les caractéristiques idéales pour les batteries alimentant les téléphones portables sont une grande autonomie, de faibles dimensions et un poids léger.

Le contenu de ce chapitre est basé sur les références suivantes : [Buchmann97], [Batteries2001], [gsmelcotec], [byd], [saftbatteries], [panasonic] et [polystor]

Nous définirons la décharge de la batterie comme étant la partie de fonctionnement pendant laquelle la batterie fournit de l'énergie à sa charge, en l'occurrence les régulateurs de tension, et la charge comme étant la période pendant laquelle l'énergie initiale de la batterie est restaurée. La capacité sera la quantité d'énergie contenue par la batterie en A·h, tandis que l'auto décharge correspondra à l'énergie perdue lors de l'inactivité de la batterie.

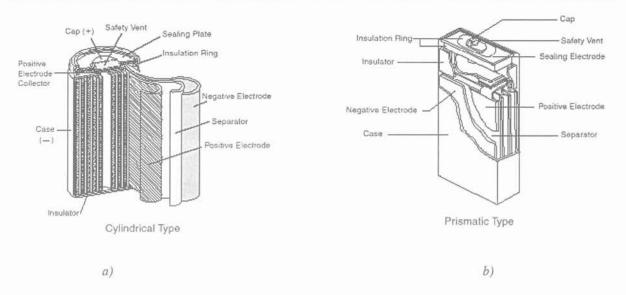

La figure F1.3-7 donne une représentation de la composition des batteries qui sont actuellement disponibles sur le marché sous une forme cylindrique ou de prisme.

F1.3-7: Composition des batteries rechargeables a) Cas des batteries en cylindre b) Cas des batteries en prisme

#### Batteries Nickel-Cadmium (NiCd).

Ce sont les batteries les plus traditionnelles, elles utilisent de l'hydroxyde de nickel comme électrode positive, du cadmium comme électrode négative, et un électrolyte alcalin. Leur tension de sortie minimale est de 1V.

Ces batteries ont l'avantage de pouvoir être chargées rapidement et simplement, elles possèdent une bonne durée de vie et sont d'un coût faible. Elles sont disponibles dans de nombreuses configurations de dimensions et de performances, et sont le plus souvent utilisées pour alimenter des systèmes qui ont besoin d'une forte autonomie et d'un coût faible.

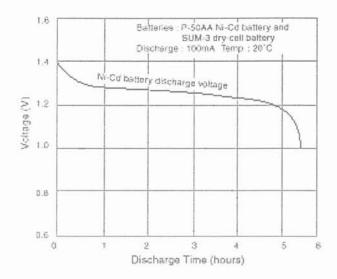

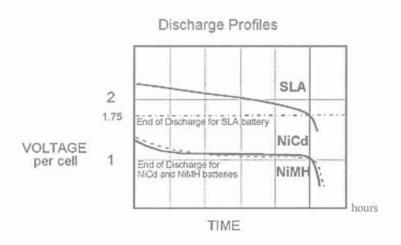

La figure F1.3-8 montre une courbe de décharge, c'est à dire de tension de sortie de ces batteries en fonction du temps, dans cet exemple le courant tiré de la batterie est de 100mA.

F1.3-8: Décharge des batteries NiCd

#### Batteries en Nickel Metal Hydride (NiMH)

Ces batteries sont disponibles depuis les années 1980. L'électrode positive est de l'hydroxyde de nickel, l'électrode négative un alliage de métaux qui permet d'absorber et de restituer de l'hydrogène, et l'électrolyte est alcalin. Ces batteries sont déchargées lorsque leur tension de sortie atteint 1V.

Elles sont peu toxiques et permettent d'améliorer d'environ 30% la capacité par rapports aux batteries NiCd, mais leur durée de vie est plus faible. La charge s'effectue de façon plus complexe. Finalement le coût est un peu plus élevé, mais ce sont les batteries actuellement utilisées pour l'alimentation des téléphones portables.

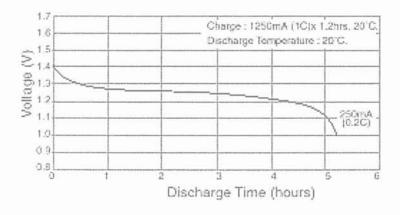

La courbe de décharge, figure F1.3-9, reste similaire à celle des batteries NiCd.

F1.3-9 : Courbe de décharge des batteries NiMH

#### Batteries Sealed Lead Acid (SLA)

Ces batteries présentent l'avantage d'avoir peu d'auto décharge mais elles ne sont pas adaptées à la téléphonie portable. En effet, elles ne sont économiques que pour les applications pour lesquelles le poids n'est pas une priorité car leur capacité est faible.

La figure F1.3-10 donne l'allure des courbes de décharge pour les batteries NiCd, NiMH et SLA.

F1.3-10 : Décharge des batteries NiCd, NiMH et SLA

#### Batteries Lithium Ion (Li-ion)

Ces batteries sont apparues dans les années 90. L'élément majoritaire de l'électrode positive est de l'oxyde de cobalt lithium, celui de l'électrode négative est du carbone, et l'électrolyte est un solvant organique.

Ces batteries peuvent fournir de plus fortes tension et capacité que les précédentes, ce qui permet d'obtenir une plus grande densité d'énergie. De plus elles sont plus légères car le lithium a un poids faible. Elles ont par contre longtemps posé des problèmes de sécurité à cause de l'instabilité du lithium lors des charges.

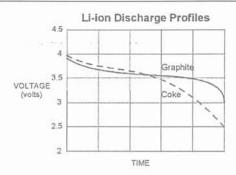

La figure F1.3-11 montre les courbes de décharge pour deux types d'électrodes, celles en graphite et celles en coke. On s'aperçoit que les électrodes en graphite donnent une tension de batterie minimale plus élevée, par contre elles délivrent un courant plus fort et s'élèvent moins en température.

Des études sont en cours pour trouver de nouvelles électrodes qui permettraient d'augmenter la capacité de ces batteries.

F1.3-11 : Décharge des batteries Li-ion avec des électrodes en graphite ou en coke

Cette technologie de batterie demande des protections pour combler son instabilité. Un circuit interne contrôle les pics de tension lors de la charge ainsi que les chutes de tension brusque lors de la décharge. Les courants de charge et de décharge et la température de la cellule sont aussi surveillés.

#### • Batteries Lithium Polymer (Li-polymère)

Cette technologie est récente puisque les premières productions ont débuté au cours de l'année 2000. La conception de ces batteries est basée sur un électrolyte solide qui permet d'en faciliter la fabrication et donc d'obtenir un coût faible et une sécurité accrue par rapport aux batteries Li-ion. Elles offrent une forte densité d'énergie et une auto décharge faible mais sont plutôt dédiées aux applications à faible puissance car leur courant de décharge est moins élevé que pour les batteries précédentes. Cette technologie permet aussi d'obtenir une grande flexibilité dans la forme de la batterie ainsi que des épaisseurs relativement faibles, de l'ordre de 3 à 5mm. Elles présentent cependant les inconvénients d'avoir une capacité moins importante que les batteries Li-ion et d'avoir un nombre de cycles de charge/décharge plus faible particulièrement, si la décharge est importante.

#### Batteries Alcalines rechargeables

Ces batteries sont utilisées en grande partie pour les applications faible puissance et faible coût. Elles ont une durée de vie assez faible, mais ceci est compensé par une auto décharge réduite. Par contre elles perdent de la capacité au cours des cycles de charge/décharge et délivrent un courant qui est largement insuffisant pour alimenter les applications telles que les téléphones portables. Nous ne nous y intéresserons donc pas plus.

Toutefois les batteries peuvent être conçues différemment à partir d'une même technologie pour répondre à des besoins d'applications diverses. Les performances peuvent aussi varier en fonction des fabricants.

Le tableau T 1.3-3 regroupe les principales caractéristiques de ces technologies de batterie.

|                                 | NiCd             | NiMH             | SLA              | Li-Ion                  | Li-<br>Polymer        | Alcaline             |

|---------------------------------|------------------|------------------|------------------|-------------------------|-----------------------|----------------------|

| Densité<br>d'énergie<br>(Wh/kg) | 40/60            | 60/80            | 30               | 100                     | 150/200               | 80<br>(initialement) |

| Nombre de cycles                | 1500             | 500              | 200/500          | 500/1000                | 300                   | 10<br>(jusqu'à 65%)  |

| Temps de charge relatif         | X                | 2X               | 8X               | 3X                      | 8X                    | 2X                   |

| Tolérance à la surcharge        | Moyenne          | Faible           | Forte            | Très faible             |                       | Moyenne              |

| Auto<br>décharge par<br>mois    | 20%              | 30%              | 5%               | 10%                     | 5%                    | 0.3%                 |

| Tension de sortie nominale      | 1.25V            | 1.25V            | 2V               | 3.6V                    | Entre 2.5V<br>et 3.6V | 1.5V                 |

| Courant de sortie               | >2·C             | 0.5/1·C          | 0.2·C            | 1·C<br>ou moins         | 0.2·C                 | 0.2·C                |

| Température<br>d'utilisation    | -40 à<br>+60°C   | -20 à<br>+60°C   | Jusqu'à<br>+60°C | -20 à<br>+60°C          |                       | 0 à +65°C            |

| Coût typique (référence)        | \$50             | \$70             | \$25             | \$100                   | \$90                  | \$5                  |

| Coût par cycle                  | \$0.04<br>(7.5V) | \$0.14<br>(7.5V) | \$0.1<br>(6V)    | \$0.1/0.2<br>(7.2V)     | \$0.6<br>(8.1V)       | \$0.5<br>(9V)        |

| Disponible depuis               | 1950             | 1990             | 1970             | Milieu des<br>années 90 | 2000                  | 1992                 |

Le nombre de cycles est le nombre de charge/décharge de la batterie.

Le coût par cycle est le coût typique divisé par la durée de vie de la batterie.

T 1.3-3 : Principales caractéristiques des batteries actuellement sur le marché

La durée de vie est basée sur une baisse de la capacité de la batterie de 100 à 80%, excepté pour les alcalines.

La surcharge correspond à la charge continue au-delà de la charge complète que peut accepter la batterie.

L'auto décharge est donnée pour la température ambiante.

Courant de sortie : Une batterie de capacité C=1000mAh fournit 1000mA pendant 1 heure si elle a un courant de sortie de 1·C, elle fournit un courant de 500mA pendant 2 heures si elle a un courant de sortie de 0.5·C, elle fournit 2000mA pendant 30 minutes si elle a un courant de sortie de 2·C.

Les technologies de batteries suivantes sont celles du futur, elles sont encore à l'étude mais promettent des caractéristiques intéressantes pour les applications portables.

## Batteries Zinc-Air [aern] [Tinker01]

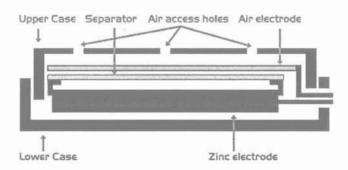

Ces batteries consistent en une cellule dont une électrode est en zinc. L'air passe pendant la décharge, mais reste bloqué pendant la charge. En effet, comme le montre la figure F1.3-12, seul le zinc est stocké dans la batterie, l'air nécessaire est prélevé dans l'atmosphère ambiante par respiration de l'accumulateur.

F1.3-12: Constitution d'une cellule Zinc-Air

Les premiers prototypes délivrent une tension nominale de 3.6V et possèdent une densité d'énergie qui peut aller de 200 à 300Wh/Kg.

## Batteries Aluminium-Air [trimolgroup]

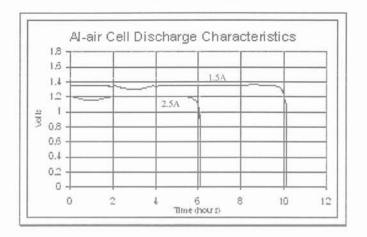

Des prototypes de ces batteries sont prévus pour l'année 2002. Ils permettraient d'obtenir une tension nominale de 1.2V avec une densité d'énergie de 800Wh/Kg, soit deux fois supérieure à celle des batteries Zinc-Air et huit fois plus que celle des batteries Li-Ion, ce qui autoriserait une autonomie en communication de 24h et en veille d'environ un mois.

Ces batteries ont l'avantage d'être facilement recyclables et peu nocives pour l'environnement. Comme le montre la figure F1.3-13, la tension reste stable au cours de la décharge, ce qui facilite la conception des circuits que ces batteries alimentent, mais rend plus difficile la détection de fin de charge. De plus ces batteries présentent une forte auto décharge.

F1.3-13 : Courbe de décharge des batteries Al-Air

## Batteries Fuel Cell [Murray01], [Bloch01]

Ces batteries fonctionnent à partir d'hydrogène stocké, qui combiné avec de l'oxygène produit de l'eau et de l'électricité.

L'hydrogène seul offre une densité d'énergie de 1000 à 23000Wh/Kg, mais les premiers prototypes de batterie donnent une densité de 80Wh/Kg. Pour une tension nominale de 1.2V, la tension minimale, tension pour laquelle la batterie est considérée comme déchargée, est de 0.75V.

Le principal avantage de ces batteries est qu'elles n'ont pas besoin de chargeur, il suffit de changer les cartouches de carburant.

#### 1.3.2.3 Condensateurs

Pour limiter la taille et l'épaisseur des téléphones portables, les condensateurs utilisés en tant que composants externes doivent pouvoir être montés en surface et ne pas dépasser une épaisseur de 1.8mm.

Deux sortes de condensateurs répondent à ces critères, les premières sont fabriquées à partir de tantale et les secondes à partir de céramique. Nous allons voir leurs principales caractéristiques dans les paragraphes suivants.

Les condensateurs sont modélisés par un condensateur en série avec une résistance, l'ESR (Equivalent serie resistor), et une inductance, l'ESL. Nous nous intéresserons particulièrement aux variations des deux premiers points, valeur du condensateur et de l'ESR. En effet la valeur de l'ESL est soumise à peu de variations, elle reste de l'ordre de 1 à 2nH.

L'ESR et l'ESL proviennent de la structure et des matériaux de fabrication des condensateurs.

## 1.3.2.3.1 Condensateurs en céramique multicouches

Les données de ce paragraphe sont basées sur les références suivantes : [avxcorp], [kemet], [murata], [rohmelectronics], [tdk] et [vishay]

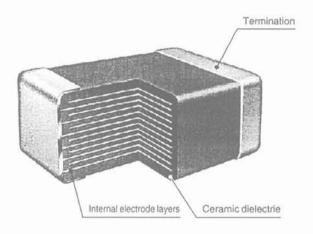

Comme le montre la figure F1.3-14, les condensateurs céramiques sont constitués par des couches alternées de diélectrique céramique et d'électrodes reliées entre elles par des terminaisons.

F1.3-14: Constitution des condensateurs céramiques multicouches

La valeur de la capacité est alors donnée par l'équation suivante :

$$C = \frac{A \cdot n \cdot \varepsilon_0 \cdot \varepsilon_r}{d}$$

avec A: Surface des électrodes

n: Nombre d'électrodes

d : distances entre les électrodes

$\varepsilon_0$ : permittivité absolue

ε<sub>r</sub> : permittivité relative du diélectrique

Les condensateurs en céramique peuvent se diviser en deux classes : ceux dits de type 1 pour lesquels  $\epsilon_r$ <500 et ceux de type 2, dans ce cas  $\epsilon_r$ >500. Les variations diffèrent selon le type de diélectrique utilisé.

## 1.3.2.3.1.1 Diélectrique de type 1

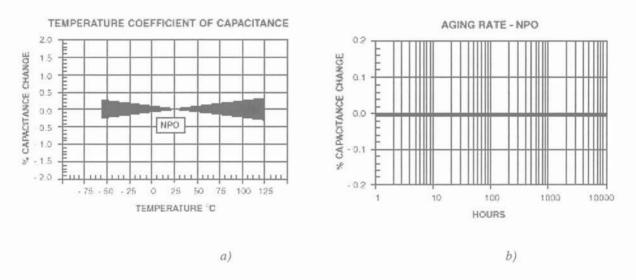

Le diélectrique de type 1 est basé sur un mélange de titane où le baryum est minoritaire. Le plus courant est le COG, que l'on trouvera aussi sous l'appellation NPO.

Les condensateurs qui utilisent un diélectrique de type 1 présentent de bonnes qualités. Leur capacité varie quasiment linéairement avec la température, mais cette variation reste très faible,  $\pm 0.4\%$ . Elle est indépendante de la tension appliquée et n'est pas soumise à un phénomène de vieillissement.

Cependant, la capacité volumique de ce type de condensateur reste particulièrement faible et si l'on veut garder un condensateur d'épaisseur inférieure à 1.8mm, la capacité sera au maximum de 220nF, ce qui élimine la possibilité d'utiliser ce type de condensateur dans nos applications où les condensateurs externes sont de l'ordre de 1µF.

F1.3-15 : Courbes de variations de la capacité a) En fonction de la température b) en fonction du temps, courbe de vieillissement

## 1.3.2.3.1.2 Diélectrique de type 2

Ce type de diélectrique est toujours un mélange de titane, mais cette fois, contrairement aux diélectriques de type 1, le baryum est majoritaire et la permittivité relative du diélectrique est plus importante.

L'appellation de ces condensateurs est régie par une codification, la codification EIA qui est rappelée dans le tableau T 1.3-4. La première ligne donne le code et les colonnes en

dessous donnent la signification de chacune des parties de ce code. On s'aperçoit que les diélectriques de type 2 sont classés selon leurs variations en température.

| Code: | 0805                    | X7R<br>(1)           |        |                      |        |                                                    |               | 103 (2)                     | M<br>(3)  |            |

|-------|-------------------------|----------------------|--------|----------------------|--------|----------------------------------------------------|---------------|-----------------------------|-----------|------------|

|       | Format<br>du<br>boîtier | Température<br>T min |        | d'utilisation T max. |        | Variation de la<br>capacité avec la<br>température |               | Valeur<br>de la<br>capacité | Tolérance |            |

|       |                         | Code                 | T (°C) | Code                 | T (°C) | Code                                               | Variation (%) | en pF                       | Code      | Tolérance  |

|       |                         | Z                    | +10    | 2                    | +45    | R                                                  | ±15           |                             | В         | ±0.10pF    |

|       |                         | Y                    | -30    | 4                    | +65    | S                                                  | +22           |                             | C         | ±0.25pF    |

|       |                         | X                    | -55    | 5                    | +85    | T                                                  | +22, -33      |                             | D         | ±0.5pF     |

|       |                         |                      |        | 6                    | +105   | U                                                  | +22, -56      |                             | F         | ±1%        |

|       |                         |                      |        | 7                    | +125   | V                                                  | +22, -82      |                             | G         | ±2%        |

|       |                         |                      |        |                      |        |                                                    |               |                             | J         | ±5%        |

|       |                         |                      |        |                      |        |                                                    |               |                             | K         | ±10%       |

|       |                         |                      |        |                      |        |                                                    |               |                             | M         | ±20%       |

|       |                         |                      |        |                      |        |                                                    |               |                             | P         | +100%, 0%  |

|       |                         |                      |        |                      |        |                                                    |               |                             | Z         | +80%, -20% |

<sup>- (1)</sup> Pour les céramiques de type 2, la dépendance à la température est donnée par le code :

Ex:  $\underline{Y}5V$ : le premier sigle donne la température d'utilisation min.

$Y\underline{5}V$ : le deuxième sigle donne la température d'utilisation max.

$Y5\underline{V}$ : le troisième sigle donne la variation de la capacité dans la gamme de température d'utilisation sous 0V

- (2) Valeur de la capacité (en pF):

Les 2 premiers chiffres indiquent la valeur nominale, le 3<sup>e</sup> le nombre de zéros qui suivent, la valeur est donnée en pF (103=10000pF).

Pour les valeurs inférieures à 10pF, on insère un R en 2<sup>e</sup> position à la place de la virgule (2R2=2.2pF).

- (3) Tolérance : Les tolérances notées en gras correspondent aux valeurs les plus utilisées

T 1.3-4 : Codification des diélectriques de type 2

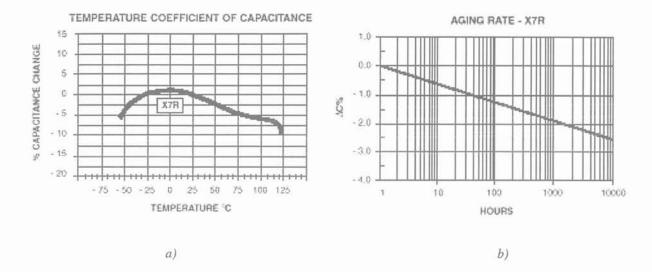

Les condensateurs en céramique de type 2 ont une plus forte capacité volumique qui permet d'obtenir des valeurs de l'ordre de grandeur adapté à nos régulateurs, mais les dispersions sont beaucoup plus importantes en fonction de la température, de la fréquence, de la tension appliquée et le phénomène de vieillissement est beaucoup plus marqué. En fait, plus la capacité volumique est forte, plus les variations vont être importantes.

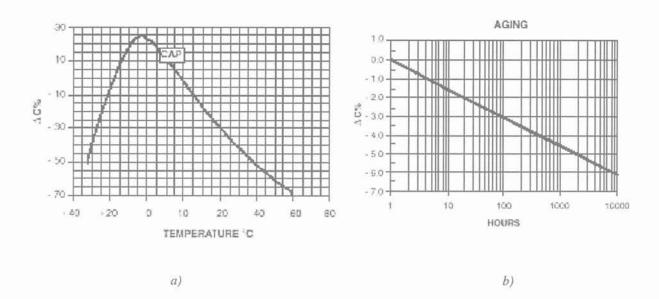

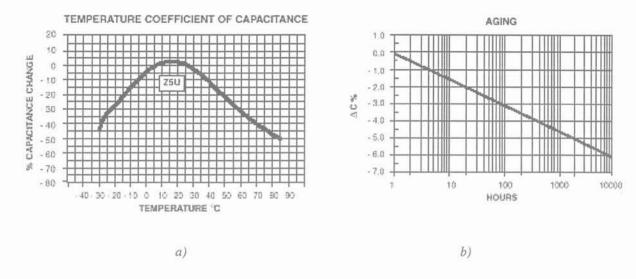

Ainsi, selon le diélectrique la variation en température peut être de ±20% jusqu'à +22%, -82% sans qu'il n'y ait de linéarité entre la capacité et la température. Les figures F1.3-16, F1.3-17 et F1.3-18 montrent que la capacité augmente jusqu'à la température ambiante et diminue au-delà.

La tension appliquée sur le condensateur va aussi faire varier sa capacité sans qu'il n'y ait de linéarité. Pour les classes de tension faibles qui nous intéressent, l'application d'une tension DC diminue la capacité tandis que l'application d'une tension AC l'augmente.

Le vieillissement est dû à un réalignement de la structure cristalline du diélectrique qui engendre des pertes.

F1.3-16 : Diélectrique X7R a) Capacité en fonction de la température b) Vieillissement : -2%/dec

F1.3-17 : Diélectrique Y5V a) Capacité en fonction de la température b) Vieillissement : -5%/dec

F1.3-18 : Diélectrique Z5U

a) Capacité en fonction de la température

b) Vieillissement : -3%/dec

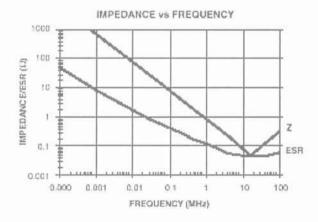

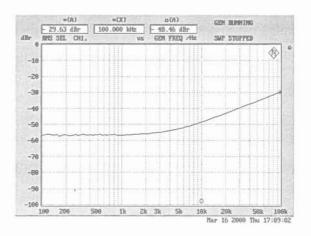

La figure F1.3-19 représente les variations en fréquence de l'impédance, Z, et de l'ESR d'un condensateur céramique Y5V. L'impédance varie inversement à la fréquence en 1/jω jusqu'à la fréquence de résonance du condensateur, ≈10MHz. L'ESR DC est importante mais diminue fortement lorsque la fréquence augmente. D'après les données des fabricants, l'ESR diminue aussi lorsque la température augmente.

F1.3-19 : Courbes d'impédance et d'ESR en fonction de la fréquence pour un condensateur céramique Y5V L'ESR est importante en DC, mais elle tombe rapidement avec la fréquence

Bien que leurs performances électriques varient d'une façon plus ou moins importantes selon le diélectrique, ces condensateurs présentent l'avantage d'avoir une forte capacité volumique, ce qui fait que, tant que leur capacité n'est pas trop importante, ils sont moins chers, plus petits et plus fiables que les autres condensateurs.

## 1.3.2.3.2 Condensateurs en tantale

Ce paragraphe est basé sur les références suivantes : [avxcorp], [kemet], [nec] et [vishay]

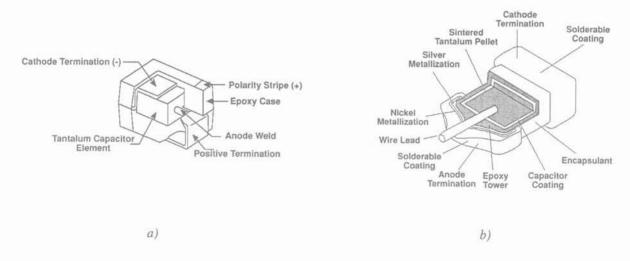

La fabrication des condensateurs en tantale avec un électrolyte solide diffère complètement de celle des condensateurs en céramique multicouche. Deux possibilités sont représentées sur la figure F1.3-20. Dans le premier cas l'ensemble capacitif est placé dans un boîtier alors que dans le second cas il est enrobé dans une résine.

La capacité du condensateur est alors déterminée par la formule suivante

$C = \frac{e \cdot A}{t}$  avec e : constante qui vaut 26 A : surface du diélectrique

t : épaisseur du diélectrique

F1.3-20 : Coupes de condensateurs en tantale a)Condensateur moulé b) Condensateur enrobé

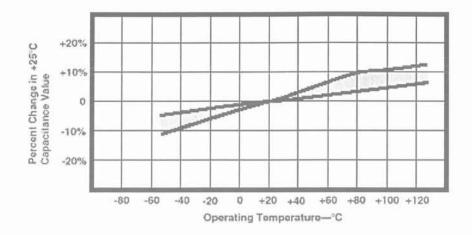

D'après les fabricants, les condensateurs en tantale sont soumis à moins de variations que les condensateurs en céramique à base de diélectrique de type 2. La figure F1.3-21 montre effectivement que la variation de la capacité en fonction de la température est de l'ordre de  $\pm 10\%$  alors que dans le cas du meilleur céramique elle est de  $\pm 15\%$ .

F1.3-21 : Capacité en fonction de la température pour les condensateurs tantale La capacité augmente avec la température, la variation reste inférieure à  $\pm 12\%$

Comme pour les condensateurs en céramique, l'ESR diminue lorsque la température augmente, fig. F1.3-22.

Multiplier of 100kHz ESR

-25

F1.3-22 : ESR en fonction de la température pour les condensateurs en tantale

L'ESR diminue lorsque la température augmente

25

Temperature - Degrees Centigrade

50

75

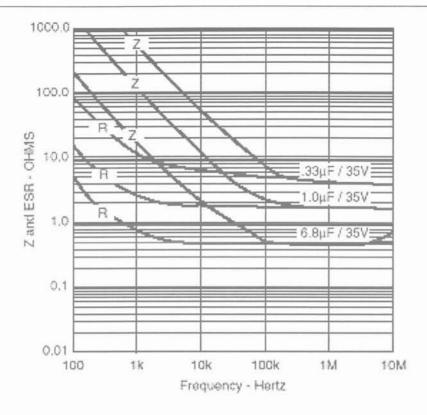

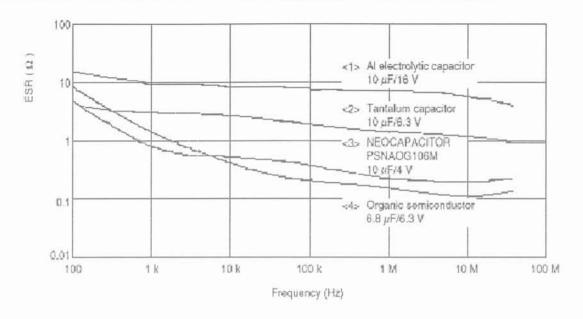

Sur la courbe de variation en fréquence de l'ESR, fig. F1.3-23, nous constatons que celle-ci diminue avec la fréquence. Il est particulièrement net que cette variation s'effectue selon deux pentes, la première à basse fréquence est importante tandis que la deuxième, à plus hautes fréquences, est beaucoup plus douce. En effet, à basses fréquences, l'ESR est principalement due à la résistance du diélectrique alors qu'à hautes fréquences l'ESR provient essentiellement de la résistance de l'électrolyte et de l'effet de peau dans les électrodes.

F1.3-23 : ESR ( R) et impédance (Z) en fonction de la fréquence pour condensateur en tantale L'ESR diminue selon deux pentes, une importante à basses fréquence et une faible à hautes fréquences

Les condensateurs en tantale permettent d'obtenir des capacités importantes, jusqu'à 220µF pour des boîtiers qui respectent l'épaisseur tolérée mais au prix de dimensions importantes. Ils offrent en outre peu de variations de leurs performances électriques et ne sont pas soumis au phénomène de vieillissement. Par contre ils restent moins fiables et plus coûteux que les condensateurs en céramique pour des valeurs de capacité inférieures à 10µF.

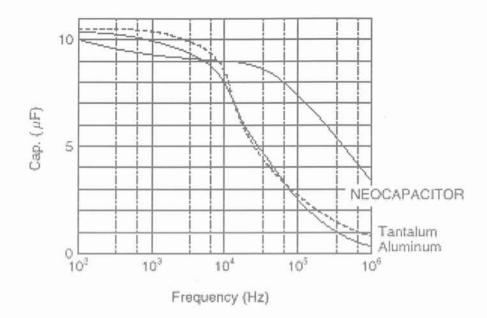

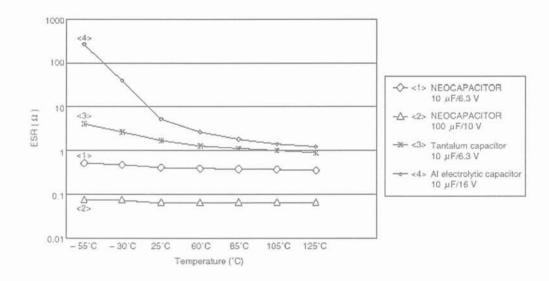

Une nouvelle génération de condensateur en tantale est récemment apparue. Les figures suivantes, F1.3-24 à F1.3-26, donnent leurs principales caractéristiques. L'appellation NeoCapacitor utilisée ici est celle du fabricant NEC.

F1.3-24 : Capacité en fonction de la fréquence pour les condensateurs NeoCapacitor Les nouveaux condensateurs en tantale possèdent une fréquence de résonance plus élevée mais la capacité varie plus à basses fréquences

F1.3-25 : ESR en fonction de la température (f=100kHz) pour les condensateurs NeoCapacitor L'ESR varie moins en température et sa valeur est plus faible

F1.3-26 : ESR en fonction de la fréquence pour les condensateurs NeoCapacitor

## 1.3.2.4 Inductances

Comme pour les condensateurs, la principale contrainte sur les inductances repose sur ses dimensions qui doivent rester les plus faibles possibles afin de limiter la taille du téléphone portable.

Pour ces composants les informations sont beaucoup plus restreintes. Nous avons donc été amenés à faire des mesures sur une inductance donnée pour établir un modèle avec les différents éléments parasites.

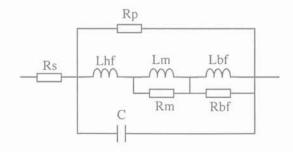

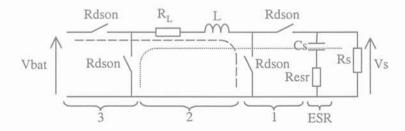

En se basant sur les résultats obtenus dans [Schellmanns99], nous partons du modèle représenté par la figure F1.3-27

F1.3-27: Représentation de l'inductance

L'impédance de ce modèle vaut alors :

$$\mathrm{impedance}_{\mathrm{n}} \coloneqq \left[ \left( \frac{\mathrm{i} \cdot \mathrm{W}_{\mathrm{n}} \cdot \mathrm{Lbf} \cdot \mathrm{Rbf}}{\mathrm{i} \cdot \mathrm{W}_{\mathrm{n}} \cdot \mathrm{Lbf} + \mathrm{Rbf}} + \frac{\mathrm{i} \cdot \mathrm{W}_{\mathrm{n}} \cdot \mathrm{Lm} \cdot \mathrm{Rm}}{\mathrm{i} \cdot \mathrm{W}_{\mathrm{n}} \cdot \mathrm{Lm} + \mathrm{Rm}} + \mathrm{i} \cdot \mathrm{W}_{\mathrm{n}} \cdot \mathrm{Lhf} \right)^{-1} + \frac{1}{\mathrm{Rp}} + \mathrm{i} \cdot \mathrm{C} \cdot \mathrm{W}_{\mathrm{n}} \right]^{-1} + \mathrm{Rs}$$

## où Wn est une pulsation

- Lhf est la valeur de l'inductance

- Rs, la résistance série qui domine le comportement de l'impédance à basses fréquences

- · C et Rp représentent la résonance

- Les cellules Lm//Rm et Lbf//Rbf représentent les pertes par courants de Foucault.

Un premier modèle avait été calculé avec une seule de ces cellules, mais pour améliorer la correspondance entre la mesure et la courbe obtenue à partir du modèle, nous avons introduit une deuxième cellule, ce qui suffit pour obtenir un résultat précis.

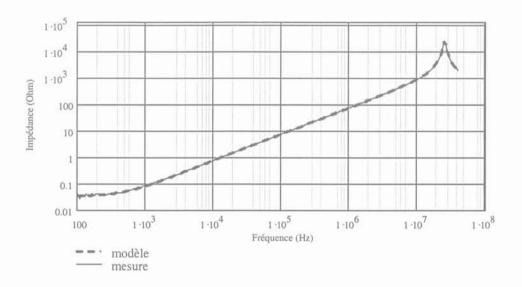

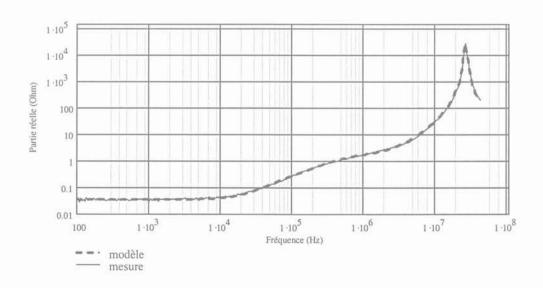

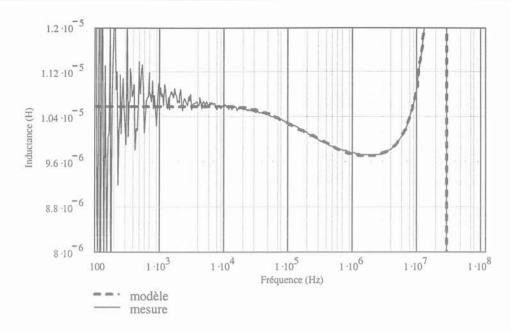

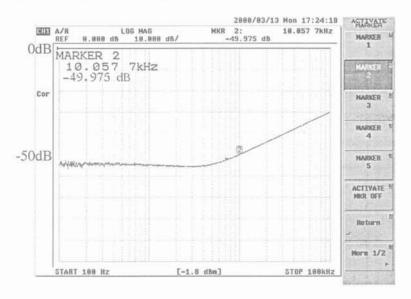

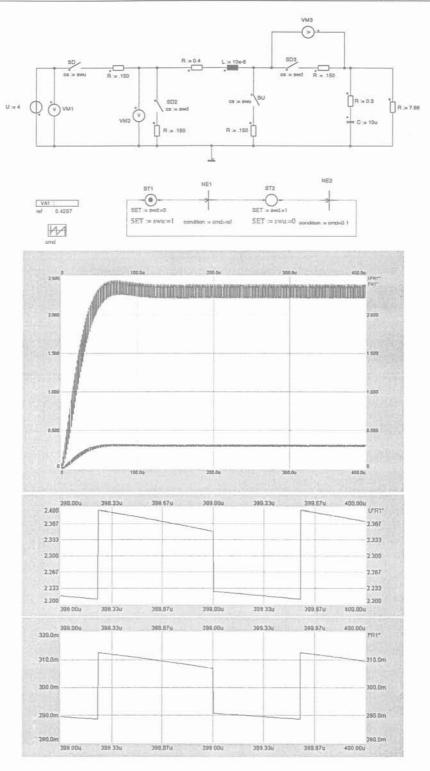

Les mesures sur l'inductance ont été effectuées au LEG avec un analyseur d'impédance HP4194A, elles permettent d'obtenir le module, figure F 1.3-28, et la phase de son impédance en fonction de la fréquence ainsi que ses parties réelle et imaginaire, respectivement figure F 1.3-29 et figure F 1.3-30. Nous superposons à celles-ci les courbes obtenues à partir du modèle. Il reste alors à ajuster les valeurs des différents paramètres pour faire correspondre le modèle à la mesure.

- Pour cela nous donnerons au paramètre Lhf sa valeur théorique, 10μH,

- Puis nous ajustons Rs avec la courbe de l'impédance en basses fréquences, fig. F

1.3-28,

- C est tout d'abord déterminé à partir de la fréquence de résonance  $Frésonance = \frac{1}{2\pi \cdot \sqrt{Lhf \cdot C}}, \text{ puis ajusté sur la courbe d'impédance pour que le}$

pic de résonance se produise à la même fréquence dans les deux cas,

- Rp permet d'ajuster la valeur du module de l'impédance à la fréquence de résonance,

- Les cellules Lm//Rm et Lfb//Rbf sont déterminées par la courbe d'inductance, fig.

F 1.3-30, mais doivent aussi vérifier que la relation Lbf+Lm+Lhf concorde avec la valeur de la courbe inductance.

Finalement cette méthode permet de déterminer les valeurs des paramètres du modèle choisi. Dans notre cas :

Lhf=9.63µH, Lbf=0.45µH, Lm=0.5µH,

Rs=32m $\Omega$ , Rp=19.6k $\Omega$ , Rbf=0.2 $\Omega$ , Rm=1.2 $\Omega$ ,

C=4.18pF

Les courbes F 1.3-28 à F 1.3-30 permettent de constater que la concordance entre la mesure effectuée et les courbes obtenues d'après le modèle est très satisfaisante.

$F~1.3-28: Module~de~l'imp\'edance\\ La~courbe~calcul\'ee~\`a~partir~du~mod\`ele~correspond~bien~\`a~la~mesure$

F 1.3-29 : Partie réelle La courbe calculée à partir du modèle correspond bien à la mesure

F 1.3-30 : Inductance La courbe obtenue à partir du modèle correspond bien aux mesures

Pour justifier le bruit qui apparaît à basse fréquence sur la courbe F 1.3-30, nous faisons l'hypothèse qu'il provient, lors de la mesure, de parasites liés à la dominance de la résistance Rs.

## CONCLUSION

Dans ce chapitre nous avons vu le rôle des régulateurs de tension pour les systèmes alimentés par une source d'énergie unique, et plus précisément la batterie dans le cas des téléphones portables. Nous avons expliqué le principe de fonctionnement des trois types de régulateurs de tension rencontrés dans les systèmes de gestion de l'énergie délivrée par une batterie aux autres circuits intégrés. Pour permettre une compréhension plus aisée d'une part de l'enjeu de cette étude et d'autre part des phénomènes parasites lors de la suite de cet exposé, nous avons alors montré comment se décompose une famille de technologies selon les critères de fonctionnalité des circuits ainsi réalisés par STMicroelectronics. A partir de là, nous avons détaillé les caractéristiques des composants électriques disponibles dans la technologie CMOS analogique 0.5µ, dont un transistor bipolaire.

Comme la conception de ces régulateurs de tension est à la fois dépendante des variations de la tension délivrée par la batterie, mais aussi des variations des valeurs des composants externes, composants non intégrés, tels que les capacités et les ESR des condensateurs ainsi que la valeur de l'inductance et de sa résistance série, nous avons terminé ce chapitre par une courte étude sur les variations de ces valeurs. Afin que celle-ci ne soit pas

restrictive car les composants externes finalement utilisés dans l'application ne sont que très rarement connus au moment de la conception du régulateur, nous n'en tirons pas de modélisation précise, mais seulement un ordre de grandeur de l'évolution de ces valeurs, ce qui a toutefois l'inconvénient de nous pénaliser.

# CHAPITRE 2

### INTRODUCTION

## 2.1 Pourouoi Utiliser Une Technologie Cmos?

| 221    | Voc   | ABIT | Y A Y | TOTAL | ASSO     | CITE |

|--------|-------|------|-------|-------|----------|------|

| horald | V C)C | ABU  | LAI   | REL   | A.S.S.L. |      |

- 2.2.1 Drop-out, Tension De Dechet

- 2.2.2 COURANT DE SORTIE MAXIMUM (EN FONCTIONNEMENT NORMAL)

- 2.2.3 REJECTION DE L'ALIMENTATION

- 2.2.4 Consommation

- 2.2.5 RENDEMENT

- 2.2.6 REGULATION DE LIGNE

- 2.2.7 REGULATION DE LIGNE TRANSITOIRE

- 2.2.8 REGULATION DE CHARGE

- 2.2.9 REGULATION DE CHARGE TRANSITOIRE

- 2.2.10 Precision Sur La Tension De Sortie

- 2.2.11 PROTECTION CONTRE LES COURTS-CIRCUITS

- 2.2.12 TEMPS D'ETABLISSEMENT DE LA TENSION DE SORTIE

- 2.2.13 BRUIT

#### 2.3 REALISATION

- 2.3.1 L'AMPLIFICATEUR

- 2.3.2 LA BOUCLE DE CONTRE REACTION

- 2.3.3 Mos De Sortie

## 2.4 COMPENSATION DYNAMIQUE

- 2.4.1 RAPPEL SUR LA STABILITE DES SYSTEMES BOUCLES

- 2.4.2 Principe De Compensation D'Un Regulateur Lineaire

- 2.4.3 APPLICATION AU LDO EN TECHNOLOGIE CMOS

## 2.5 PROTECTION CC

- 2.5.1 ASSERVISSEMENT EN COURANT CLASSIOUE

- 2.5.2 Nouvelle Protection Contre Les Courts-Circuits Partie Statique

- 2.5.3 PARTIE DYNAMIOUE

- 2.5.4 PRE POLARISATION EN PDN

- 2.5.5 IMPRECISION DU COURANT DE REFERENCE

- 2.5.6 SIMULATIONS DE VERIFICATION

#### 2.6 RESULTATS

- 2.6.1 SIMULATIONS

- 2.6.2 MESURES

#### CONCLUSION

## 2 LDO CMOS

#### INTRODUCTION

Le premier régulateur que nous allons étudier est un régulateur linéaire, c'est jusqu'à présent le plus courant et le mieux connu, mais il est encore susceptible de nombreuses évolutions afin d'accroître ses performances.

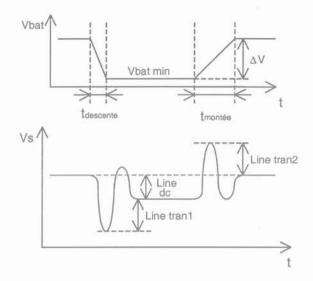

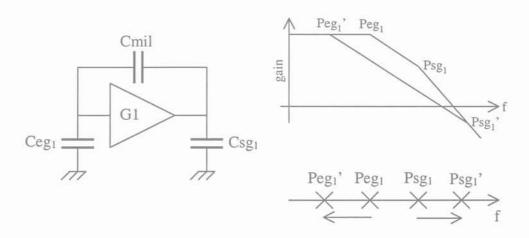

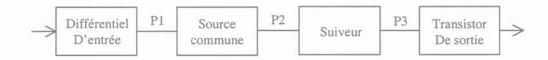

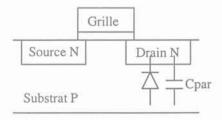

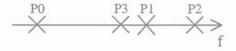

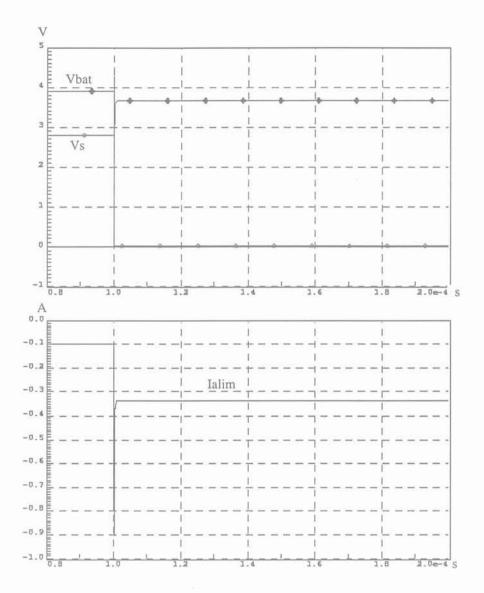

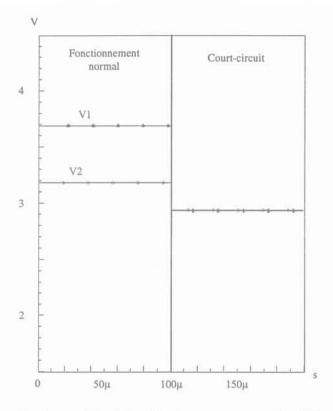

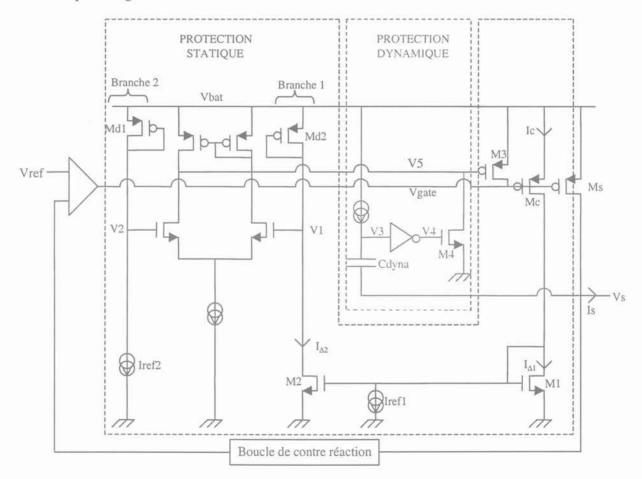

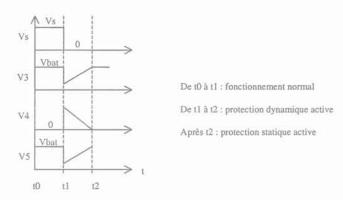

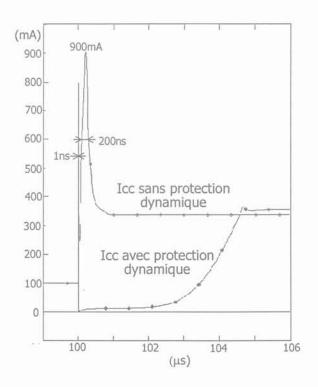

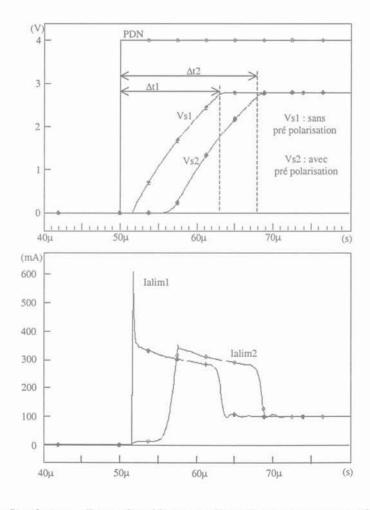

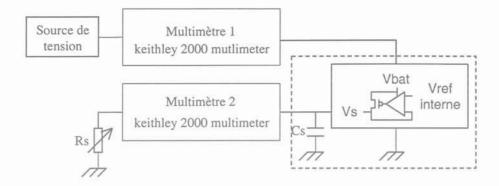

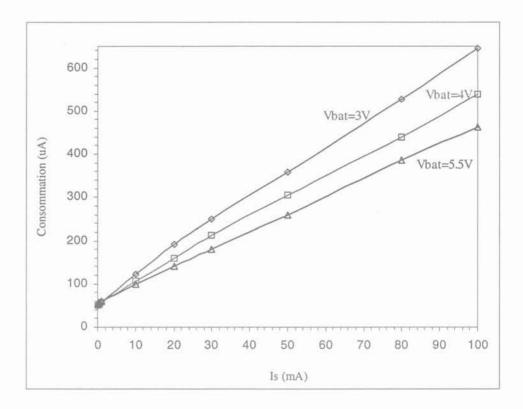

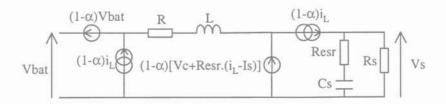

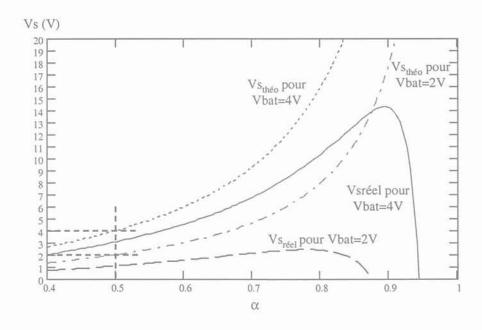

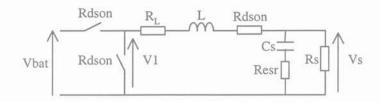

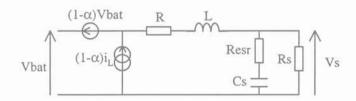

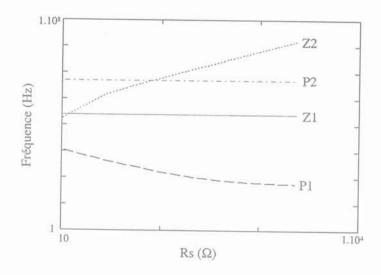

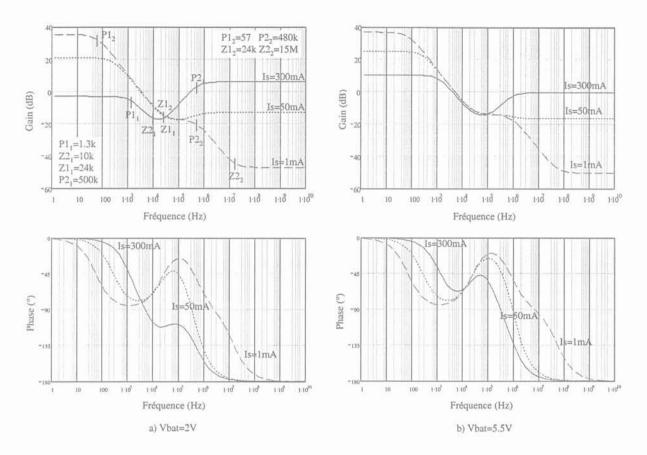

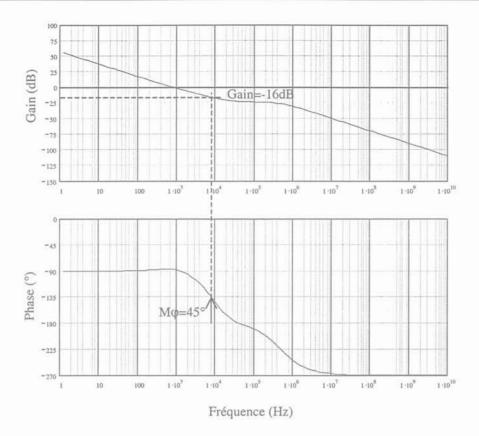

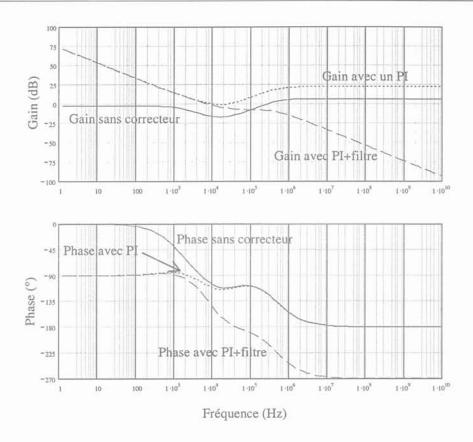

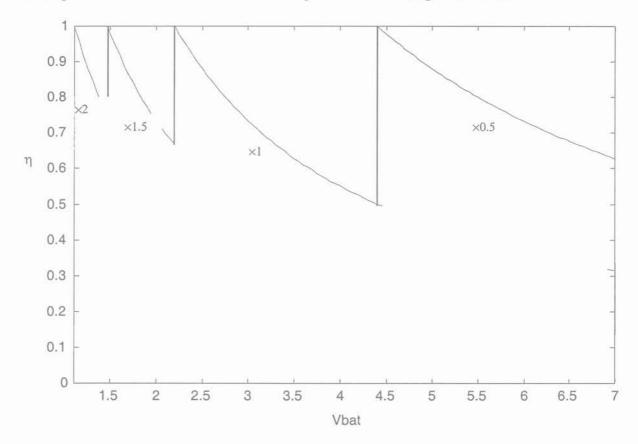

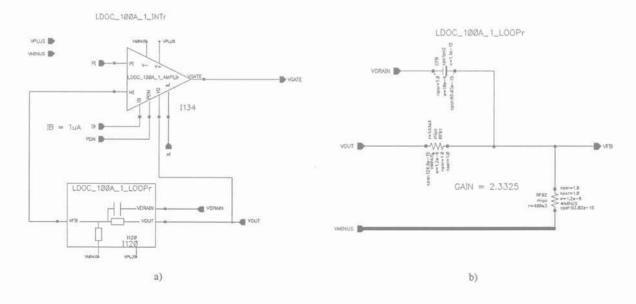

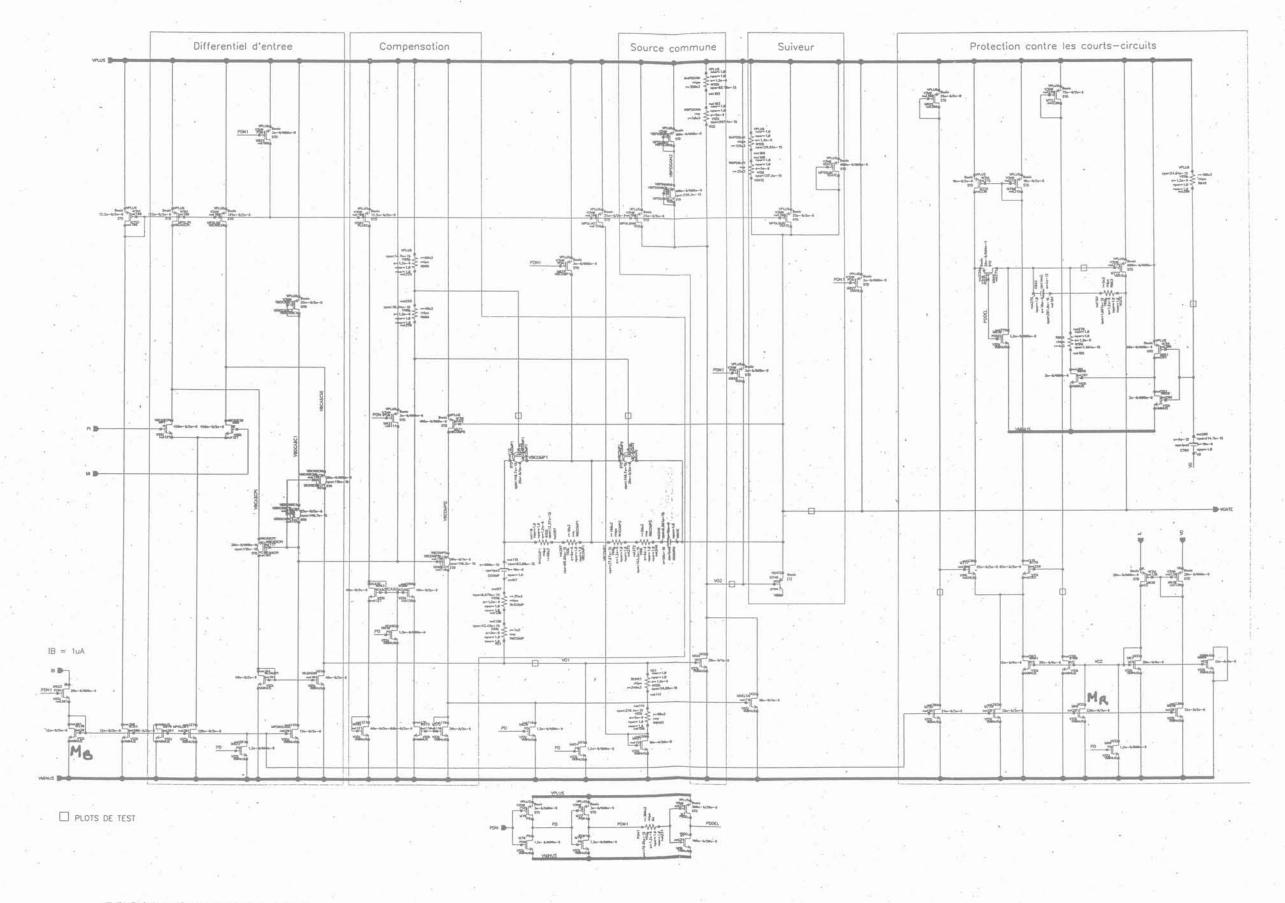

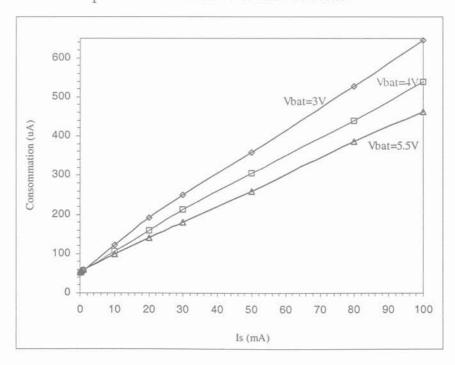

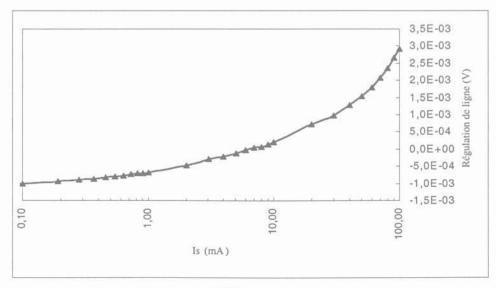

Nous débuterons ce chapitre par une explication sur les besoins de concevoir ce type de cellules à partir d'une technologie CMOS analogique et non plus à partir d'une technologie BiCMOS analogique. Nous définirons ensuite le vocabulaire spécifique à la régulation de tension, ce qui nous permettra d'aborder la suite de cet exposé, la réalisation. Le développement de celle-ci est brièvement décrit, il sert de point de départ à l'étude des deux points clés du chapitre : Le système de compensation et la protection contre les courts-circuits.