# Development of an ultra-fast X-ray camera using hybrid pixel detectors.

Arkadiusz Dawiec

#### ▶ To cite this version:

Arkadiusz Dawiec. Development of an ultra-fast X-ray camera using hybrid pixel detectors.. Human-Computer Interaction [cs.HC]. Université de la Méditerranée - Aix-Marseille II, 2011. English. NNT: . tel-00631274

### HAL Id: tel-00631274 https://theses.hal.science/tel-00631274v1

Submitted on 12 Oct 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

CPPM-T-2011-01

# UNIVERSITÉ DE LA MÉDITERRANÉE AIX-MARSEILLE II FACULTÉ DES SCIENCES DE LUMINY

163, avenue de Luminy 13288 Marseille Cedex 09

#### THÈSE DE DOCTORAT

Spécialité : Instrumentation

présentée par

#### Arkadiusz DAWIEC

en vue dobtenir le grade de docteur de l'Université de la Méditerranée

# Développement d'une caméra X couleur ultra-rapide à pixels hybrides

Development of an ultra-fast X-ray camera using hybrid pixel detectors

Soutenue le 4 mai 2011, devant le jury composé de :

Mr Jean-François BERAR

Mr Jean-Claude CLEMENS

Examinateur

Mr Bernard DINKESPILER

Co-encadrant

Mr Wojciech DULINSKI

Examinateur

Mr Richard JACOBSSON

Rapporteur

Mr Eric KAJFASZ

Examinateur

Directeur de thèse

Mr Christian MOREL

# Acknowledgements

I would like to express my gratitude to many people who have helped me and made this thesis possible.

First and foremost I want to thank my thesis supervisor, Professor Christian Morel, leader of the imXgam group, for his motivation, patience and support during my research and thesis-writing times.

I would like to thank my thesis committee: Jean-François Bérar, Jean-Claude Clémens, Bernard Dinkespiler, Wojciech Dulinski, Richard Jacobsson and Eric Kajfasz, for their insightful comments and questions.

My endless gratitude goes to my co-supervisor Bernard Dinkespiler, who was a great mentor, source of knowledge and new ideas. My sincere thanks also goes to Jean-Claude Clémens, who was always open for a fruitful discussion and willing to share his knowledge. It was a real privilege to work with them.

Special thanks goes to Pierre-Yves Duval, for his work on software development, his advices and comments that helped me to finish this project.

I am grateful to Franck Debarbieux who helped me to prepare and conduct a final test of the camera with a mouse. In this place I also wish to express my warm thanks to the members of the imXpad group, for their friendliness and all of the invaluable support that I have received from them during my work.

I would like to thank our synchrotron partners: Stéphanie Hustache, Kadda Medjoubi (SOLEIL), Jean-François Bérar, Nathalie Boudet (ESRF), for their kind support that have been of great value during my studies.

I am indebted to our secretary ladies, Fanny, Hélène and Esthere, for helping me to find my way through all the bureaucratic and administration issues and thus helped me to concentrate on my research.

Last but not least, I wish to thank my family for their support. Especially, I owe my loving thanks to my wife Edyta, without her encouragement and understanding it would not have been impossible for me to finish this work.

## Abstract

#### Title:

Development of an ultra-fast X-ray camera using hybrid pixel detectors.

#### Abstract:

The aim of the project, of which the work described in this thesis is part, was to design a high-speed X-ray camera using hybrid pixels applied to biomedical imaging and for material science. As a matter of fact the hybrid pixel technology meets the requirements of these two research fields, particularly by providing energy selection and low dose imaging capabilities. In this thesis, high frame rate X-ray imaging based on the XPAD3-S photons counting chip is presented. Within a collaboration between CPPM, ESRF and SOLEIL, three XPAD3 cameras were built. Two of them are being operated at the beamline of the ESRF and SOLEIL synchrotron facilities and the third one is embedded in the PIXSCAN II irradiation setup of CPPM. The XPAD3 camera is a large surface X-ray detector composed of eight detection modules of seven XPAD3-S chips each with a high-speed data acquisition system. The readout architecture of the camera is based on the PCI Express interface and on programmable FPGA chips. The camera achieves a readout speed of 240 images/s, with maximum number of images limited by the RAM memory of the acquisition PC. The performance of the device was characterize by carrying out several high speed imaging experiments using the PIXSCAN II irradiation setup described in the last chapter of this thesis.

#### Keywords:

Hybrid pixels, XPAD3, photon counting, PCI Express, X-ray imaging, X-ray camera, FPGA

# Résume

#### Titre:

Développement d'une caméra à rayons X ultra-rapide utilisant des détecteurs à pixels hybrides.

#### Résume:

L'objectif du projet, dont le travail présenté dans cette thèse est une partie, était de développer une caméra à rayons X ultra-rapide utilisant des pixels hybrides pour l'imagerie biomédicale et la science des matériaux. La technologie à pixels hybrides permet de répondre aux besoins des ces deux champs de recherche, en particulier en apportant la possibilité de slectionner l'énergie des rayons X détectés et de les imager à faible dose. Dans cette thèse, nous présentons une caméra ultra-rapide basée sur l'utilisation de circuits intégrés XPAD3-S développés pour le comptage de rayons X. En collaboration avec l'ESRF et SOLEIL, le CPPM a construit trois caméras XPAD3. Deux d'entre elles sont utilisée sur les lignes de faisceau des synchrotrons SOLEIL et ESRF, et le troisième est installé dans le dispositif d'irradiation PIXSCAN II du CPPM. La caméra XPAD3 est un détecteur de rayons X de grande surface composé de huit modules de détection comprenant chacun sept circuits XPAD3-S équipés d'un système d'acquisition de données ultrarapide. Le système de lecture de la caméra est basé sur l'interface PCI Express et sur l'utilisation de circuits programmables FPGA. La caméra permet d'obtenir jusqu'à 240 images/s, le nombre maximum d'images étant limité par la taille de la mémoire RAM du PC d'acquisition. Les performances de ce dispositif ont été caractérisées grâce à plusieurs expériences à haut débit de lecture réalisées dans le système d'irradiation PIXSCAN II. Celles-ci sont décrites dans le dernier chapitre de cette thèse.

### Mots-clés :

Pixels hybrides, XPAD3, comptage de photons, PCI Express, imagerie à rayons X, caméra à rayons X, FPGA

# Contents

| In | $\mathbf{trod}^{\cdot}$ | uction  |                                  | 1  |

|----|-------------------------|---------|----------------------------------|----|

| 1  | Phy                     | sics of | f X-ray imaging                  | 3  |

|    | 1.1                     | X-ray   | interaction with matter          | 5  |

|    |                         | 1.1.1   | Photoelectric effect             | 5  |

|    |                         | 1.1.2   | Scattering                       | 6  |

|    |                         | 1.1.3   | X-ray attenuation and filtration | 10 |

|    |                         | 1.1.4   | Radiation damage                 | 12 |

|    | 1.2                     | Imagii  | ng techniques with X-rays        | 13 |

|    |                         | 1.2.1   | Radiography                      | 14 |

|    |                         | 1.2.2   | Crystallography                  | 16 |

| 2  | Sen                     | nicond  | uctor pixel detectors            | 19 |

|    | 2.1                     |         | ple of operation                 | 19 |

|    |                         | 2.1.1   | Semiconductors physics           | 19 |

|    |                         | 2.1.2   | Charge collection                | 27 |

|    |                         | 2.1.3   | Signal formation                 | 32 |

|    |                         | 2.1.4   | Noise in semiconductor detectors | 33 |

|    | 2.2                     | Semic   | onductor pixel detectors         | 34 |

|    |                         | 2.2.1   | Charge Coupled Devices (CCD)     | 34 |

|    |                         | 2.2.2   | Monolithic pixel sensor          | 35 |

|    |                         | 2.2.3   | Hybrid pixel detector            | 38 |

| 3  | XP                      | AD3 X   | Z-ray camera                     | 51 |

|    | 3.1                     |         | luction                          | 51 |

|    | 3.2                     |         | O3 photon counting chip          | 52 |

|    |                         | 3.2.1   | Global architecture              | 52 |

|    |                         | 3.2.2   | Pixel details                    | 53 |

|    |                         | 3.2.3   | Modes of operation               | 55 |

|    |                         | 3.2.4   | Global configuration registers   | 58 |

|    |                         | 3.2.5   | Calibration                      | 59 |

|    |                         | 3.2.6   | Data transfer                    | 62 |

|    | 3.3                     | Archit  | tecture of the XPAD3 camera      | 63 |

|    |                         | 3.3.1   | Overview                         | 63 |

|    |                         | 3.3.2   | Detection modules                | 65 |

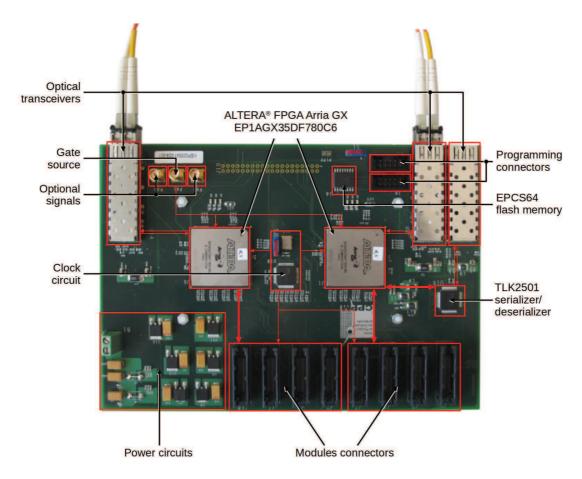

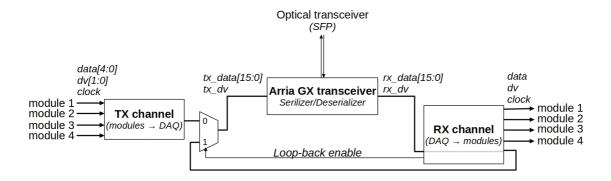

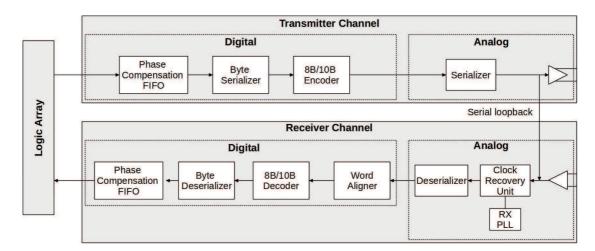

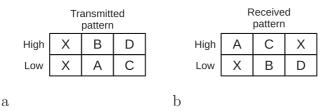

|    |                         | 3.3.3   | The HUB board                    | 77 |

|    |                         | 3 3 1   | The PCI Express® heard           | 25 |

viii *CONTENTS*

|              |       | 3.3.5   | Software library                                           | . 97  |

|--------------|-------|---------|------------------------------------------------------------|-------|

| 4            | Exp   | erime   | ntal results                                               | 105   |

|              | 4.1   | Exam    | ple of synchrotron source experiments                      | . 105 |

|              |       | 4.1.1   |                                                            |       |

|              |       | 4.1.2   | Diffraction on an epitaxial GaInAs film grown on GaAs sub- |       |

|              |       |         | strate                                                     | . 108 |

|              | 4.2   | Fast re | eadout results                                             |       |

|              | 1.2   | 4.2.1   | The PIXSCAN II demonstrator                                |       |

|              |       | 4.2.2   | Study of a free falling steel ball                         |       |

|              |       | 4.2.3   |                                                            |       |

|              |       | 4.2.4   |                                                            |       |

|              |       | 1.2.1   | Thouse ungregicity                                         | . 121 |

| Co           | onclu | sions   | and prospects                                              | 131   |

| A            | PCI   | Expr    | ess Configuration Space                                    | 135   |

| В            | Exa   | mple o  | of a data acquisition program                              | 137   |

| $\mathbf{C}$ | Influ | uence   | of the Stokes force on a free falling ball                 | 141   |

| D            | Rela  | ation b | between the diameter of a circle and its RMS               | 145   |

| E            | Soft  | waro o  | design tools                                               | 147   |

|              |       |         | are tools                                                  |       |

|              |       |         | amming guidelines                                          |       |

|              | 12.2  | 1 TOGIA | anning guidennes                                           | . 140 |

| Li           | st of | Figure  | es                                                         | 150   |

| Li           | st of | Tables  |                                                            | 159   |

### Introduction

The progress in X-ray imaging techniques has continued since the time of their discovery by Wilhelm Röntgen at the end of XIX<sup>th</sup> century. The first application of X-rays was radiography and was initiated with the first public presentation of an X-ray image of the hand of the famous Swiss anatomist Albert von Kölliker, two months after Rötgen's discovery. Shortly after, their use in determining the atomic structure of crystals were discovered, thus initiating a new field of science called X-ray crystallography. Since then, advance in both the fields of X-ray medical imaging and X-ray crystallography depends on the improvement of X-ray sources and X-ray detectors. Currently, CCD detectors that were state-of-theart at the end of the XX<sup>th</sup> century cannot fully benefit from new high intense X-ray synchrotron beams. Similarly, detectors that are currently used medical imaging have reached their limits in terms of minimum radiation dose to the patients in order to get images with sufficient contrast and quality. The hybrid pixel technology applied to photon counting is an example of a recent advance applied to X-ray detection. These type of devices offer a quite high signal-to-noise ratio (SNR) at a low radiation dose. Additionally, the possibility to count single photons and to select energies independently in every pixel opens the possibility to perform experiments that were hardly feasible most recently. Moreover, hybrid pixels can be read out much faster than CCDs, and potentially without dead time.

The work presented in this thesis is based on the development of hybrid pixels detectors for X-ray photon counting, which is carried out within the imXgam group at CPPM. The goal of this thesis was to design and develop a high frame rate data acquisition system for the XPAD3 hybrid pixel camera.

The structure of the thesis reads as follows.

Chapter 1 contains a theoretical introduction to the physics of the X-ray radiation. The interactions of X-ray photons with matter are described, as well as the main techniques used in X-ray imaging for biomedical and crystallography applications.

2 CONTENTS

In chapter 2, different designs of semiconductor pixel detectors are discussed. The first part of this chapter includes the physics of the semiconductors that is required to comprehend the concept of semiconductor detectors, whereas in the second part, different architectures of the semiconductor pixel detectors are described.

A detailed description of the architecture of the XPAD3 detector is given in chapter 3. This chapter starts with the description of the XPAD3 photon counting chip, followed by a detailed description of the readout system developed within this work.

Three experiments were carried out to demonstrate and characterize the performance of the XPAD3 camera. A short data analysis of each of these experiments is given in chapter 4. Moreover, results of two experiments that were carried out at the SOLEIL synchrotron facility are also presented.

Finally, the presentation of this thesis ends with some conclusions and prospects.

# Chapter 1

# Physics of X-ray imaging

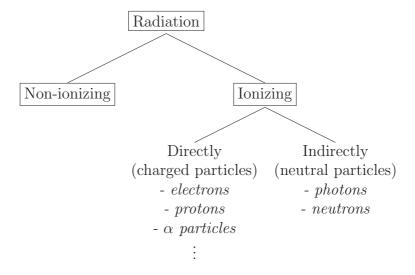

Radiation can be described as emission and propagation of energy trough matter. Depending on the level of energy per quanta, and thus on its ability to ionize mater, radiation can be classified either as non-ionizing or ionizing (see figure 1.1) [74]. Non-ionizing radiation covers all the spectrum of electromagnetic radiation with the frequency below  $\sim 10^{15}~MHz$  (i.e. near ultraviolet, visible light and radio waves). Ionizing radiation has an energy exceeding the ionization potential of atoms. There are two different types of ionizing radiation, indirect and direct. Indirect ionization is done in a two-step process: i) release of charged particles by a photon (i.e. an electron or an electron/positron pair) and ii) energy deposition in the atom. Indirectly ionizing radiation covers the electromagnetic spectrum with frequencies above near-ultraviolet ( $\sim 10^{15}~MHz$ ) and neutrons. Directly ionizing

Figure 1.1: Classification of radiation [74].

radiation comprises charge particles like electrons, protons, alpha-particles and heavy ions. Charge particles deposit their energy in the absorber through direct Coulomb interaction with orbital electrons of an atom.

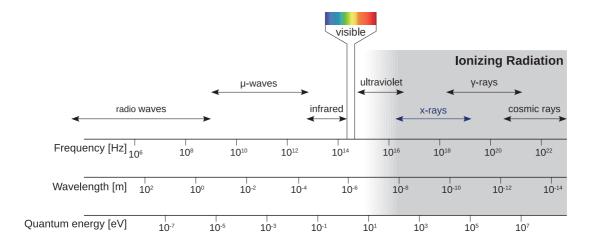

X-ray radiation is a form of electromagnetic radiation discovered in 1895 by Wilhelm C. Röntgen. X-rays have a frequency between  $3 \times 10^{16}~Hz$  and  $3 \times 10^{19}~Hz$  (figure 1.2). Thus, according to the formula

$$E = \frac{hc}{\lambda} \tag{1.1}$$

where h is the Planck's constant  $(6.626 \times 10^{-34} J \cdot s)$ , c is the speed of light ( $\approx 3 \times 10^8 m/s$ ) and  $\lambda$  is the wavelength, the energy E of X-ray photons varies from 120 eV to 120 keV, which is enough to ionize atoms and molecules [62]. X-rays with a wavelength longer that 1 nm are called soft X-rays and those with shorten wavelengths are called hard X-rays. The wavelength of hard X-rays is of the order of 1 Å (1  $Angstrom = 10^{-10} m$ ). This length is comparable to atomic sizes, which makes them very useful for diffraction experiments. The most usual sources of X-rays are X-ray tubes, where radiation is produced as a result of deceleration of very fast electrons hitting a solid object (target). The resulting spectrum is composed of two components, a continuous spectrum of X-rays coming from bremsstrahlung (breaking radiation) and characteristic X-ray peaks resulting from direct ionization of shell electrons of the target atoms [50]. Vacancies created in the K-shell of the atom are filled by electrons dropping from the upper shells while emitting X-rays with energies corresponding to the energy difference between

Figure 1.2: Spectrum of electromagnetic radiation.

the atomic levels. X-rays produced by transitions from the L-shells are called  $K_{\alpha}$  and those from the M-shells are  $K_{\beta}$ . The second source of X-rays are synchrotron radiation facilities where accelerated electrons move within circular trajectories. Some electromagnetic devices such as wigglers are also radiating energy in the X-ray domain.

### 1.1 X-ray interaction with matter

When an X-ray photon is traversing through matter, there are three possible outcomes: i) it can transfer its energy to atoms of the material, ii) it can be scattered, or iii) it can pass through it without interacting. The probability that an interaction occurs is expressed in terms of a cross section ( $\sigma$ ). The bigger the cross section, the higher the probability of interaction will be. A cross section is expressed in units of barns, where 1 barn =  $10^{-24}$  cm<sup>2</sup>. The total cross section is the sum of the cross sections of the different possible interactions between the photons and the absorber.

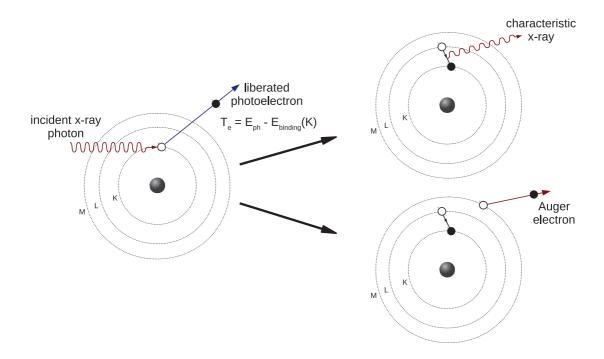

#### 1.1.1 Photoelectric effect

The photoelectric effect results from a collision between the incident photon and an inner-shell electron of an atom (see figure 1.3). During this interaction, the total energy of the photon is transferred to the electron. If the energy of the photon  $(E_{ph})$  is higher than the binding energy of the electron, this electron can be ejected and become a free photoelectron. The kinetic energy of the photoelectron  $(T_e)$  is the difference between the photon energy and the electron binding energy  $(E_{binding})$ .

$$T_e = E_{nh} - E_{binding} \tag{1.2}$$

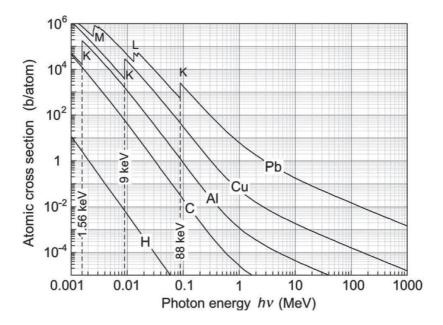

The photoelectric effect is responsible for the ionization of the atom by creating a vacancy in one of the electron shells. This vacancy is filled by a cascade of electron transitions and emission of characteristic X-rays or Auger electrons with energies corresponding to the difference between the binding energies of the shells. The photoelectric cross section depends on the energy of the X-ray photon. The photoelectric effect is most probable when  $E_{ph} \cong E_{binding}$  and decreases with increasing  $E_{ph}$ . When the process becomes energetically possible, the probability of interaction suddenly increases and appears as an edge in the cross section curve

FIGURE 1.3: Photoelectric effect. An X-ray photon with energy  $E_{ph}$  interacts with a K shell electron that becomes a free photoelectron with a kinetic energy equals to the difference between  $E_{ph}$  and the binding energy of the K-shell electron  $E_{binding}(K)$ .

(figure 1.4). The edge related to the K-shell at  $E_{binding}(K)$  is called K-edge and the ones to the L-shell at  $E_{binding}(L)$  L-edges, and so forth.

A good approximation of the photoelectric cross section is given by the equation

$$\sigma \approx \frac{Z^5}{(E_{ph})^{7/2}} \text{, for } E_{ph} < m_e c^2;$$

(1.3)

where Z represents atomic number of the absorber. It can be seen that the photoelectric effect becomes important for high Z atoms and for photons with an energy below 1 MeV, hence it has a large cross section in the range of X-ray energies.

### 1.1.2 Scattering

A scattering interaction occurs when the direction of an incident photon is altered from its original trajectory. The scattering process may cause energy loss to the photon. In this case, it is called *inelastic scattering*, otherwise it is called *elastic scattering*.

FIGURE 1.4: Cross section of the photoelectric effect for various materials (from [74]).

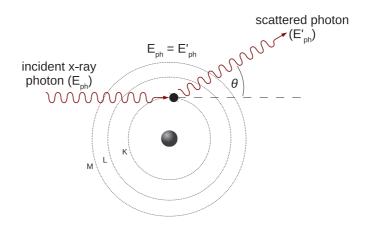

#### 1.1.2.1 Elastic scattering

Elastic scattering, also called coherent or Rayleigh scattering, is a collision between an X-ray photon and an electron of the target atom. During the interaction, the atom absorbs the change of the momentum and the photon is being scattered with an angle  $\theta$  (figure 1.5). There are no energy transfers from the incident photon to the absorber: the energies of the scattered and incident photons are the same ( $E_{ph} = E'_{ph}$ ). The scattering angle depends on the energy of the incident

FIGURE 1.5: Elastic scattering.

photon and probability of interaction increases at low scattering angles. Elastic scattering is important for X-rays with low energies and for nucleus with high atomic numbers.

The differential cross section of Rayleigh scattering can be described by the formula

$$\frac{d\sigma_R}{d\Omega} = \frac{r_e^2}{2} (1 + \cos^2 \theta) \{ F(x, Z) \}^2$$

(1.4)

were  $d\Omega = 2\pi sin\theta d\theta$ , which is equivalent to

$$\frac{\mathrm{d}\,\sigma_R}{\mathrm{d}\,\theta} = \pi r_e^2 \sin\theta (1 + \cos^2\theta) \{F(x, Z)\}^2 \tag{1.5}$$

where F(x, Z) is an atomic form factor that depends on the momentum transfer  $x = \sin(\theta/2)/\lambda$ . The square of this component represents the probability that the Z electrons of the absorber atom acquire the photon momentum without absorbing its energy. The atomic form factor decreases from Z towards zero when the scattering angle  $\theta$  increases.

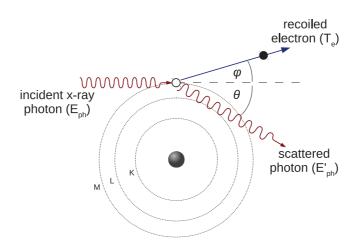

#### 1.1.2.2 Inelastic scattering

Inelastic scattering takes place when a change of direction is accompanied with a loss of energy by the incident photon. This process is also known as the incoherent or Compton scattering. When an X-ray photon collides with a weakly-bound electron of an atom, it losses part of its energy, which is absorbed by the electron being removed from its shell and becomes a free electron. The mechanism of the interaction is shown in figure 1.6. After scattering, the incident photon with an

FIGURE 1.6: Compton scattering.

initial energy  $E_{ph}$  has become a new photon with a lower energy  $E'_{ph}$  and with a direction altered by an angle  $\theta$ . The photon scattering angle can take values from 0° (forward scattering) to 180° (back scattering). The electron (recoiled or Compton electron) is ejected from its outer shell with a kinetic energy  $T_e$  at an angle  $\phi$  from the direction of the initial photon. Both, the scattered photon and the recoiled electron may have enough energy to cause further ionization in the target material.

From the relativistic relationships of the energy and momentum conservation, the energy of the scattered photon  $(E'_{ph})$  as a function of the photon scattering angle  $\theta$  is expressed by the following formula

$$E'_{ph} = E_{ph} \frac{1}{1 + \alpha(1 - \cos\theta)} \tag{1.6}$$

where

$$\alpha = \frac{E_{ph}}{m_e c^2} = \frac{E_{ph}}{511 \text{ keV}} \tag{1.7}$$

represents the incident photon energy normalized to the rest mass energy of the electron  $m_e c^2$ . In case of forward scattering, the energy of the photon remains the same  $(E_{ph} = E'_{ph})$ .

The kinetic energy of the recoil electron is given by the difference between the energies of the incident and scattered photons

$$T_e = E_{ph} - E'_{ph} = E_{ph} \frac{\alpha (1 - \cos \theta)}{1 + \alpha (1 - \cos \theta)}$$

$$\tag{1.8}$$

For a given incident photon energy, the maximum energy transferred to the Compton electron is when the photon is backscattered ( $\theta = 180^{\circ}$  and  $\phi = 0^{\circ}$ ).

The electronic cross section of Compton Scattering ( $_e\sigma_C$ ) on a quasi-free electron was first derived in 1929 by Oscar Klein and Yoshio Nishina [61] and is expressed by the following formula [74]

$${}_{e}\sigma_{C} = 2\pi r_{e}^{2} \left\{ \frac{1+\alpha}{\alpha^{2}} \left[ \frac{2(1+\alpha)}{1+2\alpha} - \frac{\ln(1+2\alpha)}{\alpha} \right] + \frac{\ln(1+2\alpha)}{2\alpha} - \frac{1+3\alpha}{(1+2\alpha)^{2}} \right\}$$

(1.9)

where  $r_e$  is the classical electron radius  $(2.82 \times 10^{-15}m)$  and  $\alpha$  is the normalized photon energy as in equation 1.7. The  $_e\sigma_C$  is independent of the atomic number Z of the absorber, since it is a reaction with a quasi-free electron. Therefore, its binding energy can be neglected. The atomic cross section of Compton scattering

$(a\sigma_C)$  is proportional to the atomic number of the absorber Z

$$_{a}\sigma_{C} = Z_{e}\sigma_{C} \tag{1.10}$$

#### 1.1.3 X-ray attenuation and filtration

Attenuation is the reduction in the intensity of an X-ray beam resulting from the absorption or the scattering of the X-ray photons after travelling through matter. The intensity of an attenuated monochromatic beam of energy E is given by the equation

$$N = N_0 e^{-\mu(\delta, E, Z)x} \tag{1.11}$$

where  $N_0$  is the intensity of the incident beam,  $\mu$  is the linear attenuation coefficient for a material with an atomic number Z and x is the thickness of the material. N represents the number of photons that have passed through the material without interacting. With high energy X-rays and thin, low Z absorbers, no interactions are often the most probable case. The linear attenuation coefficient is expressed in inverse length units  $(cm^{-1})$  and is dependent on the density of the absorber  $\delta$ . Therefore, more often a mass attenuation coefficient  $\mu_m = \mu/\delta$  is used, since it is independent from the density. It is expressed in units of  $cm^2/g$ . The mass attenuation coefficient is related to the probability of the interaction per mass unit. Therefore it can be expressed as a cross section using following relationship

$$\mu_m = \sigma \frac{N_A}{A} \tag{1.12}$$

where  $N_A$  is Avogadro's number  $(6.022 \times 10^{23} atom/mol)$  and A is atomic mass. The total mass attenuation coefficient  $\mu_{m,total}$  is the sum of the attenuation coefficients for all the different types of photon interactions:

$$\mu_{m,total} = \mu_{m,ph} + \mu_{m,C} + \mu_{m,R}$$

$$= (\sigma_{ph} + \sigma_C + \sigma_R) \frac{N_A}{A}$$

(1.13)

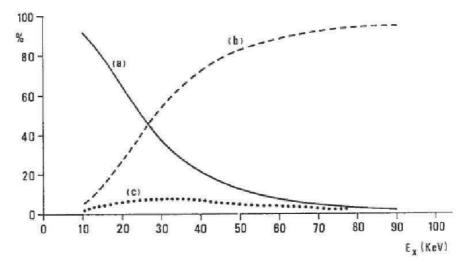

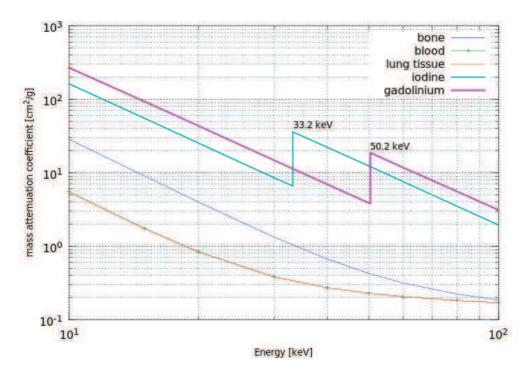

where  $\mu_{m,ph}$ ,  $\mu_{m,C}$ ,  $\mu_{m,R}$  are the mass attenuation coefficients for the photoelectric effect, the Compton and the Rayleigh scatterings, and  $\sigma_{ph}$ ,  $\sigma_{C}$  and  $\sigma_{R}$  are the corresponding cross sections. In figure 1.7, the relative percentages of photon interactions with water are shown as a function of the photon energy. It can be seen that in the lower energy range, the photoelectric effect is dominant, whereas

Figure 1.7: Relative percentages of photon interactions with water as a function of energy for three different processes: a) photoelectric effect, b) Compton scattering and c) Rayleigh scattering (from [15]).

in the higher energy range, Compton scattering contributes to most of the attenuation. The Rayleigh scattering is an elastic interaction and does not contribute significantly to the total attenuation whatever the energy of the photon.

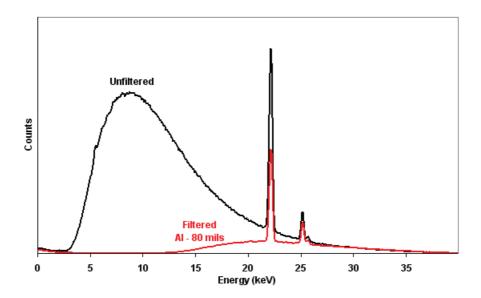

The spectrum of X-rays generated from an X-ray tube comprises soft X-rays that are ineffective in terms of imaging for the purpose of medical radiography, but are nonetheless absorbed by the imaged object and thus contribute to the total radiation dose absorbed by the patient. Therefore soft X-rays are selectively removed from the spectrum by using a sheet of metal placed between the X-ray source and

FIGURE 1.8: X-ray spectra with (red) and without (black) 2 mm aluminium filtering.

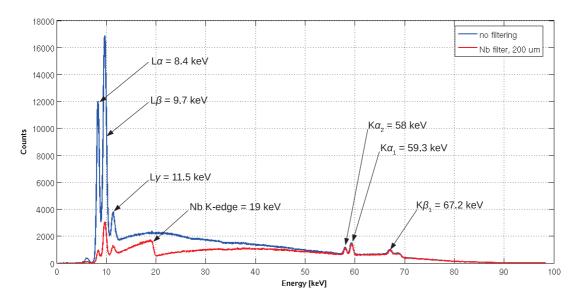

the object. This piece of additional material attenuates the X-ray beam predominantly within this useless part of the spectrum. Most often, aluminium (Al with Z=13) or glass ( $SiO_2$  with Z=14) filters are used, which attenuate almost all X-rays with energies below 15 keV. In figure 1.8, spectra of the beam are shown before and after filtration with 2 mm of aluminium. It can be seen that most of the low energetic photons have been cut off from the original spectrum.

#### 1.1.4 Radiation damage

Effects caused by the X-ray radiation have a cumulative nature and are related to the energy deposited in the absorber during irradiation, which may lead to malfunctioning of electronics devices or damages in biological tissues. Two radiation dose figures are used to measure the magnitude of radiation exposure, equivalent dose for biological tissues and absorbed dose for other media. The absorbed dose is defined by the amount of the energy deposited in the media per absorber unit mass and is expressed in SI units in Gray (Gy)

$$1 Gy = \frac{1 J}{1 kq} \tag{1.14}$$

The equivalent dose depends on the deposited energy, but also on the nature of the particle that looses its energy in the traversed distance. It is defined by a quality factor Q. Hence, equivalent dose is the product of absorbed dose multiplied by the factor Q, and is expressed in SI unit in  $Sievert\ (Sv)$ . In case of X-rays the quality factor Q is equal to 1.

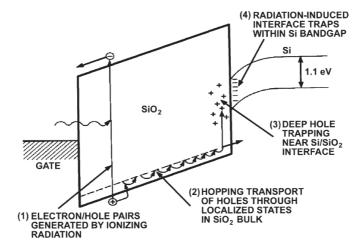

The main effects caused by X-rays in electronics devices are due to energy deposition in the insulator region (silicon dioxide,  $SiO_2$ ) of the transistors, which leads to a degradation of the performance or damages of the device. As a result of the ionization caused by an incident particle, e-h pairs are created in the  $SiO_2$  region. Parts of the pairs do not recombine after interaction and start to drift under the presence of an electric field, as shown in figure 1.9. This leads to two parasitic effects: i) hole trapping in the insulator causing charge buildup in the region and ii) rise of the defects in the interface region between silicon and silicon dioxide,  $Si - SiO_2$ . The defects in the interface regions are traps in the boundary region between different materials where charge may get blocked, thus changing the energy distribution in the region, i.e. introduces new energy levels in the band gap in the  $Si - SiO_2$  region. Numerous traps are created during the fabrication process and ionization activates them or induces new ones. These two effects,

FIGURE 1.9: Schematic drawing of the effects caused by ionizing radiation in MOS devices (from [65]).

charge buildup in the silicon dioxide and interface defects, modify the threshold voltage of the transistor that causes failures or at least malfunction of the device. In addition to this, the first effect (holes trapping in the insulator) may lead to the creation of parasitic channels in NMOS transistors, thus resulting in a rise of the leakage current in the device. Holes trapped in the dioxide region can be released by increasing the temperature, which increases its mobility (this process is called annealing).

### 1.2 Imaging techniques with X-rays

Almost since they were discovered, X-rays were found to be useful as a messenger reporting on the internal structure of solid object. The two main applications of X-ray imaging are radiography, spectroscopy and crystallography.

Radiography is a transmission based technique with which X-ray photons pass through the investigated object and are detected by the detector. The resulting image reflects the intensity of the beam after passing through the studied object. This projection carries information on the total mass attenuation of the object along the direction of the rays. This technique is nowadays a primary method used in medical imaging diagnostic as well as in industrial applications (e.g. homeland security, product inspection).

X-ray spectroscopy is based on the measurement of the absorption cross-section in the region of absorption edges. This technique allows to study structures and

properties of various materials (e.q. liquids, crystals, doped materials for electronics). Crystallography is a technique that allows to reconstruct the arrangement of the atoms in a crystal by striking it with an X-ray beam and analysing the pattern created by the scattered photons.

In this chapter, selected techniques that are interesting from the perspective of the use of the XPAD3 X-ray camera will be presented in more details.

#### 1.2.1 Radiography

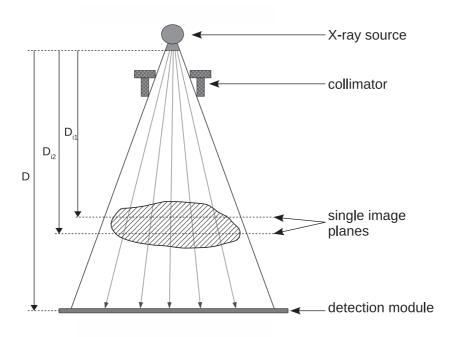

The two principal techniques of X-ray radiological imaging are radiography and computed tomography. The images produced by conventional radiography result from a 2D conical projection of a 3D object, as depicted in figure 1.10. This projection image is sometimes difficult to interpret. Computed tomography (CT) is using many of the projections regularly sampled all around the object to reconstruct slices through the object.

FIGURE 1.10: Principle of planar X-ray radiography.

#### 1.2.1.1 Computed tomography

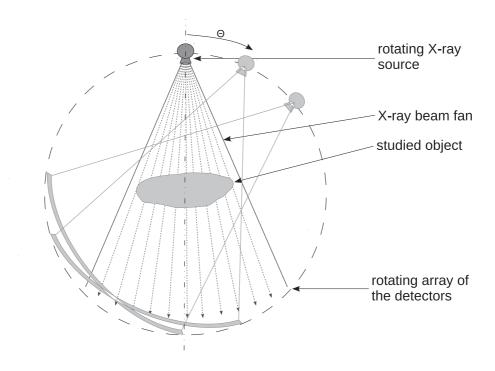

X-ray CT was invented by Godfrey N. Hounsfield, and the first CT scanner was built by him in 1972 at EMI Central Research Laboratories (*Electric and Musical*

Industries Ltd.). Later on, in 1979, he was awarded the Nobel Prize in Medicine jointly with Allen M. Cormack for the development of computer assisted tomography. Computed tomography is based on the acquisition of multiple 1D fan beam or 2D cone beam projections of thin slices of the object at different angles all around the object. In most common CT scanners, the X-ray source (X-ray tube) and the detector rotates around an object as depicted in figure 1.11. The reconstruction of CT slices makes it possible to visualize the object in different planes (e.g. axial, coronal or sagittal). However, a crucial limitation of CT scanning was the data collection time directly impacting the radiation dose absorbed by the patient. In order to reduce it and eventually the radiation dose, different architectures of scanners were studied and developed. Some of them are multi-slice scanners (to record a few slices at a time thanks to a small axial opening of the fan beam), spiral scanners (in which the object is linearly transported through the beam while the X-ray tube and the detector array are continuously rotated around the object) or scanners with multiple X-ray sources and a complete detector ring (to achieve simultaneous scans from different angles and/or at different energies).

FIGURE 1.11: Slice view of the CT scanner.

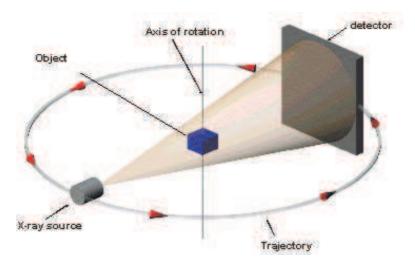

One progress in CT imaging that is of particular interest for the work presented in this thesis is cone beam CT (CB-CT). In opposition to standard scanners, CB-CT uses a cone shaped X-ray beam with full opening as depicted in figure 1.12, which allows to scan the full volume of interest at once. The main technological

FIGURE 1.12: Schematic view of a CT scanner with cone shaped X-ray beam.

challenges in CB-CT are the big surface of the X-ray detector together with the very fast data readout. Since an image of a single projection is created at once, there is a huge amount of data emerging from the detector for each projection that has to be transferred to the computer as fast as possible in order to perform a full scan in a minimum time.

#### 1.2.2 Crystallography

In crystallography, X-ray radiation is used to reconstruct the internal structure of a crystal. In opposition to radiography, elastic interaction between X-ray photons and molecules allows to detect the arrangement of atoms in a crystal lattice. The measurement of diffraction angle on the crystal sample provides information about the spacing of atomic planes in the crystal.

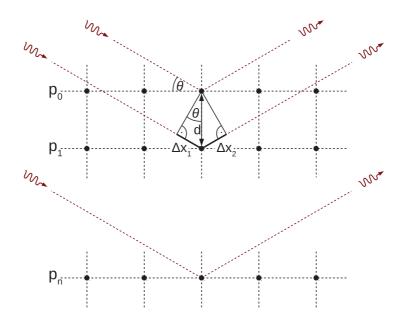

The diffraction of a monochromatic X-ray beam on the crystal atomic planes oriented at an angle  $\theta$  respective to the beam is illustrated in figure 1.13. X-rays diffracted on the plane  $p_0$  travel a distance which is shorter than those diffracted on the consecutive planes  $(p_1 \dots p_n)$ . The difference in this distance between two consecutive planes is expressed by

$$\Delta x = \Delta x_1 + \Delta x_2 = 2d \sin\theta \tag{1.15}$$

If this distance  $\Delta x$  is a multiple of the incident beam wavelength, then a constructive interference of the diffracted waves occurs. In other cases, diffracted waves interfere with different phases and a destructive interference takes place. This

Figure 1.13: X-rays diffracted on a crystal lattice.

effect is known as the Bragg's law for X-ray diffraction

$$n\lambda = 2d \sin\theta \tag{1.16}$$

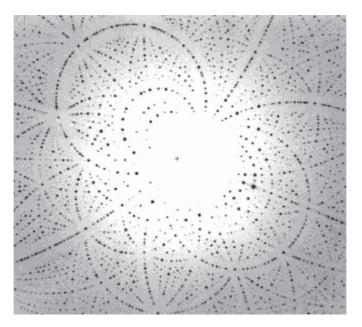

where d is the distance between the planes,  $\lambda$  is the wavelength of the X-rays and  $\theta$  is the angle of diffraction. By changing the orientation of the crystal sample, it is possible to expose another diffraction plane of the crystal and hence to reconstruct finally the three-dimensional structure of the sample. Characteristic diffraction patterns comprise discrete spots ( $Laue\ spots$ ) of high intensities created by coherent interference of X-rays diffracted on parallel planes. The only condition is that the distance between two planes has to be greater than half of the X-ray wavelength (for  $d < \lambda/2 \Rightarrow sin\theta > 1$ ). An example of X-ray diffraction on a protein sample is shown in figure 1.14.

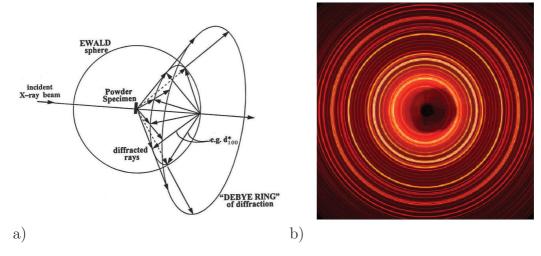

#### 1.2.2.1 Powder diffraction

By using a polycrystalline powder instead of a single crystal, the randomly organized small crystals of the powder provide every possible atomic plane orientation that fulfil the Bragg's condition. Each group of reflecting planes diffracts X-rays with the same angle, thus giving rise to a number of diffraction cones (Debye cones) as depicted in figure 1.15a. The resulting pattern is composed of diffraction rings

FIGURE 1.14: Laue spots as a result of X-ray diffraction on a protein sample (from [3]).

centred on the beam axis, each of them being composed of indistinguishable Laue spots that form a continuous line (figure 1.15b).

FIGURE 1.15: (a) View of the Debye cone resulting from X-ray diffraction diffraction on a polycrystalline sample and (b) the resulting diffraction pattern (from [49],[99]).

# Chapter 2

# Semiconductor pixel detectors

Position sensitive detector provide an information on the impact position of a particle. They have been intensively developed in the last decades and can be found presently in many applications related to radiation detection. Pixel detectors can offer high spatial resolution and thus are widely used in medical application, crystallography and tracking vertex detectors in High Energy Physics (HEP).

In the semiconductor radiation detectors, signal arises from a charge generated by an incoming particle. The collected charge is further processed by the frond-end electronics. The read-out electronics may be either a separated chip connected to the detector (strip or pixel hybrid detector), or it may be integrated on the same substrate as the detector (e.g. monolithic pixel detectors or charge coupled devices).

### 2.1 Principle of operation

### 2.1.1 Semiconductors physics

To understand the, principle of semiconductor detectors a primary knowledge on semiconductor physics is required. In this section, selected aspects necessary to comprehend operation of semiconductor pixel detectors will be discussed.

#### 2.1.1.1 Energy band model

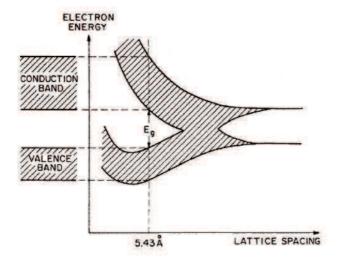

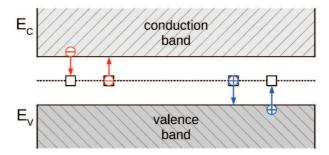

The electrical parameters of solid materials can be described using the energy band model. The band theory assumes that in a condensed materials, such as crystals, electrons can occupy energy levels grouped in bands. In a solid material composed of N closely spaced atoms, electrons of an adjacent atom are reciprocally influenced. The discrete energy levels of each individual atom do not remain, but become grouped in bands (formed by many closely spaced energy levels of single atoms). Allowed energy bands are separated by a  $forbidden\ band$ , which consists

FIGURE 2.1: Energy levels of silicon atoms as a function of lattice spacing (from [64]).

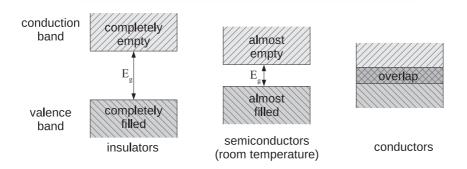

in energy levels that are not available for electrons. Energy levels as a function of lattice spacing for silicon are shown in figure 2.1. At large distances, atoms have the same energy levels. As lattice spacing decreases, these levels start to form energy bands. Within a given material, two distinct energy bands are important to determine its electrical properties. The highest completely filled energy band at a temperature of 0 K is called the valence band. The band placed above, partially filled or empty, is called the conduction band. In order to bring the material into a conduction state, electrons needs to move by changing their quantum state. Therefore this movement is possible only towards the unfilled conduction band. In figure 2.2, three types of materials depending on their electrical properties are presented. In the case of a wide forbidden gap, electrons from the valence band cannot acquire enough energy to jump to the conduction band in order to contribute to conduction. Such material is an insulator. In the case of a conductor, the valence and conduction bands overlaps, or the conduction band is partially filled. In both cases, many vacant states are available for electrons. The third group

FIGURE 2.2: Different types of materials depending on the energy band structure ( $E_g$  - forbidden gap).

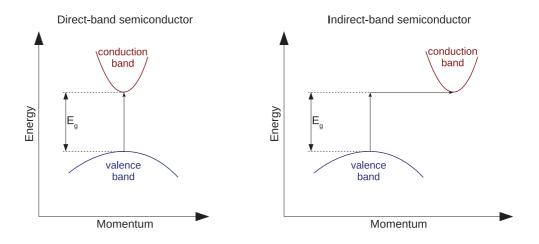

of materials in figure 2.2, the semiconductors, have a relatively small forbidden gap with an empty conductive band and a filled valence band at low temperature. However, thermal excitation at room temperature is sufficient to transfer a few electrons to the conduction band, thus leading to a weak conductivity. Two types of semiconductors depending on their band gap structure are recognized. These are the *direct-band* and the *indirect-band* semiconductors. When an electron, due to excitation, is promoted from the valence to the conduction band, one needs to care about momentum conservation. In the case of a direct-band semiconductor,

FIGURE 2.3: Direct-band and indirect-band types of semiconductors.

the highest state of the valence band and the lowest state of the conduction band have the same momentum (figure 2.3). For indirect-band semiconductors, besides energy, an electron needs to change its momentum in order to pass trough the band gap. In most of the cases, this is done with phonon assistance.

#### 2.1.1.2 Intrinsic and extrinsic semiconductors

Intrinsic semiconductors contain a negligible concentration of impurities compared to thermally generated electrons and holes. Each electron, thermally elevated from the valence band to the conduction band, leaves a hole behind it. In an intrinsic semiconductor, the numbers of generated holes and electrons are approximately the same. The density of free electrons, n, and of holes, p is given by

$$n = N_C e^{-\frac{E_C - E_F}{kT}} (2.1)$$

$$p = N_V e^{-\frac{E_F - E_V}{kT}} (2.2)$$

where  $N_C$ ,  $N_V$  are the effective densities of energy states in the conduction and valence bands,  $E_C$  and  $E_V$  are the energy levels of the conduction and valence bands, k is the Boltzmann constant and T is the absolute temperature.  $E_F$  is the Fermi level, which corresponds to the energy at which the probability of occupation for an electronic state is one half. The product of electron and hole concentrations is given by

$$np = n_i^2 (2.3)$$

where  $n_i$  is the intrinsic carrier density. The relation 2.3 is called the *mass action law*. For intrinsic semiconductors, the Fermi level is derived from the assumption that the numbers of electrons and holes are equal  $n = p = n_i$  and expressed by

$$E_i = \frac{E_C + E_V}{2} + \frac{3kT}{4} ln\left(\frac{m_p}{m_n}\right)$$

(2.4)

where  $m_p$  and  $m_n$  are the effective masses of holes and electrons. The intrinsic Fermi level  $E_i$  is located in the middle of the forbidden gap, since the deviation due to the second term of the sum is only of the order of 0.01 eV.

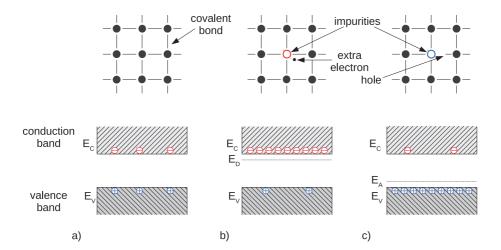

Intrinsic semiconductors are rather weak conductors, because this property depends strongly on the purity of the material and on its temperature. The improvement of the conductivity of a semiconductor is obtained by doping, which consists in adding small amounts of impurities to the material. Impurities replace crystal lattice atoms, thus introducing new energy levels in the forbidden gap of the material. Doped semiconductors are called *extrinsic*. The doping material is chosen in such a way that it has a different number of valence electrons than a semiconductor atom, thus adding new electrons or holes (figure 2.4). Dopants that bring extra electrons are called *donors* and those that bring extra holes *acceptors*. In case of donors, the introduced energy level is very close to the conduction

FIGURE 2.4: Crystal lattice bond structure (top) and energy band model (bottom) of (a) intrinsic, (b) n-type and (c) p-type semiconductors.

band. At room temperature, all donor states are ionized and all donor electrons are transported to the conduction band. Hence, the concentration of electrons, n, is equal to the concentration of donor atoms,  $N_D$ . Therefore, donor doped materials are called n-type semiconductors. Similar considerations can be made, for acceptor type dopants. In that case, an additional energy level is placed close to the valence band. In order to create a valence band with crystal atoms, acceptors will trap an electron from the valence band, thus leaving a hole behind them. The concentration of created holes, p, is equal to the concentration of acceptor atoms,  $N_A$ . Acceptor doped materials are called p-type semiconductors. In both cases, the intrinsic Fermi level is shifted towards the conduction or the valence bands for donors or acceptors, respectively. New energy levels are expressed by

$$E_{F} = \begin{cases} E_{i} + kT \ln \left(\frac{N_{D}}{n_{i}}\right), & \text{donor dopant} \\ E_{i} - kT \ln \left(\frac{N_{A}}{n_{i}}\right), & \text{acceptor dopant} \end{cases}$$

(2.5)

According to the *mass action law* (eq. 2.3), the increase of majority carriers (electrons in n-type materials and holes in p-type materials) is accompanied with a decrease of minority carriers.

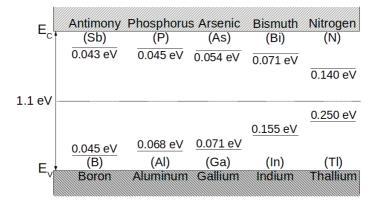

FIGURE 2.5: Change of the silicon band gap depending on the material used as a donor or an acceptor.

As an example, the band gap modulation of silicon with different types of dopant materials [64, 78] is shown in figure 2.5. Silicon have four valence electrons, hence acceptor materials from the boron group with three valence electrons are used, and materials from the nitrogen group with five valence electrons are used as a donors.

#### 2.1.1.3 Charge generation and recombination

There are two main mechanisms of charge generation in a semiconductor: thermal excitation and charge particle interaction. The energy needed to promote an electron from the valence to the conduction band strongly depends on the type of semiconductor and on its energy gap (table 2.1). Thermal generation is often a parasitic process that leads to a rise of *leakage current* in radiation detectors,

|                                     | Si        | CdTe           | Ge        | GaAs                |

|-------------------------------------|-----------|----------------|-----------|---------------------|

| Atomic Number Z                     | 14        | 48 (Cd)        | 32        | 31 (Ga)             |

|                                     |           | 52 (Te)        |           | 33 (As)             |

| Density $[g/cm^3]$                  | 2.33      | 6.2            | 5.32      | 5.32                |

| Energy gap $[eV]$                   | 1.12      | 1.4            | 0.66      | 1.424               |

| Energy/e-h pair $[eV]$              | 3.62      | 4.4            | 2.9       | 4.2                 |

| Intrinsic resistivity $[\Omega cm]$ | 320000    | $\approx 10^9$ | 50        | $3.3 \times 10^{8}$ |

| Electron mobility $[cm^2/(Vs)]$     | 1450      | 1000           | 3900      | 8500                |

| Hole mobility $[cm^2/(Vs)]$         | 450       | 80             | 1900      | 400                 |

| Electron lifetime $[s]$             | $10^{-4}$ | $10^{-6}$      | $10^{-4}$ | $10^{-8}$           |

| Hole lifetime $[s]$                 | $10^{-4}$ | $10^{-6}$      | $10^{-4}$ | $10^{-8}$           |

Table 2.1: Properties of different semiconductors at a temperature of 300 K (from [64],[83]).

and hence to signal degradation. Thus, for several materials with a small energy gap, such as germanium (Ge), it is necessary to operate them at low temperatures in order to decrease the influence of leakage current. In radiation detectors, the signal comes from the ionization by the impinging particle. Depending on the type of radiation, the shape of ionization paths are different, involving sometimes secondary processes. In case of X-rays, many electron-hole pairs are generated in a small spatial region around the interaction point. The number of electron-hole pairs, N, may be estimated from the energy needed to generate one electron-hole pair given by  $N = E_{xray}/E_{e-h}$ .

The thermal generation rate is independent from the concentration of donors and acceptors and is given by  $G_{th} = n_i/\tau_g$ , where  $\tau_g$  is the generation lifetime. Under a thermal equilibrium, a continuous balance between generation and recombination of electron-hole pairs occurs,  $G_{th} = R_{th}$ , according to the mass action law (equation 2.3). Depending on the type of semiconductor, the thermal recombination rate is limited by the concentration of minority charge carriers, i.e.  $R_{th} = p/\tau_{rn}$ for n-type semiconductors and  $R_{th} = n/\tau_{rp}$  for p-type semiconductors. Factors  $\tau_{rn}$ and  $\tau_{rp}$  are recombination lifetimes in n- and p-type semiconductors. The excess of carriers created by radiation or injection disturbs this equilibrium. When the external stimulus is stopped, an equilibrium state will be eventually reached by the process of recombination regulated by the lifetime of excess minority carriers  $\tau_r$ . On the other hand, if all charge carriers are removed from the semiconductor (e.g. by applying an external voltage), thermal generation will be the dominating process while the recombination rate will be very low. The equilibrium state will be reached again with a time constant determined by the generation lifetime  $\tau_g$ . The above explanation is valid for direct semiconductors. In case of indirect materials, processes of generation and recombination are significantly different. The probability of direct band-to-band recombination in indirect semiconductors

FIGURE 2.6: Mechanisms of generation and recombination trough energy states in the forbidden gap.

is very small due to different crystal momentum between electrons of the conduction band and holes of the valence band (see figure 2.3). Recombination occurs as a step process that involves emission/capture of electrons/holes into intermediate energy states in the forbidden gap called *generation/recombination* centers. Generation/recombination centers consist of semiconductor defects or impurities. Mechanism of charge carrier trapping and emission are shown in figure 2.6.

### 2.1.1.4 Charge carriers transport

Motion of free charge carriers occurs through scattering on crystal lattices and impurities. This results in random direction movements. Hence, there are no net displacements at thermal equilibrium. In that case, we are dealing with a thermal motion defined by the mean free time between collisions  $\tau_c$ , and by the velocity acquired between collisions  $v_{th}$ . The characteristic length of thermal motion is  $l_{th} = v_{th}\tau_c$ . Typically, at room temperature (300 K),  $\tau_c \approx 10^{-13} - 10^{-12}$  s,  $v_{th} \approx 10^7$  cm/s and  $l_{th} \approx 100$  Å.

An electric field, E, applied to the semiconductor causes acceleration of the carriers in the direction defined by the electric field. The motion of charge carriers caused by the electric field is called *drift current*. During a mean free time,  $\tau_c$ , carriers gain a velocity defined by

$$v_{drift} = \begin{cases} -\frac{qE}{m_n} \tau_c = -\mu_n E, & \text{for electrons} \\ \frac{qE}{m_p} \tau_c = \mu_p E, & \text{for holes} \end{cases}$$

(2.6)

where  $\mu_n$  and  $\mu_p$  are the mobility of electrons and holes. An increase of the electric field induces a saturation of the carriers velocity. These parameters strongly depend on the temperature and doping concentration. Carriers mobility for different materials are collected in table 2.1. The drift current density is given as follows

$$J_{drift} = \begin{cases} -qnv_{drift,n} = -qn\mu_n E, & \text{for electrons} \\ qpv_{drift,p} = qp\mu_p E, & \text{for holes} \end{cases}$$

(2.7)

The diffusion current arises in the presence of an inhomogeneous gradient distribution of free charge carriers. The diffusion current has a direction opposite to the concentration gradient, since the carriers move predominantly from the region of higher concentration towards the region of lower concentration. The diffusion currents for the two types of carriers are given by

$$J_{diff} = \begin{cases} qD_n \nabla n, & \text{for electrons} \\ -qD_p \nabla p, & \text{for holes} \end{cases}$$

(2.8)

where  $D_n$  and  $D_p$  are the diffusion coefficients for electrons and holes. Diffusion coefficient and mobility are related trough the *Einstein relationship*

$$\frac{D_n}{\mu_n} = \frac{D_p}{\mu_p} = \frac{kT}{q} \tag{2.9}$$

where the fraction kT/q is known as the thermal voltage and is equal to 25 mV at 300 K .

The total current for one type of carriers is the sum of the diffusion and drift currents:

$$J_n = J_{drift,n} + J_{diff,n} = qn\mu_n E + qD_n \nabla n$$

$$J_p = J_{drift,p} + J_{diff,p} = qp\mu_p E - qD_p \nabla p$$

(2.10)

and the total current in the semiconductor is given by

$$J_{total} = J_n + J_p (2.11)$$

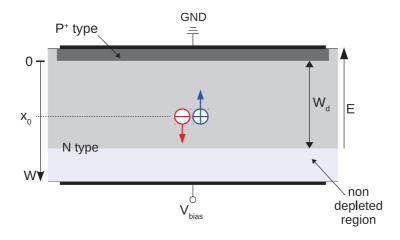

# 2.1.2 Charge collection

The charge in a semiconductor detector originates from direct ionization caused by a traversing particle. The electron-hole pairs created during this process are separated by the presence of an electric field across the active volume. In order to limit the leakage current in the device, different sensor structures are implemented depending on the material. For low band gap materials, like silicon, a junction is required in order to limit leakage current at room temperature. A commonly used structure for this type of semiconductor is the reversed biased p-n junction with a depleted region acting as an active volume for signal detection. For other materials with inherent high resistivities, e.g. diamond, a simple ohmic contact is sufficient.

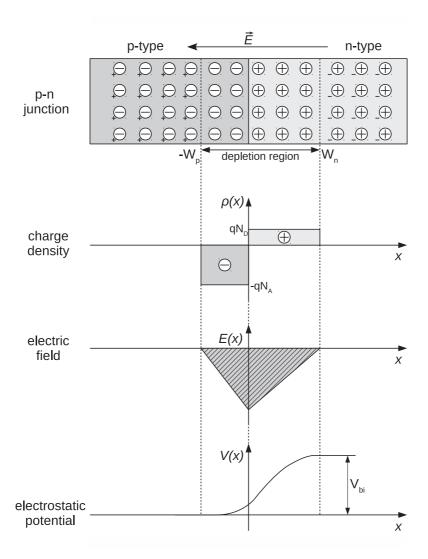

The p-n junction is formed when two adjacent regions of semiconductors are differently doped forming n- and p-type materials in one piece of material. Majority carriers from one side diffuse towards the other side (i.e. holes from the p-side towards the n-side and electrons from the n-side towards the p-side). Diffused charge carriers combine with dopant ions (i.e. extra electrons with acceptor holes

FIGURE 2.7: Electric characteristic functions of a typical abrupt p-n junction.

and extra holes with dopant electrons), which results in a space charge across the junction (positive in the n-side and negative in the p-side). These space charge prevent electron-hole pairs from recombination. In spite, they drift along the field lines. As a result, the region around the junction becomes free of mobile carriers and is called the *depleted region*. The potential difference across the depletion zone is called the *built-in potential* or the *junction potential*. The built-in potential,  $V_{bi}$ , is equal to the difference of the Fermi potential levels for p- and n-type materials (equation 2.5) and is given by

$$V_{bi} = \frac{kT}{q} ln \left( \frac{N_D N_A}{n_i^2} \right) \tag{2.12}$$

At thermal equilibrium, the total negative charge in the n-type side is equal (in

absolute value) to the total positive charge in the p-type side of the depletion region,  $N_A W_p = N_D W_n$ , thus conserving the electrical neutrality of the device. In figure 2.7, the characteristic functions of an abrupt p-n junction are plotted. The width of the depleted region<sup>1</sup> at thermal equilibrium is given by

$$W = \sqrt{\frac{2\epsilon_s \epsilon_0}{q} \frac{N_A + N_D}{N_A N_D} V_{bi}}$$

(2.13)

In a typical detector diode, one side of the junction has a doping concentration a few orders of magnitude higher than the other, usually  $N_A \gg N_D$ . Therefore, the depletion region extends mainly into one side of the junction. The width of the depleted region can be now expressed by

$$W = \sqrt{\frac{2\epsilon_s \epsilon_0}{q} \frac{1}{N_D} V_{bi}} \tag{2.14}$$

The width of the depletion region can also be increased by applying an external voltage with the same polarity as the built-in potential. It increases proportionally to the square root of the applied voltage. The above equations (2.13 and 2.14) can be used to calculate the external voltage required to deplete completely a semiconductor of given thickness and doping concentrations.

A metal-semiconductor contact is created when a semiconductor is joined together with a metal layer. Its structure can be characterized by using the energy band model as it was done for p-n junctions. In order to induce the diffusion of the electron from the semiconductor to the metal, the Fermi energy level of the metal and the semiconductor has to be lined up, so that a voltage across the junction is created, which is equal to the difference between the potential functions<sup>2</sup> of the materials

$$V_{bi} = \Phi_{met} - \Phi_{sem} \tag{2.15}$$

The region around the junction on the semiconductor side becomes depleted from the electrons building up a positive space charge in the vicinity of the junction. In order to establish an equilibrium state, positive charges are compensated by a surface charge at the metal side. The height of the created barrier, called *the*

<sup>&</sup>lt;sup>1</sup>Obtained by solving the Poisson's equation for the electric potential  $(\frac{d^2V}{dx^2} = \frac{\rho_s}{\epsilon_s \epsilon_0})$ , where  $\epsilon_s$  and  $\epsilon_0$  are the relative dielectric constant for the semiconductor and the permittivity of vacuum), with the assumption of an abrupt change of dopant concentrations

$<sup>^2\</sup>Phi$  is the energy needed to move an electron from a solid (Fermi level) to the vacuum state. In order to obtain a rectyfing metal-semiconductor contact, the condition  $\Phi_{met} > \Phi_{sem}$  has to be fulfilled

Schottky barrier, is given by:

$$q\Phi_{Bn} = q(\Phi_{met} - \chi) \tag{2.16}$$

where  $q\chi$  is the electron affinity<sup>3</sup> of the semiconductor. The width of the depletion region can be modulated by applying an external potential and is expressed with the same equation as for p-n junctions (eq. 2.14).

In order to estimate the time needed to collect the charge created by an impinging particle, a parallel plate detector with a reversely biased silicon p-n junction will be considered (figure 2.8). In a partially depleted detector ( $V_{bias} \leq V_{depl}$ ), the

FIGURE 2.8: Charge collection with a partially depleted p-n junction.

electric field inside the bulk is expressed as a function of the depth x

$$E(x) = \begin{cases} \frac{2(V_{bias} + V_{bi})}{W_d} \left(1 - \frac{x}{W_d}\right), & \text{for } x \le W_d \\ 0, & \text{for } x > W_d \end{cases}$$

(2.17)

The time needed for charge carriers created at a given point  $x_0$  to reach the point x is given by

$$t(x) = \tau_c \ln\left(\frac{W - x}{W - x_0}\right), \quad \tau_c = \frac{\epsilon_{Si}}{\mu q N_D}$$

(2.18)

where  $\tau_c$  is the collection time constant, which is independent of the applied voltage, but relates to the doping concentration and carriers mobility. Therefore, the

$<sup>^{3}</sup>$ The affinity is the energy needed to move an electron from the bottom of the conduction band to the vacuum state.

time required for carriers to reach the detector electrodes is expressed by

$$t = \tau_c \ln\left(\frac{W}{W - x_0}\right) \tag{2.19}$$

However, when the depletion region does not extend over the full width of the detector, the velocity of the electrons which are drifting towards the low field region will drop to zero around the boundary of the depletion zone. Most of the charges will be collected through diffusion. Some others may recombine in the non depleted region. Therefore, the charge collection time for a partially depleted detector is mainly determined by the diffusion across the non depleted region. Although, it should be said that the charge carriers generated in the non depleted region may not contribute to the total signal. In case they cannot reach the depletion region, they are lost due to recombination processes.

The charge collection time is reduced significantly when the detector is operating with a bias voltage exceeding the depletion voltage ( $V_{bias} > V_{depl}$ ). In that case, a uniform electric field is added to the electric field distribution (eq. 2.17)

$$E(x) = \frac{2(V_{depl} + V_{bi})}{W} \left(1 - \frac{x}{W}\right) + \frac{V_{bias} - V_{depl} - V_{bi}}{W}$$

$$E(x) = E_0 \left(1 - \frac{x}{W}\right) + E_1$$

(2.20)

The time needed for charge carriers created at a given point  $x_0$  to reach the point x is then given by

$$t(x) = \frac{W}{\mu E_0} \ln \left( \frac{E_0 + E_1 - E_0 \frac{x}{W}}{E_0 + E_1 - E_0 \frac{x_0}{W}} \right)$$

(2.21)

Hence the individual collection times for holes and electrons traversing the whole detector thickness are given by

$$t_{c,p} = \frac{W}{\mu_p E_0} \ln\left(1 + \frac{E_0}{E_1}\right)$$

$$t_{c,n} = \frac{W}{\mu_p E_0} \ln\left(1 + \frac{E_0}{E_1}\right)$$

(2.22)

For example, a silicon detector of 300  $\mu m$  thickness and 10  $k\Omega$  typical resistivity biased with 60 V have collection times of  $\sim$  10 ns and  $\sim$  35 ns for electrons and holes, respectively.

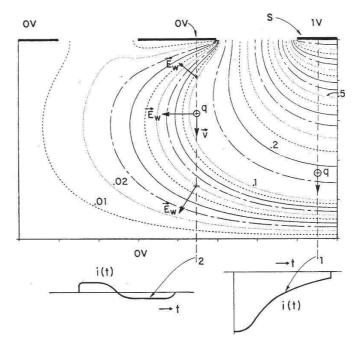

## 2.1.3 Signal formation

The signal current is generated on the collecting electrodes by the movement of the generated charges in the active volume of the detector. The electric charge induced on the given electrode can be calculated using the Ramo's theorem [76], which states that the amount of electric charge generated on the electrode is determined by the position of the drifting charges and the weighting potential,  $\phi_w(x)$ , of the electrode at this position. For a charge q drifting from the point  $x_1$ to the point  $x_2$ , the electric charge induced on the electrode is given by

$$Q = q \left[ \phi_w(x_2) - \phi_w(x_1) \right] \tag{2.23}$$

The instantaneous current induced on the collecting electrode due to the charge motion is expressed by

$$i = E_w qv (2.24)$$

where v is the instantaneous velocity of the electron and  $E_w$  is the weighting field of the given electrode. This is obtained by applying an unit potential to the electrode under consideration and by grounding all the others. The distribution of signal weighting potential depends on the geometry of the detector electrodes and is different than the electric field distribution (except for detectors with only two electrodes or pad detectors with electrodes significantly bigger than the thickness of the detector). In the case of a pixel detector, the weighting potential is highly concentrated in the region of the signal electrode. Thus, most of the current is generated while the moving charges get close to or directly on the signal electrode. Otherwise, if the charges will not end on the measurement electrode, the signal current induced on this electrode will be canceled. The induced electric charge, which is due to the motion of both types of charge carriers, electrons and holes, towards the opposite electrodes, has a net effect on the positive current of the negative electrode and on the negative current of the positive electrode. When a charge is not collected on the measurement electrode, it then induces a current on this electrode that will change the sign of the measured current and sets its integral to zero (figure 2.9).

FIGURE 2.9: Plot of the weighting field in a segmented detector (from [75]).

### 2.1.4 Noise in semiconductor detectors

Noise optimization in a semiconductor detector is required in order to improve SNR (Signal-to-Noise Ratio) and consequently energy resolution of the detector. Detector noise and electronics noise cannot easily be treated separately. However, the ultimate achievable noise performance is limited by two physical phenomenons in the sensor itself, independently of the following electronics.

The first one is the variance of the number of charges produced by an incoming particle. As already stated, this number of charges is related to the impinging particle energy by

$$N = \frac{E}{E_{eh}} \tag{2.25}$$

If this energy transfer follows a Poisson law, the variance of N would simply be V(N) = N. Hopefully, this is not true and V(N) = FN, where F is the Fano factor, F = 0.2 in case of semiconductors. This means that, even with a perfect chain (detector and electronics), an incoming energy E will produce a gaussian shaped peak of variance

$$\sigma^2 = FN = F \frac{E}{E_{eh}} \tag{2.26}$$

As an example, the standard deviation of Gaussian peak produced by an incoming energy of 25 keV will be of  $\sim 37~e^-$ , corresponding to a FWHM<sup>4</sup> of 370 eV.

<sup>&</sup>lt;sup>4</sup>Full Width at Half Maximum

The second physical phenomenon limiting noise performance is related to the variance of the number of charges created by thermal generation in the sensor. This generation follows also a Poisson law and its variance is  $V(N_{th}) = N_{th}$ . In the case of a reverse bias diode, this is usually expressed in terms of a reverse current,  $I_r$ . Suppose that we integrate the signal from the sensor during a time period  $\tau$ , we will then integrate also the reverse current during the same time period and therefore, the integrated charge due to this current will be  $I_r\tau$ . The variance of this charge is also  $I_r\tau$  and, as before, this leads to a Gauss distribution of  $\sigma^2 = I_r\tau$ . This means that for slow systems (large  $\tau$ ), the reverse current is an crucial issue.

# 2.2 Semiconductor pixel detectors

In this section, selected architectures of pixel detectors for X-ray imaging in life sciences and for experiments in synchrotron radiation experiments will be discussed.

# 2.2.1 Charge Coupled Devices (CCD)

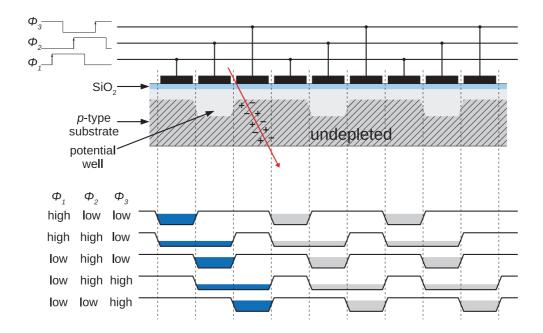

The Charge Coupled Device (CCD) is a matrix of Metal-Oxide-Semiconductor capacitors (MOS), each of them representing one pixel. The working principle of CCD is the displacement of charges collected in potential wells within the space charge region. A cross section of the device is shown in figure 2.10. The potential pockets where the charges generated by the radiation are collected, are created by operating the device in over-depletion mode and applying different potentials to adjacent gates of the capacitors. This creates a potential barrier under the neighboring gates that confines the charges collected in the region under the gate with the highest potential. Since all capacitors in one column have a common gate, the charges in one pixel are isolated against spreading in the direction of the gate by implanting channel stoppers (p strips implantations). In order to move charges in the shift-register manner, every third gate is kept on the same potentials  $\Phi_1$ ,  $\Phi_2$  and  $\Phi_3$ . Appropriate clocking of these voltages will cause the displacement of the charges along the row in one direction towards the readout anode as depicted in figure 2.10.

A big advantage of CCD devices is the very high granularity and the possibility to build large scale devices. In addition they do not have any dead zones. However, the readout of this type of the detector is a relatively slow process, which becomes a real issue in the case of large surface detectors. Moreover, because charges need

FIGURE 2.10: Cross section of a three phase CCD with a charge transfer diagram. Sequential change of the voltages applied to gates  $\Phi_1$ ,  $\Phi_2$  and  $\Phi_3$  cause charge transfer from one cell to the other towards the readout anode located at the and of the row.

to be moved through a large number of elements, the transfer efficiency is a very important parameter of the CCD device. Another aspect is the weak radiation hardness, which affects the charge carriers lifetime and the charge trapping occurrences, and consequently results in a degradation of the charge transfer efficiency.

Different architectures of CCDs were studied in order to improve key parameters and to make them practical devices in various fields of use ([64],[102]). The buried-channel or two phase CCD was designed in order to improve the charge transfer efficiency and speed. Another example are pnCCDs with fully depleted silicon substrate and with enhanced sensitivity and fast readout for X-ray detection applications in astronomy, crystallography or medical imaging.

# 2.2.2 Monolithic pixel sensor

The architecture of a monolithic pixel detector assumes that the sensor is integrated in the same substrate with its readout electronics. Different approaches to developing these types of devices were studied and undertaken. They are mainly

driven by the needs for vertex tracking detectors for future colliders (e.g. International Linear Collider (ILC)). The most important (and most challenging) requirements for these detectors are the small size of pixels, the high rate data acquisition and the low material budget. In this section, Monolithic Active Pixel Sensors (MAPS) built in standard CMOS technology will be presented in more details. Indeed, these are the most advanced developments and are currently the only devices of this type that have the potential to build large area detectors. It should be noted, however, that there is ongoing research and development on different concepts of (semi-)monolithic pixel sensors (e.g. DEPFET<sup>5</sup> detectors [2]), although these cannot offer yet a small pixel pitch or large surface detector.

### 2.2.2.1 Monolithic Active Pixel Sensor (MAPS)

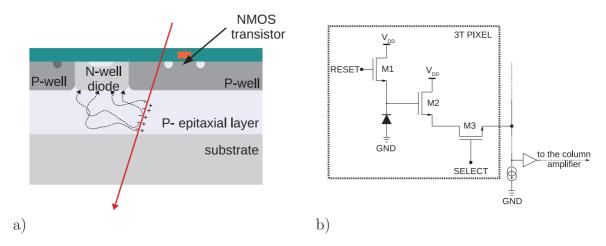

A cross-section of MAPS built in standard CMOS technology is shown in figure 2.11a.

Figure 2.11: Monolithic Active Pixel Sensor built in standard CMOS technology: (a) cross section and principle of operation, (b) basic pixel architecture based on three N-MOS transistors and a collecting diode (3T pixel).

The availability of slightly doped epitaxial silicon layer in CMOS process is essential for MAPS design. It is grown on top of a low resistivity silicon bulk. The active element in this design is a n-well/p-epi diode. Only the region under the n-well is depleted. Charges liberated by a traversing particle are kept in this thin epitaxial layer (usual of a few to 15  $\mu m$  thickness) by potentials of p-wells located at the border of the pixel and reach the region of the collection diode by thermal diffusion. Charge carriers generated in the substrate can contribute to the total

<sup>&</sup>lt;sup>5</sup>Depleted Field Effect Transistor

signal charge only if they were generated at the border of the epitaxial layer. A big difference of doping levels between the substrate and the epitaxial layer results in a decrease of charge lifetime, since charges recombine in the substrate before they can be collected. The charge signal is usually very small. Therefore, low noise electronics is a critical issue in this development. A typical three transistors based pixel architecture (reset (M1), source follower (M2) and row select (M3)) is presented in figure 2.11b. One of the advantages of this design is its high granularity (a pixel pitch  $< 15~\mu m$  is possible), due to a simple architecture of the single pixel and to the use of a commercial CMOS process. In addition to this, through thinning of the p-substrate and back-illumination, a 100% fill factor can be achieved.

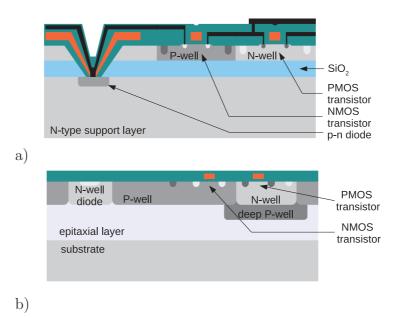

The main disadvantage of MAPS devices in standard CMOS technology is that the electronics read-out must consist only of NMOS transistors. In a twin-tube standard process, a P-MOS transistor has to be embedded in a n-well in order to get the positive bias. Since the n-well is used as a collecting diode, any other implantation of n-well would decrease the collected charge signal. Different attempts have been undertaken to overcome this limitation. One of them is to use a non-standard Silicon on Insulator (SOI) technology, with a buried oxide layer  $(SiO_2)$  used to isolate the fully depleted substrate from the electronically active

FIGURE 2.12: Different MAPS designs that allow use of both N- and P-MOS transistors in non-standard technologies: (a) in Silicon on Insulator (SOI) technology, (b) using INMAPS (Isolated N-well) process what allows deep p-well implants.

silicon on top of the insulator [57]. The charge collection is done by vias connecting the readout electronics with the substrate through the oxide. A schematic view of the device is shown in figure 2.12. Another approach is to use deep p-well implantation, which provides effective isolation (INMAPS process [5],[19]) of the n-well with P-MOS transistors (figure 2.12(b)).

## 2.2.3 Hybrid pixel detector

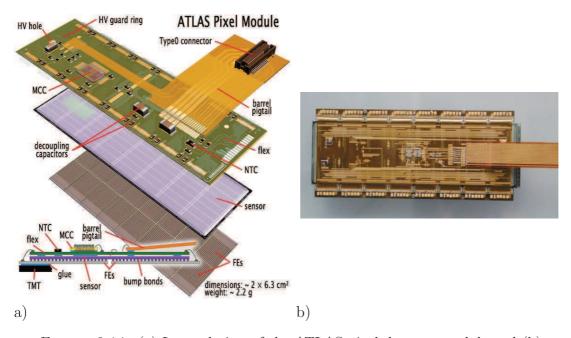

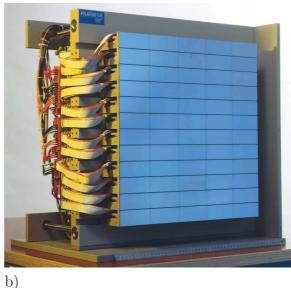

In the hybrid pixel detector architecture, the sensor and the electronics chips are fabricated on different substrates, thus ending with two separate chips. The development of this type of detector was initiated for vertex detectors for HEP experiments (e.g. LHC<sup>6</sup> experiments ATLAS<sup>7</sup>, ALICE<sup>8</sup>, CMS<sup>9</sup> and LHCb<sup>10</sup> at CERN). The needs for these experiments was to achieve high spatial resolution, high timing precision (event time stamps) and high radiation tolerance. Hybrid pixel detectors have successfully fulfilled all these requirements and large surface detectors (e.g.  $\sim 1.7~m^2$  for ATLAS [105] and  $\sim 1~m^2$  for CMS [106]) were successfully built, thus empowering the reliability of the technology.

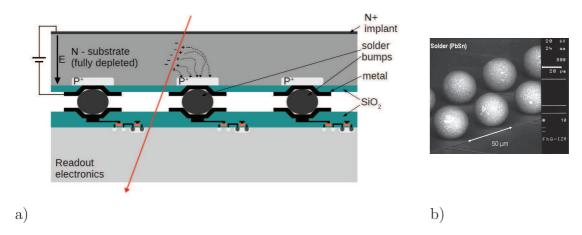

Figure 2.13: Hybrid pixel detector (a) cross-section and (b) SnPb bumps used for the sensor and electronics chip interconnection.

The separation between readout electronics and sensor electronics allows to optimize the sensor and readout parts independently. The two elements of the detector

<sup>&</sup>lt;sup>6</sup>Large Hadron Collider

<sup>&</sup>lt;sup>7</sup>A large Toroidal LHC ApparatuS

<sup>&</sup>lt;sup>8</sup>A Large Ion Collider Experiment

<sup>&</sup>lt;sup>9</sup>Compact Muon Solenoid

<sup>&</sup>lt;sup>10</sup>Large Hadron Collider beauty

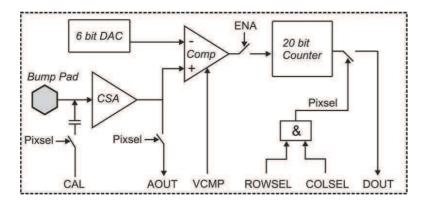

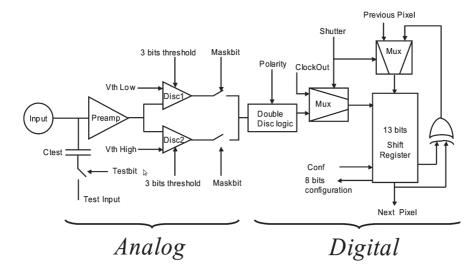

are connected together in the final stage of the production via the flip-chip technology (figure 2.13(b)). A cross-section through a hybrid pixel detector is shown in figure 2.13(a). A sensor of n-type high resistivity silicon with  $p^+$  pixel implants is most often used, but it is also possible to use different materials with higher atomic number and higher efficiencies (e.g. CdTe, CdZnTe or GaAs). The readout electronics chip is designed in a standard, commercial CMOS process with a high density of transistors. Since the sensor part is completely separated from the readout part, this type of pixel does not suffer from any limitation and allows for various signal processing schemes that can be tuned for every given application. The front-end part is always built with a charge amplifier followed by a comparator. The basic pixel architecture of a hybrid pixel detector for X-ray detection is made of three main blocks: charge detection, signal selection and local hit memory. The charge detection block converts the charges generated in the sensor, which gives rise to the voltage (current) signal that is afterwards compared with a detection threshold. The comparison results are then stored in a local memory (counter).

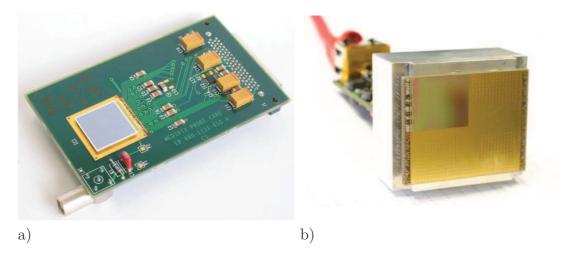

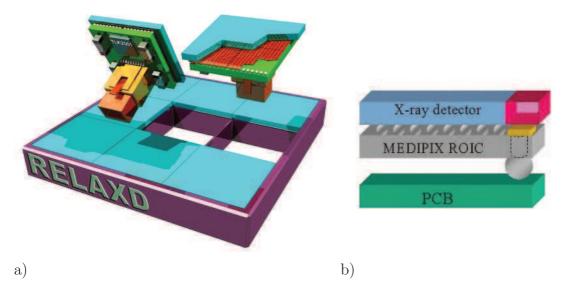

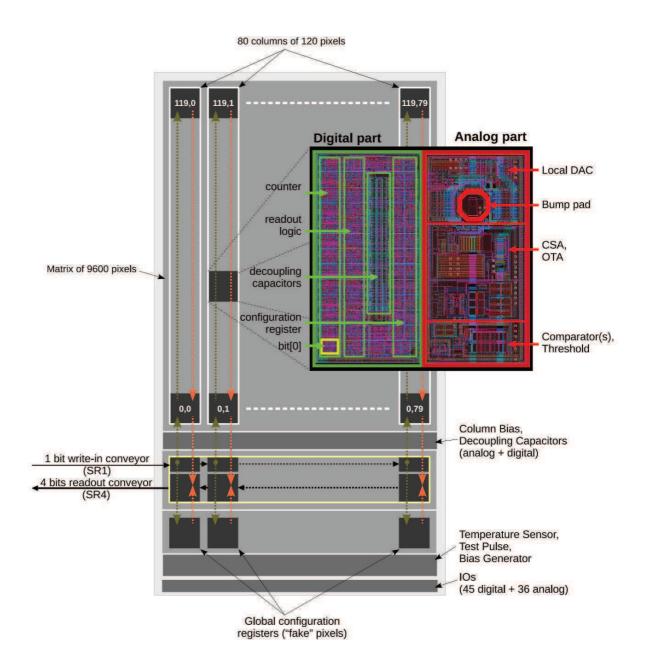

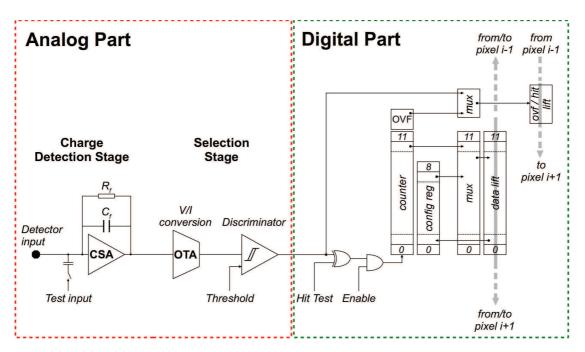

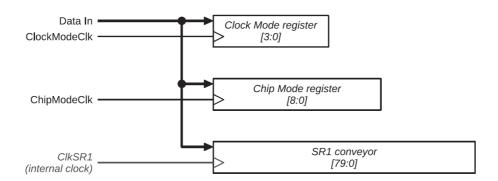

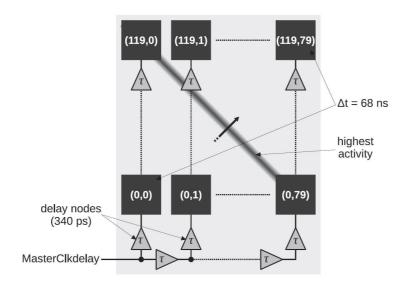

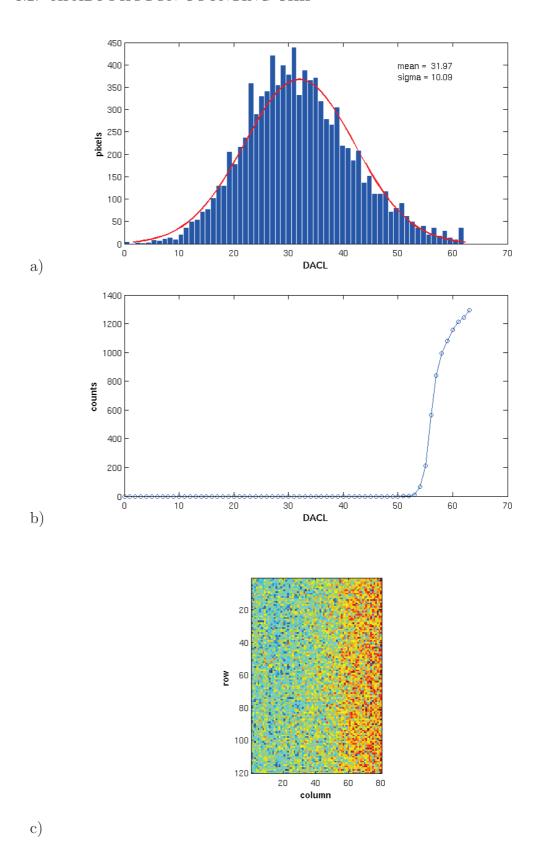

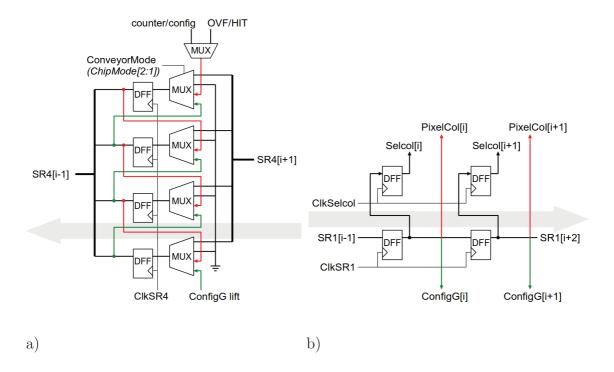

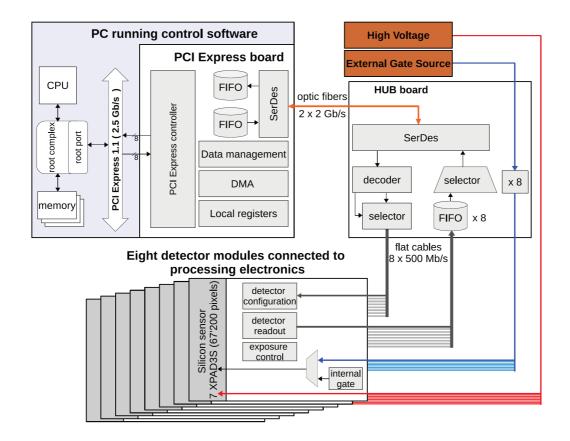

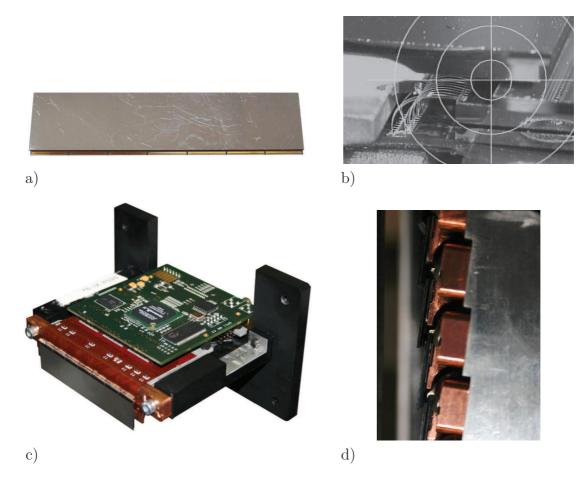

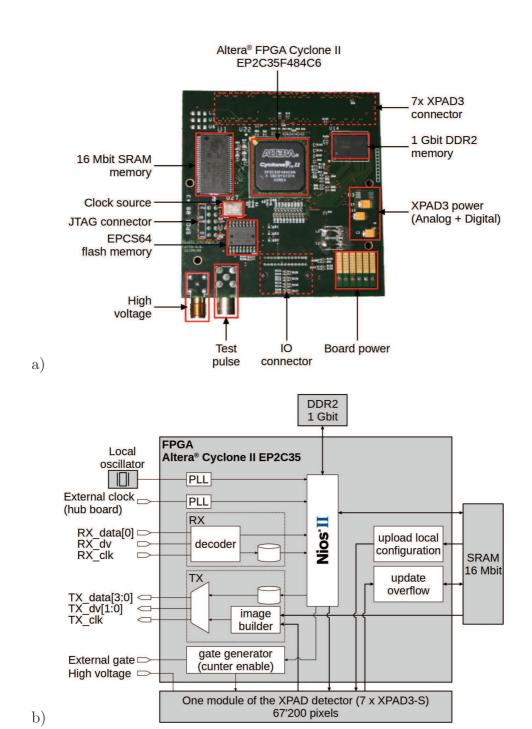

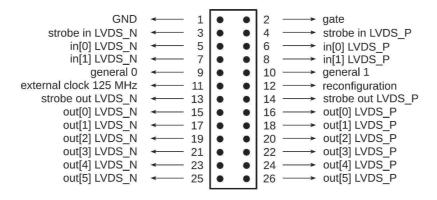

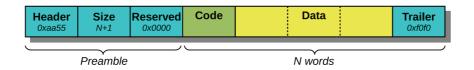

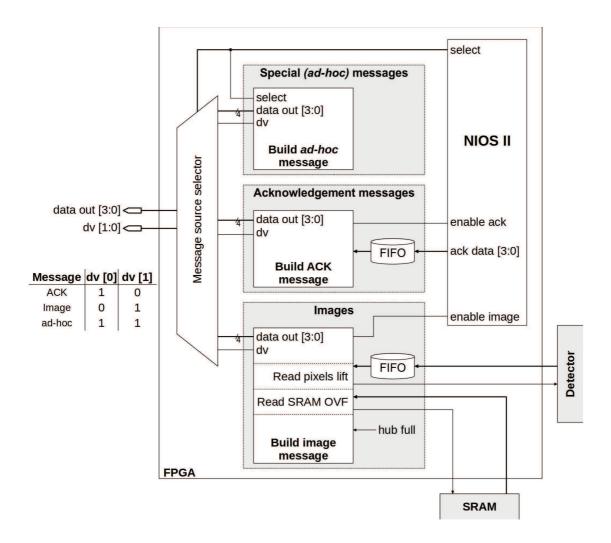

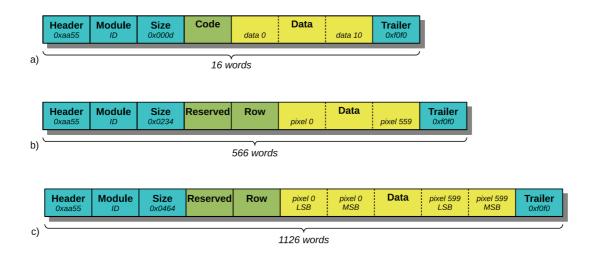

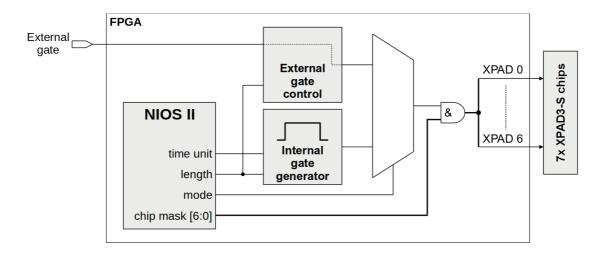

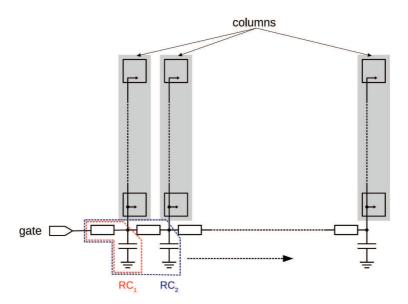

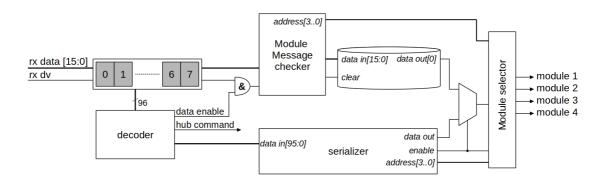

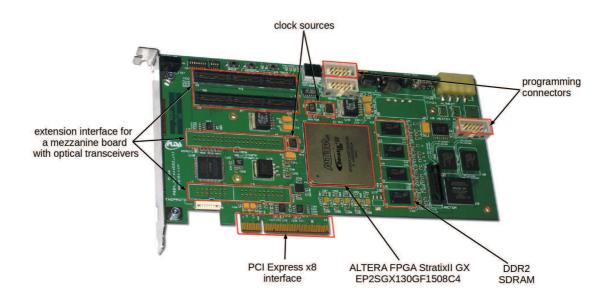

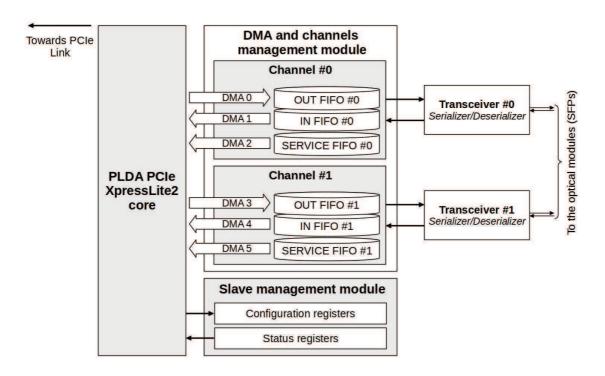

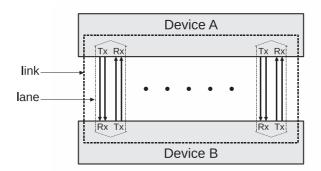

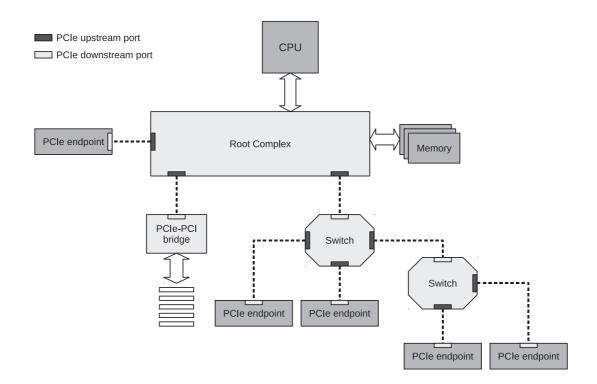

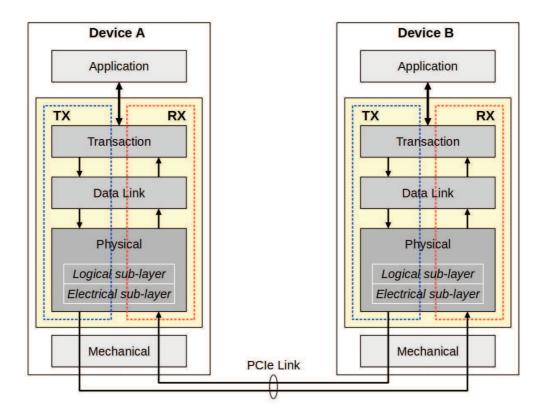

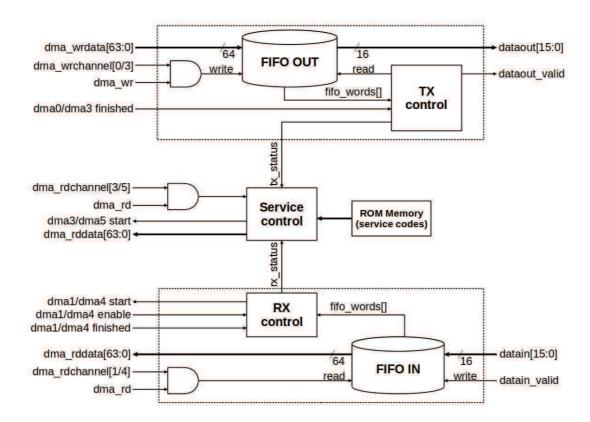

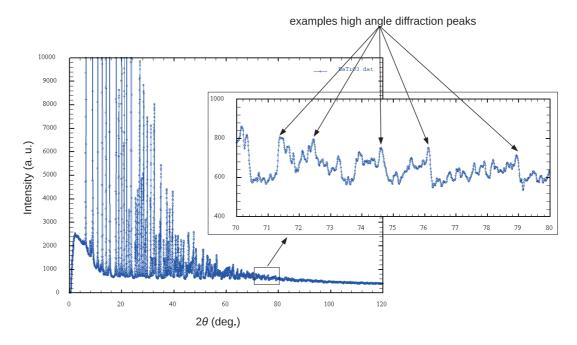

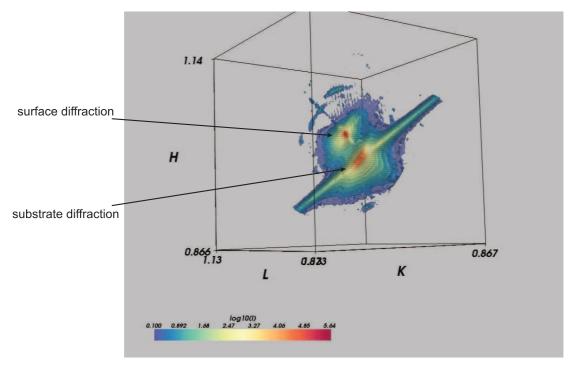

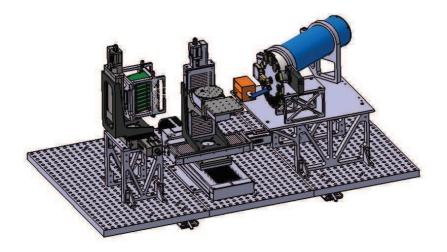

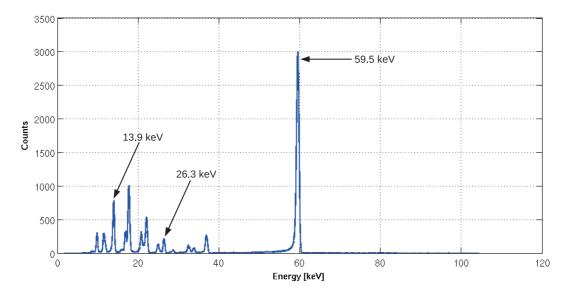

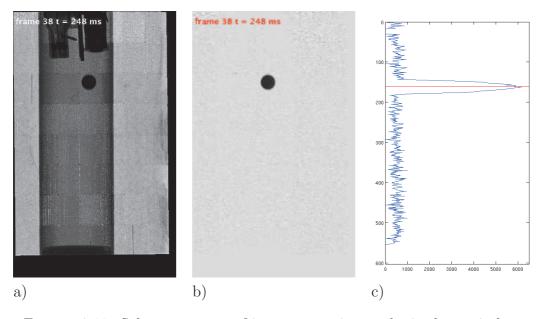

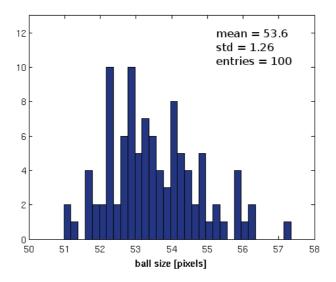

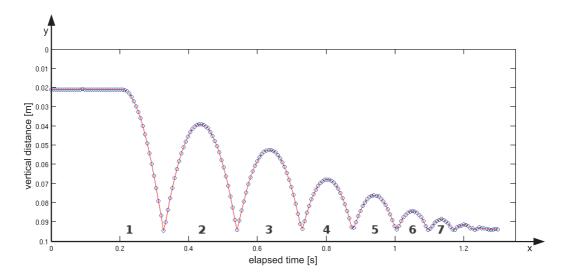

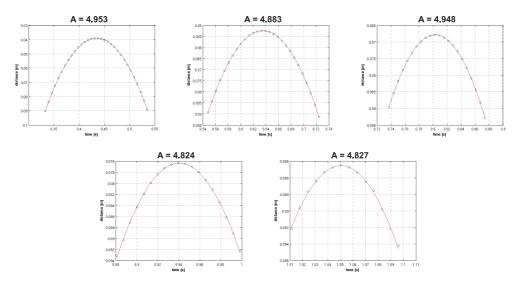

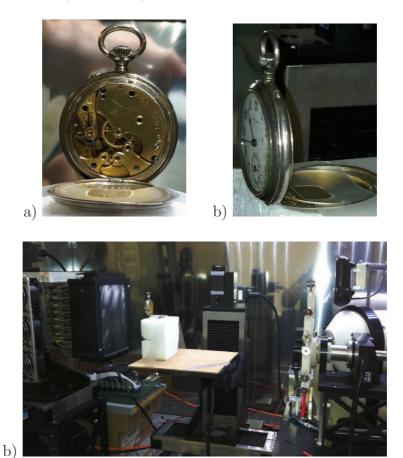

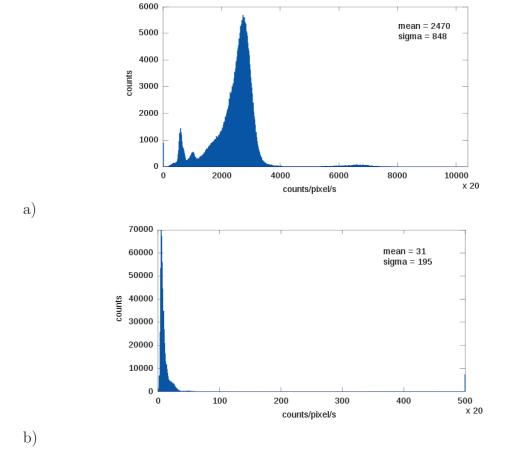

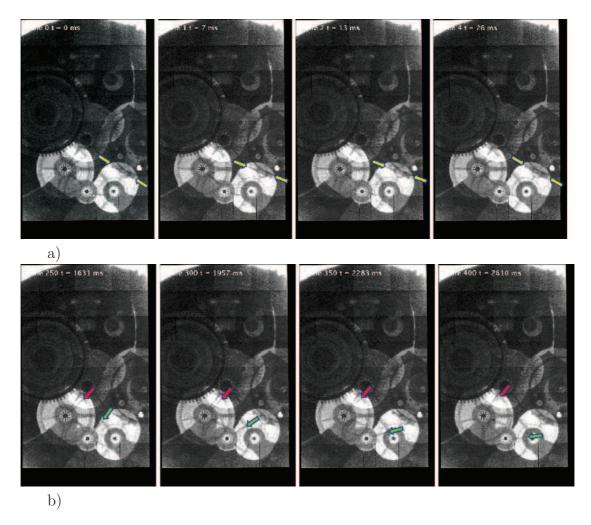

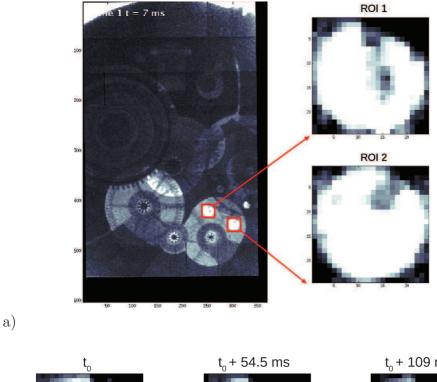

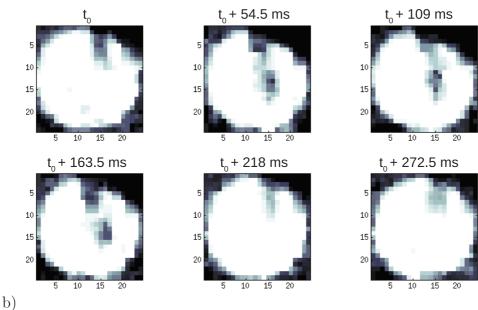

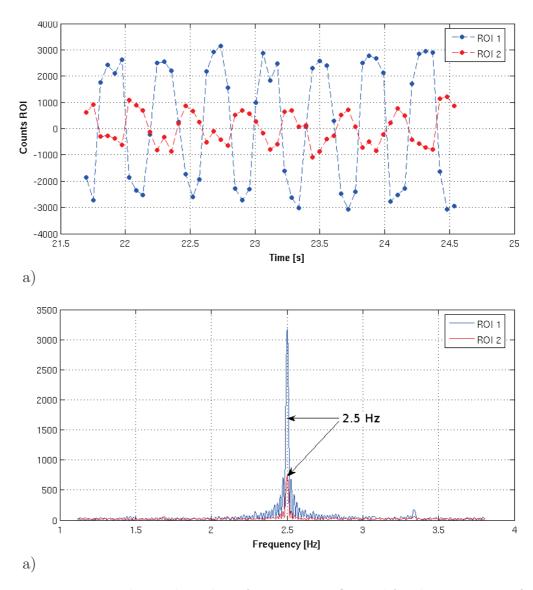

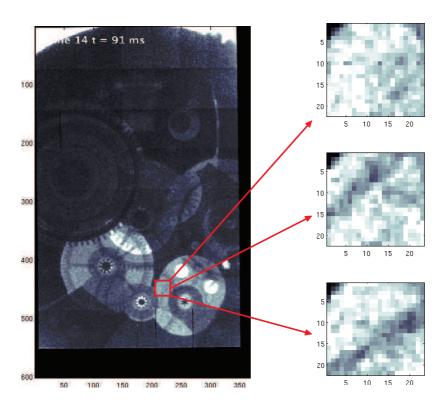

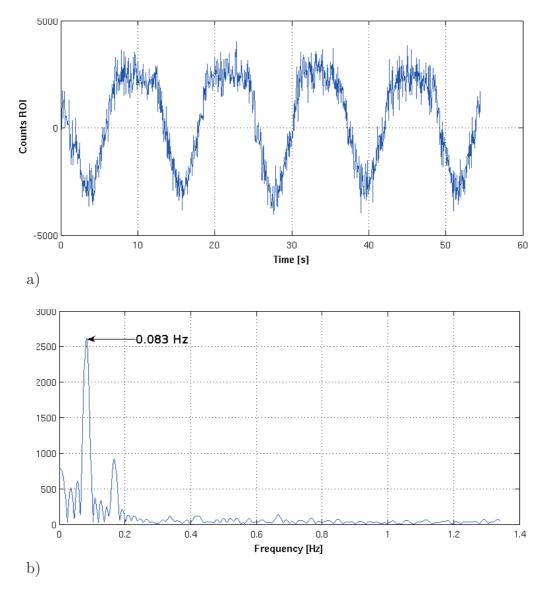

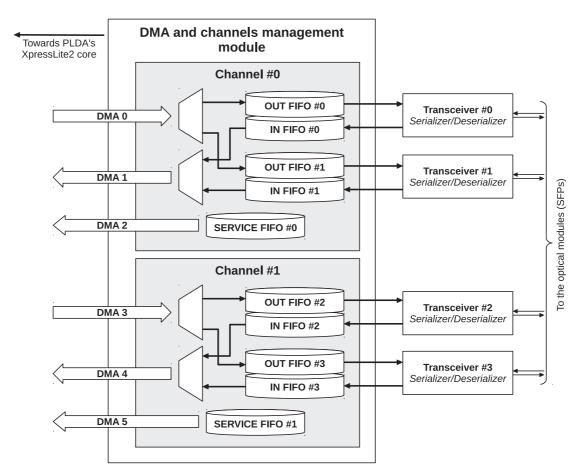

The ability to detect and count individual radiation quanta, and thus to image selected energies extends the use of hybrid pixel detectors to different fields of imaging like medical imaging and synchrotron radiation experiments. However, integration of the entire amplifying, thresholding and signal processing electronics in each one of the pixels limits the granularity of the detector and hence spatial resolution. Additionally, the high complexity and the many production steps (chip and sensor production, bump-bonding and flip-chip) result in a lower production yield that makes these detectors quite expensive devices.