# Méthodologie d'estimation des métriques de test appliquée à une nouvelle technique de BIST de convertisseur SIGMA / DELTA

Matthieu Dubois

#### ▶ To cite this version:

Matthieu Dubois. Méthodologie d'estimation des métriques de test appliquée à une nouvelle technique de BIST de convertisseur SIGMA / DELTA. Autre. Université de Grenoble, 2011. Français. NNT: 2011 GRENT033. tel-00633056v2

### HAL Id: tel-00633056 https://theses.hal.science/tel-00633056v2

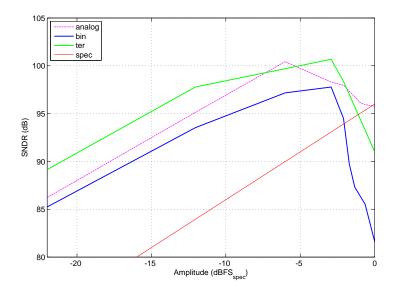

Submitted on 19 Mar 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITÉ DE GRENOBLE

#### **Thèse**

Pour obtenir le grade de

#### Docteur de l'Université de Grenoble

Spécialité : Micro-/Nanoélectronique

Arrêté ministériel: 7 août 2006

Présentée par

#### **Matthieu Dubois**

Thèse dirigée par **Salvador Mir** et coencadrée par **Haralampos Stratigopoulos**

préparée au sein Laboratoire des Techniques de l'informatique et de la Microélectronique pour l'Architecture des systèmes intégrés (TIMA) et de l'école doctorale Électronique, Électrotechnique, Automatique et Traitement du Signal (EEATS)

# Méthodologie d' estimation des métriques de test appliquée à une nouvelle technique de BIST de convertisseur $\Sigma \Delta$

Thèse soutenue publiquement le **23 juin 2011**, devant le jury composé de :

#### Mr. Jean-Michel Fournier

Professeur de l'Université de Grenoble, Président

#### Mr, Dominique Dallet

Professeur à l'Institut Polytechnique de Bordeaux, Rapporteur

#### Mr. Georges Gielen

Professeur à l'université K.U. Leuven (Belgique), Rapporteur

#### **Mme, Marie-Minerve Louërat**

Chargée de Recherche au laboratoire LIP6 à Paris, Examinatrice

#### Mr, Christophe Gaillard

Ingénieur chez Dolphin Integration à Grenoble, Examinateur

#### Mr, Gildas Léger

Chargé de Recherche au laboratoire IMSE-CNM Séville (Espagne), Examinateur

#### Mr. Salvador Mir

Directeur de Recherche au laboratoire TIMA, Directeur de thèse

#### Mr. Haralampos Stratigopoulos

Chargé de Recherche au laboratoire TIMA, Co-encadrant de thèse

ISBN: 978-2-84813-168-9

## Remerciements

Ces lignes, les dernières écrites, s'adressent aux personnes qui, de près ou de loin, d'une manière ou d'une autre, ont contribué à l'aboutissement de ces travaux. Si leur liste est trop longue pour tenir sur une seule page, je m'efforce dans ces quelques phrases de regrouper ces personnes.

Les premiers remerciements s'adressent aux membres du jury et à son président, pour le temps consacré à la lecture de ce manuscrit et à la participation à la soutenance. Ils s'adressent aussi à mon directeur de thèse, Salvador Mir, pour la formulation du sujet, l'encadrement de ces travaux et, surtout, pour ses qualités humaines. Sincères remerciements aux membres du laboratoire qui contribuent au quotidien à maintenir entre les couloirs une atmosphère chaleureuse. Cette thèse n'aurait pas abouti sans l'aide du service informatique et sans le support d'Alejandro et de Robin, toujours disponibles et accueillants.

De l'ambiance! Elle n'a jamais manqué. Je remercie chacun pour ces moments partagés ensembles, l'ancienne génération du bureau N120 aux derniers venus et Jeanne, simplement inclassable. Je remercie aussi les touristes des bureaux voisins pour leur accueil dans les instants de pause. Je remercie vivement Haralampos, co-encadrant attentif au bon déroulement de ces travaux mais aussi pour les journées de ski, les vacances en Grèce ou encore les nombreuses soirées en ville.

Présent sur la dernière ligne droite, je remercie la *dream team* et le *box* des précaires pour leur accueil au LETI. Enfin, pour tous les moments de vie hors des couloirs du TIMA, je remercie les amis là-bas en Ardèche, les amis d'ici et ceux d'ailleurs aussi, ma famille et Maud, plus paticulièrement.

# Table des matières

| R  | Remerciements |                                                         |    |  |  |

|----|---------------|---------------------------------------------------------|----|--|--|

| Ta | able o        | des matières                                            | 3  |  |  |

| 1  | Intr          | roduction                                               | 5  |  |  |

| 2  | Con           | nception et modélisation de circuits intégrés mixtes    | 11 |  |  |

|    | 2.1           | Conception industrielle                                 | 12 |  |  |

|    |               | 2.1.1 Conception et vérification                        | 12 |  |  |

|    |               | 2.1.2 Aléas de la production et fautes analogiques      | 13 |  |  |

|    |               | 2.1.3 Rendement de production                           | 15 |  |  |

|    |               | 2.1.4 Conclusion                                        | 16 |  |  |

|    | 2.2           | Modélisation analytique                                 | 17 |  |  |

|    |               | 2.2.1 Fonction de transfert                             | 17 |  |  |

|    |               | 2.2.2 Modélisation comportementale hiérarchique         | 18 |  |  |

|    |               | 2.2.3 Conclusion                                        | 23 |  |  |

|    | 2.3           | Modélisation Statistique                                | 23 |  |  |

|    |               | 2.3.1 Prédiction de rendement                           | 24 |  |  |

|    |               | 2.3.2 Analyse de sensibilité                            | 25 |  |  |

|    |               | 2.3.3 Propagation hiérarchique                          | 27 |  |  |

|    |               | 2.3.4 Fonction de régression                            | 28 |  |  |

|    |               | 2.3.5 Estimation de la densité de probabilité conjointe | 31 |  |  |

|    | 2.4           | Conclusion                                              | 33 |  |  |

| 3  | Tes           | t et conception en vue du test des circuits mixtes      | 35 |  |  |

|    | 3.1           | Test de production                                      | 36 |  |  |

|    | 3.2           | Méthodes de test                                        | 37 |  |  |

|    |               | 3.2.1 Test fonctionnel                                  | 37 |  |  |

|    |               | 3.2.2 Test structurel                                   | 38 |  |  |

|    |               | 3.2.3 Test alternatif                                   | 40 |  |  |

|    |               | 3.2.4 Conclusion                                        | 41 |  |  |

|    | 3.3           | Couverture de faute                                     | 41 |  |  |

|    |               | 3.3.1 Définitions                                       | 42 |  |  |

|    |               | 3.3.2 Injection de faute                                | 43 |  |  |

|    |               | 3.3.3 Détectabilité                                     | 44 |  |  |

|    |               | 3.3.4 Optimisation des vecteurs de test                 | 44 |  |  |

|    | 3.4           | Métriques de test                                       | 45 |  |  |

|    |               | 3.4.1 Définitions                                       | 45 |  |  |

|    |               | 3.4.2 Calcul des métriques de test                      | 47 |  |  |

|    |               | 3.4.3 Évaluation de techniques de test                  | 48 |  |  |

|    |               | 3.4.4 Conclusion                                        | 50 |  |  |

|    | 3.5           | Conception en vue du test                               | 50 |  |  |

|    |               | 3.5.1 Vue d'ensemble                                    | 50 |  |  |

|    |               | 3.5.2 Test statique des CAN                             | 52 |  |  |

Table des matières

Table des matières

|   |      | 3.5.3           | Analyse de la réponse                                   | 56                   |

|---|------|-----------------|---------------------------------------------------------|----------------------|

|   |      | 3.5.4           | Test dynamique                                          | 59                   |

|   | 3.6  | Conclu          | asion                                                   | 64                   |

| 4 | Flot | de co           | nception en vue du test                                 | 67                   |

| _ | 4.1  |                 | •                                                       | 38                   |

|   | 1.1  | 4.1.1           | 0 1                                                     | 38                   |

|   |      | 4.1.2           |                                                         | 38                   |

|   |      | 4.1.3           |                                                         | 71                   |

|   | 4.2  |                 |                                                         | 71                   |

|   | 4.4  | 4.2.1           |                                                         | 71                   |

|   |      | 4.2.1           |                                                         |                      |

|   |      |                 | <u>.</u>                                                | 73                   |

|   |      | 4.2.3           | O .                                                     | 75                   |

|   | 4.0  | 4.2.4           | 1                                                       | 30                   |

|   | 4.3  | Concli          | sion                                                    | 32                   |

| 5 | Aut  | o-test          | de CAN- $\Sigma\Delta$                                  | 35                   |

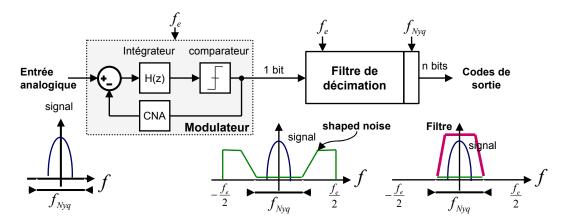

|   | 5.1  | Foncti          | onnement d'un convertisseur $\Sigma\Delta$              | 36                   |

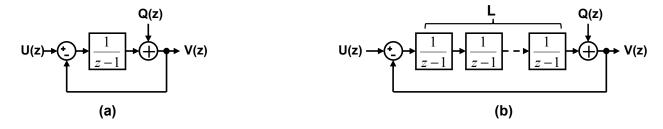

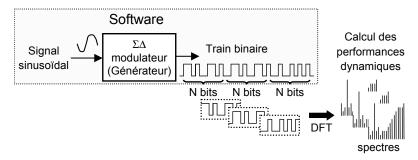

|   | 5.2  | Auto-t          | test numérique de convertisseur sigma-delta             | 37                   |

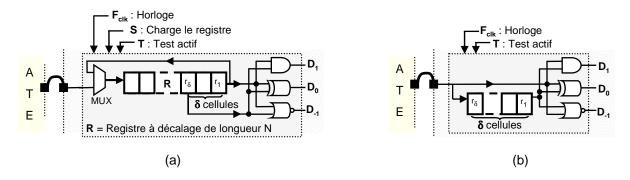

|   |      | 5.2.1           | •                                                       | 38                   |

|   |      | 5.2.2           | 1 1                                                     | 38                   |

|   |      | 5.2.3           |                                                         | 91                   |

|   |      | 5.2.4           |                                                         | 93                   |

|   | 5.3  | -               |                                                         | )4                   |

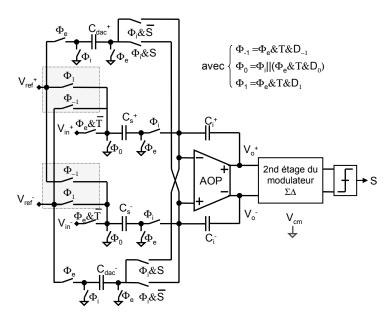

|   | 0.0  | 5.3.1           | 1                                                       | )4                   |

|   |      | 5.3.2           | •                                                       | ) <del>-</del><br>96 |

|   |      | 5.3.3           | 1 8                                                     | 96                   |

|   | 5.4  |                 | 1 1                                                     | 90<br>97             |

|   | 0.4  | 5.4.1           | •                                                       | 91<br>97             |

|   |      |                 |                                                         |                      |

|   | 5.5  | 5.4.2<br>Conclu | Implantation numérique et analogique                    |                      |

|   |      |                 |                                                         | ,0                   |

| 6 |      | _               | n en vue du test d'un CAN- $\Sigma\Delta$               |                      |

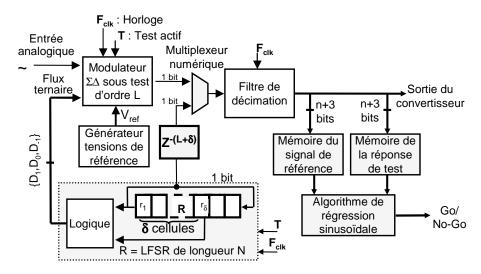

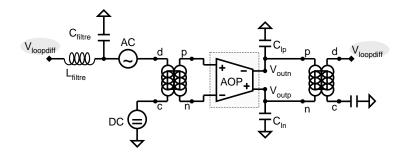

|   | 6.1  |                 | ption d'un convertisseur $\Sigma\Delta$                 | )6                   |

|   |      | 6.1.1           | Architecture système                                    | )6                   |

|   |      | 6.1.2           | Description du modèle comportemental                    | 0                    |

|   |      | 6.1.3           | Simulations paramétriques                               | 15                   |

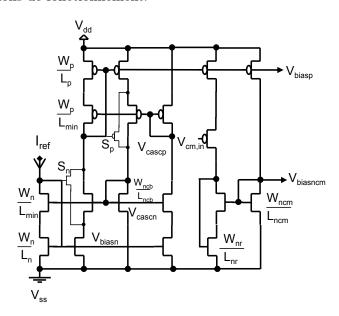

|   |      | 6.1.4           | Dimensions de l'amplificateur opérationnel              | 6                    |

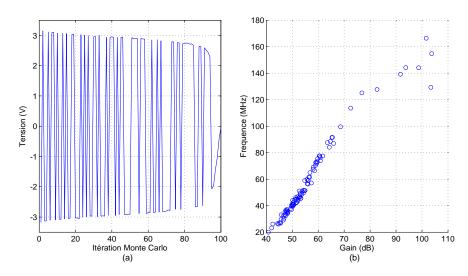

|   |      | 6.1.5           | Robustesse                                              | 18                   |

|   |      | 6.1.6           | Conclusion                                              | 21                   |

|   | 6.2  | Conce           | ption en vue du test                                    | 22                   |

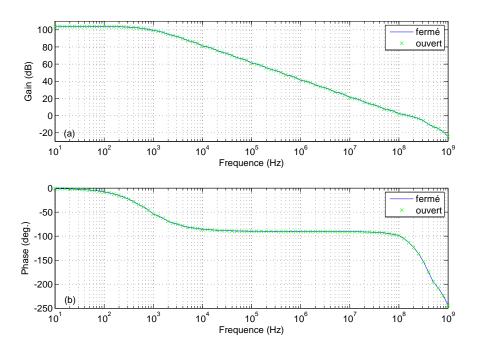

|   |      | 6.2.1           | Simulations nominales de vérification                   |                      |

|   |      | 6.2.2           | Extraction de vecteurs des paramètres comportementaux   |                      |

|   |      | 6.2.3           | Conclusion                                              |                      |

|   | 6.3  |                 | ation des métriques de test des techniques de BIST      |                      |

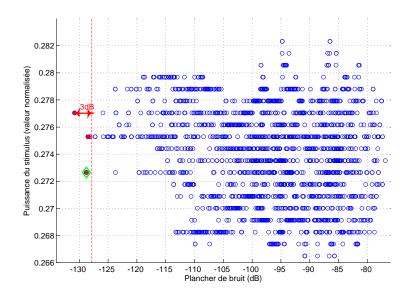

|   | 0.0  | 6.3.1           | Génération de l'échantillon de référence                |                      |

|   |      | 6.3.2           | Comparaison entre les stimuli binaires et ternaires     |                      |

|   |      | 6.3.2           | Métriques et limites de test                            |                      |

|   |      | 6.3.4           | =                                                       |                      |

|   |      | 0.5.4           | Conclusion                                              | ) /                  |

| 7 | Cali | _               | automatique d'un CAN- $\Sigma\Delta$ à partir d'un BIST |                      |

|   | 7.1  | Calibr          | age                                                     | 36                   |

|   |      | 7.1.1           | Principe                                                | 36                   |

|   |      | 7.1.2           | Redondances avec un BIST                                | 37                   |

Table des matières

Table des matières

|               |                   | 7.1.3  | Application au test numérique de CAN- $\Sigma\Delta$ | 137        |  |  |

|---------------|-------------------|--------|------------------------------------------------------|------------|--|--|

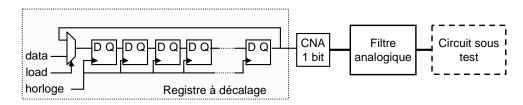

|               | 7.2               | Présen | tation du démonstrateur                              | 138        |  |  |

|               |                   | 7.2.1  | Description globale                                  | 138        |  |  |

|               |                   | 7.2.2  | Blocs numériques                                     | 139        |  |  |

|               |                   | 7.2.3  | Composante analogique                                | 144        |  |  |

|               |                   | 7.2.4  | Interface graphique                                  | 146        |  |  |

|               | 7.3               | Résult | ats expérimentaux                                    | 147        |  |  |

|               |                   | 7.3.1  | Boucle de calibrage                                  | 148        |  |  |

|               |                   | 7.3.2  | Déverminage                                          | 149        |  |  |

|               |                   | 7.3.3  | Conclusion                                           | 149        |  |  |

| 8             | Con               | clusio | n                                                    | <b>151</b> |  |  |

| Bi            | bliog             | raphie |                                                      | 154        |  |  |

| Pι            | ıblica            | ations |                                                      | 163        |  |  |

| ${f T}_{f a}$ | Table des figures |        |                                                      |            |  |  |

Table des matières

Table des matières

# Introduction

La miniaturisation des systèmes électroniques contribue fortement à la création de nouveaux appareils et services touchant tous les secteurs de l'activité humaine. Malgré la diversité de ces nouvelles applications, tout système électronique se base sur deux familles de circuits intégrés, les circuits numériques et les circuits analogiques. Le domaine numérique concerne principalement les outils informatisés et leur communication. Leur développement s'appuie sur un fonctionnement binaire du circuit pour implanter des opérations mathématiques indépendantes du support physique. Cette indépendance permet de concevoir des opérations complexes reproductibles avec la même résolution. Inversement, les circuits électroniques analogiques fonctionnent avec des signaux continus. L'interaction entre deux circuits analogiques s'effectue par une relation mettant en jeu des grandeurs physiques, principalement un potentiel ou un courant électrique. La caractéristique de chaque circuit est fortement dépendante des conditions de fonctionnement (tension d'alimentation, température, etc.).

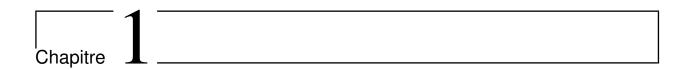

Le lien entre ces deux familles est établi par les circuits mixtes et, en particulier, les convertisseurs analogiques-numériques (CAN) et numériques-analogiques (CNA). La coexistence des circuits analogiques et numériques dans un unique circuit intégré est nécessaire pour développer des applications interactives avec l'environnement humain. La figure 1.1 représente un système électronique typique de traitement d'une information extérieure. L'information provient sous la forme d'une quantité physique (température, pression, onde électromagnétique, etc.), qui est transformée en un signal électrique continu par un capteur adapté. Ce signal est converti en codes numériques pour être corrigé (réduction du bruit, puissance du signal, sécurisation des données, etc.) avant d'être diffusé par des moyens de communications numériques (internet, téléphonie mobile, etc.) ou encore enregistré sur des supports physiques adaptés (disque dur, mémoire flash, etc.). Inversement, une information numérisée est transformée par un CNA en signaux électriques continus, eux-mêmes reproduits par un système physique permettant de communiquer avec l'environnement.

Figure 1.1 – Interaction des systèmes électroniques dans l'environnement humain.

Les enjeux de conception diffèrent entre un circuit numérique et un circuit analogique et mixte. Les systèmes numériques intègrent sur une très faible surface de silicium un grand nombre de blocs ayant des fonctions différentes reliés entre eux par un réseau complexe de communication. La description logique d'une fonction se synthétise automatiquement en circuits électriques élémentaires, les portes logiques, et de nombreux outils de conception assistée par ordinateur (CAO¹) permettent la vérification de chaque fonctionnalité en prenant en compte les problèmes de délai de propagation, l'interdiction des états interdits, etc. Ces outils optimisent l'arrangement des portes logiques et des bascules de synchronisation pour améliorer la fréquence de fonctionnement, la consommation électrique et la surface du circuit. Enfin, les techniques de placement et de routage dessinent la vue topologique de ces blocs en respectant les contraintes obtenues pendant la phase de vérification. Ainsi, la conception numérique est fortement automatisée, tandis que la conception analogique ne dispose pas d'outils si efficaces, car la sensibilité des performances d'un circuit analogique vis-à-vis du procédé technologique et de son environnement est trop importante pour créer automatiquement des blocs élémentaires.

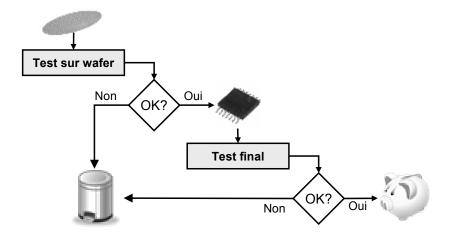

La production correspond à l'intégration sur un support physique des fonctionnalités définies dans le cahier des charges. Cette phase est constituée par un ensemble de procédés physiques et de réactions chimiques. La moindre modification de cette étape entraı̂ne une différence entre les performances du circuit conçu et celles du circuit produit. Par conséquent, il est nécessaire de vérifier si le fonctionnement du circuit est conforme à la liste de spécifications détaillée dans le cahier des charges. C'est l'objectif de la phase de test.

Suivant la nature du circuit testé, la stratégie est différente. En effet, le test d'un circuit numérique consiste à injecter des vecteurs de test permettant idéalement de pouvoir contrôler et observer tous les états du circuit à chaque instant. Le D-algorithme, premier algorithme d'automatisation du test de circuits numériques, se base sur ces notions d'observabilité et de contrôlabilité du circuit [1]. La détection des circuits défaillants se fait par une simple comparaison des résultats de test provenant du circuit produit et des résultats de simulations. La génération des vecteurs de test se fait pendant la conception et la vérification du circuit pour garantir un taux de couverture de faute élevé et l'automatisation de cette étape a progressé avec les outils de CAO associés. À contrario, le test des circuits analogiques et mixtes repose encore sur la vérification de la liste des spécifications par la mesure des performances. Son développement consiste à mettre en place un environnement faible bruit, limiter les interférences, choisir les générateurs de signaux, etc... La phase de conception ne tient pas compte de la testabilité du circuit et l'observabilité et la contrôlabilité ne sont pas optimisées avant la production du circuit limitant les possibilités de réduction des coûts.

#### Motivation

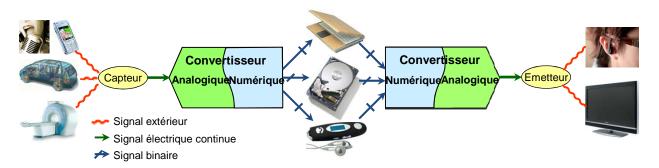

La figure 1.2 représente l'évolution du coût de production et de test par transistor intégré dans un microprocesseur en fonction du temps. Ainsi, l'augmentation de la densité d'intégration permet de réduire les coûts de production, mais implique un allongement des séquences de test pour vérifier le fonctionnement de chaque bloc. Ces prévisions établies pour des microprocesseurs démontrent que le coût du test d'un transistor dépasse certainement son coût de production pour les circuits analogiques et mixtes. En effet, la tendance pour ce type de circuits est une occupation de 20% de la surface de silicium contre 70% du coût du test du circuit complet [2].

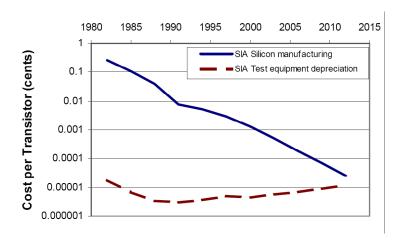

La figure 1.3 établit une répartition temporelle du nombre de publications en rapport avec le test et le test intégré<sup>2</sup> des circuits analogiques parues dans la base de données de l'IEEE<sup>3</sup>. Sur cette figure, le nombre de publications dans ces domaines a doublé ces dix dernières années. Cet intérêt montre le besoin des industriels et la difficulté des chercheurs pour réduite le coût du test de ces circuits.

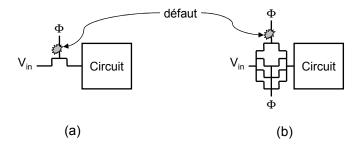

Plusieurs pistes ont été suivies pour réduire le coût du test analogique : adapter le test numérique basé sur la détection de fautes structurelles aux circuits analogiques, déterminer des mesures de test

<sup>&</sup>lt;sup>1</sup>CAD : Computer Aided Design

<sup>&</sup>lt;sup>2</sup>BIST : Built-In Self-Test

<sup>&</sup>lt;sup>3</sup>Institute of Electrical and Electronics Engineers

Figure 1.2 – Coût de production et de test par transistor d'un microprocesseur.

Figure 1.3 – Nombre de publications impliquant le test de circuits analogiques.

simples et fortement corrélées avec les performances du circuit, ou encore, ajouter une très faible surface de circuiterie pour faciliter le test. Les deux premières méthodes ne permettent pas la vérification par une mesure directe des performances, mais réduisent le temps de test et l'investissement nécessaire à l'achat d'appareils de mesures dehaute qualité. La dernière proposition implique une augmentation du coût liée à la surface de silicium occupée. Toutefois, cette surface peut être estimée et optimisée si le développement du circuit de test s'effectue simultanément au développement du circuit à tester.

Mais l'utilisation dans des lignes de production à fort volume de nouvelles techniques de test intégré pour des circuits analogiques et mixtes reste marginale comparée aux techniques employées dans le monde numérique. En effet, le remplacement d'une méthode de test éprouvée par une nouvelle technique fait courir le risque de réduire la qualité du test. Cette qualité se détermine principalement par la capacité de différencier correctement les circuits fonctionnels des circuits défectueux. Par conséquent, il est nécessaire d'étudier la qualité d'une technique de test avant son implantation dans le flot de production.

#### Objectif

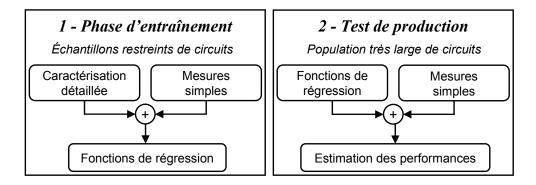

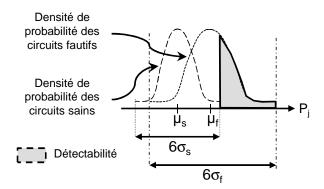

L'évaluation d'une qualité d'une technique de test avant son implantation dans le flot de production s'effectue forcément pendant la phase de conception du circuit. Les travaux de Bounceur[3] se basent sur une estimation de la densité de probabilité conjointe des performances et des mesures de test pour évaluer la qualité d'une technique de test à partir des métriques de test définies par Sunter et al.[4]. Ces métriques quantifient la capacité d'une technique de test de différencier correctement les circuits fonctionnels des circuits défaillants. Cette densité est obtenue à partir de simulations Monte Carlo électriques, un outil proposé dans les logiciels de CAO pour estimer la robustesse des circuits vis-à-vis des variations des paramètres du procédé technologique [5]. Mais la génération d'un échantillon reflétant les conditions de production d'un circuit peut s'effectuer au moyen de simulations électriques si la complexité de ce circuit est raisonnable. Dans le cas contraire, le temps de simulation est incompatible avec la durée consacrée au développement du circuit. D'autre part, ces travaux ne considèrent que l'estimation d'une densité par une loi paramétrique.

Par conséquent, il est nécessaire d'adapter cette méthodologie d'estimation des métriques de test aux circuits analogiques et mixtes complexes pour évaluer l'efficacité de techniques de test en partie par million. Cette généralisation doit aussi concerner la forme des échantillons, c'est-à-dire s'affranchir des conditions trop restrictives mais nécessaires au calcul d'une loi paramétrique. Enfin, il est judicieux de considérer l'environnement de conception industrielle de circuits intégrés pour développer cette méthodologie.

#### Contribution

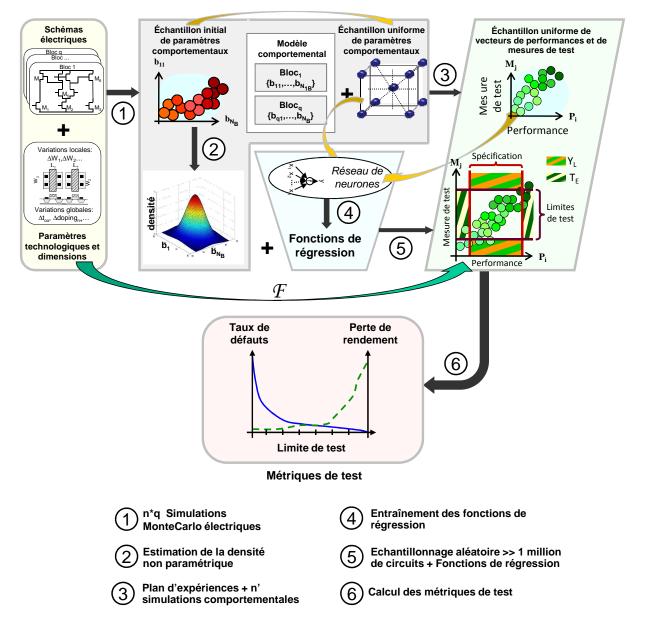

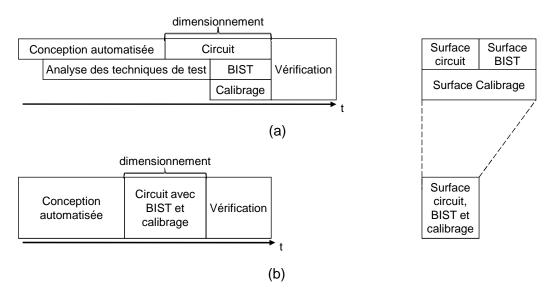

L'évaluation d'une technique de test intégrée pendant la phase de conception nécessite la synthèse d'un échantillon virtuel suffisamment large pour permettre une estimation des métriques de test en partie par million. La génération d'un large échantillon a déjà été l'objet de recherches pour estimer le rendement d'un circuit. Nous proposons d'adapter ce type d'analyse à l'estimation des métriques d'une technique de test à partir de la distribution conjointe des performances et des mesures de test. Pour réduire les efforts spécifiques à l'estimation de ces métriques, cette méthodologie utilise le flot de conception d'un circuit analogique et mixte et réutilise des résultats obtenus pendant la conception. Avec ces conditions, le temps de mise sur le marché du produit est inchangé.

Ensuite, une nouvelle technique de test intégrée mise au point pendant ces travaux de recherche est détaillée en montrant ses avantages vis-à-vis de l'état de l'art. La génération du stimulus de test est optimisée par un nouvel algorithme de sélection et la faisabilité de la méthodologie d'estimation ainsi que la qualité de la technique de test sont démontrées par simulations comportementales et électriques d'un modulateur  $\Sigma\Delta$ .

Enfin, un prototype implantant une technique de test sur un circuit programmable met en évidence l'utilité d'une technique de BIST pour faciliter le calibrage automatisé. Ce prototype a été réalisé en collaboration avec un partenaire industriel, STMicroelectronics dans le cadre d'un projet européen NanoTest-MEDEA+. En particulier, l'algorithme d'analyse de la réponse de test et l'interface graphique permettant de piloter le calibrage ont été développées par leur soin.

#### Plan du manuscrit

Le chapitre suivant cette introduction est consacré au flot industriel de conception de circuits intégrés analogiques et mixtes dont la complexité contraint à respecter une succession d'étapes pour optimiser les rendements de production. Ce flot, dit *Top-Down*, se base sur la création de plusieurs modèles du circuit, qui permettent de prédire les performances du système complet, de chaque bloc et des circuits électriques élémentaires. Plus précisément, le modèle comportemental sert de description intermédiaire importante pour établir les dimensions des circuits élémentaires, qui sont optimisées en étudiant l'impact des variations des paramètres du procédé technologie sur les performances du circuit grâce à des modèles statistiques.

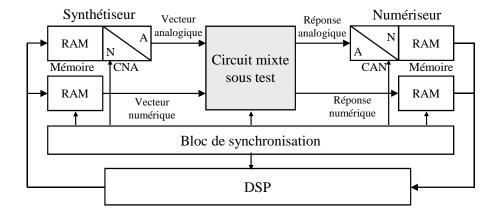

Dans le troisième chapitre, le thème du test de circuits intégrés analogiques et mixtes est abordé en présentant les différentes formes de test : le test fonctionnel, structurel et alternatif et les métriques associées. Ensuite, l'application de la conception en vue du test est illustrée par la description des techniques existantes pour améliorer la testabilité des CAN.

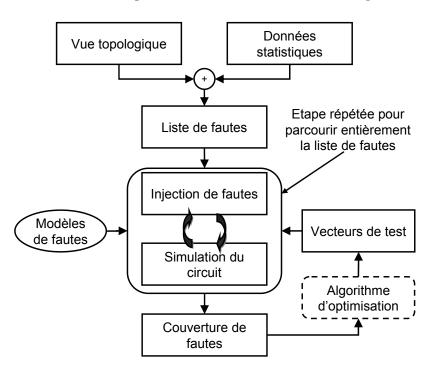

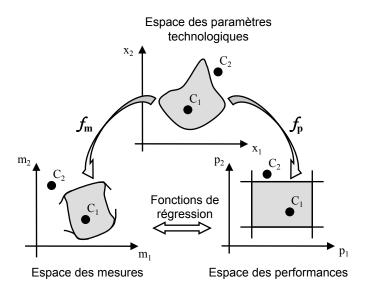

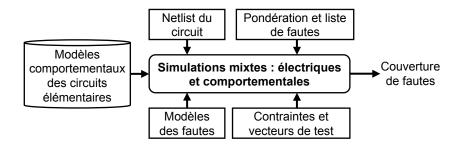

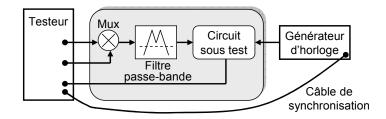

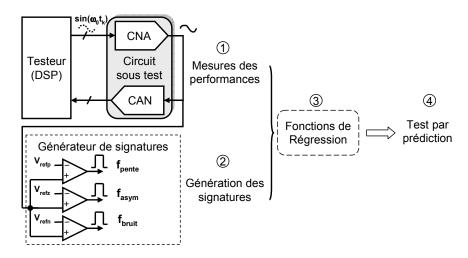

Le quatrième chapitre présente la méthodologie d'estimation des métriques de test adaptée aux circuits intégrés analogiques et mixtes. La première section propose une vue d'ensemble de cette méthodologie basée sur la propagation hiérarchique des variations des paramètres du procédé technologique aux performances et mesures de test. Ensuite, la méthodologie est détaillée en s'attardant sur les hypothèses et les conditions nécessaires au passage d'une étape à la suivante.

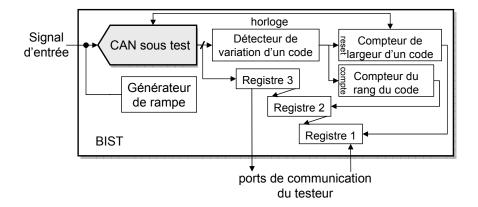

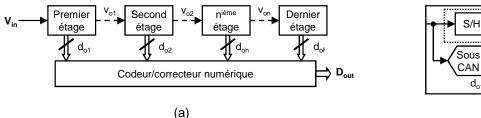

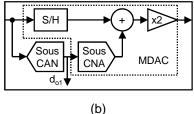

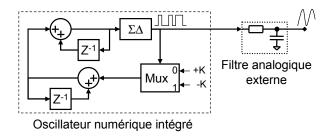

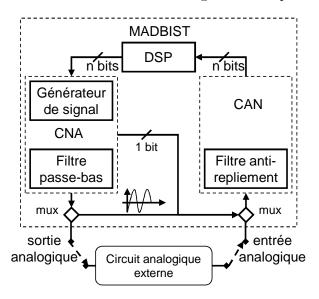

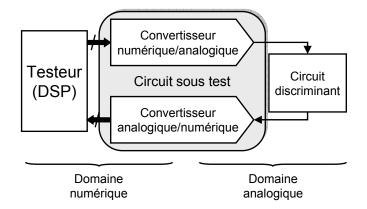

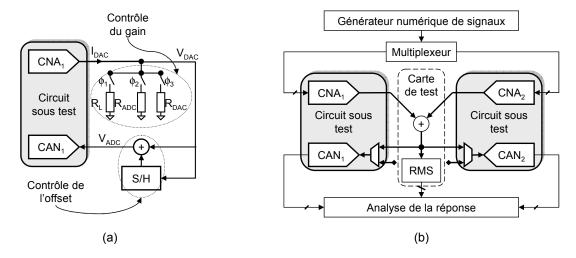

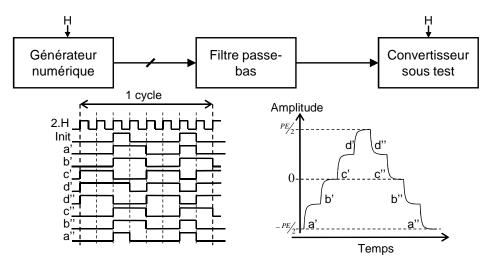

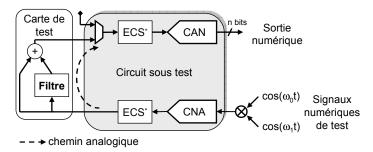

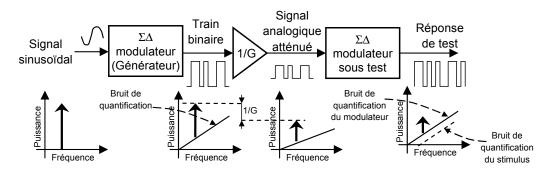

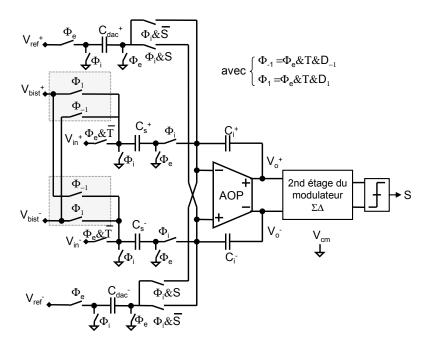

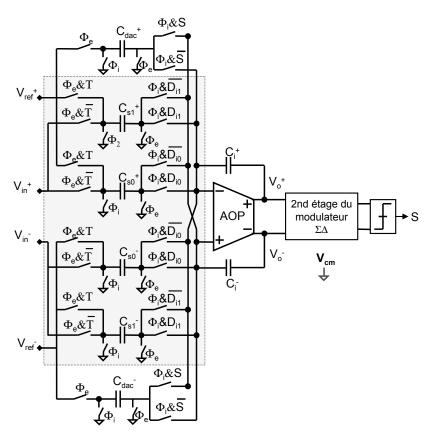

Le cinquième chapitre est consacré à une nouvelle technique de test intégré, purement numérique, de modulateurs  $\Sigma\Delta$ . Le fonctionnement ainsi que les différentes implantations du test numérique de ce type de modulateur sont rappelés dans la première partie. Ensuite, la génération du stimulus de test est détaillée. En particulier, les caractéristiques d'un stimulus ternaire sont comparées à celles du stimulus binaire correspondant. La conclusion de ce chapitre est illustrée par un exemple d'implantation sur une puce de cette nouvelle méthodologie.

Dans le sixième chapitre, différentes techniques de test numérique d'un modulateur  $\Sigma\Delta$  sont évaluées à partir d'une estimation des métriques de test. Ce chapitre applique la conception Top-Down à un modulateur pour mettre en évidence les étapes permettant d'obtenir les informations nécessaires à la mise en œuvre de la méthodologie d'évaluation. Enfin, les métriques de test obtenues pour chaque technique sont estimées pour comparer leur efficacité par rapport à un test standard.

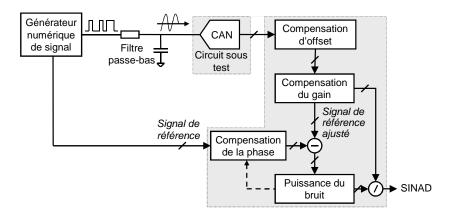

Le dernier chapitre présente une application attrayante de l'implantation d'une technique de test sur le même silicium que le circuit sous test : le calibrage. Un démonstrateur conçu à partir d'un circuit programmable permet de calibrer un modulateur  $\Sigma\Delta$  à partir de l'injection d'un signal de test binaire. Les résultats obtenus montrent la faisabilité du système.

La conclusion reprend les principales contributions de ces travaux et propose des lignes directrices pour leur continuité.

Introduction

# Conception et modélisation de circuits intégrés mixtes

La fabrication de circuits intégrés s'adapte à la pression du marché en implantant toujours plus de nouvelles fonctionnalités sur une seule puce et, parallèlement, en augmentant la densité d'intégration [6]. Ces deux tendances font croître la difficulté de concevoir et de fabriquer des systèmes miniaturisés compétitifs. Guidée par la réduction des coûts, chaque étape est optimisée pour satisfaire le client et rentabiliser l'activité. Le changement est difficile à introduire, il requiert la preuve de sa nécessité et la volonté de chacun à s'y soumettre.

Dans ce chapitre, un portrait de l'environnement de production des circuits analogiques et mixtes est dressé, car la mise en place d'une méthodologie prenant en compte l'évaluation de la qualité de nouvelles techniques de test doit être effectuée en respectant les étapes de conception existantes. Il est préférable de contribuer légèrement à l'existant plutôt que de proposer de nouveaux outils impliquant des modifications conséquentes du flot de développement.

La première partie présente les différentes phases de ce flot, puis les défauts de production et leur impact sur le rendement de fabrication de circuits intégrés. Cette vue d'ensemble permet d'ériger le constat suivant : la modélisation tient une place majeure dans la conception de circuits complexes. Cette importance atteint tous les niveaux de description du circuit, du niveau système au niveau électrique. Ainsi, la seconde partie traite les différentes approches de modélisation d'un circuit complexe en fonction du niveau de détails requis. Dans cette partie, de nombreux modèles de convertisseurs analogiques-numériques viennent illustrer les propos. Enfin, la prédiction du rendement de production a nécessité la mise en place d'outils statistiques, dont les principaux font l'objet de la troisième partie de ce chapitre.

#### 2.1 Conception industrielle

#### 2.1.1 Conception et vérification

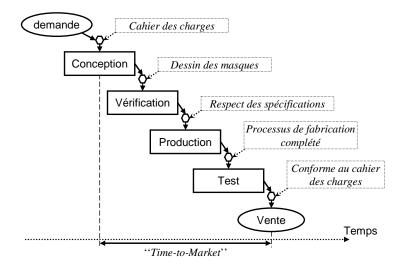

Le cycle de fabrication d'un circuit intégré se divise en 4 phases : la conception, la vérification, la production et le test. La figure 2.1 représente la chronologie de ces phases séparées par le critère validant leur complétion. Le cycle commence par l'élaboration d'un cahier des charges défini avec le client ou en interne suivant le produit ciblé. Un circuit se définit par un nombre de fonctionnalités et de performances correspondantes, les spécifications. Dans les faits, l'équipe de développement travaille à partir d'un cahier des charges plus strict pour anticiper de nouvelles exigences du client ou encore pour développer non pas un seul produit mais une gamme avec différentes options.

Figure 2.1 – Évolution d'un projet de fabrication d'un circuit intégré.

La phase de conception commence dés que les principales spécifications ont été fixées. L'enjeu de cette phase est de minimiser le temps nécessaire à la réalisation d'un circuit respectant toutes les conditions du cahier des charges. Le temps de mise sur la marché<sup>1</sup> est primordial pour l'activité de l'entreprise, car la vente de circuit est la principale source de revenus, et pour éviter qu'un produit concurrent ne se positionne premier sur le marché. Une solution pour remplir le défi de produire rapidement des circuits performants est d'adopter la stratégie "diviser pour mieux régner".

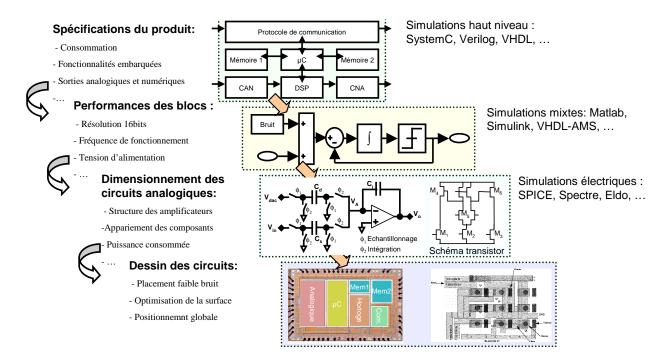

La figure 2.2 illustre un exemple de décomposition hiérarchique, dite Top-Down de l'étape de conception d'un circuit intégré [7]. L'objectif de ce flot est de déterminer les dimensions des composants électriques élémentaires qui permettent de satisfaire les spécifications. En partant du cahier des charges, l'équipe de conception effectue des simulations au niveau système du circuit complet découpé en blocs fonctionnels: micro-contrôleur, mémoire, convertisseurs analogique-numérique (CAN) et numériques-analogiques (CNA), émetteurrécepteur de radio-fréquence, etc. Les résultats de ces simulations permettent de choisir une architecture complète décrite par les différents blocs et leurs interconnexions, mais aussi, de déterminer une liste de contraintes des performances de chaque bloc. La conception des blocs se base sur ces contraintes et plus elles sont fortes, plus la conception du circuit est complexe. Ainsi, chaque niveau est construit à partir des résultats des simulations du niveau précédent afin d'atteindre la description électrique du circuit [8]. À partir des simulations électriques, les dimensions de chaque composant (transistors, capacités, etc.) sont fixées en vue de dessiner leur représentation géométrique finale. L'enjeu est de prédire toutes les performances du circuit comme, par exemple, la consommation électrique. Cette dernière est rarement prise en compte dans les modèles des niveaux supérieurs qui se concentrent principalement sur l'étude du traitement du signal. Ces simulations sont aussi effectuées en fixant des conditions de fonctionnement extrêmes définies dans les spécifications. La phase de conception s'achève lorsque les dessins de tous les composants électriques sont regroupés pour former les masques de production.

<sup>&</sup>lt;sup>1</sup>TTM : Time-To-Market

La conception *Top-Down* s'est imposée dans l'environnement de travail des ingénieurs même si elle nécessite l'emploi de nombreux outils, qui permettent de compléter chaque étape et de simuler les modèles avec différents niveaux d'abstraction. Son implantation représente un coût important car les ingénieurs de conception prennent le temps de se former à l'emploi des différents outils. En plus, leur développement ou l'achat de licences d'utilisation sont onéreux.

Enfin, une étape supplémentaire de vérification, dite Bottom-Up est nécessaire, car une erreur de description du circuit se répercute sur les niveaux d'abstraction suivants [9]. Cette étape de vérification consiste à simuler un modèle électrique extrait à partir de la vue topologique<sup>2</sup> pour prédire les performances du circuit en tenant compte de tous les phénomènes parasites. Cependant, les temps de simulation étant excessivement longs et l'existence d'une infinité de cas particuliers à vérifier empêchent une conduite formelle de la vérification. Cette dernière est conduite de manière intuitive en fonction de l'expérience de l'équipe de conception. La vérification commence avant la fin de la phase de conception et se poursuit même après l'envoi des masques de production en fabrication, car déceler une faute de conception le plus tôt possible réduit considérablement son impact sur le coût de fabrication du produit.

Figure 2.2 – Illustration du schéma de conception Top-Down d'un circuit intégré.

#### 2.1.2 Aléas de la production et fautes analogiques

Une fois le circuit virtuel terminé, sa fabrication se compose d'une succession d'étapes, appelée procédé technologique <sup>3</sup>, dont la mise au point consiste à établir un protocole ordonnant ces étapes et à détailler tous les procédés et tous les produits employés. Parallèlement, les règles de dessin des masques de production sont établies pour garantir le respect par le circuit produit des performances prédites par simulation.

Cependant, malgré la minutie accordée à l'exécution de chaque étape, la mesure des performances des circuits produits et les résultats de simulation du circuit conçu diffèrent, car de légères perturbations surviennent pendant la production. Si le *process* est au point et si le circuit respecte les règles de dessin, les perturbations sont aléatoires. Toute perturbation reproductible est imputable à une erreur du respect du protocole de fabrication.

<sup>&</sup>lt;sup>2</sup>Layout

$<sup>^{3}</sup>Process$

Les sources de ces perturbations proviennent [10]

- des paramètres de contrôle : homogénéité de la température de cuisson du silicium, durée d'exposition, concentration des gaz, etc.

- de la topologie du circuit : formes complexes non symétriques, composant élémentaire particulier (MEMS, EEPROM, etc.)

- de l'environnement externe : taux d'humidité, emplacement de la galette de silicium dans le four, activité sismique, etc.

Ces perturbations se classent en fonction de leur nature physique ou en fonction de leur impact sur les performances du circuit.

Dans le premier cas, leur classement forme deux catégories : les variations locales et les variations globales [11].

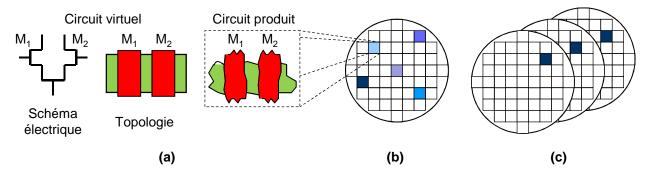

#### Les variations locales

Elles impliquent une relation entre les variations de la longueur et de la largeur du composant. Leur impact sur le rendement des circuits analogiques augmente avec la densité d'intégration des procédés technologiques. Le terme s'emploie particulièrement pour des composants élémentaires appariés comme illustré sur la figure 2.3.(a). Le défaut d'appariement diminue en augmentant la surface et la proximité sur le silicium des composants, et grâce à des techniques de dessin spécifiques [12, 13].

#### Les variations globales

Les variations globales se définissent comme étant indépendantes des dimensions du composant élémentaire et représentent l'écart de performances entre deux circuits de conception identique, mais produits sur des emplacements différents de la plaquette de silicium<sup>4</sup> ou sur une autre plaquette, comme illustré respectivement sur les figures 2.3.(b) et 2.3.(c) [14].

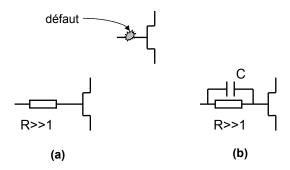

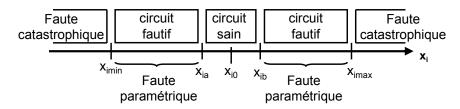

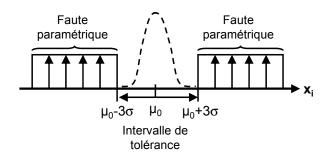

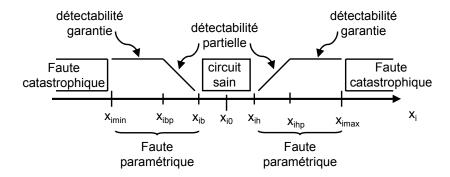

Lorsque les perturbations du *process* sont définies en fonction de leur impact sur les performances du circuit, elles sont appelées fautes. Plus précisément, deux types de fautes sont définies : les fautes paramétriques et les fautes catastrophiques. Ces définitions impliquent que chaque paramètre technologique possède une plage de valeurs, définie par le fondeur, entre lesquelles le fonctionnement du composant élémentaire est garanti.

**Figure 2.3** – Variations (a) locales, (b) globales et (c) entre différents lots de plaquette.

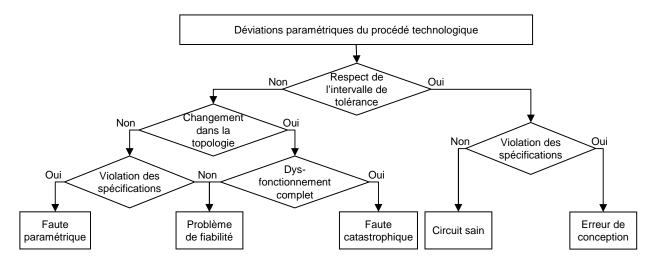

À partir de l'arbre de décision représenté sur la figure 2.4, les différentes conséquences des perturbations se résument en fonction de leur impact sur le fonctionnement du circuit : faute paramétrique ou catastrophique, circuit sain, problème de fiabilité et dysfonctionnement complet.

- Faute paramétrique : un ou plusieurs paramètres du process ne respectent pas les contraintes de fabrication entraînant le non-respect d'au moins une des spécifications du circuit.

- Faute catastrophique : une erreur dans la topologie entraîne un dysfonctionnement complet du circuit. Ce type de fautes apparaît, en particulier, lorsqu'une particule étrangère se pose sur la surface de silicium contrariant localement la chaîne de complétion du circuit.

$<sup>^4</sup>$ wafer

- Erreur de conception : aucune erreur lors de la production pourtant au moins une des (toutes les) spécifications du circuit n'est pas respectée (ne sont pas respectées). C'est, par exemple, le résultat d'un mauvais dimensionnement du circuit. Inversement, un ou plusieurs paramètres du process ne respectent pas les contraintes de fabrication entraînant un dysfonctionnement général du circuit. C'est aussi une erreur de conception, car un circuit analogique doit maintenir un fonctionnement cohérent, quelles que soient les variations paramétriques. Dans le cas contraire, il est très probable que ce circuit produise un grand nombre de fautes paramétriques.

- Problème de fiabilité: une erreur de fabrication provoque une modification dans la topologie du circuit sans modifier le fonctionnement du circuit ou en entraînant uniquement le non-respect d'au moins une des spécifications. C'est une faute très probable lorsque le circuit est composé de plusieurs composants élémentaires branchés parallèlement, par exemple, des miroirs de courant. Ces circuits sont défaillants dans la mesure où la fiabilité du circuit est remise en cause. Un autre problème de fiabilité se pose si un ou plusieurs paramètres du process ne respectent pas les contraintes de fabrication sans affecter le fonctionnement du circuit. Par exemple, une épaisseur d'oxyde de grille trop faible implique un problème de fiabilité à long terme, car elle risque de se rompre. Ou encore, la violation d'une des spécifications résultant d'une modification de la topologie du circuit. Ce type de problème fait l'objet d'un contrôle particulier, dit contrôle de qualité.

Figure 2.4 – Classification des fautes analogiques.

Enfin, la représentation la plus juste est la vue topologique, mais cette dernière n'étant disponible qu'une fois le circuit entièrement dimensionné, elle s'utilise plutôt pendant la phase de vérification. Ainsi, la prédiction des performances obtenues par des simulations électriques est considérée comme étant la plus proche des valeurs réelles des performances de circuits produits, car les perturbations du process sont incluses dans les modèles électriques des composants élémentaires [15, 16]. Ces perturbations sont représentées par des variables statistiques déterminées par le fondeur pendant la mise au point du process. Pour étudier leur impact sur le fonctionnement du circuit, les outils de conception assistée par ordinateur permettent notamment de sélectionner les valeurs hautes et basses de ces variables. Ces simulations électriques, dites simulations de coin <sup>5</sup>, sont considérées comme trop pessimistes vis-à-vis de la réalité, mais apportent un premier aperçu des performances du circuit pour des variations extrêmes des paramètres du process.

#### 2.1.3 Rendement de production

Les fautes catastrophiques et les fautes paramétriques sont les deux sources de production de circuits défectueux [17]. Les fautes catastrophiques proviennent majoritairement des particules pré-

<sup>&</sup>lt;sup>5</sup> Corner simulations

sentes dans l'air des salles de production, mais leur quantité est bien maîtrisée, car les fondeurs sont responsables des circuits défectueux présentant des fautes catastrophiques. Le concepteur s'intéresse à leur détection, car leur présence dans un circuit peut poser un problème de fiabilité à long terme. Pour les circuits mixtes, la perte de rendement imputable aux fautes catastrophiques est faible, car elle est fonction de la surface occupée par le système analogique, qui reste bien inférieure à la surface consacrée à la partie numérique [18].

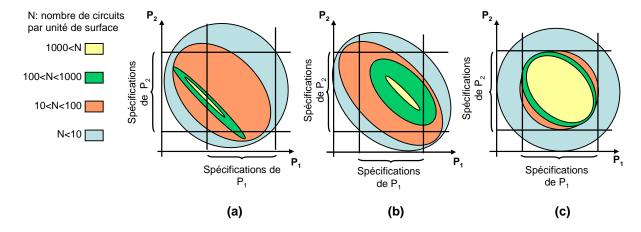

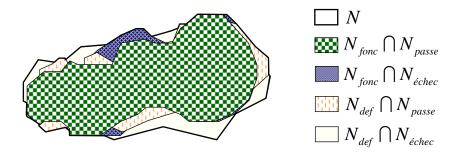

Les variations des paramètres du *process* entraı̂nent des différences entre les performances des circuits produits. Comme tous les circuits doivent respecter les spécifications mentionnées dans le cahier des charges, il est important de limiter la dispersion des performances par rapport aux variations du *process*. Ainsi, la figure 2.5 montre les différentes possibilités qui se présentent pendant la production d'un circuit par rapport à deux de ses performances.

Figure 2.5 – Échantillon de circuits produits (a) à faible rendement, (b) centré et (c) robuste.

Dans le cas (a), le rendement de production sera très faible, car la majorité des circuits ne respecte pas la performance  $P_1$ . Dans le cas (b), le dimensionnement du circuit est centré, car la majorité des circuits se situe au milieu de la zone spécifiée. Le rendement sera meilleur que dans le premier cas, mais la dispersion des performances par rapport aux déviations du *process* est large, ce rendement n'est donc pas optimal. Par contre, le cas (c), avec peu de circuits en dehors de la zone de spécification, représente un échantillon centré et robuste.

#### 2.1.4 Conclusion

Le coût de production d'un circuit intégré se décompose principalement en deux parties : les coûts liés au développement et au temps de mise sur le marché, et les coûts liés à la surface du circuit sur le silicium. À cause de la pression du marché, les faibles délais de développement forcent les ingénieurs à employer une méthode hiérarchique de conception capable de prédire les performances du circuit rapidement. Cette méthode s'appuie sur plusieurs niveaux de description pour accélérer le temps de simulation et élaborer des systèmes de plus en plus complexes. Pour réduire les coûts directs de production, l'optimisation des dimensions du circuit s'effectue, non seulement en vue d'obtenir le meilleur rapport entre la surface du circuit et ses performances, mais aussi, en vue d'optimiser le rendement de production. La prédiction du rendement pendant la phase de conception s'effectue par simulations électriques, qui prennent en compte l'impact des variations des paramètres du process sur les performances du circuit. Mais les temps de simulation des circuits complexes sont incompatibles avec le temps de mise sur le marché. Cette contrainte supplémentaire renforce le besoin de créer des modèles reproduisant le comportement du circuit en fonction non seulement des stimuli externes, mais aussi, en fonction des paramètres de conception. Deux types de modèle sont donc nécessaires : la modélisation analytique, qui exprime la fonctionnalité du circuit et la modélisation statistique pour exprimer l'impact des paramètres du process sur le fonctionnement du circuit.

#### 2.2 Modélisation analytique

Appliquée à la conception de circuits intégrés, la modélisation analytique vise à établir une description du comportement du circuit permettant d'estimer ses performances. Le nouveau modèle permet d'accélérer les temps de simulation et obtenir ainsi les performances du circuit dans un laps de temps raisonnable. Les simplifications apportées limitent l'intervalle de validité du modèle et un compromis s'établit entre la précision de la prédiction et le temps de simulation. Plusieurs niveaux de description sont mis au point pour répondre aux besoins de conception. Ainsi, au niveau le plus élevé, l'intérêt est porté sur la vision globale du circuit et le modèle prend en compte l'environnement de fonctionnement et les connexions et le traitement des informations entre les différents blocs internes. Ensuite, la description est mieux détaillée pour définir l'architecture de chaque bloc. Enfin, les paramètres décrivant le modèle au niveau n servent de contraintes à la conception des blocs du niveau n-1 [19].

#### 2.2.1 Fonction de transfert

Le modèle le plus rudimentaire consiste à considérer le circuit à modéliser comme une boîte noire caractérisée uniquement par des relations entre les entrées et les sorties. Par exemple, la fonction de transfert statique d'un CAN associe un code de sortie à un intervalle de tension en entrée. Dans ce cas, le modèle est dit pseudo-statique, car l'influence du signal d'entrée n'est pas prise en compte dans la description du comportement du CAN. Ce modèle élémentaire s'utilise pour des simulations mettant en jeu des systèmes numériques complets (mémoires, filtres, communications externes, etc.), car l'intérêt est porté sur la chaîne complète du traitement du signal, dont le CAN ne représente qu'une petite partie.

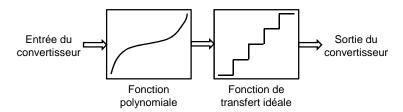

Toutefois, pour un CAN réel, la largeur des pas de quantification varie en fonction du code. Comme il est fastidieux de modifier chaque état de quantification manuellement, la fonction de transfert du CAN est partagée en deux : la composante non-linéaire et la fonction idéale, comme représenté sur la figure 2.6.

**Figure 2.6** – Découpe de la fonction de transfert pseudo-statique d'un CAN représentant les erreurs de linéarité.

Pour obtenir une représentation plus juste, la partie non-linéaire peut être représentée par une fonction mathématique composée de moins de paramètres que d'états de quantification. Par exemple, une fonction polynomiale classique, ou de Chebychev, ou encore une série de Fourier ont été proposées pour estimer le comportement non-linéaire du CAN [20]. Les séries de Volterra permettent de prendre en compte l'effet de mémoire lié aux imperfections du CAN, prépondérant pour des CAN à haute-fréquence [21]. Enfin, cette représentation des erreurs de linéarité s'utilise pour vérifier le fonctionnement d'un CAN pourvu d'un système de calibrage numérique en sortie du CAN [22]. Mais les niveaux donnés par une fonction polynomiale sont fixés pour chaque CAN et aucun bruit n'est ajouté au bruit de quantification.

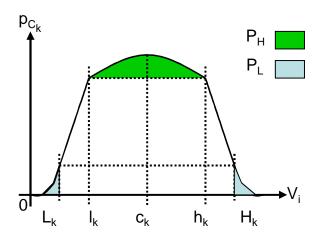

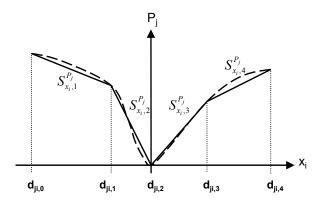

Un moyen de représenter non seulement les erreurs de linéarité de chaque code, mais aussi, d'ajouter un niveau de bruit thermique consiste à considérer l'apparition d'un code en fonction d'une fonction de probabilité dépendante de la tension d'entrée [23]. La figure 2.7 illustre la fonction de densité de probabilité  $P_{C_k}$  d'apparition du code  $C_k$  en fonction de la tension d'entrée  $V_i$ . Cette fonction est définie par une probabilité haute  $P_H$  pour une tension comprise entre  $l_k$  et  $h_k$  et une probabilité basse  $P_L$  pour une tension V en deça de  $L_k$  et au dessus de  $H_k$ . Un tirage aléatoire des

$l_k$ ,  $h_k$ ,  $L_k$  et  $H_k$  permet de définir la fonction statique du CAN. Ensuite, la simulation du modèle consiste à générer, grâce aux densités de probabilité de tous les codes, la valeur du code de sortie en fonction de la valeur de la tension d'entrée. Ainsi, un unique code de sortie n'est pas attribué à une tension d'entrée, mais à une densité de probabilité d'apparition du code en fonction de la tension d'entrée. Cette expression au moyen d'une densité permet de générer un bruit aléatoire équivalent au bruit thermique.

Figure 2.7 – Probabilité d'apparition d'un code  $C_k$  en fonction de la tension d'entrée  $V_i$  du CAN modélisé.

Enfin, le langage de programmation importe pendant la conception du modèle, car il est peu aisé d'effectuer des simulations rapides avec des langages de programmation différents. La plupart des logiciels acceptent plusieurs langages de description, mais les temps de simulation pâtissent de cette augmentation de complexité de description du modèle. Ainsi,  $Barianacki\ et\ al.\ [24]$  modélisent un CAN- $\Sigma\Delta$  uniquement en langage VHDL, un langage réservé aux systèmes numériques. La volonté d'utiliser ce langage de description repose sur l'objectif de valider l'architecture du filtre numérique de décimation. Dans ces travaux, le CAN est décomposé en deux parties distinctes : le modulateur et le filtre numérique. Cette division en sous-blocs facilite la description du modèle.

#### 2.2.2 Modélisation comportementale hiérarchique

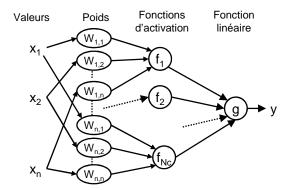

Pour les circuits complexes, la difficulté d'établir la fonction de transfert complète se résout en divisant le circuit en blocs définis par leur fonctionnalité. Ainsi, la modélisation hiérarchique consiste à décomposer le bloc principal en sous-blocs, dont les performances servent de paramètre au bloc principal.

La modélisation par une fonction de transfert ne convient pas à l'approche de conception *Top-Down* si les simulations n'établissent pas la relation entre les performances d'un bloc et celles des sous-blocs le constituant. Avec cette relation, l'espace des performances est exploré pour délimiter les intervalles de validité des paramètres de conception des sous-blocs. Ces intervalles constituent une liste de contraintes pour concevoir à leur tour les sous-blocs.

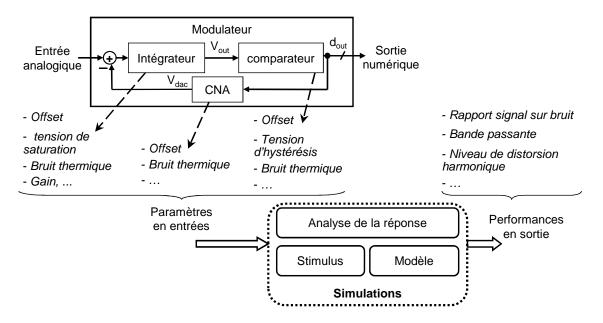

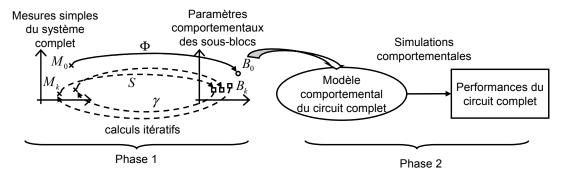

La figure 2.8 donne un exemple de ce type de description d'un CAN- $\Sigma\Delta$ . Le bloc étudié est un modulateur  $\Sigma\Delta$  défini par le rapport signal-sur-bruit. Cette performance dynamique est très surveillée pour ce type de convertisseur. Le modulateur se décompose en trois sous-blocs : l'intégrateur, le comparateur et le CNA. Chaque sous-bloc exprime une fonction entre les entrées et les sorties caractérisée par une ou plusieurs variables de conception à déterminer. Par exemple, l'équation (2.1) donne une description possible du fonctionnement du comparateur :

$$d_{out} = \begin{cases} 1 & \text{si } V_{in} \ge V_{seuil} \\ 0 & \text{sinon,} \end{cases}$$

(2.1)

avec  $d_{out}$ , le niveau logique de sortie du comparateur et  $V_{in}$ , le niveau analogique de l'entrée. La variable  $V_{seuil}$  correspond à la tension de seuil de décision du comparateur. Ses limites se fixent

en effectuant de nombreuses simulations, dont le but est de déterminer à partir de quelle valeur de  $V_{seuil}$  une des performances du bloc modulateur n'est plus respectée. L'intervalle des valeurs de  $V_{seuil}$  respectant les spécifications du modulateur devient une spécification du sous-bloc comparateur.

Cette modélisation commence par le choix des paramètres de conception, mais aucune méthode formelle ne permet de déterminer si les paramètres choisis suffisent pour exprimer toutes les relations nécessaires à la description du fonctionnement du sous-bloc. Le choix se fait de manière intuitive, c'est-à-dire en fonction de l'expérience de la personne en charge de concevoir le bloc. En reprenant l'exemple du comparateur, la description pourrait prendre en compte le délai de réponse, un hystérésis en entrée, ou encore, le niveau de bruit thermique. Si l'impact de ces paramètres de conception sur les performances du bloc complet n'est pas modélisé, les contraintes à imposer à ces paramètres restent indéterminées. La liste de contraintes représente uniquement les limites de paramètres modélisés.

Figure 2.8 – Modélisation comportementale hiérarchique d'un CAN  $\Sigma\Delta$ .

Le développement d'un modèle comportemental ayant en entrée des paramètres de conception a fait l'objet de nombreux travaux qui se classifient en fonction de trois principaux critères : temps de simulation, précision et flexibilité [25]. Il ressort de ces différents moyens de description deux méthodes permettant un bon compromis entre ces trois critères. La première méthode nécessite un effort de modélisation important pour exprimer la relation entrée-sortie directement à partir d'un système d'équations différentielles linéaires. La seconde méthode est intéressante, car elle utilise l'environnement de conception de circuits analogiques basé sur les lois électriques. Enfin, une dernière méthode est présentée, car elle ne requiert pas de déterminer les paramètres comportementaux prépondérants, mais en revanche, manque de flexibilité pour être utilisée pendant la phase de conception.

#### Calcul analytique

La description s'effectue en trouvant une fonction analytique décrivant le comportement entre les quantités physiques des entrées et des sorties du sous-bloc en fonction des paramètres de conception. Ainsi, il devient possible de connecter chaque sous-bloc entre eux pour former un bloc fonctionnel complet. Les quantités physiques sont souvent la tension ou le courant pour des systèmes électriques.

En conservant l'exemple du modulateur  $\Sigma\Delta$ , la quantité physique choisie est la tension électrique. Pour chaque sous-bloc, une fonction analytique exprime la relation entre la tension de sortie et la tension d'entrée en fonction des paramètres de conception. Dans le cas présent, l'effort de modélisation se situe principalement au niveau de l'intégrateur, car c'est un circuit purement ana-

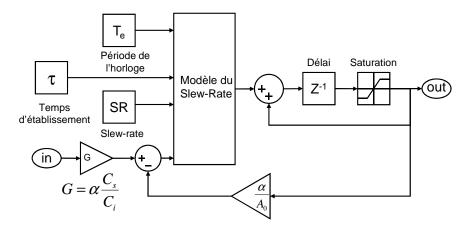

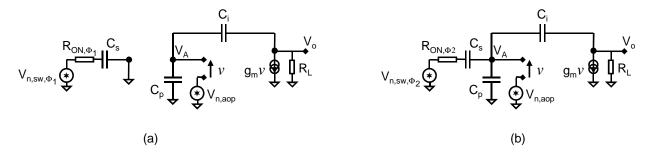

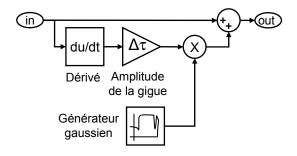

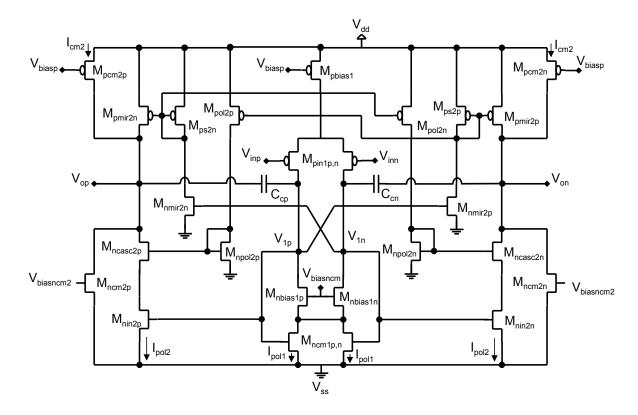

logique. La description se simplifie en s'appuyant sur l'architecture à capacités commutées de cet intégrateur. En effet, dans le cas d'un système à temps discret, le calcul de la tension de sortie à chaque coup d'horloge suffit pour exprimer pleinement son comportement. Ainsi *Malcovati et al.* [25] expriment la tension de sortie de l'intégrateur  $V_{out}(t)$  pour  $0 < t < T_s/2$  par

$$v_{out}(t) = \begin{cases} v_{out}(nT_s - T_s) + \alpha V_s \left(1 - e^{-\frac{t}{\tau}}\right) & \text{si } 0 > t_0 \\ v_{out}(nT_s - T_s) + \alpha V_s \left(1 - e^{-\frac{t-t_0}{\tau}}\right) + \frac{SR}{\omega_t} e^{-\frac{t-t_0}{\tau}} & \text{si } T_s/2 > t_0 \ge 0 \\ v_{out}(nT_s - T_s) + SR \cdot t & \text{si } t_0 \ge T_s/2. \end{cases}$$

(2.2)

$T_s$  correspond à la période d'échantillonnage et  $V_s$ , la tension d'entrée de l'intégrateur. Les paramètres de conception s'expriment au travers des coefficient  $\alpha$ ,  $\tau$  et SR.  $\alpha$  représente la perte de gain de l'intégrateur lié au gain en boucle ouverte fini de l'amplificateur opérationnel,  $\tau$  la bande passante et SR le slew-rate. Enfin, le paramètre  $t_0$  est défini par la relation  $t_0 = \alpha V_s / \text{SR} - \tau$ . Ainsi, les simulations permettent de calculer les performances du modulateur en fonction de trois paramètres de conception de l'AOP et des capacités d'intégration. Les contraintes sur ces paramètres de conception sont établies en trouvant l'intervalle de valeurs conduisant au respect des spécifications.

De la même manière,  $Del\ Rio\ et\ al.\ [26]$  expriment la sortie d'un intégrateur du même type à l'instant d'échantillonnage k en fonction du courant de polarisation  $I_0$  et de la transconductance  $g_m$  de la paire différentielle de l'AOP. Malgré des choix de paramètres de conception différents et une expression analytique différente du comportement de l'intégrateur, les résultats des simulations comportementales présentées montrent une bonne prédiction de l'estimation des performances du modulateur comparées à des mesures effectuées sur un circuit produit. Ces deux exemples illustrent l'absence d'évaluation permettant de quantifier la précision du modèle. La similarité des résultats obtenus par simulation et par les mesures expérimentales est soumise à l'opinion de chacun.

Cette modélisation est très populaire, car en faisant varier les paramètres définis dans les sousblocs, le concepteur analyse facilement leur influence sur les performances du système global [27, 28]. D'autre part, le système complet se construit en connectant des sous-blocs caractérisés par des propriétés intrinsèques. Les performances de différentes architectures et un premier aperçu des contraintes de conception sont obtenus en connectant ces sous-blocs différemment [25]. En plus, il est possible d'ajouter de nouveaux blocs pour étudier l'influence de leurs paramètres comportementaux dans divers domaines d'applications du système global. Ainsi, Fornasari et al. [29] ajoutent le bruit en 1/f<sup>6</sup> au modèle présenté par Malcovati et al. [25]. Ce bruit est dominant dans les systèmes de traitement du signal de faibles fréquences. De la même manière, Zare-Hosni et al. [30] prennent en compte parmi les paramètres de conception, les erreurs de linéarité imputables aux interrupteurs d'échantillonnage situés à l'entrée du modulateur à capacités commutées ou encore la variation du gain en boucle ouverte de l'AOP en fonction de la tension de sortie de l'intégrateur. Enfin, une description mieux détaillée d'un type d'AOP à deux étages réalisée par Ruiz-Amaya et al. [31] remettent en cause la précision des premières descriptions basées sur un modèle d'AOP avec un seul pôle dominant. Une étude reprise par Pugliese et al. [32] concluent sur l'importance de prendre en compte les paramètres supplémentaires de l'AOP pour dimensionner correctement les circuits élémentaires du modulateur. Ces nouvelles études s'ajoutent au flou laissé par les premiers modèles sur la précision obtenue ainsi que la détermination des paramètres comportementaux prépondérants.

Finalement, le développement d'un modèle très détaillé, c'est-à-dire un modèle comportant un nombre important de paramètres de conception de l'étape suivante, permet d'établir une liste de contraintes précise, solide appui pour la conception des étages inférieurs. Par contre, cette augmentation du nombre de paramètres apporte une seule information : l'influence de ces derniers sur les performances du système global. Leur ajout n'implique pas forcément une amélioration de la précision de la description, car aucune étude complémentaire n'a mis en évidence les paramètres prépondérants sur les performances du circuit complet. Tous ces travaux montrent clairement que la limite de la précision du modèle commence par le choix des paramètres comportementaux.

<sup>&</sup>lt;sup>6</sup>flicker noise

#### Macro-modélisation

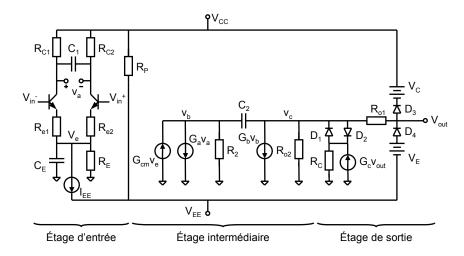

Un macro-modèle décrit le fonctionnement d'un circuit électrique en utilisant uniquement des composants passifs et des sources de courant et de tension commandées. En complément du schéma électrique, le macro-modèle se définit avec des fonctions analytiques qui acceptent en entrée les performances du circuit à modéliser pour fournir en sortie les valeurs correspondantes des paramètres élémentaires. Ainsi, une reproduction fidèle du comportement du modèle est atteinte en comparaison avec le circuit dimensionné. La figure 2.9 représente le macro-modèle d'un AOP, dont les performances permettent de déterminer la valeur de chaque composant élémentaire [33]. Par exemple, le terme  $G_{cm}$  s'exprime en fonction du CMRR  $^7$  de l'amplificateur. Une simulation du schéma électrique permet d'obtenir le CMRR de l'amplificateur puis de calculer le terme  $G_{cm}$ . Tous les paramètres décrivant le macro-modèle sont définis à partir de simulations du schéma électrique.

Figure 2.9 – Macro-modèle d'un AOP.

Le comportement dynamique et les principaux points de polarisation du macro-modèle correspondent au fonctionnement du circuit électrique. Cette correspondance est établie pour un intervalle de valeurs délimité par la zone de fonctionnement linéaire du circuit à modéliser [34]. En dehors de cette zone, les relations entre les points de polarisation et les performances dynamiques du circuit changent, diminuant la précision du modèle. La prise en compte des points de polarisation permet de simuler le macro-modèle directement dans l'environnement électrique en substituant l'entité du circuit original par son macro-modèle. Pendant la phase de vérification visant à comparer les performances du circuit et de son macro-modèle, le banc de simulation n'est pas modifié garantissant que la différence entre les résultats de simulation provient de la modélisation.

Par contre les simulations mixtes, c'est-à-dire des simulations de circuits composés de macro-modèles et de circuits dimensionnés n'apportent pas un gain en temps de simulation aussi important que le gain obtenu par des simulations de modèles comportementaux. Cette contrainte oblige à recourir à un niveau de modélisation plus abstrait pour effectuer des simulations d'un circuit constitué de plusieurs sous-blocs décrits par leur macro-modèle [35].

#### Table de correspondance

Une table de correspondance (LUT  $^8$ ) est une structure de données employée pour remplacer un calcul complexe par une simple opération de consultation. Pour les systèmes à temps discret, une table de correspondance donne la relation entre la sortie du système y, l'entrée u et l'état du circuit d à un instant  $t_{k+1}$ , et la sortie à l'instant précédent  $t_k$

$$y_{t_{k+1}} = F(y_{t_k}, u_{t_{k+1}}, d_{t_{k+1}}). (2.3)$$

<sup>&</sup>lt;sup>7</sup>Common-Mode Rejection Ratio : taux de réjection du mode-commun

<sup>&</sup>lt;sup>8</sup>Look-Up Table

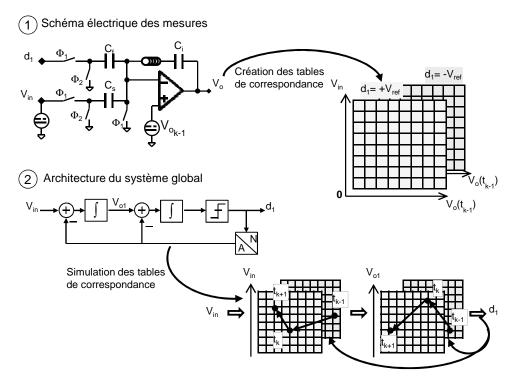

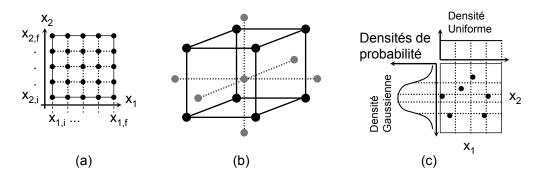

La table de correspondance est obtenue en parcourant l'espace des paramètres d'entrée et en calculant les sorties correspondantes du système à modéliser. Sa création nécessite le recours aux simulations électriques du système, dont la décomposition ne s'effectue plus en considérant les circuits élémentaires, mais correspond à une fonctionnalité plus étendue [36]. Ainsi, la figure 2.10 est un exemple de génération d'une table de correspondance d'un modulateur à capacités commutées. Pour construire la table de référence, il faut établir la valeur de la tension de sortie en fonction des trois entrées. La tension de référence du CAN,  $V_{ref}$ , ne pouvant prendre que deux valeurs différentes, deux tables exprimant la tension de sortie en fonction du signal d'entrée,  $V_{in}$ , et de la tension de sortie de cet étage à l'instant précédent,  $V_{o_{k-1}}$ , sont générées. Ensuite, les tables sont utilisées pendant les simulations temporelles au niveau bloc.

Figure 2.10 - Création et simulation au moyen de tables de correspondance.

L'utilisation d'une table de correspondance permet de s'affranchir de définir toutes les performances des circuits élémentaires ayant une influence prédominante sur le comportement du système. Par contre, la phase d'élaboration est la partie la plus longue et augmente avec la taille du sous-bloc à modéliser. D'ailleurs, l'étape préliminaire de cette phase consiste à trouver le nombre minimal de simulations électriques à effectuer pour remplir la table sans détériorer la précision. Yu et al. [37] proposent un algorithme qui adapte le nombre de simulations électriques à effectuer en fonction de la monotonicité de la sortie du système. Si la sortie varie peu, alors les points sont espacés. Dans le cas contraire, plus de points sont échantillonnés pour obtenir une meilleure représentation de cette portion de l'espace d'entrée du modèle. Lorsque la grille est complète, une fonction d'interpolation quadratique est construite. Le choix d'une fonction quadratique repose sur la continuité de la fonction dérivée aux points d'évaluation. Enfin, la conception du schéma électrique de test s'effectue en respectant les conditions de fonctionnement du système dans son environnement. Dans le cas contraire, la précision du modèle est altérée sans pouvoir quantifier l'erreur commise. Une fois la table de correspondance terminée et les fonctions d'interpolation définies, la simulation du modèle s'effectue simplement par une simple lecture de la table de correspondance en fonction des niveaux des entrées.

Cette méthode présente l'inconvénient majeur de n'être utilisable qu'une fois le circuit complet terminé. En effet, la table de correspondance doit être reconstruite dés la moindre modification du schéma électrique. Par conséquent, leur utilisation est appropriée à la phase de vérification pour accélérer les simulations haut-niveau sans diminuer la précision des résultats par rapport aux

simulations au niveau transistor. Par contre, cette précision n'est garantie que dans une plage de valeurs des paramètres d'entrée. En dehors de cette plage, il est difficile de prévoir le fonctionnement du circuit.

Enfin, la création d'une table de correspondance pendant la phase de vérification s'effectue pour des sous-blocs du circuit. Ainsi, un modèle complet du circuit est obtenu en mélangeant des blocs décrits par des paramètres comportementaux et les tables de correspondance des autres sous-blocs. Par exemple, un convertisseur Flash ne contient que 3 types de blocs analogiques : un réseau de résistances, un réseau d'interrupteurs et des comparateurs. La résistance en circuit fermé des interrupteurs ainsi que le délai nécessaire à la fermeture de l'interrupteur sont calculés pour compléter des tables de correspondance [38]. Ainsi, pendant les simulations du convertisseur complet, l'utilisateur peut évaluer l'influence de la taille des transistors sur le fonctionnement du convertisseur.

#### 2.2.3 Conclusion

La modélisation analytique a pour objectif d'accélérer les temps de simulation nécessaires à la prédiction des performances des circuits virtuels, dont les temps de simulation électrique sont irréels. Indispensable étape dans la conception *Top-Down*, elle permet aussi de guider le concepteur analogique à déterminer les performances de chaque circuit électrique en vue d'effectuer un dimensionnement optimal.

La solution présentant le meilleur rapport précision, temps de simulation et flexibilité repose sur la décomposition hiérarchique du bloc en différents sous-blocs, dont les paramètres sont les performances des circuits électriques élémentaires du système à modéliser. La précision obtenue sur la prédiction comparée à une simulation électrique est difficile à quantifier, car le modèle est simplifiée de manière intuitive et en supposant le fonctionnement du circuit dans une plage limitée. Mais la flexibilité et les temps de simulation de l'ordre d'une poignée de secondes font de ce type de modélisation un excellent outil dans la conception d'un circuit intégré.

Cette étape de modélisation sert à optimiser les performances du système, mais pour estimer la robustesse du circuit en fonction des variations du *process*, il faut recourir à une étude statistique du circuit. Ainsi, dans le paragraphe suivant, nous considérons que le modèle choisi est la meilleure description du système pour nous intéresser non plus à la précision de la prédiction, mais à la précision de la variation de la prédiction en fonction des variations des paramètres du *process*.

#### 2.3 Modélisation Statistique

Contrairement à de la modélisation analytique, dont l'objectif est de construire un modèle explicatif d'un phénomène en exploitant le principe de causalité, un modèle statistique va être construit à partir de données disponibles, sans aucun à priori sur les mécanismes en jeux. Pendant la phase de conception, la modélisation statistique d'un circuit intégré sert à en prédire les performances en fonction des variations du *process*. La précision de la prédiction augmente avec la taille de l'échantillon utilisé pour construire le modèle. Mais cet échantillon est obtenu par simulation, dont la durée s'allonge fortement avec la taille du circuit.

Initialement, l'intérêt du modèle statistique provient de la volonté d'estimer le rendement de production d'un circuit pendant la phase de conception. Mais les bénéfices de la génération rapide d'un échantillon représentatif des conditions de production se sont étendues à d'autres applications comme la conception automatique de circuits analogiques, l'étude de la robustesse ou encore la conception en vue du test que nous développerons dans le prochain chapitre. Les solutions proposées pour générer rapidement un modèle statistique avec une précision en partie par million se regroupent en deux catégories. La première consiste à remplacer les longues simulations par des relations simples entre l'espace initial et l'espace de sortie et la seconde à minimiser la taille de l'échantillon sans réduire la précision du modèle. Au cours de ce paragraphe, nous développons les méthodes les plus courantes répondant à ces deux enjeux comme l'étude de sensibilité, l'introduction d'un modèle

intermédiaire, les fonctions de régression et leur élaboration au moyen de plans d'expérience, ou enfin, l'estimation de la densité de probabilité.

#### 2.3.1 Prédiction de rendement

L'estimation du rendement de production se calcule à partir de la fonction de densité de probabilité conjointe p des paramètres du process. Soit n, le nombre de paramètres initiaux, et  $A \subset \mathbb{R}^n$ , l'ensemble des vecteurs  $x \in \mathbb{R}^n$  de paramètres technologiques pour lesquels le circuit respecte toutes les spécifications. Soit z, la fonction définie par

$$z(x) = \begin{cases} 1 & \text{si } x \in A \\ 0 & \text{sinon.} \end{cases}$$

(2.4)

Alors, le rendement  $Y^9$  s'exprime par

$$Y = \int_{\mathbb{R}^n} z(x)p(x)dx. \tag{2.5}$$

La fonction de densité de probabilité p est définie pendant la caractérisation du process, qui a lieu avant la phase de conception d'un produit et reste périodiquement mise à jour. Le calcul de Y s'effectue couramment avec une précision en partie par million (ppm).

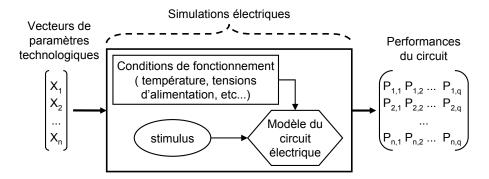

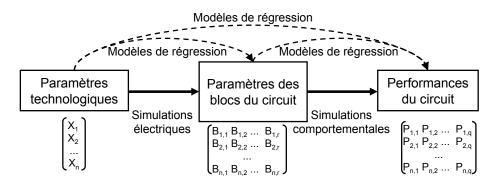

Par contre, les fonctions z et intégrale sont à déterminer. En première approche, la fonction z est remplacée par des simulations électriques comprenant le schéma et les conditions de fonctionnement du circuit ainsi que les différents stimuli de test comme illustré sur la figure 2.11. Chaque simulation accepte en entrée un vecteur de paramètres technologiques et délivre en sortie les performances correspondantes.

Figure 2.11 – Établissement d'une relation entre l'espace des paramètres du process et les performances du circuit par des simulations électriques.

La fonction intégrale est estimée en échantillonnant les vecteurs des paramètres technologiques par la méthode Monte Carlo [5]. Cette méthode vise à calculer une valeur numérique en utilisant des procédés aléatoires, principalement pour estimer des surfaces. Pour appliquer cette méthode, les densités de probabilité des paramètres technologiques sont échantillonnées aléatoirement donnant une population non biaisée. Pour chaque vecteur, une simulation électrique est effectuée en vue de calculer la valeur de la performance correspondante. Si cette valeur appartient à l'intervalle définie dans les spécifications, le circuit est considéré sain autrement il est défectueux. Le rendement s'établit en évaluant le rapport entre le nombre de circuits sains et le nombre de circuits synthétisés. La fonction intégrale continue est remplacée par la somme des circuits synthétisés et l'estimation du rendement  $\hat{Y}$  se calcule grâce à l'équation suivante,

$$\hat{Y} = \frac{1}{N} \sum_{i=1}^{N} z(x_i), \tag{2.6}$$

<sup>&</sup>lt;sup>9</sup>Yield

avec N, le nombre de vecteurs des paramètres du process. L'erreur entre la valeur de rendement estimé  $\hat{Y}$  et Y est bornée par l'inégalité de Chebytchev,

$$P\left\{ \left| \hat{Y} - Y \right| < \epsilon \right\} \ge 1 - \frac{1}{4N\epsilon^2}.\tag{2.7}$$

En conséquence, le nombre de simulations doit être quadruplé pour seulement doubler la précision de l'estimation. En pratique, la durée des simulations électriques est trop importante pour estimer le rendement en partie par million et le recours aux simulations Monte Carlo a pour objectif d'évaluer grâce à quelques échantillons la robustesse du circuit. L'estimation du rendement pour des circuits mixtes complexes s'avère impossible en utilisant de simples simulations électriques, car l'évaluation de leurs performances nécessite des temps de simulation bien supérieurs à la période dédiée à la conception du circuit. Le franchissement de cette barrière est atteint en appliquant des techniques élaborées de modélisation statistique pour remplacer la fonction z et le calcul de l'intégrale.

#### 2.3.2 Analyse de sensibilité

L'analyse de sensibilité étudie comment des perturbations sur les entrées du modèle engendrent des perturbations sur la réponse. Il est possible de grouper les méthodes d'analyse de sensibilité en trois classes : les méthodes de screening, l'analyse de sensibilité globale et l'analyse de sensibilité locale

Les méthodes de screening permettent d'établir par une analyse qualitative une hiérarchie au sein des variables d'entrée en fonction de leur influence sur la variabilité de la réponse. L'analyse de sensibilité globale étudie comment la variabilité des entrées se répercute sur la variabilité de la sortie en déterminant quelle part de variance de la sortie est due à telle entrée ou à tel ensemble d'entrées. Enfin, l'analyse de sensibilité locale étudie comment de petites perturbations des variables d'entrée autour d'une valeur nominale  $X_0 = (x_{0_1}, ..., x_{0_p})$  se répercutent sur la valeur de la sortie  $P = (P_0, ..., P_q)$ .

La méthode d'analyse locale la plus classique est l'approche  $\mathrm{OAT}^{10},$  qui consiste à calculer ou estimer les indices de sensibilité S définis par

$$S_{x_i}^{P_j} = \frac{x_i}{P_j} \frac{\delta P_j}{\delta x_i} |_{\delta x_i \to 0}, \tag{2.8}$$

avec  $P_j$ , le  $j^{me}$  paramètre de sortie et  $x_i$ , la variable d'entrée. Sous sa forme la plus simple, sa mise en oeuvre requiert l'utilisation d'une fonction analytique F connue exprimant la relation

$$(P_0, ..., P_q) = F(x_1, ..., x_p),$$

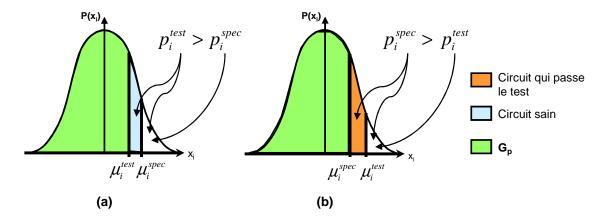

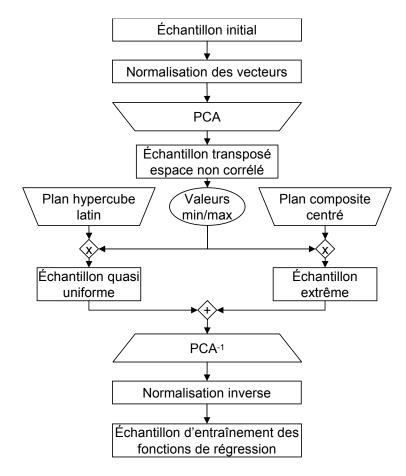

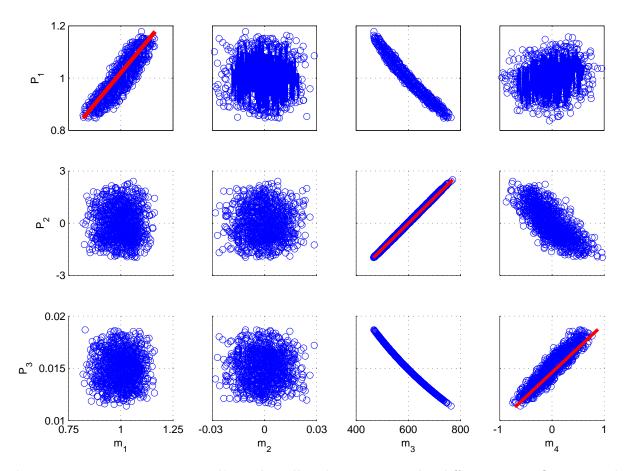

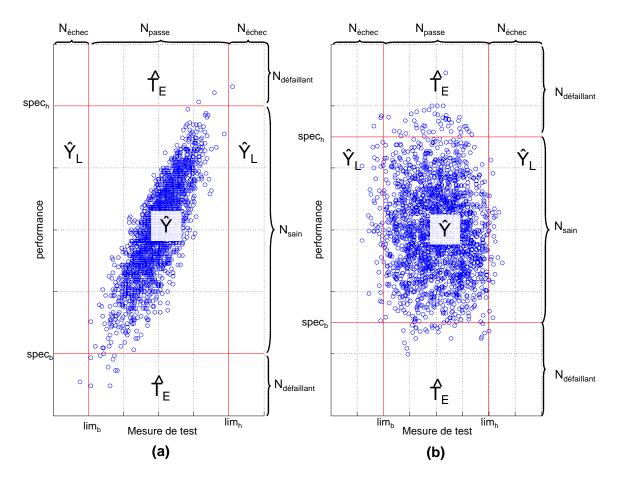

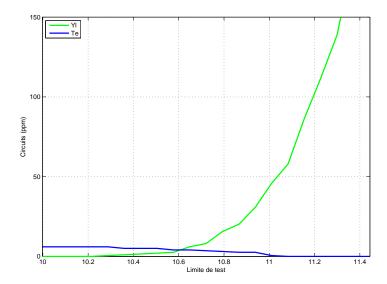

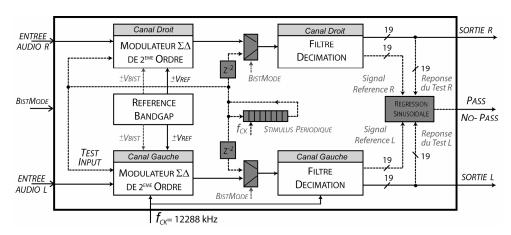

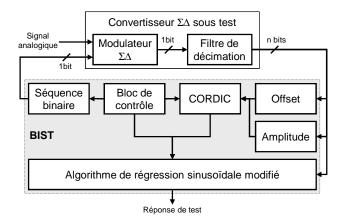

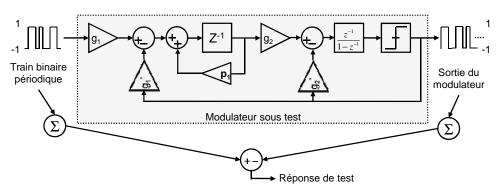

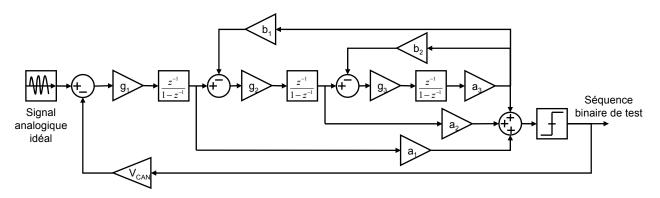

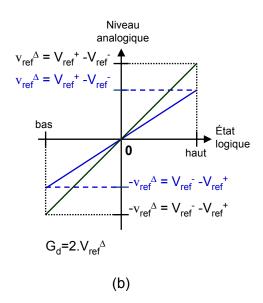

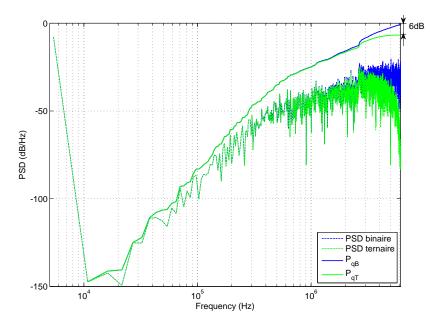

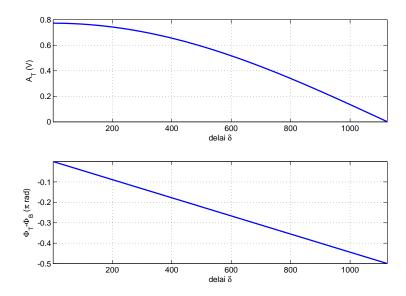

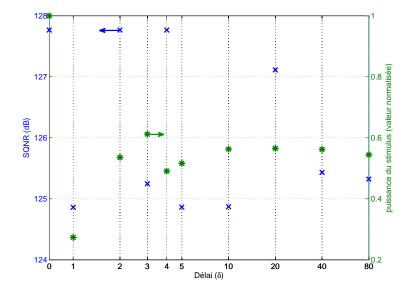

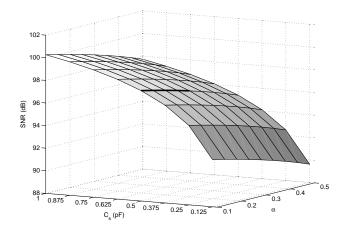

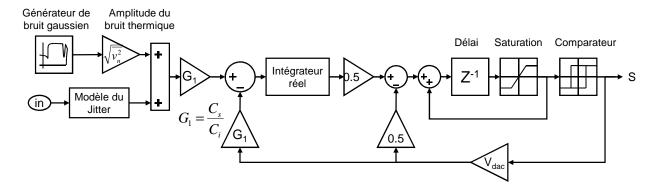

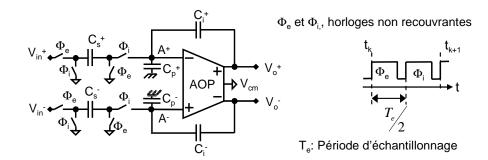

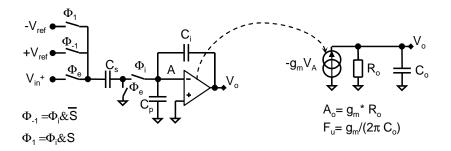

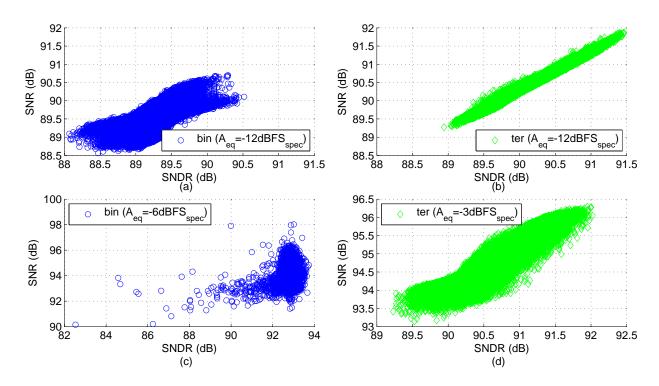

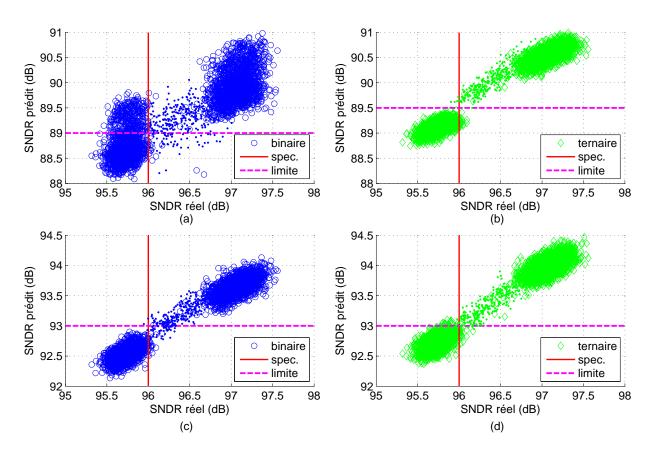

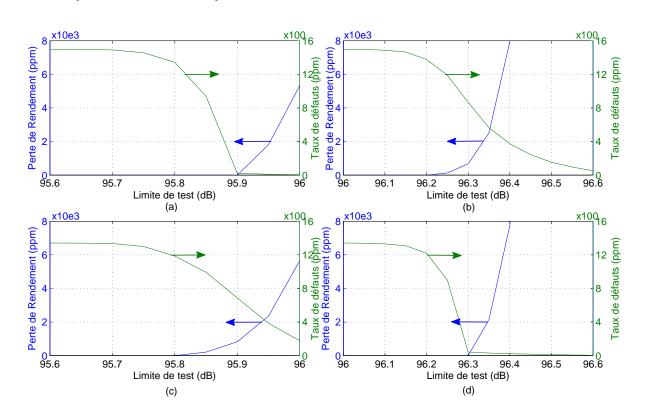

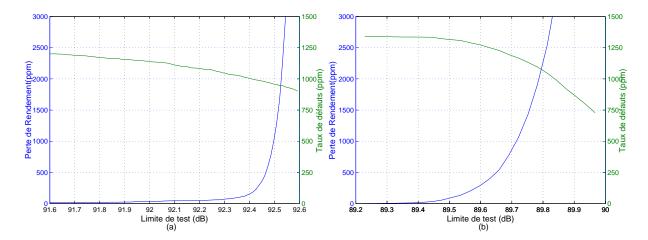

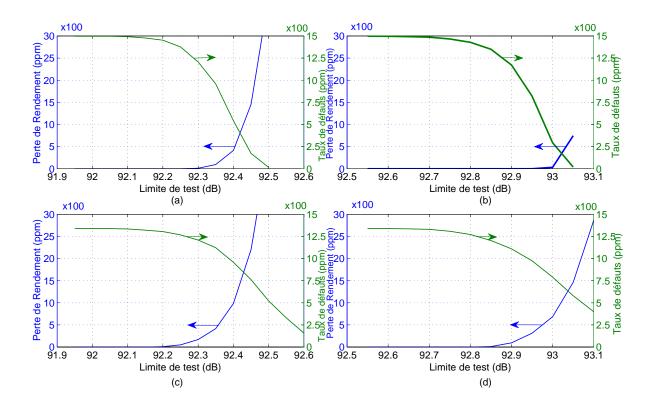

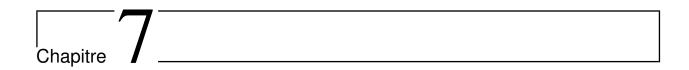

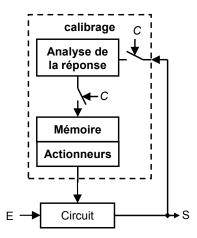

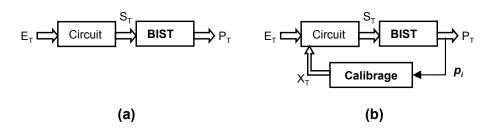

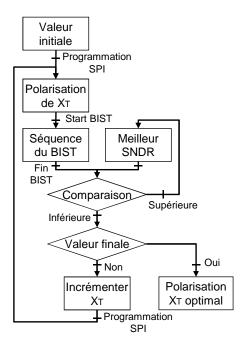

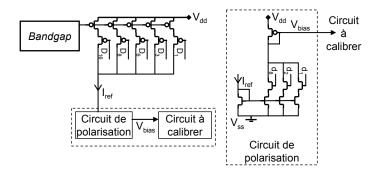

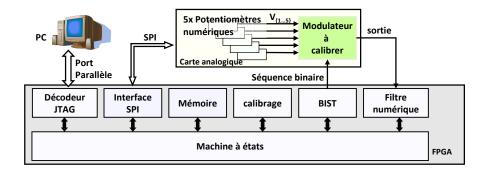

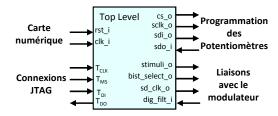

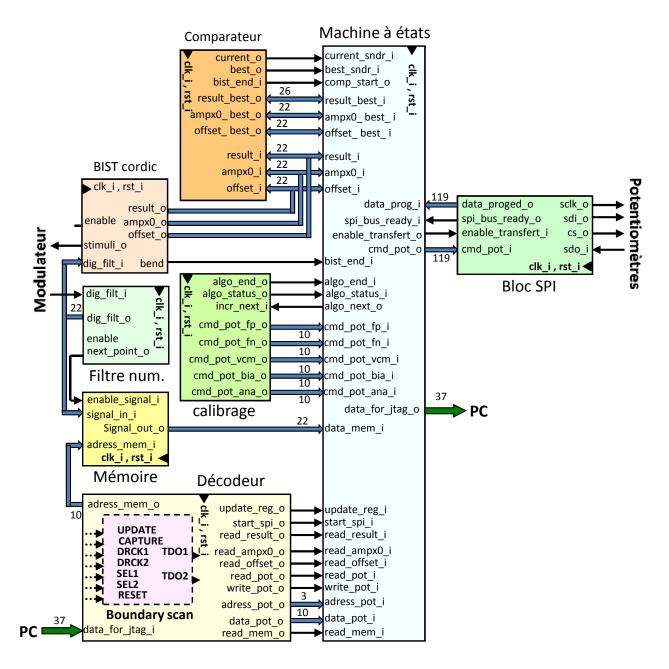

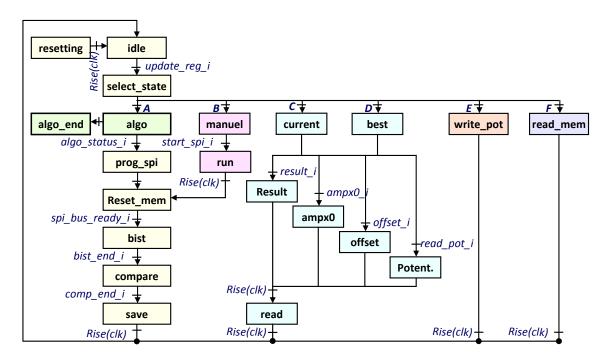

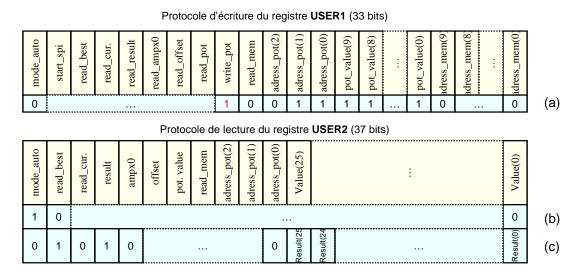

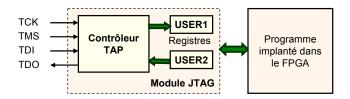

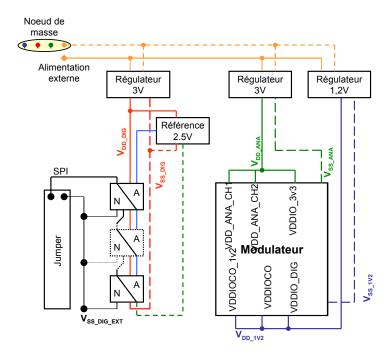

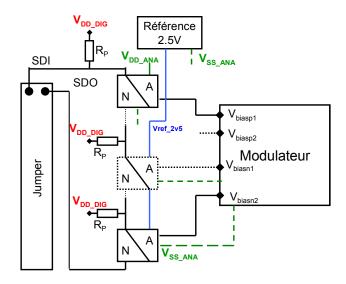

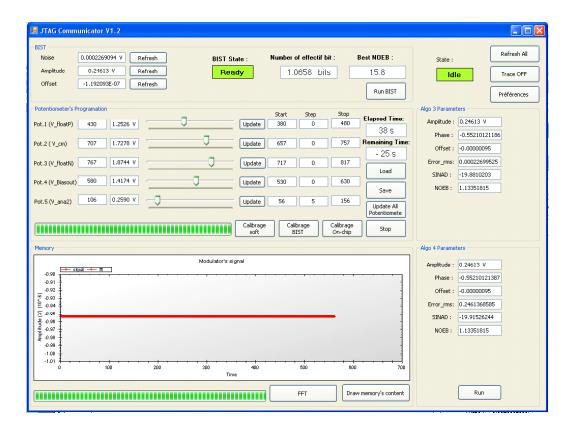

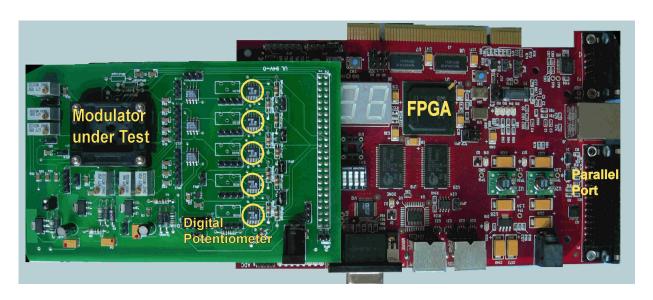

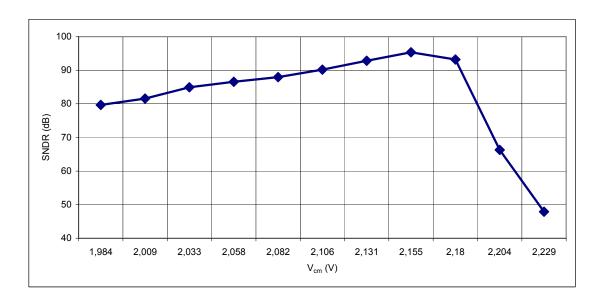

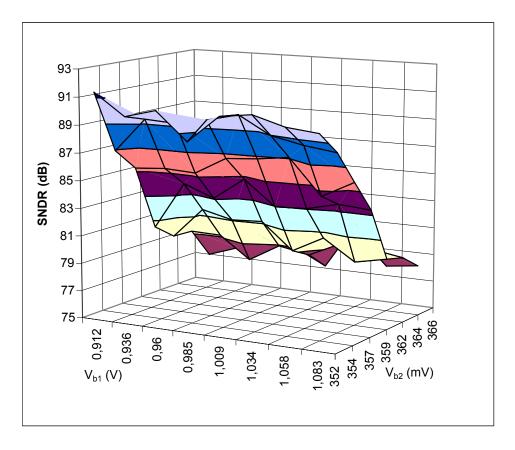

(2.9)