## Exécution sécurisée de code sur systèmes embarqués Daniele Perito

### ► To cite this version:

Daniele Perito. Exécution sécurisée de code sur systèmes embarqués. Autre [cs.OH]. Université de Grenoble, 2011. Français. NNT: 2011GRENM045. tel-00639053

## HAL Id: tel-00639053 https://theses.hal.science/tel-00639053v1

Submitted on 8 Nov 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ DE GRENOBLE

## THÈSE

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Informatique

Arrêté ministérial : 7/08/2006

Présentée par

### **Daniele Perito**

Thèse dirigée par Claude Castelluccia

préparée au sein INRIA et de Université de Grenoble

## Garanties d'exécution de code sur systèmes embarqué - Trustworthy Code Execution on Embedded Devices

Thèse soutenue publiquement le **13/10/2011**, devant le jury composé de :

Pr. Andrzej Duda

Grenoble INP-Ensimag, Président

Pr. Peter Langendoerfer

IHP, Rapporteur

Pr. Refik Molva

Eurecom, Rapporteur

Pr. Srdjan Capkun

ETH, Examinateur

Pr. Ahmad-Reza Sadeghi

TU-Darmstadt, Examinateur

Dr. Claude Castelluccia

INRIA, Directeur de thèse

## Abstract

Embedded devices are currently used in many critical systems, ranging from automotive to medical devices and industrial control systems. Most of the research on such devices has focused on improving their reliability against unintentional failures, while fewer efforts have been spent to prevent intentional and malicious attacks. These devices are increasingly being connected via wireless and connected to the Internet for remote administration, this increases the risk of remote exploits and malicious code injected in such devices. Failures in such devices might cause physical damage and health and safety risks. Therefore, protecting embedded devices from attacks is of the utmost importance.

In this thesis we present novel attacks and defenses against low-end embedded devices. We present several attacks against software-based attestation techniques proposed for embedded devices. Furthermore we design and implement a novel software-based attestation technique that is immune to the aforementioned attacks. Finally, we design a hardware solution to attest and establish a dynamic root of trust on embedded devices, this solution is proven secure and does not rely on the strong assumptions used for software attestation.

### Résumé

Les systèmes embarqués sont utilisés dans de nombreux systèmes critiques, des les automobiles jusqu'aux les systèmes de contrôle industriels. La plupart des recherches sur ces systèmes embarqués se sont concentrés sur l'amélioration de leur fiabilité face à des fautes ou erreurs de fonctionnement non intentionnelles, moins de travaux on été réalisés considérant les attaques intentionnelles. Ces systèmes embarqués sont de plus en plus connectés, souvent à Internet, via des réseaux sans fils, par exemple pour leur administration à distance. Cela augmente les risques d'attaques à distance ou d'injection de code malicieux. Les fautes de fonctionnement de ces équipements peuvent causer des dommages physiques comme par example rendre des appareils médicaux defectueux. Par conséquent, il est primordial de protéger ces systèmes embarqués contre les attaques.

Dans cette thèse nous présentons des attaques et défenses contre les systèmes embarqués contraints. Nous présentons plusieurs attaques contre des techniques d'attestation logicielle utilisées dans les systèmes embarqués. Puis nous présentons la conception et l'implémentation d'une technique d'attestation logicielle qui est résistante aux attaque présentées précédemment. Finalement, nous présentons la conception d'une solution permettant de réaliser l'attestation de code ainsi que la création d'une racine de confiance dynamique (dynamic root of trust) pour les systèmes embarqués. La sécurité de cette solution est prouvée, et ne repose pas sur des hypothèses fortes, comme dans le cas des solutions d'attestation logicielle.

## Acknowledgments

First and foremost I would like to thank my family for their immense and unconditional support. It was a long journey that took me far from home, but they always supported me.

Second, I would like to thank my advisor Claude Castelluccia as I could not have hoped for a better mentor. Claude helped me focus my research efforts, but also left me a great deal of freedom that allowed me to pursue my ideas and travel and collaborate with other teams. Also, I would like to thank Professor Gene Tsudik for his tremendous support. I would like to thank all the members of the Planete team, and especially Aurélien Francillon, for the great discussions we had and the work we have done together. I would also like to thank Helen Pouchot that helped me so much in the organization of my travels and journeys.

Finally, I would like to thank the reviewers of the thesis for their helpful comments and suggestions.

### Published work during the PhD

### **International Conferences**

- [DFPT12] Karim El Defrawy, Aurélien Francillon, Daniele Perito and Gene Tsudik. *SMART: Secure and Minimal Architecture for (Establishing Dynamic) Root of Trust.* Network & Distributed System Security Symposium, NDSS 2012.

- [CDP12] Claude Castelluccia, Markus Duermuth, Daniele Perito. Adaptive Password-Strength Meters from Markov Models. Network & Distributed System Security Symposium, NDSS 2012.

- [PCKM11] Daniele Perito, Claude Castelluccia, Mohamed Ali Kaafar, Pere Manils. *How Unique and Traceable are Usernames?*. Proceedings of the Privacy Enhancing Technology Symposium, PETS 2011.

- [BBP<sup>+</sup>11] Elie Burzstein, Romain Beauxis, Hristo Paskov, Daniele Perito, Celine Fabry, John Mitchell. The Failure of Noise-Based Non-Continuous Audio Captchas. Proceedings of the 32nd IEEE Symposium on Security and Privacy, S&P 2011.

- [PT10] Daniele Perito and Gene Tsudik. Secure Code Update for Embedded Devices via Proofs of Secure Erasure. Proceedings of the European Symposium on Research in Computer Security, ESORICS 2010.

- [CCP10] Claude Castelluccia, Emiliano De Cristofaro, Daniele Perito. Private Information Disclosure from Web Searches Proceedings of the Privacy Enhancing Technology Symposium, PETS 2010.

- [CFPS09b] Claude Castelluccia, Aurélien Francillon, Daniele Perito and Claudio Soriente. On the Difficulty of Software-Based Attestation of Embedded Devices. Proceedings of the 16th ACM conference on Computer and Communications Security, CCS 2009.

- [CKMP09] Claude Castelluccia, Mohamed Ali Kaafar, Pere Manils, Daniele Perito. Geolocalization of Proxied Services and its Application to Fast-Flux Hidden Servers. Proceedings of the ACM Internet Measurement Conference, IMC 2009.

- [CFPS09a] Aurélien Francillon, Daniele Perito, Claude Castelluccia. Defending Embedded Systems Against Control Flow Attacks. In ACM Conference on Computer and Communications Security, Workshop on Virtual Machine Security, 2009.

## Contents

|          | Ack                              | nowledgments                                                                                                                                                                                                                                                                         | Ĺ        |

|----------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1        | <b>Intr</b><br>1.1<br>1.2<br>1.3 | coduction1Context of This Work21.1.1Low-end Embedded Devices21.1.2Cyber-Physical Systems31.1.3Critical Infrastructure41.1.4Embedded Systems Security4Problem Statement51.2.1Code Injection Attacks61.2.2Attacks Against the Integrity and Confidentiality of the Data7Contributions8 | 22344557 |

| <b>2</b> | Pro                              | tecting Embedded Devices against Remote Attacks 11                                                                                                                                                                                                                                   | 1        |

| 4        | 2.1                              | State of The Art                                                                                                                                                                                                                                                                     |          |

|          | 2.1                              | 2.1.1    Control Flow Exploitation    12                                                                                                                                                                                                                                             |          |

|          |                                  | 2.1.2 Control Flow Protection                                                                                                                                                                                                                                                        |          |

|          | 2.2                              | Instruction Based Memory Access Control for Control Flow Integrity 17                                                                                                                                                                                                                |          |

|          |                                  | 2.2.1 Overview of our solution                                                                                                                                                                                                                                                       |          |

|          |                                  | 2.2.2 A separate return stack                                                                                                                                                                                                                                                        |          |

|          |                                  | 2.2.3 Instruction Based Memory Access Control                                                                                                                                                                                                                                        | )        |

|          |                                  | 2.2.4 Other design considerations                                                                                                                                                                                                                                                    |          |

|          | 2.3                              | Implementation                                                                                                                                                                                                                                                                       | L        |

|          |                                  | 2.3.1 Implementation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 21$                                                                                                                                                                                      | L        |

|          |                                  | 2.3.2 Evaluation $\ldots \ldots 25$                                                                                                                                                                                   | j        |

|          | 2.4                              | Considerations                                                                                                                                                                                                                                                                       | )        |

| 3        | Det                              | ecting Compromised Embedded Devices via Software Attes-                                                                                                                                                                                                                              |          |

|          | tati                             |                                                                                                                                                                                                                                                                                      | )        |

|          | 3.1                              | State of the Art                                                                                                                                                                                                                                                                     | )        |

|          |                                  | 3.1.1 Software Attestation                                                                                                                                                                                                                                                           | L        |

|          | 3.2                              | Attacks on Existing Software-based Attestation Schemes 34                                                                                                                                                                                                                            | Ł        |

|          |                                  | 3.2.1 Generic Challenge-response protocol                                                                                                                                                                                                                                            |          |

|          |                                  | 3.2.2 Adversary model                                                                                                                                                                                                                                                                | Ł        |

|          |                                  |                                                                                                                                                                                                                                                                                      |          |

|   |            | 3.2.3  | Two generic attacks on code attestation protocols                                                   | 35         |

|---|------------|--------|-----------------------------------------------------------------------------------------------------|------------|

|   |            | 3.2.4  | On the difficulty of designing secure time-based attestation                                        |            |

|   |            |        | protocols                                                                                           | 40         |

|   |            | 3.2.5  | ICE-based attestation schemes                                                                       | 45         |

|   |            | 3.2.6  | Considerations                                                                                      | 47         |

|   | 3.3        | Impro  | ving Software Attestation via Proof of Secure Erasure                                               | 48         |

|   |            | 3.3.1  | Assumptions                                                                                         | 48         |

|   |            | 3.3.2  | Design Rationale                                                                                    | 50         |

|   |            | 3.3.3  | Secure Code Update                                                                                  | 50         |

|   |            | 3.3.4  | Efficient Proof of Secure Erasure                                                                   | 52         |

|   |            | 3.3.5  | Implementation and Performance                                                                      | 55         |

|   |            | 3.3.6  | Limitations and Challenges                                                                          | 58         |

|   |            | 3.3.7  | Considerations                                                                                      | 59         |

|   |            |        |                                                                                                     |            |

| 4 | Sec        | ure At | testation and Dynamic Root of Trust with Minimal                                                    |            |

|   | Har        | dware  | Support                                                                                             | 61         |

|   | 4.1        | State  | of the Art                                                                                          | 63         |

|   |            | 4.1.1  | Hardware attestation                                                                                | 63         |

|   |            | 4.1.2  | Dynamic Root of Trust                                                                               | 64         |

|   | 4.2        | Desigr | n Elements and Goals                                                                                | 65         |

|   | 4.3        | Overv  | iew of the Solution                                                                                 | 65         |

|   |            | 4.3.1  | Building Blocks                                                                                     | 65         |

|   |            | 4.3.2  | Adversarial Assumptions                                                                             | 67         |

|   |            | 4.3.3  | Security Objectives                                                                                 | 68         |

|   | 4.4        | SMAR   | T in Detail                                                                                         | 68         |

|   |            | 4.4.1  | Attestation ROM                                                                                     | 70         |

|   |            | 4.4.2  | MCU Modifications                                                                                   | 71         |

|   | 4.5        | Securi | ty Analysis                                                                                         | 73         |

|   | 4.6        | Protoc | cols with SMART                                                                                     | 75         |

|   |            | 4.6.1  | Remote Attestation of Memory Parts                                                                  | 75         |

|   |            | 4.6.2  | Remote Proof of Reset                                                                               | 76         |

|   |            | 4.6.3  | Attested Reading of Measurements                                                                    | 76         |

|   |            | 4.6.4  | Other Uses and Extensions                                                                           | 77         |

|   | 4.7        | Implei | mentation $\ldots$ | 78         |

|   |            | 4.7.1  | Implementation details                                                                              | 79         |

|   |            | 4.7.2  | Lessons Learned from Experiments                                                                    | 82         |

|   | 4.8        | Discus | ssion                                                                                               | 84         |

| 5 | Com        | alusia | n and Future Directions                                                                             | 85         |

| J |            |        | tives                                                                                               | <b>8</b> 5 |

|   | 5.1<br>5.2 | v      |                                                                                                     | 85<br>86   |

|   | 5.2        |        | E Directions                                                                                        | 80<br>86   |

|   |            | 5.2.1  | Extensions to our Work                                                                              |            |

|   |            | 5.2.2  | Future Applications                                                                                 | 87         |

# List of Figures

| 2.1          | Common stack layout                                                                                                            | 13       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.2          | Traditional stack layout                                                                                                       | 18       |

| 2.3          | IBMAC stack layout. The Base control flow stack pointer is the                                                                 | 10       |

| 2.4          | only register that needs to be initialized in order to support IBMAC.                                                          | 19       |

| 2.4          | Stack configurations and Control flow stack pointer description and                                                            | 01       |

| 9 F          | additional locking logic                                                                                                       | 21<br>24 |

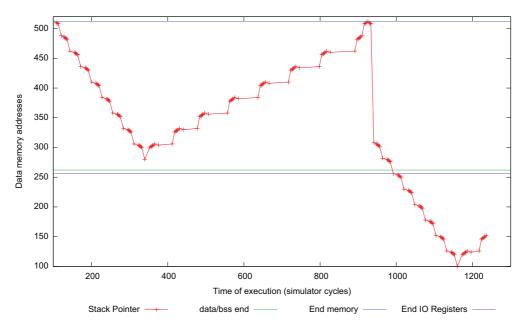

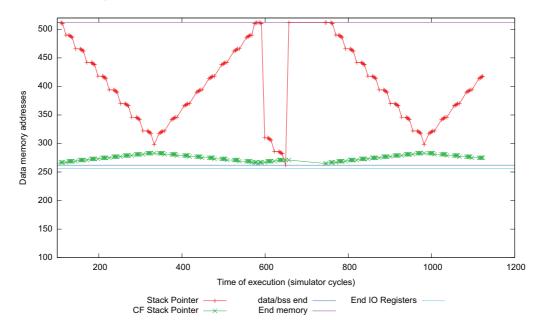

| $2.5 \\ 2.6$ | Example of a program that causes the stack to overflow Comparison of the data memory layout during the execution of the        | 24       |

| 2.0          | program of figure 2.5. In order to keep the example simple we ran                                                              |          |

|              | the simulation with only 512 bytes of data memory address space.                                                               | 26       |

|              | the simulation with only 512 bytes of data memory address space.                                                               | 20       |

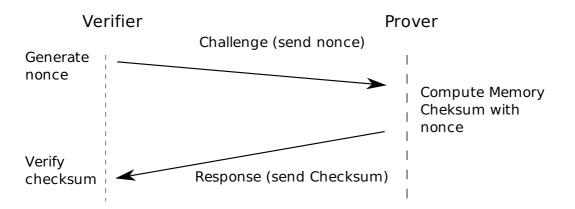

| 3.1          | Basic attestation challenge response protocol                                                                                  | 31       |

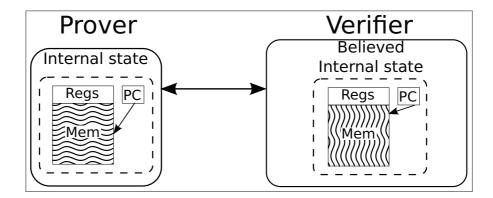

| 3.2          | Generic remote attestation.                                                                                                    | 32       |

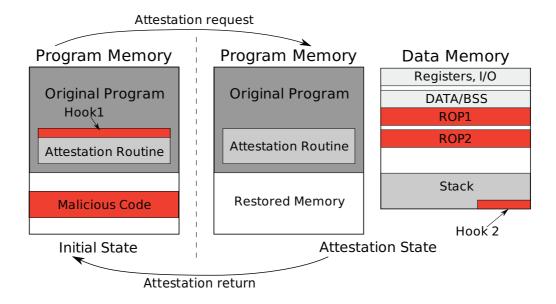

| 3.3          | Return-Oriented Programming attack.                                                                                            | 36       |

| 3.4          | Example of attestation function                                                                                                | 37       |

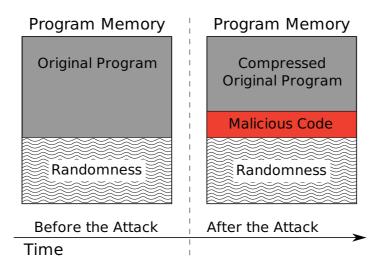

| 3.5          | Compression Attack.                                                                                                            | 38       |

| 3.6          | Outline of the memory shadowing attack, with inserted instructions                                                             |          |

|              | and translated addresses.                                                                                                      | 41       |

| 3.7          | Timing of different attacks. The timings collected on SWATT with 128 KBytes were performed with the same number of cycles that |          |

|              | the original SWATT. On 128 KBytes the number of SWATT cycles                                                                   |          |

|              | should be increased, according to the <i>Coupon's Collector Problem</i> ;                                                      |          |

|              | we have not done it in order to have easily comparable values                                                                  | 42       |

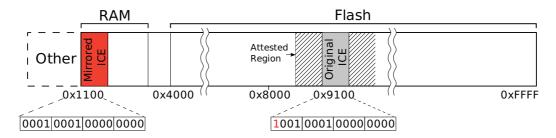

| 3.8          | While the legitimate ICE routine is stored at address 0x9100, a                                                                |          |

|              | malicious copy of the routine is stored at address 0x1100. These                                                               |          |

|              | two addresses differ only in their most significant bit allowing the                                                           |          |

|              | attacker to run the malicious copy of ICE and still pass attestation.                                                          | 46       |

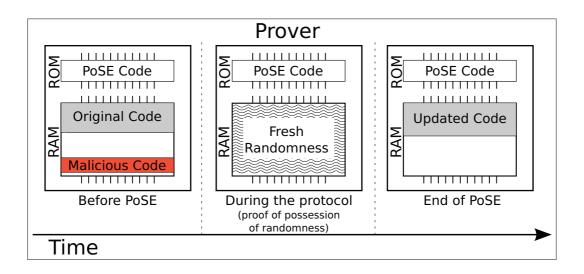

| 3.9          | Prover's Memory during Protocol Execution                                                                                      | 51       |

| 3.10         | Base Case Protocol                                                                                                             | 51       |

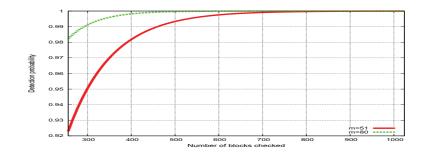

| 3.11         | Probability of detecting memory modifications for $\#$ of checked                                                              |          |

|              | blocks varying between 256 (5%) and 1024 (20%) $\ldots \ldots \ldots$                                                          | 54       |

| 3.12         | Optimized Protocol                                                                                                             | 54       |

| 4.1          | Protocol description                                                                                                           | 70       |

|              |                                                                                                                                |          |

| 4.2 | Annotated HMAC invocation in SMART. Note the use of COUNT              |    |

|-----|------------------------------------------------------------------------|----|

|     | annotation for pointers. It specifies the maximum size of buffers      |    |

|     | used                                                                   | 71 |

| 4.3 | Schematic view of access control for attestation key                   | 72 |

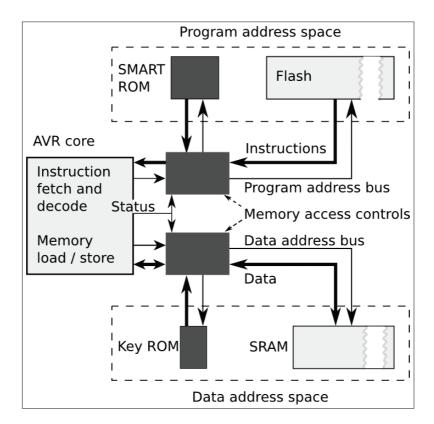

| 4.4 | Modifications to AVR. Dark gray boxes represent logic added to the     |    |

|     | processor. Core control signals provide information about internal     |    |

|     | processor status to memory bus controls                                | 80 |

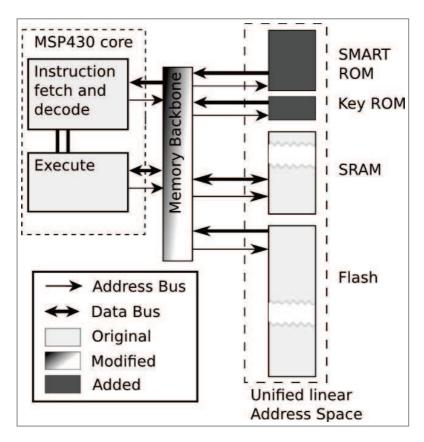

| 4.5 | Modifications to MSP430. Memory backbone was modified to               |    |

|     | control access to ROM and $\mathcal{K}$ . Since MSP430 is based on Von |    |

|     | Neumann architecture, concurrent access can occur to different         |    |

|     | memory parts (e.g., instruction fetch and read data). In that          |    |

|     | case, memory backbone arbitrates bus access and temporarily            |    |

|     | saves/restores data.                                                   | 81 |

|     |                                                                        |    |

## List of Tables

| 3.1 | Compression results for Micaz applications (similar results where |    |

|-----|-------------------------------------------------------------------|----|

|     | found for TelosB applications).                                   | 40 |

| 3.2 | Compression Attack, using Canonical Huffman encoding              | 40 |

| 3.3 | Notation Summary.                                                 | 49 |

| 3.4 | MAC constructions on MicaZ                                        | 56 |

| 3.5 | Code and volatile memory size                                     | 57 |

| 4.1 | HMAC execution timing                                             | 82 |

| 4.2 | Changes made (in $\#$ of HDL lines of code) in AVR and MSP430     |    |

|     | processors, respectively, excluding comments and blank lines      | 83 |

| 4.3 | Comparison of chip surface used by each component of the original |    |

|     | MCU to its modified version. kGE stands for thousands of Gate     |    |

|     | Equivalents (GE-s). One GE is proportional to the surface of the  |    |

|     | chip and computed form the surface of the module divided by the   |    |

|     | surface of a NAND2 gate, $9,37 * 10^{-6} mm^2$ with this library  | 83 |

|     |                                                                   |    |

# Chapter 1

## Introduction

### Contents

| 1.1 Con | text of This Work                                        | <b>2</b> |

|---------|----------------------------------------------------------|----------|

| 1.1.1   | Low-end Embedded Devices                                 | 2        |

| 1.1.2   | Cyber-Physical Systems                                   | 3        |

| 1.1.3   | Critical Infrastructure                                  | 4        |

| 1.1.4   | Embedded Systems Security                                | 4        |

| 1.2 Pro | blem Statement                                           | 5        |

| 1.2.1   | Code Injection Attacks                                   | 6        |

| 1.2.2   | Attacks Against the Integrity and Confidentiality of the |          |

|         | Data                                                     | 7        |

| 1.3 Con | $\operatorname{tributions}$                              | 8        |

Embedded systems are encountered in many settings, ranging from mundane to critical. In particular, sensor and actuator networks are used to control industrial systems as well as various utility distribution networks, such as electric power, water and fuel. They are also widely utilized in automotive, railroad and other transportation systems. Furthermore they are widely used to control implanted medical devices, such as pacemakers. In such environments, it is often imperative to verify the internal state of an embedded device to assure lack of spurious, malicious or simply residual code and/or data. It is also imperative to prevent remote exploitation when security vulnerabilities (e.g., due to coding mistakes) are present in the code.

In the past, embedded devices used in critical applications were rarely inter connected to the outside world or to other devices, hence they benefited from a blanket protection against remote intrusion. However, in the last few years the increased adoption of open wireless communications for these devices has augmented the risk of remote exploits for such devices. When embedded devices are used in safety critical applications, software faults caused by malicious activity can have dire real-world consequences. Notably, the recent Stuxnet worm [FMC11] demonstrated the magnitude of damage that could stem from attacks to embedded devices. Stuxnet infected Programmable Logic Controllers (PLC) used in industrial control systems for nuclear reactors. By doing so, it altered the operational parameters of the uranium enrichment centrifuges of one nuclear plant located in Iran, causing permanent damage to the centrifuges. Embedded devices are also used in automotive control systems. Recently, such systems have been shown vulnerable to a variety of attacks [KK10], including malicious re-flashing of in-car electronic safety systems. Protecting such devices from exploitation is still an open research challenge. Another possible application domain is direct recording electronic (DRE) voting machines, that have been shown vulnerable to return-oriented programming attacks in [CFK<sup>+</sup>09] and other forms of manipulation of the ballot reporting [WWH<sup>+</sup>10]. These machines are equipped with embedded devices similar to those targeted by our work.

These facts make embedded devices security an important challenge. We believe that, while examples of real life attacks are still limited, it is vital to design and deploy the correct security solutions in a proactive rather than reactive way.

### 1.1 Context of This Work

The focus of this work is the protection of the execution environment in low-end embedded devices from malicious attacks. In particular, we focus on embedded devices used in cyber-physical systems and used to operate the critical infrastructure.

### 1.1.1 Low-end Embedded Devices

Embedded devices are computer systems designed to perform one or a limited set of specific functions. They are embedded in the sense that all their parts (e.g. memory and CPU) are contained in one single encasing or chip. Embedded devices usually lack of any user interface and are programmed and debugged using a single debug interface.

In this work we focus on low-end embedded devices, that have hard constraints on their computational capabilities, memory, energy and cost. In particular, all the protocols and techniques presented in this work have been implemented and tested on two devices, the Texas Instruments MSP-430 and the Atmel AVR family of micro-controller units (MCU). These embedded devices rely, respectively, on a 16-bit and an 8-bit instruction set. The MSP-430 is based on a Von Neumann architecture, which means that both instructions and data are stored in a single address space. The AVR instead relies on a Harvard architecture, where instructions and data are stored in physically separate memories. These micro-controllers are both embedded on one silicon die where the CPU as well as the memories reside (both RAM and flash storage). The same chip also holds external peripherals such as signal converters (digital to analog and analog to digital), bus interfaces (e.g., UART, etc.), with the possibility of attaching network interface (e.g., Zigbee). Encasing all the components in one single die allows to keep productions costs and energy consumption low. Also, since embedded devices are designed to perform specific tasks, their design can be optimized further reducing their final cost.

Embedded devices are used in a variety of applications ranging from safety critical (e.g., energy plants or automotive systems) to mundane (MP3 players and digital watches). In this work we concentrate on the challenges that arise in securing the operation of the former class of applications, where embedded devices are used as part of cyber physical systems and perform as both actuators and sensors.

### 1.1.2 Cyber-Physical Systems

A cyber-physical system (CPS) is a system where there is tight coordination of the system's computational and physical elements [Lee08]. Cyber-physical systems are composed of three main components: the processing unit, one or more physical sensor (temperature, humidity, etc.) and actuators. Today, CPS are used in a wide variety of applications ranging from automotive, industrial control systems, energy production, health care, aerospace, etc. The definition of cyber-physical systems and embedded devices often overlap, however when referring to cyber-physical systems the stress is on the tight integration between the computing part and the sensors and actuators, rather then the embedded nature of the computation.

There are a number of applications already deployed of cyber-physical systems and more are envisioned to come in the future. Embedded devices are used to control medical devices, such as internal defibrillators and pacemakers or insulin pumps. Most modern cars are largely controlled by, so called, *electronic control devices* that supervision many aspects of the driving ranging from steering to breaking and more. Energy plants of all types (including nuclear plants) rely on embedded devices to monitor and adjust the operational parameters of the systems. Factories rely on embedded devices to control various aspects the production and distribution, called industrial control systems. Cyber-physical systems present a number of interesting challenges that sets them apart from traditional computers and, in 2007, they were identified as as the most important research priority by the NITRD in an address to the US President [NN07].

Cyber-physical systems are required to operate unattended for extended periods of time, possibly in harsh environments. They are often subject to strict reliability and timing constraints. Faults might results in real-world safety risks. The devices can be physically tampered with for malicious purposes. In this work we are interested in exploring the security challenges that arise when embedded devices are used in cyber-physical systems, especially when these devices are used to operate and control the critical infrastructure.

### 1.1.3 Critical Infrastructure

The term critical infrastructure is used by governments to identify and describe assets and systems that are essential to the proper functioning of a society and economy. According to a 2006 report to the European Union [fCIP07] member states are advised to identify their critical infrastructure based on criteria that include:

- "Scope The disruption or destruction of a particular critical infrastructure will be rated by the extent of the geographic area which could be affected by its loss or unavailability.

- Severity The consequences of the disruption or destruction of a particular infrastructure will be assessed on the basis of several parameters listed below."

In turn severity is rated in terms of: public effect (population affected); economic effect (significance of economic loss and/or degradation of products or services); environmental effect; political effects; psychological effects; public health consequences.

While there is no general consensus on what exactly constitutes the critical infrastructure, based on this definition the following national assets associated with: transport and distribution; telecommunication; electricity generation and distribution; water supply; public health; financial services (banks); security services (police and military) and more.

### 1.1.4 Embedded Systems Security

In the context of cyber physical systems and the critical infrastructure, embedded devices security poses a number of unique challenges that are different from traditional computing devices.

**Energy Constraints** Some embedded devices are battery powered and need to operate for extended periods of time. Implantable medical devices, for example, are fully encased in the patient's body and cannot rely on any external energy source, but still need to operate for years without any intrusive replacement. Any security protocol designed for such devices needs to use computation and communication in a very efficient manner to preserve battery life. Furthermore, the security protocols themselves might introduce threats to the availability of the device, if the attacker is specifically interested in exhausting the device's battery<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>This class of attacks is sometimes called sleep deprivation attacks.

Low Cost Some embedded devices are deployed in large numbers and are therefore very cost sensitive: even a small addition in the design might result in high final costs. An increase in few cents in the production cost might render a system economically infeasible.

**Real-time Constraints** Most embedded devices operate under tight timing constraints. Security related operation must be designed not to interrupt normal operation. This presents a very hard challenge since many cryptographic primitives (e.g., cryptographic hashes) are extremely difficult to be made efficient.

**Physical Attacks** Embedded devices might be left unattended in unprotected areas for extended periods of time. This leaves them vulnerable to physical tampering to completely subvert the platform, gain cryptographic keys and more. Embedded devices must be designed to withstand such attacks, or at least make these attacks detectable remotely.

### **1.2** Problem Statement

As explained, embedded devices are used in a large number of critical applications. It is therefore essential to protect them against malicious attackers. However, given the vast number of possible attacks against low-end embedded devices one is confronted with the problem of designing a set of counter-measures that covers as many attack vectors as possible (ideally all) while remaining efficient and, possibly, low-cost. Several trade-offs, corner cases and implicit assumptions need to be analyzed and made explicit. For example, are the embedded devices tamper resistant? If yes, to which degree and at what cost? If no, are hardware attacks realistic?

The list of such questions is very big and very soon one realizes that the design space is extremely vast. First there is a very large combination of possible adversarial assumptions. Second and perhaps more important, there is a large number of solutions to choose from. These solutions can be implemented in hardware or software; can be implemented on the device or at the network level; they can rely on tamper resistant hardware or not; etc. Luckily, this vast design space has already been charted on commodity devices, where the problem of securing execution has been studied for more than a decade. This means that designing security solutions for embedded devices has the advantage of being able to look at the big picture and choosing the solutions that provide the best trade-offs, for example, in terms of security and efficiency. Also, this approach guarantees that the solutions implemented do not overlap or collide.

One of the great advantages of working with embedded devices is the general lack of legacy constraints. In fact, it is not uncommon for a micro-controller unit to be heavily customized to fit the needs of a specific application. This is in stark contrast with commodity devices, such as server and desktop computers, where legacy is one of the biggest, if not the biggest, hurdle in designing solutions to the problem of securing execution.

To guide in the design of our solutions we follow a map of possible attacks and, therefore, explore adversarial assumptions.

### **1.2.1** Code Injection Attacks

Here we list the attacks that we consider and address in this work. They encompass the ways in which malicious code can be injected in an embedded device.

**Remote Exploits** This form of attacks is perhaps the most well-known and widely studied. In this case, the attacker and the victim device communicate over a communication channel, for example a TCP/IP connection or the system call interface of an operating system. The attacker tries to abuse and subvert the communication protocol and format to expose an implementation bug on the victim device. Once discovered, the bug can be used to subvert the flow of control on the victim and inject malicious code that performs actions chosen by the attacker.

Attacks Against Software Updates Most software systems – and the ones on embedded devices are not an exception – share the need of being amendable to updates. Updates can occur for a number of reason, but most commonly it is due to a implementation bug that needs to be fixed or a feature that needs to be added. This factor has important consequences on security, since, often, there is no immutable trusted code base that can be trusted implicitly. Instead the system needs to be able to accept new code, provided that it comes from a trusted source. This process can be subverted by an attacker, if the right countermeasures are not put in place, and lead to malicious code being injected on the victim device. This type of attack could be possible even if remote exploits are completely mitigated. More subtly, even if the software update protocol is secure, malicious code injection is still possible if the computer that issues the update has been compromised. This type of attacks have been recently discovered in the context of external defibrillators [HRMM+11] and it was the case in the StuxNet outbreak [FMC11].

Attack Against Management Interfaces Furthermore, embedded devices often have debugging and management interfaces, e.g., JTAG interfaces. These interface are frequently used during development and prior to deployment and give highly privileged access to the device and allow to upload new software or change the settings. As explained, embedded devices are often left unattended for long periods of time and therefore these debugging interface might be accessed by an attacker. Security of the debugging interfaces is enforced in two main fashions, either by preventing un-authorized access by authenticating the legitimate administrators (for example via passwords) or by blocking completely the debug interface when the device goes to a production environment (for example by blowing specific fuses on the device). Neither of these approaches are completely secure though (passwords can be guessed and fuses can be tampered with) allowing malicious code injection.

**Injection at Production Time** Consider the following situation<sup>2</sup>, Alice sells an empty SIM card to Bob. Bob goes ahead and uploads its code on the SIM card. Bob does not see anything wrong, however the card originally contained malicious code and the upload procedure was rigged to allow a malicious piece of code by Alice to be present on Bob's SIM card. This malicious piece of code could remain silent unless a specific event is triggered by Alice.

# 1.2.2 Attacks Against the Integrity and Confidentiality of the Data

There are other attacks that, albeit not addressed in our work need to be considered in the design of secure embedded devices. Even though these attacks range from logical to physical, we group them because the goal they achieve, which is violating the integrity or confidentiality of the data stored on the embedded devices.

Non Control Data Attacks Non control data attacks have been explored in [CXS<sup>+</sup>05a] and involve an attacker remotely exploiting an implementation bug, not unlikely the code injection remote exploitation mentioned above. However, the goal of the attacker is not to inject code but to simply change the value of variables used for security purposes. Consider, for example, an attacker that could change the value of a key to a known value, therefore exposing all subsequent communications. Also consider the case of an attacker resetting the value of a flag used for access control purposes. In both these examples, no code is injected on the victim device but a comparable effect is produced for the attacker.

Side Channel Attacks Simple and Differential Power Analysis attacks trace the power consumption of an embedded device and measure the tiny fluctuations that occur when the MCU is computing different instructions or handling different data [MOP07]. By doing so, these attacks are able to recover bits of the secret key. Several related attacks are possible that fall in the broad definition of *side channel attacks*, these include electro-magnetic analysis and timing analysis. Side channel attacks have been originally developed to extract secret from smart cards and therefore, are extremely relevant to embedded devices.

<sup>&</sup>lt;sup>2</sup>This example is taken from [GN07]

**Physical Attacks** Physical attacks encompass a wide variety of attack techniques that range from fault injection to the depackaging of the embedded chip to steal its secrets. Fault injection attacks, for example, aim at putting the embedded device in state that can be exploited by the attacker via the manipulation of its surrounding conditions, e.g., manipulating the voltage issued to the CPU. More invasive attacks can modify paths on the circuits of an embedded device to cause faults and recover secrets stored on the device. A complete survey of such techniques is beyond the scope of this work and can be found at [Sko05]. Such attacks can be countered by encasing the embedded device in tamper resistant or tamper evident casing and by including appropriate control logic to detect the unusual conditions exploited in fault injection attacks. Those attacks operate at a different layer than the one analyzed in this work. However, when designing our solutions we considered the amenability to such protective techniques.

### **1.3** Contributions

Given the landscape defined above we can now proceed to explain where our contributions stand. First, we are interested in investigating techniques to **prevent** code injection via control flow exploitation of low-end embedded devices. Our solution can only help prevent remote exploit attacks (commonly referred as buffer overflow attacks), but it cannot prevent other forms of injection, such as malware introduced at production time. For this reason we also focus our attention to techniques that can **detect** malicious code if present. Hence, we look at techniques to verify the current state of a remote embedded device, namely via *device attestation*. We also concentrate on techniques to establish a *dynamic root of trust*, i.e., executing a small trusted piece of code untampered even when the embedded device has been compromised. This small trusted piece of code can, if needed, perform device attestation.

In doing so we focus on techniques that minimize hardware modifications to existing embedded devices in order to reduce cost. Furthermore, we strive to design solutions that have a small footprint and overhead on the normal operations, realizing how security protocols might interfere with the normal operations of the cyber-physical systems.

The contributions of this work are manifold:

- First, we present a lightweight hardware modification to the AVR MCU family, called IBMAC, that helps preventing remote exploitation of buffer overflows on embedded devices (Chapter 2).

- Then we thoroughly review several protocols proposed in the literature to perform software attestation of embedded devices. We find that most of the proposed solutions are vulnerable to several attacks and do not provide the claimed guarantees (Section 3.2).

- We therefore design PoSE, a software attestation solution that overcomes the limitation of the previously proposed protocols (Section 3.3).

- Finally, we present SMART that uses a hardware/software co-design to guarantee the execution of a piece of code on a remote embedded device (Section 4). This small piece of code can perform device attestation, if needed.

## Chapter 2

## Protecting Embedded Devices against Remote Attacks

### Contents

| 2.1 | Stat                  | e of The Art                                                            | 12        |

|-----|-----------------------|-------------------------------------------------------------------------|-----------|

|     | 2.1.1                 | Control Flow Exploitation                                               | 12        |

|     | 2.1.2                 | Control Flow Protection                                                 | 15        |

| 2.2 | Inst                  | ruction Based Memory Access Control for Con-                            |           |

|     | $\operatorname{trol}$ | Flow Integrity                                                          | 17        |

|     | 2.2.1                 | Overview of our solution                                                | 17        |

|     | 2.2.2                 | A separate return stack $\ldots \ldots \ldots \ldots \ldots \ldots$     | 18        |

|     | 2.2.3                 | Instruction Based Memory Access Control                                 | 19        |

|     | 2.2.4                 | Other design considerations $\ldots \ldots \ldots \ldots \ldots \ldots$ | 20        |

| 2.3 | Imp                   | lementation                                                             | <b>21</b> |

|     | 2.3.1                 | Implementation                                                          | 21        |

|     | 2.3.2                 | Evaluation                                                              | 25        |

| 2.4 | Cons                  | siderations                                                             | <b>25</b> |

This chapter presents a control flow enforcement technique based on an Instruction Based Memory Access Control (IBMAC) implemented in hardware. It is specifically designed to protect low-cost embedded systems against malicious manipulation of their control flow as well as preventing accidental stack overflows. This is achieved by using a simple hardware modification to divide the stack in a data and a control flow stack (or return stack). Moreover access to the control flow stack is restricted only to return and call instructions, which prevents control flow manipulation. This *Return Stack* is stored in data memory at a different location than the normal stack and is protected in hardware against accidental or malicious modification. Our approach is binary compatible with legacy applications, only requires minimal changes to the tool-chain and does not the increase memory requirements. Additionally, it makes an optimal usage of stack memory and prevents accidental stack corruption at run-time. The solution is implemented on the AVR micro-controller using both a simulator and a full implementation on an FPGA. The implementation on reconfigurable hardware showed a small resulting overhead in terms of number of gates, and therefore a low overhead of expected production costs.

This demonstrates the possibility to implement this feature with a modest overhead in terms of logical elements units, with no run-time impact, and backward compatibility on all major software functionality. In order to support this feature the device needs application specific configuration to be performed at boot time. This configuration is performed during the boot of the software on the device. This configuration is performed during the very first step of software initialisation and therefore can be performed by the C library after basic initialisation of memory. Apart from this change the compiler libraries and programs do not need modifications.

### 2.1 State of The Art

By control flow exploitation we mean all the techniques and attacks that try to subvert the normal flow of control of a program and inject malicious code. These attacks are aimed at gaining remote and privileged access to a computer systems by subverting the data structures that regulate the control flow of a program (e.g., the return addresses stored on the stack). Programs that do not implement appropriate checks allow attackers to remotely write data beyond the normal boundaries and thus overwrite control structures in the program. This enables the attacker to execute code with the same privileges as the exploited code.

In this section we will survey the current state of the art of both prevention as well as exploitation techniques. We begin by describing older attack techniques first and introduce the general problem. We then move to more recent attack techniques and finally describe the prevention mechanisms that have been proposed.

### 2.1.1 Control Flow Exploitation

### 2.1.1.1 Buffer Overflows

Buffer overflows were first described by Spafford in [Spa89]. Spafford reports his efforts in reverse engineering the remote infection of a BSD derived versions of UNIX that occurred in November 1988. Spafford finds that a *worm* propagated through the network by exploiting a bug in the implementation of the *fingerd* demon that allowed remote code injection and the execution of a UNIX shell. These types of attacks, later called buffer overflows (or buffer overruns), did not become popular until later in the nineties following the publication of [One96, Mud95].

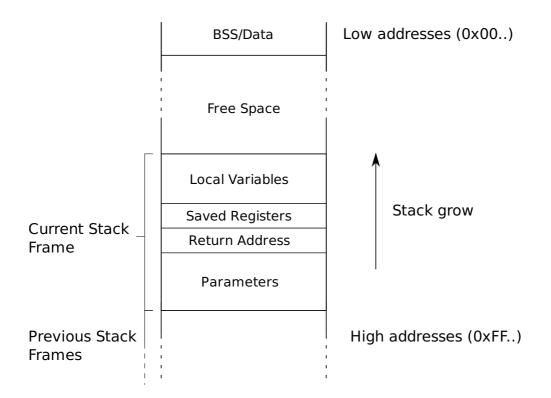

Figure 2.1: Common stack layout

In order to understand how buffer overflows work one needs first to understand how functions and procedures are managed in most systems and programming languages [Ale05]. When a piece of code calls a function the following steps take place:

- 1. the calling procedure pushes arguments on the stack in reverse order;

- 2. the calling procedure executes a call instruction that stores the address of the calling procedure on the stack and then jumps to the called function;

- 3. the called function saves the old frame pointer on the stack and then the stack pointer is decremented to make room for the local variables.

In figure 2.1 there is a depiction of the resulting typical stack layout when a function call occurs. Now consider the following code:

```

#include <stdio.h>

int main (int argc, char *argv[]) {

char buf[16];

strcpy(buf, argv[1]);

return 0;

}

```

This code is trivially vulnerable to a buffer overflow attack. In fact, according to the ANSI C specifications the strcpy function copies characters in the destination buffer buf until a '0' character is encountered. However, if an attacker provides a string that is longer than the allocated length, buf is overflown and data adjacent to buf in memory can be overwritten. Specifically, the attacker can overwrite the saved return address on the stack. By carefully crafting the content of the input buffer the attacker can divert the return address, inject its own code and make the process execute arbitrary code. This arbitrary code is usually referred to as *payload* or *shell code*.

However, the attack is slightly more complicated than this simple explanation. In fact the attacker has to know the current address of the stack frame to overwrite the return address in memory with the correct value. A common technique is to include a *NOP sledge* in the payload: a NOP sledge is a series of NOP instructions that have the sole purpose of increasing the attacker's chances of correctly guessing the address of the payload. In fact, if the guessed address points to any location within the series of NOPs, execution will continue through the NOPs and eventually reach the payload. This way the attacker does not need to know the exact location of the payload but only its approximate location to fall within the sequence of NOPs.

### 2.1.1.2 Return to libc

The buffer overflow technique described above assumes the data on the stack to be executable, this way the attacker can inject arbitrary code on the stack and execute it. However, this assumption is not always true. Harvard architectures (like the AVR used in this work) explicitly distinguish code and data. This makes the data non executable. Furthermore, one of the first techniques proposed to prevent buffer overflows (described later in Section 2.1.2.1) is designed to prevent the execution of the data on the stack.

In order to circumvent this limitation, soon a new class of attacks was discovered [Sol97b]. In this class of attacks the attacker does not inject any payload code on the stack, since its execution would be impossible. Instead, the attacker overwrites the return address on the stack with the address of a function already present in the address space of the vulnerable program. The attacker can manipulate the parameters stored on the stack to pass parameters to the target function appropriately. The target function can be any function that has been loaded inside the address space of the attacked process.

Since most C programs load the C library by default (libc) this class of attacks often used functions in the C library and was called *return to libc* or *return-into-libc*.

#### 2.1.1.3 Return-Oriented Programming

The return to libc attack is somewhat limited to the functions already present in the program's memory and, in general, does not allow the attacker to execute arbitrary code. To counter the effectiveness of this attack, for example, certain security critical functions (like the UNIX system call) could be removed entirely from the program's code making the exploit more difficult to accomplish.

In order to circumvent these limitations Shacham introduced a technique called return-oriented programming (ROP) [Sha07] to exploit vulnerable programs. Instead of executing a complete function present in the address space of a vulnerable program, ROP aims at discovering very short sequences of assembly instructions (two or three instructions long) that terminate with a return. These short sequences, called *gadgets*, provide the basis for a return oriented programming attack. In fact, by carefully crafting the data injected on the stack, a chained sequence of gadgets can be executed within the attacked process to perform arbitrary computation. Later the technique was expanded and augmented to perform attacks without relying on the return instruction [CDD<sup>+</sup>10].

### 2.1.2 Control Flow Protection

Control flow attacks have been predominant in many forms since their first appearance. Many different techniques have been proposed to prevent the remote exploitation of vulnerable code, mostly on commodity computers like servers and desktop class machines.

#### 2.1.2.1 Non-Executable Data

One of the first methods to defeat stack based buffer overflows was to make the stack non-executable [Sol97a]. This way even if the attacker is able to inject code on the stack, she cannot execute it. This eventually evolved into what is now referred to as DEP – Data Execution Prevention – (also referred to as X <sup>^</sup>W) that is now included in most modern operation systems. In DEP the data memory pages are marked as non-executable either using hardware or software support. When using hardware support, a Non Execute (NX) flag is set for the memory pages of the stack. The processor in turn refuses to execute such memory locations preventing simple stack based overflow. It must be noted, however, that this technique does not prevent other types of exploits like, for example, return-to-libc or ROP attacks.

#### 2.1.2.2 Control Flow Integrity

In Control Flow Integrity, Abadi et al. [ABEL05] propose to embed additional code and labels in the code, such that at each function call, or return, a program is able to check whether it is following a *legitimate* path in a precomputed control

flow graph. If the corruption of a return address occurs, that would make the program follow a non legitimate path, then the execution is aborted as malicious action or malfunction is probably ongoing. The main drawback of the approach is the need for instrumentation of the code, although this could be automated by the compiler tool-chain, it has both a memory and computational overhead and thus might be infeasible on resource constrained devices.

#### 2.1.2.3 Stack Canaries

Canaries were proposed as a solution to buffer overflows in [BST00]. The authors propose to place a *canary* value between the return pointer and local function variables. The value of the canary value is set in the prologue of each function and is checked for validity in the epilogue. In cases when the canary value is altered, there is a clear indication that a memory corruption has occurred and appropriate actions can be taken by the epilogue function, like terminating the process and logging the event.

Canaries introduce a measurable overhead in the normal operation of a program, as the prologue and epilogue are instrumented inside the code at compilation time. Furthermore, canaries have been shown to have a number of vulnerabilities [Ale05]. For example, if the attacker is able to find a double corruption then it can first corrupt a pointer to point past the canary and then modify the return pointer on the stack without modifying the canary.

#### 2.1.2.4 Address Space Layout Randomization

Address space layout randomization [The] can hinder control flow attacks. It is a technique where the base addresses of various sections ( .text,.data,.bss, etc.) of a program memory are randomized before each program execution. The memory corruption is not prevented with this technique but exploitation of the vulnerabilities is made considerably more difficult. In fact, the attacker has to correctly guess the randomized address of the target code to execute to complete the attack.

Although, in [SPP<sup>+</sup>04] show that the effectiveness of address-space randomization is limited on 32-bit architectures by the number of bits available for address randomization. This problem would be even more severe on embedded systems that typically have a 8-bit or 16-bit address space.

#### 2.1.2.5 Protecting the Return Stack

In [Sta] the authors present StackShield that uses a compiler supported return stack. Where the compiler inserts a header and a trailer to each function in order to copy to/from a separate stack the return address from/to the normal stack. As this is implemented at the compiler level there is no backward compatibility, the programs need to be re-compiled with this modified compiler. Moreover, as additional instructions are introduced there is non negligible a computation and memory overhead.

Furthermore in [XKPI02] the authors propose a return stack mechanism where dedicated call and ret instructions store and read control flow information from a dedicated stack. However the only guarantee for this return stack integrity is that is located far away the normal stack, which does not prevent modification of the return stack, it just makes it more difficult. Double corruption attacks [Ale05] would allow an attacker to corrupt a data pointer first and then modify an arbitrary memory location on the return stack.

A number of systems already use a separate control flow stack like the PIC micro-controller (for example the pic16[bbM]) or some AVR chips (AVR AT90S1200 [08302]). However those solutions are not designed to improve security. They either allow direct modification of the hardware stack (vulnerable to double corruption) or have a limited stack stored inside the MCU (very limited call depth). For example the AVR AT90S1200 has a return stack supporting only 3 re-entrant routines, if more than 3 re-entrant interrupts or functions calls are performed the hardware return stack is corrupted.

### 2.2 Instruction Based Memory Access Control for Control Flow Integrity

### 2.2.1 Overview of our solution

The main idea behind IBMAC is to protect return addresses on the stack from being overwritten with arbitrary data. By doing so, as we will show later, IBMAC also protects embedded systems from memory corruption caused by stack overflows.

The intuition is that control flow data should be only read and written by the call and ret family of instructions and modifications by other instructions should be prevented. Hence, restricting access to return addresses to call and ret instructions in hardware seems only logical. However in a normal stack layout, return addresses are interleaved to other types of data, making access controls difficult. In fact, such a fine grained access control would be slow and would lead to a considerable memory overhead, since all the words in memory that have to be protected would need to have an additional flag bit.

That is the main reason why we decided to modify the stack layout adding an additional *Return Stack*, specifically designed to store only return addresses. However, changing the memory layout could have lead to major compatibility issues. That is why our principal design goal was to have a very simple hardware implementation, without extra memory requirement and focused on compatibility. The result is that IBMAC does not require modifications to the tool-chain and most binary libraries could be used without being rebuilt. IBMAC also improves software reliability as stack memory over-consumption [RRW05] can be detected

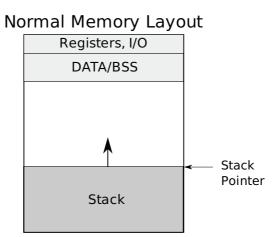

Figure 2.2: Traditional stack layout

at run-time so that a reboot or other actions can be performed (e.g. dedicated interrupt).

Finally we implemented IBMAC as an optional feature that can be activated for example with a write-once configuration register at boot<sup>1</sup>. With those constraints fulfilled and a proven implementation, we believe that this is a very realistic scheme with limited production costs and significantly increased security.

### 2.2.2 A separate return stack

In Figure 2.2 an architecture with a single stack is shown. While it is convenient to have a single stack, it makes it very difficult to protect the stored return addresses. We therefore implemented a modification to the instruction set architecture in order to support the use of two separate stacks: a *Return Stack* and a *Data Stack*. The return stack is used to store control flow information (return addresses) and the data stack is used to store regular data.

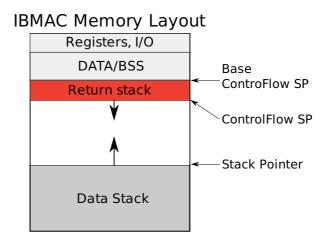

There are several different possible layouts in which those two stacks could be arranged in memory. The arrangement chosen in our implementation is depicted in figure 2.3. The first thing to note comparing figure 2.2 and 2.3 is that the data stack lies where the original single stack was. This was the best solution to maximize backward compatibility, as with this layout the allocation of the stack works in exactly the same way as before and no modifications to the compiler are necessary.

The second thing to note is that the return stack and the data stack grow in opposite directions. This was done in order to optimize memory consumption, as with this layout no memory is wasted in comparison with the original stack layout. The fact that the return stack grows in the opposite direction does not

<sup>&</sup>lt;sup>1</sup>This could be a *fuse* register on the AVR for example, as fuses cannot be modified without physical tampering.

Figure 2.3: IBMAC stack layout. The Base control flow stack pointer is the only register that needs to be initialized in order to support IBMAC.

hinder backward compatibility, as this stack is exclusively handled in hardware by the modified call and ret instructions.

The third thing to note is that the return stack does not have any static limitation, but instead is only limited by the data stack. However this can also be a drawback as it those not leave room for an unbounded *heap*. In section 2.2.4 we discuss this problem in more detail.

### 2.2.3 Instruction Based Memory Access Control

The separate return stack layout presented in the previous section provides an easy way to separate control flow information from regular data allocated on the stack. However, it does not prevent modification and corruption of control flow information, but only makes it a bit more difficult as control flow data is not close to stack allocated buffers. Complex attacks would still be able to exploit the return stack. For example if an attacker is able to corrupt the pointer to an array and to further write data to this array she would be able to write data at an arbitrary memory location.

This is the reason why an extra protection layer for the return stack is required. On a general purpose operating system this could be provided by an MMU. However, those are generally not available on low-end embedded devices. The reasons for that are multiple: first, those MCUs are designed for to be at a very low price range, each additional feature comes at an increase of the silicon size and consequently increase the final manufacture price. Second, they are usually designed to execute monolithic applications, therefore they do not require memory protection between different applications or the application and a kernel. The challenge is therefore to protect only the return stack at a very small cost, which is not the case with a complete Memory Management Unit. Our hardware modification has been designed around the following considerations:

- only control flow related instructions will need to modify the control flow stack

- the data manipulation instructions do not need to access control flow information

Given this observations it is possible to control memory accesses and decide whether to grant or refuse access to the return stack based on which instruction is performing the memory access. On the AVR we used, we identified only two instructions that needed to be able to access the return stack, namely the call and the ret instructions and their derivatives. The hardware implementation of these two instructions has been modified in such a way to set an internal flag to 1 whenever they are executed. When this signal is high memory access is granted to the control flow stack. If not, the system is rebooted (or could alternatively trow a dedicated interrupt).

### 2.2.4 Other design considerations

Dynamic memory allocation is one of the basic building blocks of modern operating systems and programing languages. However, it is often avoided on low cost embedded systems for the following reasons: first it is usually difficult to predict the worst case memory usage, which can quickly lead to memory exhaustion on these systems; second, memory fragmentation is a serious problem for architectures without a memory management unit. In fact, on architectures with a memory management unit even if memory fragmentation happens in the virtual address space, it is always possible to defragment the physical memory, freeing large blocks of contiguous memory, in a transparent way for the application. This is not possible in the case of processors lacking a MMU because it would be necessary to keep track of all pointers and update them when the defragmentation process moves a contiguous memory block  $^2$ .

Usually on the AVR family of processors memory allocation is either performed statically i.e. global variables or when with dynamic allocation on the stack <sup>3</sup>.

Nevertheless, if a heap is needed it is usually allocated within a fixed range of memory addresses for allocation. In such a case, the return stack can be made to start after the end of the heap, with risking overflows or memory waste.

<sup>&</sup>lt;sup>2</sup>It is possible to use double pointers, as done in the Contiki operating system. However, all access must be preformed with double de-reference, if an intermediate pointer is kept by the application and defragmentation occurs the memory might be corrupted by accessing an invalid address

$<sup>^3\</sup>mathrm{Variable}$  memory allocation on the stack is possible using as GNU gcc's non standard alloca function

| Register Name | Description                                | Atmega103   | Atmega128   |

|---------------|--------------------------------------------|-------------|-------------|

|               |                                            | Address     | Address     |

| SP_CF_L       | Control Flow stack pointer Low             | \$00 (\$20) | \$46 (\$66) |

| SP_CF_H       | Control Flow stack pointer High            | \$01 (\$21) | \$47 (\$67) |

| SSCR          | Split Stack Control Register (sec 2.3.1.4) | \$10 (\$30) | \$49 (\$69) |

| CF_SS_L       | Control Flow Stack Start Low               | \$02 (\$22) | \$55 (\$75) |

| CF_SS_H       | Control Flow Stack Start High              | \$03 (\$23) | \$56 (\$76) |

(a) New register allocation for the additional registers.

| Register name | Needs   | Locking           | Unlocking | Authorized                  |

|---------------|---------|-------------------|-----------|-----------------------------|

| Register name | Locking | condition         | condition | modifications               |

| SP            | No      | N/A               | N/A       | Any                         |

| CF_SP         | Partial | After First Write | Reboot    | Internal to CF instructions |

| CF_SP_Start   | Yes     | After First Write | Reboot    | None                        |

| SSCR          | Yes     | After First Write | Reboot    | None                        |

(b) New registers locking logic

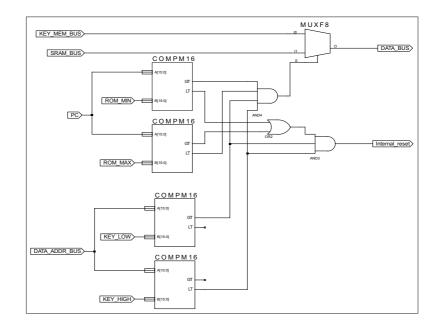

Figure 2.4: Stack configurations and Control flow stack pointer description and additional locking logic

### 2.3 Implementation

### 2.3.1 Implementation

In order to validate our approach we implemented the changes to both a simulator and a soft core in a FPGA.

### 2.3.1.1 Implementation on a simulator

We modified the AVRORA [TLP05] simulator in order to simulate the modified core, this made possible simulate the complete platform composed of an Atmega128[ATM] MCU and a IEEE 802.15.4[Soc] radio device. The simulation involved running *unmodified* TinyOS applications, for wireless sensor networks. The changes to AVRORA simulator were implemented in about 200 lines of code out of the 50,000 lines of code that compose the AVRORA simulator (0.4% change).

### 2.3.1.2 Implementation on an FPGA

We implemented the modifications in a VHDL implementation of the Atmega103 core available at opencores.org. Although this micro-controller version is discontinued, it is very similar to the Atmega128 and the modifications implemented are probably very similar to those required for an Atmega128. The modifications were made with changes of 8% of the VHDL source code (500 lines out of 6000). The