# Méthodologie pour un processus d'analyse temporelle dirigé par les modèles pour les systèmes automobiles

Saoussen Anssi Rekik

# ▶ To cite this version:

Saoussen Anssi Rekik. Méthodologie pour un processus d'analyse temporelle dirigé par les modèles pour les systèmes automobiles. Autre [cs.OH]. Université Paris Sud - Paris XI, 2011. Français. NNT : 2011PA112239. tel-00647906

# HAL Id: tel-00647906 https://theses.hal.science/tel-00647906

Submitted on 3 Dec 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Methodology for Model-based Timing Analysis Process for Automotive Systems

# Méthodologie pour un Processus d'Analyse Temporelle Dirigé par les Modèles pour les Systèmes Automobiles

# **THESE**

Présentée et soutenue publiquement le

09 Novembre 2011

Par

## SAOUSSEN ANSSI

Pour obtenir le grade de

# DOCTEUR EN INFORMATIQUE DE

l'Université Paris-Sud

Devant le jury composé de :

Prof. Guy Vidal-Naquet, Université Paris-Sud Président

Prof. Lionel Briand, Université d'Oslo

est I

Prof. Jean-Philippe BABAU, Université de Brest

Rapporteur

Rapporteur

Prof. François TERRIER, CEA LIST

Directeur de thèse

Dr. Ing. Sébastien GERARD, CEA LIST

Encadrant de thèse

Ing. Stefan Kuntz, Continental Automotive

Encadrant de thèse

$\label{eq:tomy father} To \ my \ father,$  For all the love he gave to us...

# Acknowledgements

This work has been financially supported by the ANRT (Association Nationale de la Recherche Technique) in France.

I am grateful to my thesis committee for devoting their time to read the manuscript and to participate in my dissertation. I have particularly appreciated the thoroughness and insightful comments from Lionel Briand and Jean-Philippe Babau on earlier drafts.

Special thanks go to my thesis supervisor Prof. François Terrier for giving me the opportunity to develop this thesis at the CEA LIST labs.

I want to thank my advisor Sébastien Gérard for his crucial support in the development of the ideas presented here.

I am grateful to my technical advisor in Continental Stefan Kuntz for his support during this work and the very interesting technical discussions that we had together. I would like to salute his technical brilliance and his strong cultural sensitivity. This work allowed me to learn much from him.

I would like to thank Frédéric-le-Hung, our team manager in Continental, for his support during these three years and his open-mindedness.

I had the pleasure to work with Denis Claraz and Philippe Cuenot in Continental; I would like to thank them for their interesting feedbacks and recommendations for the deployment of this thesis work in Continental.

Special thanks go to my earlier technical advisor in CEA, Huascar Espinoza, for his help and recommendations during the state-of-the-art studies.

During these three years I had the pleasure to participate to two research projects, EDONA and Memvatex. I would like to thank all the members of these projects. In particular, I would like to warmly thank Sara Tucci from CEA for her interesting ideas for the scientific publications that we wrote together.

I am thankful to all the people of the LIST lab in CEA and the ADE team in Continental. I always found high availability of technical support, a very comfortable discussion environment, a lot of resources to develop the work efficiently, wide openness for work diffusion, and team participation.

I am immeasurably thankful to my parents, Sayeh and Khadija, my brothers Imed and Ridha, my sisters Naziha, Salwa, Henda, and my cousins Sonia and Randa in Tunisia for all their love, sacrifices and endless encouragement. They always stand by me and never let me down in spite of physical distance. I owe all my success to their love, care and sacrifices. They taught me the real sense of sacrifice and altruism.

Finally, there are no words to express my gratitude to my dearly beloved husband Ahmed-Amine for his sacrifices and everlasting encouragement. He gives me energy, peace of mind and happiness. This thesis is dedicated to him for everything he means to me...

# **RESUME**

Ce travail de thèse a été effectué dans le cadre d'une collaboration technique entre le CEA-LIST à Paris et le service « développement avancé électronique » de Continental Automotive à Toulouse.

# 1. Objectifs de la thèse

Dans ce travail de thèse on se propose de définir une méthodologie décrivant un processus d'analyse temporelle dirigée par les modèles pour les systèmes automobiles. Cette méthodologie vise à donner un guide aux ingénieurs de développement logiciel automobile pour l'intégration de la vérification temporelle dans un processus de développement dirigé par les modèles. Ceci permettrait alors la détection au plus tôt des erreurs de conception liées au comportement temps réel des systèmes.

En plus de la définition de la méthodologie elle-même, sa validation doit être aussi étudiée en montrant à quelle mesure elle contribue à résoudre les problèmes rencontrés actuellement dans le domaine du développement logiciel automobile. L'acceptabilité de la méthodologie est également à étudier pour évaluer son potentiel d'adoption pour le développement des systèmes de contrôle moteur (Engine management System EMS) à Continental.

#### 2. Contexte de la thèse

# 2.1. Contexte Industriel

Aujourd'hui, l'architecture des systèmes automobile est devenue de plus en plus complexe avec une utilisation massive du logiciel embarqué pour assurer les diverses fonctionnalités d'une voiture.

Pour répondre correctement aux besoins de ces clients ainsi qu'aux contraintes de concurrences, un équipementier (tel est le cas de Continental Automotive) doit considérer deux facteurs essentiels: la maitrise du temps et du coût du développement logiciel ainsi que la garantie de la fiabilité du système conçu. Vue la complexité croissante du logiciel embarqué automobile, la garantie de sa fiabilité dépend énormément de la capacité de maîtriser cette complexité lors du développement. En plus de la maîtrise de la complexité, la fiabilité des systèmes automobiles doit être également assurée à travers les techniques de vérification et de validations. La vérification et la validation des contraintes de temps est d'une importance énorme pour garantir cette fiabilité. Aujourd'hui la vérification temporelle des systèmes automobiles est effectuée très tard au cours du développement (après la phase

d'intégration). Elle se base essentiellement sur des tests et des mesures plutôt que sur une approche formelle et systématique. Ainsi, Pour développer un logiciel fiable tout en respectant les contraintes de concurrences, il y a un besoin fort pour des approches de développement qui permettent de: 1) Maîtriser la complexité du logiciel lors du développement.2) Réduire le temps et le coût de développement. 3) Définir une activité de développement ainsi qu'une chaine d'outils homogène et continue.4) Permettre l'intégration de la vérification temporelle au cours du processus de développement.

# 2.2. Approches existantes

Pour apporter des solutions aux besoins du développement du logiciel automobiles, plusieurs approches, méthodes et techniques ont été définit aux cours de la dernière décennie. Ces approches visent soit à donner des méthodes de développement permettant l'amélioration des processus de développement des systèmes automobiles (tel est le cas des approches définit dans le cadre de l'ingénierie dirigée par les modèles), soit à permettre de vérifier le comportement temps réel des systèmes (comme les technique d'analyse d'ordonnancement et de performance).

Dans le domaine automobiles, les approches et langages de modélisations qui ont été définit sont:

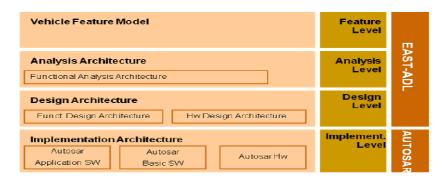

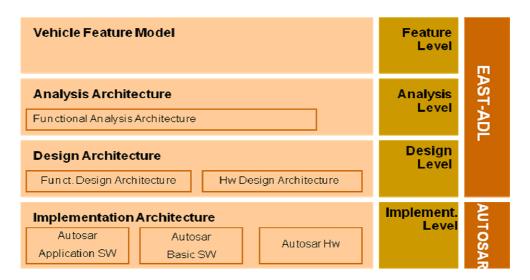

• EAST-ADL: Ce langage permet la modélisation de l'architecture électrique/électronique des systèmes automobiles suivant plusieurs niveaux d'abstraction. Il donne plusieurs concepts permettant la modélisation de la structure fonctionnelle (sur les niveaux Analyse et Design) et matérielle (à partir du niveau design) des systèmes automobiles. La Figure 1 montre les niveaux d'abstraction d'EAST-ADL (le niveau implémentation s'appuie sur les concepts d'AUTOSAR)

Figure 1 Niveaux d'abstraction d'EAST-ADL

- TADL: Ce langage permet la modélisation des propriétés et des contraintes temporelles des éléments structurels décrits dans une architecture EAST-ADL ou AUTOSAR.

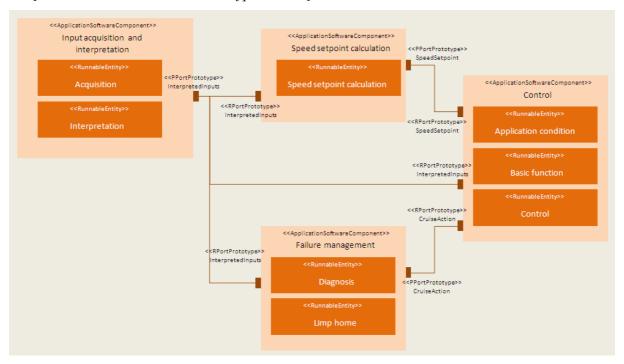

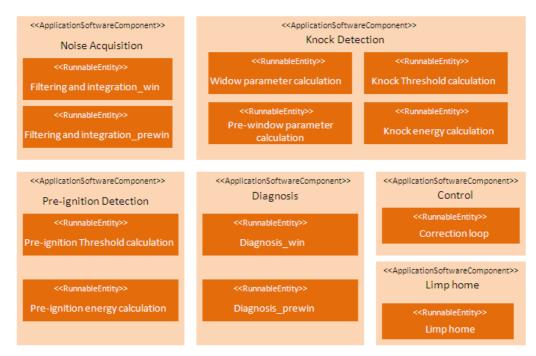

- AUTOSAR : Il donne une approche pour décrire une architecture logicielle standard pour l'automobile. Il offre un modèle d'architecture logicielle organisé suivant trois niveaux : le logiciel applicatif, le RTE (RunTime Environment) et les couches logicielle de bas nivaux (basic software). Le RTE fait le lien entre le logiciel applicatif et les couches logicielle basses. Le logiciel est organisé sous forme de composants logiciels (software components). Pour chaque composant, il est possible de décrire les unités exécutables qu'il contient (runnable entities) ainsi que ses interfaces de communication (port)

- MARTE: Ce langage permet de modéliser l'architecture des systèmes temps réel. Il

offre un set de concepts de modélisation pour permettre d'effectuer de l'analyse

d'ordonnancement basée sur les modèles.

Parmi les techniques de vérification temporelle on cite essentiellement l'analyse d'ordonnancement. Dans le contexte de cette technique, plusieurs tests d'ordonnançabilité ainsi que des outils d'analyse d'ordonnancement ont été développés. Parmi ces outils il ya des outils académique tel que Cheddar et MAST et d'autres commerciaux tel que SymTA/S et Chronval. L'évaluation de ces outils d'analyse montre que SymTA/S est le plus adapté pour faire de l'analyse d'ordonnancement pour les applications automobiles.

L'évaluation des ces approches de développement et de vérification temporelle (effectué aux cours de ces travaux de thèse) a montré qu'il y a un manque pour un guide méthodologique pour l'intégration de la vérification temporelle notamment l'analyse d'ordonnancement au cours du cycle de développement dirigé par les modèles. Ce travail de thèse propose une approche qui permettrait de résoudre ce problème.

# 3. Méthodologie

- 3.1. Objectifs de la méthodologie :

- Définition d'un processus de développement dirigé par les modèles qui assure une activité de développement continue et homogène tout au long du processus. Ce processus doit être facilement utilisable par un ingénieur Continental pour le développement des systèmes de control moteur (Engine Management Systems

EMS). La méthodologie définit doit décrire les différentes phases du processus ainsi que l'approche suivit pour le développement et l'affinement des modèles d'une phase à autre.

- Donner un guide pour l'intégration de la vérification temporelle dans ce processus de développement. Ceci requiert la définition du type de vérification temporelle à effectuer durant chaque phase, les techniques et les outils de vérification temporelle à utiliser ainsi que la description de la manière d'utiliser les résultats d'analyse de chaque phase pour affiner les modèles de la phase suivante.

- Décrire la manière de développer des modèles analysables. Plus particulièrement comment extraire à chaque phase les modèles comportementaux nécessaires pour l'analyse temporelles des modèles architecturaux utilisés pour la description de l'architecture.

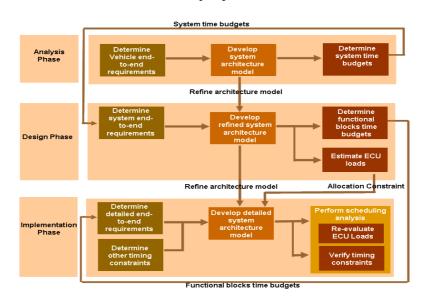

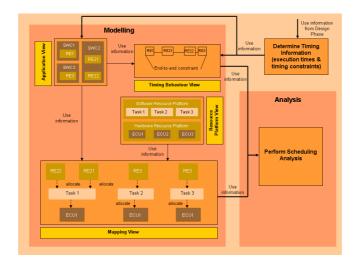

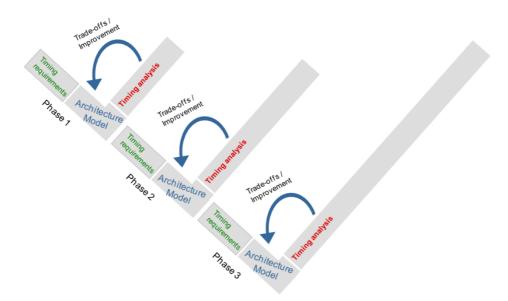

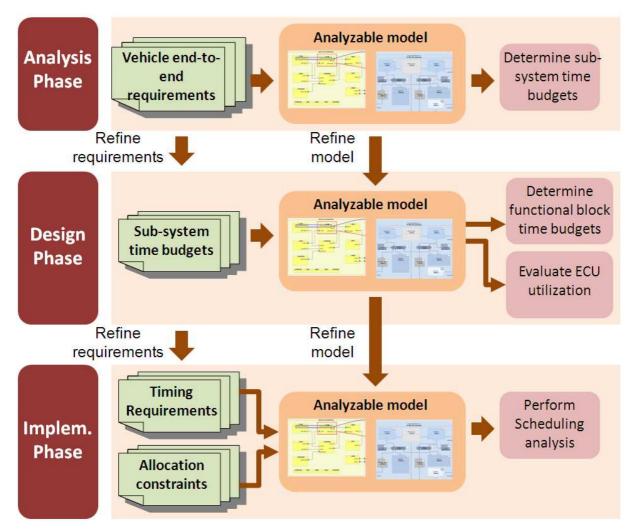

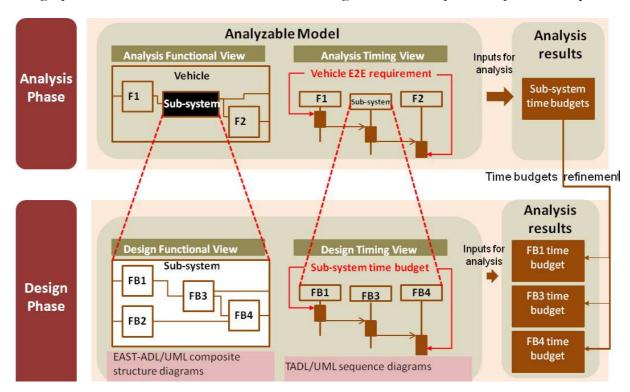

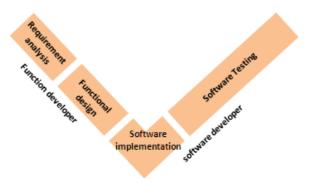

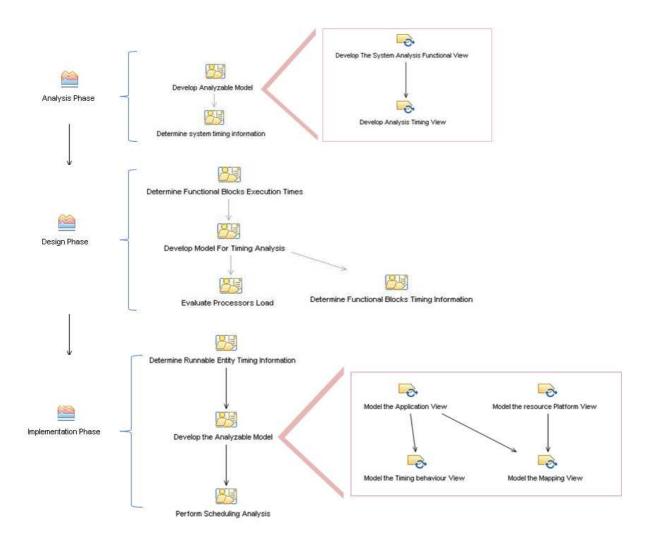

Figure 2 donne une vue générale du processus d'analyse temporelle dirigé par les modèles que la méthodologie vise à définir; aux cours de chaque phase, le concepteur a en entrée un nombre d'exigences temporelle, il conçoit donc l'architecture qui doit respecter ces exigence et puis il effectue une analyse temporelle pour vérifier que l'architecture conçu respecte bien ces exigences.

Figure 2: Processus d'analyse temporelle dirigé par les modèles

## 3.2. Description de la méthodologie :

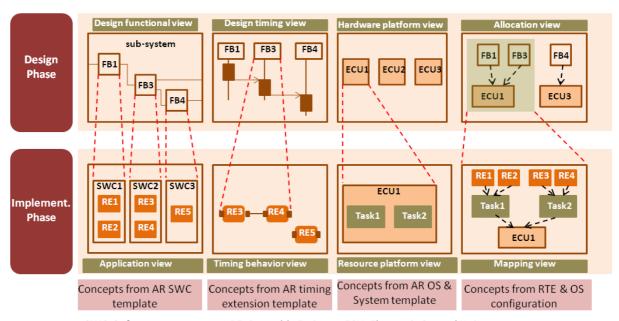

Notre méthodologie propose de réutiliser les niveaux d'abstraction du processus de modélisation d'EAST-ADL/AUTOSAR (figure 2) pour définir notre processus d'analyse temporelle dirigé par les modèles. Cependant, le processus EAST-ADL/AUTOSAR présente seulement les niveaux d'abstraction et les concepts à utiliser à chaque niveau. Il ne

donne aucune approche décrivant la manière d'affiner les modèles d'un niveau à autre. En plus, il ne propose aucune chaine outil pour supporter le processus de développement. Notre méthodologie doit donc adapter et améliorer ce processus pour apporter des solutions pour ces problèmes.

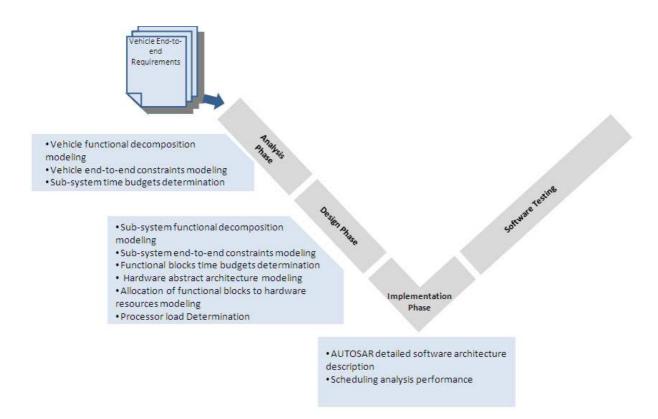

On propose de commencer l'analyse temporelle à partir du niveau Analyse car le niveau Véhicule ne donne pas assez de moyen permettant d'effectuer une analyse temporelle. Notre processus se compose donc de trois phases : Analyse, Design et Implémentation. Sur chaque phase, on décrit les activités de modélisation ainsi que d'analyse temporelles qui doivent se faire.

Le figure 3 donne une vue générale du processus définit. Les paragraphes suivants expliquent les activités effectués durant chaque phase.

Figure 3 Les phases de la méthodologie proposée

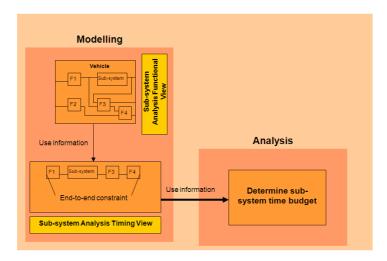

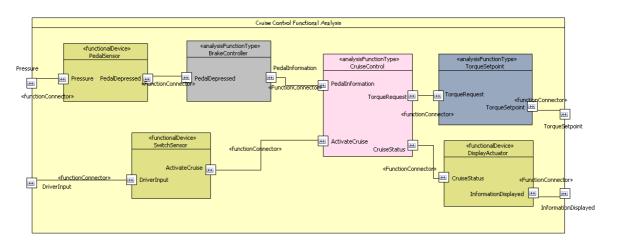

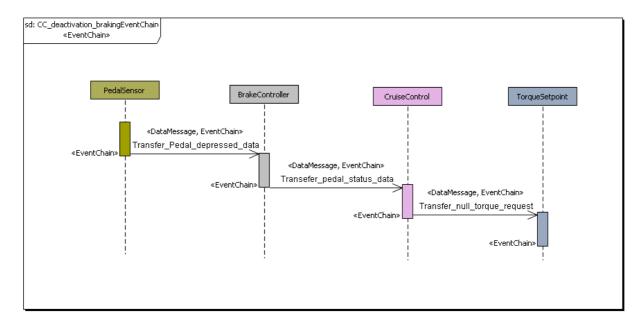

## Phase Analyse

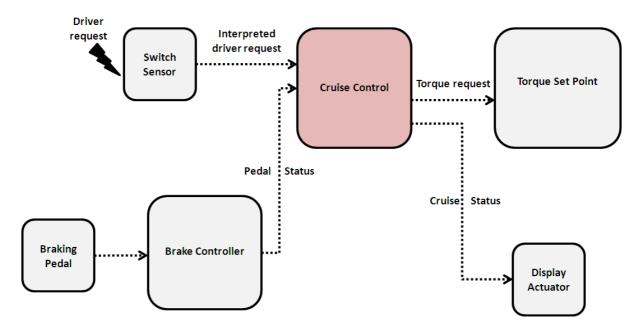

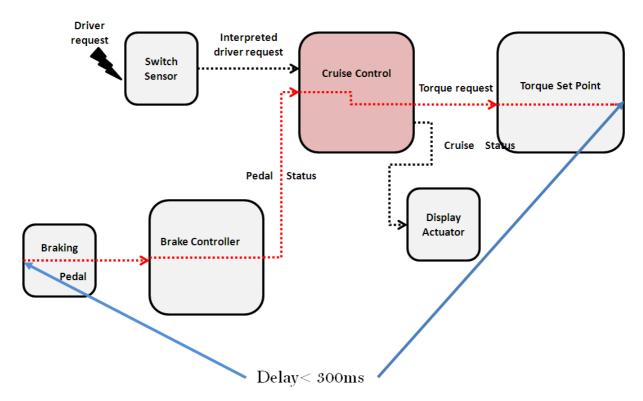

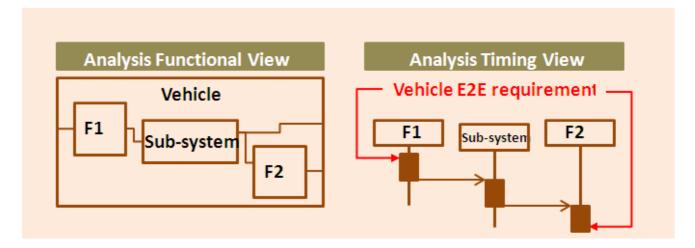

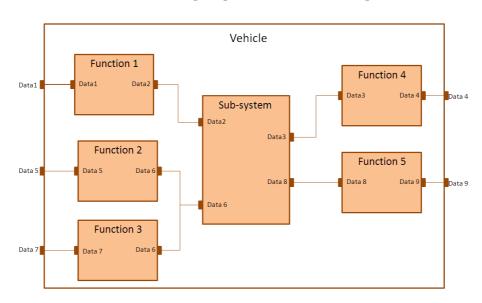

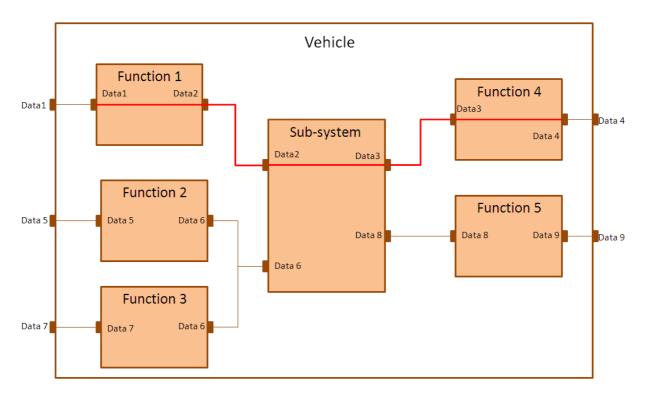

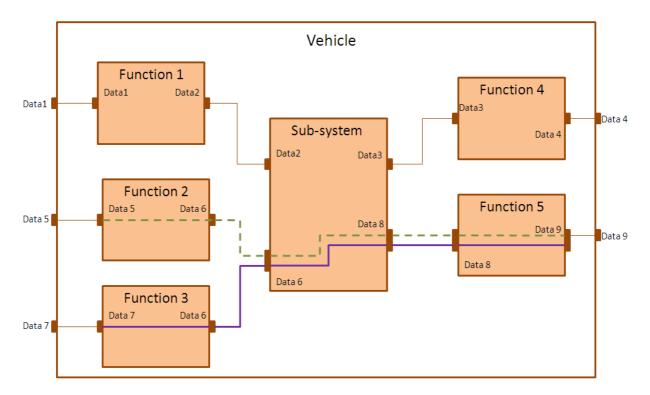

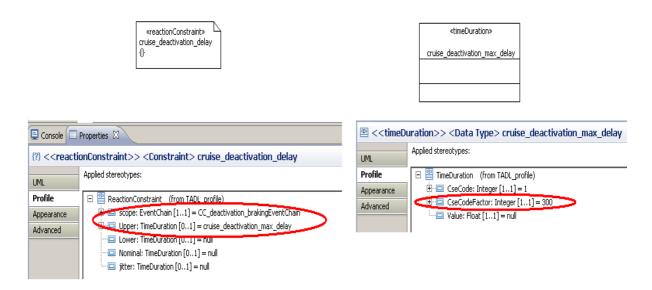

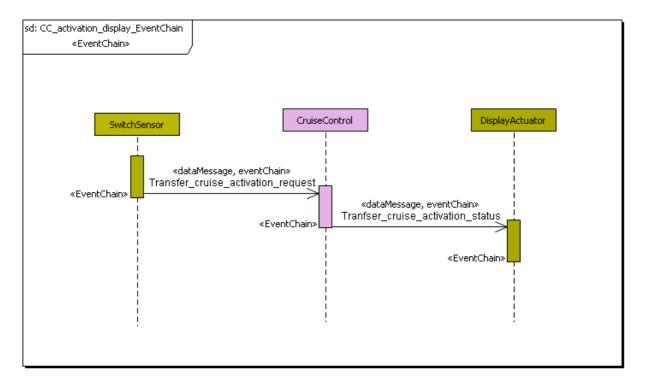

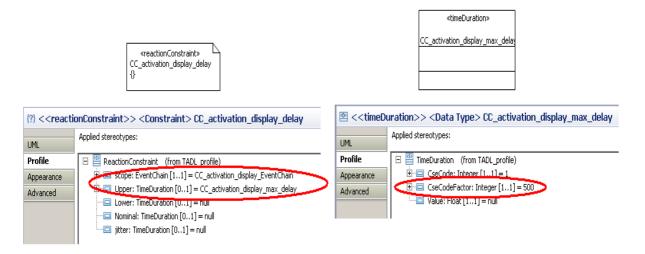

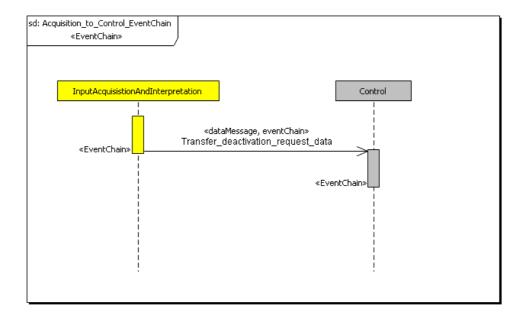

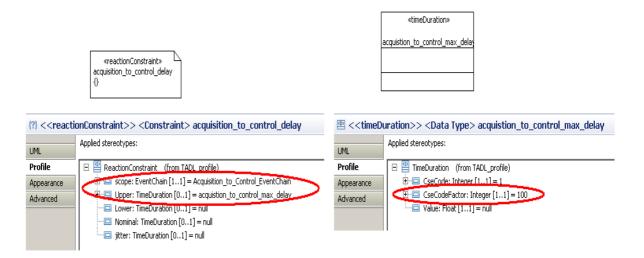

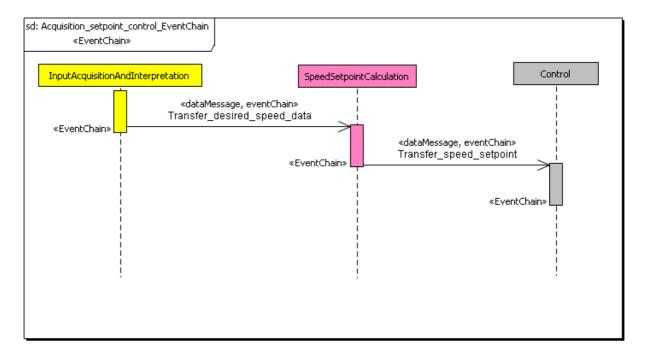

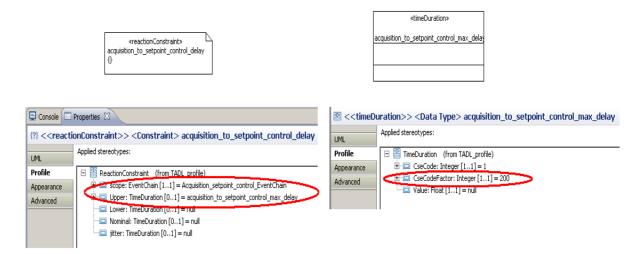

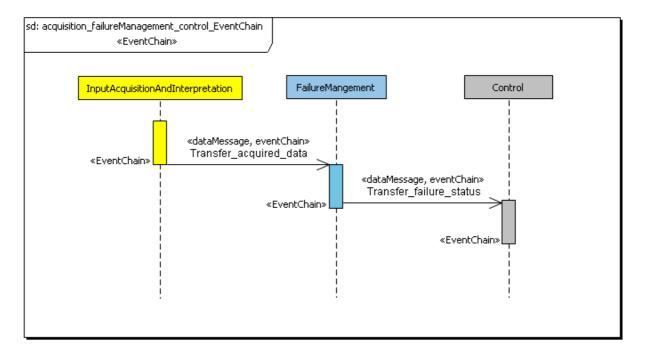

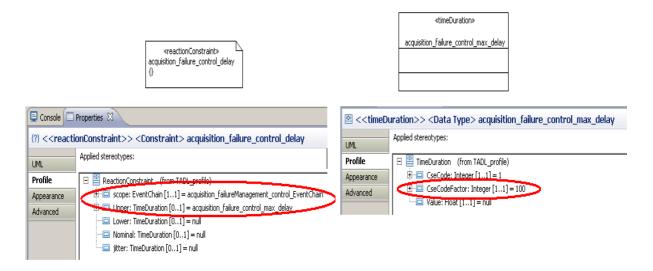

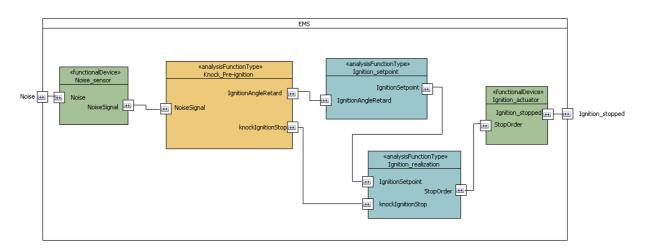

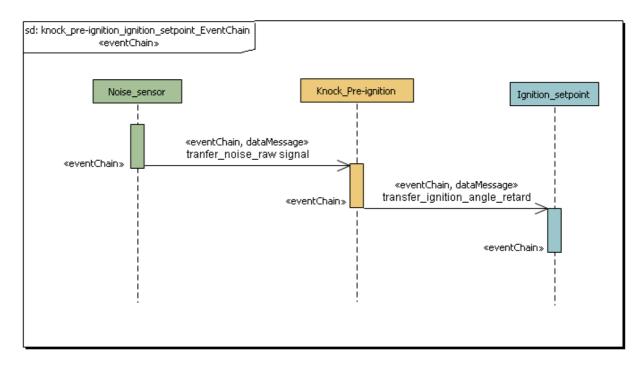

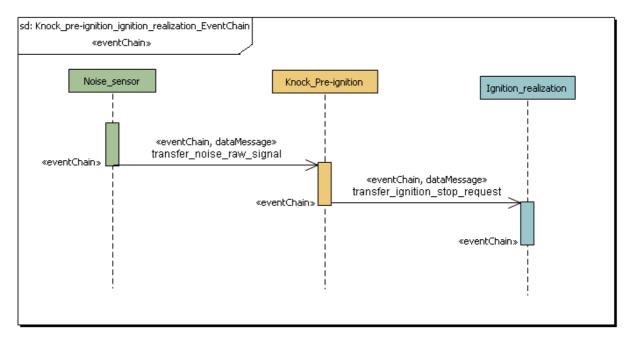

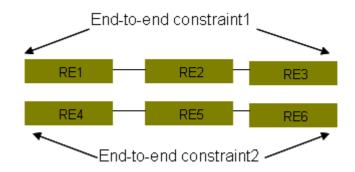

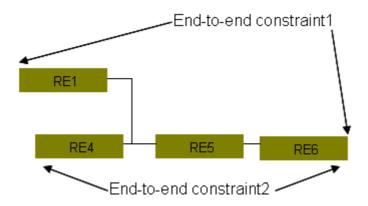

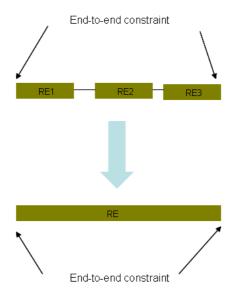

Au cours de cette phase, une vue décrivant l'architecture fonctionnelle du système (« subsystem analysis funtional view ») est développée en utilisant les concepts d'EAST-ADL pour la modélisation fonctionnelle et les « composite structure diagram » d'UML2. Cette vue décrit le système dans son environnement véhicule. Une deuxième vue (« sub-system analysis timing view ») décrivant le comportement temporel du système est développé à partir de la première vue fonctionnelle en utilisant les concepts de TADL et les diagrammes de séquence pour représenter les informations temporelles du système (notamment les contraintes temporelles). L'analyse temporelle effectuée durant cette phase se base sur cette

dernière vue comportementale. L'analyse temporelle de cette phase vise à vérifier la bonne intégration du système dans le véhicule en termes de compatibilité temporelle. Le concepteur a en entrée une liste d'exigences de bout-en-bout (end-to-end requirements). Ces exigences impliquent le système en cours de développement et les autres fonctions du véhicule qui communiquent avec lui. Pour chaque exigence de bout-en-bout, le concepteur doit déterminer un budget temps (« time budget ») qu'il faut allouer au system en cours de développement pour respecter cette exigence. Chaque budget déterminé durant la phase analyse représente une contrainte à respecter durant la phase design. La figure 4 montre les activités de modélisation et d'analyse effectuées durant cette phase.

Figure 4 Activités de modélisation et d'analyse temporelle de la phase Analyse

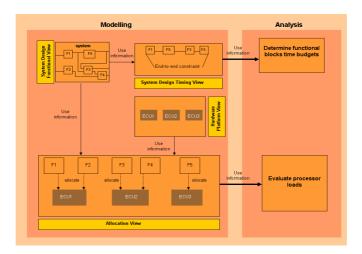

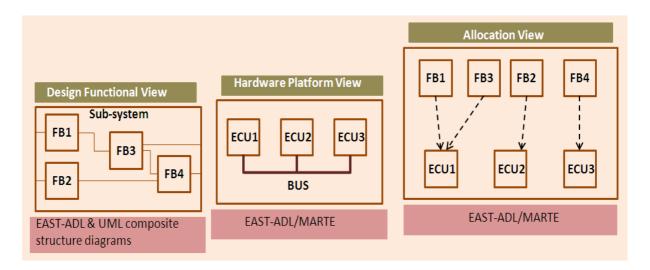

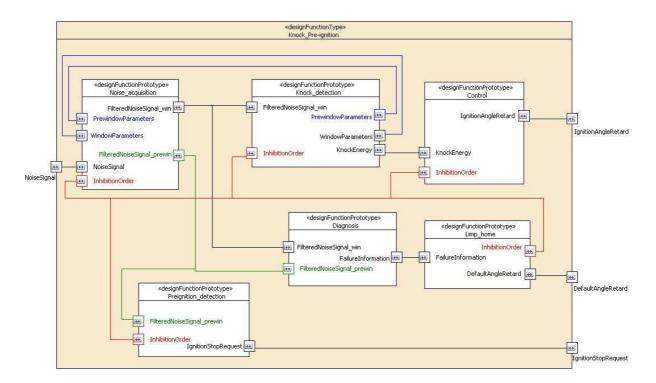

## **Phase Design**

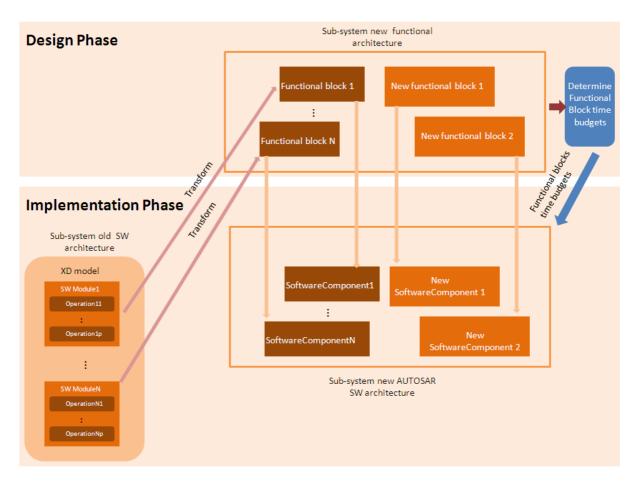

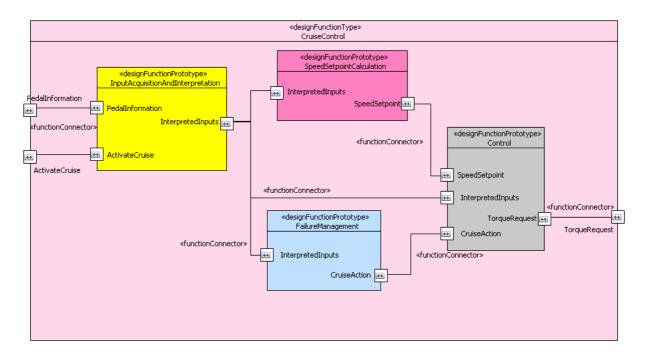

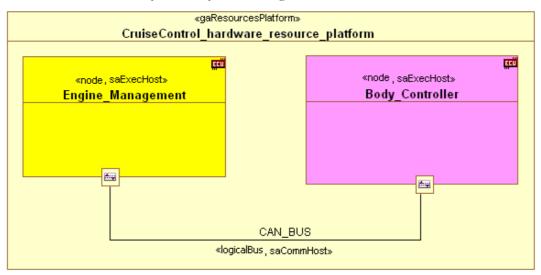

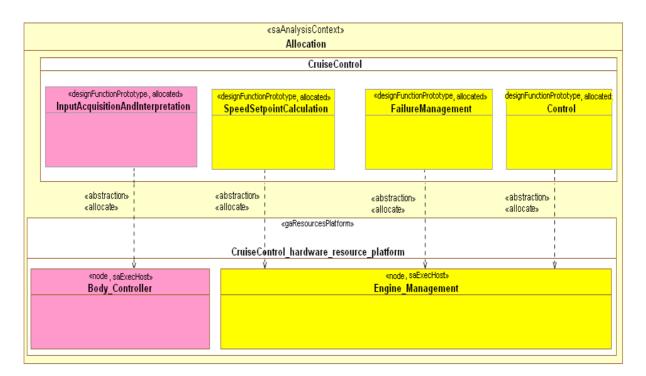

Durant cette phase, la décomposition fonctionnelle du système est représentée à travers une vue qui décrit les blocks fonctionnels qui le composent (« sub-system design functional view »). Les ressources matérielles sont aussi décrites durant cette phase (« hardware platform view »). Le concepteur effectue donc deux types d'analyse temporelle : la première consiste à affiner les budgets temps alloués au system durant la phase précédente (Analyse) en déterminant les budgets temps qu'il faut allouer à chaque block fonctionnel qui le compose. La deuxième analyse temporelle consiste à explorer l'architecture matérielle pour déterminer la meilleure plateforme matérielle à utiliser (en termes de performance) ainsi que le meilleur scénario d'allocation des blocks fonctionnels aux ressources matérielles. Ceci est fait par le biais d'une exploration empirique d'un nombre de scénarios d'allocation candidats qui se base sur le calcul de l'utilisation des processeurs pour chaque scénario.

Remarque : Dans cette dernière analyse temporelle (exploration de l'architecture matérielle), on ne considère pas de modèle de ressources logicielle tel que les tâches OS ni l'allocation des blocks fonctionnels à ces ressources. On considère seulement le modèle fonctionnel, le modèle de ressources matérielles et l'allocation directe des blocks fonctionnels aux ressources matérielles.

La figure 5 montre les activités de modélisation et d'analyse effectuées durant cette phase.

Figure 5 Activités de modélisation et d'analyse temporelle de la phase Design

# **Phase Implementation**

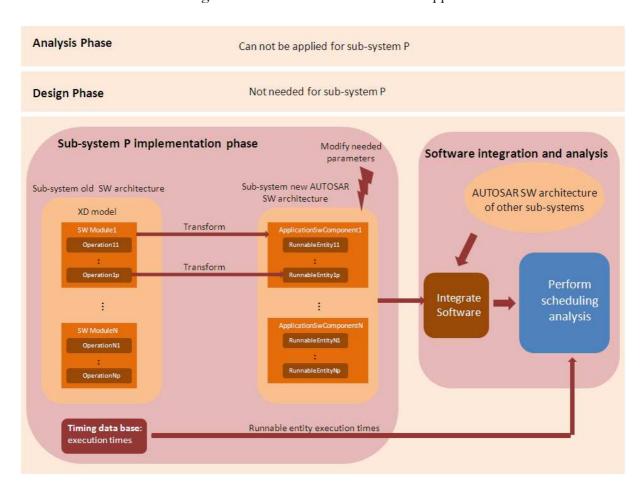

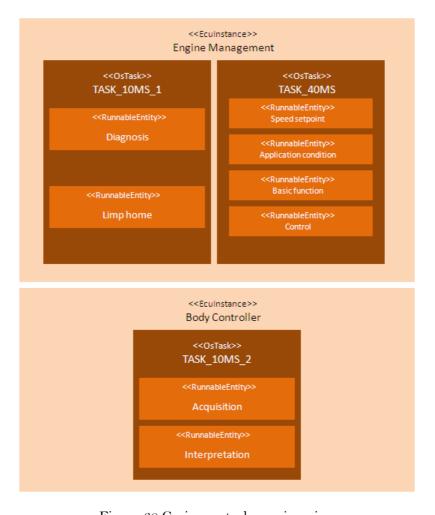

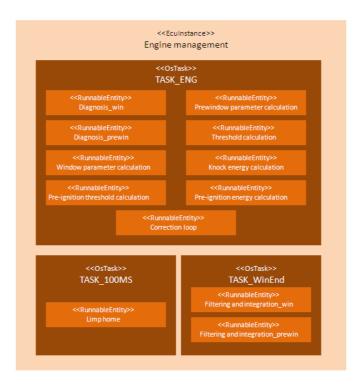

Durant cette phase, un modèle complet décrivant les différents aspects nécessaires pour effectuer une analyse d'ordonnancement (architecture logiciel, ressources logicielle et matérielles, allocation, etc.) est développé en utilisant les concepts d'AUTOSAR. Ce modèle est l'affinement du modèle fonctionnel et matériel développé au cours de la phase design en se basant sur les résultats d'analyse temporelle effectué durant cette phase (design). La figure 6 montre les activités de modélisation et d'analyse effectuées durant cette phase.

Figure 6 Activités de modélisation et d'analyse temporelle de la phase Implémentation

# 4. Déploiement et Validation de la méthodologie

# 4.1. Déploiement de la méthodologie

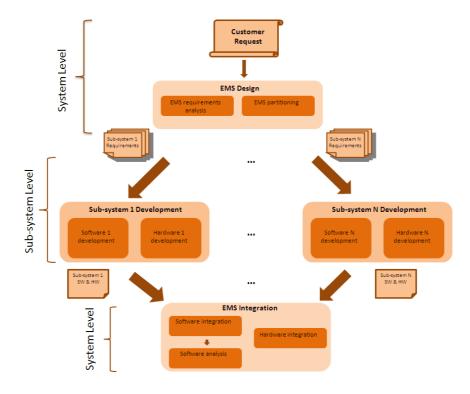

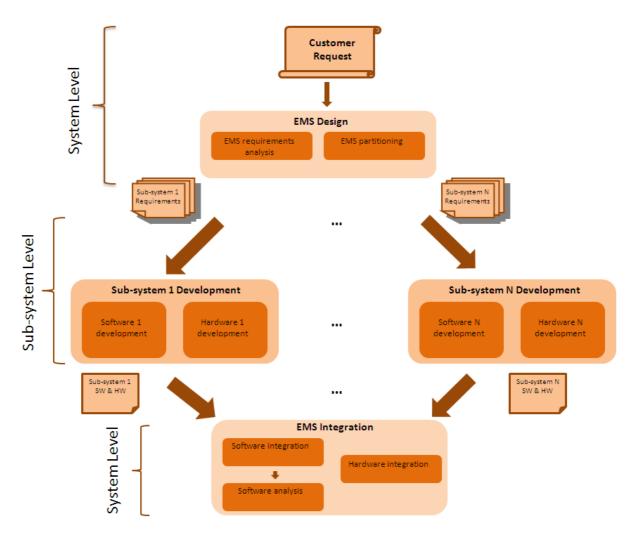

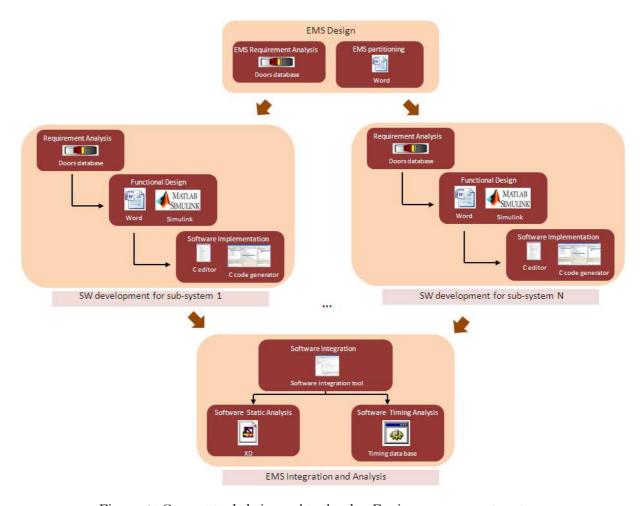

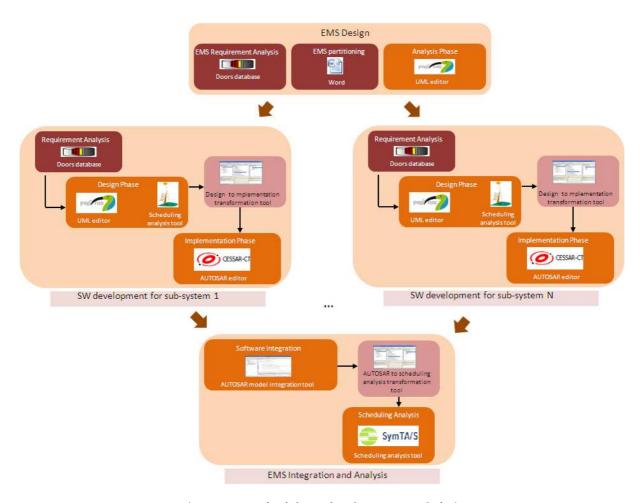

Dans cette partie, on propose une approche de déploiement de la méthodologie en décrivant la manière de l'appliquer dans le contexte de développement des fonctions de contrôle moteur à Continental (EMS). Figure 7 décrit le processus de développement actuel des EMS chez Continental.

Figure 7 Processus actuel de développement des EMS

EMS Page |

EMS requirements analysis |

Chearmination of sub-system |

Sub-system 1 time budget |

Sub-system 1 CPU load budget |

Sub-system 1 CPU load budget |

Sub-system 1 CPU load budget |

Sub-system N charamistion of sub-system (CPU load budget |

Sub-system N charamistion of sub-system (CPU load budget |

Sub-system N charamistion |

Sub-system N charamistic |

Sub-system N charamistion |

Sub-system N charamistic |

Sub-system N cha

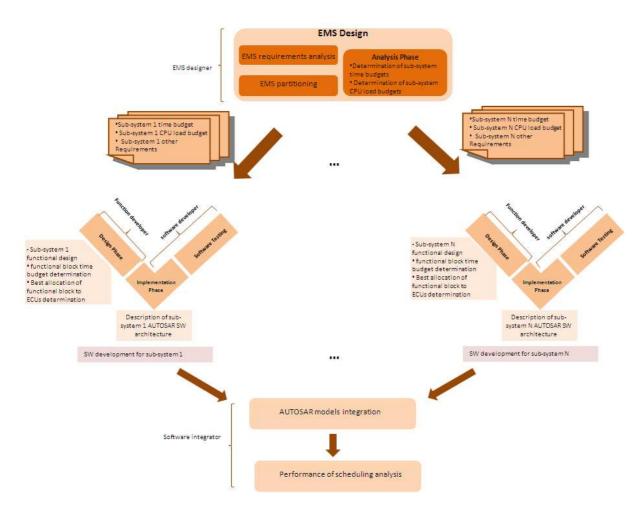

La figure 8 montre ce même processus dans le cas de l'application de notre méthodologie

Figure 8 Application de la méthodologie pour le développement des EMS

# 4.2. Acceptabilité de la méthodologie

En se basant sur l'approche de déploiement décrite précédemment, on a étudié l'acceptabilité de notre méthodologie en termes de compétences demandés, les tâches à effectuer aux cours de chaque phase ainsi que la chaine d'outil proposée. Tous ces éléments ont été comparé avec les compétences, tâches et chaine d'outil utilisé actuellement chez Continental. Cette étude montre un bon potentiel d'adoption de notre méthodologie chez Continental. Ceci est particulièrement valide pour la phase Implémentation de la méthodologie surtout que Continental est en train de migrer vers une nouvelle plateforme basé sur les concepts d'AUTOSAR.

# 4.3. Validation générale de la méthodologie

La contribution de la méthodologie à satisfaire les besoins du développement logiciel automobile (présentés dans la section 1) a été aussi étudiée. La valeur ajoutée de notre méthodologie consiste à donner la possibilité de commencer l'analyse temporelle tôt au cours de processus de développement (beaucoup plus tôt que l'analyse temporelle effectuée actuellement chez Continental). Ceci permet de réduire le temps et le coût nécessaires pour l'amélioration de l'architecture en cas de détection tardive d'erreur. En outre, notre Methodology for Model-based Timing Analysis Process

méthodologie permet une bonne maitrise de la complexité de l'architecture conçue tout au long du processus de développement.

# **Contents**

| INTRODU       | CTION                                                    | 18 |

|---------------|----------------------------------------------------------|----|

| 1. TH         | IESIS TECHNICAL CONTEXT                                  | 19 |

| 2. TH         | IESIS OBJECTIVES                                         | 20 |

| 3. TH         | IESIS OUTLINE                                            | 21 |

| PART I:       | INDUSTRIAL CONTEXT AND RELATED WORK                      | 23 |

| 1. AU'        | TOMOTIVE STATE OF PRACTICE AND CHALLENGES                | 24 |

| 2. Rei        | LATED WORK: MODEL-BASED APPROACHES & TIMING VERIFICATION | 27 |

| 2.1.          | MODEL-BASED APPROACHES                                   | 27 |

| 2.2.          | TIMING VERIFICATION: SCHEDULING ANALYSIS                 | 39 |

| 2.3.          | CONCLUSION                                               | 48 |

| 3. Wo         | ORK ORIENTATION AND APPROACH FEASIBILITY                 | 48 |

| 3.1.          | APPROACH PRINCIPLE AND FEASIBILITY ISSUES                | 48 |

| 3.2.          | Modeling Languages Expressivity Evaluation               | 49 |

| 3.3.          | SCHEDULING ANALYSIS TOOLS EVALUATION                     | 55 |

| 3.4.          | CONCLUSION AND APPROACH DIRECTIONS                       | 66 |

|               | : METHODOLOGY FOR MODEL-BASED TIMING ANALYSIS I          |    |

| •••••         |                                                          | 70 |

| 1. ME         | ETHODOLOGY OVERVIEW & PROCESS PHASES                     | 71 |

| 2. AN         | ALYSIS PHASE                                             | 73 |

| 2.1.          | ANALYSIS OBJECTIVES AND REQUIRED ANALYZABLE MODEL        | 73 |

| 2.2.          | SOLUTIONS FOR ANALYZABLE MODEL AND TIMING ANALYSIS       | 76 |

| 3. <b>D</b> E | SIGN PHASE                                               | 81 |

| 3.1.          | REFINEMENT OF SUB-SYSTEM TIME BUDGETS                    | 81 |

| 3.2.          | PERFORMANCE OF HARDWARE ARCHITECTURE EXPLORATION         | 84 |

| 4. IMI        | PLEMENTATION PHASE                                       | 96 |

| 4.1.          | DETERMINATION OF RUNNABLE ENTITY TIMING INFORMATION      | 96 |

| 4.2.          | DEVELOPMENT OF THE ANALYZABLE MODEL                      | 97 |

| 4.3.                                              | PERFORMANCE OF SCHEDULING ANALYSIS                  | 101   |  |

|---------------------------------------------------|-----------------------------------------------------|-------|--|

| PART III                                          | : METHODOLOGY DEPLOYMENT AND VALIDATION             | . 103 |  |

| 1. ME                                             | THODOLOGY APPLICATION TO EMS DEVELOPMENT            | . 104 |  |

| 1.1.                                              | Introduction                                        | 104   |  |

| 1.2.                                              | ENGINE MANAGEMENT SYSTEM DEVELOPMENT AT CONTINENTAL | 104   |  |

| 1.3.                                              | MIGRATION TO THE NEW METHODOLOGY PROCESS            | 108   |  |

| 2. EXA                                            | AMPLES                                              | . 117 |  |

| 2.1.                                              | DEVELOPMENT FROM SCRATCH: CRUISE CONTROL            | 117   |  |

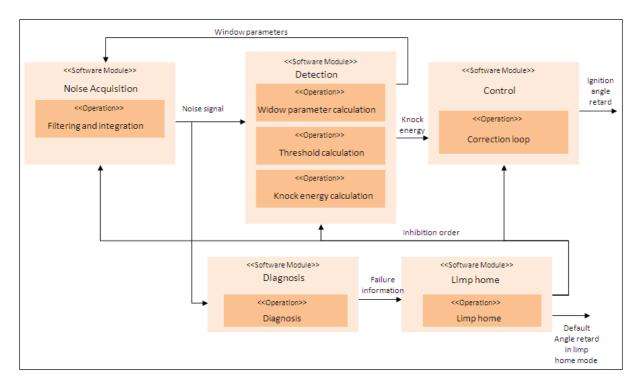

| 2.2.                                              | DEVELOPMENT BY REUSE: KNOCK                         | 136   |  |

| 3. ABO                                            | OUT THE METHODOLOGY ACCEPTABILITY                   | . 153 |  |

| 3.1.                                              | TASKS, ROLES, SKILLS                                | 153   |  |

| 3.2.                                              | TOOL SUPPORT                                        | 159   |  |

| 3.3.                                              | METHODOLOGY TOOLING                                 | 164   |  |

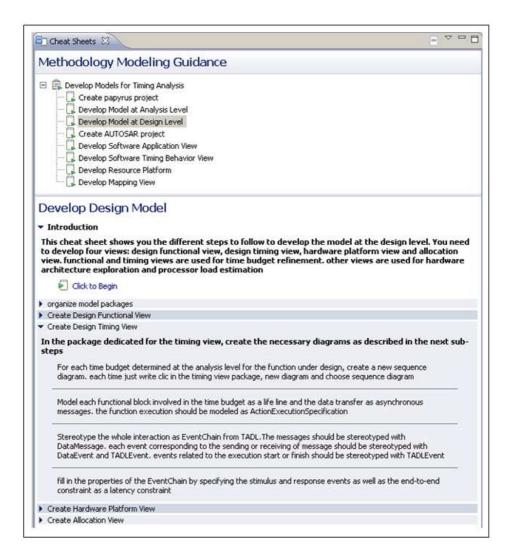

| 3.3.2.                                            | CHEAT SHEET GUIDES                                  | 165   |  |

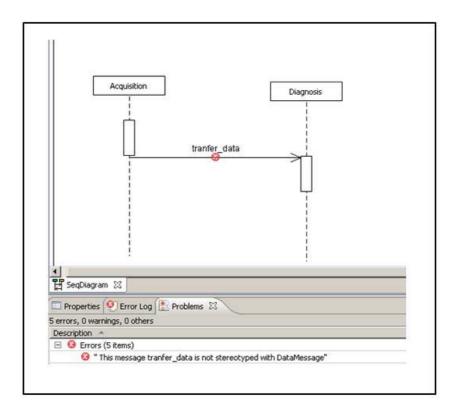

| 3.3.3.                                            | MODEL VALIDATION RULES                              | 166   |  |

| 4. ME                                             | THODOLOGY GENERAL VALIDATION                        | . 168 |  |

| 4.1.                                              | SYSTEM COMPLEXITY MASTERING                         | 168   |  |

| 4.2.                                              | DEVELOPMENT TIME AND COST REDUCTION                 | 168   |  |

| 4.3.                                              | SEAMLESS DEVELOPMENT PROCESS                        | 170   |  |

| 4.4.                                              | ENABLING TIMING VERIFICATION                        | 170   |  |

| CONCLUSION AND PERSPECTIVES173                    |                                                     |       |  |

| ANNEX1: DEFINITION OF AN AUTOSAR OS TASK MODEL177 |                                                     |       |  |

| PEFFRENCES 105                                    |                                                     |       |  |

# Introduction

This chapter introduces the thesis work that has been performed in the context of a technical collaboration between the CEA LIST near Paris and the Advanced Development Electronics (ADE) service of Continental Automotive in Toulouse.

CEA LIST is a key software system and technology research center whose mission consists among others in providing methodologies and tools for real time embedded system development (systems architecture and design, methods and facilities for software and system dependability, etc). This laboratory works on several research projects in partnership with industrial partners from nuclear, automotive, aeronautical, defense and medical domains. Thus, the laboratory investigates and develops innovative solutions corresponding to the requirements of these industrial partners.

The ADE service is a part of the Engine System (ES) business unit within the Powertrain division at Continental. This service provides innovative techniques and methodologies for the development of automotive electronic systems. These innovative approaches aim at providing solutions for the challenges met to develop Engine Management Systems (EMS) within the ES business unit. An Engine Management System (EMS) is a system used to control the engine functionalities (e.g., Combustion, injection, ignition, etc). At Continental, Engine Management Systems are developed to control many types of gasoline and diesel engines for many customers all over the world. To develop these systems, many requirements should be satisfied, including customer requirements but also environmental norms (gas emission). In addition, due to the competition factor, development time and cost for engine management systems should be mastered. The ADE service investigates innovative approaches to meet all these challenges in future engine management system generations.

This introduction is divided in three sections. The first section presents a brief overview of the general technical context in which this work has been done. The second section presents the thesis objectives and the third section describes the outline of the manuscript.

# 1. Thesis Technical Context

Automotive real time systems are characterized by increasing complexity and tight requirements for safety and timing. Today, highly competitive automotive industries developing real-time systems must face industry requirements both quickly and dependably. "Quickly" refers to the "time-to-market" issue, where delays in design or implementation incur penalties and reduce market profit. "Dependably" refers to the trustworthiness of the services provided by developed systems. One of the key dependability factors in real time systems is system failure. Unlike fabrication faults and faults during usage, design faults are supposed to be found and eliminated by system verification. Hence, whenever fault tolerance cannot be guaranteed, fault prevention is the only way to avoid system failure [13].

Quantitative analysis [1] (such as performance and scheduling analysis) is a sound approach to study non-functional properties at an early stage. It allows designers to detect unfeasible real-time architectures, prevent costly design mistakes, and provide an analytical basis to assess design tradeoffs associated to resource optimization. Quantitative analysis uses mathematical-based techniques which purpose is to prove that a system meets its requirements at any time. While the maturity of quantitative techniques has led to a set of well established mathematical formalisms such as rate monotonic analysis (RMA) [2], Petri nets [3], queuing theory [4] and timed automata [5], their widespread use with complex industrial systems and into integrated tool environments still remains largely open. Quantitative analysis is a difficult and time-consuming task, and to save time, many industries either forgo it until absolutely necessary or train their designers to perform preliminary analysis. However, most designers are under-trained in analysis and too busy to perform useful analysis.

Model-Based Engineering (MBE) is gaining momentum in automotive system and software development domains, as a means for mastering system complexity and assessing system-level tradeoffs geared to achieving higher quality and dependability [6]. MBE and modeling languages lead a major approach to enrich real-time systems engineering practices, by moving the development process from lines-of-code to coarser-grained architectural elements. One of the advantages expected from this approach is the ability to employ correct-by-construction, but also incremental design processes (which rely extensively on automated transformations and synthesis) and to formalize computer-based correctness analysis.

The model-based development community has invested special efforts in incorporating the abilities to specify analytical constructs and non-functional properties with enough expressive power, while still preserving the modeling abstraction level used by MBE practitioners. Important research work has been carried out in order to provide modeling languages (e.g., UML [7], SDL [8], AADL [9], MARTE [10], and TADL [11]) with clear and well-formed semantics to support quantitative analysis.

However, most of the current works are characterized by providing only means and concepts for the modeling of non-functional and especially timing information of the system. Unfortunately, none of these approaches provide sufficient guidance on how to integrate timing verification and validation into the model-based development process.

# 2. Thesis Objectives

The underlying work investigates the definition of a methodology describing a model-based timing verification process for automotive systems. It aims at giving guidance to software development engineers about how to integrate timing verification within a model-based development process enabling hence early detection of time-related errors.

In particular, this thesis work focus on the following specific objectives:

- 1. One fundamental objective that drove our research work is the definition of a model-based development process ensuring a seamless development activity that can be easily adopted in the context of engine management system development. The methodology defined should describe the different phases of the model-based process and how models should be refined from one phase to another.

- 2. The second objective is to give guidance on how to integrate timing verification in each phase of this development process. This means defining the kind of timing verification that should be performed during each phase, the verification techniques and tools that can be used and how analysis results of each phase can be used to refine the architecture during the next phase.

- 3. From a modeling and analysis point of view, the methodology defined should give a way on how to develop analyzable models in each phase and especially how to derive behavioral views needed for timing analysis from modeling views intended e.g. for structure description.

4. Besides the definition of the methodology itself, in this work we aim to validate the methodology suggested by evaluating its degree of acceptability and showing to which extent it allows resolving the problems faced currently in the context of automotive software development.

# 3. Thesis Outline

This manuscript is composed of three major parts. The first part contains three chapters. The first chapter describes precisely the particular context of this study related to the development of automotive software in the particular case of Continental as a supplier. This chapter ends by listing the needs of automotive domain in term of software development. The second chapter gives an investigation and a state-of the art of the available model-based approaches that attempted to bring answers and solutions to some of these needs. The third chapter draws the general features of our approach to define a methodology for a model-based timing analysis process. This is done after studying the feasibility of the approach based on the chosen directions that will be presented in the same chapter.

The second part of the manuscript presents the methodology itself. This part is composed of four chapters. The first chapter gives a general overview of the defined process. The remaining three chapters tackle respectively the different process phases, the analysis phase, the design phase and the implementation phase. Each chapter describes both the modeling and timing analysis activities carried out during each phase.

The third part is dedicated to the deployment and validation of the proposed methodology. This part is composed of four chapters. The first chapter presents an approach describing how we intend to apply our methodology for the development of Engine Management Systems (EMS) at Continental. The second chapter illustrates the approach by presenting the application of the methodology to the development of two use cases. The third chapter studies the acceptability of the methodology by showing the extent to which this methodology can be adopted by Continental engineers. In this chapter we identify the gap between the proposed methodology and the current development process at Continental in terms of required vs. available skills, tasks, tool chain, etc.

The methodology tooling is also studied by presenting the tools that were implemented to guide Continental engineers and ease their use of the methodology.

The last chapter of this part presents the final validation of the methodology by showing to which extent it provides solutions for the automotive software development needs determined during the first part of this work.

The conclusion summarizes the study and discusses the possible perspectives for this work.

# Part I: Industrial Context and Related Work

This first part aims at describing in detail the industrial context in which this thesis work was done. The technical directions chosen for this work to meet the automotive domain needs are presented and justified based on this context itself but also based on some already available approaches. The first chapter presents the automotive context and highlights the automotive needs in term of software development and timing verification. The second chapter presents the available approaches that attempted to bring solutions for these needs. We highlight the limitations of these approaches and we conclude on the need for a new approach to satisfy better the automotive needs. The third chapter gives a general overview of the directions chosen for our work based on the available approaches and a feasibility study for our approach.

# 1. Automotive State of Practice and Challenges

In the automotive domain, the first time that software was deployed into cars was to control the engine and, in particular, the ignition, 30 years ago [6]. At the beginning of software deployment in cars, software-based solutions were very local, isolated and unrelated. Hence, there were dedicated controllers (Electronic Control Units or ECUs) for the different functions as well as dedicated sensors and actuators. With the intention to optimize wiring, bus systems were deployed into cars allowing ECUs to be connected to each other and exchange information.

Today, premium cars feature not less than 70 ECUs connected by more than five different bus systems [6]. Within only 30 years, the amount of software in cars went from zero to more than 10.000.000 lines of code. More than 2000 individual functions are realized or controlled by software in premium cars. Software as well as hardware became enabling technologies in cars. They enable new features and functionalities. Hardware is becoming more and more a commodity while software determines the functionality and therefore becomes the dominant factor for system complexity.

To understand better the automotive needs in term of software development, it is important to clarify the state of practice in this domain. The development of a car involves mainly two partners, the manufacturer (OEM) and the first-tier suppliers. The aim of the manufacturer is to market cars that satisfy the needs and the desires of the customers, on one hand by respecting the manufacturing standards and norms and on the other hand by ensuring the prosperity of his group [12]. For these reasons, manufacturers have usually a strong and global trade expertise. A car can be seen as an assembly of many systems integrated together to ensure the various functionalities of the vehicle. The OEM intervenes during two particular phases, the specification of systems and their integration into the vehicle. The development of these systems is then carried out by the different suppliers that are involved; such as the case of Continental Automotive. Once the request is specified by the manufacturer, the supplier should develop the system that respects the requirements specified. In this context of multi-partner development, the systems developed by a supplier are more and more sophisticated and require usually highly specialized technical skills. Due to concurrency pressure, manufacturers choose then to delegate the development of such systems to several suppliers and focus only on vehicle integration and validation. In the case of Continental Automotive, a system requested by a manufacturer may vary from a simple software component to a whole system consisting of software, hardware (ECU) and mechanics (actuators, etc).

Being able to satisfy efficiently customer request is the key factor for a supplier to save his place in market. Efficiently means quickly, dependably and in a cost-efficient way. Quickly refers to the time-to-delivery where the supplier is continuously submitted to the customer pressure to deliver systems as early as possible. Development cost is also among the decisive factors that guarantee the competitiveness of a supplier. Up to 40% of the production costs of a car are due to electronics and software. Today, the costs of cars get more and more influenced by development costs of software; 50-70% of the development costs of the software/hardware systems are software costs [6].

Dependability means the trustworthiness of the service delivered by the developed system. To develop dependable systems, suppliers should take up many challenges. In fact, the size and structure of the embedded software and hardware in cars are enormous. Most of the software is hard real time critical or at least soft real time critical. Several functions are safety critical ones. In addition, car functions are quite heterogeneous (from embedded real time control to infotainment, from comfort functions to driver assistance, etc). As a result, the complexity and spectrum of requirements for on board software is enormous. In front of this complexity and time/cost pressure, suppliers have usually recourse to reuse existing solutions from one car to the next. However this remains insufficient with regard to development time and cost¹. In addition, the amount of automation in software production is today quite low. Tools are many times used in an isolated manner. There is neither a properly formalized design flow nor seamless tool chain for distributed functions.

It is hence obvious that there is a need for a suitable development process that reduces complexity, enables innovation and saves time and costs.

Guaranteeing dependability is not ensured only by mastering system complexity. In fact verification and validation is also of paramount importance in software development. This allows verifying the proper functioning of the system and validating it against the requirements specified by the customer. As mentioned previously, developing time critical systems is among the challenges that suppliers should take up. Mastering the development

<sup>&</sup>lt;sup>1</sup> This statement is based on the study of the state of practice of software development at Continental

of such systems requires being able to understand, analyze and validate their real time behavior. Automotive software development costs are significantly impacted by wrong design choices made in the early stages of development, but often detected after implementation. Most timing-related failures are detected very late in the development process, during implementation or system integration phases. Timing verification is usually addressed by means of measuring and testing rather than through formal and systematic analysis. For this reason, innovative and complex functionalities are not implemented in a cost-efficient way.

The need for defining an approach that permits timing verification throughout the development process, starting from the early phases of design, is thus obvious

Such an approach would enable early prediction of system timing behavior and allow potential weak points in design to be corrected as early as possible.

To conclude, in automotive software development, there is an obvious need today for development approaches that allow:

- Mastering system complexity

- Reducing software development time and cost

- Defining seamless development activity supported by a seamless tool chain

- Ensuring system dependability, especially timing correctness through verification and validation.

During the last decade, many approaches, methods and techniques have been developed to bring solutions for the abovementioned automotive needs. For example, model based engineering is gaining momentum in the automotive domain, as a means intended for mastering system complexity and assessing system-level tradeoffs geared to achieve higher quality and dependability.

Continental supports the development and the use of several model-based development approaches such as AUTOSAR [18], EAST-ADL [46] and TADL [48]. The directions of our work are chosen with respect to this context.

In the domain of timing verifications, we can talk especially about quantitative techniques (scheduling and performance analysis) where a variety of schedulability tests and tools have been developed as a means to predict early real time system behavior.

In this thesis work, we focus on a key problem of automotive industry which is software timing verification. After studying available approaches that attempted to bring answers to automotive needs in the next sections, we present, in the second part of this manuscript, a methodology enabling the integration of timing verification in a model-based development process.

# 2. Related Work: Model-based Approaches & Timing Verification

# 2.1. Model-based Approaches

# 2.1.1. Basics of Modeling Languages

As engineers work with many different kinds of models, it is important to understand which models are dealt with in this thesis. Therefore, few definitions are given to provide a basis to understand the rest of the thesis. [13]

#### Models and Metamodels

Models, as conceived in engineering, are representations of reality. The aim of the engineering modeling process is to make our world measurable, calculable, predictable, and thus more manageable. Computer models are computerized abstractions, data structures, or simulations of, not only real systems or phenomena, but also of fictional objects, settheoretic structures and mathematical representations.

To know the nature of different models used in computer systems, we may identify two relationships. The first relationship, called "represented by", identifies a representation role of a given modeled object over a model. For instance, a computer program can be "represented by" a set of data flow diagrams. A given model could also represent another model. For example, a mathematical function can be represented by a numerical approximation. The second relationship, called "conforms to", identifies a dependency of a given model on a modeling language. Thus, we could say that a given data flow diagram representing a piece of programming code conforms to the rules and modeling elements defined, for example, for Gane-Sarson diagrams. [13]

In MBE, the latter relationships receive special attention since domain specific modeling languages are described and prescribed by models. These models are called *metamodels*. A metamodel is yet another abstraction highlighting properties of the model itself. This model is said to conform to its metamodel like a program conforms to the grammar of the programming language in which it is written. This means that a metamodel describes the various kinds of contained model elements and the way they are arranged, related and constrained.

# UML Profile Basics

In this thesis work, some notions related to the definition and use of UML profiles are used. We describe here some basic notions related to this issue.

Profiles [14] are the built-in lightweight mechanism that serves to extend Meta Object Facility (MOF)-based languages. More specifically, profiles are used to customize UML for a specific domain or purpose via extension mechanisms that enrich the semantics and syntax of the language. A *stereotype* is the basic feature for UML extension. It can be viewed as the specialization of an existing UML concept, which provides capability for modeling domain-specific concepts or patterns. Stereotypes may have attributes (also called *tags*) and be associated with other stereotypes or existing UML concepts. From a notational viewpoint, stereotypes can give a different graphical symbol for UML model elements. For instance, a class stereotyped as «clock» might use a picture of a clock symbol instead of the ordinary class symbol. Additionally, stereotypes can also be influenced by restrictions expressed in constraints. The standard machine-readable textual language for defining constraints in MOF-based languages is Object Constraint Language (OCL) [15].

# 2.1.2. Model-Based Development in Automotive Domain

Model-based and component-based approaches are gaining more and more success and popularity in today's automotive software domain. This success is due to the state of practice and the way of proceeding in this domain [6]. In fact, in order to integrate one software unit into the car, a supplier must design, integrate and test against the units of other suppliers. Since the code inside the units (e.g. ECUs) is the intellectual property of the suppliers, the other supplier (or the OEM) often will not get the code of the other units. As a consequence, both have to build up some kind of "black box model" that they code/integrate/test against. The high degree of interaction between OEM and suppliers makes the need for clear interfaces and specifications evident. Models that take into account the static and dynamic

aspects of sub-systems are attractive ways to specify the sub-systems architecture, syntactic interfaces and behavior. Models could help very much in the communication between OEMs and first and second tier suppliers. But, the major advantage expected from model based development is the ability to employ correct-by-construction, but also incremental design processes (which rely extensively on automated transformations and synthesis) and to formalize computer-based correctness analysis. In addition, there are many claims that model-based and component-based approaches using architecture description languages can help improve the overall system quality, foster reuse and evolution, and increase the potential for automatic validation and verification.

The root of model based development is the advent of UML (Unified Modeling Language) [7] as a standard modeling language. However, the general-purpose aspect of UML made its use complicated for specific domains as it requires mastering in detail UML concepts. UML use becomes hence difficult for engineers who are expected to have domain skills and knowledge rather than UML knowledge. As a consequence, this led to the advent of domain specific languages, DSL [16]. Domain-specific languages allowed modeling concepts to map directly domain concepts rather than computer technology concepts.

In automotive domain, several modeling approaches and languages have been developed during the last decade to cope with automotive software development challenges. These approaches give means and concepts to capture the electric/electronic automotive architecture such is the case of the modeling languages EAST-ADL [17] and AUTOSAR [18]. For real time modeling, we cite TADL [11] and also MARTE [10], the OMG language for modeling and analysis of real time systems.

The next section gives a detailed overview of these approaches.

## 2.1.3. Model Based Approaches Presentation

#### EAST-ADL

EAST-ADL [46] (Electronic Architecture and Software Technology-Architecture Description language) is intended to capture the electric/electronic architecture of automotive systems at different level of abstraction ranging from feature to implementation level. EAST-ADL has been developed and improved in the context of several research projects. The last available version of EAST-ADL has been developed in the context of the ATESST2 project [17].

EAST-ADL provides a rich set of concepts to model system structure through several levels of abstraction. From one level to another, the structural model of the system is refined by including more precise implementation oriented details. Figure 1 shows an overview of the EAST-ADL abstraction levels. Note that, as shown in this figure, the Implementation level of EAST-ADL is based on AUTOSAR.

Figure 1 EAST-ADL/AUTOSAR modeling process

Modelling of vehicle electronic systems with EAST-ADL starts with the capture of features at the Feature level, thus providing product line organization and description. These features are then realized at Analysis level by abstract entities, which model the functions and functional devices that interact with the vehicle environment. At the Design level, models are refined by including more realization-oriented details that allow subsequent decomposition/refinement of the functional architecture. The Hardware Design Architecture, which is denoted in parallel, captures the primary hardware entities as abstract elements (e.g. sensor, actuator, power, ECU or electrical wiring including the communication bus) to describe the topology of the system's electronic architecture.

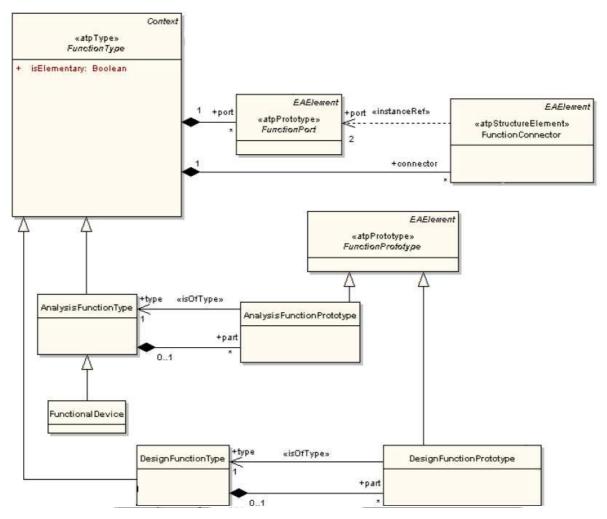

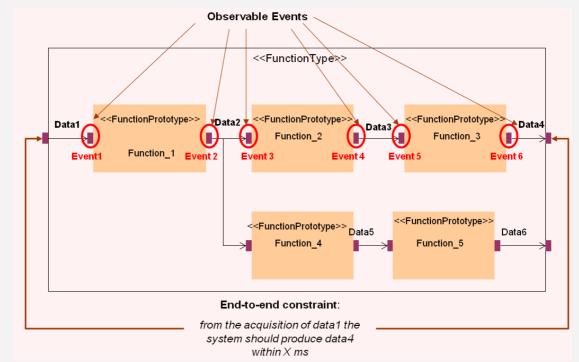

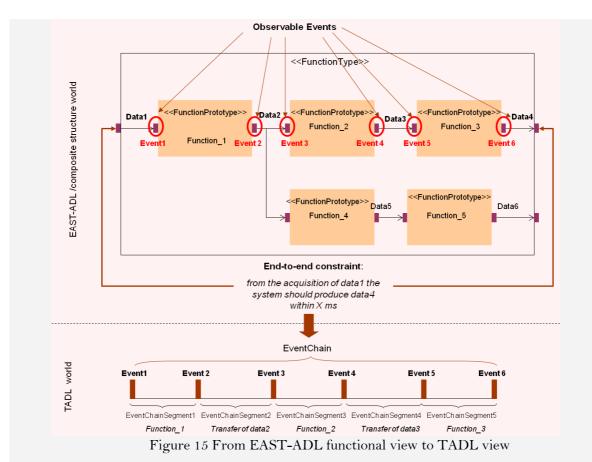

EAST-ADL gives means and concepts to model system functional architecture [47]. Figure 2 gives an overview of the EAST-ADL metamodel for functional modelling. Modelling of functional architecture with EAST-ADL is based on the core concept of "FunctionType". A "FunctionType" is used to model system functions at both Analysis level ("AnalysisFunctionType") and Design level ("DesignFunctionType"). An ("AnalysisFunctionType" (respectively ("DesignFunctionType") can be composed of "AnalysisFunctionPrototypes" (respectively "DesignFunctionPrototypes") that represent its sub functions. Interaction

between EAST-ADL FunctionTypes is captured through "FunctionPort" and "FunctionConnector" concepts.

Figure 2 EAST-ADL metamodel for functional modelling [47]

EAST-ADL also provides concepts for abstract hardware modelling. For example sensors and actuators can be captured respectively through the concepts "sensor" and "actuator" from EAST-ADL. Communication buses can be modelled as "LogicalBus". The concept "Node" allows modelling ECUs involved in the system.

For timing modelling, EAST-ADL adopted TADL concepts to annotate architecture models with timing properties and constraints.

# TADL

TADL (Timing Augmented Description Language) [48] has been developed in the context of the European research project TIMMO (TIMing MOdeling) [11]. The definition of TADL is based on modelling concepts from EAST-ADL and AUTOSAR by which the

structural definition of the considered system is modelled. The augmentation is done by adding information related to timing and events referring to structural elements [48].

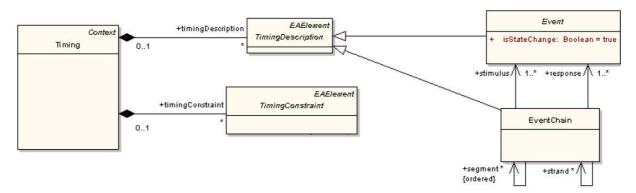

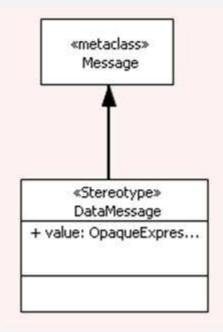

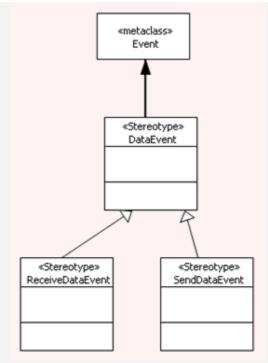

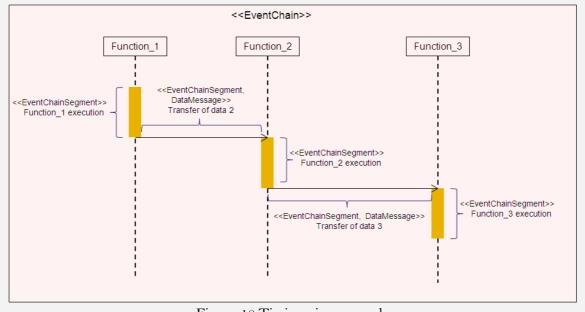

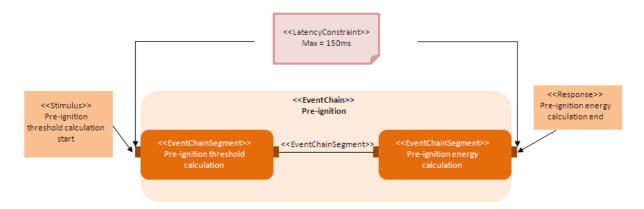

TADL proposes a set of concepts to annotate structural models (function and software) with timing properties and constraints such as maximum delays, repetitions and sampling rates and synchronization constraints [49]. Figure 3 gives an overview of the TADL metamodel. TADL concepts are centred on the concepts of "Event" and "EventChain". An "EventChain" describes the causal relationship of a set of functionality-dependant events. Every event chain describes a causal relationship between two events. The first is called "Stimulus" (e.g. event representing the activation of a function) and the second is called "Response" (e.g. event representing the termination of a function). Furthermore, event chains can be hierarchically decomposed into an arbitrary number of sub-chains called "EventChainSegment". TADL timing constraints can be attached to events and event chains to specify e.g. the repetition rate of an event or the maximum latency of an event chain.

Figure 3 TADL metamodel [49]

#### AUTOSAR

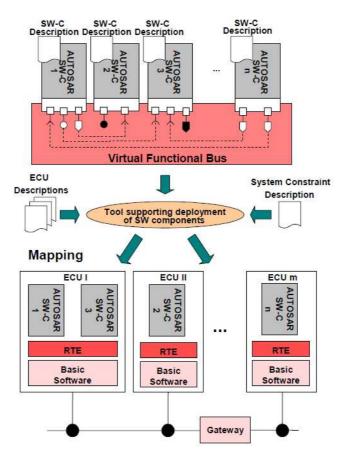

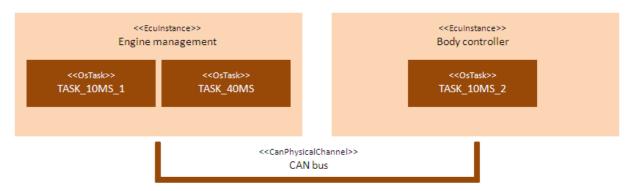

AUTOSAR (Automotive Open System Architecture) [18] is a standardized architecture for automotive software that is developed by an international consortium of automotive OEMs, Tier-1 suppliers and tool vendors. AUTOSAR offers a software component model and a three layered software architecture divided into application software, runtime environment (RTE), and basic software (e.g., drivers and communication system). Figure 4 shows an overview of AUTOSAR software architecture.

Figure 4 AUTOSAR software architecture from VFB to mapping

AUTOSAR introduces the Virtual Functional Bus (VFB) concept to separate applications from infrastructure. An application consists of interconnected "AUTOSAR Software Components". The VFB (shown in the top part of figure 4) provides standardized communication mechanisms and services for these components. The VFB acts independently from the chosen mapping of these components to the infrastructure of the interconnected ECUs (shown in the bottom part of the figure 4).

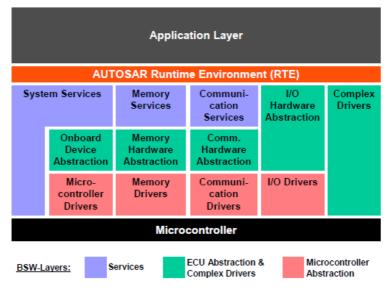

The realization of the VFB concept is possible if each AUTOSAR ECU has standardized basic software functionalities and interfaces. Figure 5 shows the layered architecture of an AUTOSAR ECU, which basically identifies an application layer and the AUTOSAR Basic Software (BSW). These parts are linked via the AUTOSAR Runtime Environment (RTE). That means the RTE can be interpreted as the runtime implementation of the VFB on a specific ECU.

The RTE realizes an intermediate layer between the hardware independent application software components and the hardware dependent basic software components.

Figure 5 The AUTOSAR ECU layered architecture

The reuse of software components between different vehicle platforms, OEMs and suppliers is one of the major goals of AUTOSAR. Therefore a methodology supporting a distributed, function-driven development process was created [50]. AUTOSAR specifies also compatible software interfaces at application level. However, the functional contents of the application modules and components are different and related to the corporate identity and the desired characteristics of the car manufacturer or its system suppliers.

AUTOSAR has developed a metamodel which precisely defines the concepts used to describe a self-contained AUTOSAR system and a methodology. For example, software models are organized into units called "SoftwareComponents" [51]. Those components encapsulate the implementation of the functionality and the behaviour they provide, and simply expose well-defined connection points called ports. In particular, atomic software components are entities that support an implementation and hold behavioural entities called "RunnableEntity". A runnable is an entity that can be executed and scheduled independently from any other runnable entity. AUTOSAR gives also concepts to describe the basic software entities [51] as well as the OS (Operating System) configuration [52], RTE configuration [58] and Hardware topology description [54] (ECU, Bus, etc)

Timing aspect is considered in AUTOSAR through its timing extensions [55] that allow modelling the timing information of the system through concepts that express timing properties and constraints on events and event chains (inspired by the concepts and semantics defined in TADL in order to ease integration of AUTOSAR models with EAST-ADL models).

#### MARTE

MARTE (Modeling and Analysis of Real Time Embedded Systems) is the OMG standard dedicated for the modeling of real time systems. It provides means and constructs for modeling non functional properties and time concepts [56].

MARTE offers also a dedicated framework for model-based scheduling analysis [13]. This modeling framework provides a rich set of concepts for modeling end-to-end flows, software and hardware resource platform and for allocation of application modules to platform resources.

# 2.1.4. Model-based Approaches Evaluation

As mentioned previously, the aforementioned model-based approaches were developed to deal with specific automotive challenges (EAST-ADL, TADL, and AUTOSAR) and more generally with real time systems challenges (MARTE). As presented in the first chapter, automotive system development challenges can be categorized in four points:

- Mastering system complexity

- Reducing software development time and cost

- Defining seamless development activity supported by a seamless tool chain

- Ensuring system dependability, especially timing correctness through verification and validation.

Table 1 summarizes the capabilities of the studied model-based approaches against the aforementioned needs.

## Mastering system complexity

Looking at the EAST-ADL/AUTOSAR modeling process, we can conclude that there is a good potential to master system complexity. In fact developing automotive systems using these approaches is based on modeling the system architecture starting from abstract functional description until implementation detailed description. Hence, at early design phases, designers focus only on functional aspects abstracting away implementation-related details. In addition, hardware details can be described separately only starting from the Design level.

At Implementation level, using AUTOSAR allows also mastering the system complexity. In fact, AUTOSAR defines different views to enable the description of self-contained software

architecture. In the VFB view, the focus is made on the description of software components and their communication regardless of the platform and the mapping (of software component to ECUs) chosen. In ECU view, the configuration of the ECU may be described through describing the configuration of the RTE and the OS. Finally, in the system view, the focus is made on the system topology by describing e.g. the ECUs and communication buses used by the system. In addition, as shown in figure 5, AUTOSAR offers a layered software architecture giving the possibility to deal separately with the application software, basic software and the hardware. Application software complexity is also reduced as each application software component can be described independently from other software components.

TADL focuses only on modeling the timing aspect of systems by relying on the modeling process offered by EAST-ADL and AUTOSAR.

MARTE also focuses only on modeling the timing aspect of systems without any modeling process support. However, the MARTE scheduling analysis framework allows modeling the different scheduling and timing related features in separate views (application, software/hardware resources, allocations, etc). This allows the designer to focus separately on each aspect without involving details from other views.

### Reducing development time and cost

Using the EAST-ADL/AUTOSAR approach, development cost and time can be reduced as there is a good potential for easier reuse of software and hardware components and hence saving the time and cost required for redeveloping them.

In addition, using a model-based approach allows a better representation of system information (using models). Thus, the time required to collect such information (for further use) is significantly reduced during the development process.

#### Defining seamless development process and tool chain

The modeling process of EAST-ADL/AUTOSAR seems to be interesting as it gives the possibility to design the system architecture starting from abstract functional description until detailed implementation description. However, this process defines only the abstraction levels and the modeling concepts to be used at each level. It does not give any guidance about model refinement from a level to another. In addition it proposes no tool chain

support that allows describing and validating the system architecture along the development process.

As mentioned previously, TADL relies on the modeling process offered by EAST-ADL and AUTOSAR. In addition, a methodology has been defined to describe how the concepts defined by this language can be used at each abstraction level.

MARTE focus only on giving concepts for timing modeling without defining any modeling process or methodology

### Enabling timing verification

From a timing verification point of view, the aforementioned model-based approaches attempted to give means for the development of time critical systems. This is mainly ensured through giving concepts for expressing timing properties and constraints on models (TADL, AUTOSAR and MARTE).

However, supporting timing verification by these approaches is limited only to giving such means and concepts. In fact several methodological problems remain unsolved by these approaches, such as:

- How to integrate timing verification during the model-based development process?

- Which timing verification techniques should be used during each development phase?

- How to develop analyzable model to enable a particular timing verification and how to use provided concepts?

To enable model-based timing verification, these approaches should be complemented by a new one that allows answering these questions.

Table 1 Modeling approaches capabilities

|                                               | EAST-ADL/AUTOSAR                                                                                                                                                                                                                                                                                                                                                                                     | TADL                                                                                                                                                       | MARTE                                                                                                                                                                          |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Master<br>system<br>complexity                | Development through abstraction levels (From abstract functional description to detailed implementation).  Enable the designer to focus on different aspect at different levels  Software is organized into separate software components  Software architecture described through different views (VFB, ECU, System)  Layered software architecture (application software, basic software, hardware) | Focuses on annotating structural elements with timing information  Relies on the means offered by EAST-ADL and AUTOSAR to master complexity                | Focus on modeling timing information without giving a modeling process  Scheduling analysis models can be organized on separate views (application, platform, allocation, etc) |

| Reduce<br>development<br>time and<br>cost     | Potential for easier reuse of software and hardware components (save redevelopment time and cost)  Reduce information collection time through using models                                                                                                                                                                                                                                           | Reduces information collection time through using models                                                                                                   | Reduces information collection time through using models                                                                                                                       |

| Define<br>seamless<br>development<br>activity | Define only the abstraction levels  No guidance for model refinement and transformation  No tool chain defined to enable architecture description and validation                                                                                                                                                                                                                                     | Relies on the modeling process of EAST-ADL/AUTOSAR  Methodology defined to describe how to use TADL concepts based on EAST-ADL/AUTOSAR structural elements | No modeling process/methodology is defined  No tool chain defined                                                                                                              |

| Enable<br>timing<br>verification              | Give only concepts to express timing information (timing properties & constraints)  No guidance for model-based timing verification (how to integrate timing verification, how to develop analyzable models, which tools to use, how to use results, etc)                                                                                                                                            |                                                                                                                                                            |                                                                                                                                                                                |

### 2.2. Timing Verification: Scheduling Analysis

### 2.2.1. Introduction

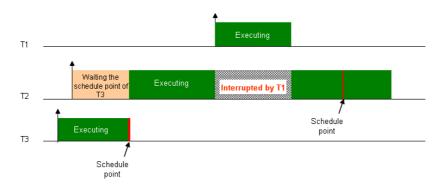

Since 1980s, many models, methods and tools were proposed to check if a real time system fulfills its requirements (e.g. Petri nets [19], synchronous languages [20], etc). One of these methods, usually called scheduling analysis is a part of a larger set of quantitative methods, the real time scheduling theory. Based on a schedulability test, scheduling analysis allow verifying the schedulability of a task set. Schedulability tests are based on the calculation of the worst case response time of a task, which is the longest time between the activation of a task and its subsequent completion. Once the worst-case response time is known, the feasibility of a task can be checked by comparing its worst-case response time to its deadline. In next sections, we present the most known results achieved in schedulability analysis in term of schedulability tests and scheduling analysis tools development.

### 2.2.2. Schedulability Tests: Brief Historical Review

In this section, we present a historical review of the most known results achieved within schedulability test development for fixed-priority monoprocessor systems.

In 1973, Liu and Layland published a paper on the scheduling of periodic tasks that is generally regarded as the foundational and most influential work in fixed priority real time scheduling theory [21]. They made the following assumptions:

- All tasks are periodic

- All tasks are released at the beginning of period and have a deadline equal to their period

- All tasks are independent, i.e., have no resource or precedence relationships

- All tasks have fixed computation time or, at least, an upper bound on their computation time which is less than or equal to their periods

- No task may voluntary suspend itself

- All tasks are fully preemptible

- All overheads are assumed to be null

- There is just one processor.

Based on this model, Liu and Layland gave a sufficient utilization-based condition for the feasibility of a fixed priority task set scheduled with the rate monotonic algorithm (RMA) [21]. They proved that a set of n periodic tasks, each having a computation time  $C_i$  and a period  $T_i$  is feasible with this algorithm if

$$\sum_{i=1}^{n} \frac{C_i}{T_i} \le n \left( 2^{\frac{1}{n}} - 1 \right)$$

Due to the limitations of Liu and Layland test (pessimistic condition, unrealistic task model with deadlines equal to periods, task priorities have to be assigned according to the rate monotonic policy) more complex feasibility tests were developed to address the above limitations. In 1987, Lehoczky et al. [22] gave the first exact schedulability test for the Liu and Layland task model. Concurrently, another group of researchers looked at the problem of determining the worst case response time of a task. Joseph and Pandya [23] and Audsley et al. [24] developed independently an algorithm to compute the worst-case response time  $R_i$  of a task  $\tau_i$  as the least-fixed-point of the following recursive equation:

$$R_i = C_i + \sum_{j=1}^{i-1} \left\lceil \frac{R_i}{T_j} \right\rceil C_j$$

In 1982, Leung [25] considered fixed priority scheduling of a set of tasks with deadlines less than their periods. Lehoczky [26] considered another relaxation of the Liu and Layland model to permit a task to have a deadline greater than its period. The Lehoczky approach uses the notion of "busy-period". A "level *i* busy period" is defined as the maximum time for which a processor executes tasks of priority greater than or equal to the priority of task *i*. Lehoczky shows how the worst-case response time of a task *i* can be found by examining a number of windows, each defined to be the length of the busy period starting at the window, and each window starting at an arrival of task *i*. In the early 1990, Tindell [27] extended the Lehoczky response time analysis providing an exact test for tasks with arbitrary deadlines.

A further relaxation of Liu and Layland task model is to permit tasks to have specified offsets (phasing). Tindell proposed in [28] a test for fixed priority tasks in which task offsets can be taken into account. This test has been later extended by Palencia and Gonzalez to take into account static and dynamic task offsets [29].

Wang and Saksena [30] introduced a feasibility test where they take into account non-preemptible tasks in addition to preemptible ones.

The development of scheduling analysis tools implementing such schedulability tests lies at the very core of scheduling analysis issue. In the next section, we give an overview of currently available scheduling analysis tools.

### 2.2.3. Scheduling Analysis Tools Presentation

While the number of scheduling analysis tools is constantly increasing, they also vary widely in terms of analysis capabilities and supported features.

#### • MAST

MAST [31] is an open source tool developed by the University of Cantabria in Spain. MAST is still under development and is intended to allow modeling real time applications and performing scheduling analysis for them. The tool offers a suite of scheduling analysis tests, ranging from classic RMA for fixed priority monoprocessor systems to more sophisticated analyses for EDF (Earliest Deadline First) schedulers [21] and distributed systems. In MAST, each real time situation is described through a set of concurrent transactions [41]. A transaction represents the execution of a set of activities triggered by an external event. An activity is an instance of an operation. The output of each activity is an internal event that may in turn activate other activities. Events may have timing requirements associated with them. Activities follow a predecessor/successor relationship with the possibility for an activity to have multiple successors or multiple predecessors. Each activity is bound to a single schedulable resource (task) and a schedulable resource refers to one processing resource. This way, the concept of activity encapsulates the allocation of the operation on a single schedulable resource and the allocation of the schedulable resource on a single processing resource. Table 2 and 3 summarize respectively the most important required inputs for the analysis as well as the output result of MAST.

Table 2 MAST required inputs

| Required input      | Description                                                                                                                                                                                                              |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| information         |                                                                                                                                                                                                                          |

| Processing Resource | They represent the processing capacity of a hardware component that executes some of the modeled system activities (Regular Processor) or message transmission (Packet Based Network).                                   |

| Scheduling Server   | They represent schedulable entities in a processing resource (e.g. OS task)                                                                                                                                              |

| Shared Resource     | They represent resource that are shared among different threads or tasks and that must be used on a mutually exclusive way.                                                                                              |

| Operation           | It represent a piece of code or a message                                                                                                                                                                                |

| Transaction         | A transaction represents a flow of executing activities that are interrelated. A transaction is defined with a list of external events, a list of internal events and their timing requirements and a list of activities |

| External Event      | It represents an event that activates a transaction. It can be e.g. periodic or sporadic.                                                                                                                                |

| Activity            | It represents an instance of an operation to be executed<br>by a scheduling server. An activity is defined by an input<br>event, and output event, an operation and the scheduling<br>server hosting this operation      |

| Internal Event      | It is an event that is generated by an activity. It can trigger the activation of another activity within the same transaction.                                                                                          |

| Timing Requirement  | Represents the timing requirement imposed on the instant of generation of an internal event. It represent a deadline or a maximum jitter on the generation instant of the event.                                         |

Table 3 MAST output results

| Output result              | Description                                                   |  |

|----------------------------|---------------------------------------------------------------|--|

| System/processing          | If positive, it represents the percentage by which all        |  |

| resource/transaction slack | the execution times of all the operation contained in         |  |

|                            | the global system (or used by the processing resource         |  |

|                            | or the transaction) may be increased while still              |  |

|                            | keeping the system schedulable. If negative it is the         |  |

|                            | percentage by which all these execution times have to         |  |

|                            | be decreased to make the system schedulable.                  |  |

| Worst/best/average         | Represents the worst/best/average response time of            |  |

| Transaction response time  | time   the transaction (generation of the output event of the |  |

|                            | transaction) with reference to the external event of          |  |