# High-performance floating-point computing on reconfigurable circuits

Bogdan Mihai Pasca

#### ▶ To cite this version:

Bogdan Mihai Pasca. High-performance floating-point computing on reconfigurable circuits. Other [cs.OH]. Ecole normale supérieure de lyon - ENS LYON, 2011. English. NNT: 2011ENSL0656. tel-00654121v2

#### HAL Id: tel-00654121 https://theses.hal.science/tel-00654121v2

Submitted on 26 Apr 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre: 656

N° attribué par la bibliothèque : 2011ENSL0656

#### ÉCOLE NORMALE SUPÉRIEURE DE LYON Laboratoire de l'Informatique du Parallélisme

#### **THÈSE**

présentée et soutenue publiquement le 21 Septembre 2011 par Bogdan PASCA

pour l'obtention du grade de

# Docteur de l'École Normale Supérieure de Lyon spécialité : Informatique

au titre de l'École Doctorale de Mathématiques et d'Informatique Fondamentale de Lyon

# High-performance floating-point computing on reconfigurable circuits

Directeur de thèse: Florent DE DINECHIN

Après avis de : Paolo IENNE

Olivier SENTIEYS

Devant la commission d'examen formée de :

Octavian CRET Membre Florent DE DINECHIN Membre Paul FEAUTRIER Membre

Paolo IENNE Membre/Rapporteur

Martin LANGHAMMER Membre

Olivier SENTIEYS Membre/Rapporteur

## Acknowledgements

First of all, I want to thank my family for their priceless and unconditioned support all throughout this thesis. They made me what I am today and I will be forever grateful.

Next, I want to kindly thank my girlfriend Mioara for her love and support which helped me to seamlessly overcome all encountered challenges. Thank you for being supportive and encouraging during the late hours we spent at the office on our endless deadlines.

I also want to thank our Romanian community from ENS, for all the brilliant time spent together. The endless polemics on various subjects were both cultivating and helped me significantly improve my argumentation capabilities. The long and challenging bike rides, gym practice, climbing, running ... made me always push myself one step further, which I also tried to apply to research.

I especially want to thank my supervisor Florent for believing in my potential and efficiently using my skills throughout the thesis time. His guidance was excellent, always coming up with interesting subjects to work on, but also providing me with sufficient freedom to tackle my own research subjects.

I also want to thank my thesis reviewers, whose constructive comments helped me further improve this manuscript, and the jury members for their pertinent and challenging questions during the defense.

A big thanks to CompSys members, Alexandru and Christophe, for the interesting discussions carried around the long coffee/tea brakes. These discussions did not only widen my research interests, but also resulted in one research article during the last year of this thesis.

Last but not least, I want to thank the Arenaire team members, for their kindness and for always having the door open for me. I also like to thank our team assistants, Severine and Damien for all their help in simplifying the sometimes overwhelming paperworks.

Many thanks to my friends and everyone else which I haven't mentioned here for their help and support.

## Contents

| 1 | Intr | oduction                                       | 1  |

|---|------|------------------------------------------------|----|

| 2 | Fiel | d Programmable Gate Arrays                     | 5  |

|   | 2.1  | Architecture                                   | 6  |

|   |      | 2.1.1 Logic elements                           | 6  |

|   |      | 2.1.2 DSP blocks                               | 9  |

|   |      | 2.1.3 Block memory                             | 12 |

|   | 2.2  | FPGA design flow                               | 13 |

|   | 2.3  | Application markets                            | 15 |

| 3 | Floa | iting-point arithmetic                         | 17 |

|   | 3.1  | Generalities                                   | 17 |

|   |      | 3.1.1 Representation                           | 17 |

|   |      | 3.1.2 Rounding                                 | 20 |

|   |      | 3.1.3 Errors                                   | 21 |

|   | 3.2  | Floating-point arithmetic on FPGAs             | 22 |

| 4 | Cus  | tom arithmetic data-path design                | 25 |

|   | 4.1  | Arithmetic operators                           | 26 |

|   |      | 4.1.1 FPGA-specific arithmetic operator design | 26 |

|   |      | 4.1.2 From libraries to generators             | 27 |

|   | 4.2  | Design choices for FloPoCo                     | 28 |

|   | 4.3  | A motivating example                           | 28 |

|   | 4.4  | The FloPoCo framework                          | 31 |

|   |      | 4.4.1 Operators                                | 31 |

|   |      | 4.4.2 Automatic pipeline management            | 32 |

|   |      | 4.4.3 Synchronization mechanisms               | 33 |

|   |      | 4.4.4 Managing subcomponents                   | 34 |

|   |      | 4.4.5 Sub-cycle accurate data-path design      | 35 |

|   |      | 4.4.6 Frequency-driven automatic pipelining    |    |

|   |      | 4.4.7 The Target class hierarchy               |    |

|   |      | 4.4.8 The bottom-line                          |    |

|   |      | 4.4.9 Test-bench generation                    |    |

|   |      | 4.4.10 Framework extensions                    |    |

|   | 4.5  |                                                | 41 |

vi

| 5                | Bina | ary addition in FloPoCo                                              | 43             |

|------------------|------|----------------------------------------------------------------------|----------------|

| 5.1 Related work |      | Related work                                                         | 43             |

|                  | 5.2  | Design-space exploration by resource estimation                      | 45             |

|                  | 5.3  | Pipelined addition on FPGA                                           | 45             |

|                  |      | 5.3.1 Classical RCA pipelining                                       | 47             |

|                  |      | 5.3.2 Resource estimation techniques                                 |                |

|                  |      | 5.3.3 Alternative RCA pipelining                                     | 48             |

|                  |      |                                                                      | 49             |

|                  | 5.4  | Short-latency addition architecture                                  | 49             |

|                  |      | 5.4.1 Classic carry-select adder                                     |                |

|                  |      | 5.4.2 Acceleration of inter-block carries                            |                |

|                  |      | 5.4.3 The Add-Add-Multiplex (AAM) carry-select architecture          |                |

|                  |      | 5.4.4 The Compare-Add-Increment (CAI) carry-increment architecture 5 |                |

|                  |      | 5.4.5 The Compare-Compare-Add (CCA) carry-select architecture        |                |

|                  |      | 5.4.6 Block-splitting strategies                                     |                |

|                  |      | 5.4.7 Area complexity of the designs                                 |                |

|                  | 5.5  | Global inference of shift-registers                                  |                |

|                  | 5.6  | Reality check                                                        |                |

|                  | 0.0  | 5.6.1 Estimation formulas                                            |                |

|                  |      | 5.6.2 Synthesis results                                              |                |

|                  | 5.7  | Conclusions                                                          |                |

|                  | 5.7  | Conclusions                                                          | 50             |

| 6                | Larg | ge multipliers with fewer DSP blocks                                 | 63             |

|                  | 6.1  | Large multipliers using DSP blocks                                   | 63             |

|                  | 6.2  | Visual representation of multipliers                                 |                |

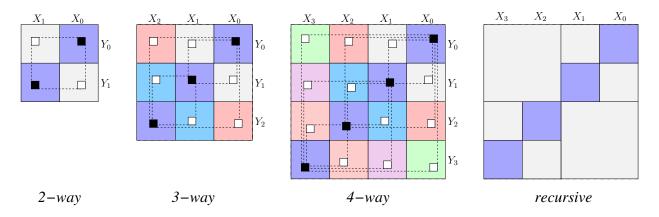

|                  | 6.3  | Karatsuba-Ofman algorithm                                            |                |

|                  |      | 6.3.1 Two-part splitting                                             |                |

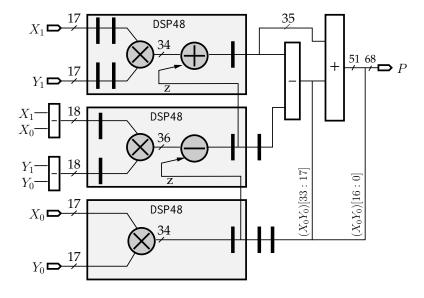

|                  |      | 6.3.2 Implementation issues on Virtex-4                              |                |

|                  |      | 6.3.3 Three-part splitting                                           |                |

|                  |      | 6.3.4 4-part splitting                                               |                |

|                  |      | 6.3.5 N-part splitting                                               |                |

|                  |      | 6.3.6 Issues with the most recent devices                            |                |

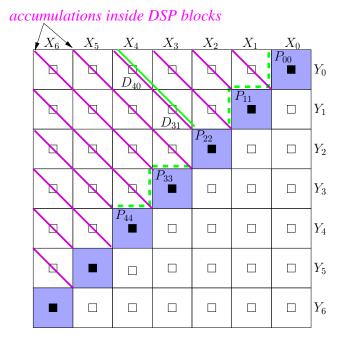

|                  | 6.4  | Non-standard tilings                                                 |                |

|                  | 0.1  |                                                                      | -<br>73        |

|                  |      | 6.4.2 Algorithm                                                      |                |

|                  |      |                                                                      | 74             |

|                  | 6.5  | Squarers                                                             |                |

|                  | 0.0  | •                                                                    | , <sub>5</sub> |

|                  |      | 6.5.2 Squarers on Stratix-III and Stratix-IV                         |                |

|                  |      | •                                                                    | 70<br>77       |

|                  | 6.6  |                                                                      |                |

|                  | 6.6  | Truncated multipliers                                                | 77<br>78       |

|                  |      | •                                                                    |                |

|                  |      | 6.6.2 FPGA fitting                                                   |                |

|                  | ( 7  | 8                                                                    | 79<br>01       |

|                  | 6.7  | Conclusion                                                           | 31             |

Contents

| 7  | Poly        | nomial-based architectures for function evaluation 83    |

|----|-------------|----------------------------------------------------------|

|    | 7.1         | Related work                                             |

|    | 7.2         | Function evaluation by polynomial approximation          |

|    |             | 7.2.1 Range reduction                                    |

|    |             | 7.2.2 Polynomial approximation                           |

|    |             | 7.2.3 Polynomial evaluation                              |

|    |             | 7.2.4 Accuracy and error analysis                        |

|    |             | 7.2.5 Parameter space exploration for the FPGA target 90 |

|    | 7.3         | Reality check                                            |

|    |             | 7.3.1 Optimization effect                                |

|    |             | 7.3.2 Examples and comparisons                           |

|    | 7.4         | Conclusion, open issues and future work                  |

| 8  | Mul         | tiplicative square root algorithms 97                    |

|    | 8.1         | Algorithms for floating-point square root                |

|    |             | 8.1.1 Notations and terminology                          |

|    |             | 8.1.2 The cost of correct rounding                       |

|    | 8.2         | Square root by polynomial approximation                  |

|    | 8.3         | Results, comparisons, and some handcrafting              |

|    | 8.4         | Conclusion and future work                               |

| 9  | Floa        | ting-point exponential 107                               |

|    | 9.1         | Related work                                             |

|    | 9.2         | Algorithm and architecture                               |

|    | <i>7.</i> ∠ | 9.2.1 Algorithm overview                                 |

|    |             | 9.2.2 Range reduction                                    |

|    |             | 9.2.3 Computation of $e^Y$                               |

|    | 9.3         | Implementation issues                                    |

|    | 9.5         | 9.3.1 Constant multiplications                           |

|    |             | 9.3.2 Overall error analysis                             |

|    |             | 9.3.3 The case study of single precision                 |

|    |             |                                                          |

|    |             |                                                          |

|    | 9.4         | 9.3.5 Parameter selection                                |

|    | 9.4         |                                                          |

|    |             | 9.4.1 Synthesis results                                  |

|    |             | 9.4.2 Comparison with other works                        |

|    | 0.          | 9.4.3 Comparison with microprocessors                    |

|    | 9.5         | Conclusion and future work                               |

| 10 |             | ting-point accumulation and sum-of-products 119          |

|    | 10.1        | A fast and accurate accumulator                          |

|    |             | 10.1.1 Overall architecture                              |

|    |             | 10.1.2 Parameterisation of the accumulator               |

|    |             | 10.1.3 Fast accumulator design using partial carry-save  |

|    |             | 10.1.4 Post-normalisation unit, or not                   |

|    |             | 10.1.5 Synthesis results                                 |

|    | 10.2        | Application-specific accumulator design                  |

|    |             | 10.2.1 A performance vs. accuracy tradeoff               |

|    |             | 10.2.2 A case study                                      |

|    |             | 10.2.3 Accuracy measurements                             |

viii Contents

| 10.3       | Accurate Sum-of-Products                                                                           | 127                                            |

|------------|----------------------------------------------------------------------------------------------------|------------------------------------------------|

|            |                                                                                                    |                                                |

|            |                                                                                                    |                                                |

|            |                                                                                                    |                                                |

| _          | •                                                                                                  | 131                                            |

|            |                                                                                                    |                                                |

| 11.2       |                                                                                                    |                                                |

|            |                                                                                                    |                                                |

|            |                                                                                                    |                                                |

|            |                                                                                                    |                                                |

|            | •                                                                                                  |                                                |

|            |                                                                                                    |                                                |

|            | 11.2.6 Algorithm                                                                                   |                                                |

| 11.3       | Computing kernel accuracy and performance                                                          | 146                                            |

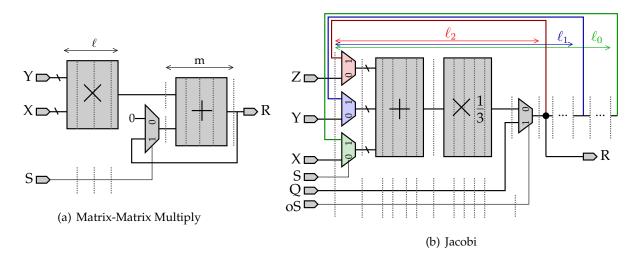

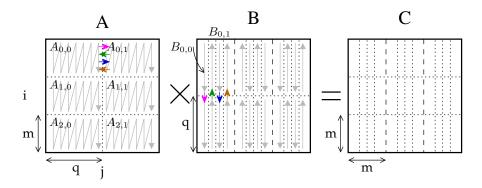

|            | 11.3.1 Matrix-matrix multiplication                                                                |                                                |

|            | 11.3.2 One dimensional Jacobi stencil computation                                                  | 148                                            |

|            | 11.3.3 Lessons                                                                                     | 149                                            |

| 11.4       | Reality check                                                                                      | 149                                            |

| 11.5       | Conclusion and future work                                                                         | 151                                            |

| <b>.</b> . |                                                                                                    | 4=0                                            |

|            |                                                                                                    | 153                                            |

|            |                                                                                                    |                                                |

| 12.2       |                                                                                                    |                                                |

|            |                                                                                                    |                                                |

|            |                                                                                                    |                                                |

| 100        | * *                                                                                                |                                                |

| 12.3       |                                                                                                    |                                                |

|            |                                                                                                    |                                                |

|            |                                                                                                    |                                                |

|            |                                                                                                    |                                                |

|            |                                                                                                    |                                                |

|            |                                                                                                    |                                                |

| 12.4       | Conclusion                                                                                         | 165                                            |

| Cone       | clusions and Perspectives                                                                          | 167                                            |

|            | 10.4<br>10.5<br><b>Higl</b><br>11.1<br>11.2<br>11.3<br>11.4<br>11.5<br><b>Usin</b><br>12.1<br>12.2 | 11.3 Computing kernel accuracy and performance |

## **List of Figures**

| 2.1  | Very simplified view of a generic FPGA layout                                              | 5  |

|------|--------------------------------------------------------------------------------------------|----|

| 2.2  | Left: CLB composition and interconnect in Virtex-4 devices Right: Detailed view of         |    |

|      | a Virtex-4 Slice                                                                           | 6  |

| 2.3  | Ripple-Carry Adder (RCA) implementation in Virtex-4 devices                                | 7  |

| 2.4  | Architectural overview of the Adaptative Logic Module (ALM) block present in               |    |

|      | Stratix devices                                                                            | 9  |

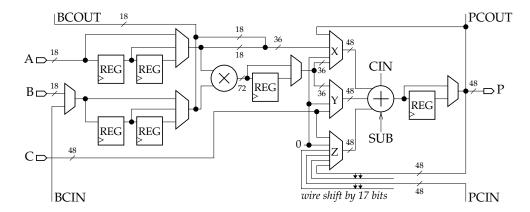

| 2.5  | Overview of the Xilinx DSP48                                                               | 10 |

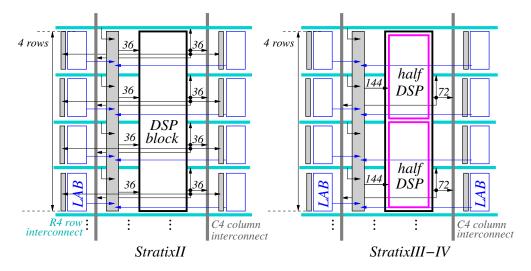

| 2.6  | Interconnect of the DSP blocks Left: StratixII and Right: StratixIII-IV devices            | 11 |

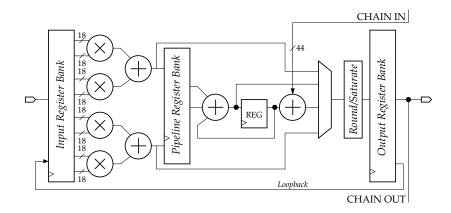

| 2.7  | Very simplified overview of the Stratix-III half-DSP block                                 | 11 |

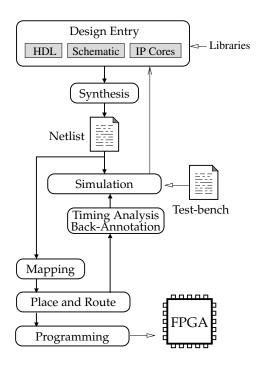

| 2.8  | Classical FPGA design flow                                                                 | 14 |

|      |                                                                                            |    |

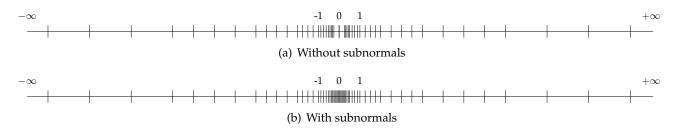

| 3.1  | Distribution of floating-point numbers in a system $\xi(2,3,-2,3)$ , having a IEEE-754     |    |

|      | equivalent $p=3$ and $w_e=3$ . The -3 and 4 values of $e$ are used to represent the        |    |

|      | 1 1                                                                                        | 19 |

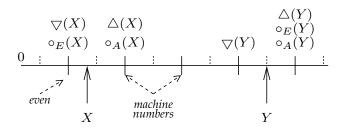

| 3.2  |                                                                                            | 20 |

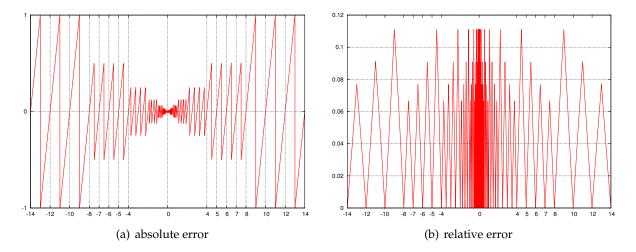

| 3.3  | The absolute and relative errors of our representation                                     |    |

| 3.4  | Instruction distribution in SPICE circuit modeling using FPGAs [94]                        | 23 |

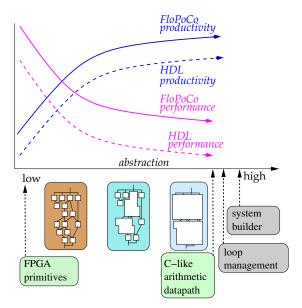

| 4.1  | Productivity in porting applications to FPGAs and the relative performance of these        |    |

| 1.1  | circuits provided the different levels of abstraction are provided for circuit description | 27 |

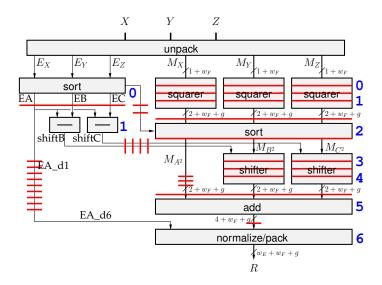

| 4.2  | 1                                                                                          | 29 |

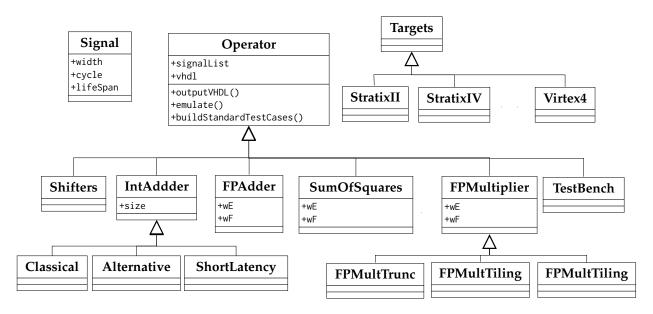

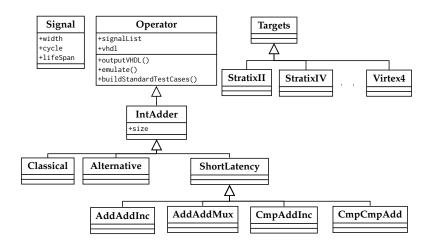

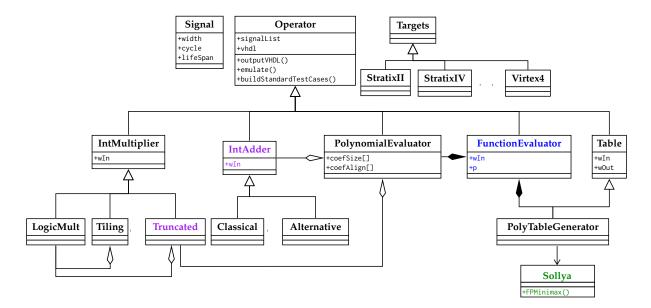

| 4.3  | Very simplified overview of the FloPoCo class hierarchy                                    |    |

| 4.4  |                                                                                            | 33 |

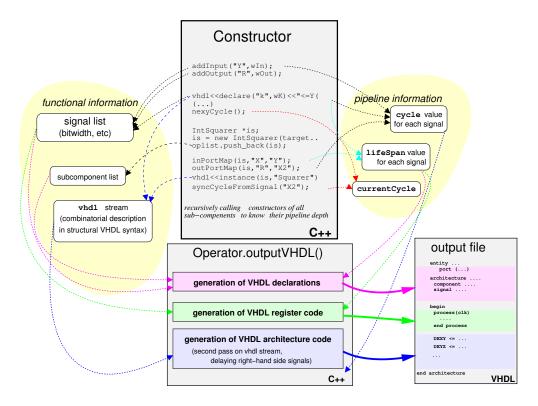

| 4.5  |                                                                                            | 38 |

| 1.0  |                                                                                            |    |

| 5.1  | FloPoCo class structure for binary addition                                                |    |

| 5.2  |                                                                                            |    |

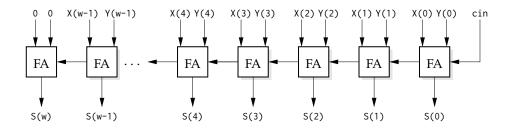

| 5.3  |                                                                                            | 47 |

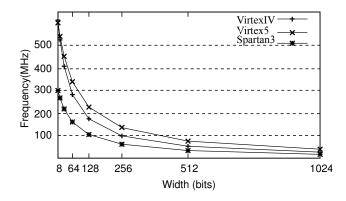

| 5.4  | L J                                                                                        | 48 |

| 5.5  |                                                                                            | 48 |

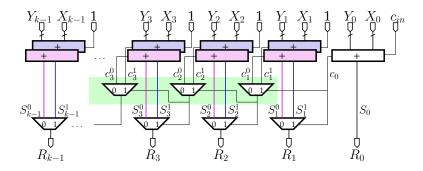

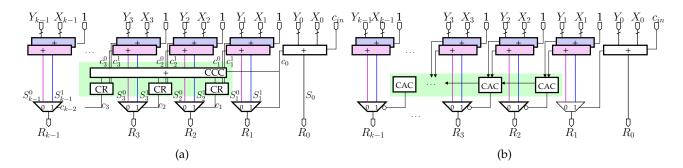

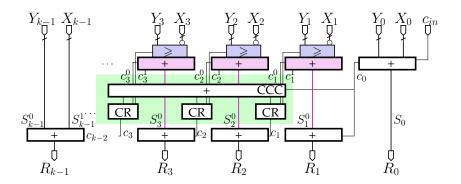

| 5.6  | Proposed FPGA architecture                                                                 |    |

| 5.7  | Classic Carry-Select Architecture                                                          |    |

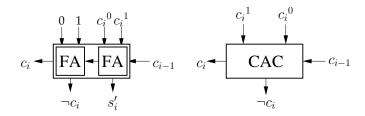

| 5.8  | Carry-Add-Cell (CAC) implementation and representation                                     |    |

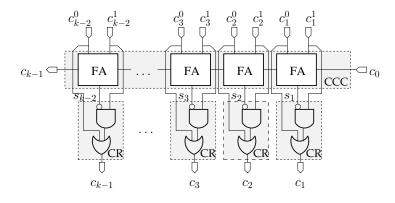

| 5.9  | Carry Computation Circuit with Carry Recovery                                              |    |

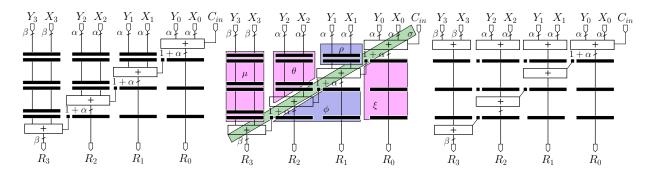

| 5.10 | The AAM Carry-Select Architecture using (a) the CCC and CR and (b) the CAC                 | 53 |

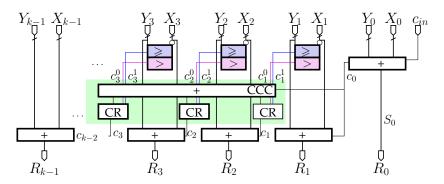

| 5.11 | The CAI Carry-Increment Architecture                                                       |    |

|      | The CCA Carry-Select Architecture                                                          |    |

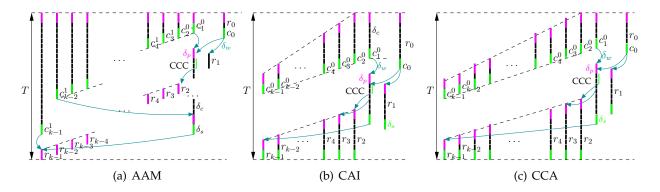

|      | Computation scheduling for the proposed architectures                                      |    |

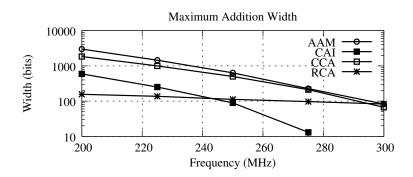

| 5.14 | Maximum adder width vs circuit frequency on Virtex5                                        | 60 |

x List of Figures

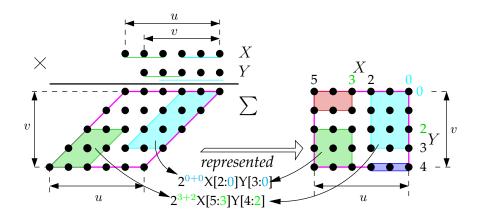

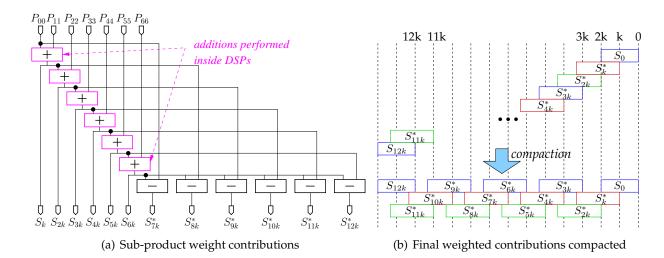

| 6.1             | $u \times v$ -bit multiplier                                                                                                                                       | 64  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.2             | $u \times v$ -bit multiplier                                                                                                                                       | 66  |

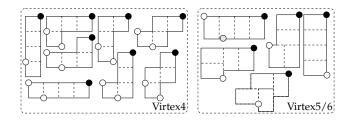

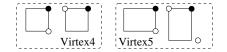

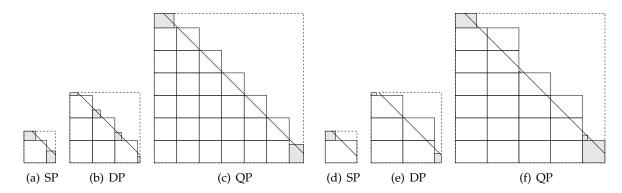

| 6.3             | 34x34bit multiplier using Virtex-4 DSP48                                                                                                                           | 67  |

| 6.4             | 119x119bit multiplier using Virtex-4 DSP48 for QP mantissa multiplier                                                                                              | 70  |

| 6.5             | 119x119-bit Karatsuba                                                                                                                                              | 71  |

| 6.6             | 53-bit multiplication using Virtex-5 DSP48E. The dashed square is the 53x53 multi-                                                                                 |     |

|                 | plication                                                                                                                                                          | 72  |

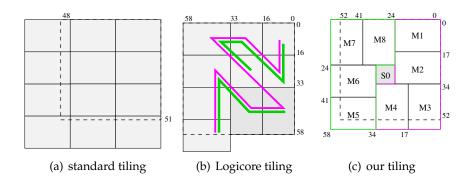

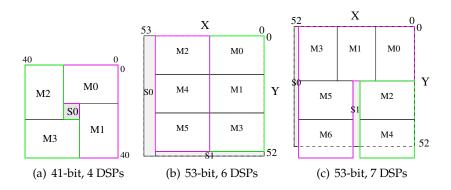

| 6.7             | Some super-tiles exactly matching DSP blocks                                                                                                                       | 74  |

| 6.8             | Super-tiling primitives                                                                                                                                            | 74  |

| 6.9             | Various tilings of large multipliers                                                                                                                               | 75  |

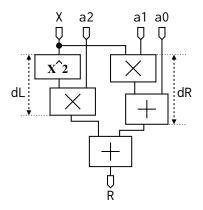

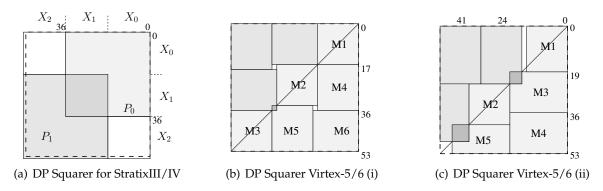

| 6.10            | Double-precision squaring. Tilings for StratixIII/IV and Virtex-5/6 devices                                                                                        | 77  |

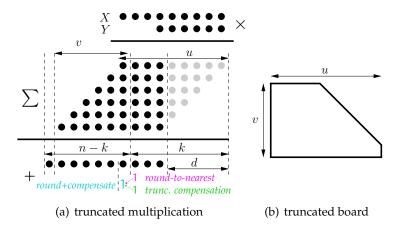

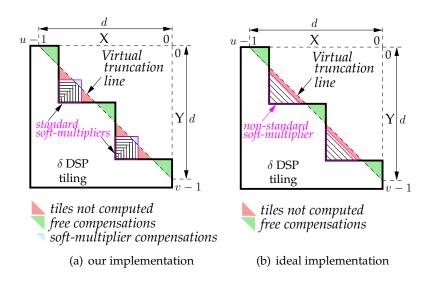

| 6.11            | Truncated multiplication and the corresponding tiling multiplication board                                                                                         | 78  |

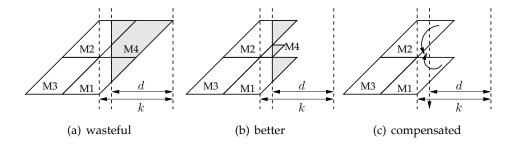

| 6.12            | Truncation applied to multipliers. Left: Classical truncation technique applied to DSPs. Center: Improved truncation technique; M4 is computed using logic. Right: |     |

|                 | FPGA optimized compensation technique; M4 is not computed                                                                                                          | 79  |

| 6.13            | Tiling truncated multiplier using DSPs and soft-core multipliers                                                                                                   | 80  |

| 6.14            | Mantissa multipliers for SP,DP,QP, Virtex4 (left) and Virtex5 (right) ensuring faithful                                                                            |     |

|                 | rounding. The gray tiles represent soft-core multipliers                                                                                                           | 81  |

| 7.1             | FloPoCo class structure integrating the generic fixed-point FunctionEvaluator                                                                                      | 84  |

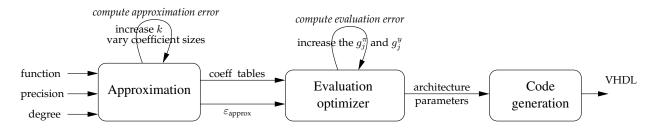

| 7.2             | Automated implementation flow                                                                                                                                      | 85  |

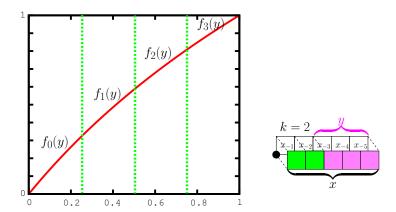

| 7.3             | Range reduction example for the $f(x) = \log_2(x)$ , for $x \in [0,1)$ where the input interval is split into four sub-intervals                                   | 86  |

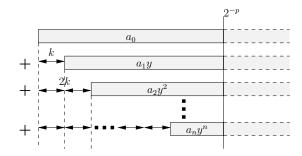

| 7.4             | Alignment of the monomials                                                                                                                                         |     |

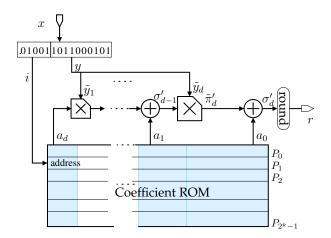

| 7. <del>1</del> | The function evaluation architecture                                                                                                                               | 91  |

| 7.0             | The function evaluation definectate                                                                                                                                | 71  |

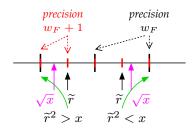

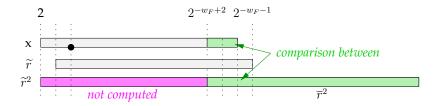

| 8.1             | Deducing the correctly rounded value of $\sqrt{x}$ on $w_F$ bits from a faithfully rounded result on $w_{F+1}$ bits                                                | 99  |

| 8.2             | Bits involved in the comparison of $x^2 \ge x$ are highlighted                                                                                                     |     |

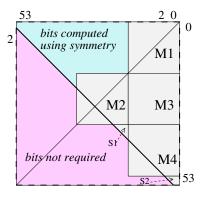

| 8.3             | The multipliers required for the squaring operation operation $r^2$ for double-precision                                                                           | 100 |

| 0.5             | on Virtex4                                                                                                                                                         | 100 |

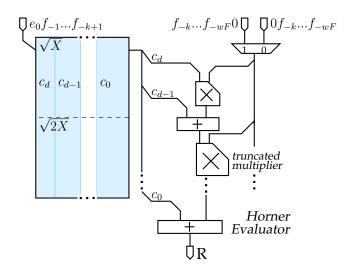

| 8.4             | Generic polynomial evaluator for the square root                                                                                                                   |     |

| 8.5             | Handcrafted architecture for single precision                                                                                                                      |     |

| 0.0             |                                                                                                                                                                    |     |

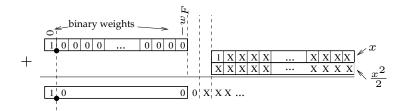

| 9.1             | Operand alignment for $1 + x + x^2/2$ for $x < 2^{-w_F-2}$                                                                                                         | 108 |

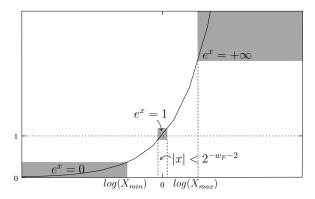

| 9.2             | The ranges of the input where the exponential takes specific values                                                                                                | 109 |

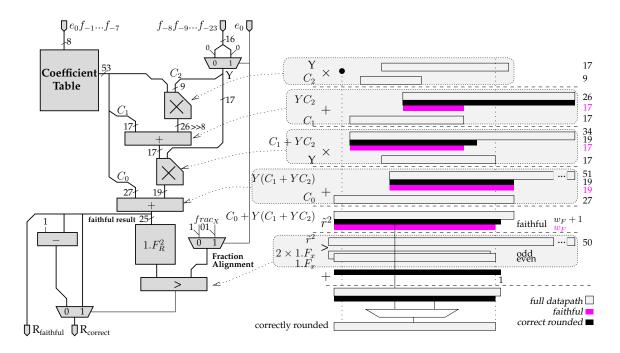

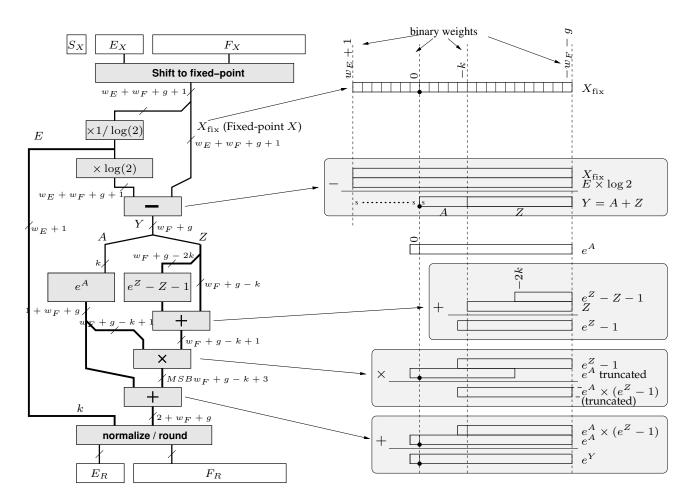

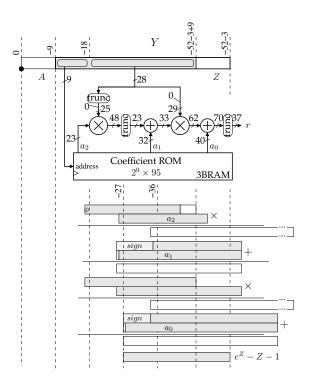

| 9.3             | Architecture and fixed-point data alignment                                                                                                                        | 110 |

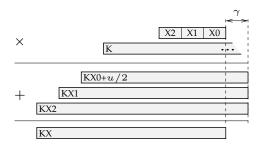

| 9.4             | Improved accuracy constant multiplication                                                                                                                          | 113 |

| 9.5             | The architecture evaluating $e^Z-Z-1$ for Virtex-5/Virtex-6                                                                                                        | 115 |

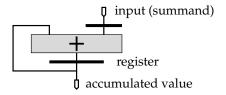

| 10.1            | Iterative accumulator                                                                                                                                              | 119 |

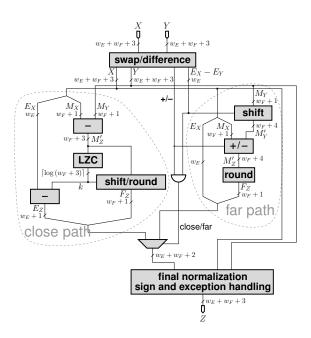

| 10.2            | A typical floating-point adder ( $w_E$ and $w_F$ are the exponent and significand sizes) .                                                                         | 120 |

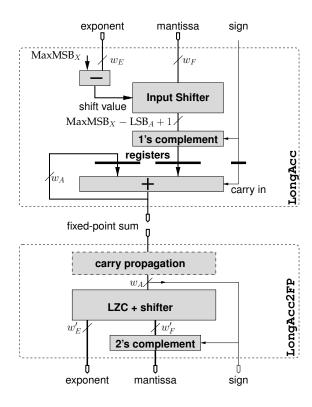

|                 | The proposed accumulator (top) and post-normalisation unit (bottom)                                                                                                |     |

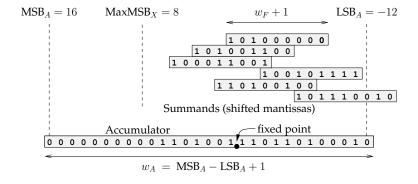

|                 | Accumulation of floating-point numbers into a large fixed-point accumulator                                                                                        |     |

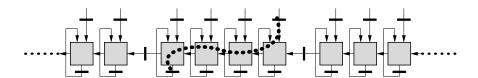

|                 | Accumulator with 4-bit partial carry-save. The boxes are full adders, bold dashes                                                                                  |     |

|                 | are 1-bit registers, and the dots show the critical path                                                                                                           | 122 |

List of Figures xi

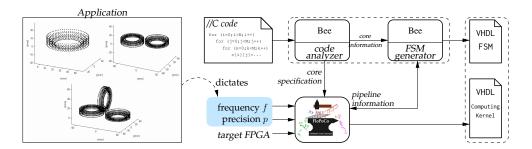

| 11.1  | Automation flow: the C code is first parsed by the Bee research compiler; FloPoCo                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | is then invoked for generating the required arithmetic pipeline; the pipeline infor-                                                                                              |

|       | mation is then passed back to the Bee compiler for use in operation scheduling; next, the pipeline depth adjustments are sent to FloPoCo for generating the final                 |

|       | VHDL                                                                                                                                                                              |

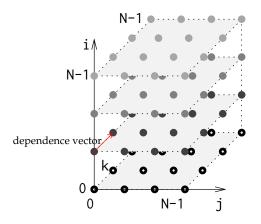

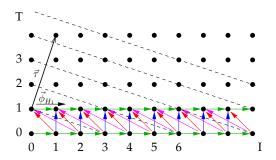

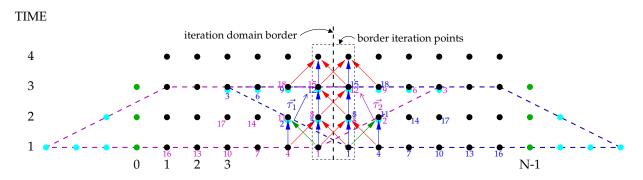

| 11 2  | Iteration domain for the matrix-matrix multiply code in Listing 11.1 for N=4 133                                                                                                  |

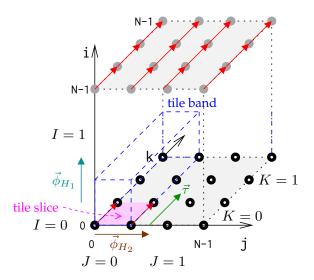

|       | Matrix-matrix multiplication iteration domain with tiling                                                                                                                         |

|       | The iteration domain and dependence vectors for 1D Jacobi stencil computation in                                                                                                  |

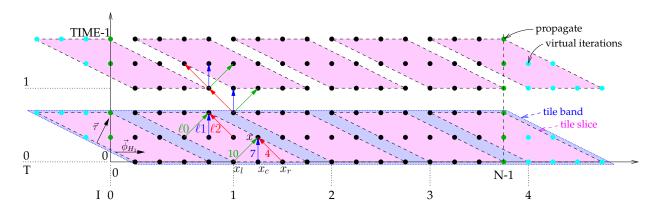

| 11.1  | Listing 11.3                                                                                                                                                                      |

| 11.5  | Tiled iteration domain for 1D Jacobi stencil computation                                                                                                                          |

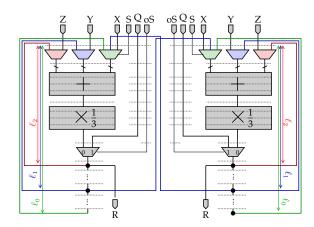

|       | Computational kernels of our two motivating examples. These were generated us-                                                                                                    |

|       | ing FloPoCo                                                                                                                                                                       |

| 11.7  | Matrix-matrix multiply using blocking                                                                                                                                             |

|       | Matrix-matrix multiply blocking applied using our technique. Scheduling of com-                                                                                                   |

|       | putations is modified in order to minimize external memory usage                                                                                                                  |

| 11.9  | Inter tile slice iteration domain for Jacobi 1D stencil code. The parallel hyperplane                                                                                             |

|       | has $\vec{\tau} = (1,3)$ and describes the tile-slices which can be executed in parallel. The                                                                                     |

|       | dashed lines indicated various translations of the hyperplane $H_{\vec{\tau}}$ showing different                                                                                  |

|       | levels of parallelism                                                                                                                                                             |

|       | OAn alternative to executing the Jacobi Kernel using 2 processing elements                                                                                                        |

|       | Architecture for the second proposed parallelization of Jacobi 1D                                                                                                                 |

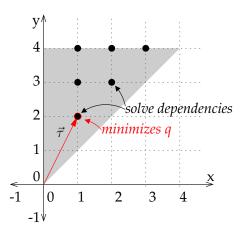

| 11.12 | 2The solution to the ILP finding $	au$ for the Jacobi example $\dots \dots \dots$ |

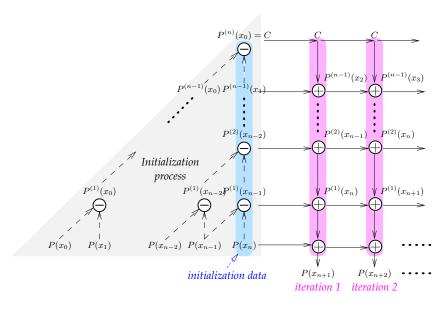

| 12.1  | The tabulated difference method                                                                                                                                                   |

|       | Polynomial Evaluator based on the tabulated differences method                                                                                                                    |

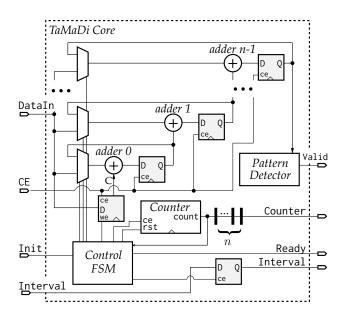

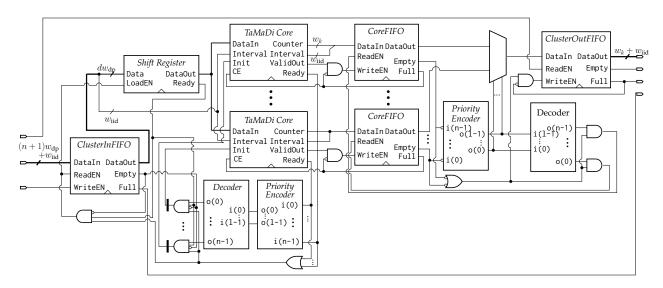

|       | Overview of the TaMaDi Cluster architecture                                                                                                                                       |

| 12.4  | Structure of one element in the ClusterInFIFO                                                                                                                                     |

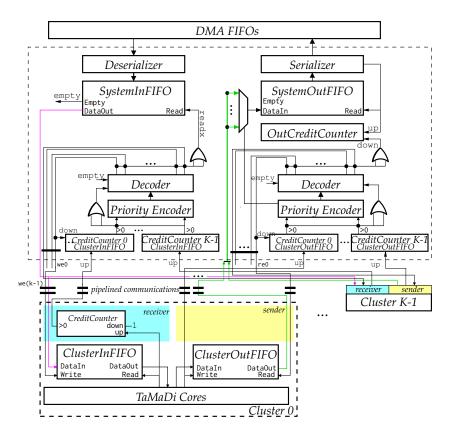

|       | Global system dispatcher interface                                                                                                                                                |

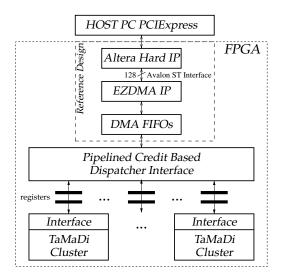

|       | Global system architecture                                                                                                                                                        |

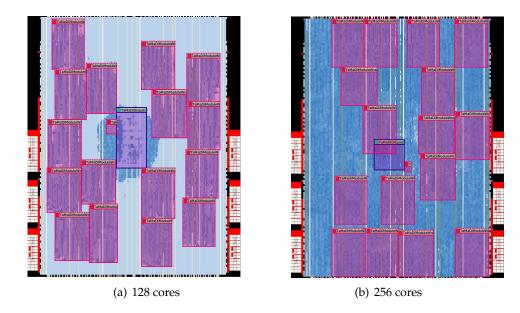

| 12.7  | Placement of the synthesized the TaMaDi System using logical regions 164                                                                                                          |

## **List of Tables**

| 2.1<br>2.2 | Main operating modes of the Virtex-4 DSP48 block                                                                                                                                        | 10<br>12   |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.1<br>3.2 | IEEE-754 2008 binary ( $\beta=2$ ) floating-point (FP) formats                                                                                                                          | 18<br>19   |

| 4.1        | Some synthesis results for $x^2 + y^2 + z^2$                                                                                                                                            | 30         |

| 5.1        | Resource estimation formulas for the pipelined adder architectures with shift-register extraction (SRL) (Xilinx only) and without SRL (Xilinx and Altera)                               | 49         |

| 5.2        | Advanced resource estimation formulas for the pipelined classical architecture, when shift-register extraction is activated                                                             | 50         |

| 5.3        | CAC Truth table. Greyed-out rows are not needed                                                                                                                                         | 51         |

| 5.4        | Inter-Block Carry Propagation Cases                                                                                                                                                     | 52         |

| 5.5        | Area comparison against pipelined RCA schemes for Virtex5 and addition size $L$                                                                                                         | 58         |

| 5.6        | Relative Error for the estimation formulas on a 128-bit adder Virtex4 and StratixIII devices for a requested frequency of 400MHz.                                                       | 59         |

| 5.7        | Resource usage of 128-bit wide pipelined adders for different utilization contexts for a target frequency of 400MHz (SRL allowed, post place-and-route)                                 | 59         |

| 5.8        | Post place-and-route results on Virtex5 (-3) for various adder sizes and a target $f$ =250MHz using ISE 11.5. $\delta_{cp}$ denotes the length of the design's critical path            | 60         |

| 5.9        | Post place-and-route synthesis results for 128-bit addition on StratixIII                                                                                                               | 60         |

| 6.1        | 34x34 multipliers on Virtex-4 (4vlx15sf363-12)                                                                                                                                          | 66         |

| 6.2        | 51x51 multipliers on Virtex-4 (4vlx15sf363-12)                                                                                                                                          | 68         |

| 6.3        | Synthesis results of large Karatsuba multipliers. For Stratix-II/III we used the <code>lpm_mult</code> megafunction provided with the Megawizerd tool for generating binary multipliers | 71         |

| 6.4        | Comparison of multiplier implementations on Virtex5 devices. All our implementations are targeted at 400MHz. Frequency is expressed in MHz                                              | <b>7</b> 5 |

| 6.5        | 32-bit and 53-bit squarers on Virtex-4 (4vlx15sf676-12)                                                                                                                                 | 76         |

| 6.6        | Truncated multipliers providing faithful rounding for common floating point formats                                                                                                     | 78         |

| 6.7        | Truncated multiplier results                                                                                                                                                            | 80         |

| 7.1        | The decrease in internal datapath truncations allows reducing DSP count                                                                                                                 | 92         |

| 7.2        | Examples of polynomial approximations obtained for several functions. $S$ represents the scaling factor so that the function image is in $[0,1]$                                        | 93         |

xiv List of Tables

| <ul><li>7.3</li><li>7.4</li></ul> | Synthesis Results using ISE 11.1 on VirtexIV xc4vtx100-12. <i>l</i> is the latency of the operator in cycles. All the operators operate at a frequency close to 320 MHz. The grayed rows represent results without coefficient table BRAM compaction and the use of truncated multipliers                                               |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.1                               | FloPoCo polynomial square root for Virtex-4 4vfx100ff1152-12 and Virtex5 xc5vlx30-3-ff324. The command line used is flopoco -target=Virtex4 Virtex5 -frequency= $f$ FPSqrtPoly $w_E$ $w_F$ 0 degree                                                                                                                                     |

| 9.1                               | Synthesis results of the various instances of the floating-point exponential operator. We used QuartusII v9.0 for StratixIII EPSL50F484C2 and ISE 11.5 for VirtexIV XC4VFX100-12-ff1152, Virtex5 XC5VFX100T-3-ff1738 and Virtex6 XC6VHX380T-3-ff1923                                                                                    |

| 10.1                              | Compared synthesis results for an accumulator based on FP adder, versus proposed accumulator with various combinations of parameters, for Virtex-4 and Stratix-III devices targeting 400 MHz                                                                                                                                            |

| 10.2                              | Synthesis results for a LongAcc2FP compatible with Table 10.1, rounding an accumulator of size $2w_F$ to an FP number of size $w_F$ . Virtex-4 results are obtained using                                                                                                                                                               |

| 10.3                              | ISE 11.5 and for Stratix-III using Quartus 10.1 (after place and route)                                                                                                                                                                                                                                                                 |

| 10.4                              | from [57]                                                                                                                                                                                                                                                                                                                               |

| 10.5                              | absorb at least 100,000 products in [0,1]. The accumulator parameters are $MSB_A =$                                                                                                                                                                                                                                                     |

| 10.6                              | $\lceil \log_2(100,000) \rceil$ , MaxMSB $_X = 1$ MSB $_A = -2*w_F - 2$                                                                                                                                                                                                                                                                 |

| 11.1                              | Minimum, average and maximum relative error out of a set of 4096 runs, for $N=4096$ , the elements of A and B are uniformly distributed on the positive/entire floating-point axis. The third architecture uses truncated multipliers having an error of 1 ulp with ulp $=2^{-w_F-6}$ . Implementation results are given for a Virtex-4 |

| 11.2                              | speedgrade-3 FPGA device                                                                                                                                                                                                                                                                                                                |

| 11.3                              | plementation results are given for a Virtex-4 speedgrade-3 FPGA device 148 Synthesis results for the full (including FSM) MMM and Jacobi1D codes. Results                                                                                                                                                                               |

| 11.4                              | obtained using Using Xilinx ISE 11.5 for Virtex5, and QuartusII 9.0 for StratixIII 150 Synthesis results for the parallelized MMM and Jacobi1D. Results obtained using using Quartus II 10.1 for StratixIII with $w_E=8, w_F=23$                                                                                                        |

|                                   | Post place-and-route results of the TaMaDi Core PE                                                                                                                                                                                                                                                                                      |

|                                   | width/Core for a StratixIV. Similar results hold for other FPGAs                                                                                                                                                                                                                                                                        |

| 12.4                              | Post place-and-route results of the TaMaDi System. The Core parameters are: $w_{\rm dp} = 120$ bits and $N = 4$                                                                                                                                                                                                                         |

## **Acronyms**

**FPGA** Field Programmable Gate Array

**GPU** Graphical Procesing Unit

**HPC** High-Performance Computing

**IC** Integrated Circuit

**ASIC** Application-Specific Integrated Circuit

**CUDA** Compute Unified Device Architecture

**HDL** Harware Description Language

PAL Programmable Array of Logic

**CPLD** Complex Programmable Logic Device

**LE** logic element

**LUT** look-up table

**CLB** Configurable Logic Block

**LAB** Logic Array Block

**MLAB** Memory Logic Array Block (LAB)

**ALM** Adaptative Logic Module

**ALUT** adaptative look-up table

**RAM** Random-Access Memory

**SRAM** Static Random-Access Memory (RAM)

**EDIF** Electronic Digital Interchange Format

**XNF** Xilinx Netlist Format

**FSM** Finite State Machine

**FP** floating-point

**SP** single precision

**DP** double precision

**QP** quadruple precision

**FPU** Floating-Point Unit

**CR** correct rounding

**FR** faithful rounding

**HLS** High-Level Synthesis

**DSP** Digital Signal Processing

**FFT** Fast Fourier Transform

xvi List of Tables

**FIR** Finite Impulse Response

**PE** Processing Element

**RCA** Ripple-Carry Adder

**FA** Full-Adder

**MSB** Most Significant Bit

### **Publications**

- 1. Florent de Dinechin, Jean-Michel Muller, Bogdan Pasca, and Alexandru Plesco. An FPGA architecture for solving the Table Maker's Dilemma. In *International Conference on Application-specific Systems, Architectures and Processors*, 2011. *Best Paper Award*

- 2. Hong Diep Nguyen, Bogdan Pasca, and Thomas B. Preußer. FPGA-specific arithmetic optimizations of short-latency adders. In *International Conference on Field Programmable Logic and Applications*. IEEE, 2011.

- 3. Florent de Dinechin and Bogdan Pasca. Designing custom arithmetic data paths with FloPoCo. *IEEE Design and Test*, 2011.

- 4. Christophe Alias, Bogdan Pasca, and Alexandru Plesco. Automatic generation of FPGA-specific pipelined accelerators. In *The 7th International Symposium on Applied Reconfigurable Computing*, 2011.

- 5. Florent de Dinechin and Bogdan Pasca. Floating-point exponential functions for DSP-enabled FPGAs. In *IEEE International Conference on Field-Programmable Technology*. IEEE, 2010.

- 6. Sebastian Banescu, Florent de Dinechin, Bogdan Pasca, and Radu Tudoran. Multipliers for floating-point double precision and beyond on FPGAs. In *International Workshop on Higly-Efficient Accelerators and Reconfigurable Technologies (HEART)*. ACM, 2010.

- 7. Florent de Dinechin, Mioara Joldes, and Bogdan Pasca. Automatic generation of polynomial-based hardware architectures for function evaluation. In *International Conference on Application-specific Systems, Architectures and Processors*, 2010.

- 8. Florent de Dinechin, Mioara Joldes, Bogdan Pasca, and Guillaume Revy. Multiplicative square root algorithms for FPGAs. In *International Conference on Field Programmable Logic and Applications*. 2010.

- 9. Florent de Dinechin, Hong Diep Nguyen, and Bogdan Pasca. Pipelined FPGA adders. In *International Conference on Field Programmable Logic and Applications*. 2010.

- Florent de Dinechin, Mioara Joldes, Bogdan Pasca, and Guillaume Revy. Racines carrées multiplicatives sur FPGA. In SYMPosium en Architectures nouvelles de machines (SYMPA), 2009.

- 11. Florent de Dinechin and Bogdan Pasca. Large multipliers with fewer DSP blocks. In *International Conference on Field Programmable Logic and Applications*. 2009.

- 12. Florent De Dinechin, Cristian Klein, and Bogdan Pasca. Generating high-performance custom floating-point pipelines. In *International Conference on Field Programmable Logic and Applications*, 2009.

- 13. Florent de Dinechin, Bogdan Pasca, Octavian Creţ, and Radu Tudoran. An FPGA-specific approach to floating-point accumulation and sum-of-products. In *IEEE International Conference on Field-Programmable Technology*, 2008.

# CHAPTER 1 Introduction

The classical version of Moore's Law predicts that the capacity of Integrated Circuits (ICs) doubles every 18 months. Microprocessor manufacturers followed this law by reducing the operating voltages and using smaller and faster transistors. Frequency scaling got to the point that circuits emitted too much heat to be reasonably dissipated – the so called power wall. This lead the main microprocessor manufacturer, Intel, to publicly announce in 2004 that it would dedicate all it future design efforts to multi-core environments. Nowadays, Intel offers a 8-core version of the high-end Xeon processor (V8), while Opteron from AMD is provided in a 12-core version, both at 45nm manufacturing process.

Just doubling the number of cores in a die doesn't guarantee a speedup of two over the initial microprocessor for a given application. Indeed, Amdahl's law [34] suggests that the maximum expected overall improvement of a system using N processors is highly influenced by the amount of sequential execution of the program, but also by the degree of parallelism of the parallel sections. Most of the existing software, developed during the single-core era is essentially sequential and therefore does't benefit from any improvement on a multicore system. One idea, dating back from the 1960s, is to write compilers that would automatically parallelize these sequential programs. The success of these approaches seems to be inversely proportional to the number of targeted cores. One reason for this insuccess is that the sequential solution these tools start with already looses some of the "parallel semantics" of the problem to be solved. Consequently, making efficient use of multiple cores requires recovering some of this lost parallelism. This requires recoding parts of the application using the thread programming model or using one of the well known APIs supporting process intercommunication: MPI, PVM or OpenMP. Another reason for the poor performance of these parallelized programs is that in a multicore system inter-process communication, usually resolved by shared-memory techniques, is very costly. In any case, the success of this approach will depend on the data-level parallelism of the initial application.

One success story is computer graphics. Graphics processing is an application domain having massively parallel computational kernels: entire animation scenes and also parts of each frame can be processed in parallel. Traditionally, Graphical Procesing Units (GPUs) consisted of numerous but rather simple Processing Elements (PEs) capable of processing the numerous graphics-related tasks in a flow-like manner. In 2001, with the introduction of first programmable GPU (the NV20 series) programmers could execute custom visual-effects programs using the Shader Language 1.1. In 2007 nVIDIA formalized the GPU's computing capabilities under the name of Compute Unified Device Architecture (CUDA): the parallel computing architecture present in nVIDIA GPUs. General-purpose computations can be expressed using *C for CUDA*, a C subset with nVIDIA extensions. As the PEs of modern GPUs support some of the basic floating-point operators, it is tempting to use them to perform massively parallel scientific computations.

Nevertheless, acceleration degree is very application-dependent (applications should have high data-level parallelism and main computation task should be supported in silicon by the PEs) and obtaining good accelerations requires a significant amount of code refactoring.

Field Programmable Gate Arrays (FPGAs) have also benefited from the advances in circuit integration. With increased capacities, FPGAs moved from being used as glue-logic to prototyping Application-Specific Integrated Circuits (ASICs), and recently to ASIC replacements and application accelerators [111, 65, 57]. If in the past, performance- and power-demanding systems were usually built using ASICs, their use today is being limited by their prohibitive manufacturing price. Moving down in the manufacturing process from 130nm to 90nm has doubled ASIC mask prices and requires millions more in engineering. This restricts the viable use of ASICs to medium and hi-volume markets (more than 100K chips sold). On the other hand, older technology ASICs (130nm and higher) are neither price- nor performance-efficient when compared to the current 45nm FPGAs.

FPGAs have recently been considered as accelerators for a wide spectrum of applications with various computational needs: data mining [39] and genome sequencing [126], logical testing and numerical aggregation operations, medical imaging [57], scientific visualization, physics simulations [114] computational chemistry [88], financial analytics [117, 161]. All these applications involve operations like coordinate mapping, mathematical transformations, filtering etc. and involve massive low and medium-grain parallelism. The architecture of Modern FPGAs have been augmented with "ASIC-like" features: fast-carry chains for enhanced binary addition performance, multiplier blocks for better mapping of digital signal processing applications and arithmetic functions, embedded memories for increasing on-chip throughput etc. These new added features make FPGAs very suitable for accelerating these applications. On one hand, they allow the ad-hoc implementation of the exotic arithmetic operators needed by these computations and not supported in hardware by processors or GPUs. These operators can be deeply pipelined and function at FPGA nominal frequency, yielding significant speedups over their software implementations counterparts. On the other hand, coarser computational data-paths, possibly using these exotic operator instances, may be instantiated. Rather then communicating by means of shared memories wasting computation cycles and power, the data-path components may be simply wired together using the FPGA's reconfigurable interconnect network, allowing the data produced to be directly consumed, thus maximizing efficiency. This thesis studies the FPGA implementation of such arithmetic operators and also the design of coarser arithmetic data-paths.

It's possible to use standard Harware Description Languages (HDLs) (VHDL or Verilog) to manually design arithmetic operators. Handcrafting basic standard operators (not necessarily optimal) is possible using VHDL, but designing exotic operators is a task impossible to perform using VHDL alone. For instance, implementing operators such  $\sqrt{x}$  or some elementary functions  $(e^x, \log x \dots)$  using polynomial approximations requires pre-computing tables of values which are function- and precision-specific, but also depend approximating polynomial degree. External tools are usually used to pre-compute these values.

Operator generators can naturally alleviate the limitations of VHDL. The design space exploration can be done using a high-level programming language (C++, Java, ...) and operator specific VHDL description can be generated. To our knowledge Xilinx pioneered this approach with Logicore. Nowadays, main FPGA manufacturers (Altera and Xilinx) ship operator generators with their design tools, allowing far more parameters for each operator than one could get using a parametrized operator library.

In their simplest form generators can simply perform some design space exploration and write VHDL code files. Therefore, generators are at least as expressive as VHDL. However, the generator's framework could also allow reusing already designed operators, help signal declarations, possibly facilitate pipelining but also provide specialized assistance: help manage arithmetic ar-

gument reduction and other. Due to their proprietary nature, it is unclear how many of these features are provided by the generator frameworks of Altera and Xilinx. Operator generators can also be used for on-the-fly generation of arithmetic components by High-Level Synthesis (HLS) tools targeting FPGAs. They are more flexible and easier to maintain than VHDL arithmetic operator libraries.

FloPoCo <sup>1</sup> (**Flo**ating-**Po**int **Co**res, but not only) is an open-source C++ framework for the generation of arithmetic datapaths. It provides a command-line interface that inputs operator specifications, and outputs synthesizable VHDL. The main goal of this thesis was to develop and refine the FloPoCo generator framework for the class of arithmetic operators. Consequently, one of the main contributions of this thesis is the framework itself. It assists in designing and testing arithmetic operators which can be flexible in input/output precision, may be easily retargeted to other FPGA devices and allow a user-defined trade-off between operating-frequency and occupied resources. All this significantly shortens the arithmetic operator design cycle therefore enhancing productivity.

The second main contribution concerns the library of flexible arithmetic operators designed using the FloPoCo framework. These operators include basic fixed-point and floating-point operators, an automatic generator of fixed-point function implementations based on polynomial approximation, operators for the floating-point square-root and exponential functions and also one meta-operator allowing the fast assembly of available floating-point operators. The work done for describing these operators has validated the framework and motivated its continuous development. Often, the framework enhancements for one operator have improved the performance of other existing operators.

The third contribution of this thesis is the efficient use of the pipelined arithmetic operators generated by FloPoCo in an application context. FloPoCo optimizes the architecture of the generated operators for user defined application constraints, which causes the operator's latency to be dependent on these constraints. Our main objective was to optimize the execution scheduling of codes using these operators which we successfully achieved for applications described using perfectly nested loops with uniform data dependencies.

The final contribution of this thesis is the validation of the FloPoCo framework for implementing a complete application. The framework is put to the test for implementing a flexible, parametric description of an FPGA-specific architecture for solving the "Table Maker's Dilemma". The final architecture consists of several operator layers, all having multiple flexible parameters, and is designed to fill-up the largest FPGAs available. Thanks to the FloPoCo framework, for an extensive set of parameters including the deployment FPGA, an architecture composed of thousands of lines of code is generated in seconds. It allows exploring a large set of possible implementations to select the one which best fits the target FPGA.

We strongly believe that the FPGA implementation of arithmetic data-paths should make the best use of the FPGA's flexibility and available resources. Our experiences in designing arithmetic operators, both before and during the development of FloPoCo, have helped establish and refine a framework which offers, in our opinion, just the right abstraction level for an FPGA-specific arithmetic circuit description.

The rest of this thesis is organized as follows: after briefly presenting in Chapter 2 an overview of the modern FPGA architecture and particularly, the features relevant for arithmetic operator design, we will give in Chapter 3 a brief introduction to floating-point arithmetic and present the relevant works regarding the implementation of floating-point operators in FPGAs. Chapter 4 will then show the various gains of using FloPoCo for designing custom arithmetic datapaths and present in detail the framework's features. Next, Chapter 5 will present the various binary-adder architectures present in FloPoCo and prove that the optimal architecture for a given

<sup>1.</sup> http://flopoco.gforge.inria.fr/

scenario can be chosen based on analytically deduced resource estimation formulas. Chapter 6 will then give an insight on how to build binary multipliers and squarers using fewer multiplier resources. Next, we will present in Chapter 7 a generic fixed-point function evaluation implementation based on polynomial approximation which is both scalable and more performant than other available implementations. This function evaluator is used as the main building block of the floating-point square-root operator presented in Chapter 8 and also as a key component in the implementation of the floating-point exponential function presented in Chapter 9. Next, Chapter 10 presents the FloPoCo implementation of a FPGA-specific floating-point accumulator and of a dot-product operator based on this accumulator. In Chapter 11 we focus on efficiently scheduling the computations of computing kernels described by specific loop nests on pipelined-operators, in the context of using FloPoCo as a back-end for semi-automatic HLS. Finally, in Chapter 12 we show that FloPoCo can effectively be used for describing the architecture of a complete computing application for solving the Table Maker's Dilemma.

#### CHAPTER 2

## Field Programmable Gate Arrays

FPGAs are memory-based integrated circuits whose functionality can be programmed after manufacturing. They were commercially introduced in 1985 by Xilinx [11] with the XC2064 product, and are natural descendants of Complex Programmable Logic Devices (CPLDs).

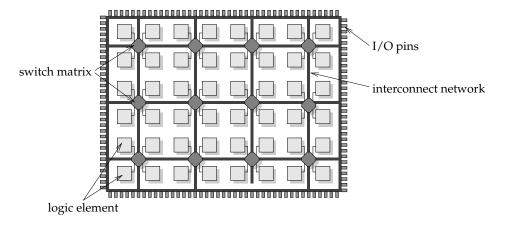

Unlike CPLDs which are organized as small arrays of PALs, FPGAs have a much finer granularity. An FPGA is structured as large bidimensional array (>100K) of logic elements (LEs). The LEs contain small programmable memories (most FPGAs are SRAM-based) and are interconnected by a configurable wiring network. One possible layout of an FPGA architecture which matches this description is presented in Figure 2.1. The reconfigurability of both LE and the interconnect network allows the implementation of any logical circuit provided it fits in the FPGA.

However, reconfigurability comes at a price. Despite an equivalent technological processes, the typical frequency of FPGA designs is in the low hundreds of MHz, whereas the microprocessor counterpart runs at several GHz. A one-to-one comparison between an arithmetic operator supported in silicon in a microprocessor (FP addition for example) and its FPGA counterpart will roughly yield a speedup of 10 in favor of the microprocessor. FPGAs may recover this thanks to the massive parallelism and fine-grain flexibility.

We review next architectural features of FPGAs introduced by the two market leaders Altera and Xilinx between 2004 (with the introduction of the Stratix-II and Virtex-4 devices) up to 2011. We focus on the elements which concern the design of arithmetic operators and we ignore features like: transceivers and embedded processors whose documentation takes more than two thirds of the device handbooks.

Figure 2.1 Very simplified view of a generic FPGA layout

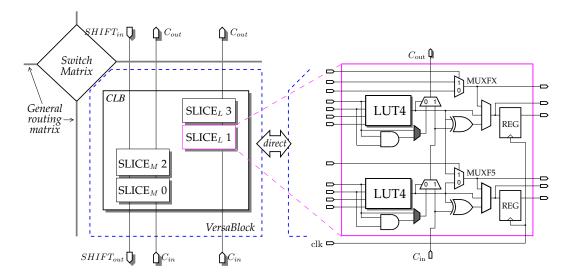

**Figure 2.2** Left: CLB composition and interconnect in Virtex-4 devices Right: Detailed view of a Virtex-4 Slice

#### 2.1 Architecture

The architecture of modern FPGAs is composed of logic elements (implemented as look-up tables), embedded memories, embedded multipliers and several other components as well. Some of these features like look-up tables (LUTs) and small multipliers (in the case of Altera devices) are regrouped into clusters. The advantage of clustering these components is that it reduces the routing pressure. Within a cluster the elements can be fully interconnected while keeping a relatively low number of wires for connecting the cluster to the general routing network. Moreover, some direct connections to neighboring clusters can exist, allowing clusters to interact while bypassing the slower general routing network.

In the case of Xilinx devices, the clusters of LUTs are are called Configurable Logic Blocks (CLBs) whereas in the case of Altera these are called Logic Array Blocks (LABs). The granularity of these clusters is both manufacturer and FPGA-family dependent. It greatly impacts routing and therefore the performance of the FPGA. Modern FPGAs from Xilinx use CLBs of eight LUTs (again, the LUTs size and features vary among device families) whereas Altera uses a slightly larger LAB, with 16 LUTs for Stratix-II and 20 LUTs for Stratix-III/-IV.

Both manufacturers use a second hierarchical regrouping of elements within a cluster: Slices for Xilinx and Adaptative Logic Modules (ALMs) for Altera. The elements of this level regroup together two LUTs together with several other enhanced features which will be reviewed next.

#### 2.1.1 Logic elements

#### **Xilinx**

The CLB structure varies between FPGA generations. In the case of Virtex-4 devices [18] the CLB is made out of four slices grouped in pairs. The pairs are organized in two columns, as presented in Figure 2.2. The slices in the right column are called  $SLICE_Ls$  (the L comes from logic) and those in the left column are  $SLICE_M$  (M comes from memory).  $SLICE_Ms$  provide the same functions as  $SLICE_Ls$  but additionally feature a superset of memory-related functions. A simplified overview of the layout of a  $SLICE_Ls$  is presented on the right of Figure 2.2.

There are two function generators in each Virtex4 slice, denoted by LUT4 in Figure 2.2. Each function generator is implemented as a programmable 4-input LUT totaling 16-bits of memory.

2.1 Architecture 7

This allows the implementation of any 4-input boolean function.

Moreover, slices also contain multiplexers (denoted by MUXF5 and MUXFX in Figure 2.2). They can play two roles: (1) in combination with fast local routing resources they allow implementing functions of more than four variables and (2) can implement multiplexers of up to 16:1 in one CLB and up to 32:1 in two neighboring CLBs.

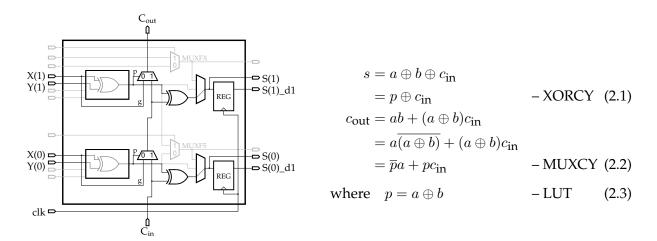

Slices also provide enhanced performance of binary adder and subtracter implementation using the RCA scheme. In this configuration, each half-slice assumes the role of a full-adder. Dedicated fast carry lines traversing vertically the CLBs allow the carry-bit to ripple faster than using the general routing network. Figure 2.3 highlights the slice configuration and presents the implemented full-adder equations necessary for performing binary addition.

Slices also contain storage elements. These can be configured either as flip-flops or as latches. They allow for fine-grain pipelining of logic designs that increases circuit throughput. For example, if the storage elements in Figure 2.3 are configured as D-Q flip-flops, then the signals  $S_{(0)}_{-}d1$  and  $S_{(1)}_{-}d1$  are available one clock cycle later after signals  $S_{(0)}$  and  $S_{(1)}$ .

Additional memory-related functionalities are featured by SLICE<sub>M</sub>s:

- the 16-bit LUT memory can also be configured as a synchronous RAM. Consequently, the CLB can be configured as a 16×4, 32×2, 64×1 single-port or 16×2 dual-port (two pairs of ports for reading and writing) memory.

- the 16-bit LUT memory can play the role of a shift-register, often denoted in Xilinx terminology by SRL16. The 16 suffix specifies that one element can delay serial data from one to 16 clock cycles. In order to build larger shift registers (often needed in digital signal processing but also in datapath synchronization in deeply pipelined designs) the Virtex-4 fabric also contains dedicated cascade lines, ripping vertically from top to bottom (Figure 2.2). Consequently. one single CLB (2 SLICE<sub>M</sub>) may produce delays of up-to 64 cycles. Moreover, these cascade lines also ripple beyond CLB borders allowing to extend the shift-register length at minor delay increases.

The CLB configuration of the more modern Virtex-5 [23] and Virtex-6 [20] devices differs only slightly from that of Virtex-4 devices. The CLB still contains eight function generators, however these are split into two larger slices (one  $SLICE_M$  and one  $SLICE_L$ ).

The function generators in both Virtex-5 and Virtex-6 devices are implemented as six-input LUTs having two independent outputs (O6 and O5). They can implement any six-input boolean function. In this context the O6 output is used exclusively. Nevertheless, as shown by Rose [33] who searched the optimal LUT size in FPGAs, the optimal LUT size is somewhere between 4 and

Figure 2.3 Ripple-Carry Adder (RCA) implementation in Virtex-4 devices

6 with a cluster size ranging from 4 to 10, depending on the application. Consequently, in order to maximize the utilization of the LUT memory, two five-input functions can be implemented in the same LUT provided that they share inputs. In this case both the O5 and the O6 outputs are used.

It is often that in pipelined designs, when both O5 and O6 outputs are used, they are synchronized. Either both outputs bypass the storage elements, or they both need storage elements. For a Virtex-5 device, when both LUT outputs need to be registered, the second storage element needs to be used from a close-by free register of a LUT-FF pair. Nevertheless, this introduces important routing delays, especially when no free registers are not found within CLB borders.

In order to overcome this inconvenience, an extra storage element was added to the Virtex-6 slice. Consequently, both LUT outputs have independent storage elements. When used in LUT6 configuration, the second register is unused and is therefore accessible via the general routing network for area efficient design packing.

Several multiplexers are also available allowing multiplexers of up to 16:1 to be implemented in one single slice. Wider multiplexers are possible but require going through the general routing network and are therefore much slower.

There are some differences in the additional functions provided by SLICE<sub>M</sub>s when compared to Virtex-4 devices:

- with an increased memory of 64-bits per function generator the Virtex-5/6 FPGAs provide 4 times more distributed memory per  $SLICE_M$ . The supported configurations are numerous allowing single-port memories of up 256 bits with a configuration of  $256\times1$ , dual-port memory with configurations  $64\times3$  and  $32\times6$  and quad-port  $64\times1$  or  $32\times2$  for quad-port memories.

- the size of the shift-registers has increased to 32-bit per LUT (SRL32) from the 16 bits per LUT in Virtex-4 devices. However, the cascading connections stop at CLB borders allowing shift-registers of maximum 128 bits (32 bits  $\times$  4 function generators for each SLICE<sub>M</sub>) to be implemented swithout going through the slow general routing network.

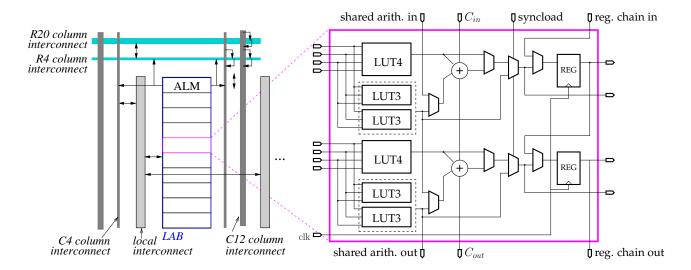

#### Altera

Each ALM in Stratix-II [14], Stratix-III [22] and Stratix-IV [27] devices is composed out of several LUT resources (one 4-input and two 3-input LUTs for each half ALM) and up-to eight input lines that can be shared between two adaptative look-up tables (ALUTs). As shown in Figure 2.4 each ALUT disposes of 32 bits of programmable memory ( $2^4 + 2 \cdot 2^3$ ) and can therefore implement any function of 4 inputs (16 out of 32 bits used), as for Virtex4 devices. Moreover, the 64-bits of memory corresponding to the two ALUTs in an ALM can be combined to implement any 6-input function . There are several other combinations possible in sharing the 64-bits of data among eight inputs, including the LUT5-LUT3 configuration with independent inputs.