## Customizable Memory Controller Architecture and Service Continuity for Off-Chip SDRAM Access in NoC-Based MPSoCs

Khaldon Hassan

### ▶ To cite this version:

Khaldon Hassan. Customizable Memory Controller Architecture and Service Continuity for Off-Chip SDRAM Access in NoC-Based MPSoCs. Micro and nanotechnologies/Microelectronics. Université de Grenoble, 2011. English. NNT: . tel-00656470

## HAL Id: tel-00656470 https://theses.hal.science/tel-00656470

Submitted on 4 Jan 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### UNIVERSITÉ DE GRENOBLE

## **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Micro et Nano Electronique

Arrêté ministériel : 7 août 2006

Présentée par

### Khaldon HASSAN

Thèse dirigée par **Pr. Frédéric PETROT** et codirigée par **M. Marcello COPPOLA**

préparée au sein du Laboratoire TIMA et STMicroelectronics dans l'École Doctorale EEATS

## Architecture De Contrôleur Mémoire Configurable et Continuité de Service Pour l'Accès à la Mémoire Externe Dans Les Systèmes Multiprocesseurs Intégrés à Base de Réseaux Sur Puce

Thèse soutenue publiquement le **2 septembre 2011** devant le jury composé de :

### **Mme. Lorena ANGHEL**

Professeur, Grenoble INP (TIMA), Présidente

### M. Gilles SASSATELLI

Directeur de Recherche, CNRS (LIRMM), Rapporteur

### M. Sébastien PILLEMENT

Maître de conférence, Université de Rennes 1 (IRISA), Rapporteur

### M. Yves MATHIEU

Professeur, Télécom ParisTech (LTCI), Examinateur

### M. Amer BAGHDADI

Maître de conférence, Télécom Bretagne (LabSticc), Examinateur

### M. Frédéric PETROT

Professeur, Grenoble INP (TIMA), Directeur de thèse

### M. Marcello COPPOLA

Manager, STMicroelectronics, Co-encadrant

# Customizable Memory Controller Architecture and Service Continuity for Off-Chip SDRAM Access in NoC-Based MPSoCs

Supervised by Prof. Frédéric PETROT

## **Khaldon HASSAN**

September 2<sup>nd</sup> 2011

Grenoble

France

To my loving parents

Hayat & Mohsen

who unconditionally supported me

all along my life

| Ac            | know    | leda | em   | ents  |

|---------------|---------|------|------|-------|

| $\mathcal{L}$ | KIIOVVI | lcug | CIII | CIILO |

This work would not have been possible without the contributions of many people. I would like to thank Mr. Marcello COPPOLA for the opportunity to carry out my master project in STMicroelectronics in Grenoble, and then to start the PhD journey with his great team: Spidergon ST Network-on-Chip Team. I would like to express my sincere gratitude to Pr. Frédéc Petrot for being my academic advisor, and a role model as mentor and scientist.

I would like to thank Riccardo LOCATELLI, who was here from the very beginning and who technically and scientifically supported me during the last 3 years. Special thanks to Giuseppe MARRUCCIA, Valerio CATALANO, Michael SOULIÉ, Florentine DUBOIS and Déborah LALOMIA for being exceptional colleagues at ST. They made my PhD life more exciting and left me lots of unforgettable memories of this period. I would also like to thank all my colleagues in the SLS group at TIMA Lab.

I would like to take this opportunity to extend my gratitude to all my friends in Syria and France, especially to Rami AL BATAL and Yanal WAZAEFI.

Most importantly I would like to acknowledge the constant support and encouragement of my family. My deepest gratitude and thanks to my parents Hayat and Mohsen for their love, encouragement, and belief in me all along my life. My special thanks to my sisters Chourouk and Soulaf, and my brother Iyas, who supported me a lot.

Finally my heartfelt thanks to Valeria Mongelli for being the greatest girlfriend throughout the long working hours and mood swings to finish the PhD.

HE ONGOING advancements in VLSI technology allow System-on-Chip (SoC) to integrate many heterogeneous functions into a single chip, but still demand, because of economical constraints, a single and shared main off-chip SDRAM. Consequently, main memory system design, and more specifically the architecture of the memory controller, has become an increasingly important factor in determining the overall system performance.

Choosing a memory controller design that meets the needs of the whole system is a complex issue. This requires the exploration of the memory controller architecture, and then the validation of each configuration by simulation. Although the architecture exploration of the memory controller is a key to successful system design, state of the art memory controllers are not as flexible as necessary for this task. Even if some of them present a configurable architecture, the exploration is restricted to limited sets of parameters such as queue depth, data bus size, quality-of-service level, and bandwidth distribution.

Several classes of traffic co-exist in real applications, e.g. *best effort* traffic and *guaranteed service* traffic, and access the main memory. Therefore, considering the interaction between the memory subsystem and the interconnection system has become vital in today's SoCs. Many on-chip networks provide guaranteed services to traffic classes to satisfy the applications requirements. However, very few studies consider the SDRAM access within a *system approach*, and take into account the specificity of the SDRAM access as a target in NoC-based SoCs.

This thesis addresses the topic of dynamic access to SDRAM in NoC-based SoCs. We introduce a totally customizable memory controller architecture based on fully configurable building components and design a high level cycle approximate model for it. This enables the exploration of the memory subsystem thanks to the ease of configuration of the memory controller architecture. Because of the discontinuity of services between the network and the memory controller, we also propose within the framework of this thesis an *Extreme End to*

*End* flow control protocol to access the memory device through a multi-port memory controller. The simple yet novel idea is to exploit information about the memory controller status in the NoC. Experimental results show that by controlling the *best effort* traffic injection in the NoC, our protocol increases the performance of the *guaranteed service* traffic in terms of bandwidth and latency, while maintaining the average bandwidth of the *best effort* traffic.

**Key words:** memory controller, SDRAM, NoC, MPSoC, performance analysis, traffic classes, end-to-end protocol, modelling.

ÉVOLUTION de la technologie VLSI permet aux systèmes sur puce (SoCs) d'intégrer de nombreuses fonctions hétérogènes dans une seule puce et demande, en raison de contraintes économiques, une unique mémoire externe partagée (SDRAM). Par conséquent, la conception du système de mémoire principale, et plus particulièrement l'architecture du contrôleur de mémoire, est devenu un facteur très important dans la détermination de la performance globale du système.

Le choix d'un contrôleur de mémoire qui répond aux besoins de l'ensemble du système est une question complexe. Cela nécessite l'exploration de l'architecture du contrôleur de mémoire, puis la validation de chaque configuration par simulation. Bien que l'exploration de l'architecture du contrôleur de mémoire soit un facteur clé pour une conception réussite d'un système, l'état de l'art sur les contrôleurs de mémoire ne présente pas des architectures aussi flexibles que nécessaire pour cette tâche. Même si certaines d'entre elles sont configurables, l'exploration est restreinte à des ensembles limités de paramètres tels que la profondeur des tampons, la taille du bus de données, le niveau de la qualité de service et la distribution de la bande passante.

Plusieurs classes de trafic coexistent dans les applications réelles, comme le trafic de service au mieux et le trafic de service garanti qui accèdent à la mémoire partagée d'une manière concurrente. En conséquence, la considération de l'interaction entre le système de mémoire et la structur d'interconnexion est devenue vitale dans les SoCs actuels. Beaucoup de réseaux sur puce (NoCs) fournissent des services aux classes de trafic pour répondre aux exigences des applications. Cependant, très peu d'études considèrent l'accès à la SDRAM avec une approche système, et prennent en compte la spécificité de l'accès à la SDRAM dans les systèmes sur puce à base de réseaux intégrés.

Cette thèse aborde le sujet de l'accès à la mémoire dynamique SDRAM dans les systèmes sur puce à base de réseaux intégrés. Nous introduisons une architecture de contrôleur de mémoire totalement configurable basée sur des blocs fonctionnels configurables, et pro-

posons un modèle de simulation associé relativement précis temporellement et à haut niveau d'abstraction. Ceci permet l'exploration du sous-système de mémoire grâce à la facilité de configuration de l'architecture du contrôleur de mémoire. En raison de la discontinuité de services entre le réseau sur puce et le contrôleur de mémoire, nous proposons également dans le cadre de cette thèse un protocole de contrôle de flux de bout en bout pour accéder à la mémoire à travers un contrôleur de mémoire multiports. L'idée, simple sur le principe mais novatrice car jamais proposée à notre connaissance, se base sur l'exploitation des informations sur l'état du contrôleur de mémoire dans le réseau intégré. Les résultats expérimentaux montrent qu'en contrôlant l'injection du trafic de service au mieux dans le réseau intégré, notre protocole augmente les performances du trafic de service garanti en termes de bande passante et de latence, tout en préservant la bande passante moyenne du trafic de service au mieux.

**Mots clés:** contrôleur de mémoire, SDRAM, réseaux intégrés sur puce, multiprocesseurs, analyse de performance, classes de trafic, protocole de bout-en-bout, modélisation.

## Contents

| Ge | enera | d Introduction                                    | XXV    |

|----|-------|---------------------------------------------------|--------|

|    | 1     | Thesis scope                                      | xxviii |

|    | 2     | Thesis organization                               | xxviii |

| 1  | Pro   | blem Definition                                   | 1      |

|    | 1.1   | DDRn SDRAM concepts                               | 3      |

|    | 1.2   | Memory controller concepts                        | 5      |

|    | 1.3   | Quality of service in networks-on-chip            | 7      |

|    | 1.4   | Continuity of services in NoC-based systems       | 8      |

|    | 1.5   | Experiments                                       | 8      |

|    |       | 1.5.1 Simulation environment                      | 9      |

|    |       | 1.5.2 Platform configuration                      | 9      |

|    |       | 1.5.3 Simulation & results                        | 11     |

|    |       | 1.5.4 Experiments summary                         | 15     |

|    | 1.6   | Conclusion                                        | 15     |

| 2  | Stat  | te of the Art                                     | 17     |

|    | 2.1   | Memory controllers                                | 19     |

|    | 2.2   | On-chip interconnects                             | 26     |

|    | 2.3   | Combined interconnect-memory controller solutions | 30     |

|    | 2.4   | Conclusion                                        | 33     |

| 3  | Men   | nory Controller Customizable Architecture         | 35     |

|    | 3.1   | Introduction                                      | 37     |

|    | 3.2   | DDR3 SDRAM operations                             | 38     |

|   | 3.3  | Design | n abstraction in system modelling                                    | . 41 |

|---|------|--------|----------------------------------------------------------------------|------|

|   | 3.4  | Design | n approach                                                           | . 41 |

|   | 3.5  | Assum  | nptions                                                              | . 42 |

|   | 3.6  | Front- | end building components                                              | . 42 |

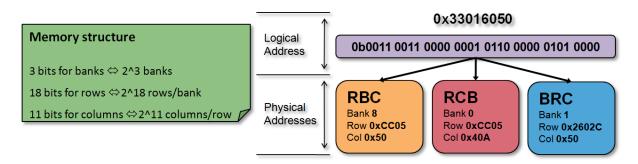

|   |      | 3.6.1  | Memory mapping                                                       | . 42 |

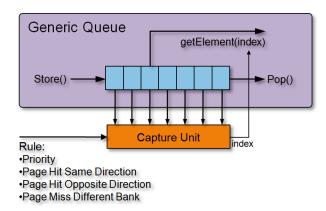

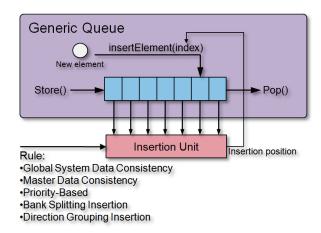

|   |      | 3.6.2  | Generic queue                                                        | . 43 |

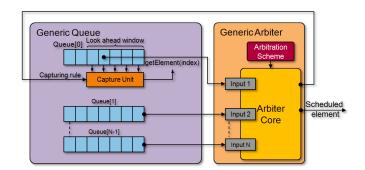

|   |      | 3.6.3  | Capture unit                                                         | . 44 |

|   |      | 3.6.4  | Insertion unit                                                       | . 47 |

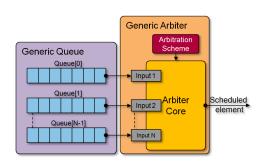

|   |      | 3.6.5  | Generic arbiter                                                      | . 51 |

|   |      | 3.6.6  | Flow control                                                         | . 53 |

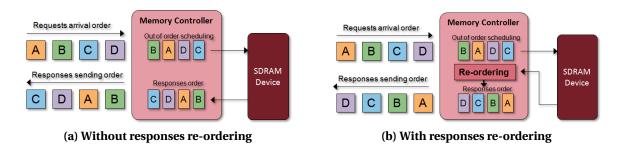

|   |      | 3.6.7  | Re-ordering unit                                                     | . 55 |

|   |      | 3.6.8  | Summary                                                              | . 55 |

|   | 3.7  | Examp  | ples of memory controller front-end                                  | . 56 |

|   |      | 3.7.1  | Memory controller Alpha                                              | . 56 |

|   |      | 3.7.2  | Memory controller Beta                                               | . 56 |

|   |      | 3.7.3  | Memory controller Gamma                                              | . 57 |

|   |      | 3.7.4  | Summary                                                              | . 58 |

|   | 3.8  | Back-e | end building components                                              | . 59 |

|   |      | 3.8.1  | DDR3 SDRAM commands generator                                        | . 60 |

|   |      | 3.8.2  | Memory manager                                                       | . 60 |

|   |      | 3.8.3  | Data handler                                                         | . 61 |

|   | 3.9  | DDR3   | SDRAM model                                                          | . 62 |

|   | 3.10 | Concl  | usion                                                                | . 62 |

| 4 | Evtr | omo Fr | nd to End Flow Control Protocol for SDRAM Access                     | 63   |

| 7 |      |        | luction                                                              |      |

|   | 4.2  |        | t-based flow control                                                 |      |

|   | 7.2  | 4.2.1  | Analytical model for the <i>end-to-end</i> credit-based flow control |      |

|   | 4.3  |        | end flow controls                                                    |      |

|   | 4.4  |        | are on the memory system in modern MPSoCs                            |      |

|   | 4.5  |        | nteed service traffic in the memory controller                       |      |

|   | 4.6  |        | ation risk of the requests queue                                     |      |

|   | 4.0  | 4.6.1  | Problem description                                                  |      |

|   |      | 4.6.2  | Possible solutions                                                   |      |

|   | 4.7  |        | Extreme End-to-End Protocol                                          |      |

|   | 7.1  | 4.7.1  | Novel system approach                                                |      |

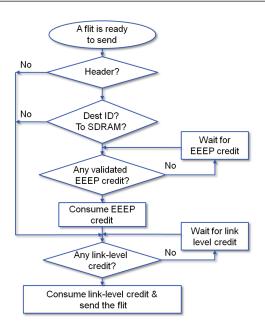

|   |      | 4.7.1  | EEEP principle                                                       |      |

|   |      | 4.1.4  | EEE principie                                                        | . 13 |

|   |     | 4.7.3 EEEP mechanism                                            | 75  |

|---|-----|-----------------------------------------------------------------|-----|

|   |     | 4.7.4 Requests queue sizing method                              | 75  |

|   |     | 4.7.5 EEEP guarantees and limitation                            | 77  |

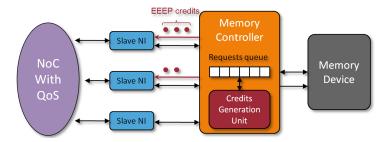

|   |     | 4.7.6 System modifications to support EEEP                      | 78  |

|   | 4.8 | Conclusion                                                      | 79  |

| 5 | Imp | olementation of the Customizable Memory Controller Architecture | 81  |

|   | 5.1 | Development environment                                         | 83  |

|   | 5.2 | NED language overview                                           | 84  |

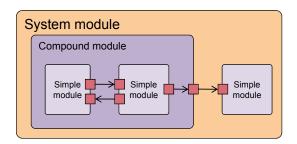

|   | 5.3 | Model structure in OMNeT++                                      | 85  |

|   | 5.4 | General description of a building component                     | 86  |

|   | 5.5 | Memory controller building components parameters                | 87  |

|   |     | 5.5.1 Memory mapping parameters                                 | 88  |

|   |     | 5.5.2 Generic queue parameters                                  | 88  |

|   |     | 5.5.3 Capture unit parameters                                   | 88  |

|   |     | 5.5.4 Insertion unit parameters                                 | 88  |

|   |     | 5.5.5 Generic arbiter parameters                                | 89  |

|   |     | 5.5.6 Re-ordering unit parameters                               | 89  |

|   | 5.6 | EEEP components parameters                                      | 89  |

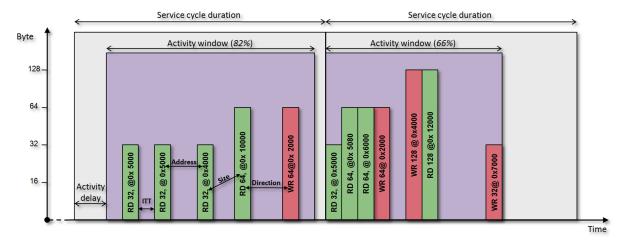

|   | 5.7 | Traffic generator                                               | 90  |

|   | 5.8 | Conclusion                                                      | 92  |

| 6 | Exp | eriments and Results                                            | 93  |

|   | 6.1 | Memory system                                                   | 95  |

|   |     | 6.1.1 Memory controller architecture                            | 95  |

|   | 6.2 | Standalone tests                                                | 96  |

|   |     | 6.2.1 Memory controller configuration for standalone tests      | 96  |

|   |     | 6.2.2 Memory timing tests                                       | 97  |

|   |     | 6.2.3 Priority and ageing mechanism test                        | 99  |

|   |     | 6.2.4 Summary                                                   | .02 |

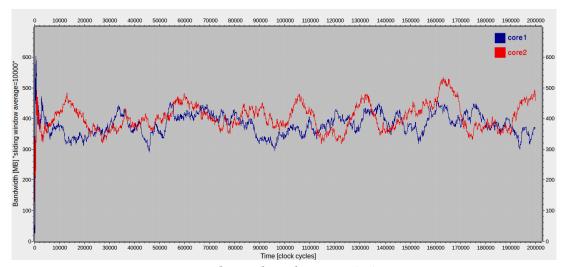

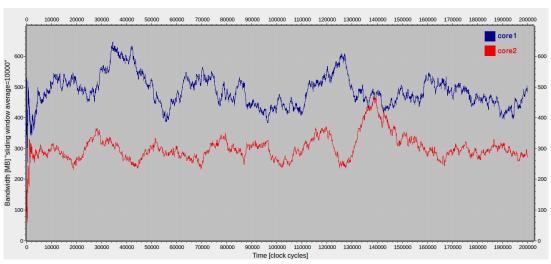

|   | 6.3 | EEEP tests                                                      | .02 |

|   |     | 6.3.1 Traffic modelling                                         | 03  |

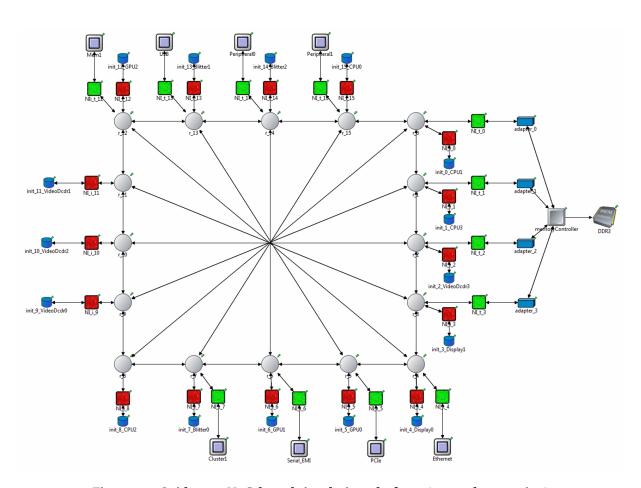

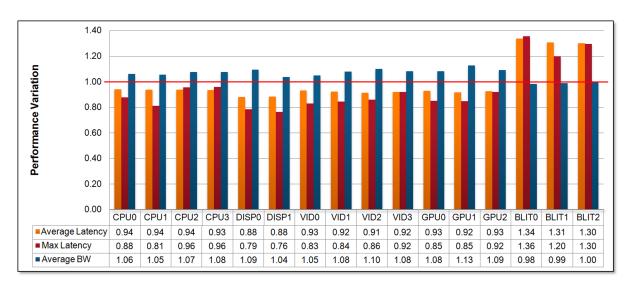

|   |     | 6.3.2 EEEP in a Spidergon NoC-based SoC                         | 03  |

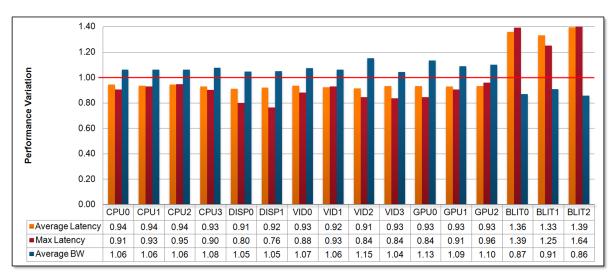

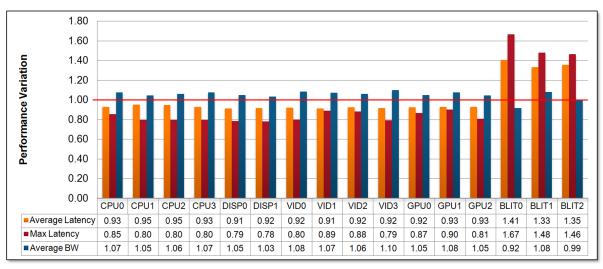

|   |     | 6.3.3 EEEP in a 2DMesh NoC-based SoC                            | 07  |

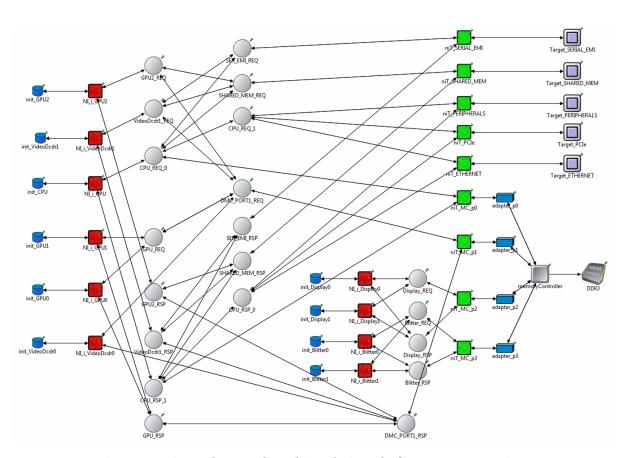

|   |     | 6.3.4 EEEP in an irregular NoC-based SoC                        | .07 |

|   |     | 6.3.5 Analysis                                                  | .11 |

|   | 6.4 | Conclusion                                                      | 12  |

### Contents

| 7  | Con  | clusio          | n and Perspectives                          | 113 |

|----|------|-----------------|---------------------------------------------|-----|

|    | 7.1  | Concl           | usion                                       | 115 |

|    | 7.2  | Future          | e work directions                           | 116 |

|    |      | 7.2.1           | 3D stacking - wide I/O memories             | 117 |

|    |      | 7.2.2           | More memory system information exploitation | 117 |

|    |      | 7.2.3           | Extreme End-to-End Protocol evolution       | 117 |

| Ap | pend | lixs            |                                             | 127 |

| A  | Prol | blem D          | efinition: Simulation Platform              | 127 |

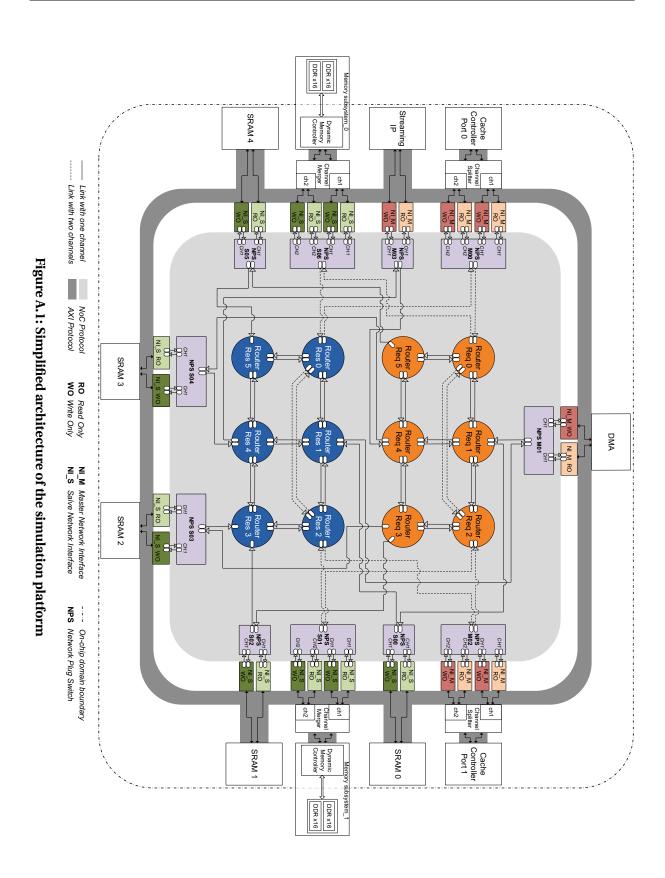

|    | A.1  | Spide           | rgon STNoC building blocks                  | 128 |

|    | A.2  | Platfo          | rm composition                              | 128 |

| В  | Men  | nory C          | ontroller Scheduling Algorithms             | 131 |

| C  | List | of Pub          | lications                                   | 137 |

| D  | Abo  | ut the <i>l</i> | Author                                      | 139 |

# List of Figures

| 1.1 | Simplified architecture of a modern DDR SDRAM                                  | 4  |

|-----|--------------------------------------------------------------------------------|----|

| 1.2 | Time to complete a series of memory references without (a) and with (b) access |    |

|     | reordering                                                                     | 6  |

| 1.3 | Simplified architecture of a memory controller                                 | 7  |

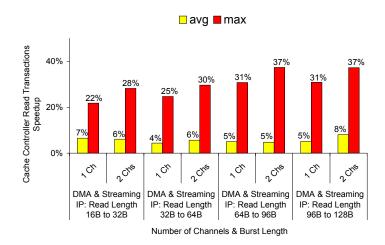

| 1.4 | Off-chip memory access speedup for cache controller read requests when low-    |    |

|     | priority IPs send read requests                                                | 13 |

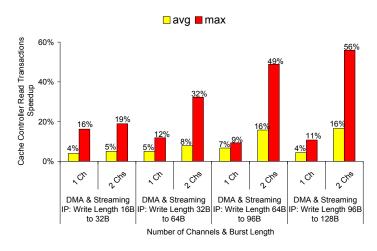

| 1.5 | Off-chip memory access speedup of cache controller read requests when low-     |    |

|     | priority IPs send write requests                                               | 13 |

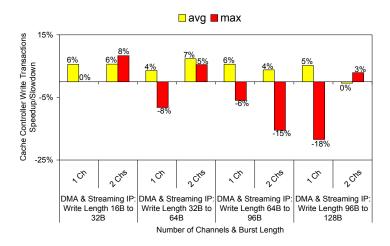

| 1.6 | Off-chip memory access speedup/slowdown of cache controller write requests     |    |

|     | when low-priority IPs send write requests                                      | 14 |

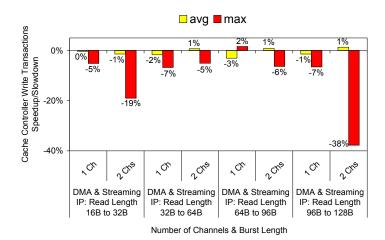

| 1.7 | Off-chip memory access speedup/slowdown of cache controller write requests     |    |

|     | when low-priority IPs send read requests                                       | 15 |

| 2.1 | The logical view of SMC architecture, source [10]                              | 20 |

| 2.2 | Bandwidth optimized SDRAM controller architecture, source [80]                 | 21 |

| 2.3 | (a) Quality aware memory controller (b)MIS architecture, source [48]           | 22 |

| 2.4 | Organization of the on-chip STFM memory controller, source [56]                | 24 |

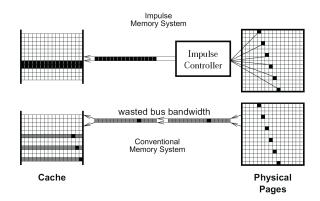

| 2.5 | Using Impulse to remap the diagonal of a dense matrix into a dense cache line. |    |

|     | The black boxes represent data on the diagonal, whereas the gray boxes repre-  |    |

|     | sent nondiagonal data. Source [12]                                             | 25 |

| 2.6 | The Impulse memory architecture. Source [12]                                   | 25 |

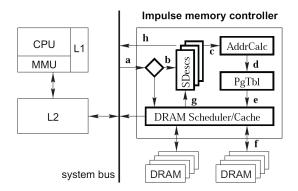

| 2.7 | Predator memory controller architecture, source [1]                            | 25 |

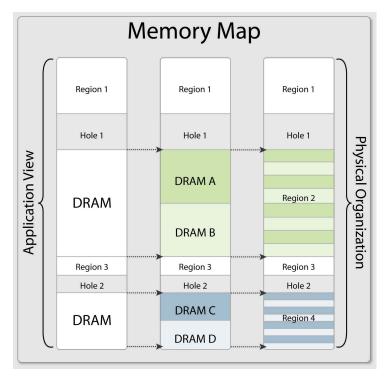

| 2.8 | Memory map interpretation when using Sonics IMT, source [72]                   | 31 |

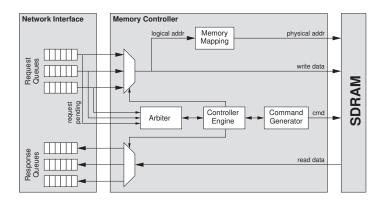

| 2.9 | The proposed memory controller integrated in the slave-side network inter-     |    |

|     | face, source [21]                                                              | 32 |

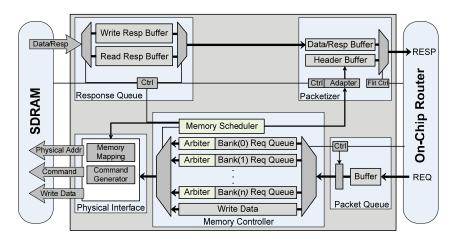

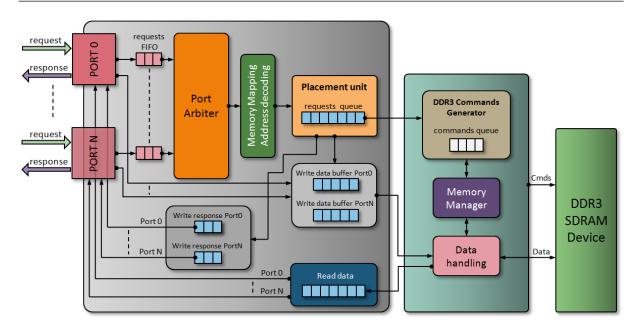

| 3.1 | Generic architecture of a memory controller connected to SDRAM devices         | 38 |

|     |                                                                                |    |

| 3.2  | Simplified diagram of the DDR3 SDRAM FSM                                                       | 39  |

|------|------------------------------------------------------------------------------------------------|-----|

| 3.3  | Examples of memory mapping                                                                     | 43  |

| 3.4  | Simplified architecture of the generic queue                                                   | 44  |

| 3.5  | capture unit in conjunction with a generic queue                                               | 46  |

| 3.6  | Insertion unit in conjunction with a generic queue                                             | 48  |

| 3.7  | Generic arbiter connection with a generic queue                                                | 51  |

| 3.8  | Generic arbiter connection with a generic queue including a capture unit                       | 51  |

| 3.9  | Ordering aspects in memory controllers                                                         | 55  |

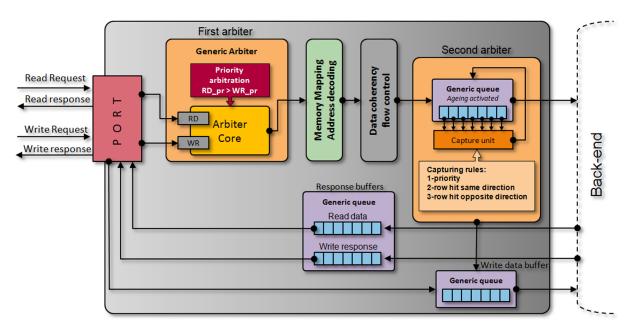

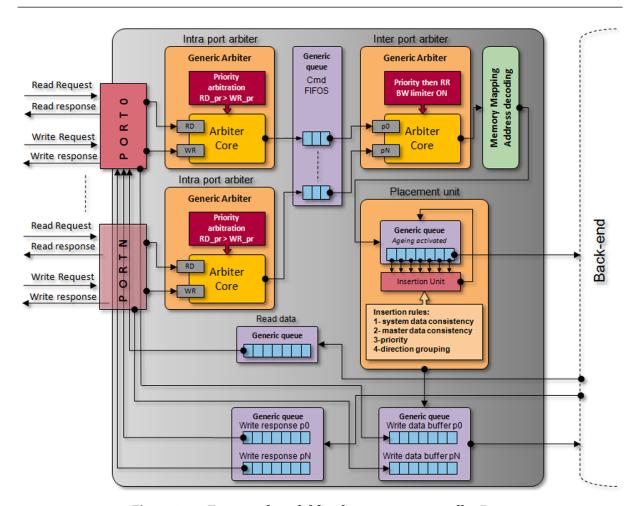

| 3.10 | Front-end model for the memory controller Alpha                                                | 57  |

| 3.11 | Front-end model for the memory controller Beta                                                 | 58  |

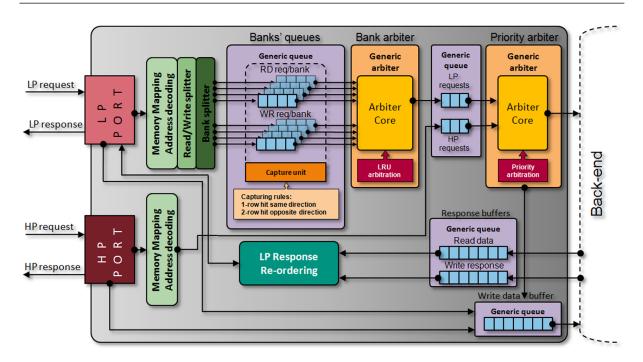

| 3.12 | Front-end model for the memory controller Gamma                                                | 59  |

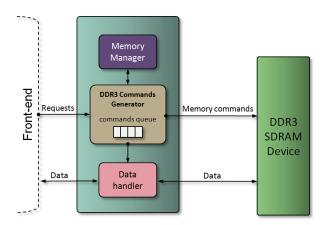

| 3.13 | Back-end architecture                                                                          | 60  |

| 4.1  |                                                                                                | 0.5 |

| 4.1  | The front-end and the back-end of a memory controller                                          | 65  |

| 4.2  | Link level credit-based flow control                                                           | 66  |

| 4.3  | Simplified NI architecture that supports the <i>end-to-end</i> credit-based flow control       |     |

| 4.4  | Overview of TILEpro64 that includes 4 memory controllers, source [78]                          | 69  |

| 4.5  | SoC consumer portable design complexity trends, source ITRS [37]                               | 70  |

| 4.6  | Saturation risk of the requests queue in a memory controller                                   | 72  |

| 4.7  | EEEP extend versus other flow controls extend                                                  | 74  |

| 4.8  | An overview of the EEEP implemented in a system                                                | 75  |

| 4.9  | EEEP diagram for best effort traffic request packets                                           | 76  |

| 4.10 | Memory controller modification to support EEEP                                                 | 79  |

| 5.1  | Model structure in OMNeT++: compound and simple modules, gates, connec-                        |     |

|      | tions                                                                                          | 85  |

| 5.2  | The NED description of the generic arbiter                                                     | 86  |

| 5.3  | The initialization method of the generic arbiter                                               | 86  |

| 5.4  | The activity method of the generic arbiter                                                     | 87  |

| 5.5  | The activity method of the generic arbiter                                                     | 90  |

| 5.6  | The header of a stimuli file for the <i>back-annotated</i> generation mode                     | 91  |

|      |                                                                                                |     |

| 6.1  | Architecture of the multi-port memory controller                                               | 96  |

| 6.2  | Back-end log file: direction switching and bank preparation delay                              | 98  |

| 6.3  | Back-end log file: bank interleaving mechanism                                                 |     |

| 6.4  | Back-end log file: requests format                                                             | 99  |

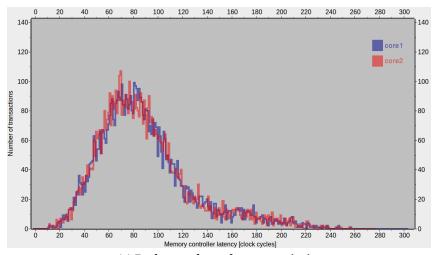

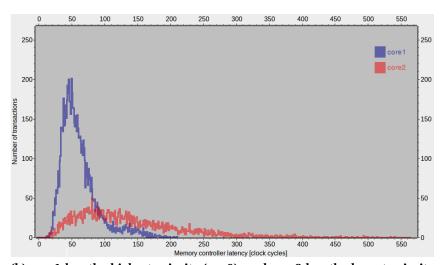

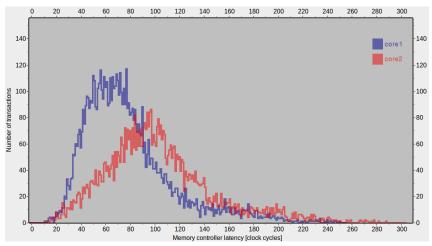

| 6.5  | Memory controller latency histogram for core1 and core2                                        | 100 |

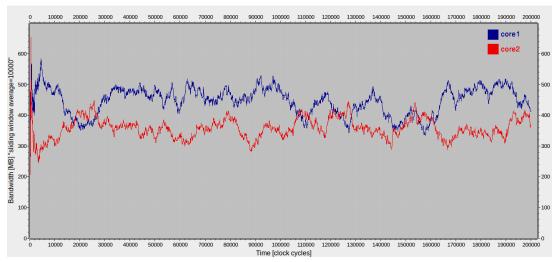

| 6.6  | Moving average bandwidth for core1 and core2                                                   |     |

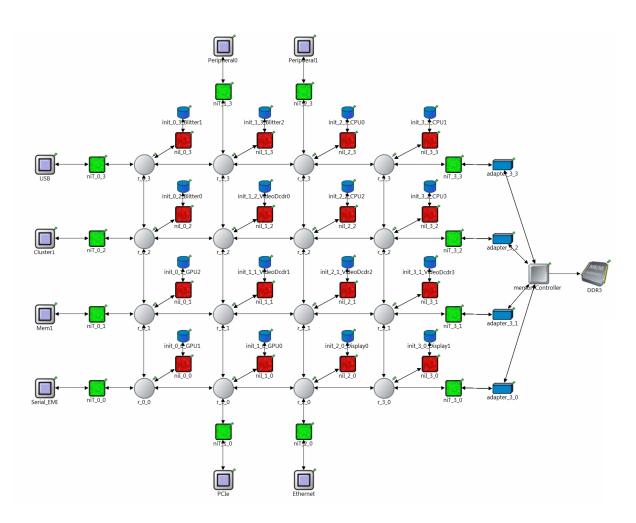

| 6.7  | Spidergon NoC-based simulation platform (across last routing) $\ \ \ldots \ \ldots \ \ \ldots$ | 105 |

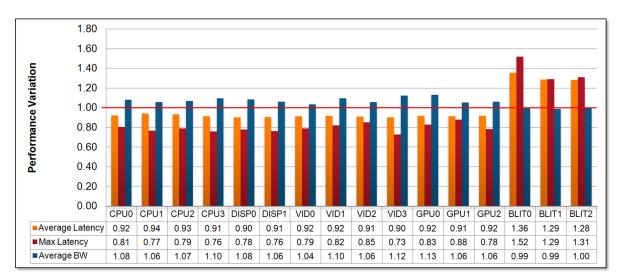

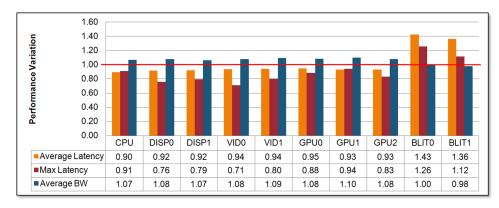

| 6.8  | Performance variation when EEEP is activated in a Spidergon NoC-based SoC $$ .                 | 106 |

| 6.9  | 2DMesh NoC-based simulation platform (XY routing)                                              | 108 |

| 6.10 | Performace variation when EEEP is activated in a 2DMesh NoC-based SoC $\dots$ 109          |

|------|--------------------------------------------------------------------------------------------|

| 6.11 | irregular NoC-based simulation platform (source routing)                                   |

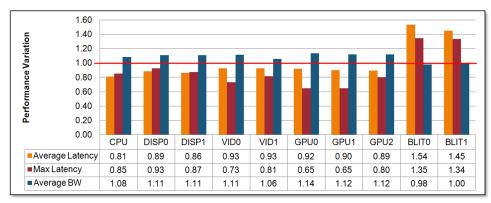

| 6.12 | Performace variation when EEEP is activated in an irregular NoC-based SoC $$ . $$ . $$ 111 |

| A.1  | Simplified architecture of the simulation platform                                         |

## List of Tables

| 1.1 | DDRn SDRAM timing parameters description                                          | 5   |

|-----|-----------------------------------------------------------------------------------|-----|

| 1.2 | Traffic generator characteristics                                                 | 10  |

| 2.1 | Main features of the state of the art memory controllers                          | 26  |

| 2.2 | Main features of the state of the art networks-on-chip providing QoS              | 29  |

| 3.1 | DDR3 SDRAM state digram command definitions                                       | 39  |

| 3.2 | DDR3 SDRAM timing parameters description                                          | 40  |

| 3.3 | Brief description of the generic queue model                                      | 45  |

| 5.1 | Memory mapping parameters                                                         | 88  |

| 5.2 | Generic queue parameters                                                          | 88  |

| 5.3 | Capturing unit parameters                                                         | 88  |

| 5.4 | Insertion unit parameters                                                         | 89  |

| 5.5 | Generic arbiter parameters                                                        | 89  |

| 5.6 | Re-ordering unit parameters                                                       | 89  |

| 5.7 | EEEP parameters                                                                   | 90  |

| 5.8 | Traffic generator, example of the <i>constrained random</i> configuration         | 91  |

| 6.1 | Memory controller configuration for standalone tests                              | 97  |

| 6.2 | Samsung DDR3-800 SDRAM timing parameters                                          | 97  |

| 6.3 | Traffic generators configuration in <i>constrained random</i> mode                | 102 |

| 6.4 | Memory controller configuration for EEEP tests                                    | 103 |

| 6.5 | Traffic generators configuration in <i>constrained random</i> mode for EEEP tests | 104 |

| A.1 | Routing table of both request and response networks                               | 129 |

# List of Algorithms

| l  | Row hit same direction capture                                 |

|----|----------------------------------------------------------------|

| 2  | Row miss different bank capture                                |

| 3  | Master data consistency insertion                              |

| 4  | Bank splitting insertion                                       |

| 5  | Round-Robin, bandwidth scheduling                              |

| 6  | Priority then Round-Robin scheduling with bandwidth limiter 54 |

| 7  | Data consistency flow control                                  |

| 8  | Re-ordering unit                                               |

| 9  | Anticipation of the bank preparation commands 61               |

| 10 | Highest priority capture                                       |

| 11 | Row hit opposite direction capture                             |

| 12 | Global system data consistency insertion                       |

| 13 | Priority-based insertion                                       |

| 14 | Direction grouping insertion                                   |

| 15 | Round-robin scheduling                                         |

| 16 | Initialize least-recently-used                                 |

| 17 | Least-recently-used scheduling                                 |

| 18 | Least-recently-used update                                     |

| 19 | Priority scheduling                                            |

| General Introduction |

|----------------------|

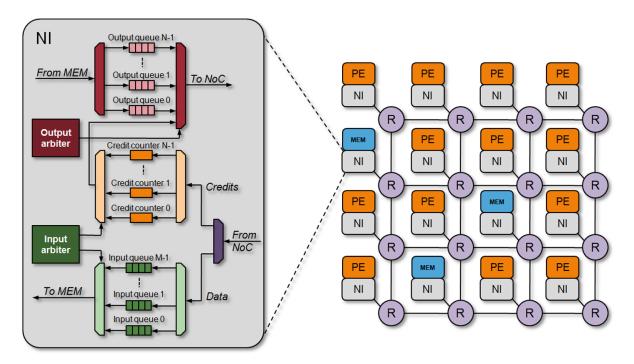

ROM the invention of the integrated circuit until now, the microelectronics industry owes its success to the miniaturization of the transistor on silicon. For nearly 40 years, this miniaturization has been the main factor that increasingly enabled the design of more complex integrated systems. Nowadays, the enhancement of technology processes allows the integration of complete systems into a single chip made of many processing engines such as processors, graphic processing units, video decoders, audio decoders, and display controllers. These systems are called: Multi Processor Systems on Chips (MPSoCs). They are almost found in all electronic devices, especially in consumer electronics such as digital cameras, games consoles, mobile phones and tablet computers.

The increasing integration density in these systems leads to an increasing number of processing engines into a single chip, which in turn requires more efficient on-chip communication systems to inter-connect these processing engines. The history of interconnection systems began with various bus-based systems. From single shared bus to complex hierarchical buses, these complex buses have rapidly shown a strong drawback not only of lack of bandwidth but also of poor scalability with the MPSoCs size. The huge growth in the number of processing engines in MPSoCs coupled with increasing requirements of high bandwidth and low latency have led to a new scalable interconnection structure: Network-on-Chip. By providing scalable performance and higher degree of communication parallelism, NoCs have emerged as suitable interconnect structures for MPSoCs communication requirements.

The development of technology processes has also led to more efficient memory devices with higher bandwidth and storage capacity. Double-Data Rate Synchronous Dynamic Random Access Memories (DDR SDRAMs) were introduced as a cost-effective path for upgrading data bandwidth to memory, and have quickly become the memory of choice in consumer electronics market. DDR SDRAMs have seen a drastic drop in price since 2001, bringing them to price parity with conventional SDRAMs. For technology reasons related to the processes of production, DDR SDRAMs are off-chip. They are often clustered in a memory subsystem made up of *off-chip* memory devices connected to an *on-chip* memory controller. In order to make cost-efficient systems, the designers always try to minimize the number of external pins in a given system. This is why the memory subsystem is often unique and always shared between processing engines, which access it through the network-on-chip.

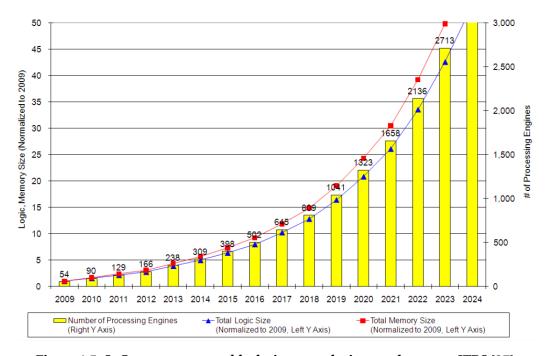

The International Technology Roadmap for Semiconductors (ITRS) predicts that the number of processing engines in the system-on-chip consumer portable designs is going to reach 1000 processing engines in 2019. This emphasizes the increasing pressure on the shared

memory system. Even if several memory systems do exist in the same chip, the ratio between the number of processing engines and the number of memory systems is at least 10. Besides, the traffic patterns that access the shared memory can no longer be deterministic because they tightly depend on the applications run by the user. Therefore, the variety of processing engines in modern MPSoCs leads to a mixture of traffic classes in the memory controller. This mixture of *dynamic* traffic and high pressure make the task of the memory controller more complex.

### 1 Thesis scope

This thesis deals with the shared SDRAM access in NoC-based MPSoCs. Many researchers have focused either on network-on-chip services or on memory controller architectures. However, very few studies consider the access to the shared memory with a *system approach*: from the initiators to the memory system through the routers of the network.

High performance access to the SDRAM is firstly related to the memory subsystem itself, which is made up of SDRAMs modules and a memory controller, and secondly to an optimized sharing of the resource for the different traffic that targets it. As the shared external SDRAM is often unique in a given system, the overall system performance is tightly correlated with the memory subsystem performance.

Exploring the memory controller architecture in a given system helps the designer to find the most appropriate architecture that meets the system requirements in terms of bandwidth and latency. Therefore, we introduce in this work our *customizable architecture* of memory controller, and provide the necessary tools to create and explore memory controller architectures.

Furthermore, we highlight the negative impact on the overall system performance of the service discontinuity between the network-on-chip and the memory subsystem, and we emphasize the importance of the service extension from the NoC to the memory controller. We introduce then a way to couple the services of both network-on-chip and shared memory subsystem through our *extreme end-to-end protocol*.

## 2 Thesis organization

The rest of the manuscript is organized as follows:

Chapter 1 "Problem Definition" provides an overview of the DDR SDRAM access through networks-on-chip. It shows the memory controller task complexity, and how this complexity puts a lot of constraints on the design and makes the architecture exploration of the memory controller very difficult. It also shows the importance of the services coupling between the network and the memory system, and emphasizes the continuity of the guaranteed service,

which can only be ensured by the joint use of architectural and protocol mechanisms.

Chapter 2 "State of The Art" presents the state-of-the-art design of networks-on-chip and memory controller that have a relationship with the off-chip main SDRAM. A particular attention is given to the reconfigurability of the memory subsystem design, to the services provided by the network, and to traffic classes that target the main memory subsystem. At the end, a summary and synthesis of existing reviewed memory controllers and networks-on-chip is provided.

Chapter 3 "Dynamic Memory Controller Customizable Architecture" presents our customizable memory controller design. It begins by providing a detailed description of the DDR3 SDRAM operations. It describes then our high-level building components library that can model any known architecture of memory controller. These building components are cycle approximate, and can precisely simulate all access delays to the shared memory system.

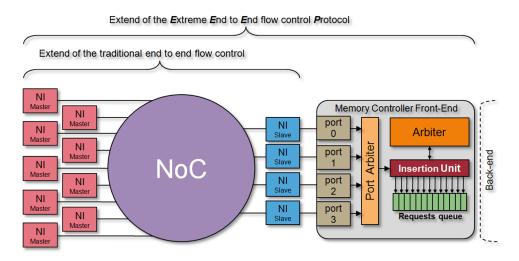

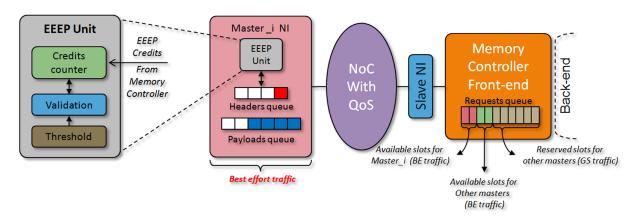

Chapter 4 "Extreme End to End Flow Control Protocol for SDRAM Access" presents our novel end-to-end protocol for shared memory access through a multi-port memory controller. It describes the novelty of this protocol, and the importance of the memory controller state sharing with the network-on-chip.

Chapter 5 "Implementation of the Customizable Architecture of Memory Controller" gives an overview of the development environment (OMNeT++), and describes our method of implementation.

Chapter 6 "Experiments and Results" presents performance analysis of a memory controller architecture modelled with our building components library. It also shows the evaluation of our extreme end-to-end protocol with three different NoC topologies: Spidergon, 2D-mesh, and irregular. A complete analysis of the shared memory access with our protocol is given at the end of this chapter.

Chapter 7 "Conclusion and Perspectives" will wrap up the manuscript by summarizing the major contributions of the thesis and proposing interesting research directions as future work.

# CHAPTER ${f 1}$

## Problem Definition

### **Contents**

| Contents |                                             |

|----------|---------------------------------------------|

| 1.1      | DDRn SDRAM concepts                         |

| 1.2      | Memory controller concepts                  |

| 1.3      | Quality of service in networks-on-chip      |

| 1.4      | Continuity of services in NoC-based systems |

| 1.5      | Experiments                                 |

|          | 1.5.1 Simulation environment                |

|          | 1.5.2 Platform configuration                |

|          | 1.5.3 Simulation & results                  |

|          | 1.5.4 Experiments summary                   |

| 1.6      | Conclusion                                  |

DR SDRAMs stands for Double Date Rate Synchrounous Dynamic Random Access Memory. These memory were introduced as a cost-effective path for upgrading data bandwidth to memory and have quickly become the memory of choice in consumer electronics markets. DDR SDRAMs have seen a drastic drop in price since 2001, bringing them to price parity with conventional SDRAMs. For technology reasons related to the processes of production, DDR SDRAMs are off-chip. They are always shared between IP components, and accessed through an interconnect structure such as a bus or a network-on-chip (NoC).

Revolutionary changes in memory speed, efficiency, size and costs were required in the early 2000's to support the CPUs enhancements. However, these enhancements were not sufficient to fill the frequency gap between the CPU and the memory. The classical CPU-DDR SDRAM case shows that the frequency gap between CPU and main memory eventually offsets most performance gains from further improvements on the CPU speed. For instance, a cache miss is equivalent to hundreds cycles for today's CPUs, a time long enough for the processor to execute hundreds of instructions. While the DDR SDRAM IO frequency has been improving by 37% per year since 2001, the CAS¹ Latency of SDRAM that fundamentally determines its overall performance has been only improving by 5% per year [75; 76; 77]. Hennessy and Patterson showed that microprocessor performance has been improving by 55% per year since 1987, which emphasizes the growing gap between CPUs speed and SDRAM access time [35].

The requirements of MPSoCs<sup>2</sup> for high bandwidth and low latency makes the DDR SDRAM access become a bottleneck. The multi-threading technique used nowadays in multimedia SoCs<sup>3</sup> with heterogeneous cores increases the contention on the main memory system and demands memory systems with more complex architecture and higher performance.

## 1.1 DDRn SDRAM concepts

DDR1, DDR2 and DDR3 are the three generations of DDR SDRAM which exist on the market. DDRn SDRAM uses a double-data-rate architecture to achieve high-speed operation. The double data rate architecture is essentially a  $2^n.w$  prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins where w represents the memory data bus width. A single read or write access for the DDRn SDRAM effectively consists of a single  $2^n.w$ -bit wide, one-clock-cycle data transfer at the internal DRAM core and  $2^n$  corresponding w-bit wide, one-half-clock-cycle data transfers at the I/O pins.

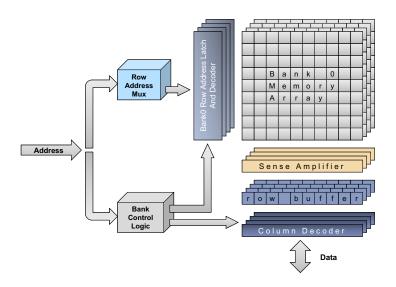

DDRn SDRAMs are three-dimensional memories with the dimensions of bank, row, and column. Figure 1.1 shows a simplified architecture of modern DDRn SDRAM. Each bank is organized as a two-dimensional array of SDRAM cells, consisting of multiple rows and columns.

<sup>&</sup>lt;sup>1</sup>Column Access Strobe

<sup>&</sup>lt;sup>2</sup>Multi Processor System-on-Chip

<sup>&</sup>lt;sup>3</sup>System-on-Chip

Figure 1.1: Simplified architecture of a modern DDR SDRAM

It operates independently of the other banks and contains an array of memory cells that are accessed an entire row at a time. When a row of this memory array is accessed (*row activation*) the entire row of the memory array is transferred into the bank's row buffer. The row buffer serves as a cache to reduce the latency of subsequent accesses to that row. While a row is active in the row buffer, any number of reads or writes (*column accesses*) may be performed.

When the column access is completed, the cache row must be written back to the memory array by an explicit operation bank precharge. This operation prepares the bank for the next row activation command. Read and write commands can be issued with an auto precharge flag resulting in an automatic precharge at the earliest possible moment after the transfer is completed. In order to retain data, all row in the memory array must be refreshed periodically, which is done by precharching all banks and issuing a refresh command. The refresh operation takes  $t_{RFC}$  cycles and must be repeated every  $t_{REF}$  cycles. Table 1.1 shows some DDRn SDRAM nomenclatures.

A memory request falls into two different categories:

- 1. **Row hit**: The request is accessing the row currently in the row buffer. Only a read or a write command is needed. This case results in the lowest bank access latency  $t_{CL}$ .

- 2. **Row miss**: This category can be divided into two subcategories:

- Row closed: There is no row in the row buffer. An activate command needs to be issued to open the row followed by a read or write command. The bank latency of this case is  $t_{RCD} + t_{CL}$  as both a row access and a column access are required.

- Row conflict: The access is to a row different from the one currently in the row buffer. The contents of the row buffer first need to be written back into the memory

**Parameter Name** Description tCL Column access strobe Latency tRCD Row to Column delay tRP Row Precharge delay tWR Write Recovery delay tWTR Write To Read delay tREF REFresh interval tRFC ReFresh Cycle delay

Table 1.1: DDRn SDRAM timing parameters description

array using the *precharge* command. The required row then needs to be opened and accessed using the *activate* and *read/write* commands. This results in the highest bank access latency  $t_{RP}+t_{RCD}+t_{CL}$

Additional delays have to be considered when the last column access is a write operation.  $t_{WR}$  defines the Write Recovery time, which is the minimum time interval between the end of a write operation and the start of a *precharge* command.  $t_{WTR}$  defines the Write To Read turnaround time that represents the minimum time interval between the end of a write operation and the start of a read operation.

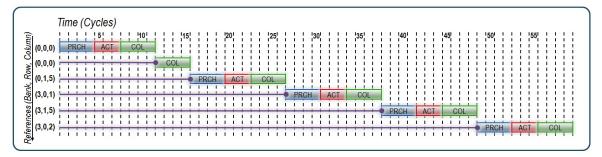

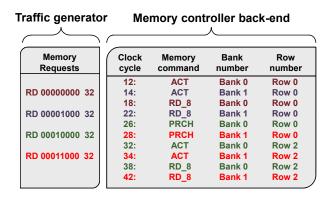

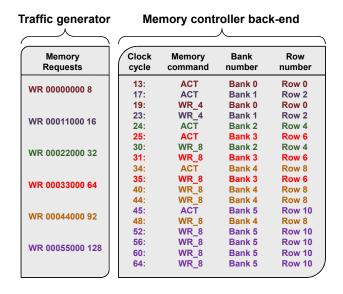

To see the advantage of memory access scheduling, consider the sequence of six memory operations shown in Figure 1.2a. Each reference is represented by the triple (bank, row, column). Suppose we have a memory system utilizing a DDR SDRAM that requires 4 cycles to precharge, 3 cycles to access a row of a bank, and 4 cycles to achieve a read/write operation in a column. Once a row has been accessed, a new column access can issue each cycle until the bank is precharged. If these six references are performed in order, each requires a precharge and a row access (if the row is not ready), and then a column access. These six references require 59 clock cycles to be performed in order. If we assume that the system data consistency will remain guaranteed when we perform the references in a different order, a total of only 34 clock cycles will be needed. Figure 1.2b shows the *out-of-order* scheduling of the six references.

Consequently, the order in which DDR SDRAM accesses are scheduled has a dramatic impact on memory bandwidth and latency. Therefore, typical scheduling algorithms try to increase the row hit ratio to optimize the memory system efficiency. This work is done by the *memory controller*, which is the topic of the next subsection.

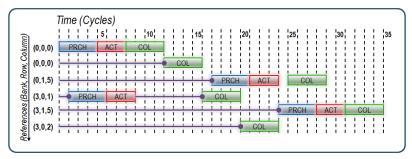

## 1.2 Memory controller concepts

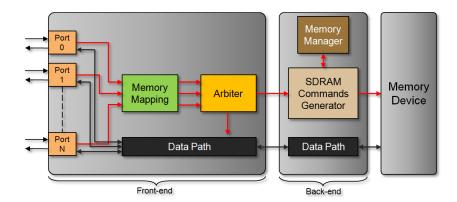

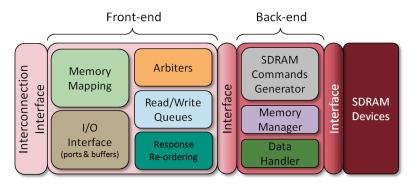

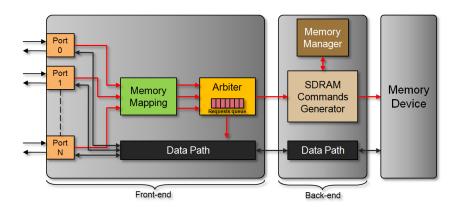

The memory controller plays a principal role in the optimization process of the memory access. It is the interface between the system and the memory modules. The common tasks of a memory controller are memory mapping, request scheduling, command generation and memory management. These tasks are mapped to the memory controller architecture. A typical architecture of a memory controller is showed in Figure 1.3. It is divided into two logical

(a) Without access scheduling (59 clock cycles)

(b) With access scheduling (34 clock cycles)

Figure 1.2: Time to complete a series of memory references without (a) and with (b) access reordering.

blocks called front-end and back-end [2].

- The *front-end* includes the memory mapping and the arbiter. The memory mapping does the translation from the *logical address* space used by the requestors to the *physical address* space (bank, row, column) used by the memory. The arbiter role is to decide what request will next access the memory. The choice can depend on one or more criteria, e.g. the age of the request, the average bandwidth consumed by the requestor, the priority of the requestor, the request direction (read or write), etc...

- The *back-end* includes the commands generator and the memory manager. After the *front-end* arbiter has chosen the request to serve, the actual memory commands have to be generated and sent to the memory. The commands generator is memory-technology-dependent, and designed to target a specific SDRAM. It is programmed with the timings for a particular memory device, and needs to keep track of the state of each memory bank and ensure that no timings are violated. The memory manager guarantees the proper behaviour of the memory and carries out several tasks such as initialization, refreshing and powering down.

The quality of service (QoS) in a memory controller refers to satisfying the initiators requirements in terms of bandwidth and latency while optimizing the memory bus efficiency and guaranteeing the data consistency. Moreover, the memory controller needs to obey all

Figure 1.3: Simplified architecture of a memory controller

SDRAM timing constraints to provide correct functionality. This makes the memory controller task complicated and induces a lot of constraints on its design.

# 1.3 Quality of service in networks-on-chip

The huge growth in the number of embedded components and their need for higher bandwidth and lower latency have led to a new scalable interconnect structure known as Network-on-Chip (NoC). By providing scalable interconnect system and higher degree of parallelism in comparison with previous on-chip communication systems, NoCs have emerged as suitable interconnection solution for modern and future on-chip systems [27].

The quality of service (QoS) in a NoC refers to a resource reservation mechanism guaranteeing that special packets do not share the resources with other packets. These special packets are called *guaranteed service* (GS) packets while the other packets are called *best effort* packets. Best effort is the basic service of a NoC and does not provide any kind of QoS. Therefore, the latency of the packets cannot not be bounded and the throughput cannot be guaranteed. The guaranteed service in a NoC fixes a minimum throughput threshold, and a maximum latency and jitter threshold. In term of QoS, we can define two major types of guarantees [64]:

- The *hard* QoS guarantees the maximum predictability of the network. It bounds and constrains the latency, the throughput and the jitter. This kind of guarantees may be achieved by reserving exclusive accesses to the resources for the guaranteed traffic.

- The *soft* QoS, which is less strict, guarantees the same metrics as the *hard* but has some degree of unpredictability. This kind of guarantees may be achieved by mixing some exclusive and non-exclusive accesses to the shared resources.

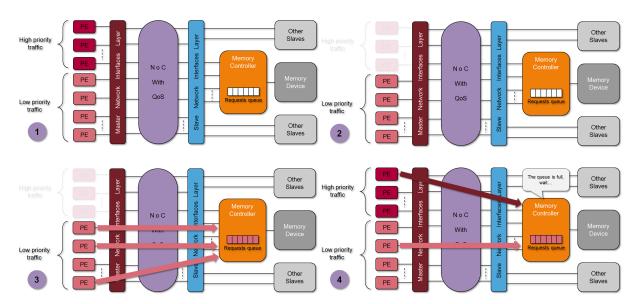

Although the network-on-chip provides QoS to several classes of traffic, it cannot ensure the *continuity* of the QoS when the traffic is addressed to an off-chip memory device because

it crosses the boundary of the network. Neither the network nor the initiators are aware of the memory controller status. We mean by the memory controller status the current activated rows in the SDRAM; the free slots in the buffers; the pressure on each memory bank and the row miss rate after the accesses re-ordering. This lack of information in the network emphasizes the discontinuity of the QoS between the initiators and the memory device.

# 1.4 Continuity of services in NoC-based systems

Whatever the type of the QoS that the network-on-chip provides, either *hard* QoS or *soft* QoS, its continuity from the initiator to the target is essential to satisfy the requestors needs. A large number of paths has been taken by researchers to reduce the system overhead. These paths have been divided into two main approaches. The first one focuses on the memory devices and their scheduler, whereas the second one takes into consideration the interconnect architecture. Recent studies show that memory-oriented approaches can reduce application time execution [17; 58]. However, focusing on memory access alone is not enough. Even with zero latency SDRAM access, the overhead of primary memory system would not be eliminated, because transactions through a shared on-chip communication system such as a NoC still require time.

The interconnect latency between a master and the memory subsystem becomes trickier for latency-sensitive masters, e.g. a *cache controller*. Moreover, most of memory controllers store requests before sending them to the SDRAM, which increases the transactions latency. It makes sense to optimize the combination of external-memory controller and interconnect, and shows the importance of a *system approach* to minimize the overall latency when using a complex interconnection system such as a network-on-chip.

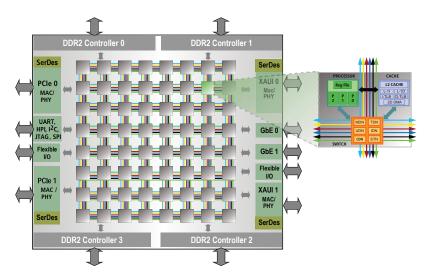

# 1.5 Experiments

Realizing the importance of a *system approach* to optimize external memory access in MP-SoCs, we study in this section the interaction between the memory system and the network-on-chip in an MPSoC platform. The platform in use is a part of an internal STMicroelectronics design that includes a Spidergon STNoC and two commercial and well-spread memory controllers. The platform in use is at RTL level and implemented in VHDL. The NoC in this design represents the interconnect backbone that connects several clusters to the memory subsystems. We focus on this platform because it represents a real case study and offers QoS in both network-on-chip and memory system.

We aim, by running these simulations, at optimizing the *latency-sensitive* traffic sent by the *cache controller* when it accesses the memory subsystems. Note that the *latency-sensitive* traffic coexists with other classes of traffic sent by a *DMA* and a *streaming IP*.

Although we tried to optimize the off-chip memory access by programming the QoS in

the system and by adding dedicated hardware in the network, the QoS *continuity* is still not guaranteed when the traffic crosses the boundary of the network to enter into the memory controller. This is what we are going to show in the following subsections.

#### 1.5.1 Simulation environment

We use in this experiment the Spidergon STNoC [16] as an on-chip interconnect structure. This interconnect is the backbone part of an STMicroelectronics design. Its role is to connect several clusters with the memory subsystems. The necessary details about the simulation platform are given in Annex A.

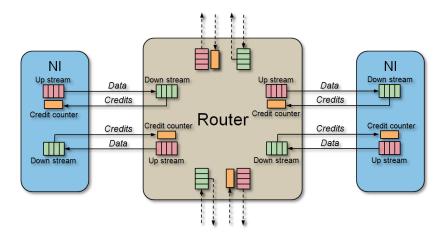

The QoS in Spidergon STNoC indicates the ways to manage bandwidth and latency to ensure a minimal requirement for each traffic flow. Arbitration is a critical part of the router, since it determines the level of QoS support of the network and impacts router performance in terms of critical path delay. As far as bandwidth is concerned, Spidergon STNoC supports the Fair Bandwidth Allocator (FBA) QoS mechanism. It is an end-to-end service that guarantees fair and programmable weighted bandwidth allocation on the top of a distributed network [16].

The Network Plug Switch and the Router can implement two virtual channels through one physical link with the necessary logical blocks for arbitration within a given channel, and between two channels (see Annex A.1 for more information about Spidergon STNoC building blocks). The main advantage of the virtual channels (VCs) technique is a low wire area overhead per additional virtual channel compared to the duplication of the physical link. This stems from the fact that the traffic classes are multiplexed over the same long wires.

Economically viable SDRAMs are driven by single port memory controllers. Thus, we make use of an industrial memory controller existing in the current the state of the art. The memory controller offers QoS in term of latency for read transactions. Entries are arbitrated with an algorithm that optimizes the efficiency of the memory data bus. To achieve optimum memory bus efficiency entries might be arbitrated out of order from their arrival time. The way to ensure QoS is by using priorities for read accesses that require low latency read data. The QoS for read access is determined when the arbiter receives it, and it is based on the requestor ID. No QoS exists for write accesses.

We aim at providing the same level of QoS to high-priority transactions such as *cache controller* transactions in the network and the memory controller. We separate high-priority transactions from other transactions by mapping them to a dedicated *VC*. In addition, we give this *VC* the highest priority in NIs and routers through the network. Moreover, we program the memory controller so as to minimize the stall time of transactions having high priority.

## 1.5.2 Platform configuration

As several configurations of each component are possible, we experimented what we feel the most relevant ones in order to be able to evaluate the performance of the NoC and measure

the DDR1 SDRAM access latency when implementing virtual channels.

#### **Traffic generators**

Each traffic generator has an AMBA AXI interface with two separate channels for read and write requests. The number of outstanding requests<sup>4</sup> for each channel is configurable. The traffic generator has the capability of generating constrained-random traffic in accordance with a statistical distribution which determines the inter-transaction time. We have a full control over AMBA AXI bus parameters such as address range; transaction ID and burst length. A preview of traffic generators characteristics is given in Table 1.2.

**Table 1.2: Traffic generator characteristics**

| IP Name          | Data Rate | Latency  | Jitter   | Burst Length <sup>a</sup>         | Issuing Capabilities |

|------------------|-----------|----------|----------|-----------------------------------|----------------------|

| Cache Ctrl port0 | low       | low      | low      | 32 <sup>b</sup>                   | 2 reads, 2 writes    |

| Cache Ctrl port1 | low       | low      | low      | 32                                | 2 reads, 2 writes    |

| DMA              | high      | tolerant | tolerant | $16 \rightarrow 128^{\text{a,c}}$ | 2 reads, 2 writes    |

| Streaming IP     | high      | tolerant | high     | $16 \rightarrow 128$              | 2 reads, 2 writes    |

<sup>&</sup>lt;sup>a</sup> In Bytes

The traffic balancing of all these generators is defined as 50% towards on-chip SRAMs, and 50% towards off-chip DDR SDRAMs.

#### Memory subsystems

Two identical memory subsystems are connected to the NoC. Each one is made up of the combination of a single port dynamic memory controller and two x16 DDR SDRAMs. The memory controller is programmed after the reset signal. During this period we configure it in specifying the maximal admissible latency value for each initiator (identified by its unique source ID). Thus the memory controller will be able to schedule the requests according to these maximum latency values.

The QoS in the memory controller indicates the ways to manage bandwidth and latency. The latency guarantee of a flow is based on the flow ID, while the minimal bandwidth of a flow is based on the flow ID and the memory bank status (row hit/miss). Within these experiments, the *Cache Controller* read transactions latency must be less than 40 clock cycles.

b Corresponds to the cache line width

<sup>&</sup>lt;sup>c</sup> Allowed burst sizes are : 16, 32, 64, 96, 128 bytes

$<sup>^4</sup>$ The number of outstanding requests is the maximum number of requests the traffic generator can send before receiving any response

#### Interconnect

We use in this simulation platform the Spidergon STNoC interconnect technology. We implement two separated NoCs, one for requests and one for responses. In order to minimize the number of buffers and thus the interconnect area, we only implement two channels on the path between *cache controller* ports and *memory subsystems* (see Figure A.1). The *channel splitters* differentiate among *cache controller* transactions targets and map them to two channels. The *channel splitter* can be activated or not:

- When enabled, it maps *cache controller* transactions towards off-chip memory subsystems to channel 2 (*ch2*) that provides the highest QoS in the NoC, and all other transactions to channel 1 (*ch1*).

- When disabled, it maps all *cache controller* transactions to one channel (*ch1*) with the highest priority. *DMA* and *streaming IP* transactions are also mapped to *ch1* but with low priority.

Therefore, we are able to make a fair comparison of the external memory access latencies when we use a separated channel for *cache controller* transactions only.

As we use a single port memory controller, we need a *channel merger* block to merge both channels in one AMBA AXI bus when the *channel splitter* is enabled. Note that the routing algorithm in the request network and the response network are symmetrical.

### Service coupling of both Spidergon STNoC and memory controller

For the first configuration (only 1 channel), we prioritize all *cache controller* transactions towards the memory subsystems by giving them the highest priority in the router arbiters, and by choosing an arbitration algorithm based on packets priority.

For the second configuration (2 channels), we prioritize the *cache controller* transactions towards the memory subsystems by mapping them to a dedicated channel *ch2*, and by configuring the router arbiters so as to prioritize *ch2* over *ch1* without packets locking on *ch1*. In this way, the high priority requests/responses on *ch2* do not stall behind the other requests/responses on *ch1* on the same physical channel between routers (see Figure A.1).

For both platform configurations (one channel or two channels), we give the highest priority to all *cache controller* transactions.

#### 1.5.3 Simulation & results

To evaluate the capabilities offered by the current memory controller, we measure the latency of the *cache controller* accesses to the external DDR SDRAMs. We change the mapping of its transactions through the interconnect and we measure the latency variation by means of transactions spies. We do here an exploration job in order to evaluate the influence of the burst length of *DMA* and *streaming IP* over *cache controller* transactions. The *cache controller* is sending read&write requests to all slaves; *DMA* and *streaming IP* are also sending

read&write requests to all slaves. We select one range among four burst length ranges for each experiment. The burst length ranges are: 16 to 32; 32 to 64; 64 to 96; and 96 to 128 bytes (see section (1.5.2) for more information about the traffic generation).

For each burst range, we compute the memory access speedup when we use one channel with QoS<sup>5</sup> activated in the memory controller compared to the basic case when the QoS in the memory controller is deactivated( see equation (1.1)). We perform a similar calculation for the memory access speedup when we use two channels with activated QoS in the memory controllers compared to the basic case when no QoS is provided in the memory controllers (see equation (1.2)). When the QoS is deactivated in the memory controller, it becomes unable to cope with the requestors requirements, because it omits the request source ID. However, it continues to provide QoS in term of memory bus efficiency, and tries to increase the row hit rate.

$$Speedup_{(1ch)} = 100 \cdot \frac{Lat_{1ch}^{DMC\_QoS\_on} - Lat_{1ch}^{DMC\_QoS_{off}}}{Lat_{1ch}^{DMC\_QoS_{off}}}$$

(1.1)

$$Speedup_{(2chs)} = 100 \cdot \frac{Lat_{2chs}^{DMC} - QoS_{on} - Lat_{1ch}^{DMC} - QoS_{off}}{Lat_{1ch}^{DMC} - QoS_{off}}$$

(1.2)

Two speedup values are computed, one based on average latency and the other one based on maximum latency. We monitor the round trip latency of *cache controller* reads and writes in four different cases:

#### Cache controller read requests versus DMA and streaming IP read requests

Both low priority IPs *DMA* and *streaming IP* are sending read requests to external DDR SDRAMs. Figure 1.4 shows the off-chip memory access speedup for this scenario. We can note that the implementation of two channels is useful when the burst length of read requests increases. The use of both channels guarantees a speedup of 37% for off-chip memory access based on maximum latency, when the read request burst length crosses 64 bytes.

### Cache controller read requests versus DMA and streaming IP write requests

In this case, the low-priority IPs *DMA* and *streaming IP* are issuing write requests. Figure 1.5 shows the off-chip memory access speedup for *cache controller* read transactions. The speedup obtained in this case when we use two channels is more important than the previous case. Indeed, low-priority write transactions create contention on the physical links connecting the routers *req0* and *req2* to memory subsystems. By using a second channel

<sup>&</sup>lt;sup>5</sup>The definition of the memory controller QoS is given in section (1.5.2).

Figure 1.4: Off-chip memory access speedup for cache controller read requests when low-priority IPs send read requests

for high-priority requests, we can accelerate the memory access by bypassing the long write requests.

The results of both previous cases were expected because the services provided by Spidergon STNoC and memory controllers are coupled. The following two cases show the impact of low-priority transactions over the latency of *cache controller* transactions when the QoS is not extended to the memory controller.

Figure 1.5: Off-chip memory access speedup of cache controller read requests when low-priority IPs send write requests

### Cache controller write requests versus DMA and streaming IP write requests

As we mentioned previously, the dynamic memory controller we are using does not provide any QoS in term of latency for write requests (the memory controller QoS in term of memory bus efficiency is still enabled). Even if we guarantee a maximum latency threshold for write transactions through the request and the response network, they may be stalled in the memory subsystem. Figure 1.6 shows the memory access speedup/slowdown. The memory access speedup which is based on the latency average value is still positive. However, we can not guarantee a maximum latency threshold for the high-priority write transactions.

As the arbiter tries to increase the memory bus efficiency, it prioritizes the requests that increase the row hit rate in DDR SDRAMs banks. The address locality of the *streaming IP* is very high because it accesses adjacent rows. For this reason the memory controller arbiter schedules consecutive write requests coming from the *streaming IP*, and accessing the same row. In consequence, some *cache controller* write requests must wait until the sequence of requests crosses the row boundary, and can be scheduled at the next *Activate Row* command.

If we focus on the last burst length range  $(96\rightarrow128\ \text{bytes})$  in Figure 1.6, we see that there is no slowdown when we use 2 channels. This is explained by the fact that the memory controller cannot schedule a write request while it does not receive the entire packet to write (between 96 and 128 bytes). As the *cache controller* ports send 4-byte-write requests (see table 1.2), their packets can bypass the long packets, and the memory controller entirely receives them before the low priority packets. So the number of high priority requests which are ready to be scheduled will be grater in comparison with the other cases (low-priority burst length  $16\rightarrow96$  bytes).

Figure 1.6: Off-chip memory access speedup/slowdown of cache controller write requests when low-priority IPs send write requests

### Cache controller write requests versus DMA and streaming IP read requests

This simulation scenario is a good example of the need of an extended QoS of service throughout the request and response path between the masters and the DDR SDRAM devices. Although the Spidergon STNoC ensures a maximum latency threshold for the *cache controller* write requests, the low-priority read requests from *DMA* and *streaming IP* gain the upper hand in the memory controller. Figure 1.7 shows how the *cache controller* write requests

are slowed down when low-priority IPs issue read requests towards the external DDRs. The longer the burst length of low-priority read requests, the higher the stall time of high-priority write requests.

In this case, the memory controller arbiter gives the priority to the *DMA* and *streaming IP* read requests whenever it receives these read commands. So the 4-byte write requests of the *cache controller* ports must wait for several arbitration cycles to be scheduled.

Figure 1.7: Off-chip memory access speedup/slowdown of cache controller write requests when low-priority IPs send read requests

#### 1.5.4 Experiments summary

From the previous experiments it is clear that the services provided by the network for the *cache controller* traffic must be extended to the memory controller in order to ensure the same QoS throughout the path between the *cache controller* ports and the memory devices. Even if we map the *cache controller* traffic to a dedicated channel and we give this channel the highest priority inside the network, we cannot be sure that the same level of QoS will be guaranteed inside the memory controller. The impact of the QoS *discontinuity* is obvious when the *cache controller* sends write requests to the memory subsystems while *DMA* and *streaming IP* send read requests to the memory subsystems. Low-priority reads requests are often scheduled before high-priority write requests.

The question arises here: what are the main modifications to apply to the memory controller so that it can provide the appropriate level of quality-of-service?

## 1.6 Conclusion

In this chapter we provided an overview of the DDR SDRAM access through networks-onchip. We have also shown the importance of the service coupling between the network and the memory system. The task of a memory controller is complex because it has not only to obey all SDRAM timing constraints to provide correct functionality, but also to satisfy the initiators requirements in terms of bandwidth and latency. This puts a lot of constraints on the design and makes the exploration of the memory controller architecture very difficult. From a system perspective, the impact of the memory controller architecture on the memory subsystem performance, and consequently on the system performance, is very important. The continuity of the guaranteed service can only be ensured by the joint use of architectural and protocol mechanisms. However, these mechanisms remain to be defined in the VLSI context within its constraints in terms of area and power consumption.

Being able to explore the architecture of the memory controller and its arbitration algorithms is essential to find an optimized architecture with the appropriate arbitration algorithms. This emphasizes the importance of having a memory controller with a *totally customizable architecture*. Such a customizable architecture allows us to study the interaction between the memory system and the network-on-chip, and to measure the impact of the memory controller on the overall system performance.

Another path that is worth considering is the use of some pieces of information related to memory subsystem status in the network-on-chip. However, we should know what information the memory controller has to share with the NoC in order to enhance the network performance within the process of SDRAM requests scheduling.

Designing a memory controller with a totally customizable architecture for NoC-based MPSoCs, and implementing features for DDR SDRAM access in the network-on-chip will be addressed in this thesis with the aim of easing the architecture exploration of a dynamic memory controller and optimizing the access to shared memories in NoC-based MPSoCs.

# CHAPTER ${f 2}$

State of the Art

# Contents

| 2.1 | Memory controllers                                | 19 |

|-----|---------------------------------------------------|----|

| 2.2 | On-chip interconnects                             | 26 |

| 2.3 | Combined interconnect-memory controller solutions | 30 |

| 2.4 | Conclusion                                        | 33 |

**ECOGNIZING** the importance of high performance off-chip SDRAM communication as a key to a successful system design, several memory controllers and on-chip interconnection systems have been proposed. In this chapter, the state of the art on the networks-on-chip and the memory controllers is analysed. The range of the analysis is limited to the topics that provide *guaranteed services*. We separate the related work in three categories: memory controllers, on-chip interconnects, and combined interconnectmemory controller solutions. Principles of SDRAMs and memory controllers are given in Chapter 1,sections (1.1) and (1.2) respectively.

# 2.1 Memory controllers

Existing SDRAM controller designs are either statically or dynamically scheduled, depending on wich kind of systems they target. Statically scheduled memory controllers combine static front-end arbitration with static scheduling of SDRAM commands in the back-end. The precomputed schedule in the back-end makes the design unable to adapt to changes in the behaviour of the requestors. As the static arbitration couples latency and allocated bandwidth, it is not able to satisfy the requirements of latency-latency requestors with low bandwidth requirements without wasting bandwidth. Conversely, dynamically scheduled memory controllers combines dynamic front-end arbitration with dynamic back-end scheduling. These controllers target high-efficiency and flexibility to fit in high-performance systems with dynamic applications whose behaviours may not be known up front [2]. We are addressing in this section the dynamically scheduled memory controllers.

In order to improve the memory efficiency, a number of dynamic memory controllers use information about memory state when scheduling. This consideration is typically done in the back-end. However, some designs communicate memory state to the front-end arbiter, which blurs the distinction between the two. Among the information about the memory state that he front-end use we may mention the open row in each bank and the memory bus direction (read or write).

**Rixner** *et al.* [67] present a controller that privileges the requests which target an open row in a bank. They show that none of the fixed policies studied provide the best performance for all workloads and under all circumstances. However, the FR-FCFS (first-ready first-comefirst-served) policy exploits the locality within the 3-D memory structure (bank/row/column) at best, and provides a 17% performance improvement on the whole set of applications. The optimization mechanisms presented in this study became inevitable for any efficient design of memory controller.

In addition to the open row policy some references use front-end priority-based arbitration to keep up with the requirements of *latency-sensitive* requestors. This kind of requestors often correspond to processors that stall while waiting for a cache lines. **Shao and Davis** [71] propose the *burst scheduling access reordering* mechanism which clusters memory accesses to the same rows of the same banks into bursts to maximize bus utilization of the SDRAM

device. Subject to a static threshold, memory reads are allowed to preempt ongoing writes for reduced read latency, while qualified writes are piggybacked at the end of bursts to exploit row locality in writes and prevent write queue saturation. Nevertheless, clustering memory accesses to the same rows of the same banks could not be efficient for all traffic scenarios.

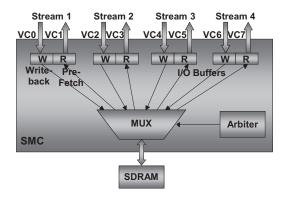

Many dynamic designs use rate regulator in the front-end to protect requestors from each other. This is especially important in controllers with priority-based arbiters, since these are often prone to starvation. **Burchard** *et al.* [10] present a real time streaming memory controller (SMC) that uses a rate regulator in the front-end and considers the memory bus direction within the threads arbitration. The SMC has been designed to allow external SDRAM to be accessed from a PCI Express network. A simplified architecture of the SMC is depicted in Figure 2.1. They propose a fully parametrized credit-based arbitration algorithm. They also propose the extension of the virtual channels (VC) provided by the PCIEx inside the SMC. As they map one stream by VC, the maximum number of parallel streams accessing the SMC is limited by the number of PCIEx VCs (eight VCs), which makes this architecture not scalable.

Figure 2.1: The logical view of SMC architecture, source [10]