# Efficient search-based strategies for polyhedral compilation: algorithms and experience in a production compiler

Konrad Trifunovic

# ► To cite this version:

Konrad Trifunovic. Efficient search-based strategies for polyhedral compilation : algorithms and experience in a production compiler. Other [cs.OH]. Université Paris Sud - Paris XI, 2011. English. NNT : 2011PA112096 . tel-00661334

# HAL Id: tel-00661334 https://theses.hal.science/tel-00661334v1

Submitted on 19 Jan2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE PARIS-SUD 11 U.F.R. SCIENTIFIQUE D'ORSAY

In Partial Fulfillment of the Requirements for the Degree of DOCTOR OF PHILOSOPHY Discipline: Computing science

# Konrad TRIFUNOVIC

Subject:

# **EFFICIENT SEARCH-BASED STRATEGIES**

# FOR POLYHEDRAL COMPILATION:

# ALGORITHMS AND EXPERIENCE IN A PRODUCTION COMPILER

Thesis supervisor: Dr. Albert Cohen

Thesis committee:

M. John Cavazos

M. Philippe Clauss

M. Albert Cohen

M. Yannis Manoussakis

M. Ayal Zaks

University of Delaware

University of Strasbourg

University Paris Sud

IBM Haifa Research Labs

2\_\_\_\_\_

# Contents

| 1  | Intro | oduction                                      | 9  |

|----|-------|-----------------------------------------------|----|

| I  | Basi  | ic Concepts                                   | 15 |

| 2  | Bacl  | sground                                       | 17 |

|    | 2.1   | Mathematical background                       | 17 |

|    | 2.2   | The polyhedral model                          | 18 |

|    |       | 2.2.1 Static Control Parts                    | 19 |

|    | 2.3   | Polyhedral representation                     | 20 |

|    |       | 2.3.1 Polyhedral statements                   | 20 |

|    |       | 2.3.2 Iteration domains                       | 21 |

|    |       | 2.3.3 Data access functions                   | 22 |

|    |       | 2.3.4 Schedules                               | 22 |

|    | 2.4   | Related work and an historical overview       | 23 |

|    | 2.5   | Summary                                       | 23 |

| 3  | Prog  | ram Transformations in the Polyhedral Model   | 25 |

|    | 3.1   | Canonical Form of the Scheduling Functions    | 25 |

|    |       | 3.1.1 Motivation                              | 25 |

|    |       | 3.1.2 Canonical form of the scheduling matrix | 26 |

|    | 3.2   | Capturing semantical constraints              | 28 |

|    |       | 3.2.1 Data dependences                        | 29 |

|    |       | 3.2.2 Memory based dependences                | 31 |

|    |       | 3.2.3 Array data-flow analysis                | 31 |

|    | 3.3   | Transformations and legality                  | 33 |

|    | 3.4   | Related work                                  | 37 |

|    | 3.5   | Summary                                       | 37 |

| II | Th    | e framework                                   | 39 |

|    | ~     |                                               |    |

| 4  | -     | phite framework                               | 41 |

|    | 4.1   | Related Work                                  | 41 |

|    | 4.2   | An overview of the compilation flow           | 42 |

|    |       | 4.2.1 GIMPLE internal representation          | 44 |

|    | 4.3   | Inside GRAPHITE                               | 44 |

|    |       | 4.3.1 SCoP outlining                          | 46 |

|    |                                                                                                        | 4.3.2 Mapping three-address intermediate representation into polyhedra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47                                                                                                                   |

|----|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

|    | 4.4                                                                                                    | The data dependence analysis of three-address code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53                                                                                                                   |

|    | 4.5                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57                                                                                                                   |

|    | т.5                                                                                                    | 4.5.1 Granularity of scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 58                                                                                                                   |

|    |                                                                                                        | 4.5.1       Granutarity of scheduling         4.5.2       Functions represented as relations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 60                                                                                                                   |

|    |                                                                                                        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60                                                                                                                   |

|    | 1.0                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                      |

|    | 4.6                                                                                                    | Conclusions and future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62                                                                                                                   |

|    |                                                                                                        | 4.6.1 Benefits of direct manipulation of the three-address code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 62                                                                                                                   |

|    |                                                                                                        | 4.6.2 Future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63                                                                                                                   |

| 5  | Laz                                                                                                    | y memory expansion scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 65                                                                                                                   |

|    | 5.1                                                                                                    | State of the art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66                                                                                                                   |

|    |                                                                                                        | 5.1.1 Our contribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66                                                                                                                   |

|    | 5.2                                                                                                    | Motivating example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 66                                                                                                                   |

|    | 5.3                                                                                                    | Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 69                                                                                                                   |

|    |                                                                                                        | 5.3.1 Live ranges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 69                                                                                                                   |

|    |                                                                                                        | 5.3.2 Live range violation analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70                                                                                                                   |

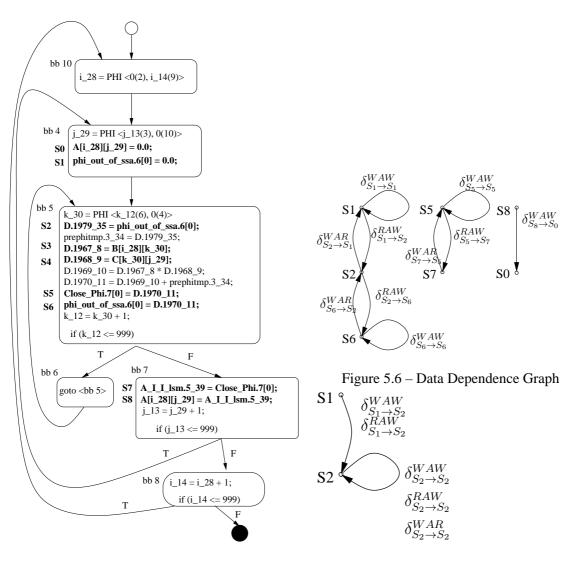

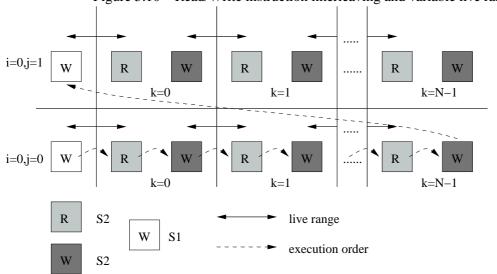

|    |                                                                                                        | 5.3.3 An example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 71                                                                                                                   |

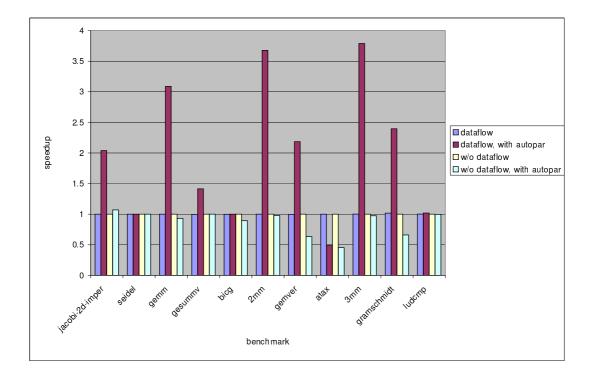

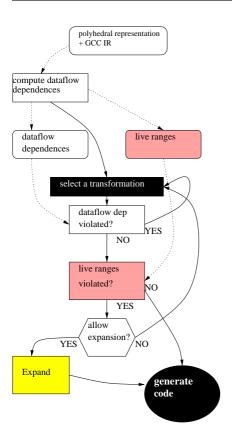

|    | 5.4                                                                                                    | Performance benefits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 72                                                                                                                   |

|    | 5.5                                                                                                    | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 73                                                                                                                   |

|    | 5.6                                                                                                    | Conclusions and perspectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 76                                                                                                                   |

|    | 5.0                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10                                                                                                                   |

| II | тт                                                                                                     | wanda a saanah stratagy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 77                                                                                                                   |

| 11 | 1 10                                                                                                   | owards a search strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | //                                                                                                                   |

| 6  | Ana                                                                                                    | lytical cost model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79                                                                                                                   |

|    | 6.1                                                                                                    | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80                                                                                                                   |

|    |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 00                                                                                                                   |

|    |                                                                                                        | 6.1.1 SIMD Vectorization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80                                                                                                                   |

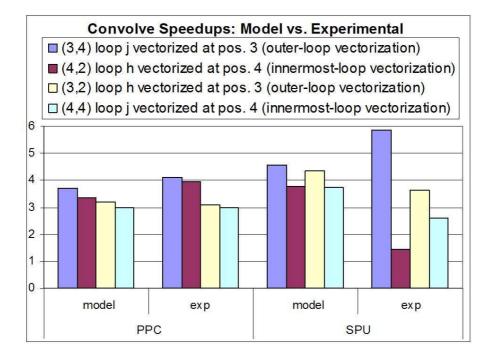

|    |                                                                                                        | <ul><li>6.1.1 SIMD Vectorization</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                      |

|    | 6.2                                                                                                    | 6.1.2 Motivating Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80                                                                                                                   |

|    | 6.2                                                                                                    | 6.1.2Motivating ExamplePolyhedral Modelling of Vectorization Metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80<br>81                                                                                                             |

|    | 6.2                                                                                                    | <ul> <li>6.1.2 Motivating Example</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 80<br>81<br>83                                                                                                       |

|    | 6.2                                                                                                    | <ul> <li>6.1.2 Motivating Example</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 80<br>81<br>83<br>84<br>84                                                                                           |

|    | 6.2                                                                                                    | 6.1.2Motivating ExamplePolyhedral Modelling of Vectorization Metrics6.2.1Modelling the Access Patterns6.2.2Access Pattern Sensitivity to Scheduling6.2.3Cost Model Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 80<br>81<br>83<br>84<br>84<br>85                                                                                     |

|    |                                                                                                        | 6.1.2Motivating Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80<br>81<br>83<br>84<br>84<br>85<br>87                                                                               |

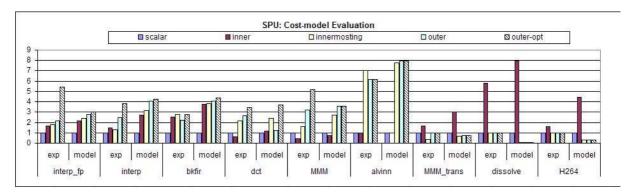

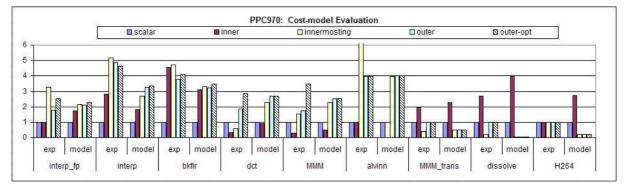

|    | <ul><li>6.2</li><li>6.3</li></ul>                                                                      | 6.1.2Motivating ExamplePolyhedral Modelling of Vectorization Metrics6.2.1Modelling the Access Patterns6.2.2Access Pattern Sensitivity to Scheduling6.2.3Cost Model Function6.2.4Vectorization Profitability MetricsEvaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 80<br>81<br>83<br>84<br>84<br>85<br>87<br>87                                                                         |

|    |                                                                                                        | 6.1.2Motivating ExamplePolyhedral Modelling of Vectorization Metrics6.2.1Modelling the Access Patterns6.2.2Access Pattern Sensitivity to Scheduling6.2.3Cost Model Function6.2.4Vectorization Profitability MetricsEvaluation6.3.1Driving the search process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 80<br>81<br>83<br>84<br>84<br>85<br>87<br>87<br>87                                                                   |

|    |                                                                                                        | 6.1.2Motivating Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80<br>81<br>83<br>84<br>85<br>87<br>87<br>87<br>87<br>89                                                             |

|    |                                                                                                        | 6.1.2Motivating ExamplePolyhedral Modelling of Vectorization Metrics6.2.1Modelling the Access Patterns6.2.2Access Pattern Sensitivity to Scheduling6.2.3Cost Model Function6.2.4Vectorization Profitability MetricsEvaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 80<br>81<br>83<br>84<br>84<br>85<br>87<br>87<br>87<br>87<br>89<br>90                                                 |

|    | 6.3                                                                                                    | 6.1.2Motivating ExamplePolyhedral Modelling of Vectorization Metrics6.2.1Modelling the Access Patterns6.2.2Access Pattern Sensitivity to Scheduling6.2.3Cost Model Function6.2.4Vectorization Profitability MetricsEvaluation6.3.1Driving the search process6.3.2Experimental setup6.3.3Qualitative Evaluation6.3.4Evaluation on a benchmark suite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 80<br>81<br>83<br>84<br>84<br>85<br>87<br>87<br>87<br>87<br>89<br>90<br>92                                           |

|    | 6.3<br>6.4                                                                                             | 6.1.2Motivating ExamplePolyhedral Modelling of Vectorization Metrics6.2.1Modelling the Access Patterns6.2.2Access Pattern Sensitivity to Scheduling6.2.3Cost Model Function6.2.4Vectorization Profitability MetricsEvaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 80<br>81<br>83<br>84<br>85<br>87<br>87<br>87<br>87<br>89<br>90<br>92<br>93                                           |

|    | 6.3                                                                                                    | 6.1.2Motivating ExamplePolyhedral Modelling of Vectorization Metrics6.2.1Modelling the Access Patterns6.2.2Access Pattern Sensitivity to Scheduling6.2.3Cost Model Function6.2.4Vectorization Profitability Metrics6.3.1Driving the search process6.3.2Experimental setup6.3.3Qualitative Evaluation6.3.4Evaluation on a benchmark suiteRelated WorkConclusions and future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80<br>81<br>83<br>84<br>85<br>87<br>87<br>87<br>87<br>87<br>90<br>92<br>93<br>94                                     |

|    | 6.3<br>6.4                                                                                             | 6.1.2Motivating ExamplePolyhedral Modelling of Vectorization Metrics6.2.1Modelling the Access Patterns6.2.2Access Pattern Sensitivity to Scheduling6.2.3Cost Model Function6.2.4Vectorization Profitability MetricsEvaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 80<br>81<br>83<br>84<br>85<br>87<br>87<br>87<br>87<br>89<br>90<br>92<br>93                                           |

| 7  | 6.3<br>6.4<br>6.5                                                                                      | 6.1.2Motivating ExamplePolyhedral Modelling of Vectorization Metrics6.2.1Modelling the Access Patterns6.2.2Access Pattern Sensitivity to Scheduling6.2.3Cost Model Function6.2.4Vectorization Profitability Metrics6.3.1Driving the search process6.3.2Experimental setup6.3.3Qualitative Evaluation6.3.4Evaluation on a benchmark suiteRelated WorkConclusions and future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80<br>81<br>83<br>84<br>85<br>87<br>87<br>87<br>87<br>87<br>90<br>92<br>93<br>94                                     |

| 7  | 6.3<br>6.4<br>6.5                                                                                      | 6.1.2Motivating ExamplePolyhedral Modelling of Vectorization Metrics6.2.1Modelling the Access Patterns6.2.2Access Pattern Sensitivity to Scheduling6.2.3Cost Model Function6.2.4Vectorization Profitability MetricsEvaluation6.3.1Driving the search process6.3.2Experimental setup6.3.3Qualitative Evaluation6.3.4Evaluation on a benchmark suiteRelated WorkConclusions and future work6.5.1Future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 80<br>81<br>83<br>84<br>85<br>87<br>87<br>87<br>87<br>89<br>90<br>92<br>93<br>94<br>94                               |

| 7  | 6.3<br>6.4<br>6.5<br>Trai                                                                              | 6.1.2       Motivating Example         Polyhedral Modelling of Vectorization Metrics         6.2.1       Modelling the Access Patterns         6.2.2       Access Pattern Sensitivity to Scheduling         6.2.3       Cost Model Function         6.2.4       Vectorization Profitability Metrics         6.3.1       Driving the search process         6.3.2       Experimental setup         6.3.3       Qualitative Evaluation         6.3.4       Evaluation on a benchmark suite         Related Work                                                                                                                                                                                                                                                                                                                                                                                         | 80<br>81<br>83<br>84<br>85<br>87<br>87<br>87<br>87<br>89<br>90<br>92<br>93<br>94<br>94<br><b>97</b>                  |

| 7  | 6.3<br>6.4<br>6.5<br><b>Tran</b><br>7.1                                                                | 6.1.2       Motivating Example         Polyhedral Modelling of Vectorization Metrics         6.2.1       Modelling the Access Patterns         6.2.2       Access Pattern Sensitivity to Scheduling         6.2.3       Cost Model Function         6.2.4       Vectorization Profitability Metrics         6.2.4       Vectorization Profitability Metrics         6.3.1       Driving the search process         6.3.2       Experimental setup         6.3.3       Qualitative Evaluation         6.3.4       Evaluation on a benchmark suite         Related Work                                                                                                                                                                                                                                                                                                                                 | 80<br>81<br>83<br>84<br>85<br>87<br>87<br>87<br>87<br>89<br>90<br>92<br>93<br>94<br>94<br>94<br>94<br>97             |

| 7  | <ul> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Tran</li> <li>7.1</li> <li>7.2</li> </ul>              | 6.1.2       Motivating Example       Polyhedral Modelling of Vectorization Metrics         6.2.1       Modelling the Access Patterns       6.2.1         6.2.2       Access Pattern Sensitivity to Scheduling       6.2.2         6.2.3       Cost Model Function       6.2.3         6.2.4       Vectorization Profitability Metrics       6.2.4         Evaluation       6.3.1       Driving the search process         6.3.1       Driving the search process       6.3.3         G.3.3       Qualitative Evaluation       6.3.4         Evaluation on a benchmark suite       6.3.4       Evaluation on a benchmark suite         6.3.4       Evaluation on a benchmark suite       6.5.1       Future work         6.5.1       Future work       6.5.1       Future work       6.5.1         Related work       1       1       1         Motivation soft the current approaches       1       1 | 80<br>81<br>83<br>84<br>85<br>87<br>87<br>87<br>87<br>87<br>90<br>92<br>93<br>94<br>94<br>94<br>94<br>97<br>97       |

| 7  | <ul> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>Tran</li> <li>7.1</li> <li>7.2</li> <li>7.3</li> </ul> | 6.1.2       Motivating Example       Polyhedral Modelling of Vectorization Metrics         6.2.1       Modelling the Access Patterns       6.2.1         6.2.2       Access Pattern Sensitivity to Scheduling       6.2.2         6.2.3       Cost Model Function       6.2.3         6.2.4       Vectorization Profitability Metrics       6.2.4         Evaluation       6.3.1       Driving the search process         6.3.1       Driving the search process       6.3.3         G.3.3       Qualitative Evaluation       6.3.4         Evaluation on a benchmark suite       6.3.4       Evaluation on a benchmark suite         6.3.4       Evaluation on a benchmark suite       6.5.1       Future work         6.5.1       Future work       6.5.1       Future work       6.5.1         Related work       1       1       1         Motivation soft the current approaches       1       1 | 80<br>81<br>83<br>84<br>85<br>87<br>87<br>87<br>87<br>87<br>90<br>92<br>93<br>94<br>94<br>94<br>97<br>98<br>00<br>00 |

|     |                           | 7.5.1   | Dependence satisfaction                                     | 101 |

|-----|---------------------------|---------|-------------------------------------------------------------|-----|

|     | 7.6                       | The spa | ace of legal affine transformations                         | 102 |

|     |                           | 7.6.1   | Multidimensional schedules                                  | 105 |

|     | 7.7                       | Discret | e sets of one-dimensional legal solutions                   | 106 |

|     |                           | 7.7.1   | State of the art                                            | 107 |

|     |                           | 7.7.2   | Narrowing the search space                                  | 107 |

|     |                           | 7.7.3   | Building non-convex sets of one-dimensional legal schedules |     |

|     | 7.8                       | Non-co  | onvex solution sets                                         | 110 |

|     |                           | 7.8.1   | Efficient operations on solution sets                       | 111 |

|     | 7.9                       | Sets of | multi-dimensional legal solutions                           | 114 |

|     |                           | 7.9.1   | Representing weak/strong satisfaction                       | 114 |

|     |                           | 7.9.2   | Orthogonal completion                                       | 115 |

|     | 7.10                      | Toward  | ls search methodology                                       | 118 |

|     |                           | 7.10.1  | Finding global solutions                                    | 119 |

|     |                           | 7.10.2  | Dependence satisfaction strategies                          | 120 |

|     |                           | 7.10.3  | Distribution/fusion scheme                                  | 122 |

|     | 7.11                      | Conclu  | sions                                                       | 123 |

| 8   |                           |         | and perspectives                                            | 125 |

|     | 8.1                       | Perspec | ctives                                                      | 127 |

| A   | Appl                      | ication | of Farkas lemma                                             | 129 |

| Per | Personal Bibliography 133 |         |                                                             |     |

# Notation

| Mathematical                |                                       |

|-----------------------------|---------------------------------------|

| $\mathbb{R}$                | a set of real numbers                 |

| $\mathbb{Z}$                | a set of integer numbers              |

| Q                           | a set of rational numbers             |

| $(i_1, i_2, \ldots, i_n)^T$ | a column vector represented in a row  |

| Polyhedral model            | -                                     |

| i                           | iteration vector                      |

| t                           | timestamp vector                      |

| S                           | statement set                         |

| S                           | a polyhedral statement                |

| $(S,\mathbf{i})$            | statement instance                    |

| $\mathcal{D}^{S}$           | an iteration domain of statement S    |

| $ \mathcal{D}^{S} $         | iteration volume                      |

| $\mathrm{A}\in\mathcal{A}$  | an array in an array set              |

| $\Theta^S$                  | a scheduling function for statement S |

| R                           | a data reference                      |

| $f(\mathbf{i})$             | access function                       |

| $\ell(\mathbf{i})$          | linearized access function            |

| G = (V, E)                  | dependence graph                      |

| $\mathcal{P}_{e}$           | dependence polyhedron                 |

# Chapter 1

# Introduction

The responsibility of a *compiler* is to translate the programs written in a language suitable for use by human programmer into the machine language of the target machine. Naturally, the compiler is required to produce the *correct* translation to the machine code.

In 1944 John von Neumann has laid the foundation to almost all widely used architectures today - that of decoupling the program memory from data memory. This also implied a sequential execution model, in which the machine instructions are executed sequentially, changing the global state of the memory through stores and loads.

Besides producing the correct code, compilers were enhanced with *optimizations*, so that the translated machine code performance could match the performance of the hand-crafted one. Contributions in scalar optimizations, interprocedural analysis, instruction scheduling and register allocation mainly achieved this goal.

The major driving forces for the sustained computing performance increase were the advancements in instruction level parallelism (ILP) and ever increasing clock rates of uniprocessors - according to the Moore's law. This obviated the need for advanced compiler optimizations, since the performance boost could have been obtained by running non-modified sequential codes on the new machines. Advanced compiler optimizations were considered as a domain of specialized, scientific computing community, specializing in the expensive parallel and vector machines programmed mainly in FORTRAN.

#### End of uniprocessor era

The trends have changed in the early 2000s, since it was noticed that increasing the ILP brought diminishing returns, altogether with physical limitations and power dissipation that have put an end to the increase in the clock-speeds of uniprocessors. The capacity to increase the number of transistors has since then been used in another direction: providing *multiple cores* on the single chip.

### The era of multi-core

Multi-core processors are now in widespread use in almost all areas of the computing: in desktop or laptop machines, accelerators like the Cell Broadband Engine, GPUs, GPGPUs and in mobile embedded devices implemented as MP-SoCs (Multiprocessor System-on-Chip).

In the scientific computing field, where specialized multiprocessors have been used since 1960's, the commodity multicore and GPGPUs are entering very rapidly, as main building blocks of the computational clusters.

### Optimizing compilers are again in demand

To harness the power of multiple cores and complex memory hierarchies, the need for powerful compiler optimizations is now again in high demand. Compilers are now required to efficiently map the semantics of the, mostly imperative, high-level programming languages into the efficient use of target architecture resources [82].

Increasing the number of cores on a chip does not improve the performance of the legacy, singlethreaded applications. What is more, the sequential programming paradigm, due to the simplicity of the von Neumann computational model, is still used to program the new applications. Those applications do not benefit from the performance improvements of the new architectures.

In order to utilize the peak performance of the current multi-core architectures, the optimizing compiler is responsible for finding the intrinsic *parallelism* within the computations of the source program. Also, the memory hierarchy has to be utilized carefully, in order to narrow down the gap between latencies of the main memory and the computing core - the *memory wall* problem.

#### Semantic gap

There is a notorious semantic gap between the semantics of the currently used imperative programming languages and the target platform execution model. Nevertheless, while more than 200 parallel programming paradigms and environments have been proposed, few of them are in a widespread use the majority of the applications are still written in imperative sequential languages such as C, C++ or FORTRAN.

Most current applications are written using a single thread of execution. There is a good reason for this - writing single-threaded code is intuitive and practical: one has to manage only a single state space, it is easily analysable, the proof of correctness could be obtained in an inductive way, the execution trace is predictable and reproducible.

On the other hand, writing the parallel programs introduces the problems such as communication, synchronization and data transfers. Writing hand-crafted parallel code is costly, error-prone and, mostly importantly, impossible to debug, since the race conditions in parallel program are generally non-reproducible. Hand-crafted parallel programs are *non-portable*, since the synchronization mechanisms, communication costs, scheduling policies and other issues are highly platform specific. The non-portability manifests itself in two ways: platform non-portability and *performance non-portability*.

#### Automatic program transformations

Very promising solution to the mentioned semantic gap problem is to enable the *automatic transformation* of sequential code into the form that best fits the target execution architecture.

The task of the compiler is now to understand the semantics of the input sequential source program and to perform the transformation, while preserving the semantics, into the form that best fits the target platform execution model, e.g., parallel threads, vectorized instructions, memory accesses clustered into blocks. This is a challenging task, since all the responsibility of translating the semantics into performance now relies on the compiler.

#### **Loop Transformations**

Focusing the program transformations on loop nests is particularly interesting, since the majority of compute-intensive applications spend most of their execution time in loops. Loop transformations have a long history and they have been used in restructuring compilers for enabling automatic parallelization and vectorization of the scientific FORTRAN codes.

Loop transformations potentially have a very powerful performance impact, since they might enable parallelism, vectorization or memory locality. The major challenge for efficiently employing the loop transformations is to find the best *composition* of loop transformations and to *predict* the performance impact of those transformations.

### **The Polyhedral Model**

The polyhedral model is a powerful algebraic abstraction for reasoning about loop transformations expressed as *schedules*. The polyhedral model might be viewed as an *abstract interpretation* framework for reasoning about dynamic program execution statically - at compile time. The foundations of the polyhedral model have their roots in operational research and systolic array design.

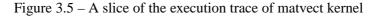

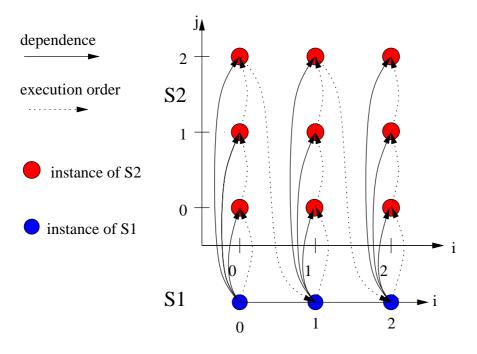

An execution trace of the sequential program is modelled as an ordered sequence of *statement instances*. It is assumed that each statement of the input program might be executed multiple times in a loop, giving rise to statement instances - one instance for each execution of the loop.

### **Single-Shot Optimization Approach**

Traditionally, the program transformation using the polyhedral model is done in a sequence of three steps: (1) getting the program into the polyhedral model, (2) computing the scheduling transformation expressed in the polyhedral model, and (3) generating the transformed code from the polyhedral model.

The crucial step is the *scheduling* step that provides the actual program transformation. The automatic scheduling algorithms [67, 34] based on integer linear programming exist, and they are based on the *best effort* heuristics.

The advantage of the best effort scheduling heuristic is that the transformation is *computed* within a single step. Hopefully, the best possible transformation within the space of legal transformations is chosen.

The space of legal (loop) transformations is huge, and selecting the best transformation within this space is still an open problem. The best effort heuristics rely on a limited performance predicting cost-functions, abstracting away the architectural details of the target platform. The optimal transformation might easily be mispredicted.

#### **Iterative Optimization Approach**

Due to the intrinsic difficulty of selecting the best program transformation within a *single step*, a viable alternative approach is the *iterative* feedback-directed compilation. Iterative optimization resorts to *testing* the different program transformations. For each transformation, the code is generated. The code is then executed and the runtime impact of the transformation is evaluated.

A carefully crafted heuristic for generating the multiple program transformations is the key component of this approach. Experimental evidence confirms that iterative approach can be much better at adapting the semantics of the program to the execution platform than the single-shot, model based heuristics. Obviously - by trying more times, there is a better chance of getting the optimal transformation.

While the iterative approach might give better results in terms of the output program performance, it has one fundamental drawback: the whole process might be very *time consuming*. It is not uncommon for the iterative approach to take hours or days to converge to the best solution.

The iterative approach breaks the traditional view of the compilation: the compiler is now a component of the optimizing feedback loop, and not a self-standing tool that transforms the input source code to the binary. While the iterative compilation is a good approach to specialized program optimization, the two characteristics of this approach - that of having an unpredictable running time and reliance on the actual generated program execution - preclude it from being incorporated into the *general purpose* compiler.

## **Problem Statement and Proposed Solution**

Our view is that the single-shot, best effort heuristics for loop optimizations not precise enough to model the complex performance characteristics of the modern architectures. On the other hand, the iterative compilation approach, due to its unpredictable runtime and reliance on experimental program evaluation is not directly employable in the general purpose compiler. The **problem statement** could be summarized as follows:

We want to keep the *effectiveness* of the model-based transformation approach, while bridging the gap between transformation prediction *precision* between single-shot and iterative approaches.

In order to achieve this, we propose a **solution** in the form of a new, search-based transformation approach, that could be summarized as follows:

A new transformation search approach is based on the controlled enumeration of the transformation candidates, each transformation candidate being evaluated at the compilation time, according to a precise cost function based on the target machine model.

We postulate that the new proposed solution brings us closer to solving the stated problem. The new approach takes the benefits of both model-based and iterative approaches. The *effectiveness* is achieved by having an expressive but limited search space, whose complexity could be controlled. The fact that the cost function is evaluated at compile-time, and not through experimental evaluation, brings the *pre-dictability* of the running time of the transformation search, allowing it to be incorporated into the general purpose compiler.

The *precision* is achieved by the fact that we use a machine dependent cost function that directly evaluates the execution cost on a specified machine. This function is much more precise than the simplistic linear cost functions, that are used in the current model-based approaches. Though, this precision comes with a price: non-linear cost functions cannot be optimized using linear programming machinery, as it is done in the current model-based approaches - our solution uses a *search based* strategy to evaluate those non-linear cost functions.

# Contributions

The main contributions of this thesis are to provide algorithms, methodologies and the compilation framework that enable our new search-based strategy. The relevant contributions are detailed in the respective chapters.

Our contributions are built on top of the polyhedral model, which serves as the theoretical foundation of the work. The polyhedral model is used to express the data dependences, the cost-model functions and schedules.

Contrary to the current source-to-source polyhedral frameworks, we have investigated the direct polyhedral compilation on the low-level three address code. While being a challenging task, this low-level of abstraction is the foundation for our precise performance cost-modelling that is out of reach of the current source-to-source polyhedral compilers.

We take a fresh look at the problem of finding the program transformations. Contrary to the current linear cost-function based scheduling algorithms, we propose a *search strategy* that evaluates the complex cost-model function on the discrete set of legal transformations represented as *decision diagrams*. By

doing so, we take the benefits of the iterative optimization, while not requiring the generation of the transformed programs and measuring their actual runtime.

## **Thesis overview**

The thesis is organized in 3 parts and a conclusion. Contributions and related work are provided in each chapter.

The first part of the thesis gives the background material, starting from the basic mathematical definitions. The polyhedral model is defined, together with the detailed discussion of this abstract representation. Later, we discuss the topics of representing the program semantics, polyhedral transformations and legality of those transformations. The mathematical background is included so that the manuscript is self-contained - a reader familiar with the topic of linear optimization might directly skip to the sections devoted to the polyhedral program model.

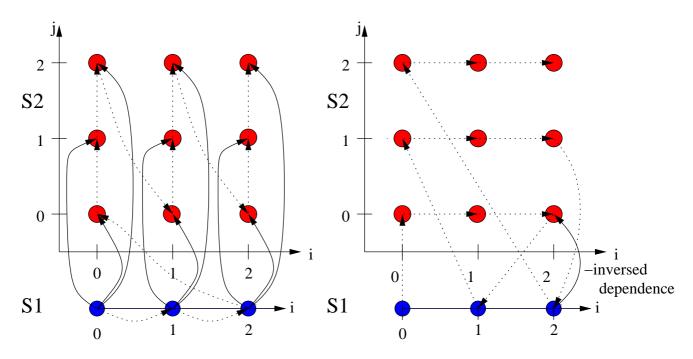

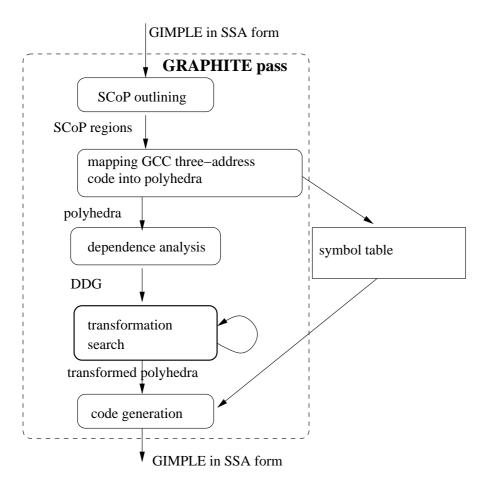

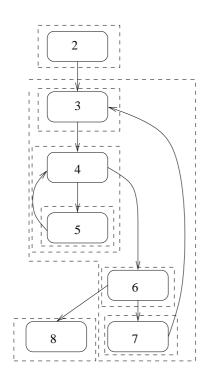

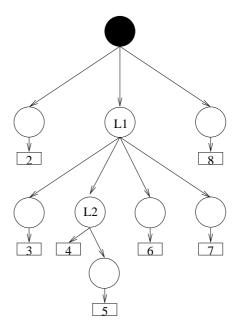

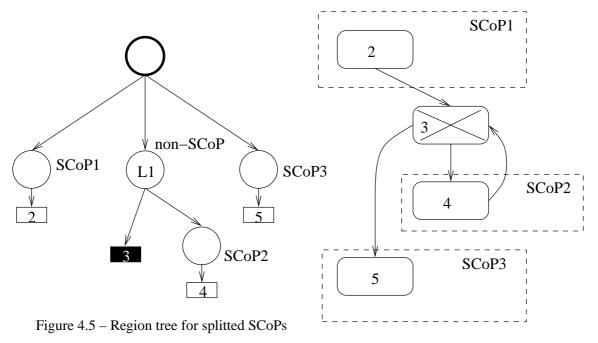

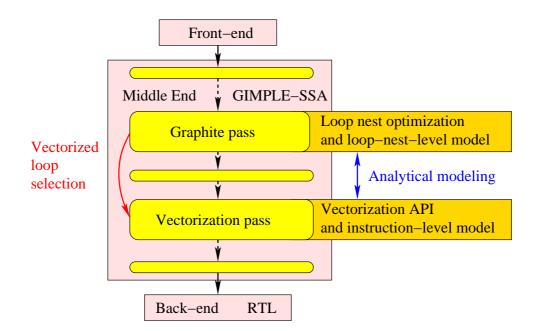

The second part of the thesis is a detailed description of our three-address-code polyhedral compilation framework - GRAPHITE. The crucial design decisions were explained, together with our contributions in not so well investigated topics. A novel approach for efficiently handling the restrictions imposed by memory-based dependences is explained as well.

The third part is the core subject of the thesis. It is dedicated to the description of the search-based transformation methodology. A detailed explanation of our precise, machine-level cost-model is provided. The final part of the thesis is our proposal for the new search strategy, starting with a review of the most important related work in this field. We show how our search strategy is built on an enumeration of the discrete sets of legal transformations, represented as decision diagrams.

Our techniques are implemented in GRAPHITE polyhedral framework, that is a part of the widely used GCC compiler.

# Part I

**Basic Concepts**

# Chapter 2

# Background

The polyhedral model representation is based on linear algebra, linear programming and convex optimization theory.

In this chapter we present the polyhedral model and the mathematical notations we use in the rest of the dissertation. The basic linear algebra and convex optimization background is given as well.