# Caractérisation et modélisation du transistor JFET en SiC à haute température

Youness Hamieh

### ▶ To cite this version:

Youness Hamieh. Caractérisation et modélisation du transistor JFET en SiC à haute température. Autre. INSA de Lyon, 2011. Français. NNT: 2011ISAL0038. tel-00665817

## HAL Id: tel-00665817 https://theses.hal.science/tel-00665817

Submitted on 2 Feb 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THESE**

Présentée devant

# L'Institut National des sciences Appliquées de Lyon

Pour obtenir

### LE GRADE DE DOCTEUR

Ecole doctorale : Electronique Electrotechnique Automatique (E.E.A) Spécialité: Génie Electrique

Par

### **Youness HAMIEH**

# Caractérisation et modélisation du transistor JFET en SiC à haute température

Soutenue publiquement le 11 mai 2011 devant la Commission d'examen

### Jury

| M.Frédéric MORANCHO   | Professeur (LAAS-CNRS)       | Rapporteur  |

|-----------------------|------------------------------|-------------|

| M.Stéphane RAEL       | Professeur (GREEN-INPL)      | Rapporteur  |

| M.Stéphane LEFEBVRE   | Professeur (CNAM de Cachan)  | Examinateur |

| M.Farid-MEIBODY TABAR | Professeur (GREEN-INPL)      | Invité      |

| M.Olivier BERRY       | Ingénieur (Hispano-Suiza)    | Invité      |

| M.Hervé MOREL         | Directeur de recherche CNRS  | Directeur   |

| M.Dominique BERGOGNE  | Maître de conférences (UCBL) | codirecteur |

Cette thèse a été préparée au Laboratoire Ampère de l'INSA de lyon

### INSA Direction de la Recherche – Ecoles Doctorales – Quadriennal 2007-2010

| SIGLE        | ECOLE DOCTORALE                              | NOM ET COORDONNEES DU RESPONSABLE                                                  |

|--------------|----------------------------------------------|------------------------------------------------------------------------------------|

|              |                                              |                                                                                    |

|              | CHIMIE DE LYON                               | M. Jean Marc LANCELIN                                                              |

| CHIMIE       | http://sakura.cpe.fr/ED206                   | Université Claude Bernard Lyon 1                                                   |

|              |                                              | Bât CPE                                                                            |

|              | M. Jean Marc LANCELIN                        | 43 bd du 11 novembre 1918                                                          |

|              | W. Ocali Maic Line Din                       | 69622 VILLEURBANNE Cedex                                                           |

|              |                                              | Tél: 04.72.43 13 95 Fax:                                                           |

|              | Insa: R. GOURDON                             | lancelin@hikari.cpe.fr                                                             |

|              | ELECTRONIQUE,                                | M. Alain NICOLAS                                                                   |

| E.E.A.       | ELECTROTECHNIQUE, AUTOMATIQUE                | Ecole Centrale de Lyon                                                             |

|              | http://www.insa-lyon.fr/eea M. Alain NICOLAS | Bâtiment H9                                                                        |

|              | Insa : C. PLOSSU                             | 36 avenue Guy de Collongue<br>69134 ECULLY                                         |

|              | ede2a@insa-lyon.fr                           | Tél: 04.72.18 60 97 Fax: 04 78 43 37 17                                            |

|              | Secrétariat : M. LABOUNE                     | eea@ec-lyon.fr                                                                     |

|              | AM. 64.43 – Fax : 64.54                      | Secrétariat : M.C. HAVGOUDOUKIAN                                                   |

|              | EVOLUTION, ECOSYSTEME,                       | M. Jean-Pierre FLANDROIS                                                           |

| E2M2         | MICROBIOLOGIE, MODELISATION                  | CNRS UMR 5558                                                                      |

|              | http://biomserv.univ-lyon1.fr/E2M2           | Université Claude Bernard Lyon 1                                                   |

|              |                                              | Bât G. Mendel                                                                      |

|              | M. Jean-Pierre FLANDROIS                     | 43 bd du 11 novembre 1918                                                          |

|              | Insa: H. CHARLES                             | 69622 VILLEURBANNE Cédex                                                           |

|              |                                              | Tél: 04.26 23 59 50 Fax 04 26 23 59 49                                             |

|              |                                              | 06 07 53 89 13                                                                     |

|              |                                              | e2m2@biomserv.univ-lyon1.fr                                                        |

|              | INTERDISCIPLINAIRE SCIENCES-                 | M. Didier REVEL                                                                    |

| EDISS        | SANTE                                        | Hôpital Cardiologique de Lyon<br>Bâtiment Central                                  |

|              | Soo - Sofia Doudiama                         | 28 Avenue Doyen Lépine                                                             |

|              | Sec : Safia Boudjema M. Didier REVEL         | 69500 BRON                                                                         |

|              | Insa : M. LAGARDE                            | Tél: 04.72.68 49 09 Fax: 04 72 35 49 16                                            |

|              | mad . W. ENGANDE                             | Didier.revel@creatis.uni-lyon1.fr                                                  |

|              | INFORMATIQUE ET                              | M. Alain MILLE                                                                     |

| INFOMATHS    | MATHEMATIQUES                                | Université Claude Bernard Lyon 1                                                   |

|              | http://infomaths.univ-lyon1.fr               | LIRIS - INFOMATHS                                                                  |

|              | M. Alain MILLE                               | Bâtiment Nautibus                                                                  |

|              |                                              | 43 bd du 11 novembre 1918                                                          |

|              |                                              | 69622 VILLEURBANNE Cedex                                                           |

|              |                                              | Tél: 04.72. 44 82 94 Fax 04 72 43 13 10                                            |

|              | MATERIALLY DE LVON                           | infomaths@bat710.univ-lyon1.fr - alain.mille@liris.cnrs.fr  M. Jean Marc PELLETIER |

|              | MATERIAUX DE LYON                            | INSA de Lyon                                                                       |

| Matériaux    |                                              | MATEIS                                                                             |

|              | M. Jean Marc PELLETIER                       | Bâtiment Blaise Pascal                                                             |

|              |                                              | 7 avenue Jean Capelle                                                              |

|              | Secrétariat : C. BERNAVON                    | 69621 VILLEURBANNE Cédex                                                           |

|              | 83.85                                        | Tél: 04.72.43 83 18 Fax 04 72 43 85 28                                             |

|              |                                              | Jean-marc.Pelletier@insa-lyon.fr                                                   |

|              | MECANIQUE, ENERGETIQUE, GENIE                | M. Jean Louis GUYADER                                                              |

| MEGA         | CIVIL, ACOUSTIQUE                            | INSA de Lyon                                                                       |

|              | M. Jean Louis GUYADER                        | Laboratoire de Vibrations et Acoustique                                            |

|              | W. Jean Louis GUTADER                        | Bâtiment Antoine de Saint Exupéry<br>25 bis avenue Jean Capelle                    |

|              | Secrétariat : M. LABOUNE                     | 69621 VILLEURBANNE Cedex                                                           |

|              | PM: 71.70 -Fax: 87.12                        | Tél:04.72.18.71.70 Fax: 04 72 43 72 37                                             |

|              | Ι ΙΝΙ . / Ι./Ο -Ι αΛ . Ο/. ΙΖ                | mega@lva.insa-lyon.fr                                                              |

|              | ScSo*                                        | M. OBADIA Lionel                                                                   |

| ScSo         |                                              | Université Lyon 2                                                                  |

| 2320         | M. OBADIA Lionel                             | 86 rue Pasteur                                                                     |

|              |                                              | 69365 LYON Cedex 07                                                                |

|              | Insa: J.Y. TOUSSAINT                         | Tél: 04.78.77.23.88 Fax: 04.37.28.04.48                                            |

|              |                                              | Lionel.Obadia@univ-lyon2.fr                                                        |

| *C-C II:-4-: | Geographie Aménagement Urbanisme Archéolog   | · C · 1:: C · 1 · A · 1 · 1 · .                                                    |

<sup>\*</sup>ScSo : Histoire, Geographie, Aménagement, Urbanisme, Archéologie, Science politique, Sociologie, Anthropologie

#### Mot

- Et je vous dis que la vie est en effet obscure sauf là où il y a élan,

- Et tout élan est aveugle sauf là où il y a la connaissance.

- Et toute connaissance est vaine sauf là où il y a le travail,

- Et tout travail est futile sauf là où il y a l'amour.

Gibran Khalil GIBRAN

A mon pays natal LIBAN

A mes parents

A tous ceux qui me sont chers

### Remerciements

Ces trois années de thèse à l'Institut National des Sciences Appliquées de Lyon (INSA) en France sont maintenant derrière moi. Me voici aujourd'hui confronté à l'ultime épreuve et non des moindres jalonnant la rédaction de ce manuscrit, celle des remerciements. J'ai eu l'immense privilège de mener cette thèse sous la direction de M. Hervé MOREL, sa culture scientifique exceptionnelle, son ouverture d'esprit, son intuition immédiate du comportement dont, l'analyse rigoureuse me prenait des journées pour, finalement confirmer ses prédictions initiales ne sont que quelques-unes des qualités qui ont rendu passionnant chacune de nos entrevues. En m'accordant, avec simplicité son attention et sa confiance tout au long de ces trois ans de travail, je voudrais particulièrement le remercier pour la disponibilité dont il a fait preuve, son investissement dans un parcours de recherche dont les méandres m'auraient découragé sans son assistance. Ses conseils éclairés vont sincèrement me manquer, surtout sur le plan scientifique.

Toute ma gratitude va également à M. Dominique BERGOGNE, qui a codirigé mon travail au quotidien avec une gentillesse, une compétence et un enthousiasme sans limite.

Je remercie cordialement les différents membres de mon jury de thèse, qui m'ont fait l'honneur de valider le dernier « examen de passage » de ma vie d'étudiant. De prime d'abord mes deux rapporteurs M. Frédéric MORANCHO et M. Stéphane RAEL qui se sont montrés d'une disponibilité exemplaire. Mes remerciements vont également à l'endroit de M. Farid MEIBODY-TABAR et M. Olivier BERRY pour leur participation au Jury.

Un merci particulier au dirigeants de la compagnie Hispano-Suiza notamment M. Régis MEURET et Mme. Sonia DOKHAR qui par le biais du projet SEFORA ont rendue cette thèse possible. Que toutes les personnes qui m'ont soutenu sous quelques formes que se soit durant mes différents séjours de travail sur le site de Réau trouvent ici l'expression de ma profonde reconnaissance.

Un grand merci à tous les membres du Laboratoire AMPERE que j'ai côtoyé durant les années de cette thèse et qui de prés ou de loin ont contribué et facilité la réalisation de ces travaux.

Enfin, pour ces trois années et globalement pour les vingt-six années de ma vie, je saisis l'occasion qui m'est donnée pour exprimer toute ma gratitude envers ma famille, en particulier mes chers parents, mon père Mohamed, ma mère Iman dont le soutien constant depuis mon Liban natal agissait à distance comme le meilleur des catalyseurs. Pour rester dans ce domaine familial, de tout mon cœur, un grand merci à mon cher frère ainé le Dr. Moustafa ainsi qu'à mes chères sœurs Badria, Nissrine, Mayssaa, Najlaa et Rim.

Je ne saurai terminer sans adresser mes vifs et chaleureux remerciements à ma "sœur du cœur" Faten OBEID et son fils Arwad, à Vanessa EL-KHOURY, Elias AL ALAM, Adnan HNEINE, Emil OBEID, Bassem MOVAWAD et Dr. Siméon DIAMPENI.

Que toutes les personnes qui se reconnaitront trouvent ici l'expression de ma profonde gratitude.

### **RESUME**

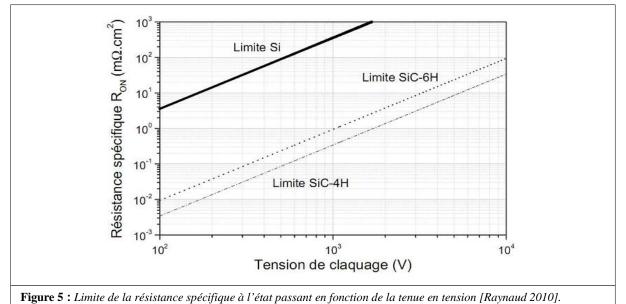

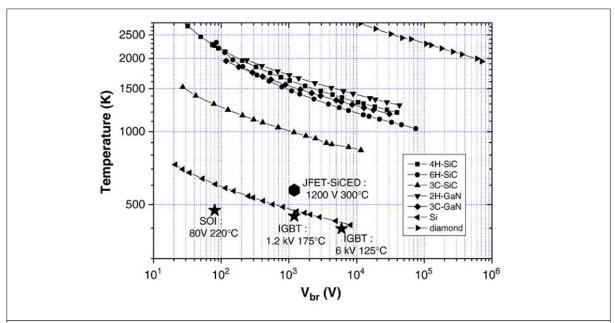

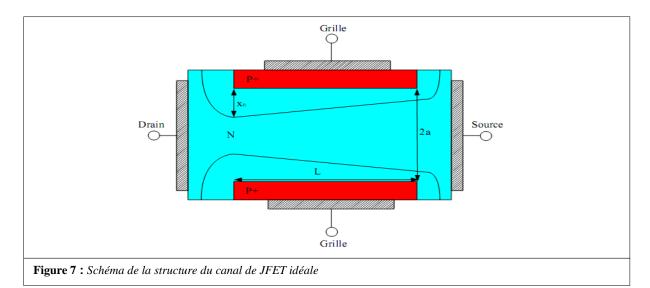

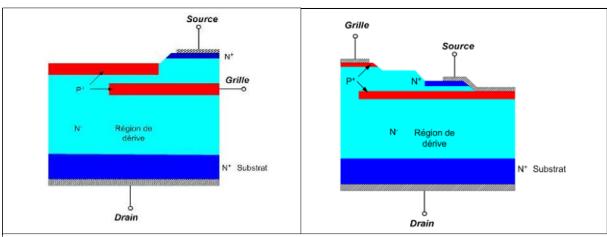

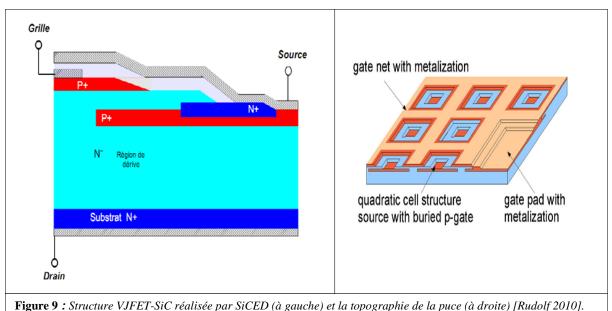

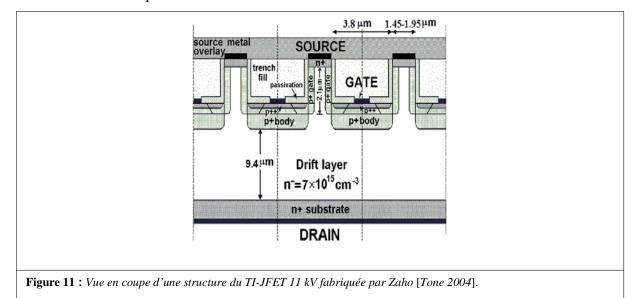

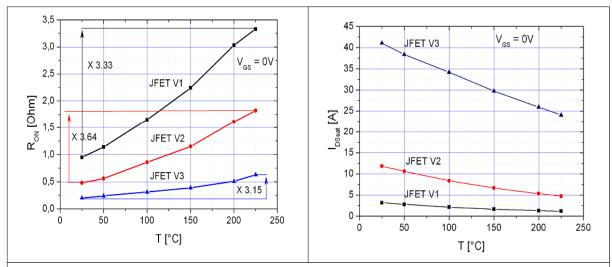

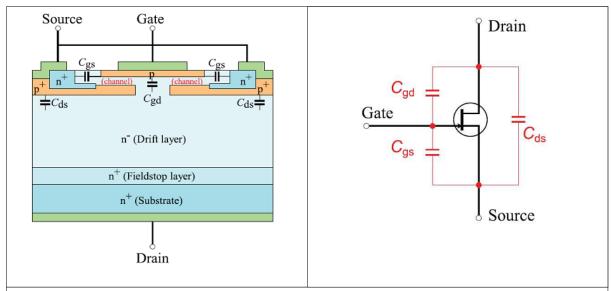

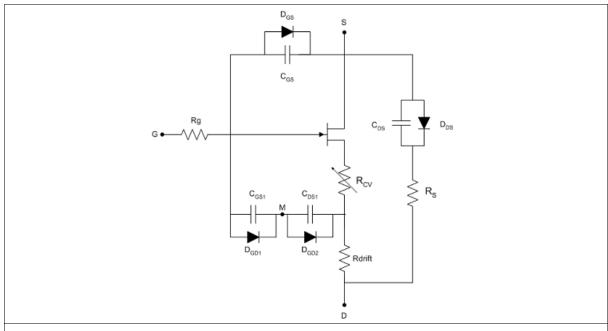

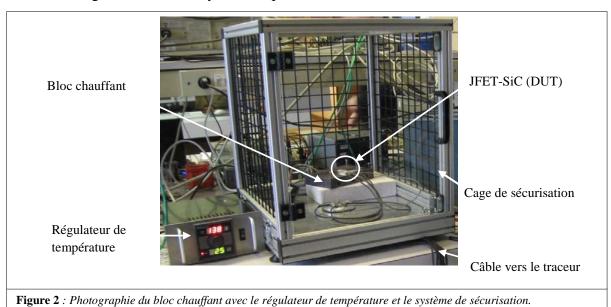

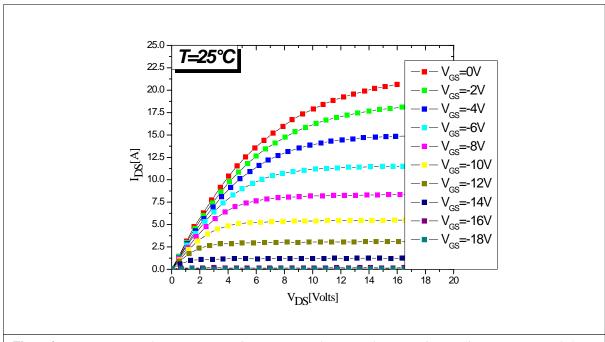

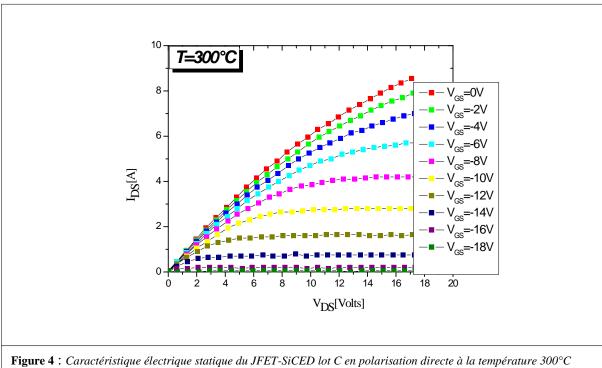

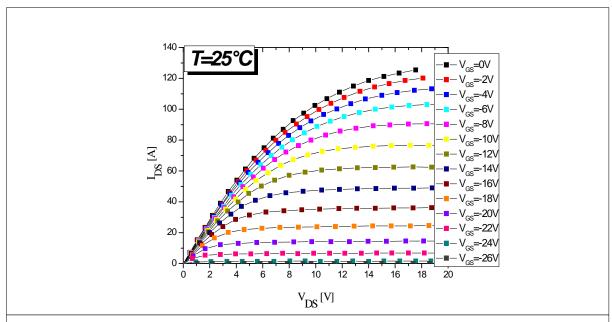

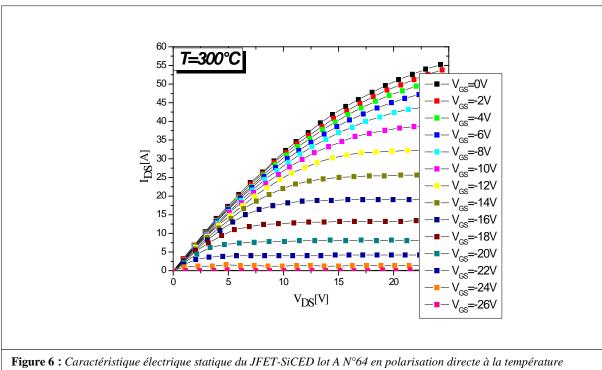

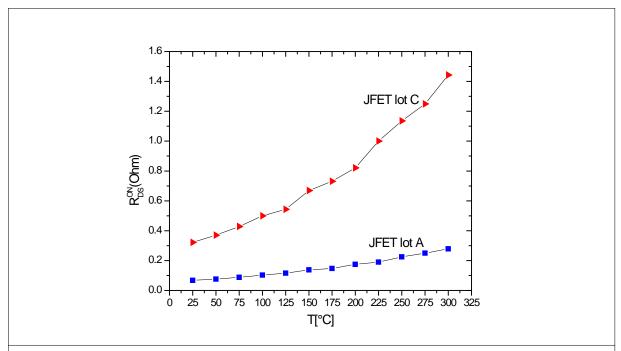

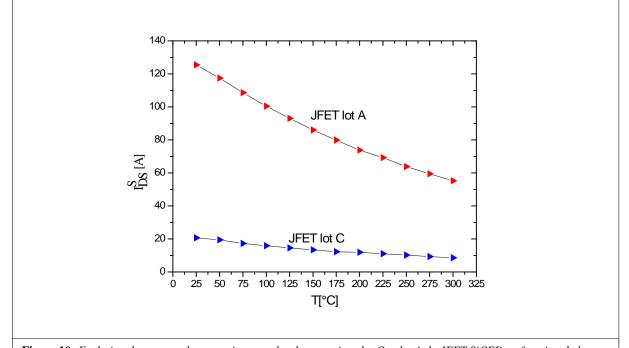

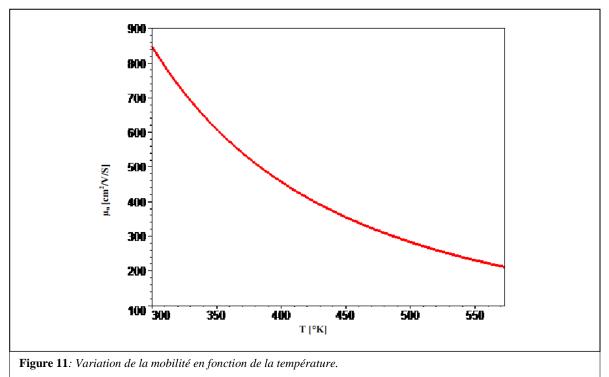

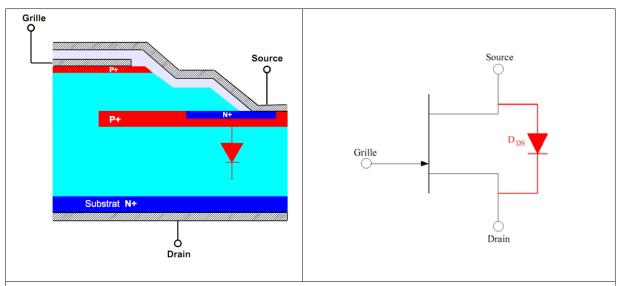

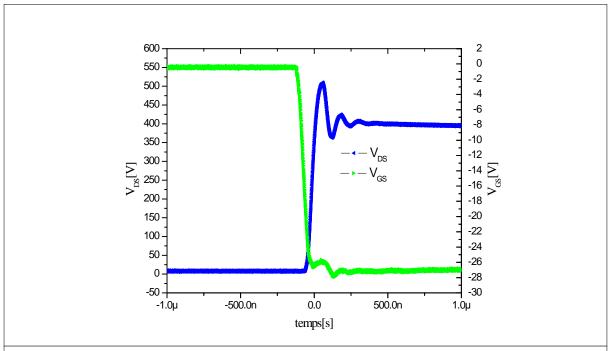

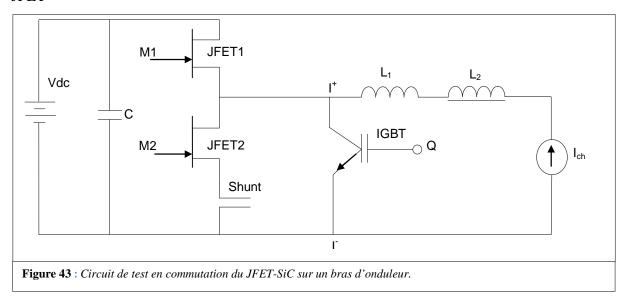

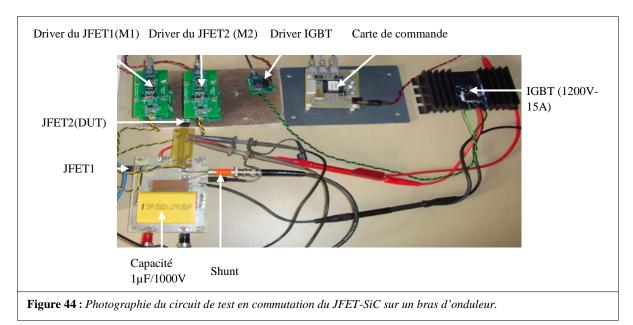

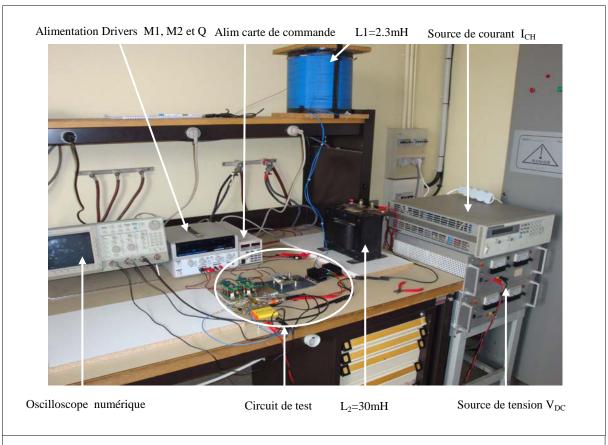

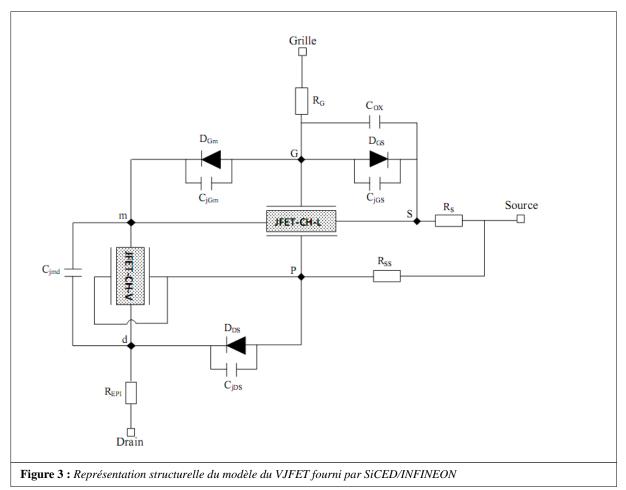

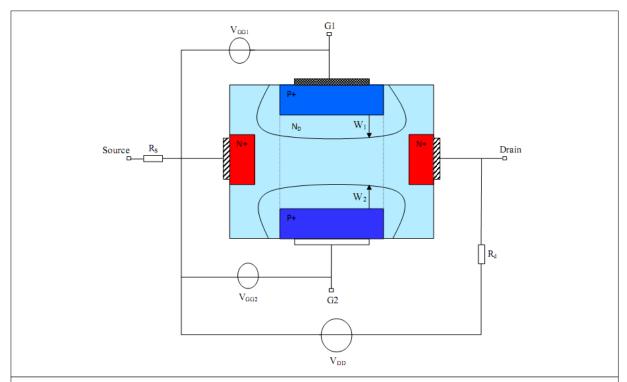

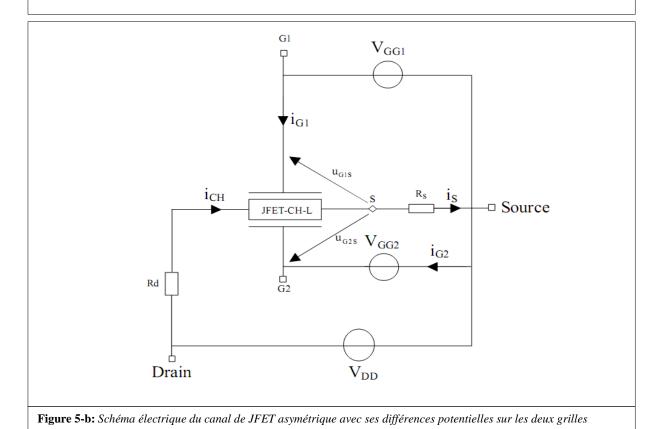

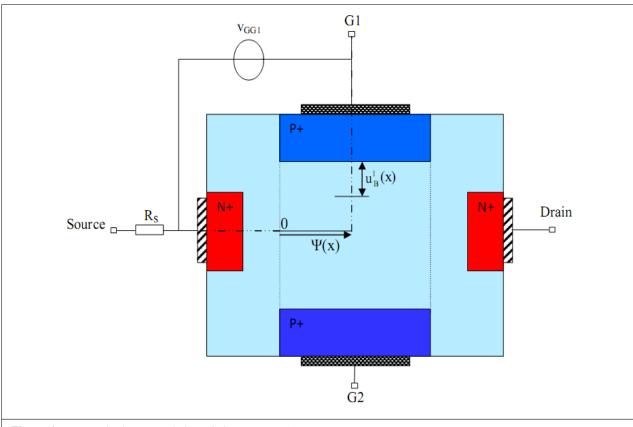

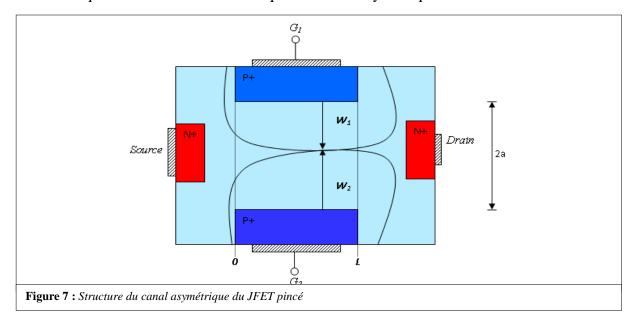

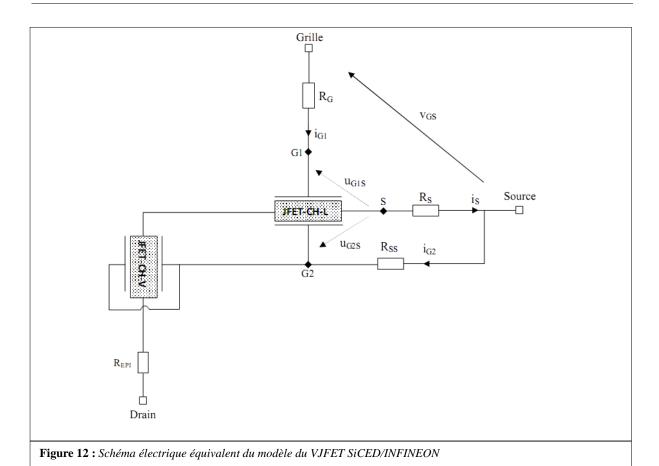

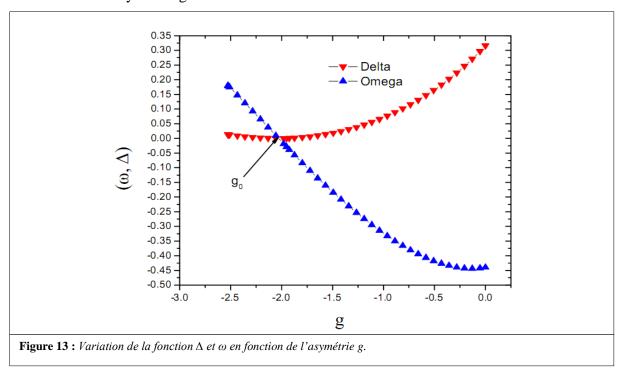

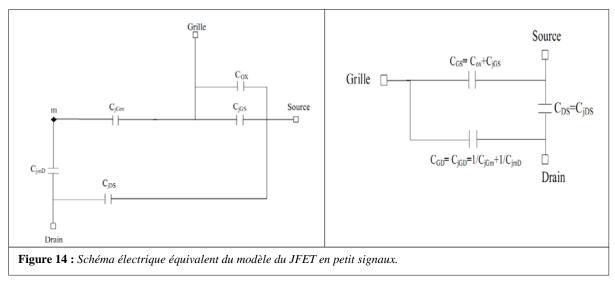

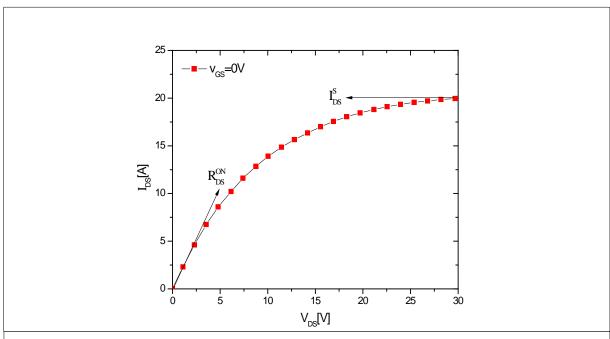

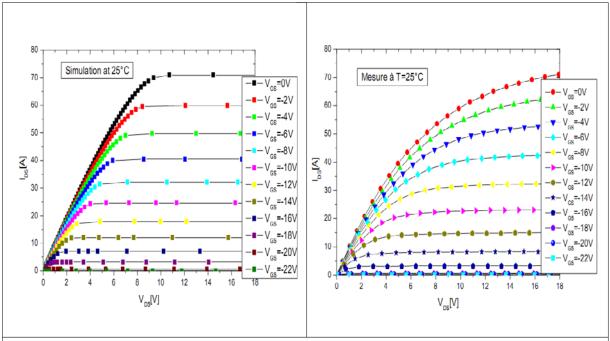

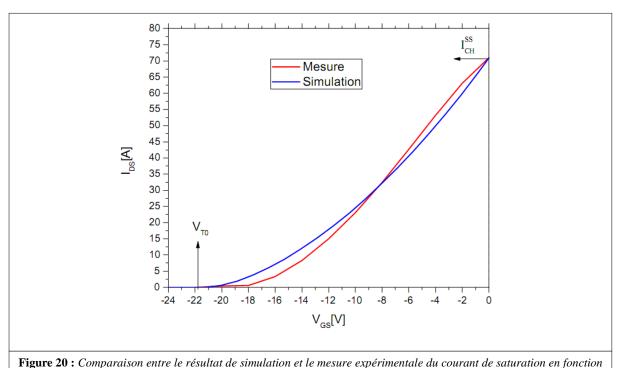

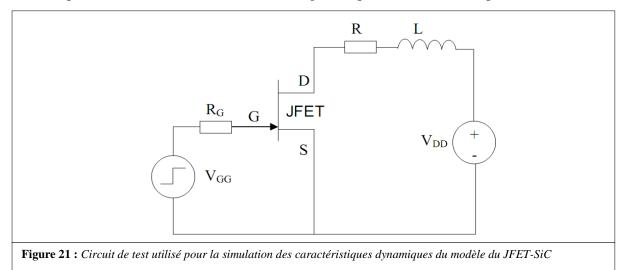

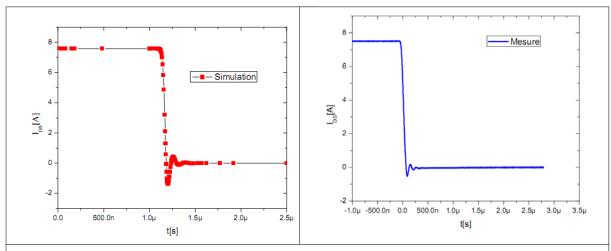

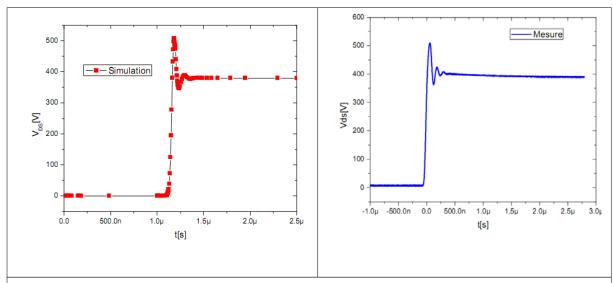

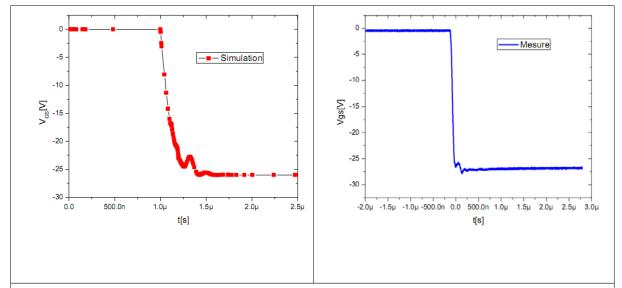

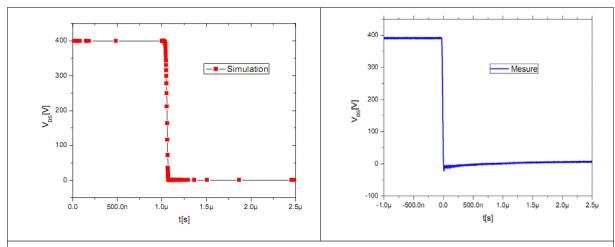

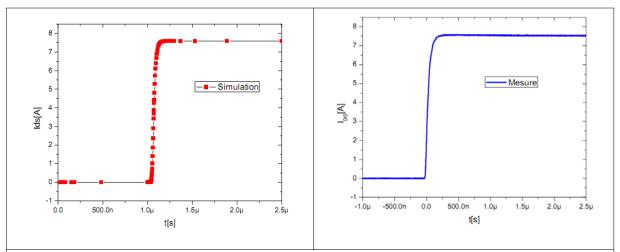

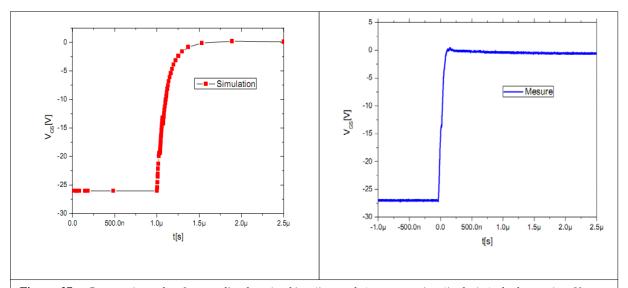

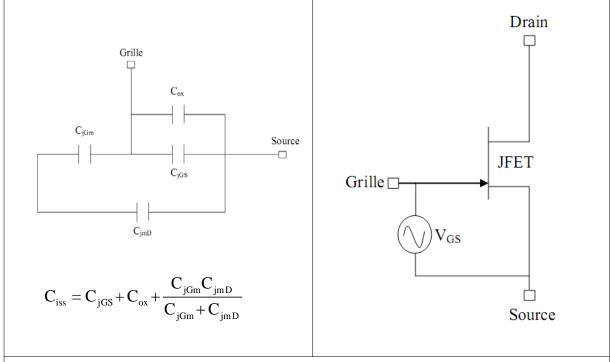

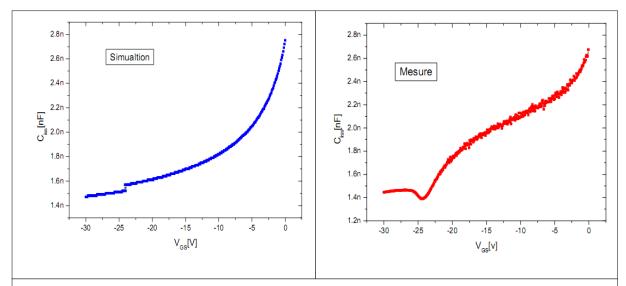

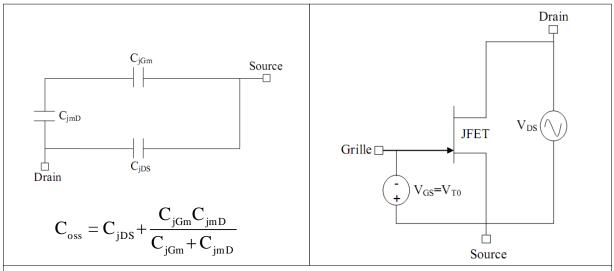

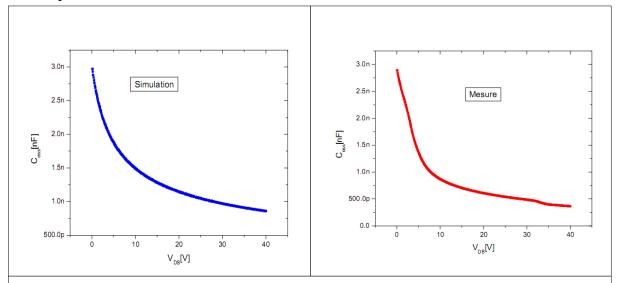

Dans le domaine de l'électronique de puissance, les dispositifs en carbure de silicium (SiC) sont bien adaptés pour fonctionner dans des environnements à haute température, haute puissance, haute tension et haute radiation. Le carbure de silicium (SiC) est un matériau semiconducteur à large bande d'énergie interdite. Ce matériau possède des caractéristiques en température et une tenue aux champs électriques bien supérieures à celles du silicium. Ces caractéristiques permettent des améliorations significatives dans une grande variété d'applications et de systèmes. Parmi les interrupteurs existants, le JFET en SiC est l'interrupteur le plus avancé dans son développement technologique, et il est au stade de la précommercialisation. Le travail réalisé au cours de cette thèse consiste à caractériser électriquement des JFET en SiC de SiCED en fonction de la température (25 °C-300 °C). Des mesures ont été réalisé en statique (courant-tension), en dynamique (capacité-tension) et en commutation sur charge R-L (résistance-inductance) et dans un bras d'onduleur. Un modèle multi-physique du transistor JFET de SiCED à un canal latéral a été présenté. Le modèle a été développé en langage MAST et validé aussi bien en mode de fonctionnement statique que dynamique en utilisant le simulateur SABER. Ce modèle inclut une représentation asymétrique du canal latéral et les capacités de jonction de la structure. La validation du modèle montre une bonne concordance entre les mesures et la simulation.

MOTS-CLES : carbure de silicium (SiC), JFET, composant de puissance, haute température, caractérisations électriques, modélisation analytique.

### **ABSTRACT**

In the field of power of electronics, silicon carbide (SiC) devices are well suited to operate in environments at high temperature, high power, high voltage and high radiation. The silicon carbide belongs to the class of wide band gap semiconductor material. Indeed, this material has higher values than the silicon ones for the temperature breakdown and a high electric field breakdown. These characteristics enable significant improvements in wide varieties of applications and systems. Among the existing switches, SiC JFET is the most advanced one in its technological development because it is at the stage of pre-marketing. The study realized during this thesis was to electrically characterize SiC JFETs from SiCED versus the temperature (25°C-300°C). The characteristic are based on static measurements (current-voltage), capacitive measurements (capacitive-voltage) and switching measurements in an R-L (resistor-inductor) load circuit and an inverter leg. A multi-physical model of the VJFET with a lateral channel is presented. The model was developed and validated in MAST language both in static and dynamic modes using the SABER simulator. The model includes an asymmetric representation of the lateral channel and the junction capacitances of the structure. The validation of the model shows a good agreement between measurements and simulation.

Keywords: Silicon carbide (SiC), Power Devices, JFET, high temperature, electrical characterization, analytic modeling.

# Tables des matières

| Ta  | bles des m  | atières                                                          | 1    |

|-----|-------------|------------------------------------------------------------------|------|

| Int | roduction   | générale                                                         | 4    |

| Soi | mmaire      |                                                                  | 6    |

| Ch  | apitre1: L  | e SiC pour l'électronique de puissance                           | 7    |

| 1   | Introducti  | o <b>n</b>                                                       | 7    |

| 2   | Pourquoi    | le SiC?                                                          | 7    |

|     | 2.1 Un      | peu d'histoire                                                   | 7    |

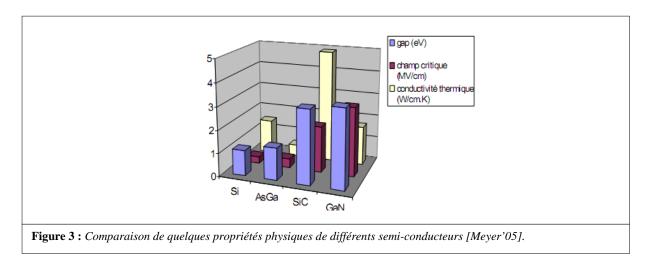

|     | 2.2 Proj    | priétés du SiC                                                   | 8    |

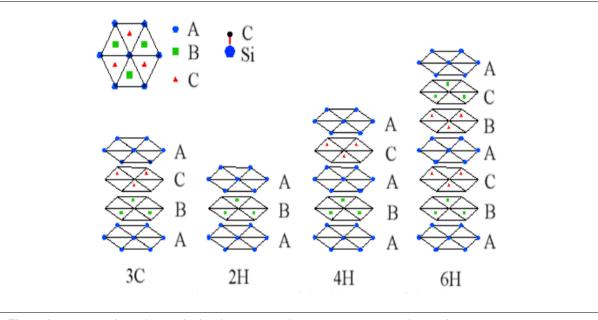

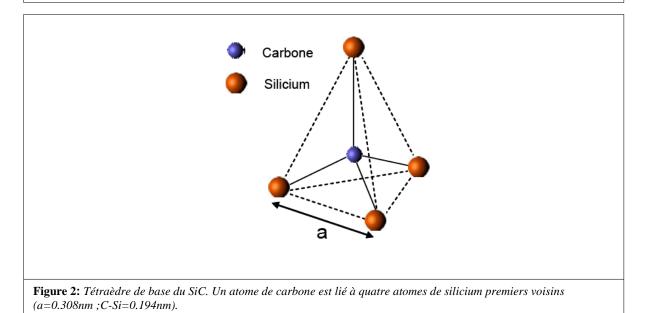

|     | 2.2.1       | Aspect cristallographie                                          | 8    |

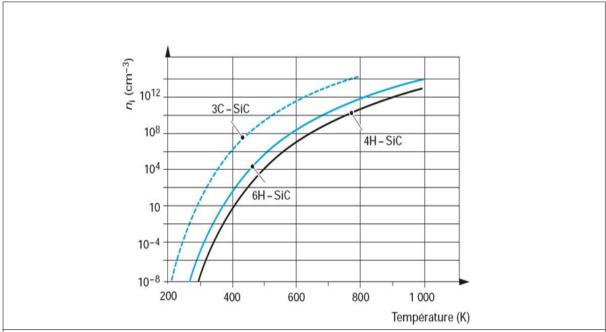

|     | 2.2.2       | Propriétés électriques                                           | . 10 |

| 3   | Les comp    | osants de puissance en SiC                                       | . 14 |

|     | 3.1 Les     | JFET en SiC                                                      | . 16 |

|     | 3.1.1       | Principe de fonctionnement                                       | . 15 |

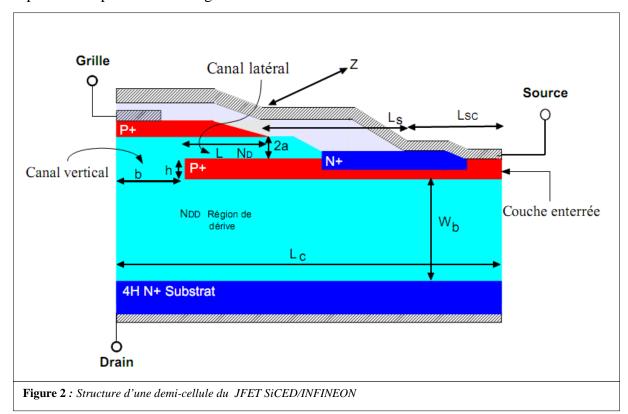

|     | 3.1.2       | JFET-SiC de SiCED.                                               | . 16 |

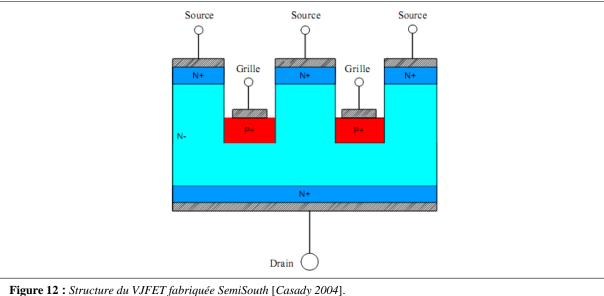

|     | 3.1.3       | JFET-SiC de SemiSouth                                            | . 20 |

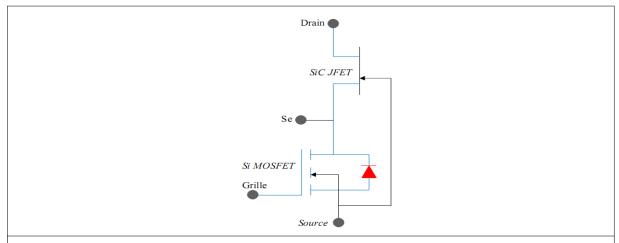

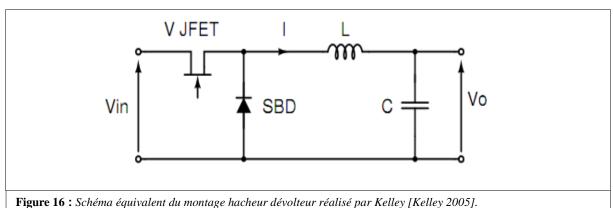

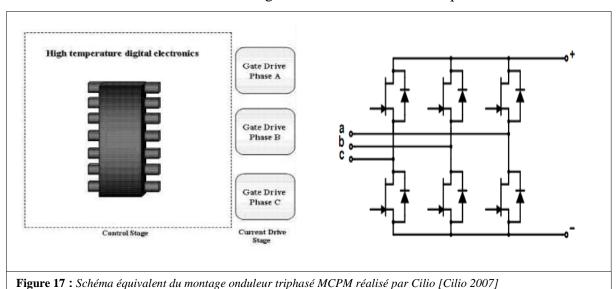

|     | 3.2 Sys     | èmes à base de JFET en SiC                                       | . 21 |

| 4   |             | rt sur la caractérisation et sur la modélisation de JFET-SiC     |      |

|     | 4.1 Car     | actérisation électrique de JFET-SiC                              | . 27 |

|     | 4.1.1       | Caractérisation électrique statique                              |      |

|     | 4.1.2       | Mesure capacitive C (V)                                          |      |

|     | 4.1.3       | Caractérisation dynamique en commutation                         | . 34 |

|     | 4.2 Mod     | délisation de transistors JFET-SiC                               | . 37 |

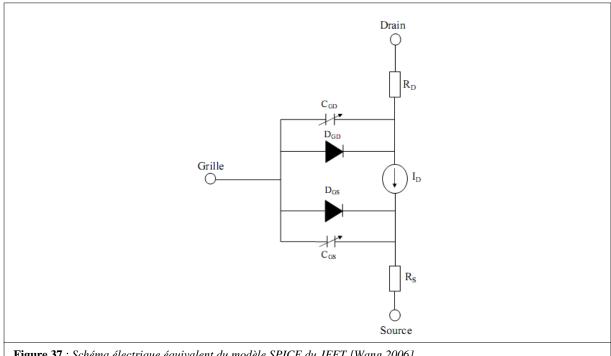

|     | 4.2.1       | Modèle SPICE du JFET-SiC                                         | . 37 |

|     | 4.2.        | 1.1 Equation du modèle du JFET en statique                       | . 39 |

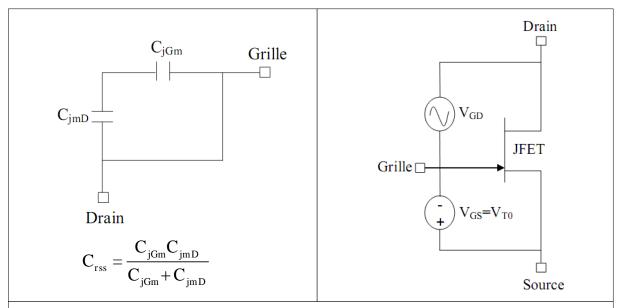

|     | 4.2.        | 1.2 Equation du modèle du JFET en dynamique                      | . 40 |

|     | 4.2.2       | Modèle VHDL-AMS du JFET-SiC                                      | . 41 |

|     | 4.2.        | 2.1 Equation du modèle du JFET en statique                       | . 43 |

|     | 4.2.        | 2.2 Equation du modèle du JFET en dynamique                      | . 44 |

| So  | mmaire      |                                                                  | . 46 |

| Ch  | apitre2 : C | Caractérisation électrique du transistor JFET en SiC             | . 47 |

| 1   | Introducti  | on                                                               | . 47 |

| 2   | Caractéris  | ation électrique de transistors JFET-SiC de SiCED                | . 47 |

|     | 2.1 Car     | actérisation électrique statique en mode de polarisation directe | . 48 |

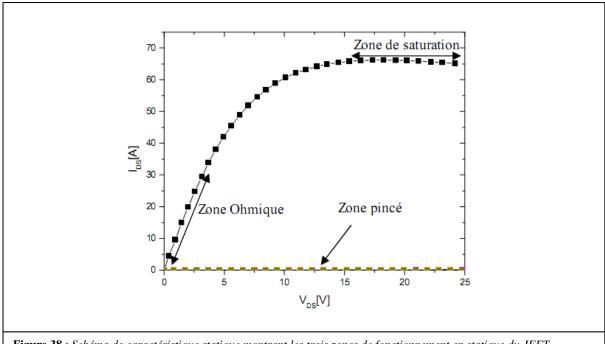

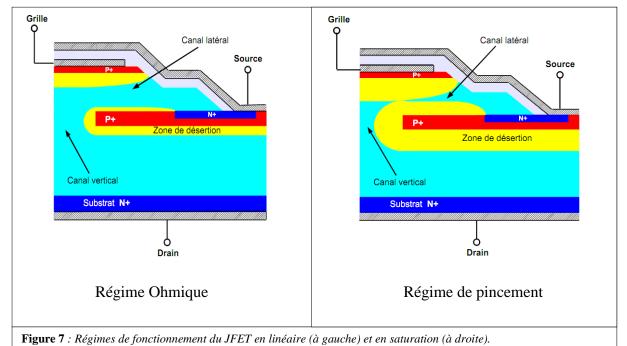

|    | 2.1.1  | Différents régimes de fonctionnement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51    |

|----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

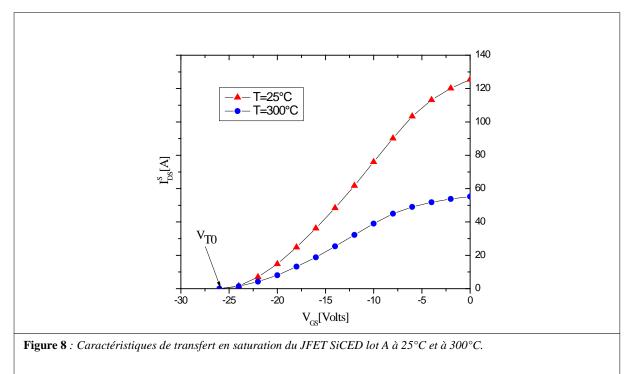

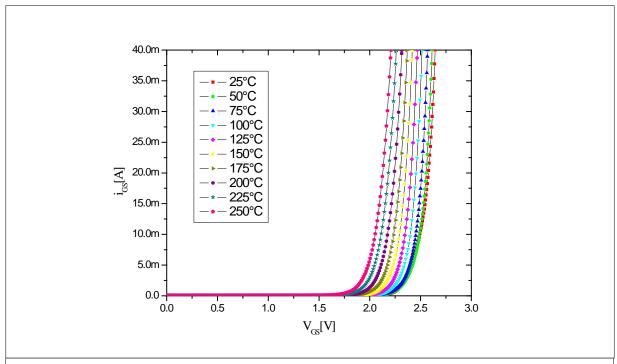

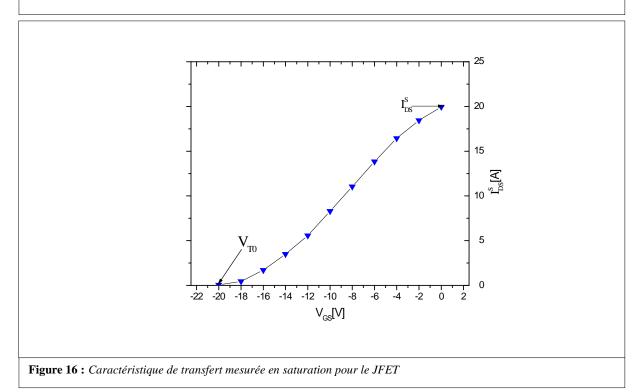

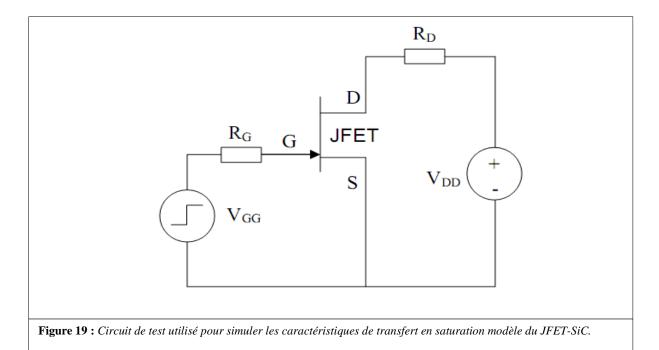

|    | 2.1.2  | Caractéristique de transfert en régime de saturation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 52    |

|    | 2.1.3  | Rôle de la température                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53    |

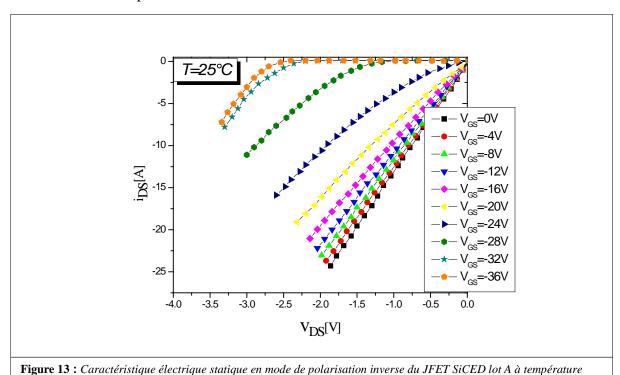

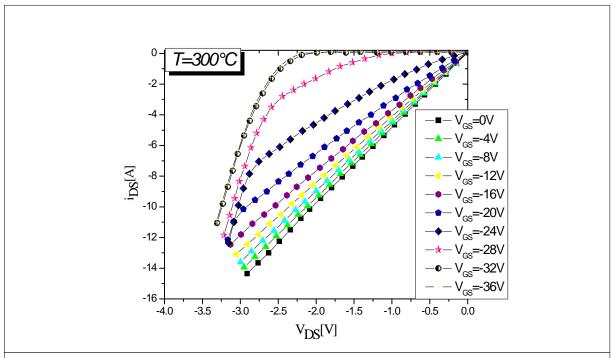

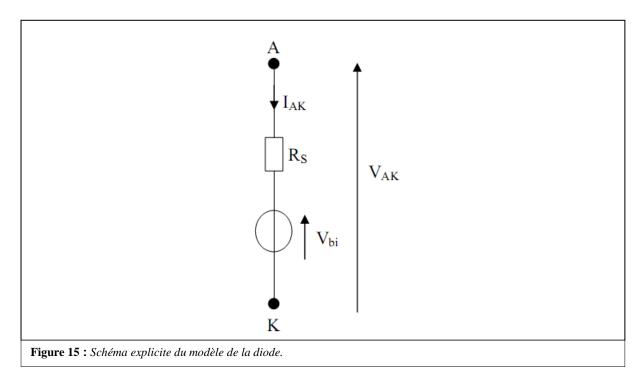

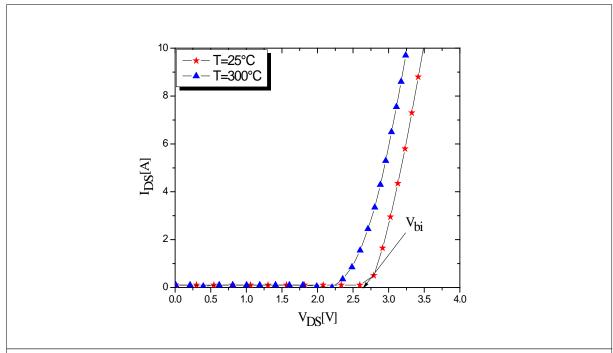

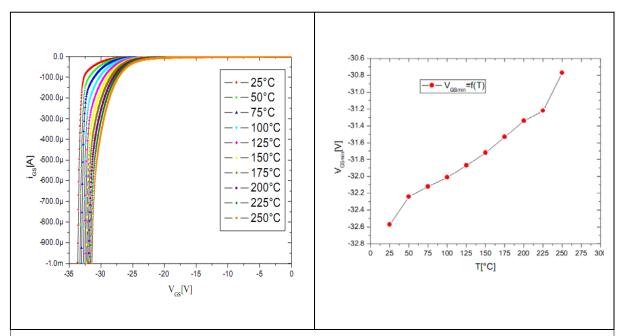

|    | 2.2 C  | aractérisation électrique statique en mode de polarisation inverse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55    |

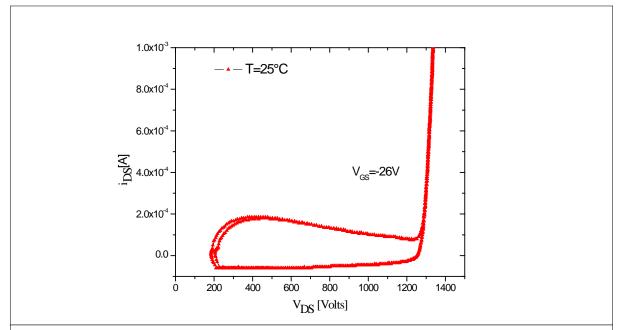

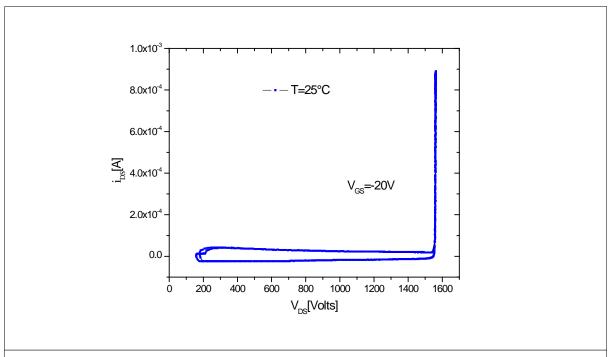

|    | 2.3 C  | aractérisation électrique statique en mode de fonctionnement direct bloqué                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 59    |

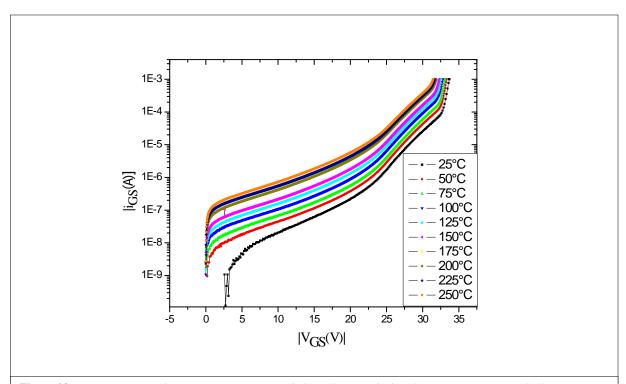

|    | 2.4 C  | aractérisation électrique statique de la jonction grille source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61    |

|    | 2.4.1  | Caractérisation électrique en mode de polarisation directe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62    |

|    | 2.4.2  | Caractérisation électrique en mode de polarisation inverse.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63    |

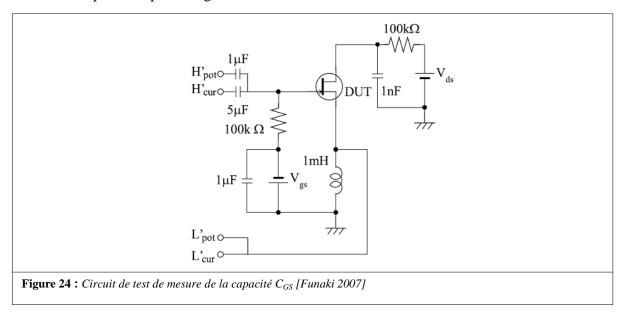

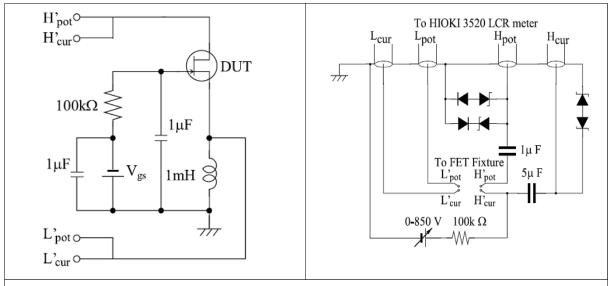

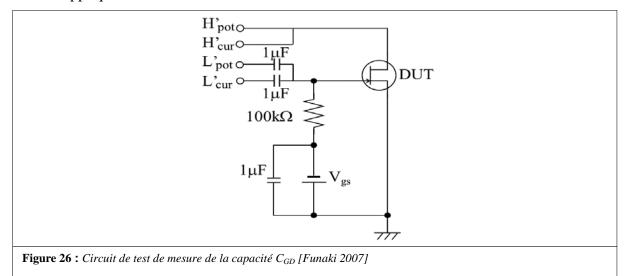

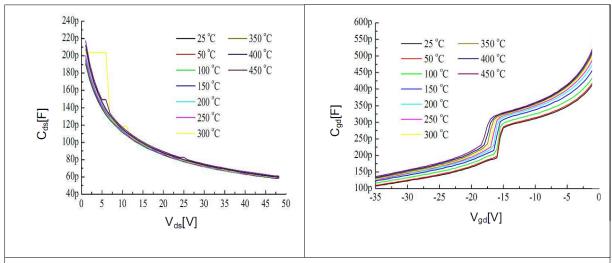

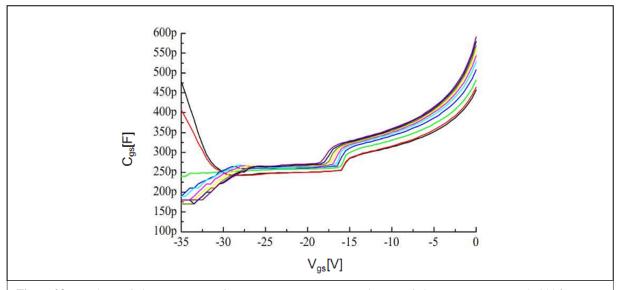

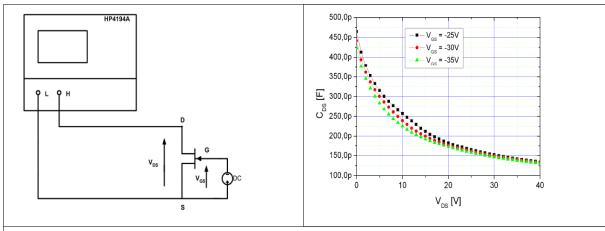

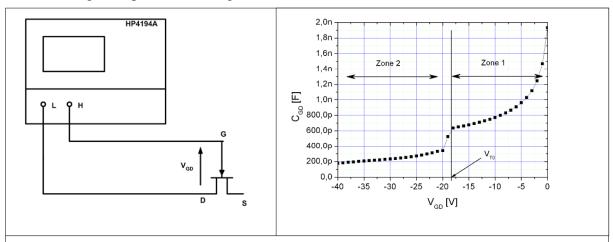

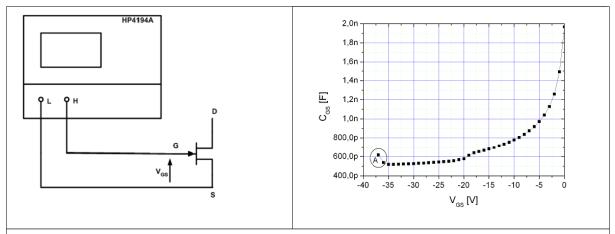

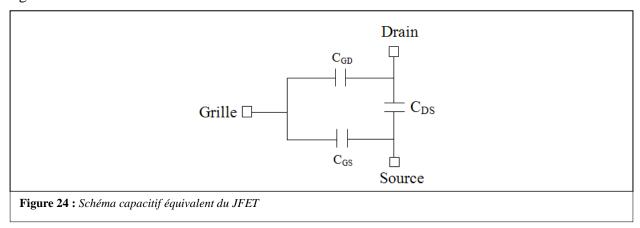

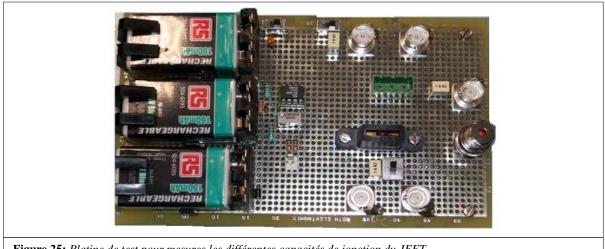

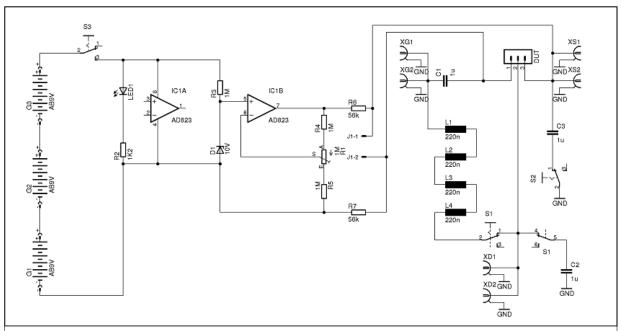

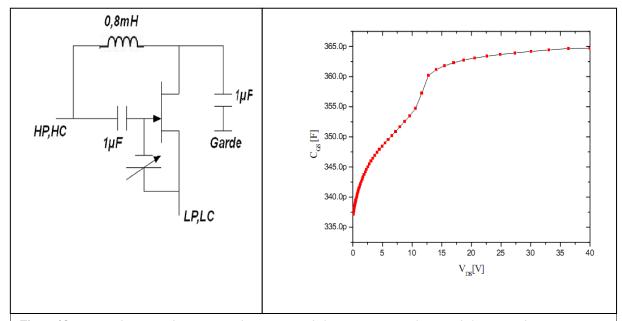

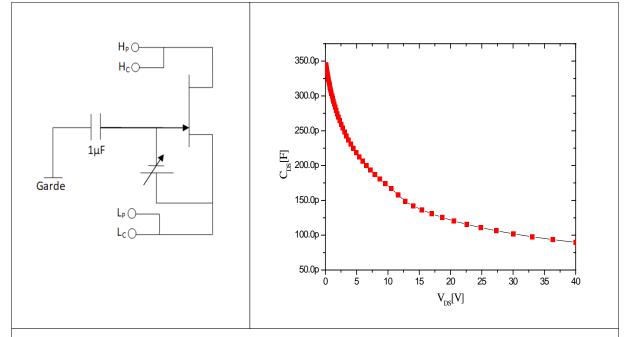

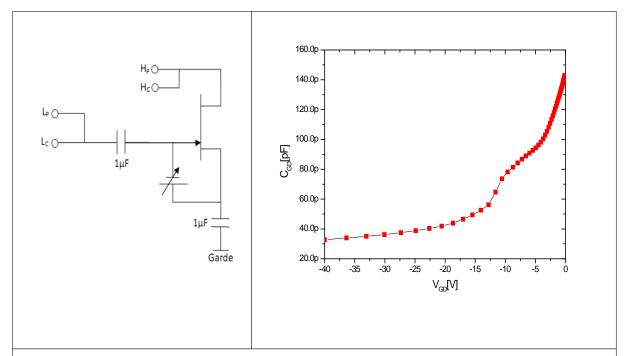

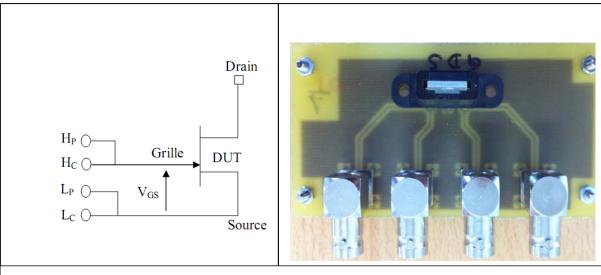

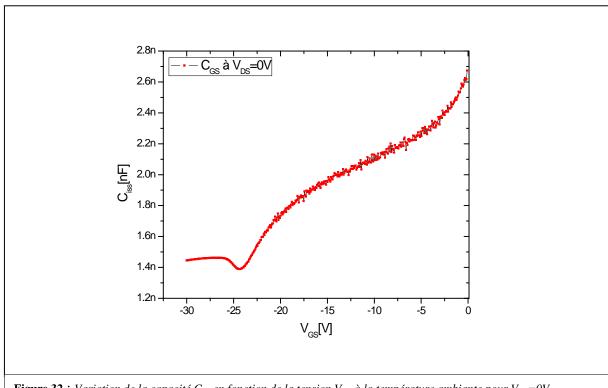

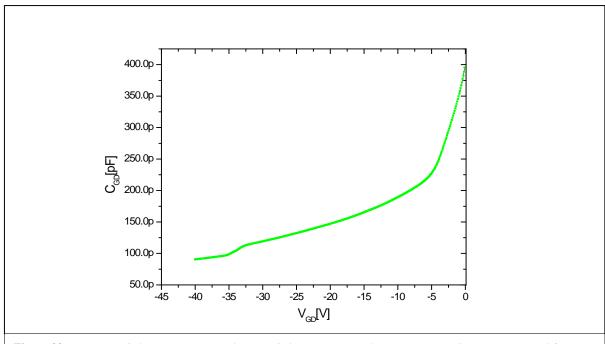

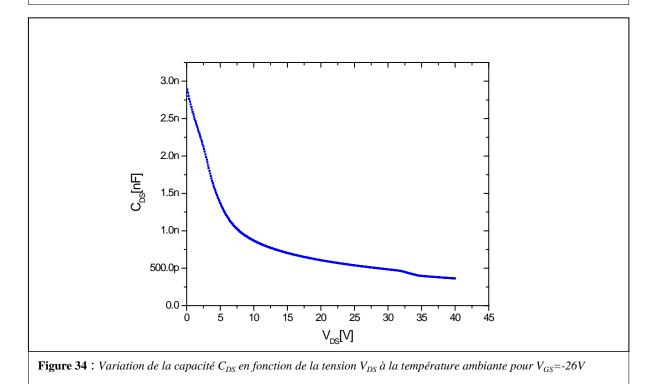

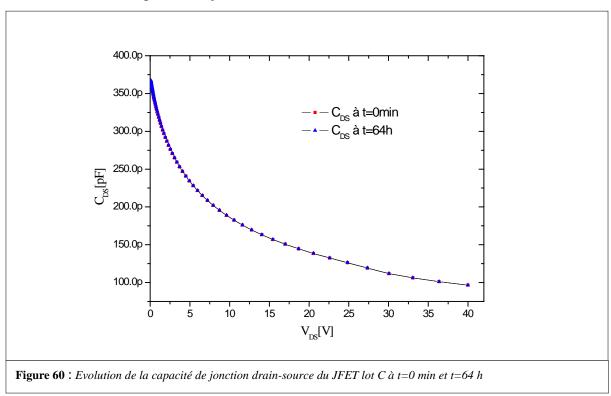

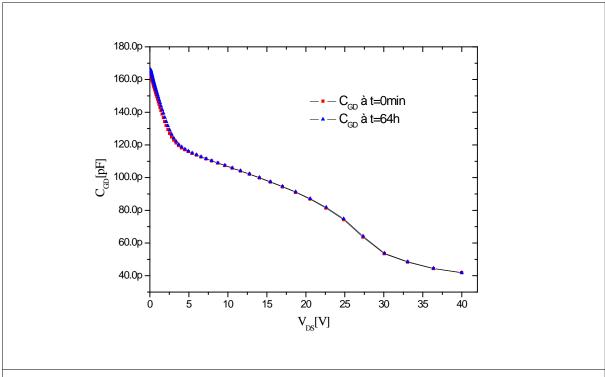

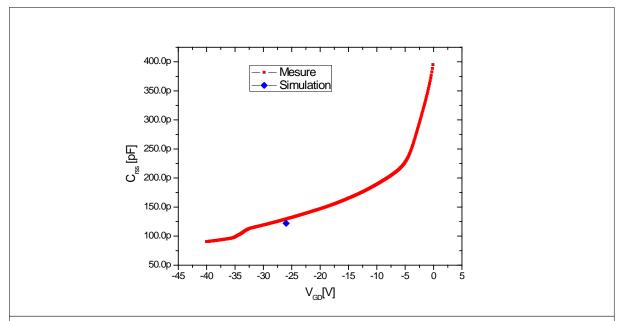

|    | 2.5 M  | lesure C(V) sur le transistor JFET de SiCED.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65    |

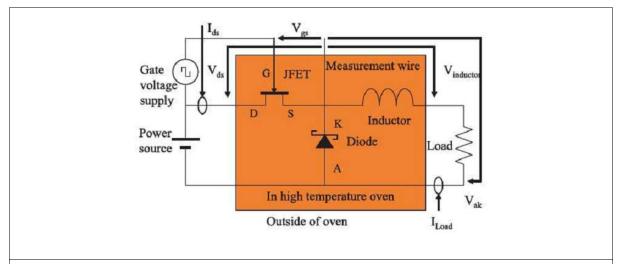

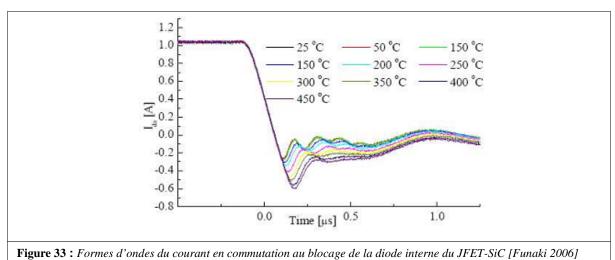

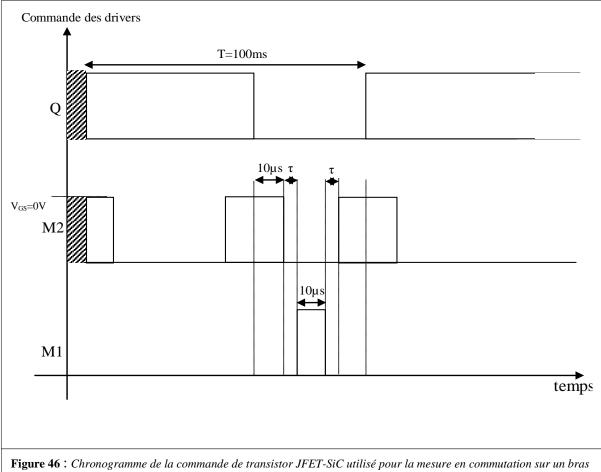

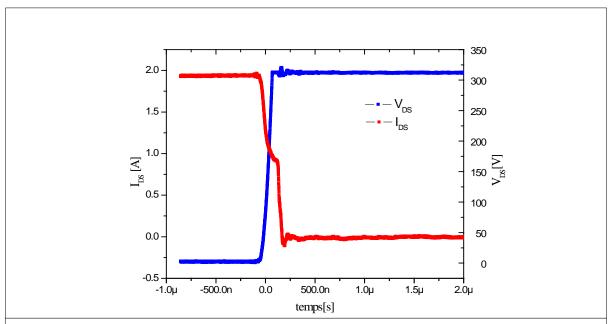

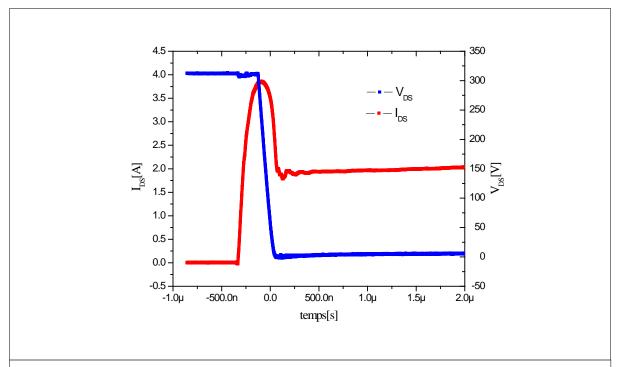

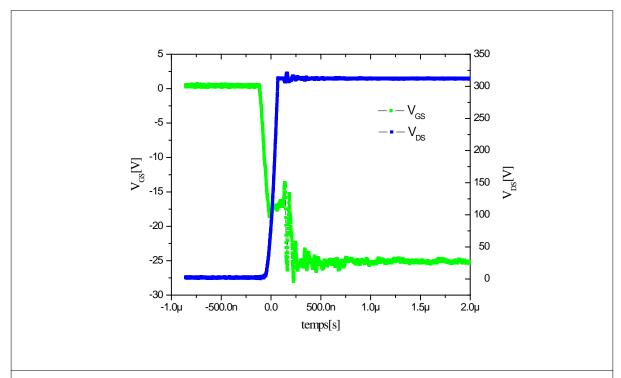

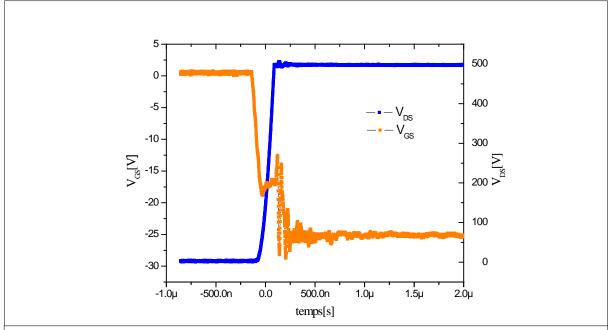

|    | 2.6 C  | aractérisation du JFET-SiC en commutation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 71    |

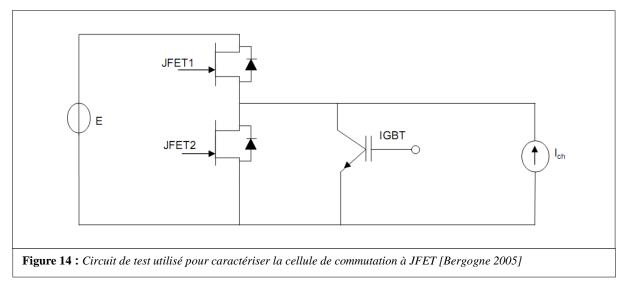

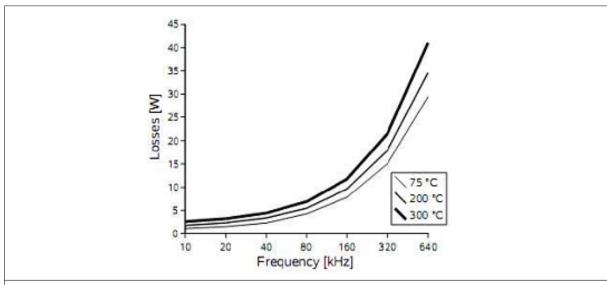

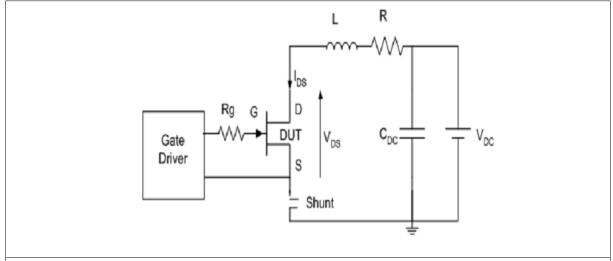

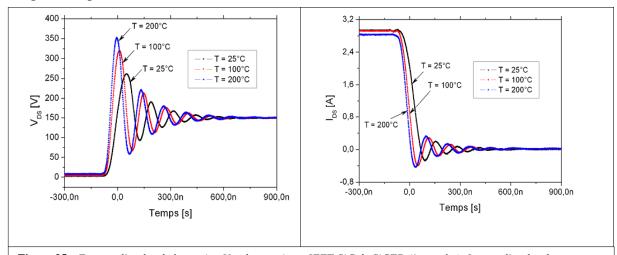

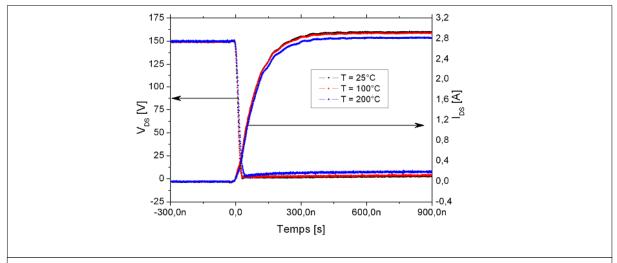

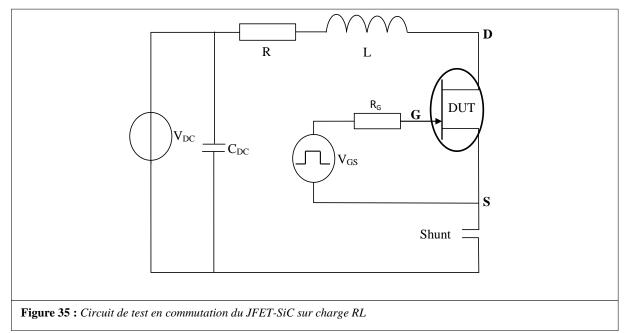

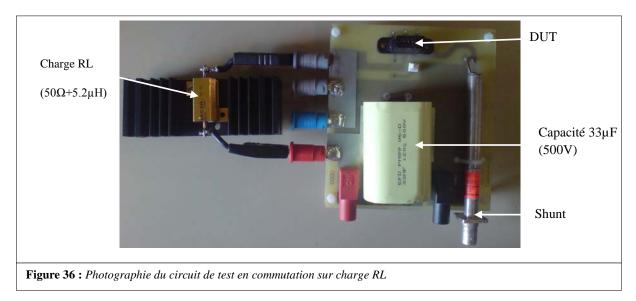

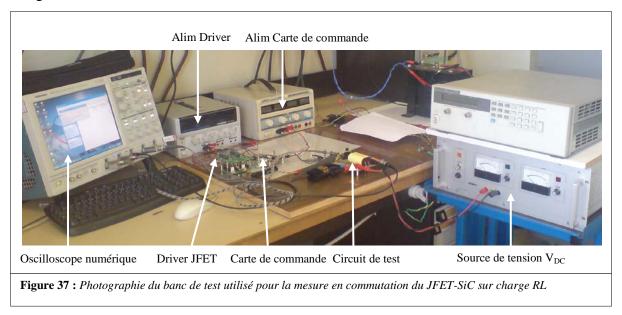

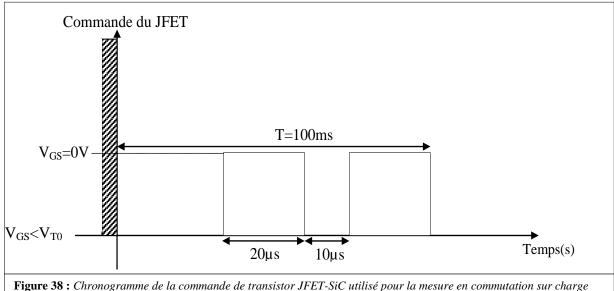

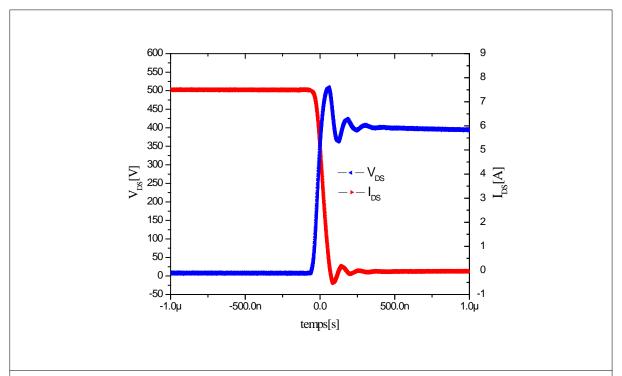

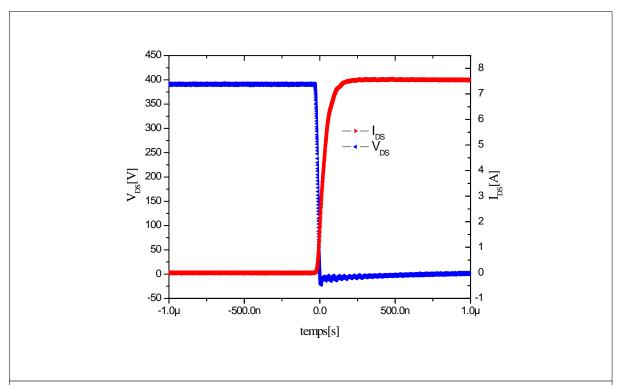

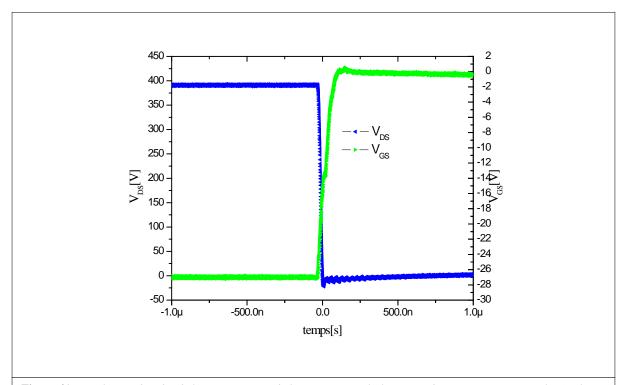

|    | 2.6.1  | Caractérisation en commutation sur charge RL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 72    |

|    | 2.6.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

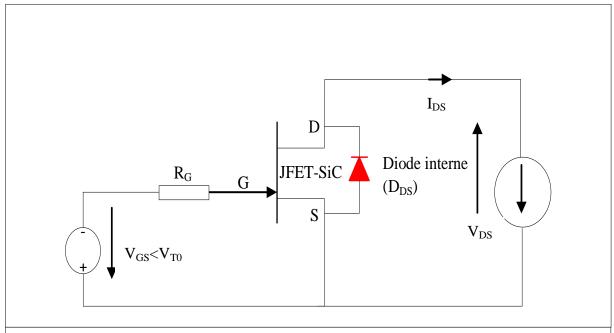

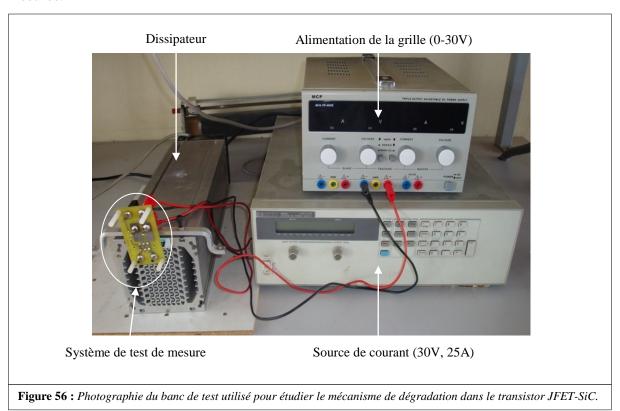

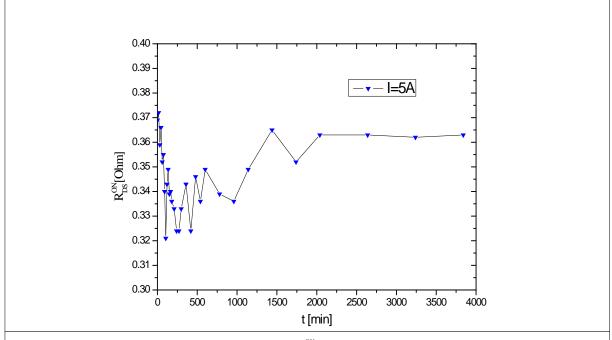

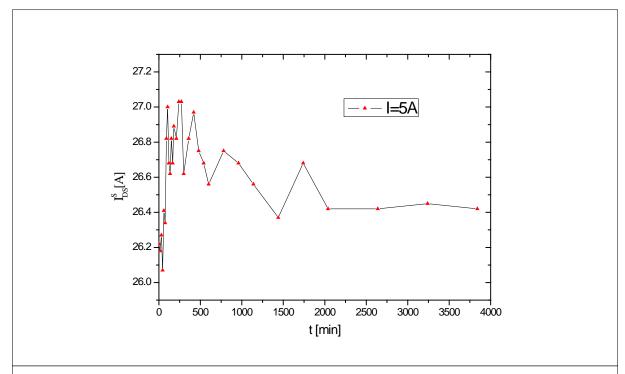

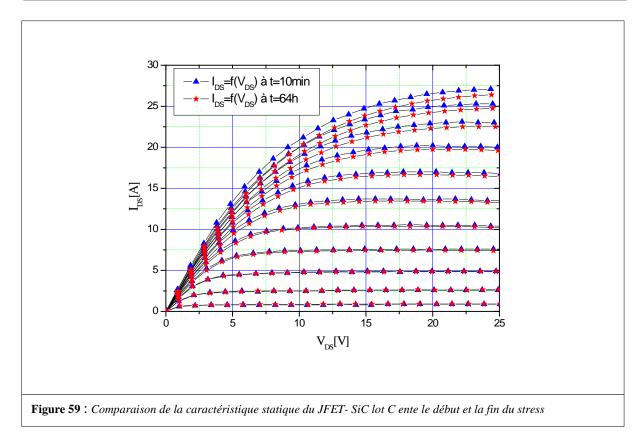

|    | 2.7 M  | lécanisme de dégradation dans le transistor JFET en SiC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 84    |

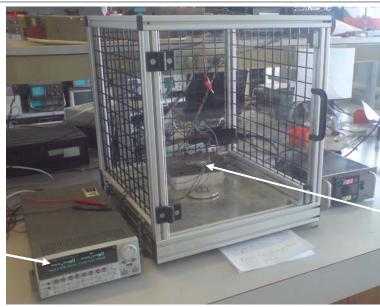

|    | 2.7.1  | Principe de l'expérience                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 84    |

| 3  |        | ion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

|    |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

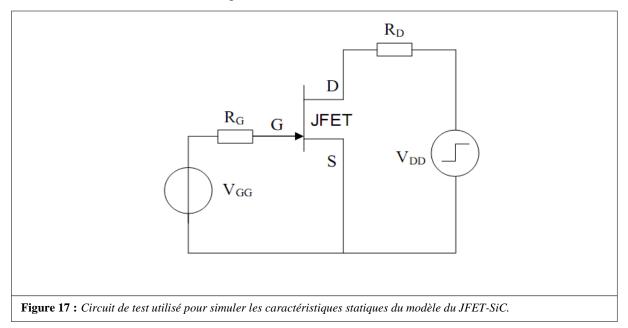

| Ch |        | Modélisation du transistor JFET en SiC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| 1  |        | etion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

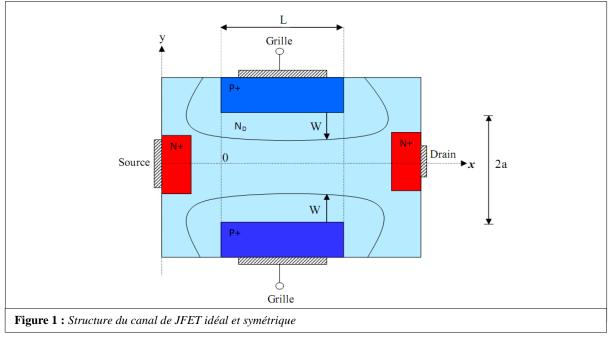

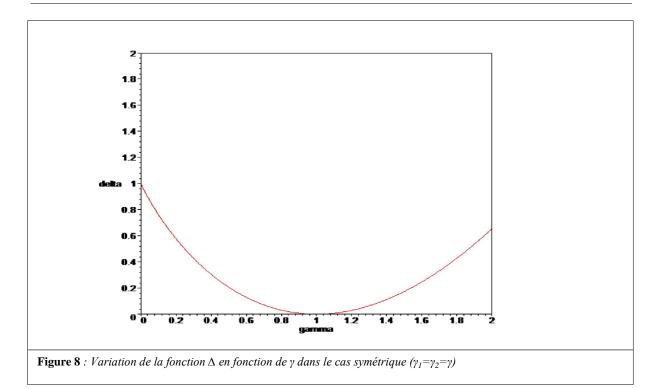

| 2  | Rappel | sur le modèle du canal symétrique du JFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 95    |

|    | 2.1 R  | appel sur les équations du modèle du canal symétrique du JFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 95    |

|    | 2.1.1  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

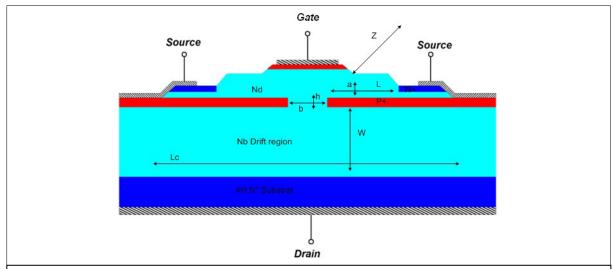

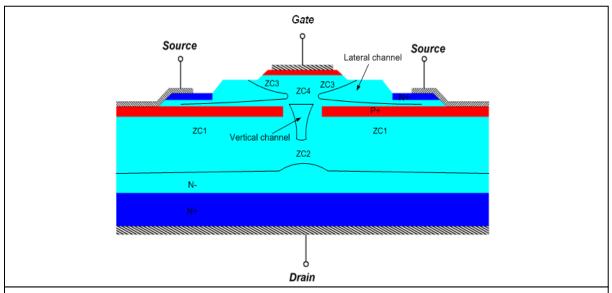

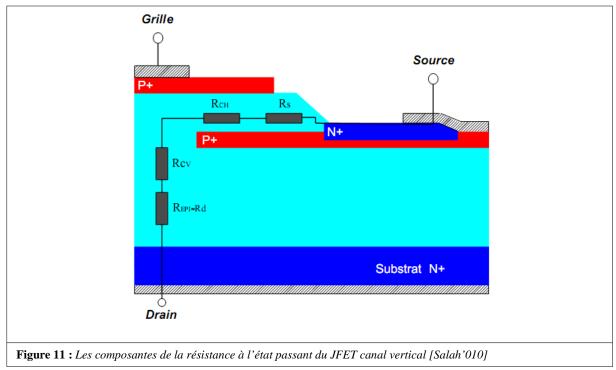

| 3  |        | e verticale du JFET SiCED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

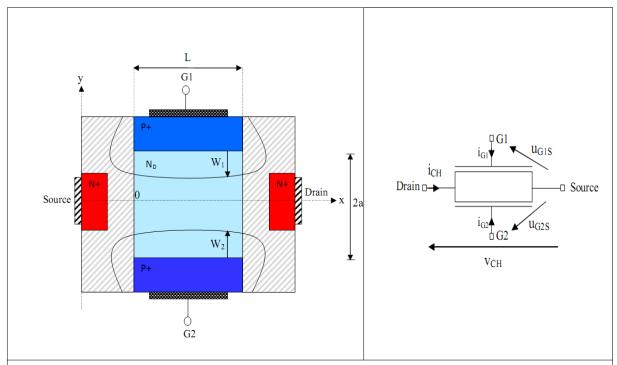

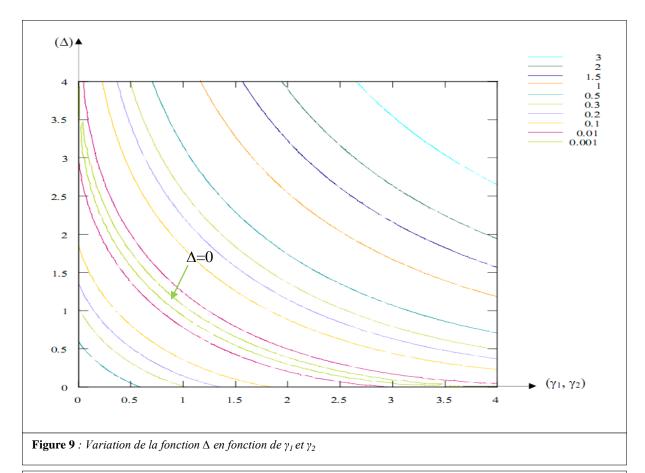

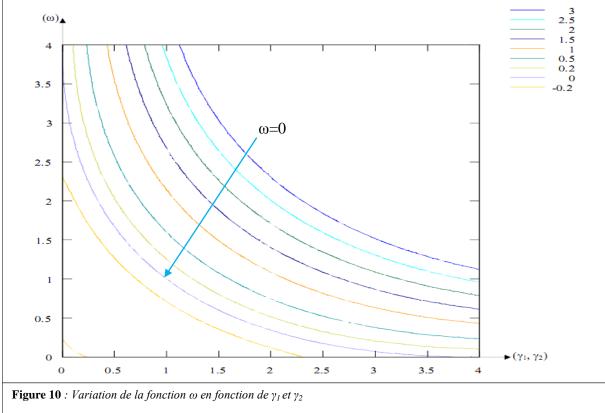

|    | 3.1 M  | odélisation du canal asymétrique du JFET SiCED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 99    |

|    | 3.1.   | 1 Equations du modèle du canal asymétrique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 100 |

|    | 3.1.   | 2 Relations entre les tensions grilles uG1S et uG2S et les extensions de ZCE W1 et                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

|    |        | W2,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |