# Agile Bandpass Sampling RF Receivers for low power Applications

Luis Lolis

#### ► To cite this version:

Luis Lolis. Agile Bandpass Sampling RF Receivers for low power Applications. Micro and nanotechnologies/Microelectronics. Université Sciences et Technologies - Bordeaux I, 2011. English. NNT: . tel-00670162

### HAL Id: tel-00670162 https://theses.hal.science/tel-00670162

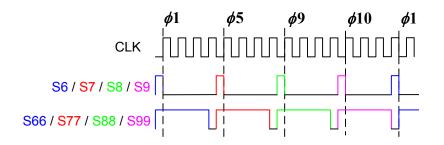

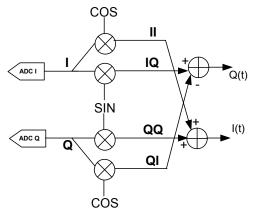

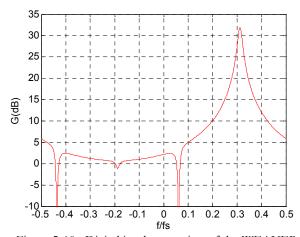

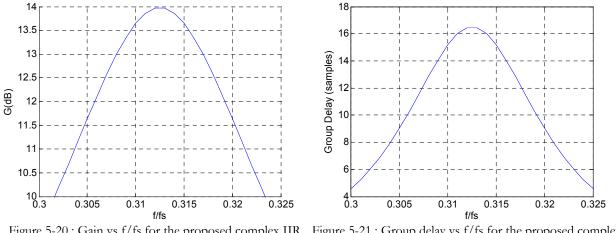

Submitted on 14 Feb 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.  $N^{o}$  d'ordre : 4231

# THÈSE

#### PRÉSENTÉE A

# L'UNIVERSITE BORDEAUX I

ÉCOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L'INGÉNIEUR

#### Luis, LOLIS

POUR OBTENIR LE GRADE DE

#### DOCTEUR

SPÉCIALITÉ : Microélectronique

# Agile Bandpass Sampling RF Receivers for low power Applications

Rapporteur Rapporteur

Soutenue le : 11 mars 2011 Après avis de :

| M. REBAI, Chiheb    | MCF-HDR | Sup'Com Tunisie    |

|---------------------|---------|--------------------|

| M. LOUMEAU, Patrick | PR      | TELECOM Paris-Tech |

Devant la commission d'examen formée de :

| M. ENZ, Christian          | PR       | CSEM                  | Président             |

|----------------------------|----------|-----------------------|-----------------------|

| M. DALLET, Dominique       | PR       | ENSEIRB               | Directeur de Thèse    |

| M. BEGUERET, Jean-Baptiste | PR       | Université Bordeaux I | Co-directeur de Thèse |

| M. PELISSIER, Michael      | Ph.DEng. | CEA-Leti              | Encadrant de Thèse    |

| M. JOET, Loïc              | Eng.     | ASYGN                 | Examinateur           |

| M. REBAI, Chiheb           | MCF-HDR  | Sup'Com Tunisie       | Examinateur           |

| M. LOUMEAU, Patrick        | PR       | TELECOM Paris-Tech    | Examinateur           |

*Université Bordeaux 1 Les Sciences et les Technologies au service de l'Homme et de l'environnement*

A Luma, A ma famille et à ceux qui me sont chers.

### Acknowledgments

Before starting this manuscript, I would like to thank the people who made possible this work. First, my sincere thanks to my advisor Dr. Michael Pelissier, for his guidance, expertise and encouragement. I also would like to show my gratitude to Dr. Carolynn Bernier and Mr. Eric Mercier for their time and precious help organizing and correcting the publications and this manuscript. I am very grateful to my thesis supervisor Prof. Dominique Dallet from ENSEIRB and thesis co-supervisor Prof. Jean-Baptiste Bégueret from Université Bordeaux I, for their valuable academic advices and supervision.

I also thank the jury members: Dr. Chiheb Rebai, professor at Ecole Supérieure des Communications de Tunis, Dr. Patrick Loumeau, professor at TELECOM Paris-Tech, Dr. Nicolas Delorme and Mr. Daniel SAIAS, CEO/CTO at Asygn Company and Dr. Christian Enz, researcher from CSEM, for accepting to participate to the Jury.

I would like to thank Mr. Pierre Vincent, LAIR laboratory Head at CEA-LETI and Mr. Jean-René Lèquepeys, DACLE department Head at CEA-LETI, for giving me the opportunity of doing this interesting and also challenging research topic. This work wouldn't be possible without the many helps and advices from all people in the LAIR laboratory, and for that I am extremely grateful. I also thank every DACLE member, particularly to Mrs Armelle De Kerleau for her kindness and Dr. Marc Belleville for his wise advices for the publication of the thesis results.

## Contents

| ACKNOWLEDGMENTS                                                                                                                             | III   |

|---------------------------------------------------------------------------------------------------------------------------------------------|-------|

| CONTENTS                                                                                                                                    | IV    |

| CHAPTER 1 :INTRODUCTION                                                                                                                     | 1     |

| 1 THE EMERGING NEEDS FOR AGILE AND LOW POWER RF TRANSCEIVERS                                                                                | 2     |

| 1.1 The WPAN, WBAN and WS&AN - A Multitude of Low Power Applications of ISM Band                                                            | n the |

| 1.2 Technological Trends towards Discrete Time Signal Processing: On the Interest<br>Bandpass Sampling                                      | of    |

| 2 PRESENTATION OF THE THESIS WORK                                                                                                           |       |

| CHAPTER 2 : THE BANDPASS SAMPLING PROCESS & THE STATE OF THE ART                                                                            | Г7    |

| 1 INTRODUCTION                                                                                                                              | 8     |

| 2 THE BANDPASS SAMPLING                                                                                                                     | 8     |

| 2.1 Theoretical analysis                                                                                                                    |       |

| 2.2 The voltage and charge sampling                                                                                                         | 13    |

| 3 AN OVERVIEW OF RF DOWN-CONVERSION AND FILTERING ON DISCRETE-TIME                                                                          |       |

| Architectures                                                                                                                               |       |

| 3.1 Architectures Classification                                                                                                            |       |

| <ul> <li>3.2 Nyquist-like sampling RX</li> <li>3.3 RF/IF Bandpass Sampling with Single Path Filters RX</li> </ul>                           |       |

| ' I I O O                                                                                                                                   |       |

| <ul> <li>3.4 RF/IF Bandpass Sampling with complex filtering RX</li> <li>3.5 A Comparative Table Summarizing the DT architectures</li> </ul> |       |

| 4 DISCRETE TIME RECEIVER BASE BLOCKS STATE OF THE ART                                                                                       |       |

| 4.1 LNA                                                                                                                                     |       |

| 4.2 Frequency Transposition                                                                                                                 |       |

| 4.3 Frequency Synthesis Blocks                                                                                                              |       |

| 4.4 Filtering Blocks                                                                                                                        |       |

| 4.5 Analog to Digital Converter                                                                                                             |       |

| 5 CONCLUSION                                                                                                                                |       |

| CHAPTER 3 :SYSTEM LEVEL MODELING AND DESIGN METHODOLOGY                                                                                     | 41    |

| 1 INTRODUCTION                                                                                                                              | 42    |

| 2 DETAILED FRAMEWORK ON THE IEEE802.15.4 AND BLUETOOTH LOW ENERGY PH                                                                        | Y-    |

| LAYER                                                                                                                                       | 43    |

| 2.1 General Aspects                                                                                                                         | 43    |

| 2.2 Sensitivity                                                                                                                             | 45    |

| 2.3 Linearity                                                                                                                               |       |

| 2.4 Channel Selection and the Interference / Blocking Performance                                                                           | 47    |

| 2.5 Dynamic Range                                                                                                                           |       |

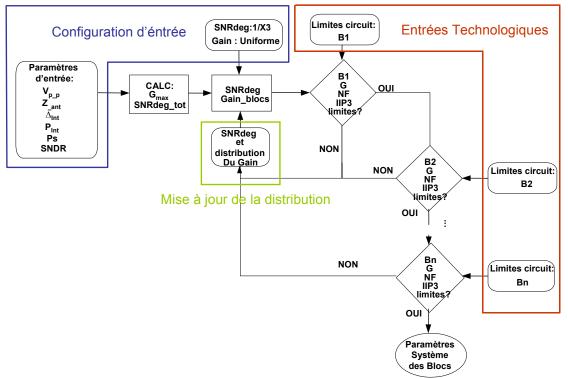

| 3 System Level Design Methodology                                                                                                           |       |

| 3.1 Definition of ADC Saturation - Maximum Gain and Adjacent Signal Filtering                                                               |       |

| <ul> <li>3.2 Definition of required SNR and SNR degradation (Noise Figure and Noise Alias</li> <li>52</li> </ul>                            | sing) |

| 3.3 Definition of SNDR degradation - IIP3 test bench and specification                                                                      | 53    |

| 3.4 Definition of the Filtering Specifications - Anti-aliasing, Image and Aliasing                                                          |       |

| Interferer Rejection                                                                                                                        | 55    |

|     | 3.5               | ADC equivalent NF and IIP3 into resolution and SFDR                                 |         |

|-----|-------------------|-------------------------------------------------------------------------------------|---------|

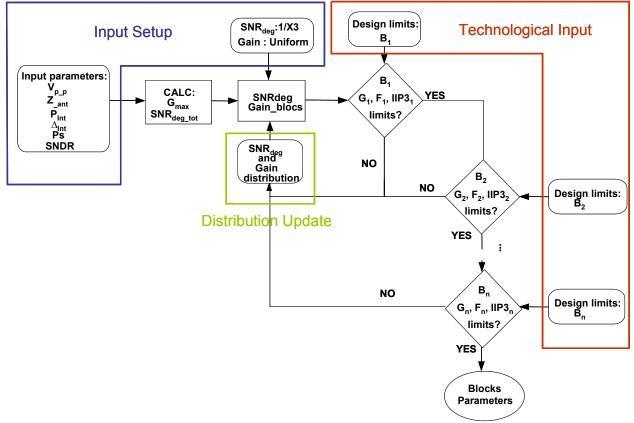

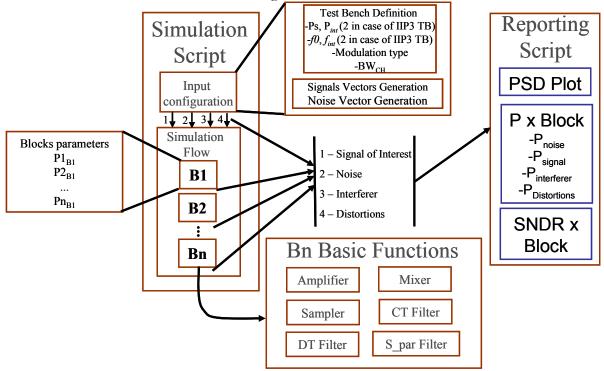

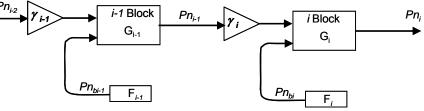

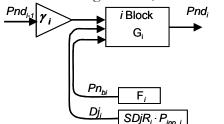

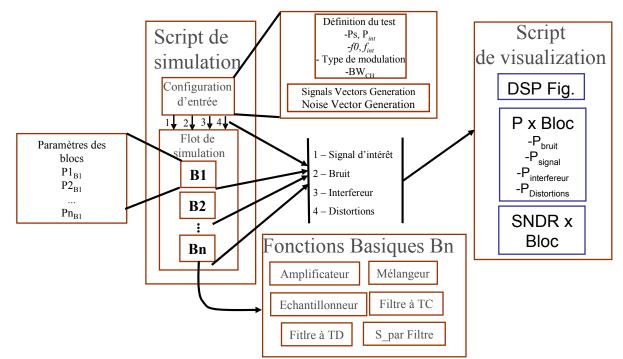

| 4   | Sys               | TEM LEVEL SIMULATION TOOL                                                           | 58      |

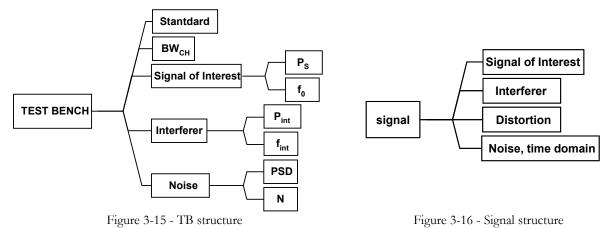

|     | 4.1               | Basic Simulation Flow                                                               |         |

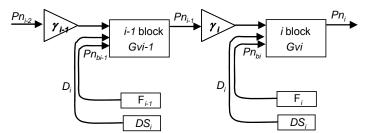

|     | 4.2               | Mathematical Principles on the System Level Simulation Tool                         | 60      |

|     | 4.3               | Base Blocks Modeling                                                                | 62      |

| 5   | Со                | NCLUSION                                                                            | 66      |

|     | APTEF             |                                                                                     |         |

| SAN | <b>IPLIN</b>      | G RF RECEIVER ARCHITECTURE                                                          | 71      |

| 1   |                   | RODUCTION                                                                           |         |

| 2   | $\uparrow_{FS}$   | S AND ↑F0 : THE NYQUIST-LIKE SAMPLING                                               | 73      |

|     | 2.1               | Architectural Description                                                           | 73      |

|     | 2.2               | Filtering Techniques & Frequency Plan                                               | 74      |

|     | 2.3               | System Level Design and Validation                                                  |         |

| 3   | $\downarrow_{FS}$ | f and $f = 0$ : RF BPS with quadrature sampling                                     |         |

|     | 3.1               | Architectural Description                                                           |         |

|     | 3.2               | Filtering Techniques & Frequency Plan                                               |         |

|     | 3.3               | System Level Design and Validation                                                  |         |

| 4   | $\downarrow_F$    | S AND $\downarrow$ F0 : IF BPS with Single Path Filtering                           |         |

|     | 4.1               | Architectural Description                                                           |         |

|     | 4.2               | Filtering Techniques & Frequency Plan                                               |         |

|     | 4.3               | System Level Design                                                                 |         |

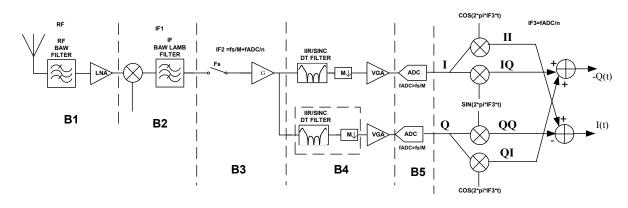

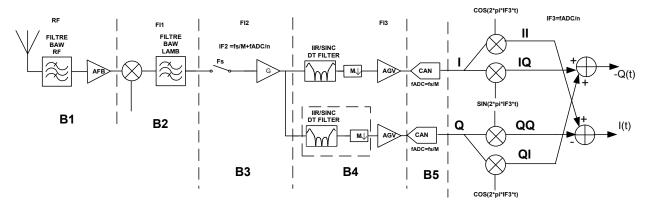

| 5   |                   | W ARCHITECTURE PROPOSITION: HIGH IF BANDPASS SAMPLING COMBINED                      |         |

| -   |                   | x DT FILTERING TO LOW-IF                                                            |         |

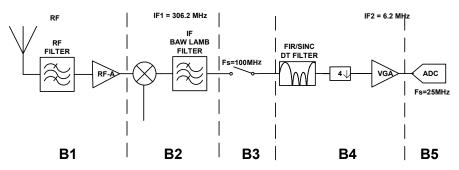

| 0   | 5.1               | Architectural Description                                                           |         |

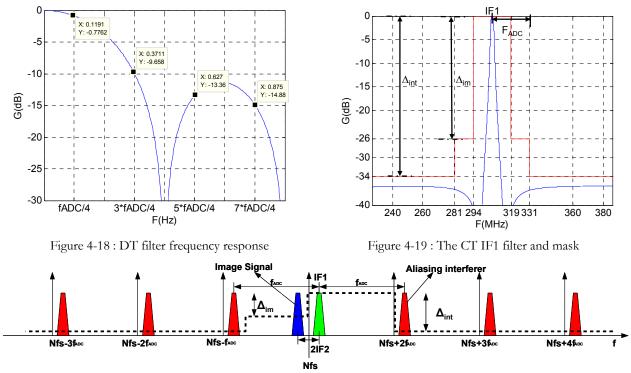

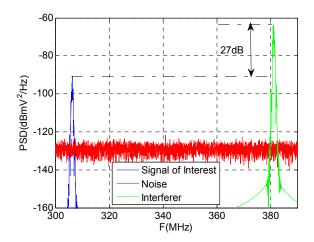

|     | 5.2               | Frequency Plan                                                                      |         |

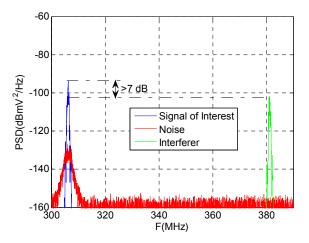

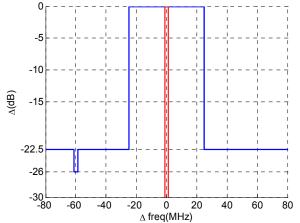

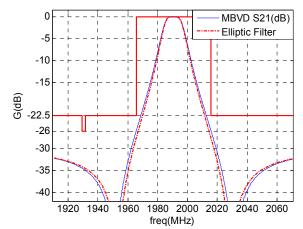

|     | 5.3               | The filtering techniques and the filtering masks                                    |         |

|     | 5.4               | System Level Design and Validation                                                  |         |

|     | 5.5               | Conclusions on the Proposed Architecture                                            |         |

| 6   | Со                | NCLUSION                                                                            |         |

| CH  | артег             | <b>R</b> 5 : IMPLEMENTATION OF THE COMPLEX IIR FILTER                               |         |

| 4   | T                 |                                                                                     |         |

| 1   |                   | RODUCTION                                                                           |         |

| 2   |                   | NERAL PRINCIPLES OF THE IIR COMPLEX FILTER                                          |         |

|     | 2.1               | Basic concept of a Discrete Time filter                                             |         |

|     | 2.2               | The Finite Impulse Response (FIR) filter                                            |         |

|     | 2.3               | The Infinite Impulse Response (IIR) filter                                          |         |

|     | 2.4               | Complex discrete time filtering - Hilbert Transform                                 |         |

| 2   | 2.5               | Implementation of the proposed complex IIR filter                                   |         |

| 3   |                   | ALYTICAL APPROACH ON THE IMPERFECTIONS                                              |         |

|     | 3.1               | Introduction to block imperfections                                                 |         |

|     | 3.2               | IIR Group delay impact on the EVM                                                   |         |

|     | 3.3               | Impact of the filter coefficients finite resolution and the unit capacitance de 133 | emition |

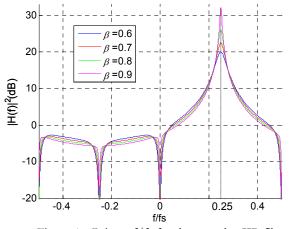

|     | 3.4               | Impact of the technological dispersion on the TF                                    | 135     |

|     | 3.5               | Noise analysis                                                                      |         |

| 4   | VH                | IDL-AMS BEHAVIORAL MODELING FOR IIR COMPLEX FILTER                                  | 142     |

|     | 4.1               | Motivation, modeling and validation test benches                                    | 142     |

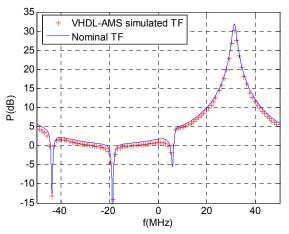

|     | 4.2               | The parasitic capacitances impact on the filter TF                                  | 148     |

|     | 4.3               | Timing Management - The Clock Tree and RC Time Constants                            |         |

|     | 4.4               | OTA impact on the filter TF                                                         | 151     |

|     | 4.5               | Intermodulation product analysis IIP3 validation                                    | 152     |

|     |                   |                                                                                     |         |

| 5 |            | 15  | Л |

|---|------------|-----|---|

| 5 | CONCLUSION | .13 | 4 |

# CHAPTER 6 : THE PHASE NOISE SPECIFICATIONS ON THE PROPOSED ARCHITECTURE 163

| 1   | Introduction                                                                    | 164  |

|-----|---------------------------------------------------------------------------------|------|

| 2   | CONTEXT - THE PHASE NOISE IMPACT IN CLASSICAL ARCHITECTURES                     | 165  |

|     | 2.1 The Phase Noise Consideration in the Mixing Operation                       | 165  |

|     | 2.2 The Phase Noise Consideration in the Nyquist Sampling Operation             | 166  |

|     | 2.3 The Bandpass Sampling System and Motivations for the Study                  | 168  |

| 3   | THE JITTER IMPACT ANALYSIS                                                      | 169  |

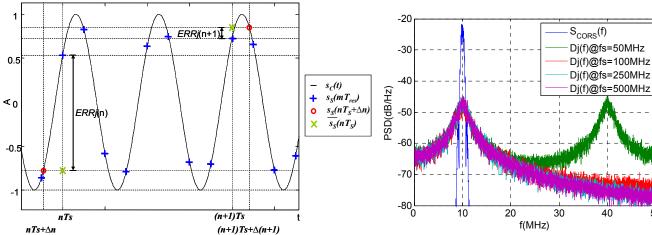

|     | 3.1 Analytical Approach - The Bandpass Sampling with Uncorrelated Jitter        | 169  |

|     | 3.2 Numerical Approach to Analyze Arbitrary Phase Noise Impact on Bandpass      |      |

|     | Sampling                                                                        | 172  |

| 4   | Case Studies                                                                    | 175  |

|     | 4.1 Method Applied on a GFSK Modulated Signal in Presence of Aperture Jitter    |      |

|     | Combined with Synthesis Jitter                                                  | 175  |

|     | 4.2 Jitter Analysis in Presence of Interferer                                   | 180  |

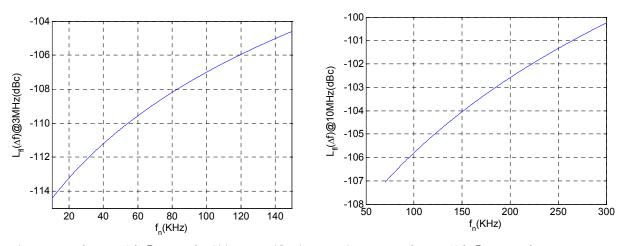

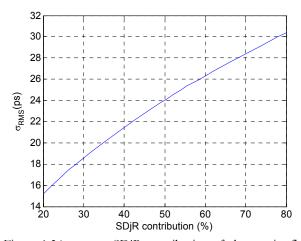

| 5   | APPLICATION OF THE PHASE NOISE ANALYSIS TO THE SYSTEM LEVEL SCALING             | 185  |

|     | 5.1 Review on the Reference Architecture and the Block to Evaluate Phase Noise  | 185  |

|     | 5.2 Defining Specifications on Phase Noise for BT-LE and IEEE802.15.4 on the    |      |

|     | Proposed Architecture                                                           |      |

|     | 5.3 Impact on the Power Consumption of the Phase Noise Specifications for Bandr | oass |

|     | Sampling                                                                        | 193  |

| 6   | CONCLUSIONS                                                                     | 194  |

| CHA | APTER 7 :CONCLUSION AND PERSPECTIVES                                            | 203  |

| 1   | General Conclusions and Results                                                 | 204  |

| 2   | LIST OF CONTRIBUTIONS                                                           |      |

| -   | 2.1 Conference Publications                                                     |      |

|     | 2.2 Patent                                                                      |      |

|     | <ul><li>2.3 Projects Deliverables</li></ul>                                     |      |

|     | <ul><li>2.4 Journal Paper</li></ul>                                             |      |

|     | <ul><li>2.5 Presentations, Seminars and non-reviewed reports</li></ul>          |      |

| 3   | Perspectives                                                                    |      |

|     |                                                                                 |      |

| BIB | LIOGRAPHY                                                                       | 209  |

|     |                                                                                 |      |

| GL  | OSSARY                                                                          | 216  |

|     |                                                                                 |      |

| RES | SUME ETENDU                                                                     | 219  |

| 1   | Introduction                                                                    | 219  |

| 2   | LA METHODE DE CONCEPTION SYSTEME ET L'OUTIL DE SIMULATION SYSTEME               | 220  |

| 3   | COMPARAISON QUANTITATIVE ET DEFINITION D'UNE NOUVELLE ARCHITECTURE DE           |      |

| RI  | ECEPTION A SOUS ECHANTILLONNAGE                                                 | 221  |

| 4   | IMPLEMENTATION DU FILTRE COMPLEXE A TEMPS DISCRET A RII                         | 222  |

| 5   | SPECIFICATIONS EN BRUIT DE PHASE POUR L'ARCHITECTURE PROPOSEE                   | 223  |

| 6   | CONCLUSIONS GENERALES                                                           | 224  |

# Chapter 1 : Introduction

| CHAPTER 1 : INTRODUCTION                                                             | 1 |

|--------------------------------------------------------------------------------------|---|

| 1 THE EMERGING NEEDS FOR AGILE AND LOW POWER RF TRANSCIEVERS                         | 2 |

| 1.1 The WPAN, WBAN and WS&AN - A Multitude of Low Power Applications on the          |   |

| ISM Band                                                                             | 2 |

| 1.2 Technological Trends towards Discrete Time Signal Processing: On the Interest of |   |

| Bandpass Sampling                                                                    | 3 |

| 2 PRESENTATION OF THE THESIS WORK                                                    | 4 |

|                                                                                      |   |

## 1 The Emerging Needs for Agile and Low Power RF Transceivers

#### 1.1 The WPAN, WBAN and WS&AN - A Multitude of Low Power Applications on the ISM Band

The Wireless Personal Area Network (WPAN) is limited to some tens of meters range (<100m) and low- to medium- data rate (< 3 Mbps). Furthermore, the WPAN has evolved and led to the consideration of other networks such the Wireless Body Area Network (WBAN) and Wireless Sensor & Actuator Network (WS&AN). WPAN applications have been standardized by the 15<sup>th</sup> working group of IEEE802 and is split in 7 task groups. The low data rate WPAN defines the 4<sup>th</sup> task group leading to the IEEE802.15.4 specifications, whereas Bluetooth had been considered by the first task group, therefore IEEE802.15.1. Primarily, it was created to link small devices and peripherals with a computer, not specifically for data transfer, although in some applications this data is processed and further sent to a wider network. Following the publication of 802.15.1-2005, the IEEE Study Group 1b voted to discontinue their relationship with the Bluetooth SIG. Later versions of Bluetooth are not IEEE standards. Therefore the Bluetooth Low Energy that we apply in our study is not part of the IEEE802.15 working group.

The Bluetooth standard was created in 1994 by Ericsson. It was defined for a data rate around 1 Mbps and 30m communication distance range. Lately, the Bluetooth 2.0 EDR extended the data rate up to 3 Mbps. The Bluetooth standard is particularly adapted to file transfer applications and connections between a PC and peripheral appliances, known as *Piconet*, where up to 8 devices can be connected in this network. The first device is the master and all the other devices are slaves communicating with the master. As mentioned before, Bluetooth got apart from IEEE in 2005 and developed its own solutions in the WPAN area. Lately, it was perceived that the Bluetooth devices and specifications were not optimized in terms of power consumption, mostly for lower distances applications (up to 10m).

The concept of *Wireless Body Area Network* (WBAN) was created mainly for medical and sport applications, such as heart beat monitoring and other body condition status. In this application the data rate is not the main issue but the service quality is very demanding. The most recent version, Bluetooth 4.0 integrates a low power section specification called *Bluetooth Low Energy* (BT-LE) which objective is mainly to increase battery life for communication devices in the WBAN context. This work is focused on the low power configuration of Bluetooth. On the IEEE802.15 side, the concept of WBAN was also explored. Created in 2007, the task group IEEE802.15.6 is developing a communication standard optimized for low power devices, operating around the human body (but not limited to humans) covering a variety of applications, such as medical, Consumer Electronics, personal entertainment to name a few. In this case, there is a direct competition in terms of applications and band in use (the advantage of IEEE802.15.6 compared to BT-LE is to cover various bands other than the 2.4 GHz *Industrial, Scientific and Medical* (ISM) band).

As previously mentioned, the IEEE802.15.4 was created by the 4<sup>th</sup> IEEE802.15 task group. It was particularly interested in low data rate and high latency times. These characteristics are also well adapted to low cost, ultra low power and low data rate applications. It started to be widely used in industrial processes, now moving from *Wireless Sensor Network* (WSN)to *Wireless Sensor & Actuator Network* (WS&AN), where the network configuration is automatically set with the addition / suppression of nodes on the network. The IEEE802.15.4 is historically also applied for medical applications on the WBAN context [1]. The standard occupies three different bands: 868MHz (Europe), 915 MHz (USA) and 2.4 GHz worldwide.

The motivation on multistandard applications comes from the variety of *Physical Layer Device* (PHY) and *Media Access Control* (MAC) layers specifications in the 2.4 GHz ISM band, and even wider variety of specifications from the network layer protocols (Layer 3) to upper layers which can run over IEEE802.15.4-based networks, including ZigBee. Observing this promising field of applications, and considering that the 2.4 GHz ISM band is in most cases addressed by these standards, we propose to develop innovative receiver architecture capable of addressing this variety of standards in the WPAN, WBAN and WS&AN context. The most remarkable standard technologies for short range, IEEE802.15.4 and Bluetooth Low Energy, are the starting references for this work.

#### 1.2 Technological Trends towards Discrete Time Signal Processing: On the Interest of Bandpass Sampling

RF transceivers that require a lot of analog components do not fully benefit from technological scaling. As a consequence, analog blocks and base band blocks such as Digital Base Band Processor (DBB) and the Application Processor (APP) do not progress similarly, the latter being best-adapted to deep-submicron technologies scaling. In such technologies, the strongest drawback limiting analog functions performances are the low voltage supply and high threshold voltages. In other words, there is considerable reduction on the voltage headroom to implement analog functions. On the other hand, the improvements on the switching characteristics of MOS transistors offer excellent time accuracy, and lithography offers precise control on the capacitance ratios [2]. Considering these trends, Mitola first envisaged the concept of Software Defined Radio (SDR) [3]. All the RF and base band stages are digital, through the application of an Analog to Digital Converter (ADC) directly connect to the antenna. It is evident that the ADC required performances should fulfill extraordinary specifications, and in this case becomes incompatible with the mandatory energy-efficient context. Although digital communication standards occupy frequency bands from 800 MHz to 6 GHz, the bandwidth of a single channel, goes to a maximum of 20MHz, apart from Ultra Wide Band (UWB) standards. Therefore, demodulation and base band processing can be reduced to this frequency in order to have multistandard digital circuitry. Signal processing operations prior to the ADC can be actually reduced to amplification, filtering and downconversion.

The idea to merge SDR concepts with power consumption constraint considerations and consists in using Discrete-Time receivers. One major argument is the possibility to exploit the natural technological scaling trend, while avoiding the weaknesses, such as reduction of voltage headroom or increasing technology variability ([2]-[4]). Theses trends are summarized and

detailed in [5]. Analog discrete-time circuits, such switched-capacitor networks, are adapted to implement the amplification, down-conversion and filtering operations mentioned above.

A particular interesting process that can be exploited on the context of Discrete Time receivers is the *Bandpass Sampling* (BPS). The BPS is one kind of Discrete Time receiver which permits conversion from *Continuous Time* (CT) domain to *Discrete Time* (DT) domain while also operating the down-conversion. The application of this principle is also motivated by the fact that the useful information occupies a bandwidth which is considerably lower than the carrier frequency. The front-end samples only the useful information, making possible to reduce both frequency synthesis and circuit cutoff frequencies. In order to apply the BPS and DT signal processing concepts into low power applications, it is even more interesting to further reduce the sampling frequency by applying high under-sampling ratio combined to anti-aliasing filters prior to the sampler Once the signal is in DT domain, process such as DT filtering, based on the principle of capacitance charge sharing, and decimation, can be applied to reduce the sampling frequency and to reject unwanted signals / interferers. Finally, these techniques enable the reduction of the ADC constraints in terms of clock frequency and resolution.

The new challenges when designing BPS receivers come from the aliasing of the spectrum while under-sampling and processing decimation. An optimized frequency plan has to be designed as well as some filtering techniques to overcome interferer's aliasing into the band of interest. Another considered aspect is to simplify the filtering networks by merging CT and DT filter techniques. We present in this work new methodologies and simulation tools able to address these various system level challenges in order to propose a new BPS architecture oriented to low power consumption and multi-standard purposes. The idea of designing a DT reconfigurable and low power receiver merges the technology trends towards the deep-submicron technologies and the evolution on the WPAN 2.4GHz ISM applications and standards.

### 2 Presentation of the Thesis Work

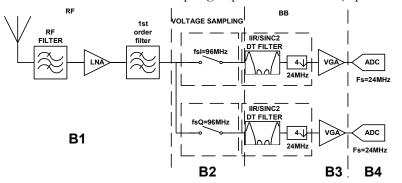

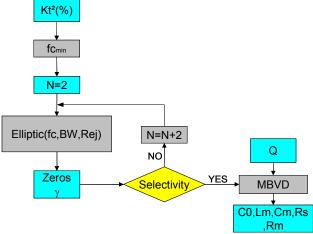

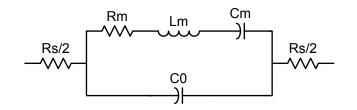

The objective of this thesis work is to propose and specify new receiver architectures able to address characteristics of both agile multi-standard and ultra low power receivers, exploring the BPS technique. In CHAPTER 2, the BPS theory is presented. We highlight the new challenges in terms of the system level design that the BPS process unveils. An overview of the various RF DT receiver architectures is presented. The idea is to set some original ways for down-conversion and filtering based on DT signal processing by merging different solutions and bringing the best of each, exploiting current available literature. On the following, the critical blocks state of the art in the receiving path is presented. The performances of the state of the art set the reference for low power system level design. CHAPTER 3 presents a system level simulation tool developed in MATLAB. Wide-band modeling is implemented to take into consideration the specificity of BPS receivers. A system level specification method which rapidly converges to the standard requirements is also presented. Using the proposed method and associated tool, a quantitative comparison has been carried out for different BPS architectures and is presented in CHAPTER 4. The system level design and block specifications over the various architectures permit to have more insight on the DT architectures trade-offs. A particular attention is brought on the filtering optimization of the receiver chain between the continuous time elements (BAW, Lamb filters) and discrete time elements (switched capacitor active or passive networks). The carried out study ends by a proposition of a new RF BPS receiver architectures based on a high intermediate frequency and a complex DT filtering, regarded as the best trade-off between power consumption and agility. The derived block specifications are compared to the state of the art of the CHAPTER 2 in order to strengthen the work towards a low power goal.

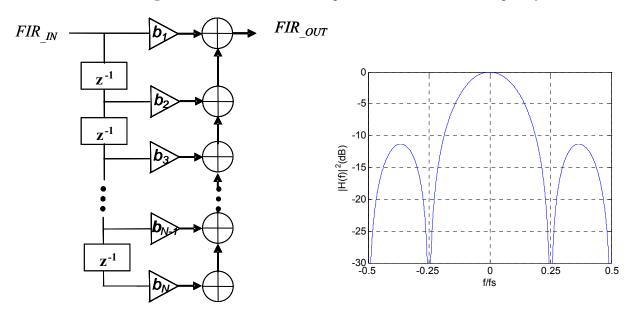

The complex DT filtering function presenting Infinite Impulse Response (IIR) is a key component of the proposed architecture. This filter has a reduced order for a high selectivity and rejection performance while avoiding drawbacks coming from zero IF architectures, such 1/f noise, DC-offset, I/Q mismatches and second order non linearity. CHAPTER 5 presents the theory of DT filtering and its implementation on silicon. The objective of CHAPTER 5 is to validate the DT filter and to evaluate the impact of circuit implementation imperfections on the required frequency response. To achieve this goal, two approaches were adopted, analytical development on the imperfections and behavioral modeling simulation. The analytical approach is defined in terms signal and noise, in order to dimension capacitance sizes. From there, the behavioral modeling is applied further evaluate the circuit imperfections such as parasitic capacitances and non-linear parameters.

#### CHAPTER 1 : INTRODUCTION

# Chapter 2 : The Bandpass Sampling Process & the State of the Art

| 1 | Inti   | RODUCTION                                                     | 8  |

|---|--------|---------------------------------------------------------------|----|

| 2 | The    | BANDPASS SAMPLING                                             | 8  |

|   | 2.1    | Theoretical analysis                                          | 8  |

|   | 2.2    | The voltage and charge sampling                               | 13 |

| 3 | An (   | Overview of RF Down-conversion and Filtering on Discrete-Time |    |

| А | RCHITE | CTURES                                                        | 17 |

|   | 3.1    | Architectures Classification                                  | 17 |

|   | 3.2    | Nyquist-like sampling RX                                      | 18 |

|   | 3.3    | RF/IF Bandpass Sampling with Single Path Filters RX           |    |

|   | 3.4    | RF/IF Bandpass Sampling with complex filtering RX             | 22 |

|   | 3.5    | A Comparative Table Summarizing the DT architectures          | 24 |

| 4 | Disc   | CRETE TIME RECEIVER BASE BLOCKS STATE OF THE ART              | 25 |

|   | 4.1    | LNA                                                           | 25 |

|   | 4.2    | Frequency Transposition                                       | 26 |

|   | 4.3    | Frequency Synthesis Blocks                                    | 28 |

|   | 4.4    | Filtering Blocks                                              | 30 |

|   | 4.5    | Analog to Digital Converter                                   | 37 |

| 5 | Con    | ICLUSION                                                      |    |

## 1 Introduction

The DT receiver is being presented in the literature as an interesting method to merge the technological down scaling trend to further improve integration and the need for agile multistandard transceivers. The objective of this thesis work is at the same time to optimize the concept of DT receiver on the multi-standard aspect and to improve the power consumption for low power RF communications such as WPAN, WBAN and WS&AN. The technique of BPS is being presented here as a solution to alleviate the frequency synthesis constraints thanks to the implementation of the down-conversion process and a CT to DT conversion.

Considering the DT-based architectures, BPS operation and DT signal processing like filtering and decimation are merged into the whole chain through down-conversion and filtering. This chapter focuses on the theory of BPS. New challenges in terms of system level design come with the application of BPS. Two different techniques are possible during the sampling process: the voltage sampling and the charge sampling. This chapter highlights the difference between both techniques.

Concerning the architecture itself, the frequency plan can be defined in different ways with regards to BPS and DT filtering techniques, depending on preferred options e.g.; oriented towards multi-standard or low power applications for instance. In this chapter, the *State of the Art* (SOA) of the DT receivers is presented. We define a classification method based on the down-conversion process, the frequency plan and filtering techniques. Three orthogonal families of DT receivers can be mentioned in the SOA. They are compared in terms of agility and power consumption characteristics. The distinct BPS configurations defined in this chapter are further applied in the ISM band and the *Ultra Low Power* (ULP) standards, in order to lead a quantitative comparison in Chapter 4.

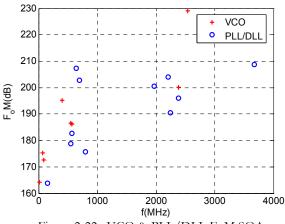

In this chapter, since the system level design of this work is low power oriented, we study the SOA on blocks whose power consumption is critical in RF transceivers. This includes the *Low Noise Amplifier* (LNA), Mixer, *Sample-and-Hold* (S/H) blocks, but also the frequency synthesis ones such as *Phase-Locked Loop* (PLL) and *Delay-Locked Loop* (DLL). The scope of this SOA concerns the 2.4GHz ISM band. Furthermore, on the system level design, the derived specifications provided in Chapter 4 will be compared to the retrieved SOA performances in order to demonstrate the feasibility of the proposed DT architectures in a low power context.

# 2 The Bandpass Sampling

#### 2.1 Theoretical analysis

The conversion from the analog to the digital domain is composed by two distinct operations: first from continuous time to discrete time domain and then from continuous amplitude to discrete amplitude domain. Sampling a signal means observing a given value from a continuous time waveform at a given time instant. During the uniform sampling process the values of the

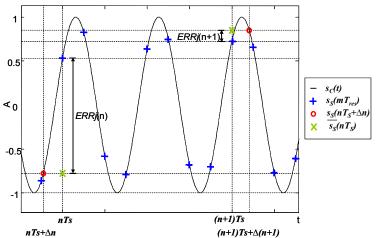

waveform are observed at the instants  $nT_s$ , where  $T_s$  is called the sampling period. The sampling process is modeled by two distinguished operations: the multiplication of the input signal  $v_{in}(t)$  (Figure 2-1) by an infinite sequence of Dirac pulses, and a discretization in time and frequency domain [6, 7]:

$$v_{in_{S}}(t) = v_{in}(t) \sum_{n=-\infty}^{\infty} \delta(t - nT_{S}) = \sum_{n=-\infty}^{\infty} v_{in}(nT_{S})$$

$$(2-1)$$

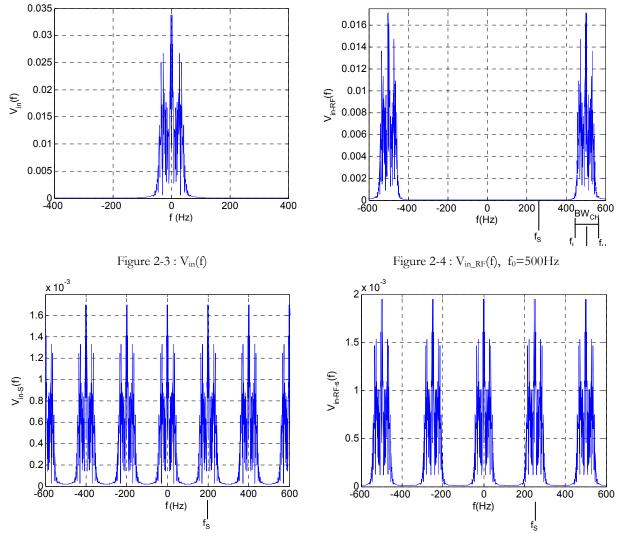

$$V_{in_{S}}(f) = V_{in}(f) * \frac{1}{T_{S}} \sum_{n=-\infty}^{\infty} \delta(f - nf_{S}) = \frac{1}{T_{S}} \sum_{n=-\infty}^{\infty} V_{in}(f - nf_{S})$$

(2-2)

The convolution by a sequence of Dirac pulses in the frequency domain means that the sampled signal is periodic in frequency at  $fs=1/T_s$  (2-2) (Figure 2-5). The signal  $v_{in_s}(t)$  (Figure 2-1) is still defined in CT-domain. The second operation is the discretization of  $v_{in_s}(t)$  to  $v_{in}[n]$ . While applying the DT Fourier Transform, we observe the discrete spectrum with a normalized frequency range r=f/fs. Lately, we show that the DT signal processing is not exclusive of the digital domain (discrete amplitude), but also possible on the analog domain (continuous amplitude). The sampled spectrum in the normalized frequency "r" domain is obtaining by substituting  $f=r \cdot f_s$ :

$$V_{in_s}(r \cdot f_s) = V_{in}(r \cdot f_s) * \frac{1}{T_s} \sum_{n=-\infty}^{\infty} \delta(f_s(r-n))$$

(2-3)

From the scaling property of the Dirac delta function [8] which defines:

$$\delta(fs(r-n)) = \frac{\delta(r-n)}{|fs|}$$

(2-4)

We infer that the scaling coefficient 1/Ts disappears on the DT spectrum. Defining  $V_{in S}(\mathbf{r})=V_{in S}(\mathbf{r}\cdot\mathbf{fs})$ , we have:

$$V_{in_{s}}(r) = V_{in}(r) * \sum_{n=-\infty}^{\infty} \delta(r-n) = \sum_{n=-\infty}^{\infty} V_{in}(r-n)$$

(2-5)

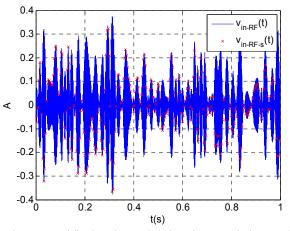

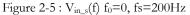

The important difference is that the scaling factor  $1/T_s$  only exists in CT domain, and disappears after the CT-to-DT conversion [6]. The Bandpass Sampling, also known as subsampling, considers a sampling frequency which does not respect the strict Nyquist-Shannon Criterion [9, 10] fs>2·f<sub>H</sub>, where f<sub>H</sub> is the highest frequency of the signal to be sampled. The BPS theory is a generalized interpretation of the Nyquist-Shannon Theorem [11]. A bandpass signal  $v_{in\_RF}(t)$  is a signal where the PSD  $V_{in\_RF}(f)$  is centered at a given center frequency f<sub>0</sub> (Figure 2-4) with a bandwidth BW<sub>CH</sub> much lower than this f<sub>0</sub> (Figure 2-4). The signal is bandpass sampled  $v_{in\_RF\_s}(t)$ , respecting the Nyquist-Shannon criterion fs>2·BW<sub>CH</sub>. The signal PSD is again periodic at fs (Figure 2-6) with an image of the signal falling into the lower band, the base band or an intermediate frequency.

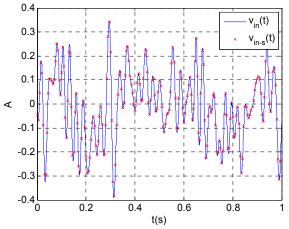

Figure 2-1 : The base band signal over sampled:  $v_{in}(t)$  and  $v_{in\_s}(t)~(fs{=}200Hz)$

Figure 2-2 : The bandpass signal under-sampled:  $v_{in\_RF}(t)$  $f_0=500Hz$  (fs=250Hz)

Figure 2-6 :  $V_{in_{RF_s}}(f)$ ,  $f_0=500Hz$ ,  $f_s=250Hz$

Figure 2-1 illustrates the base input signal along with the sampled values according to the Shannon-Nyquist criterion. In Figure 2-2, the same signal is converted to  $f_0=500$ Hz and Bandpass Sampled. The sampled signal PSD  $V_{in_s}(f)$  is given in Figure 2-5 : it is continuous and periodic at fs. In Figure 2-2, the signal input  $v_{in_RF}(t)$  is modulated by a carrier at  $f_0=500$ Hz (Figure 2-4). The signal is Bandpass Sampled compared to the carrier at fs=250Hz, leading to the

same sampled signal from the Nyquist sampling. The sampled spectrum is periodic at fs=250Hz (Figure 2-6). In both Figure 2-5 and Figure 2-6 the spectrum around the base band is the same (scaled by 1/Ts). From expression (2-5), the scaling faction 1/Ts is suppressed.

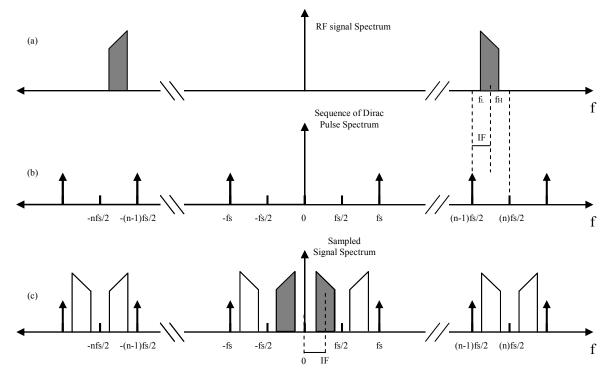

Figure 2-7 illustrates the bandpass sampled signal down-converted to the base band. The spectrum is periodic at fs, and an image of the signal at RF is convolved to the base band, and the input signal is band limited by  $f_L$  and  $f_H$  (Figure 2-7 (a)). From Figure 2-7 (b), the lowest distance between n·fs/2 (n being even) and the center frequency of the signal sets the Intermediate Frequency (IF) of the down-conversion Figure 2-7 (c). In other words, the convolution between the Dirac pulse placed at n·fs/2 and the RF signal sets the base band signal.

Figure 2-7 : Frequency representation of the BPS process ; (a) the RF signal, (b) the Dirac pulses sequence, (c) the bandpass sampled signal

Observing the frequency plan presented in Figure 2-7, the following relations have to be respected in order to avoid spectrum aliasing. The value "n" is defined as the under-sampling ratio ([11]):

$$n = 2 \cdot \frac{f_H}{f_c} \tag{2-6}$$

$$\frac{(n-1)\cdot f_s}{2} < f_L \tag{2-7}$$

$$\frac{(n) \cdot f_s}{2} > f_H \tag{2-8}$$

$$\frac{2f_H}{n} \le f_s \le \frac{2f_L}{n-1} \tag{2-9}$$

The maximum allowed bandwidth is therefore derived from (2-9):

$$BW_{\max} = \min\{2f_0 - (n-1)f_s , n \cdot f_s - 2f_0\}$$

(2-10)

The first advantage on the BPS is the down-conversion in the frequency domain and the time discretization of the signal on the same process. The second one is that low sampling frequencies can be applied in order to relax frequency synthesis. The discrete-time signal processing can still be applied in analog domain (discrete-time with continuous amplitude) in order to implement filtering process and decimation functions. These filters are referred in this thesis work as Discrete-Time filters and filters applied after the ADC are defined as Digital filters.

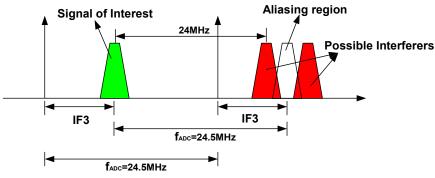

The drawback of the BPS process is the spectral folding of undesired signal into the band of interest (Figure 2-8 (a)). For instance, we have to consider the thermal noise, limited in a band BW<sub>noise</sub> which represents the cut-off frequency of the sampling system. In a sampling system, the periodicity of the spectrum implies that the wideband noise folds into each of the fs/2 bands [11]. Before sampling, consider the in-band continuous time noise PSD defined as N<sub>C\_PSD</sub> (Figure 2-8) and the out-of-band noise PSD defined as N<sub>C\_PSD</sub>/ $\Delta_{noise}$ , where  $\Delta_{noise}$  is capacity of filtering the input noise prior to sampling. The sampled noise PSD is defined as PSD<sub>S\_PSD</sub> (Figure 2-8 (b)). The increase of noise PSD between before and after sampling process is defined as the aliasing factor,  $\gamma=N_{out PSD}/N_{in PSD}$  (Figure 2-8 (b)).

The signal-to-noise ratio of the sampled signal is degraded by at least the aliased noise from DC to  $BW_{noise}$ . Thereafter, to reduce the impact of  $\gamma$ , an anti-aliasing filter is applied which rejects the out-of-band noise by  $\Delta_{noise}$ . The resulting aliasing factor is defined as :

$$\gamma = 1 + \frac{2 \cdot BW_{noise} / \Delta_{noise}}{f_s} = SNR_{deg}$$

(2-11)

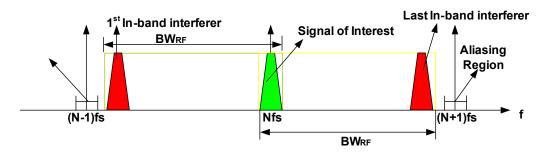

In BPS, the N<sup>th</sup> harmonic of the Dirac pulses defines the down-conversion (Figure 2-8 (a)). The distance between the N<sup>th</sup> harmonic and the signal of interest sets the Intermediate Frequency IF after sampling. In a wideband spectrum context, there can be multiple interferers folding into the band, when their frequency distance to another multiple of the sampling Dirac is also IF (Figure 2-8 (b)) : they are aliasing interferers or image interferers.

Figure 2-8 : The BPS: the spectrum before (a) and after (b) sampling

The spectrum aliasing represents the most important constraint to consider when designing BPS architectures. The accurate knowledge of the aliasing bands enables the definition of filtering techniques and frequency plan, considering the given application and specifically its frequency band in use.

#### 2.2 The voltage and charge sampling

There are two methods to implement the sampling operation at the circuit level: the *Voltage Sampling* and the *Charge Sampling*. Voltage sampling is a conventional method which is implemented by *Sample-and-Hold* (S/H) circuit. It tracks an analog signal and stores its value as a voltage in a sampling capacitance, and keeps this voltage for some length of time. The *Charge-and-Hold* (C/H) circuit integrates the signal current within a given window. The input is transferred from voltage to charge domain before it is sampled. In the next sections, we derive the sampling transfer function in order to show the basic differences between these two techniques ([12]). The output noise divided to *Gain Bandwidth* (G  $\cdot$  BW) is derived to compare the relations between noise and power consumption for both techniques.

#### 2.2.1 Voltage Sampling

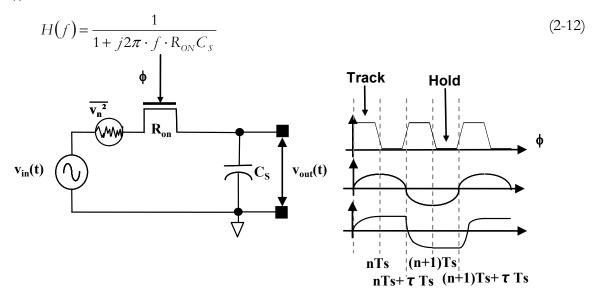

Ideally, a voltage sampling can be modeled as the input voltage signal sampled by ideal sampler (2-1). Actual implementations use the S/H block presented in Figure 2-9. The samples are considered at all nTs times. The sample is Hold between nTs and nTs+ $\tau$ Ts, ( $\tau$  is the duty cycle 0< $\tau$ <1). During the Hold period, the signal can be quantized by an ADC or DT analog signal processing can be implemented (i.e. DT filters). The next sample is tracked from nTs+ $\tau$ Ts to (n+1)Ts. At (n+1)Ts, the next sample is considered. If, in the tracking phase, the exact value of  $v_{in}(t)$  is hold, the sampled DT signal is the same than as defined in (2-1). On the other hand, during the tracking phase, the switch ON resistance  $R_{ON}$  and the sampling capacitance Cs represent a low-pass filter between  $v_{out}(t)$  and  $v_{in}(t)$  (Figure 2-9), defined in the frequency domain as H(f):

Figure 2-9 : The Sample-and-Hold circuit and the clock scheme

The sampled signal is therefore defined by:

$$V_{out\_S}(r) = \sum_{n=-\infty}^{\infty} V_{out}(r-n) = \sum_{n=-\infty}^{\infty} V_{in}(r-n) \cdot H(r-n)$$

(2-13)

In conclusion, the discrete time sequence is the application of the sampling process of a low-pass filtered Continuous Time signal.

#### 2.2.1.1 Input Referred Noise and the Gain Bandwidth Product.

The noise generated by the S/H circuit is defined by the switch resistance  $R_{ON}$  and the circuit cut-off frequency. The total noise is the generated PSD noise integrated along the frequency:

$$v_n^2 \left( V^2 \right) = \int_0^\infty 4 \cdot K \cdot T \cdot R_{ON} \left| H(f) \right|^2 df = 4 \cdot K \cdot T \cdot R_{ON} \cdot \int_0^\infty \frac{1}{1 + \left( 2\pi \cdot f \cdot R_{ON} C_s \right)^2} df$$

$$v_n^2 \left( V^2 \right) = \frac{KT}{C_s}$$

(2-14)

$$PSD_{S/H}\left(V^2 / H_{\mathcal{Z}}\right) = \frac{K \cdot T}{C_s} \cdot \frac{2}{fs}$$

(2-15)

where k is the Boltzmann Constant, T is the temperature in Kelvin and fs=1/Ts. The input referred noise depends on the process gain on the sampling level. Consider a buffer presenting a transconductance "gm" and a unit load resistance; we observe the *Gain Bandwidth* (G·BW) (in hertz) product:

$$GBW = \frac{gm}{2\pi C_s}$$

(2-16)

The output noise-to-gain bandwidth ratio is defined as follows:

$$\frac{PSD}{G \cdot BW} = \frac{4\pi^2 C_s^2}{gm^2} \cdot \frac{K \cdot T}{C_s} \cdot \frac{2}{fs}$$

(2-17)

What is observed is that power consumption (in this case represented by gm) will depend on the required input referred noise figure and gain. In this section, it is shown that the choice for the sampling capacitance and for the transconductance gain infers the sampling system bandwidth, gain and noise. Small capacitances lead to high noise at constant power consumption. A third aspect is the sampling frequency which folds the KT/C noise in the fs/2 band.

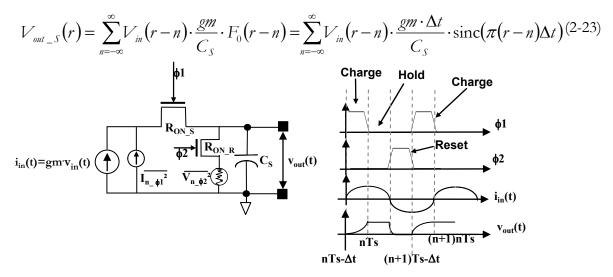

#### 2.2.2 Charge Sampling

In charge sampling, the voltage is transferred into a current source, and it is integrated in  $C_s$  between nTs- $\Delta t$  and nTs (Figure 2-10). The integrated value is therefore held and reset; the charging integration restarting at (n+1)Ts- $\Delta t$ .

The sampled voltage is defined as [13]:

$$v_{out}(nTs) = \frac{1}{Cs} \int_{nTs-\Delta t}^{nTs} gm \cdot v_{in}(t) dt = \frac{1}{Cs} \int_{-\infty}^{\infty} gm \cdot v_{in}(t) \cdot \left[u(t - (nTs - \Delta t)) - u(t - nTs)dt\right]$$

(2-18)

where u(t) is the unit step function. Now, let consider  $f_0(t)$  defined as:

$$f_0(t) = u(-t + \Delta t) - u(-t)$$

(2-19)

The equation (2-18) becomes:

$$v_{out}(nTs) = \frac{1}{Cs} \int_{-\infty}^{\infty} gm \cdot v_{in}(t) \cdot f_0(nTs - t) dt = \frac{gm}{Cs} \cdot [v_{in}(t) * f_0(t)] \cdot \delta(t - nTs)$$

(2-20)

$$v_{out}(t) = \frac{gm}{Cs} \cdot \left[ v_{in}(t) * f_0(t) \right] \longleftrightarrow V_{out}(f) = \frac{gm}{Cs} \cdot V_{in}(f) \cdot F_0(f)$$

(2-21)

Similar to H(f) defined in (2-12),  $F_0(f)$  represents the frequency response for the filtering function prior to sampling [13]:

$$F_0(f) = \Delta t \cdot \operatorname{sinc}(\pi/\Delta t) \tag{2-22}$$

Similarly to (2-5), the DT spectrum of the charge sampled signal is given by:

Figure 2-10 : The Charge-and-Hold circuit and the clock scheme

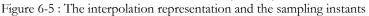

The sinc function is an intrinsic filtering function on the charge integration, which can be considered as an anti-aliasing function. As the voltage sampling is limited by the gm and the Cs from the intrinsic low-pass function on the S/H circuit; the charge sampling is limited by Cs and gm integration process, which also represents a low-pass behavior. The cut-off frequency depends on the integration period  $\Delta t$  (and therefore on the clock), contrarily to the RC time constant for the voltage sampling. The filtering stage (H(f) F<sub>0</sub>(f)) is applied prior to sampling, therefore the filtering transfer function stages are not periodic. On the sampling process the filtered signal becomes periodic.

#### 2.2.2.1 Input Referred Noise and the Gain Bandwidth Product.

During the charging phase, the  $R_{ON}$  resistance from the sampling switch  $R_{ON-S}$  is seen as a current noise source, which is integrated in the defined window  $F_0(f)$ . The noise from the sampling switch is defined as follows:

$$v_{n_{-}\phi_{1}}^{2} \left( V^{2} \right) = \int_{0}^{\infty} \frac{4 \cdot K \cdot T}{R_{ON_{-}s}} \left| F_{0}(f) \right|^{2} df = \frac{K \cdot T}{C_{s}} \cdot \frac{2\Delta t}{R_{ON_{-}s}C_{s}}$$

(2-24)

The reset switch of Figure 2-10 also contributes to the noise level. During the charging phase, the noise from the reset switch is discharged (the time constant depending on the sampling switch  $R_{ON_s}$ ), and at the beginning of the hold phase, it is added to the sampling switch noise:

$$v_{n_{-}\phi_{2}}^{2} \left( V^{2} \right) = \int_{0}^{\infty} 4 \cdot K \cdot T \cdot R_{ON_{-}R} \cdot \frac{1}{1 + \left( 2\pi R_{ON_{-}R} C_{s} \right)^{2}} \left( e^{-\Delta t / \left( R_{ON_{-}s} C_{s} \right)} \right)^{2} df = \frac{K \cdot T}{C_{s}} \left( e^{-2\Delta t / \left( R_{ON_{-}s} C_{s} \right)} \right) (2-25)$$

Therefore, the total output noise PSD is given by:

CHAPTER 2 : THE BANDPASS SAMPLING PROCESS & THE STATE OF THE ART

$$PSD_{C/H}\left(V^2 / H_{\mathcal{Z}}\right) = \frac{K \cdot T}{C_s} \cdot \frac{2}{fs} \cdot \left(\frac{2\Delta t}{R_{ON_s}C_s} + \left(e^{-2\Delta t / (R_{ON_s}C_s)}\right)\right)$$

(2-26)

The filtering function of the charge sampling is defined by (2-21). The cut-off frequency is independent on the  $R_{ON_s}C_s$  time constant, but on the integration interval  $\Delta t$  (when  $sinc(\pi f\Delta t)=0.71$ , i.e.  $\pi f\Delta t = \pi \cdot 0.44$ ). The noise becomes scaled by the  $\Delta t/R_{ON}C_s$  ratio:

$$PSD_{C/H}\left(V^{2}/H\chi\right) = \begin{cases} \frac{KT}{C_{s}} & \text{if } 2\Delta t << R_{ON_{s}}C_{s} \\ \frac{KT}{C_{s}}\left(\frac{2\Delta t}{R_{ON_{s}}C_{s}}\right) & \text{if } 2\Delta t >> R_{ON_{s}}C_{s} \end{cases}$$

(2-27)

In order to compare this with the voltage sampling, we develop the expression for the noise divided by G·BW on the charge sampling process. The gain at DC for the charge sampling is given thanks to (2-22), G=gm· $\Delta t/C_s$ . The -3dB cut-off frequency is defined when  $\pi$ fc $\Delta t$  = $\pi$ ·0.44 (sinc( $\pi$ fc $\Delta t$ )=0.71), which leads to fc=0.44/ $\Delta t$ . GBW is defined as follows:

$$G \cdot BW = \frac{gm}{Cs} \cdot 0.44 \tag{2-28}$$

$$\frac{PSD}{G \cdot BW} = \frac{C_s^2}{gm^2} \cdot \frac{KT}{C_s} \cdot \frac{2}{fs} \cdot \left(\frac{2\Delta t}{R_{ON}C_s} + \left(e^{-2\Delta t/(R_{ON-s}C_s)}\right)\right) \cdot \frac{1}{(0.44)^2}$$

(2-29)

Better gain bandwidth is achieved by charge sampling for the same gm, where the noise can be as low as  $KT/C_s$  for high  $R_{ON S}$ .

#### 2.2.3 Comparative study summary

The following table summarizes the different characteristics of both sampling techniques:

| Parameters    | Voltage sampling     | Charge sampling               |  |

|---------------|----------------------|-------------------------------|--|

| BW(Hz)        | $1/(2\pi R_{ON}C_S)$ | $0.44/\Delta t$               |  |

| Noise         | % 1/C <sub>s</sub>   | $\% \Delta t / (R_{ON}C_{S})$ |  |

| Realization   | Simple               | V-I Converter                 |  |

| Realization   | Simple               | Resetting Structure           |  |

| Anti-aliasing | LP filter            | Sinc filter                   |  |

Table 2-1 : The low power and/or wideband LNA SOA

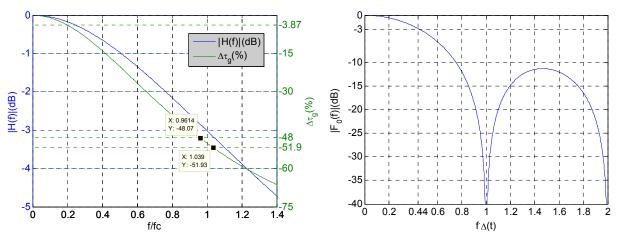

The voltage sampling is mostly dependent on the RC time constant, and for high frequencies, the switch resistance is a critical parameter to consider. At Nyquist sampling, the  $\tau=2\pi$ RC time constant is defined to be at least  $\tau=1/(5 \cdot f_H)$ , where  $f_H$  is the highest frequency to be sampled. The H(f) (2-12) transfer function presents a non-constant group delay  $\tau_g$ , which leads to signal distortion. Figure 2-13 illustrates (right hand axis) the variation of the group delay in percent. At Nyquist sampling, if the time constant is one fifth of the highest sampling frequency to be sampled ( $\tau=1/(5 \cdot f_H)$ )  $f_H=0.2 \cdot f_c$ , from Figure 2-11 we observe that it represents a variation on the group delay of  $\Delta \tau_g=3.7\%$ . On the other hand, in BPS process, the band occupied by the signal is very small compared to the center frequency  $f_0$ >>BW<sub>CH</sub>. For a signal centered at the cut-off frequency of the system  $f_0=1/\tau$ , the variation of  $\Delta \tau_g=3.7\%$  is observed when  $f_0/BW_{CH}=12.67$ . In conclusion, the constraint to define RC time constant in BPS is reduced if compared to Nyquist sampling. In this case H(f) at  $f_0$  can be seen just as losses in the sampling

process. It is important to notice that the voltage sampling transfer function is independent on the sampling frequency and on the duty cycle.

On the charge sampling, the transfer function is defined by a sinus cardinal where the cut-off frequency is dependent on the sampling interval  $\Delta t$  (Figure 2-10). The charge sampling needs a linear V-I converter and a reset stage, which leads to somewhat more complex circuits. The sinus cardinal function has the advantage of presenting a transfer function with linear phase, where the cut-off frequency can be closer to  $f_H$  for Nyquist sampling process. For the BPS it becomes a drawback since the transfer function depends on the applied sampling frequency. Considering a duty cycle of  $\Delta t \cdot f s = 0.5$ , if the signal center frequency is  $f_0 = f s$ , the signal is already attenuated by a factor greater than 3dB. For higher frequencies the sinus cardinal filter will suppress the signal of interest. In order to reduce the sampling frequency,  $\Delta t$  has to be kept constant, and in this case, the duty cycle is changed. In any of cases the charge sampling becomes a constraint on the clock generation.

Figure 2-11 : The group delay relative variation in voltage sampling

Figure 2-12 : The charge sampling sinc filter

In conclusion, if lower sampling frequencies and simple clock generation are aimed at, the voltage sampling has to be preferred. For high under-sampling ratios, implemented with either voltage or charge sampling, an anti-aliasing filter is mandatory to reduce the impact of the aliasing noise. The RC time constant drawback noticed in Nyquist operations is less constraining in BPS test cases when  $f_0$ >>BW<sub>CH</sub>.

# 3 An Overview of RF Down-conversion and Filtering on Discrete-Time Architectures

#### 3.1 Architectures Classification

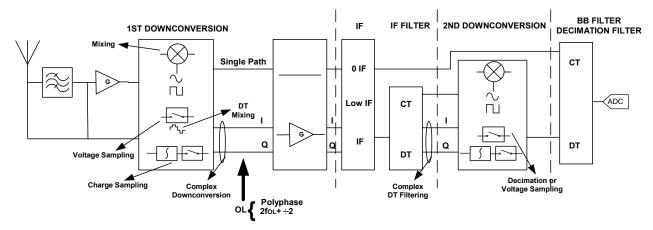

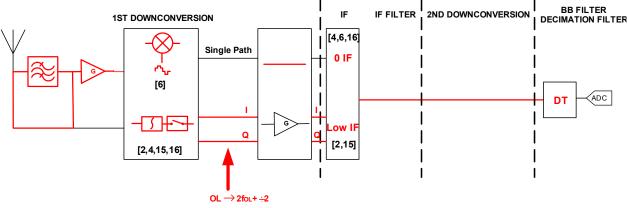

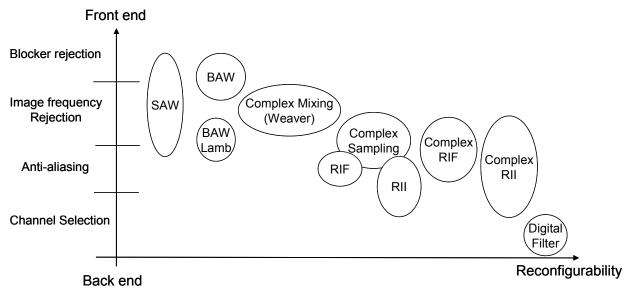

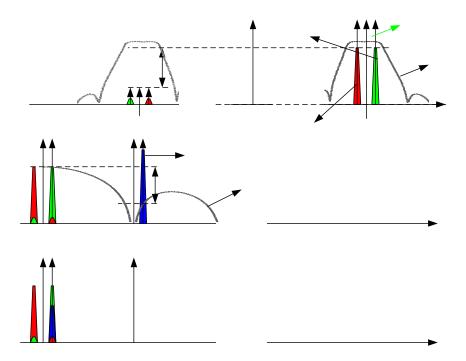

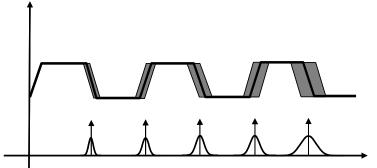

In order to classify the various DT receiver architectures, we derive a generic mapping of the possible down-conversion and filtering techniques (Figure 2-13). The studied DT architectures in the literature are [2, 4, 6, 14-20]:

Figure 2-13 : - Synoptic of the down-conversion and filtering techniques.

In most cases, the RF filter is mandatory, since the linearity constraints on the LNA would be impossible to fit considering low power requirements. The idea in this work is to find the fair trade-off between reconfigurability and power consumption. *Software Defined Radio* architectures often use wideband LNAs without any RF filters [4, 6]. When non linear LNA's are employed, a bank of RF filters is needed to address multiple bands.

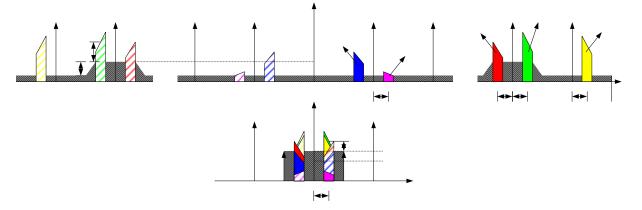

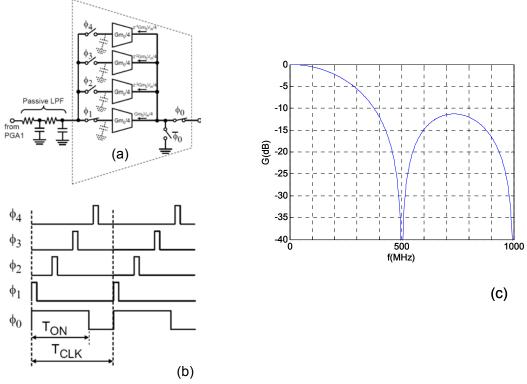

Frequency down-conversion can be implemented using classical mixer stages, where the Local Oscillator (LO) can present various waveforms. Different waveforms are implemented in order avoid harmonic intermodulation products. Charge sampling [2, 4, 15-17] and voltage sampling [6, 14, 18, 19] have also been implemented directly at RF frequencies. The first down-conversion can be implemented in single path or in quadrature. Three distinct groups appear in this classification:

- Nyquist-like sampling Receiver (RX) [2, 4, 6, 15, 16].

- RF/IF Bandpass Sampling with single path filters RX [14, 19, 20].

- RF/IF Bandpass Sampling with complex filtering RX [17, 18].

The first family of architectures presents a sampling frequency at least  $fs=f_{RF}$ . The minimum under-sampling ratio is n=2. We then refer this kind of process as Nyquist-like sampling RX. The second family exploits the properties of BPS in order to reduce the sampling frequency, while applying voltage sampling. Precise quadrature synthesis is needed for the complex sampling operation. The third family implements the concept of complex filtering in DT domain. The complex filter is used either to implement direct conversion with single clock generation or to implement image rejection at low-IF. On the following sections, the various receiving strategies from the SOA will be classified according to the generic scheme of Figure 2-13, and pros and cons are listed for each architecture family.

#### 3.2 Nyquist-like sampling RX

The common point of all architectures in this family is the single down-conversion to zero- or low-IF. Quadrature frequency synthesis is therefore necessary to discriminate the receiving paths in the former case. The classification for such receivers is in Figure 2-14. Charge

and voltage sampling examples are present in this type of architecture. The related SOA for this architecture family is in [2, 4, 6, 15, 16].

The RF filter is suppressed in the case where several RF bands are desired; on the other hand more complicated DT filtering networks are implemented to achieve the required rejection and highly linear LNA are used. Although the inherent integration filter is capable to implement out-of-band anti-aliasing filtering, many out–of-band signals are still present from DC to  $f_{RF}$  which may saturate the amplifier stage and block the signal of interest.

Considering the inherent integration filtering of charge sampling [2, 4, 15, 16], the undersampling ratio (2-6) is limited to 2, which leads to sampling frequencies as high as the RF center frequencies. The presented quadrature frequency synthesis blocks consist of a clock reference at  $2 \cdot f_{RF}$  then followed by a divider-by-two. Thereby, considering the rising or the falling edges of this division process, the quadrature clocks are generated. This technique while improving I/Q mismatches compared to polyphase *Voltage Controlled Oscillator* (VCO) requires generating the base frequency at least at twice the RF frequency.

Figure 2-14 : - Down-conversion and filtering techniques for [2, 4, 6, 15, 16]

Over-sampling, and DT mixing is present in [6]. This technique allows applying *Harmonic* Rejection (HR) with a DT mixing process. In [6], the generated frequency is  $fs=8 \cdot f_{RF}$ , where 8 different phases define a sine/cosine pair. This technique improves anti-aliasing characteristics and harmonics intermodulation rejection. The selected gains are  $1:\sqrt{2}: -\sqrt{2}:-1:-1:-\sqrt{2}:\sqrt{2}:1$  for cosine wave and  $\sqrt{2}:1:1:\sqrt{2}:-\sqrt{2}:-1:-1:-\sqrt{2}$  for sine wave. The DFT of this sequence leads to a signal where the  $3^{rd}$  and  $5^{th}$  harmonics are rejected.

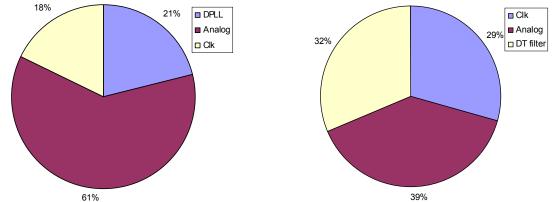

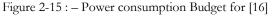

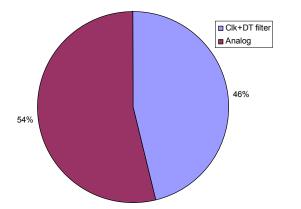

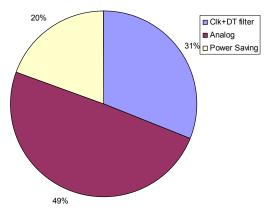

For all receivers considered in this section, once the signal is down-converted, successive decimations down to the ADC sampling frequency are implemented. In order to avoid the noise / interferer aliasing in the band presented in Figure 2-8, consecutive DT filtering and decimation are implemented. There is a trade -off between the DT filter / decimation circuit complexity and the ADC performances. Higher ADC sampling frequency is present in [16], where more performing DT filtering techniques are presented in [4]. In this case, the filters orders or the number of decimation steps increase. Implementing DT filtering at high fs is sensitive to parasitic capacitances and represents a constraint on the clock tree generation (mismatch and clock buffers). Figure 2-15 and Figure 2-16 illustrate the power consumption distribution for [16] and [4], respectively. Notice that the clock and the synthesis power consumptions represents from 30% to 40% of the total receiver power.

At zero-IF, careful design is required to reduce 1/f noise, DC offset and second order non-linearity [4, 6, 16]. A low-IF frequency plan is preferred in [2, 15]. Both choices suffer from I/Q mismatch: at zero-IF, it leads to EVM degradation whereas at low-IF, it leads to finite image rejection. Apart from the drawbacks of zero-IF, low-IF presents a more constraining test bench regarding I/Q mismatch, considering that the image signal is an interferer which power is higher than the signal of interest one.

Figure 2-16 : – Power consumption Budget for [4]

The sampling frequency, which sets the down-conversion, changes for each channel to be addressed. Since constant decimation order is applied, the ADC works at a variable sampling rate. A fractional decimation is needed Between the ADC sampling frequency and the digital base band, where digital processors work at constant rate. The DT signal processing gives certain flexibility to the circuit. Consider the filtering function defined on the normalized frequency range. The filter notches are defined at multiples of the decimated frequency, meaning that they shift in absolute value with the sampling frequency. The ADC clock frequency can be reduced changing the decimation order. In conclusion, this family of architectures proposes a great agility to address various standards, considering that the reconfiguration relies on a wide frequency range synthesis and several filtering/decimation stages. A bank of RF front-end filters or highly linear LNAs are used, depending on the integration level / power consumption trade-off.

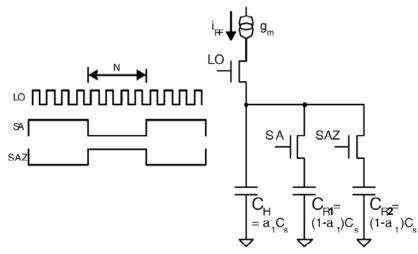

#### **RF/IF Bandpass Sampling with Single Path Filters RX** 3.3

In this case, low sampling frequencies are preferred, which implies that charge sampling is avoided. The voltage sampling S/H circuits are better adapted for that matter [14, 19, 20]. The classification for such receivers is illustrated in Figure 2-17:

Figure 2-17: - Down-conversion and filtering techniques for [14, 19, 20]

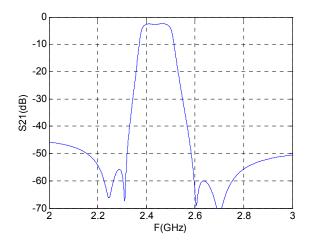

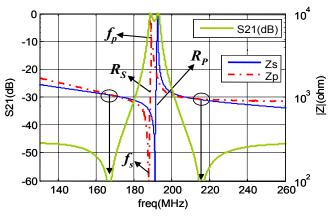

In order to reduce the sampling frequency, [20] the charge sampling becomes impractical since the inherent integration filtering rejects the signal of interest (as presented in section 2). Considering that the RF filter bandwidth correctly rejects out-of-band blockers, the sampling frequency can be reduced as low as  $BW_{RF}$ . For direct conversion, the quadrature clock at 2 fs is sensibly small compared with the previous architecture family. To correctly separate the I/Q signals, the under-sampling ratio is set as follows: (n/2) must be an odd number ([20]). Lately in Chapter 4, we will observe that this topology is even more sensitive to I/Q mismatch than if  $fs=f_{RF}$ . This is the case since the phase difference multiplies over the harmonics of fs. With a low sampling frequency and no intrinsic filtering, the voltage sampling with high "n" needs anti-aliasing filtering. For the thermal noise, smooth filtering is sufficient. For example the output noise of a tuned LNA presents low enough noise to support the aliasing factor. CT anti-aliasing at RF are implemented by *Surface Acoustic Wave* (SAW), *Bulk Acoustic Wave* (BAW), BAW *Lamb Wave Resonators* (LWR) and LC tuned LNA filters.

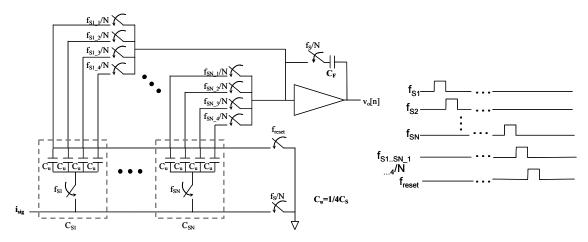

Single path sampling can be used to avoid problems from I/Q mismatch. In [19], the first BPS sampling operation is used for down-conversion. From the first sampling process the signal is down-converted from the RF frequencies to an IF. Consider the aliasing cases illustrated in Figure 2-8, the IF must be higher than the front-end filter BW to avoid image and out-of-band aliasing. The frequency plan is defined in such a way that a single sampling frequency (fs=761.8 MHz) is applied to down-convert three RF bands (GSM, UMTS and IEEE802.11g) to the same IF (114.6 MHz to 189.2 MHz) range. Since a single fs is applied, the IF band is as wide as the RF band. To address several channels, the second sampling frequency is variable inside the IF band. The decimation ratio between the first and the second sampling frequencies is mostly non integer. The simplest way to implement this decimation is to reconvert the signal from CT-domain to DT-domain, and then resampling. The CT-domain to DT-domain conversion is implemented by an interpolation filter at IF. The wide IF bandwidth is the main drawback of this architecture, since the filter needs a very large relative bandwidth (BW<sub>IF</sub>/IF≈49%). The second sampling frequency is centered on the channel to demodulate. The complex IF sampling also suffers from I/Q mismatches, but at lower frequencies, this constraint is better overcome.

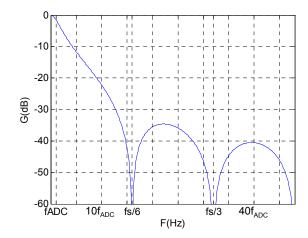

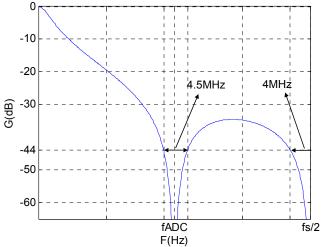

In [14], a higher under-sampling ratio of n=23 is considered, where an anti-aliasing filter is implemented at the LNA output. In this work, the same RF filter design is applied before and after the LNA. Both filters and the LNA are off-chip in this work. In [14], the sampling frequency is slightly higher than the RF BW. From the first sampling stage to the ADC, several DT filter and decimation stages are applied. The signal is down-converted to IF1=fs/3. The image signal at  $f_{RF}+2fs/3$  is filtered prior to sampling by RF filtering techniques. From the first sampling frequency to the ADC clock frequency, several decimations by 2 are implemented. After the decimation process, the signal falls again at fs<sub>dec</sub>/3, where fs<sub>dec</sub> is the decimated sampling frequency. A possible interferer that is centered at fs/6 will also fall at fs<sub>dec</sub>/3. The DT filter is implemented in such a way to have the pass band at fs/3 and a zero at fs/6. The chosen filter type is the Bi-quadratic filter ([14]) (IIR filter). The same DT filter can be used along with all decimation stages. Low-IF and low f<sub>ADC</sub> can be achieved as long as the image rejection specification is met by the bi-quadratic filter.

This architecture family relies on reducing the sampling frequency while applying voltage BPS. Possible passive IF filtering for anti-aliasing can be implemented by BAW-Lamb filters and SAW filters. The SOA on the filtering blocks is presented in section 4.4.2. The RF front-end filter is used as an interferers anti-aliasing filter, and tuned LNAs for noise anti-aliasing prior to sampling. Single path sampling to low-IF presented in [14] merges the sampling frequency reduction and relax 1/f noise, DC-offset and IIP2 constraints. The drawback is the DT filter implementation complexity.

#### 3.4 RF/IF Bandpass Sampling with complex filtering RX

The complex demodulation presented in section 3.2 consists on having two sampling clocks which are shifted in phase by 90°, and, for the low-IF case study, on applying the complex sampling for image rejection. In section 3.3, single path sampling is applied with the image signal being rejected prior to sampling by a CT filter (at RF or IF). The complex sampling suffers from I/Q mismatch which will generate distortion at base band level in the case of zero-IF or limited image rejection in the case of low-IF. The image rejection implemented by CT filters is only achieved with selective filters or with relatively high IF.

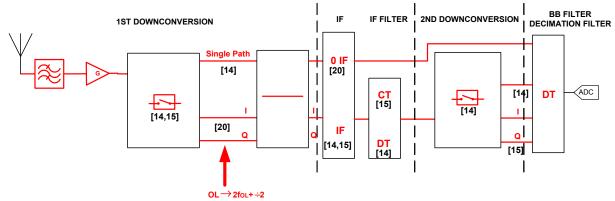

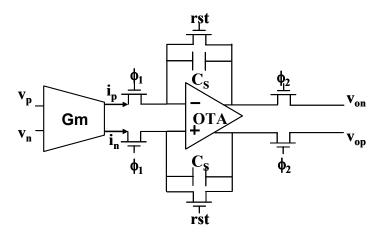

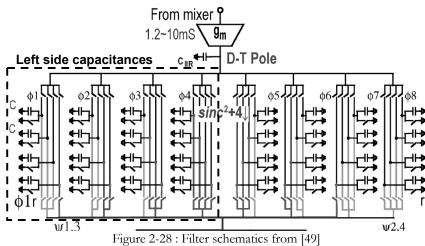

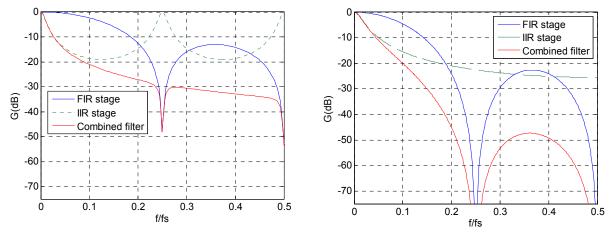

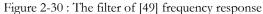

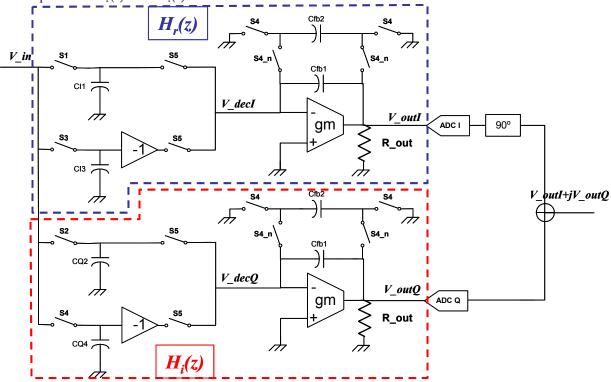

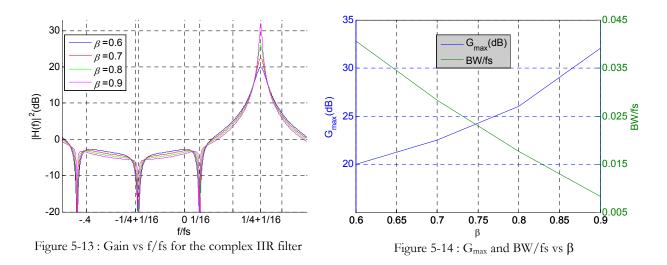

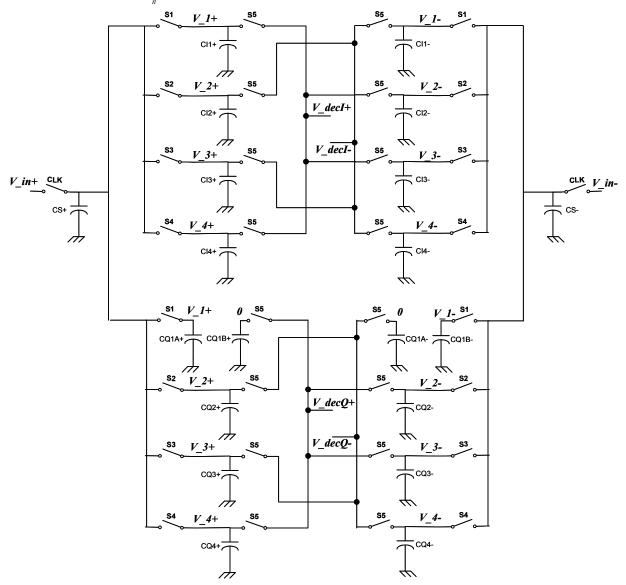

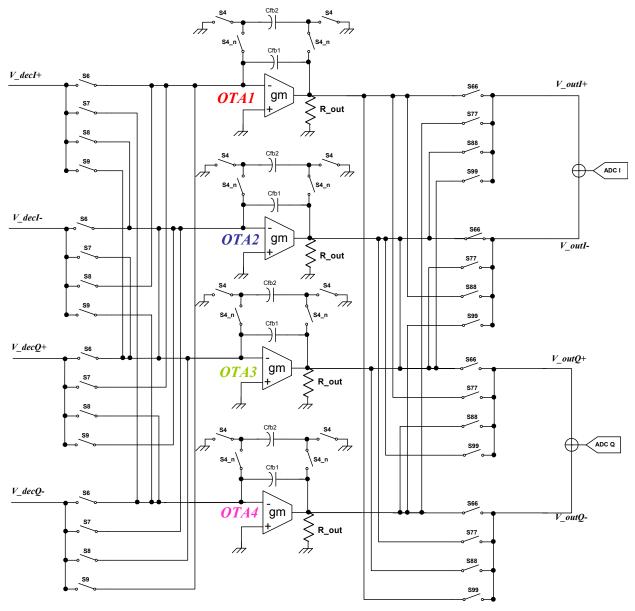

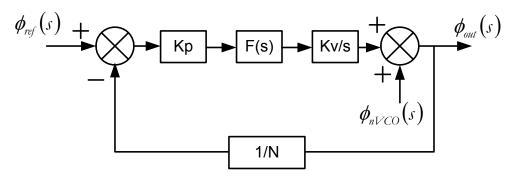

In order to avoid I/Q mismatch issues from complex sampling process and to relax or suppress off-chip CT filters, the technique of complex DT filtering is implemented in [17, 18]. The main idea is to shift the frequency response of a low-pass DT filter into an intermediate frequency using the Hilbert Transform [21]. The theory of the DT filtering, and in particular the complex DT filtering, is presented in Chapter 5. The resulting filter contains complex coefficients and is non-symmetric from a frequency point of view, enabling to filter image frequency signals. The receiving strategy of [17, 18] is summarized in Figure 2-18:

Figure 2-18 : - Down-conversion and filtering techniques for [17, 18]

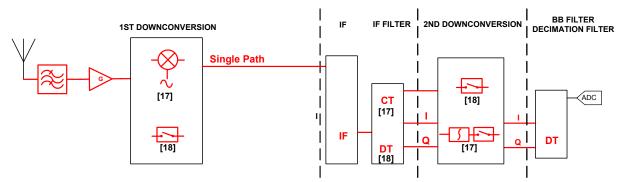

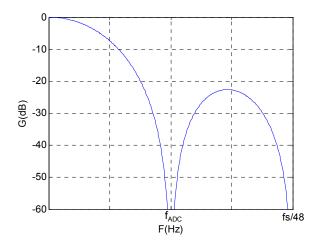

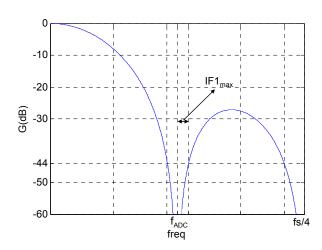

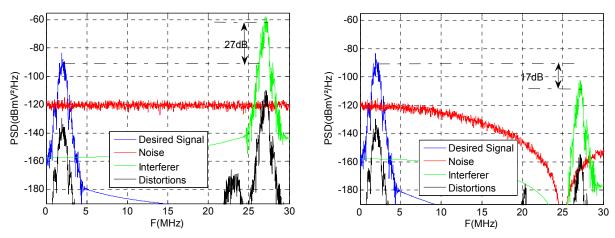

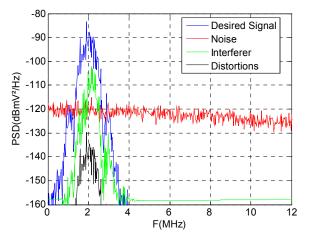

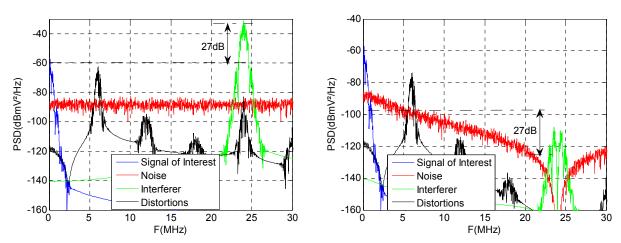

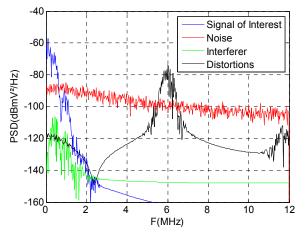

In [18], the center frequency of the complex filter is equal to fc=fs/4. Through voltage sampling, the signal is down-converted to IF1=fc or IF1 close to fc. In [18], it has been chosen to have IF1=fc. In [18], two operating modes are observed: the first one implementing a high sampling frequency in order to reduce the S/H noise impact (2-14) and the second one applying half of the sampling frequency to observe the power savings. In Figure 2-19 and Figure 2-20 we illustrate the power budget for high and low sampling frequency modes and the power saving (20% less power consumption). The front-end filter rejects the first image frequency signal at  $f_{RF}$ -2·IF1. The decimation implements a second down-conversion. Where IF1=fc=fs/4 (which is the case for [18]), the signal is down-converted to zero-IF. In this case, the complex filter is used to separate I/Q signal. When fc=fs/4 the phase shift between I and Q paths transfer function at fc is  $\pi/2$ , therefore, quadrature sampling phase shift can be implemented using a single clock reference and several filtering paths. If IF2≠0, image rejection is implemented by using a modified weaver structure ([22]). I/Q mismatch is avoided using single clock. The possible mismatches between the I/Q filter coefficients come from capacitance mismatch. The use of correct unit capacitances and dedicated layout techniques leads to very small mismatch. Therefore, it does not need compensation techniques which demand additional power consumption. In Chapter 5 we show the impact of the capacitance mismatches on a DT filter transfer function.

Figure 2-19 : – Power consumption Budget for [18], high fs mode.

Figure 2-20 : – Power consumption Budget for [18], fs/2 mode.

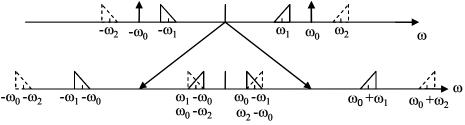

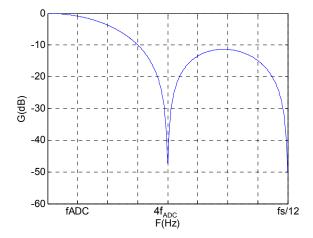

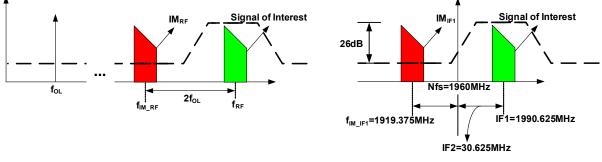

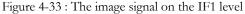

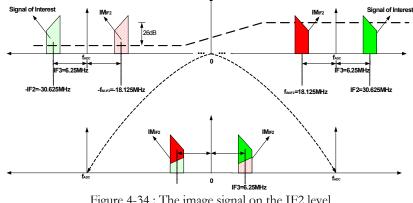

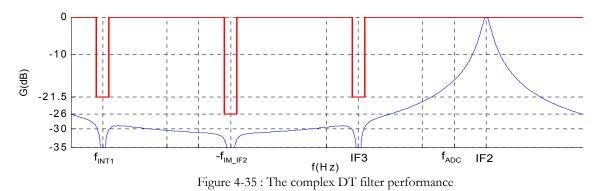

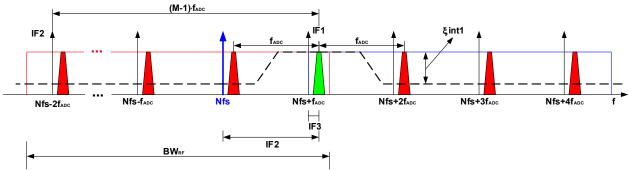

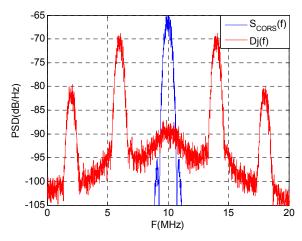

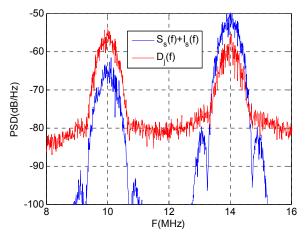

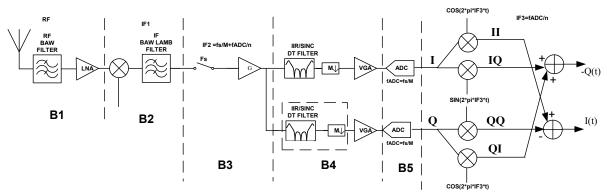

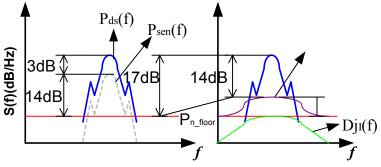

In [17], the signal is first down-converted to an IF1 through classical mixer stage and bandpass filtered by a CT BAW filter. The front-end filter rejects the image frequency signal at f<sub>im RF</sub>=f<sub>RF</sub>-2·IF1. Differently from [19], the various RF channels are down-converted to a single IF1. From this single IF1, there is no need to apply different sampling frequencies on blocks, which is the case for the architectures described in section 3.2. The CT filter at IF1 level can relax the required performances on the DT filter (see proposed architecture of Chapter 4). In [17] it was chosen to implement charge sampling and fs>IF1. When analyzing the double side spectrum, the IF falls on the negative side, which means the PSD of the sampled signal is mirrored at the positive side. The DT filter is frequency shifted to fc=-fs/4. In [17] a high IF1 is chosen, therefore, a high sampling frequency is needed, due to inherent charge sampling Sinc filter. The consequence is a high DT filter and the decimation orders on the implementation. During the sampling process, the signal shifts to a second intermediate frequency IF2, and differently from [18], we have IF2 $\neq$ fc. The image signal at f<sub>im IF1</sub>=IF1+2·IF2 is rejected by the CT IF1 filter. In consequence, the decimation process down-converts the signal to a low-IF IF3. This choice is motivated to avoid the previously mentioned zero-IF drawbacks. The complex DT filter in this case is used to implement the image frequency rejection of f<sub>im IF2</sub>=IF2-2·IF3 at the DT filter level. This solution merges the complex filtering techniques (which relax I/Q mismatches) and avoids the drawbacks of zero-IF architectures.

Notice that the signal at IF2 is not placed at the center frequency of the complex DT filter, therefore, the filter transfer function is not optimized for the image frequency rejection. If it was the case, more selective filters such as complex IIR (see Chapter 5) should be applied. Finally, reducing sampling frequency through voltage sampling can lead to reduction of the frequency synthesis complexity thereby to the power consumption.

#### 3.5 A Comparative Table Summarizing the DT architectures

Table 2-2 summarizes the discussed pros and cons of the various DT architectures from the SOA. In order to develop a quantitative comparison between these three architecture families, Chapter 4 is dedicated to derive the system level specifications for the focused BPS standards. A new architecture is presented, merging the positive points from each configuration and taking into account agility and power consumption.

| Туре                                     | Ref         |                                                                                                               | Pros                                                                 |                                  | Cons                                                                                                                                          |                                   |                                                     |                                                                  |  |

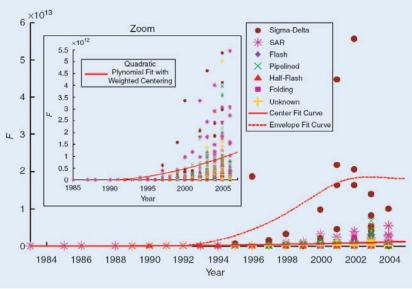

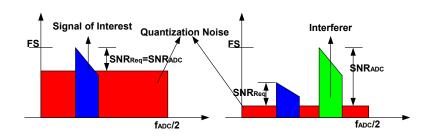

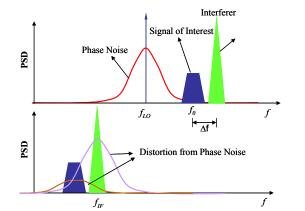

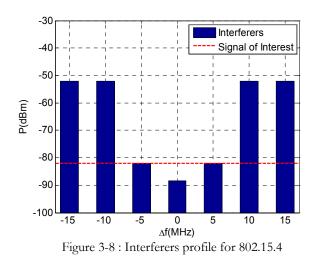

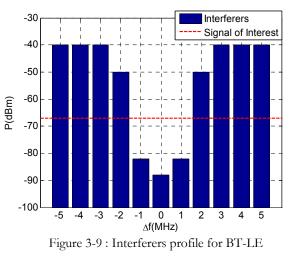

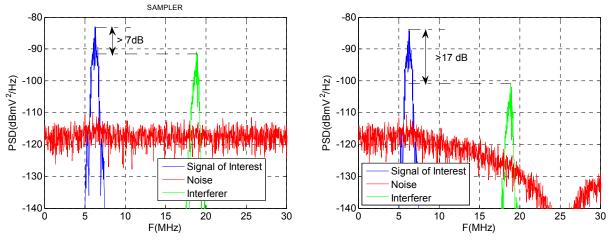

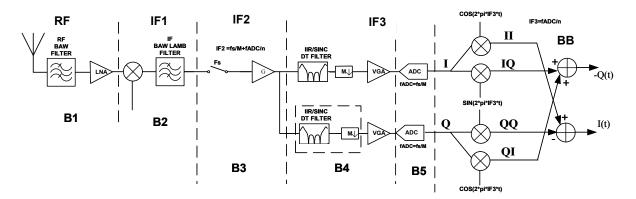

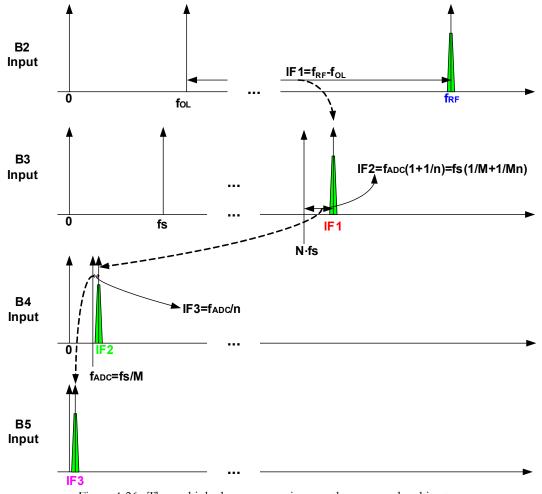

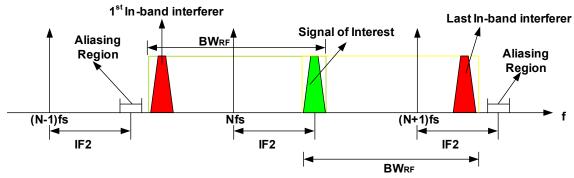

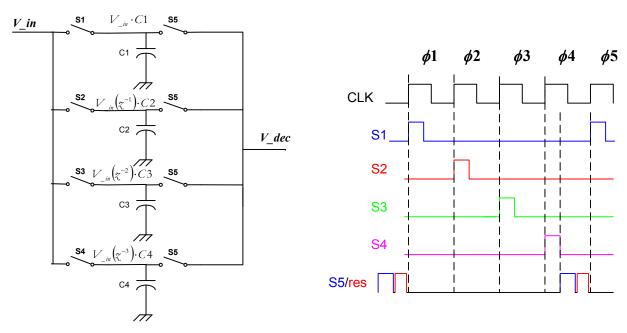

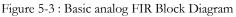

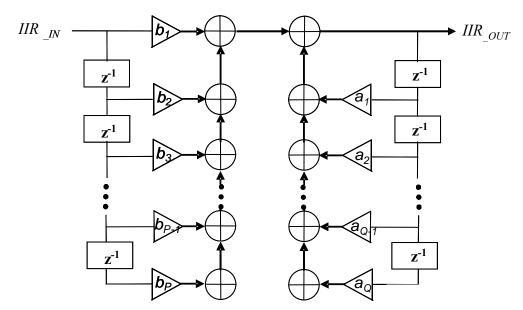

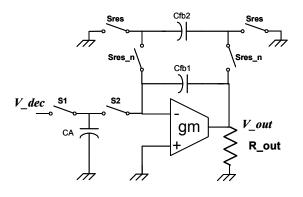

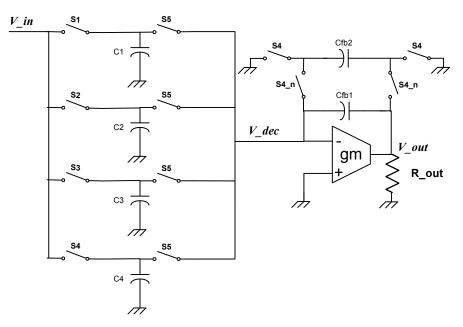

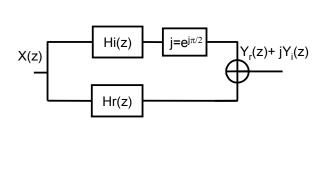

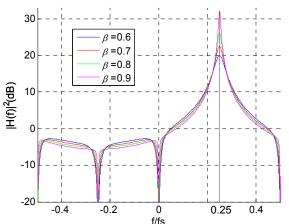

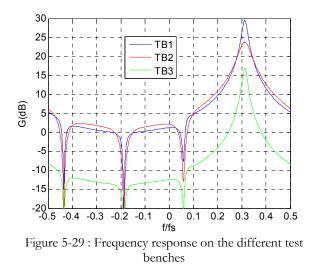

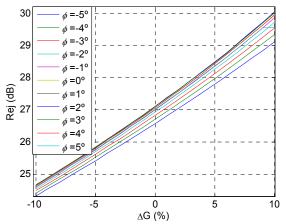

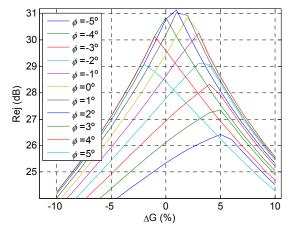

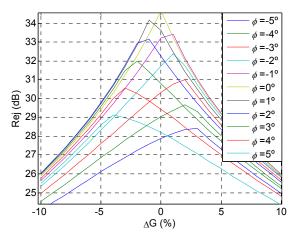

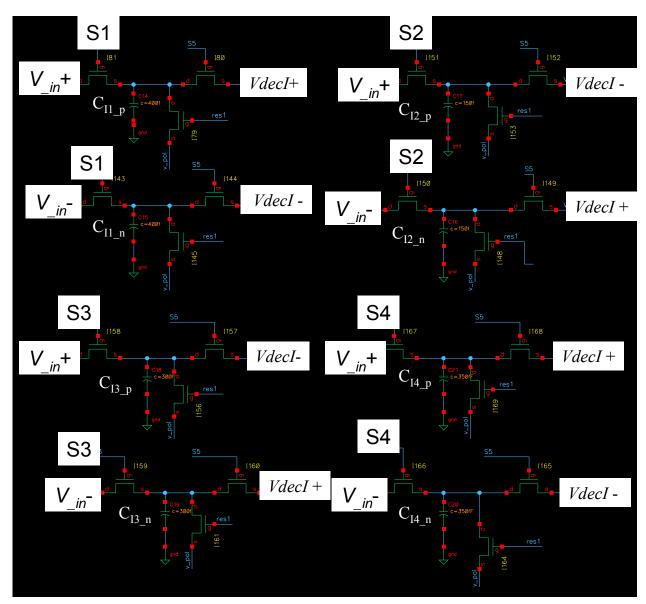

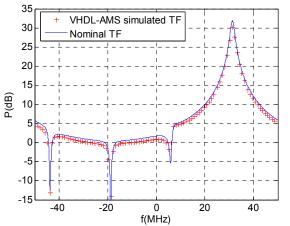

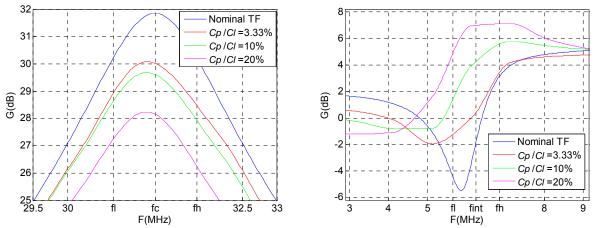

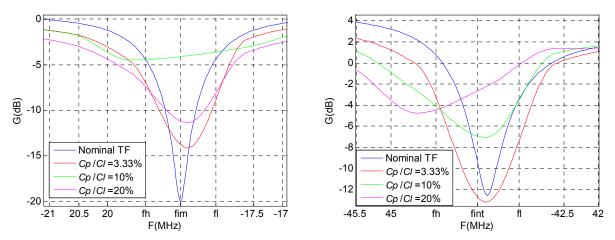

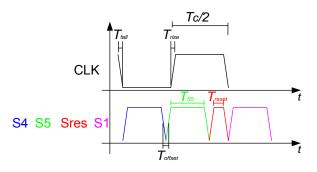

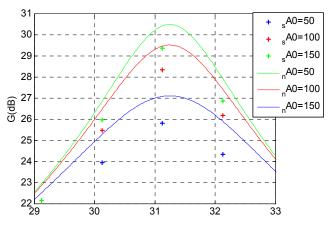

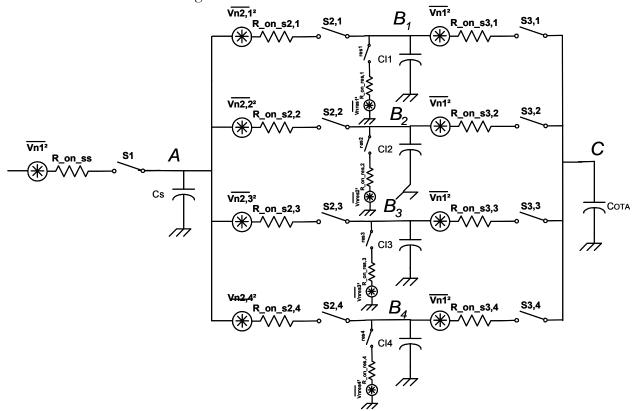

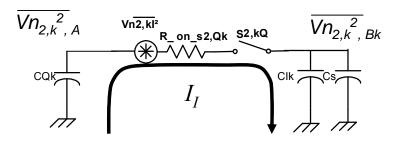

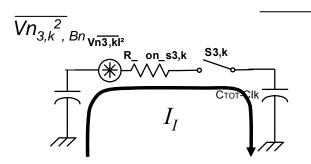

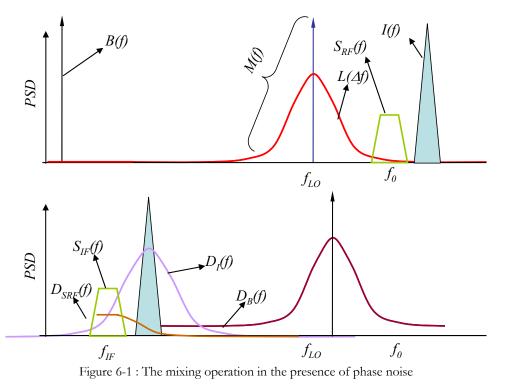

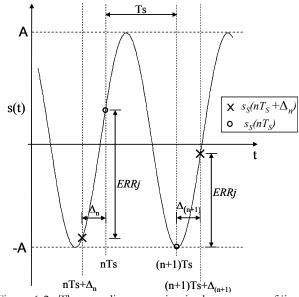

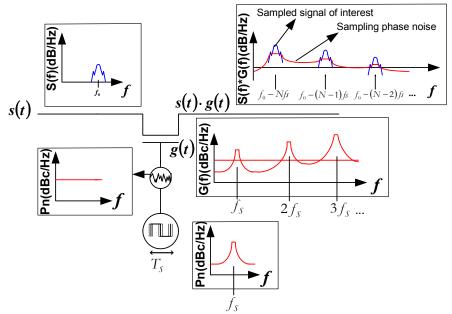

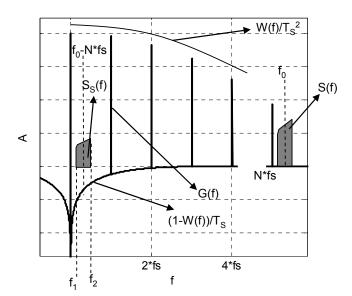

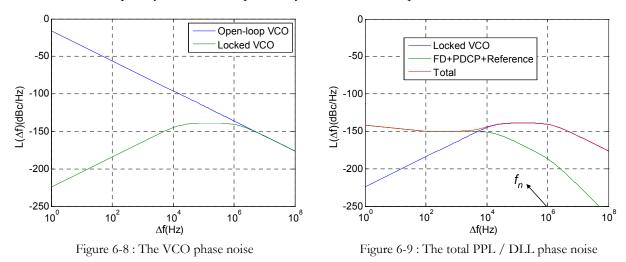

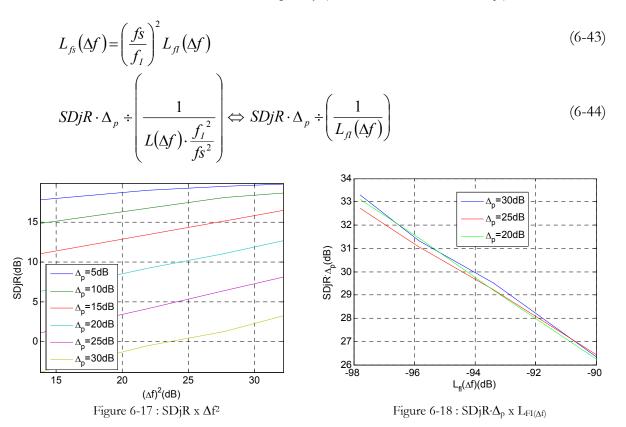

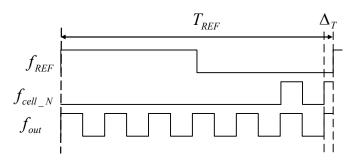

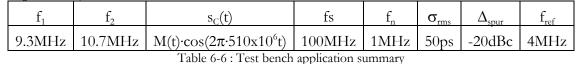

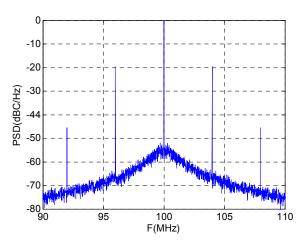

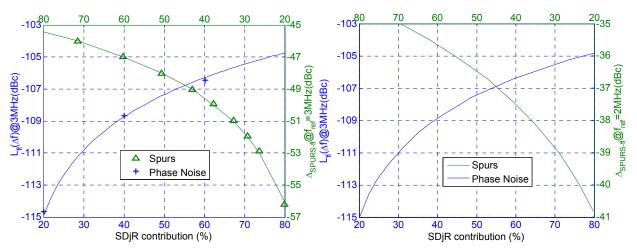

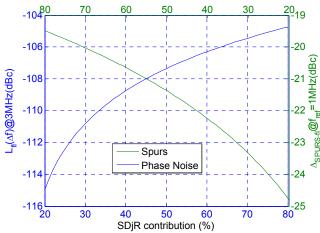

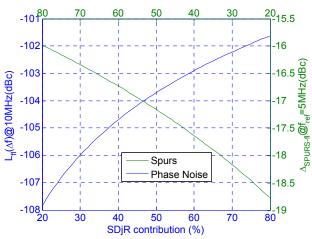

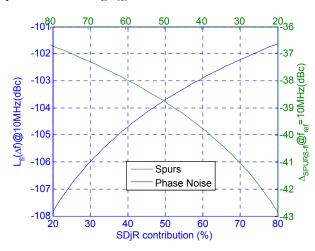

|------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------|------------------------------------------------------------------|--|