### Reconfigurable Logic Architectures based on Disruptive Technologies

Pierre-Emmanuel Gaillardon

#### ▶ To cite this version:

Pierre-Emmanuel Gaillardon. Reconfigurable Logic Architectures based on Disruptive Technologies. Other. Ecole Centrale de Lyon, 2011. English. NNT: 2011ECDL0027. tel-00674438

### HAL Id: tel-00674438 https://theses.hal.science/tel-00674438

Submitted on 27 Feb 2012

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° ordre : 2011-27

#### Thèse de l'Université de Lyon

Délivrée par l'Ecole Centrale de Lyon Spécialité : Dispositifs de l'Electronique Intégrée Soutenue publiquement le 15 Septembre 2011

par

#### M. Pierre-Emmanuel Gaillardon

Ingénieur CPE-Lyon

Master Recherche GEGP « Dispositifs de l'Electronique Intégrée »

Préparée au Laboratoire d'Intégration Silicium des Architectures Numériques (CEA-LETI-DACLE)

# Reconfigurable Logic Architectures based on Disruptive Technologies

Ecole Doctorale Electronique, Electrotechnique, Automatique

#### Composition du jury :

| M. A. Souifi,   | Professeur, INSA Lyon,                    | en qualité de Président  |

|-----------------|-------------------------------------------|--------------------------|

| M. S. Mitra,    | Associate Professor, Stanford University, | en qualité de Rapporteur |

| M. L. Torres,   | Professeur, Université Montpellier II,    | en qualité de Rapporteur |

| M. J.O. Klein,  | Professeur, Université Paris Sud,         | en qualité d'Examinateur |

| M. I. O'Connor, | Professeur, Ecole Centrale de Lyon,       | en qualité de Directeur  |

| M. F. Clermidy, | HDR, CEA-LETI,                            | en qualité d'Encadrant   |

## Acknowledgments

While this thesis is written in English, I feel nice to write most of these acknowledgments in French, as it will enforce my thanks.

Afin de débuter ces remerciements, je vous propose une petite anecdote. En fin d'année 2007, la veille de la fête des lumières, je me trouvais en entretien à l'Ecole Centrale de Lyon en vue d'une bourse de thèse. Je rencontrais ainsi deux personnes qui présentèrent chacun leurs travaux pendant 30 minutes. Autant dire qu'après cette heure de présentation (par deux ténors de la communication scientifique), je fis bien pâle figure lorsque je dus me présenter. A cette époque, je n'avais que pour seul arme la motivation. Près de 4 ans après, j'espère que ces deux personnes sont satisfaites du travail accompli. Pour ma part je le suis et ce fût un véritable honneur que d'avoir travaillé avec le **Professeur Ian O'Connor** et le **Docteur Fabien Clermidy**. Que dire à part vous remercier bien chaleureusement? Il y aurait évidemment trop à narrer mais je peux tout de même insister sur la patience de Ian pour ses nombreuses corrections orthographiques, la pleine maitrise du marketing de titre de Fabien et la pertinence de vos encadrements laissant une grande part à l'autonomie. Je ne parle même pas de vos qualités humaines tant de fois montrées jusqu'aux tréfonds de Gaslamp quarter.

Ces deux personnes sont les premières garantes de la pertinence de ce travail, mais une thèse ne serait rien sans un jury de grande qualité. Je tiens tout d'abord à remercier le **Professeur Lionel Torres** et le **Professeur Subhasish Mitra** pour avoir accepté de rapporter ce travail. Il en va de même pour le **Professeur Abdelkader Souifi** et le **Professeur Jacques-Olivier Klein** pour avoir accepté de l'examiner. It is my pleasure to have this thesis reviewed by such a significant board. Thank you very much for having accepted this charge.

Avant de remercier mes collaborateurs, je souhaiterais dédier un paragraphe à **Haykel Ben Jamaa**. Ce fût un réel plaisir que de travailler avec lui pendant la durée de son post-doc et après son embauche. Haykel est une personne de très grande qualité sur le plan professionnel et humain. J'ai énormément appris à ses côtés du point de vue de la technique, de la méthodologie (Haykel a toujours une idée en stock à creuser et toujours une solution à un problème!) et de la communication (Haykel est le roi de la publication!).

Cette thèse, de part les diverses technologies utilisées, a été le fruit de nombreuses collaborations internes comme externes. Sur le plan interne, j'ai eu grand plaisir à travailler avec les différentes équipes du LETI. Je remercierai ainsi Marina Reyboz pour sa gentillesse et son expertise dans les modèles compacts, Giovanni Betti Beneventi et Luca Perniola pour leur collaboration sur les mémoires à changement de phase, Perrine Batude pour son prometteur procédé 3-D monolithique, sa sympathie et sa salsa, Thierry Poiroux pour sa connaissance sur le graphene et sa gestion du projet SNOW, Paul-Henry Morel et Thomas Ernst pour leurs procédés à base de nanofils et leur ouverture d'esprit lors de chaque collaboration concepteurs/technologues, Gérald Cibrario et Marjorie Gary pour leur superbes DKs (Vive la PDK Team!), Karim Azizi Mourier le champion du terminal sans qui il ne serait pas possible d'avoir un tel environnement de CAD, Sigrid Thomas et Véronique Robert, nos chères ingénieurs brevets, toujours disponibles pour entendre une idée. Un grand merci également à Thomas Gauthier et à Houcine Oucheikh, les deux stagiaires d'école d'ingénieur que j'ai eu le plaisir de co-encadrer et qui ont réalisé un travail

appréciable. Dans le cadre du projet Nanograin, des collaborations ont été entretenues avec des partenaires tels que l'Institut des Nanotechnologies de Lyon et le Laboratoire de l'Intégration du Matériau au Système à Bordeaux. J'eus ainsi le grand plaisir de travailler avec Nataliya Yakymets, Kotb Jabeur, Sébastien Le Beux, Sébastien Frégonèse, Cristell Maneux et Thomas Zimmer. Je remercie également le Professeur Giovanni De Micheli, de l'Ecole Polytechnique Fédérale de Lausanne, pour m'avoir invité à donner un séminaire au sein de son groupe et proposé un poste de collaborateur scientifique. Je suis très heureux de pouvoir travailler au sein du LSI à compter de l'automne.

Je remercie également toutes les personnes que j'ai eu l'occasion de cottoyer pendant ces années de thèse, et tout particulièrement les membres de mon laboratoire : notre chef François Bertrand, les permanents Didier V., Christian, Denis, Fredéric, Jérôme, Olivier, Alexandre, Edith (A quand l'organisation d'une « special session » et d'un tutorial Salsa ?), Yvain, Pascal, Ivan, Sébastien, Romain, Didier L., Bastien et non permanents qui se sont succédés au sein du laboratoire, tout particulièrement mes amis Riadh, Imen, Pallavi, Santhosh, Rodolphe, Antoine, Bilel, Jean-Philippe et Maxime; les membres du laboratoire L3I et particulièrement Anaïs, Bertrand et Rémi; et du laboratoire LE2TH, particulièrement Cyril, Patrick, Stéphanie, Frédéric, Grégory et Hubert.

Toute cette belle organisation ne serait rien sans le devouement de l'administration. J'ai été heureux de mener ces travaux au sein du département DACLE sous la direction de Jean-René Lequepeys puis de Thierry Collette, mais également de profiter des conseils et de l'expérience de Marc Belleville et d'Ahmed Jerraya. Je remercie tout particulièrement Armelle et Caroline, nos adjointes de direction qui sont de vraies fées.

Durant ces années de thèse, j'ai eu l'opportunité d'effectuer des enseignements au sein de l'école d'ingénieur CPE Lyon, mais également au sein des classes préparatoires CPE. Je remercie ainsi Nacer Abouchi, Evelyne Steffen, François Bois, Thierry Tixier, François Joly et Renaud Daviot pour m'avoir proposé ces enseignements. Je remercie également Tahar Limane et Jean-Marie Becker toujours disponibles pour répondre à des questions théoriques.

Sortant à présent du cadre purement institutionnel, je voudrais faire une place de choix à **Sophie** pour avoir relu une grande partie de ce manuscrit. Merci Doudou! Je crois que l'un comme l'autre, nous souhaitons également en profiter pour remercier et féliciter les Le Bars pour leur mariage (③).

J'aimerai également remercier mes amis plongeurs Grenoblois. Arrivé en thèse comme simple plongeur, j'ai mis à profit ces quelques années pour évoluer jusqu'au monitorat. Ce fût très agréable d'appartenir au « Subatomic » où je salue mes amis **Jean-Benoit**, **Frédéric**, **Jean-Louis**, **Sylvain**, **Hervé**, **Sandrine**, **Laetitia**, **Jean-Christophe** et tous les autes. Je remercie également tous mes MF2 préférés pour m'avoir mené jusqu'au MF1 : **Corinne**, **Sébastien**, **Fabien** et **Pascal**. C'est toujours un grand plaisir de partager quelques moments sous l'eau avec vous tous.

L'occasion est bonne également pour saluer mes amis qui subissent toujours indirectement les affres de la thèse. Je remercie tout particulièrement la Oufff Team pour avoir assuré le robot en plein dans ma période de rédaction. Merci donc à **Cyril**, **Philippe**, **Anne-Sophie** et **Rémi**. Merci tout particulièrement à **Cyril** car lui plus que les autres a subi un grand nombre de fois mes retards pour cause de publication ou de manuscrit à terminer.

Enfin, je remercie ma famille pour tout le soutien qu'ils m'apportent. Toujours présents, j'espère leur apporter un peu de fierté (La pallette de Champagne parle d'elle-même!) en compensation de tout ce qu'ils font pour moi. Merci **Maman**, **Papa**, **Pépé**, **Tonton F**, **Tatie D**, **Tonton J**, **Tatie V** et **Zouzine**. Je pense également fort à mes deux grand-mères au moment d'écrire ces lignes.

## Table of Contents

| CHAPTER 1 | Introduction                                  | 1  |

|-----------|-----------------------------------------------|----|

| 1.1 The S | Scaling Era                                   | 1  |

| 1.2 New   | Challenges                                    | 3  |

| 1.2.1 P   | Process Integration and Devices               | 3  |

| 1.2.2 S   | Systems and Tools                             | 4  |

| 1.3 Archi | tectural and Technological Opportunities      | 4  |

| 1.3.1 F   | Reconfigurable Architectures                  | 5  |

| 1.3.2 T   | Technological Evolutions                      | 5  |

| 1.3.2.1   | MOS Extensions                                | 6  |

| 1.3.2.2   | Emerging Devices and Memories                 | 6  |

| 1.4 The N | Nanoscale Chicken and Egg Dilemma             | 6  |

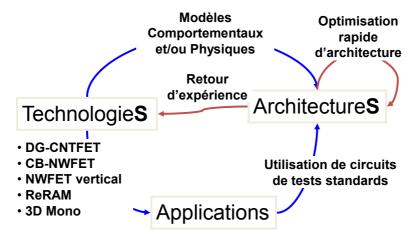

| 1.5 Work  | Methodology                                   | 7  |

| 1.6 Resea | arch Contributions                            | 8  |

| 1.6.1 N   | Methodology and Tools                         | 8  |

| 1.6.2 N   | Memories and Routing Resources for FPGA       | 9  |

| 1.6.3 L   | Logic Blocks for FPGA                         | 9  |

| 1.6.4 N   | Nanoscale Architectures                       | 10 |

| 1.7 Organ | nization of the Thesis                        | 10 |

| CHAPTER 2 | Background and Motivation                     | 13 |

| 2.1 Conv  | entional Reconfigurable Architecture Overview | 14 |

| 2.1.1 T   | The FPGA Architecture                         | 14 |

| 2.1.1.1   | Generalities                                  | 14 |

| 2.1.1.2   | General Architectural organization            | 15 |

| 2.1.1.3   | Logic Block Architecture                      | 16 |

| 2.1.1.4   | Routing Architecture                          | 18 |

| 2.1.1.5   | Architectural Parameterization and Optimum    | 19 |

| 2.1.2 N   | Market Trends                                 | 20 |

| 2.1.2.1   | Increase of the CLBs Complexity               | 20 |

| 2.1.2.2   | Transition from Homogeneity to Heterogeneity  | 21 |

| 2.1.2.3   | Non-Volatility Features                       | 22 |

| 2.1.3 Limitations of FPGAs                                         | 23 |

|--------------------------------------------------------------------|----|

| 2.2 Emerging Reconfigurable Architectures Overview                 | 24 |

| 2.2.2 Morphic Approach                                             | 24 |

| 2.2.3 Heterogeneous Approach                                       | 25 |

| 2.2.3.1 Regular Architectures                                      | 25 |

| 2.2.3.2 Enhanced Reconfigurable Architectures                      | 27 |

| 2.2.4 Global Comparisons and Discussions                           | 28 |

| 2.3 Architectural Formalization and Template                       | 29 |

| 2.3.1 Global Statement                                             | 29 |

| 2.3.2 Generic Architectural Template                               | 30 |

| 2.4 Conclusion and Work Position                                   | 31 |

| CHAPTER 3 Innovative Structures for Routing and Configuration      | 33 |

| 3.1 Context and Objectives                                         | 34 |

| 3.1.1 Context Position                                             | 34 |

| 3.1.2 Objectives                                                   | 35 |

| 3.2 Proposal 1: Resistive memory technologies                      | 35 |

| 3.2.1 Introduction                                                 | 35 |

| 3.2.2 Phase Change Memory Properties and Technological Assumptions | 36 |

| 3.2.2.1 Physical Phenomena                                         | 36 |

| 3.2.2.2 Technological Assumptions                                  | 37 |

| 3.2.2.3 Opportunities                                              | 37 |

| 3.2.3 Elementary Memory Node                                       | 38 |

| 3.2.3.1 Concept                                                    | 38 |

| 3.2.3.2 Programming Circuitry                                      | 39 |

| 3.2.3.3 N-ary Logic Generalization                                 | 40 |

| 3.2.3.4 Technological Integration Opportunities                    | 40 |

| 3.2.4 Routing Elements                                             | 41 |

| 3.2.4.1 Concept                                                    | 42 |

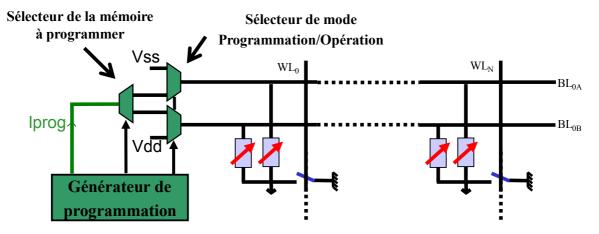

| 3.2.4.2 Programming Circuitry                                      | 42 |

| 3.2.5 Functional validation and performance characterization       | 43 |

| 3.2.5.1 Methodology                                                | 43 |

| 3.2.5.2 Compact Modeling                                           | 43 |

| 3.2.5.3 Transient Simulations                                      | 44 |

| 3.2.5.4 Performance Estimation                                     | 45 |

| 3.2.5.5 Discussion                                                 | 47 |

| 3.3 Proposal 2: Monolithic 3-D Integration Process                 | 48 |

| 3.3.1 Introduction                                                 | 48 |

| 3 3 2 Technological Assumptions                                    | 49 |

|   | 3.3.3 El    | ementary Blocks                                               | 50 |

|---|-------------|---------------------------------------------------------------|----|

|   | 3.3.3.1     | 3-D Memory                                                    | 51 |

|   | 3.3.3.2     | LUT Impact                                                    | 51 |

|   | 3.3.3.3     | Routing Structure Impact                                      | 51 |

|   | 3.3.4 Pe    | erformance Characterization                                   | 54 |

|   | 3.3.4.1     | Methodology                                                   | 54 |

|   | 3.3.4.2     | SRAM Configuration Performance                                | 54 |

|   | 3.3.4.3     | LUT Performance                                               | 55 |

|   | 3.3.4.4     | Cross point Performance                                       | 55 |

|   | 3.3.4.5     | Comments                                                      | 56 |

|   | 3.4 Propos  | sal 3: Vertical Silicon Nanowire FET Process                  | 56 |

|   | 3.4.1 In    | troduction                                                    | 56 |

|   | 3.4.2 Te    | echnological Assumptions                                      | 57 |

|   | 3.4.3 V     | ertical 3-D Logic                                             | 58 |

|   | 3.4.3.1     | Smart Vias                                                    | 58 |

|   | 3.4.3.2     | Logic Gates                                                   | 58 |

|   | 3.4.3.3     | SRAMs                                                         | 59 |

|   | 3.4.4 Pe    | erformance Characterization                                   | 60 |

|   | 3.4.4.1     | Methodology                                                   | 60 |

|   | 3.4.4.2     | Device Characterization                                       | 61 |

|   | 3.4.4.3     | NOT Gate Characterization                                     | 62 |

|   | 3.4.4.4     | Discussion                                                    | 63 |

|   | 3.5 Global  | Comparisons and Discussions                                   | 63 |

|   | 3.6 Conclu  | asion                                                         | 64 |

| C | HAPTER 4    | Architectural Impact of 3-D Configuration and Routing Schemes | 67 |

|   | 4.1 Motiva  | ation and Global Methodology                                  | 68 |

|   | 4.2 Bench   | marking Tool for FPGA-like Architectures                      | 68 |

|   | 4.3 Resisti | ve Memory-based FPGA Performance                              | 69 |

|   | 4.3.1 PC    | CM-FPGA Architecture                                          | 69 |

|   | 4.3.2 M     | ethodology                                                    | 70 |

|   | 4.3.3 Si    | mulation of Large Circuits                                    | 70 |

|   | 4.3.3.1     | Impact on the Routing Structures                              | 71 |

|   | 4.3.3.2     | Impact on the Configuration Memories                          | 71 |

|   | 4.3.4 In    | npact of Technologies                                         | 71 |

|   | 4.3.5 Di    | iscussion                                                     | 72 |

|   | 4.4 3-D M   | onolithic Integrated FPGA Performances                        | 73 |

|   | 4.4.1 O     | verall FPGA Architectural View                                | 73 |

|   | 4.4.2 M     | ethodology                                                    | 73 |

|   |             |                                                               |    |

| 4.4.3     | Simulation of Large Circuits                             | 74 |

|-----------|----------------------------------------------------------|----|

| 4.4.3.1   | Monolithic 3-D Integration Impact on Global Area         | 74 |

| 4.4.3.2   | Monolithic 3-D Integration Impact on Critical Path Delay | 74 |

| 4.4.4 I   | Discussion                                               | 75 |

| 4.5 Verti | cal NWFETs-based FPGA Performances                       | 75 |

| 4.5.1 F   | Real 3-D Routing for FPGAs                               | 75 |

| 4.5.2 N   | Methodology                                              | 76 |

| 4.5.3 S   | Simulation of Large Circuits                             | 76 |

| 4.5.4 I   | Discussions                                              | 77 |

| 4.6 Discu | ssion                                                    | 77 |

| 4.7 Conc  | lusion                                                   | 78 |

| CHAPTER 5 | Disruptive Logic Blocks                                  | 81 |

| 5.1 Conte | ext and Objectives                                       | 82 |

| 5.2 Propo | osal 1: Ambipolar Carbon Electronics                     | 83 |

| 5.2.1 I   | ntroduction                                              | 83 |

| 5.2.2     | CNT-based Devices Properties and Opportunities           | 84 |

| 5.2.3 T   | Technological Assumptions and Device Modeling            | 86 |

| 5.2.3.1   | Process Flow and Layout Proposal                         | 86 |

| 5.2.3.2   | DG-CNFET Compact Model                                   | 87 |

| 5.2.3.3   | Process Tuning                                           | 87 |

| 5.2.4 H   | Functionality improvement : In-Field Reconfigurability   | 88 |

| 5.2.5 H   | Performance Evaluation                                   | 89 |

| 5.2.5.1   | DG-CNFET Evaluation Methodology                          | 89 |

| 5.2.5.2   | Silicon CMOS Performance Evaluation Methodology          | 90 |

| 5.2.5.3   | Simulation Results                                       | 91 |

| 5.2.6 I   | Dynamic Logic Circuit Improvement                        | 93 |

| 5.2.6.1   | Concept                                                  | 93 |

| 5.2.6.2   | Buffer Cell Illustration                                 | 93 |

| 5.2.6.3   | Density Improvement Example                              | 94 |

| 5.2.7 I   | Discussion                                               | 94 |

| 5.3 Propo | osal 2: 1-D Silicon Crossbars                            | 95 |

| 5.3.1 I   | ntroduction                                              | 95 |

| 5.3.2 T   | Sechnological Assumptions                                | 96 |

| 5.3.3     | SiNWFET Configurable Logic Cell                          | 96 |

| 5.3.3.1   | Nanowire Crossbar Logic                                  | 96 |

| 5.3.3.2   | Multiplexer Design Methodology                           | 97 |

| 5.3.3.3   | Layout Design                                            | 98 |

| 5.3.4 H   | Performance Evaluations                                  | 99 |

| 5.3.    | 4.1 Methodology                                                  | 99      |

|---------|------------------------------------------------------------------|---------|

| 5.3.    | 4.2 Electrical Simulations                                       | 99      |

| 5.3.    | 4.3 Discussion                                                   | 100     |

| 5.4 Pr  | oposal 3: Lithographic Crossbars                                 | 101     |

| 5.4.1   | Introduction                                                     | 101     |

| 5.4.2   | Technological Assumptions                                        | 101     |

| 5.4.3   | Logic Design Methodology                                         | 102     |

| 5.4.    | 3.1 Inverter construction                                        | 102     |

| 5.4.    | 3.2 Generalization to complex logic circuits                     | 102     |

| 5.4.4   | Performance Evaluation                                           | 103     |

| 5.4.    | 4.1 Methodology                                                  | 103     |

| 5.4.    | 4.2 Performance Estimations with Parasitic-Free Circuits         | 104     |

| 5.4.    | 4.3 Impact of the Width of Horizontal Wires Including Parasition | cs 106  |

| 5.4.    | 4.4 Impact of the Parasitic Capacitances                         | 106     |

| 5.4.    | 4.5 Impact of Scaling Including Parasitics                       | 107     |

| 5.4.    | 4.6 Performance Estimations including Parasitics                 | 108     |

| 5.4.    | 4.7 Discussion and Guidelines                                    | 108     |

| 5.5 G   | lobal Comparisons                                                | 110     |

| 5.6 Co  | onclusion                                                        | 110     |

| CHAPTER | Disruptive Architectural Proposals and Performance Analyst       | sis 113 |

| 6.1 In  | troduction                                                       | 114     |

| 6.2 A   | rchitectural Proposals                                           | 115     |

| 6.2.1   | Introduction                                                     | 115     |

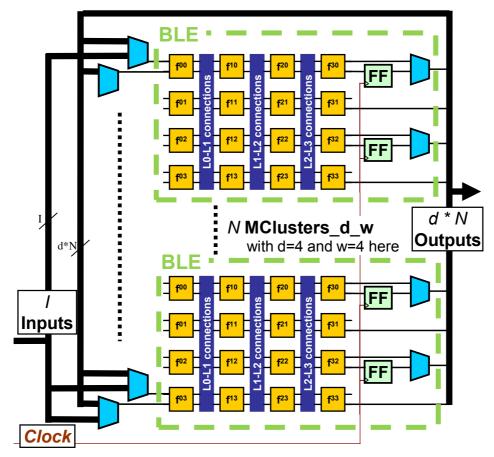

| 6.2.2   | MCluster Organization                                            | 115     |

| 6.2.    | 2.1 MCluster: Adding a "Logic Layer"                             | 115     |

| 6.2.    | 2.2 MCluster: Simplifying the Interconnect Overhead              | 116     |

| 6.2.3   | BLE and CLB organization                                         | 117     |

| 6.2.4   | FPGA Final Organization                                          | 117     |

| 6.3 Be  | enchmarking Tool                                                 | 118     |

| 6.3.1   | General Overview of the Flow                                     | 119     |

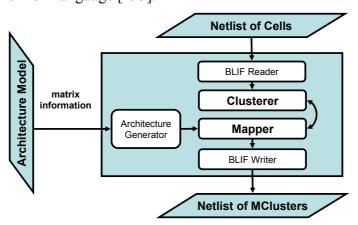

| 6.3.2   | MPACK: Matrix PACKer                                             | 120     |

| 6.3.    | 2.1 Concept                                                      | 121     |

| 6.3.    | 2.2 Mapping Algorithm : Architectural Optimization               | 121     |

| 6.3.    | 2.3 Mapping Algorithm : Brute-Force Mapper                       | 124     |

| 6.3.    | 2.4 Clustering Algorithm                                         | 126     |

| 6.4 Ev  | valuation of Fixed Interconnect Topologies                       | 127     |

| 6.4.1   | Methodology                                                      | 128     |

| 642     | Packing Success Rate                                             | 128     |

| 6.4.3        | Fault Tolerance                                          | 129    |

|--------------|----------------------------------------------------------|--------|

| 6.4.         | 3.1 Physical Origin of Defects at Nanoscale              | 129    |

| 6.4.         | 3.2 Analysis Protocol and Results                        | 129    |

| 6.4.4        | Average Interconnect Length                              | 130    |

| 6.4.5        | Discussion                                               | 131    |

| 6.5 Gl       | obal Architecture Evaluations                            | 131    |

| 6.5.1        | Methodology                                              | 131    |

| 6.5.2        | Evaluation Results                                       | 131    |

| 6.5.         | 2.1 Impact of the Granularity                            | 131    |

| 6.5.         | 2.2 Impact of Latch Depopulation                         | 132    |

| 6.5.         | 2.3 Performance Comparison with CMOS                     | 133    |

| 6.5.3        | Discussion                                               | 134    |

| 6.6 Co       | onclusion                                                | 137    |

| CHAPTER      | Conclusions and Future Work                              | 139    |

| 7.1 Gl       | obal Comparison                                          | 139    |

| 7.2 Co       | onclusions and Contributions                             | 140    |

| 7.2.1        | Global Conclusions                                       | 140    |

| 7.2.2        | Contributions to Methodology and Tools                   | 141    |

| 7.2.3        | Contributions to Memories and Routing Resources for FPGA | 141    |

| 7.2.4        | Contributions to Logic Blocks for FPGA                   | 142    |

| 7.2.5        | Contributions to Architectures                           | 143    |

| 7.3 Fu       | iture Work                                               | 143    |

| 7.3.1        | Design Generalization and Technology Heterogeneity       | 143    |

| 7.3.2        | Fault Tolerance                                          | 144    |

| References   |                                                          | i      |

| List of Publ | lications                                                | XV     |

| List of Acro | onyms                                                    | xvii   |

| APPENDE      | Memento of Presented Technologies                        | xxi    |

| APPENDIX     | Résumé Etendu                                            | xxxiii |

## List of Figures

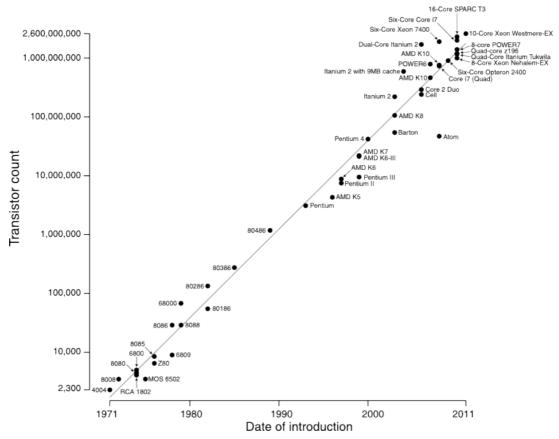

| Figure 1.  | Processor transistor count and Moore's Law since 1971 [4]                                                                                    | 2    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|

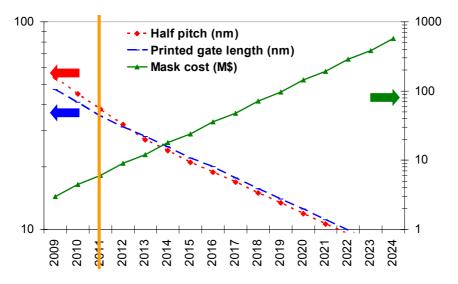

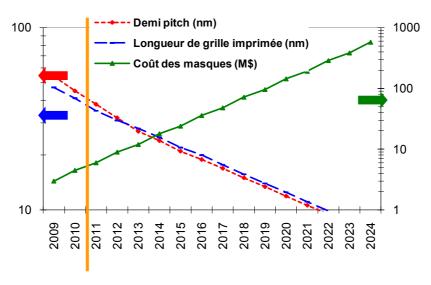

| Figure 2.  | Projected evolution of dimensions and mask cost [6]                                                                                          | 3    |

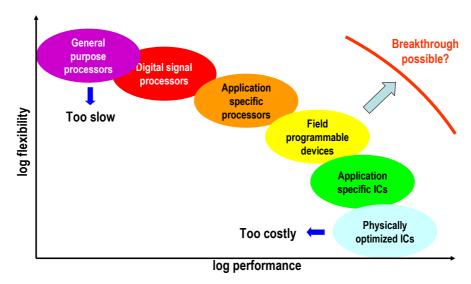

| Figure 3.  | Spectrum of implementation solutions for data processing algorithms                                                                          |      |

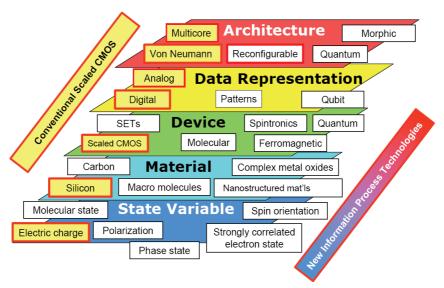

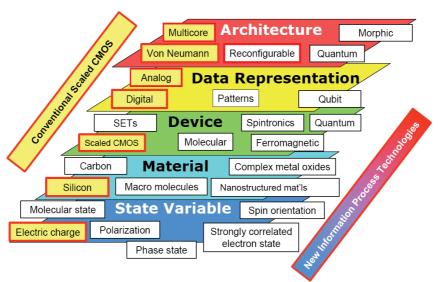

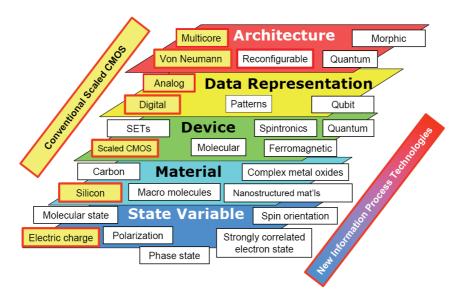

| Figure 4.  | Electronic systems hierarchical organization and opportunities [7]                                                                           | 6    |

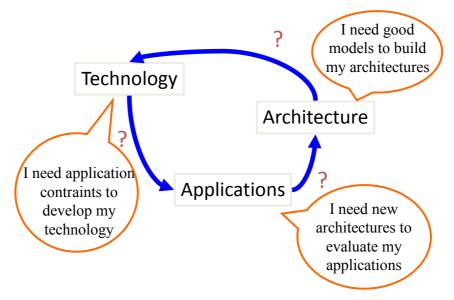

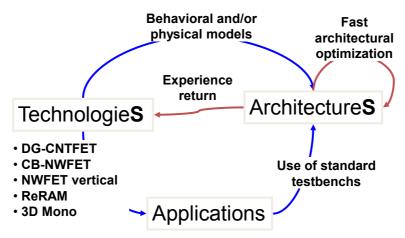

| Figure 5.  | The Chicken and Egg Dilemma of the disruptive technology                                                                                     |      |

| Figure 6.  | Template based Fast Evaluation methodology                                                                                                   |      |

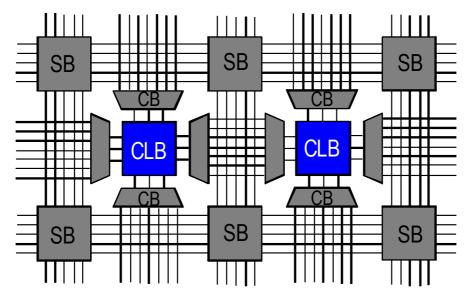

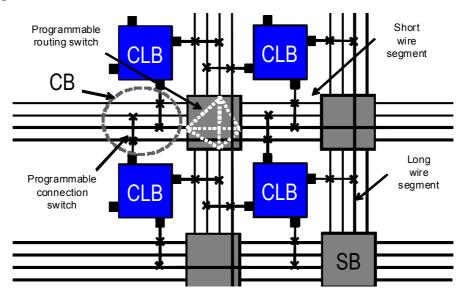

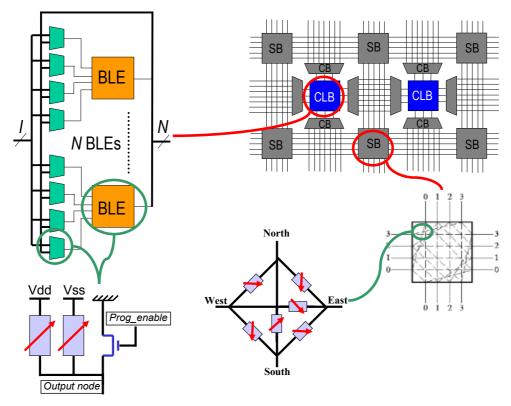

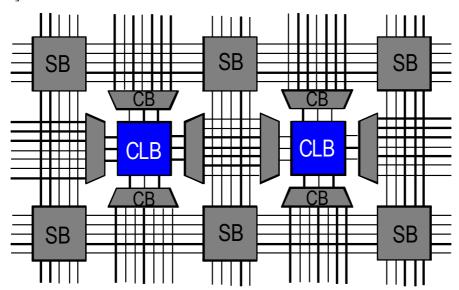

| Figure 7.  | Island-style Field Programmable Gate Array organization                                                                                      |      |

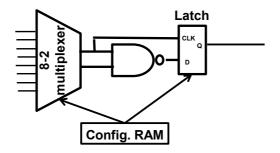

| Figure 8.  | Transistor-level programmability for FPGA [13]                                                                                               | . 16 |

| Figure 9.  | Simple gate FPGA logic block [14]                                                                                                            | . 17 |

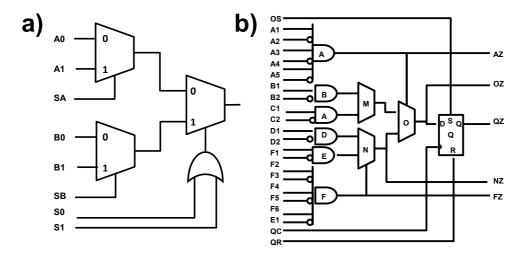

| Figure 10. | Complex gate FPGA logic blocks – a) Actel Act-1 LB [15] b) Quicklogic pASIC1 LB [16]                                                         | . 17 |

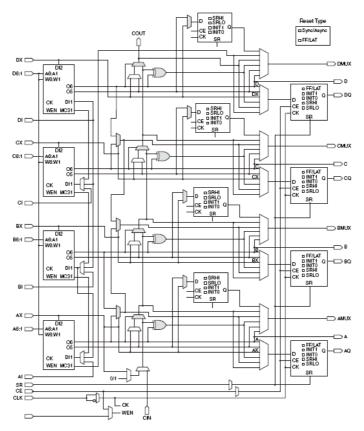

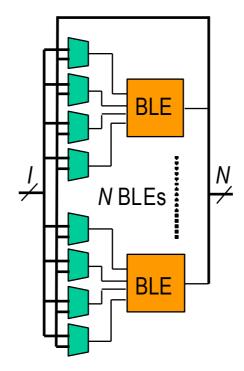

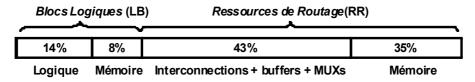

| Figure 11. | Configurable Logic Block architecture [17]                                                                                                   | . 18 |

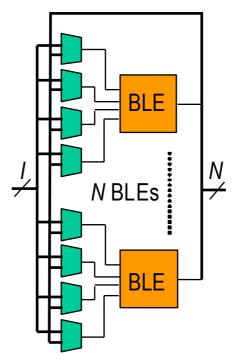

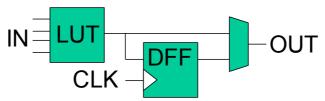

| Figure 12. | Basic Logic Element architecture [17]                                                                                                        |      |

| Figure 13. | Details on the routing organization in an island-style FPGA [17]                                                                             |      |

| Figure 14. | Virtex-6 logic block [20]                                                                                                                    | . 21 |

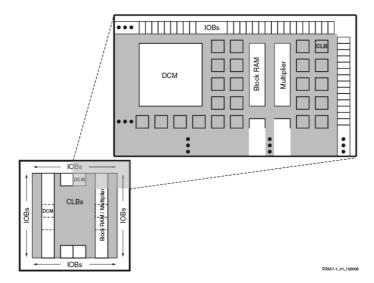

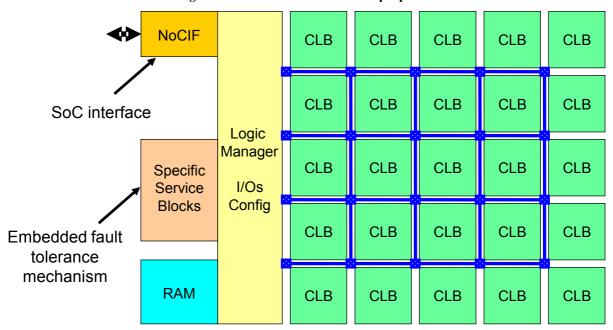

| Figure 15. | Xilinx Spartan-3A architecture organization [31]                                                                                             | . 22 |

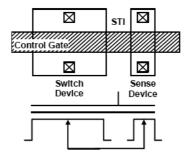

| Figure 16. | Schematic of a merged programming-data path floating gate transistor [35]                                                                    | . 23 |

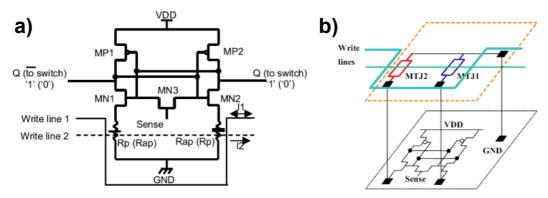

| Figure 17. | Magnetic Tunnel Junction unbalanced flip flop (a) and associated above IC structure (b) [37]                                                 | . 23 |

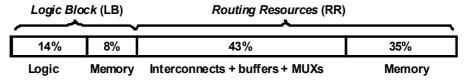

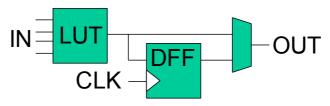

| Figure 18. | Field Programmable Gate Arrays area repartition per block [38]                                                                               |      |

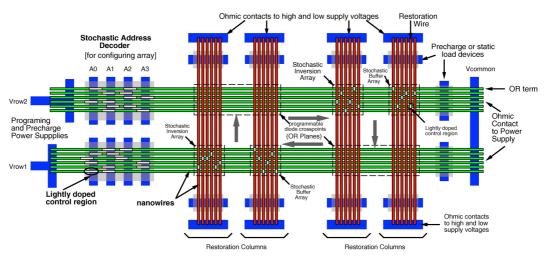

| Figure 19. | NanoPLA architecture [154]                                                                                                                   |      |

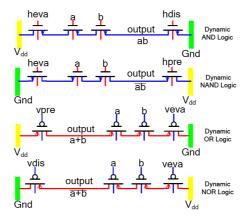

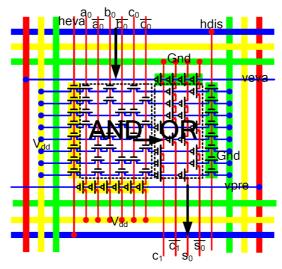

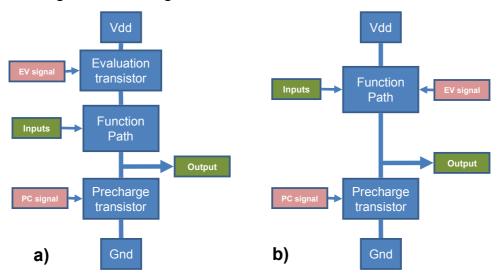

| Figure 20. | Dynamic logic implementation of AND, NAND, OR and NOR functions [65]                                                                         | . 26 |

| Figure 21. | NASIC structure (implementing a 1-bit adder) [65]                                                                                            |      |

| Figure 22. | Structure of the programmable NWFET (a), associated characterization (b) and nanowire-nanowire coupled multigate device (c) [50]             |      |

| Figure 23. | XOR function example built with four ambipolar transistors [52]                                                                              |      |

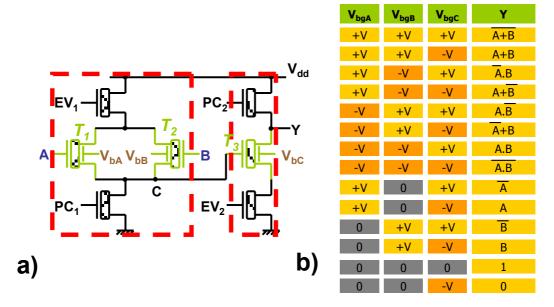

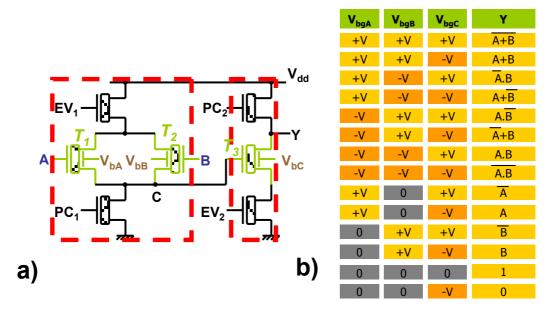

| Figure 24. | a) Transistor level schematic and b) configuration table for CNT reconfigurable cell [122]                                                   |      |

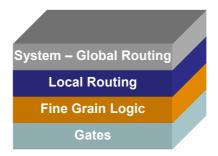

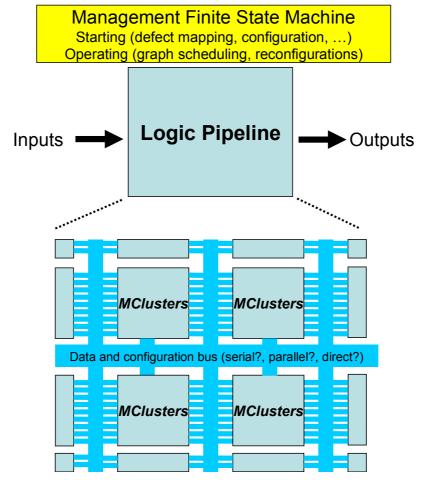

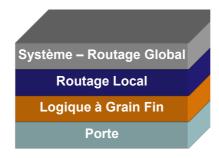

| Figure 25. | Layered organization of the generic template architecture                                                                                    |      |

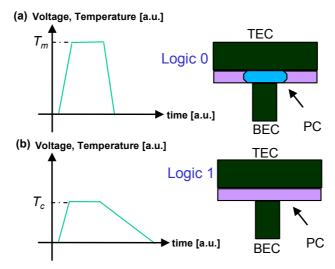

| Figure 26. | Schematic of PCM device in Logic 0 (named RESET) and Logic 1 (named SET) configurations and of the programming pulses suitable to obtain the |      |

|            | states.                                                                                                                                      | . 37 |

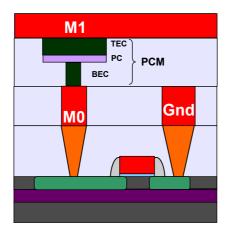

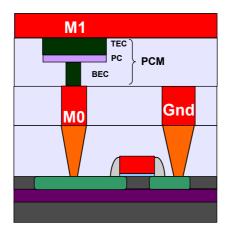

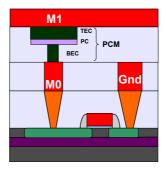

| Figure 27. | Cross sectional schematic showing a PCM device integration.                                                                                  | . 38 |

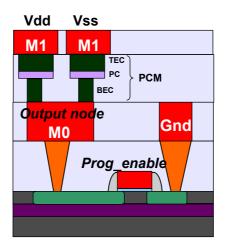

| Figure 28. | Logic-in-PCM elementary memory node                                                                                                          | . 38 |

| Figure 29. | Node in read configuration                                                                                                                   | . 39 |

| Figure 30. | Node in write configuration                                                                                                                  | . 39 |

| Figure 31. | Line sharing illustration in standalone-memory-like architecture                                                                             | . 40 |

| Figure 32. | Ternary logic node based on PCMs                                                                                                                                     | . 40 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 33. | Cross-sectional view of the memory node using standard process integration                                                                                           | . 41 |

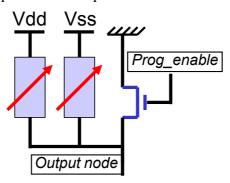

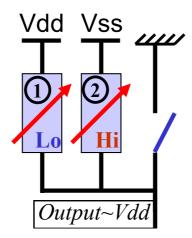

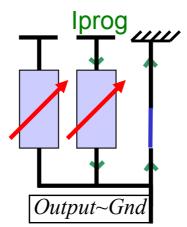

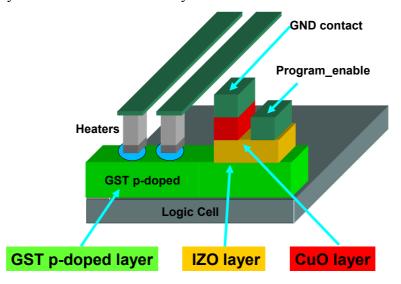

| Figure 34. | Full Back-End integration illustration of the PCM-based memory node using an oxide BJT                                                                               | . 41 |

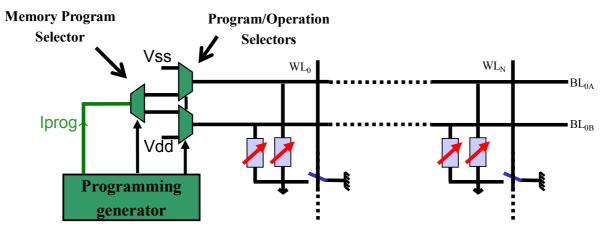

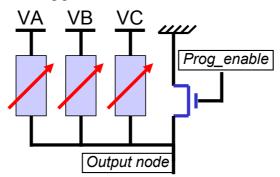

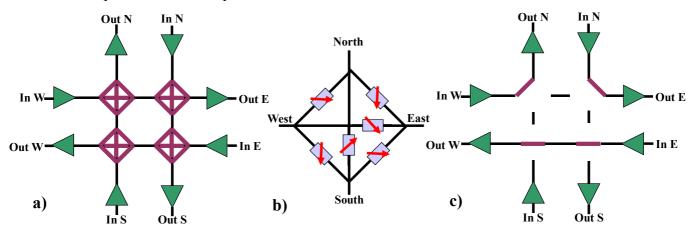

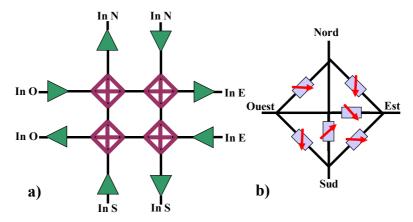

| Figure 35. | (a) PCM-based 2x2 switchbox architecture (b) zoom on the cross point structure (c) example of programmed switchbox (memories in off-state are not shown for clarity) | . 42 |

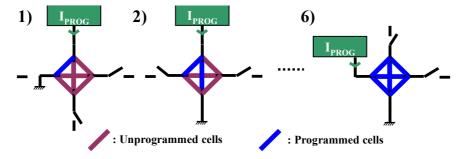

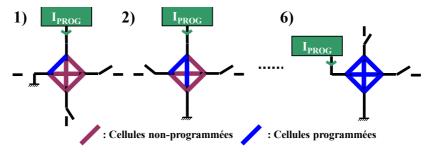

| Figure 36. | Example of switchbox programming sequence                                                                                                                            | . 43 |

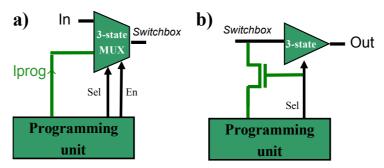

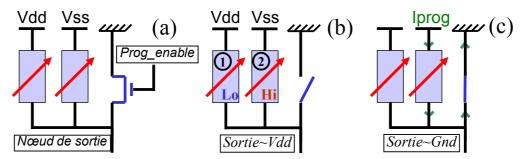

| Figure 37. | Input (a) and output (b) drivers for PCM-based crossbar                                                                                                              |      |

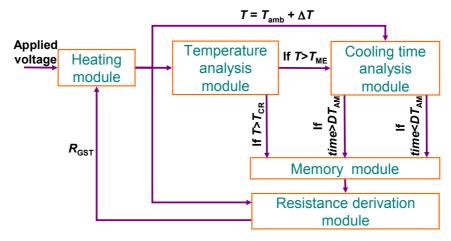

| Figure 38. | Synopsis of the behavioural model with the five modules                                                                                                              | . 44 |

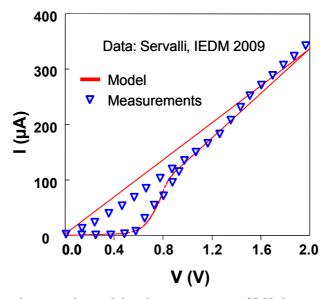

| Figure 39. | Comparison between the model and measurements of I-V characteristics of the amorphous and crystalline phases of a PCM cell.                                          |      |

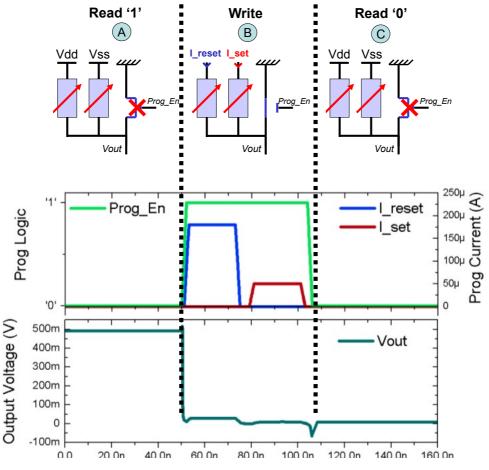

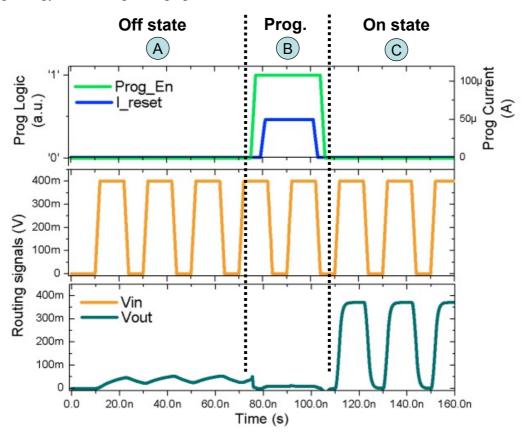

| Figure 40. | Binary memory node transient simulation                                                                                                                              | . 45 |

| Figure 41. | Elementary routing element transient validation simulation                                                                                                           | . 46 |

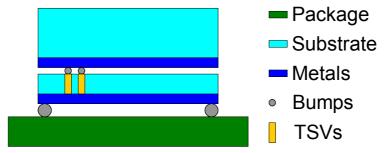

| Figure 42. | TSVs-based die stacking cross-sectional view                                                                                                                         | . 48 |

| Figure 43. | Cross-sectional view of 3-D parallel integration (left) and 3-D monolithic sequential integration (right)                                                            | . 49 |

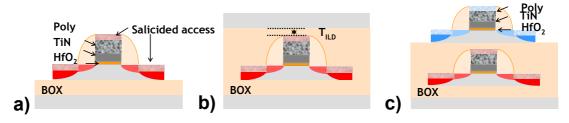

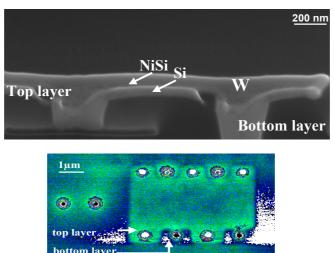

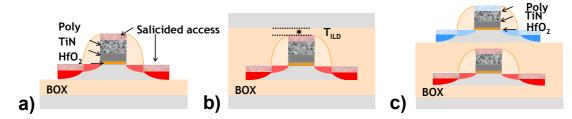

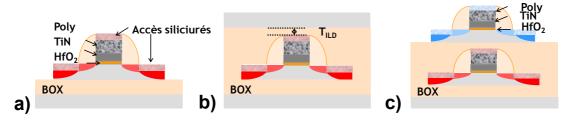

| Figure 44. | Cross-sectional view of 3-D monolithic steps – a) optimized bottom FDSOI process b) high quality top film deposition c) low temperature top FDSOI process            | . 50 |

| Figure 45. | Contacts between metal layer and top/bottom layers [97]                                                                                                              | . 50 |

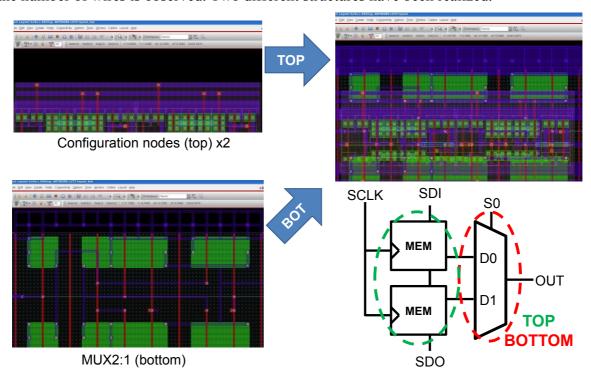

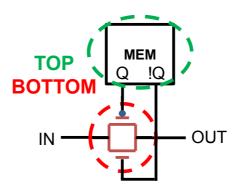

| Figure 46. | 3-D memory for reconfigurable logic – a) schematic b) layout on top levels                                                                                           | . 51 |

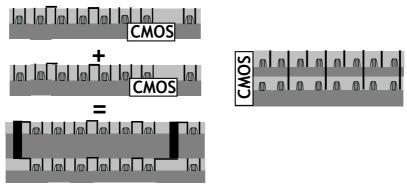

| Figure 47. | Two layer monolithic 3-D based 1bit Look-Up Table – layout and schematic                                                                                             | . 52 |

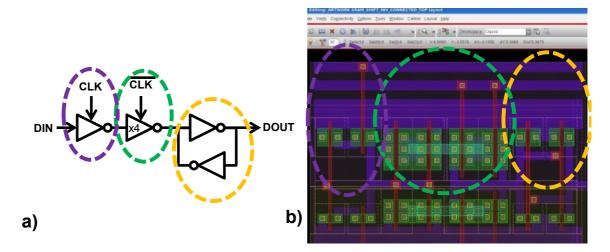

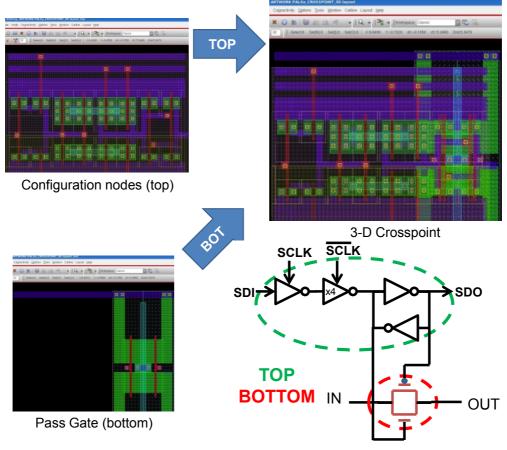

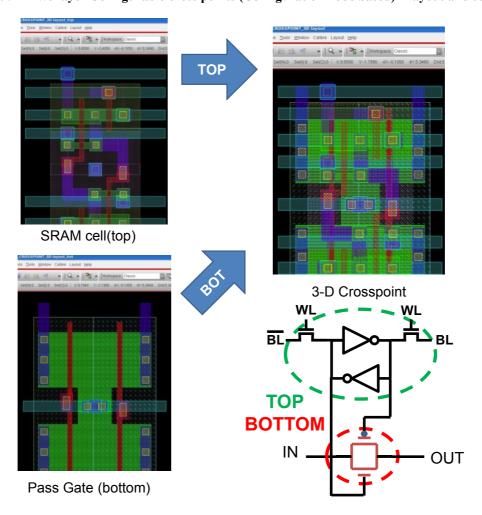

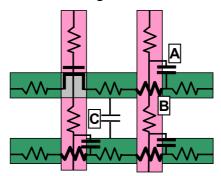

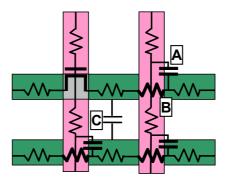

| Figure 48. | Cross point schematic                                                                                                                                                | . 52 |

| Figure 49. | Two layer Configurable cross points (Configuration node based) – layout and schematic                                                                                | . 53 |

| Figure 50. | Two layer Configurable cross points (SRAM cell based) – layout and schematic                                                                                         | . 53 |

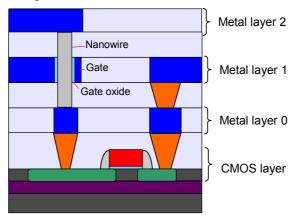

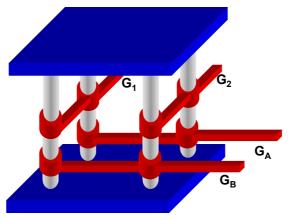

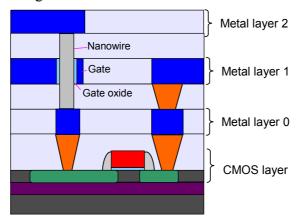

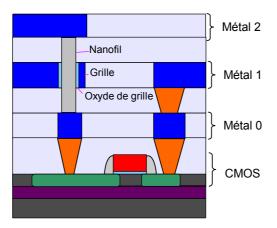

| Figure 51. | Cross sectional schematic showing a BEOL FET and standard CMOS FET co-integration                                                                                    |      |

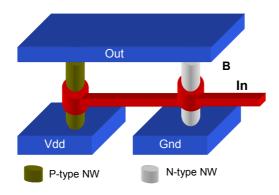

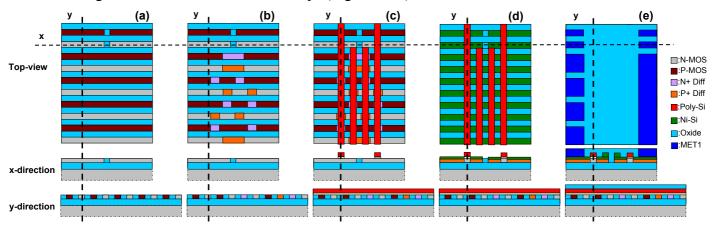

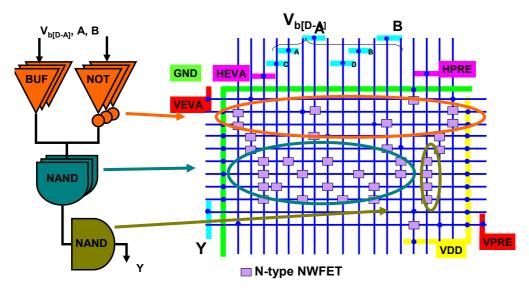

| Figure 52. | Boolean logic with vertical FETs                                                                                                                                     | . 58 |

| Figure 53. | NOT function implemented in a 3-D standard cell                                                                                                                      | . 59 |

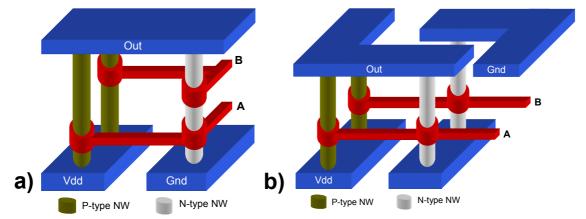

| Figure 54. | NAND function implemented in a 3-D standard cell – a) layout on two gate levels b) layout with only one gate per nanowire                                            | . 59 |

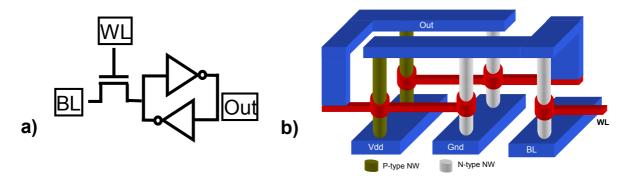

| Figure 55. | 5T SRAM cell implemented in a 3-D standard cell – a) schematic b) cross view                                                                                         | . 60 |

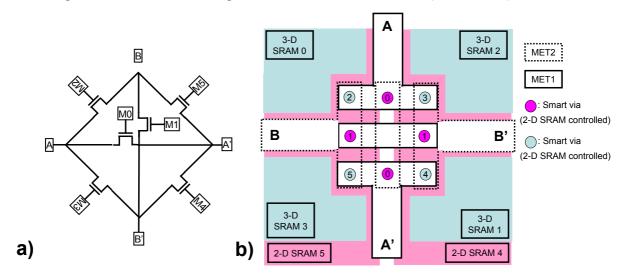

| Figure 56. | Cross point implemented using 3-D smart vias and 3-D SRAMS – a) schematic b) top view                                                                                | . 60 |

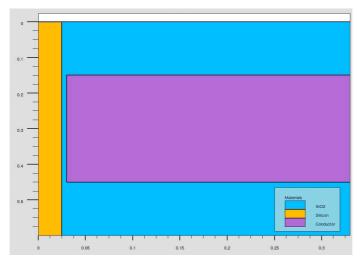

| Figure 57. | TCAD cylindrical representation of the vertical NWFET structure (scales are in micron)                                                                               | . 61 |

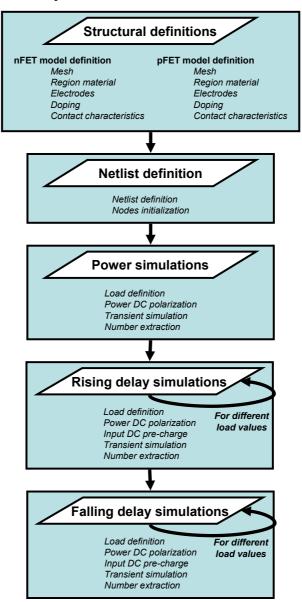

| Figure 58. | TCAD circuit characterization methodology flow chart                                                                                                                 | . 61 |

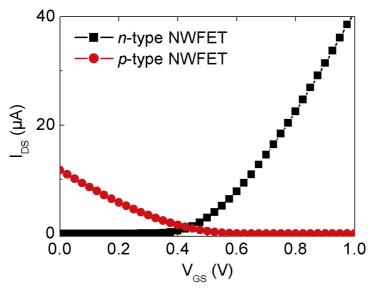

| Figure 59. | I-V characteristics for vertical nanowire FET                                                                                                                        | . 62 |

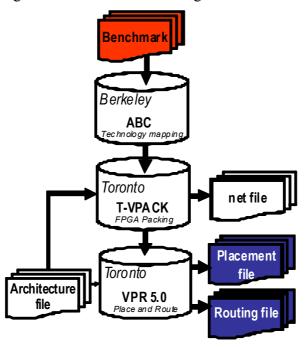

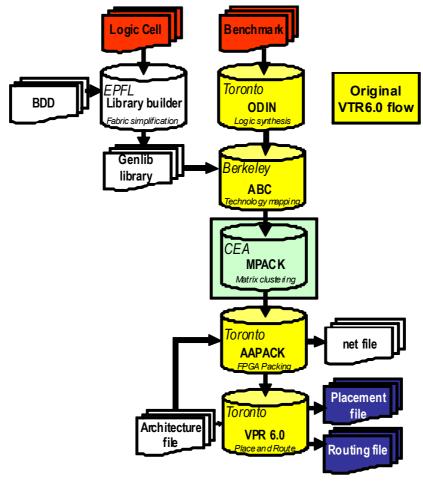

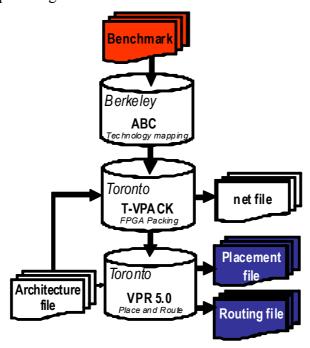

| Figure 60. | FPGA benchmarking flow diagram                                                                                                                                       | . 69 |

| Figure 61. | PCM-based FPGA organization                                                                                                                                          | . 70 |

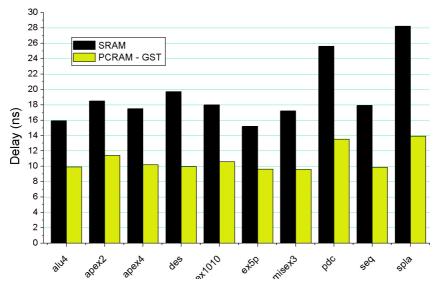

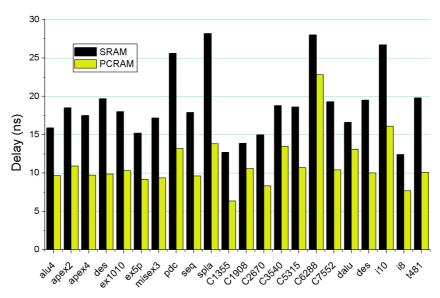

| Figure 62. | Delay estimation for FPGAs synthesized with GST-PCM- and SRAM-based Switchboxes                                                                                      | . 71 |

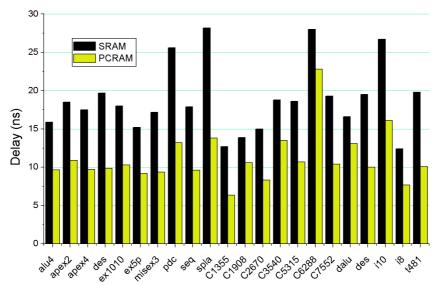

| Figure 63. | Delay estimation for FPGAs synthesized with PCM- and SRAM-based LUTs and MUXs                                                                                                                                                                                                                                                                                                                                                                                                 | . 72 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

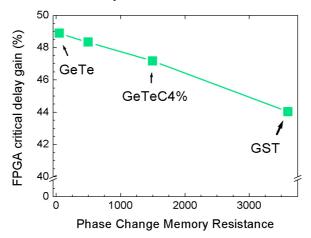

| Figure 64. | Variation of the FPGA critical path delay with the PCM on-resistance (delay averaged over the whole benchmark set)                                                                                                                                                                                                                                                                                                                                                            | . 72 |

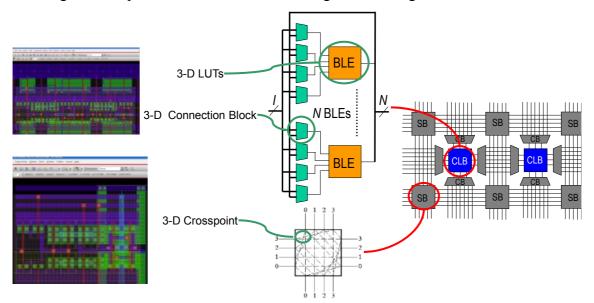

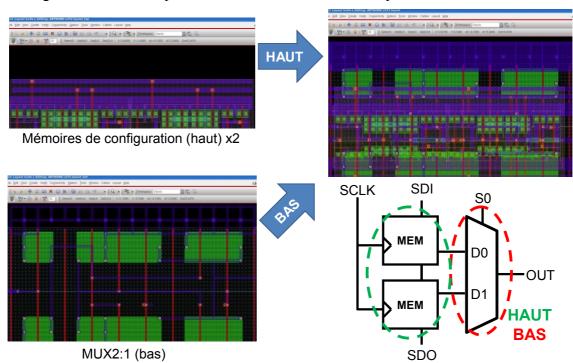

| Figure 65. | Monolithically 3-D integrated FPGA organization                                                                                                                                                                                                                                                                                                                                                                                                                               | . 73 |

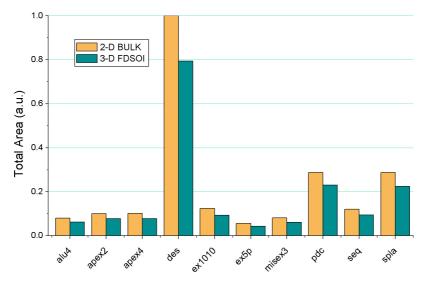

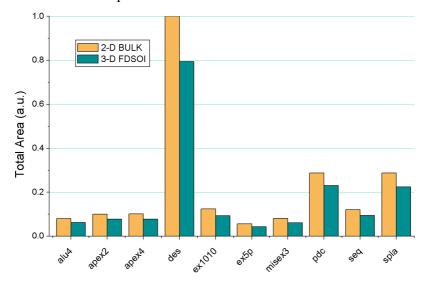

| Figure 66. | Area estimation for FPGAs synthesized with standard bulk circuits and monolithic 3-D integrated FDSOI circuits.                                                                                                                                                                                                                                                                                                                                                               |      |

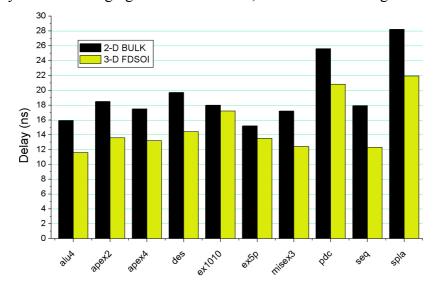

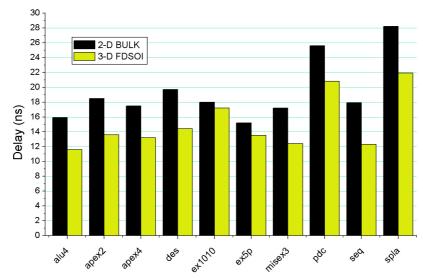

| Figure 67. | Delay estimation for FPGAs synthesized with standard bulk circuits and monolithic 3-D integrated FDSOI circuits.                                                                                                                                                                                                                                                                                                                                                              | . 74 |

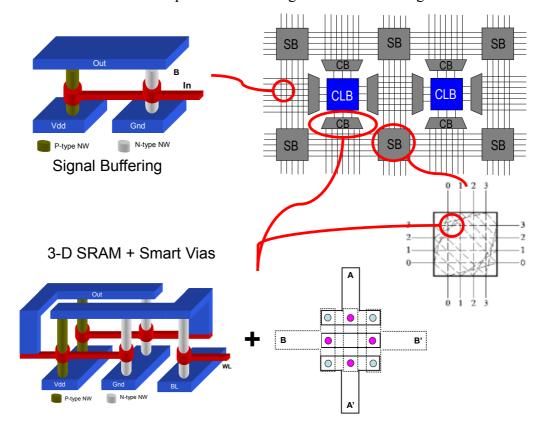

| Figure 68. | Vertical-NWFET-based FPGA overall organization                                                                                                                                                                                                                                                                                                                                                                                                                                | . 76 |

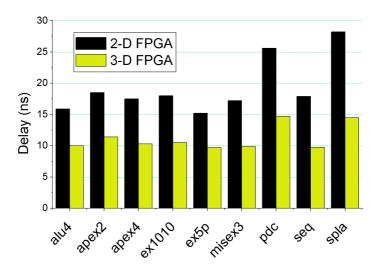

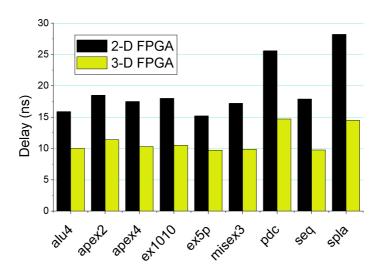

| Figure 69. | Delay estimation for 2-D and 3-D FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 76 |

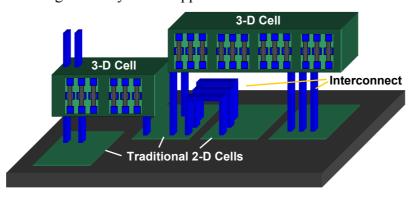

| Figure 70. | Illustration of the 3-D and 2-D cell co-integration                                                                                                                                                                                                                                                                                                                                                                                                                           | . 77 |

| Figure 71. | a) Schematics of a CNFET with a back-gate configuration [142] b) Measured characteristics of a typical CNTFET (CNT $\phi$ =1.4nm, Ti contacts                                                                                                                                                                                                                                                                                                                                 |      |

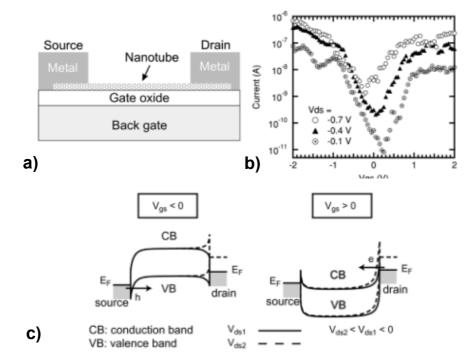

|            | and gate oxide 10-nm of SiO <sub>2</sub> ) [142] c) Band diagrams of the structure [142]                                                                                                                                                                                                                                                                                                                                                                                      | . 85 |

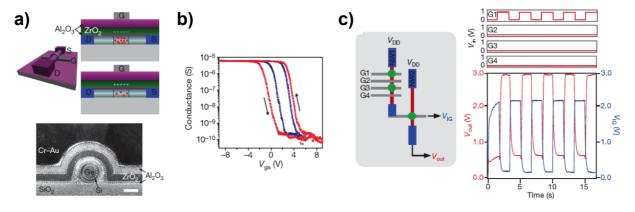

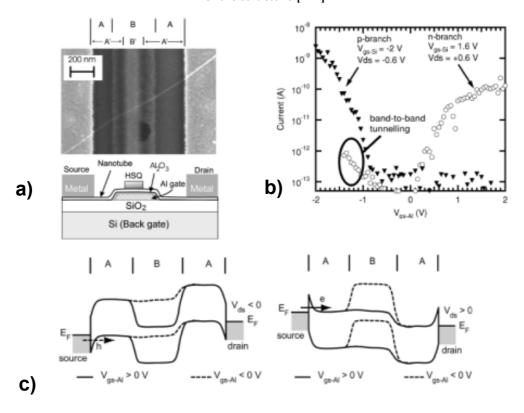

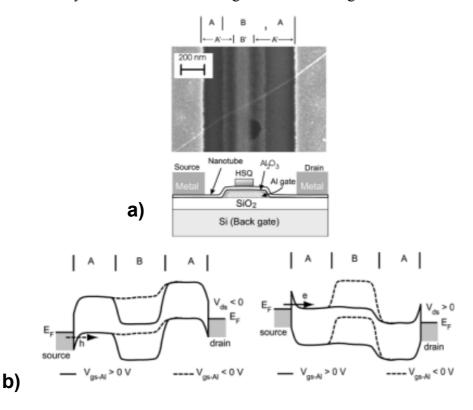

| Figure 72. | a) SEM image (top) and schematic cross-sectional diagram of a DG-CNTFET [142] b) Measured characteristics of a DG-CNTFET (Back-gates are polarized to shown p- and n-type unipolar behaviors) [142] c) Band diagrams of the structure (Left $V_{gs-Si} < 0$ , and right $V_{gs-Si} > 0$ ) [142]                                                                                                                                                                               | . 85 |

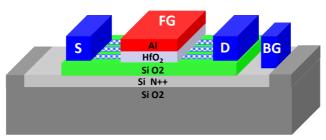

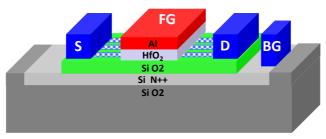

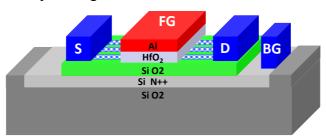

| Figure 73. | DG-CNFET device schematic using the proposed process-flow and showing the source (S), drain (D), front- (FG) and back-gate (BG) contacts                                                                                                                                                                                                                                                                                                                                      | . 86 |

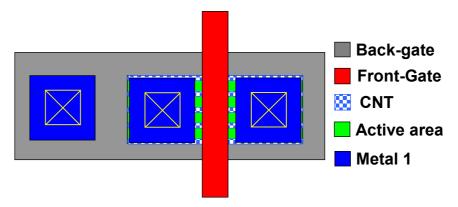

| Figure 74. | DG-CNTFET device layout                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 86 |

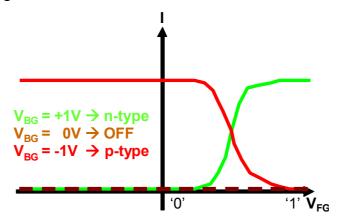

| Figure 75. | Specified I-V curve of a tuned DG-CNTFET                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 87 |

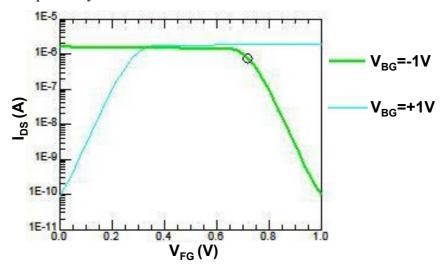

| Figure 76. | Simulated I-V curve of a tuned DG-CNTFET [IMS]                                                                                                                                                                                                                                                                                                                                                                                                                                | . 88 |

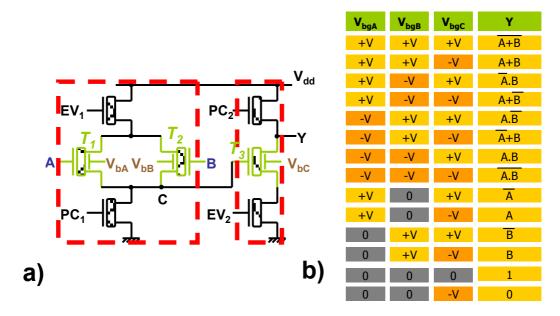

| Figure 77. | a) Transistor level schematic and b) configuration table for CNT reconfigurable cell [122]                                                                                                                                                                                                                                                                                                                                                                                    | . 89 |

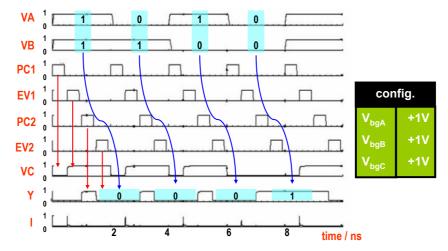

| Figure 78. | Reconfigurable logic gate waveforms in NOR configuration [122]                                                                                                                                                                                                                                                                                                                                                                                                                | . 89 |

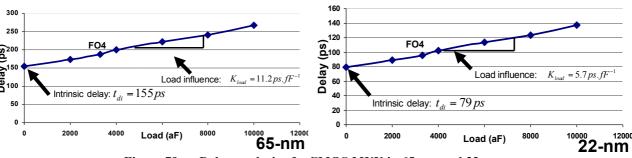

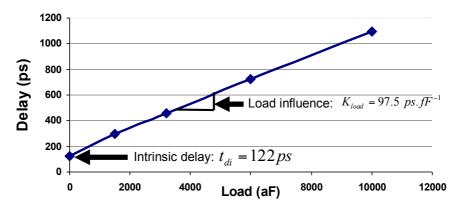

| Figure 79. | Delay analysis of a CMOS MUX in 65-nm and 22-nm.                                                                                                                                                                                                                                                                                                                                                                                                                              | . 91 |

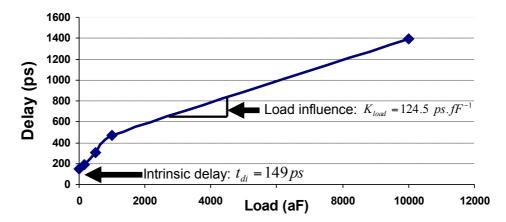

| Figure 80. | Delay analysis of DG-CNTFET Reconfigurable Cell                                                                                                                                                                                                                                                                                                                                                                                                                               | . 92 |

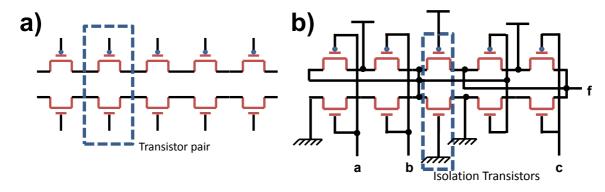

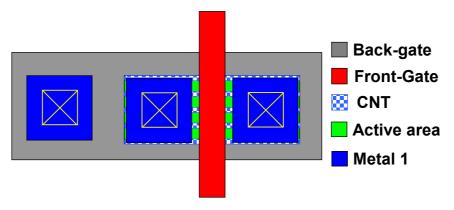

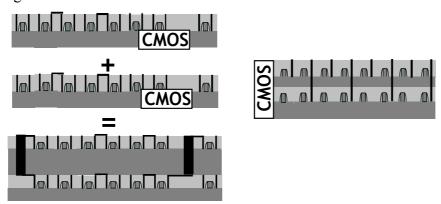

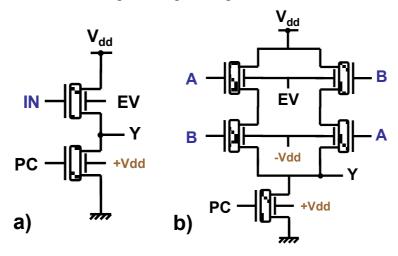

| Figure 81. | a) Generalized scheme for CMOS dynamic logic b) Generalized scheme for double-gate-based cells                                                                                                                                                                                                                                                                                                                                                                                |      |

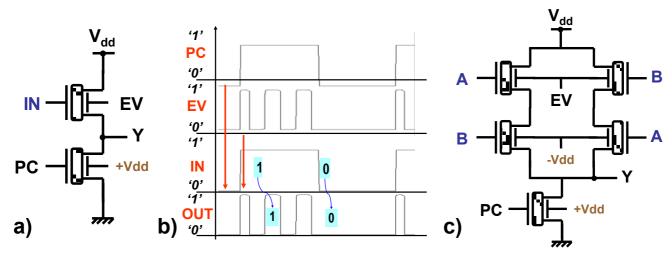

| Figure 82. | a) Buffer cell schematic b) associated waveform and c) XOR cell                                                                                                                                                                                                                                                                                                                                                                                                               | . 94 |

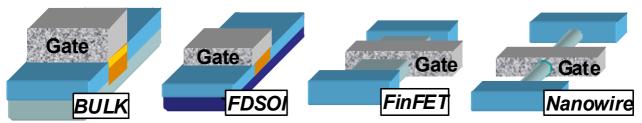

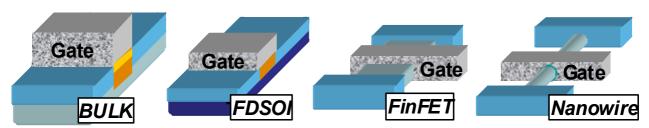

| Figure 83. | Silicon electronics evolution from bulk to nanowires                                                                                                                                                                                                                                                                                                                                                                                                                          | . 95 |

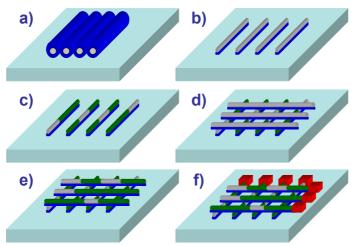

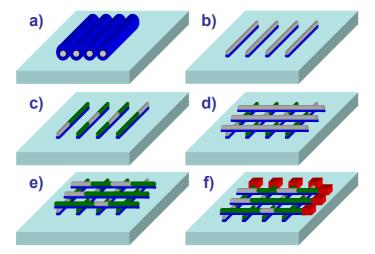

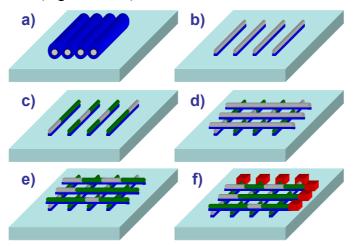

| Figure 84. | Manufacturing process to build a nanowire crossbar. <i>a)</i> Deposition of silicon nanowire after growth, oxidation and Langmuir Blodgett alignment. <i>b)</i> Etching of the oxide shell. <i>c)</i> Salicidation of the nanowire regions which will not be transistor channels. <i>d)</i> Deposition, alignment and etching of the oxide shell of the second layer. <i>e)</i> Salicidation as step c. <i>f)</i> metallization to contact the nanowires around the crossbar. | . 96 |

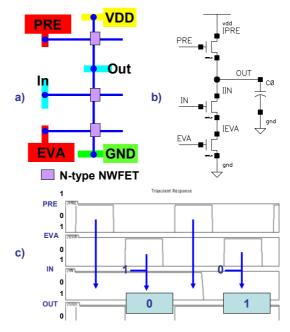

| Figure 85. | NOT function realized on <i>n</i> -type nanowires using dynamic logic. <i>a</i> )                                                                                                                                                                                                                                                                                                                                                                                             |      |

| Eigura 06  | Pseudo-physical view b) Schematic view c) Associated waveform.                                                                                                                                                                                                                                                                                                                                                                                                                |      |

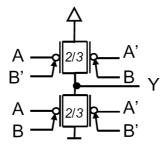

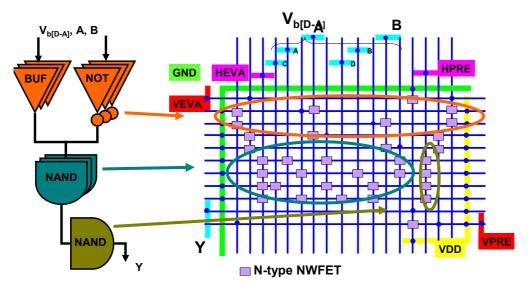

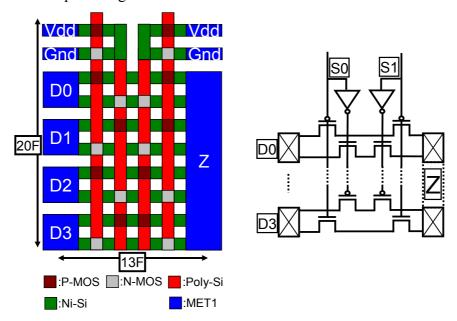

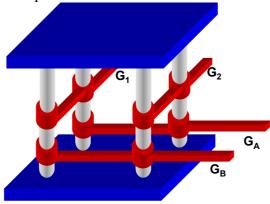

| Figure 86. | Representation of CB-NWFET dynamic reconfigurable logic cell                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| Figure 87. | Metal/via layout of the dynamic logic cell                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

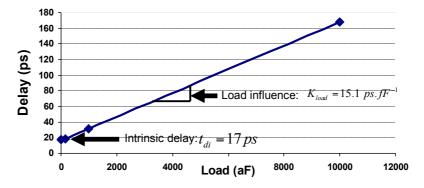

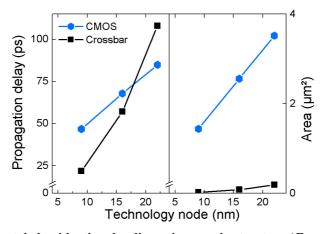

| Figure 88. | Delay analysis of Nanowire Reconfigurable Cell                                                                                                                                                                                                                                                                                                                                                                                                                                | . 99 |

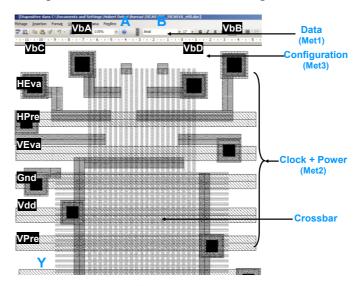

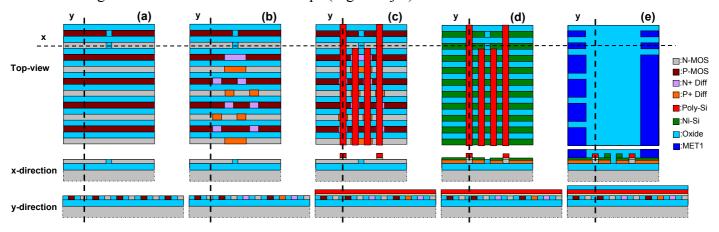

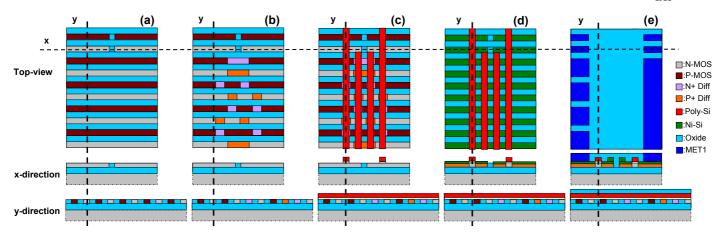

| Figure 89. | Manufacturing process to build a FDSOI crossbar: a) grating patterning and active regions doping. b) Passive regions definition. c) Gate deposit. d) Passive regions finalization and salicidation. e) Metallization to contact passive regions.                                                                                                                                                                                                                              | 102  |

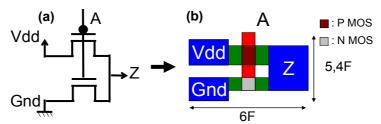

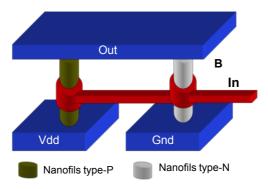

| Figure 90. | Crossbar inverter structure (a) equivalent circuit and (b) layout                                                                                                                                                                                                                                                                                                                                                                                                             | 102  |

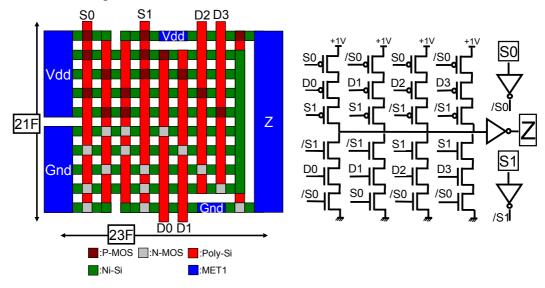

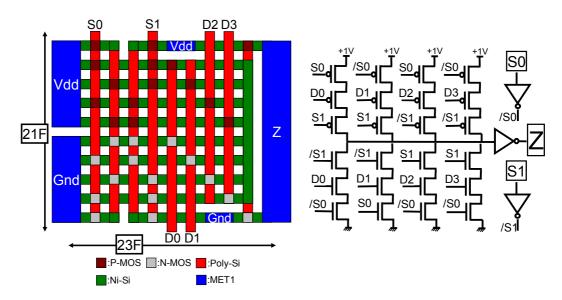

| Figure 91.  | Stand-alone 4:1 MUX crossbar implementation (separate doping regions) and equivalent schematic                                                                                     | 103  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

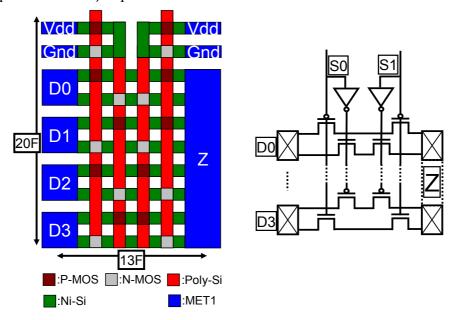

| Figure 92.  | FPGA-suited 4:1 MUX crossbar implementation (alternating doping                                                                                                                    | 105  |

| riguic 72.  | regions) and equivalent schematic                                                                                                                                                  | 104  |

| Figure 93.  | Modeling of parasitic devices                                                                                                                                                      | 104  |

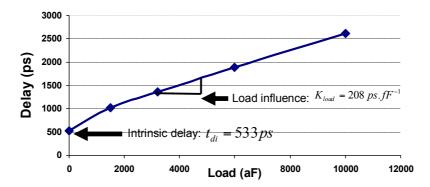

| Figure 94.  | Delay analysis of lithographic crossbar in a parasitic-free context                                                                                                                | 105  |

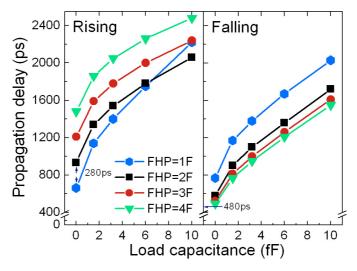

| Figure 95.  | Influence of P-type horizontal wire size $(F_{HP})$ on MUX propagation delay (Output of the inverter) $(F_{HN} = F_V = F_I = F = 60 \text{ nm})$                                   | 106  |

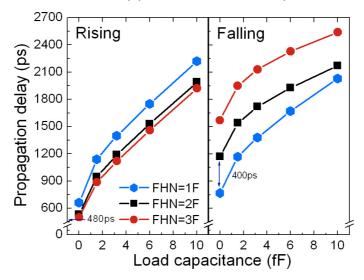

| Figure 96.  | Influence of N-type horizontal wire size (FHN) on MUX propagation delay (Output of the inverter) $(F_{HP} = F_V = F_I = F = 60 \text{ nm})$                                        |      |

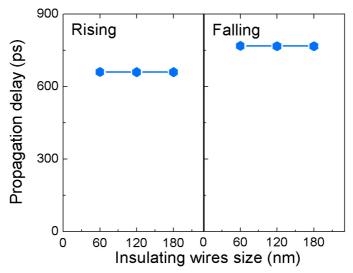

| Figure 97.  | Influence of insulating wire size $(F_I)$ on MUX propagation delay $(F_{HP} = F_{HN} = F_V = F = 60 \text{ nm})$                                                                   | 107  |

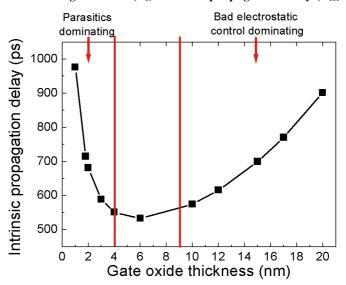

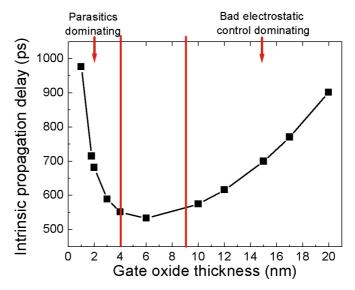

| Figure 98.  | Influence of gate oxide thickness ( $T_{OX}$ ) on MUX propagation delay ( $F_{HP} = F_{HN} = F_V = F_I = F = 60 \text{ nm}$ )                                                      | 107  |

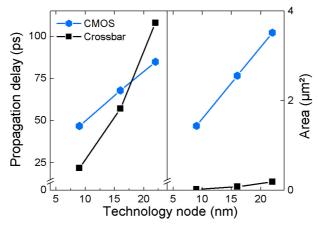

| Figure 99.  | Impact of scaling $(F_{HP} = F_{HN} = F_{V} = F_{I} = F)$                                                                                                                          | 108  |

| Figure 100. | Delay analysis of lithographic crossbar with parasites                                                                                                                             |      |

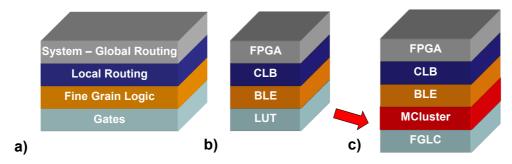

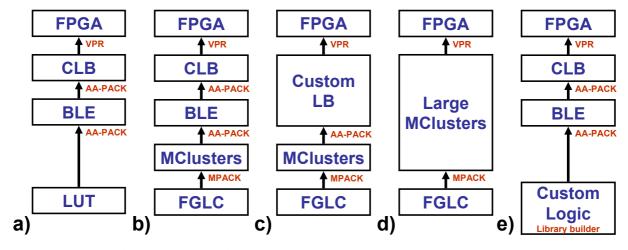

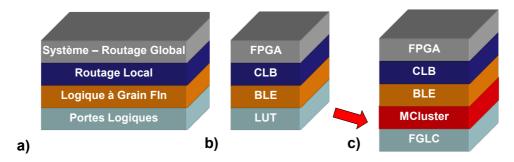

| Figure 101. | Conventional hierarchical template (a), FGPA model (b) and modified levels (c)                                                                                                     |      |

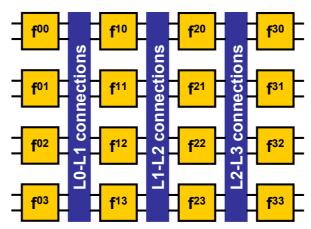

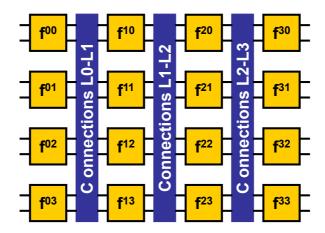

| Figure 102. | MCluster approach for reconfigurable architectures (MCluster 4 4)                                                                                                                  |      |

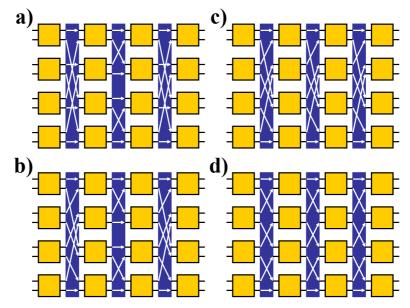

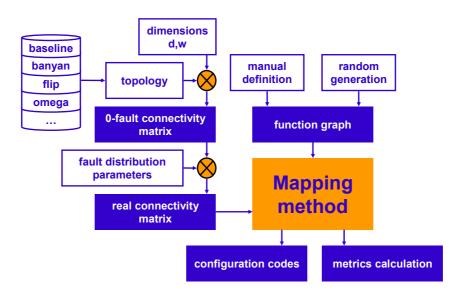

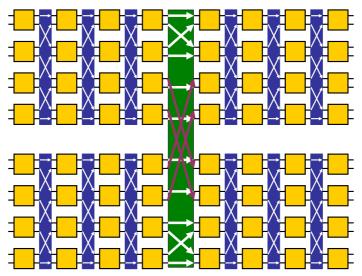

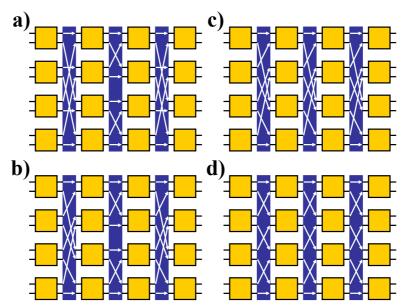

| Figure 103. | Matrix of 16 reconfigurable gates with fixed interconnect topology (a)Banyan, b)Baseline, c)Flip, d)Modified Omega)                                                                |      |

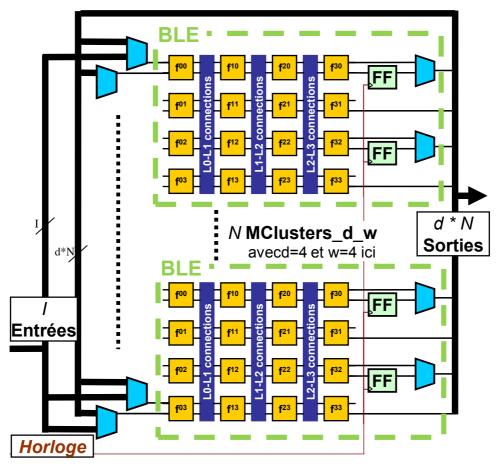

| Figure 104. | MCluster-based CLB proposal                                                                                                                                                        |      |

| Figure 105. | Final FPGA layer organization                                                                                                                                                      |      |

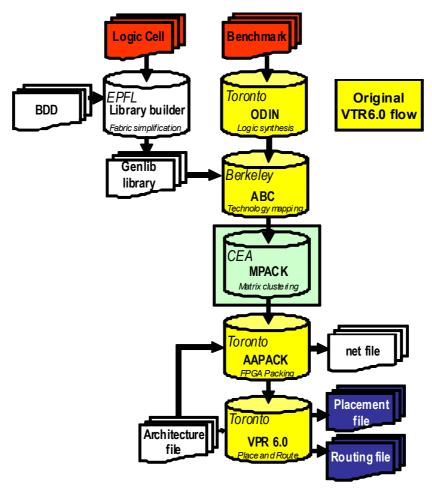

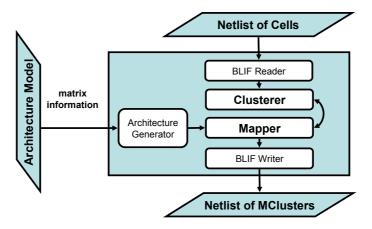

| Figure 106. | Disruptive technology compatible benchmarking flow diagram                                                                                                                         |      |

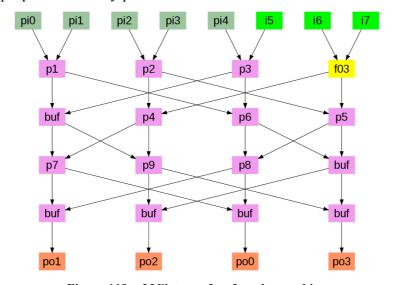

| Figure 107. | Illustration of possible scenarios compatible with the proposed toolflow                                                                                                           |      |

| Figure 108. | MPack model flow                                                                                                                                                                   |      |

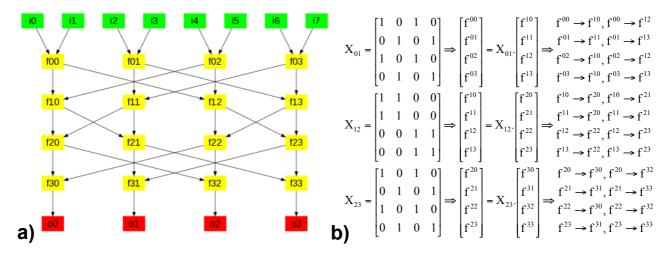

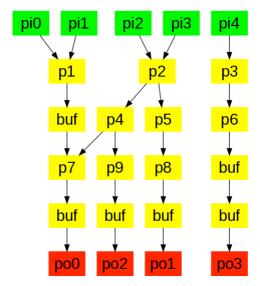

| Figure 109. | a) Banyan_4_4 topological arrangement (logic cells are in yellow, virtual input nodes are in green, virtual output nodes are in red) and b) associated cross-connectivity matrices |      |

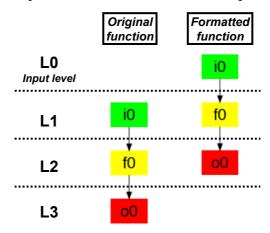

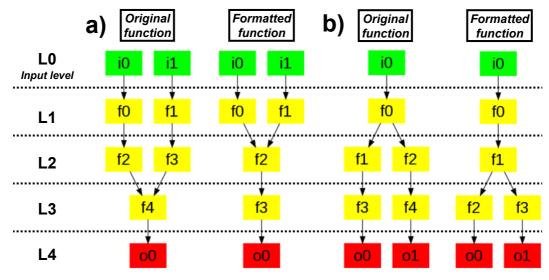

| Figure 110. | Input level correction illustration                                                                                                                                                |      |

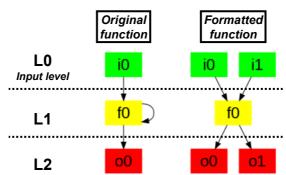

| Figure 111. | Feedback correction illustration                                                                                                                                                   |      |

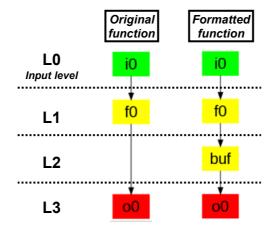

| Figure 112. | Jump correction illustration.                                                                                                                                                      |      |

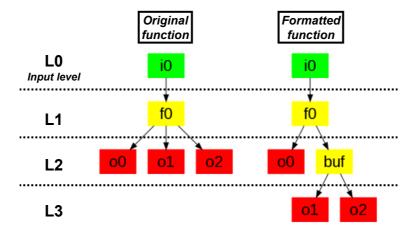

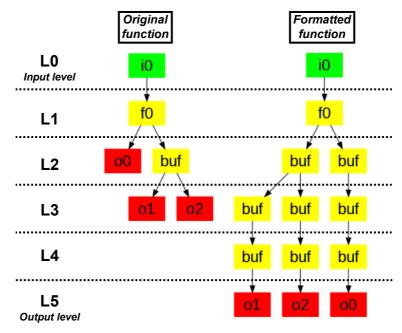

| Figure 113. | Multiple buffering/inverting path simplification illustration – a) incoming                                                                                                        | 1.23 |

| 118010 110. | path – b) outgoing path                                                                                                                                                            | 123  |

| Figure 114. | Illustration of multiple output correction                                                                                                                                         |      |

| Figure 115. | Output level correction illustration                                                                                                                                               |      |

| Figure 116. | MPack mapping algorithm (pseudo-code)                                                                                                                                              |      |

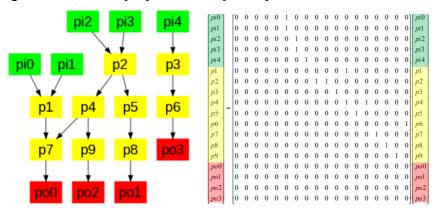

| Figure 117. | Function graph to map onto the Banyan_4_4 interconnect topology and its associated adjacency matrix                                                                                |      |

| Figure 118. | Function graph after correction step                                                                                                                                               | 126  |

| Figure 119. | MCluster after function packing                                                                                                                                                    |      |

| Figure 120. | MPack' clustering algorithm (pseudo-code)                                                                                                                                          |      |

| Figure 121. | Performance evaluation method for fixed interconnection topologies                                                                                                                 |      |

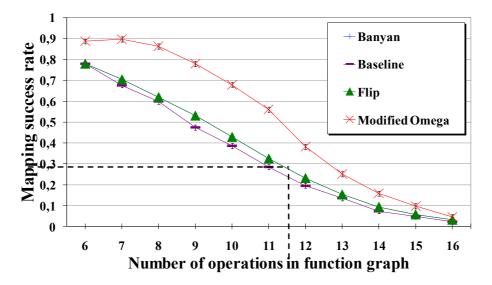

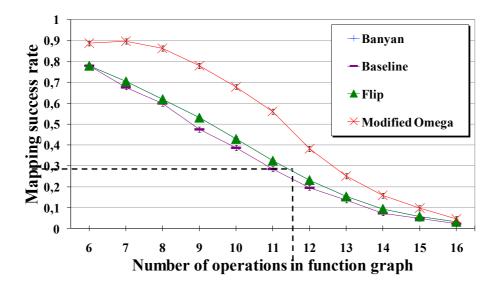

| Figure 122. | Programmability success rates for Banyan, Modified Omega, Flip and Baseline interconnect topologies within 4-deep 4-wide matrices                                                  |      |

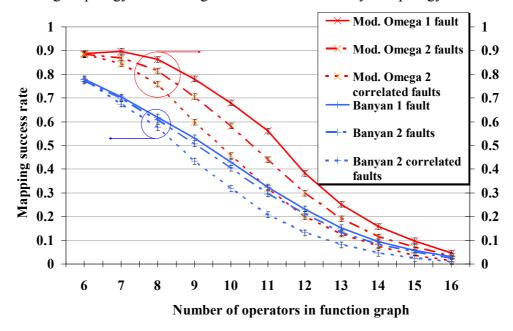

| Figure 123. | Comparison of programmability success rates for Banyan and Modified Omega interconnect topologies within 4-deep 4-wide matrices in the case of faulty links and faulty cells       |      |

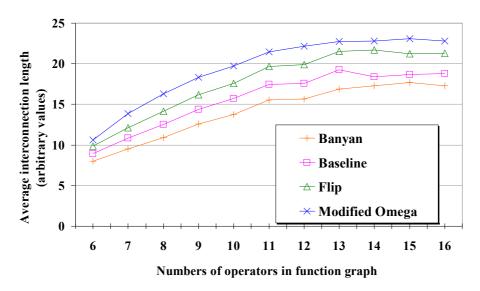

| Figure 124.                                                                         | Comparison of average interconnect length for Banyan, Modified Omega,       |  |  |  |  |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|

|                                                                                     | Flip and Baseline interconnect topologies within 4-deep 4-wide matrices 130 |  |  |  |  |

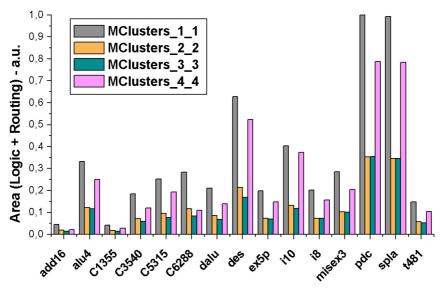

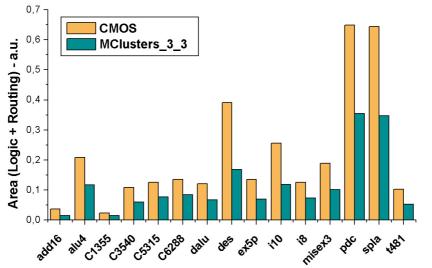

| Figure 125.                                                                         | Area estimation for MCluster-based FPGAs with various granularities 132     |  |  |  |  |

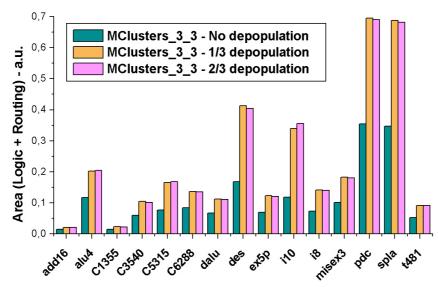

| Figure 126. Area estimation for MCluster_3_3-based FPGAs with different             |                                                                             |  |  |  |  |

|                                                                                     | depopulation scenarios                                                      |  |  |  |  |

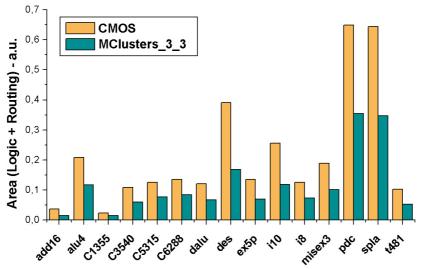

| Figure 127.                                                                         | Area estimation for 3 by 3 MCluster-based and CMOS-based FPGAs 133          |  |  |  |  |

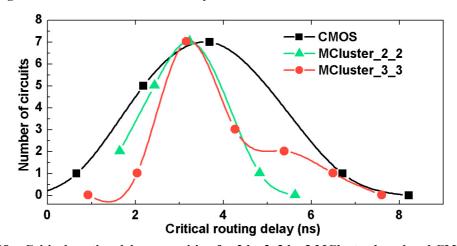

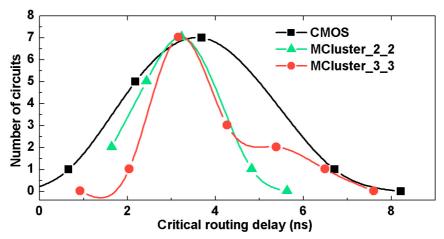

| Figure 128. Critical routing delay repartition for 2 by 2, 3 by 3 MCluster-based an |                                                                             |  |  |  |  |

|                                                                                     | CMOS-based FPGAs                                                            |  |  |  |  |

| Figure 129:                                                                         | Modified-Omega based MCluster with early internal outputs and cell          |  |  |  |  |

|                                                                                     | depopulation                                                                |  |  |  |  |

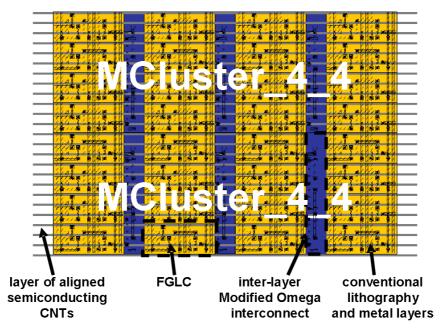

| Figure 130.                                                                         | Illustration of two MClusters_4_4 physical implementation on parallel       |  |  |  |  |

|                                                                                     | carbon nanotubes layer                                                      |  |  |  |  |

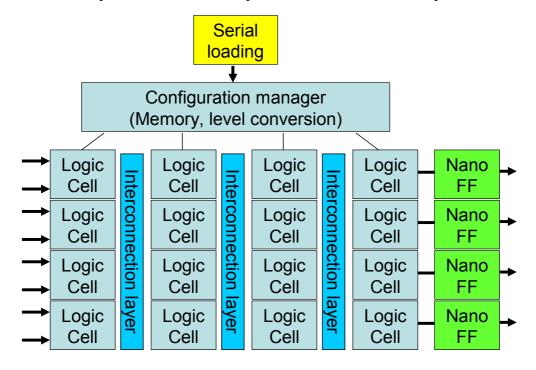

| Figure 131.                                                                         | MCluster organization for speculative CNLB                                  |  |  |  |  |

| Figure 132.                                                                         | Speculative pipelined organization of CNLB                                  |  |  |  |  |

| Figure 133.                                                                         | Double-stage MCluster organization with two-level hierarchic                |  |  |  |  |

|                                                                                     | interconnection strategy                                                    |  |  |  |  |

|                                                                                     |                                                                             |  |  |  |  |

## List of Tables

| Table I.     | Linear scaling rules impact on device parameters [5]                                                                   | 2    |

|--------------|------------------------------------------------------------------------------------------------------------------------|------|

| Table II.    | State-of-Art architecture global metrics comparisons                                                                   |      |

| Table III.   | Specification estimation wrt. memory distribution through an FPGA (extracted from Xilinx Virtex6 architecture [20])    |      |

| Table IV.    | Detailed technology performance evaluation                                                                             |      |

| Table V.     | Technology performance evaluation (2x2 switchbox)                                                                      |      |

| Table VI.    | Density survey of TSV technologies [96]                                                                                | 49   |

| Table VII.   | Evaluation of SRAM Shifter performance                                                                                 |      |

| Table VIII.  | Evaluation of Look-Up Table performance                                                                                | . 55 |

| Table IX.    | Evaluation of Cross point performance                                                                                  | 56   |

| Table X.     | Simulation results summary                                                                                             | 62   |

| Table XI.    | Technology comparison (4-input LUT test case)                                                                          | 64   |

| Table XII.   | Architectural evaluation summary                                                                                       | . 78 |

| Table XIII.  | Global evaluation of the DG-CNFET cell performances                                                                    | 91   |

| Table XIV.   | Power consumption vs. function (22-nm node – 4GHz)                                                                     | 92   |

| Table XV.    | Dynamic DGCNFET-based cell transistor requirements                                                                     | 94   |

| Table XVI.   | Global evaluation of the CB-NWFET MUX performances                                                                     | 99   |

| Table XVII.  | Detailed Power Consumption figures for sublithographic cell (22-nm – 4GHz)                                             | 100  |

| Table XVIII. | Evaluation of a Parasitic-Free 4-to-1 MUX in lithographic crossbar technology                                          |      |

| Table XIX.   | Detailed Power Consumption figures for the sublithographic cell in a parasitic-free context (65-nm – 650MHz)           |      |

| Table XX.    | Evaluation of scaling with parasitics                                                                                  | 108  |

| Table XXI.   | Evaluation of lithographic crossbar-based structure with parasitics                                                    | 108  |

| Table XXII.  | Detailed Power Consumption figures for sublithographic cell (65-nm – 650MHz)                                           | 109  |

| Table XXIII. | Global comparison of analyzed disruptive technology cells                                                              | 110  |

|              | Analysis summary                                                                                                       |      |

| Table XXV.   | Summary of global gain figures for the proposed architectures with respect to a baseline CMOS 65-nm FPGA architectures | 139  |

## CHAPTER 1 Introduction

Our post-industrial way of life can be defined by an ever-growing need for mass consumer products. Every day, the industry generates novel innovations that continually boost the market. Planes are increasingly automated, cars assist the drivers in a various number of situations for security or leisure (e.g. speed control, parking assistance, etc.) and cell phones are able to communicate over the internet and to use several different networks. Video game consoles are controlled by handset motions or even player movements. Such evolutions mean that the systems have to be more intelligent, have simpler interface and be more communicative. The enabler behind all these novelties is the generalized use of embedded electronic systems, which have long become an integral and pervasive part of the human society. As the demand in terms of entertainment, data volume and connectivity is in constant growth, the system performance needs to improve more each day. The market is boosted by application requirements and remains in constant progress and evolution.

Electronic systems are complex systems, which aim to address computation in a specific target application. They are built around a physical hardware core, which can be programmed by loading and adding software modules. The hardware is the basic key for computation, in the sense that it is used to manage information at the physical level, i.e. in conventional systems and at the most elementary level, the electronic charge. The hardware is closely related to design and manufacturing techniques. The design defines the organization of the components in the system (i.e. the architecture). The manufacturing techniques define the physical components. This makes the related field highly multi disciplinary.

The basic unit of electronic systems is the transistor. Invented in 1947 by William Shockley, John Bardeen and Walter Brattain, the transistor is able to work as a switch at the smallest scale [1]. While the first demonstrated transistor was a bipolar transistor made of Germanium, the technology moved quickly to Silicon-based transistor and to the demonstration of the first *Metal-Oxide-Semiconductor Field Effect Transistor* (MOSFET) in 1959 [2]. The Silicon MOSFET transistor is still in use in the most advanced modern integrated circuits. By scaling the device and using a large number of transistors on a same substrate, it became possible to create integrated circuits of higher complexity and functionality. The era of the semiconductor industry has been defined by scaling, and consequent improvement for almost half a century: the industry has followed an exponential evolution from the first realization of integrated circuits to the current *Very Large Scale Integration* (VLSI<sup>1</sup>) with billions of transistors.

#### 1.1 The Scaling Era

The way in which the semiconductor industry has evolved is unique with the scope of industrial history by its impact on society and rate of progress. Since the creation of the transistor, the semiconductor industry has grown exponentially, a trend which has been enshrined in Moore's Law [3] (Figure 1). Starting in 1965 and based on empirical

<sup>&</sup>lt;sup>1</sup> This term was first coined at the 100ktransistor mark. Other terms were later proposed (e.g. ULSI) to reflect the continually increasing complexity of integrated circuits, but VLSI remains the term of choice within the community.

observation, this law predicts an exponential growth (a doubling) of the number of transistors per die for each new technology generation. Even the growth rate (or time between technology generations) has not been constant though during recent decades, it still has a factor of 2 every 2 years. As illustrated by figure 1, it is worth noticing that the transistor count of processors has followed a similar trend for the last four decades.

Figure 1. Processor transistor count and Moore's Law since 1971 [4]

The increase in the number of transistors is an obvious consequence of the scaling. Scaling leads to the reduction of the dimensions of elementary drawn transistors, making it is thus possible to integrate more devices within the same area. Further scaling brings many more additional advantages than the sole matter of density. Since the majority of technological parameters are scaled according to a given scaling strategy. The impact of scaling on the main device parameters for constant electric field (the dominant scaling strategy for deep submicron technology generations) is presented in Table I. It is important to observe that scaling leads to a reduction of device power by a factor of  $\alpha^2$  and a speed up in the intrinsic delay by a factor of  $\alpha$ .

| • | able 1. | Linear scanng rules impact on | device parameters [5] |

|---|---------|-------------------------------|-----------------------|

|   |         | n 4                           | C 1' C 4              |

Linear scaling rules impact on device peremeters [5]

Tabla I

| Parameters                                 | Scaling factor |

|--------------------------------------------|----------------|

| Transistor length and width (L, W)         | $1/\alpha$     |

| Junction depth $(x_i)$                     | $1/\alpha$     |

| Oxide thickness $(t_{ox})$                 | $1/\alpha$     |

| Doping concentration $(N_d, N_a)$          | α              |

| Supply voltage $(V_D)$                     | $1/\alpha$     |

| Drive current $(I_D)$                      | $1/\alpha$     |

| Electric field (E)                         | 1              |

| Capacitance ( $\varepsilon$ . $A/t_{ox}$ ) | $1/\alpha$     |

| Delay time $(\tau = C.V_D/I_D)$            | $1/\alpha$     |

| Power dissipation ( $\sim V_D.I_D$ )       | $1/\alpha^2$   |

| Device density (~1/A)                      | $\alpha^2$     |

This fast evolution is unique. As an illustration, if other industries had followed a comparable rate of change, a one-way ticket between Paris and New York may would now cost only 0.01€, while the total flight time would have been reduced down to 0.25 s. Similarly, a car scaled by the same proportions would only cost 20€, reach a speed of 3000 km.s<sup>-1</sup>, would only weight 10 mg and would only consume 11 of fuel per 100 000 km.

First only seen as a trend based on empirical observation, the Moore's Law has become much more than just a speculation. It has been regarded (and is still considered) as a real specification for growth, enabling the definition of objectives for research and development in the semiconductor industry. This has given rise in recent years to the *International Technology Roadmap for Semiconductors* (ITRS), compiled by a consortium of academic and industrial leaders in the fields of semiconductor, and whose goal is to survey the trends in semiconductor technology and predict its future evolution up to fifteen years ahead. As a consequence, it defines the objectives for future technology nodes and identifies roadblocks to overcome. Figure 2 shows the current tendency of scaling of the main technology node parameters (metal layer half pitch and printed gate length). It is essential to highlight that Moore's Law is still expected to be maintained for the next two decades.

Figure 2. Projected evolution of dimensions and mask cost [6]

Nevertheless, it is also worth pointing out that ITRS recognizes the existence of physical and economical limits to this growth.

### 1.2 New Challenges

The ITRS has indicated significant future hurdles that may impede the original scaling law. Limitations are found at various levels, from fundamental device characteristics to advanced system design methodologies.

#### 1.2.1 Process Integration and Devices

The process integration and the devices will suffer from leakage and quantum effects, as well as from intrinsic fabrication hurdles (for example lithography steps).

#### • Electrostatic Channel Control

With channel scaling, *Short Channel Effects* (SCE) are becoming increasingly dominant. The short channel effect reflects the lowering of the threshold voltage with a decreasing channel length. This effect is due to a two-dimensional distribution of the surface potential in the channel. Furthermore, in short channel devices, the *Drain-Induced Barrier Lowering* (DIBL) effect could be added. The DIBL consists of making the threshold voltage dependent on the drain bias. Both of these effects lower the threshold voltage and make the devices more vulnerable to variability.

#### • Leakage

It is worth noticing that when the lateral dimensions of a transistor are scaled, the oxide thickness is also scaled. This leads to an exponential growth of the tunnel current through the gate oxide, thereby an increase in the gate leakage.