# Compositional modeling of globally asynchronous locally synchronous (GALS) architectures in a polychronous model of compotation

Yue Ma

#### ▶ To cite this version:

Yue Ma. Compositional modeling of globally asynchronous locally synchronous (GALS) architectures in a polychronous model of compotation. Embedded Systems. Université Rennes 1, 2010. English. NNT: . tel-00675438

## HAL Id: tel-00675438 https://theses.hal.science/tel-00675438v1

Submitted on 1 Mar 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre : 4245 ANNÉE 2010

## THÈSE / UNIVERSITÉ DE RENNES 1

sous le sceau de l'Université Européenne de Bretagne

pour le grade de

## DOCTEUR DE L'UNIVERSITÉ DE RENNES 1

Mention: Informatique

#### **Ecole doctorale MATISSE**

présentée par

## Yue MA

préparée à l'unité de recherche 6074 IRISA Institut de Recherche en Informatique et Systèmes Alèatoires IFSIC

Compositional modeling of globally asynchronous locally synchronous (GALS) architectures in a polychronous model of computation

#### Thèse soutenue à Rennes le 29 Novembre 2010

devant le jury composé de :

#### **Jean-Paul BODEVEIX**

Professeur à l'Université Paul Sabatier/rapporteur

#### Frank SINGHOFF

Professeur à Université de Bretagne Occidentale / rapporteur

#### **Christophe WOLINSKI**

Professeur à l'Université de Rennes 1/examinateur

## Abdoulaye GAMATIÉ

Chargé de recherche CNRS/examinateur

#### Thierry GAUTIER

Chargé de recherche INRIA/examinateur

#### Jean-Pierre TALPIN

Directeur de recherche INRIA/directeur de thèse

## Acknowledgements

First of all, I am grateful to all the members of my dissertation committee. I wish to thank Prof. Christophe Wolinski for his acceptance to be the president of committee.

I would like to thank Jean-Paul Bodeveix, professor of Université Paul Sabatier, and Frank Singhoff, professor of Université de Bretagne Occidentale, for their acceptance to be reporters for this thesis.

I would like also to thank Abdoulaye Gamatié, CNRS researcher, to judge this work. I wish to thank Thierry Gautier, INRIA researcher, to judge this thesis, and help me constanly writing my articles and progressing my French during my three years.

This thesis would not have been possible without the guidance of my thesis advisor, Jean-Pierre Talpin. His continuous supervision, encouragement, and of course constructive criticism have been great help and support in my research work.

I also need to thank all the members of INRIA ESPRESSO team for sharing the good ambiance during my stay at INRIA. In addition, I appreciate the review of this thesis by Paul Le Guernic. I also want to express my additional gratitude to Loïc Besnard for sharing accommodation with me, and Huafeng Yu for sharing experiences when we worked together for the demo.

Special thanks to my family, I could not accomplish my study in France without your support and encouragement for these three years.

## **Contents**

Introduction

| I | Rés  | sumé (  | en français                                                     | 11   |

|---|------|---------|-----------------------------------------------------------------|------|

| 1 | Rési | umé en  | français                                                        | 13   |

|   | 1.1  | Introd  | uction                                                          | . 13 |

|   | 1.2  | Introd  | uction au langage AADL et aux architectures avioniques          | . 15 |

|   |      | 1.2.1   | Abstractions du langage AADL                                    | . 15 |

|   |      | 1.2.2   | Annexe comportementale de AADL                                  | . 16 |

|   |      | 1.2.3   | Architecture avionique et ARINC 653                             | . 16 |

|   | 1.3  | Langa   | ge Signal et modélisation ARINC en Signal                       | . 16 |

|   |      | 1.3.1   | Le langage Signal                                               | . 17 |

|   |      | 1.3.2   | Modélisation de concepts ARINC en Signal                        | . 18 |

|   | 1.4  | Travau  | ux reliés : formalisations de AADL                              | . 19 |

|   | 1.5  | Modél   | lisation de composants AADL en processus Signal                 | . 20 |

|   |      | 1.5.1   | Chaîne de transformation                                        | . 20 |

|   |      | 1.5.2   | Principes de transformation                                     | . 21 |

|   |      | 1.5.3   | Du temps logique abstrait vers un temps de simulation concret . | . 21 |

|   |      | 1.5.4   | Modélisation de thread                                          | . 24 |

|   |      | 1.5.5   | Modélisation des autres composants                              | . 27 |

|   | 1.6  | Spécif  | fication de comportements AADL                                  | . 28 |

|   |      | 1.6.1   | Forme SSA                                                       | . 29 |

|   |      | 1.6.2   | Systèmes de transition AADL                                     | . 29 |

|   |      | 1.6.3   | Interprétation des transitions / actions                        | . 30 |

|   | 1.7  | Génér   | ation de modèles de simulation distribués                       | . 34 |

|   |      | 1.7.1   | Placement                                                       | . 34 |

|   |      | 1.7.2   | Ordonnanceur                                                    | . 36 |

|   |      | 1.7.3   | Ajout des communications                                        | . 36 |

|   | 1.8  | Vérific | cation et simulation                                            | . 37 |

|   |      | 1.8.1   | Vérification formelle                                           | . 37 |

|   |      | 1.8.2   | Simulation                                                      | . 38 |

|   | 1.0  | 0 1     |                                                                 | 20   |

1

| II | Co   | onceptions of AADL and Signal                   | 41               |

|----|------|-------------------------------------------------|------------------|

| 2  | Intr | oduction to AADL and Avionic architectures      | 43               |

|    | 2.1  | AADL language abstractions                      | 44               |

|    |      | 2.1.1 The SAE AADL standard                     | 44               |

|    |      | 2.1.2 AADL meta-model and models                | 45               |

|    |      | 2.1.3 AADL open source tools                    | 46               |

|    | 2.2  | Summary of the core AADL components             | 48               |

|    |      | 2.2.1 Software components                       | 50               |

|    |      | 2.2.2 Execution platform components             | 55               |

|    |      | 2.2.3 System component                          | 58               |

|    | 2.3  | System binding                                  | 59               |

|    | 2.4  | Component interaction                           | 60               |

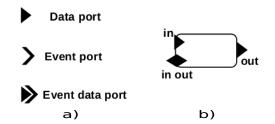

|    |      | 2.4.1 Port                                      | 60               |

|    |      | 2.4.2 Port connection                           | 61               |

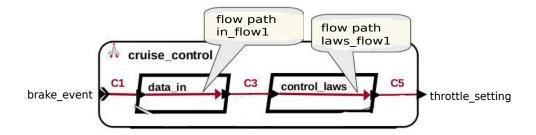

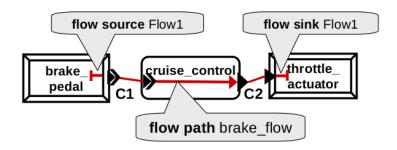

|    | 2.5  | Flows                                           | 63               |

|    | 2.6  | AADL behavior annex                             | 64               |

|    | 2.7  | Avionics system architecture and ARINC653       | 65               |

|    |      | 2.7.1 Avionics system architecture overview     | 65               |

|    |      | 2.7.2 ARINC standard                            | 66               |

|    |      | 2.7.3 AADL and ARINC                            | 69               |

|    | 2.8  | AADL components considered in this thesis       | 70               |

|    | 2.9  | Conclusion                                      | 70               |

| _  | ~•   |                                                 |                  |

| 3  | _    | al Language and modeling ARINC in Signal        | 73               |

|    | 3.1  | Signal language                                 | 74               |

|    |      | 3.1.1 Signal, execution, process                | 74               |

|    |      | 3.1.2 Data types                                | 75               |

|    |      | 3.1.3 Elementary processes                      | 76               |

|    |      | 3.1.4 Process operators                         | 77<br><b>-</b> 0 |

|    |      | 3.1.5 Parallel semantic properties              | 78<br><b>-</b> 2 |

|    |      | 3.1.6 Modularity features                       | 79               |

|    |      | 3.1.7 Endochronous acyclic processes            | 80               |

|    |      | 3.1.8 Time domains and communications in Signal | 80               |

|    |      | 3.1.9 Non-determinism modeling in Signal        | 82               |

|    |      | 3.1.10 Adequacy of Signal for AADL modeling     | 83               |

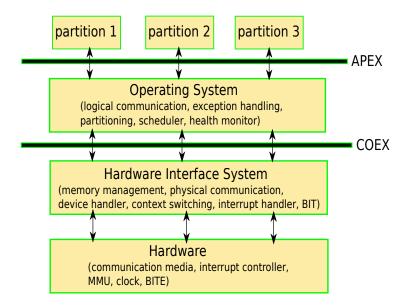

|    | 3.2  | Modeling ARINC concepts in Signal               | 84               |

|    |      | 3.2.1 Partitions                                | 84               |

|    |      | 3.2.2 Partition-level OS                        | 85               |

|    |      | 3.2.3 Processes                                 | 86               |

|    |      | 3.2.4 APEX services                             | 87               |

|    | 3.3  | Conclusion                                      | 88               |

|   | I Pa        | rototyping AADL models in a polychronous model of com-<br>on | 89  |

|---|-------------|--------------------------------------------------------------|-----|

| 4 | Forn        | nalizing AADL                                                | 91  |

| - | 4.1         | AADL background                                              | 91  |

|   | 4.2         | Related works                                                | 92  |

|   |             | 4.2.1 Modeling AADL in MARTE                                 | 93  |

|   |             | 4.2.2 Modeling AADL in SystemC                               | 94  |

|   |             | 4.2.3 Code generation from AADL to C                         | 94  |

|   |             | 4.2.4 Modeling AADL in Fiacre                                | 94  |

|   |             | 4.2.5 Modeling AADL in TASM                                  | 96  |

|   |             | 4.2.6 Modeling AADL in ACSR                                  | 98  |

|   |             | 4.2.7 Modeling ARINC653 systems using AADL                   | 98  |

|   |             | 4.2.8 Modeling AADL in BIP                                   | 98  |

|   |             | 4.2.9 Modeling AADL in Lustre                                | 101 |

|   | 4.3         | Summary and comparison                                       | 103 |

|   | 4.4         | Conclusion                                                   | 104 |

| 5 | Fron        | n AADL components to Signal processes                        | 105 |

|   | 5.1         | Transformation chain                                         | 107 |

|   | 5.2         | Transformation principles                                    |     |

|   | 5.3         | From abstract logical time to more concrete simulation time  |     |

|   |             | 5.3.1 Modeling computation latencies                         |     |

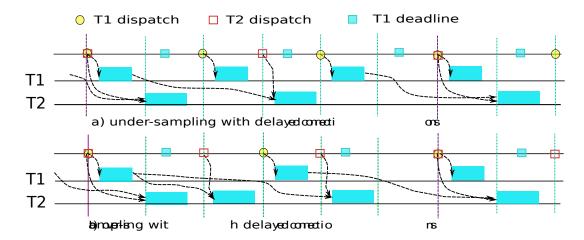

|   |             |                                                              | 112 |

|   |             | 5.3.3 Towards modeling time-based scheduling                 |     |

|   | 5.4         | $\boldsymbol{c}$                                             | 114 |

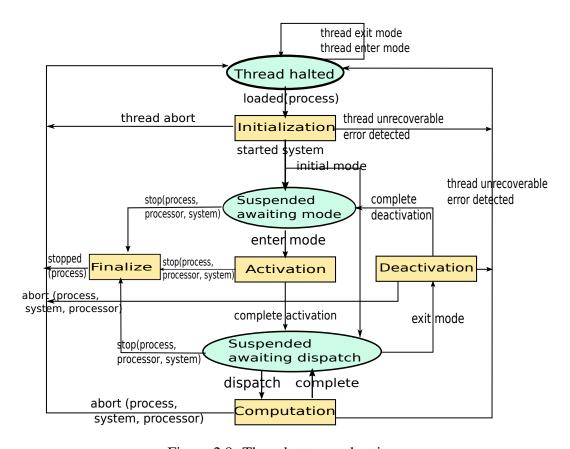

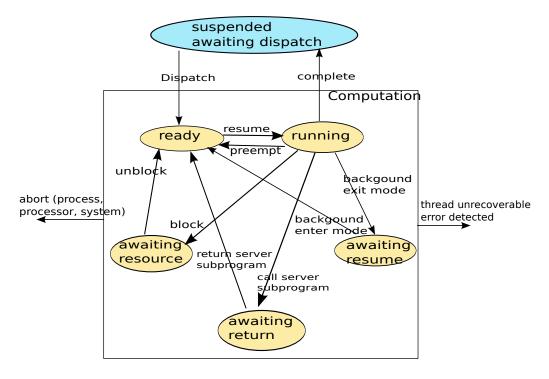

|   |             | 5.4.1 Interpretation of a thread                             |     |

|   |             | 1                                                            | 117 |

|   | 5.5         | Processor modeling                                           |     |

|   | 5.6         | Bus modeling                                                 |     |

|   | 5.7         | System modeling                                              |     |

|   | 5.8         | Other components modeling                                    |     |

|   |             | $\mathcal{E}$                                                | 130 |

|   |             | 1 6                                                          | 132 |

|   |             | $\varepsilon$                                                | 133 |

|   | <b>7</b> 0  |                                                              | 134 |

|   | 5.9         | Port and port connection modeling                            |     |

|   |             |                                                              | 135 |

|   | <b>5</b> 10 | $\mathcal{C}$                                                | 136 |

|   |             |                                                              | 139 |

|   | 5.11        | Conclusion                                                   | 140 |

| 6 |             | DL behavior specification                                    | 141 |

|   | 6.1         | Static Single Assignment (SSA)                               | 142 |

|   | 6.2         |                                                              | 143 |

|   |             |                                                              | 144 |

|   |             | 6.2.2 Transitions                                            | 144 |

|    |          | 6.2.3     | Actions                                         | 146         |

|----|----------|-----------|-------------------------------------------------|-------------|

|    | 6.3      | Interpr   | retation of transitions/actions                 | 148         |

|    |          | 6.3.1     | Step 1: actions to basic actions                | 149         |

|    |          | 6.3.2     | Step 2: basic actions to SSA form actions       |             |

|    |          | 6.3.3     | Step 3: SSA to Signal                           |             |

|    |          | 6.3.4     | Global interpretation                           | 162         |

|    | 6.4      | Case st   | tudy                                            | 162         |

|    | 6.5      | Conclu    | asion                                           | 165         |

| 7  | Dist     | ributed   | simulation model generation                     | 167         |

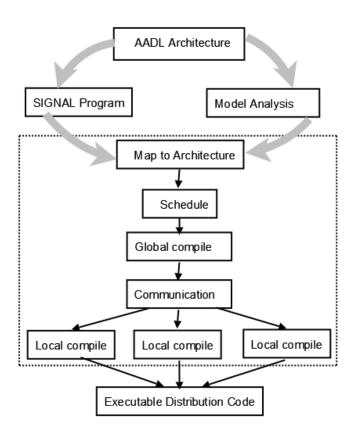

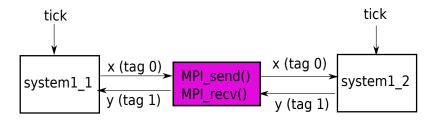

|    | 7.1      | Distrib   | outed code generation in Polychrony             | 167         |

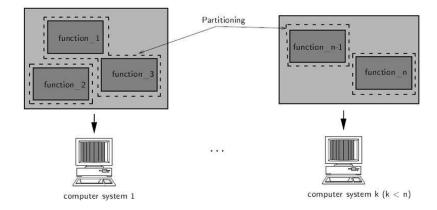

|    |          | 7.1.1     | Mapping                                         | 169         |

|    |          | 7.1.2     | Scheduler                                       |             |

|    |          | 7.1.3     | Adding communications                           |             |

|    | 7.2      | An exa    | ample                                           |             |

|    |          | 7.2.1     | System description                              | 177         |

|    |          | 7.2.2     | Modeling and Distributing the example in Signal |             |

|    | 7.3      | Conclu    | asion                                           | 181         |

| ττ | 7 17     | al: d a4: | 1an                                             | 83          |

| IV | <b>V</b> | alidati   | on 1                                            | .03         |

| 8  | Vali     | dation o  | of GALS systems                                 | 185         |

|    | 8.1      | Forma     | l verification                                  |             |

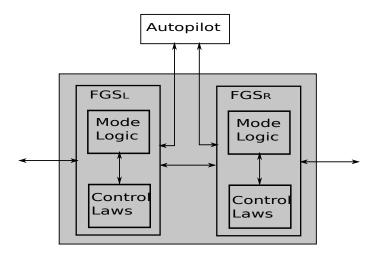

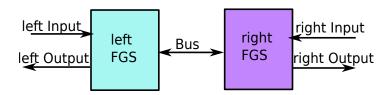

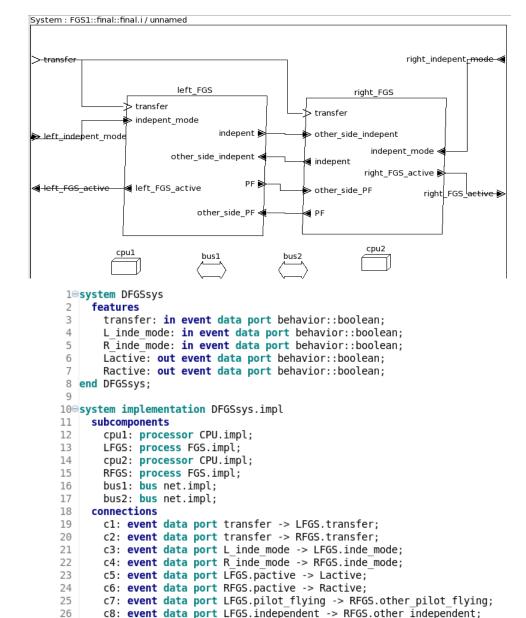

|    |          | 8.1.1     | Case study of a dual flight guidance system     |             |

|    |          | 8.1.2     | FGS Modeling in AADL                            |             |

|    |          | 8.1.3     | Interpreting the model in Signal                |             |

|    |          | 8.1.4     | Checking safety properties with Sigali          |             |

|    | 8.2      |           | ation                                           |             |

|    |          | 8.2.1     | Case study of a door management system          |             |

|    |          | 8.2.2     | System Modeling in AADL                         |             |

|    |          | 8.2.3     | Interpreting the model in Signal                |             |

|    |          | 8.2.4     | Other models and system integration             |             |

|    |          | 8.2.5     | Profiling                                       |             |

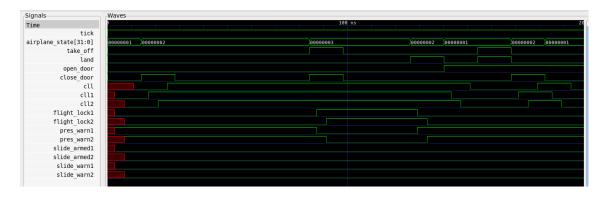

|    | 0.2      | 8.2.6     | VCD-based simulation                            |             |

|    | 8.3      | Conclu    | asion                                           | 201         |

| Co | onclus   | ion       |                                                 | 203         |

| Bi | bliogr   | aphy      |                                                 | 207         |

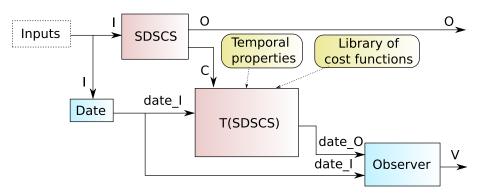

| A  | SDS      | CS exai   | mnle                                            | 219         |

|    | SDS      | CS exai   | inple 2                                         | <b>-1</b> / |

|    | A.1      |           | •                                               | 219         |

#### **CONTENTS**

| B | FGS | example               |  |  |  |  |  |  |  |  |  |  |  |  |  | 229 |

|---|-----|-----------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|-----|

|   | B.1 | AADL specifications   |  |  |  |  |  |  |  |  |  |  |  |  |  | 229 |

|   | B.2 | Signal specifications |  |  |  |  |  |  |  |  |  |  |  |  |  | 231 |

## Introduction

This thesis aims at developing a methodology to model and verify globally asynchronous locally synchronous (GALS) systems in an integrated modular avionics (IMA) design framework. This methodology consists of composing the synchronous models of individual processes according to the asynchronous model of an architecture. The resulting model can be simulated and verified using multi-clocked synchronous toolkits such as the Polychrony environment. Translations of heterogeneous models to polychronous models have been designed and implemented.

#### The modeling of real-time embedded systems

An embedded system [151, 48] is a computing system designed to perform dedicated functions often with real-time computing constraints. It is embedded as part of a complete device including electronic parts and mechanical parts. Nowadays, embedded systems can be found everywhere in our daily life and are often used to perform safety critical functions [105, 77] in domains such as avionics, automobile and telecommunications.

A real-time embedded system [150, 76] is one whose actions are subject to precise timing deadlines. A real-time system responds to periodic and sporadic input events (from, e.g., sensors) by timely calculating and performing output actions (on, e.g., actuators). Failing to respect deadlines may compromise correctness and have severe consequences [108]. One common example real-time software is that embedded within the ABS of modern cars. While the car is braking, the ABS periodically monitors speed (of the car, of the wheel) and may sporadically command to release the brake in order to prevent the wheel to lock while the car is not stopped. In other words, a real-time embedded system [96, 103, 150] is defined as a system whereby the correctness of the system depends not only on the logical result of computations, but also on the time at which the result is produced [150].

Examples of real-time embedded systems are aircraft engine control systems, nuclear monitoring systems and medical monitoring equipment, in which many embedded components (like the ABS) are operating and communicating in real-time. They are becoming more and more complex. This increasing complexity presents new challenges for system design: embedded systems can be constrained in time but also in size, power consumption or cost.

Model-based engineering enables the designers to deal with these concerns using the architecture description of the system as the main axis during the design phase.

Some of the classical design methodologies for real-time embedded systems are: structured analysis and design methods [160], object-oriented analysis and design meth-

ods (UML [30]) and formal system specification and design methods (SDL [32], Estelle [156, 79]).

Defining the architecture of the system before its implementation enables the analysis of the constraints imposed on the system from the beginning of the design cycle until the final implementation. Formal languages have been developed to support such architectural descriptions. They are known as architectural description languages (ADLs [129, 128, 131, 31, 4, 141]), modeling the system as a set of components and the interactions among them. One of the main ADLs currently used in avionics industry in system design for embedded systems is AADL (Architecture Analysis and Design Language) [1, 28, 41, 80].

AADL is developed as a new methodology for embedded system design, which was proposed around 2004. In AADL, the general purpose computing hardware, such as memories, processors, buses, etc., can all be modeled by software, which provides more flexibility. This modeling aspect of system design activity is becoming increasingly essential, since it allows prototyping and experiments without necessarily having a physical implementation of the system. This gives AADL a higher flexibility in design choices, lower cost, earlier decisions and fast to be adapted to new applications. Moreover, component-based approaches provide a way to significantly reduce overall development costs through modularity and re-usability. Thanks to this technology, a single AADL model can specify and analyze real-time embedded and high dependability systems, and map software onto computational hardware elements.

The AADL can model locally synchronous systems as well as asynchronous systems. The synchronous pattern consists of periodic threads which are logically simultaneous at every global real time. While for a globally asynchronous system, there are multiple reference times, for example, the threads executed on different clock processors, they represent different synchronization domains. This Globally Asynchronous Locally Synchronous (GALS) [71] model can be reflected in AADL by multiple synchronization domains and the asynchronous communications across synchronization domains.

#### From synchronous to GALS systems

#### The synchronous model

The synchronous assumption [50] was proposed in the late 80s for modeling, specifying, validating and implementing reactive and real-time system applications in an efficient and convenient way.

A synchronous model [52, 51, 93] follows the basic assumptions: first, the computations and internal communications are abstracted as instantaneous actions: they have a zero logical duration. Second, logical time is presented as a succession of events: it is handled according to a partial order over classes of simultaneous events; there is no explicit reference to a notion of physical time.

The synchronous model has had major successes due to several advantages: synchronous languages have formal and clear semantic definition, synchronous parallel composition reduces programming complexity and is useful for structuring programs, and many verification methods have been developed on the synchronous framework.

A synchronous system is viewed through the chronology and simultaneity of observed events during its execution. This is a main difference from classical approaches where the system execution is rather considered under its chronometric aspect (i.e., duration has a significant role). The mathematical foundations of the synchronous approach provide formal concepts that favor the trusted design of embedded real-time systems [88].

Typical synchronous languages are: Signal [115, 54, 90, 114], Lustre [92, 95] (data-flow synchronous languages), and Esterel [55, 162] (state based language). The three languages are built on a common mathematical framework that combines synchrony (i.e., time advances in lockstep with one or more clocks) with concurrency (i.e., functional concurrency) [52]. These synchronous languages benefit from the simplicity of the synchronous assumption.

#### The asynchronous model

An asynchronous system [145, 46, 91] is one to which a request is sent out and does not need to wait for a response. If a response is generated, notification from the system is received once it is complete. No global clock exists in the asynchronous paradigm.

An asynchronous system is represented by a program, which consists of a denumerable number of tasks. Under the control of a particular device, e.g., real-time operating system, these tasks run concurrently to achieve the system functions. The temporal logic of the system behavior is strongly influenced by the execution platform. The length of the logical execution of the task is unknown, which induces non-determinism [83].

In contrast to the synchronous model, the asynchronous model has the following characteristics [51]:

- Reactions (programs progress via an infinite sequence of reactions) can not be observed any more. Since no global clock exists, global synchronization barriers which indicate the transition from one reaction to the next one are no more observable.

- 2. Composition occurs by means of interleaving flows shared between two processes.

This paradigm is much closer to distributed architectures than synchrony. It only requires communication channels to respect the condition that an ordered stream of sent data reaches its destination in the same order. In the domain of distributed systems, asynchronous languages (e.g., SDL [32], Ada [5]) are naturally and variously used. An asynchronous model may be used simply for the interfacing of a synchronous system to its environment and to other synchronous systems, or possibly for more complete applications. Examples of asynchronous systems are distributed computer networks and I/O systems for conventional computers.

#### The GALS model

The synchronous model turns out to be difficult to satisfy certain embedded systems' requirements, especially large distributed real-time systems. Providing a fully synchronized clock over multiple distributed nodes may make the model synchronization very

expensive and actually infeasible. Thus, a combination of synchronous and asynchronous design patterns is required.

Recent approaches introduce a growing amount of asynchrony, a mix of synchronous and asynchronous design patterns. This situation has been known as GALS (Globally Asynchronous Locally Synchronous [71, 134, 66]), which was proposed by Chapiro in 1984 [71]. Gathering the benefits of both the synchronous and asynchronous approaches, the GALS model is emerging as an architecture of choice for implementing complex specifications in both hardware and software. It is composed of several independent synchronous components which operate with their own local synchronous clocks, and connected through asynchronous communication schemes. In circuit design, it relates to the modeling of small synchronous blocks communicating asynchronously. In software design, it relates to finite automata that communicate with registers.

The main feature of these systems is the absence of a global timing reference and the use of several distinct local clocks, possibly running at different frequencies. Thus, unlike for a purely asynchronous design, the existing synchronous tools can be used for most of the development process, while the implementation can exploit the more efficient asynchronous communication schemes.

The idea of the GALS approach is to combine the advantages of synchronous and asynchronous design methodologies while avoiding their disadvantages: the clock distribution in a GALS circuit can be realized easier than in a synchronous circuit. A GALS model is easier to implement than a synchronous model, particularly when different components are distributed far away or that their computation speed is very high. Another advantage of the GALS implementation, specifically in the case of embedded systems, is the electric consumption. A distributed GALS system consumes less than its equivalent synchronous system, because each component can adjust its operation speed by reporting its workload, even pause when not seeking. In a synchronous system, the components can operate at different but constant speeds. Moreover, at each cycle, each component is active even if there is no data to be processed.

#### **Existing problems and our solution**

GALS designs have emerged in the recent years in response to the above mentioned challenges and have received major attention from the system level design community [134, 66]. However, developing separately synchronous software components and deploying them on the target architecture using classical design methods for asynchronous systems, it is difficult to validate the integrated system. The problem of validating the whole system is crucial: the execution of the software on the target architecture is generally asynchronous, but this phase of the design is the most error-phone. The validation can be performed by testing the implementation, however, this will result in later error detection. Further more, testing an asynchronous implementation is difficult.

In this thesis, we propose a methodology of modeling and validating of globally asynchronous composition of synchronous components in a multi-clock synchronous programming framework, Polychrony, especially in an IMA [39, 37] design architecture. A main goal of such an approach is to study properties of globally asynchronous systems using existing simulation and model-checking toolkits for the synchronous framework.

In order to support the virtual prototyping, simulation and formal validation of early, component-based, embedded architectures, we define a model of the AADL into the polychronous model of computation of the Signal programming language.

Our solution can be seen as a transformation of the design of asynchronously connected local synchronized components to a synchronous model. Since it may be non trivial to represent adequately asynchrony and non-determinism in a synchronous framework, we propose a method to use existing techniques and libraries of the Signal environment, consisting of a model of the APEX-ARINC-653 [37] real-time operating system services. It provides a suitable and adequate library to model embedded architectures in the specific case of Integrated Modular Avionics (IMA). This framework is the one considered in the TopCased [29] project.

#### Related works

Synchronous modeling of asynchronous systems is also studied in [94]. The authors define a generic semantic model for synchronous and asynchronous computation, after that, the attention is focused on implementing communication mechanisms.

There are also some tools to modeling non-synchronous systems using synchronous languages and developing system level design methodology:

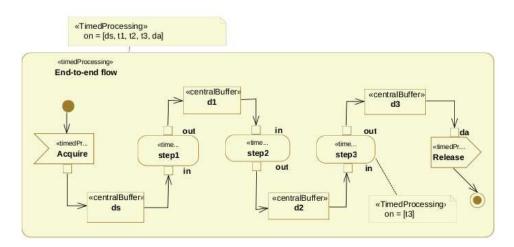

- [124] relies on the MARTE [14] Time Model and the operational semantics of its companion language CCSL [142], to equip UML activities with the execution semantics of an AADL specification. It investigates how MARTE can be made to represent AADL periodic/aperiodic tasks communicating through event or data ports, in an approach to end-to-end flow latency analysis.

- AADL2Fiacre [56] deals with the transformation of AADL models into Fiacre [56] models to perform formal verification and simulation.

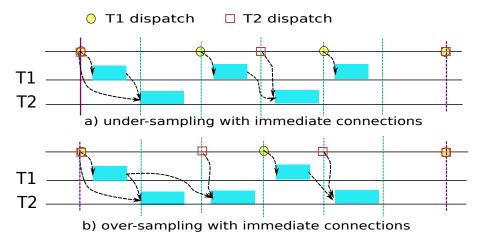

- AADL2BIP [138] models AADL data communication with BIP (Behavior Interaction Priority [7]). It focuses on deterministic data communication, and shows how BIP deals with the modeling of immediate and delayed data communications supporting undersampling and oversampling of AADL.

- [140] proposes a formal semantics for the AADL behavior annex using Timed Abstract State Machine (TASM [135]). A semantics of AADL execution model is given, and a prototype of behavior modeling and verification is proposed.

- AADL2SYNC [3] is an AADL to synchronous programs translator, which is extended in the framework of the European project ASSERT, resulting in the system-level tool box translating AADL to LUSTRE.

#### **Polychrony**

Polychrony is a framework based on Signal, a domain-specific, synchronous data-flow language dedicated to embedded and real-time system design [113]. While being declarative like Scade or Lustre, and not imperative like Esterel [72], its multi-clocked model

of computation (MoC) stands out by providing the capability to design systems where components own partially related activation clocks. This polychronous MoC is called *polychrony* [115].

The main characteristic of Polychrony is that it can be used to describe systems that contain components, which work at different or even independent clocks. Instead of requiring the user to define a global clock, Polychrony calculates clock trees, that result from the different clock dependencies expressed in the description.

Polychrony provides models and methods for a rapid, refinement-based, integration and a formal conformance-checking of GALS architecture. It contains tools for properties verification, and integrates the Signal compiler, which is able to generate sequential code or distributed code in some conditions, and it also includes a graphical user interface for Signal. It goes beyond the domain of purely synchronous circuits to embrace the context of architectures consisting of synchronous circuits and desynchronization protocols.

In the Polychrony workbench, time is represented by partially ordered synchronization and scheduling relations, to provide an additional ability to model high-level abstractions of systems paced by multiple clocks: locally synchronous and globally asynchronous systems. This gives the opportunity to seamlessly model heterogeneous and complex distributed embedded systems at a high level of abstraction, while reasoning within a simple and formally defined mathematical model.

In Polychrony, design can proceed in a compositional and refinement-based manner by first considering a weakly timed data-flow model of the system under consideration, and then providing expressive timing relation to gradually refine its synchronization and scheduling structure to finally check the correctness of the assembled components. Signal favors the progressive design of correct by construction systems by means of well-defined model transformations, that preserve the intended semantics of early requirement specifications to eventually provide a functionally correct deployment on the target architecture.

As mentioned earlier, the multi-clock polychronous model differs from other synchronous specification models by its capability to allow the design of systems, where each component holds its own activation clock as well as single-clocked systems in a uniform way. A great advantage is its convenience for component-based design approaches that allow modular development of increasingly complex modern systems.

Polychrony provides the ability to model and build GALS systems in a fully synchronous design framework, and deploy it on an asynchronous network preserving all properties of the system proven in the synchronous framework. Thanks to the polychronous approach, bounded FIFOs [86] are provided for communications between synchronous components, allowing to find a desynchronizing protocol to formally investigate the behavior of synchronous components in an asynchronous environment [133, 75].

#### Contribution

This thesis focuses on the modeling and validation of AADL systems in a multi-clock synchronous programming framework, Polychrony, especially in a IMA design architecture. The synchronous modeling and high-level validation, which are based on the synchronous language Signal, are the main contributions of this thesis.

We define a translation based on the semantics of AADL into the polychronous model

of computation of the Signal programming language. This solution can be seen as a transformation of the design of asynchronously connected local synchronized components to a synchronous model.

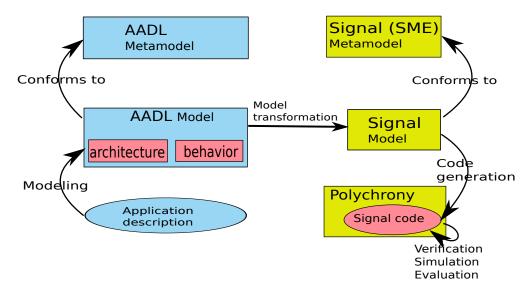

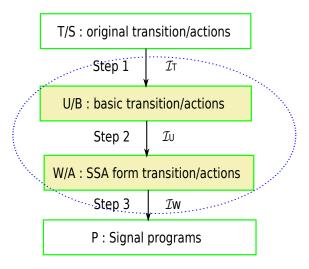

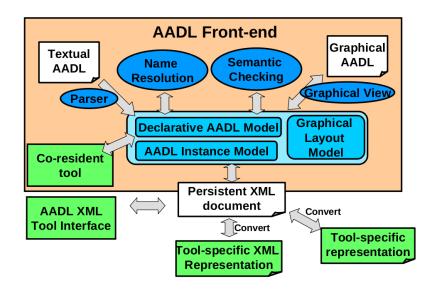

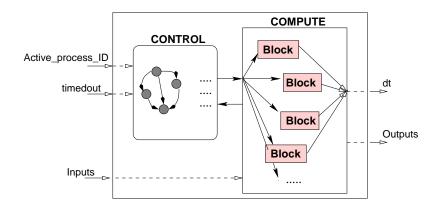

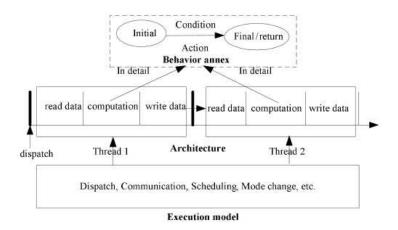

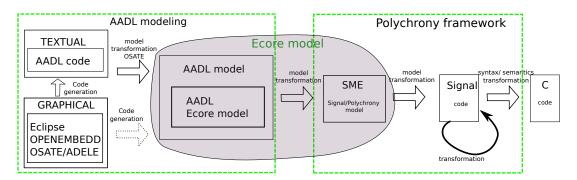

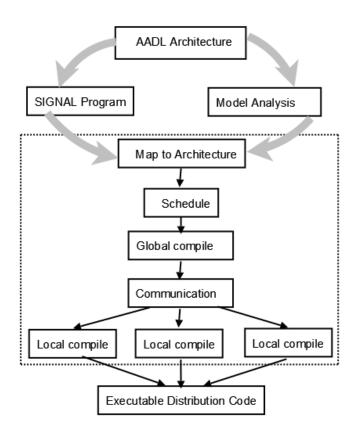

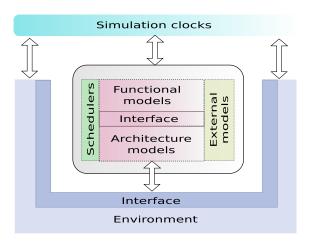

Figure 1: A global view of the approach

A global view of the transformation is illustrated in Figure 1. It starts from using the AADL language to model real-time applications, which may be represented from an initial textual description. Then by giving the semantics of AADL components in the polychronous model of computation, the AADL model is transformed into Signal model. Finally, Signal code is generated, and verification, simulation and other analyses are performed.

Since there are some difficulties in representing asynchrony and non-determinism in a synchronous framework, we propose to use existing techniques and libraries of the Signal environment [84, 85, 87], consisting of a model of the APEX-ARINC-653 [37] real-time operating system services. Consequently, the components can be translated into or projected onto different APEX-ARINC services.

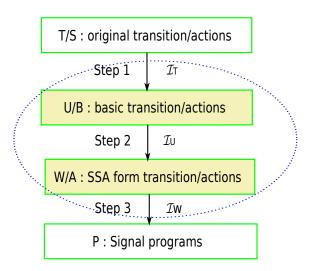

AADL has been extended to describe complex behaviors without introducing external source code, by the Behavior Annex. To implement a complete system specification, we also translate the behaviors into synchronous equations. We formalize the semantics of the actions and transitions, and interpret them using SSA as an intermediate formalism [61, 154]. In this interpretation, we show not only how to translate the core imperative programming features into Signal equations, but also extend it to the mode automata that control the activation of such elementary transitions and actions.

Signal-Meta Under Eclipse (SME) [24] is the model-driven front-end of Polychrony framework. It provides the meta-model on which Signal model is based. The resulting Signal model generated from this transformation conforms to the SME meta-model. High-level validation is then carried out with the generated Signal code in order to check the correctness of the corresponding AADL specifications.

The implementation of the transformation has been carried out in the framework of OpenEmbeDD [17], which is an Eclipsed-based "Model Driven Engineering" platform dedicated to embedded and real-time systems.

Introduction

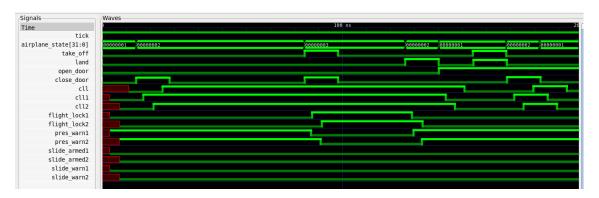

All the preceding studies have been experimented with the Polychrony toolset. A case study of door management system is finally illustrated, with emphasis on the high-level modeling through AADL, and the simulation and formal validation through the tools associated with the Signal language.

#### **Outline**

In the present document, we propose a methodology to model and verify a GALS system in a polychronous framework. This method transforms the AADL model using the IMA architecture to Signal model. This dissertation has four parts:

#### Part I

Part I gives an extended abstract in French.

**Chapter 1.** The first chapter presents an extended abstract of this thesis in French. Each section presents an abstract of the corresponding chapter.

#### Part II

Part II presents the background. It has two chapters.

**Chapter 2.** This chapter introduces the AADL language. AADL is an SAE standard aimed at high level design and evaluation of the architecture of embedded systems. We introduce the components and behaviors of AADL. The IMA architecture and the ARINC standard, especially the ARINC653 specification which defines an APplication EXecutive (APEX) for space and time partitioning, are presented in this chapter.

**Chapter 3.** Chapter 3 is related to the Signal language. It first introduces the model of Signal. It starts with an introduction of polychronous model of computation, and then continues with a specification of the syntax and semantics of the Signal language. The modeling library of IMA ARINC applications in Signal is also presented.

#### **Part III**

Part III exhibits our contributions for modeling, prototyping and implementation, which includes four chapters.

**Chapter 4.** Chapter 4 reviews related works. It proposes an overview of existing AADL models and transformations. A brief comparison of these works is given in this chapter.

**Chapter 5.** Chapter 5 describes the modeling of AADL specifications into the polychronous model using APEX-ARINC services in the IMA framework. The general modeling approach and transformation principles are first presented. Then the problems in AADL to Signal transformation are depicted, and solutions are given. The transformation of a subset of AADL components is described, including the main executable and schedulable component, the thread, the component responsible for scheduling, the processor, and communication components, bus, etc. Apart from the component modeling, two types of data port communication are also represented in Signal.

**Chapter 6.** In Chapter 6, we present the transformation of AADL behavior specification, mainly for the transitions and actions. This interpretation uses SSA as an intermediate formalism. It gives a thorough description of an inductive SSA transformation algorithm across transitions and actions that produces synchronous equations.

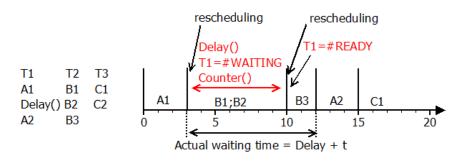

**Chapter 7.** Chapter 7 focuses on the distribution. The principles that generate distributed Signal from the AADL specification are presented. Then the scheduler and communication between the distributed programs are described. A case study is given to explain the distribution.

#### **Part IV**

Part IV contains one chapter about verification and simulation.

**Chapter 8.** Chapter 8 presents the verification and simulation of GALS systems in the case of our considered approach from AADL. We present the static resolution and dynamic model-checking techniques that come with the Polychrony environment to verify the functional requirements of the system. A case study of dual flight guidance system is presented, which gives formal verification. Then another case study of door management system is given, which illustrates the implementation of the proposed transformation of AADL and the simulation.

**Conclusion.** We conclude the thesis and discuss some perspectives of these works.

## Part I Résumé en français

## **Chapter 1**

## Résumé en français

#### 1.1 Introduction

Les systèmes embarqués se rencontrent aujourd'hui partout, y compris dans la vie quotidienne, et sont souvent utilisés pour effectuer des tâches critiques [105, 77] dans des domaines tels que l'avionique, l'automobile et les télécommunications. Un système embarqué temps réel [150, 76] est un système dont les actions sont assujetties à des délais temporels. Un système temps réel répond à des événements d'entrée périodiques ou sporadiques (par exemple, à partir de capteurs) par le calcul et l'exécution d'actions permettant de produire des sorties (par exemple, sur des actionneurs). Un défaut de respect des délais peut compromettre l'exactitude des résultats et avoir des conséquences graves (temps réel strict) [108].

Le langage AADL (Architecture Analysis and Design Language) est proposé comme support à une nouvelle méthodologie pour la conception de systmes embarqués. En AADL, la partie matérielle, tel que mémoires, processeurs, bus, etc, peut être modélisée sous forme logicielle, ce qui offre une plus grande souplesse car cela permet des prototypages et expérimentations sans nécessairement disposer d'une implantation physique du système. En outre, les approches à base de composants, comme c'est le cas en AADL, fournissent un moyen de réduire considérablement les coûts de développement via la modularité et la réutilisation de composants.

Le modèle synchrone a obtenu des succès majeurs dans les systèmes temps réel en raison d'un certain nombre d'avantages : les langages synchrones sont basés sur une définition sémantique précise et claire ; la composition parallèle synchrone réduit la complexité de programmation et est utile pour structurer les programmes ; et de nombreuses méthodes de vérification ont été développées dans le cadre synchrone.

Les approches les plus récentes tendent à introduire dans les modèles un nombre croissant d'éléments asynchrones, tout en essayant de préserver les bonnes propriétés des modèles synchrones. On obtient ainsi un mélange de modèles de conception synchrones et asynchrones, comme par exemple le modèle GALS (Globalement Asynchrone Localement Synchrone [71, 134, 66]). Rassemblant les avantages des deux approches, synchrone et asynchrone, le modèle GALS est en train de devenir une architecture de choix pour la mise en œuvre de spécifications complexes à la fois matérielles et logicielles.

Les approches GALS sont l'objet d'une attention particulière de la part de la communauté des concepteurs au niveau système [134, 66]. Le problème de la validation de

l'ensemble du système est essentiel : l'exécution du logiciel sur l'architecture cible est généralement asynchrone, mais cette phase de la conception est la plus sujette aux erreurs. La validation peut être effectuée au moyen de tests de la mise en œuvre, cependant, cela implique une détection tardive des erreurs. De plus, tester une implémentation asynchrone pose des problèmes de non déterminisme.

Dans cette thèse, nous proposons une méthodologie de modélisation et de validation de la composition globalement asynchrone de composants synchrones. Nous nous plaçons dans le cadre de la programmation synchrone multi-horloge, ou *polychrone*, en considérant plus particulièrement les architectures de type IMA [39, 37]. Un des principaux objectifs de l'approche est d'étudier les propriétés des systèmes globalement asynchrones en utilisant des outils de simulation et de vérification de modèle (*model-checking*) existant dans le cadre synchrone. Pour permettre le prototypage virtuel, la simulation et la validation formelle au plus tôt des architectures embarquées à base de composants, nous définissons une modélisation de AADL dans le modèle de calcul polychrone du langage de programmation Signal.

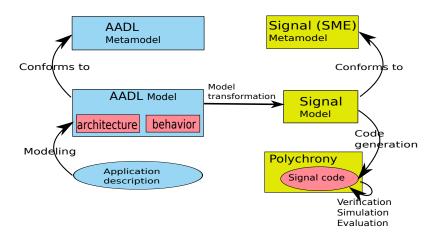

Notre solution peut être considérée comme une transformation d'une conception en composants localement synchronisés connectés de façon asynchrone, vers un modèle synchrone. Une vision globale de la transformation est illustrée sur la figure 1.1. On utilise en premier lieu le langage AADL pour modéliser une application temps réel, qui peut être représentée à partir d'une description textuelle initiale. Étant donné la sémantique des composants AADL dans le modèle de calcul polychrone, le modèle AADL est alors transformé en modèle Signal. À partir de ce modèle, un programme Signal est généré, et l'outil Polychrony peut être utilisé pour effectuer de la vérification, des simulations et d'autres analyses.

Figure 1.1: Vision globale de l'approche.

Sachant qu'il peut être non trivial de représenter de façon adéquate l'asynchrone et le non déterminisme dans un cadre synchrone, nous proposons une méthode qui utilise des techniques et des bibliothèques existant dans l'environnement de Signal, consistant notamment en un modèle des services du système d'exploitation temps réel APEX-ARINC-653 [37]. Nous disposons ainsi d'une bibliothèque permettant de modéliser des architectures embarquées dans le cadre IMA.

## 1.2. INTRODUCTION AU LANGAGE AADL ET AUX ARCHITECTURES AVIONIQUES

## 1.2 Introduction au langage AADL et aux architectures avioniques

#### 1.2.1 Abstractions du langage AADL

Le langage AADL est une norme de la SAE, qui a été défini pour les systèmes embarqués critiques temps réel. Il doit rendre possible l'utilisation d'approches formelles diverses pour l'analyse de systèmes constitués de composants matériels et logiciels.

**Catégories de composants** Pour modéliser les systèmes embarqués complexes, AADL fournit trois catégories de composants : composants logiciels, composants de plate-forme d'exécution et composants "composites".

- Les données, les sous-programmes, les "threads" et les processus représentent collectivement le logiciel d'une application ; ils sont appelés composants logiciels.

- Les composants de la plate-forme d'exécution comprennent les processeurs, les dispositifs (*device*), les mémoires et les bus. Ils supportent l'exécution des threads, le stockage des données et du code, et la communication entre les threads.

- Les systèmes sont appelés composants composites. Ils permettent d'organiser en structures hiérarchiques avec des interfaces bien définies les composants logiciels et les composants de la plate-forme d'exécution.

Types et implémentations de composants Les composants AADL sont définis par des déclarations de type et d'implémentations. Un type de composant représente l'interface fonctionnelle du composant et ses attributs observables de l'extérieur. Une implémentation décrit le contenu du composant, spécifie sa structure interne en termes de souscomposants, les connexions entre les éléments de ces sous-composants, les flots sur une séquence de sous-composants, les modes permettant de représenter les états de fonctionnement, et les propriétés.

**Propriétés** Une propriété spécifie des caractéristiques du composant qui s'appliquent à toutes les instances de ce composant, sauf si elles sont redéfinies dans des implémentations ou des extensions. Des valeurs peuvent être attribuées aux propriétés par des déclarations d'association de propriété.

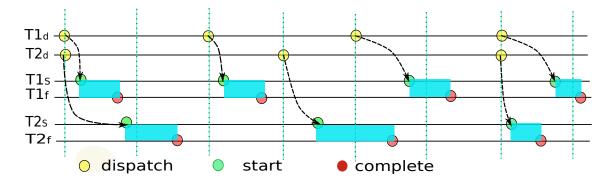

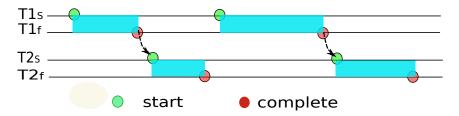

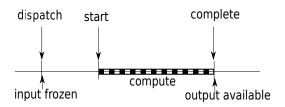

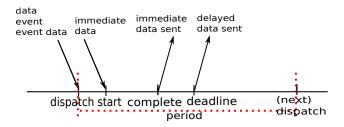

**Domaine temporel** Trois horloges  $(t_d, t_s, t_f)$  sont associées à chaque thread t. L'horloge  $t_d$  est l'horloge à laquelle le thread est "dispatché". Si le port prédéfini **dispatch** est connecté, l'arrivée d'un événement sur ce port entraîne le dispatch du thread. L'horloge  $t_s$  est l'horloge à laquelle le thread démarre, et  $t_f$  est l'horloge à laquelle le thread se termine. Ces deux horloges peuvent être spécifiées respectivement par les propriétés **Input\_Time** et **Output\_Time**. De nombreuses autres caractéristiques temporelles, par exemple l'échéance, le temps d'exécution, le temps de transmission, etc., peuvent être spécifiées par les propriétés définies dans AS5506 [41].

<sup>&</sup>lt;sup>1</sup>Nous gardons ici le terme anglais plutôt que "fil d'exécution" ou "tâche".

#### 1.2.2 Annexe comportementale de AADL

L'annexe comportementale (*Behavior Annex*) de AADL [74] est une extension au noyau du standard qui fournit un moyen de spécifier le comportement fonctionnel local des composants. Elle permet une description précise des comportements, tels que les calculs, les communications au moyen des ports, etc. Une annexe comportementale peut être attachée à un thread ou à un sous-programme. Les threads et les sous-programmes démarrent à partir d'un état initial, et une transition vers un état final (resp., un état de retour) termine le thread (resp. le sous-programme). Les transitions peuvent être gardées par des conditions, et des actions peuvent y être attachées.

#### 1.2.3 Architecture avionique et ARINC 653

**Architecture IMA** Une caractéristique forte des architectures IMA [39] est le fait que plusieurs applications avioniques peuvent être hébergées sur un seul système, partagé. Ces applications sont assurées d'une allocation statique sécurisée des ressources partagées, de sorte qu'aucune propagation de faute ne se produise d'un composant à un autre. Ce problème est adressé au moyen d'un *partitionnement* fonctionnel des applications selon la disponibilité des ressources en temps et en mémoire [37].

Une partition est composée de processus qui représentent les unités d'exécution. Chaque processus est caractérisé par des informations utiles à l'OS de niveau partition, responsable de l'exécution correcte des processus dans une partition. Des mécanismes appropriés sont prévus pour la communication et la synchronisation entre processus (par exemple, buffers, événements, sémaphores) et entre partitions (par exemple, ports et canaux).

La norme avionique ARINC définit les principes de base du partitionnement, ainsi qu'un ensemble de services, conformes à l'architecture IMA. L'interface APEX, définie dans la norme ARINC, comprend les services de communication et de synchronisation, et les services de gestion des *processus* et des *partitions*.

AADL et ARINC AADL peut être utilisé en particulier pour une modélisation conforme à ARINC. AADL et ARINC ont certaines caractéristiques similaires. La partition ARINC est proche du processus AADL. Le processus AADL représente un espace d'adressage protégé, un espace de partitionnement où une protection est assurée contre les accès d'autres composants à l'intérieur du processus. Ainsi, la partition ARINC et le processus AADL sont des unités du partitionnement. Les mécanismes de communication définis dans ARINC supportent les communications de messages en file et sans file. Cela est similaire aux connexions AADL. Une différence est que ARINC ne prend pas en compte, à ce niveau, la connexion matérielle par bus entre les différents composants.

#### 1.3 Langage Signal et modélisation ARINC en Signal

L'approche synchrone est l'une des solutions possibles pour une conception sûre des systèmes embarqués. Le modèle multi-horloge ou polychrone se distingue des autres modèles synchrones par son cadre uniforme. Il permet aussi bien la conception de systèmes

dans lesquels chaque composant dispose de sa propre horloge d'activation, que de systèmes mono-horloge. Cette caractéristique rend la sémantique de Signal plus proche de la sémantique de AADL que ne l'est celle d'autres modèles purement synchrones ou asynchrones. Cela facilitera ainsi la validation du système.

#### 1.3.1 Le langage Signal

Le langage flot de données synchrone Signal est dédié à la conception de systèmes embarqués dans des domaines d'applications critiques. Les caractéristiques propres au modèle relationnel qui sous-tend Signal sont d'une part de fournir la notion de polychronie — c'est-à-dire la capacité à décrire les circuits et les systèmes avec plusieurs horloges — et d'autre part de permettre le raffinement — autrement dit, la capacité à permettre la conception de système depuis les étapes initiales de spécification des exigences, jusqu'aux étapes finales de synthèse et de déploiement.

Signal est un langage relationnel qui s'appuie sur le modèle polychrone [58]. Signal manipule des suites non bornées de valeurs typées  $(x_t)_{t \in \mathbb{N}}$ , appelées signaux, notées x et indexées implicitement par les valeurs discrètes de leur horloge, notée  $\hat{x}$ . À un instant donné, un signal peut être présent ou absent. Deux signaux sont dits synchrones s'ils sont toujours présents (ou absents) aux mêmes instants.

En Signal, un processus (dénoté P ou Q) consiste en la composition synchrone (notée  $P \mid Q$ ) d'équations sur signaux (notées x := y f z). Une équation x := y f z définit le signal de sortie x par la relation sur ses signaux d'entrée y et z auxquels est appliqué l'opérateur f. Le processus P/x restreint la portée du signal x au processus y. La syntaxe abstraite d'un processus y en Signal est définie comme suit :

$$P, Q ::= x := y f z | P | Q | P/x$$

**Domaines temporels et communications en Signal** Nous discutons ici certains écarts et similitudes sémantiques entre AADL et Signal. Signal peut fournir un outillage à base d'opérateurs dérivés permettant de réduire les écarts.

- Outillage d'horloges. Les horloges peuvent être étroitement liées aux domaines temporels AADL et des opérateurs sont définis en Signal pour manipuler les horloges.

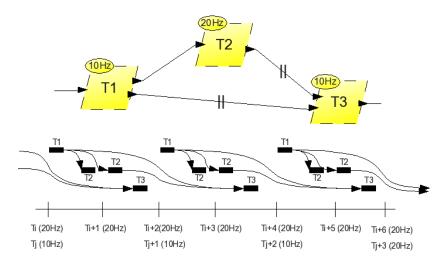

- Horloges périodiques en Signal. Des horloges périodiques peuvent être spécifiées en Signal à l'aide de relations affines sur les horloges. Dans Polychrony, le calcul d'horloges de Signal implémente des règles de synchronisabilité basées sur les propriétés des relations affines, et vis-à-vis desquelles les contraintes de synchronisation peuvent être examinées.

- Communications. Le principe de base de la communication en Signal est la diffusion, ce qui signifie qu'un signal donné est transmis comme plusieurs signaux identiques. Il est également possible en Signal d'avoir plusieurs signaux ou expressions associés à un signal donné, au moyen de définitions partielles.

- Outillage pour le report des communications. Le report des communications peut être implémenté en Signal à l'aide de cellules mémoire et de FIFO.

• Outillage pour briser l'atomicité. Pour un programme Signal, l'horloge la plus rapide d'un processus n'est pas toujours une horloge d'entrée : des instants nouveaux peuvent être insérés entre les instants existants. Le sur-échantillonnage permet la spécification de contraintes entre les entrées et les sorties de telle sorte qu'il ne puisse pas se produire de valeur d'entrée supplémentaire tant que les contraintes en question ne sont pas respectées par les calculs (intermédiaires) de la sortie [115].

#### 1.3.2 Modélisation de concepts ARINC en Signal

Les applications avioniques qui s'appuient sur la norme avionique ARINC 653, basée sur l'architecture IMA, peuvent être spécifiées dans le modèle de Signal. Une bibliothèque de services APEX ARINC est fournie en Signal. L'environnement de conception Polychrony comprend ainsi une bibliothèque Signal de composants correspondant aux services d'exécutif temps réel définis dans ARINC [37]. Cette bibliothèque, conçue par Abdoulaye Gamatié [83], s'appuie sur quelques blocs de base [84, 85], qui permettent de modéliser les *partitions*: il s'agit des services APEX-ARINC-653, d'un modèle de RTOS, et d'entités d'exécution.

**Services de l'APEX** Les services de l'APEX modélisés en Signal comprennent les services de communication et de synchronisation utilisés par les *processus* (par exemple, *SEND\_BUFFER*, *WAIT\_EVENT*, *READ\_BLOCKBOARD*), les services de gestion des *processus* (par exemple, *START*, *RESUME*), les services de gestion des *partitions* (par exemple, *SET\_PARTITION\_MODE*), et des services de gestion du temps (par exemple, *PERIODIC\_WAIT*).

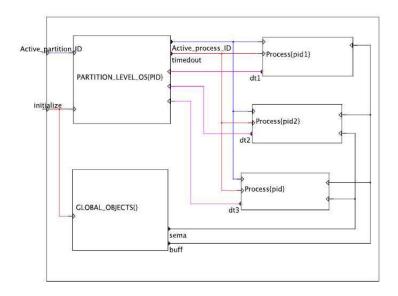

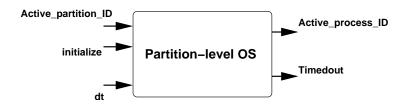

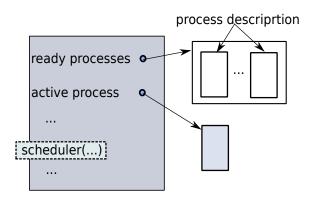

**OS** de niveau partition Le rôle de l'OS de niveau partition est d'assurer l'exécution correcte des processus dans une partition. Chaque fois que la partition s'exécute, l'OS de niveau partition sélectionne un processus actif dans la partition.

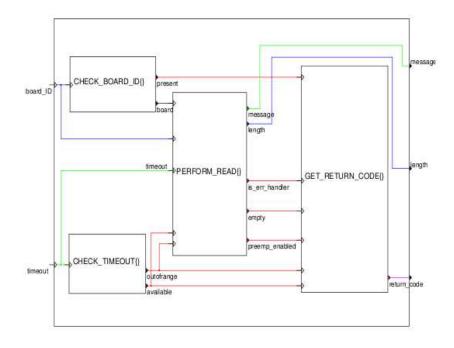

**Processus ARINC** La définition d'un modèle de *processus* ARINC en Signal prend en compte d'une part sa partie calcul et d'autre part sa partie contrôle. Le sous-composant CONTROL spécifie la partie contrôle du *processus*. Il s'agit d'un système de transition qui indique quelles instructions doivent être exécutées lorsque le modèle du *processus* est actif. Le sous-composant COMPUTE décrit les actions effectuées par le *processus*. Il est composé de *blocs* d'actions. Ces *blocs* représentent des pièces élémentaires de code à exécuter sans interruption. Les calculs associés à un *bloc* sont supposés *se terminer dans un laps de temps borné*.

**Partitions** Après la phase d'initialisation, la *partition* est activée (par exemple, lors de la réception d'un signal *Active\_partition\_ID*). L'OS de niveau partition sélectionne un processus actif dans la partition. Ensuite, la sous-partie CONTROL de chaque processus vérifie si le processus concerné peut s'exécuter. L'exécution du modèle de la partition suit ce schéma de base jusqu'à ce que l'OS de niveau module sélectionne une nouvelle partition à exécuter.

#### 1.4 Travaux reliés : formalisations de AADL

Le langage AADL fournit un bon support pour la description et l'analyse de systèmes embarqués complexes. Afin de valider des propriétés formelles sur un modèle AADL, d'effectuer des analyses d'ordonnançabilité ou de performance, d'effectuer de la vérification, un cadre formel qui puisse fournir des diagnostics sur le système doit être défini et utilisé. Un tel objectif ne peut être atteint que si l'on peut transformer le modèle AADL dans un autre modèle, dont les outils associés offrent ces fonctionnalités. Nous donnons ici un bref apercu de quelques transformations de AADL.

- L'utilisation de MARTE pour modéliser AADL a concerné principalement les deux protocoles de communication, immédiat et retardé, dans l'optique d'une analyse de la latence sur les flots "end-to-end". Ce travail s'efforce de construire un simulateur générique pour AADL, mais l'objectif d'un langage analysable formellement reste une perspective [119].

- La modélisation de AADL en Fiacre se concentre sur un objectif de vérification de modèle [56]. Par rapport à BIP, Fiacre a des constructions moins puissantes mais il a de bonnes propriétés au niveau de la compositionnalité et du temps réel.

- La traduction de AADL vers BIP permet la simulation de modèles AADL, ainsi que l'application de techniques de vérification. L'absence de localité dans BIP rend difficile le raisonnement compositionnel [138].

- La modélisation de AADL en TASM permet de présenter la sémantique temporelle de l'annexe comportementale de AADL en utilisant TASM. TASM dispose de mécanismes de consommation de ressources plus abstraits, mais prend difficilement en compte certains modèles d'ordonnancement [140].

- La traduction référencée de AADL vers SystemC vise la simulation et l'analyse de performances. Cependant, les spécifications de comportement n'ont pas été prises en considération [157].

- L'objet de la génération de code C depuis AADL développée dans Ocarina est de cibler des applications distribuées à haute intégrité. Avec l'outil PolyORB-HI-C, des blocs Simulink peuvent être utilisés comme sous-programmes AADL [?]. Une transformation de blocs Simulink (utilisés en tant que threads AADL) en Signal est également implémentée dans notre travail coopératif effectué dans le cadre du projet CESAR [35]. Nous utilisons AADL pour modéliser l'architecture et Simulink pour modéliser les parties fonctionnelles.

- L'objectif de la modélisation de ARINC653 à l'aide de AADL est de proposer un processus approprié de développement de type MDE permettant de saisir et de prendre en compte les exigences architecturales en utilisant AADL et son annexe ARINC653 [73]. Cette approche modélise des architectures ARINC653 en AADL, alors que notre travail consiste en une démarche inverse : nous modélisons un système AADL en Signal dans un cadre ARINC653.

• L'objectif principal de AADL2SYNC est d'effectuer une simulation et une validation qui prennent en compte à la fois l'architecture du système et les aspects fonctionnels. Ce travail construit un simulateur exprimé dans un langage purement synchrone : Lustre. Un protocole de communication quasi-synchrone est utilisé pour émuler l'asynchronisme et remédier ainsi aux limitations dues au caractère purement synchrone ; néanmoins sa capacité d'expression reste limitée [3, 99].

Par rapport à ces travaux, notre approche a des objectifs multiples. Nous modélisons un système AADL en Signal afin d'effectuer de la vérification formelle (en utilisant Sigali), de la simulation (en utilisant VCD), et de la génération de code C/Java, puisque le modèle polychrone du langage Signal offre en effet un support formel pour l'analyse, la vérification, la simulation et la génération de code, mises en œuvre dans la plate-forme Polychrony. En outre, le modèle polychrone fournit des modèles et des méthodes pour l'intégration rapide, basée sur le raffinement, et la vérification formelle de conformité des architectures GALS [152].

## 1.5 Modélisation de composants AADL en processus Signal

Cette section se concentre sur la modélisation synchrone des composants AADL dans une architecture IMA, de sorte qu'un modèle AADL puisse être traduit en un modèle exécutable du langage flot de données polychrone Signal. Cette modélisation est une contribution qui doit aider à combler le fossé existant entre modèles asynchrones et synchrones.

#### 1.5.1 Chaîne de transformation

Notre transformation de modèles AADL en spécifications synchrones est séparée en deux étapes : d'une part, la transformation elle-même, des modèles AADL vers des modèles synchrones, puis la génération de code synchrone à partir des modèles synchrones obtenus à la première étape.

Nous formalisons la transformation de AADL en isolant les catégories syntaxiques de base qui caractérisent ses capacités expressives : systèmes, processus, threads, sousprogrammes, données, dispositifs, processeurs, bus et connexions.

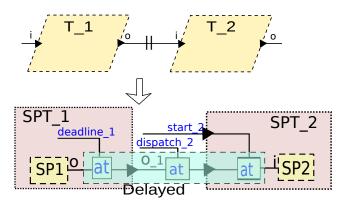

Figure 1.2: Vue globale de la chaîne de transformation AADL-SME/Signal.

#### 1.5. MODÉLISATION DE COMPOSANTS AADL EN PROCESSUS SIGNAL

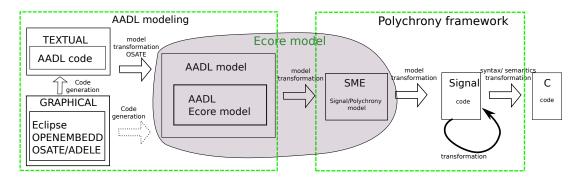

La figure 1.2 illustre la chaîne de transformation semi-automatique d'un modèle AADL vers un modèle Signal, jusqu'à la génération de code exécutable, en C ou Java par exemple. Dans la transformation, les modèles SME [24], qui sont conformes au métamodèle de Signal, sont considérés comme des modèles intermédiaires.

Le modèle ecore de AADL est traduit en un modèle SME/Signal en utilisant ATL (Atlas Transformation Language), dans lequel sont définies les règles de transformation. Le modèle SME peut ensuite être transformé en programme Signal. Le programme Signal est alors compilé et un code exécutable C (ou Java/C++) peut être généré.

#### 1.5.2 Principes de transformation

Cette transformation de modèle est basée sur l'étude des similarités entre AADL et les services APEX-ARINC. La transformation d'un modèle AADL vers Signal repose sur l'architecture IMA [121]. Les principes de base de la transformation de base sont présentés dans la table 5.1.

| AADL                          | Signal                                           |  |  |  |  |  |

|-------------------------------|--------------------------------------------------|--|--|--|--|--|

| thread                        | processus ARINC                                  |  |  |  |  |  |

| processus                     | partition ARINC                                  |  |  |  |  |  |

| port                          | FIFO bornée                                      |  |  |  |  |  |

| connexion de ports de données | processus Signal (selon le type de la connexion) |  |  |  |  |  |

| processeur                    | OS de niveau partition en ARINC                  |  |  |  |  |  |

| type de données               | type de données Signal                           |  |  |  |  |  |

| système                       | processus Signal constitué de sous-processus     |  |  |  |  |  |

| bus                           | processus de communication Signal                |  |  |  |  |  |

| dispositif                    | processus Signal                                 |  |  |  |  |  |

Table 1.1: Principes de base de la transformation.

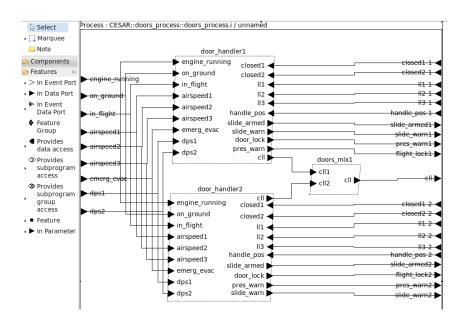

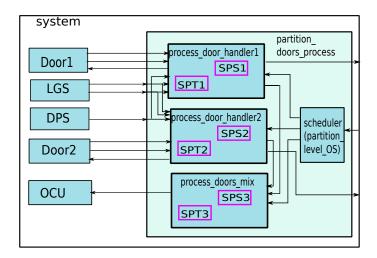

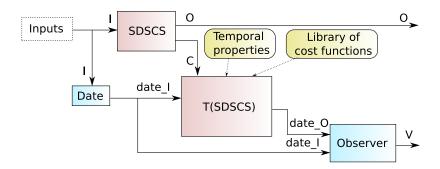

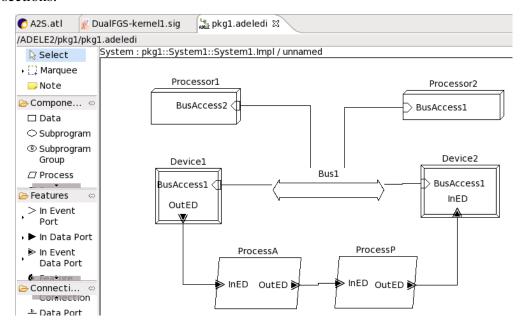

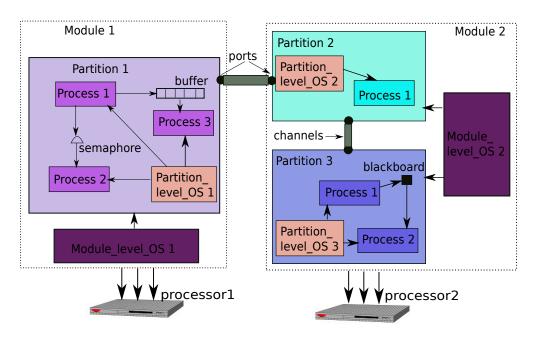

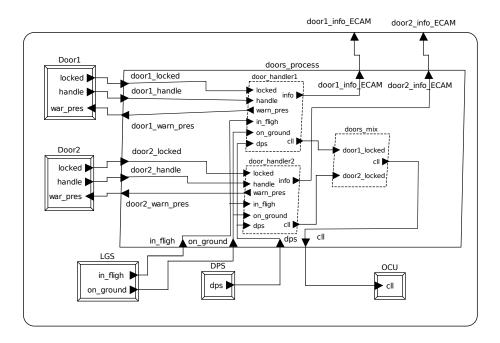

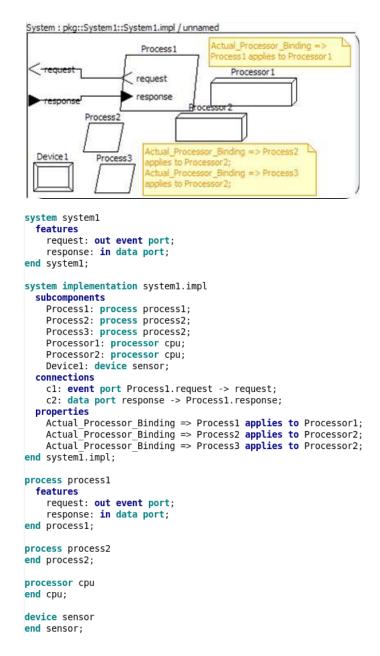

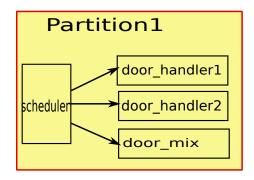

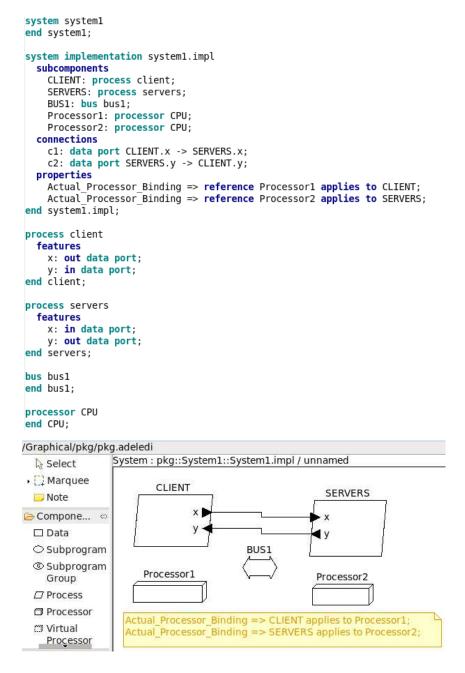

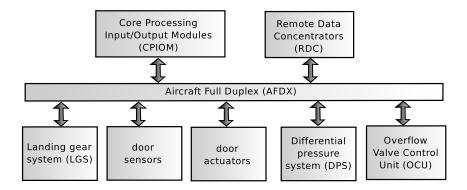

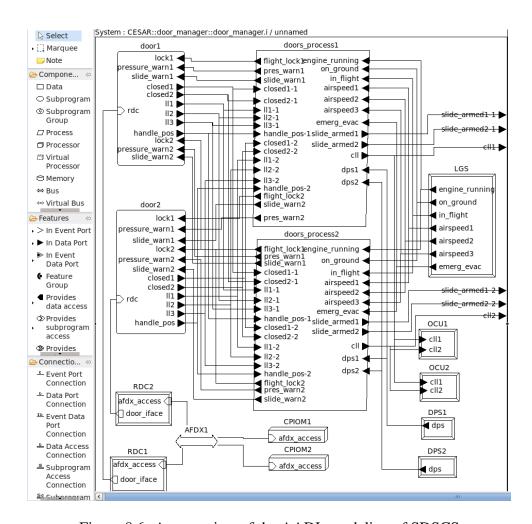

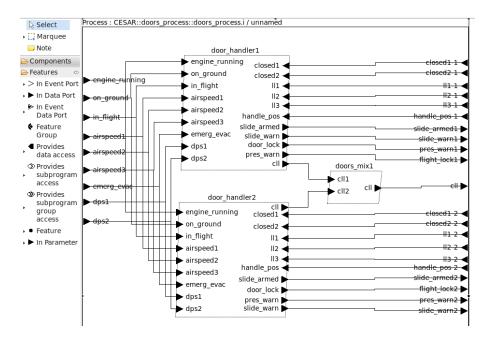

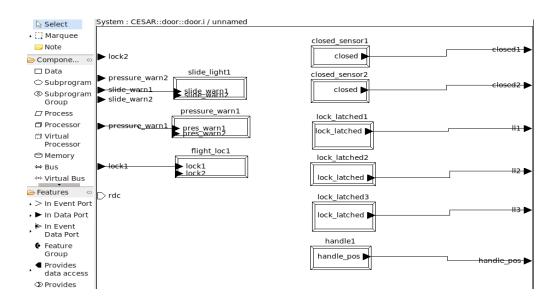

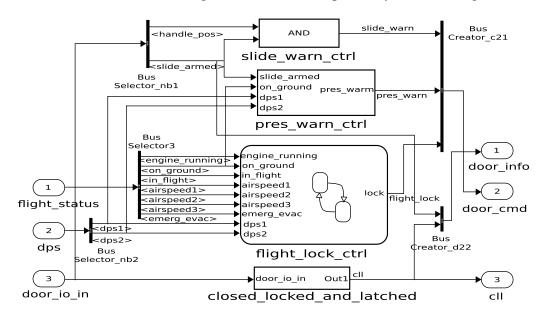

Un exemple permet de donner une première idée de la transformation. Le système SD-SCS (dont la description détaillée se trouve dans l'annexe A), représenté sur la figure 1.3, a un processus *doors\_process* qui traite les messages provenant des dispositifs *Door1*, *Door2*, *LGS*, *DPS* et *OCU*. Le processus *doors\_process* se compose de trois threads : *door\_handler1*, *door\_handler2* et *doors\_mix*, qui calculent et génèrent les sorties.

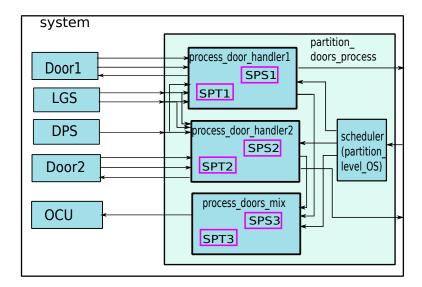

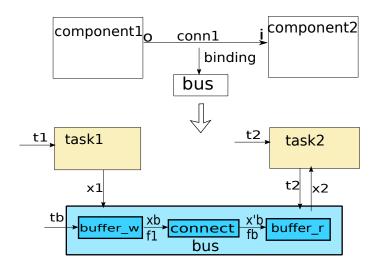

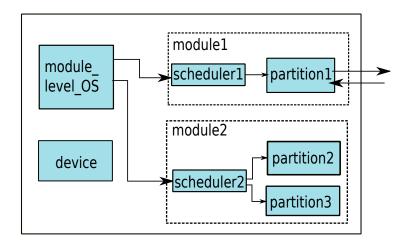

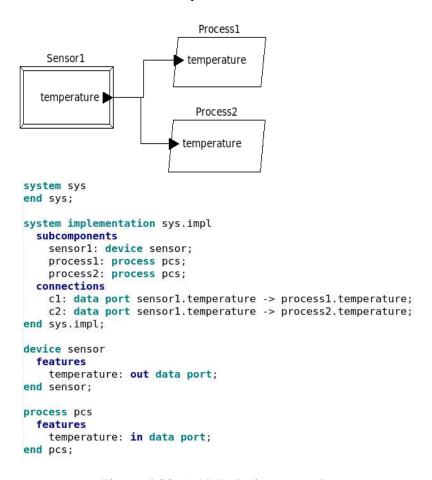

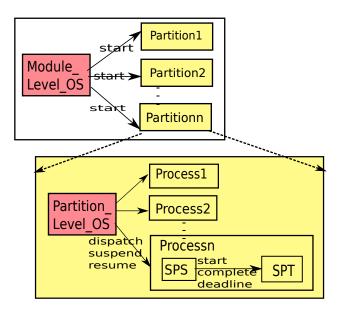

Le modèle Signal correspondant (dans l'architecture ARINC) est montré (partiellement) sur la figure 1.4. Le processus *doors\_process* est traduit en une *partition* ARINC, *partition\_doors\_process*. Les trois *processus* qui la composent, *process\_door\_handler1*, *process\_door\_handler2* et *process\_doors\_mix*, correspondent aux trois threads de la figure 1.3. L'ordonnanceur est modélisé par l'*OS de niveau partition (partition\_level\_OS)*. Les dispositifs sont implémentés comme des processus Signal extérieurs à la *partition*, à laquelle ils fournissent leur interface externe.

#### 1.5.3 Du temps logique abstrait vers un temps de simulation concret

Le paradigme synchrone fournit une représentation idéalisée du parallélisme. Tandis que AADL prend en compte les durées de calcul et les délais de communication, permettant

Figure 1.3: Les threads du processus *doors\_process*.

Figure 1.4: Modèle Signal du système SDSCS simplifié.

ainsi de produire des données d'un même instant logique à des instants différents dans la mise en œuvre. Ces instants sont définis précisément dans les propriétés des ports et des threads. Pour résoudre ce problème, nous conservons la vision idéale de calculs et communications instantanés, et déportons le calcul des latences et des délais de communication vers des processus spécifiques de "mémorisation", qui introduisent les retards et synchronisations requis. En conséquence, certaines propriétés entraînent la définition de signaux de synchronisation explicites. L'utilisation du cadre polychrone, adapté à la modélisation d'un temps logique abstrait, doit faire face aux problèmes décrits ci-après.

Modélisation des latences de calcul. Une caractéristique principale des programmes polychrones est l'exécution logique instantanée, par rapport au temps logique. Les composants dans le modèle polychrone ne consomment pas de temps logique : les sorties sont générées immédiatement lorsque les entrées sont reçues. Alors qu'en AADL, un thread peut exécuter une fonction ou un calcul pendant un intervalle de temps spécifié, défini par les propriétés temporelles. Par conséquent, la modélisation de AADL dans le cadre polychrone nécessite une forme d'adaptateur pour interfacer le temps logique abstrait et le temps de simulation concret.

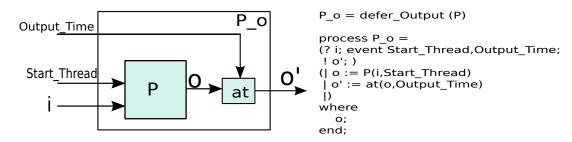

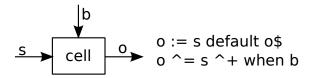

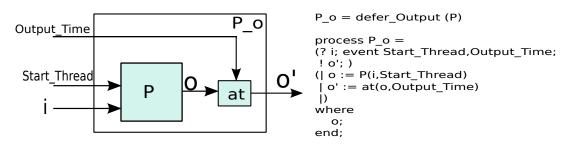

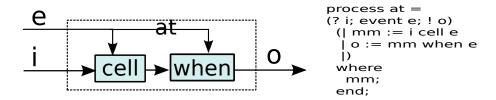

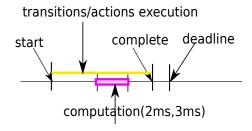

Figure 1.5: Modélisation d'une tâche consommant du temps.

À chaque sortie o d'un processus P, nous associons un processus  $P\_o$  dont la sortie est la valeur de o retardée jusqu'à ce que son  $Output\_Time$  représenté par le signal événement d'entrée  $Output\_Time$  se produise (figure 1.5). En raison de l'ordonnancement, un processus qui est logiquement synchrone d'un signal "dispatch" peut être effectivement démarré plus tard. Ainsi, à chaque processus P, nous associons un signal événement d'entrée " $Start\_Thread$ " et l'exécution de P est synchronisée avec  $Start\_Thread$ .

Modélisation des délais de propagation. Lors de l'exécution de programmes synchrones, chaque événement ou signal significatif est précisément daté par rapport aux autres signaux, et par rapport à la séquence des pas de calcul. Alors que pour un modèle AADL, l'instant de disponibilité des entrées peut être déterminé par différentes valeurs de propriétés.

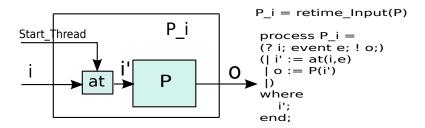

Le langage Signal fournit des moyens d'exprimer l'activation : ce sont les horloges des signaux. L'idée principale pour modéliser le temps non précisément connu de AADL dans un cadre synchrone est d'utiliser des entrées supplémentaires, appelées conditions d'activation, pour modéliser les délais de propagation.

Une condition d'activation (pour l'instant de démarrage) peut être utilisée pour exprimer l'activation d'un thread, qu'il soit périodique ou apériodique. La modélisation

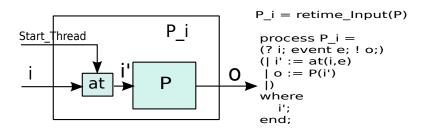

Figure 1.6: Condition d'activation.

représentée sur la figure 1.6 considère un programme synchrone P (qui est la transformation d'un thread), une entrée d'activation  $Start\_Thread$ , et définit un nouveau programme  $P\_i$  dont l'activation est conditionnée.

**Vers la modélisation d'ordonnancement basé sur le temps.** Un autre problème se pose à partir des mécanismes d'activation et de retard tels que décrits dans les paragraphes précédents : comment contrôler ces conditions d'activation et de retard, et d'où doivent-elles être générées ?

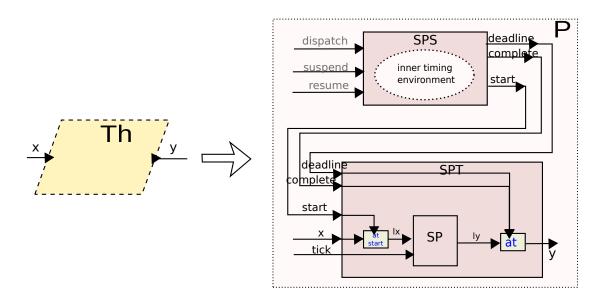

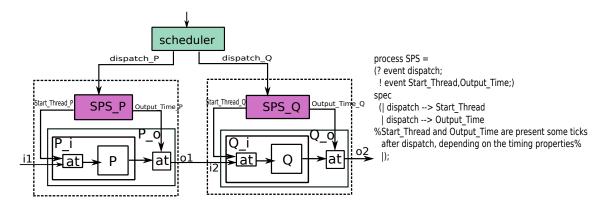

Pour réoudre ce problème, nous supposons qu'est associé à chaque thread *P* un environnement temporel *SPS*, qui calcule les horloges de démarrage et de terminaison du thread, ainsi que d'autres signaux de contrôle, lorsque le thread est activé par l'ordonnanceur. Quand que le thread est dispatché, les instants de démarrage et de terminaison peuvent être calculés en fonction des propriétés temporelles spécifiées.

#### 1.5.4 Modélisation de thread

Les threads sont les principaux composants AADL exécutables et ordonnançables. Un thread Th représente une unité concurrente ordonnançable d'exécution séquentielle définie par un code source. Pour caractériser sa capacité expressive, un thread Th encapsule une fonctionnalité qui peut consister en des ports  $P \in \mathcal{F}$ , des connexions  $C = P \times P$ , des propriétés  $R \in \mathcal{R}$ , des spécifications de comportement T/S et des sous-programmes Su qui peuvent être invoqués par le thread.

$$Th = \langle P, C, R, Su, T/S \rangle$$

La sémantique d'exécution d'un thread AADL est la suivante :

- 1. Lire et geler les entrées. Le contenu des données entrantes est gelé pour la durée d'exécution du thread. Par défaut, l'entrée est gelée au moment du dispatch. Si la propriété *Input\_Time* est spécifiée, ce moment est déterminé par la valeur de la propriété. Toute entrée arrivant après ce gel devient disponible à l'instant d'entrée suivant.

- 2. Exécuter et calculer. Quand l'activité du thread entre dans l'état de calcul, l'exécution de la séquence de code source correspondant au point d'entrée du thread est gérée par un ordonnanceur.

- 3. Actualiser et rendre disponibles les sorties. Par défaut, une sortie est transférée vers d'autres composants à l'instant de terminaison (au moment de l'échéance en cas

de connexion de port de données retardée), ou comme spécifié par la valeur de la propriété *Output\_Time*.

#### Étapes d'interprétation

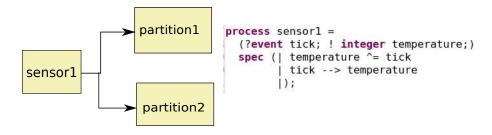

1. Un thread AADL Th est d'abord traduit en un processus Signal SP, qui correspond à un processus ARINC, du point de vue de la structure fonctionnelle. SP a les mêmes flots d'entrée/sortie que Th, plus un "tick" additionnel, qui est un tick interne provenant du processeur (l'ordonnanceur). Ce tick sera utilisé dans la transformation des comportements et des actions/calculs qu'ils contiennent. Les actions effectives, représentées par la spécification du comportement, sont décrites dans la section consacrée à la spécification du comportement.

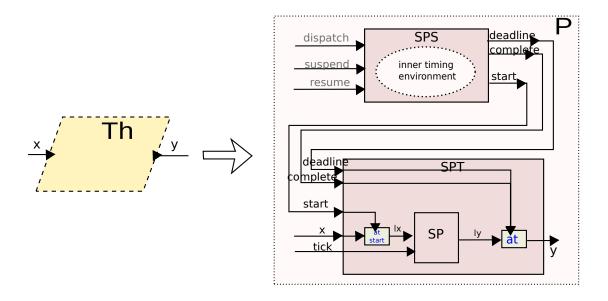

Figure 1.7: Traduction d'un thread AADL en un thread Signal.

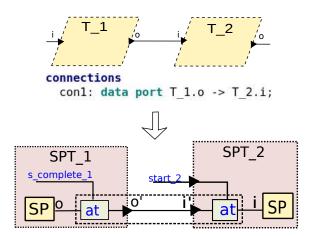

- 2. En raison de la différence de sémantique temporelle entre AADL et Signal, les propriétés temporelles d'un thread AADL sont traduites par un autre processus Signal, SPT (figure 1.7), qui joue le rôle d'interface sémantique temporelle entre AADL et Signal.

- Les principales fonctions de SPT en regard de SP sont : 1) mémoriser les signaux d'entrée, et les conserver jusqu'à ce que le thread soit activé par l'événement *start*, 2) activer le *processus* Signal fonctionnel SP au moment du *start*, 3) mémoriser les sorties du thread jusqu'à la date de terminaison (lorsque l'événement *s\_complete* est arrivé). La mémorisation des signaux et l'activation du thread servent ici de pont entre la sémantique des threads en AADL et le modèle synchrone.

- 3. L'exécution d'un thread est caractérisée par certains aspects temps réel. Un thread est ordonnancé suivant des propriétés temporelles. En raison de cette sémantique de contrôle temps réel, un nouveau *processus*, SPS (figure 1.7), est ajouté, à l'intérieur duquel les signaux de contrôle temporel sont automatiquement calculés lorsqu'il est

activé. Quand il reçoit les signaux gérant l'ordonnancement (par exemple, *dispatch*) depuis l'ordonnanceur de threads, il commence à calculer ses propres signaux temporels pour l'activation et la complétion du *processus* SPT.

**Règles d'abstraction** Nous donnons une description abstraite des règles de transformation d'un thread  $Th = \langle P, C, R, Su, T/S \rangle$  en un processus Signal (en tant que *processus* APEX ARINC). La notation  $\mathcal{I}$  représente l'interprétation.

1. Un composant thread est traduit par un *processus* ARINC, paramétré par I(P), I(C), I(R), I(Su), I(T/S). La notation  $Program^{parameters}$  est utilisée pour dénoter que les paramètres Program la définition du Program. Le rôle de ces paramètres est expliqué plus en détail ci-dessous. La fonctionnalité du thread est traduite en deux sous-processus, SPS et SPT, à l'intérieur du Processus.

$$\mathcal{I}(Th) \ = \ (SPS^{\mathcal{I}(R)} \mid SPT^{\mathcal{I}(P), \ \mathcal{I}(C), \ \mathcal{I}(Su), \ \mathcal{I}(T/S)})$$

2. Le sous-processus *SPS* est paramétré par les propriétés *R*. L'interface de *SPS* inclut les entrées *tick*, *dispatch*, *suspend*, *resume* et les sorties *start*, *complete*, *deadline*.

Les propriétés  $r \in R$ , par exemple,  $Input\_Time$ ,  $Output\_Time$ , sont interprétées dans SPS. Les valeurs de ces propriétés sont utilisées pour compter les ticks logiques pour les instants de démarrage et de terminaison du thread.

- 3. Le sous-processus  $SPT^{I(P),\ I(C),\ I(Su),\ I(T/S)}$  est paramétré par  $I(P),\ I(C),\ I(Su),\ I(T/S)$ . Les ports P sont traduits comme des entrées/ sorties, et les connexions, sous-programmes et comportements sont traduits dans le sous-processus SPT. Le détail de ces paramètres est expliqué ci-dessous.

- 4. Les ports d'entrée/sortie *P* du thread sont traduits en entrées/sorties de Signal. L'interface du *processus* ARINC inclut ces signaux et les entrées événements *tick, dispatch, suspend, resume* reçues de l'ordonnanceur. La valeur *p.direction* désigne la direction d'un port *p*.

$$inputs = \{ \text{tick, dispatch, suspend, resume} \} \cup I(p) \quad \forall p \in P, \ p.direction = \mathbf{in}$$

$outputs = \{I(p)\} \quad \forall p \in P, \ p.direction = \mathbf{out}$

# 1.5. MODÉLISATION DE COMPOSANTS AADL EN PROCESSUS SIGNAL

5. Les transitions/actions T/S sont interprétées dans un processus synchrone SP en suivant les étapes présentées dans la section suivante. Ce processus synchrone SP est encapsulé dans le sous-processus SPT. La valeur c.type désigne le type de la connexion c, qui peut être soit **immediate** ou **delayed**.

$$SPT = (IM \mid SP^{I(Su),I(C)} \mid OM)$$

où

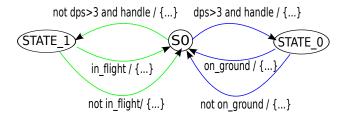

$$SP^{I(Su),I(C)} = I(T/S)$$