# Taking architecture and compiler into account in formal proofs of numerical programs

Thi Minh Tuyen Nguyen

#### ▶ To cite this version:

Thi Minh Tuyen Nguyen. Taking architecture and compiler into account in formal proofs of numerical programs. Other [cs.OH]. Université Paris Sud - Paris XI, 2012. English. NNT: 2012PA112090. tel-00710193

## HAL Id: tel-00710193 https://theses.hal.science/tel-00710193

Submitted on 20 Jun 2012

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

$N^o$  NNT: 2012PA112090

## UNIVERSITÉ DE PARIS-SUD

ÉCOLE DOCTORALE: INFORMATIQUE PARIS-SUD

DISCIPLINE: INFORMATIQUE

# THÈSE DE DOCTORAT

soutenue le 11 juin 2012

par

Thi Minh Tuyen NGUYEN

# Preuves formelles de programmes numériques en prenant en compte l'architecture et le compilateur

Composition du jury:

Président : Jean-Michel MULLER

Rapporteurs: David MONNIAUX

César A. MUÑOZ

Examinateurs Xavier LEROY

Florent HIVERT

Claude MARCHÉ, co-directeur Sylvie BOLDO, co-directrice

### Acknowledgements

This thesis is the result of more than three years of work under the supervision of Sylvie Boldo and Claude Marché, to who I would like to express my sincere gratitude. They gave me a chance to work in a big team. I would like to thank to Sylvie for her helps from the beginning of my PhD. She was always available to discuss with me each time I needed her. I would like to thank to Claude for his guidance. Spending time working with him gave me more ideas to finish my thesis.

I also thank my reviewers David Monniaux and Cesar A. Muñoz who spent much of their time to understand my memoir and gave me constructive comments. I especially thank Cesar Muñoz who came to Paris to attend my defence.

Not forget, great appreciations go to ProVal team. This is the best team that I've ever worked with. I also thank Régine for her helps in setting up my life. I thank Guillaumne for his helps in using Gappa tool. Thanks Romain, François, Asma, Kalyan, etc.

I would like to thank the people in Hisseo project who gave me helpful ideas for improving my work.

The special thank goes to my father, mother, brothers and sisters who shared with me all my difficulties. They gave me the motivation to finish my PhD.

Last but not least, thanks Luyen, my husband and my son, Minh Thien.

# Contents

| ating-point standard adent issues rification Language as in Why  sthesis  aroofs  unds for floating-point operations oint operation error in 64-bit rounding | . 10 . 11 . 13 . 13 . 16 . 18 . 20 . 21 . 23 . 25 . 25 . 27                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| ating-point standard ndent issues rification Language ns in Why  sthesis  croofs  ands for floating-point operations oint operation                          | . 11  13 . 13 . 13 . 16 . 18 . 20 . 20 . 21 . 23 . 25 . 25 . 25                                |

| ating-point standard ndent issues rification Language ns in Why  sthesis  rroofs  ands for floating-point operations oint operation                          | 13 13 13 16 18 20 20 21 23 25 25 27                                                            |

| ating-point standard indent issues rification Language is in Why  sthesis  croofs  ands for floating-point operations oint operation                         | . 13<br>. 13<br>. 16<br>. 18<br>. 20<br>. 21<br>. 23<br>. 25<br>. 25                           |

| ating-point standard indent issues rification Language is in Why  sthesis  croofs  ands for floating-point operations oint operation                         | . 13<br>. 16<br>. 18<br>. 20<br>. 20<br>. 21<br>. 23<br>. 25<br>. 25<br>. 25                   |

| rification Language as in Why  sthesis  croofs  unds for floating-point operations oint operation                                                            | . 16 . 18 . 20 . 20 . 21 . 23 . 25 . 25 . 25                                                   |

| rification Language as in Why  sthesis  croofs  ands for floating-point operations oint operation                                                            | <ul> <li>18</li> <li>20</li> <li>21</li> <li>23</li> <li>25</li> <li>25</li> <li>27</li> </ul> |

| oroofs  ands for floating-point operations oint operation                                                                                                    | <ul> <li>20</li> <li>20</li> <li>21</li> <li>23</li> <li>25</li> <li>25</li> <li>25</li> </ul> |

| oroofs  Inds for floating-point operations oint operation                                                                                                    | <ul> <li>20</li> <li>21</li> <li>23</li> <li>25</li> <li>25</li> <li>27</li> </ul>             |

| oroofs  Inds for floating-point operations oint operation                                                                                                    | <ul> <li>20</li> <li>21</li> <li>23</li> <li>25</li> <li>25</li> <li>27</li> </ul>             |

| proofs  ands for floating-point operations oint operation                                                                                                    | <ul> <li>21</li> <li>23</li> <li>25</li> <li>25</li> <li>25</li> </ul> 27 29                   |

| proofs  unds for floating-point operations oint operation                                                                                                    | <ul><li>23</li><li>25</li><li>25</li><li>25</li></ul>                                          |

| proofs  unds for floating-point operations oint operation                                                                                                    | . 25<br>. 25<br><b>27</b>                                                                      |

| proofs  unds for floating-point operations oint operation                                                                                                    | . 25 27 29                                                                                     |

| proofs  unds for floating-point operations oint operation                                                                                                    | 27<br>29                                                                                       |

| ands for floating-point operations oint operation                                                                                                            | 29                                                                                             |

| •                                                                                                                                                            | 20                                                                                             |

| error in 64-bit rounding                                                                                                                                     | . 40                                                                                           |

|                                                                                                                                                              | . 30                                                                                           |

| error in 80-bit rounding                                                                                                                                     |                                                                                                |

| error in double rounding                                                                                                                                     |                                                                                                |

|                                                                                                                                                              | . 31                                                                                           |

| <u>ams</u>                                                                                                                                                   |                                                                                                |

| S                                                                                                                                                            | . 32                                                                                           |

| nce of operations                                                                                                                                            | . 33                                                                                           |

|                                                                                                                                                              | . 33                                                                                           |

| nizes a computation                                                                                                                                          | 35                                                                                             |

| tion                                                                                                                                                         |                                                                                                |

|                                                                                                                                                              | . 35                                                                                           |

|                                                                                                                                                              |                                                                                                |

|                                                                                                                                                              | . 41                                                                                           |

|                                                                                                                                                              | . 41<br>43                                                                                     |

| a<br>s<br>n                                                                                                                                                  | inizes a computation                                                                           |

|    | 5.3  | •                                                        | 46 |

|----|------|----------------------------------------------------------|----|

|    | 5.4  | Clock drift example                                      | 47 |

|    | 5.5  | Scalar product example                                   | 49 |

| II | На   | ardware-dependent proofs                                 | 51 |

| 6  | Prin | nciple of proofs on assembly code with Why               | 53 |

|    | 6.1  | Steps of proofs                                          | 53 |

|    | 6.2  | Essential elements of assembly language                  | 54 |

|    |      | 6.2.1 Operands and Instruction Naming                    | 54 |

|    |      | 6.2.2 EFLAGS register                                    | 55 |

|    |      | 6.2.3 General-purpose instructions                       | 56 |

|    |      | 6.2.4 Calling procedures using call and ret              | 56 |

|    |      | 6.2.5 Some assembler directives                          | 57 |

|    |      | · · · · · · · · · · · · · · · · · · ·                    | 58 |

|    | 6.3  | •                                                        | 59 |

|    | 6.4  | Examples                                                 | 61 |

| 7  | Cas  | e of Simple programs                                     | 65 |

|    | 7.1  | 1 1 0                                                    | 65 |

|    | 7.2  | ·                                                        | 65 |

|    |      | $oldsymbol{arphi}$                                       | 65 |

|    |      | •                                                        | 66 |

|    |      |                                                          | 68 |

|    |      | 7.2.4 Translation of an instruction                      | 69 |

|    |      | 7.2.5 Sequences and functions                            | 70 |

|    | 7.3  | Soundness of translation                                 | 71 |

|    |      | 7.3.1 Reminder of the soundness of Why                   | 72 |

|    |      |                                                          | 73 |

|    |      | 7.3.3 Definition of the execution of an assembly program | 74 |

|    |      | •                                                        | 75 |

|    | 7.4  | •                                                        | 77 |

|    |      | 7.4.1 Simple example                                     | 77 |

|    |      | 7.4.2 Square example                                     | 78 |

| 8  | Floa |                                                          | 83 |

|    | 8.1  | •                                                        | 83 |

|    |      | <i>'</i>                                                 | 83 |

|    |      | <b>0.</b>                                                | 84 |

|    |      |                                                          | 86 |

|    | 8.2  | 1 9 11                                                   | 87 |

|    | 8.3  | ·                                                        | 89 |

|    |      |                                                          | 89 |

|    |      | · · · · · · · · · · · · · · · · · · ·                    | 89 |

|    |      |                                                          | 90 |

|    |      | ,                                                        | 91 |

|    |      |                                                          | 92 |

|    |      |                                                          | 95 |

|    | 8.4  | Translation of annotations to Why                        | 96 |

|    |      | 8.4.1 Translation of annotations in presence of floating-point arithmetic   | 96           |

|----|------|-----------------------------------------------------------------------------|--------------|

|    | 8.5  | Soundness of translation                                                    | 97           |

|    |      | 8.5.1 Definition of the execution of a assembly program                     | 97           |

|    |      | 8.5.2 Relation between Why state and assembly state (case of floating-point |              |

|    |      | programs)                                                                   | 98           |

|    |      | 8.5.3 About exact value                                                     | 99           |

|    | 8.6  | Illustrations                                                               |              |

|    | 0.0  | 8.6.1 Double rounding example                                               |              |

|    |      | 8.6.2 Overflow example                                                      |              |

|    |      | 8.0.2 Overnow example                                                       | 104          |

| 9  | Han  | adling Conditional and loop statements                                      | 109          |

| •  | 9.1  | Conditional instructions in assembly                                        |              |

|    | J.1  | 9.1.1 Jump instructions                                                     |              |

|    |      |                                                                             |              |

|    | 0.0  |                                                                             |              |

|    | 9.2  | Definition of programs supported                                            |              |

|    | 9.3  | Translation of comparison instructions                                      |              |

|    |      | 9.3.1 Translation of cmp instruction                                        |              |

|    |      | 9.3.2 Translation of floating-point comparison instructions                 |              |

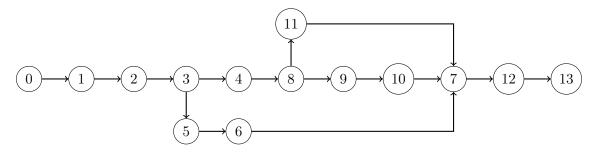

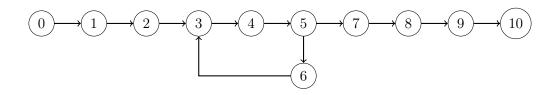

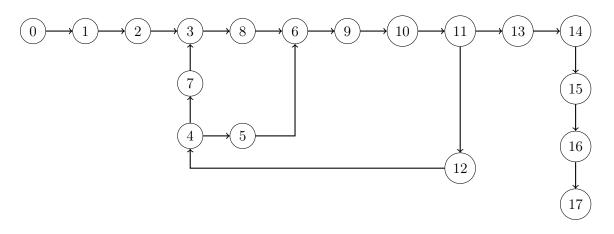

|    | 9.4  | Control Flow Graph construction from assembly code                          | 112          |

|    |      | 9.4.1 Example with if statement                                             | 112          |

|    |      | 9.4.2 Example with do while statement                                       | 114          |

|    |      | 9.4.3 Example with goto, do while and if statement                          | 114          |

|    | 9.5  | Translation from a CFG to Why                                               |              |

|    | 9.6  | Examples                                                                    |              |

|    |      | 9.6.1 Clock drift                                                           |              |

|    |      | 9.6.2 KB3D                                                                  |              |

|    | 9.7  | Discussion                                                                  |              |

|    | 9.1  | Discussion                                                                  | 120          |

| 10 | Han  | ndling Arrays and Pointers                                                  | 127          |

|    |      | Handled programs                                                            |              |

|    |      | New rules of translation for operands and instructions                      |              |

|    | 10.2 | 10.2.1 Representation of memory in Why                                      |              |

|    |      | 10.2.2 Definition of memory model                                           |              |

|    |      | 10.2.2 Definition of memory model                                           |              |

|    |      |                                                                             |              |

|    | 10.9 | 10.2.4 Translation of annotations to Why                                    |              |

|    |      | When local variables are pointed by %rsp                                    |              |

|    | 10.4 | Examples                                                                    |              |

|    |      | 10.4.1 Maximum of an array                                                  |              |

|    |      | 10.4.2 Scalar Product                                                       | 142          |

|    | ъ.,  |                                                                             | - 4 <b>-</b> |

| 11 |      |                                                                             | 147          |

|    | 11.1 | Motivations                                                                 |              |

|    |      | 11.1.1 Examples of the chapter                                              |              |

|    |      | 11.1.2 Goals of the chapter                                                 |              |

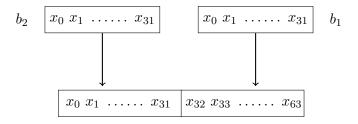

|    |      | About endianness                                                            |              |

|    | 11.3 | Why 3                                                                       | 150          |

|    |      | 11.3.1 Logic                                                                | 150          |

|    |      | 11.3.2 Theories                                                             | 151          |

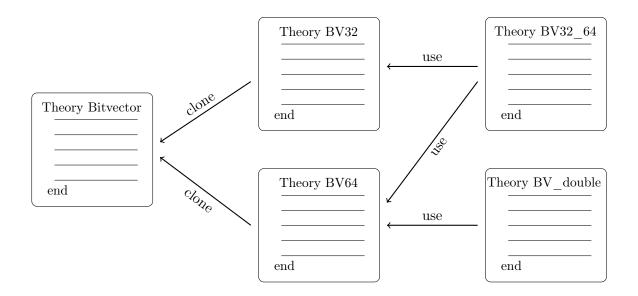

|    | 11.4 | Bitvector theories in Why 3                                                 |              |

|    |      | 11.4.1 Theory BitVector                                                     |              |

|        | 11.4.2 Theory BV32 and BV64                 |

|--------|---------------------------------------------|

|        | 11.4.3 Theory BV32_64                       |

|        | 11.4.4 Theory BV_double                     |

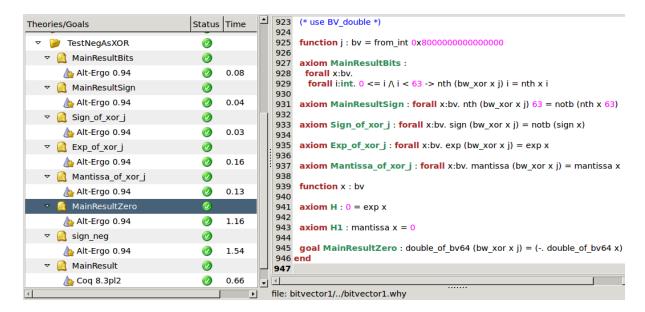

| 11.5   | Examples                                    |

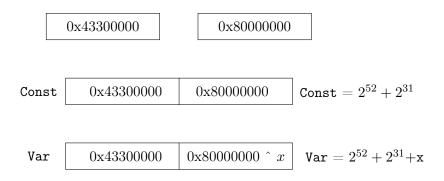

|        | 11.5.1 Negation by xor                      |

|        | 11.5.2 Conversion of an integer to a double |

| 11.6   | <u>Discussion</u>                           |

| 12 Cor | nclusion and Future works 165               |

| 12.1   | Summary                                     |

|        | 12.1.1 Hardware-independent approach        |

|        | 12.1.2 Hardware-dependent approach          |

|        | 12.1.3 Comparison with related works        |

|        | 12.1.4 Difficulties                         |

| 12.2   | Future works                                |

|        | 12.2.1 Hardware-independent approach        |

|        | 12.2.2 Hardware-dependent approach          |

## Chapter 1

## Introduction

The problem of program correctness is always an issue, especially as software applications are more and more complex. Moreover, software correctness plays a crucial role in the overall software quality especially in the automatic control of engines like airplanes or subways. A bug in such systems can not only lost a lot of money but also human life. Thus, the validation of program implementation, which checks whether the code conforms to developer's intentions, is necessary.

A common method for reducing bugs in programs is testing. However, this technique cannot cover all cases of the input space, and thus, although the tests are successful, the implementation may still contain errors. Another possibility is to use formal verification methods. It mathematically proves the correctness of the specification. Although formal verification is used in critical software, there are some aspects which are not studied fully such as computations on floating-point numbers.

Before describing the contributions and the organization of this thesis, we introduce some reasons which cause the discrepancies of results in floating-point programs and give a state of the art of formal verification in general and a state of the art of formal verification for floating-point arithmetic.

## 1.1 Floating-point arithmetic

Nowadays, floating-point computations are widely used in critical systems from domains such as physics, aerospace system, nuclear simulation, etc. In systems which use floating-point computations, the calculations are not exact. This means that there is an approximation for each operation and thus rounding error occurs. There were some famous disasters caused by calculation bugs. The first one is Patriot Missile Failure [67] on February 25, 1991. The cause was an inaccurate calculation of the time since boot due to computer arithmetic errors. The second one is the explosion of the Ariane 5 on June 4, 1996, just forty seconds after lift-off. "The internal SRI <sup>1</sup> software exception was caused during execution of a data conversion from 64-bit floating point to 16-bit signed integer value. The floating point number which was converted had a value greater than what could be represented by a 16-bit signed integer.", explained the report of the Inquiry Board [52]. The third one is a famous FDIV bug in 1994 in the Intel Pentium processor that costs \$500 millions [38]. The effort to reduce errors is thus necessary for the safety and reliability of programs.

As we have presented, inaccurate calculation is an issue in critical systems. The reason is that there exist inconsistencies between program executions on different architectures. The IEEE-

<sup>&</sup>lt;sup>1</sup>SRI stands for Système de Référence Inertielle or Inertial Reference System.

754 is the IEEE standard for floating-point arithmetic. This standard specifies interchange, arithmetic formats and methods for binary and decimal floating-point arithmetic in computer programming environments. An implementation of a floating-point system conforming to this standard may be realized entirely in software, hardware or in any combination of software and hardware. This standard ensures that we get exactly the same results from the floating-point calculations of a program when it executes in any processor that follows strictly this standard. In Java, the floating-point calculations in a class or a method containing the modifier strictfp<sup>2</sup> will follow strictly the standard. In C, the compiler gcc for x86-64 architectures uses -msse and -msse2 by default to enable SSE extensions. For example, a double number is represented in 64 bits; a calculation on double is always rounded in 64 bits. However, the computations do not always follow strictly the IEEE-754 standard because of some architecture-dependent issues. This means that for a double type in C for example, by changing options of the compiler, the calculation is not always done directly in 64 bits. The first architecture-dependent issue is the x87 floating-point unit (FPU) featured in processors of IA32 architecture. It uses the 80-bit internal floating-point registers on the Intel platform. The second one is the fused multiply-add (FMA) instruction, supported by the PowerPC and the Intel Itanium architectures, computes  $xy \pm z$ with a single rounding. Besides, compiler issues like optimization may also cause discrepancies in results. Because of the issues above, the floating-point computations of a program running on different architectures may be different [58].

#### 1.2 Formal verification

Formal verification is more and more studied and used in both academy and industry research in order to guarantee the safety of programs. There are many approaches for verifying programs formally. Among of them are approaches which verify the source code such as static analysis, others formally verify the machine code implementation.

Static analysis is an approach for checking a program without running it. Deductive verification techniques which perform static analysis of code, rely on the ability of theorem provers to check validity of formulas in first-order logic or even more expressive logics. They usually come with expressive specification languages such as JML [15, 46] for Java, ACSL [9] for C, Spec# [6] for C#, etc. to specify the requirements. For automatic analysis of floating-point codes, a successful approach is abstract interpretation based static analysis, that includes Astrée [22, 59] and Fluctuat [26].

We introduce here a short history about the formalization of floating-point arithmetic for the specification and the verification. Floating-point arithmetic has been firstly formalized in 1989 by G. Barrett [8]. This is only the formalization of the IEEE standard for binary floating-point arithmetic in the specification language Z. However, there are not any proofs using this specification. Then, in 1995, Carreño and Miner [17] presented the specification of the IEEE-875 Floating-point standard in HOL and PVS [63]. Two year later, Harrison [39] presented his works on the specification of floating-point in HOL Light – a tool written by himself – about the specification of floating-point arithmetic and demonstrated how to use this specification for proving. The works of Russinoff [65] are the formal verification of floating-point multiplication, division and square root instructions of the AMD-K7 microprocessor in ACL2 [47]. The formalization of IEEE-754 standard in Coq [20] was first done in 2001 by Théry, Rideau and Daumas [24]. The common point of these works is the formalization of the floating-point standard for a specification language.

<sup>&</sup>lt;sup>2</sup>http://java.sun.com/docs/books/jls/third\_edition/html/expressions.html#249198

There are few attempts in specifying and proving behavioral properties of floating-point programs in deductive verification system. In 2004, Miné used relational abstract domains to dectect floating-point run-time errors [57]. Leavens presented how to handle NaN problems in floating-point operations for JML in Java in 2006 [48]. Another proposal has been made in 2007 by Boldo and Filliâtre [11]. Authors introduced a methodology and proofs in Coq to perform formal verification of floating-point C programs which was implemented in a tool called Caduceus [34]. In 2010, Ayad and Marché [4] extended this to the support of special values and to the use of automatic theorem provers. This work was implemented in the Jessie plug-in of Frama-C platform. However, these works only follow strictly the IEEE-754 standard, with neither FMA, nor extended registers, nor considering optimization aspects.

Formal verification of machine-code programs is an approach for verifying a program at machine-code level. The specification and correctness of machine-code programs has been first studied in 1961 by Goldstein and von Neumann [37]. After that, program verification was applied to machine code by Maurer [54] in 1976. This paper presented the effort to put techniques for proving the correctness of assembly language and machine language programs into practice. More precisely, it is used for programs written for the Litton C400 airborne computer including overflow analysis, round-off and truncation analysis, fixed-point scaling considerations, etc.. A year later, Floyd-Hoare-style verification condition generator was applied to machine code by Clutterbuck and Carré [18]. In 1996, Boyer and Yu [14] formalized the MC68020 Instruction Set in the automated reasoning system Nqthm (also known as "the Boyer-Moore theorem prover" and predecessor of ACL2). In this paper, bit vector operations are defined with non-negative integer arithmetic and not for floating-point arithmetic. Another point is that they were able to verify few programs only specified in Nqthm. In 2006, Matthews et al. [53] published a paper on mechanized Hoare logic reasoning for machine code in the form of verification condition generator (VCG) inside the ACL2 theorem prover. Meanwhile, Leroy [49] used Coq for the correctness of an optimizing compiler which takes a significant subset of C as input and produces PowerPC assembly code as output from a simple imperative intermediate language called Cminor. In a separate work on compilation, Li and Slind et al. [51] showed that one can compile programs with proof, directly from the logic of the HOL4 theorem prover. In 2007, Pavlova [64] proposed a framework which allows the verification of Java bytecode programs. In that thesis, she defined both a Bytecode Modeling Language (BML) and a verification condition generator for Java bytecode which is independent from the source code. A year later, Myreen [61] made contributions both to approaches for verification of programs and methods for automatically constructing correct code. This work was implemented only for the HOL4 theorem prover.

Although there are a lot of former works on formal verification at low-level programs, none of them considers any aspect of floating-point computation behavioral verification at assembly level.

#### 1.3 Contributions

As our goal is to verify floating-point programs in considering architecture and compiler aspect, this thesis consists of two approaches: first, proving floating-point properties by using static analysis for multiple architectures; second, analyzing assembly code and translating it to verification conditions proved by automatic or interactive provers.

The first approach proves numerical programs whatever the environment, or in other words, it proves numerical programs with few restrictions on the compiler and the processor. More precisely, considering rounding-to-nearest mode, double precision numbers and computations, we calculate the rounding error for each operation independent to hardware and the choice of

compiler. This approach is implemented in Frama-C platform <sup>3</sup> associated with Why [35] for static analysis of C code <sup>4</sup>.

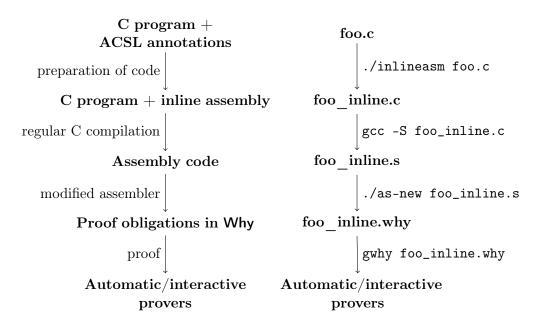

The second approach is to prove a program on its assembly code. This means that we prove a program depending on the architecture and compiler. Indeed, with the first approach, we assure that the result is correct in an interval and thus we cannot prove an exact value. Once we compile the program into assembly code, all the necessary information is known such as the precision of each operation, the order of operations, etc. By analyzing assembly code and translating its instructions to verification conditions in the intermediate verification language Why, we can prove a numerical program totally dependent to the architecture and the compiler. A modified version of GAS (GNU Assembler) is used to generate Why verification conditions (VCs) and then these VCs are proved by automatic or interactive provers. Our contributions consist of a translator which allows us to translate all annotations in C program under the forme of inline assmemly and another translator which interpret assembly code into Why. This implementation is integrated in a modified version of GAS that we've mentioned above <sup>5</sup>.

The structure of this dissertation is as follows:

Chapter 2 presents basic knowledge about the IEEE-754 floating-point standard and some architecture-dependent issues. We also present in this chapter a few words about Why intermediate verification language; Frama-C framework and ANSI/ISO C Specification Language (ACSL).

Chapters 3, 4 and 5 present the approach for proving numerical programs for multiple architectures. Chapter 3 studies how to bound a floating-point operation and how to prove a program independent to hardware. Next, Chapter 4 consider the bound when the additions/subtractions re-organize in case of optimization. Chapter 5 then illustrates this approach by examples.

Chapters 6 to 10 will present step by step how to translate assembly code of a numerical program into Why. Chapter 6 introduces an overview of how to prove a C program by using our approach and presents essential elements of assembly language. Chapter 7 presents how to translate assembly instructions to Why with simple programs. Then this translation will be extended for floating-point programs in Chapter 8. Chapter 9 considers programs containing conditional and loop statements. Chapter 10 presents a memory model for programs which contain arrays and pointers. Chapter 11 is a preliminary attempt to support programs with operations at the bit level.

The last chapter gives the summary of contributions and discusses directions of future works.

<sup>3</sup>http://frama-c.com/

<sup>&</sup>lt;sup>4</sup>This approach is integrated in the version 2.30 of Why, available at http://why.lri.fr/download/why-2.30.tar.gz

<sup>&</sup>lt;sup>5</sup>These tools are available at http://www.lri.fr/~nguyen/contrib/

## Chapter 2

# Background

This chapter includes the background on the floating-point arithmetic, architecture-dependent and compiler optimization issues. We also presents the Why intermediate language, the ACSL specification language and the Frama-C framework as they will be used in the next chapters.

### 2.1 Floating-point arithmetic

This section consists of two subsections: firstly, we will talk about the IEEE-754 standard; secondly, we will present architecture-independent issues.

#### 2.1.1 The IEEE-754 floating-point standard

The IEEE-754 standard [1] for floating-point arithmetic was developed to define formats and behaviors for floating-point numbers and computations.

There are five basic formats defined in this standard:

- Three binary formats, with encodings in lengths of 32, 64 and 128 bits.

- Two decimal formats, with encodings in lengths of 64 and 128 bits.

In this thesis, we take into account only 32-bit and 64-bit binary formats.

#### Floating-point data

The set of finite floating-point numbers representable within a particular format is determined by the following integer parameters:

- b = the radix, 2 or 10,

- p =the number of digits in the significand (precision),

- emax = the maximum exponent,

- emin = the minimum exponent where <math>emin = 1 emax for all formats.

Within each format, the following floating-point data is represented:

• Signed zero or non-zero floating-point numbers of the form

$$(-1)^s \times b^e \times m \tag{2.1}$$

where

- -s is 0 or 1,

- -e is any integer such that  $emin \le e \le emax$ ,

- m is a number represented by a digit string of the form  $d_0 \cdot d_1 d_2 \dots d_{p-1}$  where  $d_i$  is an integer digit  $0 \le d_i < b$  (therefore  $0 \le m < b$ ).

- Two infinities:  $+\infty$  and  $-\infty$ ,

- Two NaNs: qNaN (quiet) and sNaN (signaling).

There are two kinds of floating-point number: normal and subnormal. The smallest positive normal floating-point number is  $b^{min}$  and the largest one is  $b^{max} \times (b - b^{1-p})$ . The non-zero floating-point numbers for a format with magnitude less than  $b^{min}$  are called subnormal numbers.

#### Binary format encodings

In this thesis, we use only binary formats. The representation of floating-point data in the binary format is coded in k bits in the three fields ordered as follow:

- 1-bit sign S,

- w-bit biased exponent E = e + bias,

- (t = p-1)-bit trailing significand field  $T = d_1 d_2 \dots d_{p-1}$ . The leading bit of the significand,  $d_0$ , is implicitly encoded in the biased exponent E.

| 1 bit                                 | w bits            | t = p - 1 bits               |  |  |

|---------------------------------------|-------------------|------------------------------|--|--|

| S                                     | E                 | T                            |  |  |

| (sign)                                | (biased exponent) | (trailing significand field) |  |  |

| $E_0 \dots E_{w-1} d_1 \dots d_{p-1}$ |                   |                              |  |  |

The values of k, p, emax, t, w and bias are listed as follows:

| Parameter                                   | binary32 | binary64 |

|---------------------------------------------|----------|----------|

| k, storage width in bits                    | 32       | 64       |

| sign bit                                    | 1        | 1        |

| w, exponent field width in bits             | 8        | 11       |

| bias, E-e                                   | 127      | 1023     |

| t, trailing significand field width in bits | 23       | 52       |

| p, precision in bits                        | 24       | 53       |

| emax, maximum exponent $e$                  | 127      | 1023     |

The range of the encoding biased exponent E include:

- every integer in  $[1, 2^w 2]$  to encode normal numbers.

- the reserved value 0 to encode  $\pm 0$  and subnormal numbers.

- the reserved value  $2^w 1$  to encode  $\pm \infty$  and NaNs.

The value v of the floating-point datum represented are:

| E              | T        | v                                                                                                                        |  |

|----------------|----------|--------------------------------------------------------------------------------------------------------------------------|--|

| $2^{w}-1$      | $\neq 0$ | NaN                                                                                                                      |  |

| $2^{w}-1$      | 0        | $(-1)^S \times (+\infty)$                                                                                                |  |

| $[1, 2^w - 2]$ |          | $(-1)^S \times 2^{E-bias} \times (1+2^{1-p} \times T)$ (normal numbers have an implicit leading significand bit of 1)    |  |

| 0              | $\neq 0$ | $(-1)^S \times 2^{emin} \times (0 + 2^{1-p} \times T)$ (subnormal numbers have an implicit leading significand bit of 0) |  |

| 0              | 0        | $(-1)^S \times (+0)$ (signed zero)                                                                                       |  |

#### Rounding error

Let x is a real number,  $x_1$  and  $x_2$  are the two floating-point numbers closest to x such that  $x_1 \le x \le x_2$ . Let  $\circ(x)$  the rounding value of x to a floating-point number. IEEE-754 standard includes five standard rounding modes:

- Round-to- $+\infty$ :  $\circ(x) = x_2$ .

- Round-to- $-\infty$ :  $\circ(x) = x_1$ .

- Round-to-zero:

$$\circ(x) = \begin{cases} x_1 \text{ if } |x_1| \le |x_2|, \\ x_2 \text{ if } |x_1| > |x_2|. \end{cases}$$

• Round-to-nearest (ties to even):

$$\circ(x) = \begin{cases} x_1 \text{ if } |x_1 - x| < |x_2 - x|, \\ x_2 \text{ if } |x_1 - x| > |x_2 - x|, \\ \text{the one with the bit } p - 1 \text{ of the significand being 0 if } |x_1 - x| = |x_2 - x|. \end{cases}$$

• Round-to-nearest (ties away from zero):

$$\circ(x) = \begin{cases} x_1 \text{ if } & |x_1 - x| < |x_2 - x| \text{ or} \\ & (|x_1 - x| = |x_2 - x| \text{ and } |x_1| > |x_2|), \\ x_2 \text{ if } & |x_1 - x| > |x_2 - x| \text{ or} \\ & (|x_1 - x| = |x_2 - x| \text{ and } |x_1| \le |x_2|). \end{cases}$$

When approximating a real number x by its rounding  $\circ(x)$ , a rounding error usually happens. We here consider only round-to-nearest mode, that includes both the default rounding mode (ties to even) and the new round-to-nearest, ties away from zero. In radix 2 and round-to-nearest mode, a well-known bound on the error is given by D. Goldberg [36] as follows:

• If a floating-point f = o(x) is such that  $|f| \ge 2^{e_{min}}$  then we bound the rounding error by the relative error:

$$\left| \frac{x - f}{x} \right| \le 2^{-p}$$

• For smaller f, the value of the relative error becomes large (up to 0.5). In that case, f is a subnormal number and we prefer a bound based on the absolute error:

$$|x - f| \le 2^{e_{min} - p}$$

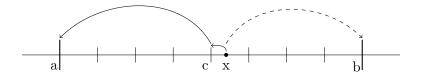

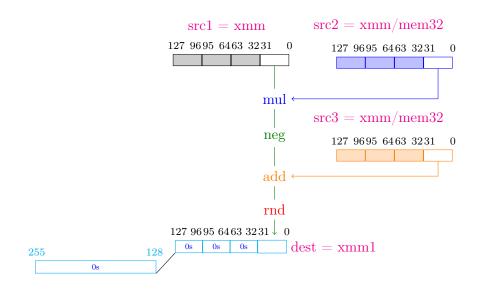

Figure 2.1: Bad case for double rounding

```

int main(){ double x = 1.0; double y = 0 \times 1p - 53 + 0 \times 1p - 64; // y = 2^{-53} + 2^{-64} double z = x + y; printf("z=%a\n",z);}

```

Figure 2.2: A simple program giving different answers depending on the architecture.

#### 2.1.2 Architecture-dependent issues

With the same program containing floating-point computations, the result may be different depending on the compiler and the processor. We present in this subsection some architecture-dependent issues.

#### x87 floating-point unit

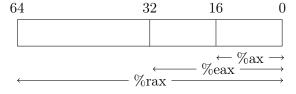

A well-known cause of discrepancy happens in the IA32 architecture (Intel 386, 486, Pentium etc.) [58]. The IA32 processors feature a floating-point unit called "x87". This unit has 80-bit registers in "double extended" format (64-bit significand and 15-bit exponent), often associated to the long double C type. When using the x87 mode, the intermediate calculations are computed and stored in the x87 registers (80 bits). The final result is rounded to the destination format. Extended registers may lead to double rounding, where floating-point results are rounded twice. For instance, the operations are computed in the long double type of x87 floating-point registers, then rounded to IEEE double precision type for storage in memory. Double rounding may yield different result from direct rounding to the destination type.

An example is given in Figure 2.1: the long vertical lines are floating-point numbers representable in 64 bits, the short ones are floating-point numbers representable in 80 bits. We assume x is near the midpoint c of two consecutive floating-point numbers a and b in the destination format. Using round-to-nearest, with single rounding, x is rounded to b. However, with double rounding, it may firstly be rounded towards the middle c and then be rounded to a (if a is even). The two obtained results are different.

A C program illustrated for Figure 2.1 is presented in Figure 2.2: the values x = 1.0 and  $y = 2^{-53} + 2^{-64}$  are exactly representable in double precision. With strict IEEE-754 double precision computations for double type, the result obtained is  $z = 1 + 2^{-52}$ . Otherwise, on IA32, if the computations on double is performed in the long double type inside x87 unit, then converted to double precision, z = 1.0.

Another example which gives inconsistencies between x87 and SSE is presented in Figure 2.3. It is part of the KB3D [27], an aircraft conflict detection and resolution program. In this example, we have a function int sign(double x) which returns a value which is either -1 if

Figure 2.3: A more complex program giving different answers depending on the architecture.

x < 0, or 1 if  $x \ge 0$ . The function int eps\_line(double sx, double sy, double vx, double vy) then makes a direction decision depending on a sign after few floating-point computations. We execute this program on SSE unit and obtain that Result = 1. When it is performed on IA32 inside x87 unit, the result is Result = -1.

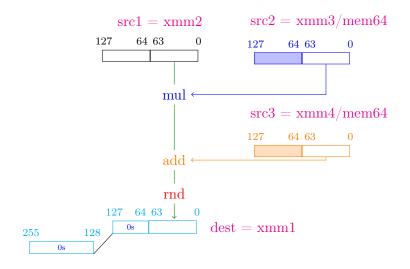

#### FMA

Another cause of discrepancy in the result of a floating-point program is the fact that some processors (IBM PowerPC or Intel/HP Itanium) have a fused multiply-add (FMA) instruction which computes  $x \times y \pm z$  as if with unbounded range and precision, and rounds only once to the destination format. This operation can speed up and improve the accuracy of dot product, matrix multiplication and polynomial evaluation. But how should  $a \times b + c \times d$  be computed? When a FMA is available, the compiler may choose either  $\circ(a \times b + \circ(c \times d))$ , or  $\circ(\circ(a \times b) + \circ(c \times d))$  which may give different results.

#### Optimization issues

The last cause for discrepancies occurs when compilers optimize floating-point computations. This includes re-organizing additions or multiplications, use of distributivity, etc. Those mathematically correct identities are usually refuted by floating-point operations.

When we compile a C program with optimization options<sup>1</sup>, the assembly code may be changed. Here are some options of gcc:

- $\bullet$  -00: no optimization. This is the default.

- -0, -01: the compiler tries to reduce code size and execution time, without performing any optimizations.

- -02: Optimize even more. As compared to -0, this option increases both compilation time and the performance of the generated code. -02 turns on -finline-small-functions that

<sup>&</sup>lt;sup>1</sup>http://gcc.gnu.org/onlinedocs/gcc/Optimize-Options.html

```

double f(double x){

return x/1e308;

}

double square(double x){

double y = x*x;

return y;

}

int main(){

printf("%g\n",f(square(1E308)));

return 0;

}

```

Figure 2.4: A program giving different answers depending on the optimization.

allows to integrate functions into their callers when their body is smaller than expected function call code.

- -03: Optimize yet more. It turns on all optimizations specified by -02 and also other options including -finline-functions.

- -funsafe-math-optimizations: Allow optimizations for floating-point arithmetic, e.g. use associative math, use reciprocal instead of division, disregard floating-point exceptions (division by 0, overflow, underflow, etc).

The options above may change the assembly code and thus affect the result of floating-point calculations except the first and the second one.

Inline function means that the function is integrated into their caller. On x87, inlining may change the result. The program in Figure 2.4 which is presented by D. Monniaux [58] illustrates this case. When compiling it with -mfpmath=387 -02, function inlining occurs, the two functions f and square are integrated in the function main and intermediate values are stored in 80-bit registers, not in 64-bit registers. This means that the result is 1E308 and not overflow although it is overflow (the result is Inf) with default option of gcc.

## 2.2 Why- An Intermediate Verification Language

Why<sup>2</sup> is a software verification platform [35]. It is also known as an intermediate language for program verification. In this dissertation, we use Why as a tool to express our results in the logic world.

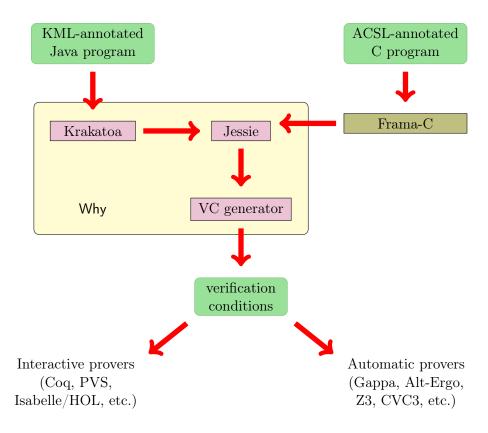

Figure 2.5 shows us the process of how Why receives Java and C programs as inputs and generates verification conditions which are proved by automatic or interactive provers. Why has front-ends for C and Java in which the front-end for C is in fact integrated in the Frama-C environment for static analysis of C programs.

One advantage of Why is that it allows us to declare logical models (types, functions, predicates, axioms, lemmas) that can be used in programs and annotations. Another advantage is that the Why tool supports a set of existing provers:

<sup>&</sup>lt;sup>2</sup>http://why.lri.fr/

Figure 2.5: Why platform

- Proof assistants: Coq, PVS, etc.

- Automatic theorem provers: Alt-Ergo [19], CVC3 [7], Gappa [25, 55], etc.

In the input language of Why, we can define a pure model in the logic world by declaring abstract sort names, declaring logic symbols operating on these sorts and posing first-order axioms to axiomatize the behavior of these symbols. Equality and both integer and real arithmetic are built-in in the logic. We can then declare a set of references which are mutable variables denoting logic values. Finally, we can define procedures which can modify these references. The body of such a procedure is made of statements in a while-style language.

Why includes also logical annotations (pre- and post-conditions, loop invariants and variants, intermediate assertions). Procedures are equipped with pre- and post-conditions. The Why VC generator then produces the necessary VCs to ensures that the body respects the post-condition. One can alternatively just declare procedures by only giving pre- and post- conditions, but also declaring the set of modified references. This feature allows to declare how the atomic operations on a given data type behave.

The detail of the syntax of Why is found at: http://why.lri.fr/. In this section, we will present in a few words axiomatizations, logic functions and parameters which we will use in the thesis.

#### 2.2.1 Logical declarations in Why

#### Axiomatization

The axiomatization includes abstract types, declarations of functions and predicates, axioms. For example:

```

predicate is_int32(x:int) = -2147483648 <= x and x <= 2147483647

type int32

logic integer_of_int32: int32 -> int

axiom int32_coerce: forall x:int32. is_int32(integer_of_int32(x))

```

**Predicate** gives a definition based on propositions. For example:

```

predicate is_int32(x:int) = -2147483648 \le x and x <= 2147483647

```

This predicate says that its argument ranges between -2147483648 and 2147483647.

**Type** is a declaration of an abstract type. For example:

```

type int32

```

The type int32 is an abstract type which represents a 32-bit integer.

**Logic function** is a function symbol which declares type of inputs and one of output. The body of the function is not defined. Normally, we need to declare axioms to specify logic functions. For example:

```

logic integer_of_int32: int32 -> int

```

The function logic integer\_of\_int32 returns an integer value from an abstract type int32.

**Axiom** is a logical statement that is assumed to be true.

```

axiom int32_coerce: forall x:int32, is_int32(integer_of_int32(x))

```

This axiom says that all value x having type int32 always denotes an integer value in the range of 32-bit word.

#### 2.2.2 Programs in Why

A program in Why can be defined as a function with a body, or declared as a parameter.

#### Reference declaration with parameter

Parameter can be used to declare a reference (mutable value) in Why. For example:

```

parameter value: int ref

```

#### Function with let

A function in Why may contain annotations (preconditions, post-conditions and assertions) and statements.

```

let f (n:int) =

{    }

r := min !r n

{ r <= r@ }</pre>

```

The function f takes an integer n as input and assigns the value of min !r n to r. It has no precondition and a post-condition which specifies that the final value of r is not greater than its initial value (denotes by r@).

#### Function declaration with parameter

Parameter can be used for the declaration of an "abstract program" with precondition and post-condition. For example:

```

parameter add_int: a:int -> b:int ref ->

{     }

unit writes b

{ b = b@ + a }

```

The parameter add\_int takes an integer a and a variable b having type int with no precondition, returns unit (nothing). The post-condition is that the new value of b is the sum of a and the previous value of b. Notice that in parameter, there is a declaration of side-effects: the reads and writes keywords declare the set of references possibly accessed and modified, respectively.

#### **2.2.3** Example

In order to know how to write a Why program, a small program is presented as follows:

```

parameter x: int32 ref

parameter inc: n:int32 ref ->

{ is_int32(integer_of_int32(n) + 1) }

unit writes n

{ integer_of_int32(n) = integer_of_int32(n@) + 1 }

let main() =

{ is_int32(integer_of_int32(x) + 2)}

inc x;

inc x;

void

{ integer_of_int32(x) = integer_of_int32(x@) + 2 }

}

```

All the logical declarations of this program are explained in subsection 2.2.1. We declare a parameter x having type int32, another parameter inc which returns the value of input after adding 1.

In the function main, we assign to x the value of inc !x. This function is used twice. The post-condition of the function main assures that the new value of x is equal to the sum of old

```

Alt-Ergo CVC3

x: int32

Proof obligations

2.4.1 Statistics

0.93

H1: is int32(integer of int32(x) + 2)

H2: is int32(integer of int32(x) + 1)

function main

x0: int32

Ø

Ø

3/3

H3: integer_of_int32(x0) = integer_of_int32(x) + 1

Correctness

H4: is int32(integer of int32(x0) + 1)

1. precondition

0

x1: int32

Ø

2. precondition

Ø

H5: integer of int32(x1) = integer of int32(x0) + 1

Ø

Ø

integer of int32(x1) = integer of int32(x) + 2

let main() =

{ is_int32(integer_of_int32(x)+2) }

inc x;

inc x;

void

{ integer of int32(x) = integer of int32(x@) + 2 }

```

Figure 2.6: Result of a Why program

one and 2. A screen-shot in Figure 2.6 illustrates how to prove a Why program using automatic provers.

There are three obligations generated. The two first ones check the precondition of the parameter inc. As the parameter inc has a precondition, each time it is invoked, the precondition must be proved. In the function main, inc is called twice, this is the reason why we have two obligations that check the precondition of inc. The last one checks the post-condition of the function main.

We present below the VCs for these obligations and show how to prove it manually.

#### VCs for the first obligation

The VCs for proving the precondition of the first inc x in the function main are:

```

x: int32

H1: is_int32(integer_of_int32(x) + 2)

-----is_int32(integer_of_int32(x) + 1)

```

The hypothesis of this obligation is the precondition of main. As in H1 we have int(x) + 2 which is in range of 32-bit integer and as int(x) is also in the range thanks to axiom int32\_coerce, easily we prove that int(x) + 1 is also in this range.

#### VCs for the second obligation

The VCs for proving the precondition of the second inc x in the function main are:

They are explained by:

```

H1: int(x) + 2 is in range of 32 - bit integer.

H2: int(x) + 1 is in range of 32 - bit integer.

H3: int(x0) = int(x) + 1

```

Goal: int(x0) + 1 is in range of 32 - bit integer.

We need to prove that: int(x0) + 1 is in range of 32-bit integer. This means that (int(x) + 1) + 1 or int(x) + 2 (from H2, replace int(x0) with int(x) + 1) must be in range of 32-bit integer. As int(x) is in the range and from H1, this obligation is proved.

#### VCs for the post-condition obligation

The VCs generated for post-condition of the function main are shown below:

Goal: int(x1) = int(x) + 2

H5: int(x1) = int(x0) + 1

We need to prove that: int(x1) = int(x) + 2. From H5, we replace int(x1) with int(x0) + 1, then from H3, we replace int(x0) with int(x) + 1. Now what we have is: ((int(x) + 1) + 1) = int(x) + 2 and the obligation is proved.

H4: int(x0) + 1 is in range of 32 - bit integer.

#### 2.2.4 Use of Why in this thesis

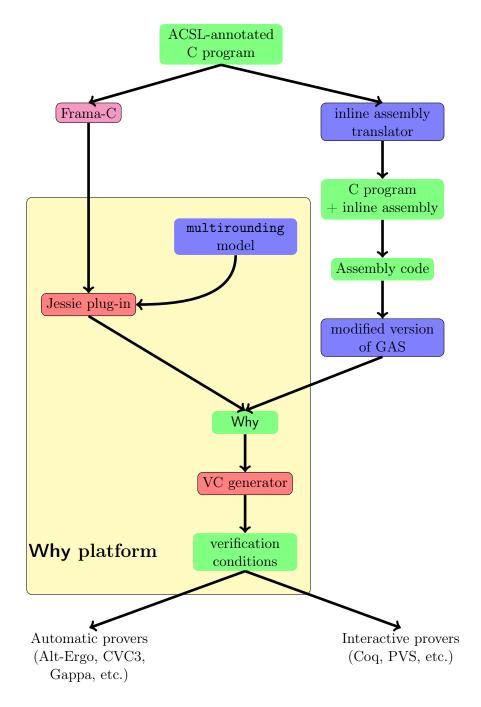

We all know about the syntax of Why. The question now is how it works in this thesis. In the whole thesis, we use the platform Why to generate verification conditions which are then proved by automatic or interactive provers. The use of Why is illustrated in Figure 2.7. In Part 1, we use Frama-C/Jessie which is a front-end of the Why platform for deductive program verification for proving a numerical program. Here, we define a model written in Why called multirounding. The Jessie plug-in uses this model to interpret each operation in a C program. In Part 2, we use

Figure 2.7: Use of Why

Why as the output of our translator. This means that we will translate the assembly code into programs in Why. These Why programs are then the inputs of VC generator to generate VCs. In Chapter 11, Why 3 – the next generation of Why (also called Why 2) – is used. We consider in this chapter that Why 3 is a specification language and we write the program directly in Why 3. The VCs are generated from this Why 3 program by Why 3 platform.

```

/*@ requires \abs(x) <= 0x1p-5;

@ ensures \abs(\result - \cos(x)) <= 0x1p-23;

@*/

float my_cos(float x) {

//@ assert \abs(1.0 - x*x*0.5 - \cos(x)) <= 0x1p-24;

return 1.0 f - x*x*0.5 f;

}

```

Figure 2.8: A C program annotated in ACSL

#### 2.3 ACSL and Frama-C

#### 2.3.1 ACSL

The ANSI/ISO C Specification Language (ACSL) <sup>3</sup> is a behavioral specification language for C programs. It is inspired by Caduceus [34, 33], itself inspired by JML [15, 46]. Its goal is to allow us to formally verify that the implementation of a C function respects its specifications.

The most important ACSL concept is the function contract. A function contract for a C function **f** is a set of requirements over the arguments of **f** and/or a set of properties that are ensured at the end of the function.

ACSL annotations are written in special C comments:

- /\*@ \*/ for one or multiple lines,

- //@ for a single-line annotation.

There are three important annotations in ACSL:

**Precondition** Precondition begins by the keyword requires. It contains the conditions which must hold before calling a function.

**Post-condition** Post-condition begins with the keyword ensures. It is the conditions which must hold after calling a function.

**Assertion** Properties which must hold at a program point.

The example in Figure 2.8 contains a C function float my\_cos(float x) with ACSL annotations. It provides an approximation of the cosine function on a small interval around 0. The precondition assumes that the absolute value of x is not greater than  $2^{-5}$  (=  $\frac{1}{32}$ ). The post-condition says that the absolute value of total error (which includes method error and rounding error) is not greater than  $2^{-23}$ . The method error is stated in an assertion which says that the bound of method error is  $2^{-24}$ .

Notice that all the operations in the annotations are done in real, they are not floating-point operations.

#### 2.3.2 Frama-C

Frama-C is a framework for static analysis of C code. This framework is flexible as it is easy to add a new plug-in. There are some ready-to-use plug-ins:

<sup>3</sup>http://frama-c.com/acsl.html

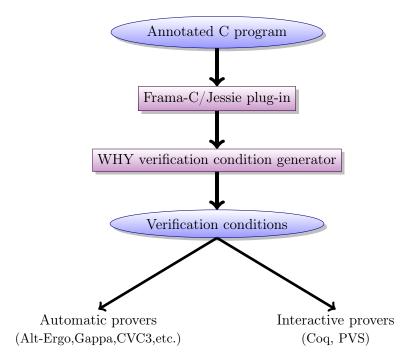

Figure 2.9: Proof of numerical programs in Frama-C/Jessie

Value analysis This plug-in uses abstract interpretation techniques. It computes variation domains for variables.

**Jessie** This is deductive verification plug-in. It is based on weakest precondition computation techniques. It aims at deductive verification of behavioral properties of the code, specified using the ACSL language.

In Jessie, there are some ready-to-use models for floating-point arithmetic called strict model and full model. The strict model includes rounding modes; single and double types; basic operations, etc. However, this model forbids exceptional values. The full model is an extension of the strict one. It allows to verify the programs in considering special values such as infinities, NaN, etc..

Figure 2.9 shows us how to prove a numerical program with Frama-C/Jessie. The input of this plug-in is an annotated C program. Its annotations are specified in ACSL. The output of Frama-C/Jessie plug-in is then the input of Why verification condition generator. This generator creates VCs which can be proved by automatic provers (Alt-Ergo, Gappa, CVC3, etc.) or interactive provers (Coq, PVS). The Gappa tool is an automatic prover, which handles formulas made of equalities and inequalities over expressions involving real constants and arithmetic operations. While Gappa does not handle quantifiers, SMT solvers which are a decision procedure that can handle quantifiers, various types of arithmetic and other decidable theories. This is the reason why in our examples, we often combine several automatic provers to prove a program.

Now let's back to example in Figure 2.8. All the needed properties about floating-point arithmetic are specified in ACSL. The analysis of this program is done by using Frama-C/Jessie with the strict model which follows strictly the IEEE-754 standard. The verification conditions generated are proved by Gappa except the assertion which is proved using Coq and interval tactic [56].

# Part I

# Hardware-independent proofs of numerical programs

# Chapter 3

# Hardware-independent bounds for floating-point operations

This chapter presents how to bound the rounding error of floating-point operations whatever the architecture and the compiler.

### 3.1 Bounds for one floating-point operation

As we want both correct and interesting properties on a floating-point computation without knowing which rounding will be in fact executed, the chosen approach is to consider only the rounding error. This will be insufficient in some cases, but we believe this can give useful and sufficient results in most cases.

As explained, the choice between 64-bit, 80-bit and double rounding is the main reason that causes the discrepancies of result. We prove a rounding error bound that is valid whatever the hardware, and the chosen rounding (corresponds to interval arithmetic [41, 60] and standard model [42]).

We denote by  $\circ_{64}$  the round-to-nearest in the double 64-bit type, by  $\circ_{80}$  the round-to-nearest to the extended 80-bit registers.

**Theorem 3.1** For a real number x, let  $\square(x)$  be either  $\circ_{64}(x)$ , or  $\circ_{80}(x)$ , or the double rounding  $\circ_{64}(\circ_{80}(x))$ . We have either

$$\left(|x| \ge 2^{-1022} \text{ and } \left| \frac{x - \Box(x)}{x} \right| \le 2050 \times 2^{-64} \right)$$

or

$$(|x| \le 2^{-1022} \text{ and } |x - \Box(x)| \le 2049 \times 2^{-1086}).$$

The proof is done by case analysis in the following subsections. This theorem is the basis of our approach to correctly prove numerical programs whatever the hardware. These bounds are tight as they are reached in all cases where  $\Box$  is the double rounding. They are a little bigger than the ones for 64-bit rounding (2050 and 2049 instead of 2048) for both cases. These bounds are therefore both correct, very tight, and just above the 64-bit's.

As  $2^{-1022}$  is a floating-point number, we have  $\Box(2^{-1022}) = 2^{-1022}$ . As all rounding functions are monotone<sup>1</sup>,  $\Box(x)$  is also monotone. Then  $|x| \geq 2^{-1022}$  implies  $|\Box(x)| \geq 2^{-1022}$  and vice versa.

Now let us prove the bounds of Theorem 3.1 on the rounding error for all possible values of  $\square$ .

<sup>&</sup>lt;sup>1</sup>A monotonic function f is a function such that, for all x and y,  $x \le y$  implies  $f(x) \le f(y)$ .

#### 3.1.1 Case 1: Rounding error in 64-bit rounding

From the formulas given by D. Goldberg [36] (explained in subsection 2.1.1), with 64-bit rounding, we have p = 53 and  $e_{min} = -1022$ . Therefore:

• With

$$|\circ_{64}(x)| \ge 2^{-1022}$$

:  $\left|\frac{x - \circ_{64}(x)}{x}\right| \le 2^{-53}$

• With

$$|\circ_{64}(x)| \le 2^{-1022}$$

:  $|x - \circ_{64}(x)| \le 2^{-1075}$

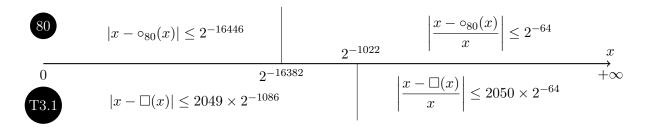

Let us see Figure 3.1, the rounding error bounds of 64-bit rounding are above the line and the ones of Theorem 3.1 (T3.1) are below the line. The rounding error bounds of D. Goldberg are smaller than the desired ones, therefore Theorem 3.1 holds in 64-bit rounding.

$$\begin{vmatrix} |x - \circ_{64}(x)| \le 2^{-1075} & \left| \frac{x - \circ_{64}(x)}{x} \right| \le 2^{-53} \\ 0 & \left| x - \square(x) \right| \le 2049 \times 2^{-1086} & \left| \frac{x - \square(x)}{x} \right| \le 2050 \times 2^{-64} \end{vmatrix}$$

Figure 3.1: Rounding error in 64-bit rounding vs. Theorem 3.1

#### 3.1.2 Case 2: Rounding error in 80-bit rounding

The 80-bit registers used in x87 have a 64-bit significand and a 15-bit exponent. Thus, p = 64 and  $e_{min} = -16382$ . By applying the formulas of D. Goldberg:

• With

$$|\circ_{80}(x)| \ge 2^{-16382}$$

:  $\left|\frac{x - \circ_{80}(x)}{x}\right| \le 2^{-64}$

• With

$$|\circ_{80}(x)| \le 2^{-16382}$$

:  $|x - \circ_{80}(x)| \le 2^{-16446}$

Figure 3.2: Rounding error in 80-bit rounding vs. Theorem 3.1

In Figure 3.2, the rounding error bounds in 80-bit rounding are above the line and the ones of Theorem 3.1 are below the line. Intuitively, the rounding error bounds in case of 80-bit rounding are much smaller in this case than Theorem 3.1's except in the case where |x| is between  $2^{-16382}$  and  $2^{-1022}$ . There, we have

$$|x - \circ_{80}(x)| \le 2^{-64} \times |x|$$

$\le 2^{-64} \times 2^{-1022} = 2^{-1086}.$

All bounds are smaller than that of Theorem 3.1, so Theorem 3.1 holds in 80-bit rounding.

#### 3.1.3 Case 3: Rounding error in double rounding

The bounds here will be the one of Theorem 3.1. We split in two cases depending on the value of |x|.

**Normal range** We first assume that  $|x| \ge 2^{-1022}$ . We bound the relative error by some computations and the previous formulas:

$$\left| \frac{x - \circ_{64}(\circ_{80}(x))}{x} \right| \le \left| \frac{x - \circ_{80}(x)}{x} \right| + \left| \frac{\circ_{80}(x) - \circ_{64}(\circ_{80}(x))}{x} \right|$$

$$\le 2^{-64} + \left| \frac{\circ_{80}(x) - \circ_{64}(\circ_{80}(x))}{\circ_{80}(x)} \times \frac{\circ_{80}(x)}{x} \right|$$

$$\le 2^{-64} + \left| \frac{\circ_{80}(x) - \circ_{64}(\circ_{80}(x))}{\circ_{80}(x)} \right| \times \left( \left| \frac{\circ_{80}(x) - x}{x} \right| + 1 \right)$$

$$\le 2^{-64} + 2^{-53} \times \left( \left| \frac{\circ_{80}(x) - x}{x} \right| + 1 \right)$$

$$\le 2^{-64} + 2^{-53} \times (2^{-64} + 1) = 2050 \times 2^{-64}$$

**Subnormal range** We now assume that  $|x| \leq 2^{-1022}$ . The absolute error to bound is  $|x - \circ_{64}(\circ_{80}(x))|$ . We have two cases depending on whether x is in the 80-bit normal or subnormal range.

If x is in the 80-bit subnormal range, then  $|x| < 2^{-16382}$  and

$$|x - \circ_{64}(\circ_{80}(x))| \le |x - \circ_{80}(x)| + |\circ_{80}(x) - \circ_{64}(\circ_{80}(x))|$$

$$\le 2^{-16446} + 2^{-1075} < 2^{-1086} + 2^{-1075} = 2049 \times 2^{-1086}$$

If x is in the 80-bit normal range, then  $2^{-16382} \le |x| < 2^{-1022}$  and

$$|x - \circ_{64}(\circ_{80}(x))| \le |x - \circ_{80}(x)| + |\circ_{80}(x) - \circ_{64}(\circ_{80}(x))|$$

$$\le 2^{-64} \times |x| + 2^{-1075}$$

$$< 2^{-64} \times 2^{-1022} + 2^{-1075} = 2^{-1086} + 2^{-1075} = 2049 \times 2^{-1086}$$

Then Theorem 3.1 holds in double rounding.

In conclusion, Theorem 3.1 is proved for all 3 roundings.

In practice, instead of dividing into two cases: normal range and subnormal range, we can use the following formula:

$$|x - \Box(x)| \le \varepsilon \times |x| + \eta \tag{3.1}$$

with  $\varepsilon = 2050 \times 2^{-64}$  and  $\eta = 2049 \times 2^{-1086}$ .

In strict IEEE-754, where inputs and outputs are on 64 bits, we can set  $\eta=0$  for addition and subtraction. Unfortunately here, inputs may be 80-bit numbers so  $\eta$  cannot be set to 0. Note also that absolute value and negation may produce a rounding if we put a 80-bit number into a 64-bit number.

#### 3.1.4 Proof in Coq

We used the Gappa Coq library <sup>2</sup> (version 0.13) for Coq (version 8.2) [12] to prove the correctness of Theorem 3.1.

<sup>&</sup>lt;sup>2</sup>The Gappa Coq Library adds a Gappa tactic to the Coq Proof Assistant. This tactic invokes the Gappa tool to solve properties about floating-point or fixed-point arithmetic. It can also solve simple inequalities over real numbers.

Figure 3.3: Coq theorem certifying the correctness of Theorem 3.1

The corresponding theorem (see Figure 3.3) and proof (228 lines) are in Coq <sup>3</sup>.

As we use the Gappa tactic in Coq to prove the theorem, a bound on x is necessary. This is the reason why we add the requirement that  $|x| \leq 2^{35000}$ . This value is large enough to satisfy all operations (addition, subtraction, multiplication, division, square root, negation and absolute value) in all types (64 or 80-bit rounding).

The Coq proof exactly corresponds to the one described. It is not very difficult, but needs many computations and a very large number of subcases. The formal proof gives a very strong guarantee on this result, allowing its use without doubt in the Frama-C platform.

## 3.2 Proofs of numerical programs

In the previous section, we gave a bound for one operation. If we have a program containing a sequence of operations, how can we prove it? In this section, we will use Theorem 3.1 to prove such a program.

#### 3.2.1 When FMA occurs

Theorem 3.1 gives rounding error formulas for various roundings denoted by  $\Box$  (64-bit, 80-bit and double rounding). Now, let us consider the FMA that computes  $x \times y + z$  with one single rounding. The question is whether a FMA was used in a computation. We therefore need an error bound that covers all the possible cases.

The idea is very simple: we consider a FMA as a rounded multiplication followed by a rounded addition. And we only have to consider another possible "rounding" that is the identity:  $\Box(x) = x$ .

This specific "rounding" magically solves the FMA problem: the result of a FMA is  $\Box(x \times y + z)$ , that may be considered as  $\Box_1(\Box_2(x \times y) + z)$  with  $\Box_2$  being the identity. So we handle in the same way all operations even in presence of FMA or not, by considering one rounding for each basic operation (addition, multiplication, etc.). Of course, this "rounding" easily verifies the formulas of Theorem 3.1.

<sup>&</sup>lt;sup>3</sup>The proof is available at http://www.lri.fr/~nguyen/research/rnd\_64\_80\_post.html

What is the use of this odd rounding? The idea is that each basic operation will be considered as rounded with a  $\square$  that may be one of the four possible roundings. Let us go back to the computation of a\*b+c\*d: it becomes  $\square(\square(a \times b) + \square(c \times d))$  with each  $\square$  being one of the 4 roundings. It gives us 64 possibilities. In fact, only 45 possibilities are allowed (for example, the addition cannot be exact). But *all* the real possibilities are *included* in all the considered possibilities. And all considered possibilities have a rounding error bounded by Theorem 3.1.

So, by considering the identity as a rounding like the others, we handle all the possible uses of the FMA in the same way as we handle multiple roundings.

#### 3.2.2 Bounds of a sequence of operations

**Theorem 3.2** Let  $\odot$  be an operation among addition, subtraction, multiplication, division, square root, negation and absolute value. Let  $x = \odot(y,z)$  be the exact result of this operation (without rounding). Then, whatever the architecture and the compiler, the computed result  $\tilde{x}$  is such that

$$\begin{split} &If \ |x| \geq 2^{-1022}, \ then \\ & \quad \tilde{x} \in \left[ x - 2050 \times 2^{-64} \times |x| \ , \ x + 2050 \times 2^{-64} \times |x| \right] \quad \backslash \quad \left] - 2^{-1022} \ , \ 2^{-1022} \left[ . \right. \\ & If \ |x| \leq 2^{-1022}, \ then \\ & \quad \tilde{x} \in \left[ x - 2049 \times 2^{-1086} \ , \ x + 2049 \times 2^{-1086} \right] \cap \left[ -2^{-1022} \ , \ 2^{-1022} \right]. \end{split}$$

This is straightforward as the formulas of Theorem 3.1 subsume all possible roundings (64 or 80-bit) and operations (using FMA or not), whatever the architecture and the compiler choices.

**Theorem 3.3** If we define each result of an operation by the formulas of Theorem 3.2, and if we are able to deduce from these intervals an interval  $\mathcal{I}$  for the final result, then the really computed final result is in  $\mathcal{I}$  whatever the architecture and the compiler that preserves the order of operations.

This is proved by using Theorem 3.2.

## 3.3 Implementation

What we have until now is the bound of the rounding error for a sequence of operations. The question is how to use Theorem 3.1 to prove a program in Frama-C/Jessie?

An interesting point of the Jessie plug-in is that we can change the interpretation of floating-point operations easily. We define a new "pragma" called multirounding in the same way as the strict model of Jessie plug-in and change the interpretation of each basic floating-point operation (addition, subtraction, multiplication, division, absolute value, square root and negation). In order to do this, we put as post-conditions the formulas of Theorem 3.1 for operations in the Frama-C platform to look into the rounding error of the whole program. Ordinarily, the pragma directive is the method specified by the C standard for providing additional information to the compiler, beyond what is conveyed in the language itself. In our pragma as in Jessie, each floating-point number is represented by two values, an exact one (a real value, as if no rounding occurred) and a rounded one (the true floating-point value). At each computation, we are only able to bound the difference between these two values, without knowing the true rounded value.

For example, the post-condition of the addition is defined by the following predicate:

double is an abstract type, double\_value and double\_exact are logic functions which return a rounded and an exact value from a double. This abstract type and the two logic functions have already defined in the strict and full model and we reuse them in our approach. In this predicate, we also define the exact result which is the addition of two exact values. Notice that the value  $0x1.004p-53 = 2050 \times 2^{-64}$  and  $0x1.002p-1075 = 2049 \times 2^{-1086}$ .

The post-conditions for other operations (subtraction, multiplication division, square root, negation, absolute value) are defined in the same way as the addition.

Each operation is declared by a parameter and the post-condition will use the predicate above. The parameter add\_double for addition in double, for example, is declared as follows:

```

parameter add_double :

m:mode -> x:double -> y:double ->

{ no_overflow_double(m,double_value(x) + double_value(y)) }

double

{ add_double_post(m,x,y,result) }

```

This parameter returns a double value. The precondition assures that there is no overflow in the addition. The post-condition is the predicate add\_double\_post.

Notice that the rounding modes that we handle in this approach are rounding-to-nearest modes (ties to even and ties away from zero). Thus, in this Why parameter, either  $m = nearest_even$  or  $m = nearest_even$  are allowed.

## Chapter 4

# When the compiler re-organizes a computation