### Study and design of a manycore architecture with multithreaded processors for dynamic embedded applications

Charly Bechara

### ► To cite this version:

Charly Bechara. Study and design of a many core architecture with multithreaded processors for dynamic embedded applications. Other [cs.OH]. Université Paris Sud - Paris XI, 2011. English. NNT: 2011PA112283 . tel-00713536

### HAL Id: tel-00713536 https://theses.hal.science/tel-00713536

Submitted on 2 Jul2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

energie atomique • energies alternatives

### **UNIVERSITE PARIS-SUD 11**

### ÉCOLE DOCTORALE : Informatique Paris-Sud (EDIPS) Laboratoire : LCE, CEA LIST

**DISCIPLINE** Informatique

### THÈSE DE DOCTORAT THÈSE DE DOCTORAT SUR TRAVAUX

soutenue le 08/12/2011

par

### **Charly BECHARA**

# Study and design of a manycore architecture with multithreaded processors for dynamic embedded applications

Directeur de thèse : Co-directeur de thèse :

Composition du jury :

*Président du jury : Rapporteurs :*

Examinateurs :

Daniel ETIEMBLE Nicolas VENTROUX

Alain MERIGOT Frédéric PETROT Olivier SENTIEYS Agnès FRITSCH Professeur - Université Paris-Sud, LRI Ingénieur chercheur (PhD) - CEA LIST

Professeur - Université Paris-Sud Professeur - INP, Grenoble Professeur - Université de Rennes (ENSSAT) Chef du laboratoire (PhD) – Thales Communications France

# Abstract

Embedded systems are getting more complex and require more intensive processing capabilities. They must be able to adapt to the rapid evolution of the high-end embedded applications that are characterized by their high computation-intensive workloads (order of TOPS: Tera Operations Per Second), and their high level of parallelism. Moreover, since the dynamism of the applications is becoming more significant, powerful computing solutions should be designed accordingly. By exploiting efficiently the dynamism, the load will be balanced between the computing resources, which will improve greatly the overall performance.

To tackle the challenges of these future high-end massively-parallel dynamic embedded applications, we have designed the AHDAM architecture, which stands for "Asymmetric Homogeneous with Dynamic Allocator Manycore architecture". Its architecture permits to process applications with large data sets by efficiently hiding the processors' stall time using multithreaded processors. Besides, it exploits the parallelism of the applications at multiple levels so that they would be accelerated efficiently on dedicated resources, hence improving efficiently the overall performance. AHDAM architecture tackles the dynamism of these applications by dynamically balancing the load between its computing resources using a central controller to increase their utilization rate.

The AHDAM architecture has been evaluated using a relevant embedded application from the telecommunication domain called "spectrum radio-sensing". With 136 cores running at 500 MHz, AHDAM architecture reaches a peak performance of 196 GOPS and meets the computation requirements of the application.

**Keywords:** Multicore, MPSoC, manycore, asymmetric, multithreaded processors, embedded systems, dynamic applications, simulation

# Résumé

Les systèmes embarqués sont omniprésents dans notre vie quotidienne. Un grand nombre de produits contiennent un ou plusieurs processeurs invisibles pour l'utilisateur dans un emballage sophistiqué. Ils effectuent des traitements complexes et communiquent avec l'environnement pour satisfaire les besoins des utilisateurs.

Les systèmes embarqués couvrent tous les aspects de la vie moderne et il y a de nombreux exemples de leur utilisation. Dans le domaine des télécommunications, il existe de nombreux systèmes embarqués, des commutateurs téléphoniques pour les réseaux jusqu'aux téléphones mobiles. Dans le domaine de l'électronique grand public, les systèmes embarqués sont utilisés dans les assistants numériques personnels (PDA), les lecteurs MP3, les consoles de jeux vidéo, les appareils photo numériques, les lecteurs de DVD, les GPS et les imprimantes. Cette liste est n'est pas exhaustive et il y a beaucoup d'autres exemples dans d'autres domaines comme les systèmes de transport, les équipements médicaux, les applications militaires, etc.

Les utilisateurs finaux ne veulent pas seulement davantage de fonctionnalités et de meilleures performances, mais ils sont aussi intéressés par des dispositifs ayant le même niveau de performance, mais moins chers. Ainsi, on observe des convergences dans les marchés de l'électronique grand public. Les montres numériques et les pagers ont évolué vers les assistants numériques personnels (PDA) et les téléphones intelligents (Smartphones). De même, les ordinateurs de bureau et les portables convergent vers les netbooks qui utilisent le processeur Atom d'Intel et les processeurs ARM. Ces dispositifs demandent de plus en plus des capacités calculatoires pour un budget énergétique faible avec des contraintes thermiques strictes.

Pendant près de 40 ans, les innovations technologiques sont succédées dans le but de réduire les temps d'exécution des programmes exécutés par le processeur. Une technique s'est appuyée sur la réduction des dimensions des transistors, qui a conduit à une augmentation du nombre de composants intégrables sur une puce, permettant d'implanter des architectures plus complexes et une augmentation de la fréquence d'horloge du processeur, d'où une exécution plus rapide des instructions. Cependant, ce gain de performance est aujourd'hui limité par les problèmes énergétiques et de dissipation thermique. En plus, les systèmes embarqués fonctionnent avec un budget de puissance limitée et donc d'augmenter la fréquence du processeur pour améliorer la performance n'est plus une solution pour les concepteurs de système.

Heureusement, de nombreuses applications embarquées sont naturellement parallèles. Les applications sont parallélisées au niveau des tâches pour atteindre des performances supérieures. Il existe deux solutions pour s'attaquer au parallélisme de tâches (TLP).

La solution la plus simple pour exécuter plusieurs tâches consiste à utiliser un processeur "monothread" avec toutes les techniques déployées pour accélérer le traitement d'un seul flux d'instructions. Le système d'exploitation organise et répartit les threads sur le processeur pour donner l'impression qu'ils sont exécutés en parallèle. Cela peut être considéré comme une virtualisation des ressources d'exécution. Pour cette virtualisation, deux techniques d'accélération pour les processeurs monothreads sont largement utilisées. La première, appelée le parallélisme temporel, consiste à réduire le temps d'exécution en divisant l'exécution des instructions en plusieurs étapes successives avec un chevauchement dans l'exécution de plusieurs instructions. C'est ce qu'on appelle une exécution pipeline. La seconde, appelée le parallélisme spatial, repose sur la multiplication des ressources d'exécution. Dans ce type d'architectures, l'expression du parallélisme peut être explicite ou implicite. Le parallélisme est explicite lorsque le compilateur gère les dépendances de données et le flux de contrôle pour garantir l'exécution correcte du programme. Le contrôle est alors relativement simple et permet d'utiliser des fréquences d'horloge plus élevées ou de réduire les besoins énergétiques à performance donnée. Les architectures VLIW en sont l'exemple type. D'autre part, lorsque l'architecture traite dynamiquement tous les aléas d'exécution, le parallélisme est exploité de manière implicite. Ces architectures sont appelés superscalaires. Cette approche simplifie la tâche du compilateur au prix d'une plus grande complexité du matériel: les mécanismes de spéculation, l'exécution dans le désordre et les prédictions de branchement ont un grand impact sur l'efficacité énergétique et l'efficacité transistor de l'architecture du processeur.

La deuxième solution consiste à multiplier le nombre de cœurs pour exécuter les tâches en parallèle. L'avancement de la technologie des semi-conducteurs a permis aux fabricants de puces d'augmenter la puissance de calcul globale en intégrant des processeurs supplémentaires ou "cœurs" sur la même puce, ce qui est la version moderne des multiprocesseurs. Ainsi, cette solution exploite le parallélisme au niveau des threads (TLP), où plusieurs threads peuvent être exécutés en parallèle sur plusieurs cœurs. Dans le domaine des systèmes embarqués, ces architectures sont connues sous le terme MPSoC, qui signifie Multi-Processor System-On-Chip.

Dans ce contexte, c'est une architecture MPSoC pour les systèmes embarqués qui est étudiée et évaluée dans cette thèse.

Les systèmes embarqués sont de plus en plus complexes et requièrent des besoins en puissance de calcul toujours plus importants. Ils doivent être capables de s'adapter à l'évolution rapide des applications qui requièrent un haut niveau de performance (ordre du TOPS: Téra-opérations par seconde) et de parallélisme. Notamment, les applications haut de gamme ont beaucoup de parallélisme au niveau de tâches (TLP) et de parallélisme au niveau des boucles (LLP). Par conséquent, les architectures MPSoC doivent cibler l'ère "manycore" afin de répondre à ces besoins de calcul élevés. Les architectures multicœurs doivent être efficace au niveau transistor et énergie, puisque la taille de la puce et le budget énergétiques sont limitées dans les systèmes embarqués. Ainsi, ils doivent être conçus avec un bon équilibre entre le nombre de cœurs et la quantité de mémoire sur la puce. Les processeurs doivent être très efficaces en transistor et énergie. Il devrait n'y avoir aucune perte injustifiée de l'énergie dans les ressources d'exécution avec des techniques telles que la spéculation. Dans de telles architectures multicœurs complexes, il y a beaucoup de sources de latences qui provoquent des arrêts temporaires d'exécution des instructions, d'où une perte d'efficacité et d'énergie puisque les circuits continuent d'être alimentés pendant ces suspensions de fonctionnement. Dans ce contexte, les processeurs multithreads sont une solution intéressante à étudier.

Une caractéristique importante des applications embarquées de calculs intensifs est le dynamisme. Alors que certains algorithmes sont indépendants des données avec un flux de contrôle régulier, d'autres algorithmes sont très dépendants des données et leur temps d'exécution varie en fonction des données d'entrée, du contrôle de flux irrégulier, et de leur auto-adaptabilité aux environnements applicatifs. Par conséquent, l'architecture MPSoC devrait être très réactive par rapport aux besoins de calcul afin d'augmenter le taux d'occupation d'exécution des ressources. Ainsi, il devrait permettre une répartition de charge globale et dynamique entre les ressources d'exécution.

Pour répondre aux besoins de ces applications de calcul intensif massivement parallèle et dynamique, nous proposons dans cette thèse l'architecture AHDAM qui signifie architecture homogène asymétrique avec allocation dynamique ou bien Asymmetric Homogeneous with Dynamic Allocator Manycore architecture. Cette architecture a été conçue afin de masquer efficacement la latence d'accès à la mémoire extérieure dont de nombreux accès sont nécessaires lors de la manipulation de grands volumes de données. Pour cela, des processeurs multitâches ont été utilisés. Par ailleurs, l'architecture AHDAM imbrique plusieurs niveaux de parallélisme afin de tirer partie efficacement des différentes formes de parallélisme des applications, et ainsi atteindre un haut niveau de performance. Enfin, cette architecture utilise un contrôleur centralisé pour équilibrer la charge de calcul entre ses ressources de calcul afin d'augmenter leur taux d'utilisation et d'exécuter efficacement les applications fortement dynamiques.

Le chapitre 1 présente le contexte de notre travail en se concentrant principalement sur les exigences des applications et des solutions architecturales existantes. Le cadre de notre étude sont les applications massivement parallèles et dynamiques pour l'embarqué. Ces applications sont très parallèles. Le parallélisme peut être extrait au niveau thread (TLP) et au niveau des boucles (LLP). Ainsi, une application peut avoir de nombreux threads qui peuvent être traitées en parallèle. Par conséquent, les architectures MPSoCs de type "manycore" sont des solutions naturelles pour ces applications. En outre, le dynamisme de ces applications nécessite une solution efficace pour gérer l'utilisation des ressources et équilibrer les charges dans le MPSoC afin de maximiser la performance globale.

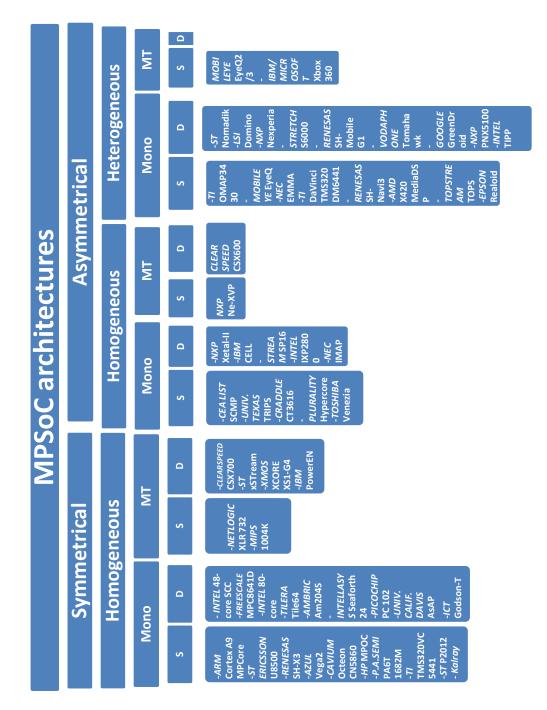

On identifie trois grandes familles de MPSoCs pour les systèmes embarqués dans l'état de l'art: les MPSoC symétriques, les MPSoC asymétriques homogènes et les MPSoC asymétriques hétérogènes.

Les MPSoCs symétriques sont constitués de plusieurs processeurs homogènes qui exécutent à la fois la tâche de contrôle et les tâches de calculs. Les MPSoCs asymétriques sont constitués d'un (parfois plusieurs) processeur de contrôle centralisé ou hiérarchisé, et plusieurs processeurs homogènes ou hétérogènes pour les tâches de calcul. Dans notre contexte d'étude, les architectures MPSoC asymétriques homogènes sont la meilleure solution pour les applications dynamiques, puisqu'elle permet l'équilibrage de charge rapide et réactive entre les processeurs homogènes. Ces architectures ont une grande efficacité transistor et énergétique en raison de la séparation entre les processeurs de contrôle et de calcul.

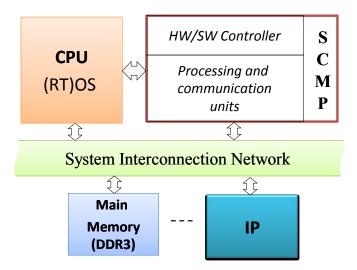

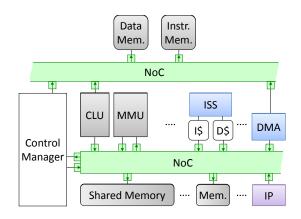

En particulier, une architecture MPSoC asymétriques homogène, appelé SCMP, qui est la propriété du laboratoire du CEA LIST, sera utilisée dans le reste de cette thèse comme l'architecture de référence pour les expérimentations. SCMP est conçue pour traiter les applications embarquées avec un comportement dynamique en faisant migrer les threads entre les cœurs de calcul en utilisant un contrôleur central.

Par ailleurs, et selon nos observations, les architectures MPSoC asymétriques homogènes ne répondent pas aux exigences des applications embarquées haut de gamme qui sont massivement parallèles. Tout d'abord, elles ne sont pas extensibles au niveau manycore parce que le contrôleur central est une source de contentions. Par exemple, SCMP peut supporter jusqu'à 32 cœurs de calcul avant de connaître une dégradation des performances. Ensuite, les puces manycore ont un nombre limité de pattes d'E/S, d'où une bande passante limitée. Cela implique que plus le trafic hors-puce augmentera, plus les processeurs subiront de suspensions dans la puce.

Il existe deux voies possibles pour améliorer les architectures MPSoCs asymétriques homogènes: la scalabilité et les processeurs multitâches matériels. Dans cette thèse, nous allons d'abord étudier les avantages/inconvénients du multithreading matériel dans l'architecture SCMP, puis nous allons proposer une nouvelle solution qui va cibler l'ère manycore. Cette solution doit relever les défis des applications embarquées.

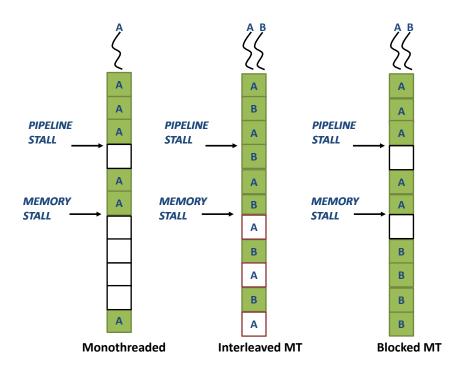

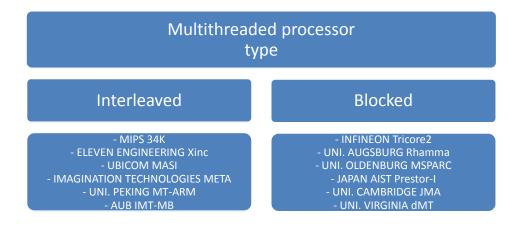

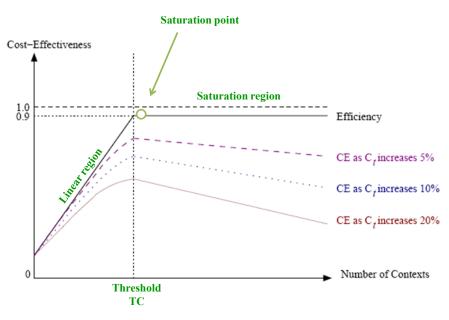

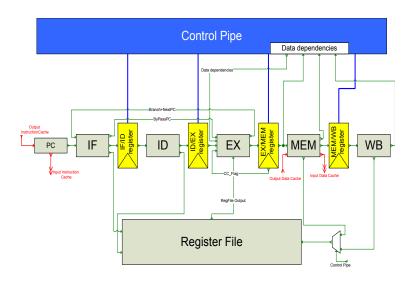

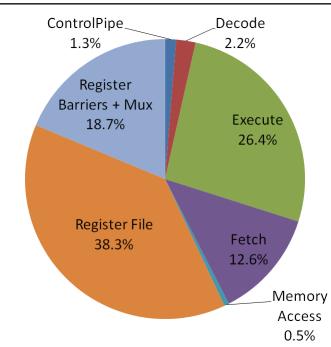

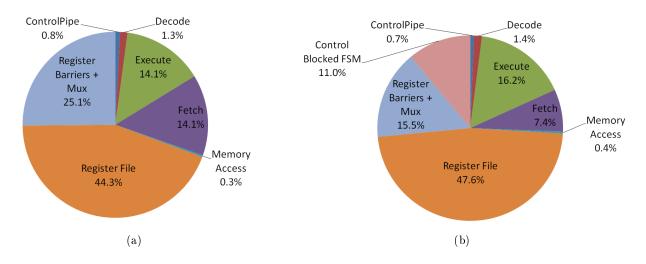

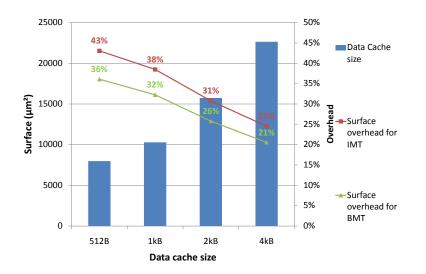

Le chapitre 2 explore et analyse les performances et l'efficacité des processeurs matériels multithreads dans les systèmes embarqués. Les processeurs embarqués doivent avoir une taille dans l'ordre du mm<sup>2</sup> et consommer de l'ordre de quelques mW. Ainsi, ils doivent utiliser une technologie simple pour exploiter l'ILP, telles que le pipeline ou l'approche VLIW. Un processeur matériel multithread fournit les ressources matérielles et des mécanismes pour exécuter plusieurs threads matériels sur un cœur de processeur, afin d'accroître son utilisation du pipeline, et donc le débit d'exécution des applications. Au sein d'un processeur multithread, les slots d'instruction inutilisés sont remplis par des instructions d'autres threads. Les threads matériels sont en compétition pour accéder aux ressources partagées et pour tolérer les aléas de pipeline avec une longue période de latence, comme c'est le cas lors d'un défaut de cache. Ces événements peuvent bloquer le pipeline jusqu'à 75% de son temps d'exécution. Ainsi, le principal avantage des processeurs multithreads sur les autres types de processeurs est leur capacité à cacher la latence d'un thread. Les futures architectures manycores ont tendance à utiliser de petits cœurs RISC comme éléments de base des traitements. Dans ce cas, plusieurs processeurs peuvent être intégrés sur une seule puce tout en gardant la consommation d'énergie globale sous un seuil tolérable. Par conséquent, nous considérons un processeur RISC (AntX) avec un pipeline à 5 étages, démarrant dans l'ordre une seule instruction par cycle. Ensuite, nous étudierons ce processeur, au niveau RTL (VHDL), avec deux techniques de multithreading: le multithreading entrelacé (IMT) et le multithreading par bloc (BMT). Nous avons synthétisé les 3 processeurs en technologie TSMC 40 nm. Les résultats de synthèse montre que le banc de registres occupe plus de 38% de la surface de base globale. Donc, il n'est pas efficace d'intégrer plus de deux threads (TC) par processeur multithread et c'est pourquoi nous nous sommes limités à deux threads par processeur. Les résultats de synthèse montrent également que les versions IMT et BMT ont 73.4% et 61.3% de surface en plus par rapport au processeur monothread. C'est le BMT qui a la plus petite surface.

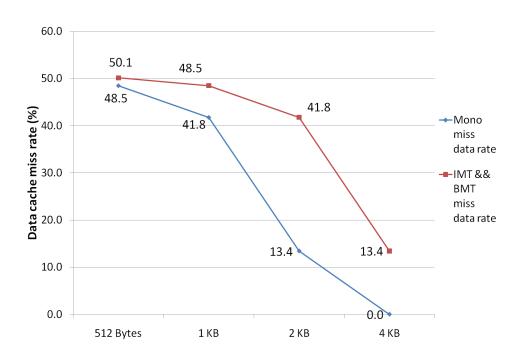

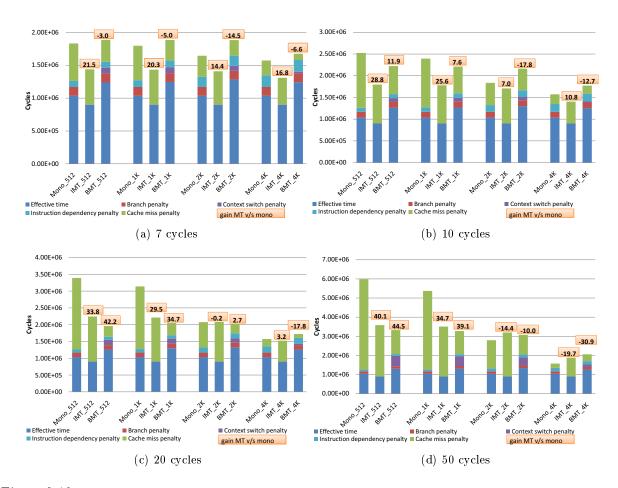

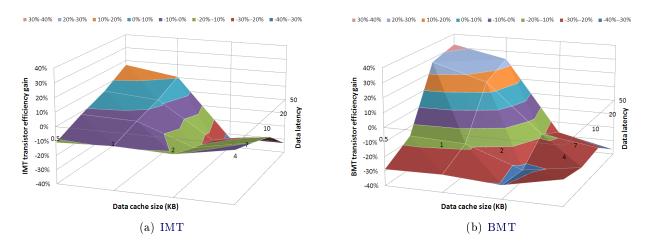

Enfin, nous avons comparé les performances et l'efficacité transistor des processeurs MT en utilisant comme application le tri-bulle, tout en variant la taille du cache L1 de données et la latence de la mémoire de données. Les résultats montrent qu'il n'y a pas de conclusion définitive sur le meilleur type de processeur multithread. En fait, il y a un compromis entre la taille des données de la mémoire cache, la latence mémoire de données, et le surcoût en surface du cœur. Choisir le meilleur processeur multitâche dépend fortement du cahier des charges du concepteur du système et des exigences d'application.

D'après cette conclusion, nous allons explorer dans le prochain chapitre l'impact du processeur multithread sur les performances d'une architecture MPSoC asymétrique: l'architecture SCMP.

#### Résumé

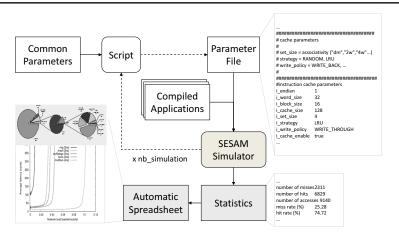

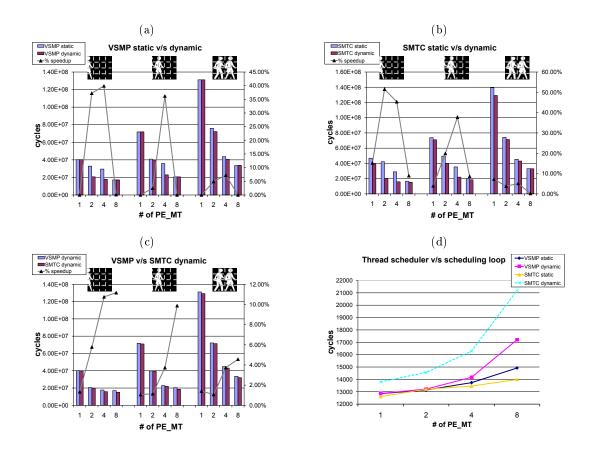

Le chapitre 3 étudie les avantages/inconvénients du multithreading matériel dans un contexte MPSoC asymétrique homogène (architecture SCMP). Pour cette exploration, nous présentons le simulateur SESAM, dans lequel l'architecture SCMP est modélisée. Ensuite, nous étendons SESAM pour supporter les processeurs multithreads. En particulier, nous avons développé un nouveau simulateur multithread au cycle près (ISS) en SystemC pour modéliser le processeur IMT/BMT avec deux threads (TC). Nous utilisons plusieurs benchmarks basés sur un contrôle des flux et des applications de streaming afin de choisir ce qui convient le mieux pour un processeur multithread entre les approches IMT et BMT, quel ordonnanceur de threads global pour plusieurs processeurs multithread donne la meilleure performance (VSMP ou SMTC), et quelle architecture MPSoC asymétrique est la plus performante et transistor efficace (SCMP ou MT\_SCMP).

Deux applications du domaine de l'embarqué sont utilisées: l'étiquetage de composants connexes (de type contrôle de flux) et WCDMA (de type dataflow/streaming). Dans le modèle d'exécution de flux de contrôle, les tâches sont traitées jusqu'à la fin, alors que dans le modèle d'exécution de flux de données, les tâches se synchronisent entre elles sur les données, créant ainsi des aléas de pipeline en plus. Les deux modèles d'exécution couvrent un large ensemble de comportements d'applications.

Les résultats montrent que le processeur multithread bloqué (BMT) et l'ordonnanceur SMTC convient le mieux pour MT\_SCMP.

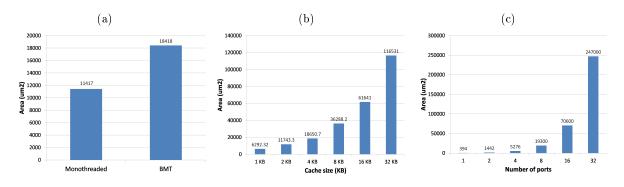

Afin d'estimer la surface des deux systèmes, nous utilisons les résultats de synthèse en technologie TSMC 40 nm pour les processeurs et les réseaux d'interconnexion, et nous estimons la taille des caches en utilisant l'outil CACTI 6.5. Pour résumer les résultats, le MT\_SCMP donne une meilleure performance de pointe, mais inférieure en efficacité transistor que SCMP. En fait, les performances de MT\_SCMP dépendent fortement de cinq paramètres principaux: le TLP de l'application, le taux de défauts de caches, la latence d'un défaut de caches, la hiérarchie mémoire, et l'ordonnancement global des threads. Ce dernier paramètre implique que pour des applications dynamiques, un équilibrage de charge dynamique et l'ordonnancement donnent une performance optimale. C'est pourquoi SCMP est une architecture hautement efficace.

Choisir des processeurs multithreads ou non pour SCMP est la responsabilité du concepteur du système. Si les performances de pointe sont un paramètre clé, les processeurs multithreads sont une solution intéressante. Cependant, pour l'efficacité transistor, les processeurs monothreads restent une solution plus efficace.

SCMP a quelques limitations pour s'attaquer aux exigences des applications dynamiques et massivement parallèles. Il y a des limites à la scalabilité au niveau manycore et des limitations pour traiter des quantités de données qui ne rentrent pas dans la mémoire sur la puce.

Pour surmonter ces limitations, nous allons concevoir dans le chapitre suivant une nouvelle architecture manycore qui s'attaque aux défis des applications dynamiques haut de gamme de l'avenir appelée architecture AHDAM.

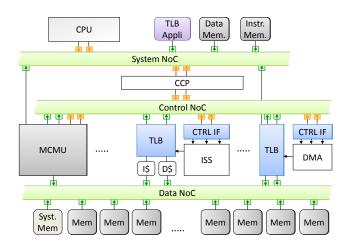

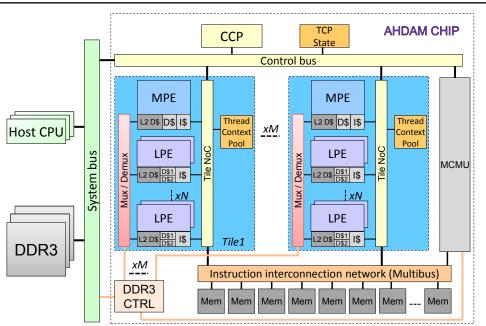

Le chapitre 4 présente une nouvelle architecture manycore appelée AHDAM, qui signifie Asymmetric Homogeneous with Dynamic Allocator Manycore architecture. Il est utilisé comme un accélérateur pour les applications massivement parallèles et dynamiques en permettant la migration des threads entre les unités d'exécution via un contrôleur central. En outre, elle est conçue pour accélérer l'exécution des codes de boucle, ce qui constitue souvent une grande partie du temps d'exécution de l'application. L'architecture AHDAM met en œuvre des processeurs monothread et multithread pour accroître l'utilisation des processeurs si nécessaire. L'architecture AHDAM est présentée en détail dans ce chapitre. En particulier, son environnement de système, son modèle de programmation, sa description architecturale et les fonctionnalités de chaque composant matériel, son modèle d'exécution, et sa scalabilité maximale, sont expliquées. L'étude montre que la scalabilité d'AHDAM peut atteindre jusqu'à 136 processeurs (8 Tuiles x 16 LPEs + 8 MPEs) en fonction de l'exigence d'application.

Enfin, le chapitre 5 évalue les performances et l'efficacité transistor de l'architecture AHDAM en utilisant une application pertinente de l'embarquée dans le domaine des télécommunications appelé radio-sensing. Cette application a été conçue par Thales Communications France. La configuration "high-sensitivity" de cette application a beaucoup d'exigences de calcul (75.8 GOPS), beaucoup de parallélisme au niveau des threads et des boucles (99.8%), une grande quantité de données (432 Mo), et elle est dynamique. L'application de "radio-sensing" est parallélisée et portée en utilisant le modèle de programmation d'AHDAM. L'architecture AHDAM est simulée en utilisant une combinaison d'outils de simulation tels que SESAM et Trimaran, et en utilisant le modèle analytique du processeur BMT que nous avons développé. Avec 136 cœurs cadencés à 500 MHz, l'architecture AHDAM atteint une performance crête de 196 GOPS et répond aux exigences de l'application.

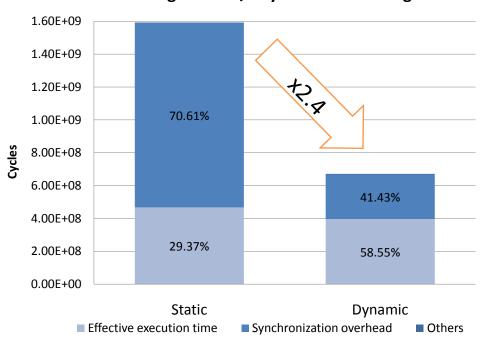

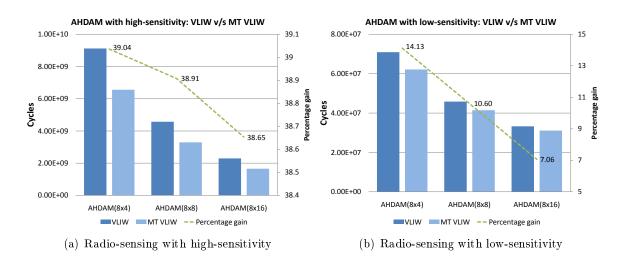

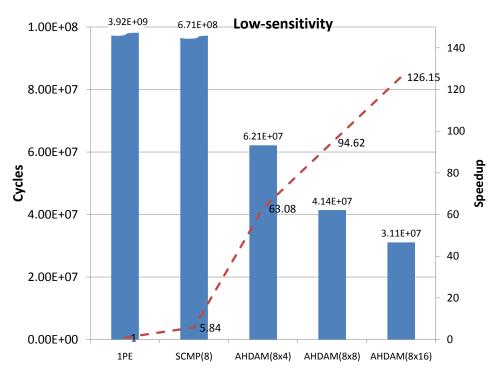

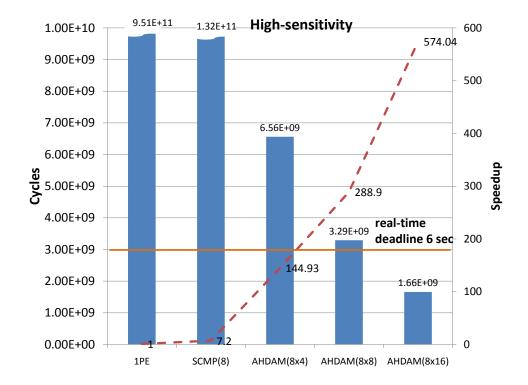

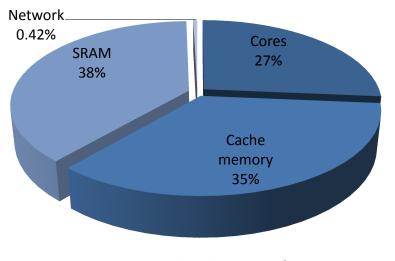

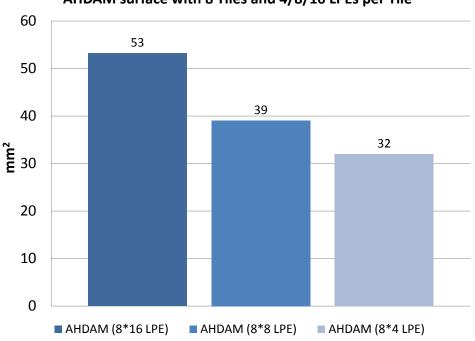

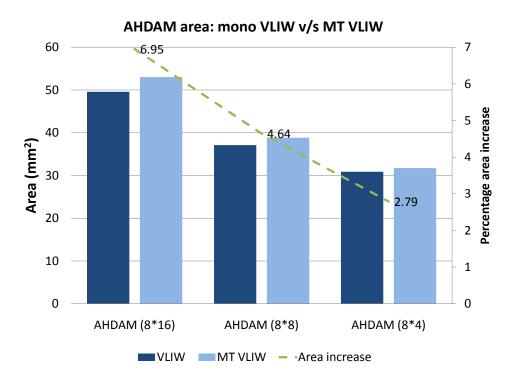

Nous évaluons l'efficacité transistor de l'architecture. Après avoir mené plusieurs expérimentations, nous concluons que la propriété asymétrique de l'architecture AHDAM est essentielle pour les applications dynamiques pour augmenter leurs performances. L'ordonnanceur dynamique donne une accélération de 2.4 par rapport à l'ordonnanceur statique de l'application de "radio-sensing". En outre, le multithreading booste les performances de l'architecture AHDAM avec un gain de 39% par rapport au monothread pour seulement 7% d'augmentation de surface totale. Donc, le multithreading augmente l'efficacité transistor de l'architecture. Enfin, l'architecture AHDAM a une accélération de 574 par rapport a 1 PE, tandis que SCMP a une accélération de 7.2. Ceci dit, l'architecture AHDAM est un progrès important par rapport à SCMP et peut répondre aux exigences des futures applications haut de gamme, massivement parallèles, et dynamiques. La surface d'AHDAM sans les interconnections est estimée d'être  $53 mm^2$  en technologie 40 nm.

Il reste beaucoup de concepts proposés dans l'architecture AHDAM qui ont encore besoin d'études, de développements et d'améliorations.

Les perspectives à court terme peuvent être divisées en trois étapes principales: le développement d'un simulateur, la construction d'un prototype, et la comparaison avec les autres architectures multicœurs.

Dans la première étape, nous avons besoin de développer un simulateur pour AHDAM, principalement une extension de l'environnement de simulation SESAM. De nouveaux composants doivent être élaborés en SystemC qui n'existaient pas auparavant pour l'architecture SCMP, telles que la mémoire cache L2 et ses protocoles, le *Thread Context Pool* et la mémoire scratchpad TCP state. En outre, un simulateur multithread VLIW doit être développé. Ensuite, nous avons besoin d'encapsuler chaque ensemble de processeurs (tuile) dans un module afin que le contrôleur

#### Résumé

matériel la voie comme un PE, et de valider toutes les fonctionnalités d'une tuile. En particulier, l'architecture du réseau sur puce doit être étudiée. Enfin, la mémoire L2 d'instructions et de données devrait être divisée en deux mémoires séparées.

Après avoir construit l'environnement de simulation AHDAM, l'environnement d'exécution proposé pour "Fork-Join" devrait être développé. Ce "runtime" est un élément essentiel de la fonctionnalité de l'architecture AHDAM et la gestion des transferts internes à une tuile ou entre tuiles. L'objectif est de trouver le nombre optimal de threads à lancer (fork) car c'est un paramètre important pour l'accélération de l'ensemble des régions de boucles. En outre, le modèle d'exécution "farming" doit être validé.

Avec un simulateur AHDAM et l'environnement d'exécution utilisable, il serait intéressant de poursuivre le développement de la chaîne de programmation automatique que nous avons commencé dans le chapitre 4. Il pourrait être basé sur l'outil PAR4ALL. Cela nous permettrait de porter facilement toutes les applications 'legacy' sur l'architecture AHDAM.

La deuxième étape principale consiste à construire un prototype de l'architecture AHDAM sur une carte d'émulation matérielle. Ce prototype sera la preuve de concept de l'architecture. Ayant un tel prototype, on peut estimer précisément l'efficacité transistor et énergétique de l'architecture AHDAM ainsi que des processeurs multithreads. En particulier, nous pouvons rendre la puce AHDAM plus économe en énergie, en explorant de nouvelles stratégies d'équilibrage de charges à l'intérieur de chaque tuile et entre les tuiles, et d'intégrer les stratégies dans l'environnement d'exécution. D'autres techniques énergétiques efficaces comme DVFS peuvent être implémentés sur FPGA. Nous pouvons imaginer que chaque tuile fonctionne avec une fréquence différente contrôlée par le contrôleur matériel selon les besoins de l'application.

Enfin, la troisième étape principale consiste à comparer l'architecture AHDAM avec d'autres solutions manycore pertinentes tels que TILE64 de Tilera, P2012, de ST Microelectronics et MPPA de Kalray. Pour cette raison, nous avons besoin de porter plusieurs applications de l'embarqué qui sont dynamiques et pertinentes et qui ont beaucoup de parallélisme et des exigences de calcul. Ces applications doivent fonctionner sur toutes ces architectures afin qu'on puisse mener une comparaison appropriée.

A ce stade, nous sommes prêts à mener un transfert technologique de la puce d'AHDAM pour des projets nationaux/européens. En particulier, nous pouvons développer deux versions d'AHDAM: bas de gamme et haut de gamme. La première version vise le marché de l'embarqué, tandis que la dernière cible le marché des serveurs, et le calcul dans le nuage en particulier. Ce qui différencie les deux puces est le nombre de tuiles, le nombre de processeurs par tuile, et les stratégies d'équilibrage de charge utilisée dans la puce qui dépendent de la performance et de l'efficacité énergétique.

Sur le long terme, il y a plusieurs améliorations architecturales imaginables pour l'architecture AHDAM.

Comme la technologie du procédé s'améliore, il y a plus de préoccupations au sujet de la fiabilité de l'architecture AHDAM. AHDAM pourrait être utilisé dans des domaines critiques tels que les applications militaires, nucléaires et spatiales, où la tolérance de panne est une décision architecturale non négligeable. Nous pouvons imaginer que la puce AHDAM appliquera la tolérance de pannes au niveau Tuile, MPE et LPE par l'intégration de composants de rechange.

En outre, il y a un écart énorme entre la vitesse du processeur et de la mémoire. Cela ne semble pas devoir changer à l'avenir sauf si une nouvelle percée technologique est trouvée pour les technologies de mémoire. En supposant que ce n'est pas le cas, il devrait y avoir une solution architecturale pour éviter de bloquer les processeurs multithread LPE. Une solution serait d'augmenter le nombre de threads matériels par LPE. Mais comme nous l'avons vu précédemment dans le chapitre 2, ce n'est pas une solution efficace en transistor pour les processeurs faible coût. Une nouvelle technique serait d'utiliser une architecture de multithreading avec entrelacement statique N sur M. Cette technique implique qu'un processeur multithread a N threads de premier plan (thread matériel) et M threads virtuels stockés dans une spéciale mémoire scratchpad à proximité du processeur multithread. De cette façon, nous augmentons le nombre de threads pris en charge par LPE.

La puce AHDAM est une architecture manycore. Mais comme nous l'avons vu dans le chapitre 4, il y a aussi des limites à l'extensibilité de l'architecture. Une solution serait d'intégrer plusieurs contrôleurs DDR3 sur puce, ce qui signifie qu'on puisse augmenter ainsi le nombre de tuiles. Une autre solution au problème d'extensibilité est de considérer l'architecture AHDAM comme un cluster optimisé dans un environnement de multi-clusters. Puis, en utilisant une solution hiérarchique, nous pouvons augmenter le nombre de cœurs (plus de 1000 cœurs). A ce stade, on pourrait imaginer que le modèle de programmation AHDAM est étendu pour supporter la communication MPI entre les différents clusters AHDAM. Ainsi, AHDAM supporterait le modèle OpenMP + MPI.

Enfin, la mémoire SRAM et les mémoires caches peuvent être empilés sur les processeurs en utilisant une technologie d'empilage 3D. Ce serait une amélioration spectaculaire de la taille de la puce, puisque 73% de la surface estimé de la puce est occupée par les caches et la mémoire SRAM. Ainsi, plus de cœurs pourraient être intégrées et les temps d'accès mémoire seraient plus rapides. Cela permettrait d'améliorer les performances de la puce AHDAM et peut-être de nouvelles améliorations architecturales pourraient être proposées avec une technologie d'empilage 3D.

Mots clés: Multicœur, MPSoC, manycore, asymétrique, processeur multitâche, systèmes embarqués, applications dynamiques, simulation

## Acknowledgments

You can dream, create, design and build the most wonderful place in the world, but it requires people to make the dream a reality – Walt Disney, film producer

I am greatly indebted to many individuals for their advice and assistant in this PhD thesis journey.

I would like to thank Thierry COLLETTE (head of CEA LIST/DACLE department), Cécile MORILLON (assistant head of CEA LIST/DACLE department), Laurent LETELLIER (ex-head of LCE laboratory), and Raphaël DAVID (head of LCE laboratory), for warmly hosting me in the DACLE department and the LCE laboratory, in addition for providing me all the resources for the success of this work.

A special warm thank for Nicolas VENTROUX (PhD thesis supervisor, R&D engineer at CEA LIST), for trusting my capabilities and giving me this opportunity to work on this PhD topic. His motivation and dynamism for this work has infected me all along this successful journey. I thank you for your daily professional and personal advices. I really enjoyed working with you.

I am also grateful to Daniel ETIEMBLE (PhD thesis director, professor at Université Paris-Sud), for his great supervision and scientific guidance. I thank you for your kind advices, and especially for your fast responsiveness that unblocked me in several issues. I was honored to be supervised by a professor from your quality and I have learned a lot from your experience.

I would like also to express my gratitude to all my PhD defense jury members. In particular, I thank Olivier SENTIEYS (reviewer, professor at Université de Rennes) and Frédéric PETROT (reviewer, professor at Grenoble-INP), for taking the time to read my thesis report and for your interesting comments about my work. In addition, I thank Alain MERIGOT (president of the jury, professor at Université Paris-Sud) and Agnès FRITSCH (examiner, head of laboratory at Thales Communications France) for accepting to be in my PhD defense jury.

These 3 years would never pass so fast and so smooth without the great support of my laboratory colleagues. I thank you all, one by one, for the great time we shared during and after the work. In particular, I would like to thank all the people who helped me to overcome all the technical problems related to my work, and also for our great discussions about my work. It is of great pleasure to continue this journey with you after the PhD.

A special thank to the department secretaries, in particular Annie, Sabrina, and Frédérique, for taking care with an ultimate speed and lovely smile all my administrative issues.

In these 3 years, I have met lot of friends at CEA from outside my laboratory to whom I am grateful. In particular, I am thinking of all the Lebanese colleagues from all the CEA departments. I thank you all for the beautiful moments we shared together. You were real quality friends.

Last but not least, a very special acknowledgment of love and gratitude to my family, the RIM's. Thank you my parents Elie and Denise, my brother Anthony and my sister Melissa, for your continuous love and support. It was the key for my success throughout the challenging years of my education. I also thank my wife's family, the KHATTAR's, for showing their ultimate care and sharing this joy with me.

Finally, there are no words that can express my feelings of gratitude to my wife Manar. Your big

support, your great tolerance, your daily encouragements, and your shining love made this tough journey very special. I love you.

# Contents

|          | $\mathbf{Abs}$ | stract                                                                                      | i   |

|----------|----------------|---------------------------------------------------------------------------------------------|-----|

|          | Rés            | sumé                                                                                        | iii |

|          | Ack            | knowledgments                                                                               | xi  |

|          | Intr           | roduction                                                                                   | 1   |

|          |                | Context of study                                                                            | 1   |

|          |                | Problematic                                                                                 | 2   |

|          |                | Outline of this report                                                                      | 3   |

| 1        | MP             | SoC architectures for dynamic applications in embedded systems                              | 5   |

|          | 1.1            | Dynamic applications in embedded systems                                                    | 6   |

|          | 1.2            | MPSoC architectures: state of the art                                                       | 8   |

|          |                | 1.2.1 Characteristics                                                                       | 9   |

|          |                | 1.2.2 Classification                                                                        | 12  |

|          |                | 1.2.3 Synthesis                                                                             | 16  |

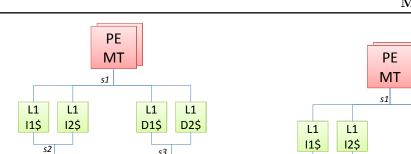

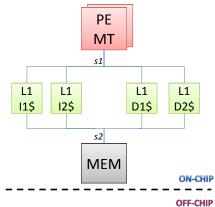

|          | 1.3            | SCMP: an asymmetric MPSoC                                                                   | 17  |

|          |                | 1.3.1 Architecture overview                                                                 | 17  |

|          |                | 1.3.2 Programming models                                                                    | 20  |

|          |                | 1.3.3 SCMP processing example                                                               | 22  |

|          | 1.4            | Why these MPSoC architectures are not suitable?                                             | 23  |

| <b>2</b> | Mu             | ltithreaded processors in embedded systems                                                  | 25  |

|          | 2.1            | Classification                                                                              | 26  |

|          |                | 2.1.1 Multithreaded processor design space                                                  | 27  |

|          |                | 2.1.2 Cost-effectiveness model                                                              | 31  |

|          |                | 2.1.3 Synthesis                                                                             | 33  |

|          | 2.2            | Implementation of a small footprint multithreaded processor for embedded systems            | 33  |

|          |                | 2.2.1 Monothreaded AntX                                                                     | 33  |

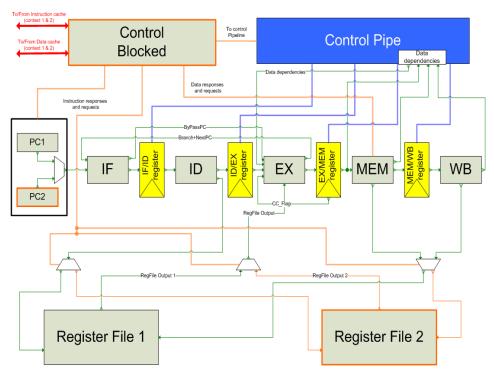

|          |                | 2.2.2 Interleaved MT AntX                                                                   | 35  |

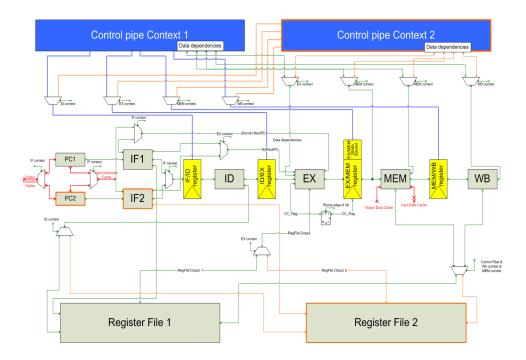

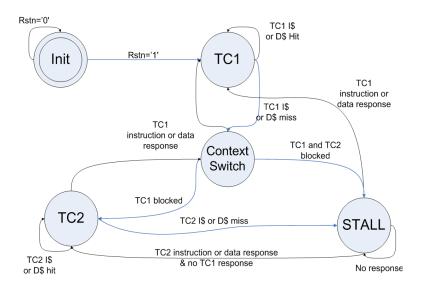

|          |                | 2.2.3 Blocked MT AntX                                                                       | 37  |

|          | 2.3            | Performance evaluation                                                                      | 39  |

|          |                | 2.3.1 Monothreaded v/s Multithreaded processors: area occupation $\ldots \ldots \ldots$     | 39  |

|          |                | 2.3.2 Monothreaded v/s Multithreaded processors: performance and transistor ef-<br>ficiency | 41  |

|          |                | 2.3.3 Synthesis                                                                             | 44  |

### Contents

| 3 | $\mathbf{M}\mathbf{u}$ | tithreaded processors in asymmetric homogeneous MPSoC architectures           | 47  |

|---|------------------------|-------------------------------------------------------------------------------|-----|

|   | 3.1                    | MPSoC Simulation environment                                                  | 48  |

|   |                        | 3.1.1 SESAM: A Simulation Environment for Scalable Asymmetric Multiprocessing | 49  |

|   |                        | 3.1.2 Extending SESAM for multithreaded processors                            | 53  |

|   | 3.2                    | A Multithreaded Instruction Set Simulator                                     | 56  |

|   |                        | 3.2.1 The requirements for ISS and ADL                                        | 56  |

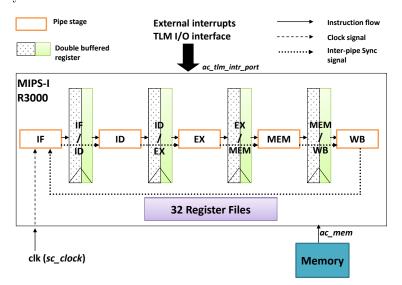

|   |                        | 3.2.2 Monothreaded cycle-accurate ISS model                                   | 59  |

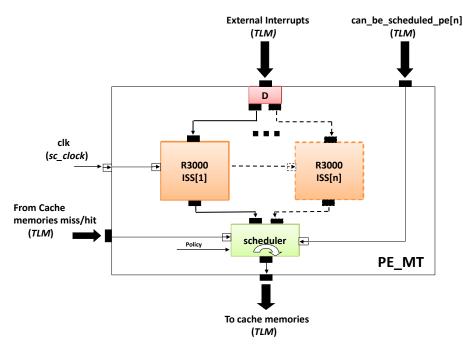

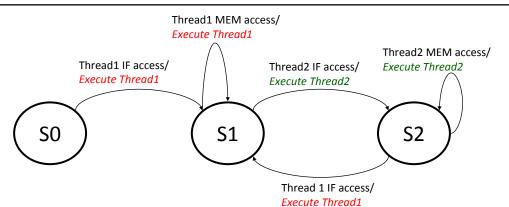

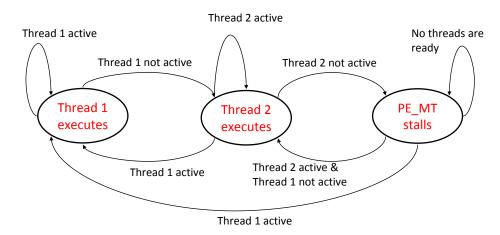

|   |                        | 3.2.3 Multithreaded cycle-accurate ISS model                                  | 62  |

|   | 3.3                    | Performance evaluation                                                        | 66  |

|   |                        | 3.3.1 Applications description                                                | 66  |

|   |                        | 3.3.2 Which multithreaded processor system?                                   | 68  |

|   |                        | 3.3.3 Which global thread scheduling strategy? VSMP v/s SMTC                  | 71  |

|   |                        | 3.3.4 SCMP v/s MT_SCMP: chip area                                             | 73  |

|   |                        | 3.3.5 SCMP v/s MT_SCMP: performance                                           | 74  |

|   |                        | 3.3.6 Synthesis                                                               | 78  |

| 4 | ΛН                     | DAM: an Asymmetric Homogeneous with Dynamic Allocator Manycore ar-            |     |

| 4 |                        |                                                                               | 81  |

|   | 4.1                    | System description                                                            | 82  |

|   | 4.2                    | AHDAM programming model                                                       | 83  |

|   | 4.3                    | AHDAM architecture design                                                     | 84  |

|   |                        | 4.3.1 Architecture description                                                | 85  |

|   |                        | 4.3.2 Why splitting the L2 instruction and data memories?                     | 89  |

|   |                        | 4.3.3 Why is the LPE a blocked multithreaded processor?                       | 93  |

|   | 4.4                    | Execution model                                                               | 95  |

|   | 4.5                    | Scalability analysis                                                          | 97  |

|   |                        | 4.5.1 Control bus dimensioning                                                | 97  |

|   |                        | 4.5.2 CCP reactivity                                                          | 98  |

|   |                        |                                                                               | .00 |

|   |                        |                                                                               | .01 |

|   | 4.6                    | Discussion                                                                    | .02 |

| 5 | Eva                    | luation                                                                       | 03  |

| 0 | 5.1                    |                                                                               | .04 |

|   | 0.1                    |                                                                               | .04 |

|   |                        |                                                                               | .04 |

|   | 5.2                    |                                                                               | .00 |

|   | 5.3                    |                                                                               | .09 |

|   | 0.0                    |                                                                               | .10 |

|   |                        |                                                                               | .10 |

|   |                        |                                                                               | .12 |

|   |                        |                                                                               | .13 |

|   | 5.4                    |                                                                               | .14 |

| Conclusions and Perspectives | 119 |

|------------------------------|-----|

| Synthesis of my work         | 119 |

| $\mathbf{Perspectives}$      | 121 |

| Short term                   | 121 |

| Long term                    | 122 |

| Glossary                     | 125 |

| Bibliography                 | 129 |

| Personal publications        | 143 |

# List of Figures

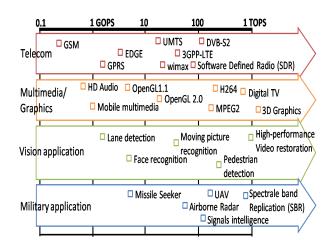

| 1.1  | Embedded applications performance                                                                                                                        |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

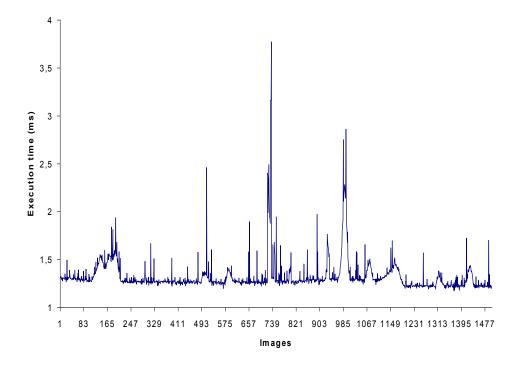

| 1.2  | Dynamic execution of the connected component labeling algorithm                                                                                          |

| 1.3  | MPSoC classification                                                                                                                                     |

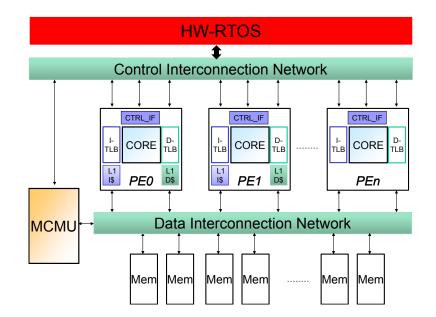

| 1.4  | SCMP system architecture                                                                                                                                 |

| 1.5  | SCMP architecture                                                                                                                                        |

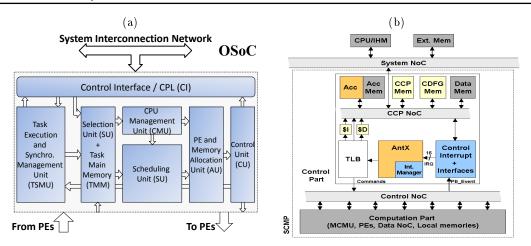

| 1.6  | SCMP central controller                                                                                                                                  |

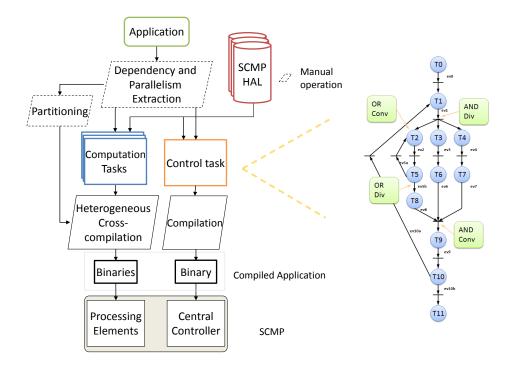

| 1.7  | SCMP programming model                                                                                                                                   |

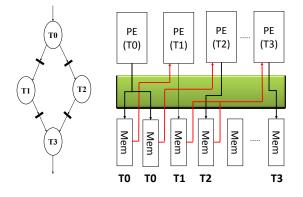

| 1.8  | SCMP control-flow execution model                                                                                                                        |

| 1.9  | SCMP streaming execution model                                                                                                                           |

|      |                                                                                                                                                          |

| 2.1  | Thread context v/s execution cores                                                                                                                       |

| 2.2  | Multithreaded processor design space                                                                                                                     |

| 2.3  | Multithreaded processor execution core                                                                                                                   |

| 2.4  | Multithreaded instruction issue types                                                                                                                    |

| 2.5  | Examples of IMT and BMT processors                                                                                                                       |

| 2.6  | Cost-effectiveness of a multithreaded processor                                                                                                          |

| 2.7  | Monothreaded AntX                                                                                                                                        |

| 2.8  | Surface repartition for monothreaded AntX                                                                                                                |

| 2.9  | Interleaved multithreaded AntX                                                                                                                           |

| 2.10 | Blocked multithreaded AntX                                                                                                                               |

| 2.11 | Blocked multithreaded AntX FSM for 2 thread contexts                                                                                                     |

| 2.12 | Surface repartition for IMT and BMT AntX                                                                                                                 |

| 2.13 | IMT and BMT processor area overhead with respect to the monothreaded processor 40                                                                        |

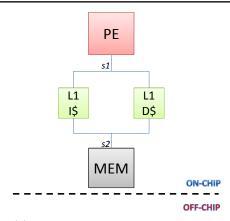

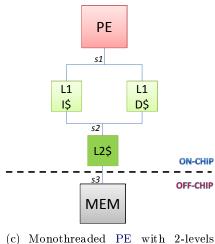

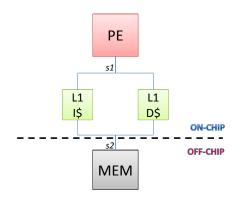

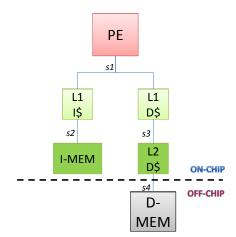

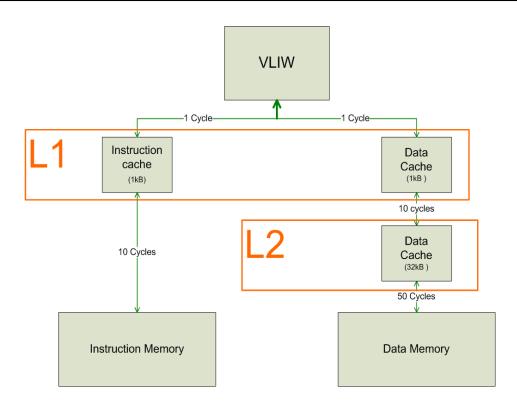

| 2.14 | AntX hierarchical memory system 41                                                                                                                       |

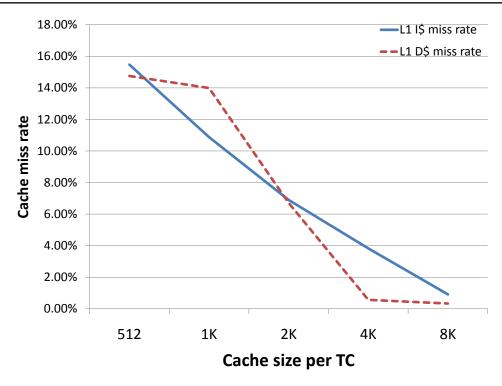

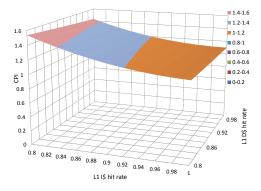

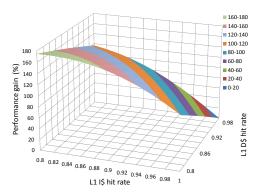

| 2.15 | Data cache miss rates for monothreaded and IMT/BMT AntX 42                                                                                               |

| 2.16 | Performance results in cycles of monothreaded v/s IMT/BMT AntX 43                                                                                        |

| 2.17 | Transistor efficiency gain of IMT/BMT AntX processor with respect to                                                                                     |

|      | monothreaded AntX processor                                                                                                                              |

| 9.1  | CECAM and and an incoment                                                                                                                                |

| 3.1  | SESAM exploration tool and environment                                                                                                                   |

| 3.2  | SESAM infrastructure                                                                                                                                     |

| 3.3  | SCMP infrastructure modeled in SESAM                                                                                                                     |

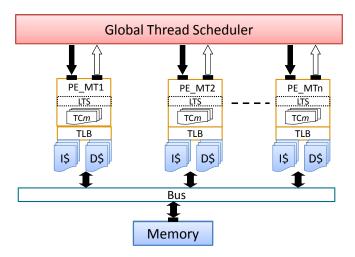

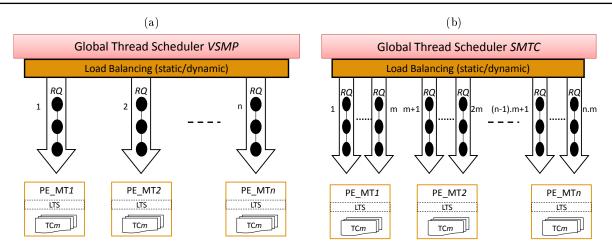

| 3.4  | Abstraction view of SESAM with multiple multithreaded processors                                                                                         |

| 3.5  | VSMP v/s SMTC scheduler architecture $\dots \dots \dots$ |

| 3.6  | ArchC simulator generator                                                                                                                                |

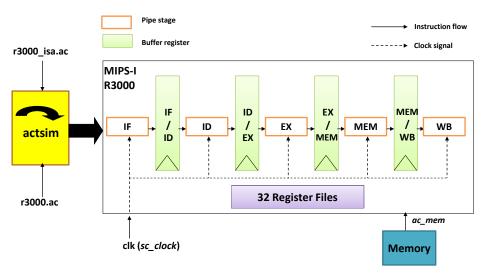

| 3.7  | R3000 cycle-accurate model generation by actsim tool                                                                                                     |

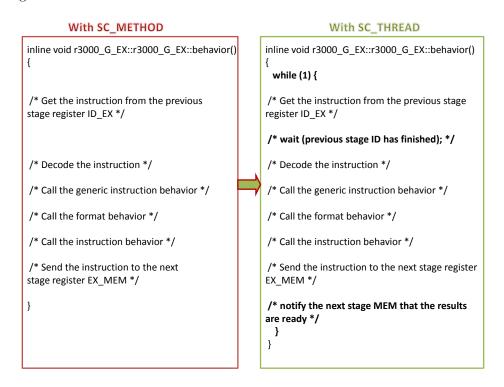

| 3.8  | Pseudo-code for the EX-stage module in ArchC 2.0                                                                                                         |

| 3.9  | New R3000 cycle-accurate model for SoC simulator integration capabilities 61                                                                             |

| 3.10 | Multithreaded ISS model                                                                                                                                  |

| 3.11 | Interleaved multithreading scheduler FSM                                                                                                                 |

|             | Interleaved multithreading pipeline representation                                                                                                 | 64              |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|             | Blocked multithreading scheduler FSM                                                                                                               | 65              |

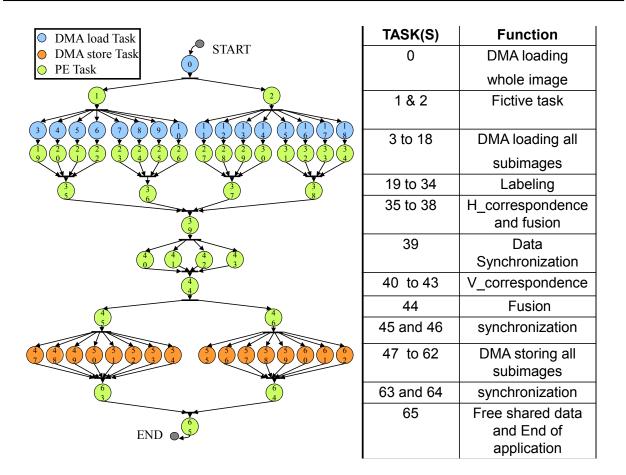

|             | CDFG of the connected component labeling algorithm                                                                                                 | 67              |

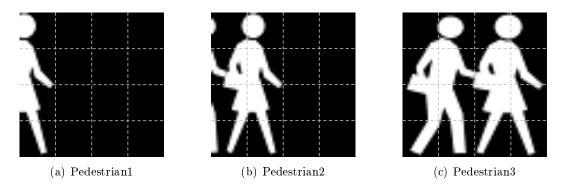

|             | 2 pedestrians crossing a road                                                                                                                      | 67              |

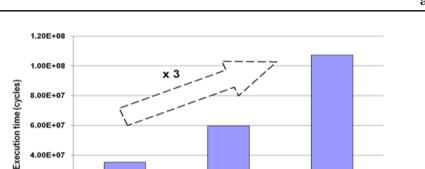

|             | Dynamic behavior of the connected component labeling application                                                                                   | 68              |

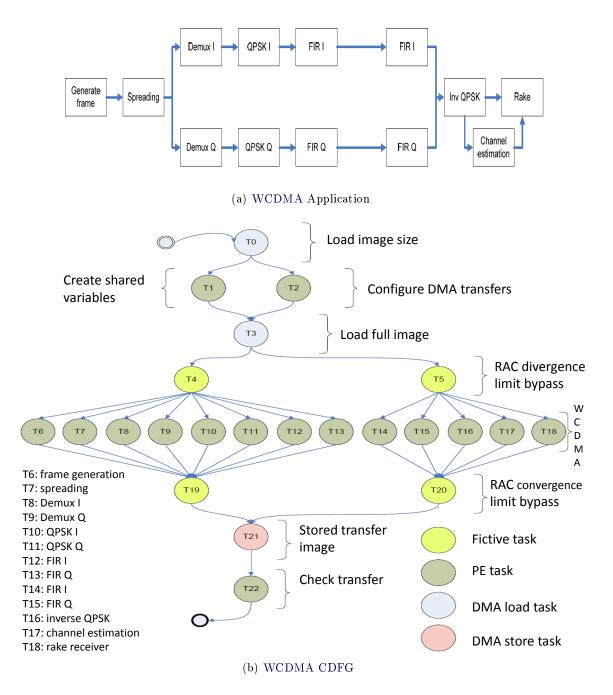

|             | WCDMA application and CDFG                                                                                                                         | 69              |

|             | L1 I\$ and D\$ miss rates for the connected component labeling application                                                                         | 70              |

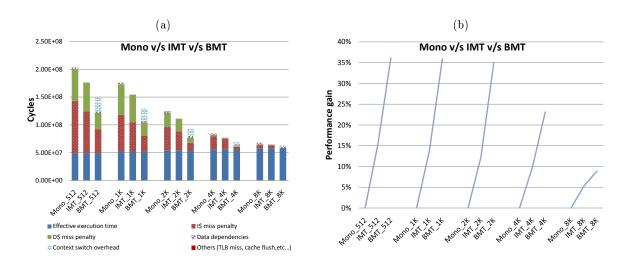

| 3.19        | Performance results of MT_SCMP with 1 processor: Monothreaded v/s IMT v/s $$ DMT                                                                   | 71              |

| 2.00        | BMT                                                                                                                                                | 71<br>73        |

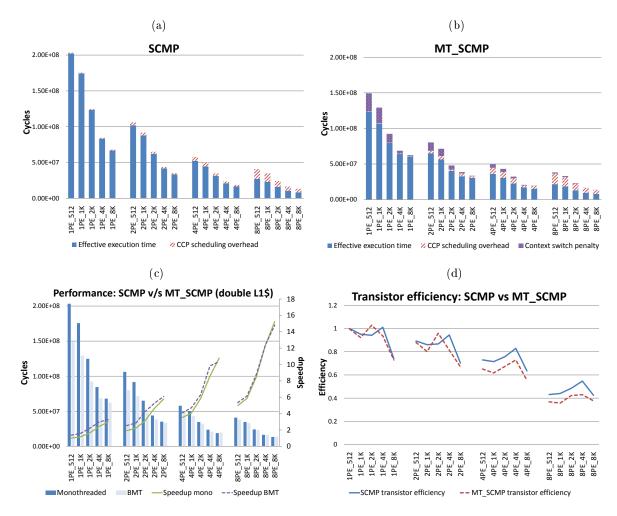

|             | Components area in 40 nm technology for different SCMP modules                                                                                     | 73<br>74        |

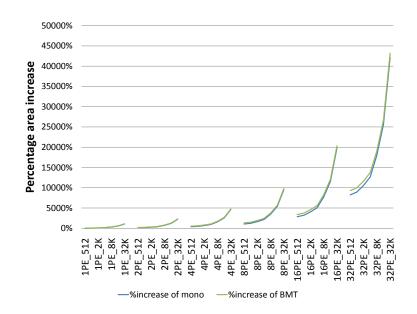

|             | Percentage area increase of SCMP with different number of processors                                                                               | 74<br>75        |

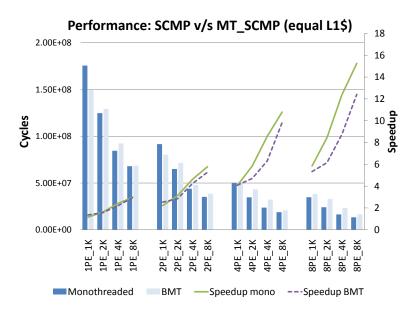

|             | Performance of SCMP v/s MT SCMP for control-flow (labeling) application $\dots$                                                                    | 75<br>76        |

|             | Performance on Scivil v/s MT_Scivil for control-now (labeling) appreation Performance and speedup comparison between SCMP v/s MT_SCMP for control- | 70              |

| 0.24        | flow (labeling) application                                                                                                                        | 77              |

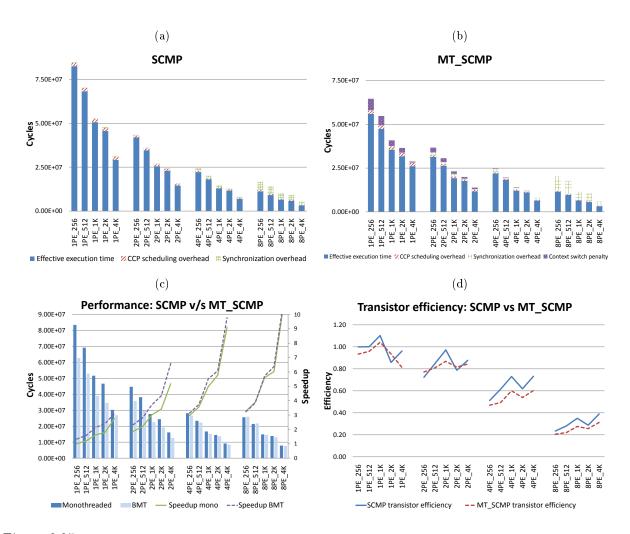

| 3 25        | Performance of SCMP $v/s$ MT_SCMP for streaming (WCDMA) application                                                                                | 79              |

| 0.20        | renormance of bottin v/s mr_bottin for streaming (web tint) application                                                                            | 10              |

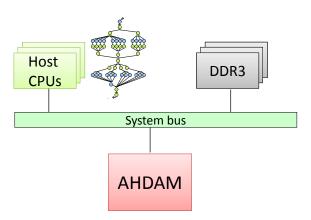

| 4.1         | AHDAM system environment                                                                                                                           | 82              |

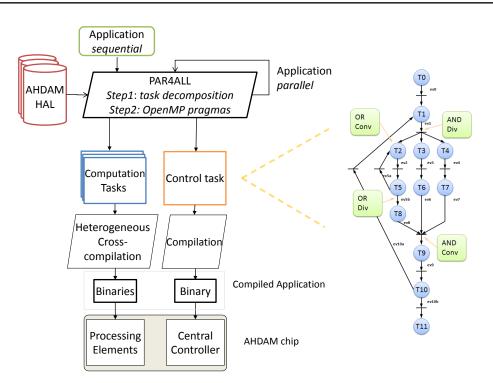

| 4.2         | AHDAM programming model                                                                                                                            | 84              |

| 4.3         | AHDAM architecture                                                                                                                                 | 86              |

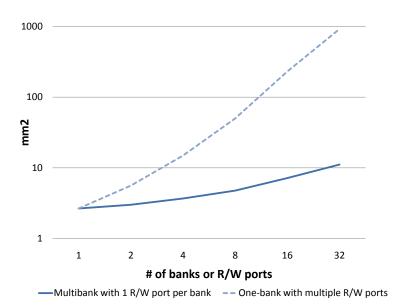

| 4.4         | Estimated synthesis results of multi-banked memories                                                                                               | 87              |

| 4.5         | Processor-memory system architectures                                                                                                              | 90              |

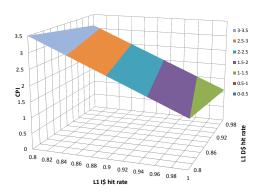

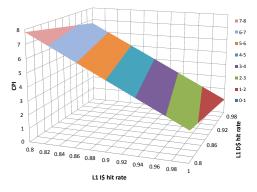

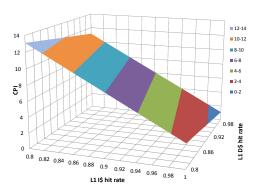

| 4.6         | CPI performance of 4 different processor-memory system architectures                                                                               | 92              |

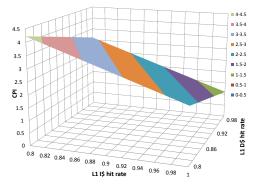

| 4.7         | 2 different processor-memory system architectures with a BMT processor                                                                             | 94              |

| 4.8         | CPI performance of AHDAM with BMT processor compared to monothreaded pro-                                                                          | 05              |

| 4.0         | cessor                                                                                                                                             | $\frac{95}{96}$ |

| 4.9<br>4.10 | A task code example of serial and parallel regions using OpenMP pragmas AHDAM control bus connecting the CCP with M MPEs                           | 90<br>98        |

| 4.11        | Total number of MPEs supported by a $32/64/128$ -bit control bus                                                                                   | 98<br>98        |

|             | CCP scheduling tick length for variable number of PEs and tasks                                                                                    | 99              |

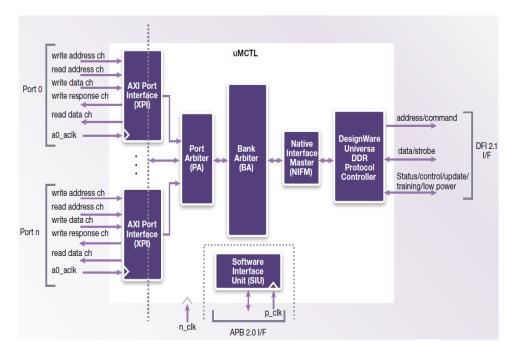

|             | DesignWare Universal DDR Memory Controller Block Diagram                                                                                           | 100             |

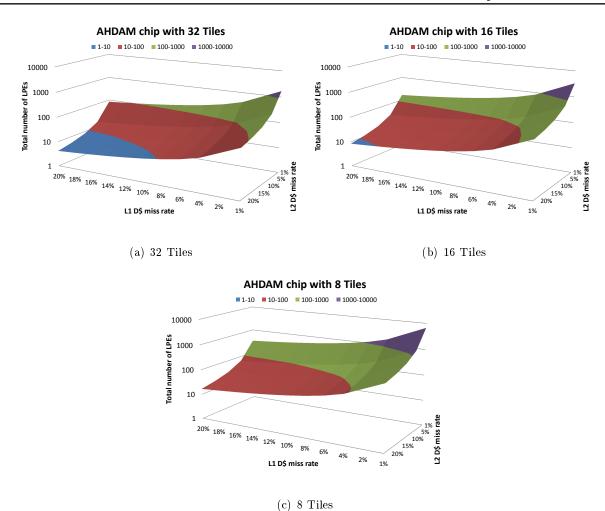

|             | Maximum number of LPEs per Tile for $32/16/8$ Tiles                                                                                                | 100             |

| 1.11        |                                                                                                                                                    | 102             |

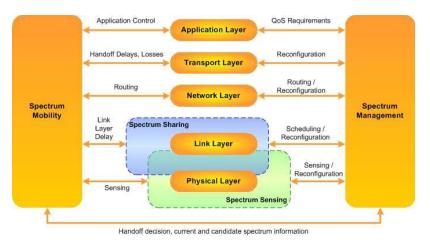

| 5.1         | Spectrum Sensing description                                                                                                                       | 104             |

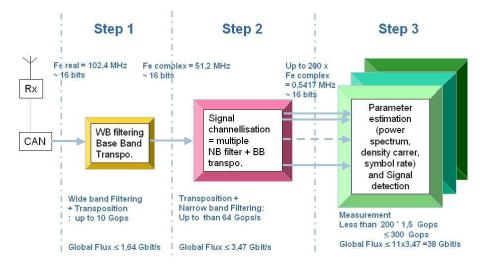

| 5.2         | Spectrum Sensing main steps, maximal flows and complexities                                                                                        | 105             |

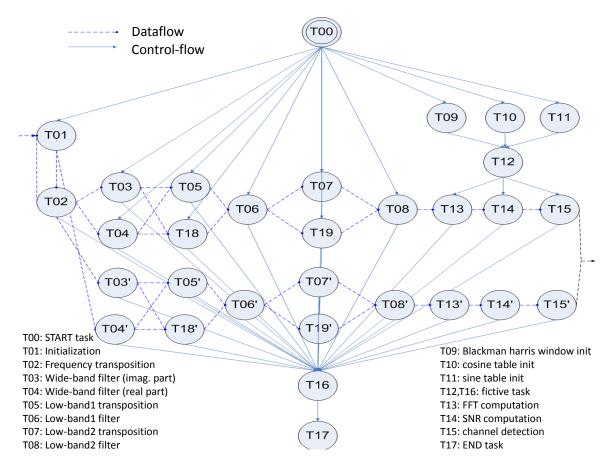

| 5.3         | CDFG of the radio-sensing application                                                                                                              | 106             |

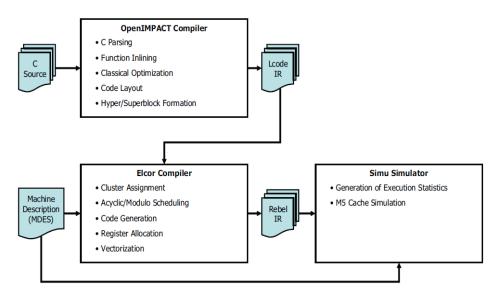

| 5.4         | Trimaran organization                                                                                                                              | 108             |

| 5.5         | Trimaran configuration for modeling the LPE with AHDAM memory hierarchy $\ldots$                                                                   | 109             |

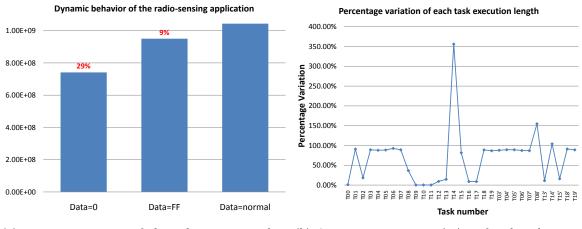

| 5.6         | Dynamic behavior of the radio-sensing application                                                                                                  | 110             |

| 5.7         | Static v/s dynamic scheduling on SCMP for the radio-sensing application                                                                            | 111             |

| 5.8         | Performance of AHDAM architecture with LPE as monothreaded 3-way VLIW v/s                                                                          |                 |

| <b>.</b> .  | multithreaded 3-way VLIW                                                                                                                           | 112             |

| 5.9         | Performance of AHDAM v/s SCMP v/s mono for radio-sensing with low-sensitivity                                                                      | 113             |

| 5.10        | Performance of AHDAM v/s SCMP v/s mono for radio-sensing with high-sensitivity                                                                     | 114             |

| 5.11 | AHDAM architecture surface repartition                                   | 116 |

|------|--------------------------------------------------------------------------|-----|

| 5.12 | AHDAM architecture surface with 8 Tiles and $4/8/16$ LPEs per Tile       | 117 |

| 5.13 | AHDAM architecture surface with monothreaded VLIW and multithreaded VLIW |     |

|      | for 8 Tiles and $4/8/16$ LPEs per Tile                                   | 118 |

# List of Tables

| 1.1 | Comparison of MPSoC architectures                                                                                                                    | 16  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | Probability of the stall cycles per memory access of level 1 memory hierarchy with seperate I\$ and D\$ for a monothreaded PE                        | 91  |

|     | Comparison between 4 processor-memory systems                                                                                                        | 93  |

| 4.3 | Probability of the stall cycles per memory access of level 1 memory hierarchy with seperate and segmented I\$ and D\$ for a blocked multithreaded PE | 94  |

| 5.1 | AHDAM components area occupation                                                                                                                     | 115 |

# Introduction

One thing is sure. We have to do something. We have to do the best we know how at the moment...If it doesn't turn out right, we can modify it as we go along. – Franklin D.Roosevelt, president

#### Contents

| Context of study       | 1        |

|------------------------|----------|

| Problematic            | <b>2</b> |

| Outline of this report | 3        |

### Context of study

Embedded systems exist everywhere in our quotidian life. Almost every single product contains one or multiple processors hidden from the end user in a fascinating package. They are performing the computation and communication with the environment to bring the intelligence and satisfy the end user needs.

Embedded systems span all aspects of modern life and there are many examples of their use. In the telecommunication domain, there are numerous embedded systems from telephone switches for the network to mobile phones at the end-user. Computer networking uses dedicated routers and network bridges to route data. In the consumer electronics domain, embedded systems are employed in personal digital assistants (PDAs), MP3 players, videogame consoles, digital cameras, DVD players, GPS receivers, and printers. This list is exhaustive and there are much more examples that exist in other domains such as the transportation systems, medical equipments, military applications, etc...

The end users no longer only wants more features and better performance, but are increasingly interested in devices with the same performance level at a lower price. Thus, consumer electronic markets, and therefore industries, started to converge. Digital watches and pagers evolved into powerful personal digital assistants (PDA) and smartphones. Similarly, desktop and laptop computers were recently reduced to netbooks that use Intel Atom and ARM processors. The resulting devices demand ever more computational capabilities at decreasing power budgets and within stricter thermal constraints [42].

During nearly 40 years, the technological innovations followed one another with the goal of reducing the processor execution times. One technique relied on shrinking the physical transistor integration, which led to an increase in the processor clock frequency, hence a faster instruction execution. However, this performance gain is limited today by the physical integration barriers. In addition, embedded systems function on a limited power budget and thus increasing the processor frequency to improve the performance is no longer a solution for system designers.

Fortunately, many embedded applications are parallel by nature. Applications are parallelized on the task level to reach higher performances. There exist 2 solutions to tackle to the task level parallelism (TLP).

The simplest solution to execute multiple tasks consists in using a monothreaded processor with all the techniques deployed to accelerate the processing of a single instruction flow. The operating system schedule and allocate the threads concurrently on the processor giving the impression that they are running in parallel. This can be thought of as virtualization of the execution resources. For this virtualization, two acceleration techniques for the monothreaded processors are largely used. The first one, called *temporal parallelism*, consists in reducing the execution time by dividing the instruction execution into several successive stages. This is referred to a *pipeline* execution. The second one, called *space parallelism*, relies on the multiplication of the execution resources. Expressing the parallelism in this type of architecture can be *explicit* or *implicit*. The parallelism is *explicit* when the compiler manages the data dependencies and the control flow in order to guarantee the availability of the resources. The control is then relatively simple and makes it possible to use higher clock frequencies. For instance, this is the case for the VLIW [48, 115] architectures. On the other hand, when the architecture deals dynamically with all these execution hazards, the parallelism is exploited in an *implicit* way. These architectures are called superscalar. The advantages of this approach are the simplicity of the parallelism description and its dynamic management during the execution. Nevertheless, the complexity of the speculation mechanisms, out-of-order executions and branch predictions has great impact on the energy efficiency and transistor efficiency of the processor architecture.

The second solution consists of multiplying the number of cores and executing the tasks in parallel. The advancement in semiconductor processing technology allowed chip manufacturers to increase the overall processing power by adding additional CPUs or "cores" to the microprocessor chip. Hence, this solution exploits the parallelism at the thread level (TLP), where multiple threads can be executed in parallel on multiple cores. These architectures are known as *MPSoC*, which stands for *Multi-Processor System-On-Chip*.

The context of study of this thesis will be the design of MPSoC architectures for the embedded systems.

### Problematic

Embedded systems require more intensive processing capabilities and must be able to adapt to the rapid evolution of the high-end embedded applications. These embedded applications are getting more and more complex. Their computation requirements have reached the order of TOPS (Tera Operations Per Second) and they have a large data set. These applications have lot of thread level parallelisms and loop level parallelisms. Therefore, MPSoC architectures must target the manycore era in order to meet this high computation demands. The manycore architecture must be transistor and energy efficient, since the chip size and the power budget are limited in the embedded systems. Thus, they must be designed with a good balance between the number of cores and the on-chip memory. The cores should be highly transistor and energy efficient, where specialization is a key element. There should be no unjustified waste of energy in execution resources with techniques such as speculation. In such complex manycore architectures, there are lots of sources of latencies

#### Introduction

that cause the cores to be stalled, thus wasting energy. In this context, multithreaded processors are an interesting solution to investigate.

An important feature of these embedded computation-intensive applications is the dynamism. While some algorithms are data independent with a regular control flow, other algorithms are highly data-dependent and their execution time vary with respect to their input data, their irregular control flow, and their auto-adaptability to the application environments. Therefore, the MPSoC architecture should be highly reactive with respect to the computation needs in order to increase the execution resources occupation rate. Thus, it should support global and dynamic load-balancing of threads between the execution resources.

Based on these observations, we will design a new manycore architecture that tackles the challenges of future high-end massively parallel dynamic applications. The manycore architecture is called AHDAM, which stands for *Asymmetric Homogeneous with Dynamic Allocator Manycore architecture*.

### Outline of this report

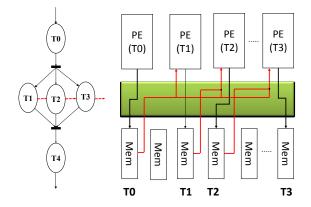

Chapter 1 presents the context of our work by focusing mainly on the applications requirements and the existing architectural solutions. First, it highlights the performance requirements of future high-end massively-parallel dynamic embedded applications. Then, it presents a state of the art of the *MPSoCs* for embedded systems by providing a classification of the overall architectures' space that currently exist in the literature. Three big families are identified: Symmetric MPSoCs, Asymmetric Homogeneous MPSoCs, and Asymmetric Heterogeneous MPSoCs. The Asymmetric Homogeneous MPSoCs will be exploited since its characteristics can meet the future embedded applications constraints. An asymmetric homogeneous architecture consists of one (sometimes several) centralized or hierarchized control core, and several homogeneous cores for computing tasks. In particular, an asymmetric homogeneous MPSoC, called SCMP [151], which is proprietary to CEA LIST laboratory, will be retained for the rest of this thesis as the architecture of reference for experimentations. SCMP is designed to process embedded applications with a dynamic behavior by migrating the threads between the cores using the central controller. Finally, and based on our observations, we will analyze why the currently existing asymmetric homogeneous MPSoC architectures do not meet the requirements of future high-end massively-parallel dynamic embedded applications, and what are the possible solutions. In particular, we will be interested in hardware multithreading as an efficient solution to increase the performance of the asymmetric homogeneous MPSoC architectures.

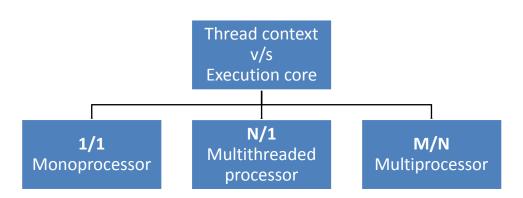

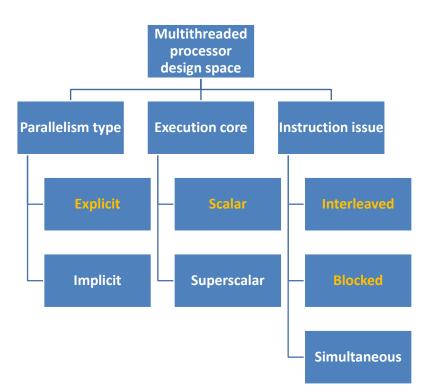

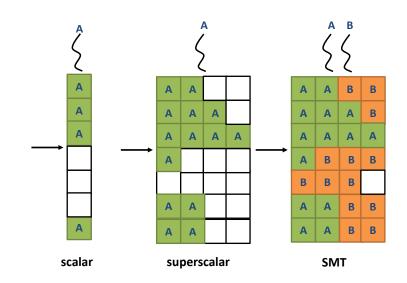

At the beginning, chapter 2 explores and analyzes the performance and efficiency of hardware multithreaded processors in embedded systems. First of all, it provides a classification of the different types of multithreaded processors that exist in the literature. In particular, two multithreading techniques for single-issue cores will be retained: *Interleaved multithreading* (IMT) and *Blocked multithreading* (BMT). These multithreaded architectures should meet the embedded systems requirements and are suitable for manycore architectures. Then, we apply the two multithreading techniques on a small footprint monothreaded core at the RTL level (VHDL), and synthesize the 3 cores in 40 nm TSMC technology. In this way, we compare the area overhead of each multithreaded processor type (IMT and BMT) with respect to the monothreaded core. Finally, we compare the

performance of the monothreaded, IMT, and BMT cores in a typical processor system configuration, and we show the characteristics of each processor type and under which conditions it should be used.

Then, chapter 3 explores the advantages/disadvantages of hardware multithreading in an asymmetric homogeneous MPSoC context (SCMP architecture). In order to conduct this exploration, we present the SESAM simulation framework, where the SCMP architecture is modeled. Then, we extend SESAM to support multithreaded processors. In particular, we have developed a new cycleaccurate multithreaded Instruction Set Simulator (ISS) in SystemC to model the IMT processor with 2 thread contexts (TC). After replacing the monothreaded processor by an IMT/BMT processor with 2 TCs, we used several benchmarks in order to know which multithreaded processor type suits best the SCMP architecture and to measure the transistor efficiency of the new SCMP architecture with multithreaded processors. For this reason, two types of applications are used from the embedded domain: connected component labeling (control-flow) and WCDMA (dataflow/streaming). In the control-flow execution model, the tasks are processed until completion, while in the dataflow execution model, the tasks synchronize between each other on data, thus creating more processor stalls. Both execution models cover a large set of applications behavior. The benchmarking results show that multithreading boosts the performance of SCMP, however it does not reach the desired level to make it a transistor efficient solution. Chapter 3 concludes that SCMP has some limitations for tackling the requirements of the future massively-parallel dynamic applications. In particular, it was due to the scalability limitations to the manycore level and the lack of support for large data set sizes of applications that does not fit in the on-chip memory.

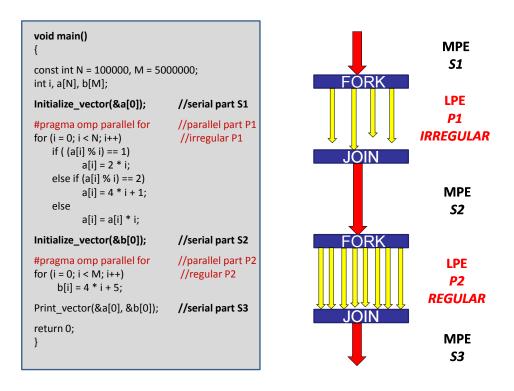

To overcome these limitations, chapter 4 presents a new manycore architecture called AHDAM [17]. AHDAM stands for Asymmetric Homogeneous with Dynamic Allocator Manycore architecture. It is used as an accelerator for massively parallel dynamic applications by migrating the threads between the execution units using a central controller. In addition, it is designed to accelerate the execution of the loop codes, which often constitutes a large part of the overall application execution time. AHDAM architecture implements monothreaded and multithreaded cores to increase the cores utilization when necessary. AHDAM architecture is presented in details in this chapter. In particular, its application system environment, its programming model, its architectural description and the functionalities of each hardware component, its execution model, and its maximum scalability, are presented in this chapter.

Finally, chapter 5 evaluates the performance and transistor efficiency of AHDAM architecture by using a relevant embedded application from Thales Communications France in the telecommunication domain called *radio-sensing*. This application has lots of computation requirements, lots of parallelism at the thread and loop levels, a large data set, and is dynamic. The radio-sensing application is parallelized and ported using the AHDAM programming model flow. We evaluate the transistor efficiency of the architecture. In particular, we estimate the overall chip area in 40 nm technology for multiple chip configurations and we evaluate its performance by running the radio-sensing application on different chip configurations. The AHDAM architecture shows excellent results compared to the SCMP architecture.

# MPSoC architectures for dynamic applications in embedded systems

A problem well stated is a problem half solved. - Charles F. Kettering, inventor

#### Contents

| 1.1 | Dyna  | amic applications in embedded systems       |

|-----|-------|---------------------------------------------|

| 1.2 | MPS   | SoC architectures: state of the art         |

|     | 1.2.1 | Characteristics                             |

|     | 1.2.2 | Classification                              |

|     | 1.2.3 | Synthesis                                   |

| 1.3 | SCM   | IP: an asymmetric MPSoC                     |

|     | 1.3.1 | Architecture overview                       |

|     | 1.3.2 | Programming models                          |

|     | 1.3.3 | SCMP processing example                     |

| 1.4 | Why   | these MPSoC architectures are not suitable? |

During the last decades, computing systems were designed according to the CMOS technology push resulting from Moore's Law, as well as the application pull from ever more demanding applications [42]. The emergence of new embedded applications for mobile, telecom, automotive, digital television, mobile communication, medical and multimedia domains, has fueled the demand for architectures with higher performances, more chip area and power efficiency. These complex applications are usually characterized by their computation-intensive workloads, their high-level of parallelism, and their dynamism. The latter implies that the total application execution time can highly vary with respect to the input data, irregular control flow, and auto-adaptive applications.

Traditional high-performance superscalar general-purpose processors implement several architectural enhancement techniques such as out-of-order execution, branch prediction, and speculation, in order to exploit the instruction-level parallelism (ILP) of a sequential program. However, the ILP has reached its limits [156] and cannot be more exploited. To compensate the ILP limitation, chip manufacturers relied on increasing the clock frequency to provide free performance gain. Yet, a higher clock frequency implies more power dissipation. Therefore, superscalar processors have low transistor/energy efficiency that render them not suitable for embedded systems applications. On the other hand, the advancement in semiconductor processing technology allowed chip manufacturers to increase the overall processing power by adding additional CPUs or "cores" to the microprocessor package. Hence, this coarse-grained solution consists of exploiting the parallelism at the thread level (TLP), where multiple threads can be executed in parallel on multiple cores or concurrently on hardware multithreaded cores. According to the authors in [158], all the microprocessor chip architectures for the embedded systems world are called MPSoC, which stands for *Multi-Processor System-On-Chip*.

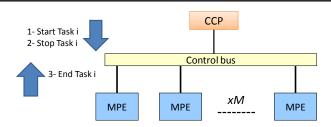

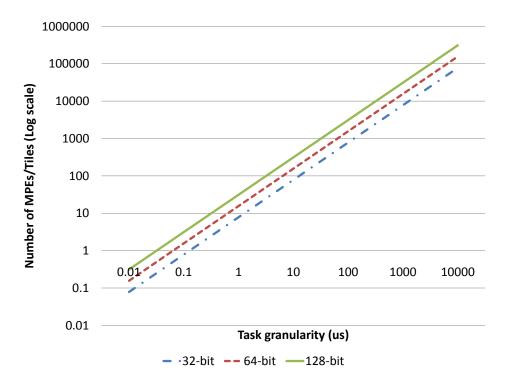

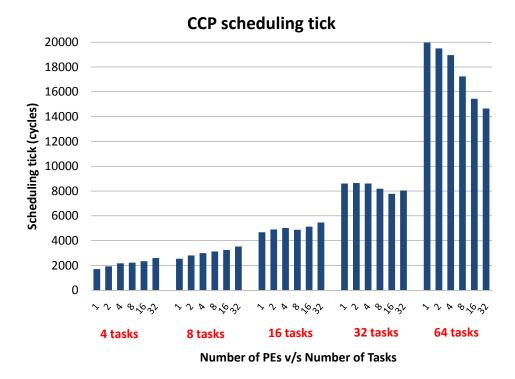

MPSoCs consist of any number of processing cores greater than 1 connected to any number of IPs (Intellectual Property) through an interconnection network, all integrated in one microprocessor package. The interconnection network can be a simple bus or a complex Network-On-Chip (NoC). MPSoCs provide the necessary execution resources to exploit the Thread-Level Parallelism (TLP) of an application.