# Structures MOS-IGBT sur technologie SOI en vue de l'amélioration des performances à haute température de composants de puissance et de protections ESD

Houssam Arbess

#### ▶ To cite this version:

Houssam Arbess. Structures MOS-IGBT sur technologie SOI en vue de l'amélioration des performances à haute température de composants de puissance et de protections ESD. Autre. Université Paul Sabatier - Toulouse III, 2012. Français. NNT: . tel-00715137

# HAL Id: tel-00715137 https://theses.hal.science/tel-00715137

Submitted on 6 Jul 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### En vue de l'obtention du

# **DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE**

Délivré par l'Université Toulouse III - Paul Sabatier Discipline ou spécialité : Conception des Circuits Microélectroniques et Microsystèmes

#### **Présentée et soutenue par** Houssam ARBESS **Le** 22 mai 2012

**Titre :** Structures MOS-IGBT sur technologie SOI en vue de l'amélioration des performances à haute température de composants de puissance et de protections ESD

#### **JURY**

Mme. Marise BAFLEUR, Directrice de recherche, LAAS-CNRS, Toulouse M. David TREMOUILLES, chargé de recherche à l'UPS, Toulouse

M. Philippe GALY, HDR, STMicroelectronics, Crolles

M. Dominique PLANSON, Professeur à l'INSA, Lyon

M. Alain CAZARRE, Professeur à l'UPS, Toulouse

M. Bruno ALLARD, Professeur à l'INSA, Lyon

Directrice de thèse Co-directeur Rapporteur Rapporteur Examinateur Examinatuer

**Ecole doctorale :** *GEET*

Unité de recherche : LAAS-CNRS Toulouse Directeur(s) de Thèse : Mme. Marise BAFLEUR Rapporteurs : M. Dominique PLANSON & M. Philippe GALY

# Remerciement

Ces travaux de thèse on été effectués au sein du laboratoire d'analyse d'architecture et des systèmes (LAAS) du Centre National de la Recherche Scientifique (CNRS) et dans le groupe Intégration de Systèmes de Gestion de l'Énergie (ISGE).

Je tiens à remercier premièrement Messieurs Raja CHATILA, Jean-Louis SANCHEZ et Jean ARLAT directeurs successifs du LAAS, pour m'avoir accueilli pendant toute la durée de la thèse. Je voudrais également signaler l'exceptionnelle qualité des moyens logistiques mis à disposition des chercheurs dans ce laboratoire.

Un grand remerciement à ma directrice de thèse et la responsable du groupe ISGE Madame Marise BAFLEUR. Merci pour sa confiance, son soutien, sa disponibilité et pour toutes les discussions que nous avons eu pendant ces trois ans. Merci pour ses remarquables compétences et ses grandes qualités humaines. Elle a grandement contribué à l'aboutissement de ces travaux dans les meilleures conditions.

Je remercie Mr. David TREMOUILLES qui était mon codirecteur de thèse, pour ses conseils et pour toutes les discussions efficaces que nous avons eu.

Je tiens également à remercier Messieurs Philippe GALY de l'institut STMicroelectronics-Crolles et Dominique PLANSON (Professeur des universités à l'INSA de Lyon) pour avoir accepté d'être les rapporteurs de mes travaux de thèse. Je remercie aussi Messieurs Alain CAZARRE (Professeur à l'Université Paul Sabatier de Toulouse) et Bruno ALLARD (Professeur des universités à l'INSA de Lyon), pour avoir accepté d'être des examinateurs dans le jury.

Je voudrais remercier Nicolas MAURAN, technicien au LAAS, qui s'est investi dans les mesures réalisées au LAAS.

Je remercie Camille CAZENEUVE du service du personnel pour tous ses soutiens administratifs durant la thèse.

A mes collègues au LAAS : Moustafa, Elias, Emilie, Adnan, Gaëtan, Peihua, Alonã,... merci beaucoup pour les bons moments que nous avons passé ensembles.

Merci de nouveau à Moustafa et Gaëtan pour toutes les discussions que nous avons eu sur les simulations sur Sentaurus.

Merci à tous mes amis, Khalil Al-Astal, Nadim Nasreddine, Ibrahim Albluwi, Hadi El-Bayda, Ahmad Al Sheikh, Anouar Rachdi, Mahmoud Maksoud, Bahjat El Rez, Ali Shokr, Dr. Rida Hassaïne et tous les amis qui m'ont soutenu pendant ces trois ans

J'aime remercier mes parents, Ma mère, mon père, mes frères et mes sœurs pour m'avoir soutenu et encouragé toutes ces années d'étude, pendant la thèse et même pendant le Master et avant.

Enfin, pour mon épouse Ranim, la mère de mon petit Mouhammad, merci d'être toujours près de moi pour me soutenir, m'écouter et me conseiller.

Merci à toutes les personnes que je n'ai pas citées et qui ont de près ou de loin participé à la réalisation de ce travail.

الله الماد ا

# Résumé

Structures MOS-IGBT sur technologie SOI en vue de l'amélioration des performances à haute température de composants de puissance et de protections ESD

La miniaturisation ainsi que les nouvelles applications de l'électronique, comme par exemple, l'intégration mécatronique au plus près des moteurs dans l'automobile, requièrent un fonctionnement à haute température des composants. Pour répondre à cette contrainte de la haute température, la technologie SOI (Silicium sur Isolant) permet d'étendre la gamme de températures de fonctionnement tout en garantissant la nécessaire isolation entre les composants.

Dans le cadre du projet FNRAE COTECH, nos travaux avaient pour objectifs d'améliorer le fonctionnement des structures électroniques à haute température d'une technologie SOI (200°C). N'ayant pas la possibilité de modifier les paramètres technologiques de la technologie étudiée, nous avons exploré diverses solutions de conception que ce soit en termes de topologie du composant ou d'architecture de composant.

Après une analyse exhaustive de la bibliographie relative aux effets de la haute température sur les performances et la fiabilité des composants, nous avons recherché la technologie SOI la mieux adaptée pour l'application qui est la conception d'un driver haute température pour la commande d'un onduleur à base de composants JFET SiC. La technologie retenue est une technologie de puissance intelligente comprenant une bibliothèque CMOS basse tension (5V), des transistors de puissance LDMOS (25V, 45V et 80V) et des transistors bipolaires NPN et PNP.

Afin de caractériser cette technologie en température, dans un premier temps, nous avons conçu un véhicule de test en introduisant certaines règles de dessin bénéfiques pour le comportement en température, à la fois pour les composants basse et haute puissance. Nous avons également étudié une nouvelle architecture de composants combinant au sein d'un même composant un composant MOS et un composant IGBT, dans un objectif d'auto-compensation des effets négatifs de la température.

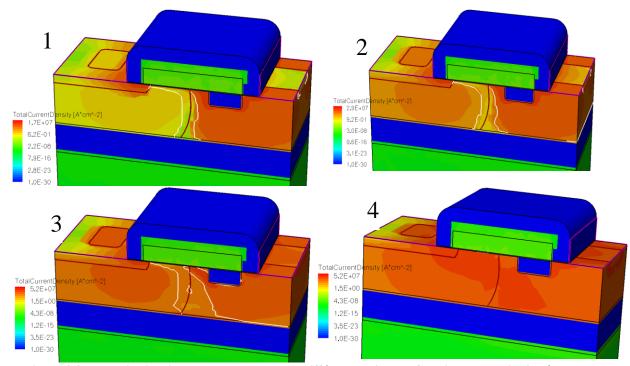

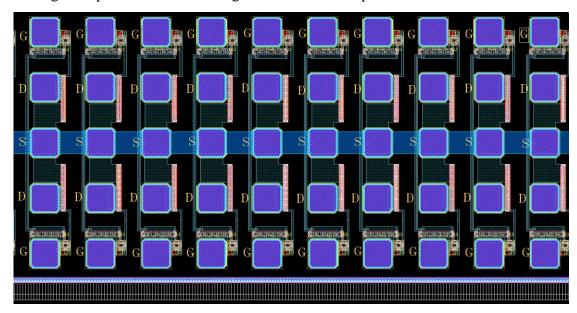

Afin d'optimiser la conception de ces composants mixtes MOS-IGBT, la méthodologie que nous avons adoptée s'est appuyée sur des simulations physiques 2D et 3D Sentaurus. La simulation 3D a été un outil d'optimisation indispensable pour l'optimisation de ces structures mais n'a cependant pu être utilisée que de manière qualitative du fait de l'absence d'accès aux paramètres technologiques. Dans le cadre de ce travail, deux véhicules de test ont été réalisés et caractérisés.

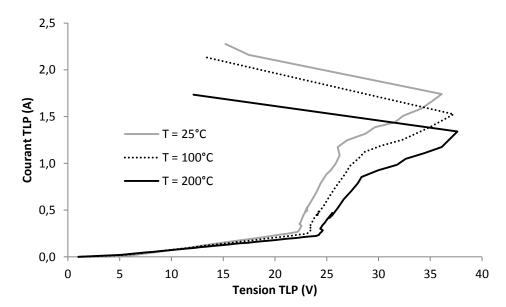

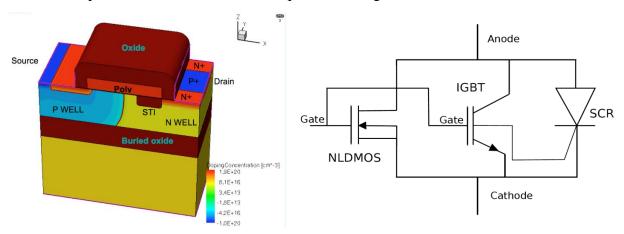

Ces structures mixtes MOS-IGBT ont été proposées en tant que structures de protection contre les décharges électrostatiques (ESD) pour remplacer une structure de protection de type "power clamp". Cette architecture mixte confère plusieurs avantages qui sont la possibilité d'activer le thyristor parasite permettant ainsi d'obtenir une très faible résistance à l'état passant quasiment indépendante de la température, une amélioration significative de la robustesse ESD et un gain en surface considérable

(facteur 10). L'inconvénient majeur associé au déclenchement du thyristor est son faible courant de maintien incompatible avec une immunité du circuit au risque de latch-up.

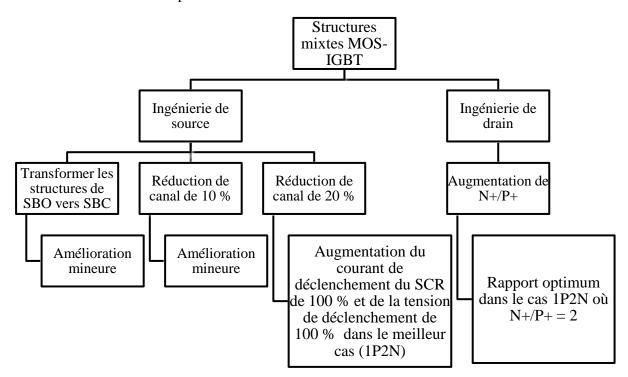

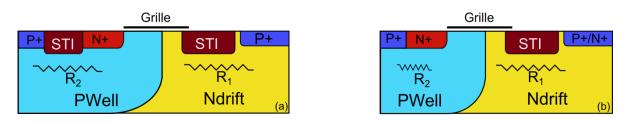

En s'appuyant sur la simulation 3D, nous avons proposé plusieurs solutions, à la fois topologiques et d'architecture, permettant d'augmenter significativement le niveau de ce courant. Ces diverses solutions ont été validées expérimentalement.

Enfin, les bonnes performances de ces structures mixtes ont motivé leur étude en tant que structures de puissance. Dans ce cas, l'objectif majeur est d'éviter le déclenchement du thyristor parasite. Grâce à la simulation 3D, nous avons proposé plusieurs voies d'optimisation permettant d'exploiter les bonnes performances de ces structures à la fois en température et en commutation.

## **Abstract**

MOS-IGBT structures on SOI technology for improving the high-temperature performance of power components and ESD protections

Miniaturization and new applications of electronics, such as integrating mechatronics as close as possible to automotive engines, require high-temperature operation components. To meet this requirement, SOI technologies (silicon on insulator) allows extending the operation temperature range while providing the necessary isolation between components.

Within the framework of COTECH FNRAE project, the objectives of our work were the improvement of the SOI electronic structures at high-temperature operation (200°C). As the technological parameters of our technology could not be changed, we explored various design solutions like the topology of the component or its architecture.

After an exhaustive analysis of the literature in the field of high-temperature electronics and reliability, we selected the most suitable SOI technology for the application that is a high-temperature driver for the control of a power inverter based on JFET SIC components. The chosen technology is a smart power technology including low voltage CMOS (5 V), LDMOS power transistors (25 V, 45 V and 80 V), NPN and PNP bipolar transistor.

To characterize this technology at different temperatures, as a first step, we designed a test vehicle by introducing specific design rules beneficial for the temperature behavior, both for low and high power components. We also studied new components architecture by combining in a single component a MOS and an IGBT, with an objective of self-compensation of the negative effects of temperature.

To optimize the performance of these components (mixed MOS-IGBT), our methodology was based on using 2D and 3D Sentaurus physical simulation. The 3D simulation was an essential tool for the optimization of these structures, but was only used as a qualitative tool since we could not have access to the technological parameters. As part of this work, two test vehicles were produced and characterized.

These mixed structures MOS-IGBT have been proposed as ESD protection structures (Electro Static Discharge protection structures), to replace the LDMOS of a power clamp circuit. This mixed architecture provides several benefits that are the activation of the parasitic thyristor resulting in a very low on-state resistance almost independent of temperature, a significant improvement in ESD robustness and a considerable area saving (factor 10). The major disadvantage associated with the triggering of the thyristor is its low holding current incompatible with the required latch-up immunity of the circuit.

Based on 3D simulation, we have proposed several solutions, both topological and architectural, to significantly increase the level of the holding current. These various solutions have been experimentally validated.

Finally, the good performance of these mixed structures have motivated their study as power structures. In this case, the major objective is to avoid the triggering of parasitic

thyristor. Thanks to 3D simulation, we have proposed several ways of optimization to take advantage of the good temperature and switching performance of these structures.

# Table des matières

| ln | trodu | ıction  | générale                                                                        | 13 - |

|----|-------|---------|---------------------------------------------------------------------------------|------|

| 1  | Eta   | at de l | 'art                                                                            | 14 - |

|    | 1.1   | Intro   | duction                                                                         | 18 - |

|    | 1.2   | Géné    | ralités sur la technologie SOI                                                  | 20 - |

|    | 1     | 2.1     | Technologie SOI                                                                 | 20 - |

|    | 1     | 2.2     | Fabrication d'une plaquette SOI                                                 | 20 - |

|    | 1     | 2.3     | FDSOI, PDSOI et BCD                                                             | 24 - |

|    | 1     | 2.4     | Avantages de la technologie SOI                                                 | 25 - |

|    | 1     | 2.5     | Inconvénients de la technologie SOI.                                            | 28 - |

|    | 1.3   | •       | ct de la haute température sur les caractéristiques électriques des dispositifs |      |

|    | élect | roniq   | ues                                                                             |      |

|    |       | 3.1     | Impact de la haute température sur la tension de seuil                          |      |

|    |       | 3.2     | Courant de fuite à haute température                                            |      |

|    |       | 3.3     | Fonctionnement en logique (I <sub>ON</sub> /I <sub>OFF</sub> )                  |      |

|    |       | 3.4     | Tension de claquage et R <sub>ON</sub>                                          |      |

|    | 1.3   | 3.5     | Fiabilité de l'oxyde de grille                                                  |      |

|    | 1.4   | Impa    | ct sur le comportement de structures de protection contre les ESD               |      |

|    | 1.4   | 4.1     | Principaux éléments de protection ESD                                           |      |

|    | 1.4   | 4.2     | Protection ESD à haute température                                              |      |

|    | 1.5   |         | posants de puissance sur SOI                                                    |      |

|    | 1.6   | Etat    | de l'art des technologies à haute température                                   | 45 - |

|    | 1.0   | 6.1     | Electromigration                                                                |      |

|    | 1.0   | 6.2     | Barrière métallique de contact                                                  | 47 - |

|    | 1.0   | 6.3     | Epaisseur de l'oxyde grille                                                     | 48 - |

|    | 1.0   | 6.4     | Techniques de conception                                                        |      |

|    | 1.0   | 6.5     | Gestion thermique                                                               | 49 - |

|    | 1.7   |         | nologies SOI pour les applications haute température                            |      |

|    | 1.8   | Conc    | lusion                                                                          | 53 - |

|    | 1.9   | Réféi   | rences bibliographiques                                                         | 54 - |

| 2  | Et    |         | le fonctionnement à haute température des structures à basse tension            |      |

|    | 2.1   |         | duction                                                                         |      |

|    | 2.2   |         | mètres de la technologie utilisée                                               |      |

|    | 2.3   | Trans   | sistors MOS basse tension de type N                                             | 61 - |

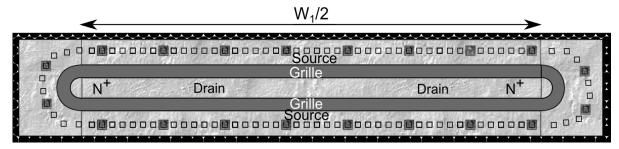

|   | 2.  | 3.1    | Structures proposées                                                    | 62 -        |

|---|-----|--------|-------------------------------------------------------------------------|-------------|

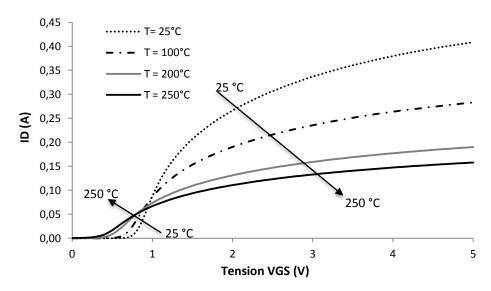

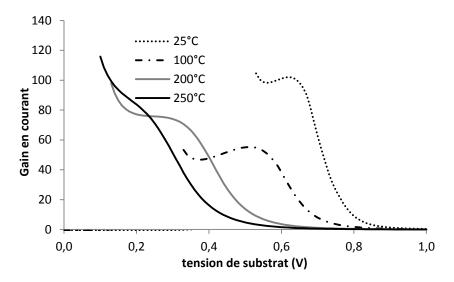

|   | 2.  | 3.2    | Caractérisation des dispositifs NMOS basse tension                      | 65 -        |

|   | 2.4 | Stru   | ctures MOS basse tension de type P                                      | 72 -        |

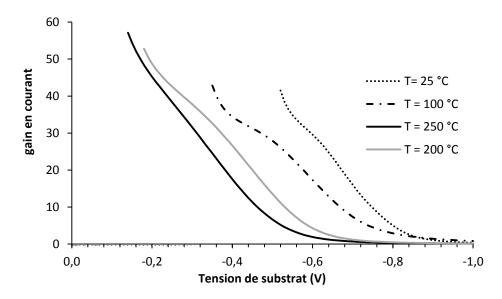

|   | 2.  | 4.1    | Caractéristiques électriques des dispositifs PMOS basse tension         | 72 -        |

|   | 2.5 | Cond   | clusion                                                                 | 76 -        |

|   | 2.6 | Réfé   | rences bibliographiques                                                 | 77 -        |

| 3 | St  | tructu | res mixtes MOS-IGBT dans le domaine de la puissance                     | 80 -        |

|   | 3.1 | Intro  | oduction                                                                | 82 -        |

|   | 3.2 | Stru   | ctures de puissance MOS et IGBT                                         | 83 -        |

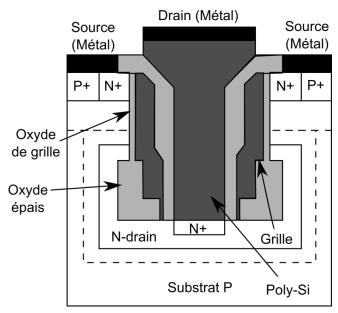

|   | 3.  | 2.1    | LDMOS                                                                   | 83 -        |

|   | 3.  | 2.2    | IGBT                                                                    | 85 -        |

|   | 3.  | 2.3    | NLDMOS 25 V et 45 V                                                     | 88 -        |

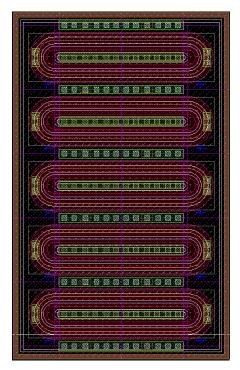

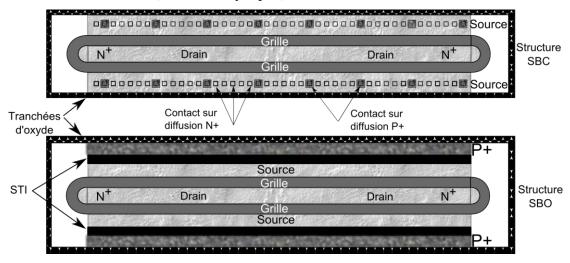

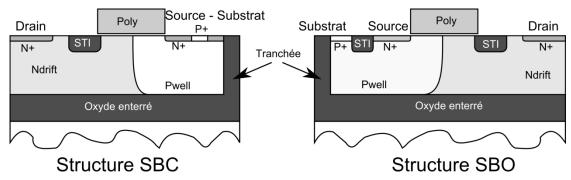

|   | 3.  | 2.4    | Présentation des composants                                             | 88 -        |

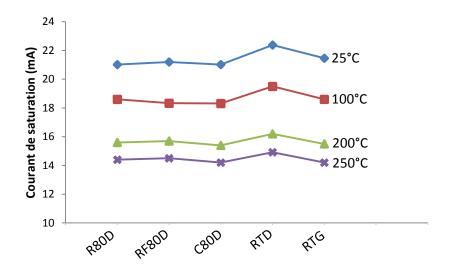

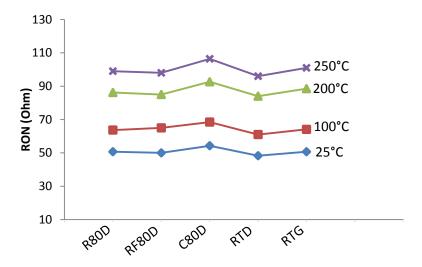

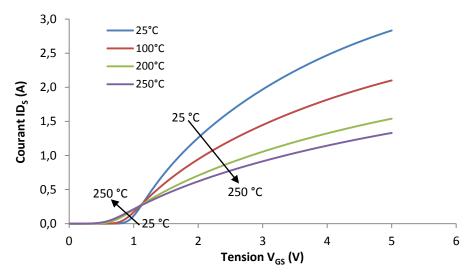

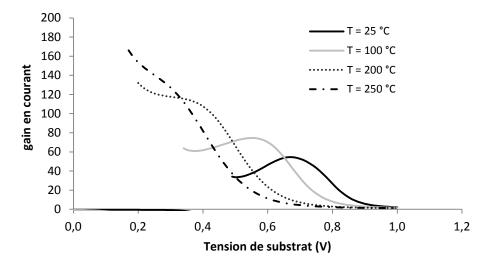

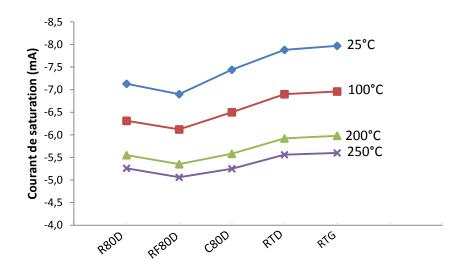

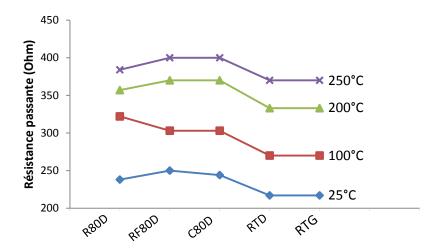

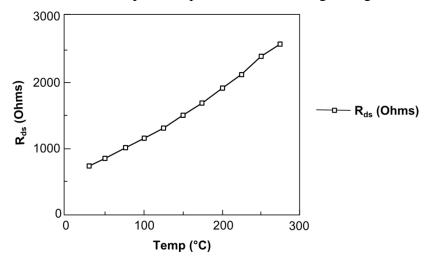

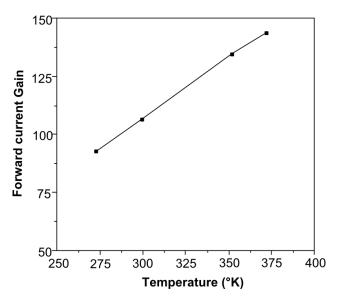

|   | 3.  | 2.5    | Variation de R <sub>ON</sub> avec la température                        | 90 -        |

|   | 3.  | 2.6    | Variation de la tension de seuil                                        | 91 -        |

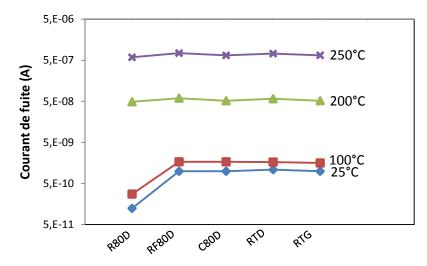

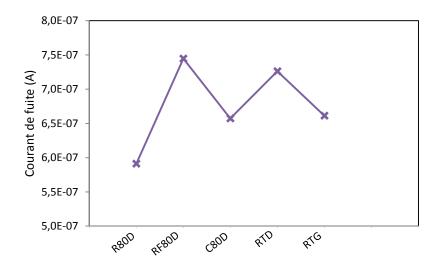

|   | 3.  | 2.7    | Courant de fuite pour les différents composants en fonction de la tempé | rature 92 - |

|   | 3.  | 2.8    | Effet bipolaire parasite                                                | 92 -        |

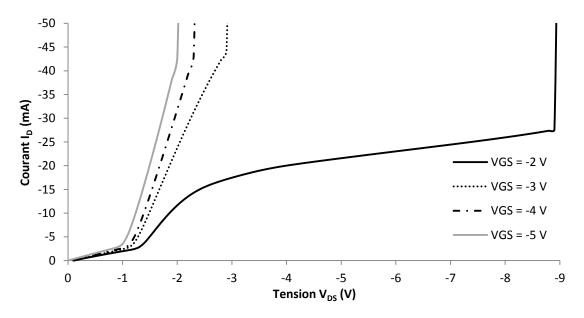

|   | 3.3 | Cas    | d'un PLDMOS 25 V et 45 V                                                | 94 -        |

|   | 3.4 | Stru   | ctures Mixtes MOS-IGBT                                                  | 95 -        |

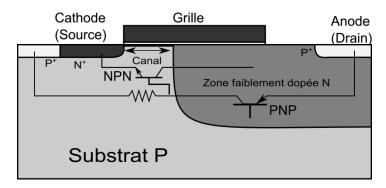

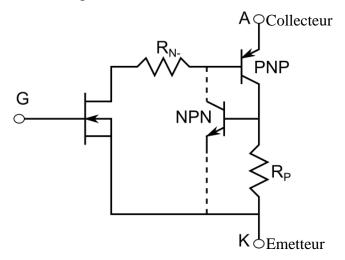

|   | 3.  | 4.1    | Définition                                                              | 95 -        |

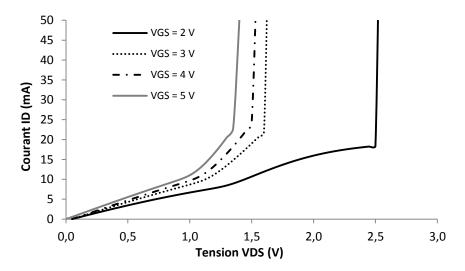

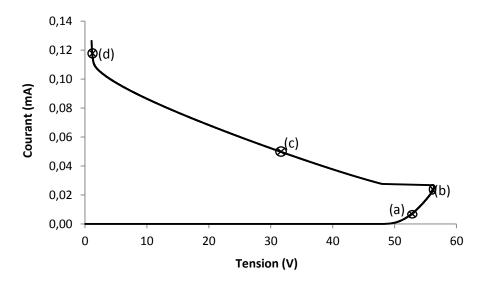

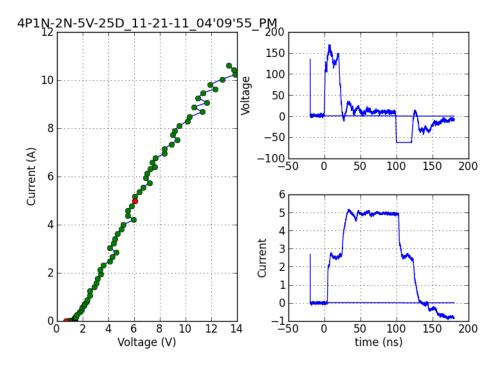

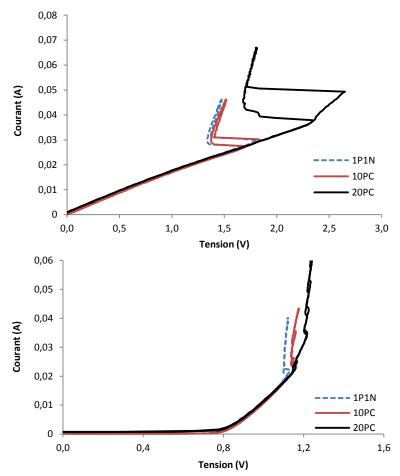

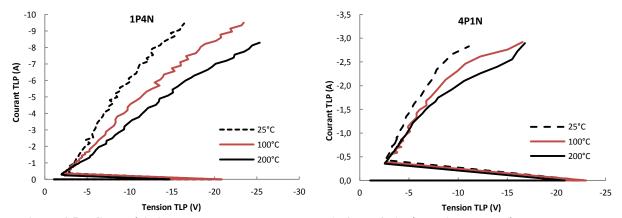

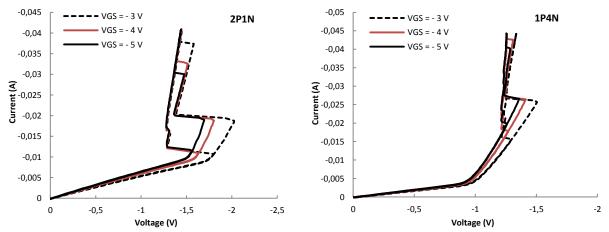

|   | 3.  | 4.2    | Caractérisation électriques                                             | 97 -        |

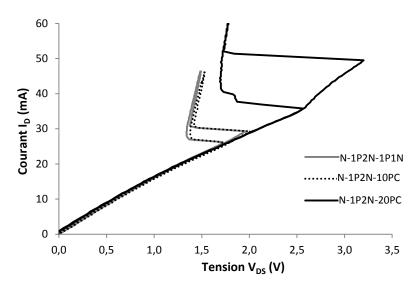

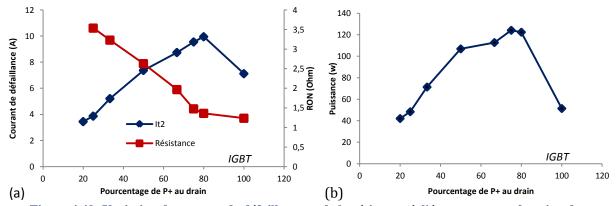

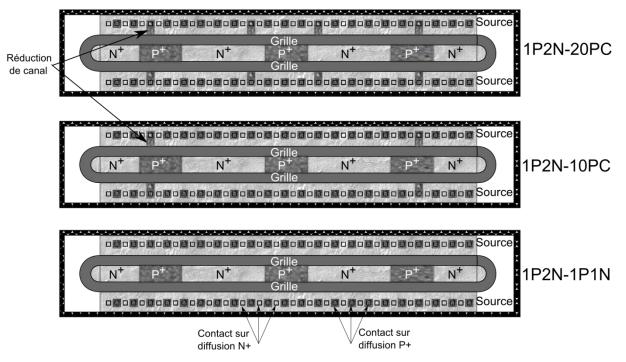

|   | 3.5 | Opti   | misation des structures mixtes                                          | 99 -        |

|   | 3.  | 5.1    | Méthodologie de simulation                                              | 100 -       |

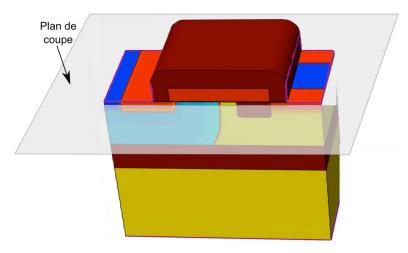

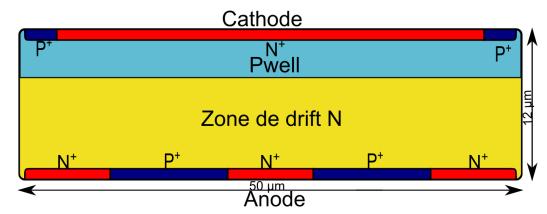

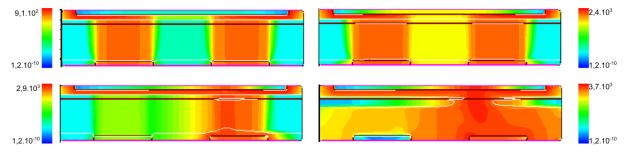

|   | 3.  | 5.2    | Description de la structure                                             | 101 -       |

|   | 3.6 | Stru   | ctures mixtes optimisées                                                | 106 -       |

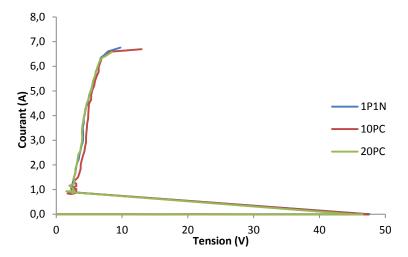

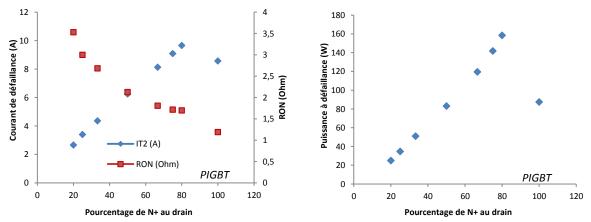

|   | 3.  | 6.1    | Caractérisations électriques                                            | 108 -       |

|   | 3.  | 6.2    | Autres voies d'optimisation                                             | 115 -       |

|   | 3.7 | Cond   | clusion                                                                 | 117 -       |

|   | 3.8 | Réfé   | rences bibliographiques                                                 | 118 -       |

| 4 | St  | tructu | res mixtes MOS-IGBT pour l'amélioration de la protection ESD            | 120 -       |

|   | 4.1 | Intro  | oduction                                                                | 122 -       |

|   | 4.2 | Mod    | lèles de stress ESD                                                     | 124 -       |

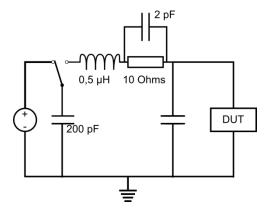

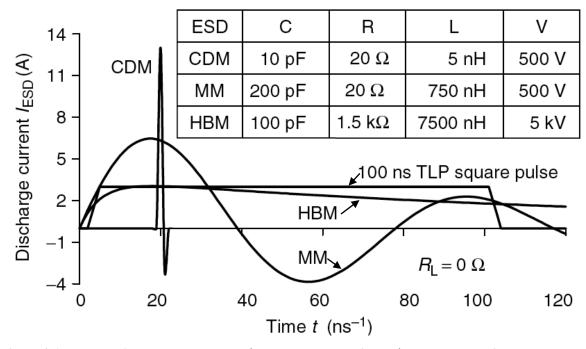

|   | 4.  | 2.1    | Modèle du corps humain (HBM)                                            | 124 -       |

|   | 4.  | 2.2    | Modèle de la machine (MM)                                               | 125 -       |

| 4.  | .2.3   | Modèle du dispositif chargé (CDM) 12                                                       | 5 - |

|-----|--------|--------------------------------------------------------------------------------------------|-----|

| 4.3 | Moti   | ivation 12                                                                                 | 7 - |

| 4.  | 3.1    | Fonctionnement du LDMOS en protection ESD 12                                               | 8 - |

| 4.  | 3.2    | Fonctionnement d'IGBT en protection ESD 13                                                 | 0 - |

| 4.4 | Struc  | ctures mixtes MOS-IGBT proposées                                                           | 1 - |

| 4.  | 4.1    | Caractérisation TLP de la structure de protection de TFSMART1 à basse et à haute           |     |

| te  | empéra | atures 13                                                                                  | 1 - |

| 4.  | 4.2    | Structure proposée MOS-IGBT 13                                                             | 2 - |

| 4.  | 4.3    | Résultats expérimentaux à température ambiante 13                                          | 4 - |

| 4.  | 4.4    | Résultats expérimentaux à haute température 14                                             | 1 - |

| 4.5 | Opti   | misation des structures 14                                                                 | 3 - |

| 4.  | .5.1   | Méthodologie de simulation 14                                                              | 4 - |

| 4.  | .5.2   | Simulation TCAD trois dimensions 14                                                        | 6 - |

| 4.6 | Cara   | ctérisation des structures optimisées 15                                                   | 6 - |

| 4.  | 6.1    | Caractérisation des structures mixtes type N 15                                            | 6 - |

| 4.  | .6.2   | Caractérisation des structures mixtes de type P 16                                         | 7 - |

| 4.7 | Opti   | misation par variation de la longueur de la zone de drift, de STI et autres solutions - 17 | 3 - |

| 4.8 | Conc   | clusion 17                                                                                 | 6 - |

| 4.9 | Réfé   | rences hibliographiques - 17                                                               | ጸ - |

# Introduction générale

En 1977, le coût associé à l'électronique dans l'automobile était en moyenne de 110 \$ [1]. En 2003, ce même coût avait plus que décuplé avec une moyenne de 1510 \$ [2]. Le moment charnière de cette évolution-révolution dans l'électronique automobile a été la réglementation gouvernementale dans les années 1970 rendant obligatoire le contrôle des émissions de CO<sub>2</sub> et les nécessaires économies de carburant pour y aboutir. Le contrôle de la consommation du carburant est une opération complexe ne pouvant pas être accomplie avec les systèmes traditionnels mécaniques. Ainsi, ces réglementations gouvernementales associées aux rapides développements de l'électronique de puissance et de la microélectronique permettant une forte miniaturisation combinée à des coûts attractifs, ont conduit à un accroissement continu de l'électronique dans l'automobile [3].

De plus, la demande croissante de miniaturisation et réduction du poids des convertisseurs de puissance pour l'industrie automobile requiert des circuits électroniques capables de fonctionner à une température plus élevée (175°C ou plus) avec peu ou sans dissipation de chaleur [4]. Un résumé des différentes applications d'électronique à haute température dans l'automobile est présenté dans le Tableau 1. D'autres applications comme celles de l'aéronautique, du spatial et de bien d'autres domaines (forages, nucléaire, solaire...), ont également des besoins de fonctionnement de l'électronique à haute température.

| Moteur                      | 150-200 °C      |

|-----------------------------|-----------------|

| Transmission                | 150-200 °C      |

| Capteurs ABS des roues      | 150-200 °C      |

| Pression du cylindre        | 200-300 °C      |

| Détection sur l'échappement | Ambiante 300 °C |

Tableau 1: Gamme de températures maximales dans l'automobile [5]

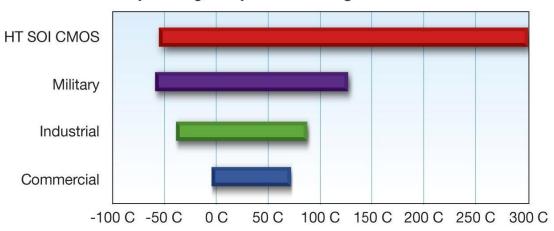

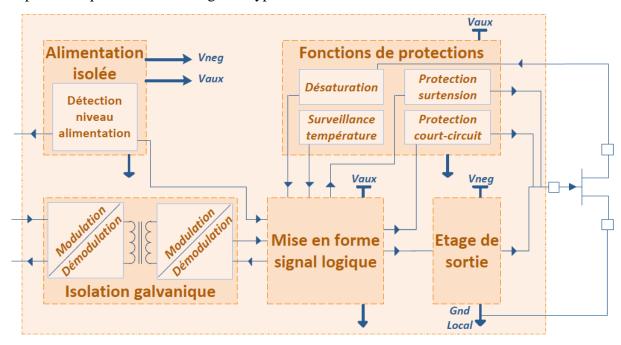

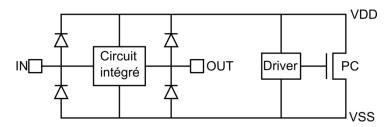

Ces dernières années, l'évolution vers le véhicule hybride a généré la nécessité d'une électronique à haute température, fiable et peu couteuse pouvant fonctionner à des températures extrêmes localisées sous le capot. Dans ce travail, et dans le cadre du projet COTECH, nous avons étudié le comportement électrique des composants d'une technologie sur silicium sur isolant (SOI) 0,8 µm, qualifiée pour la haute température (200°C ambiante). Le but de ce projet est de concevoir un driver pour un onduleur JFET SiC capable de fonctionner à haute température (200°C ambiante).

Dans ce cadre, notre contribution était d'étudier et d'améliorer les performances en température des composants de cette technologie pour un fonctionnement étendu jusqu'à 250°C. Nous avons principalement focalisé notre étude sur les composants de puissance latéraux MOS et IGBT ainsi que l'amélioration des performances des protections contre les décharges électrostatiques (ESD).

Le premier chapitre de notre mémoire est essentiellement consacré à l'étude bibliographique du domaine. Nous présentons tout d'abord les différentes méthodes de fabrication des plaquettes SOI et nous comparons les performances de composants MOS réalisés en technologie SOI et sur substrat massif. Ensuite, nous rappelons l'impact de la

haute température sur la variation des grandeurs physiques importantes dans le fonctionnement des composants électroniques. Enfin, nous étudions les principales structures de protection ESD et l'effet de la température sur leurs performances. A la fin de ce chapitre, nous donnons un état de l'art des technologies SOI à haute température.

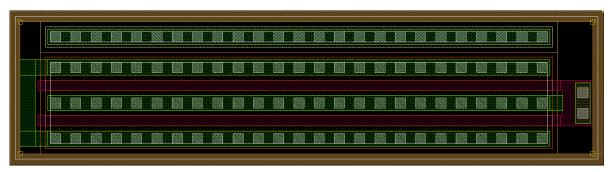

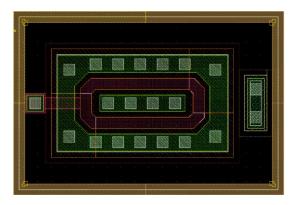

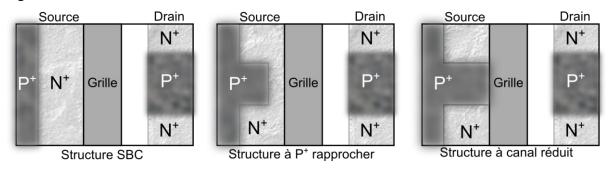

Dans le deuxième chapitre, après une brève présentation de la technologie SOI, TFSMART1, sur laquelle nous avons développé ces travaux, nous étudions le fonctionnement à haute température des composants MOS, basse puissance et basse tension de type N et P, de la technologie. Cette étude porte à la fois sur les cellules de la bibliothèque mais également sur l'impact de différentes topologies. Cette première étude nous a permis de dégager certains principes de conception améliorant les performances à haute température.

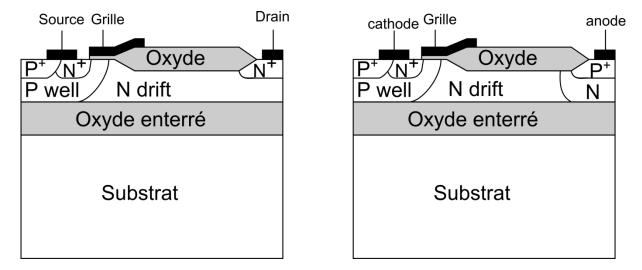

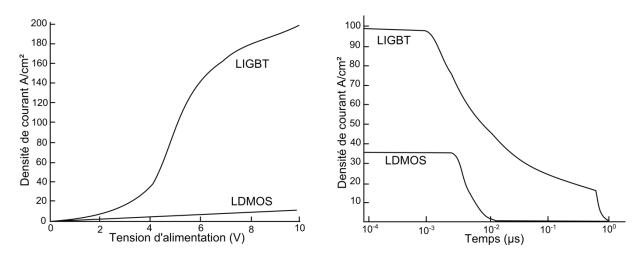

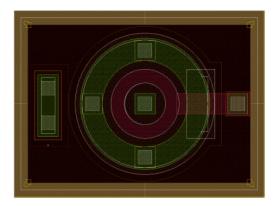

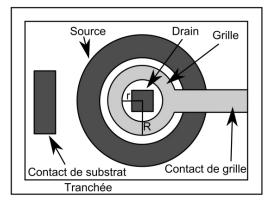

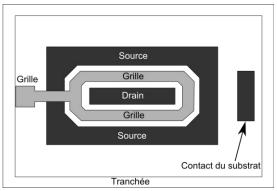

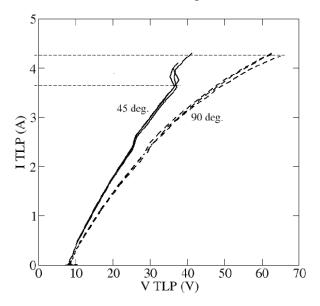

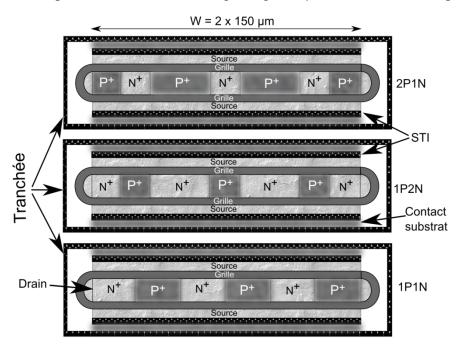

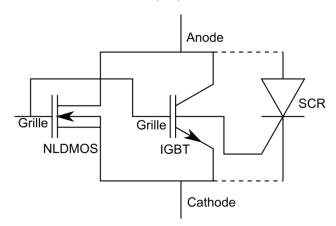

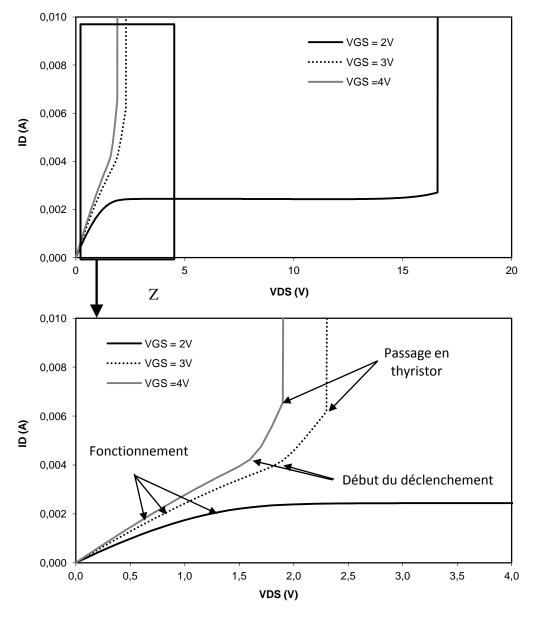

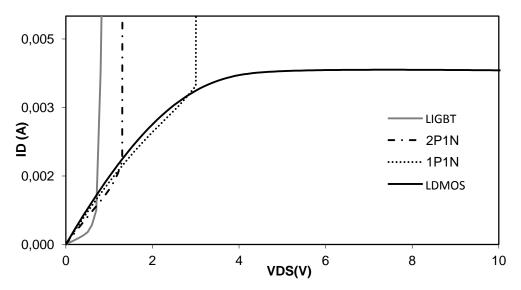

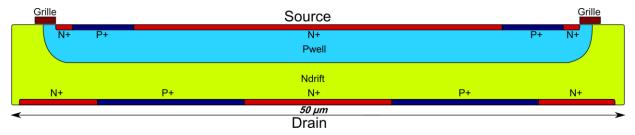

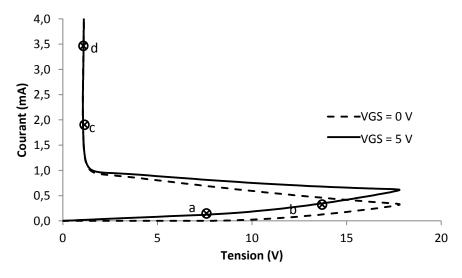

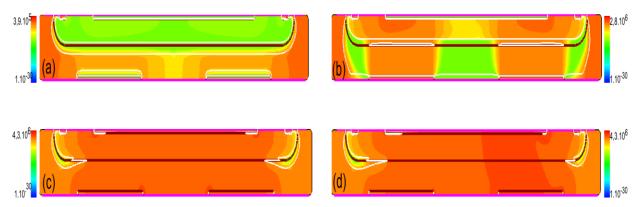

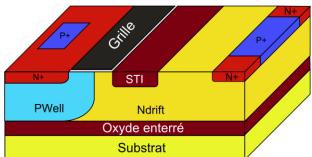

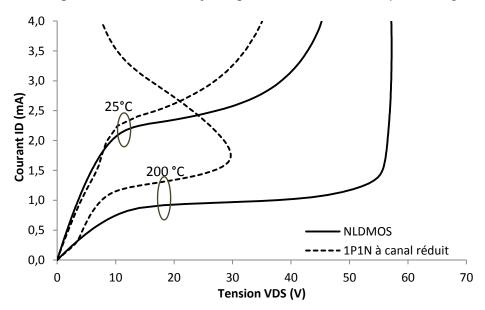

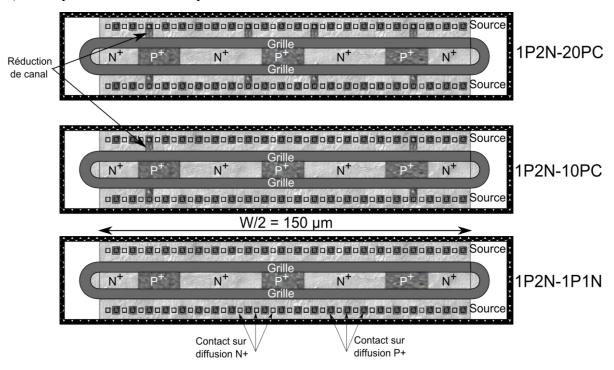

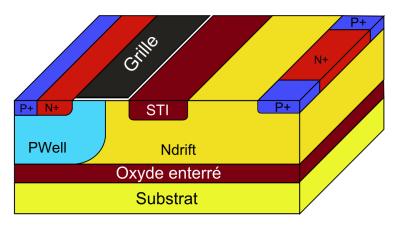

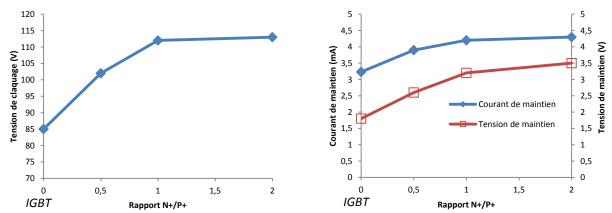

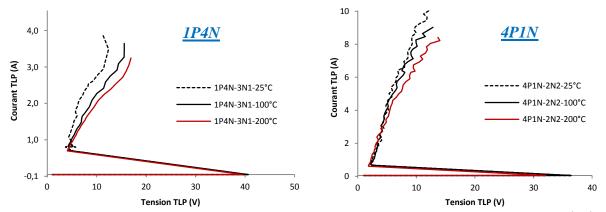

Le troisième chapitre est dédié à l'étude et à l'optimisation de structures de puissance (25 et 45 V), de type N et P à haute température. Dans cet objectif, nous proposons un composant mixte de puissance, basé sur un LDMOS et intégrant un LIGBT en remplaçant une partie de la diffusion N+ de la source par une diffusion P+, pour le cas du composant type N et inversement pour le cas du type P. Ces nouvelles structures ont fait l'objet de deux réalisations sur silicium. Leur optimisation s'est appuyée sur la simulation TCAD Sentaurus 3D. Malgré des résultats expérimentaux n'atteignant pas les performances estimées par la simulation car ne disposant pas des paramètres technologiques réels, les solutions proposées ont pu être validées et de nouvelles perspectives d'amélioration envisagées. Il est ainsi démontré qu'il y a un grand intérêt en termes de résistance à l'état passant et courant de saturation à introduire un mode IGBT dans une structure de puissance à basse tension, en particulier, à haute température. Le verrou majeur, comme dans tout IGBT, reste le contrôle du thyristor parasite pour lequel plusieurs solutions efficaces ont pu être validées.

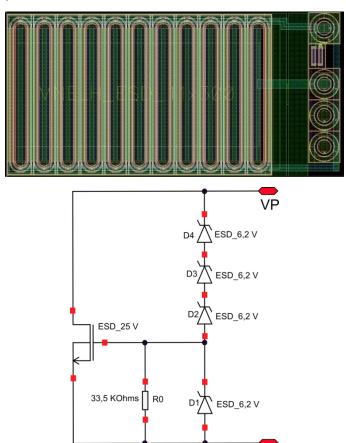

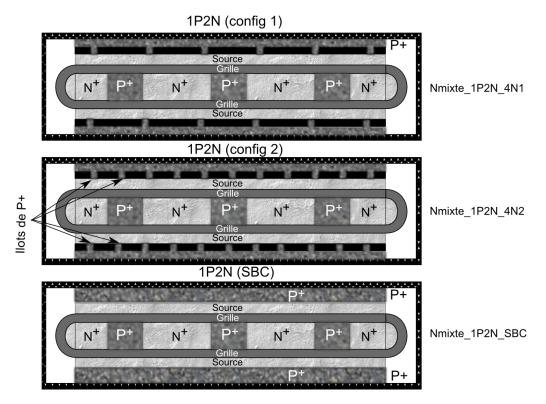

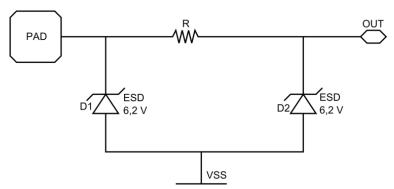

Le quatrième chapitre est consacré à l'étude de structures de protection contre les ESD à haute température. L'étude des composants de puissance nous a permis de voir l'intérêt des structures mixtes MOS-IGBT et en particulier, de leur utilisation comme structure de protection ESD en autorisant cette fois le déclenchement du thyristor parasite qui est le meilleur composant en terme de densité de puissance. La structure de protection envisagée est celle du remplacement d'une protection centralisée basée sur un LDMOS de puissance qui est composée de 11 cellules élémentaires. La nouvelle protection est composée d'une seule de ces cellules élémentaires et intègre un LIGBT par la simple implémentation de zones P+ dans le drain du LDMOS. L'optimisation vis-à-vis des performances ESD a été menée grâce à des simulations TCAD 3D, en particulier, pour améliorer son immunité au latch-up. Nous présentons une caractérisation exhaustive de ces structures à la fois en mesures impulsionnelles de type TLP et en température jusqu'à 200°C. Les gains en performances obtenus grâce à ces composants mixtes sont tout d'abord une surface réduite de 90 %, une robustesse ESD en termes de courant de défaillance passant de 1.7A à 3.8A et jusqu'à 10A selon la topologie de la structure. Les solutions proposées et étudiées en simulation pour améliorer l'immunité au latch-up ont été partiellement validées car encore insuffisantes. Malgré l'aspect qualitatif des simulations, nous avons pu parfaitement corréler expérimentalement les tendances et proposer de nouvelles perspectives d'amélioration.

Enfin, nous rassemblons à la fin de ce mémoire nos conclusions sur les résultats majeurs obtenus au cours de ces travaux et donnons quelques perspectives à leur poursuite.

# Chapitre I Etat de l'art

# 1.1 Introduction

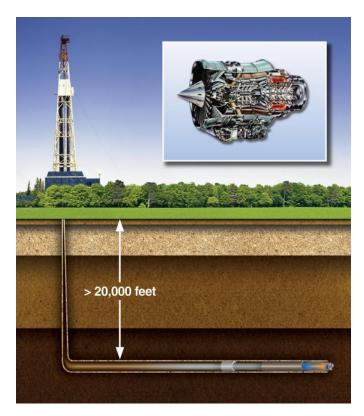

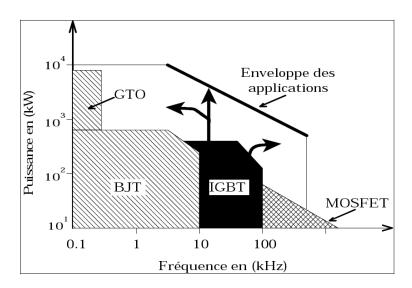

L'évolution des technologies des semi-conducteurs vers des géométries de plus en plus fines permet un accroissement des performances et des fonctionnalités des circuits intégrés mais s'accompagne simultanément d'une augmentation de la puissance dissipée. Cette évolution dans l'industrie automobile, aéronautique et pétrolière requiert une nouvelle utilisation de l'électronique dans la mécatronique et dans certains cas, les circuits sont fixés au plus près du moteur où la température est élevée, ou sous la terre (le cas de l'industrie du pétrole (Figure 1.1)). Pour répondre à ce besoin, il est nécessaire de concevoir des dispositifs pouvant fonctionner à haute température. On retrouve les mêmes contraintes pour les capteurs qui doivent également fonctionner à haute température [1]. Dans ce contexte, de nouvelles architectures d'électronique de puissance sont requises pour répondre à ces nouvelles exigences : haute tension et haute température (200°C) liée à l'intégration mécatronique des modules de puissance.

Figure 1.1: Application Haute température [2], [3] (Forage pétrolier et contrôleur du moteur d'avion).

Pour répondre aux contraintes de cette intégration, de nouveaux composants de puissance basés sur les matériaux à grand gap comme le SiC permettent la conception d'onduleurs à faible pertes fonctionnant à haute température et haute tension [4]. Ces modules de puissance de nouvelle génération requièrent cependant une électronique de contrôle et de commande rapprochée qui pour l'instant ne peut être réalisée qu'en silicium. Cette électronique sur silicium devra également pouvoir fonctionner à haute température.

Le cadre de nos travaux est celui du projet COTECH, financé par la Fondation de Recherche pour l'Aéronautique et l'Espace, dont le but est de réaliser un circuit de commande d'un onduleur à JFET SiC. La technologie SOI (« Silicon on insulator » ou « silicium sur

isolant ») est la plus appropriée pour fabriquer ces étages de pilotage. La technologie SOI, outre la réduction des éléments parasites, offre la possibilité d'intégrer conjointement des composants basse et haute tensions, permet une isolation efficace entre blocs et limite la dérive en température des caractéristiques des composants.

Dans ce chapitre consacré à l'état de l'art des technologies pour la haute température, nous avons répertorié les techniques de fabrication des plaquettes SOI, les avantages de cette technologie par rapport à la technologie sur substrat massif et ses inconvénients. Ensuite, nous nous sommes intéressés aux caractéristiques électriques comme la tension de seuil, le courant de fuite, la tension de claquage et la fiabilité de l'oxyde de grille pour deux types de technologies (SOI partiellement dépeuplé PDSOI et SOI totalement dépeuplé FDSOI) à haute température, et nous les avons comparées aux caractéristiques de la technologie sur substrat massif. Nous avons également analysé l'impact de la température élevée sur l'électromigration et sur la diffusion du métal de contact avec le silicium. L'impact de la température sur les structures de protection contre les décharges électrostatiques (ESD) est aussi examiné dans ce rapport car il y a une forte dépendance des paramètres électriques de la protection ESD avec la température.

# 1.2 Généralités sur la technologie SOI.

Afin de répondre aux besoins d'accroissement de la densité d'intégration et d'éliminer plusieurs problèmes liés au substrat massif dans les technologies nanométriques, la technologie silicium a évolué vers la technologie SOI.

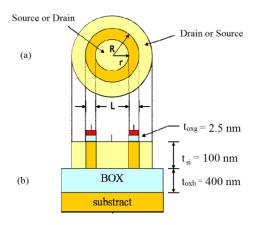

#### 1.2.1 Technologie SOI

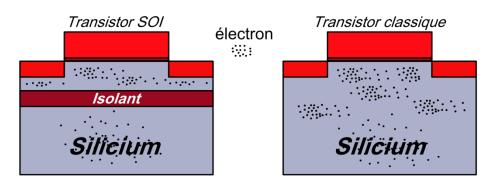

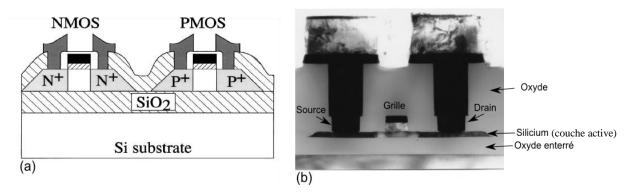

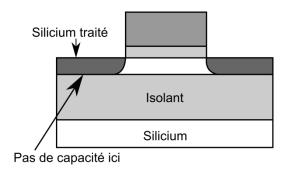

La technologie SOI ou Silicon On Insulator, est une structure constituée d'un empilement d'une couche de silicium sur une couche d'isolant (Figure 1.2) (Figure 1.3). L'isolant peut être, de l'oxyde de silicium (SiO<sub>2</sub>), du saphir (oxyde d'aluminium) Al<sub>2</sub>O<sub>3</sub>, ou tout autre genre d'isolant et leur épaisseur peut varier entre 100nm et 3µm. Le substrat dans ce cas joue seulement le rôle d'un support mécanique et peut être constitué par des matériaux divers, mais la matière la plus courante utilisée est le silicium pour les raisons de compatibilité avec les technologies classiques et de coût. La couche de silicium sur isolant, qui est la couche active a une épaisseur dépendante de l'application (basse ou haute tension). Cette épaisseur peut varier entre 50nm et 100µm.

Figure 1.2: Transistor SOI (gauche) et sur substrat massif (droite)

$Figure \ 1.3: (a) \ Architecture \ schématique \ et \ (b) \ photo \ d'une \ coupe \ pour \ un \ MOSFET \ SOI \ [5]$

## 1.2.2 Fabrication d'une plaquette SOI

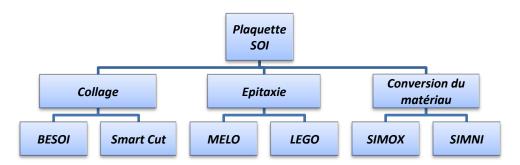

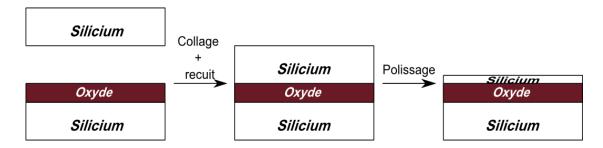

Il existe plusieurs méthodes pour réaliser une plaquette SOI, chacune a ses avantages et ses inconvénients. On peut les classer en trois grands groupes de techniques : techniques de collage, techniques d'épitaxie et technique de la conversion du matériau (figure 1.4).

Figure 1.4: Différentes techniques de réalisation d'une plaquette SOI

#### 1.2.2.1 Technique de collage.

Cette technique dite aussi wafer bonding en anglais est divisée en plusieurs technologies (Figure 1.3).

#### a) BESOI (Bonded and Etchback SOI).

Cette technique consiste à coller deux plaquettes de silicium, dont l'une a une surface oxydée, par les forces de Van der Waals ou liaisons hydrophiles entre les deux surfaces, puis à effectuer un recuit à 1100°C [5]. Cette étape est suivie par un polissage mécano-chimique jusqu'à l'obtention de l'épaisseur de silicium désirée, Figure 1.5.

Cette méthode est simple, mais elle a un inconvénient majeur, qui est son coût, puisqu'on a besoin de deux plaquettes de silicium pour obtenir une seule plaquette SOI.

Figure 1.5: Etapes du procédé BESOI

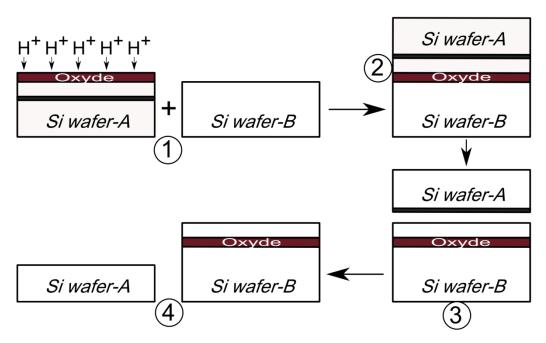

#### b) SmartCut

Ce procédé [5], [6] est basé sur le même principe de collage de deux plaquettes de silicium. La différence est l'utilisation des ions hydrogènes implantés dans la plaquette supérieure.

Donc on utilise cette fois une plaquette de silicium à surface oxydée et implantée par des ions hydrogènes, où la profondeur est fixée par l'énergie d'implantation [7]. Cette plaquette est collée à une autre par liaisons hydrophiles puis un recuit est réalisé. La première phase de ce recuit, de 400 à 600°C, permet de faire coalescer les microcavités dues à l'implantation, et permettent ainsi la propagation d'une fissure à travers toute la couche implantée d'ions hydrogènes (Figure 1.6). La seconde phase du recuit, au dessus de 1000°C, aide à consolider les liaisons chimiques entre les deux surfaces collées.

Après séparation, la rugosité de surface du silicium sur oxyde est rectifiée par un polissage.

Le reste de la plaquette donneuse est intact et peut être recyclé pour former une autre plaquette SOI, ce qui diminue le coût de fabrication par rapport au procédé BESOI utilisant deux plaquettes.

Figure 1.6: Principales étapes du procédé Smart-Cut

Le procédé Smart-Cut sert à obtenir une plaquette SOI de haute qualité, et moins coûteuse. L'ensemble de ces avantages et potentialités fait du Smart-Cut le procédé dominant sur le marché des plaquettes SOI. Il est à noter que l'inventeur et fournisseur de ces plaquettes SOI, la société SOITEC, est français et basé près de Grenoble.

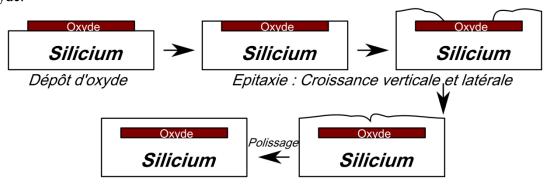

#### 1.2.2.2 Technique d'Epitaxie

La technique de croissance par épitaxie latérale [8] (Epitaxial Lateral Overgrowth : ELO ou Merged Epitaxial Lateral Overgrowth : MELO) est intéressante pour obtenir une couche SOI localisée (Figure 1.7). A partir d'une plaquette de silicium présentant des motifs d'oxyde, on réalise une épitaxie sélective de silicium. Il va donc y avoir croissance de silicium uniquement sur les zones où le substrat de silicium est à nu. La croissance de silicium se fera verticalement au dessus du substrat mais aussi latéralement au dessus du motif d'oxyde. L'épitaxie se poursuit jusqu'à atteindre une dimension latérale suffisante au-dessus de l'oxyde.

Figure 1.7: Wafer SOI réalisé par le procédé MELO (Epitaxie)

Les couches de silicium sur oxyde ainsi obtenues sont de bonne qualité puisqu'elles proviennent d'une épitaxie de silicium. Cependant, la largeur des motifs ainsi réalisés est limitée par le ratio de croissance maximum (la dimension de l'îlot d'oxyde ne doit pas être trop importante sinon l'épaisseur de silicium obtenue en fin de procédé serait démesurée). L'inconvénient majeur de ce procédé concerne les dimensions latérales d'un substrat SOI réalisé par ELO : les valeurs minimales sont voisines de 150 nm x 150 nm et maximales de 8 µm x 500 µm. Les épaisseurs de SOI sont de l'ordre de 40 à 200 nm. Par ailleurs, cette technique présente quelques étapes critiques comme l'épitaxie sélective ou le polissage mécano-chimique.

Figure 1.8 : Etapes du procédé LEGO [9]

Le LEGO (Lateral Epitaxial Growth over Oxide) est une technique basée sur la fusion et la recristallisation de motifs épais de silicium poly-cristallin sur oxyde, et qui permet d'obtenir des motifs localisés de SOI sur un substrat de silicium. Elle a été développée en premier lieu par [10] dans les années 80 et a été désormais reconsidérée à cause d'un nouveau marché pour les structures SOI partielles à faible coût, celui de l'intégration de composants de commande et de puissance sur une même puce avec une isolation diélectrique efficace [9]. La Figure 1.8 présente les étapes du procédé LEGO.

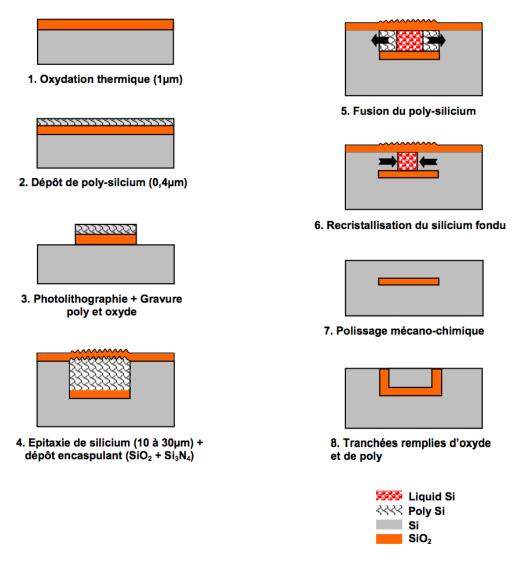

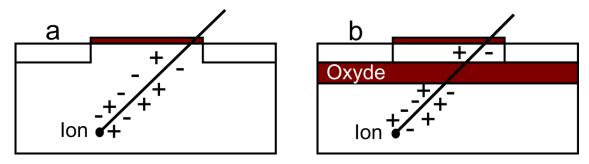

#### 1.2.2.3 Technique de conversion du matériau

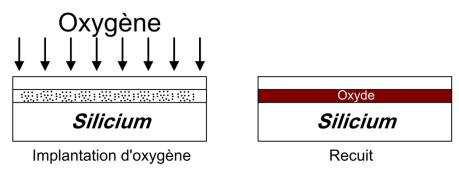

SIMOX (Separation by implantation of oxygen) [5], [11]. Cette technique consiste à implanter des ions d'oxygène afin d'obtenir la couche d'oxyde. La dose et l'énergie d'implantation permettent de déterminer la profondeur et l'épaisseur de la future couche d'oxyde (Figure 1.9) Après implantation, de nombreux défauts (dislocations et fautes d'empilement) sont générés dans la couche supérieure de silicium. Un recuit à très haute température (1300°C pendant quelques heures ou 1405°C pendant 30 minutes) est donc nécessaire pour rétablir une qualité cristalline acceptable de la couche SOI ainsi que pour lier les atomes d'oxygène avec les atomes de silicium en une couche bien délimitée de SiO<sub>2</sub> enterré (Figure 1.9)

Figure 1.9: Etapes technologiques de la technique SIMOX.

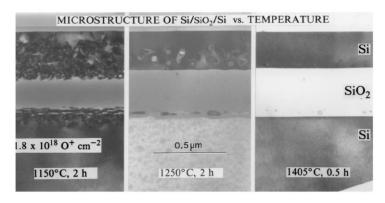

Les couches SOI ainsi obtenues sont de bonne qualité cristalline, mais la couche d'oxyde enterré réalisée par implantation n'a pas les qualités d'un oxyde thermique en terme d'isolation, ce qui est pénalisant pour des applications de puissance. La Figure 1.10 présente l'impact de la température de recuit sur la microstructure de l'interface Si/SiO<sub>2</sub> et SiO<sub>2</sub>/Si [5].

Figure 1.10: Impact de la température de recuit sur la microstructure de SIMOX [5]

La technique SIMNI (Separation by Implantation of Nitrogen) est comme le SIMOX, mais on remplace l'implantation d'oxygène par une implantation d'azote, pour obtenir du nitrure Si<sub>3</sub>N<sub>4</sub> [12]. L'intérêt d'utiliser cet isolant est sa conductance thermique qui est 10 fois plus grand que celle de l'oxyde de silicium [20].

#### 1.2.3 FDSOI, PDSOI et BCD

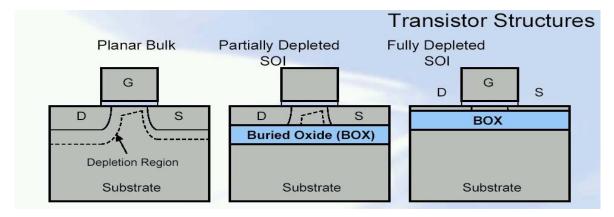

Pour les applications basse tension, il existe 2 types de plaquettes SOI : les plaquettes SOI totalement dépeuplées (FDSOI : Fully Depleted SOI) et des plaquettes SOI partiellement dépeuplées (PDSOI : Partially depleted SOI) (Figure 1.11). La différence entre les deux est

liée à la charge d'espace associée au MOS. Dans le PDSOI où la couche de SOI est mince (de 500 à 800Å) [9], les zones de charge d'espace autour du drain et de la source s'étendent jusqu'à la couche d'oxyde enterrée, mais il subsiste toujours une région quasi neutre quel que soit le régime de fonctionnement. Dans le FDSOI où la couche SOI est très mince (de 150 à 500 Å), la zone entre drain et source est entièrement dépeuplée pour créer le canal. Il n'existe alors plus de région quasi neutre. Ces deux types de transistors participent à l'effort pour un gain en vitesse et en puissance consommée.

Figure 1.11: Schéma des structures transistors MOS sur Bulk et SOI partiellement et totalement dépeuplées [10].

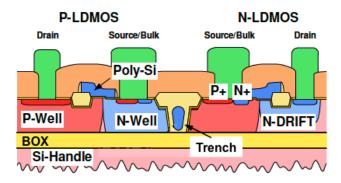

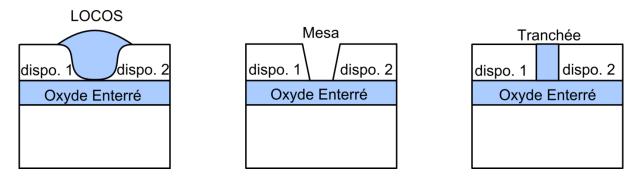

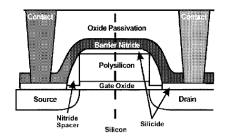

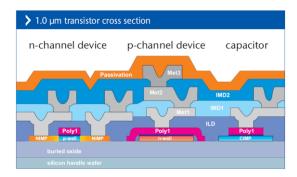

Il existe également, les technologies de type BCD (bipolar, CMOS, DMOS) où l'épaisseur de silicium actif est plus importante. L'épaisseur de silicium actif est choisi suivant le besoin de la haute tension [13][14]. Dans ce type de technologie il existe des structures basse et haute puissance, ainsi que des IGBT et des thyristors. La Figure 1.12 présente des structures électroniques de puissance réalisées en technologie BCD SOI.

Figure 1.12: Dispositifs électroniques réalisés en Technologie BCD SOI

### 1.2.4 Avantages de la technologie SOI

Depuis plusieurs années, les grandes industries microélectroniques commencent à utiliser la technologie SOI pour fabriquer leurs produits. Les avantages de cette technologie résultent en une grande amélioration des performances et de la durée de vie des composants dans plusieurs conditions. Nous allons passer en revue ci-après, les avantages de dispositifs sur substrat SOI.

#### 1.2.4.1 Haute fréquence

La fréquence de fonctionnement dans les circuits logiques dépend des temps de propagation ou des temps de commutation. Ces paramètres sont proportionnels à la capacité de sortie du transistor. Les capacités source/substrat (C<sub>JS</sub>) et drain / substrat (C<sub>JD</sub>) dans la technologie SOI sont 4 à 7 fois plus faibles que sur silicium massif (Figure 1.13). Tandis que sur silicium massif C<sub>JS</sub> (resp. C<sub>JD</sub>) équivaut à la capacité d'une jonction polarisée en inverse, dans le SOI C<sub>JS</sub> (resp. C<sub>JD</sub>) est dominée par la capacité de l'oxyde enterré sous la source (resp. le drain), qui est beaucoup plus faible. La réduction des capacités parasites se répercute au niveau du circuit et améliore les performances en hautes fréquences des SOI MOSFETs par rapport au silicium massif [15].

Figure 1.13: MOS à substrat SOI

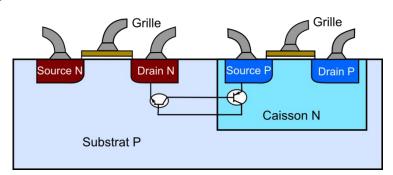

#### 1.2.4.2 Suppression du phénomène de latch-up

L'effet de latch-up est un phénomène qui induit le déclenchement du thyristor parasite représenté (Figure 1.14) par deux transistors bipolaires NPN et PNP dans les technologies CMOS sur substrat massif. Le déclenchement du latch-up est lié à la proximité des zones N<sup>+</sup> et P<sup>+</sup> de transistors NMOS et PMOS voisins. Sur le SOI, ces zones sont complètement isolées et le claquage entre ces deux zones est impossible quelle que soit la distance qui les sépare.

Figure 1.14: Présentation de l'effet de latch-up [16].

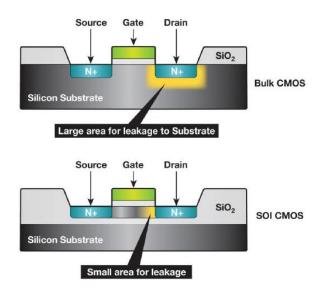

#### 1.2.4.3 Faible courant de fuite

Le courant de fuite associé aux jonctions drain/substrat et source/substrat est proportionnel à leur surface. Cette surface est diminuée en utilisant un substrat SOI car les jonctions planes de drain et de source sont éliminées à cause du contact avec l'oxyde enterré (Figure 1.15). Cette diminution du courant de fuite donne un avantage très important qui est la réduction de la consommation, qui constitue un avantage crucial pour les applications nomades et la durée de vie de la batterie.

Figure 1.15: Courant de fuite de drain et de source pour un MOS sur substrat massif et un MOS SOI [2]

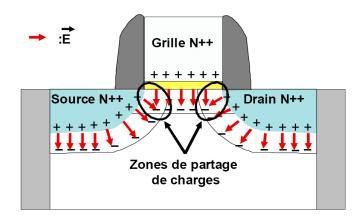

#### 1.2.4.4 Réduction de l'effet de canal court

La réduction de la longueur de grille et donc du canal est associé à des effets parasites, appelés effets de canal court (Short Channel effects), entraînant une perte de contrôle électrostatique de la grille sur le canal. Le phénomène qui en est principalement responsable, s'appelle le partage de charges (Drain Induced Barrier Lowering) [16].

Pour un transistor long, le potentiel le long du canal est quasiment constant sur l'ensemble de la longueur de grille. Plus la longueur du canal va diminuer, plus l'influence des extensions des zones de charge d'espace des régions source et drain va s'accroître, diminuant ainsi la zone contrôlée par la grille (Figure 1.16). C'est l'effet du partage de charges qui a pour effet de modifier le potentiel au centre du canal et ainsi d'abaisser la barrière de potentiel source/ canal/ drain. La tension de seuil  $V_T$  chutant ainsi de manière incontrôlée, on assiste à une augmentation du courant de fuite  $I_{OFF}$  du transistor.

Figure 1.16: Schéma montrant l'effet de partage de charges [17]

Dans la technologie SOI, l'influence des zones de charge d'espace des régions source et drain diminue, ce qui réduit leur impact sur le potentiel du centre du canal et par conséquent limite l'effet d'abaissement de la barrière de potentiel source/ canal/ drain, et donc l'effet de canal court.

#### 1.2.4.5 Augmentation de la densité d'intégration

La miniaturisation de tous les produits électroniques requiert la réduction des tailles des composants et l'accroissement de la densité d'intégration tout en gardant la même performance et la même durée de vie ou plus. L'utilisation d'un substrat SOI permet à la fois une isolation diélectrique verticale parfaite entre les différents composants (puissance, logique et analogique), grâce à la couche diélectrique enterrée et une densité d'intégration plus importante.

#### 1.2.4.6 Meilleure tenue aux radiations

Certaines applications comme l'aéronautique et l'espace sont soumises au rayonnement cosmique. Des forts flux de particules chargées engendrent des « photo-courants » dans les circuits intégrés. Par ailleurs, une particule unique très ionisante (proton ou ion) produit le long de sa trace un plasma conducteur (Figure 1.17) responsable d'effets isolés : claquages ou courts-circuits, tous deux destructifs ; basculement d'un point mémoire ou erreur dans un circuit logique, non destructifs mais entraînant des erreurs graves au niveau système.

Figure 1.17: Effet des irradiations (a) sur substrats massifs et (b) sur SOI [10].

Le durcissement [18] vis-à-vis de ces effets est obtenu principalement par la réduction du volume de silicium contenant les composants. L'utilisation de fines couches actives de silicium minimise l'impact des radiations ionisantes sur les performances des composants.

A noter que la technologie BCD, offre des avantages moins significatifs que les technologies de PDSOI et FDSOI, en particulier concernant la haute fréquence de fonctionnement, le faible courant de fuite et la réduction de l'effet de canal court. Par contre, les autres avantages cités sont valides pour toutes les structures de type SOI.

#### 1.2.5 Inconvénients de la technologie SOI.

La technologie SOI a beaucoup d'avantages, mais elle a aussi plusieurs inconvénients qui limitent son utilisation généralisée.

#### 1.2.5.1 Coût des plaquettes

Malgré les nouvelles techniques de fabrication performantes des plaquettes SOI, cette technologie reste plus chère par comparaison à celle sur substrat massif, car elle nécessite plus de matériau (wafer bonding) et plus d'étapes technologiques. A titre d'exemple, selon Virginia Semiconductor, le prix d'une plaquette SOI de 100 mm de diamètre, 400 µm d'épaisseur et dopée au bore est égal à 175 \$ par plaquette, alors que le prix d'une plaquette de silicium de 100 mm de diamètre, 500 µm d'épaisseur et dopée au bore varie entre 36 \$ et 80 \$ suivant la résistivité du silicium [19].

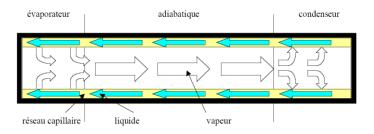

#### 1.2.5.2 Conductivité thermique

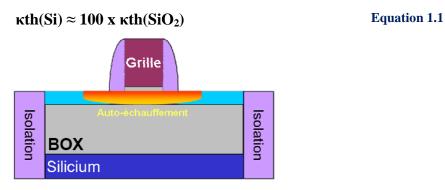

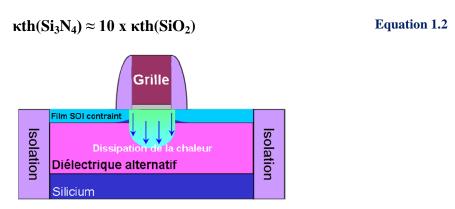

Dans l'utilisation d'un SOI, la présence de la couche d'oxyde enterrée empêche la dissipation thermique par la face arrière du substrat et peut alors poser un problème d'auto échauffement pour les composants de puissance. En effet, il y a une grande différence entre les conductivités thermiques du silicium et celle de l'oxyde [20].

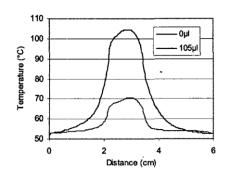

Figure 1.18: Auto échauffement dans un MOS sur substrat SOI à isolant SiO2 [20].

Une solution a été proposée par le CEA LETTI pour diminuer l'auto échauffement, qui est de remplacer l'oxyde de silicium par une couche de Si<sub>3</sub>N<sub>4</sub> qui a une conductivité thermique plus élevée que celle de l'oxyde de silicium [20].

Figure 1.19: Auto échauffement dans un MOS à substrat SOI à isolant Si3N4 [20]

# 1.3 Impact de la haute température sur les caractéristiques électriques des dispositifs électroniques

L'évolution de nombreuses applications vers le « tout électrique », comme par exemple, dans l'automobile avec le véhicule hybride, requiert de nouvelles architectures d'électronique de puissance pour répondre à ces nouvelles exigences : haute tension et haute température (200°C) liée à l'intégration mécatronique des modules de puissance.

L'élévation de la température a le même impact sur les caractéristiques électriques d'un transistor MOS à substrat SOI et massif (tension de seuil, mobilité, courant de fuite, vitesse de saturation) [21], mais avec des différences significatives comme nous allons le voir ci-après.

#### 1.3.1 Impact de la haute température sur la tension de seuil.

La tension de seuil pour un MOSFET à canal n (Bulk ou SOI), est donnée par [6]:

$$V_{TH} = \Phi_{MS} + 2\Phi_F - Q_{ox}/C_{ox} - Q_{dep}/C_{ox}$$

Equation 1.3

Avec  $\Phi_{MS}$ ,  $\Phi_{F}$ ,  $Q_{ox}$ ,  $Q_{dep}$  et  $C_{ox}$  le travail de sortie métal-semiconducteur, le potentiel de Fermi, la densité de charge dans l'oxyde de grille, la charge dépeuplée contrôlée par la grille et la capacité de l'oxyde de grille, respectivement.

Pour les dispositifs sur substrat massif ou PDSOI,  $Q_{dep} = q.Na.x_{dmax}$ , où  $x_{dmax}$  est la largeur maximale de la zone dépeuplée correspondant à la concentration de dopants  $N_a$ , qui est égale à  $\sqrt{\frac{4\varepsilon\Phi_F}{aNa}}$ .

Pour les dispositifs FDSOI,  $Q_{dep}$  a une valeur comprise entre q.Na. $t_{si}$  et q.Na. $t_{si}$ /2, avec q la charge de l'électron, Na la concentration de dopants et  $t_{si}$  l'épaisseur de la couche de silicium. Si on suppose que la grille est en polysilicium  $N^+$ , la valeur du travail de sortie est donnée par [6] :

$$\Phi_{MS} = -\frac{E_g}{2} - \Phi_F \quad Avec \quad \Phi_F = \frac{KT}{q} \ln(N_a/n_i)$$

Equation 1.4

La dépendance en température de la concentration intrinsèque de porteurs  $n_{\rm i}$ , est donnée par :

$$n_i = 3.9 \times 10^{16} T^{3/2} e^{-(Eg/2KT)}$$

Equation 1.5

Avec Eg, K et T l'énergie de bande interdite, la constante de Boltzmann et la température, respectivement. La dépendance de la tension de seuil avec la température peut être obtenue à partir des Equation 1.3 et Equation 1.5. Pour des raisons de simplification, on supposera que la charge  $Q_{ox}$  est indépendante de la température, et de même pour  $E_g$  sur la gamme de températures considérées.

Dans le cas d'un dispositif sur substrat massif ou PDSOI, la variation de la tension de seuil avec la température peut être décrite par la relation suivante.

$$\frac{dV_{TH}}{dT} = \frac{d\Phi_F}{dT} \left[ 1 + \frac{q}{C_{ox}} \sqrt{\frac{4\varepsilon_{Si} N_a}{KT \ln(Na/ni)}} \right]$$

Equation 1.6

Avec

$$\frac{d\Phi_F}{dT} = 8,63x10^{-5} \left[ \ln(N_a) - 38.2 - \frac{3}{2} \{1 + \ln(T)\} \right]$$

Equation 1.7

Dans le cas d'un dispositif FDSOI, la charge dépeuplée  $Q_{dep}$ , est égale à  $qN_at_{si}/n$ , où la valeur de n varie entre 1 et 2 et dépend de la charge de l'oxyde et de la condition de la

polarisation du substrat (back-gate bias condition). Si on suppose que n est indépendant de la température, la variation de la tension de seuil sera donnée par :

$$\frac{dV_{TH}}{dT} = \frac{d\Phi_F}{dT}$$

Equation 1.8

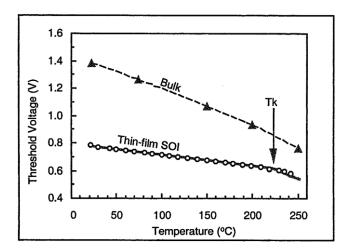

On peut remarquer par une simple comparaison entre Equation 1.6 et Equation 1.8 que  $dV_{TH}/dT$  est plus petit dans les dispositifs FDSOI que dans les dispositifs sur substrat massif et les dispositifs PDSOI. Le rapport entre la variation de la tension de seuil pour des dispositifs sur substrat massif et des dispositifs SOI minces est donné par le terme entre crochets de l'Equation 1.6 et il est typiquement entre 2 et 3, dépendant de l'épaisseur de l'oxyde de grille et de la concentration de dopants du canal. La valeur typique de  $dV_{TH}/dT$  varie entre -0,7 et -0,8 mV/K pour les MOSFETs FDSOI. Des valeurs de  $dV_{TH}/dT$  beaucoup plus grandes sont observées pour les dispositifs sur substrat massif ou PDSOI comme explicité au Tableau 1.1.

| $dV_{TH}/dT (mV/K)$                                                    | FDSOI<br>T=25°C | Bulk<br>T=25°C | FDSOI<br>T=200°C | Bulk<br>T=200°C |

|------------------------------------------------------------------------|-----------------|----------------|------------------|-----------------|

| $t_{ox} = 19 \text{ nm}$<br>Na=1,6x10 <sup>17</sup> cm <sup>-3</sup>   | -0,74           | -1,87          | -0,8             | -2,3            |

| $t_{ox} = 32.5 \text{ nm}$<br>Na = $1.2 \times 10^{17} \text{cm}^{-3}$ | -0,76           | -2,42          | -0,82            | -3,05           |

Tableau 1.1:  $dV_{TH}/dT$  (en mV/K), pour les MOSFETs Bulk et SOI (tsi = 100nm). Les données sont présentées pour 2 températures (25 et 200° C) et pour 2 valeurs d'épaisseur d'oxyde  $t_{ox}$  et de concentration de dopants Na [6].

Quand la température augmente dans un dispositif à film mince, la concentration des porteurs intrinsèques  $n_i$  augmente et  $\Phi_F$  diminue. Cela donne lieu à une diminution de la zone dépeuplée maximale, de manière que les dispositifs ne se comportent plus totalement comme des dispositifs FDSOI au dessus de la température critique  $T_k$ . A cette température,  $x_{dmax}$  devient plus petit que  $t_{si,eff}$ , où  $t_{si,eff}$  est l'épaisseur électrique d'un film, c'est-à-dire l'épaisseur du film de silicium moins la zone dépeuplée. Au dessus de  $T_k$ , le transistor se comporte comme un MOSFET SOI à film épais (Figure 1.20). On peut noter sur cette figure que le changement de comportement se produit à une température supérieure à  $200^{\circ}$ C.

Figure 1.20: Variation de la tension de seuil d'un MOSFET Bulk et FDSOI à canal n avec la température [6].

#### 1.3.2 Courant de fuite à haute température

L'augmentation du courant de fuite des jonctions est l'une des principales causes de l'échec des circuits fonctionnant à haute température. Le courant de fuite de jonction est proportionnel à la surface de jonction. La plus forte composante d'un courant de fuite de CMOS sur substrat massif à haute température, provient de la jonction plane [6]. Le courant de fuite de polarisation inverse  $N^+/P$  a pour expression :

$$I_{leak} = qA \left(\frac{D_n}{\tau_n}\right)^{\frac{1}{2}} \frac{ni^2}{N_a} + qA \frac{n_i W}{\tau_e}$$

Equation 1.9

Avec q la charge de l'électron, A la surface de la jonction,  $D_n$  le coefficient de diffusion des électrons,  $\tau_n$  la durée de vie de l'électron dans le silicium neutre de type P, W la largeur de la zone dépeuplée et  $\tau_e = (\tau_n + \tau_p)/2$  la durée de vie effective liée au processus de génération thermique dans la zone dépeuplée.

Le premier terme dans l'Equation 1.9 (courant de diffusion) est proportionnel à  $n_i^2$  et le deuxième terme de l'Equation 1.9 (courant de génération) est proportionnel à  $n_i$ . Il est expérimentalement observé [6] que le courant de fuite d'un MOSFET SOI et de diodes polarisées en inverse est proportionnel à  $n_i$  pour des températures inférieures à 100-150°C et proportionnel à  $n_i^2$  au dessus de ces températures [6], [22]. Il est intéressant de noter que la surface de la jonction A et A.W le volume de la région de charge d'espace associés à cette diode sont beaucoup plus petits pour les dispositifs SOI que pour les dispositifs sur substrat massif.

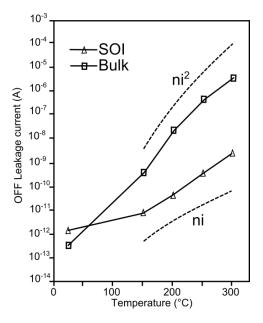

Figure 1.21: Courant de fuite dans des transistors à canal n de même géométrie sur substrats SOI et massif, en fonction de la température [6]

Les courants de fuite pour  $V_{DS} = 5V$  pour les transistors sur substrats massif et SOI à canal n de mêmes géométries sont comparés sur la Figure 1.21. A température ambiante, le courant de fuite pour le SOI est un peu plus grand que celui sur substrat massif. A haute

température, le courant de fuite des dispositifs SOI est plus petit de trois ordres de grandeur par rapport à celui des dispositifs sur substrat massif.

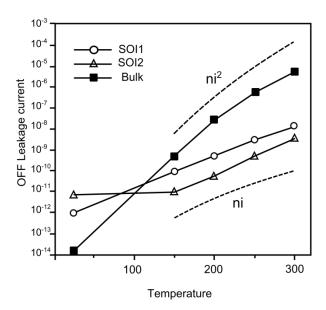

La Figure 1.22 [23] présente la variation du courant de fuite en fonction de la température pour différentes géométries de dispositifs p-MOS sur substrat massif et SOI. On peut noter la proportionnalité du courant de fuite à  $n_i$  pour les 2 géométries SOI et à  $n_i^2$  pour le dispositif sur substrat massif.

Figure 1.22: Courant de fuite en fonction de la température des dispositifs SOI1 (W/L =  $20\mu$ m/5 $\mu$ m) et SOI2 (W/L =  $3\mu$ m/3 $\mu$ m) pour des transistors p-MOS SOI avec une polarisation de zéro pour le substrat et -3 V pour le drain et d'un transistor p-MOS sur substrat massif (W/L =  $20\mu$ m/5) avec une polarisation de -3V pour le drain et 0V pour le substrat [21].

Si on développe l'expression du courant de diffusion pour le transistor n-MOS on obtient [24]:

$$I_{diff} = q.Z.\sqrt{\frac{D_n}{\tau_{rn}}} \left(1 - e^{\frac{-qV_D}{kT}}\right) \int_0^{d_{Si}} \frac{n_i^2}{N_a} e^{\frac{q.\phi(x,T)}{kT}} dx$$

Equation 1.10

Où  $D_n$  et  $D_p$  sont les constantes de diffusion des électrons et des trous, Z est la largeur du dispositif,  $\tau_{rn}$  est la durée de vie de recombinaison des électrons et des trous respectivement.  $\phi(x,T)$  représente la distribution de potentiel aux bornes du film de silicium. Pour le transistor PMOS, on a la même équation mais en remplaçant  $N_d$  par  $N_a$ ,  $D_n$  par  $D_p$  et  $\tau_{rp}$  par  $\tau_{rn}$ .

De même pour le courant de génération l'expression devient :

$$I_{gen} = q.d_{si}.Z.\frac{n_i}{\tau_g} \left\{ \sqrt{\frac{2.\varepsilon_s.K.T}{q^2.N_a}} \left[ \sqrt{\ln\left(\frac{N_a}{n_i}\right) + \frac{q.V_D}{K.T}} - \sqrt{\ln\left(\frac{N_A}{n_i}\right)} \right] \right\}$$

Equation 1.11

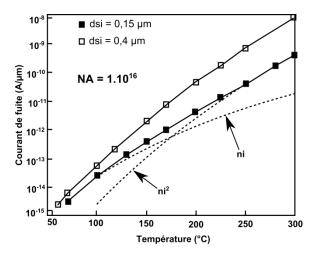

Avec  $d_{si}$ , l'épaisseur du film de silicium,  $\tau_g$  la durée de vie de génération. Donc l'épaisseur du film de silicium joue un rôle dans la variation du courant de fuite. La Figure

1.23 présente la dépendance du courant de fuite avec la température mesurée dans des dispositifs SOI pour différentes épaisseurs de film de silicium.

Figure 1.23: Dépendance en température du courant de fuite des MOSFETs SOI pour plusieurs valeurs de l'épaisseur du film de silicium à  $V_{DS}$  = 3V et  $V_{GS}$  =0 [24]

Sur cette figure (Figure 1.23), on peut voir que le courant de fuite du dispositif qui a une épaisseur de film égale à  $0.15\mu m$ , est proportionnel à  $n_i(T)$  en dessous de  $150^{\circ}C$ , ce qui démontre que le courant de génération est le courant dominant. A haute température, le courant de fuite varie comme  $n_i^2(T)$ , ce qui démontre que le courant de diffusion est dominant. Dans le dispositif de  $0.4\mu m$  d'épaisseur de film, le courant de diffusion devient dominant à partir de  $100^{\circ}C$ , donc plus l'épaisseur du film de silicium augmente plus le comportement du dispositif SOI devient proche de celui sur substrat massif.

A haute température, l'augmentation de la longueur du canal du transistor permet de diminuer le courant de fuite [25]. En effet, la longueur du canal a un effet direct sur le gain du transistor bipolaire parasite. En augmentant cette longueur, le gain en courant diminue, et par suite, le courant de fuite diminue.

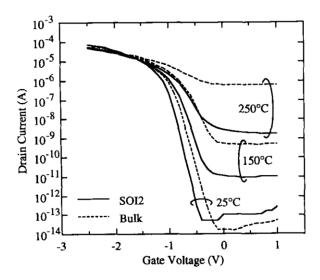

# 1.3.3 Fonctionnement en logique (I<sub>ON</sub>/I<sub>OFF</sub>)

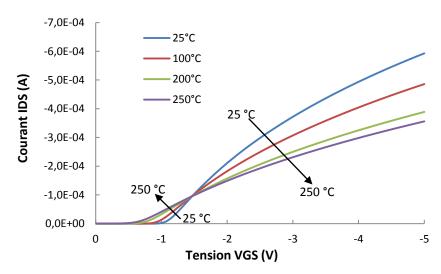

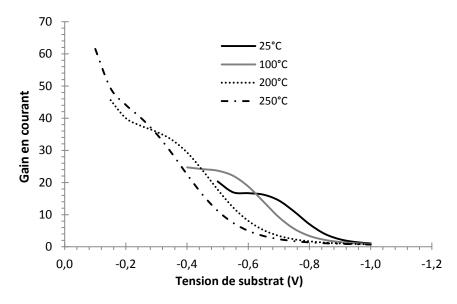

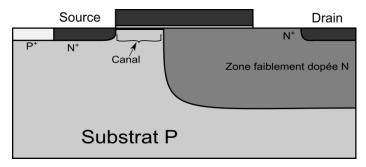

La température de fonctionnement étant la même pour tous les circuits, les circuits numériques seront également exposés. Pour maintenir un fonctionnement logique normal, il faut que le rapport de  $I_{ON}/I_{OFF}$  soit le plus grand possible. La Figure 1.24 présente le courant de drain en fonction de la tension de grille en mode d'accumulation pour un MOSFET SOI à canal p et pour différentes températures de fonctionnement. Des mesures faites par [24] montrent que des rapports  $I_{ON}/I_{OFF}$  égaux à 100 000 à 200°C et 300 à 300°C. Ces valeurs montrent que les circuits SOI restent fonctionnels même à haute température. Par comparaison, le rapport  $I_{ON}/I_{OFF}$  pour un transistor sur substrat massif est de l'ordre de 40 à 250°C, alors qu'il est de l'ordre de 5000 pour un transistor SOI, Figure 1.24.

Figure 1.24: Courant de drain en fonction de la tension de grille pour un transistor p-MOS sur substrat massif et SOI, de même géométrie (W=  $20\mu m$  et L =  $5\mu m$ ) pour différentes températures et pour  $V_{DS}$  = -3V [24].

La différence de rapport  $I_{ON}/I_{OFF}$  entre la technologie sur substrat massif et SOI montre le grand avantage de l'utilisation de la technologie SOI par rapport au substrat massif. De plus, à technologie comparable, l'aire de jonction de drain et de source est beaucoup plus petite dans les dispositifs SOI que dans les dispositifs massifs, d'un facteur allant de 15 à 100 (selon les règles de conception). Ces caractéristiques peuvent aider à une réduction drastique du courant de consommation à l'état off d'un circuit SOI par rapport à une technologie sur substrat massif.

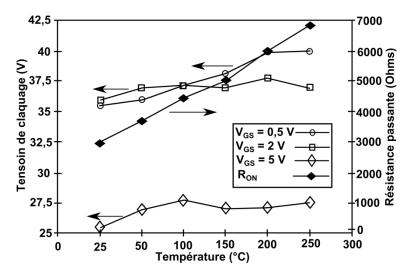

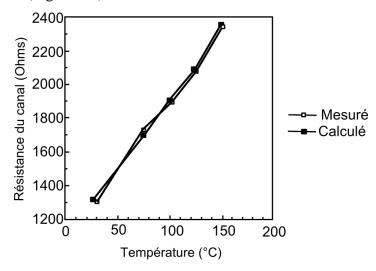

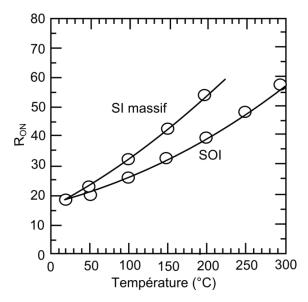

## 1.3.4 Tension de claquage et R<sub>ON</sub>

Les paramètres des composants de puissance, comme la résistance à l'état passant et la tension de claquage, sont également sensibles à la température. Des mesures de tension de claquage de jonction ont été faites sur un LDMOS SOI de largeur de grille de  $10\mu m$  et de longueur effective de  $1\mu m$  [26]. La tension de claquage diminue linéairement avec la tension de grille et chute ainsi à 25 V pour  $V_{GS}=5V$ .

Comme le montre la Figure 1.25, pour une tension de grille de 5V, la tension de claquage augmente de 25,5V à 27,5V à 100°C et ensuite se stabilise à 28 V jusqu'à 250°C à partir de laquelle le LDMOS ne fonctionne plus correctement à cause d'un important courant de fuite. La Figure 1.25 montre aussi l'évolution de la tension de claquage en fonction de la température pour  $V_{GS}=0,5V$  et 2V. Dans ce cas, on peut noter que pour  $V_{GS}=0,5V$ , la variation de la tension de claquage est bien plus importante : elle est proche de 5V, c'est-à-dire proche de 15% de la valeur à température ambiante. Dans le cas du LDMOS, cette propriété lui confère donc une meilleure tenue en tension, ce qui peut être un avantage.

Figure 1.25 : Tension de claquage pour  $V_{GS}$  = 0.5V, 2V et 5V. Et la résistance dans le cas passant en fonction de la température d'un transistor LDMOS [26]

La Figure 1.25 montre également que la résistance à l'état passant de ce même MOS augmente linéairement en fonction de la température de 3 k $\Omega$  à 27°C jusqu'à 7 k $\Omega$  à 250 °C. L'augmentation de la résistance implique une augmentation de la chute de tension et donc de la puissance consommée d'un dispositif.

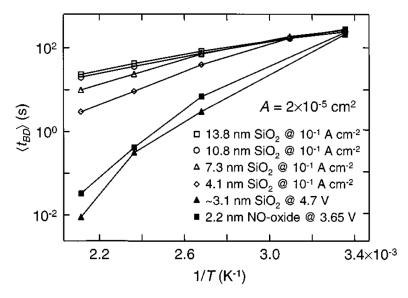

### 1.3.5 Fiabilité de l'oxyde de grille

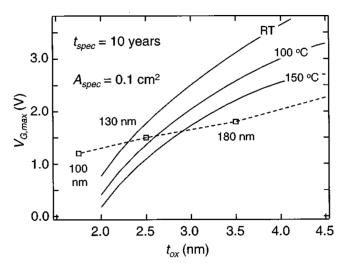

Le claquage de l'oxyde de grille soumis à un stress électrique durant le fonctionnement du dispositif, est considéré comme l'obstacle principal pour la réduction des dimensions des circuits intégrés [27]. En effet, le temps jusqu'au claquage ou t<sub>BD</sub> (Time to breakdown) de la couche d'oxyde SiO<sub>2</sub> diminue avec la diminution de l'épaisseur de la couche d'oxyde nécessaire pour la réduction des tailles des dispositifs. On caractérise les oxydes par le temps t<sub>BD</sub> nécessaire pour arriver au claquage en présence d'une tension constante.

L'élévation de la température accélère le claquage de l'oxyde de grille. Des études ont montré l'effet de l'élévation de la température sur le temps de claquage de l'oxyde. L'épaisseur de l'oxyde utilisé dans cette étude varie entre 2,2 et 13,8 nm et le temps de claquage  $t_{BD}$  (Time to breakdown) est déterminé à partir de la première discontinuité de la densité du courant.

La Figure 1.26 [27] présente la variation du temps de claquage en fonction de la température pour différentes épaisseurs d'oxyde. L'effet de la haute température sur l'oxyde mince est beaucoup plus dramatique, car il est bien plus important (4 décades) que pour un oxyde épais (1 décade).

Figure 1.26: L'effet de la haute température sur t<sub>BD</sub> pour différentes épaisseurs d'oxyde [27]

A température ambiante et lors de tests de l'oxyde sous tension constante, on montre que le  $t_{BD}$  est proportionnel à l'exponentielle de  $1/E_{ox}$  [28].

$$t_{BD} = \tau_0 \exp\left[\frac{G}{E_{ox}}\right] = \tau_0 \exp\left[\frac{GX_{ox}}{V_{ox}}\right]$$

Equation 1.12

Où  $E_{ox}$  est le champ électrique dans l'oxyde,  $X_{ox}$  est l'épaisseur de l'oxyde,  $V_{ox}$  est la tension aux bornes de l'oxyde et G (350 MV/cm) et  $\tau_0$  (1 x  $10^{-11}$  s) sont la pente et l'intersection avec l'axe des x, du graphe de ln ( $t_{BD}$ ) en fonction de  $1/E_{ox}$ , respectivement. Les mécanismes physiques associés sont la localisation de pièges à l'interface  $Si/SiO_2$  et un changement localisé de la structure chimique ayant pour effet de réduire la barrière de potentiel. L'épaisseur de l'oxyde sera donc moins épaisse,  $X_{ox}$  sera remplacé par  $X_{eff}$  qui présente l'épaisseur effective de l'oxyde et l'expression du temps de claquage de l'oxyde  $t_{BD}$  sera :

$$t_{BD} = \tau_0 \exp \left[ \frac{GX_{eff}}{V_{ox}} \right]$$

Equation 1.13

L'expression générale de la dépendance en température de  $t_{BD}$  est obtenue par l'introduction du paramètre T dans l'expression de G et  $\tau_0$  avec  $E_b$  l'énergie d'activation.

$$\tau_0(T) = \tau_0 \exp\left(\frac{-E_b}{k} \left\lceil \frac{1}{T} - \frac{1}{300} \right\rceil\right)$$

Equation 1.14

Avec k la constante de Boltzman en eV/K et les expressions de G(T) et  $\delta$  sont les suivantes :

$$G(T) = G\left(1 + \frac{\delta}{k} \left\lceil \frac{1}{T} - \frac{1}{300} \right\rceil\right)$$

Equation 1.15

$$\delta \equiv \frac{k}{G} \frac{dG(T)}{d(1/T)}$$

Equation 1.16

L'expression générale de t<sub>bd</sub> en fonction de la température devient [28] :

$$t_{BD}(T) = \tau_0 \exp \left\{ \frac{GX_{eff}}{V_{ox}} \left( 1 + \frac{\delta}{k} \left[ \frac{1}{T} - \frac{1}{300} \right] \right) - \frac{E_b}{k} \left[ \frac{1}{T} - \frac{1}{300} \right] \right\}$$

Equation 1.17

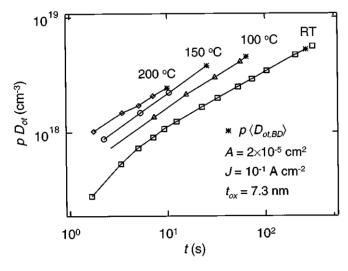

Le temps de claquage dépend donc de la concentration de défauts dans la couche d'oxyde et cette concentration augmente avec l'augmentation de la température pour le même temps de stress comme la Figure 1.27 [27] l'indique. Selon cette figure, on peut remarquer, qu'à haute température, la concentration de défauts nécessaire pour que l'oxyde de grille claque, est plus faible qu'à basse température (presque une décade entre la température ambiante (RT) et 200°C).

Figure 1.27 : Construction de défauts en fonction de temps de claquage de l'oxyde de grille pour différentes températures et pour tox = 7,3nm (RT = Room temperature) [27]

# 1.4 Impact sur le comportement de structures de protection contre les ESD

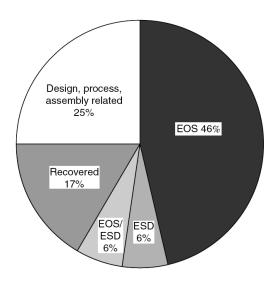

Le nombre de défaillances attribué aux phénomènes de décharges électrostatiques est aujourd'hui considérable, il est donc incontournable pour un fondeur de qualifier le niveau de protection des circuits et cela pour les différents types de décharges électrostatiques. Trois modèles de décharges électrostatiques associés à trois formes d'ondes caractéristiques sont à considérer [29]:

Les décharges électrostatiques induites par le contact humain (HBM : Human Body Model) [30].

- Les décharges électrostatiques produites au contact d'une machine (bras robotisé)

(MM : Machine Model) [31].

- Les décharges électrostatiques créées lors de la mise à la masse du circuit après qu'il ait fait l'objet d'une accumulation de charges (CDM Charged Device Model) [32].

Ces trois modèles de décharges électrostatiques sont associés à des procédures de test normalisées permettant la qualification d'un produit en vue de connaître sa robustesse ESD. Ainsi, un circuit peut être robuste vis-à-vis des décharges électrostatiques induites par contact humain sans pour autant résister à une décharge rapide se produisant lors de la mise à la masse du circuit préalablement chargé.

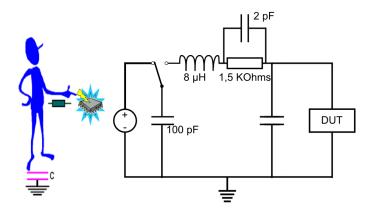

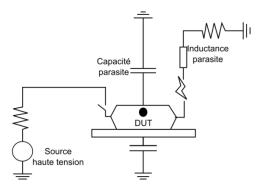

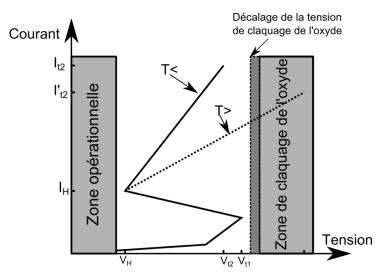

L'origine des décharges électrostatiques est aujourd'hui bien connue et est de manière générale assimilée à un événement bref pouvant fournir un courant élevé sur une durée n'excédant pas 200 ns. Le niveau de courant, la durée et la rapidité de l'onde dépendent de plusieurs facteurs comme l'impédance et l'inductance de la ligne de propagation de la décharge.

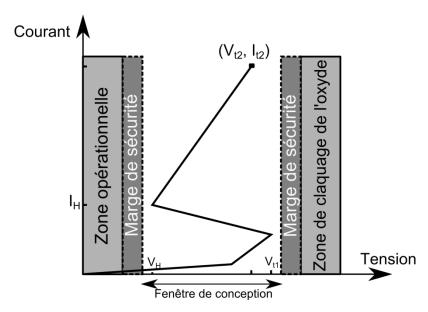

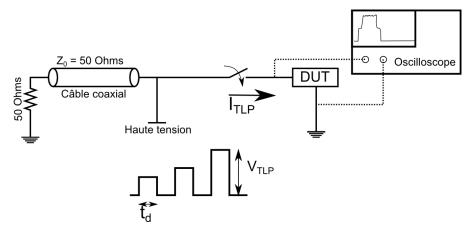

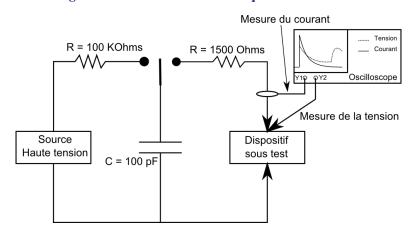

La caractérisation TLP (Transmission Line Pulses) [33], [34] est utilisée pour déterminer l'efficacité d'une structure de protection par rapport à son niveau de robustesse et à sa faculté à protéger un circuit. En effet, la forme d'onde HBM en courant (double exponentielle) permet difficilement de mettre en évidence le fonctionnement à fort courant de la protection. L'introduction de générateurs d'impulsions carrées a facilité le développement et l'analyse du niveau de performance d'une protection ESD. Le principe du banc de caractérisation TLP consiste à appliquer successivement des impulsions carrées en incrémentant le niveau de tension. Pour chaque niveau de tension, la réponse en courant de la structure est mesurée. La courbe I/V de sortie associée à une mesure du courant de fuite après chaque impulsion correspond à la signature de conduction de la protection en régime ESD. La Figure 1.28 illustre un exemple de résultat de caractérisation TLP pouvant être attribué à une protection efficace. Une protection ESD est définie comme efficace lorsqu'elle respecte la fenêtre de conception ESD. En effet, cette fenêtre est définie par un niveau bas, en dessous duquel la protection ne doit pas se déclencher, qui est imposé par le régime de fonctionnement du circuit à protéger et par un niveau haut à ne pas dépasser, défini comme la tension maximale au delà de laquelle se produiraient des défaillances irréversibles des transistors à protéger. Cette figure illustre le cas d'une protection se déclenchant à une tension V<sub>t</sub>, puis se repliant sur une tension de maintien V<sub>h</sub> et enfin présentant une défaillance au point (V<sub>t2</sub>, I<sub>t2</sub>).

Figure 1.28 : Fenêtre de conception pour une protection ESD.

#### 1.4.1 Principaux éléments de protection ESD

Afin de protéger les dispositifs ou les circuits électroniques contre les décharges électrostatiques, une structure de protection ESD doit résister elle-même à la décharge contre laquelle elle est supposée protéger. Elle doit donc être capable de supporter des champs électriques intenses et dissiper de très fortes densités d'énergie. Les principes de fonctionnement à fort courant sous les conditions ESD sont similaires aux composants semi-conducteurs de puissance [35]. La structure doit se comporter comme un interrupteur ouvert durant le fonctionnement normal du dispositif à protéger et comme un interrupteur fermé lors d'une décharge électrostatique c'est-à-dire, lorsque la tension aux bornes du circuit est plus grande que la tension d'alimentation (VDD). Par ailleurs, il faut que ces structures se déclenchent très rapidement, sinon, il y a risque de détruire le composant à protéger avant que la structure de protection ne se déclenche. Plusieurs composants électroniques peuvent jouer ce rôle de protection comme les diodes, les bipolaires, les MOS et les thyristors.

#### **1.4.1.1** Les diodes

Les diodes sont caractérisées par leur faible résistance à l'état passant entre  $20~\Omega/\mu m$  et  $100~\Omega/\mu m$  [36]. Leur faible tension de déclenchement peut être résolue par la mise en série de plusieurs diodes. Une autre solution pour résoudre le problème de la faible tension de déclenchement, est d'utiliser la diode en inverse en profitant du phénomène d'avalanche, dont la tension varie selon le dopage des régions N et P, et pour les structures submicroniques il est aux alentours de 10~V [36]. La tension de déclenchement de la série de diodes ou de la diode Zener doit être supérieure à la tension d'alimentation du circuit à protéger et avoir une robustesse importante capable de supporter et d'absorber la puissance appliquée par cette décharge électrostatique.

Les diodes sont également, largement utilisées en direct dans le cadre de stratégie de protection centralisée. Une protection centrale placée entre  $V_{DD}$  et  $V_{SS}$  est dimensionnée pour absorber toutes les décharges sur l'ensemble des entrées-sorties. La décharge est renvoyée sur

cette protection centrale à l'aide de diodes en direct. L'avantage est que la diode peut être de taille relativement faible.

#### 1.4.1.2 Les transistors bipolaires

Un transistor bipolaire en fonctionnement normal a une jonction polarisée en direct, la jonction base-émetteur, qui permet aux porteurs minoritaires d'être injectés au voisinage d'une jonction polarisée en inverse, la jonction base-collecteur [36]. Le transistor bipolaire est passant lorsque sa tension  $V_{\rm BE}$  est de l'ordre de 0,6 V.

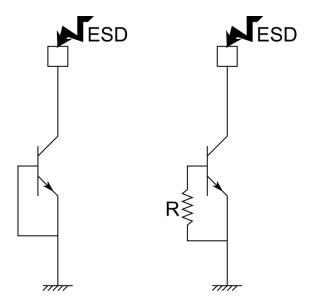

Pour un fonctionnement en structure de protection contre les décharges électrostatiques, le transistor bipolaire NPN a sa base reliée à l'émetteur soit directement par un court-circuit soit par une résistance. Lorsqu'il y a une décharge positive appliquée au collecteur, et puisque dans ce cas la tension V<sub>BE</sub> est nulle, c'est au départ le courant de fuite de la jonction collecteur-base qui circule dans ce bipolaire, et en particulier, dans la base. Ce courant circule sur la résistance intrinsèque de la base si le montage est en court-circuit ou sur la résistance externe (Figure 1.29). Lorsque la chute de tension, dans la base (dans le cas où la base et l'émetteur sont en court-circuit), ou aux bornes de la résistance (dans le cas où la base et l'émetteur sont reliés par une résistance), atteint la tension de seuil de la jonction base-émetteur, le transistor se déclenche. Après ce déclenchement, il y a une chute de résistance du bipolaire et par suite une chute de la tension, ce qui explique le repliement observé sur les caractéristiques TLP.

Figure 1.29: Utilisation des bipolaires en protection ESD

#### 1.4.1.3 Les transistors MOS

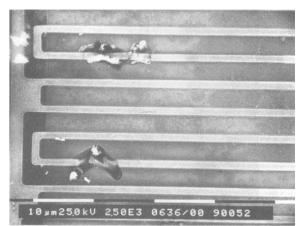

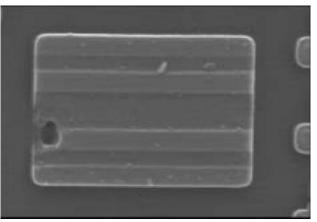

Le DMOS latéral (LDMOS) est un transistor de puissance qui est couramment utilisé dans la conception des circuits haute tension. Cependant, de très grand dispositifs (W > 10 K  $\mu$ m) peuvent être robustes mais prennent beaucoup de place. Des dispositifs plus petits (W < 5K  $\mu$ m) utilisés dans certaines applications présentent des problèmes de robustesse ESD. Ainsi l'obtention d'une robustesse de 2 kV peut être difficile [37].

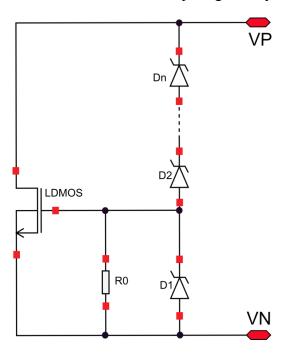

L'utilisation de LDMOS dans une protection centrale comme structure principale qui absorbe l'impulsion ESD est présentée dans la Figure 1.30. En effet, les diodes Zener servent à assurer le déclenchement du LDMOS avec une différence de potentiel compatible avec la fenêtre de conception ESD. La diode Zener D1 sert à protéger l'oxyde de grille du LDMOS.

Figure 1.30: LDMOS dans protection ESD centralisée

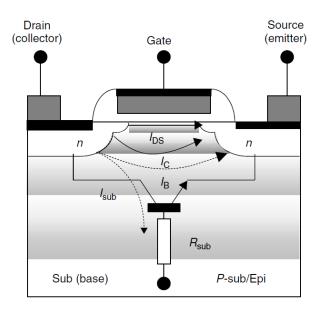

Il est également possible d'utiliser les transistors MOS comme structure de protection en montage GGMOS (grounded gate MOS) ou MOS avec grille reliée à la masse). Dans cette configuration et dans le cas d'un stress ESD, c'est le transistor bipolaire parasite du MOS qui se déclenche et sert à absorber la décharge électrostatique (voir Figure 1.31).

Figure 1.31: Vue en coupe d'un transistor NMOS montrant le bipolaire latéral parasite npn et les courants associés [36]

## 1.4.2 Protection ESD à haute température

Les travaux qui parlent de l'effet de la température sur les protections ESD sont rares [38–40]. Cependant, à haute température, les quatre paramètres, tension de déclenchement  $(V_t)$ , tension de maintien  $(V_h)$ , courant de maintien et résistance à l'état passant, peuvent varier significativement et ne plus être compatibles avec la fenêtre de conception ESD. Si  $V_t$  augmente et devient plus grand que la tension de claquage de l'oxyde ou de la défaillance de la structure à protéger, la décharge électrostatique pourrait détruire le dispositif. Le même problème peut survenir avec l'augmentation de la résistance passante de la structure de protection avec la température. Si  $V_h$  diminue et se situe dans le domaine de fonctionnement de dispositif, alors le circuit de protection risque de se déclencher pendant le fonctionnement normal du circuit, et induire des dysfonctionnements.

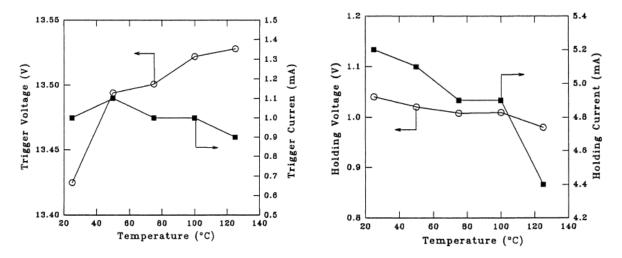

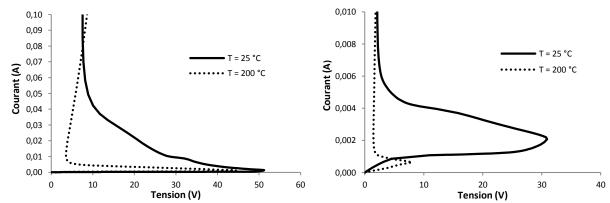

Dans le cas où le circuit de protection est de type SCR, les tensions  $V_h$  et  $V_t$  diminuent avec l'augmentation de la température. Jung [38] a démontré la diminution de  $V_h$  pour les différents types de circuits de protection SCR, DCTSCR (diode-chain triggering SCR), ZDSCR (low-voltage zener diode trigger SCR), LVTSCR (low-voltage trigger SCR) et GCSCR (gate-coupled low-voltage trigger SCR [41]). La diminution de la tension  $V_h$  est de l'ordre de 0,3V en passant de 25°C à 130°C. Jung a montré aussi que le problème de la diminution de  $V_t$  est résolu dans les deux derniers types de SCR. Dans les structures LVTSCR et GCSCR,  $V_t$  augmente avec l'augmentation de la température et dans ce cas, la protection ESD respecte la fenêtre de conception ESD. La Figure 1.32.a et Figure 1.32.b présentent l'augmentation de la tension  $V_t$  avec l'augmentation de la température et diminution de la tension  $V_h$ , avec l'augmentation de la température pour la protection LVTSCR.

Figure 1.32: Tension de déclenchement (a) et tension de maintien en fonction de la température pour une protection LVTSCR (b) [38].

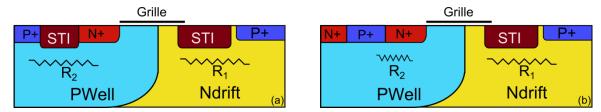

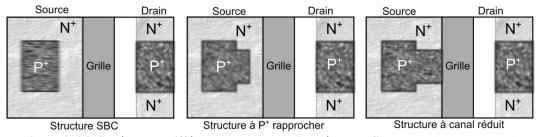

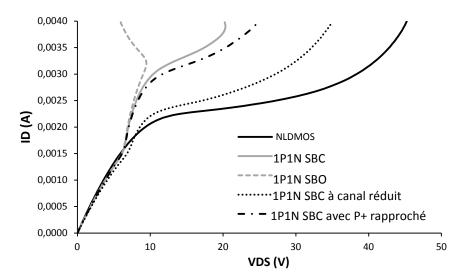

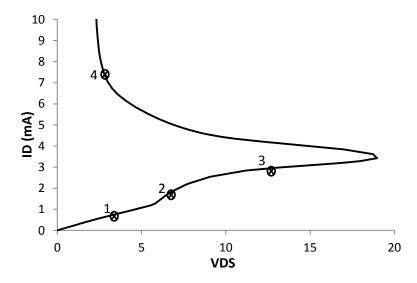

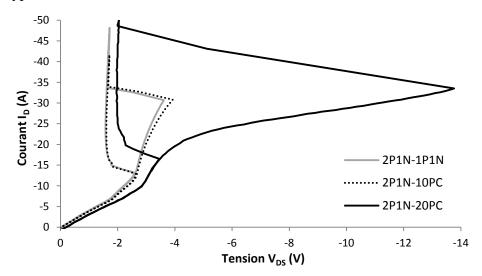

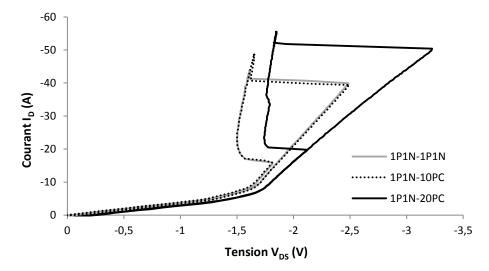

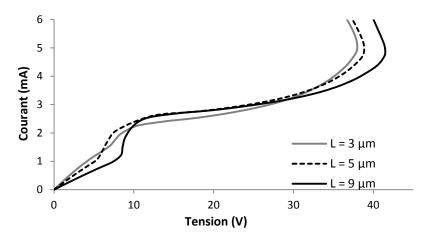

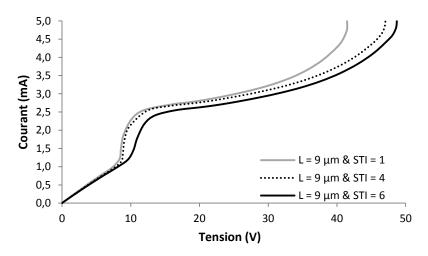

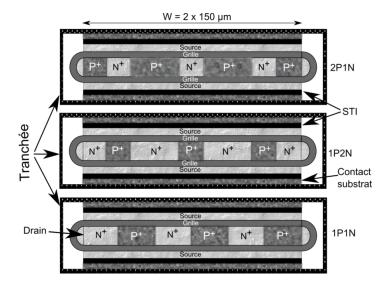

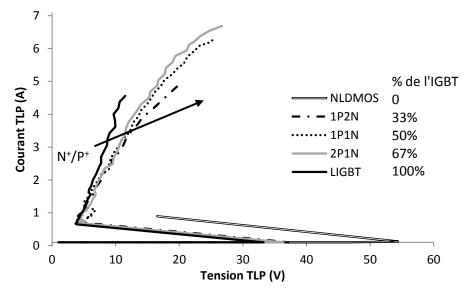

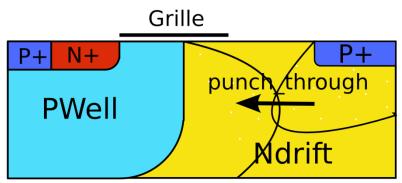

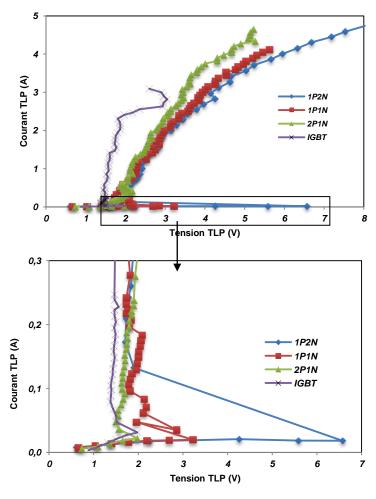

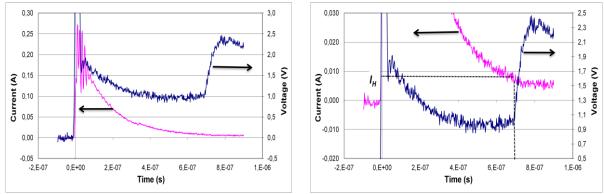

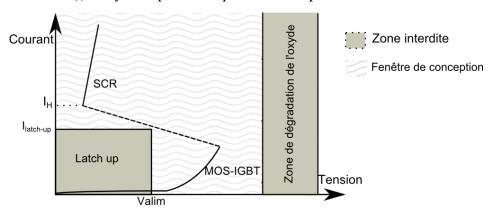

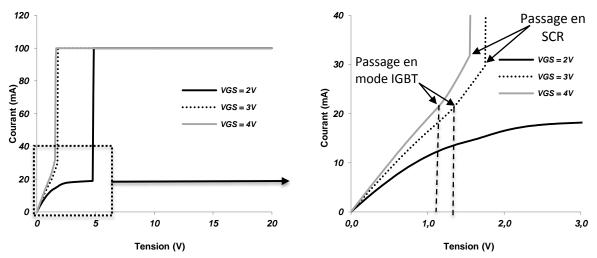

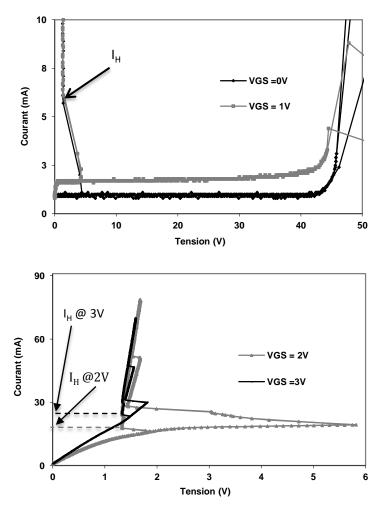

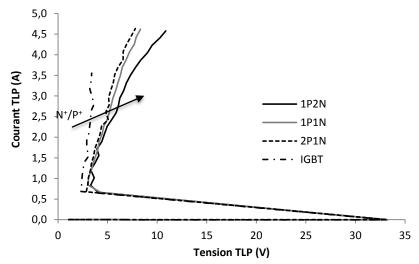

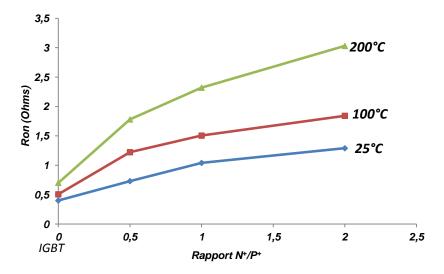

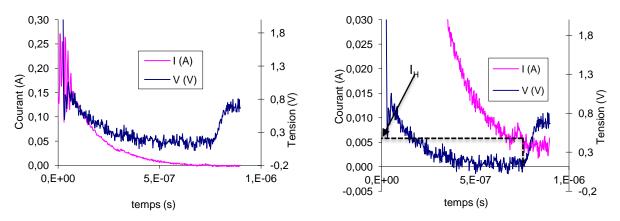

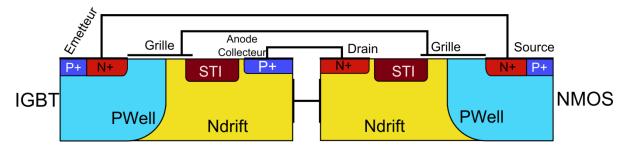

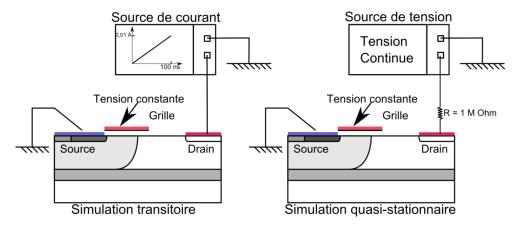

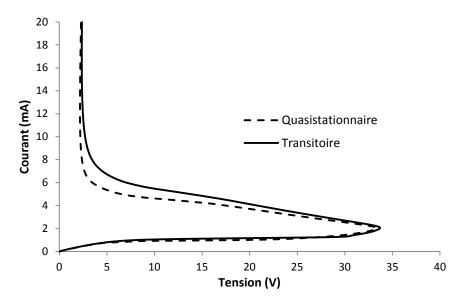

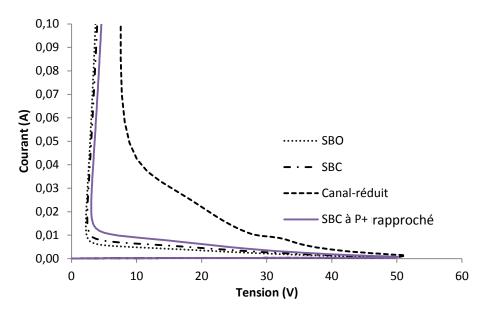

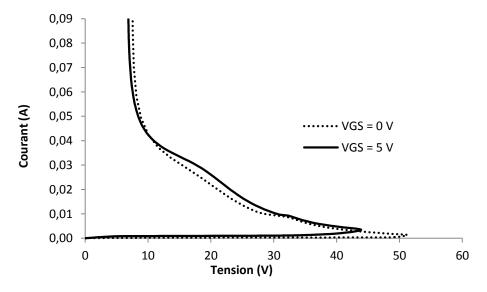

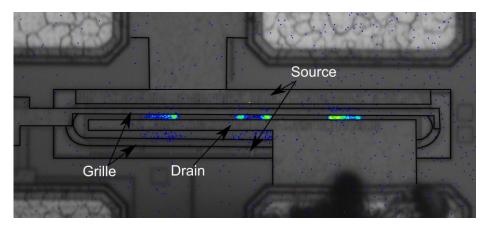

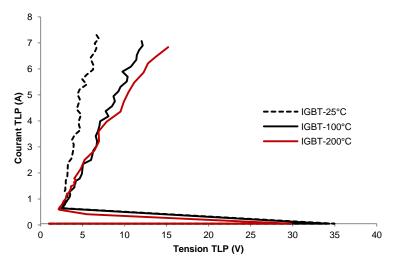

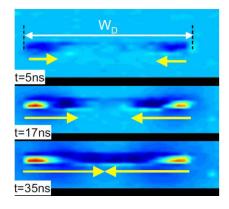

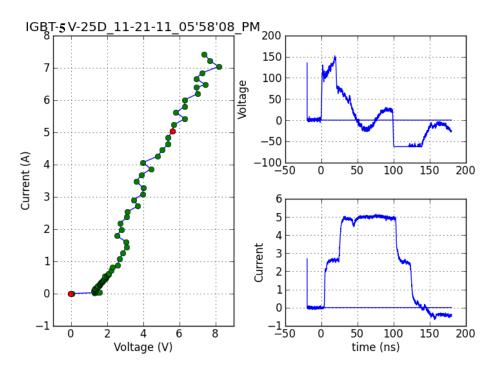

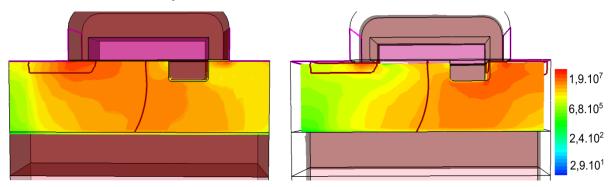

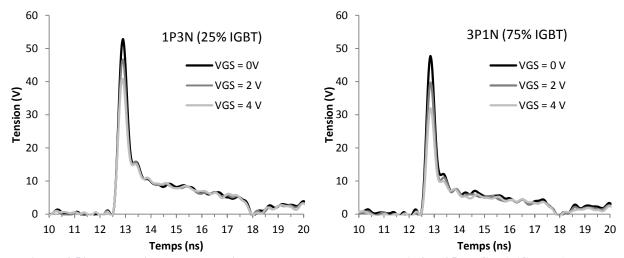

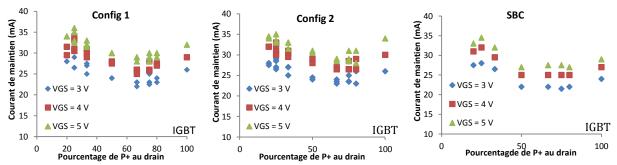

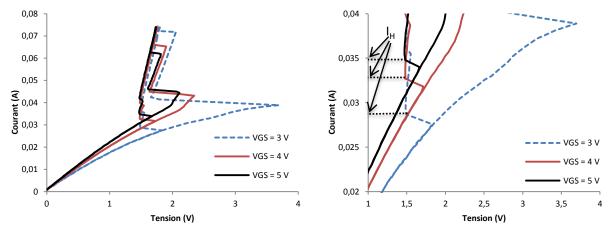

# 1.5 Composants de puissance sur SOI