# Adapting the Polytope Model for Dynamic and Speculative Parallelization

Alexandra Jimborean

#### ▶ To cite this version:

Alexandra Jimborean. Adapting the Polytope Model for Dynamic and Speculative Parallelization. Hardware Architecture [cs.AR]. Université de Strasbourg, 2012. English. NNT: tel-00733850v1

## HAL Id: tel-00733850

https://theses.hal.science/tel-00733850v1

Submitted on 19 Sep 2012 (v1), last revised 8 Nov 2012 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N° d'ordre:

# École Doctorale Mathématiques, Sciences de l'Information et de l'Ingénieur

### UdS - INSA - ENGEES

## **THÈSE**

présentée pour obtenir le grade de

## Docteur de l'Université de Strasbourg

Discipline: Informatique

par

## Alexandra Jimborean

# Adapting the Polytope Model for Dynamic and Speculative Parallelization

Soutenue publiquement le 14 Septembre 2012

#### Membres du jury:

Directeur de thèse: Philippe Clauss, Professeur, UdS, Strasbourg

Co-encadrant : Vincent Loechner, Maître de conférences , UdS, Strasbourg

Rapporteur : Albert Cohen, Directeur de Recherche, INRIA - ENS, Paris

Rapporteur : André Seznec, Directeur de Recherche, INRIA - IRISA, Rennes

Rapporteur: John Cavazos, Professeur, University of Delaware, USA

Examinateur : François Bodin, Directeur technique, CAPS Enterprise, Rennes Examinateur : Jean Christophe Beyler, Ingénieur logiciel senior, Intel, Versailles

## Contents

| 1 | Introduction                                                 |                                                                     |                                                                 |    |  |  |

|---|--------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------|----|--|--|

|   | 1.1                                                          |                                                                     | ext of the work                                                 | Ć  |  |  |

|   | 1.2                                                          | Static                                                              | -dynamic frameworks for analysis and optimization               | 11 |  |  |

| 2 | Pol                                                          | Polyhedral transformations and speculative parallelism: an overview |                                                                 |    |  |  |

|   | 2.1                                                          | The p                                                               | olytope model                                                   | 15 |  |  |

|   |                                                              | 2.1.1                                                               | Notations and definitions                                       | 16 |  |  |

|   |                                                              | 2.1.2                                                               | The polyhedral representation of a loop nest                    | 17 |  |  |

|   |                                                              | 2.1.3                                                               | Data access functions                                           | 19 |  |  |

|   |                                                              | 2.1.4                                                               | Scheduling the statements                                       | 20 |  |  |

|   |                                                              | 2.1.5                                                               | Static dependence analysis                                      | 25 |  |  |

|   |                                                              | 2.1.6                                                               | Dependence vectors                                              | 26 |  |  |

|   |                                                              | 2.1.7                                                               | Polyhedral transformations                                      | 27 |  |  |

|   |                                                              | 2.1.8                                                               | Concluding remarks                                              | 27 |  |  |

|   | 2.2                                                          | Gener                                                               | al overview of traditional TLS systems                          | 27 |  |  |

|   | 2.3                                                          | State of the art                                                    |                                                                 |    |  |  |

|   | 2.4                                                          | Limits of current TLS systems                                       |                                                                 |    |  |  |

| 3 | From polyhedral transformations to speculative parallelism 3 |                                                                     |                                                                 |    |  |  |

|   | 3.1                                                          |                                                                     |                                                                 |    |  |  |

|   |                                                              | 3.1.1                                                               | Indirect references                                             | 40 |  |  |

|   |                                                              | 3.1.2                                                               | Sparsely allocated linked list                                  | 42 |  |  |

|   |                                                              | 3.1.3                                                               | Transpose matrix with parameters                                | 43 |  |  |

|   |                                                              | 3.1.4                                                               | Banded matrix with indirect references                          | 43 |  |  |

|   |                                                              | 3.1.5                                                               | Dynamic control structures                                      | 44 |  |  |

|   | 3.2                                                          | Adapt                                                               | ted polyhedral model as an analysis model: dynamic dependence   |    |  |  |

|   |                                                              | analys                                                              | sis                                                             | 46 |  |  |

|   |                                                              | 3.2.1                                                               | Dependence analysis                                             | 47 |  |  |

|   | 3.3                                                          | Adapt                                                               | ted polyhedral model as a transformation model: code patterns . | 49 |  |  |

|   |                                                              | 3.3.1                                                               | Parallelizing transformations with code patterns                | 49 |  |  |

|   |                                                              | 3.3.2                                                               | Complex code patterns                                           | 58 |  |  |

|   |                                                              | 3.3.3                                                               | Dynamic code generation using code patterns                     | 62 |  |  |

|   |                                                              | 3.3.4                                                               | Genericness of code patterns                                    | 62 |  |  |

|   |                                                              | 3.3.5                                                               | Static versions vs Patterns                                     | 63 |  |  |

|   |                                                              | 3.3.6                                                               | Patterns vs JIT                                                 | 65 |  |  |

4 CONTENTS

|   | 3.4                | Verification and rollback systems in the polyhedral model            |      |  |

|---|--------------------|----------------------------------------------------------------------|------|--|

|   |                    | 3.4.2 Rollback                                                       |      |  |

|   |                    | 3.4.3 Conclusions                                                    |      |  |

|   |                    |                                                                      |      |  |

| 4 |                    | ategies for full exploitation of the available parallelism           | 71   |  |

|   | 4.1                | Program phases                                                       |      |  |

|   | 4.2                | Multiversioning                                                      |      |  |

|   |                    | 4.2.1 Related work                                                   |      |  |

|   |                    | 4.2.2 Open questions and limits of modern compilers                  |      |  |

|   |                    | 4.2.3 Adapting to the current behavior using multiple versions       |      |  |

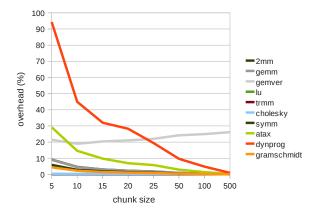

|   | 4.3                | The chunking system                                                  |      |  |

|   |                    | 4.3.1 Chunking one sequential loop                                   |      |  |

|   |                    | 4.3.2 Chunking with transformed loops                                |      |  |

|   |                    | 4.3.3 Rollbacking with chunks                                        |      |  |

|   |                    | 4.3.4 Profiling with chunks                                          |      |  |

|   | 4.4                | Conclusions                                                          | 87   |  |

| 5 | The                | e VMAD framework                                                     | 89   |  |

|   | 5.1                | Static component                                                     |      |  |

|   |                    | 5.1.1 Short introduction of the LLVM IR                              |      |  |

|   |                    | 5.1.2 Identify the loop nests marked for speculative parallelization |      |  |

|   |                    | 5.1.3 Generating multiple versions                                   |      |  |

|   |                    | 5.1.4 Inserting static information: headers and parameters           |      |  |

|   | 5.2                | Dynamic component                                                    |      |  |

|   |                    | 5.2.1 Code manipulation                                              |      |  |

|   |                    | 5.2.2 Runtime code orchestration for speculative parallelization     |      |  |

|   | 5.3                | Conclusions                                                          | 127  |  |

| 6 | Evo                | duation of the VMAD framework                                        | 129  |  |

| U | 6.1                |                                                                      |      |  |

|   | 0.1                | 6.1.1 Related work                                                   |      |  |

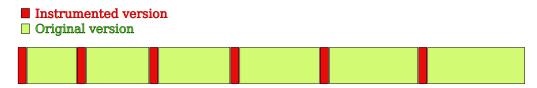

|   |                    | 6.1.2 Instrumentation by sampling in VMAD                            |      |  |

|   |                    | 6.1.3 Instrumenting memory accesses                                  |      |  |

|   |                    | 6.1.4 Results                                                        |      |  |

|   | 6.2                | Speculative parallelization                                          |      |  |

|   | 0.2                | 6.2.1 VMAD's runtime overhead                                        |      |  |

|   |                    | 0.2.1 Villia d'alliante overneux                                     | 110  |  |

| 7 | Other applications |                                                                      |      |  |

|   | 7.1                | Simple dynamic dependence analysis                                   | 151  |  |

|   | 7.2                | Runtime version selection                                            | 153  |  |

|   | 7.3                | Conclusions                                                          | 155  |  |

| 8 | Cor                | nclusions                                                            | 157  |  |

| 0 | D                  |                                                                      | 1 50 |  |

| 9 | rer                | spectives                                                            | 159  |  |

| CONTENTS |  | 5 |

|----------|--|---|

|          |  |   |

| Bibliography          | 162 |

|-----------------------|-----|

| — O <b>-</b> <i>)</i> | — · |

6 CONTENTS

## List of Figures

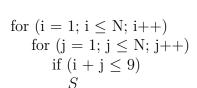

| 2.1 | Sample loop nest (left) and the iteration domain of $S$ for $N = 6$ (right) (courtesy: B. Pradelle) | 18 |

|-----|-----------------------------------------------------------------------------------------------------|----|

| 2.2 | Domain of statement $S$ from Figure 2.1                                                             | 18 |

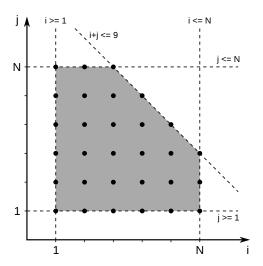

| 2.3 | Overview of a TLS system                                                                            | 29 |

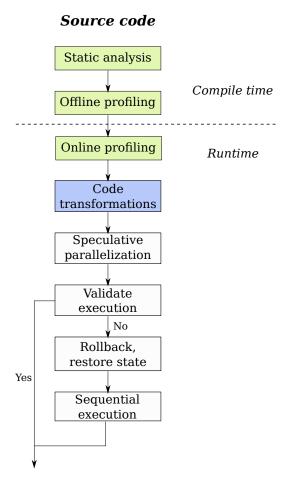

| 2.4 | Illustration of the usual TLS parallelization by chunks and conflict de-                            |    |

|     | tection (courtesy: Ph. Clauss)                                                                      | 37 |

| 3.1 | Examples of loop nests with an indirect memory reference                                            | 41 |

| 3.2 | Memory allocation for the linked list                                                               | 42 |

| 3.3 | Table for computing the distance vectors dynamically (2-depth loop nest)                            | 49 |

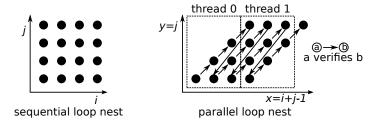

| 3.4 | Simplified code pattern                                                                             | 57 |

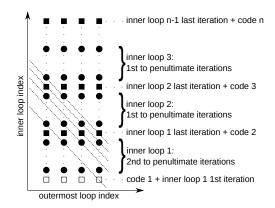

| 3.5 | General structure of a loop nest                                                                    | 58 |

| 3.6 | Graphic representation of the iterations of a loop nest (courtesy: Ph.                              |    |

|     | Clauss)                                                                                             | 59 |

| 3.7 | General structure of a parallel loop nest                                                           | 59 |

| 3.8 | Code patterns to balance genericity and performance (courtesy: Ph.                                  |    |

|     | Clauss)                                                                                             | 65 |

| 3.9 | Illustration of basic scalar values verification in the parallel loop nest                          |    |

|     | (courtesy: Ph. Clauss)                                                                              | 66 |

| 4.1 | Alternating the execution of different versions, during one run of the                              |    |

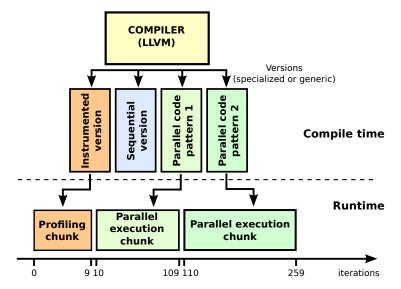

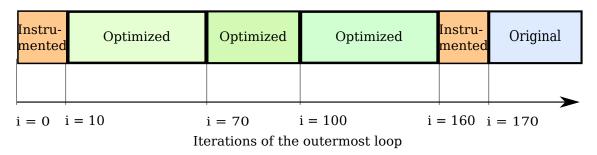

|     | loop nest (courtesy: Ph. Clauss)                                                                    | 79 |

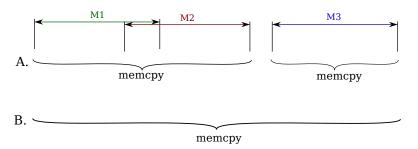

| 4.2 | Loop chunking                                                                                       | 80 |

| 4.3 | Chunked versions example                                                                            | 83 |

| 4.4 | Chunking time overhead                                                                              | 84 |

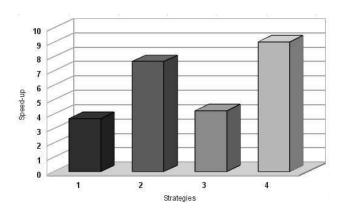

| 4.5 | Speed-up obtained with various chunking strategies                                                  | 86 |

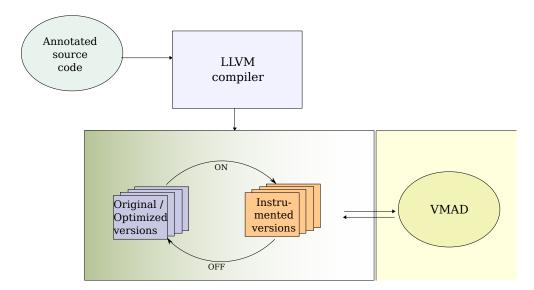

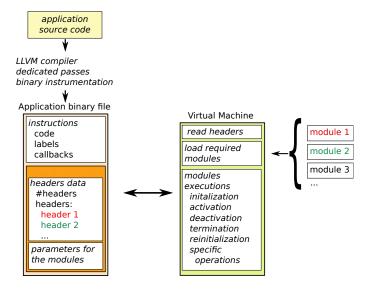

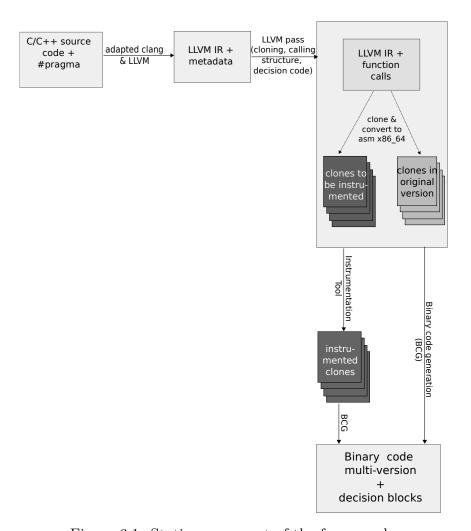

| 5.1 | Framework overview: static-dynamic collaboration                                                    | 90 |

| 5.2 | Framework overview (courtesy: Ph. Clauss)                                                           | 91 |

| 5.3 | Annotated source code                                                                               | 93 |

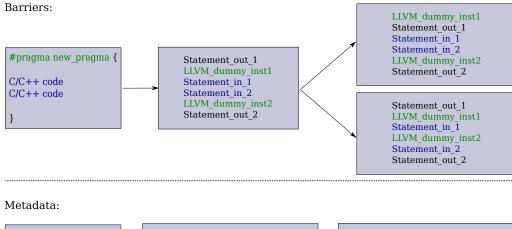

| 5.4 | Delimiting code regions using barriers compared to metadata                                         | 95 |

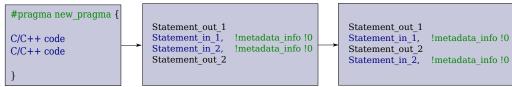

| 5.5 | Loop in LLVM IR with metadata                                                                       | 96 |

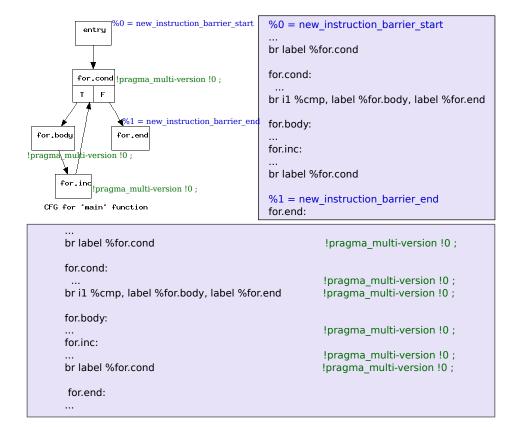

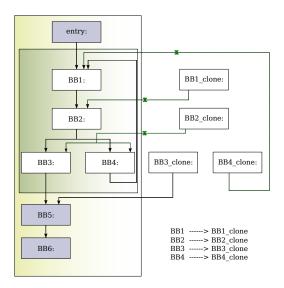

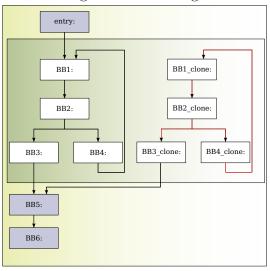

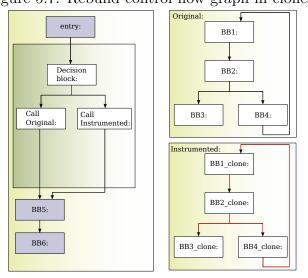

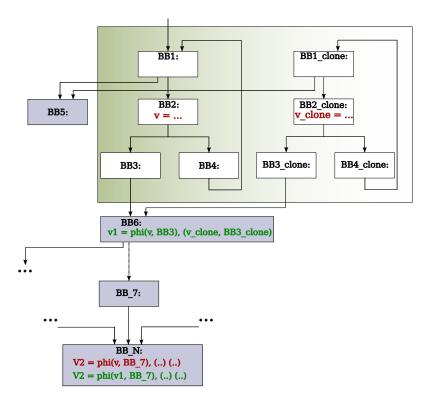

| 5.6 | Cloning                                                                                             | 98 |

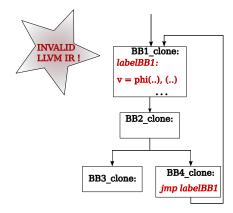

| 5.7 | Rebuild control flow graph in clones                                                                | 98 |

| 5.8 | Multi-versioning                                                                                    | 98 |

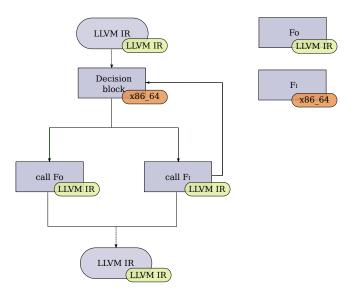

| 5.9 | Each version is transformed into a suitable representation                                          | 99 |

8 LIST OF FIGURES

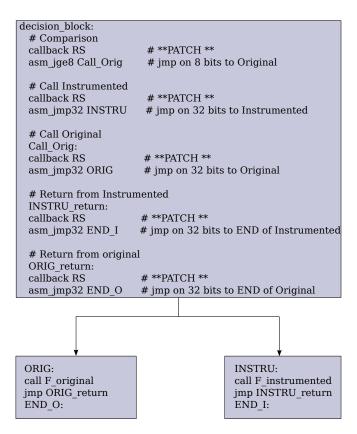

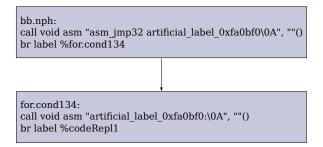

| 5.10       | callback in x86_64 assembly code                                                                                                                       | 100 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.11       | Code structure                                                                                                                                         | 101 |

| 5.12       | Shadowed control flow graph                                                                                                                            | 102 |

| 5.13       | Control flow graph rewritten in inline code                                                                                                            | 103 |

| 5.14       | Control flow graph with $\phi - nodes$                                                                                                                 | 104 |

| 5.15       | Control flow graph with $\phi - nodes$ and labels                                                                                                      | 104 |

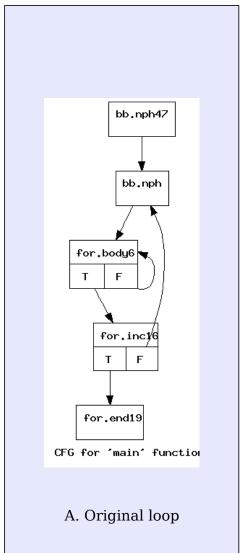

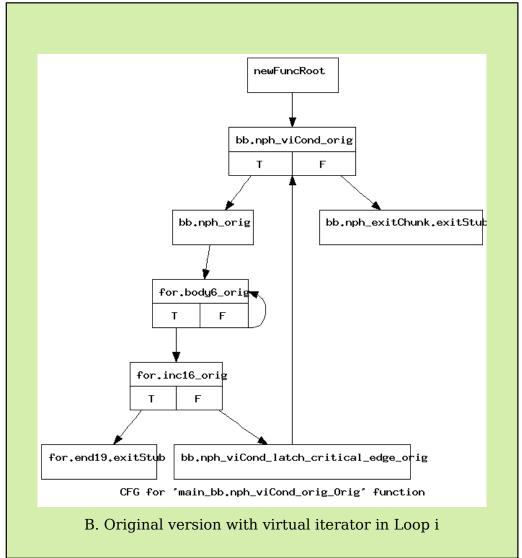

| 5.16       | Loop structure with virtual iterators                                                                                                                  | 108 |

| 5.17       | Loop structure in the parallel code pattern                                                                                                            | 109 |

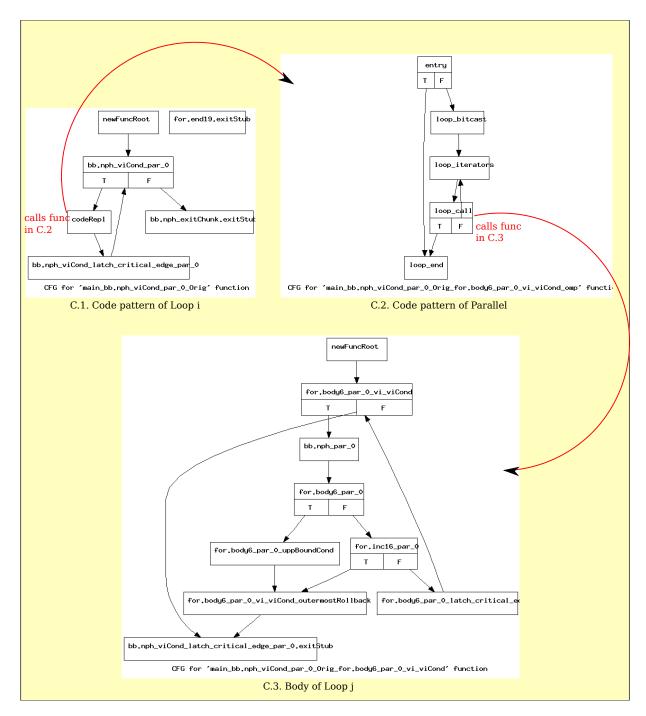

| 5.18       | Verify write accesses                                                                                                                                  | 111 |

| 5.19       | Original iterators & upper bounds wrt new iterators                                                                                                    | 112 |

| 5.20       | Computation of the next sequential iterations                                                                                                          | 113 |

| 5.21       | Verification code                                                                                                                                      | 113 |

| 5.22       | Generating OMP code in LLVM IR                                                                                                                         | 115 |

| 5.23       | List of headers and parameters                                                                                                                         | 117 |

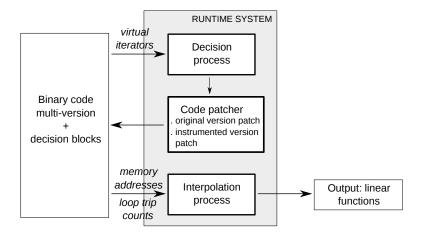

| 5.24       | Static-dynamic collaboration                                                                                                                           | 119 |

| 5.25       | Code orchestration                                                                                                                                     | 122 |

|            | Chunk size increase for the original sequential version                                                                                                | 123 |

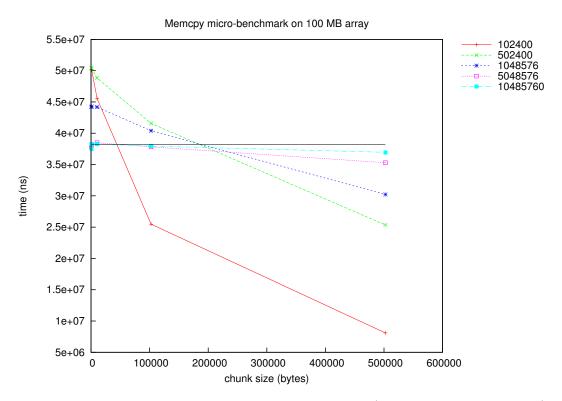

| 5.27       | memcpy time overhead                                                                                                                                   | 124 |

| 5.28       | memcpy calls                                                                                                                                           | 125 |

| 5.29       | memcpy calls with varying chunk sizes (courtesy: J-F. Dollinger)                                                                                       | 125 |

| 6.1        | Static component of the framework                                                                                                                      | 132 |

| 6.2        | Runtime component of the profiling framework                                                                                                           | 132 |

| 6.3        | Loop nest instrumentation                                                                                                                              | 133 |

| 6.4        | Code structure                                                                                                                                         | 134 |

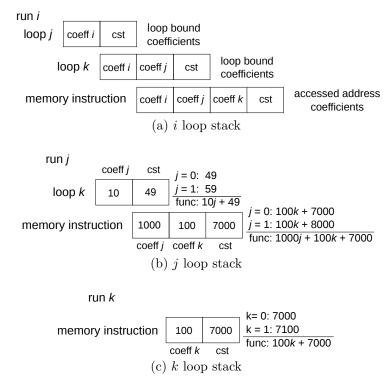

| 6.5        | Stack structure of each loop level                                                                                                                     | 135 |

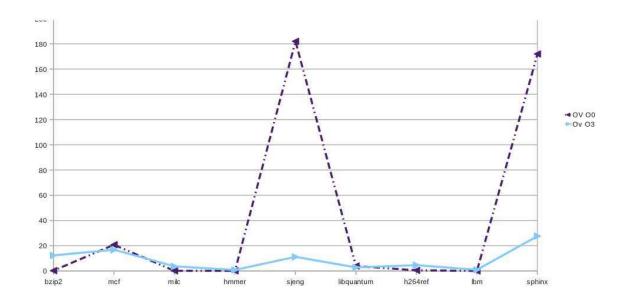

| 6.6        | Runtime overhead with O0 and O3 optimization levels                                                                                                    | 137 |

| 6.7        | Code extract from ks and its corresponding interpolation functions                                                                                     | 138 |

| 6.8        | Instrumenting memory accesses in SPEC CPU 2006                                                                                                         | 139 |

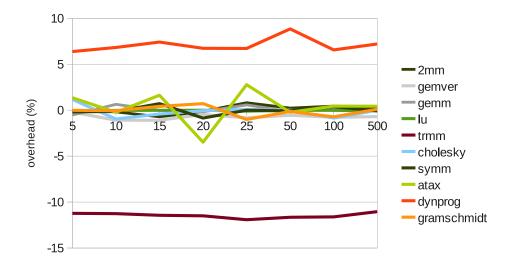

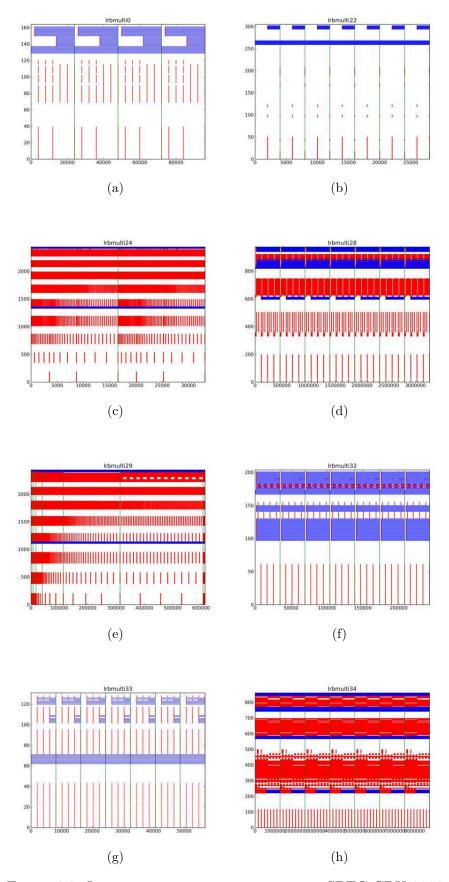

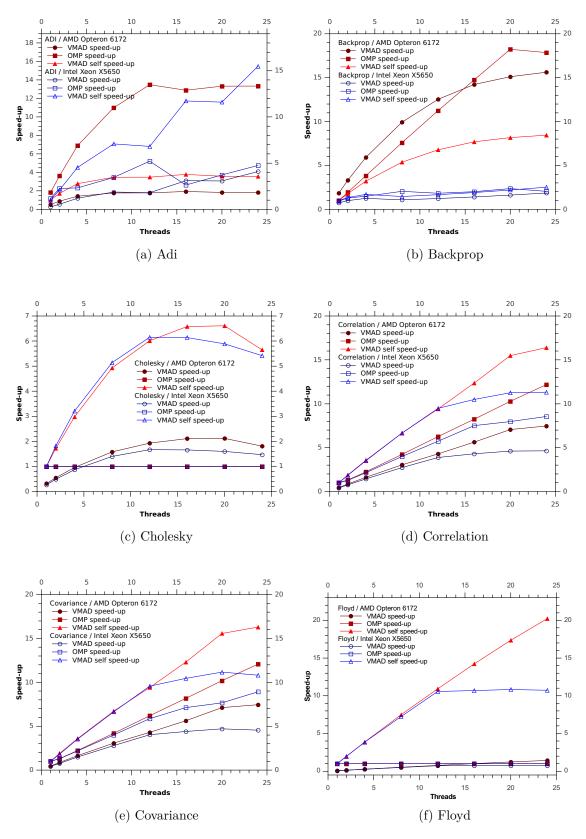

| 6.9        | Speculative parallelism results I                                                                                                                      | 142 |

| 6.10       | Speculative parallelism results II                                                                                                                     | 143 |

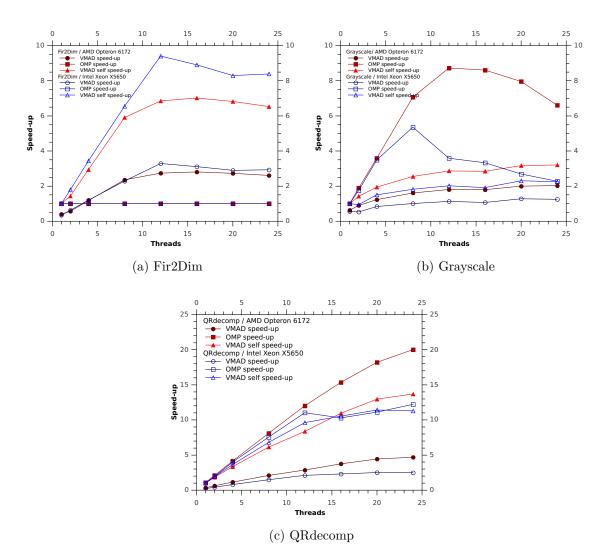

| 6.11       | Percentage of time spent by VMAD in different execution phases                                                                                         | 144 |

| 6.12       | Code speculatively parallelized with VMAD, compared to OpenMP (I)                                                                                      | 145 |

| 6.13       | Code speculatively parallelized with VMAD, compared to OpenMP (II)                                                                                     | 146 |

| 6.14       | Code speculatively parallelized with VMAD, compared to OpenMP (III) $$                                                                                 | 147 |

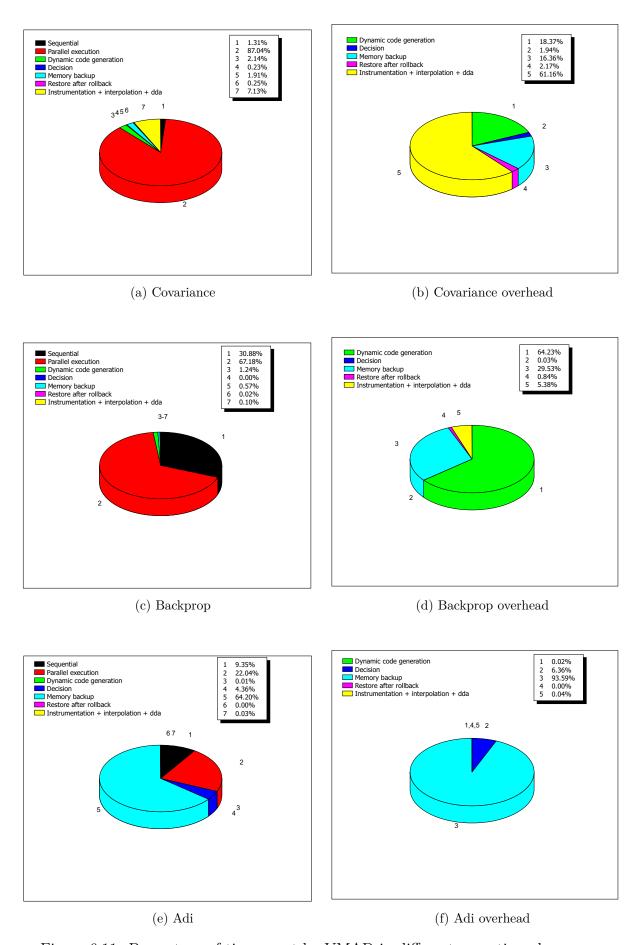

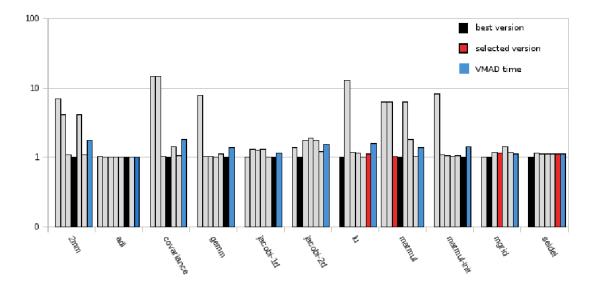

| 7.1<br>7.2 | Dynamic dependence analysis with <i>value range analysis</i> and <i>gcd</i> tests . Dynamic code selection with VMAD, Logarithmic scale (courtesy: Ph. | 152 |

|            | Clauss)                                                                                                                                                | 155 |

## Chapter 1

## Introduction

## 1.1 Context of the work

The advent of multicore processors imposes new strategies for reaching good software performance and exploiting advantageously the provided hardware. The key to success is now radically related to parallelism and applications have to be run in phases where many computations are performed simultaneously on all the available processor cores. There are several possible options to accomplish this: programs can be written by explicitly describing what can be run in parallel and what cannot, the compiler can extract parallel computations from a serial code by performing advanced code analyses and then generate parallel code, or the software can be run on top of a runtime system, or virtual machine, performing on-the-fly analyses and parallelizations. Nevertheless, although each option has been intensely studied, they all have some inherent limitations.

Even if many parallel programming languages are available, such as OpenMP, MPI, Cilk, TBB, HMPP, OpenCL or CUDA, parallel programming is in general difficult, because the programmer is required to handle complex issues, such as selecting a convenient algorithm for parallelization, analyzing the dependences between parts of the code, ensuring correct semantics, being aware of the underlying hardware characteristics and using a suitable programming model. Moreover, performance portability is difficult to be ensured due to hardware heterogeneity. Such issues significantly increase the software time-to-market. To aid the programmer in delivering parallel code, building compilers that perform automatic parallelization became an active research area.

Compilers dedicated to automatic parallelization have a rich history, particularly focusing on scientific computing applications. Examples of such compilers are SUIF [132], Polaris [13] and PIPS [35], that are able to automatically parallelize sequential programs without the programmer's intervention. They mostly focus on for-loops accessing multi-dimensional arrays and referencing array elements through linear functions of the loop indices. Thanks to precise data dependence analysis, such loops can take advantage of advanced parallelizing transformations as tiling, loop splitting or fusion, loop interchange, loop skewing and more generally linear loop transformations. The theory concerning loop analyses and transformations is unified in a well-known mathematical

10 Ch. 1. Introduction

framework called the polytope model [44, 45]. However, its applicability is limited to array-based scientific applications exhibiting explicit linearity of their loop bounds and array accesses. Loops exhibiting complex exit conditions and memory accesses through pointers or indirect arrays cannot be handled at compile-time using these techniques, since crucial information can only be known at execution-time. Moreover, it is generally difficult for a compiler to select the parallelizing and optimizing transformations that would perform well under various circumstances (in different execution contexts or on distinct processors).

The third solution is to run the targeted program in the frame of a runtime system whose role is to use advantageously the available dynamic information and automatically parallelize on-the-fly some code parts. One main advantage is that the effectiveness of a code transformation can immediately be evaluated and the course of execution can be adjusted accordingly by the runtime system in real time. In particular, *speculative* parallelizing techniques are possible since an online verification can consecutively launch recovery actions, in case previously speculated information is invalidated, such as canceling wrong computations and restarting them from the last correct state. This approach does not have, a priori, any limitation on the type of targeted code, however it is strongly constrained by the time overhead inevitably introduced. Hence, it is impossible to perform complete analyses and optimizations at runtime, as done by a compiler. On the other hand, generating *efficient* code is mandatory.

In this current context, speculative parallelization is an essential strategy to handle the parallelization of general-purpose codes. A well-researched direction in speculative parallelization is thread-level speculation (TLS) [19, 66, 70, 76, 103, 105, 106, 114, 119, 137]. A TLS framework allows optimistic execution of parallel code regions before all dependences between instructions are known. Hardware or software mechanisms track register and memory accesses to determine if any dependence violation occurs. In such cases, register and memory state are rolled back to a previous correct state and sequential re-execution is initiated. Our proposal focuses on enhancing previous works on speculative parallelism, by providing advancements in the quality of the generated parallel code. The highlights of this thesis are:

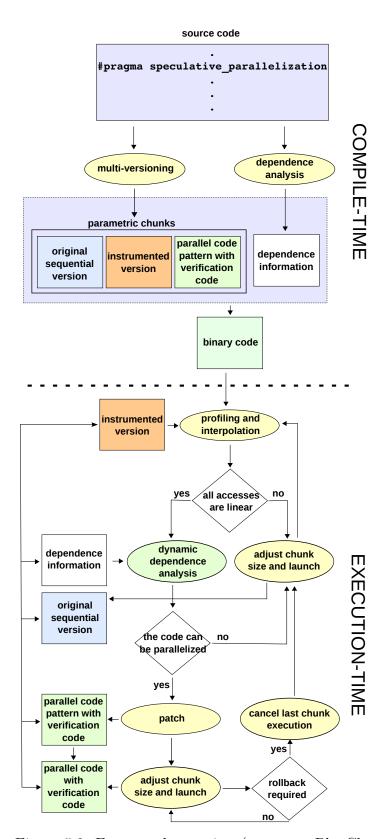

- 1. Optimize and parallelize the code at runtime, by applying a polyhedral transformation prior to parallelization. This has twofold consequences: first, boosting the performance of the generated parallel code, and second, exhibiting parallelism in codes which could not be parallelized in the original form. Chapter 2 introduces the mathematical background of the polyhedral model and a general overview of TLS systems, followed by our proposal on how the polyhedral model can be applied speculatively at runtime, in Chapter 3.

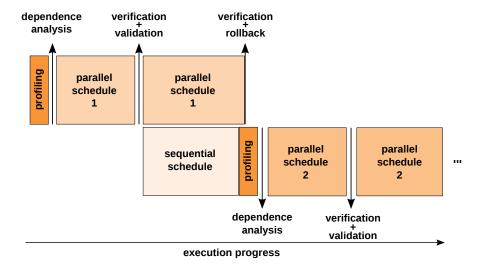

- 2. Fully exploit parallelism in codes that exhibit different phases during one execution, by adapting to the current behavior of the code. Our strategy relies on slicing the execution in intervals, where each interval represents a program's phase. For each phase, we prepare a custom code version, in accordance with the properties exhibited by the code during the certain phase. Chapter 4 details the multi-versioning and the chunking techniques we employ for this purpose.

From the point of view of the implementation techniques, this thesis provides an

insight on:

- 1. optimizing and parallelizing transformations performed at runtime, which consist of (1) a linear re-scheduling of the target loop nest's iterations in order to reveal parallelism and (2) the parallelization of the *outermost parallel* loop in the transformed code;

- 2. adaptation of the polytope model to dynamic and speculative parallelization;

- speculation based on the representation of the memory accesses as predicting linear functions of the loop indices, obtained by interpolating addresses accessed during execution samples;

- dynamic dependence analysis by computing the dependence distance vectors from memory addresses accessed during execution samples;

- dynamic generation of speculatively parallel code, using binary patterns patched at runtime;

- rollback in case of misprediction, by canceling the last executed chunk.

- 3. global orchestration of the loop nest execution, by running successive slices, or chunks, of the outermost loop that are executed serially, but intra-chunk iterations are run in parallel;

- 4. software implementation as a collaborative static-dynamic framework consisting of extensions of the LLVM compiler and an x86-64 runtime system.

We implemented the entire system in a platform called VMAD, which stands for *Virtual Machine for Advanced*, *Dynamic Code Instrumentation and Optimization*. The technical details of the framework are presented in Chapter 5, which describes the code preparation at compile-time and the actions taken by the runtime system during execution. Next, the experimental evaluations are included in Chapter 6.

Moreover, we illustrate VMAD as a generic framework, which in addition to performing speculative parallelization, is suitable to accomplish various types of complex code instrumentation, analysis and optimization. Such applications are described in Chapter 7.

Last but not least, the conclusions, introspections and perspectives of our work are presented in the end of the thesis.

The next section is dedicated to setting the context of our research, by reviewing the outstanding previous proposals concerning each important aspect of our work.

# 1.2 Static-dynamic frameworks for analysis and optimization

Our framework, VMAD, is a platform for dynamic code instrumentation and optimization, targeting automatic parallelization on-the-fly. In what follows we present some of the outstanding related works concerning the main characteristics and contributions 12 Ch. 1. Introduction

of VMAD, followed by a more detailed survey of the state of the art in the subsequent chapters. Chapter 2, Section 2.3 sets the frame of our work as a TLS system, compared to previous techniques. Once all related notions are introduced, together with the background of our work, Chapter 4, Section 4.2 presents previous approaches for multiversioning and its applications, while Section 4.3 reviews works that performed chunking on loops. Chapter 5, Section 6.1.1 gives an overview of various works targeting code instrumentation and profiling; and finally Chapter 7, Section 7.2 describes several works on runtime selection among several optimized versions.

To outline the context of our work, we review in what follows the closest and most representative tools and methods designed to perform:

- Code instrumentation: PIN [79], DynamoRIO [18],

- Polyhedral code optimization: Pluto [15],

- Speculative code parallelization: LRPD [106] and R-LRPD [33] tests.

PIN: Pin [79] is a dynamic binary instrumentation engine for the Intel architectures (x86 and x86-64 instruction sets) which allows the programmer to build customized instrumentation tools, called *Pintools*. It has already been included in many Intel commercial tools, such as Intel Parallel Inspector, Intel Parallel Amplifier and Intel Parallel Advisor. PIN inserts snippets of code in a running program to collect runtime information. Thus, PIN is suitable both for program analysis, useful in performance profiling, error detection, capture and replay; as well as for an architectural study, offering support for processor and cache simulation or trace collection. Thanks to its flexibility, various tools can be generated, for emulation, security and parallel program analysis. Since PIN is a dynamic engine, it uses Just-in-time compilation to compile (and optimize) the instrumentation code just before it is executed. The pintools can be attached to the binary code or even to the running process, without the need to recompile or re-link the code. Using this mechanism, it can also handle dynamically generated code. A pintool consists of three types of routines: instrumentation, analysis and callback routines.

- 1. Instrumentation routines: once the program is loaded in memory, PIN's strategy is to take control of the program and to JIT some small pieces of code, thus inserting in the original code calls to the analysis routines.

- 2. Analysis routines: they are executed when the code to which they are associated begins its executions and are aimed to collect the required dynamic information.

- 3. Callback routines: these are special callbacks invoked when certain conditions are met, or when specific events occur.

PIN provides an explicit API, very flexible and easy to use for building tools dedicated to a large palette of instrumentation types. However, due to its overhead, PIN is not yet ready to be used as an online profiler, as part of a dynamic optimization phase. According to Bach *et al.* [6], the inherent overhead of PIN revolves around 30%, when no pintools are executed. Depending on the purpose of instrumentation, extra overhead

is added. For instance, for basic block counting, the overhead of PIN is up to 2000%, according to Hazelwood *et al.* [79]. Unlike VMAD, one cannot instrument by sampling, as the instrumentation inserted with PIN cannot be disabled during the execution of the code, leading to a high overhead. Thus it cannot be used in a dynamic optimizer.

**DynamoRIO:** Very similar to PIN, DynamoRIO [18] is a framework designed for dynamic instrumentation of codes, by allowing the programmer to write their own tool for instrumentation, analysis, profiling, optimization or any other code transformation. Thus, unlike other similar tools, DynamoRIO does not only monitor the code, but it can also perform any kind of code modifications, as the application is running, as specified by the programmer. From a performance perspective, the base overhead of DynamoRIO is 45% in average, however, an optimized version outperforms PIN for basic block counting [18]. Still, its high overhead makes this tool unsuitable for being embedded in a dynamic optimizer.

Pluto: Pluto [15] is a framework for automatic parallelization and optimization of affine loop nests. It is a source-to-source compiler that builds an abstract representation of the loop nest, using the polyhedral model, for further loop transformations. All loop optimizations, such as tiling, fusion, unrolling, are manipulated in the polyhedral representation, from which the new loop nest is generated in the transformed form. The goal is to optimize for data locality and to expose parallelism, simultaneously. Thus, the compiler defines a cost function, aimed to evaluate distinct transformations and to select the best. The transformation is defined as a hyperplane, evaluated by the cost function, based on the data reuse distance. The transformation aims to minimize the reuse distance in order to limit the volume of communicated data. For instance, for a tiling hyperplane, the cost function can provide an upper bound on the data communicated between the tiles, depending on the tile size. Pluto is designed to detect synchronization-free parallelism, permutable loops or pipelined parallelism at various levels and to automatically transform the loops in the corresponding form. The experimental results demonstrate that codes automatically optimized and parallelized with Pluto perform very well, considerably outperforming other research or commercial compilers [14, 15, 16]. Despite its very promising performance, Pluto is limited to statically analyzable codes embedding affine loop nests, very frequent in scientific codes. On the other hand, general purpose codes cannot benefit from the great advantages of the polytope model, as they cannot be fully disambiguated at compile time. It is the goal of our work to dynamically model the loops in the polyhedral representation and to perform automatic optimizations and parallelization.

The LRPD test: Among the pioneers of speculative parallelization are the authors of the LRPD test [106], who noticed the frequency of statically undetectable parallel loops that occur in general purpose codes. Their proposal is to speculatively execute all loops in parallel and to perform a dependence analysis at runtime, to ensure that the semantics of the code is preserved. To enhance parallelism, they apply privatization and reduction parallelization methods dynamically and check their validity during execution. As soon as a dependence violation is detected, the loop is re-executed sequentially.

14 Ch. 1. Introduction

Although this might lead to significant performance losses in case of non-parallelizable loops, this work set the premises of speculative parallelization.

In contrast to previous works, they relax the constraints on the dependences, consequently only flow dependences lead to a rollback and to a sequential re-execution of the loop. To ensure correctness in the presence of output and anti-dependences, they apply privatization and reduction methods, thus eliminating those dependences. Additionally, they develop the Lazy Reduction Privatizing Doall (LRPD) test to check dependences dynamically. The compiler is forced to take conservative decisions, however during execution, one can verify the exact dependences that occur. For example, if a variable is read, but its use is under a conditional, the compiler must consider a dependence. However, at runtime the correct decision is taken, whether the variable has been used or not and whether a private copy of the value could remove the dependence. The test is also applicable to detect cross-processor dependences.

All in all, the LRPD test is able to handle any type of loops, without restrictions, nevertheless, as soon as a dependence is detected, the whole loop is re-executed sequentially.

The R-LRPD test: To overcome the limits of the LRPD test, the R-LRPD [33] test aims to exploit partial parallelism of loops. It transforms a partially parallel loop into a sequence of fully parallel loops and speculatively executes each of the newly obtained loop with the LRPD test. The execution in phases of the loops shows some similarities to our work, for detecting different behaviors of one loop during one execution. But, in addition to parallelization, VMAD targets also loop optimizations, by applying a polyhedral transformation.

## Chapter 2

# Polyhedral transformations and speculative parallelism: an overview

This chapter introduces the theoretical notions of the polytope model in Section 2.1 and a general overview of the traditional TLS systems in Section 2.2. An overview of previous approaches dedicated to speculative automatic parallelization of loops is given in Section 2.3, which presents also detailed works on components of TLS systems, such as mechanisms for predictions, dependence analysis, transactional memory; as well as previous approaches applying the polyhedral model, however statically. Finally, we conclude the chapter by underlining the limits of current TLS systems and proposing solutions to improve them.

## 2.1 The polytope model

The polytope model, also called the polyhedral model, is a very powerful mathematical abstraction used in loop optimizations. In geometry, a polytope represents a geometric object with flat sides, which can exist in any number of dimensions. In particular, we are interested in a special class of polytopes, the *convex polytopes*, having the property that they are convex sets of points in an n-dimensional space  $\mathbb{K}^n$ . This class finds its application in linear programming, as any linear transformation preserves the properties of the points building the polytope. Additionally, a convex polytope may be defined in a number of ways, depending on what is more suitable for the problem at hand. One definition is in terms of a convex set of points in space, but among other important definitions are: as the intersection of half-spaces (half-space representation) or as the convex hull of a set of points (vertex representation).

Abstracting a loop in the polyhedral representation is equivalent to associating to each dynamic instance (iteration) of each statement an integer point in space, contained in the *statement's polyhedron*. We introduce the mathematical notions required for modeling the loop nest. An exhaustive presentation of applications of the polytope model in program optimizations are given by Feautrier in multiple works [41, 42, 44, 45, 46] and has been addressed in many others dedicated to compile-time [15, 16, 55] or runtime loop optimizations [101]. For a throughout presentation of the mathematical apparatus building the underlying background of the polytope model, the reader is re-

ferred to the monograph of Schrijver [109]. In what follows we present only an overview, detailing the aspects required to understand the background of this dissertation.

#### 2.1.1 Notations and definitions

We denote by  $\vec{v}$  a vector, by  $|\vec{v}|$  its dimension, and by  $\vec{v}[i]$  the  $i^{th}$  element of  $\vec{v}$ .

**Definition 1:** (Affine function) A function f:  $\mathbb{K}^m \to \mathbb{K}^n$  is said to be affine iff  $\exists$  a matrix  $A \in \mathbb{K}^{n \times m}$  and a vector  $\vec{b} \in \mathbb{K}^n$  such that:

$$\forall \vec{x} \in \mathbb{K}^m, \ \mathbf{f}(\vec{x}) = \mathbf{A}\vec{x} + \vec{b}.$$

**Definition 2:** (Affine hyperplane) An affine hyperplane of an n-dimensional affine space V is a subspace of dimension n-1, defined by a linear equation in  $\vec{x} \in \mathbb{K}^n$  of the form:

$$\vec{a} \cdot \vec{x} = b$$

,

where  $\vec{a} \in \mathbb{K}^n$  (at least one element  $\vec{a}[i] \neq 0$ ) and b is a scalar from  $\mathbb{K}$ .

**Definition 3:** (Affine half-space) An affine hyperplane divides the space into two half-spaces, defined by the inequalities:

$$\vec{a} \cdot \vec{x} > b$$

and

$$\vec{a} \cdot \vec{x} < b$$

,

where  $\vec{a} \in \mathbb{K}^n$  (at least one element  $\vec{a}[i] \neq 0$ ) and  $b \in \mathbb{K}$ .

**Definition 4:** (Convex polyhedron) The intersection of a finite number of affine half-spaces defines a convex polyhedron, each half-space providing a face of the polyhedron. Formally, the polyhedron  $P \subset \mathbb{K}^n$  can be expressed as a set of m affine constraints in  $A \in \mathbb{K}^{m \times n}$  and  $\vec{b} \in \mathbb{K}^m$ :

$$P = \{\vec{x} \in \mathbb{K}^n | A\vec{x} + \vec{b} > 0\}$$

**Definition 5:** (Parametric polyhedron) A polyhedron P may be parametrized by a vector of parameters  $\vec{p}$  and is denoted by  $P(\vec{p})$ . It can be defined by a matrix  $A \in \mathbb{K}^{m \times n}$ , a matrix of symbolic coefficients  $B \in \mathbb{K}^{m \times p}$ , where p is the dimension of the vector of parameters  $|\vec{p}| = p$  and a vector of constants  $\vec{b} \in \mathbb{K}^m$  as:

$$P(\vec{p}) = \{ \vec{x} \in \mathbb{K}^n | A\vec{x} + B\vec{p} + \vec{b} \ge 0 \}$$

**Definition 6:** (*Polytope*) A bounded polyhedron is called a *polytope*.

Libraries such as Polylib [96], PPL [99], isl [127], Barvinok [128], PIP [41] or Cloog [9] provide a range of functions implementing operations on unions of polyhedra in  $\mathbb{Q}^n$ , such as:

- set operations (union, difference, intersection...),

- image and inverse image (preimage) with respect to an affine function (transformation),

- existence of an integer value ("point") inside the polyhedra,

- counting the number of points included in a parametric polytope (Ehrhart polynomial [30]),

- lexicographic minimum/maximum (parametrically),

- scanning integer points.

## 2.1.2 The polyhedral representation of a loop nest

The compact polyhedral representation allows to model the dynamic instances of each statement of a loop nest in a precise manner, in the view of computing the dependences between the statements and performing code transformations. Given the loop nest:

```

Listing 2.1: Affine loop nest  \begin{array}{ll} \text{for } i=1,N \\ \text{ for } j=1,N \\ \text{ S } : A[i\,,j\,] = A[i-1][j+1]+1 \\ \text{ endfor } \\ \text{endfor} \end{array}

```

the statement S can be either one instruction, or a set of consecutive instructions. A dynamic instance of S is given by each execution of S, in different iterations:  $S_{1,1}$ ,  $S_{1,2}$ , ...,  $S_{1,N}$ , ...,  $S_{N,N}$ . Since the dynamic instances are defined in terms of the values of the enclosing loop iterators, this leads us to the next definition:

**Definition 7:** (*Iteration vector*) The *iteration vector* of a statement S, denoted by  $\vec{x_S}$ , is the n-dimensional vector of values of the iterators of the n loops enclosing S.

**Definition 8:** (Domain, index set) The set of all iterations vectors of a statement S is called the domain or the index set of the statement, denoted by  $\mathcal{D}^S$ .

Figure 2.1: Sample loop nest (left) and the iteration domain of S for N = 6(right) (courtesy: B. Pradelle)

$$\begin{cases} i-1 \geq 0 \\ j-1 \geq 0 \\ i+N \geq 0 \\ j+N \geq 0 \\ -i-j+9 \geq 0 \end{cases} \mathcal{D}^{S} = \begin{cases} \binom{i}{j} \in \mathbb{Z}^{2} | \begin{pmatrix} 1 & 0 & 0 & -1 \\ 0 & 1 & 0 & -1 \\ -1 & 0 & 1 & 0 \\ 0 & -1 & 1 & 0 \\ -1 & -1 & 0 & 9 \end{pmatrix} \begin{pmatrix} i \\ j \\ N \\ 1 \end{pmatrix} \geq 0 \end{cases}$$

Figure 2.2: Domain of statement S from Figure 2.1

Consider the affine loop nest in Figure 2.1. Note that statement S is under a conditional, hence not all the points in the iteration space are actually executed. The domain of S,  $\mathcal{D}^S$ , is depicted on the right. The iteration domain is expressed as a set of linear inequalities, as shown in Figure 2.2

If the loop bounds and data accesses can be expressed as affine functions of the enclosing loop indices and other parameters, and all conditionals in the loop are statically predictable, then the domain of every statement in the loop can be defined as a polyhedron, where the iteration vector is defined in  $\mathbb{Z}^d$  and d is the depth of the innermost loop enclosing the statement S:

$$\mathcal{D} = \{ \vec{x} \in \mathbb{Z}^d | A\vec{x} \ge \vec{b} \}$$

Considering also the parameters, the complete definition of a parametric polyhedron is:

$$\mathcal{D} = \left\{ \vec{x} \in \mathbb{Z}^d | A\vec{x} + B\vec{p} + \vec{b} \ge 0 \right\}$$

Equivalently, this represents the intersection of several half-spaces. The regions of code containing only affine loop nests and conditionals that can be evaluated statically, are known as *Static Control Part (SCoP)*. In a SCoP, the loop bounds, the conditionals and

the data access functions are defined as affine functions on the enclosing loop indices and some parameters. The values of the parameters must not necessarily be known at compile-time, however, they must remain fixed during the execution of the SCoP. Additionally, there are no constraints on the structure of the loop nests, both perfectly and imperfectly nested loops being accepted.

#### 2.1.3 Data access functions

Given a statement S executed inside a loop nest, not only the iteration domain of the statement is representative, but also the memory accesses it performs. For a precise analysis of the code in the polytope model, these accesses must be modeled as affine functions of the enclosing loop indices. Informally, each memory access can be seen as an array access with the subscripts defined as affine functions of the outer loop indices. For computing the memory location actually accessed, one uses a function of the form:

$$f(\vec{x}) = F\vec{x} + \vec{f} \tag{1}$$

where F is matrix  $\mathcal{M}_{s\times d}$  and  $\vec{f}$  a vector of size s, where s is the dimension of the array and d the depth of the statement. As an example consider the loop nest:

```

Listing 2.2: Affine loop nest  \begin{array}{ll} \text{for } i=1,N \\ \text{for } j=1,N \\ \text{S : } A[i\,,j\,] = A[i-1][j+1] + B[2\cdot i+j+5] \\ \text{endfor} \\ \text{endfor} \end{array}

```

The memory accesses performed by S are two read operations,  $R^A$ : A[i-1][j+1] and  $R^B$ : B[2·i+j+5]; and one write:  $W^A$ : A[i,j]. One obtains the following access functions, with  $\vec{x} = \begin{pmatrix} i \\ j \end{pmatrix}$ :

$$f_{R^A}(\vec{x}) = \begin{pmatrix} i-1\\ j+1 \end{pmatrix} = \begin{pmatrix} 1 & 0\\ 0 & 1 \end{pmatrix} \begin{pmatrix} i\\ j \end{pmatrix} + \begin{pmatrix} -1\\ 1 \end{pmatrix}$$

$$f_{R^B}(\vec{x}) = 2 * i + j + 5 = (2 \quad 1) \binom{i}{j} + 5$$

$$f_{W^A}(\vec{x}) = \begin{pmatrix} i \\ j \end{pmatrix} = \begin{pmatrix} 1 & 0 \\ 0 & 1 \end{pmatrix} \begin{pmatrix} i \\ j \end{pmatrix} + \begin{pmatrix} 0 \\ 0 \end{pmatrix}$$

Considering also the parameter N of the loop nest, the functions are rewritten in a more compact form as:

$$f_{R^A}(\vec{x}) = \begin{pmatrix} 1 & 0 & 0 & -1 \\ 0 & 1 & 0 & 1 \end{pmatrix} \begin{pmatrix} i \\ j \\ N \\ 1 \end{pmatrix}$$

$$f_{R^B}(\vec{x}) = \begin{pmatrix} 2 & 1 & 0 & 5 \end{pmatrix} \begin{pmatrix} i \\ j \\ N \\ 1 \end{pmatrix}$$

$$f_{W^A}(\vec{x}) = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \end{pmatrix} \begin{pmatrix} i \\ j \\ N \\ 1 \end{pmatrix}$$

Data accesses to scalars are treated similarly, as if each scalar was an array with only one element.

## 2.1.4 Scheduling the statements

By applying a polyhedral transformation, one transforms a sequential loop nest into a semantically equivalent, optimized or parallel loop nest. Such transformations must express the execution order of the statements, must be instruction-wise and should handle loops in the presence of parameters. Since neither the domain, nor the data access functions of a statement can provide information concerning the execution order, one must add an extra piece of information, associated to each statement. Thus, each dynamic instance of a statement is associated a *logical date*, defining the space and time when that particular instance should be executed. For a precise and uniform representation, the logical dates are multidimensional, i.e. intuitively can be seen as days, hours, minutes, seconds ..., starting with the most significant components on the first positions, until the least significant ones (lexicographic order). Assigning a logical date is achieved by means of a function, called *scheduling function*.

**Definition 9:** (Scheduling function) The scheduling function of a statement S, known also as the schedule of S, is a function that maps each dynamic instance of S to a logical date, expressing the execution order between statements:

$$\forall \vec{x} \in \mathcal{D}^S, \theta^S(\vec{x}) = T\vec{x} + \vec{t}$$

The associated timestamps allows one to order the instructions according to the lexicographic order, denoted as  $\ll$ , as component-wise comparison of vectors:

$$(a_1, \ldots, a_n) \ll (b_1, \ldots, b_n) \Leftrightarrow \exists i : 1 \leq i \leq n, \forall m : 1 \leq m < i, a_m = b_m \land a_i < b_i$$

Intuitively, two dynamic instances having the same timestamps can be executed in parallel. More precisely, the scheduling function is a mirror of the sequential execution order of the dynamic instances. Note that, unlike the iteration vectors, the scheduling function can express also the textual ordering of the statements. For example, consider the following loop nest with several statements enclosed in the innermost loop:

```

Listing 2.3: 2-depth affine loop nest  \begin{array}{lll} \text{for } ( & i = 0; & i < N; & i++ ) \\ & \text{for } ( & j = 0; & j < N; & j++ ) \\ & & S1 \\ & & S2 \\ & & end for \\ end for \end{array}

```

Both statement S1 and S2 have the same iteration vectors, since they only depend on the enclosing loop indices. They cannot capture the execution order of different statements, defined in the same loop. On the other hand, the scheduling function is able to maintain this information, by interleaving constants between each loop level, which are aimed to express the textual order:

$$\theta^{S_1}((i,j)) = (0,i,0,j,0)$$

$\theta^{S_2}((i,j)) = (0,i,0,j,1)$

In this representation, one can easily deduce the order of the statements S1 and S2. The first two constants, 0 and 0, indicate that they are executed at the same loop level, but S1 comes before S2 in the textual order, according to the last constant of each vector.

More formally, applying the schedule  $\theta(\vec{x}) = T\vec{x} + \vec{t}$  to the integer points of the iteration domain  $\mathcal{D} = \left\{ \vec{x} | A\vec{x} \geq \vec{b} \right\}$ , is expressed as a polyhedron of the form:

$$\mathcal{D}': \left[\begin{array}{c|c} I & -T \\ \hline 0 & A \end{array}\right] \left(\begin{array}{c|c} \theta(\vec{x}) \\ \hline \vec{x} \end{array}\right) \stackrel{=}{\geq} \left(\begin{array}{c|c} \vec{t} \\ \hline \vec{a} \end{array}\right)$$

For example, given the loop in Fig 2.1 one obtains the polyhedron:

$$\mathcal{D}^{S}: \begin{pmatrix} 1 & 0 \\ -1 & 0 \\ 0 & 1 \\ 0 & -1 \\ -1 & -1 \end{pmatrix} \begin{pmatrix} i \\ j \end{pmatrix} \geq \begin{pmatrix} 1 \\ -N \\ 1 \\ -N \\ -9 \end{pmatrix}$$

and for a scheduling

$$\theta \begin{pmatrix} i \\ j \end{pmatrix} = i + j$$

one obtains:

$$\Theta^{S}: \begin{bmatrix}

\frac{1}{0} & -1 & -1 \\

0 & 1 & 0 \\

0 & -1 & 0 \\

0 & 0 & 1 \\

0 & 0 & -1 \\

0 & -1 & -1

\end{bmatrix}

\begin{bmatrix}

i' \\

i \\

j \\

\ge \begin{bmatrix}

0 \\

1 \\

-N \\

1 \\

-N \\

-9

\end{bmatrix}$$

(2)

This is commonly referred to as the *generalized change of basis*.

Scheduling matrices By applying an affine scheduling function  $\theta(\vec{x}) = T\vec{x} + \vec{t}$  on the iteration domain  $\mathcal{D}^S$  of a statement S, one obtains the scheduling matrix  $\Theta^S$  of S, where  $\Theta^S \in \mathbb{Z}^{d^t \times (d+p+1)}$ , with  $d^t = |\vec{t}|$ :

$$\forall \vec{x} \in \mathcal{D}^S, \theta^S(\vec{x}) = \Theta^S \vec{x} = \vec{t}$$

For a throughout understanding, we continue with a few examples showing the purpose of the scheduling matrices.

```

Listing 2.4: Matrix multiply for ( i = 0; i < N; i + +) for ( j = 0; j < N; j + +) {

S_1: C[i][j] = 0;

for ( k = 0; k < N; k + +)

S_2: C[i][j] + = A[i][k] * B[k][j];

}

```

*Identity schedules:* By applying the identity schedules on each of the statements in Listing 2.4:

$$\Theta_{S_1}(\vec{x}_{S_1}) = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \end{pmatrix} \begin{pmatrix} i \\ j \\ N \\ 1 \end{pmatrix} = \begin{pmatrix} i' \\ j' \end{pmatrix}$$

and

$$\Theta_{S_2}(\vec{x}_{S_2}) = \begin{pmatrix} 1 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \end{pmatrix} \begin{pmatrix} i \\ j \\ k \\ N \\ 1 \end{pmatrix} = \begin{pmatrix} i' \\ j' \\ k' \end{pmatrix}$$

one obtains the same code as listed in Listing 2.4. On the other hand, a slight change of the schedule for statement  $S_2$ :

$$\Theta_{S_1}(\vec{x}_{S_1}) = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \end{pmatrix} \begin{pmatrix} i \\ j \\ N \\ 1 \end{pmatrix} = \begin{pmatrix} i' \\ j' \end{pmatrix}$$

and

$$\Theta_{S_2}(\vec{x}_{S_2}) = \begin{pmatrix} 1 & 0 & 0 & \mathbf{1} & 0 \\ 0 & 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 \end{pmatrix} \begin{pmatrix} i \\ j \\ k \\ N \\ 1 \end{pmatrix} = \begin{pmatrix} i' + N \\ j' \\ k' \end{pmatrix}$$

results in the code in Listing 2.5.

```

Listing 2.5: Matrix multiply with a new schedule

```

```

for ( i=0; i< N; i ++)

for ( j=0; j< N; j ++)

S_1: C[i][j] = 0;

for ( i=N; i< 2*N; i ++)

for ( j=0; j< N; j ++) {

for ( k=0; k< N; k ++)

S_2: C[i-N][j]+=A[i-N][k] * B[k][j];

```

Which generates a loop distribution, because the loop nest had to be split in two different nests to preserve the semantics of the scheduling matrices.

Finally, one can perform a loop interchange with the following schedules:

$$\Theta_{S_1}(\vec{x}_{S_1}) = \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \end{pmatrix} \begin{pmatrix} i \\ j \\ N \\ 1 \end{pmatrix} = \begin{pmatrix} i' \\ j' \end{pmatrix}$$

and

$$\Theta_{S_2}(\vec{x}_{S_2}) = \begin{pmatrix} 1 & 0 & 0 & \mathbf{1} & 0 \\ 0 & \mathbf{0} & \mathbf{1} & 0 & 0 \\ 0 & \mathbf{1} & \mathbf{0} & 0 & 0 \end{pmatrix} \begin{pmatrix} i \\ j \\ k \\ N \\ 1 \end{pmatrix} = \begin{pmatrix} i' + N \\ k' \\ j' \end{pmatrix}$$

which is equivalent to the code in Listing 2.6.

#### Listing 2.6: Matrix multiply with interchange

```

for ( i=0; i < N; i ++)

for ( j=0; j < N; j ++)

S_1: C[i][j] = 0;

for ( i=N; i < 2*N; i ++)

for ( k=0; k < N; k ++) {

for ( j=0; j < N; j ++)

S_2: C[i-N][k]+=A[i-N][j] * B[j][k];

```

Canonical form of the scheduling matrices: To make the scheduling matrix more meaningful, Cohen et al. [10,31] propose a normalized representation, by decorating it both with static and dynamic information. Thus the scheduling matrix  $\Theta^S$  of a statement S contains one extra row for each loop level, to define the relative order of the statements within each iteration, plus one row for the loop at depth 0, which yields  $2d^S+1$  rows ( $d^S$  is the depth of the innermost loop enclosing S).

This encoding is suitable for expressing compositions of transformations, as it is decomposable in three sub-matrices:

- 1. The iteration ordering matrix  $A^S \in \mathcal{M}_{d^S,d^S}(\mathbb{Z})$  representing the iteration vectors;

- 2. The matrix of parameters  $\Gamma^S \in \mathcal{M}_{d^S,d_gp+1}(\mathbb{Z})$ , whre  $d_gp$  denotes the number of global parameters;

- 3. The statement ordering vector  $\beta \in \mathbb{N}^{d^S+1}$ , which specifies the order of S among the other statements executed at the same iteration.

The structure of the canonical schedule matrix is:

$$\Theta^{S} = \begin{bmatrix} 0 & \cdots & 0 & 0 & \cdots & 0 & \beta_{0}^{S} \\ A_{1,1}^{S} & \cdots & A_{1,d}^{S} & \Gamma_{1,1}^{S} & \cdots & \Gamma_{1,p}^{S} & \Gamma_{1,p+1}^{S} \\ 0 & \cdots & 0 & 0 & \cdots & 0 & \beta_{1}^{S} \\ A_{2,1}^{S} & \cdots & A_{2,d}^{S} & \Gamma_{2,1}^{S} & \cdots & \Gamma_{2,p}^{S} & \Gamma_{2,p+1}^{S} \\ \vdots & \ddots & \vdots & \vdots & \ddots & \vdots & \vdots \\ A_{d,1}^{S} & \cdots & A_{d,d}^{S} & \Gamma_{d,1}^{S} & \cdots & \Gamma_{d,p}^{S} & \Gamma_{d,p+1}^{S} \\ 0 & \cdots & 0 & 0 & \cdots & 0 & \beta_{d}^{S} \end{bmatrix}$$

In this form, various transformations can easily be expressed: by affecting  $A^S$  one defines a loop interchange (2.6), skewing or loop reversal; by altering  $\Gamma^S$  one generates shifting transformations, as in Listing 2.5; and by modifying  $\beta^S$  one can redefine the execution order of the instructions, equivalent to performing loop fission or loop fusion.

For the matrix multiplication example from Listing 2.4 one obtains:

$$A^{S_1} = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix} \qquad \Gamma^{S_1} = \begin{bmatrix} 0 & 0 \\ 0 & 0 \end{bmatrix} \qquad \beta^{S_1} = \begin{bmatrix} 0 \\ 0 \\ 0 \end{bmatrix}$$

$$A^{S_2} = \begin{bmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{bmatrix} \qquad \Gamma^{S_2} = \begin{bmatrix} 0 & 0 & 0 \\ 0 & 0 & 0 \\ 0 & 0 & 0 \end{bmatrix} \qquad \beta^{S_2} = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}$$

Considering two statements at the same loop level as in Listing 2.3, the three matrices are for each statement respectively:

$$A^{S_1} = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix} \qquad \Gamma^{S_1} = \begin{bmatrix} 0 & 0 \\ 0 & 0 \end{bmatrix} \qquad \beta^{S_1} = \begin{bmatrix} 0 \\ 0 \\ 0 \end{bmatrix}$$

$$A^{S_2} = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix} \qquad \Gamma^{S_2} = \begin{bmatrix} 0 & 0 \\ 0 & 0 \end{bmatrix} \qquad \beta^{S_2} = \begin{bmatrix} 0 \\ 0 \\ 1 \end{bmatrix}$$

This unified representation can describe a wide set of polyhedral transformations as well as compositions of such transformations in the view of generating efficient parallel code.

## 2.1.5 Static dependence analysis

Such loop transformations need to be validated according to the semantics of the sequential execution, to ensure that the resulting code preserves its correctness. The mechanism of dependence analysis was introduced for this purpose, studied extensively by Feautrier [42].

**Definition 9:** (Dependence of Statement Instances) Two statements S and R are said to be dependent, if there exist two instances  $S(\vec{x_S})$  and  $R(\vec{x_R})$ , where  $\vec{x_S}$  and  $\vec{x_R}$  belong to the iteration domains of S and R, respectively such that  $S(\vec{x_S})$  and  $R(\vec{x_R})$  access the same memory location and at least one is a write.

If in the original sequential order  $S(\vec{x_S})$  is executed before  $R(\vec{x_R})$ , R is said to be dependent on S. Under these circumstances, S is called the *source* and R is the *destination* of the dependence. Reversely S depends on R, if R is executed first in the sequential order.

To preserve the semantics, the execution of two dependent statements must be the same in the original sequential and in the transformed parallel order. On the other hand, two independent statement can be executed in arbitrary order.

Dependences are classified in three categories, depending on the order of read and write operations:

- RAW: read-after-write, or flow dependence;

- WAR: write-after-read, or anti-dependence;

- WAW: write-after-write, or output dependence;

Note that RAR, read-after-read, is not considered a dependence, since the memory is not altered, hence the order of execution of the two read operations is arbitrary. However, these accesses are considered by some optimizations to improve data locality.

Various algorithms have been designed to rewrite *anti-* and *output dependences*, which alter the same memory location. The most common strategies are privatization [106], renaming or expansion [43], such that the constraints are relaxed and more optimizing techniques become legal.

The formal representation of the dependences occurring in a loop nest is in the form of a dependence polyhedron,  $\mathcal{P}_e$ . Intuitively, if two dynamic instances  $S(\vec{x_S})$  and  $R(\vec{x_R})$  are dependent, there exists a relation  $\{\vec{x_S} \to \vec{x_R}\}$ . If  $|\vec{x_S}| = |\vec{x_R}|$  there exist an edge in the polyhedron  $\mathcal{P}_e$ , having as vertices  $S(\vec{x_S})$  and  $R(\vec{x_R})$ . Note that, the statements S and R need not be distinct, only the dynamic instances  $S(\vec{x_S})$  and  $R(\vec{x_R})$  must be different.

## 2.1.6 Dependence vectors

If  $R(\vec{x_R})$  depends on  $S(\vec{x_S})$ , or simply denoted  $R(\vec{j})$  depends on  $S(\vec{i})$ , one has that sequentially S(i) is executed before R(j). In loop dependence analysis [8], this is equivalent to saying that iteration j of loop L depends on iteration i, where L contains the statements S and R. Then, R depends on S with:

- the distance vector  $\vec{d} = \vec{j} \vec{i}$ ;

- the direction vector  $\sigma = \operatorname{sig}(\vec{d})$ ;

The sign of an integer i, denoted  $\sigma$  is

$$sig(i) = \begin{cases} 1, & if \ i > 0, \\ -1, & if \ i < 0, \\ 0, & if \ i = 0. \end{cases}$$

The sign of a vector  $\vec{d} = (d_1, d_2, ..., d_m)$  is  $sig(\vec{d}) = (sig(d_1), sig(d_2), ..., sig(d_m))$ ;

• at level  $\mathbf{l} = \mathbf{lev}(\vec{d})$ .

Given that m is the depth of the loop L, for a distance vector  $\vec{d} = (d_1, d_2, ..., d_m)$ , the *leading element* is the first non-zero element. If this is  $d_l$ , then l represents the *level* of  $\vec{d}$  and  $1 \leq l \leq m$ . Also, the level of the zero vector is defined to be m+1. The vector d is said to be *lexicographically positive* or *negative* if its leading element is positive or negative, respectively.

A distance vector or a direction vector of a dependence must always be lexicographically non-negative. Thus, considering the dependence vector  $\vec{d}$  at level l, of statements S and R,  $l \in \{1, 2, ..., m+1\}$ . If  $1 \le l \le m$  we say that the dependence of R on S is carried by the loop of depth l. The dependence of R on S is loop independent (not carried by any loop) if l = m+1, equivalent to  $\vec{d} = \vec{0}$ .

Only loop-carried dependences between statements contribute to the computation of dependences between iterations.

Using the distance vectors, one can compute the *dependence matrix* of the loop L, whose rows are the distance vectors of all the dependences in L, in any order.

## 2.1.7 Polyhedral transformations

Once the dependences between iterations are computed, one can apply polyhedral transformations (schedules) such that no dependence violations occur. Such transformations are applied in the view of improving the performance, for instance via better data locality, or to exhibit parallelism. Transformations represent a reordering of the execution of instructions and are defined as scheduling matrices  $\Theta^S$  associated to statements.

Frequently, aggressive optimizations inhibit parallelism, due to loops fusion, strength reduction, replacing arrays with scalars etc. To overcome this problem, one requires to apply optimizations such as scalar expansion, induction variable detection, loop splitting and skewing, to recover the parallelism opportunities. Selecting the optimal sequence of transformations opens an entire area of research, notorious for being a difficult combinatorial problem. We refer the reader to the works of Kennedy and Allen [2], Wolf and Lam [133] proposing loop transformations to maximize parallelism. In the geometrical frame of the polytope model [44,45], one can generalize and handle all affine transformations in a unitary manner.

To validate a schedule  $\theta$  one computes the scalar product between each of the transformation matrices  $\Theta_S$  and the dependence matrix. If in the resulting matrices, the first non-null component of each row is positive, the schedule is valid. The outermost parallel loop level is given by the first column in the resulting matrix in which all elements are null.

## 2.1.8 Concluding remarks

The polytope model is a robust and efficient framework for statically analyzable, affine codes. However, these constraints restrict its applicability to scientific codes mostly. To fight against the limitations of the polytope model, several research directions revolve around addressing the problem of scalability, as a trade-off that reduces optimality by splitting the program and introducing approximations to increase scalability [126]. Another very well researched area targets vectorization: programs are transformed in order to generate efficient SIMD code [55]. The works of Cavazos et al. [23, 92] are dedicated to find the optimal sequence of transformations to be applied in an iterative compilation framework. Extending the polytope model to general purpose codes, non-statically analyzable, is a challenge, as computing dependences online, validating a transformation and generating parallel, optimized code at runtime might incur considerable overhead. Still, this outlines our goal of dynamically optimizing general purpose codes, by applying polyhedral transformations in combination with speculative parallelization.

## 2.2 General overview of traditional TLS systems

As dynamic transformations rely on predictions in case of non-statically analyzable codes, significant research efforts have been devoted to building speculative frameworks, which allow optimistic optimization and parallelization of codes. Known under the

name of *TLS systems (Thread Level Speculation)*, they provide a mechanism to execute speculatively transformed code and a recovery strategy, that guarantees the correctness of the results, should a misprediction occur.

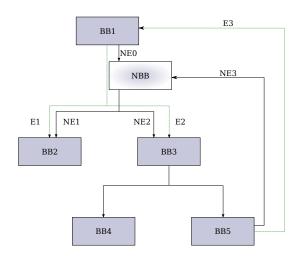

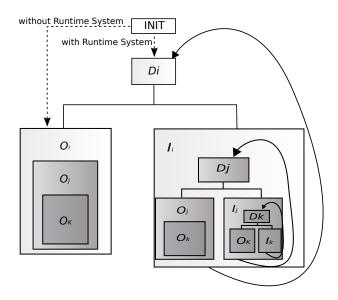

The overview of a traditional TLS system is depicted in Figure 2.3. It consists of two main phases: a first phase performed at compile-time (static), and a second phase performed at runtime (dynamic). The first phase consists of analyzing the code in order to extract general and relevant properties, as data dependences that can be disambiguated without requiring runtime information. It is also the place where, for some TLS systems, the targeted code snippets are prepared for runtime parallelization. Some systems also include a preliminary profiling step in order to be helped by some dynamic information at compile-time, provided that the same behavior will occur during the real execution.

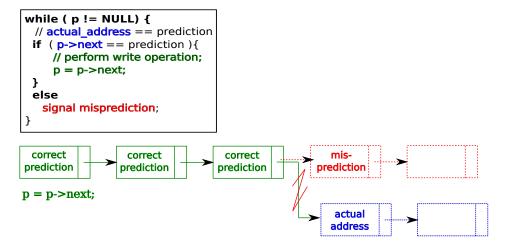

At runtime, often the target code is profiled on some execution samples in order to capture dynamic information relevant for parallelization. Classically, dynamic dependence analysis is performed, as well as some modeling of values taken by scalar variables, or values of memory addresses that are accessed. This modeling is usually dedicated to building a prediction mechanism to remove dependencies and predict the starting values used by the parallel speculative threads. In our proposal, we use multivariate linear interpolation to model the behavior observed during online profiling.

Information collected and computed from this online profiling can then be used to apply code transformations supposed to improve the forthcoming parallelization. In most TLS systems, this step is reduced to straightforward transformations, as simply cutting the outermost loop in slices that will be run in parallel. Our proposal distinguishes from previous proposals by providing elaborated scheduling transformations, as it will be shown in the rest of this thesis.

Then, during the parallel run of the code, speculation is verified in order to ensure correct semantics. Such verification usually consists of detecting conflicting accesses to the referenced memory locations. In our proposal, this is achieved by comparing each actual memory access to the predicted one. In case of misspeculation, the incorrect computations have to be canceled and the memory restored to a correct state. Usually, this is achieved by re-executing the faulty thread for which a conflicting memory access has been detected. In our proposal, the global orchestration, that executes the target loop nest by successive chunks, implements the rollback as the cancelation of the last executed chunk. Then, a chunk containing the original sequential version of the code is run to overcome the misprediction point.

In the next section, we reference some of the most representative works on staticdynamic platforms for code analysis and optimization and for speculative parallelization.

## 2.3 State of the art

There has been a considerable amount of research in TLS systems which propose speculative execution of threads, sometimes requiring architectural support, relying on hypothetical hardware mechanisms and simulators [63,76,90,103,105]. Since our proposal is a *software-only* framework, our reviews focus mostly on works of this type.

2.3. State of the art

Figure 2.3: Overview of a TLS system

Automatic parallelization One of the early proposals exploring TLS systems is [114] targeting an approach that scales on various shared-memory architectures. Since TLS requires to detect dependences violations at runtime, they propose to leverage the invalidation-based cache coherence. According to this method, the processor must first invalidate all copies of a cache line, prior to modifying it. Steffan *et al.* propose to extend this strategy and adapt it for TLS systems, by invalidating copies that were speculatively loaded in the past, in case the modification request comes from an iteration that executes before the ones that use the copies, in the sequential order.

POSH [76] is a compilation framework for transforming the program code into a TLS compatible version, by using profile information to improve speculation choices. A similar approach is presented in [63]. The Mitosis compiler [103] generates speculative threads as well as pre-computation slices (p-slices) dedicated to compute in advance values required for initiating the threads. The LRPD test [106] speculatively parallelizes forall loops that access arrays and performs runtime detection of memory dependences. Such technique is applicable only when the array bounds are known at compile time. Tian et al. [119] focus on the efficient exploitation of pipeline parallelism using a data speculation runtime system which creates copies of statically, as well as dynamically allocated data, on-demand. Similar to [104], this study handles only single-level loops.

SPICE [105] is a technique using selective value prediction to convert loops into data parallel form. A similar approach is proposed in [117]. In [28], a speculative parallelization in chunks of the outermost loop is proposed, using a sliding window for reducing the impact of load imbalance. However this last proposal is limited to array-only applications.

Softspec [19] is a technique whose concepts represent preliminary ideas of our approach. Linear memory accesses and scalar values sequences are detected, resembling our strategy, but only for innermost loops. Hence one-variable interpolating functions are built and used for simple dynamic dependence analysis via the *gcd* test. Thus, only the innermost loop can be parallelized. However, their initialization and verification mechanisms are similar to ours.

Zhong et al. present in [137] several code transformation techniques to uncover the hidden parallelism and improve TLS efficiency, as speculative loop fission, infrequent dependence isolation or speculative prematerialization.

Kulkarni et al. propose the system Galois [70] to perform speculative auto-parallelization of codes with irregular data access patterns. Inspired from database applications, in which parallelism is fully exploited, while the implementation details are transparent to the user, they define a new abstraction for the sequential programs. Galois provides new classes, such as the Galois sets and the Galois iterators, which programmers can use to highlight opportunities to exploit parallelism. Parallelization relies on a form of "scientific commutativity", i.e. non-deterministic results, yet still correct. The underlying operations of the speculative system (commutativity, rollback) are defined by descriptions given by the developer. For commutativity, the programmer annotates the code to emphasize whether the execution of different methods can be interleaved; while the rollback mechanism performs a copy of the memory area from which it restores the state in case of a misspeculation. The Galois system consists in the classes

2.3. State of the art