# Nouveaux concepts pour l'intégration 3D et le refroidissement des semi-conducteurs de puissance à structure verticale

Kremena Vladimirova

# ▶ To cite this version:

Kremena Vladimirova. Nouveaux concepts pour l'intégration 3D et le refroidissement des semi-conducteurs de puissance à structure verticale. Autre. Université de Grenoble, 2012. Français. NNT: 2012GRENT049. tel-00738000v2

# HAL Id: tel-00738000 https://theses.hal.science/tel-00738000v2

Submitted on 17 Jul 2013

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE GRENOBLE

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : **Génie électrique**Arrêté ministériel : 7 août 2006

Présentée par

# Kremena VLADIMIROVA

Thèse dirigée par Christian SCHAEFFER et codirigée par Jean-Christophe CREBIER et Yvan AVENAS

préparée au sein du Laboratoire de Génie Electrique de Grenoble (G2Elab) dans l'École Doctorale « Electrotechnique Electronique Automatique et Traitement du Signal »

# Nouveaux concepts pour l'intégration 3D et le refroidissement des semi-conducteurs de puissance à structure verticale

Thèse soutenue publiquement le **11 mai 2012**, devant le jury composé de :

# M. Thierry LEBEY

Directeur de recherche, CNRS Toulouse, Président M. Hervé MOREL

Directeur de recherche, CNRS Lyon, Rapporteur

M. Henri SCHNEIDER

Maître de conférences, INP-Toulouse, Rapporteur

M. Laurent DUPONT

Chargé de recherche, IFFSTAR, Versailles Membre

M. Olivier LESAINT

Directeur de recherche, CNRS Grenoble, Membre

M. Christian SCHAEFFER

Professeur des universités, INP-Grenoble, Membre

M. Yvan AVENAS

Maître de conférences. INP-Grenoble. Membre

M. Jean-Christophe CREBIER

Chargé de recherche, CNRS Grenoble, Membre

# Remerciements

Sur cette page dédiée aux remerciements je souhaite m'adresser à toutes les personnes qui m'ont aidé à grandir dans l'univers des sciences et des technologies durant ces trois années de thèse.

Je tiens tout d'abord à remercier l'ensemble des membres de mon jury de thèse ; Thierry Lebey d'avoir accepté d'être le président de ce jury ; Hervé Morel et Henri Schneider d'avoir accepté d'être rapporteurs de mon travail de thèse ; Laurent Dupont et Olivier Lesaint d'avoir accepté de faire partie de ce jury en tant qu'examinateurs.

Un grand merci à mon directeur de thèse Christian Schaeffer pour la confiance qu'il m'a accordé, pour son honnêteté et ses compétences scientifiques et humaines.

J'adresse ma profonde reconnaissance et mes sincères remerciements à mes encadrants Jean-Christophe Crebier et Yvan Avenas – mes maitres Jedi qui guidaient avec tant de dynamisme leur jeune padawan vers la lumière de la science. Je n'oublierai jamais nos réunions au cours desquelles des propositions, des solutions et des idées ruisselaient telle une source inépuisable née par leur passion envers la recherche. Merci!

Je remercie infiniment Claude Brun (Djidji) pour son aide précieuse pour la construction du banc de caractérisation expérimental. Merci Djidji pour ta patience, ta précision et tes compétences que tu partages si généreusement avec nous — les débutants dans le monde de la mécanique.

Je souhaite aussi remercier toutes les personnes du laboratoire qui m'ont apporté des conseils ou d'aide au cours de ma thèse – permanents, doctorants et également les stagiaires avec lesquels j'ai travaillé – mention spéciale pour mes stagiaires Julian, Fabien, Siyana, Nicolay et Georgy. Je tiens à remercier très spécialement Eric Vagnon pour son optimisme, ses idées précieuses et son implication dans les dernières mesures expérimentales.

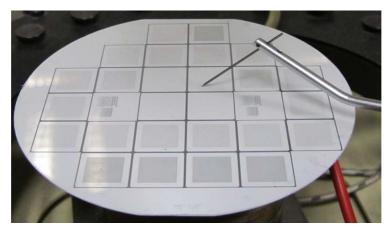

Je voudrais adresser mes remerciements à tout le personnel du CIME – Nanotech, Stephane Litaudon pour m'avoir confié tous les secrets d'utilisation de la DRIE, Delphine Constantin, Jean-Michel Terrot et Bruno Gonzalez pour leurs conseils et aides en salle blanche, Irene Pheng pour la découpe des wafers et les bondings de mes prototypes, Alexandre Chagoya pour son aide particulière concernant les outils de design, Loic Vincent pour sa disponibilité, sa bonne humeur et pour avoir supporté pendant toutes ces années toutes mes descentes en piqué dans son bureau pour lui poser des questions plus ou moins vitales.

C'est à l'homme avec qui j'ai partagé cette aventure mais d'un point de vue plus personnel à qui je souhaite témoigner mes remerciements les plus profonds. Merci Chris de m'avoir donné la force nécessaire pour repousser mes propres limites et d'avoir apporté tant de chaleur, de douceur et d'équilibre dans mon petit monde.

Un merci chaleureux à toute ma famille et plus particulièrement à ma mère qui m'a toujours soutenue et encouragée et qui dès l'âge de 3 ans en me montrant l'image suivante :

# Table des matières

| In | troduction gé     | nérale                                                                | 15       |

|----|-------------------|-----------------------------------------------------------------------|----------|

| C  | -                 | Le packaging et le refroidissement en électronique de<br>puissance    | e        |

| 1. | Introduction      |                                                                       | 21       |

| 2. | Packaging de      | es modules de puissance actuels                                       | 22<br>22 |

|    | 2.2. Packages 3I  | )                                                                     | 24       |

| 3  | Solution inno     | ovante du composant à tenue en tension verticale package              | 29       |

|    |                   | nsion périphérique des composants de puissance                        | 29       |

|    |                   | des terminaisons en tension verticales                                |          |

|    | 3.3. Terminaison  | ns planar versus terminaisons verticales pour une vre 3D              |          |

|    | 3.4. Evolution e  | t mise à profit de l'approche - puces muticomposants                  |          |

| 4. | Les techniqu      | es de refroidissement en électronique                                 | 39       |

|    |                   | s de transfert de chaleur                                             |          |

|    | 4.2. Refroidisser | nent des modules de puissance                                         | 41       |

|    |                   | ment direct                                                           |          |

|    | 4.4. Conclusion.  |                                                                       |          |

| 5. |                   | ovante du refroidisseur intégré dans le composant                     | 48       |

|    | 5.1. Présentation | n du concept                                                          | 49       |

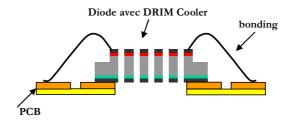

|    |                   | a composant de puissance avec DRIM Cooler                             |          |

|    |                   | uide diélectrique                                                     |          |

|    |                   | performances des composants avec DRIM Cooler                          |          |

|    |                   | contraintes des composants avec DRIM Cooler                           |          |

|    | 1                 | s conceptuelles                                                       |          |

| 6. | Conclusion.       |                                                                       | 63       |

| C  | -                 | Développements, choix technologiques et réalisation<br>les prototypes | s        |

| 1. |                   |                                                                       | 67       |

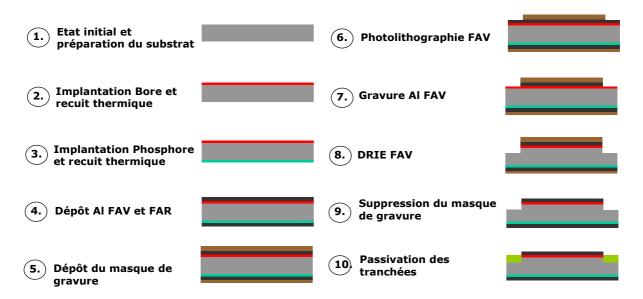

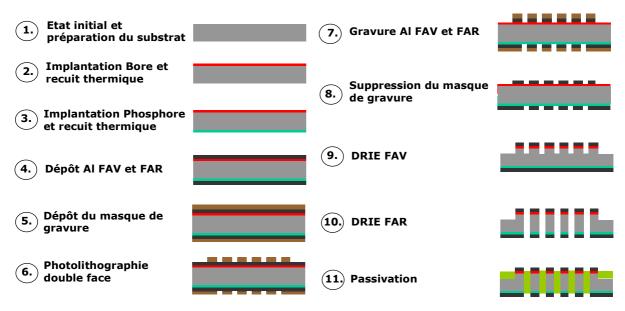

| 2. | Procédé tech      | nologique pour la réalisation pratique des diodes de                  |          |

|    | puissance à t     | erminaisons en tension verticales                                     | 67       |

|    |                   | des masques                                                           | 68       |

|    | 2.2. Diagramme    | de cheminement                                                        | 68       |

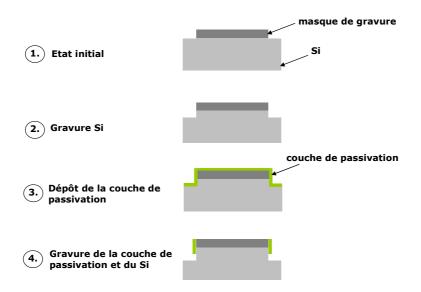

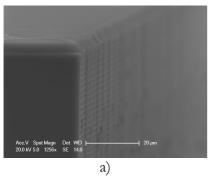

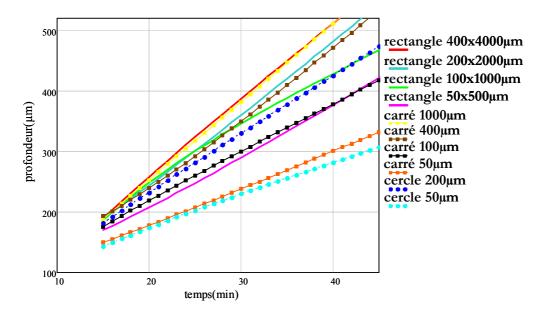

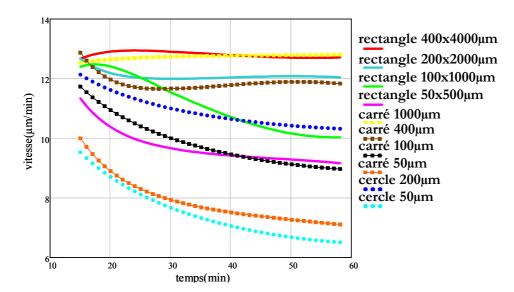

|    | 2.3. Gravure pro  | ofonde du silicium (DRIE)                                             | 69       |

|    |                   | alités                                                                | 69       |

|    |                   | ularités de la gravure DRIE                                           |          |

|    |                   | re des tranchées verticales                                           |          |

|    |                   | mique et amenée de courant                                            |          |

|    | 2.5. Passivation  | des tranchées verticales                                              | 77       |

# Table des matières

| 3. | Procédé technologique pour la réalisation pratique des diodes de puissance avec DRIM Cooler | 79         |  |  |  |  |

|----|---------------------------------------------------------------------------------------------|------------|--|--|--|--|

|    | 3.1. Dimensionnement et réalisation des masques                                             | 79         |  |  |  |  |

|    | 3.2. Diagramme de cheminement                                                               | 80         |  |  |  |  |

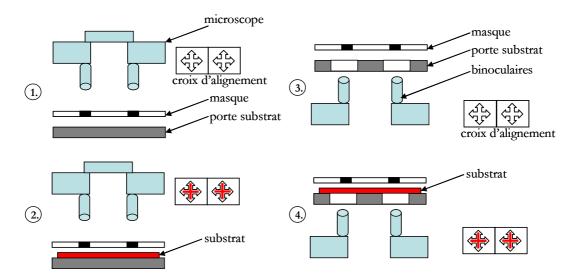

|    | 3.3. Lithographie double face                                                               | 81         |  |  |  |  |

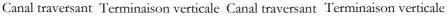

|    | 3.4. Particularités du procédé DRIE pour la réalisation des canaux traversants              | 82         |  |  |  |  |

|    | 3.5. Passivation                                                                            | 84         |  |  |  |  |

| 4. | Conclusion.                                                                                 | 85         |  |  |  |  |

| C  | Chapitre III. Analyse et validation pratique des performances                               |            |  |  |  |  |

|    | électriques                                                                                 |            |  |  |  |  |

| 1. | Introduction                                                                                | 89         |  |  |  |  |

| 2. | Dimensionnement                                                                             | 90         |  |  |  |  |

| 3. | La jonction plane                                                                           | 96         |  |  |  |  |

| 4. | Performances électriques des diodes de puissance à terminaisons                             |            |  |  |  |  |

|    | en tension verticales                                                                       |            |  |  |  |  |

|    | 4.1. Analyse théorique de la tenue en tension                                               | 99         |  |  |  |  |

|    | 4.2. Validation expérimentale                                                               |            |  |  |  |  |

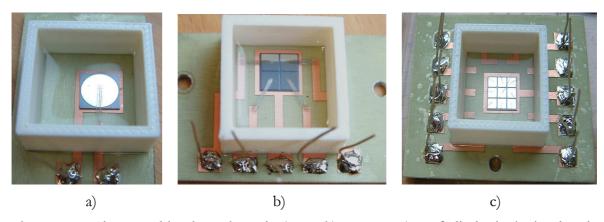

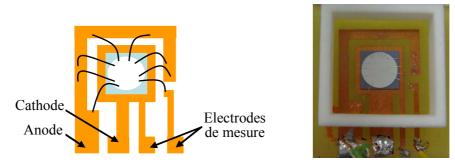

|    | 4.2.1. Réalisation du package                                                               |            |  |  |  |  |

|    | 4.2.2. Caractérisation statique                                                             | 107        |  |  |  |  |

| _  | 4.2.3. Caractérisation dynamique                                                            | 116        |  |  |  |  |

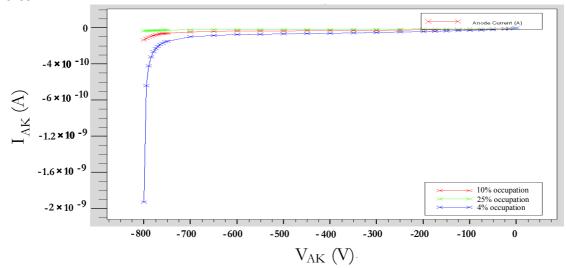

| 5. | Performances électriques des diodes de puissance avec DRIM                                  | 100        |  |  |  |  |

|    | Cooler                                                                                      | 120<br>120 |  |  |  |  |

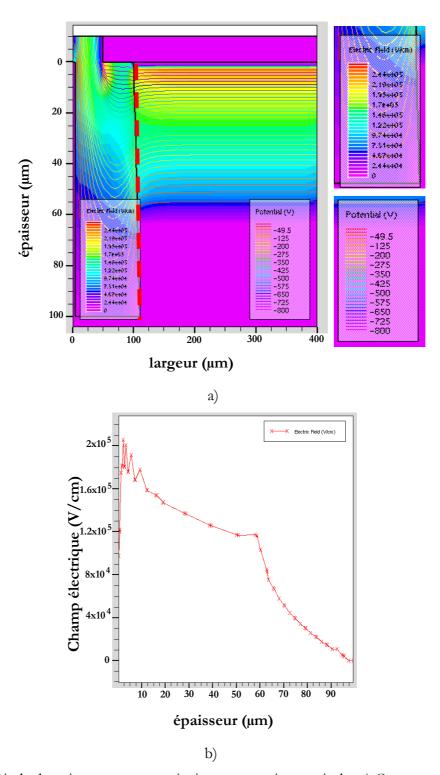

|    | 5.1. Analyse théorique de la tenue en tension                                               | 120        |  |  |  |  |

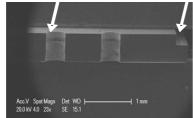

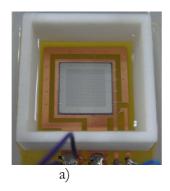

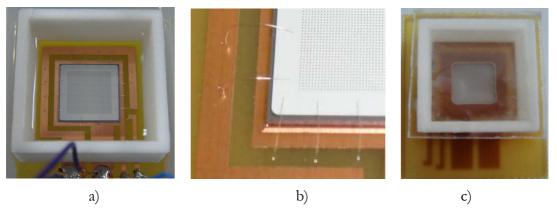

|    | 5.2.1. Réalisation du package.                                                              | 125        |  |  |  |  |

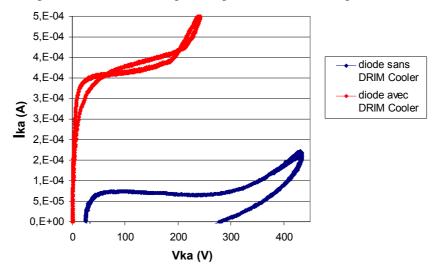

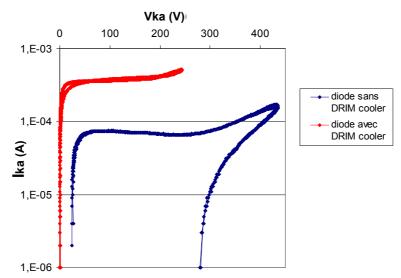

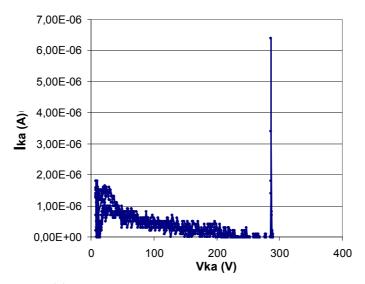

|    | 5.2.2. Caractérisation statique                                                             | 127        |  |  |  |  |

| 6. | Conclusion                                                                                  | 132        |  |  |  |  |

| 0. | Conclusion                                                                                  | 132        |  |  |  |  |

| C  | Chapitre IV. Etude et validation pratique des performances                                  |            |  |  |  |  |

|    | thermiques des diodes de puissance avec DRIM                                                |            |  |  |  |  |

| 1  | Cooler                                                                                      | 135        |  |  |  |  |

| 1. | Introduction                                                                                | 133        |  |  |  |  |

| 2. | Rappel des notions de transfert de chaleur lors de l'écoulement                             |            |  |  |  |  |

|    | d'un fluide                                                                                 | 135        |  |  |  |  |

|    | 2.1. Nombre de Reynolds                                                                     | 135        |  |  |  |  |

|    | 2.2. Nombre de Prandtl                                                                      | 136        |  |  |  |  |

|    | 2.3. Longueurs d'établissement hydraulique et thermique                                     | 136        |  |  |  |  |

|    | 2.4. Nombre de Nusselt.                                                                     | 137        |  |  |  |  |

| 2  | 2.5. Pertes de charge et coefficient de frottement.                                         | 138        |  |  |  |  |

| 3. | Analyse théorique des performances thermiques du concept                                    |            |  |  |  |  |

|    | de refroidissement DRIM Cooler                                                              | 139        |  |  |  |  |

|    | 3.1. Modélisation analytique.                                                               | 140        |  |  |  |  |

# Table des matières

| 4. | 3.2. Modélisation numérique                                | 143<br>148 |

|----|------------------------------------------------------------|------------|

| ١٠ | du concept de refroidissement DRIM Cooler                  | 149        |

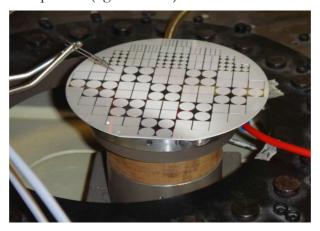

|    | 4.1. Présentation du banc de caractérisation expérimentale | 150        |

|    | 4.2. Résultats obtenus.                                    | 151        |

|    | 4.3. Problèmes rencontrés                                  | 153        |

| 5. | Conclusion                                                 | 154        |

| Co | onclusion générale                                         | 159        |

| Ré | férences bibliographiques                                  | 163        |

| Pu | ıblications                                                | 171        |

# Introduction générale

Notre société est en pleine mutation énergétique avec d'un coté l'épuisement des ressources fossiles et de l'autre l'urgence en matière de maîtrise énergétique. Cela se traduit par diverses évolutions qui, globalement, favorisent ou convergent vers le vecteur électricité. D'une part, l'électricité tend à remplacer les énergies fossiles et d'autre part, des travaux importants visent à optimiser l'utilisation de l'énergie électrique. C'est par exemple le cas au niveau des transports avec depuis longtemps le transport ferroviaire et plus récemment avec l'émergence des véhicules hybrides et électriques ou encore de l'avion plus électrique. On retrouve également les énergies renouvelables dont la production permet dans certaines conditions de réduire le recours aux énergies fossiles. Enfin, des efforts importants sont engagés pour mieux utiliser l'énergie électrique dans l'industrie ou dans l'habitat. Tous ces exemples ont un point commun, l'électronique de puissance, discipline à part entière, interface de contrôle et de conditionnement de l'énergie électrique permettant d'adapter, le plus idéalement possible la source à la charge. On parle aussi souvent d'électronique de commutation car l'approche mise en œuvre pour associer source et charge consiste à découper, cadencer puis filtrer les grandeurs électriques pour en contrôler les formes, amplitude, phase et fréquence. Ce qui caractérise l'apport de l'électronique de puissance est la nécessité d'adapter par exemple l'énergie alternative fournie par le réseau électrique de distribution en une tension continue à même d'alimenter un ordinateur portable et ceci en offrant le meilleur compromis en termes de rendement, de fiabilité et de coût. Si le rendement est longtemps resté le principal objectif de conception en électronique de puissance, la très forte augmentation et diversification des applications et des contraintes de fonctionnement de ces dernières années ont fait évoluer cette discipline qui restait quelque peu marginale. Aujourd'hui, l'électronique de puissance est en pleine mutation matérielle, technologique et conceptuelle. Des matériaux aux propriétés exceptionnelles apportent un renouveau tant au niveau des composants actifs qu'au niveau des composants passifs de filtrage. De nouvelles technologies de packaging et d'intégration permettent de généraliser la mise en œuvre des composants, simplifiant et fiabilisant les interconnexions électriques mais aussi mécaniques. Enfin, de nouveaux concepts émergent pour mieux tirer profit des structures de conversion, des caractéristiques de tel ou tel composant. De nouvelles topologies optimisant les moyens de filtrage voient le jour, de nouveaux système d'alimentation et de pilotage des transistors sont mis au point, des techniques de pilotage astucieuses sont imaginées. Cette mutation bouscule l'approche traditionnelle de la conception et de la fabrication en électronique de puissance, l'objectif restant d'obtenir des rendements de conversion élevés mais cette fois-ci dans des contextes et avec des niveaux de contraintes technico économiques beaucoup plus exigeants.

On retrouve parmi les travaux importants et en cours dans ce processus d'évolution la mise en œuvre des composants de puissance actifs, les transistors et les diodes de puissance. La mise en œuvre de ces composants a subi il y a une quinzaine d'années environ une très forte évolution avec l'arrivée du module de puissance. Les modules de puissance avaient pour caractéristiques principales le regroupement dans un objet unique de plusieurs composants actifs de puissance, pré-assemblés et pré-interconnectés. Basés sur le report des puces sur un substrat paterné isolant d'un coté, interconnectables selon un plan de câblage systématique, offrant passivation et protection aux éléments sensibles, les modules de puissance ont particulièrement structuré la conception des convertisseurs statiques. En traitant d'un coup les interconnexions électriques des semi-conducteurs, leur refroidissement et leur encapsulation, les modules de puissance ont offert une réponse globale et générique aux concepteurs. Les performances des composants ont évolué et de nouvelles générations de contraintes ont également vues le jour. La montée en fréquence, la montée en température de fonctionnement des puces, la robustesse des assemblages ont permis de pousser les modules aux limites de leurs possibilités. Depuis quelques années, de nouvelles générations de modules de puissance voient le jour. Celles-ci intègrent par exemple davantage de fonctionnalités comme des capteurs, des drivers avec les IPEM (Integrated ou Intelligent Power Electronic Module), des moyens de filtrage, etc... L'une des évolutions les plus fortes concerne probablement l'assemblage en 3D des puces qui remet très fortement en cause les fondements

mêmes du module de puissance, basé sur un agencement 2D des puces et des interconnexions entre puces. La structuration en 3D des modules de puissance regroupant par exemple une pluralité de cellules de commutation ouvre de nouveaux degrés de liberté mais pose également de nouvelles contraintes.

- comment gérer les contraintes thermomécaniques des empilements ?

- comment évacuer le flux de chaleur généré au sein de ces empilements ?

- comment gérer les amenées de courant, sans pénalité pour la tenue en tension des composants de puissance basés sur des terminaisons planar ?

C'est de ces nouvelles problématiques qu'est né le travail de recherche décrit dans ce manuscrit. L'intégration 3D, avec son cortège de nouveaux degrés de libertés apporte aussi de nouvelles contraintes et problématiques dont la communauté scientifique devait se saisir. Au G2Elab, depuis quelques années, des travaux avaient été initiés dans cette thématique avec comme angle de vue la conception couplée entre le composant de puissance et son environnement. L'idée retenue dans cette approche consistait à s'autoriser à remettre en question non seulement le packaging des composants de puissance mais également la structure même de ceux-ci, le compromis idéal pouvant logiquement apparaître si des efforts étaient faits des deux cotés du problème. Fort d'un accès aux technologies de fabrication des composants de puissance et fort d'une connaissance système multi-physiques importante, il devenait possible d'imaginer également de modifier et/ou adapter le composant de puissance, non pas dans sa structure fonctionnelle interne, semi-conductrice, mais plutôt au niveau de ses interfaces avec son environnements, que les échanges aux interfaces soient électriques, thermiques ou encore mécaniques. Les travaux concernant le nouveau concept de packaging des composants de puissance nommé Power Chipon-Chip (PCoC) avaient clairement fait apparaître tout l'intérêt de l'empilement 3D des puces de puissance constituants les cellules de commutation des convertisseurs statiques mais ils avaient aussi fait ressortir deux problématiques essentielles :

- quelles finitions de surface les composants doivent avoir pour favoriser l'empilement des puces, intercalées entre les terminaux de puissance du convertisseur ?

- comment évacuer la chaleur produite par les puces situées au milieu de l'empilement ?

Ce travail de thèse se situe précisément dans ce contexte et a pour objectif d'offrir une ou des réponses à ces nouvelles questions. C'est un travail à la frontière de l'état de l'art en électronique de puissance qui marie nouveaux concepts, matériaux et technologies. Il est focalisé sur la conception couplée composant-package de puissance, remettant en cause la finition aux interfaces du composant de puissance et créant, en son sein de nouvelles interfaces et de nouveaux chemins de propagations des grandeurs physiques.

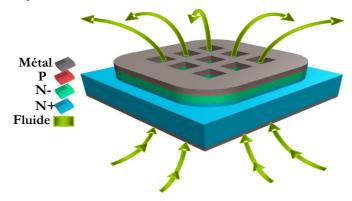

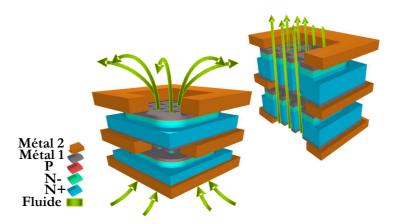

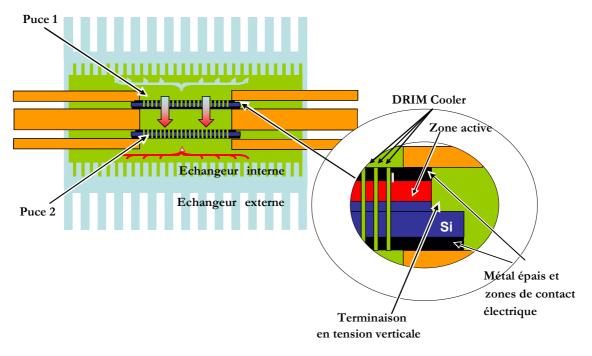

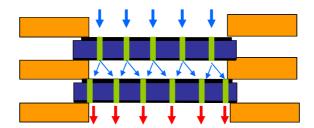

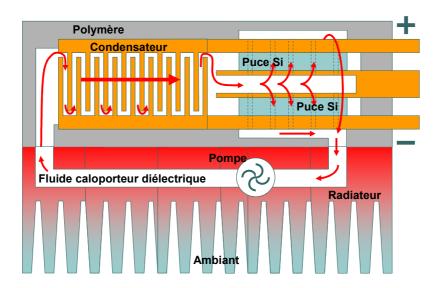

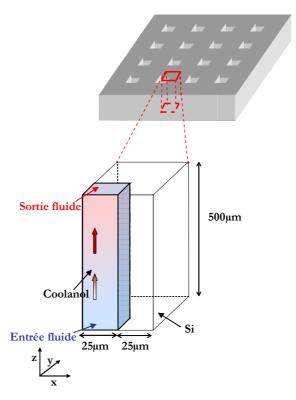

Le premier chapitre de la thèse s'attachera avant tout à mieux formaliser et mieux positionner la problématique. Nous verrons avec plus de détails ce qu'est le rôle d'un module de puissance, ses principales caractéristiques et enfin ses limitations. Nous verrons alors comment l'intégration 3D a modifié la vision du concepteur tant au niveau des interconnexions électriques, qu'au niveau des moyens de refroidissement pouvant être mis en place. Sur la base de ces analyses, nous présenterons l'approche explorée dans le cadre de la thèse visant à découpler, pour mieux les optimiser, les chemins suivis par l'énergie électrique et l'énergie thermique. Le concept nommé DRIM Cooler pour Drift Region Integrated Micro Channel Cooler sera alors présenté.

Une telle approche reposant sur la réalisation de composants de puissance avec refroidisseur intégré, le second chapitre sera consacré à l'introduction et la présentation du travail technologique qu'il fut nécessaire de mettre en place pour développer un tel concept. La prise en main de la filière de puissance et son évolution pour intégrer les étapes critiques à la nouvelle approche seront présentées. Les difficultés liées à la mise au point d'un procédé permettant de

réaliser le composant spécifique seront abordées. Des solutions pragmatiques seront proposées pour non seulement fabriquer les composants mais également rendre fonctionnelles les différentes évolutions proposées dans le premier chapitre.

La thèse étant orientée sur deux volets l'un électrique et l'autre plus thermique, le troisième chapitre sera consacré au premier des deux points laissant au quatrième et dernier chapitre le soin de présenter puis conclure sur les aspects thermiques de l'approche.

Au niveau électrique, l'enjeu du troisième chapitre sera de présenter la pertinence de l'approche d'un point de vue fonctionnel, l'objectif étant de décrire le développement d'une technique de terminaison en tension verticale à même de faciliter la mise en œuvre en 3D des composants de puissance mais également de rendre possible l'intégration de canaux au sein même du composant de puissance. Appuyé par des simulations numériques, des validations expérimentales et des mises en œuvre concrètes, ce troisième chapitre permettra au lecteur de peser les atouts et les contraintes du concept développé dans la thèse.

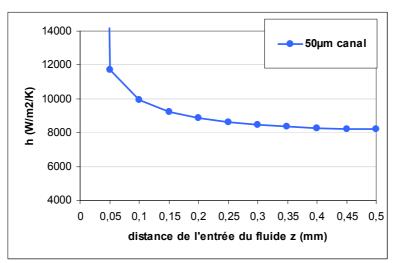

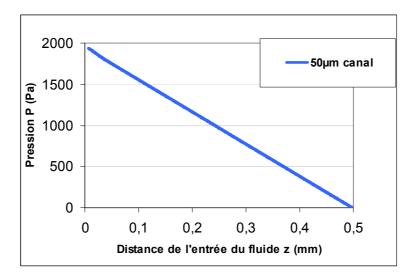

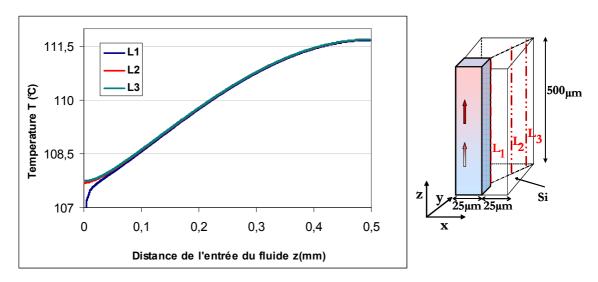

Le quatrième chapitre sera focalisé sur la modélisation et la caractérisation du dispositif avec refroidisseur intégré dans le composant de puissance. Appuyé d'une part sur des travaux de simulations numériques puis sur des travaux de caractérisations pratiques, le lecteur pourra mieux appréhender l'enjeu fonctionnel recherché durant ce travail de thèse. D'une part l'intégration du refroidisseur au sein même de la zone active du composant de puissance permet de limiter les interfaces entre le lieu des pertes et le fluide caloporteur, offrant un maximum de performances thermiques au système, mais également, une telle approche permet d'envisager le découplage des chemins électriques et thermiques et l'optimisation des gradients de température à la surface de la puce. Les limitations du concept seront également développées dans ce dernier chapitre pour donner au lecteur une vision claire et transparente de celui-ci.

# Chapitre I. Le packaging et le refroidissement en électronique de puissance

# Sommaire:

| 1. | Introduction                                                         |

|----|----------------------------------------------------------------------|

| 2. | Packaging des modules de puissance actuels                           |

|    | 2.1. Packages 2D.                                                    |

|    | 2.2. Packages 3D.                                                    |

| 3  | Solution innovante du composant à tenue en tension verticale         |

|    | adapté à son package                                                 |

|    | 3.1. Tenue en tension périphérique des composants de puissance       |

|    | 3.2. Le concept des terminaisons en tension verticales               |

|    | 3.3. Terminaisons planar versus terminaisons verticales pour une     |

|    | mise en œuvre 3D                                                     |

|    | 3.4. Evolution et mise à profit de l'approche - puces muticomposants |

|    | de puissance                                                         |

| 4. | Les techniques de refroidissement en électronique                    |

|    | 4.1. Mécanismes de transfert de chaleur.                             |

|    | 4.2. Refroidissement des modules de puissance                        |

|    | 4.3. Refroidissement direct                                          |

|    | 4.4. Conclusion.                                                     |

| 5. | Solution innovante du refroidisseur intégré dans le composant        |

|    | 5.1. Présentation du concept                                         |

|    | 5.2. Structure du composant de puissance avec DRIM Cooler            |

|    | 5.3. Choix du fluide diélectrique                                    |

|    | 5.4. Analyse des performances des composants avec DRIM Cooler        |

|    | 5.5. Analyse des contraintes des composants avec DRIM Cooler         |

|    | 5.6. Perspectives conceptuelles                                      |

| 6. | Conclusion                                                           |

## 1. Introduction

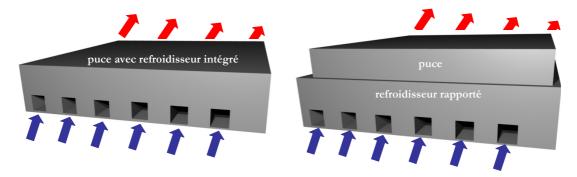

L'électronique de puissance est un domaine en croissance constante avec des demandes exigeantes concernant la gestion de l'énergie électrique avec le meilleur rendement, en proposant en permanence des solutions plus performantes, moins volumineuses et plus fiables, et tout cela à des coûts réduits. Ces ambitions constituent les principales motivations des développements technologiques visant à fabriquer des composants plus petits et plus puissants, augmentant le niveau des densités de pertes à évacuer. Ainsi, la gestion des contraintes thermiques et le choix d'un refroidissement efficace des modules ayant des densités de puissance élevées sont devenus des enjeux majeurs pour les électroniciens de puissance. Néanmoins, les systèmes de refroidissement proposés et utilisés aujourd'hui restent très traditionnels et leurs performances sont fortement conditionnées par la constitution du module.

Aujourd'hui les modules les plus « matures » et largement employés sont les modules « planaires » ou 2D dont la limitation la plus importante provient du fait que le refroidissement des composants ne peut être effectué que sur une seule face. Des solutions alternatives, motivées par le désir d'exploiter les deux faces du composant de puissance pour assurer son refroidissement, sont proposées avec les modules 3D. Toutefois, de nombreux verrous s'opposent à cette évolution naturelle comme par exemple le besoin d'adapter les matériaux fonctionnels ou d'interfaces utilisés, que ce soit au niveau des propriétés électriques, thermiques, mécaniques, thermomécaniques, ou encore le besoin de développer de nouvelles techniques de prise en contact avec la face avant du composant. Au delà de ces approches, on peut citer aussi le travail au niveau de la puce elle même afin de « l'adapter » au package prévu. C'est dans ce contexte que se situe ce travail de thèse. En effet, celui-ci s'inscrit dans une optique globale d'optimisation, d'adaptation et « d'évolution » du composant de puissance pouvant aller jusqu'à remettre en cause sa propre structure. La première solution innovante que nous proposons consiste à revoir l'agencement du composant en face avant pour simplifier sa mise en œuvre dans les assemblages 3D ce qui permet d'améliorer ses performances et son vieillissement. Une deuxième approche nous a mené vers une autre solution innovante permettant d'assurer un excellent refroidissement de la puce de puissance

Aujourd'hui la conception des puces, de leurs packages et de leurs systèmes de refroidissement est faite séquentiellement et leurs études sont donc traitées indépendamment. Avec ces travaux de recherche nous proposons une approche couplée puce/package/refroidissement associé visant à optimiser la mise en œuvre des composants de puissance dans un package 3D tout en prenant en compte simultanément les contraintes thermiques et CEM.

Dans ce chapitre nous allons d'abord présenter la conception des modules 2D et 3D afin d'introduire l'approche couplée de dimensionnement du composant de puissance et de son package. Le concept que nous proposons repose sur une technique de terminaison en tension de type tranchées profondes verticales réalisées en périphérie du composant permettant de modifier la répartition des potentiels en face avant de celui-ci afin de favoriser la mise en œuvre des prises de contact massives en face avant de la puce. Nous allons aussi présenter les degrés de liberté supplémentaires offerts par ce concept vis-à-vis de l'assemblage et des interconnexions de plusieurs composants dans le même substrat en silicium à l'échelle du wafer. Ensuite nous présenterons les principaux systèmes conventionnels de refroidissement associés aux modules de puissance en essayant de nous focaliser sur leurs forces et leurs faiblesses. Cette présentation nous permettra ensuite d'introduire le concept innovant de la puce intégrant une structure de refroidissement. Tout les intérêts de la démarche en termes de gain, de découplage des chemins de propagation thermique et électrique, de capacité de refroidissement, de densité d'intégration, de degrés de liberté vis-à-vis de la conception du refroidisseur et de nouvelles perspectives pour

l'assemblage des modules et des architectures en l'électronique de puissance seront aussi présentés et discutés.

# 2. Packaging des modules de puissance actuels

Le package des composants actifs de puissance a de multiples fonctions [BUT10]. Il doit permettre :

- les interconnexions électriques entre le ou les composants (dans le cas ou plusieurs composants sont montés dans le même module) et le circuit extérieur,

- l'évacuation de la chaleur hors du module lorsque le ou les composants sont en fonctionnement,

- la tenue mécanique et la protection de l'ensemble,

- l'isolation électrique interne et externe.

- une connectique aussi peu inductive que possible, des couplages électrostatiques et électromagnétiques les plus faibles possible.

Tous les packages doivent répondre à ces exigences. Toutefois, le choix du package optimal pour une application donnée est une étape cruciale puisqu'il va fortement influencer le comportement électrique, thermique ainsi que la fiabilité du composant ou du module.

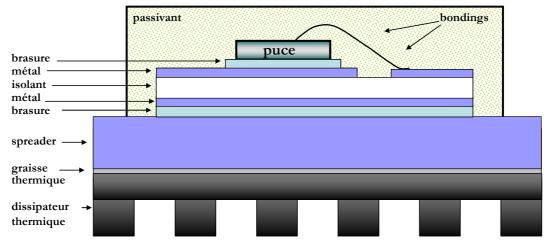

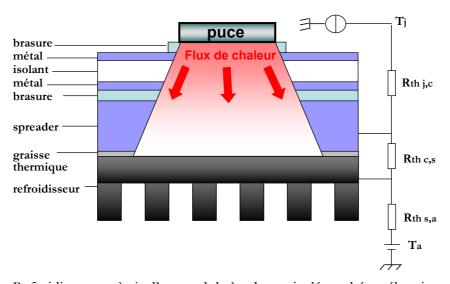

#### 2.1. Packages 2D

Les packages 2D sont aujourd'hui les plus utilisés dans les applications électroniques. Ce type de package, appelé aussi packaging planaire, consiste à reporter la ou les puces sur un empilement composé de plusieurs couches de matériaux différents (conducteurs et isolants électriques) que l'on appelle substrat (figure I.1.). Différents types de substrats isolés sont utilisés en électronique de puissance – il s'agit par exemple des SMI (substrats métalliques isolés), des substrats DBC (Direct Bonded Copper) et AMB (Active Metal Brazed) [MEN10]. Même si les technologies sont différentes, le rôle du substrat dans le module est toujours le même - le substrat assure les connections électriques des composants, la tenue mécanique et fournit les moyens pour l'assemblage avec le système de refroidissement. Sur l'exemple de la figure I.1., la face arrière du substrat est brasée sur une semelle (spreader) qui assure l'épanouissement du flux de chaleur pour favoriser l'évacuation des pertes et qui est elle-même fixée sur un dissipateur thermique.

Fig. I.1. - Vue schématique d'un module de puissance 2D.

Les connections électriques en face avant de la puce sont réalisées par des fils de bonding tandis que les connections en face arrière sont assurées par des brasures sur le substrat. Ainsi, le refroidissement du module ne peut être réalisé que sur une seule face puisque la présence des fils

de bonding ne permet pas d'utiliser la face avant des puces pour améliorer les échanges thermiques.

#### • Intérêts de l'assemblage 2D

Aujourd'hui, l'assemblage 2D (figure II.2.) domine le marché couvrant une gamme de puissances allant de quelques centaines de W à quelques MW. De fait, la technologie est bien connue et maitrisée. La production massive de ces modules a ainsi atteint un niveau de maturité et même de standardisation [IEC99].

Fig. I.2. - Exemple d'un module de puissance 2D [INF11].

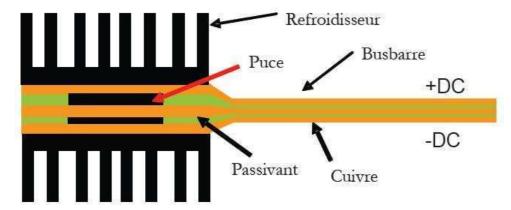

Un autre point fort des packages 2D est la possibilité d'insérer le module directement au niveau du bus barre qui relie directement les transistors et les diodes de puissance aux condensateurs de découplage (figure I.3.). Cela permet de réduire les inductances parasites du câblage et d'améliorer significativement la structure du module d'un point de vue électromagnétique.

Fig. I.3. - Module de puissance 2D associé à un bus barre [SCH05].

## • Limites de l'assemblage 2D

La technologie 2D présente plusieurs points limitant ses performances. Comme nous l'avons déjà mentionné, ce type d'assemblage constitue un ensemble de plusieurs matériaux comme le cuivre, la céramique, l'aluminium et le silicium ayant des coefficients de dilatation (CTE) assez différents. Ils subissent ainsi de forts stress et de fortes déformations pendant les cyclages thermiques. Ces contraintes thermomécaniques peuvent causer des fissures et des délaminages dans les brasures [MEN10] ou le substrat. Elles sont aussi la cause du décollement ou de la rupture des fils de bonding. Les variations brusques de température et les cyclages thermiques limitent la durée de vie et les performances de ce type de modules de puissance.

D'un point de vue électrique la limitation des packages 2D est due en particulier à leur susceptibilité aux contraintes électromagnétiques. En effet, les fils de bonding, les lyres de puissance et les pistes en cuivre du substrat induisent des inductances parasites de câblage qui provoquent des surtensions au niveau des interrupteurs lors des commutations. Cela peut aussi avoir comme effet de perturber le signal de commande de ces interrupteurs de puissance et de modifier les dynamiques de commutation. Ceci provoque en conséquence l'augmentation des pertes par commutation ce qui vient limiter la fréquence de découpage [MEN08]. Afin de réduire le caractère inductif de la maille de commutation, les puces doivent être placées au plus près les unes des autres ce qui induit une nouvelle contrainte pour le refroidissement du module qui d'autre part exige que les puces soient éloignées les unes des autres afin de pouvoir extraire plus facilement les calories produites lors de leur fonctionnement. Par conséquent pour chaque design d'un package 2D un compromis vis-à-vis des contraintes CEM/thermique doit être trouvé afin de garantir les performances désirées du module.

D'un point de vue thermique, la présence des fils de bonding en face avant de la puce de puissance signifie que l'extraction des calories ne peut être réalisée que par la face arrière qui sert à la fois au passage du courant et du flux de chaleur. Un tel couplage induit des contraintes au niveau électro-thermique qui imposent la réalisation d'un bon contact électrique et thermique sur la face arrière de la puce. Or, une comparaison de l'influence des résistances thermique et électrique de contact puce/substrat montre que la résistance thermique est la plus contraignante [VAG10]. Si le contact n'est pas bon, les performances thermiques du module sont mauvaises ce qui conduit à un déclassement important au niveau électrique car le pouvoir de dissipation est trop faible. Une approche qui propose le découplage des chemins de propagation électrique et thermique peut donc s'avérer particulièrement intéressante en ouvrant la voie vers de nouvelles structures d'assemblage des composants de puissance. Ce concept sera présenté plus loin dans ce chapitre.

Enfin, pour améliorer le refroidissement et la signature électromagnétique des modules de puissance, il paraît évident que l'une des pistes importantes consiste à revisiter la prise de contact en face avant des puces en passant d'une intégration 2D à une intégration 3D. Le paragraphe suivant est dédié à la description des modules 3D et à l'adaptabilité des puces de puissance afin de permettre un tel assemblage.

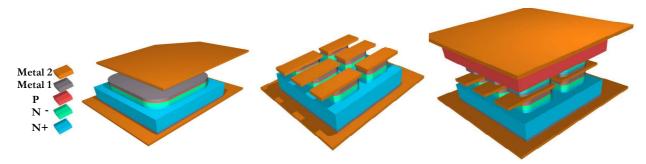

#### 2.2. Packages 3D

Dans le but d'obtenir des modules de puissance compacts avec une densité de puissance élevée tout en ayant une température de fonctionnement raisonnable, l'évolution naturelle des modules de puissance consiste en une approche tridimensionnelle (3D) qui permet d'améliorer les performances électromagnétiques mais aussi les échanges thermiques en utilisant la face avant des puces pour assurer un refroidissement double face.

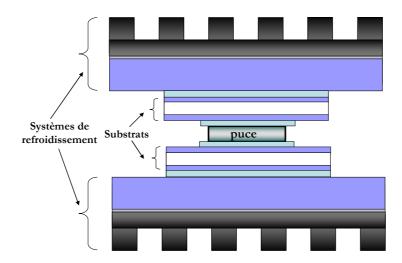

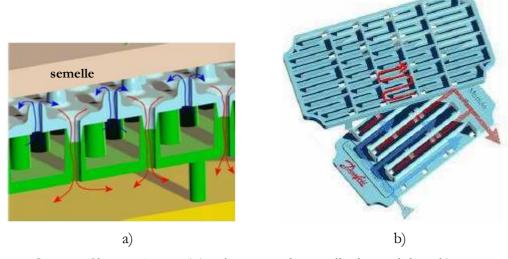

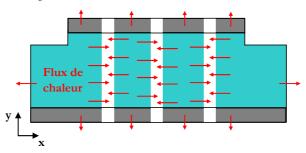

La figure I.4. montre le principe de l'assemblage 3D qui consiste à réaliser le même empilement brasure, substrat, système de refroidissement que celui utilisé dans les packages 2D mais cette fois sur les deux faces du composant de puissance.

Fig. I.4. - Vue schématique d'un module de puissance 3D.

Une telle configuration de prise en sandwich de la puce entre deux substrats permet d'améliorer significativement le refroidissement du module en favorisant l'extraction de la chaleur à travers une surface d'échange plus élevée que dans le cas des modules 2D. L'autre bénéfice des structures 3D est la réduction de l'inductance parasite issue des interconnexions entre les composants grâce à la suppression des fils de bonding en face avant des puces et la réduction de la taille des mailles de commutation.

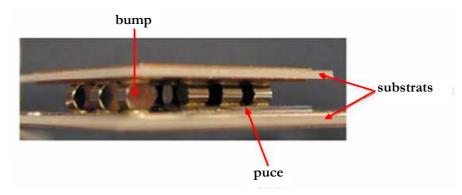

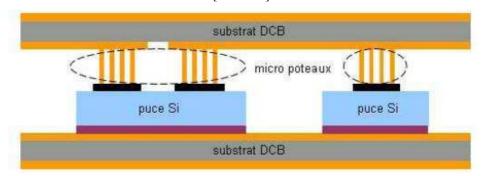

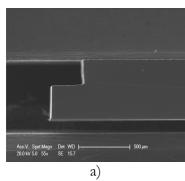

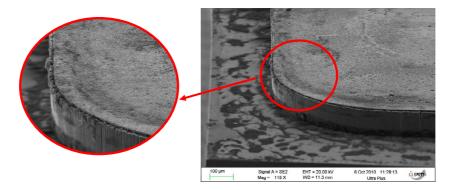

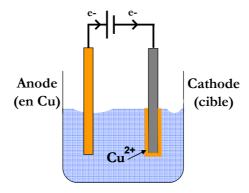

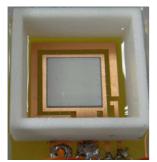

Afin de permettre l'assemblage des puces de puissance dans un package 3D, plusieurs familles d'interconnexions en face avant des puces ont été développées - contacts brasés, pressés, par ressorts, etc...Celles-ci sont très bien décrites dans la thèse de Ludovic Menager [MEN08] et dans [MEN10], et nous n'allons donc pas aborder ce point en détails. Ce que nous retiendrons c'est que dans tous les cas un traitement supplémentaire de la puce de puissance est obligatoire afin de l'adapter au package 3D prévu et de permettre la réalisation des interconnexions en face avant. Les zones d'interconnexion des composants de puissance sont métallisées en fonction de la technique de prise de contact. La plupart des composants de puissance produits industriellement aujourd'hui sont optimisés et fabriqués avec des finitions d'aluminium de faibles épaisseurs qui sont particulièrement adaptées aux interconnexions par fils d'aluminium. Toutefois, la métallisation d'aluminium ne permet pas la brasure directe et, dans le cas où l'on veut réaliser un contact brasé, la métallisation en face avant de la puce doit subir des étapes technologiques supplémentaires afin de la recouvrir avec d'autres métaux (Under Bump Metallisation) compatibles avec la brasure. En ce qui concerne les contacts pressés et par ressorts, la métallisation des puces doit être de plus forte épaisseur pour garantir une équipotentielle de qualité afin de ne pas altérer la distribution du courant à la surface du composant de puissance. Le métal et son épaisseur sont également optimisés pour "encaisser" la rugosité de surface des conducteurs électriques. Enfin, mentionnons seulement que d'autres travaux académiques sont aujourd'hui menés visant de faciliter les assemblages 3D comme par exemple la technologie nanoscratch, développée au laboratoire LAPLACE, en France, permettant de faire le report et l'interconnexion d'un composant de puissance grâce à la présence de nanopoteaux de cuivre sur le substrat et sur la puce [LUA08].

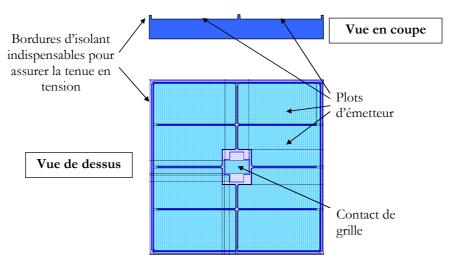

Ainsi, une optimisation couplée du composant de puissance et de son package est nécessaire afin d'obtenir un optimum global satisfaisant. Cela concerne les interconnexions mais aussi les géométries en face avant des puces qui peuvent être plus ou moins complexes. Pour illustrer cet aspect la figure I.5. montre un exemple de la géométrie d'un IGBT Infineon de référence SIGC121T60NR2C 600V /150 A [INF03] dimensions 11\*11mm, utilisé dans un assemblage 3D durant les travaux de thèse de Eric Vagnon [VAG10].

Fig. I.5. - Vue de dessus et vue en coupe d'un IGBT Infineon SIGC121T60NR2C 600V/150A [INF03].

Dans cet exemple, la face avant (vue de dessus) est composée de 8 plots de contact d'émetteur et d'un plot de contact de grille. L'isolant situé à la périphérie du composant et délimitant les plots de contact est en relief par rapport aux métallisations. Cette structuration, favorable au placement de fils d'aluminium, est très peu adaptée à celle d'une brasure massive qui offrirait une surface d'échange importante. Ainsi, la mise en œuvre de ce type de composant dans un empilement 3D est complexe à plusieurs titres [VAG10]. Il est clair qu'une optimisation de la géométrie (réalisation d'un seul plot d'émetteur et positionnement du contact de grille en bordure de la puce) est nécessaire pour simplifier la prise de contact en face avant. Le relief de l'isolant qui recouvre, en périphérie, les terminaisons en tension, indispensables pour assurer la tenue en tension du composant, ne facilite non plus les interconnexions 3D. Les terminaisons sont dans ce cas de type planar - adaptées à la connectique par wire bonding sur la face avant mais assez contraignantes pour une intégration 3D des semi-conducteurs de puissance. En effet, la distribution des équipotentielles, induite par les terminaisons planar, ne doit pas être perturbée par la présence de conducteurs à proximité de celles-ci. Ainsi dans le cas des assemblages et interconnexions 3D avec des conducteurs massifs, afin de ne pas dégrader la tenue en tension du semi-conducteur, la distance entre le conducteur et la zone périphérique de la puce doit être ajustée. Des solutions à cette problématique sont proposées par les technologies d'interconnexion basées sur l'insertion d'une couche supplémentaire entre la puce et le substrat supérieur comme les techniques de prise de contacts par métallisations électrodéposées par exemple [WYK05] qui consistent à recouvrir les métallisations (en général en aluminium) des puces avec des métallisations en cuivre électrodéposé. Nous pouvons encore citer ici les technologies Metal Post Interconnection [CAT05] basée sur la brasure de poteaux de cuivre entre la puce et le substrat, Metal Bump Interconnection [MER06] basée sur la brasure de cylindres de cuivre entre la puce et le substrat (figure I.6.), Solder Bump Interconnection [RIN97] qui repose sur l'insertion de billes de brasure entre la puce et le substrat. D'autres travaux académiques sont aujourd'hui menés dans le but d'adapter la métallisation en face avant des composants de puissance afin de faciliter la prise de contact 3D. Citons par exemple la technologie des micropoteaux de cuivre (figure I.7.) développée en France au laboratoire AMPERE permettant, comme les bumps, de surélever les contacts électriques afin de permettre un assemblage plus aisé [MEN08]. Ces techniques se différencient principalement par le développement d'étapes "packaging" à l'échelle du wafer et par la mise en place de procédés collectifs spécifiques et adaptés.

Fig. I.6. - Vue schématique de la technologie d'interconnexion 3D *Metal Bump Interconnection* [MER06].

Fig. I.7. - Vue schématique de la technologie d'interconnexion 3D basée sur des *micro poteaux de cuivre* [MEN08].

Une autre piste prometteuse qui permet la prise de contact massive en surface des composants semi-conducteurs sans que cela affecte leur tenue en tension est d'aller encore plus loin dans la modification et l'adaptation de la face avant de la puce en remplaçant les terminaisons planar par des terminaisons plus appropriées aux interconnexions 3D. Ce concept sera présenté plus loin dans ce chapitre.

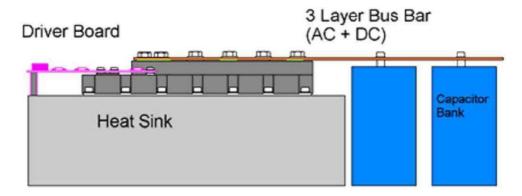

#### • Le module Power Chip-on-Chip (PCoC)

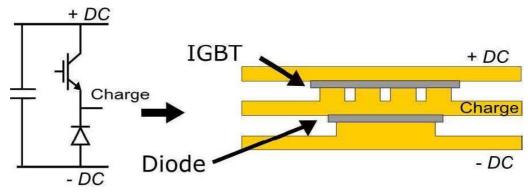

Comme nous l'avons déjà mentionné, l'utilisation de la troisième dimension dans la conception et la réalisation des modules de puissance permet un refroidissement double face des composants de puissance mais offre aussi un gain important en terme de comportement électromagnétique grâce au remplacement des fils de bonding en face avant par des interconnexions 3D. Toutefois, il a été démontré [VAG10] que ce ne sont pas les fils de bondings qui sont responsables de la plus grande valeur de l'inductance parasite de la maille de commutation mais les lyres de connexion avec le bus barre. Le laboratoire G2Elab contribue depuis quelques années à l'effort de mise en œuvre plus performante des composants semiconducteurs de puissance en proposant des topologies originales qui donnent une nouvelle vision de la gestion de l'environnement électro-thermo-mécanique (ETM). Dans ce cadre, le concept Power Chip-on-Chip (PCoC) a été proposé et validé durant les travaux de thèse de Eric Vagnon [VAG10]. Ce concept innovant concerne la réalisation d'un module de puissance compact dans lequel la troisième dimension est utilisée pour placer les puces de puissance les unes sur les autres. L'empilement des électrodes et des puces est tel que l'assemblage peut être inséré au plus près voire dans le bus barre (figure I.8.). Il en résulte un gain important en termes de comportements électrique et électromagnétique. Toutefois, le bénéfice du point de vue thermique d'une structure PCoC par rapport aux modules 3D classiques est moindre. Le refroidissement double face redevient limité à une seule face lorsque deux puces sont empilées l'une sur l'autre pour former une cellule de commutation idéale du point de vue électromagnétique comme représenté sur la figure I.8. Ainsi, un concept innovant du refroidissement direct, au plus près des composants de puissance, trouvera une application très originale dans ce type d'assemblage d'empilement des puces de puissance. Le résultat sera optimal d'un point de vue CEM et thermique également. Ce concept sera présenté plus loin dans ce chapitre.

Fig. I.8. - Vue schématique du concept PCoC – une cellule de commutation au plus près du bus barre [VAG10].

L'application du concept Power Chip-on-Chip pour la réalisation d'une cellule de commutation est représentée sur la figure I.9. La technologie de réalisation des interconnexions de l'empilement des électrodes et des puces est dans cet exemple de type contact pressé - la prise de contact des deux faces du composant est effectuée par pression de plaques massives en métal.

Fig. I.9. - Cellule de commutation suivant le concept PCoC [VAG10].

Afin de simplifier la mise en œuvre, un des objectifs recherchés avec le concept PCoC consiste à réduire la force de serrage nécessaire pour la réalisation de l'assemblage Chip-on-Chip par rapport à un boitier Press-Pack classique. Il a été démontré durant les travaux de recherche de Eric Vagnon que pour une faible force de serrage (1kN) le contact réalisé est de bonne qualité. Un autre point fort du concept PCoC est le gain important, en terme de comportement électromagnétique, qui est d'autant plus élevé que la distance entre les électrodes est petite et donc dépend de la hauteur finale de l'assemblage. Toutefois, comme nous l'avons mentionné, une distance minimale entre la surface de la puce et l'électrode doit être respectée afin de ne pas affecter la tenue en tension du composant. On se retrouve ainsi de nouveau face à la problématique de l'adaptabilité des puces de puissance produites aujourd'hui et leur mise en œuvre dans des assemblages originales et innovantes.

Le paragraphe suivant sera dédié à la description de la solution que nous avons étudiée, analysée puis testée durant ces travaux de thèse afin de simplifier la mise en œuvre des composants de puissance à structure verticale dans les packages 3D.

# 3. Solution innovante du composant à tenue en tension verticale adapté à son package

Nous avons vu dans le paragraphe précédent que les packages 3D reposent sur des connexions sur les deux faces du composant de puissance ce qui permet d'optimiser le comportement électromagnétique du module. Dans ce cas, la prise de contact sur les deux faces du composant est effectuée par des plaques "larges" en métal. Toutefois, la plupart des composants produits industriellement aujourd'hui comportent des terminaisons en tension périphériques de type planar qui ne sont pas adaptées à de telles interconnexions. La distribution des équipotentielles, induite par les terminaisons planar, ne doit pas être perturbée par la présence de conducteurs à proximité de celles-ci afin de ne pas pénaliser le fonctionnement électrique du composant. Ainsi, la zone de contact en face avant doit être éloignée de la zone périphérique. Une autre manière d'aborder cette problématique consiste en une approche couplée de la conception et de la réalisation du composant de puissance et de son package afin de pouvoir optimiser l'ensemble. Ainsi, si l'on souhaite insérer le composant de puissance entre deux plaques conductrices faisant office de bus barre et débordant du périmètre du ou des composants de puissance, il devient nécessaire de revoir le mode de gestion des périphéries de jonction des composants de puissance à structure verticale afin de maintenir optimale et minimale la distance inter conducteurs du bus barre.

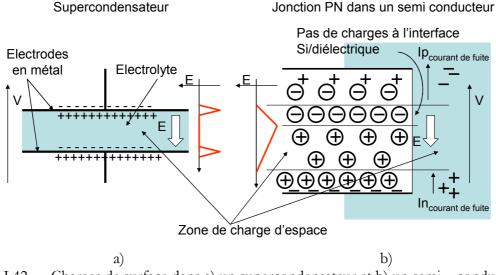

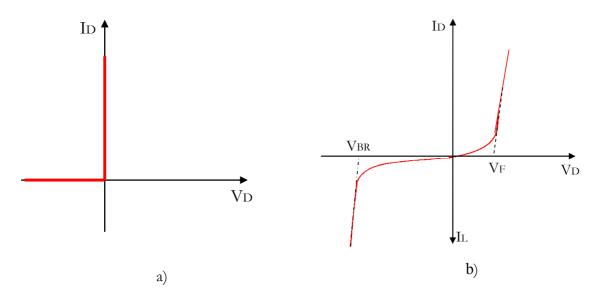

#### 3.1 Tenue en tension périphérique des composants de puissance

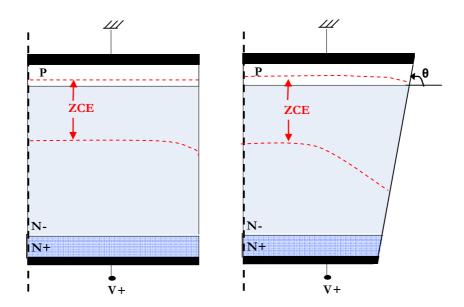

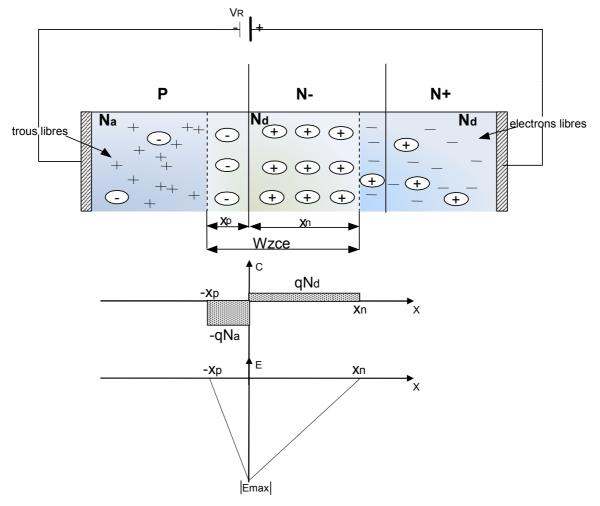

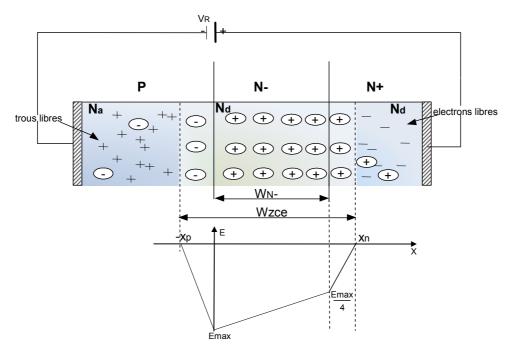

Deux contraintes principales apparaissent à la périphérie des jonctions des semi-conducteurs de puissance et nécessitent des précautions particulières afin de garantir la tenue en tension optimale des structures physiques [ARN92, LEF04]. La première est liée aux effets de bords et aux défauts cristallins en surface et au niveau des chemins de découpes qui peuvent réduire la tenue en tension du dispositif si l'intensité du champ électrique n'est pas significativement réduit et si une passivation adéquate n'est pas réalisée. La deuxième contrainte concerne la courbure des équipotentielles de la jonction polarisée en inverse qui peut entraîner le claquage prématuré du composant pour une tension plus faible que la tension optimale de la jonction plane équivalente. De nombreuses solutions technologiques qui permettent de contrôler ce claquage en surface existent [ARN92, LEF04, BAL08]. Elles sont toutes basées sur le principe de l'étalement de la zone de charge d'espace en périphérie de la jonction polarisée en inverse afin de distribuer le potentiel sur une plus grande surface de silicium et ainsi de réduire la valeur du champ électrique en surface et dans le volume du silicium sous la surface et en périphérie de la jonction (régions de courbures 2D ou 3D). Les technologies de tenue en tension périphérique peuvent être divisées en deux grandes familles - les technologies planar (anneaux de garde, passivation seule, jonctions implantées, électrode de champ, techniques RESURF, etc.) qui concernent les jonctions réalisées avec masque et les technologies qui concernent les jonctions réalisées sans masque (terminaisons en biseau, mésa, etc.).

## • Terminaisons en tension des jonctions réalisées avec masque

L'émergence de technologies de terminaisons en tension périphériques de type planar a permis de réduire le coût de fabrication des composants tout en simplifiant leur réalisation et en se rapprochant efficacement de la tenue en tension optimale.

Toutes les solutions technologiques planar, dont certaines ont déjà été citées plus haut, sont très bien décrites dans [ARN92, LEF04, BAL08, LET00]. Nous ne ferons donc pas une description exhaustive de leurs principes. Nous allons seulement présenter le principe des anneaux de garde puisque c'est la technologie la plus répandue. Elle nous servira de point de comparaison avec la technique de terminaisons du composant adapté à son package que nous allons proposer par la suite.

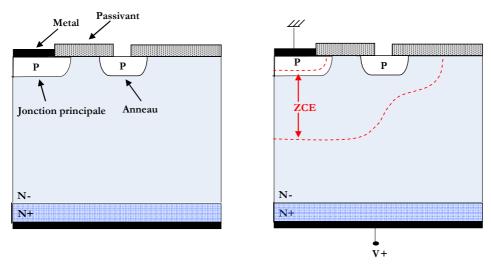

La technique des anneaux de garde ou anneaux flottants est l'une des plus anciennes [KAO67]. Le principe de cette technique est basé sur la réalisation d'un ou plusieurs anneaux, réalisés en même temps que la diffusion centrale des cellules de MOS ou IGBT, entourant la jonction principale. La figure. I.10. représente l'application de la technique des anneaux de garde pour une diode PIN.

Fig. I.10. - Terminaisons planar- anneaux de garde [LEF04].

Lorsque la jonction principale est polarisée en inverse la zone de charge d'espace (ZCE) qui se développe au sein de la structure rencontre l'anneau, fortement dopé, ce qui allonge la courbure des équipotentielles. Cela a comme effet de réduire le champ électrique en surface du composant en lui permettant de cette manière de « tenir » la tension optimale pour laquelle le composant a été dimensionné. Le nombre d'anneaux est d'autant plus grand que la tension de claquage est élevée. Les inter distances entre la jonction principale et le premier anneau puis entre les anneaux sont aussi des paramètres qui doivent être soigneusement dimensionnés afin de garantir les performances recherchées.

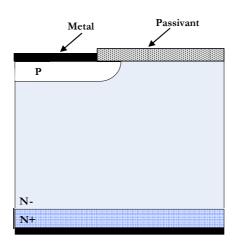

Enfin, ce que nous devons encore une fois souligner c'est que la technique de terminaison périphérique est un des facteurs qui conditionne beaucoup la mise en œuvre des composants dans les modules de puissance. Comme nous l'avons dit, les terminaisons planar sont adaptées aux interconnexions de type wire bondings mais sont très contraignantes pour la réalisation des interconnexions 3D. D'une part la présence d'un conducteur en proximité de la surface du composant de puissance risque de modifier la distribution des équipotentielles et d'affecter la tenue en tension du composant. D'autre part toutes les techniques de terminaisons de jonctions réalisées avec masque nécessitent le dépôt d'une couche de passivation en surface du composant comme représenté sur la figure I.11. Cette couche constitue la surépaisseur d'isolant qui complexifie la réalisation d'interconnexions 3D, comme nous l'avons déjà évoqué dans le paragraphe 2.2.

Fig. I.11. - Jonction réalisée avec masque pour une diode PIN [LEF04].

#### Terminaisons en tension des jonctions réalisées sans masque

Les terminaisons de type « mesa » ou biseautées sont connues de longue date et leur utilisation est aujourd'hui réservée pour les dispositifs de très forte puissance (diodes de redressement et thyristors principalement) [BAL08, LET00]. Un intérêt considérable est porté ces derniers temps envers cette technologie de terminaisons en tension puisqu'elle s'avère être très adaptée aux composants grand gap en carbure de silicium [ZHA10, WOL06].

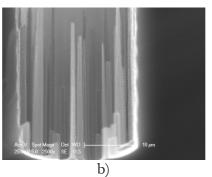

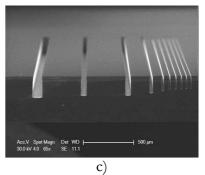

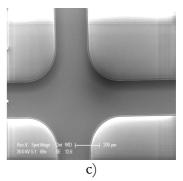

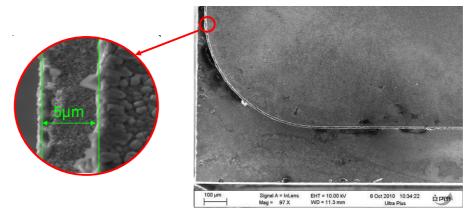

Le principe de cette technique (figure I.12.) consiste en la réalisation d'une découpe appropriée sur les bords du substrat semi-conducteur. La réalisation des terminaisons en biseau est basée sur des moyens mécaniques (sablage, ultrasons, etc) tandis que les terminaisons mesa sont basées sur des procédés de sillonnage suivis d'attaque chimique. Aujourd'hui, le développement des procédés technologiques de gravure sèche de silicium DRIE (pour Deep Reactive Ion Etching) permet la gravure de motifs avec grand facteur de forme et cela indépendamment de l'orientation cristalline. Ils sont donc aussi utilisés pour la réalisation de ce type de périphéries en tension que l'on retrouve dans la littérature sous le nom de terminaisons en tranchées profondes (deep trench terminations) [PAR02, PAR03, DRA99, KAM10, THE09]. Le principe reste toujours le même - réduire la composante tangentielle du champ électrique en surface afin de profiter de la tension de claquage de la jonction plane. Un avantage majeur de la technique de terminaisons en tranchées est que la réalisation de ce type de terminaisons périphériques permet une consommation de silicium fortement réduite par rapport aux techniques traditionnelles comme les anneaux de garde – une réduction de 30% de la surface totale du substrat a été démontrée dans les travaux de [PAR03] pour un transistor bipolaire avec tension nominale de 700V et calibre en courant de 4A.

Fig. I.12. - Terminaisons pour jonctions réalisées sans masque.

Un avantage de cette technique de terminaisons vient du choix possible d'un angle  $\theta$  approprié en périphérie du composant (figure I.12.). Différents angles – positif, négatif, double biseau, etc, chacun présentant ses avantages vis-à-vis de l'application finale, peuvent être réalisés en périphérie des dispositifs. Les mécanismes physiques mis en jeu lors de l'utilisation des différents angles sont décrits dans [BAL08, LEF04, LET00] et nous allons seulement nous intéresser à l'angle de découpe positif puisqu'il s'avère être le plus approprié pour notre application.

L'angle est dit « positif » lorsque la section du composant diminue de la région P vers la région N comme représenté sur la figure I.12. Un tel angle est très favorable pour la tenue en tension du dispositif car il permet de réduire fortement le champ électrique en surface par rapport au champ électrique en volume. La raison pour cela est que pour maintenir l'équilibre de charges positives et négatives de part et d'autre de la jonction PN, suite à la diminution de la section du composant en périphérie, la zone de charge d'espace s'élargit vers les bords du composant en lui permettant de profiter de la tenue en tension optimale pour laquelle le composant a été dimensionné. Dans ce cas, la diminution du champ électrique en surface ( $E \max_s surf$ ) par rapport au champ électrique en volume ( $E \max_s vol$ ) peut être déterminé suivant la relation suivante:

$$E \max_{surf} = E \max_{vol} \left( \frac{\sin(\theta)}{1 + \cos(\theta)} \right)$$

I.1.

D'après la relation (I.1.) plus l'angle est faible, plus le champ électrique en surface est réduit. Il est démontré dans l'ouvrage [BAL08] que l'angle positif optimal est dans la gamme de 30° à 60°. Les angles plus faibles sont à proscrire puisqu'ils nécessitent une trop grande consommation du silicium.

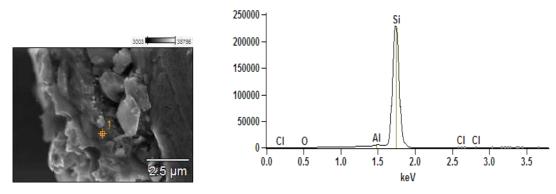

Néanmoins, nous devons mentionner qu'un paramètre très important lorsqu'on considère ce type de terminaison est la présence d'imperfections le long des parois des tranchées qui peuvent provoquer le claquage prématuré en surface. Ainsi, une attention particulière est portée sur le traitement des parois, la réalisation d'une passivation adéquate et le choix du matériau diélectrique afin de permettre le fonctionnement stable du composant en garantissant sa tenue en tension. La passivation des terminaisons des jonctions réalisées sans masque consiste à remplir complètement la tranchée ou de déposer une fine couche de diélectrique le long de la paroi. Selon la littérature

une large gamme de matériaux diélectriques peut être utilisée dans ce cas - nitride, oxyde ou PSG (pour Phosphosilicate Glass). Des travaux académiques menés au laboratoire LAAS en France [THE09] montrent que d'autres matériaux présentant de bonnes propriétés comme le polymère BenzoCycloButene (BCB) peuvent être utilisés pour la protection diélectrique des tranchées profondes des composants haute tension.

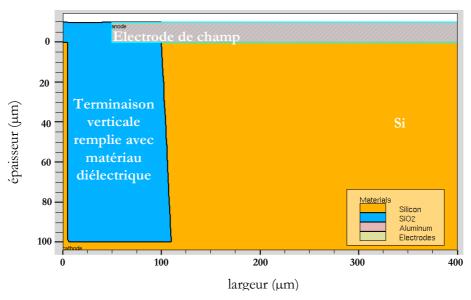

#### 3.2 Le concept des terminaisons en tension verticales

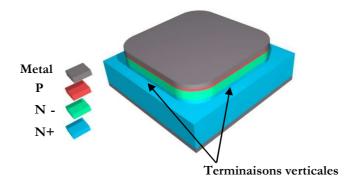

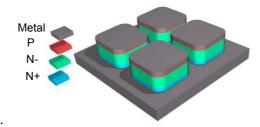

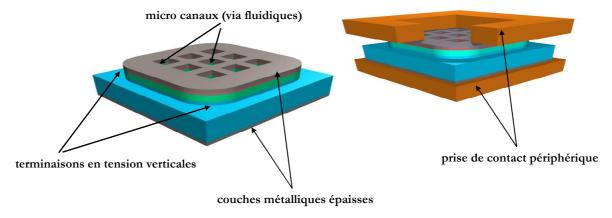

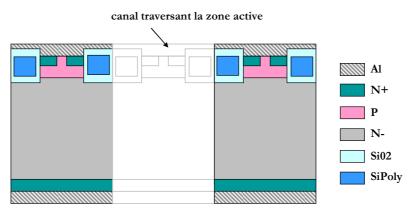

La mise à profit de la technique de terminaison périphérique des jonctions réalisées sans masque peut simplifier énormément la mise en œuvre des package 3D. Ainsi dans notre approche de conception couplée puce-package, nous avons été inspiré par cette technique afin "d'adapter" le composant pour une mise en œuvre originale et performante. La technique que nous proposons de mettre en place est celle des terminaisons en tension verticales via la création de tranchées profondes en périphérie du composant. Une telle configuration permettra la prise en sandwich du composant entre deux plaques métalliques – comme dans le cas du package PCoC que nous avons présenté dans le paragraphe 2.2. La figure I.13 représente l'application du concept des terminaisons verticales en prenant comme exemple une diode PIN.

Fig. I.13. - Technique de terminaisons en tension verticales pour une diode de puissance à structure verticale.

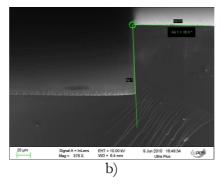

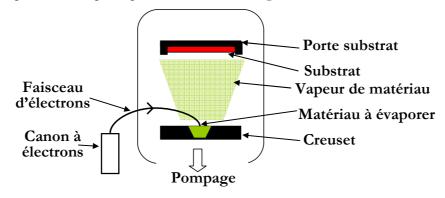

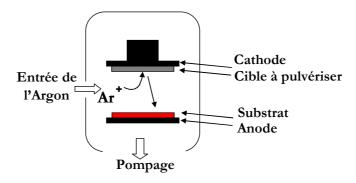

La technique de réalisation des tranchées verticales consiste en une étape de gravure ionique réactive profonde (DRIE), jusqu'à l'obtention de la profondeur et de l'angle désirés, complémentée par une étape de passivation des tranchées et du composant lui même. Dans un second point, la finition en surface de la puce, et plus particulièrement la métallisation et ses caractéristiques doivent également être adaptées.

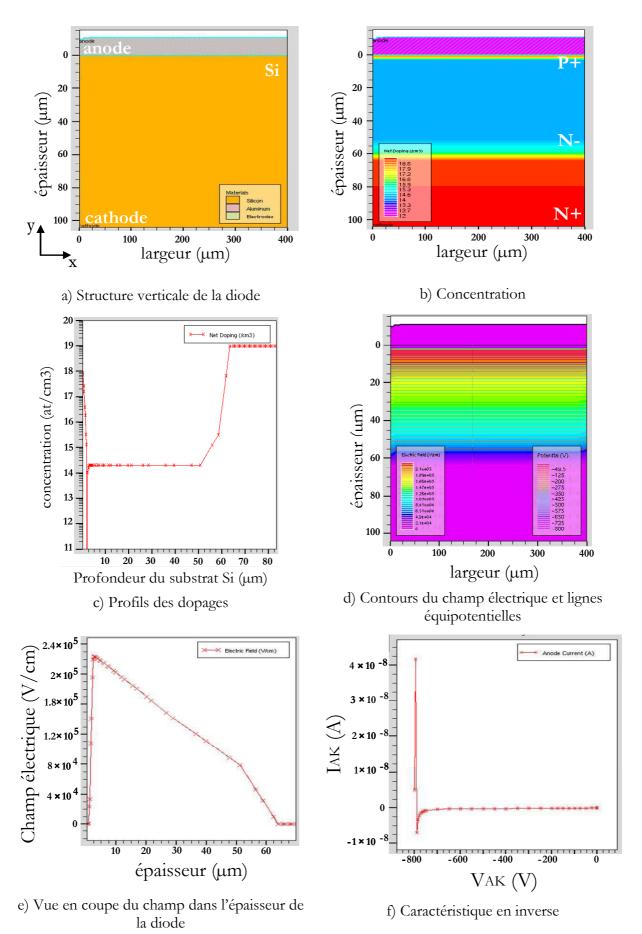

# 3.3 Terminaisons planar versus terminaisons verticales pour une mise en œuvre 3D

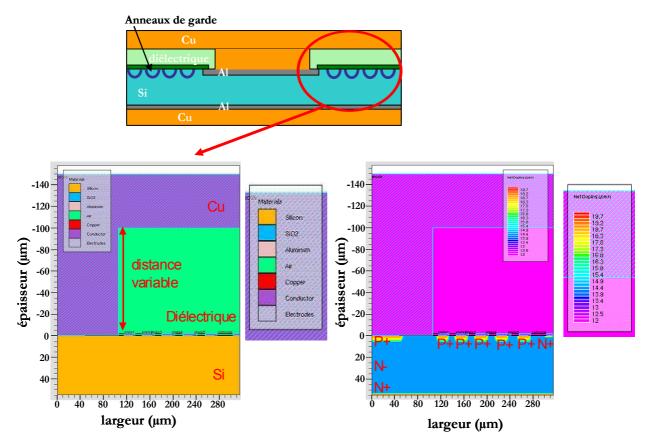

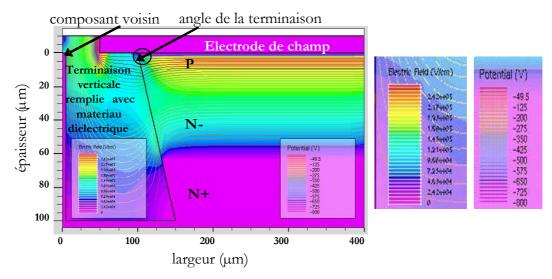

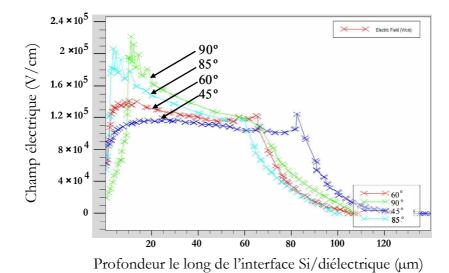

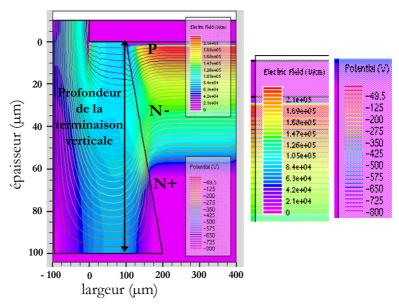

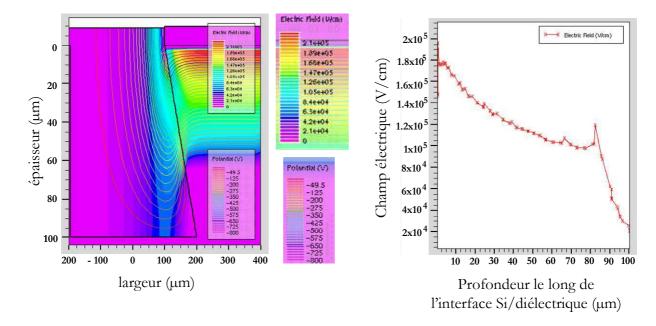

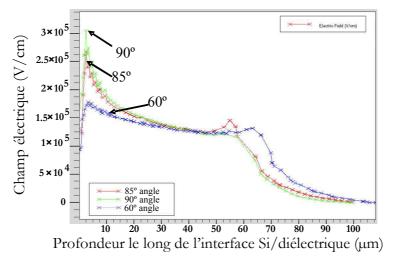

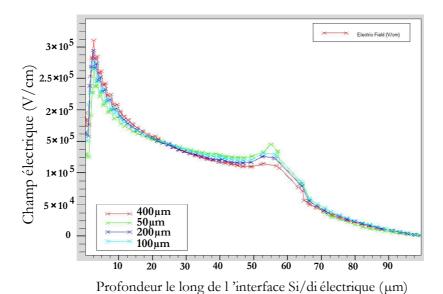

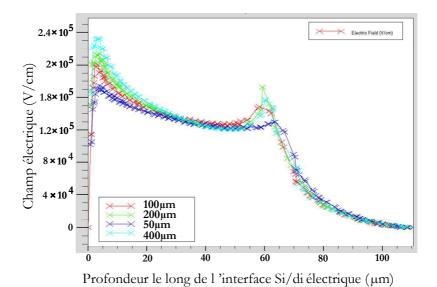

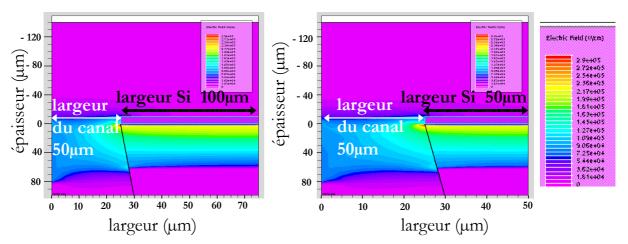

Afin de démontrer l'intérêt de la technique des terminaisons verticales pour une mise en œuvre 3D, nous avons mené une étude basée sur des simulations numériques avec le logiciel Silvaco. L'objectif était d'évaluer les effets de proximité entre la zone de tenue en tension et le conducteur massif. Les résultats qui concernent la technique que nous proposons de mettre en place ont été comparés avec la technique planar la plus répandue, celle des anneaux de garde (figure I.14.).

Fig. I.14. - Mise en œuvre 3D d'une diode PIN avec terminaisons en tension verticales et avec anneaux de garde.

Dans le premier cas, la structure simulée correspond à une diode de puissance à structure verticale polarisée en inverse avec une tension de claquage de 700V qui comporte une périphérie en tension de type anneaux de garde et une plaque large en métal de prise de contact en face avant. La distance entre la surface de la puce et la partie inférieure du conducteur est variable, réglée ici par un poteau d'épaisseur variable (figure I.15.). Le matériau diélectrique utilisé dans les simulations a une permittivité diélectrique e=3 afin de représenter le cas du matériau de passivation utilisé plus tard pour la passivation des prototypes fabriqués, c'est-à-dire le gel silicone. Plus de détails sur les paramètres des simulations ainsi que les conditions aux limites sont données dans le chapitre III.

Fig. I.15. - Structure étudiée - diode PIN avec anneaux de garde.

Nous avons fait varier la distance entre la plaque massive de prise de contact et la surface du composant de 100µm à 5µm. Nous avons constaté qu'en dessous de 20µm, la proximité de la

plaque en métal affecte la distribution des équipotentielles en surface et induit une augmentation locale du champ électrique en surface, d'autant plus considérable plus la distance diminue.

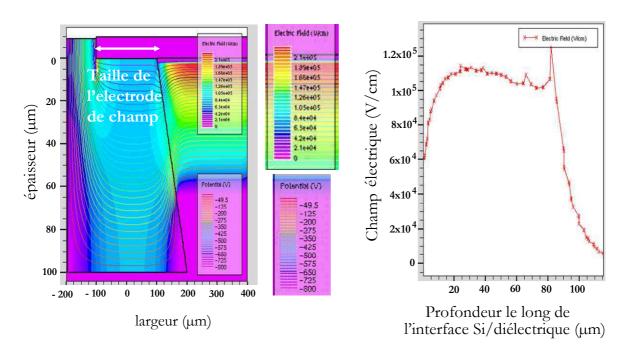

Pour illustrer le phénomène, la figure I.16.a) représente les résultats obtenus pour la distribution du champ électrique et des lignes équipotentielles lorsque la plaque massive en métal est placée à 10µm de la surface du composant.

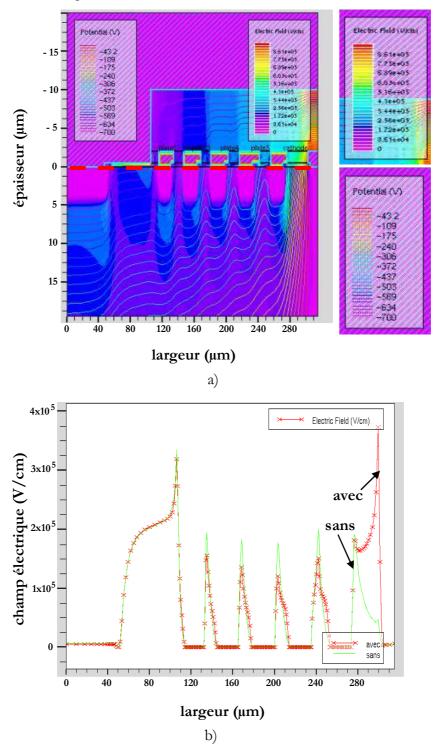

Fig. I.16. - Diode de puissance avec anneaux de garde a) Contours du champ électrique et lignes équipotentielles et b) Evolution du champ électrique à la surface (vue en coupe le long de la ligne rouge pointillée) avec et sans présence d'une électrode de contact recouvrant les anneaux de garde

On peut remarquer sur la figure I.16.a) que suite à la proximité de la plaque en métal et de la surface du composant les anneaux de garde ne conservent plus leurs effets positifs sur l'étalement des équipotentielles à la surface et en périphérie de la puce. Les lignes équipotentielles sont très concentrées et resserrées à la surface. Un composant soumis à ces conditions de fonctionnement perdra ses performances électriques en termes de tenue en tension.

La figure I.16.b) représente la comparaison entre la vue en coupe du champ électrique (vue en coupe du champ électrique le long de la ligne rouge figure I.16 a)) en surface sans électrode de contact recouvrant les anneaux et avec électrode de contact placée à 10µm de la surface. On peut remarquer sur la figure I.16 que la proximité de la plaque métallique et la surface du composant induit un pic important du champ électrique en surface au niveau du dernier anneau. Le champ électrique en surface augmente encore plus lorsque la distance diminue au delà de 10µm.

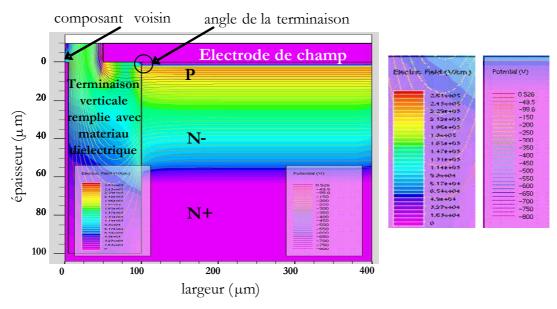

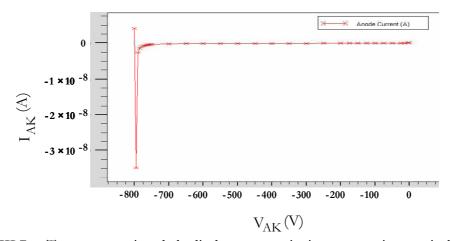

La figure I.17. représente la même diode de puissance à structure verticale mais, cette fois, avec la technique de terminaisons en tension verticales. Le contact en face avant est massif et débordant au-delà de la zone de tenue en tension.

Fig. I.17. - Structure étudiée - diode PIN avec terminaisons en tension verticales.

La figure I.18. représente la distribution du champ électrique et des lignes équipotentielles lorsque la diode est polarisée en inverse avec une tension de 800V.

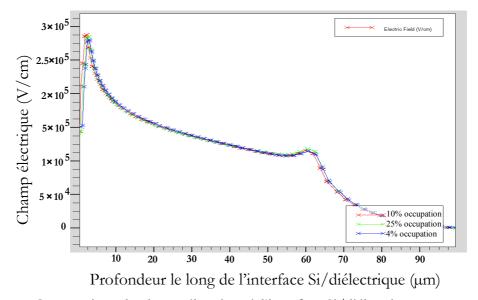

Fig. I.18. - Diode de puissance avec terminaisons en tension verticales a) Contours du champ électrique et lignes équipotentielles et b) Vue en coupe (le long de la ligne rouge pointillée) du champ électrique à l'interface Si/diélectrique.

On peut remarquer sur la figure I.18b) qui présente la vue en coupe du champ électrique le long de l'interface Si/diélectrique (ligne rouge figure I.18.a)) qu'avec cette technique de terminaison en tension, l'ajout d'une plaque massive en surface du composant n'a pas d'effets négatifs pour le champ électrique. Au contraire, la plaque massive joue le rôle d'une plaque de champ qui permet de réduire encore davantage le champ électrique à l'interface Si/passivant. La figure I.18.a) montre que, dans ce cas, l'allure et la courbure des lignes équipotentielles représentent une

condition favorable pour la tenue en tension du composant de puissance comme cela sera présenté plus précisément dans le chapitre III. On peut aussi voir sur la figure I.18.a) une forte augmentation du champ électrique au niveau de l'angle de l'électrode. Cette forte augmentation du champ électrique ne devrait pas poser de problèmes si au niveau du matériau diélectrique le champ critique de claquage est plus élevé que celui du silicium. On peut aussi imaginer qu'un passivant diélectrique est déposé au niveau de l'électrode.

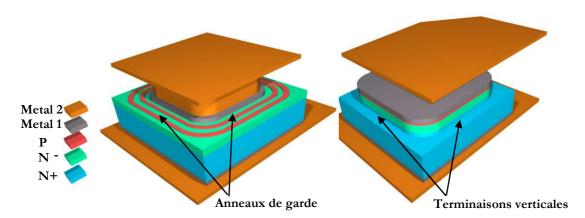

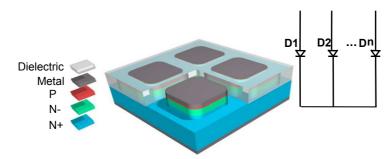

#### 3.4 Evolution et mise à profit de l'approche – puces muticomposants de puissance

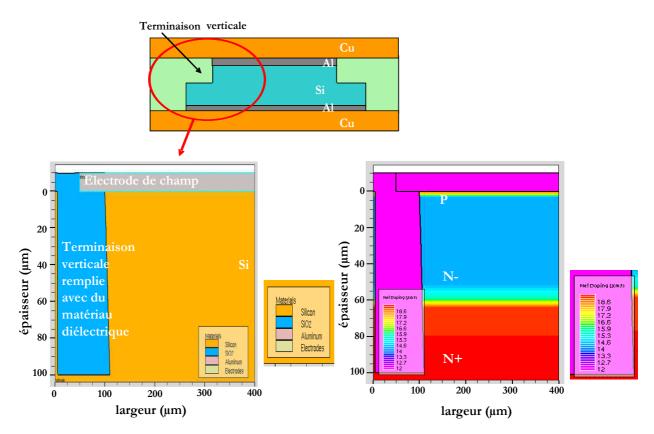

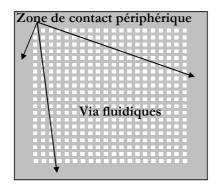

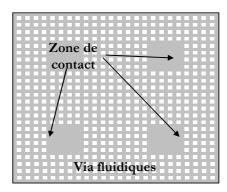

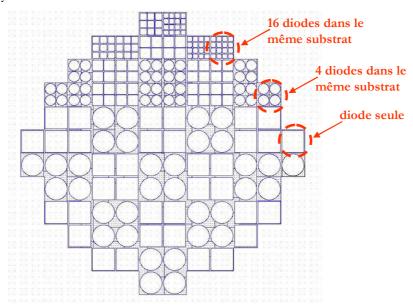

Un avantage majeur de la technique des terminaisons en tension verticales est qu'elle permet de créer des séparations au niveau de la zone active du composant et, de cette manière, on peut envisager l'intégration de plusieurs composants dans la même puce. L'idée consiste à utiliser la périphérie en tension non seulement pour réduire le champ électrique en surface mais aussi pour "iloter" chaque composant. La tranchée qui sépare les zones actives de chaque composant est ensuite remplie avec du matériau diélectrique ce qui permet de garantir l'isolation électrique de chaque composant avec son voisin. De cette manière on peut envisager l'intégration de plusieurs composants de puissance sur le même substrat commun, métallique ou semi-conducteur dégénéré [CRE09]. La figure I.19. montre une vue schématique du concept de mise en œuvre de plusieurs composants dans le même substrat en silicium. L'exemple représente des diodes de puissance à structure verticale dont la surface est intégralement occupée par plusieurs anodes et une cathode commune en face arrière.

Fig. I.19. - Vue schématique d'une puce multidiodes de puissance intégrées sur le même substrat en silicium avec la technique des terminaisons verticales.

Cette configuration permet l'assemblage et le package partiels de nombreux composants au niveau du wafer avec un minimum d'étapes supplémentaires de back end. La réduction significative du nombre d'interconnexions est un des avantages conséquents de cette technique. Plusieurs composants sont interconnectés pendant le procédé technologique ce qui rend l'assemblage reproductible, très fiable et réduit le coût final du package. Ces architectures pourraient avantageusement être bénéfiques dans des applications modernes d'électronique de puissance telles que les structures de conversion polyphasées [FOR07, LAB08, KER12].

Un avantage majeur de cette technique d'intégration monolithique de plusieurs diodes sur le même substrat est que la distinction des différents éléments semi-conducteurs peut être réalisée par l'étape finale de gravure ce qui simplifie le procédé technologique. L'approche que nous présentons a été développée sur un substrat semi-conducteur épitaxié mais elle peut facilement être appliquée sur des substrats homogènes reportés sur semelle en métal. Dans ce cas, la gravure du silicium doit être réalisée jusqu'au substrat commun en métal. La figure I.20 représente une vue schématique du concept. Le support mécanique des composants « ilotés » doit être assuré dans ce cas par la couche de métal. Pour ce faire, la couche de métal doit être suffisamment épaisse (quelques centaines de µm). Les techniques envisageables dans ce cas sont le collage moléculaire cuivre-cuivre entre une couche de cuivre électrodéposée en face arrière du wafer et une plaque épaisse en métal (cuivre ou molybdène) [BEN12] ou l'électrodéposition du cuivre en forte épaisseur.

Fig. I.20. - Vue schématique de la technique des terminaisons verticales dans le cas d'un substrat semi-conducteur homogène.

Comme nous l'avons déjà présenté avec la technique de terminaisons en tension verticales, les composants peuvent bénéficier des interconnexions 3D où les fils de bonding sont remplacés par des interconnexions massives en cuivre. Les terminaisons en tension verticales permettent la réalisation de plusieurs composants à l'échelle de la puce mais nous pouvons aussi envisager leur empilement les uns sur les autres pour concevoir une structure 3D afin de réduire l'influence des interconnexions entre les composants et de simplifier leur mise en œuvre dans les structures polyphasées ou multiniveaux. La figure I.21. représente une vue schématique de cette perspective conceptuelle dans une configuration Power Chip-on-Chip.

Fig. I.21. - Vue schématique du package Power Chip-on-Chip à l'aide des terminaisons en tension verticales - exemple d'une diode, de six diodes à cathode commune et d'un redresseur polyphasé à six bras.

Par ailleurs, comme nous l'avons déjà mentionné, un des points forts des packages 3D est qu'ils autorisent le refroidissement double face. Or, dans une configuration où deux composants sont empilés l'un sur l'autre, le refroidissement devient de nouveau limité à une seule face. Une telle configuration offre des bénéfices considérables du point de vue comportement électromagnétique mais d'un point de vue thermique ses performances restent limitées. Nous allons présenter par la suite dans ce chapitre une approche originale qui s'adresse à cette problématique. Le concept consiste à revoir la structure même du composant de puissance afin de réaliser un découplage entre les zones de tenue mécaniques, les prises de contact électrique et les surfaces d'échange thermique. Le concept innovant pour le refroidissement direct des composants de puissance offre les degrés de liberté nécessaires afin de pouvoir réaliser des assemblages optimaux d'un point de vue électromagnétique tout en ayant des performances thermiques élevées.

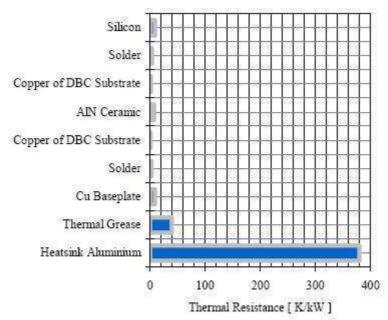

### 4 Les techniques de refroidissement en électronique

Un composant de puissance doit supporter de hautes tensions et laisser passer de forts courants d'où une certaine puissance électrique à dissiper sous forme de chaleur. Les densités de flux de chaleur des puces de puissance peuvent atteindre plusieurs centaines de W.cm<sup>-2</sup>. En même temps, les composants de puissance ont une température de jonction maximale à ne pas dépasser. Leur refroidissement efficace est donc vital afin de garantir les conditions de fonctionnement et les performances optimales. Ainsi ils nécessitent des systèmes de refroidissement adéquats pour

maintenir leur température de jonction en dessous des températures critiques de fonctionnement. Le choix du système de refroidissement dépend du niveau de pertes à évacuer et son efficacité est estimée en termes de résistance thermique équivalente et de pertes de charge. Nous allons décrire dans le paragraphe suivant quelques techniques utilisées pour le refroidissement en électronique en commençant par quelques rappels sur les mécanismes de transfert de la chaleur

#### 4.1 Mécanismes de transfert de chaleur

D'une manière générale le transfert de chaleur s'effectue par trois mécanismes : conduction convection et rayonnement.

#### Conduction

La conduction est le mode de transfert de chaleur dû aux écarts de température entre deux points d'un solide ou d'un fluide par propagation de proche en proche de l'énergie thermique des atomes, des molécules ou des électrons libres. Le flux thermique  $\Phi$  [W] traversant un objet de surface S [m²] et d'épaisseur L [m] est exprimé dans le cas 1D par la relation suivante :

$$\Phi = k \cdot \frac{S}{L} \cdot \Delta T \tag{I.2.}$$

où k [W/m.K] est la conductivité thermique et  $\Delta T$  [K] est l'écart de température entre les deux faces de l'objet.

Ainsi les différents paramètres qui interviennent dans le phénomène de conduction sont la nature et la géométrie des matériaux conducteurs de la chaleur ainsi que les interfaces thermiques qui les séparent.

#### Convection

Le transfert de chaleur par convection apparaît dans les fluides. Il est dû aux mouvements des particules qui facilitent le transfert de chaleur. Dans le cas où un fluide est en contact avec une paroi, l'échange de chaleur entre la paroi et le fluide peut être déterminé suivant la relation :

$$\Phi = h.S.(T_p - T_f) \tag{I.3.}$$

où  $h[W/m^2.K]$  est le coefficient d'échange de transfert de la chaleur entre la paroi et le fluide,  $T_p[K]$  est la température de la paroi et  $T_f[K]$  est la température de mélange du fluide. Lorsque le mouvement du fluide est imposé par une source externe (pompe, ventilateur) la convection est dite forcée. Dans le cas contraire la convection est dite libre (ou naturelle).

Le problème thermique de la convection est très complexe et nécessite la résolution d'équations de la thermique et de la mécanique des fluides. Un électronicien qui envisage la conception d'un système de refroidissement par convection devra identifier plusieurs paramètres comme le coefficient d'échange, les pertes de charge etc. qui sont dépendants du type de fluide utilisé, de la géométrie, du régime d'écoulement etc. Pour cela il sera amené à utiliser des corrélations (formules valables pour des formes géométriques particulières sous certaines conditions) et des nombres sans dimension que nous allons présenter plus en détails dans le chapitre IV.

#### Rayonnement

Les transferts thermiques par rayonnement s'effectuent entre deux corps séparés par le vide ou par un milieu transparent aux rayonnements thermiques par l'intermédiaire d'ondes électromagnétiques. Le flux transféré par rayonnement entre deux plans parallèles (paroi1 et paroi2) est défini suivant la relation:

$$\Phi = \varepsilon_{12}.\sigma_s.S(T_1^4 - T_2^4) \tag{I.4}$$

où  $\varepsilon_{12}$  est l'émissivité équivalente et  $\sigma_s$  est la constante de Stefan.

#### Notion de résistance thermique

L'analogie faite entre les phénomènes de conduction de la chaleur (loi de Fourier) et de conduction électrique permet d'introduire la notion de résistance thermique  $R_{th}$  (K/W) qui quantifie la résistance que les matériaux opposent au passage du flux de chaleur. La résistance thermique s'exprime suivant la relation suivante:

$$R_{th} = \frac{\Delta T}{\Phi} \tag{I.5}$$

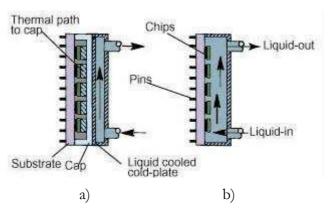

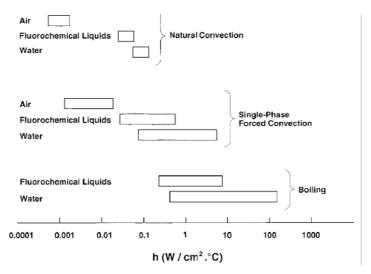

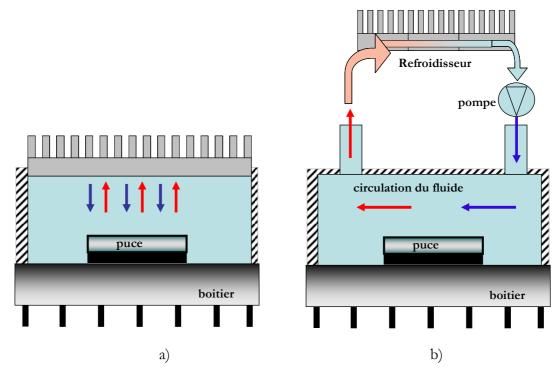

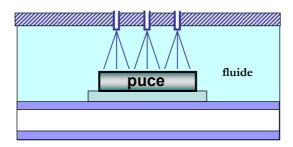

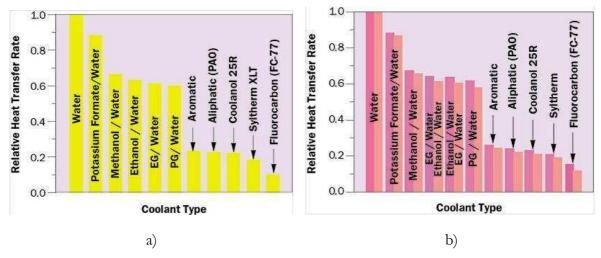

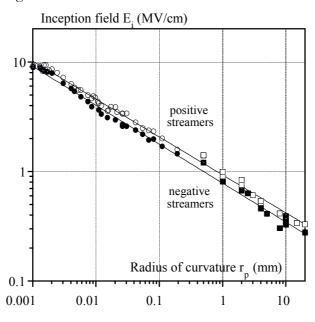

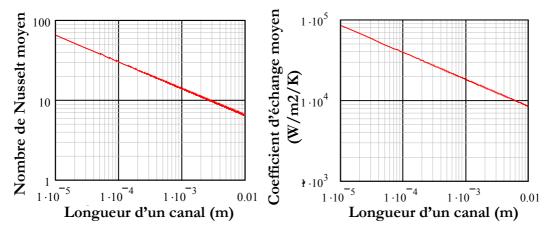

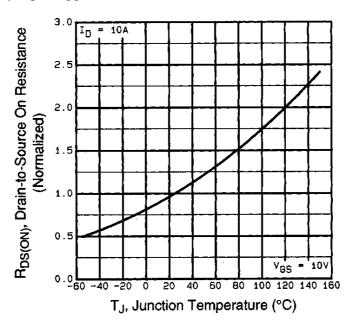

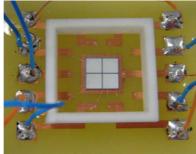

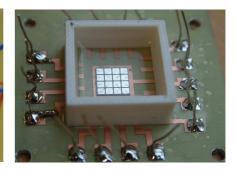

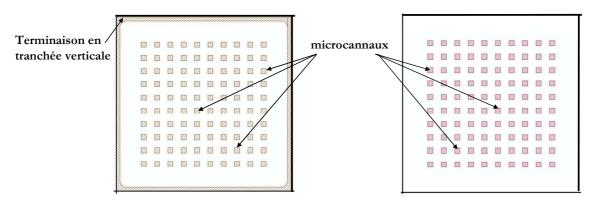

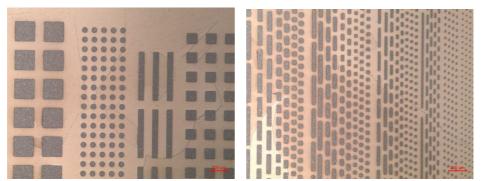

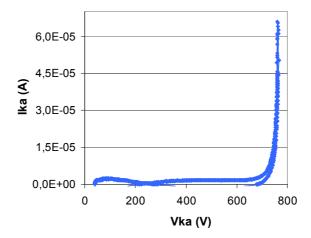

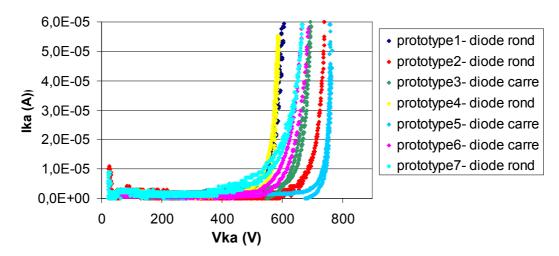

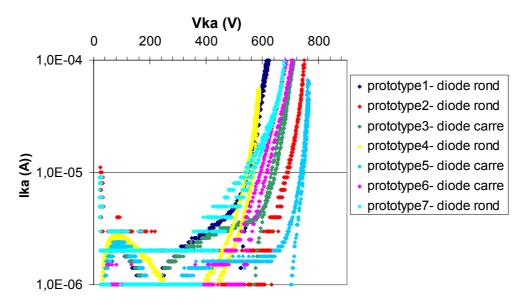

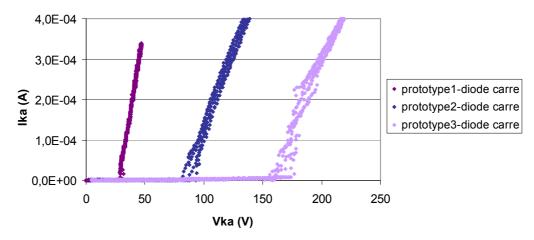

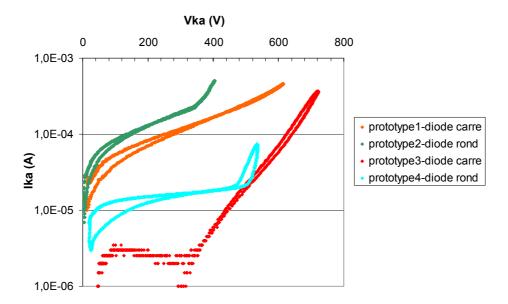

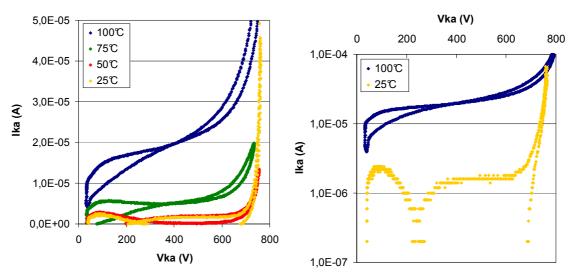

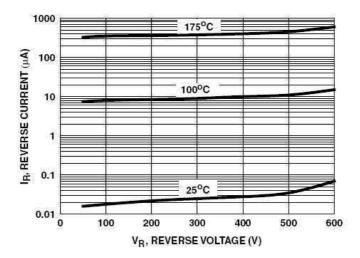

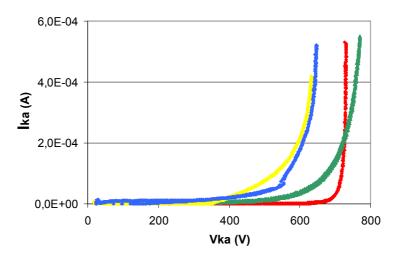

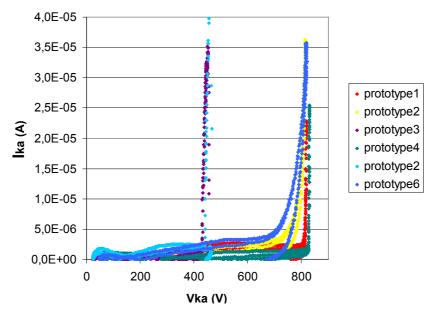

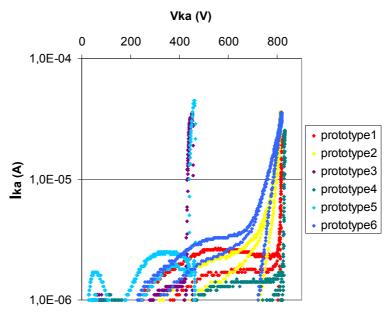

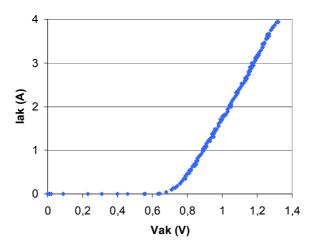

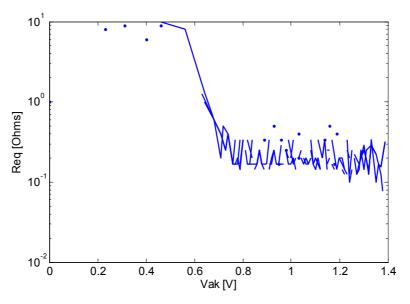

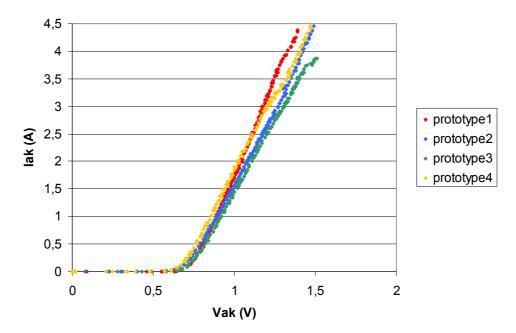

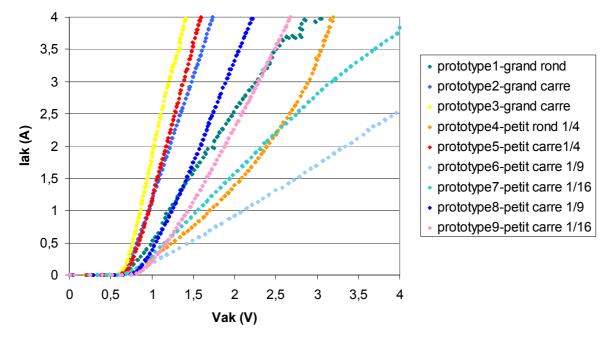

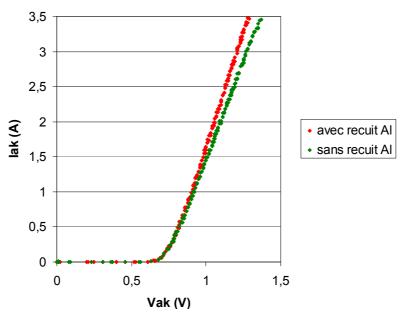

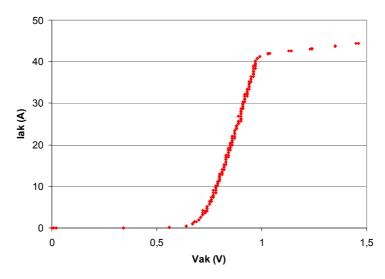

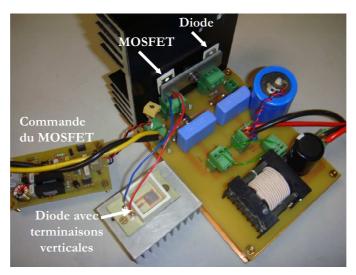

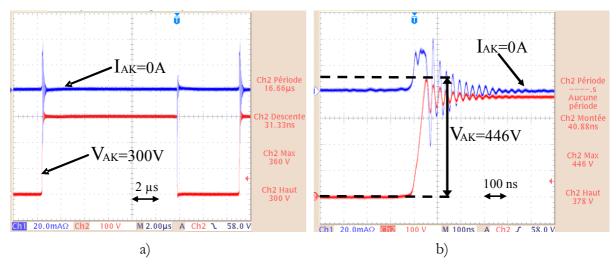

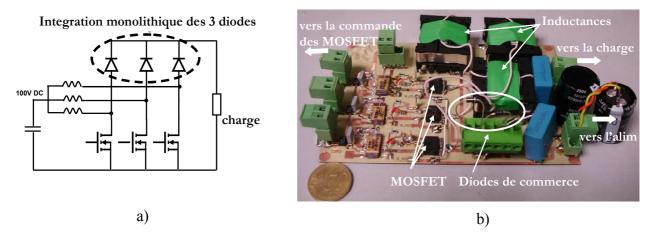

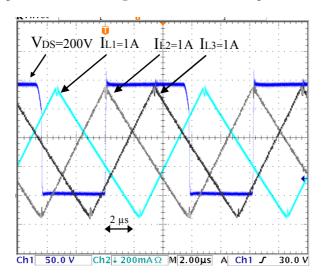

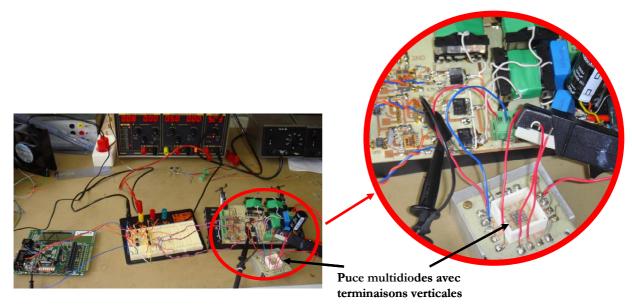

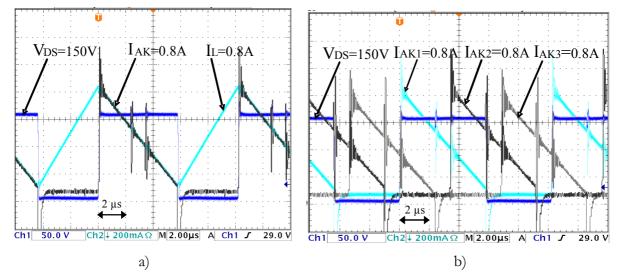

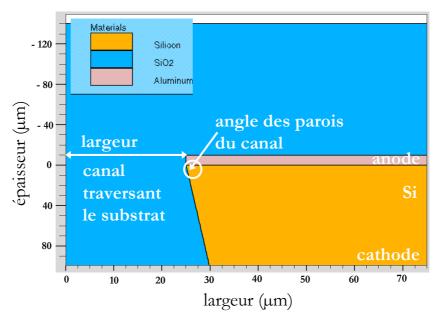

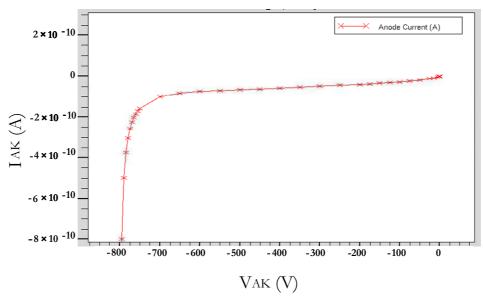

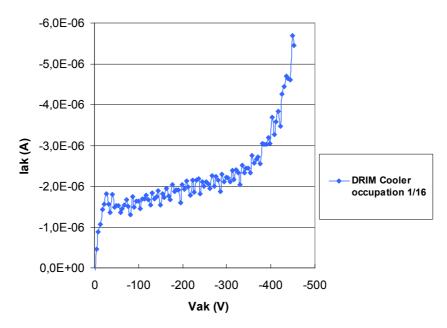

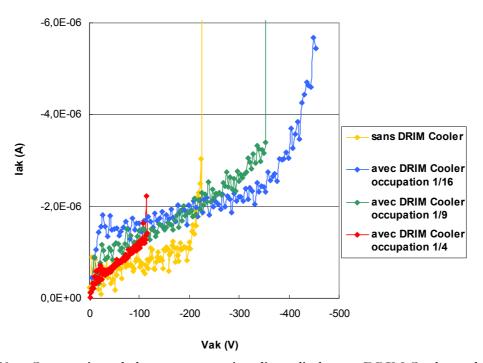

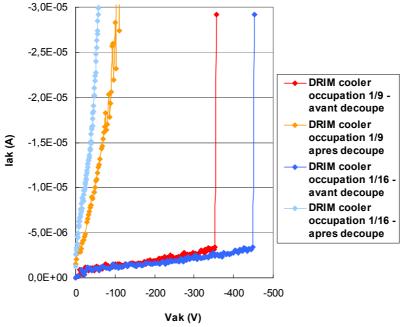

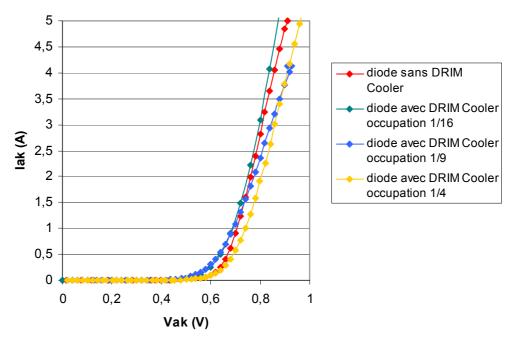

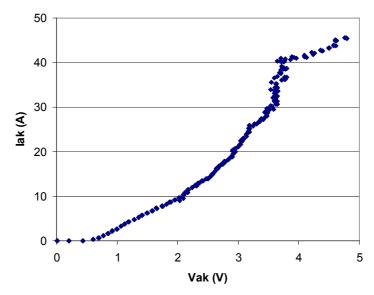

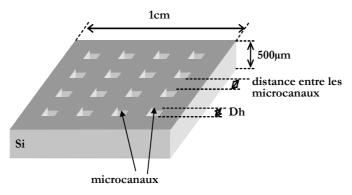

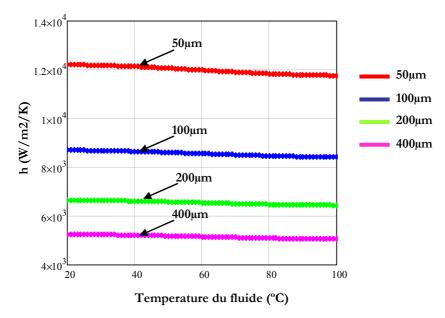

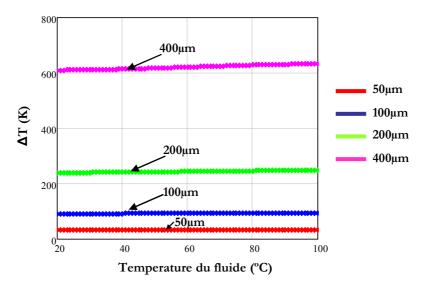

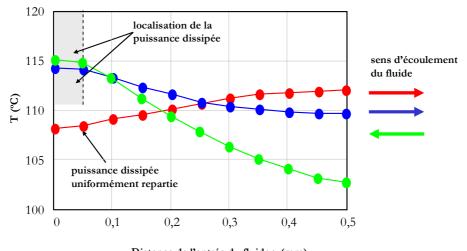

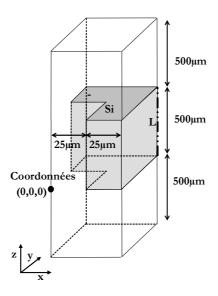

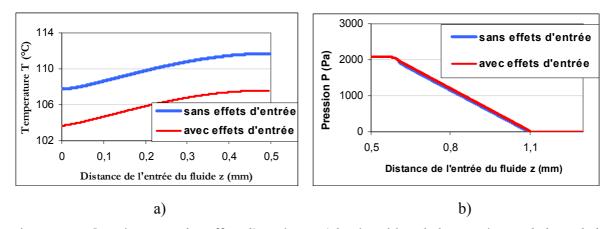

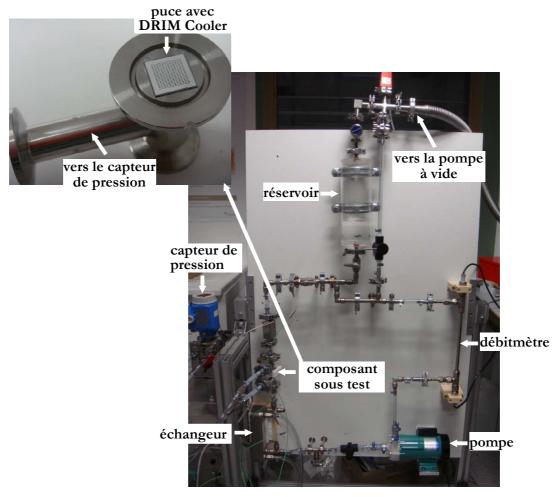

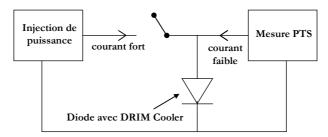

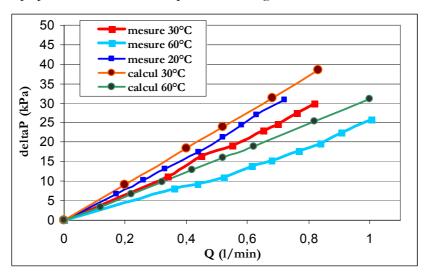

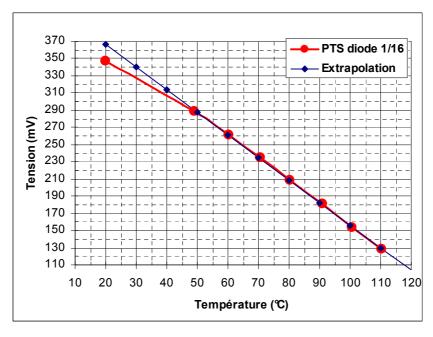

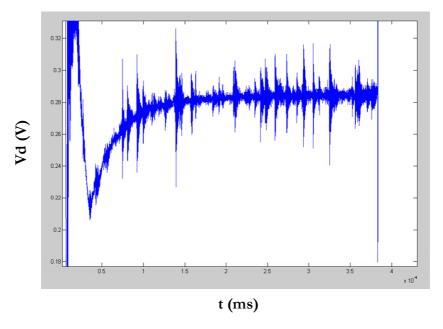

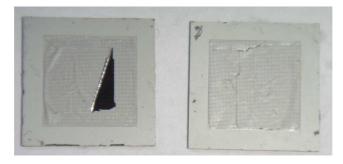

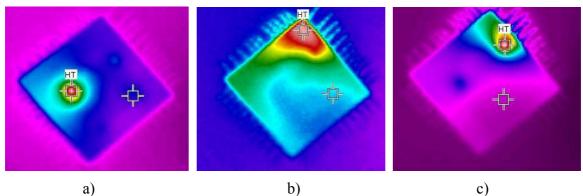

Si le transfert de la chaleur est effectué par conduction en 1D, la résistance thermique est  $R_{th}$ =L/k. Si le transfert de la chaleur est effectué par convection entre un fluide et une paroi, la résistance thermique est  $R_{th}$ =1/h.S.