# Energy-aware scheduling: complexity and algorithms

Paul Renaud-Goud

#### ▶ To cite this version:

Paul Renaud-Goud. Energy-aware scheduling: complexity and algorithms. Other [cs.OH]. Ecole normale supérieure de lyon - ENS LYON, 2012. English. NNT: 2012ENSL0727. tel-00744247

## HAL Id: tel-00744247 https://theses.hal.science/tel-00744247v1

Submitted on 22 Oct 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Nº attribué par la bibliothèque : 2012ENSL0727

### - ÉCOLE NORMALE SUPÉRIEURE DE LYON -Laboratoire de l'Informatique du Parallélisme - UMR5668 - LIP

#### THÈSE

en vue d'obtenir le grade de

## Docteur de l'École Normale Supérieure de Lyon - Université de Lyon Spécialité : Informatique

au titre de l'École Doctorale Informatique et Mathématiques

présentée et soutenue publiquement le 5 juillet 2012 par

#### Paul RENAUD-GOUD

# Energy-aware scheduling: complexity and algorithms

Directeur de thèse : Anne BENOIT Co-encadrant de thèse : Yves ROBERT

Après avis de : Olivier BEAUMONT Rapporteur

Padma RAGHAVAN Rapportrice

Devant la commission d'examen formée de :

Olivier BEAUMONT Rapporteur Anne BENOIT Membre Jean-Marc **PIERSON** Examinateur Padma RAGHAVAN Rapportrice Yves Membre ROBERT Denis TRYSTRAM Examinateur

## Remerciements

Un jour, Benoît, un ami, m'a expliqué que les remerciements étaient la partie la plus importante d'un manuscrit de thèse. Croyez bien que je ne le remercie pas. A l'inverse, je remercie Laura de m'avoir fait découvrir l'incroyable similitude entre notre formule d'énergie et  $E=mc^2$ . C'est fou.

Je me dois évidemment de remercier Olivier Beaumont et Padma Raghavan pour leur travail. Je les remercie également, ainsi que Jean-Marc Pierson et Denis Trystram, pour leur venue à ma soutenance de thèse, et leurs questions pertinentes. Et merci à Anne et Yves pour ces trois années de science (et autres) à leurs côtés.

Je remercie chaleureusement toutes les personnes qui ont partagé mon bureau, leur bureau, ou le balcon. Et pour terminer, je ne peux que remercier le lecteur perdu qui s'est donné la peine de lire les remerciements, et peut-être même un chapitre.

# **Acknowledgements**

I would like to thank Olivier Beaumont and Padma Raghavan, my two reviewers, for their work, my committee chairman, Denis Trystram, and Jean-Marc Pierson for joining my thesis committee. I thank all of them for attending my defense, and especially Padma Raghavan who had a long way to go.

# **Contents**

| In | trodu | ection                                                 | j   |

|----|-------|--------------------------------------------------------|-----|

| 1  | On t  | the performance of greedy algorithms                   | 1   |

|    | 1.1   |                                                        | 1   |

|    | 1.2   | Related work                                           | 4   |

|    | 1.3   |                                                        | 5   |

|    | 1.4   |                                                        | 5   |

|    | 1.5   | The approximation factor as a function of $p$          |     |

|    | 1.6   | Conclusion                                             |     |

|    | 1.0   |                                                        | Ī   |

| 2  | Map   | pping concurrent streaming applications 1              | 7   |

|    | 2.1   | Introduction                                           | 7   |

|    | 2.2   | Related work                                           | 9   |

|    | 2.3   | Motivating example                                     | 0   |

|    |       | 2.3.1 Interval mappings                                | 0   |

|    |       | 2.3.2 General mappings                                 | :1  |

|    | 2.4   | Framework                                              | 2   |

|    |       | 2.4.1 Applicative framework                            | 2   |

|    |       | 2.4.2 Target platform                                  | 2   |

|    |       | 2.4.3 Mapping strategies and scheduling                |     |

|    |       | 2.4.4 Performance optimization criteria                |     |

|    |       | 2.4.5 Energy model                                     |     |

|    | 2.5   | Complexity results with the PATH model                 |     |

|    | 2.0   | 2.5.1 Period minimization                              |     |

|    |       | 2.5.2 Latency minimization                             |     |

|    |       | 2.5.3 Period/latency minimization                      |     |

|    |       | 2.5.4 Period/energy minimization                       |     |

|    |       | 2.5.5 Period/latency/energy minimization               |     |

|    |       | 2.5.6 Summary of complexity results for the PATH model |     |

|    | 2.6   | Complexity results with the WAVEFRONT model            |     |

|    | 2.0   | 2.6.1 Period minimization                              |     |

|    |       | 2.6.2 Period/latency minimization                      |     |

|    |       | 2.6.3 Period/latency/energy minimization               |     |

|    | 2.7   | Simulations with the WAVEFRONT model                   |     |

|    | 2.1   | 2.7.1 Integer linear program                           |     |

|    |       | 2.7.2 Heuristics                                       |     |

|    |       | 2.7.2 Figures 2.7.3 Simulation results                 |     |

|    |       | 2.1.3 Simulation results                               | . 7 |

iv CONTENTS

|   | 2.8         | Conclusion                                                      |

|---|-------------|-----------------------------------------------------------------|

| 3 | Rep         | lica placement and update strategies in tree networks 55        |

|   | 3.1         | Introduction                                                    |

|   | 3.2         | Framework                                                       |

|   |             | 3.2.1 Replica servers                                           |

|   |             | 3.2.2 With power consumption modes                              |

|   |             | 3.2.3 Objective functions                                       |

|   |             | 3.2.4 Summary of results                                        |

|   | 3.3         | Complexity results: update strategies                           |

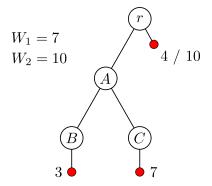

|   |             | 3.3.1 Running example                                           |

|   |             | 3.3.2 Dynamic programming algorithm                             |

|   |             | 3.3.3 Execution time of the algorithm                           |

|   | 3.4         | Complexity results with power                                   |

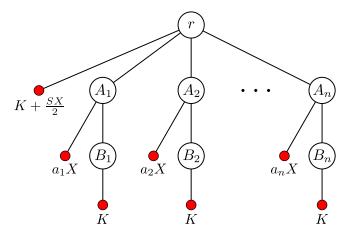

|   |             | 3.4.1 Running example                                           |

|   |             | 3.4.2 NP-completeness of MINPOWER                               |

|   |             | 3.4.3 A pseudo-polynomial algorithm for MINPOWER-BOUNDEDCOST 68 |

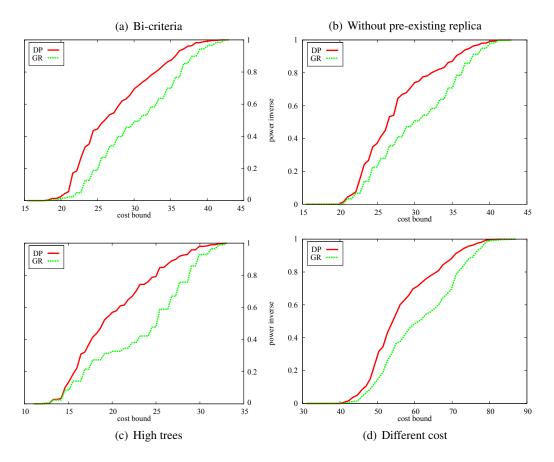

|   | 3.5         | Simulations                                                     |

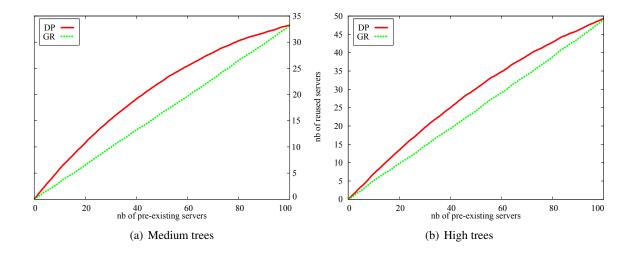

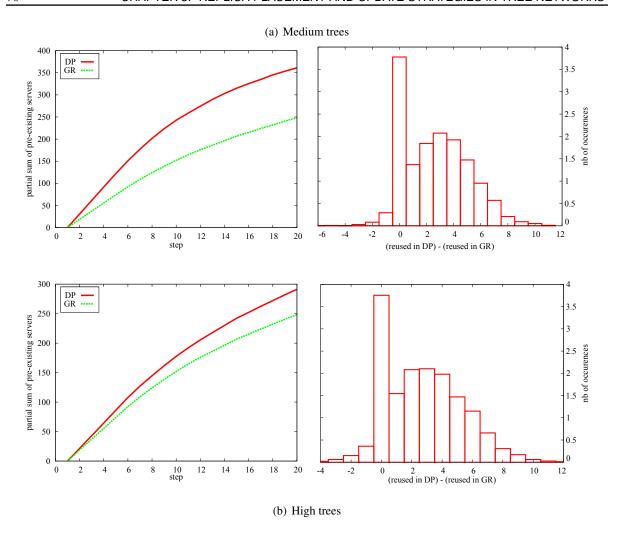

|   |             | 3.5.1 Impact of pre-existing servers                            |

|   |             | 3.5.2 With power consumption                                    |

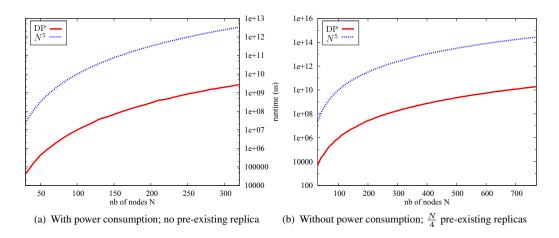

|   |             | 3.5.3 Running time of the algorithms                            |

|   | 3.6         | Conclusion                                                      |

|   | 3.0         | Conclusion                                                      |

| 4 | Map         | pping series-parallel workflows onto CMPs 75                    |

|   | 4.1         | Introduction                                                    |

|   | 4.2         | Related work                                                    |

|   | 4.3         | Framework                                                       |

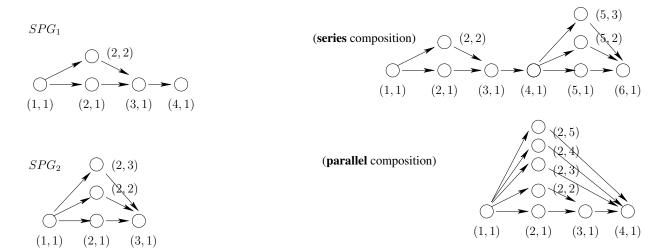

|   |             | 4.3.1 Applicative framework                                     |

|   |             | 4.3.2 Platform                                                  |

|   |             | 4.3.3 Mapping strategies                                        |

|   |             | 4.3.4 Period                                                    |

|   |             | 4.3.5 Energy model                                              |

|   | 4.4         | Complexity results                                              |

|   |             | 4.4.1 Uni-directional uni-line CMP                              |

|   |             | 4.4.2 Bi-directional uni-line CMP                               |

|   |             | 4.4.3 Square CMP                                                |

|   |             | 4.4.4 Integer linear program                                    |

|   | 4.5         | Heuristics                                                      |

|   | 1.0         | 4.5.1 Random heuristic                                          |

|   |             | 4.5.2 Greedy heuristic                                          |

|   |             | 4.5.3 2D dynamic programming algorithm                          |

|   |             | 4.5.4 1D heuristics                                             |

|   | 4.6         | Simulation results                                              |

|   | <b>⊤.</b> ∪ | 4.6.1 Simulation setting                                        |

|   |             | 4.6.1 Simulation setting                                        |

|   | 47          |                                                                 |

|   | 4.7         | Conclusion                                                      |

CONTENTS v

| 5 | Mar                | hattan routing on CMPs                                                                                                                                                                                                                                                                                                                 | 105                                                                                                   |

|---|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|   | 5.1                | Introduction                                                                                                                                                                                                                                                                                                                           | 105                                                                                                   |

|   | 5.2                | Related work                                                                                                                                                                                                                                                                                                                           | 106                                                                                                   |

|   | 5.3                | Framework                                                                                                                                                                                                                                                                                                                              | 107                                                                                                   |

|   |                    | 5.3.1 Platform and power consumption model                                                                                                                                                                                                                                                                                             | 107                                                                                                   |

|   |                    | 5.3.2 Communications                                                                                                                                                                                                                                                                                                                   | 107                                                                                                   |

|   |                    | 5.3.3 Routing rules                                                                                                                                                                                                                                                                                                                    | 108                                                                                                   |

|   |                    | 5.3.4 Problem definition                                                                                                                                                                                                                                                                                                               | 109                                                                                                   |

|   |                    | 5.3.5 Comparison of routing rules                                                                                                                                                                                                                                                                                                      | 109                                                                                                   |

|   | 5.4                | Theoretical results                                                                                                                                                                                                                                                                                                                    | 110                                                                                                   |

|   |                    | 5.4.1 Manhattan vs XY                                                                                                                                                                                                                                                                                                                  | 110                                                                                                   |

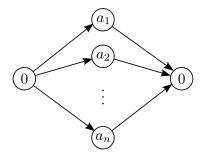

|   |                    | 5.4.2 NP-completeness                                                                                                                                                                                                                                                                                                                  |                                                                                                       |

|   | 5.5                | Heuristics                                                                                                                                                                                                                                                                                                                             | 117                                                                                                   |

|   |                    | 5.5.1 Simple greedy ( <b>SG</b> )                                                                                                                                                                                                                                                                                                      |                                                                                                       |

|   |                    | 5.5.2 Improved greedy ( <b>IG</b> )                                                                                                                                                                                                                                                                                                    |                                                                                                       |

|   |                    | 5.5.3 Two-bend ( <b>TB</b> )                                                                                                                                                                                                                                                                                                           |                                                                                                       |

|   |                    | 5.5.4 XY improver ( <b>XYI</b> )                                                                                                                                                                                                                                                                                                       |                                                                                                       |

|   |                    | 5.5.5 Path remover (PR)                                                                                                                                                                                                                                                                                                                |                                                                                                       |

|   | 5.6                | Simulations                                                                                                                                                                                                                                                                                                                            |                                                                                                       |

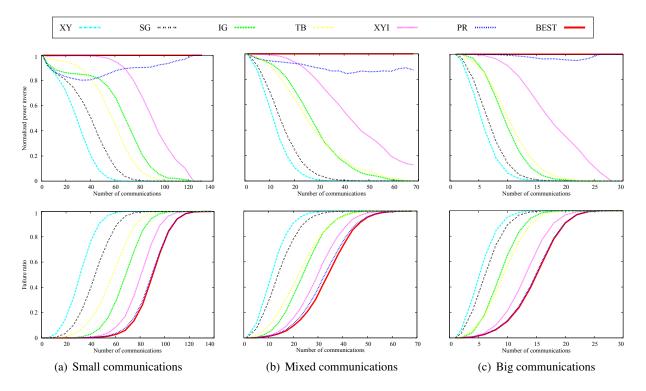

|   | 2.0                | 5.6.1 Sensitivity to the number of communications                                                                                                                                                                                                                                                                                      |                                                                                                       |

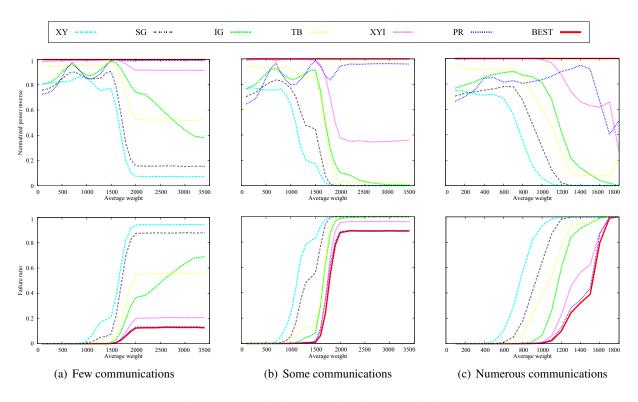

|   |                    | 5.6.2 Sensitivity to the size of communications                                                                                                                                                                                                                                                                                        |                                                                                                       |

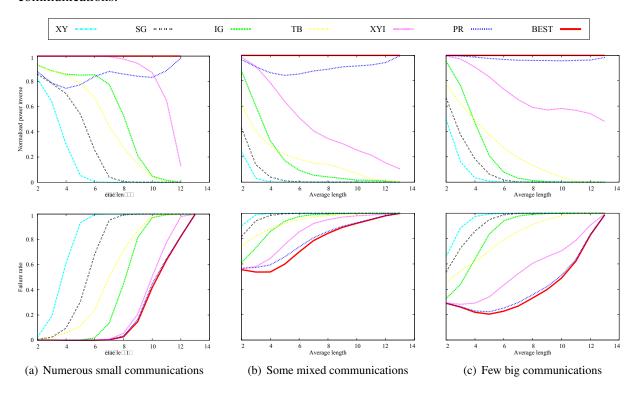

|   |                    | 5.6.3 Sensitivity to the average length of communications                                                                                                                                                                                                                                                                              |                                                                                                       |

|   |                    | 5.6.4 Summary of simulations                                                                                                                                                                                                                                                                                                           |                                                                                                       |

|   |                    | 5.6.4 Summary of Simulations                                                                                                                                                                                                                                                                                                           | 122                                                                                                   |

|   | 5.7                | Conclusion                                                                                                                                                                                                                                                                                                                             | 123                                                                                                   |

|   | 5.7                | Conclusion                                                                                                                                                                                                                                                                                                                             | 123                                                                                                   |

| 6 |                    | Conclusion                                                                                                                                                                                                                                                                                                                             | 123<br>125                                                                                            |

| 6 |                    |                                                                                                                                                                                                                                                                                                                                        | 125                                                                                                   |

| 6 | Asse               | ssment of bi-criteria heuristics for general DAGs                                                                                                                                                                                                                                                                                      | <b>125</b> 125                                                                                        |

| 6 | <b>Asse</b> 6.1    | ssment of bi-criteria heuristics for general DAGs Introduction                                                                                                                                                                                                                                                                         | <b>125</b> 125 126                                                                                    |

| 6 | Asse<br>6.1<br>6.2 | Sesment of bi-criteria heuristics for general DAGs Introduction                                                                                                                                                                                                                                                                        | 125<br>125<br>126<br>126                                                                              |

| 6 | Asse<br>6.1<br>6.2 | sment of bi-criteria heuristics for general DAGs Introduction                                                                                                                                                                                                                                                                          | 125<br>125<br>126<br>126<br>126                                                                       |

| 6 | Asse<br>6.1<br>6.2 | ssment of bi-criteria heuristics for general DAGs Introduction                                                                                                                                                                                                                                                                         | 125<br>125<br>126<br>126<br>126<br>127                                                                |

| 6 | Asse<br>6.1<br>6.2 | ssment of bi-criteria heuristics for general DAGs Introduction                                                                                                                                                                                                                                                                         | 125<br>126<br>126<br>126<br>127<br>127                                                                |

| 6 | Asse 6.1 6.2 6.3   | sment of bi-criteria heuristics for general DAGs Introduction Related work Framework 6.3.1 DAG 6.3.2 Platform 6.3.3 Frequency scaling strategies 6.3.4 Energy model                                                                                                                                                                    | 125<br>126<br>126<br>126<br>127<br>127                                                                |

| 6 | Asse<br>6.1<br>6.2 | ssment of bi-criteria heuristics for general DAGs Introduction                                                                                                                                                                                                                                                                         | 125<br>125<br>126<br>126<br>126<br>127<br>127<br>127                                                  |

| 6 | Asse 6.1 6.2 6.3   | sment of bi-criteria heuristics for general DAGs Introduction Related work Framework 6.3.1 DAG 6.3.2 Platform 6.3.3 Frequency scaling strategies 6.3.4 Energy model Slack reclamation algorithms 6.4.1 Mapping algorithm: HEFT                                                                                                         | 125<br>126<br>126<br>126<br>127<br>127<br>127<br>128<br>128                                           |

| 6 | Asse 6.1 6.2 6.3   | sment of bi-criteria heuristics for general DAGs Introduction Related work Framework 6.3.1 DAG 6.3.2 Platform 6.3.3 Frequency scaling strategies 6.3.4 Energy model Slack reclamation algorithms 6.4.1 Mapping algorithm: HEFT 6.4.2 LPHM                                                                                              | 125<br>126<br>126<br>126<br>127<br>127<br>127<br>128<br>128                                           |

| 6 | Asse 6.1 6.2 6.3   | ssment of bi-criteria heuristics for general DAGs Introduction Related work Framework 6.3.1 DAG 6.3.2 Platform 6.3.3 Frequency scaling strategies 6.3.4 Energy model Slack reclamation algorithms 6.4.1 Mapping algorithm: HEFT 6.4.2 LPHM 6.4.3 SRP                                                                                   | 125<br>126<br>126<br>126<br>127<br>127<br>127<br>128<br>128<br>128                                    |

| 6 | Asse 6.1 6.2 6.3   | sment of bi-criteria heuristics for general DAGs Introduction Related work Framework 6.3.1 DAG 6.3.2 Platform 6.3.3 Frequency scaling strategies 6.3.4 Energy model Slack reclamation algorithms 6.4.1 Mapping algorithm: HEFT 6.4.2 LPHM 6.4.3 SRP 6.4.4 LEneS                                                                        | 125<br>125<br>126<br>126<br>127<br>127<br>127<br>128<br>128<br>128<br>128                             |

| 6 | Assec 6.1 6.2 6.3  | Introduction Related work Framework 6.3.1 DAG 6.3.2 Platform 6.3.3 Frequency scaling strategies 6.3.4 Energy model Slack reclamation algorithms 6.4.1 Mapping algorithm: HEFT 6.4.2 LPHM 6.4.3 SRP 6.4.4 LEneS 6.4.5 Opt                                                                                                               | 125<br>125<br>126<br>126<br>127<br>127<br>127<br>128<br>128<br>128<br>130<br>133                      |

| 6 | Asse 6.1 6.2 6.3   | Introduction                                                                                                                                                                                                                                                                                                                           | 125<br>125<br>126<br>126<br>127<br>127<br>127<br>128<br>128<br>128<br>130<br>133                      |

| 6 | Assec 6.1 6.2 6.3  | Introduction Related work Framework 6.3.1 DAG 6.3.2 Platform 6.3.3 Frequency scaling strategies 6.3.4 Energy model Slack reclamation algorithms 6.4.1 Mapping algorithm: HEFT 6.4.2 LPHM 6.4.3 SRP 6.4.4 LEneS 6.4.5 Opt Simulations 6.5.1 Fatness and Communication-to-computation ratio                                              | 125<br>126<br>126<br>126<br>127<br>127<br>128<br>128<br>128<br>130<br>133<br>135<br>136               |

| 6 | Assec 6.1 6.2 6.3  | Introduction Related work Framework 6.3.1 DAG 6.3.2 Platform 6.3.3 Frequency scaling strategies 6.3.4 Energy model Slack reclamation algorithms 6.4.1 Mapping algorithm: HEFT 6.4.2 LPHM 6.4.3 SRP 6.4.4 LEneS 6.4.5 Opt Simulations 6.5.1 Fatness and Communication-to-computation ratio 6.5.2 Number of frequencies                  | 125<br>126<br>126<br>126<br>127<br>127<br>127<br>128<br>128<br>130<br>133<br>135<br>136               |

| 6 | Assec 6.1 6.2 6.3  | Introduction Related work Framework 6.3.1 DAG 6.3.2 Platform 6.3.3 Frequency scaling strategies 6.3.4 Energy model Slack reclamation algorithms 6.4.1 Mapping algorithm: HEFT 6.4.2 LPHM 6.4.3 SRP 6.4.4 LEneS 6.4.5 Opt Simulations 6.5.1 Fatness and Communication-to-computation ratio 6.5.2 Number of frequencies 6.5.3 Graph size | 125<br>126<br>126<br>126<br>127<br>127<br>127<br>128<br>128<br>128<br>130<br>133<br>135<br>136<br>136 |

| 6 | Assec 6.1 6.2 6.3  | Introduction Related work Framework 6.3.1 DAG 6.3.2 Platform 6.3.3 Frequency scaling strategies 6.3.4 Energy model Slack reclamation algorithms 6.4.1 Mapping algorithm: HEFT 6.4.2 LPHM 6.4.3 SRP 6.4.4 LEneS 6.4.5 Opt Simulations 6.5.1 Fatness and Communication-to-computation ratio 6.5.2 Number of frequencies                  | 125<br>126<br>126<br>126<br>127<br>127<br>128<br>128<br>128<br>130<br>133<br>135<br>136<br>136<br>137 |

Conclusion

143

| vi           | CONTENTS |

|--------------|----------|

|              |          |

| Bibliography | 149      |

Publications 159

## Introduction

Computer designers have always tried to improve the capacity of their products, and as of now, they have always succeeded. Computers become smaller and smaller, they can store more and more data, they compute faster and faster, etc. Pushed by an extension of the Moore's law, constructors have notably guaranteed that the computational power of the processors would double every 18 months.

Unfortunately, this computational power is deeply related to the chip power supply. The miniaturization of the chip, as well as the increase of the clock frequency, have led to a consequent rise of the dissipated power and the consumed energy. This recent evolution has rendered the energy issue crucial, both locally — in the small chip — and globally — in the wide world.

On the microscopic scale, the power density is beginning to be worrying, since it becomes close to the power of a nuclear reactor [116]. One of the consequences is that the temperature reaches an excessive level, which in particular weakens drastically the reliability of the chip.

On the world scale, when Mills invoked in 1999 the idea that the popularization of the computers, as well as their increasing need of electricity, would end up in a real energy issue [86], he encountered virulent criticisms, in particular by other researchers. One should point out today that he was not wrong.

The energy problem affects every computer user, from the company that uses data centers, to the lambda-user who owns his laptop at home, and including enterprises and research institutes that build supercomputers. Google revealed recently its power consumption during the year 2011: 260 million Watts, that is the whole output of a power plant, or about a quarter of the output of a nuclear plant. More generally the Climate Group and the Global e-Sustainability Initiative released in 2008 a report on cloud computing [92], which studies among others the electricity consumption of worldwide data centers. In 2007 they consumed 330 billion Watts hour, which is higher than the electricity consumption of such a big country like France. The current estimation gives an energy consumption of around 1000 billion Watts hour during the year 2020, which would overpass Russia in the ranking of countries consuming the most energy for electricity end, given that Russia is the third country in the list.

Those numbers about energy consumption can be translated as bad impacters on the environment. Also, according to a report by Greenpeace [48], the data centers are expected to reject the equivalent of 533 million tonnes of  $CO_2$  equivalent because of their electricity consumption, which comes mostly from dirty energies. If they were a country, they would end up in the top ten of the  $CO_2$  producers.

The computer scientists who work in high-performance computing expect to run an Exascale machine, able to compute  $10^{18}$  floating operations per second, in the 2020's. The first previsions show that if no effort is done concerning the energy consumption, it will be impossible for such an Exascale machine to exist. In addition, as said in "The IESP road map" [41], a reasonable power dissipation is estimated to be around  $100\,MW$ . Based on the cheapest electricity  $\cos t - 1\,W$  during  $1\,year$  at \$1, this means that every single percent of power saved will save 1 million dollar each year.

One can wonder if the energy issue is relevant for a basic user that turns on its small personal machine at home after work. A study (see [61]) shows that a personal computer is consuming  $500 \, kWh$  per year in average. Given that more than 1 billion personal computers populate the earth, their electricity

ii INTRODUCTION

consumption reaches 500 trillion Watts hour per year. And this is getting worse since 4 billions personal computers are expected in 2020.

The energy that feeds a computer is shared between different parts, such like disk drive, motherboard, fans, etc. But the most energy-hungry component is the processor: even idle, it dissipates at least half of the total power. That is why we only consider this energy in this thesis. In single core processors, this energy is the energy consumed by the Central Processing Unit. The most commonly used model about the power dissipated by a CPU is given in the following paragraph. In multi-core processors, a part of the power is dissipated in routers that ensure the communication between cores; the model that we use makes the power dissipated by CPUs (for the computations) symmetrical to the power dissipated by routers (for the communications).

The consumed power in a CPU is divided into a static part  $P_{stat}$  and a dynamic part  $P_{dyn}$ . The static part is the cost for a processor to be on, whereas the dynamic part is an additional cost for the computations, according to the speed at which the processor is running. More precisely, we have:  $P_{stat} = VI_{leak}$  and  $P_{dyn} = aCV^2 f$ , where:

- -a is the switching activity: the chip is composed of transistors, that switches during a computation;

- C is the physical capacitance;

- -V is the supply voltage;

- -f is the clock frequency, or the number of clock tops per second;

- $-I_{leak}$  is the leakage current, due to the nature of the transistors.

A lot of research has been done with the aim to reduce power consumption through hardware modifications, and tries to act on all those factors. Transistors have been improved, in order to reduce a and C. The temperature plays an important role, through the current leakage. When the temperature is rising, the current leakage is increasing, thus the dissipated power is higher, which leads to an elevation of the temperature. This vicious circle must be avoided, thanks to effective cooling systems. But the saved power in the processor must be greater than the power needed to make the cooling system work. That is why surprising cooling architectures appear sometimes, like from Google, which wants to install a data center on a boat to refresh it at least cost.

The most important breakthrough is the advent of the Dynamic Voltage and Frequency Scaling (DVFS), which is enabled on almost all recent processors: the new generation is indeed able to run at different speeds and voltages, those parameters being set up by the user. The name of this technique is a little confusing: from an energy perspective, we can think that we just have to set the voltage to its minimum and the frequency to its maximum to obtain an excellent ratio performance versus dissipated power. This is not so easy, since only a set of voltages is reachable, and each voltage is associated with a set of possible frequencies. Of course, the upper the supply voltage, the higher the running frequency can be. This reality is often simplified through an idealized model. Actually, several models exist to describe the same reality. It is commonly assumed that the voltage is proportional to the frequency, implying a dynamic power in the cube of the frequency. Concerning the set of possible frequencies, it can be either continuous — the frequency stays anywhere between a minimum frequency and a maximum frequency — or discrete — we are given a set of possible frequencies.

Finally, a simple but efficient way to reduce the consumed power, while maintaining a given level of performance, is to divide the computational units into smaller ones. This idea is exploited in the Chip MultiProcessors (CMPs): two processing units at frequency f/2 dissipate a power  $f^3/4$ , whereas one bigger processing unit at frequency f dissipates a power  $f^3$ , for the same number of operations per second.

Equipped with the power dissipation model and the promising DVFS method, there just remains to convert the try: deriving algorithms that squeeze the most out of this potential energy saving. This technique should open algorithmists' mind in order to make the existing algorithms energy-aware and to design new algorithms that will be energy-oriented.

Because of the convexity of the power function as a function of the running frequency, if a processor cannot be turned off, it is always better to run its work as slow as possible. However, this solution would not be accepted by most people: performance degradation is not allowed in the computers world. In any domain, only a tiny minority would sacrifice the performance of their applications. Obviously, a supercomputer manager would deny it, since his primary goal is to compute always faster, but even a basic user would be furious if his machine was becoming slower.

Therefore we have to find smarter ways to decide for a scheduling policy. The frequencies must be balanced, again because of the convexity of the power function, so that the total execution time, or any performance-related criterion, is not strongly downgraded. Instead of fulfilling a tight constraint on the performance, we can indeed be given an interval of validity.

The reverse problem can also be stated: we dispose of a given amount of energy, and a performance-related criterion must be maximized. This problem takes place very naturally in useful applications, e.g. an unplugged laptop must run the maximum amount of work until its battery is empty, or the lifetime of an embedded device must be maximized.

Those two very general problems can be instanciated into numerous smaller ones. During this thesis we have been dealing with some of them, which we describe briefly below.

# On the performance of greedy algorithms for power consumption minimization [B4]

We start with a simple and classical problem, accompanied by a simple and classical greedy algorithm. We are given a set of homogeneous processors and a set of independent jobs that are to be executed on the processors. We want to assign each job to a processor in the best way. This problem has been widely studied, when "best way" means "so that the totality of the jobs is finished as soon as possible", or in technical terms, "so that the makespan is minimum". In this case a natural heuristic consists in greedily assigning each job to the currently least loaded processor.

In this first chapter, we study a close problem, in which "best way" means "so that the processors consume as less energy as possible". We dispose of processors with continuous frequencies, and we must fulfill a constraint on the makespan, so that the energy consumed by a processor is equal to the cube of the sum of its computations size. Intuitively the previous algorithm seems reasonable, since it balances the computations. We exhibit lower bounds on the energy consumption of the algorithm, for online and offline versions: in this second version, jobs are sorted by non-increasing size. We show that those bounds are tight.

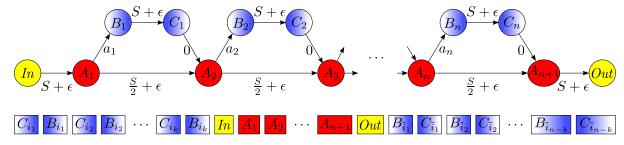

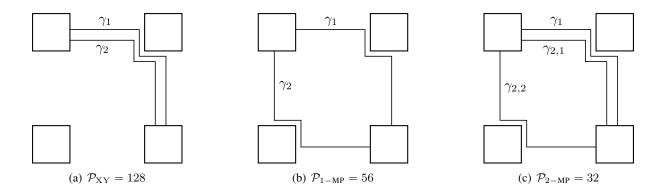

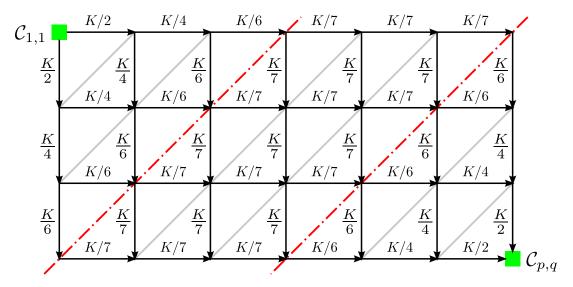

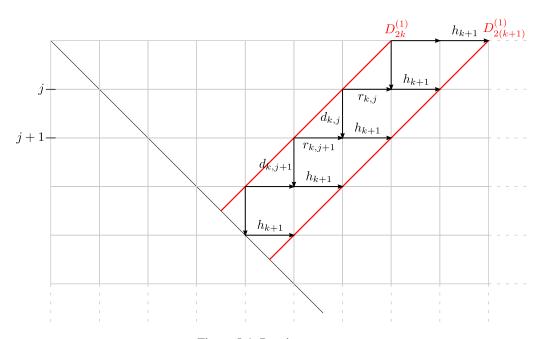

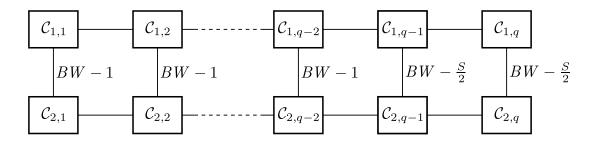

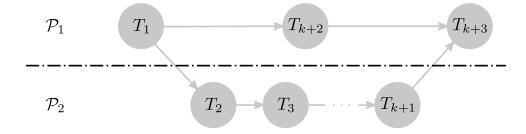

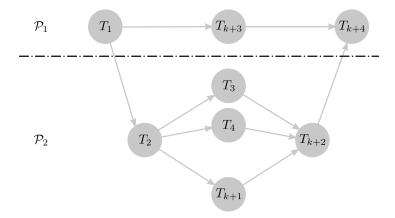

## Mapping concurrent streaming applications [B7, B6, A1]

In this second chapter, a few complications occur. On the one hand, tasks are not any more independent: we have several applications, each of them being a linear chain of tasks – apart from the entry task and the exit task, each task receives data from its previous task and sends data to its successor task. On the other hand, we optimize now three criteria, namely energy, period and latency. The energy remains the energy consumed by the processors, and latency is a measure that is close to makespan and execution time. The applications we consider here are streaming applications: in other words, they never stop to

iv INTRODUCTION

compute. A set of data enters the application through the entry task every period, and will be output by the exit task after some periods. This period is thus another performance-related criterion.

In order to understand precisely where the difficulty of the problem comes from, we define different way to map the tasks onto the processors, and establish the problem complexity under each mapping rule. The one-to-one mappings, in which a processor is assigned at most one task, are a restriction of the interval mappings, where a processor is assigned an interval of consecutive tasks. A general mapping does not suffer from any constraint. In addition to those different complexity levels of mappings, we lean on different heterogeneity degrees concerning the platform: homogeneous processors and homogeneous links between them, heterogeneous processors and homogeneous platforms.

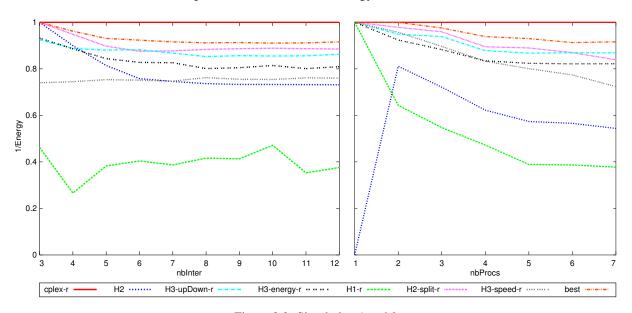

On the theoretical side, we perform an exhaustive complexity study of all mono-criterion, bi-criteria and tri-criteria problems, according to the mapping rules and the heterogeneity of the platform: we exhibit polynomial algorithms for simpler instances and NP-completeness proofs for more intricate ones. On the practical side, we design several heuristics that give a reasonable solution to the most general problem, and run simulations with randomly generated applications.

#### Replica placement and update strategies in tree networks [B5]

In this third chapter, the elements that need to be computed are no longer distributed along a linear chain but are located on the leaves of a tree. The leaves are called clients, and they send requests that need to be handled by a server upper in the tree. Such a problem finds applications in real-life: in Video on Demand services, users are requesting video files in the network. One server cannot serve all the user requests; therefore the initial file has to be replicated inside the tree, so that every user can receive its movie in acceptable time.

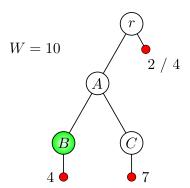

Let us describe more precisely the framework: the requests of the clients are counted per time unit, hence the requests a server handles are also per time unit. The objective function is to minimize the power consumed by the servers. Obviously, the more requests, the higher dissipated power. On top of this goal to save power, we add the notion of dynamicity. Sometimes the number of requests of a client might change, and the previous distribution of the servers may not be optimal. Despite that, moving a server or creating a new server might not be advantageous, since it implies turning on a new server and copying the file into its new location. Also we introduce a cost related to such server operations. Finally, the problem of this chapter is the following: we are given a tree, filled with clients, and provided with a set of pre-existing servers, and we want to minimize the dissipated power, without exceeding a given bound on the cost.

We study the complexity of the problem under different hypotheses, and we give notably an intricate pseudo-polynomial dynamic programming algorithm. To the best of our knowledge, we are the first to deal with power consumption and dynamicity on this problem, so we evaluate our algorithm by comparing with a classical algorithm that solves the simple replica placement problem.

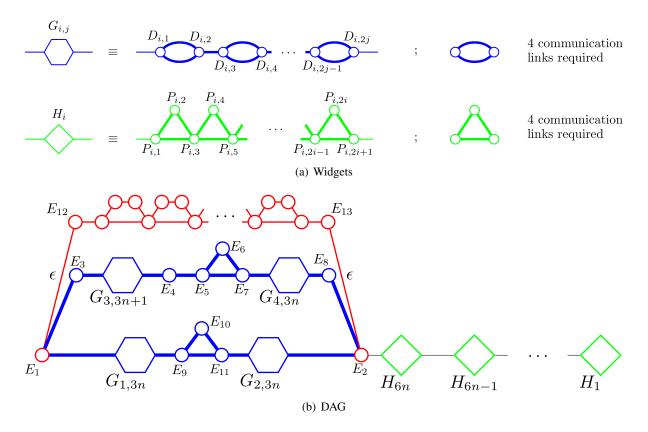

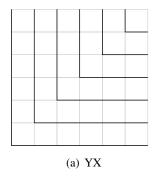

#### Mapping series-parallel workflows onto chip multiprocessors [B3]

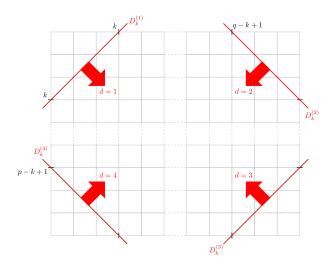

In this fourth chapter, we come back to streaming applications that have to be mapped onto a platform. We are given an application in the form of a task graph, which belongs to the series-parallel class of graphs. Since all the task graphs of streaming applications that we encountered were series-parallel, this is a reasonable assumption, and very useful from a theoretical perspective. With series-parallel graphs, we exhibit a polynomial algorithm on a simple architecture, and interesting NP-completeness proofs on more complicated ones. With general DAGs, we just would have an immediate and meaningless NP-completeness proof on the simplest architecture. We choose to map such applications onto a current and promising platform: the chip multiprocessor. Those multi-core processors, whose cores are arranged along a bi-dimensional grid, are now really common, and are expected to stay the main architecture for many years.

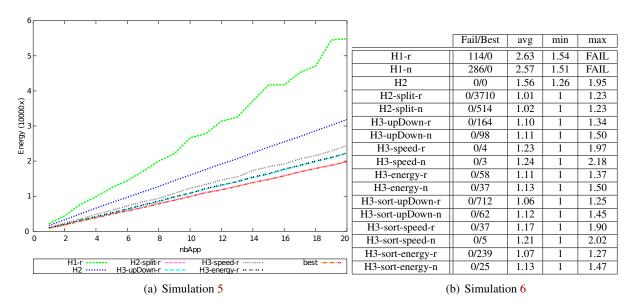

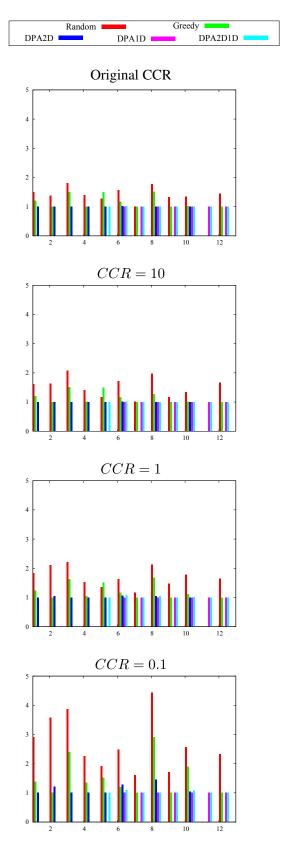

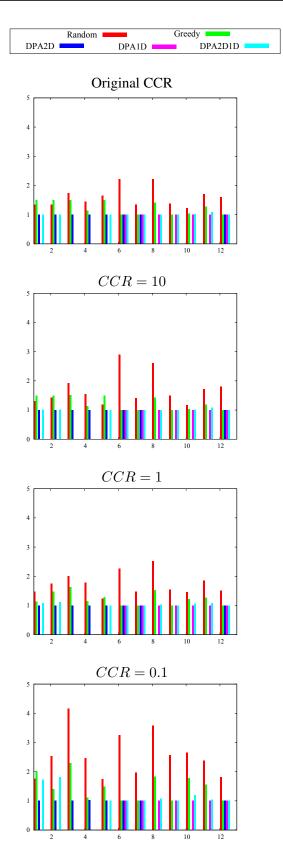

Concerning the energy issue, we take into account both the energy consumed by the computations, and the energy consumed by the communications. We try to minimize the global energy, given a bound on the period of the application. After the complexity study, we present some heuristics and assess their performance through two sets of simulations. The first one is done on a randomly generated set of applications, whereas the second one evaluates the algorithms on a set of real-life applications.

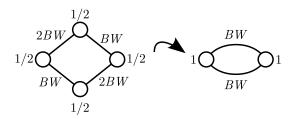

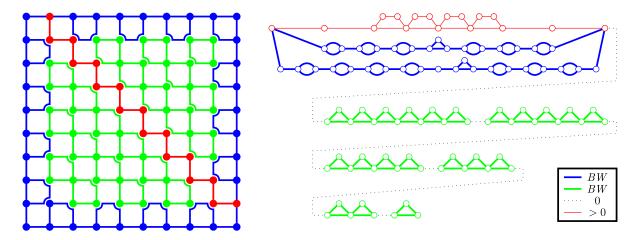

#### Manhattan routing on chip multiprocessors [B1]

In this fifth chapter, we extend the work of the previous chapter, that was mainly focused on computations. Now we only consider the energy consumed by communications, still on a chip multiprocessor. We are given a set of communications, i.e., a set of triplets composed of a source core, a destination core, and a communication volume. Our aim is to minimize the energy consumed to route all those communications through the multi-core processor.

For the sake of simplicity, the implementation of the routing strategy in current chip multiprocessors is straightforward. Communications are following an XY route: data packets are sent horizontally first, then vertically. This may lead to a huge heterogeneity in the load of the links. And since the dissipated power is convex according to total volume of the communications going through a link, this power is not optimized at all. In this chapter, we show to which extent different strategies can impact the dissipated power. We compare XY routing, with Manhattan routings — where a communication can take any Manhattan path from the source core to the destination core — both single-path and multipath. We dispose of an additional degree of freedom in this last case: a communication can be split among several Manhattan paths. We derive worst-case upper bounds of the ratio power consumed by an XY routing over power consumed by a Manhattan routing, and we exhibit examples realizing this ratio, hence showing the tightness of those bounds.

#### Assessment of bi-criteria heuristics for general directed acyclic graphs

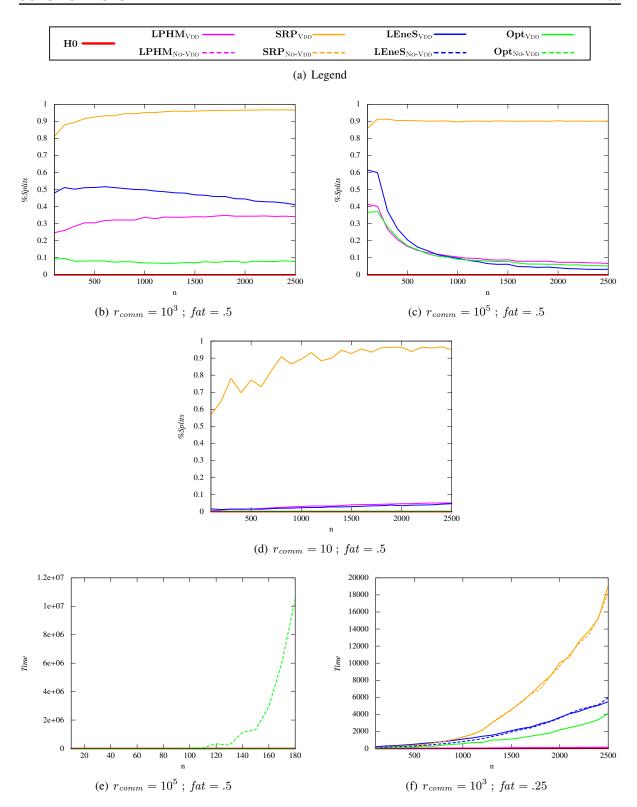

In this last chapter, we aim at assessing the performance of often quoted heuristics for the following problem. We are given a set of dependent tasks, in the form of a Directed Acyclic Graph (DAG), which has already been mapped onto a set of processors running at their highest frequency, with the objective to minimize the total execution time. The goal of the algorithms we study is to minimize the energy consumption by downgrading processors while maintaining the makespan. We develop two variants of each heuristic, for both VDD-HOPPING and NO-VDD-HOPPING models. When VDD-HOPPING is allowed, a processor can be upgraded or downgraded at any time, while in the NO-VDD-HOPPING model, a task is associated to a unique speed.

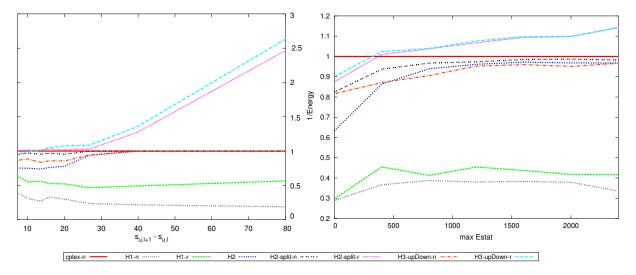

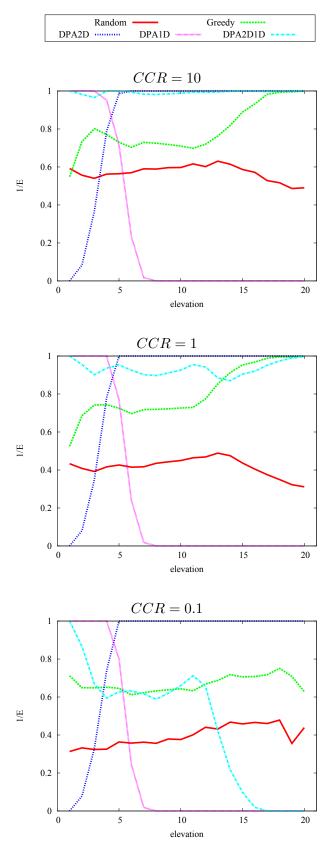

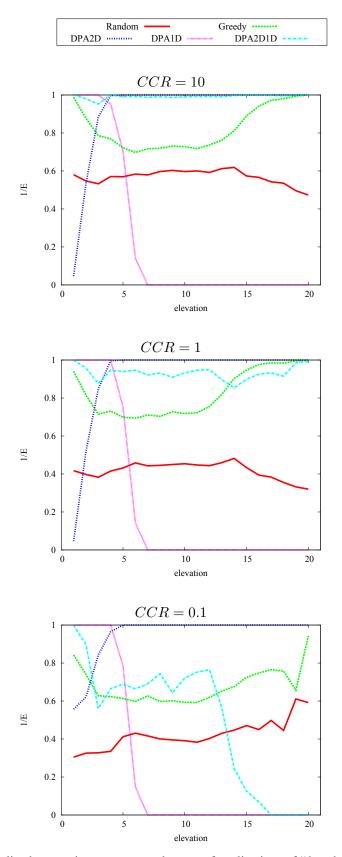

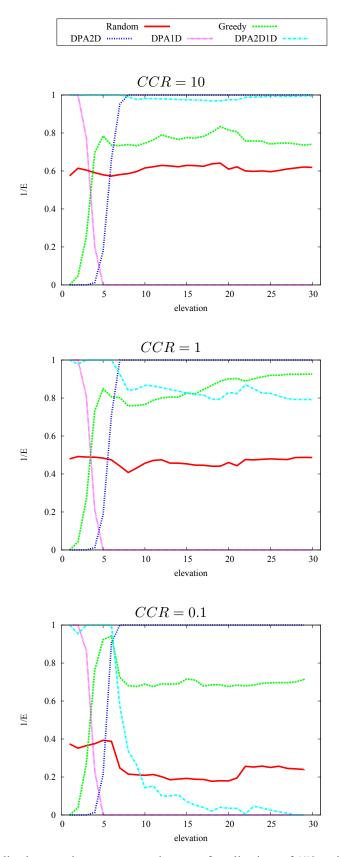

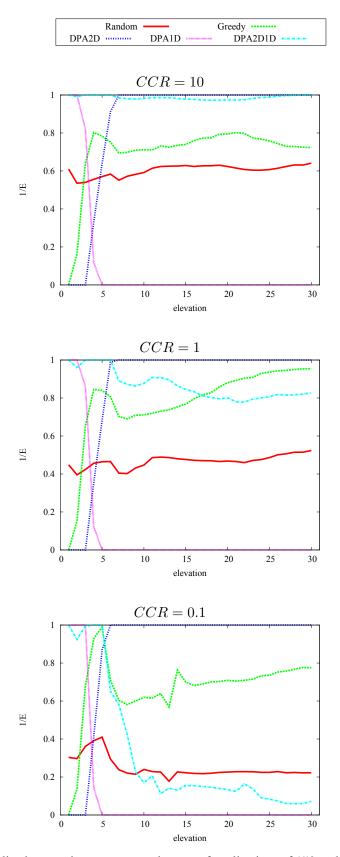

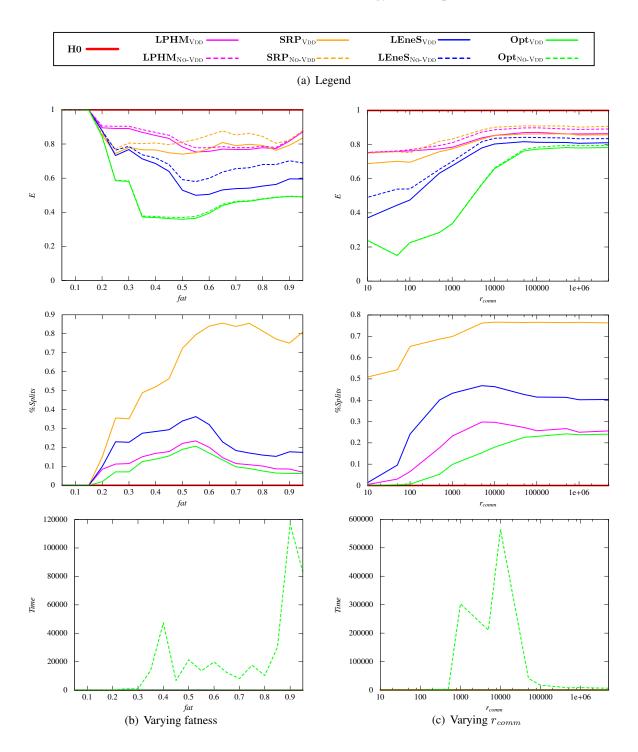

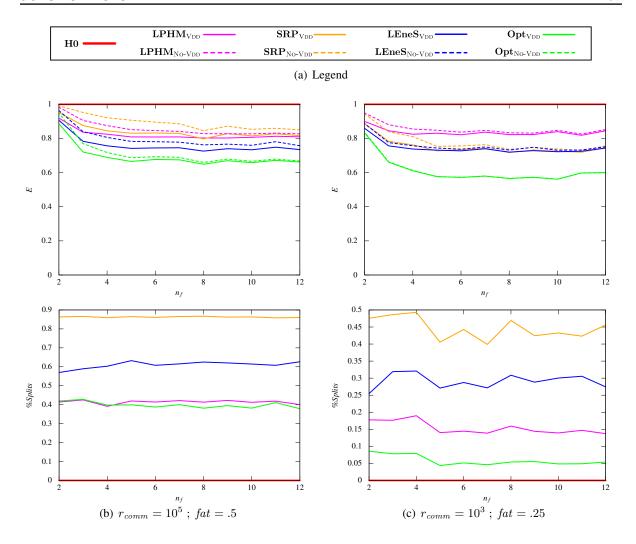

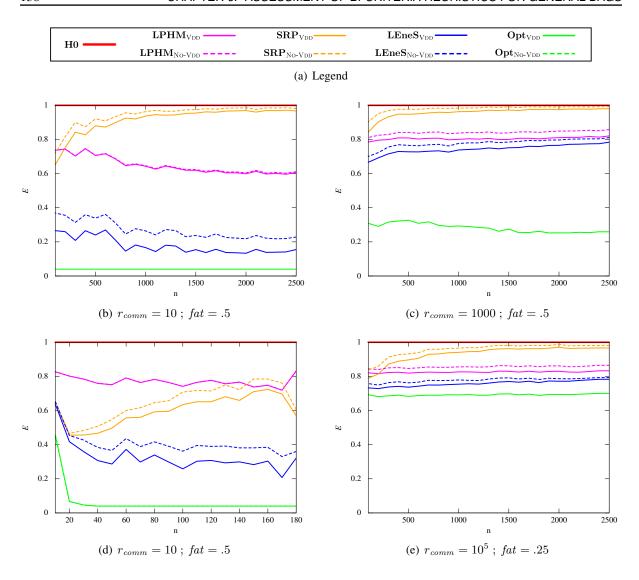

We conduct a large set of simulations and vary several parameters: fatness of the graph, communication-to-computation ratio, number of possible frequencies and graph size. By inspecting the role of each parameter, we find domains in which heuristics are competitive or not. Finally we ask whether using VDD-HOPPING model achieves significant energy savings, compared to the NO-VDD-HOPPING model.

vi INTRODUCTION

# **Chapter 1**

# On the performance of greedy algorithms for power consumption minimization

#### 1.1 Introduction

In this chapter, we revisit the well-known greedy algorithm for scheduling independent jobs on parallel processors, with the objective of energy minimization. We assess the performance of the online version, as well as the performance of the offline version, which sorts the jobs by non-increasing size before execution.

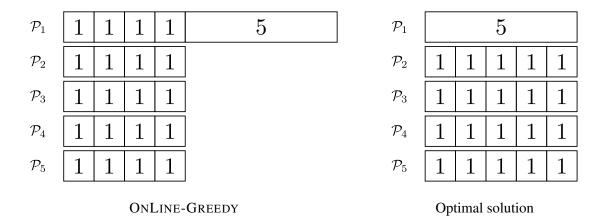

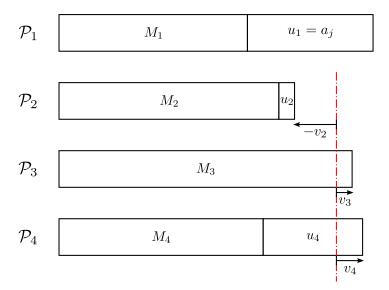

For convenience, here is a quick background on the greedy algorithm for makespan minimization. Consider a set  $\mathfrak{J}$  of n independent jobs  $J_1, \ldots, J_n$  to be scheduled on a set  $\mathfrak{P}$  of p parallel processors  $\mathcal{P}_1, \ldots, \mathcal{P}_p$ . Let  $a_i$  be the size of job  $J_i$ , that is the time it requires for execution. The algorithm comes in two versions, online and offline, or without/with sorting jobs. In the online version of the problem, jobs arrive on the fly. The ONLINE-GREEDY algorithm assigns the last incoming job to the currently least loaded processor. In the offline version of the problem (see [46]), all job sizes are known in advance, and the OFFLINE-GREEDY starts by sorting the jobs (largest sizes first). Then it assigns jobs to processors exactly as in the online version. The performance of both versions is characterized by the following propositions (see Figures 1.1 and 1.2 for an illustration of the worst-case scenarios):

**Proposition 1.1.** For makespan minimization, ONLINE-GREEDY is a  $2 - \frac{1}{p}$  approximation, and this approximation factor is met on the following instance:

```

-n = p(p-1) + 1,

-a_i = 1 for 1 \le i \le n-1,

-and \ a_n = p.

```

**Proposition 1.2.** For makespan minimization, OFFLINE-GREEDY is a  $\frac{4}{3} - \frac{1}{3p}$  approximation, and this approximation factor is met on the following instance:

```

-n = 2p + 1,

-a_{2i-1} = a_{2i} = 2p - i for 1 \le i \le p,

-and \ a_n = p.

```

Assume that we can vary processor speeds, for instance through dynamic voltage scaling. In that case we can always use the smallest available speed for each processor, at the price of a dramatic decrease in performance.

Figure 1.1: Tight instance for OnLine-Greedy (with p = 5).

Figure 1.2: Tight instance for OffLine-Greedy (with p = 5).

The problem is in fact a bi-criteria problem: given a bound M on the makespan, what is the schedule that minimizes the power consumption while enforcing the execution time bound?

For simplicity, we can assume that processors have continuous speeds (see [62, 40, 87, 95]), and scale the problem instance so that M=1. This amounts to setting each processor speed equal to its workload, and to minimizing the total energy dissipated during an execution of length one time-unit. In other words, this amounts to minimizing the total dissipated power, which is proportional to the sum of the cubes of the processor speeds (a model commonly used, e.g. in [95, 24, 12, 30]).

Formally, let  $alloc: \mathfrak{J} \to \mathfrak{P}$  denote the allocation function, and let  $load(q) = \{i \mid alloc(J_i) = \mathcal{P}_q\}$  be the index set of jobs assigned to processor  $\mathcal{P}_q$ , for  $1 \leq q \leq p$ .

The power dissipated by  $\mathcal{P}_q$  is  $\left(\sum_{i \in load(q)} a_i\right)^3$ , hence the objective is to minimize

$$\sum_{q=1}^{p} \left( \sum_{i \in load(q)} a_i \right)^3 . \tag{1.1}$$

1.1. INTRODUCTION 3

This is to be contrasted with the makespan minimization objective, which writes

$$\max_{1 \le q \le p} \sum_{i \in load(q)} a_i . \tag{1.2}$$

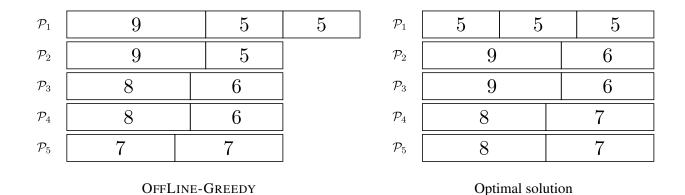

However, because of the convexity of the cubic power function, the "natural" greedy algorithm is the same for both objectives: assigning the next job to the currently least loaded processor minimizes, among all possible assignments for that job, both the current makespan and dissipated power. We observe that when p=2, the optimal solution is the same for both objectives. However, this is not true for larger values of p. For example, consider the instance with n=6, p=3,  $a_1=8.1$ ,  $a_2=a_3=5$ ,  $a_4=a_5=4$  and  $a_6=2$ .

- The optimal solution for the makespan is the partition  $\{J_1\}, \{J_2, J_3\}, \{J_4, J_5, J_6\}$ , with makespan 10 and power 2531.441.

- The optimal solution for the power is the partition  $\{J_1, J_6\}, \{J_2, J_4\}, \{J_3, J_5\}$ , with makespan 10.1 (hence not optimal) and power 2488.301 (the processor loads are better balanced than in the previous solution, leading to a lower power consumption).

This example is illustrated in Figure 1.3.

Figure 1.3: Different optimal solutions for makespan and power minimization.

Just as the original makespan minimization problem, the (decision version of the) power minimization problem is NP-complete, and a PTAS (polynomial-time approximation scheme) can be derived. However, the greedy algorithm plays a key role in all situations where jobs arrive on the fly, or when the scheduling cost itself is critical. This was already true for the makespan problem, but may be even more important for the power problem, due to the environmental (or "green") computing perspective that applies to all application fields and computing platforms.

We discuss related work in Section 1.2. The main results of the chapter are summarized in Section 1.3, and compared to previously known results. Section 1.4 is devoted to a detailed proof of both theorems, and also we provide in Section 1.5 numerical values of the approximation factors for small values of p. We give some final remarks in Section 1.6.

#### 1.2 Related work

The greedy algorithm has been widely studied in the literature, both in the offline and online versions. A more general problem than minimizing the sum of the cubes of the processor workloads (Equation (1.1)) is to minimize their  $L_T$  norm, i.e., the quantity

$$N_r = \left(\sum_{q=1}^p \left(\sum_{i \in load(q)} a_i\right)^r\right)^{\frac{1}{r}}.$$

(1.3)

Note that

$$N_{\infty} = \lim_{r \to \infty} N_r = \max_{1 \le q \le p} \sum_{i \in load(q)} a_i$$

is the makespan minimization objective (Equation (1.2)), while  $(N_3)^3$  is the power minimization objective of this chapter (Equation (1.1)).

Chandra and Wong [23] consider the problem of minimizing  $N_2$  in the offline version. They show that OFFLINE-GREEDY is a  $\frac{5}{2\sqrt{6}}$  approximation algorithm for r=2, but this bound is not tight: they give lower bounds for the approximation ratio of OFFLINE-GREEDY for the  $N_2$  problem: their bound is  $\frac{\sqrt{37}}{6}$  with an even number p of processors,  $\frac{\sqrt{83}}{9}$  with p=3 processors, and  $\sqrt{\frac{37}{36}-\frac{1}{36p}}$  with an odd number  $p \geq 5$  of processors. The gap between these bounds has been filled by Leung and Wei [79], who provide a tight approximation factor for the performance of OFFLINE-GREEDY for the  $N_2$  problem.

Chandra and Wong [23] also provide lower and upper bounds for the approximation factor of OFFLINE-GREEDY for the general  $N_r$  problem. In particular for r=3, their upper bound is  $\frac{19}{45}\sqrt[3]{15}\approx 1.04$  (and their lower bound depends on the processor number p). Note that Theorem 1.2 below gives the exact approximation factor for any value of p, thereby closing the gap between lower and upper bounds. Finally, we point out that Chandra and Wong [23] do not deal with the online version of the problem, which Theorem 1.1 below completely solves.

Awerbuch et al. [11] discuss the problem of minimizing  $N_r$  for general r and for the online version of the problem. However, they have an additional rule: each job can be assigned only to a subset of the processors, called its permissible servers. They first study the problem with unit-size jobs (which is trivial without permissible servers), and they extend their analysis to the case where each job has a different execution cost on each of its admissible servers. They prove that ONLINE-GREEDY is a  $1+\sqrt{2}$  approximation algorithm for r=2, and a  $\Theta(r)$  approximation algorithm in the general case.

Alon et al. [3] provide a PTAS (polynomial-time approximation scheme) to minimize  $N_r$ . This result is of great theoretical interest but only applies to the offline version of the problem, and is not related to the OFFLINE-GREEDY algorithm.

Finally, Avidor et al. [10] discuss the performance of ONLINE-GREEDY when minimizing  $N_r$  for general r. They provide an upper bound  $2-\Theta(\frac{\ln r}{r})$  for the approximation factor of ONLINE-GREEDY, independently of the number of processors. This is to be contrasted with Theorem 1.1 which provides a tight approximation factor for any processor number in the case r=3.

1.3. MAIN CONTRIBUTIONS 5

#### 1.3 Main contributions

The main results of the chapter are summarized in Theorems 1.1 and 1.2 below:

**Theorem 1.1.** For power minimization, ONLINE-GREEDY is a  $f_p^{(on)}(\beta_p^{(on)})$  approximation, where

$$f_p^{(\text{on})}(\beta) = \frac{\frac{1}{p^3} \left( (1 + (p-1)\beta)^3 + (p-1)(1-\beta)^3 \right)}{\beta^3 + \frac{(1-\beta)^3}{(p-1)^2}} ,$$

and where  $\beta_p^{(\mathrm{on})}$  is the unique root in the interval  $[\frac{1}{p},1]$  of the polynomial

$$g_p^{(\text{on})}(\beta) = \beta^4(-p^3 + 4p^2 - 5p + 2) + \beta^3(-2p^2 + 6p - 4) + \beta^2(-4p + 5) + \beta(2p - 4) + 1.$$

This approximation factor cannot be improved.

**Theorem 1.2.** For power minimization, OffLine-Greedy is a  $f_p^{(\text{off})}(\beta_p^{(\text{off})})$  approximation, where

$$f_p^{(\text{off})}(\beta) = \frac{\frac{1}{p^3} \left( \left( 1 + \frac{(p-1)\beta}{3} \right)^3 + (p-1) \left( 1 - \frac{\beta}{3} \right)^3 \right)}{\beta^3 + \frac{(1-\beta)^3}{(p-1)^2}} ,$$

and where  $\beta_p^{(\text{off})}$  is the unique root in the interval  $[\frac{1}{p},1]$  of the polynomial

$$g_p^{(\text{off})}(\beta) = \beta^4(-9p^3 + 30p^2 - 27p + 6) + \beta^3(-6p^2 + 18p - 12) + \beta^2(-78p^2 + 126p + 33) + \beta(18p - 180) + 81.$$

This approximation factor cannot be improved.

We point out that this chapter prove tight approximation factors for the problem of minimizing  $N_3$ , for any processor number p, both in the offline and online versions of the problem, which is totally new.

#### 1.4 Proof of the main theorems

The proof of Theorems 1.1 and 1.2 is organized as follows:

- Proposition 1.3 provides a technical bound that is valid for both the online and offline versions;

- This technical bound is used in Proposition 1.4 to show that ONLINE-GREEDY is a  $f_p^{(\text{on})}(\beta_p^{(\text{on})})$  approximation, and in Proposition 1.5 to show that OFFLINE-GREEDY is a  $f_p^{(\text{off})}(\beta_p^{(\text{off})})$  approximation;

- Finally, instances showing that the above factors are tight are given in Proposition 1.6 for ONLINE-GREEDY, and in Proposition 1.7 for OFFLINE-GREEDY.

**Proposition 1.3.** For any given instance, the performance ratio  $\frac{P_{\text{greedy}}}{P_{\text{opt}}}$  of the greedy algorithm (OnLine-Greedy or Offline-Greedy) is such that

$$\frac{P_{\text{greedy}}}{P_{\text{opt}}} \le \frac{\left(\frac{S + (p-1)a_j}{p}\right)^3 + (p-1)\left(\frac{S - a_j}{p}\right)^3}{O^3 + (p-1)\left(\frac{S - O}{p-1}\right)^3},$$

(1.4)

where

- $P_{\rm greedy}$  is the power dissipated by the greedy algorithm;

- $-P_{\mathrm{opt}}$  is the power dissipated in the optimal solution;

$$-S = \sum_{i=1}^{n} a_i;$$

- O is the largest processor load in the optimal solution;

- j is the index of the last job assigned to the processor that has the largest load in the greedy algorithm.

*Proof.* For the optimal solution, we immediately have

$$P_{\text{opt}} \ge O^3 + (p-1) \left( \frac{S-O}{p-1} \right)^3.$$

This is because of the definition of O, and of the convexity of the power function.

There remains to show that for the greedy algorithm,

$$P_{\text{greedy}} \le \left(\frac{S + (p-1)a_j}{p}\right)^3 + (p-1)\left(\frac{S - a_j}{p}\right)^3. \tag{1.5}$$

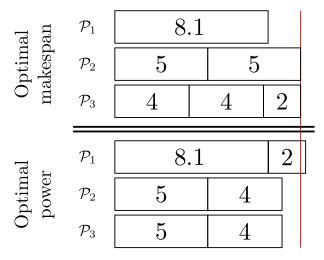

Without loss of generality, let  $\mathcal{P}_1$  be the maximum loaded processor in the solution returned by the greedy algorithm. For all  $q \in \{1, \dots, p\}$ , let  $M_q$  be the load of processor  $\mathcal{P}_q$  before the assignment of the job  $J_j$ , and let  $u_q \geq 0$  be the sum of the sizes of all jobs assigned to  $\mathcal{P}_q$  after  $J_{j-1}$ , as illustrated in Figure 1.4 for p=4. By definition of j, we have  $u_1=a_j$ . In the example,  $u_3=0$ , i.e., no jobs have been assigned to  $\mathcal{P}_3$  after  $J_{j-1}$ .

The power returned by the greedy algorithm is thus:

$$P_{\text{greedy}} = \sum_{q=1}^{p} (M_q + u_q)^3 = (M_1 + a_j)^3 + \sum_{q=2}^{p} (M_q + u_q)^3$$

.

For  $q \in \{2, ..., p\}$ , let  $v_q$  be the variation of the load of processor  $\mathcal{P}_q$  from the average load of processors other than  $\mathcal{P}_1$ :

$$v_q = M_q + u_q - \frac{S - M_1 - a_j}{p - 1}$$

,

and Figure 1.4 illustrates this notation. Then

$$P_{\text{greedy}} = \underbrace{(M_1 + a_j)^3 + \sum_{q=2}^{p} \left(\frac{S - M_1 - a_j}{p - 1} + v_q\right)^3}_{f(M_1)}.$$

Figure 1.4: Notations for p = 4.

Note that the  $v_q$  can be either positive or negative (in the example,  $v_2 \le 0$  and  $v_3 \ge 0$ ), and that their sum is always zero. To check this analytically, observe that  $(M_1 + a_j) + \sum_{q=2}^p \left( \frac{S - M_1 - a_j}{p-1} + v_q \right) = S$ , hence  $\sum_{q=2}^p v_q = 0$ .

Now, given the  $v_q$ , we have for  $p \ge 2$ , since  $1 = \frac{p-1}{p-1}$ :

$$f'(M_1) \ge \frac{3}{p-1} \times \sum_{q=2}^{p} \left( (M_1 + a_j)^2 - \left( \frac{S - M_1 - a_j}{p-1} + v_q \right)^2 \right)$$

$$\ge \frac{3}{p-1} \times \sum_{q=2}^{p} \left( M_1 + a_j - \frac{S - M_1 - a_j}{p-1} - v_q \right) \times \left( M_1 + a_j + \frac{S - M_1 - a_j}{p-1} + v_q \right).$$

By construction,

$$M_1 + a_j \ge \frac{S - M_1 - a_j}{n - 1} + v_q$$

therefore f is an increasing function.

Moreover,  $\mathcal{P}_1$  is the least loaded processor before the assignment of  $J_j$ , thus a fortiori, for  $q \in \{2, \dots, p\}$ ,

$$M_1 \le \frac{S - M_1 - a_j}{p - 1} + v_q \;,$$

hence

$$(p-1)M_1 \le (S-M_1-a_j) + \sum_{q=2}^p v_q = S-M_1-a_j$$

.

We derive that  $M_1 \leq M_1^+$ , where

$$M_1^+ = \frac{S - a_j}{p} \ . \tag{1.6}$$

Note that  $M_1^+$  does not depend on the  $v_q$ . Since f is an increasing function, we have

$$P_{\text{greedy}} = f(M_1) \le f(M_1^+).$$

We had for  $q \in \{2,\ldots,p\}$ ,  $M_1 \leq \frac{S-M_1-a_j}{p-1} + v_q$ , hence if  $M_1 = M_1^+$ ,

$$v_q \ge \frac{p}{p-1} \times M_1^+ - \frac{1}{p-1} \times (S - a_j) = 0.$$

We deduce that, for  $M_1=M_1^+$  and  $q\in\{2,\ldots,p\},\,v_q=0$  (they are all nonnegative and their sum is null). Finally, we obtain

$$P_{\text{greedy}} \le f(M_1^+) = (M_1^+ + a_j)^3 + \frac{(S - a_j - M_1^+)^3}{(p-1)^2},$$

which, given the value of  $M_1^+$  from Equation (1.6), directly leads to Equation (1.5). This concludes the proof.

**Proposition 1.4.** For power minimization, OnLine-Greedy is a  $f_p^{(on)}(\beta_p^{(on)})$  approximation.

*Proof.* We use the notations of Proposition 1.3. We first observe that  $a_i \leq O$ , for all  $i \in \{1, ..., n\}$ , by definition of O. In particular,  $a_i \leq O$ .

We introduce  $\beta = \frac{O}{S}$ . Clearly,  $\beta \in [\frac{1}{p}, 1]$ , and we can rewrite Equation (1.4) as:

$$\frac{P_{\text{online}}}{P_{\text{opt}}} \le \underbrace{\frac{\frac{1}{p^3} \left( (1 + (p-1)\beta)^3 + (p-1)(1-\beta)^3 \right)}{\beta^3 + \frac{(1-\beta)^3}{(p-1)^2}}}_{f_n^{(\text{on})}(\beta)}.$$

We now show that, for all p,  $f_p^{(\text{on})}$  has a single maximum in  $[\frac{1}{p},1]$ . After differentiating with respect to  $\beta$  and eliminating some positive multiplicative factor, we obtain that the sign of  $\left(f_p^{(\text{on})}\right)'$  is that of  $g_p^{(\text{on})}$ , where:

$$g_p^{(\text{on})}(\beta) = \beta^4(-p^3 + 4p^2 - 5p + 2) + \beta^3(-2p^2 + 6p - 4) + \beta^2(-4p + 5) + \beta(2p - 4) + 1.$$

Differentiating again two times, we obtain:

$$\left(g_p^{(\text{on})}\right)'(\beta) = 4\beta^3(-p^3 + 4p^2 - 5p + 2) + 3\beta^2(-2p^2 + 6p - 4) + 2\beta(-4p + 5) + 2p - 4;$$

$$\left(g_p^{(\text{on})}\right)''(\beta) = 24\beta^2 - 24\beta + 10 - 8p + p(-12\beta p + 36\beta - 60\beta^2) + 48p^2\beta^2 - 12p^3\beta^2 .$$

If  $p \ge 5$ ,

$$\left(g_p^{(\text{on})}\right)''(\beta) \le 34 - 40 + p(-60 + 36) + p^2(-60 + 48)\beta^2 \le 0 .$$

We check that

$$\begin{split} \left(g_2^{(\text{on})}\right)''(\beta) &= -6 \leq 0 \;, \\ \left(g_3^{(\text{on})}\right)''(\beta) &= -24\beta - 14 - 48\beta^2 \leq 0 \;\; \text{and} \\ \left(g_4^{(\text{on})}\right)''(\beta) &= -72\beta - 22 - 216\beta^2 \leq 0 \;, \end{split}$$

hence  $\left(g_p^{(\text{on})}\right)'$  is a decreasing function for all  $p \geq 2$  in the interval  $\left[\frac{1}{p},1\right]$ .

Next, we show that

$$\left(g_p^{(\text{on})}\right)'(1) = -4p^3 + 10p^2 - 8p + 2 \le 0,$$

and hence either  $g_p^{(\text{on})}$  is increasing and then decreasing in the interval  $[\frac{1}{p},1]$ , or  $g_p^{(\text{on})}$  is decreasing in the whole interval. Indeed, for p=2,  $\left(g_2^{(\text{on})}\right)'(1)=-6\leq 0$ , and for  $p\geq 3$ ,

$$\left(g_p^{(\text{on})}\right)'(1) \le p^2(-12+10) - 24 + 2 \le 0.$$

We now check the values of  $q_p^{(on)}$  at the interval bounds: for p > 2, we have

$$g_p^{(\text{on})}(1) = -p + 2p^2 - p^3 \le 0$$

, and

$$g_p^{(\text{on})}\left(\frac{1}{p}\right) = 3 - 11/p + 15/p^2 - 9/p^3 + 2/p^4 \ge 0,$$

since

$$g_2^{(\text{on})}\left(\frac{1}{2}\right) = \frac{1}{4}, g_3^{(\text{on})}\left(\frac{1}{3}\right) = \frac{56}{81}$$

, and for all  $p \geq 4$ ,  $g_p^{(\text{on})}\left(\frac{1}{p}\right) \geq 3 - 11/p \geq \frac{12 - 11}{p} \geq 0$ .

In both cases (either  $g_p^{(on)}$  is increasing then decreasing, or  $g_p^{(on)}$  is only decreasing), since

$$g_p^{(\text{on})}\left(\frac{1}{p}\right) \ge 0$$

and  $g_p^{(\text{on})}(1) \le 0$ ,

we conclude that  $g_p^{(\text{on})}$  has a single zero  $\beta_p^{(\text{on})}$  in  $[\frac{1}{p},1]$ , for which  $f_p^{(\text{on})}$  attains its maximum. Finally ONLINE-GREEDY is a  $f_p^{(\text{on})}(\beta_p^{(\text{on})})$  approximation.

**Proposition 1.5.** For power minimization, OffLine-Greedy is a  $f_p^{(\text{off})}(\beta_p^{(\text{off})})$  approximation.

*Proof.* We follow the same line of reasoning as in Proposition 1.4, with  $O = \beta S$ , but we now further assume that  $a_j \leq O/3$ . Indeed, if  $a_j > O/3$ , there are at most two jobs assigned to each processor in the optimal solution. But then  $n \leq 2p$ , and for all such instances OFFLINE-GREEDY is optimal (this is the same argument as for the makespan minimization problem, due to the convexity of the power function). With  $a_j \leq O/3 = \beta S/3$ , we rewrite Equation (1.4) as:

$$\frac{P_{\text{offline}}}{P_{\text{opt}}} \le \underbrace{\frac{\frac{1}{p^3} \left( \left( 1 + \frac{(p-1)\beta}{3} \right)^3 + (p-1) \left( 1 - \frac{\beta}{3} \right)^3 \right)}{\beta^3 + \frac{(1-\beta)^3}{(p-1)^2}}}_{f_p^{(\text{off})}(\beta)} \,.$$

The sign of  $\left(f_p^{(\text{off})}\right)'$  is the sign of  $g_p^{(\text{off})}$ , where:

$$g_p^{(\text{off})}(\beta) = \beta^4(-9p^3 + 30p^2 - 27p + 6) + \beta^3(-6p^2 + 18p - 12) + \beta^2(-78p^2 + 126p + 33) + \beta(18p - 180) + 81.$$

Differentiating again two times, we obtain:

$$\left(g_p^{\text{(off)}}\right)'(\beta) = 4\beta^3(-9p^3 + 30p^2 - 27p + 6) + 3\beta^2(-6p^2 + 18p - 12) + 2\beta(-78p^2 + 126p + 33) + 18p - 180;$$

$$\left(g_p^{(\text{off})}\right)''(\beta) = 12\beta^2(-9p^3 + 30p^2 - 27p + 6) + 6\beta(-6p^2 + 18p - 12) - 156p^2 + 252p + 66.$$

If  $p \geq 4$ ,

$$\left( g_p^{(\text{off})} \right)''(\beta) \le 12\beta^2 ((-36+30)p^2 - 108+6) + 6\beta ((-24+18)p - 12)$$

$$+ (-588+252)p + (-80+66)$$

$$\left( g_p^{(\text{off})} \right)''(\beta) \le 0.$$

Now  $\left(g_2^{(\text{off})}\right)''(\beta) = -54$  and

$$\left(g_3^{(\text{off})}\right)''(\beta) = -576\beta^2 - 72\beta - 582 \le 0,$$

thus for all p > 1 and  $\frac{1}{p} \le \beta \le 1$ ,

$$\left(g_p^{(\text{off})}\right)''(\beta) \le 0.$$

Therefore  $g_p^{(\text{off})}$  is concave.

Let us now check the values of  $g_p^{(\mathrm{off})}$  at the interval bounds. We have

$$g_p^{(\mathrm{off})}\left(\frac{1}{p}\right) \geq 21 - 35 + 15 \geq 0 \;, \; \mathrm{and}$$

$$g_p^{\text{(off)}}(1) = -9p^3 - 54p^2 + 135p - 72 \le 0$$

since

$$g_2^{(\text{off})}(1) = -72 - 216 + 270 - 72 \le 0$$

, and for  $p \ge 3$ ,  $g_p^{(\text{off})}(1) \le p(-27 - 162 + 135) - 72 \le 0$ .

We conclude that for all p>1,  $f_p^{(\text{off})}$  has a single maximum in  $[\frac{1}{p},1]$ , reached for  $\beta=\beta_p^{(\text{off})}$ , where  $g_p^{(\text{off})}(\beta_p^{(\text{off})})=0$ . Finally OffLine-Greedy is a  $f_p^{(\text{off})}(\beta_p^{(\text{off})})$  approximation.

**Proposition 1.6.** The approximation factor  $f_p^{(on)}(\beta_p^{(on)})$  for Online-Greedy cannot be improved.

*Proof.* Consider an instance with p processors and n=p(p-1)+1 jobs, where for all  $i\in\{1,\ldots,n-1\}$ ,  $a_i=1$ , and  $a_n=B=\frac{\beta_p^{(\text{on})}p(p-1)}{1-\beta_p^{(\text{on})}}$ .

ONLINE-GREEDY assigns p-1 unit-size jobs to each processor, and then the big job is assigned to any processor, leading to a power dissipation of:

$$P_{\text{online}} = \left(\frac{S + (p-1)a_j}{p}\right)^3 + (p-1)\left(\frac{S - a_j}{p}\right)^3,$$

where j = n.

From  $\beta_p^{(\text{on})} \geq \frac{1}{p}$ , we deduce that  $B \geq p$ . Therefore the optimal solution assigns  $J_n$  to the first processor, and p unit-size jobs to each other processor. We have  $a_j = O = B$  and for  $q \in \{2, \dots, p\}$ ,

$$\sum_{i \in load(q)} a_i = p = \frac{S - O}{p - 1}, \text{ and hence}$$

$$P_{\text{opt}} = O^3 + (p-1) \left(\frac{S-O}{p-1}\right)^3.$$

Moreover we have  $O = \beta_p^{(on)} S$ :

$$\begin{split} O - \beta_p^{(\text{on})} S &= B - \beta_p^{(\text{on})} (B + p(p-1)) \\ &= B - p(p-1) \beta_p^{(\text{on})} \left( \frac{\beta_p^{(\text{on})}}{1 - \beta_p^{(\text{on})}} + 1 \right) \\ O - \beta_p^{(\text{on})} S &= 0 \; . \end{split}$$

Therefore, for this instance,

$$\frac{P_{\text{online}}}{P_{\text{opt}}} = f_p^{\text{(on)}}(\beta_p^{\text{(on)}}) ,$$

which concludes the proof.

**Proposition 1.7.** The approximation factor  $f_p^{(\text{off})}(\beta_p^{(\text{off})})$  for the ratio of the Offline-Greedy cannot be improved.

*Proof.* Consider an instance with p processors and n=2p+1 jobs, where for all  $1 \le i \le p$ ,

$$a_{2i-1} = a_{2i} = 2p - i + v_i,$$

and where  $a_n = p + v_p$ .

We define

$$A = \frac{3p(1-\beta_p^{(\mathrm{off})}p)}{\beta_p^{(\mathrm{off})}(p+1)-3}, \ \ \mathrm{and}$$

$$\forall 1 \le i \le p, \ v_i = \frac{i-1}{p-1}A.$$

We first show that the jobs are sorted in non-increasing order:

- For

$$1 \le i \le p$$

,  $a_{2i-1} = a_{2i}$ ;

$$-a_n = a_{n-1} (= a_{2p});$$

- For

$$1 \le i \le p - 1$$

,

$$a_{2i+1} - a_{2i} = -1 + v_{i+1} - v_i = -1 + \frac{A}{p-1}$$

.

Consider the function

$$\hat{h}_p: \beta \mapsto \frac{3p(\beta p - 1)}{3 - \beta(p + 1)}.$$

Its derivative is nonnegative, hence  $\hat{h}_p$  is increasing.

We now prove that  $\beta_p^{(\text{off})} \leq 3/(2p+1)$ , which ensures that

$$A = \hat{h}_p(\beta_p^{\text{(off)}}) \le \hat{h}_p(3/(2p+1)) = p-1,$$

and therefore  $a_{2i+1}-a_{2i}=\frac{A}{p-1}-1\leq 0$ . Recall that  $\beta_p^{(\text{off})}$  is the unique root in the interval  $\left[\frac{1}{p},1\right]$  of  $g_p^{(\text{off})}$  (see Theorem 1.2). We already know that  $g_p^{(\text{off})}(\frac{1}{p})\geq 0$  (see proof of Proposition 1.5). We now prove that

$$g_p^{(\text{off})}(3/(2p+1)) \le 0$$

.

Indeed, we have

$$g_p^{\text{(off)}}(3/(2p+1)) = -\frac{135p(8p^3 + 3p^2 - 30p + 19)}{(2p+1)^4},$$

and  $8p^3 + 3p^2 - 30p + 19 \ge p(32 - 30) + 19 \ge 0.$

Therefore,  $\beta_p^{(\text{off})} \leq \frac{3}{2p+1}$ , which proves that  $a_{2i+1} \leq a_{2i}$ , and hence the jobs are sorted in non-increasing order.

Before the assignment of the last job, all processor loads are perfectly balanced. OFFLINE-GREEDY first assigns  $J_1, J_2, \ldots, J_p$  to  $\mathcal{P}_1, \mathcal{P}_2, \ldots, \mathcal{P}_p$  respectively. Then it assigns the jobs  $J_{p+1}, J_{p+2}, \ldots, J_{2p}$  to  $\mathcal{P}_p, \mathcal{P}_{p-1}, \ldots, \mathcal{P}_1$  respectively. After these assignments, for all  $i \in \{1, \ldots, \lceil p/2 \rceil\}$ , the load of processor  $\mathcal{P}_{2i-1}$  is:

$$a_{2i-1} + a_{2(p-(i-1))} = 3p + v_i + v_{p-(i-1)}$$

$$= 3p + \frac{i-1}{p-1}A + \frac{p-i}{p-1}A$$

$$a_{2i-1} + a_{2(p-(i-1))} = 3p + A.$$

Moreover, for all  $i \in \{1, \dots, \lfloor p/2 \rfloor\}$ , the load of processor  $\mathcal{P}_{2i}$  is

$$a_{2i} + a_{2(p-(i-1))-1} = a_{2i-1} + a_{2(p-(i-1))} = 3p + A.$$

The last job  $J_n$  is assigned to any processor, and the power dissipated by OffLine-Greedy is:

$$P_{\text{offline}} = \left(\frac{S + (p-1)a_j}{p}\right)^3 + (p-1)\left(\frac{S - a_j}{p}\right)^3,$$

where j = n.

The optimal solution assigns  $J_1, J_2, \ldots, J_{p-1}$  to  $\mathcal{P}_2, \mathcal{P}_3, \ldots, \mathcal{P}_p$  respectively. It assigns the jobs  $J_p, J_{p+1}, \ldots, J_{2p-2}$  to  $\mathcal{P}_p, \mathcal{P}_{p-1}, \ldots, \mathcal{P}_2$  respectively. The last three jobs  $J_{2p-1}, J_{2p}$  and  $J_{2p+1}$  are assigned to  $\mathcal{P}_1$ , which is the most loaded processor.

The loads of processors  $\mathcal{P}_2, \mathcal{P}_3, \dots, \mathcal{P}_p$  are perfectly balanced in the optimal assignment, and their load is 3p + pA/(p-1):

– For all  $i \in \{1, \dots, \lfloor p/2 \rfloor\}$ , the load of processor  $\mathcal{P}_{2i}$  is

$$\begin{split} a_{2i-1} + a_{2(p-i)} &= 3p + v_i + v_{p-i} \\ &= 3p + \frac{i-1}{p-1}A + \frac{p-i+1}{p-1}A \\ a_{2i-1} + a_{2(p-i)} &= 3p + pA/(p-1). \end{split}$$

– For all  $i \in \{1, \dots, \lceil p/2 \rceil - 1\}$ , the load of processor  $\mathcal{P}_{2i+1}$  is

$$a_{2i} + a_{2(p-i)-1} = a_{2i-1} + a_{2(p-i)}$$

$a_{2i} + a_{2(p-i)-1} = 3p + pA/(p-1).$

Finally, the load of processor  $\mathcal{P}_1$  is

$$O = 3a_n = 3p + 3A$$

.

and since  $3p + 3A \ge 3p + pA/(p-1)$ , it is the most loaded processor.

We can then compute the corresponding power consumption. Note that the total load S-O is equally divided between p-1 processors, and hence  $3p+pA/(p-1)=\frac{S-O}{p-1}$ . We obtain:

$$P_{\text{opt}} = O^3 + (p-1) \left( \frac{S-O}{p-1} \right)^3.$$

To conclude the proof, we need to prove that

$$O = \beta_p^{(\text{off})} S .$$

Note that

$$S = 3p^{2} + v_{p} + 2\sum_{i=1}^{p} v_{i} = 3p^{2} + A + \frac{2A}{p-1}\sum_{i=0}^{p-1} i$$

$$S = 3p^{2} + (p+1)A,$$

and therefore