# Contributions à la conception d'architectures matérielles dédiées

Steven Derrien

## ▶ To cite this version:

Steven Derrien. Contributions à la conception d'architectures matérielles dédiées. Architectures Matérielles [cs.AR]. Université Rennes 1, 2011. tel-00749092

## HAL Id: tel-00749092 https://theses.hal.science/tel-00749092

Submitted on 6 Nov 2012

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## HABILITATION À DIRIGER DES RECHERCHES

présentée devant

#### L'Université de Rennes 1

Spécialité : Informatique

par

Steven Derrien

# Plateformes, méthodologies et outils pour la conception d'architectures matérielles reconfigurables

## à soutenir le 13 décembre 2011 devant le jury composé de :

- M. Tanguy Risset, Professeur INSA de Lyon, CITI/INRIA

- M. Olivier Sentieys, Professeur Université de Rennes 1, IRISA/INRIA

- M. Patrice Quinton, Professeur ENS Cachan, IRISA/INRIA

- M. Jean-Philippe DIGUET, Directeur de recherche CNRS, LasSticc-Lorient

- M. Sanjay Rajopadhye, Professeur, Colorado State University, USA

## et au vu des rapports de :

- M. Pierre Boulet, Professeur Université Lille 1, LIFL/INRIA

- M. Jurgen Teich, Professor University of Erlangen, Allemagne

- M. Florent DE DINECHIN, Maître de conférence HDR, ENS Lyon, LIP/INRIA

# Contents

| 1. | Intro | ntroduction 5                                                      |                 |  |  |  |  |  |  |

|----|-------|--------------------------------------------------------------------|-----------------|--|--|--|--|--|--|

|    | 1.1.  | Context of the work                                                | 5               |  |  |  |  |  |  |

|    | 1.2.  | Summary of the contributions                                       | 6               |  |  |  |  |  |  |

|    |       | 1.2.1. Synthesis of loop nests hardware accelerators               | 7               |  |  |  |  |  |  |

|    |       | 1.2.2. Reconfigurable platforms for high performance computing     | 7               |  |  |  |  |  |  |

|    |       | 1.2.3. Application specific parallel hardware accelerators         | 8               |  |  |  |  |  |  |

|    |       | 1.2.4. Tools for application specific architecture design          | 9               |  |  |  |  |  |  |

|    | 1.3.  | Organization of the manuscript                                     | 11              |  |  |  |  |  |  |

| _  |       | •                                                                  |                 |  |  |  |  |  |  |

| 2. |       | onfigurable Accelerators for searching unstructured databases      | 13              |  |  |  |  |  |  |

|    | 2.1.  | Reconfigurable platforms for database processing                   | 13              |  |  |  |  |  |  |

|    |       | 2.1.1. The case for Active Storage systems                         | 14              |  |  |  |  |  |  |

|    |       | 2.1.2. The RDISK platform                                          | 15              |  |  |  |  |  |  |

|    |       | 2.1.3. The ReMIX Platform                                          | 17              |  |  |  |  |  |  |

|    | 2.2.  | A case study: Multimedia Content-Based Image Retrieval             | 18              |  |  |  |  |  |  |

|    |       | 2.2.1. Similarity search algorithm                                 | 19              |  |  |  |  |  |  |

|    |       | 2.2.2. Adapting the algorithm for hardware acceleration            | 19              |  |  |  |  |  |  |

|    |       | 2.2.3. Mapping CBIR on the RDISK platform                          | 21              |  |  |  |  |  |  |

|    |       | 2.2.4. Mapping CBIR on the ReMIX platform                          | 22              |  |  |  |  |  |  |

|    | 2.3.  | Discussion                                                         | 24              |  |  |  |  |  |  |

| 2  | N 4   | strate Devellat Assalanatan fan HMANA Dos Cla Dasa Cannanas assala | 27              |  |  |  |  |  |  |

| Э. |       | sively Parallel Accelerator for HMM Profile Base Sequence search   |                 |  |  |  |  |  |  |

|    | 5.1.  | Profile based sequence comparison                                  | 27              |  |  |  |  |  |  |

|    | 0.0   | 3.1.1. The HMMER software suite                                    | 28              |  |  |  |  |  |  |

|    | 3.2.  | Design space exploration for parallel HMMER                        | 29              |  |  |  |  |  |  |

|    |       | 3.2.1. Exploring scheduling/mappings                               | 29              |  |  |  |  |  |  |

|    |       | 3.2.2. Experimental validation                                     | 31              |  |  |  |  |  |  |

|    | 3.3.  | Parallelizing through max-prefix inference                         | 34              |  |  |  |  |  |  |

|    |       | 3.3.1. Finding hidden parallelism in P7Viterbi kernel              | 34              |  |  |  |  |  |  |

|    |       | 3.3.2. Mapping the full HMMER 3.0 pipeline to hardware             | 35              |  |  |  |  |  |  |

|    |       | 3.3.3. Experimental results                                        | 36              |  |  |  |  |  |  |

|    | 3.4.  | Related Work                                                       | 37              |  |  |  |  |  |  |

|    | 3.5.  | Discussion                                                         | 38              |  |  |  |  |  |  |

| 4  | Ultr  | a Low Power Wireless Sensor Networks                               | 41              |  |  |  |  |  |  |

| •  | 4.1.  | WSN platforms design challenges                                    | 41              |  |  |  |  |  |  |

|    | 4.2.  | A new hardware platform model for WSN                              | 43              |  |  |  |  |  |  |

|    | 4.3.  | Microtask based System Level Design flow                           | 45              |  |  |  |  |  |  |

|    | T.U.  | 4.3.1. Synthesizing microtasks from C code                         | 45              |  |  |  |  |  |  |

|    |       | 4.3.2. System-Level Synthesis                                      | $\frac{45}{47}$ |  |  |  |  |  |  |

|    | 1 1   |                                                                    |                 |  |  |  |  |  |  |

|    | 4.4.  | Experimental results                                               | 47              |  |  |  |  |  |  |

|    | 4.5.  | Discussion                                                         | 51              |  |  |  |  |  |  |

| 5. | Synt | thesis of Hardware accelerator for regular computations                   | 53 |

|----|------|---------------------------------------------------------------------------|----|

|    | 5.1. | Representing loop nests as polyhedrons                                    | 53 |

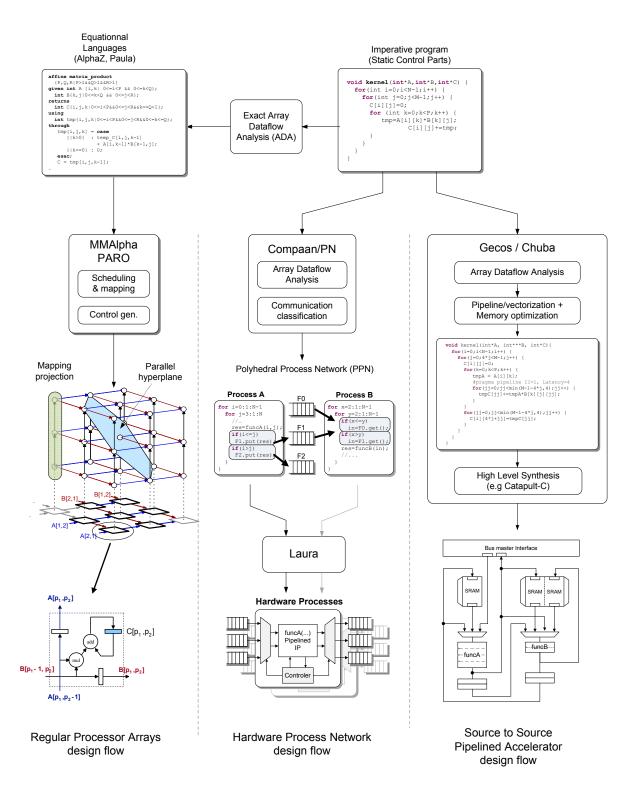

|    | 5.2. | From processor arrays to process networks                                 | 54 |

|    | 5.3. | Efficient I/O management in processor arrays                              | 57 |

|    |      | 5.3.1. Conflict free I/O schedules in partitioned processor arrays        | 58 |

|    |      | 5.3.2. Experimental results                                               | 58 |

|    |      | 5.3.3. Discussion                                                         | 60 |

|    | 5.4. | Control generation for hardware Process Networks                          | 61 |

|    |      | 5.4.1. Simple parameterized Controller                                    | 62 |

|    |      | 5.4.2. Partitioned parameterized Controller                               | 62 |

|    |      | 5.4.3. Toward a Variant based controller                                  | 63 |

|    |      | 5.4.4. Discussion                                                         | 64 |

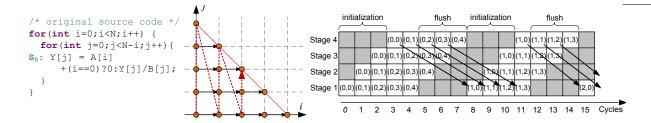

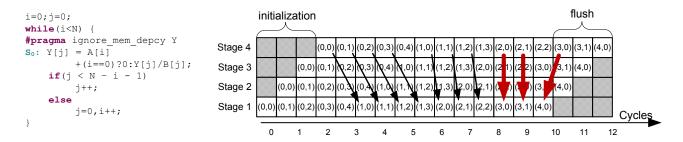

|    | 5.5. | Nested loop pipelining for HLS                                            | 64 |

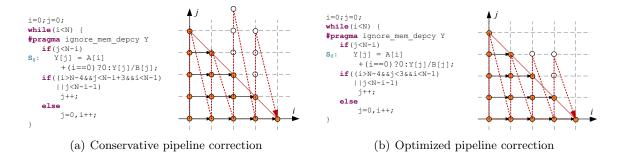

|    |      | 5.5.1. Checking pipelined coalescing legality                             | 66 |

|    |      | 5.5.2. Correcting coalescings by bubble insertion                         | 67 |

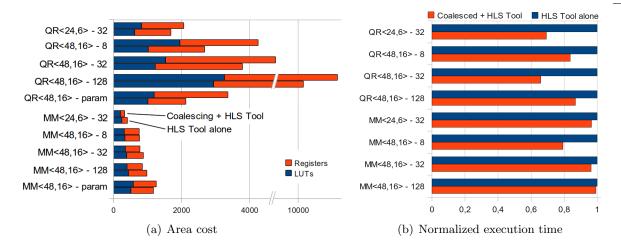

|    |      | 5.5.3. Results and validation                                             | 67 |

|    |      | 5.5.4. Related work                                                       | 69 |

|    |      | 5.5.5. Discussion                                                         | 70 |

| 6. | Con  | clusion                                                                   | 71 |

|    | 6.1. | Toward next generation of High-Level Synthesis tools                      | 71 |

|    |      | 6.1.1. Revisiting hardware synthesis in the polyhedral model              | 72 |

|    |      | 6.1.2. Domain Specific Analyses for HLS                                   | 72 |

|    | 6.2. | Automatic parallelization for heterogeneous multi-cores                   | 73 |

|    |      | 6.2.1. Constraint programming for automatic parallelization               | 73 |

|    |      | 6.2.2. Adaptive run-time parallelization for heterogeneous multi-core     | 73 |

|    |      | 6.2.3. Parallel programming tools for non parallel programmers            | 74 |

|    | 6.3. | Model Driven Engineering and optimizing compilers                         | 74 |

|    |      | 6.3.1. Domain Specific Languages for high productivity parallel computing | 74 |

|    |      | 6.3.2. Software reuse in MDE through model typing                         | 75 |

| Α. | Curi | culum Vitae                                                               | 77 |

| В. | Sele | cted publications                                                         | 81 |

| _  |      |                                                                           |    |

| C. | Pers | onal bibliography                                                         | 93 |

## Introduction

This manuscript summarizes my research activities since the defense of my PhD in December 2002. This work has been carried in several contexts, first as a post-doc at Leiden University in the group of Ed Deprettere in 2003, then as an associate professor at University of Rennes 1, in the R2D2 research group of IRISA, and then later in the CAIRN-INRIA/IRISA project-team. Since September 2009, I am benefiting from an INRIA "délégation", which helped me initiating many new research projects and collaborations, and also allowed me to start supervising some PhD students. This chapter is organized as follows, I will first start by presenting the context in which my research takes place. This will be followed by a summary of the contributions presented in the document and by a description of the organization of the manuscript.

## 1.1. Context of the work

The processor and computer design landscape is facing the toughest challenge it had to confront since the introduction of the Intel 4004 processor in 1971. The reason behind this upheaval stands in two words: *parallelism* and *energy*.

The days where software performance would grow just by magic, simply by benefiting from processor clock speed (or micro-architectural) improvement are over, as the "clock speed race" ultimately hit the "power dissipation wall". With the resulting outbreak of multi-core (and soon many-core) processors, the way we have been designing software (and the tools that we use for doing it) for more than 20 years needs to be completely reconsidered.

It would be a mistake to consider that this threat is only geared at general purpose computing systems, as embedded system designers are also confronted to similar problems. They however face an additional challenge: because of tight power, cost and performance constraints, most embedded platforms have to be based on *heterogeneous* multi-core systems. Such *heterogeneous* platforms integrate, within a single die, tens, if not hundreds of computing cores, these cores being significantly different in nature (programmable/extensible processors, custom hardware Intellectual Property blocks, coarse grain reconfigurable co-processors, etc). As a consequence, efficiently designing and programming such systems poses even greater challenges.

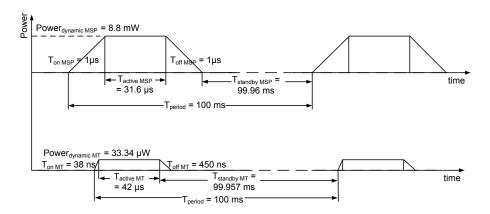

In the mean time, ubiquitous computing is becoming a reality, probably at a faster pace than we realize it. We will soon be completely surrounded by tiny computing devices, whose role will be to sense/watch and control our daily environment in a collaborative way. In addition to the numerous ethical and legal issues that such devices may raise, they will also pose stringent new challenges to computer and system architects. They will be expected to work autonomously for months if not years, either by relying on extremely limited power supplies, or by harvesting energy from their immediate environment. State of the art energy harvesting can provide at most  $20\mu W$  whereas the power budget of a low-power MCU such as the MSP430 is around  $5\,mW$  at  $16\,MHz$ . Satisfying these requirements means filling a two orders of magnitude gap in terms of energy efficiency improvements. Here again, radically new approaches are needed.

Addressing these challenges requires combining techniques and knowledge from several fields from Electrical Engineering (CAD tools, digital design, micro-electronics) to Computer Science (processor architecture, operating systems, compiler design, software engineering). In such a context, this work has been revolving around the definition of tools to help the design of complex

heterogeneous systems on chip. More precisely, this work has been focusing on automatic synthesis of hardware co-processors, to improve the energy efficiency and performance of embedded platforms. Using custom accelerators has shown to bring significant performance and energy improvements (from  $\times 10$  to  $\times 50$ ), however their design is very tedious and time consuming as it is done through  $Hardware\ Description\ Languages\ such as\ VHDL$  or Verilog.

Silicon compilers that can generate custom hardware from a high-level language, have been advocated as an answer to address this design time issue. Even though the first of such tools date back to the early 90s, it is only recently that they finally found their way in real design flows, as their efficiency and usability remained limited for quite some time. Today, there exists a large choice of robust and mature C to hardware tools [73, 30] that are used as production tools by world-class chip vendor companies.

However, there is still room for improvement, as these tools are far from producing designs with performance comparable to those of expert designers. The reason of this difference lies in the difficulty, for automatic tools, to recover information that may have been lost during the compilation process. The difficulty also stems from the lack of well defined target, as these tools must jointly define the hardware architecture and map the algorithm onto that architecture. This lead to some subtle trade-off between performance, resource usage, and energy efficiency. Our contributions in this field focused on studying how to extract and take advantage of massive parallelism and to improve energy efficiency of circuits designed using such silicon compilers.

We also investigated direct applications of reconfigurable computing, by proposing and designing several massively parallel application specific accelerators for multimedia database search and bioinformatics. These two fields involve many extremely computationally demanding algorithms that are well suited to hardware acceleration. In particular we have studied how to accelerate Markov based profile search, and specifically the HMMER software suite, a reference tool for the whole bioinformatics community [63].

We also studied the hardware acceleration of content-based retrieval algorithm for multimedia data, and in particular for image databases. These algorithms, whose goal is to search the nearest neighbors of high dimensional vectors, suffer from what is known as "the curse of dimensionality" and a search hence requires an exhaustive scan in the reference database. Here again, we have shown that these applications were good fit for hardware acceleration.

Lastly, in the context of a close collaboration with Dominique Lavenier from the IRISA/IN-RIA Symbiose team, we also contributed to the design and proposal of reconfigurable hardware based on the concept of smart storage systems, targeted at searching information in large database systems. This research work led to the construction of two prototypes: RDISK and ReMIX.

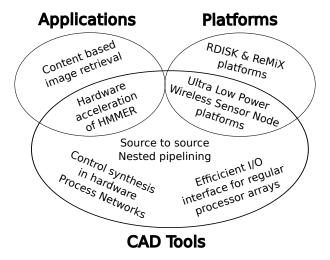

It is noteworthy that these three topics mentioned above are tightly related to each other, and addressing all these issues at once is unavoidable. As a matter of fact, the ability to improve design tools requires two things: a deep understanding of hardware platforms and FPGA technology, but also a deep knowledge of applications requirements so as to help pinpointing the limitation of existing tools. Experience has shown that such an expertise can only be acquired through recurring practical case studies on real life target platforms. Figure 1.1 illustrates the contributions presented in this work, by showing how they are related to the aforementioned topics.

## 1.2. Summary of the contributions

This section provides an overview of the research topics presented in this document. These topics are presented in chronological order, starting from earlier work which took place during my post-doc and/or that were in the direct continuation of my PhD work, to some very recent

Figure 1.1.: A visual representation of the contributions presented in this work.

work on source-to-source transformations for High-Level-Synthesis (HLS).

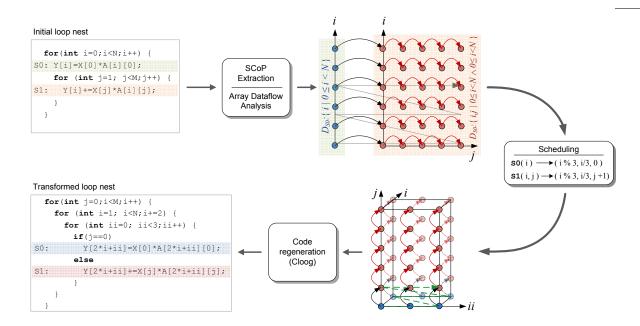

## 1.2.1. Synthesis of loop nests hardware accelerators

The first contribution after my PhD was a result of a stay as a post-doc in 2003 at Leiden University in the group of Ed Deprettere, where we worked on the problem of automatic hardware synthesis in the context of the Compaan/Laura framework [165, 153]. The goal was to synthesize efficient hardware process networks [18] leveraging the Polyhedral Process Network semantics [154]. To address the problem, we studied and investigated several approaches to improve the scalability and efficiency of the hardware controllers generated from Compaan.

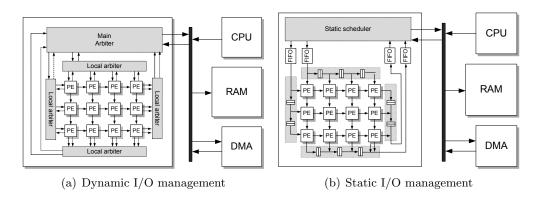

After my returning to University of Rennes, I have been working with Tanguy Risset and Alain Darte on the problem of automatic synthesis of efficient hardware/software interface for processor arrays, in the context of their integration as hardware IPs in a System on Chip. Some of my earlier work with Tanguy Risset addressed the problem of interface synthesis for one dimensional arrays, integrated as slave peripherals in a system. In this work, we extended our previous results to support partitioned processor arrays with busmaster capabilities. In particular, we proposed a technique, which is able to determine a static I/O pipeline scheme for distributing the data among the boundary processors of the array, given a partitioning of the array enforcing certain constraints,

## 1.2.2. Reconfigurable platforms for high performance computing

In the mean time, I also continued a collaboration started with Dominique Lavenier just before the end of my PhD. Our joint work has focused in the design and utilization of application specific reconfigurable platforms for high performance database processing. Two prototypes have been designed during this period, namely the RDISK and ReMIX machines. The aim of the RDISK project was to propose a new paradigm of reconfigurable hardware accelerators based on the *smart-disk* principle [87, 131, 110], the goal being to move the computational resource as close as possible to the data source. Our key idea was to attach the reconfigurable accelerator directly to the disk output, so as to be able to perform on-the-fly data filtering. A prototype RDISK cluster with 48 nodes was designed, and several bioinformatic applications (BLAST [36], WAPAM) have been accelerated on the platform, with speedup ranging from 5 to 20 per node. The RDISK cluster platform has also been serving as a reference target platform

for three PhD students (S. Guyetant, M. Giraud et A. Noumsi), and the cluster was later added to the processing resource of the GenOuest platform (http://www.genouest.org).

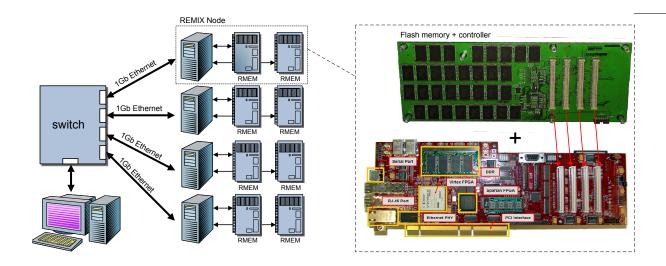

The ReMIX platform was in continuation of the RDISK, with a focus on large scale indexing, where index size exceeds capabilities of current volatile memory technologies. The idea consisted in coupling the FPGA resource to Nand Flash memory. Each node of the ReMIX cluster hence contains a Xilinx FPGA combined with 64 GB of Flash memory, organized in parallel banks to maximize I/O throughput. The approach permits to combine the benefits of non permanent storage system with those of random access memories (throughput, access latency). An 8-board prototype was realized and validated, and several accelerators have been ported to the system, with speedup factors of up to  $\times 50$  per node.

## 1.2.3. Application specific parallel hardware accelerators

While working on the RDISK and ReMIX platforms, we have also conducted several case studies. The goal of this work was twofold. The first motivation was to demonstrate the relevance of FPGAs for high-performance database applications. The other one was to see how semi-formal design methodologies could help deriving more efficient accelerator architectures, but also to search for interesting design tricks/optimizations that could be worth being integrated in high-level synthesis tools. The target application domains in this work were content based search in multimedia databases (image, video) and genomic sequence comparison in bioinformatics.

In the context of the PhD of August Noumsi (supervised by Patrice Quinton), we have been working in collaboration with the IRISA/INRIA TexMex group on the hardware acceleration of content based image retrieval algorithms. A detailed description of the work carried on this topic is provided in Section 2.2. In particular, we have quantified the impact of some architectural parameters (encoding accuracy, synchronization overhead) on the effective performance of two hardware implementations (for the RDISK and ReMIX platforms), which have exhibited important (more than  $\times 100$ ) performance improvements.

The other application domain we have studied in this context is bioinformatics, and more particularly genetic sequence comparison algorithms. The contributions related to this work are detailed in Chapter 3. These compute intensive kernels, based on dynamic programming algorithms, are very good candidates for hardware acceleration. In addition, the fact that genomic sequence databases grow in size at a faster pace than processor performance raises a need for high performance implementation of the algorithms. A number of such algorithms and applications have already been successfully accelerated on FPGAs (Smith-Waterman [140], BLAST [36]) with good performance improvements (speedup by ×100 over a software implementation). Some other algorithms turn out to be more difficult to accelerate in hardware, in particular when there is no obvious parallelization scheme. This is the case for the HMMER software suite, based on Markov models, used for sequence similarity searching.

We have proposed a scalable parallelization scheme for this algorithm, detailed in Section 3.2, which is well suited to hardware acceleration. This scheme is based on space-time transformations formalized in the polyhedral model, and enables the derivation of a generic processor array template that can easily be retargeted to different accelerator platforms, while retaining its efficiency. The template is parameterized and supports different levels of fine grain pipelining, and can handle resource constraints by allowing the designer to specify the number of processing elements used in the architecture. This result was presented in 2007 to the *IEEE International Conference on Application-specific Systems, Architectures and Processors* and received the best paper award.

We continued investigating this topic in the context of the PhD of Naeem Abbas (funded by the ANR BioWic project) and in close collaboration with Sanjay Rajopadhye from Colorado State University. Our work focused on sophisticated program transformations leveraging algebraic properties of the algorithms which extensively use reduction operations. We have shown that to the contrary of common beliefs, it is possible to parallelize the HMMER main algorithm at the price of a moderate increase in computation volume. The idea, presented in Section 3.3, is based on the uncovering of a hidden parallel prefix operation, for which there exists many efficient parallel hardware implementations, as the topic is studied since the mid-70s. The parallelization of a prefix operation however comes at the price of a slight increase in computation workload  $(O(N, \log_2 N))$  instead of O(N). The approach was validated on a high performance FPGA accelerator (XD2000i) and demonstrated speedup by up to factors of 7.5 over the highly optimized software implementation on a 3 GHz Intel Dual Core. We are currently pursuing the automation of some of these transformations within a C to hardware compilation tool.

#### 1.2.4. Tools for application specific architecture design

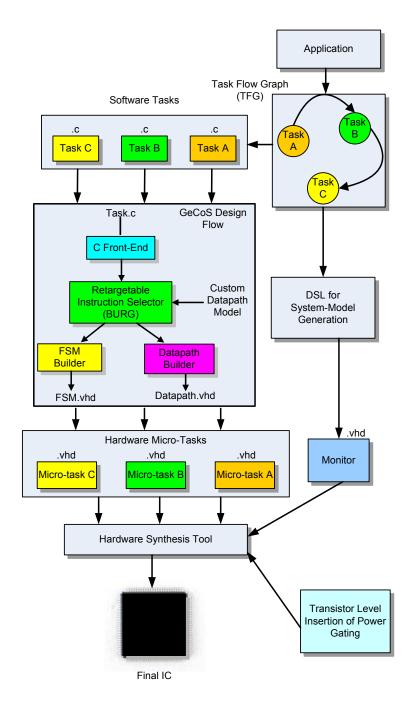

In 2007, I decided to refocus my research activities on CAD tools, and to start working again on automatic synthesis of parallel hardware accelerators. This decision was motivated by the work of Ludovic L'Hours on the first version of the Gecos compiler [105], which opened new interesting perspectives. Since 2008, Gecos serves as the reference compiler infrastructure for my research activites and for the whole CAIRN group. Two different problems have been targeted: the synthesis of ultra low-power controllers for wireless sensor networks, and source-to-source loop transformations for HLS.

## Ultra low power wireless sensor node platforms

Wireless Sensor Networks (WSN) are a very promising technology with potential applications in many domains of daily-life, such as structural-health and environmental monitoring, medicine, military surveillance, robotic explorations, and so on. A WSN is composed of a large number of nodes deployed inside a region of interest. Designing a WSN node is challenging, as designers must deal with strong form factor and energy constraints. For example, WSN nodes may need to run autonomously for months using limited energy sources (between ten and a few hundred mAh for small form factor Lithium batteries), or by harvesting energy from their environment (power supply of at most  $20 \,\mu W$ ).

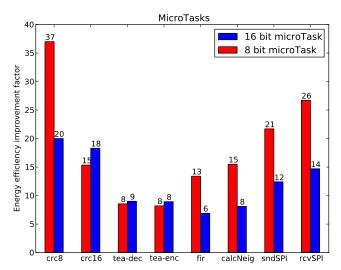

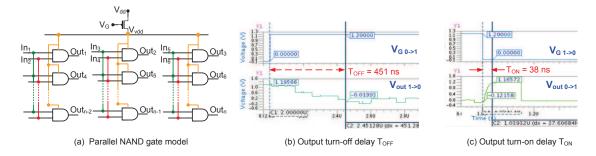

Current WSN nodes are based on micro-controllers such as the MSP430 [150] with typical power dissipation of a few mW, which are still orders of magnitude too high for many candidate applications of WSN. In the context of the PhD of Adeel Pasha (graduated on December 15 th 2010) and in collaboration with Olivier Sentieys, we tackled the problem by using a radically different approach, combining hardware specialization with concurrent task-level processing. The idea was to take maximum advantage of the opportunities of specialization by generating, for each task of the system, its custom hardware controller. By combining this idea of specialization with power gating, we have shown that it is possible to significantly reduce dynamic power while maintaining very low levels of static power dissipation.

Our approach, detailed in Chapter 4, leverages tools and techniques from micro-electronics, compiler/hardware synthesis and software engineering to offer a complete flow. This flow enables the complete specification (and synthesis) of a hardware/software platform from a combined use of C and of a platform description Domain Specific Language. The implementation of such a complex toolchain was made possible thanks to the use of Model Driven Software Development tools, which allowed us to benefit from many facilities for code generation and DSL design provided by the *Eclipse Modeling Framework*. Very interesting experimental results have been obtained, which showed that overall energy improvement by two orders of magnitude (w.r.t. to

the MSP430) is possible through this approach. This work has led to four publications including a paper presented at the IEEE/ACM Design Automation Conference in 2010.

We are pursuing this research direction in the context of the PhD of Vivek D. Tovinakere (under the supervision of Olivier Sentieys). His focus is on accurately modeling the impact of fine grain power gating techniques, and on the introduction of hardware reconfiguration. However, this work, still in progress, will not be presented in this document.

#### Source-to-source transformation for HLS

High-Level Synthesis tools, despite their progress over the last few years, do still suffer from many limitations. The initial source code that is to be mapped on hardware almost always requires to be heavily modified so that the tools are able to deal with it, but also (and mostly) so that they can derive an efficient architecture out of it. Such transformations can have significant impact on performance whenever the input code involves nested loops operating on arrays, since it is often possible to rewrite the loop to expose additional parallelism or improve locality by exploiting data reuse opportunities directly at the source code level.

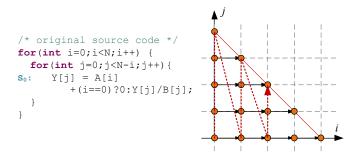

I have been working with Antoine Morvan (PhD student supervised by Patrice Quinton) on a source-to-source loop transformation toolbox based on polyhedral representations of loops since late 2008. This work is part of the S2S4HLS project <sup>1</sup> funded by the INRIA-STMicroelectronics Nano2012 program. In this work, we have been focusing on improving pipeline efficiency for loop nests that can be represented in the polyhedral model.

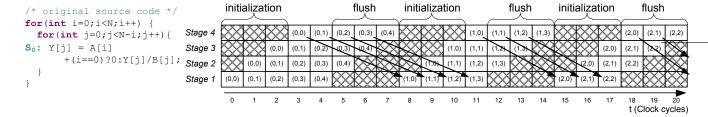

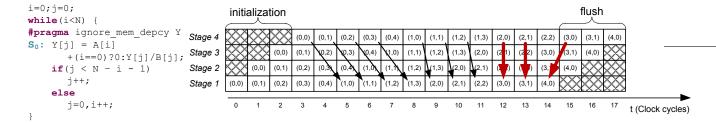

Efficient hardware acceleration of compute intensive kernels generally involves pipelining the execution of these kernels. This pipelining is applied to the innermost loops of the kernel and consists in overlapping the execution of several iterations on the hardware resources. The technique significantly improves the throughput of the accelerator, at the price of a slight increase in area and latency (related to the pipeline depth). It turns out that loop nests are well suited for a pipelined execution, as they often carry a significant amount of iteration level parallelism. However the efficiency of this pipelined execution degrades quickly as the number of iterations within the inner loop goes below a certain threshold. The degradation is caused by the pipeline fill/flush stages which then dominate execution time. This situation appears very frequently in the context of high-level synthesis, as many algorithms exhibit low innermost loop trip counts and since designers often try to derive deeply pipelined datapath, with long fill/flush stages.

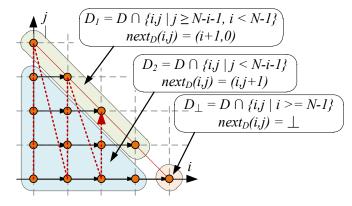

In this work we propose to reduce this overhead by pipelining the execution of the whole loop nest instead of restricting the pipelining to the innermost loop. The idea consists in coalescing the loop nest hierarchy in to a single loop, that will be further pipelined. The key problems are then (i) to build this coalesced loop, and (ii) to make sure the pipeline of this coalesced loop is legal (i.e., that it does not alter the semantics of the original code). Ensuring the legality of such a pipeline turns out to be difficult in the general case, especially for loop nests involving non constant loop bounds.

Our contribution, detailed in Section 5.5, consists in a legality check taking advantage of iteration instance wise dataflow analysis, associated with a correction technique. This correction technique can make a pipeline legal by inserting extra dummy iterations in the coalesced loop, these iteration then serving as wait states. Our technique was implemented in the Gecos source-to-source compiler and has shown encouraging results, with performance improvement of up to  $30\,\%$  for matrix multiplication and QR decomposition.

<sup>1.</sup> Source-to-Source for HLS

## 1.3. Organization of the manuscript

The remainder of the document is organized as follows, Chapter 2 describes our work on reconfigurable accelerators for unstructured databases, along with a case study application on multimedia content based search. Chapter 3 continues to discuss the topic of unstructured databases, with the focus on the design of a hardware accelerator for a sequence comparison algorithm (HMMER), widely used in the bioinformatics community. In Chapter 4, we present our work on ultra low power wireless sensor node platforms, and the design flow that supports the idea of hardware microtasks. Chapter 5 provides an overview of all our contributions on the topic of hardware synthesis in the polyhedral model. Chapter 6 summarizes our contributions, and provides detailed research perspectives both in the short and long term. A complete Curriculum Vitae, and a list of publications are also provided as appendix A and C.

# Reconfigurable Accelerators for searching unstructured databases

The work described in this chapter took place between 2003 and 2006 in close collaboration with Dominique Lavenier from the Symbiose team at IRISA. The goal was to see how reconfigurable technology could be used for accelerating search operations in unstructured databases (such as multimedia and genomic databases).

In this work, we tried to take a fresh look at reconfigurable accelerator platforms, by reconsidering the way the reconfigurable resource was coupled to the rest of the system. Our approach was motivated by our earlier experiences which showed that I/O throughput and/or latency were almost always performance bottleneck for FPGA platforms. To address this issue, we proposed two original prototype systems where the FPGA processing power is set as close as possible to the data source, following the principle of *smart storage systems*. We have also evaluated how this type of platforms could benefit to multimedia content-based search applications.

In Section 2.1, we discusses the idea of reconfigurable storage system and describe two platform prototypes RDISK and ReMIX that we designed following this idea. We then detail two different accelerators for our multimedia search algorithm. These implementations leverage both coarse grain and fine grain parallelism to reduce the search time and were carefully designed to maximize global (i.e., system level) performance. We illustrate the relevance of our approach through a case study: content-based image retrieval for large databases.

## 2.1. Reconfigurable platforms for database processing

The use of reconfigurable hardware for accelerating general purpose and scientific computing has been an active topic of research for now more than 20 years. In theory, reconfigurable accelerators are able to offer the best of both worlds: flexibility, thanks to dynamic reconfiguration, and performance thanks to parallelism and specialization. Seminal work in the domain [157, 156, 82] that took place in the early 90s had shown very promising results, and set the stage for what came to be known as the "Custom Configurable Computing" community.

However, in the late nineties, the lack of high-level design flows combined with ever increasing processor performance and severe I/O bottlenecks in FPGA platforms somewhat brought to an end most of the interest in reconfigurable computing. In particular, the steady improvements in both clock speed and micro-architectures had raised the bar too high for FPGAs to be able to compete with high-performance general purpose programmable processors. In the mid 2000s, the so-called *clock speed wall* and raising concerns for power dissipation in processors renewed interest for alternative technologies such as FPGAs. In the mean time, the outbreak of multi-core and GPUs, and in particular the programming challenges that they would represent, contributed to make FPGA design effort more acceptable, especially as many usable C to hardware compilers became available during this period. As of today, it seems that Reconfigurable Computing has found a small market niche, yet it remains to be seen whether this niche will survive in the longer term.

Independently of these architectural evolutions, another interesting phenomenon was ob-

served during the last decade: the fast wide spreading and growth of what is known as unstructured databases, carrying diverse types of information, from genomic to multimedia data. Because they cannot benefit from traditional indexing techniques (i.e., those used in relational databases), searching those databases often involves a complete scan of the dataset. This leads to poor performance as the whole data has to be read from its permanent storage medium but also since the selection algorithm has to be applied to every item, which (as far as genomic and multimedia data are concerned) is usually computationally expensive. Given that these databases size ranges from hundred of gigabytes to terabytes, and that their size tends to grow exponentially, running these analyses requires large storage capabilities along with huge computing power. In practice, only very few systems can provide both; supercomputers are geared towards processing power and storage systems are geared towards data distribution. Hence the user usually must sacrifice one for the other.

## 2.1.1. The case for Active Storage systems

Storage bottlenecks are solved through the use of High Performance data warehouses based on Storage Area Network (SAN). SANs are built upon a high-speed special-purpose networks interconnecting storage devices with servers on behalf of a larger network of users. The evolution of storage systems technology has shown that more and more intelligence is embedded into these systems (network protocols, cryptography, file systems management, etc.). While these tasks are still mainly geared toward data management and availability, we believe that the growing gap between the storage and processing capacity might induce a shift in the way these systems are designed. In particular, we believe that they may start providing data processing oriented services in the future. There are two reasons for this:

- In most cases the end user is only concerned with a small fraction of the original dataset that contains relevant information to its query. This is typically the case in DNA sequence similarity search and in multimedia content based retrieval problems. Filtering the data at its source has many benefits, as it significantly lowers the I/O volume in the storage system, hence decreasing its power consumption, and also improving its scalability.

- For such products, the cost overhead induced by additional embedded processing power would remain small (many SAN infrastructures already embed FPGAs for I/O management) with significant outcomes in terms of performance and energy.

Bringing computational power closer to the data source is not a new idea, and was explored in the context of *smart disk* devices. The *smart disk* approach suggests to use a fraction of computing power available within the hard-drive embedded controllers for data processing applications, based on the information that these processors, whose role is limited to disk head scheduling or cryptography/security, are somewhat underutilized. This concept has been investigated by several research groups in the late 90s [87, 131, 110], and their work showed promising results for a relatively wide panel of applications in which large datasets were involved. However it appeared that the hard disk storage industry would not move toward such open embedded CPU based smart disk devices, mostly because of security <sup>1</sup> and cost reasons. This is not true for the *storage systems industry* which is based on more open protocols and infrastructures.

Following this vision, we propose a new type of storage system based on "networked intelligent storage devices", which could be assembled in order to build larger scale application specific database systems. The *intelligence* of our system would lie in its ability to perform *on-the-fly filtering* of the data as it is read from the storage device. The goal is to send a small superset of the relevant data to the host. This superset will then be further analyzed to filter out

<sup>1.</sup> The software IP in hard-disk controllers is a key contributor to the actual hard disk drive performance, and this expertise is highly protected.

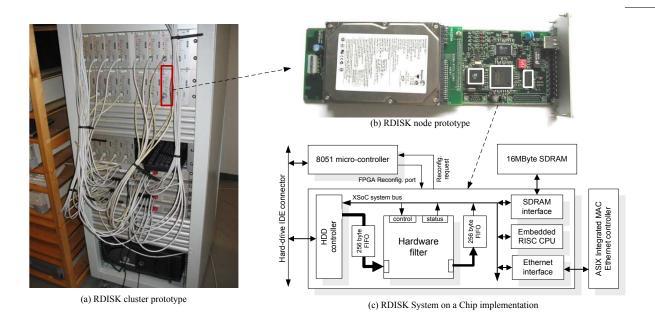

Figure 2.1.: The RDISK Node cluster and node prototypes, along with the node reconfigurable System On Programmable Chip

false positives. Because the performance benefits of a CPU based smart disk is not expected to justify its cost overhead and design complexity, the only way to be competitive is to use hardware acceleration through reconfigurable technology.

In the following, we summarize the work (carried in close collaboration with Dominique Lavenier) on RDISK and ReMIX , two intelligent storage prototypes designed between 2003 and 2006.

#### 2.1.2. The RDISK platform

The first research project that we started aimed at proposing a smart disk platform leveraging reconfigurable technology, and following the principles of Network Attached Storage (NAS): a computer data storage device connected to a network that provides filesystem level services. The following provides an overview of the work done on the RDISK platform design and implementation, both from the architectural and system level points of view.

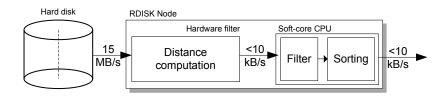

One of the goal was to propose a low-cost and scalable system, competitive in prices (in 2003) with other Network Attached Storage devices. We therefore targeted a cost of roughly \$200 per RDISK node, including PCB and a middle range HDD. This led to the choice of a platform based on a low cost \$30 Xilinx SpartanII-200 FPGA coupled to a 100 Mbit controller with 32 MB SDRAM memory and a 8051 controller for handling the device configuration. The core of the RDISK system was a System on a Chip implemented on the FPGA, represented in Figure 2.1.(c). Because of stringent resource constraints, we based the system on an open source 16 bit RISC soft-core processor, that requires less than 300 logic cells, leaving 2500 LUTs and 10 BlockRams for the data processing filter. This core was in charge of the network management and implemented a custom light weight UDP protocol. To maximize throughput, the hard-drive controller was implemented as an advanced autonomous state-machine that could handle most of the IDE-ATA protocol, and perform complex I/O requests. Our file system services were handled by the host server, to ease development.

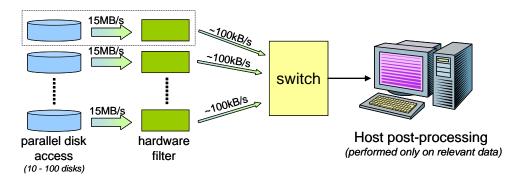

To demonstrate the feasibility of our approach, we built a complete parallel storage system, by assembling a cluster of 48 RDISK nodes together, as shown in Figure 2.1.(a). The abstract system-level view of this RDISK cluster is provided in Figure 2.2. In this system, all disks can operate in parallel, and their results are sent to the host through the network. The aggregated RDISK nodes output throughput must not saturate the host network link to guarantee the absence of bottleneck. This puts a constraint on our hardware filter selectivity (the less selective the filter is the more data has to be sent to the host). As an example, our prototype uses 48 boards, we assume that the host can handle at most 5 MB/s (half the peak 100 MBits), and that each drive provides a sustained bandwidth of 15 MB/s. This means that our hardware filters should be able to filter out 99.3% of the data read from the disk, with each individual disk output bandwidth being in the range of 100 kB/s.

Figure 2.2.: The RDISK cluster: system level view

Since the average network throughput requirements for each node are in the 100kB/s range, we did not try to optimize our network firmware and chose an IP/UDP stack in order to simplify the development of the network management layer. To minimize overhead, we used a simple UDP based protocol to receive and send commands to and from the host machine. It is worth noticing that most of this protocol could have been implemented in hardware using a complex state machine similar to the one used for controlling the disk. It would have then been possible to perform I/O access using the full 100 Mbits Ethernet bandwidth.

An important feature of the RDISK system is the way it handles dynamic reconfiguration management. All configurations for a given RDISK board are stored locally on its HDD, within a specific partition of the file-system. These bitstreams are accessible to the 8051 microcontroller that serves as a configuration manager and shares access to the HDD with the FPGA. When a new hardware configuration is to be run on the system, the host simply sends a suicide command to the selected boards, including the next configuration to be used. This message is forwarded to the configuration manager, which reconfigures the FPGA using the corresponding bitstream read from the disk, and loads its associated OS image (the whole operation lasts 800 ms).

The RDISK served as a target platform for three PhDs (S. Guyetant, M. Giraud and A. Noumsi). In 2006, the prototype was integrated to the pool of computing resources provided by the Génouest platform<sup>2</sup>. Several bioinformatic applications have been successfully ported to the architecture<sup>3</sup>, including a hardware accelerated version of the BLAST sequence alignment by S. Guyetant and a similarity search tool based on Weighted Finite Automaton (WAPAM) by Mathieu Giraud. In particular, the WAPAM program leveraged the dynamic reconfiguration capabilities: the application would synthesize on the fly a custom hardware design tailored to

$<sup>2.\ \</sup>mathtt{http://www.genouest.org}$

<sup>3.</sup> I was not directly involved in these contributions

Figure 2.3.: Simplified RMEM node architecture

the pattern at hand, and would then configure the platform with the problem instance specific accelerator. This tool was later made publicly available to registered platform users from the bioinformatics community. Even though I was not involved in these contributions, they show the relevance and interest of our proof of concept.

Another application field that was explored in the context of RDISK is content-based multimedia search. This topic is thoroughly described in Section 2.2, and will not be detailed here.

I took an important part in the design of the RDISK architecture, which was the core of S. Guyetant PhD thesis, as the node architecture was mostly based on one of my draft design. This work was carried in 2002 and 2003, before that soft-core processors (and their associated tools) would become commodity components. The development of the RDISK SoC hence required a significant development effort, to which I also contributed a lot (in particular on the soft-core CPU and on the SDRAM memory and cache controllers).

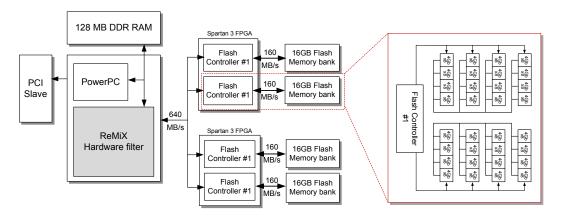

#### 2.1.3. The ReMIX Platform

The ReMIX project was started in 2005, in continuation of the RDISK project, in the context of a *Action Concertée Incitative* proposal. The design of ReMIX was mainly motivated by two observations:

- Even if attached directly at the disk output, I/O bandwidth and/or random access time still remained to be a bottleneck and prevented from fully utilizing the power of the FPGA.

- Nand-Flash memory did not suffer from the same limitations and its price had been decreasing at an exponential rate. We expected that this technology would soon become a serious competitor to magnetic storage systems.

The idea behind ReMIX was to benefit simultaneously from the high data throughput and the short access-time that can be obtained with the parallel use of Flash memory devices, and from the high computing density of a high-end FPGA. The goal was to obtain the largest possible storage capability and the smallest possible random access time.

Nand-Flash memory exhibits significant differences with respect to standard memory in the way data is accessed. In Flash technology, data is addressed at the page level, each page containing between 512 byte and 2 KB. Each access suffers from a relatively long latency  $(20\mu s)$ , but which remains three orders of magnitude better than a hard disk drive. The main weakness of this technology is the relatively slow write operation, which requires a page to be erased before it is rewritten, and the fact that the number of erase operations for a page is limited. This puts an upper bound on the lifetime of the device, and forces designers to resort to advanced wear

Figure 2.4.: ReMIX cluster architecture

leveling strategies as in modern Solid State Drives.

To minimize the hardware development effort, we based our design on a pre-existing third party PCI board integrating a Xilinx Virtex-II Pro FPGA. We then designed an extension board associating 64 GB of Nand-Flash memory <sup>4</sup> and several smaller FPGAs for handling the complex Nand-Flash protocol. In our system, the memory is organized in multiple parallel banks as illustrated in Figure 2.3, enabling sustained I/O throughput of 640 MB/s. A simple host managed file system was used to allow the user to transparently manage the content of the 64 GB Flashmemory, while guaranteeing maximal throughput when accessing data during processing stage. One weakness of this platform is the poor filter output throughput, which is restricted to 5 MB/s (the target PCI board only supporting slave I/O). A prototype cluster of 4 ReMIX node (with two ReMIX board per node) was designed and validated. The cluster, represented in Figure 2.4 was used in several other projects [98], including a port of our Multimedia application [3], that is described in the following section.

## 2.2. A case study: Multimedia Content-Based Image Retrieval

Content-Based Image Retrieval (CBIR) is a technique that is used to retrieve images from a database that are (at least) partly similar to a given query image. CBIR is drawing increasing interest due to its potential application to problems such as image and video copyright enforcement. Indeed, the large use of the Internet resulted in a huge increase of multimedia content available on the Web. Enforcing copyright has hence become a concern to its owners, and in particularly identifying undue use of images is an important issue. Because Internet is a rapidly changing support, there is a need for precise and fast image comparison algorithms that could be used to inspect the web on a daily basis.

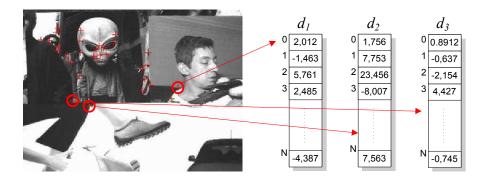

CBIR is mainly based on comparison of *image descriptors* of a *query image* with those of *database images*. Descriptors may be either *global*, i.e., they represent some global feature of an image (e.g., a grey level histogram) or *local*, in which case they describe special points of interest in the image (e.g., corners, color changes, etc.) as depicted in Figure 2.5. In this work, we deal with local descriptors as they were shown to be more robust since they are less dependent to image variations than global descriptors [122].

<sup>4.</sup> In 2005, time of the design, only 32 Gb Nand-Flash chips were available)

Figure 2.5.: Local descriptors are constructed from interest points of the image

## 2.2.1. Similarity search algorithm

Retrieving an image is done in three steps. The first step consists in associating a set of descriptors for the query image, typically, a few hundred vectors of 24 (or more) real components. The second step then computes the distance between each one of the query descriptors and those of the image database (we call this step the distance calculation stage). In the third step, we construct, for each query descriptor, a k-nearest neighbor list which contains the k database descriptors with the smallest distance to the query descriptor (selection stage). Finally, votes are assigned to the images depending on their appearance in the k-nearest neighbor lists (election stage): the image that has the largest number of votes is considered to be the best match.

The whole process is extremely time consuming: retrieving an image among a 30,000 image database required about 1,500 seconds on a standard workstation (in 2005). This is obviously impractical for many applications that would require low response time. The reason for this inefficiency was <sup>5</sup> the lack of efficient indexing scheme for such high-dimensional space, caused by what is known as the *curse of dimensionality* [37]. One solution to improve the performance of CBIR systems was to resort to special purpose implementations. Parallelizing the application on a parallel machine was the most natural choice, and has already been studied by a few authors, including Robles et al. [45, 133].

In this work, we approached the problem by combining both parallelism and special-purpose hardware. Our target architectures were the RDISK and ReMIX Platforms, and we therefore proposed two very different hardware accelerators for the algorithm. Rather than proposing ad-hoc solutions, we tried as much as possible to guide our design choice using high-level analytical performance models. The goal was to be able to take into consideration many different constraints: FPGA resource constraints, bandwidth constraints, and also some statistical information on the algorithm behavior (numerical value distribution, and run time profiling). These models would be too complex to describe in details and we invite the reader to refer to our publications on the topic [23, 3, 29].

#### 2.2.2. Adapting the algorithm for hardware acceleration

The first step in porting the algorithm to hardware is to see whether it can be transformed in order to make it more amenable to custom hardware acceleration. In the following, we describe two of such transformations that we used in this work.

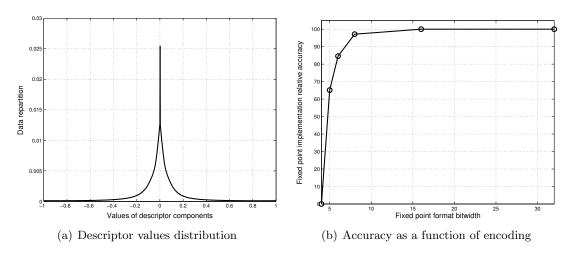

The first one is a conversion from floating-point encoding to short fixed-point integer arithmetic. Even though floating-point operators can be implemented in programmable logic [57, 56],

<sup>5.</sup> The use of past tense is deliberate, as this fact does not hold anymore, as explained in the last section of the chapter.

Figure 2.6.: Descriptor values distribution search accuracy

their area efficiency and performance are still very far from that of fixed-point integer arithmetic. Devising a custom (and short) fixed-point representation for the algorithm data has several advantage: it improves the circuit clock speed, helps increasing the degree of parallelism in the accelerator (more operators can be implemented for a same resource cost), and significantly improves database scanning time, as the database size can also be reduced. Figure 2.6(a) shows the distribution of CBIR descriptor values. The reader may notice that the range of these values is concentrated within a narrow interval. This suggests that descriptor data is amenable to short fixed-point encoding.

The second transformation was the choice of an alternative to the Euclidean distance metric used to compute the distance score. In particular, a common substitute for the Euclidean (also known as  $L_2$ ) distance, is the Sum of Absolute Difference (SAD) distance (also known as  $L_1$ ) metric, which is more suited to hardware, and also widely used in image processing.

In the context of CBIR, there is no way to directly model the impact of a loss of accuracy (by calculating the SQNR) of the search results. The only solution is to use extensive simulation and to experimentally observe the impact of a given conversion scheme (scaling factor and bitwidth) on the search results. This validation was realized through an accuracy test based on the work of Amsaleg et al. [37]. This test considers a random image  $I_{ref}$  taken from the image database. From this image, it derives a set of image variations (including  $I_{ref}$ ) using a set of transformations (cropping, rotation, JPEG encoding, etc.) taken from the Stirmark benchmark [122]. Each one of these images is then used as a query for the database to evaluate the accuracy of the retrieval. Experimental results for various fixed-point bitwidth format using  $L_1$  distance are given in Figure 2.6(b). They have been obtained for a large set of images, and correspond to several week of running time. They show that for 8 bits fixed-point encoding and above, accuracy is similar to the original software (whose accuracy is 85%).

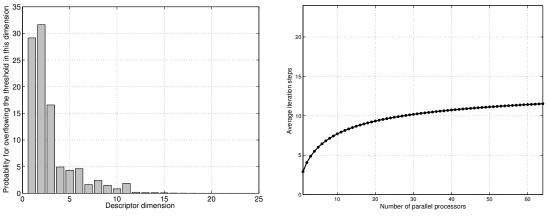

The original software implementation of the algorithm took advantage of a straight-forward, but very efficient optimization. Whenever the current distance score between a query vector and a database vector exceeds the score of the  $k^{th}$ -nearest neighbor (in the following, we call threshold this value), the later is sure to never appear in the list. It is therefore useless to continue, and the algorithm can directly proceed to the next candidate vector.

Figure 2.7(a) illustrates the efficiency of this early exit approach, as it shows that in 80% of the cases, only three iterations are enough to discard a candidate vector. However this only translates into a moderate speedup [23], mostly because of micro-architectural side-effects (the optimization induces many incorrect branch predictions). Taking advantage of this optimization

- number

- (a) Probability of early as a function of the iteration (b) Average number of iterations as a function of the number of processors

Figure 2.7.: Efficiency of the early exit optimization for CBIR

in hardware is far from trivial and may not always be the best design option.

As a matter of fact, such an optimization would be quite inefficient in practice, as the parallel distance evaluation can only proceed to the next candidate vector once all the distances score currently computed are discarded. The actual efficiency of the hardware would then decrease as the level of parallelism would grow, as depicted in Figure 2.7(b).

## 2.2.3. Mapping CBIR on the RDISK platform

We implemented the CBIR algorithm for the RDISK prototype in 2005. The critical point in the design of the filter was to optimize the workload balance in the execution pipeline represented in Figure 2.8. This pipeline involves the hardware filter and the soft-core processor, but its efficiency is also influenced by the disk I/O throughput (15 MB/s) and the network throughput  $(10 \, \text{kB/s}).$

Figure 2.8.: CBIR execution pipeline on the RDISK architecture

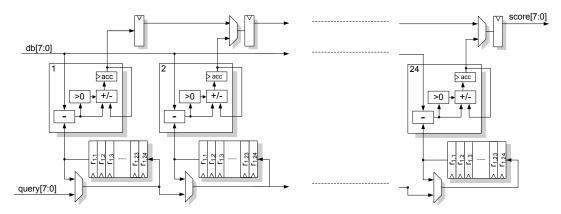

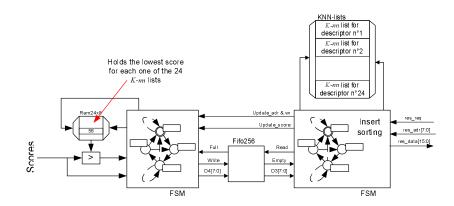

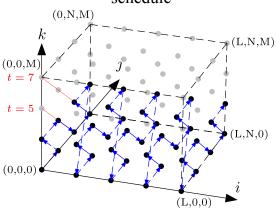

Although the details and motivations for all our design choices is out of the scope of this document, we enumerate some of the most salient characteristics of our distance computation accelerator, shown in Figure 2.9.

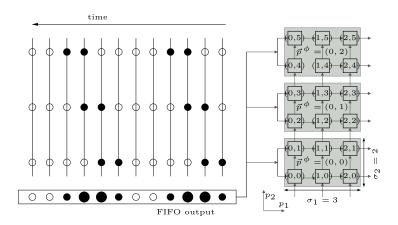

- The baseline architecture is a processor array, in which each processing element handles  $\sigma$ independent query vectors, in a interleaved way (this corresponds to a LSGP partitioned processor arrays as explained in Section 5.3). Hence, the array only needs a new database vector element once every  $\sigma$  cycles. We chose the parameter  $\sigma$  such that the filter bandwidth does not exceed hard-drive throughput to avoid I/O stalls. We also took advantage of the embedded memory blocks available in the FPGA to store the query vectors and their identifiers.

- Because the soft-core processor was not able to sustain the distance computation stage, and because implementing a custom sorting within the FPGA would have required too much resource, we made the choice of taking advantage of threshold optimization described earlier, even though its efficiency is limited.

Figure 2.9.: Distance computation block for the RDISK architecture

We have been able to implement a 36 processors array in the FPGA, in spite of the relatively limited resource available. The speedup over the software implementation is x5 for a single RDISK node, leading to a global performance improvement between x100 and x200 for a full 48 RDISK cluster, depending on the number of descriptors in the query image.

## 2.2.4. Mapping CBIR on the ReMIX platform

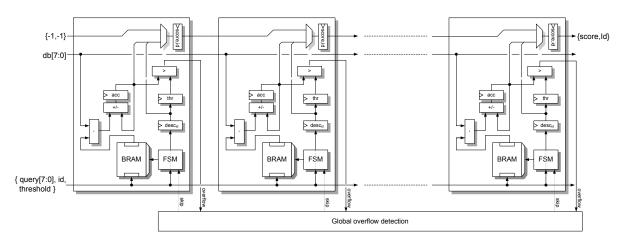

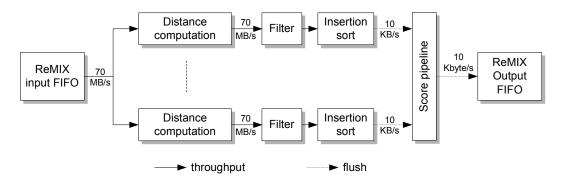

The second implementation targeted the ReMIX prototype where the architectural constraints were completely different. In particular, due the high bandwidth at the Flash memory output (640 MB/s), there was no need to use LSGP partitioning (see Section 5.3) to reduce the architecture throughput as for RDISK. Additionally, the relative abundance of resource on the FPGA allowed us to consider a massively parallel architecture, consisting of multiple pipelines within a single FPGA, as illustrated in Figure 2.10.

Figure 2.10.: System level view of the whole ReMIX CBIR search pipeline

The main difference, as shown in Figure 2.11, is that the ReMIX distance accelerator does not leverage dynamic threshold as in the case of RDISK. Our motivation for disabling this optimization was the area overhead induced by the handling of the threshold. This overhead had in turn a negative impact of the number pipelines that could fit on the FPGA, and we

Figure 2.11.: Distance computation block for the ReMIX architecture

observed that the (limited) performance benefits of the optimization did not compensate for the loss of parallelism. In our distance computation processor, a processing element outputs a new score every 24 cycles. Therefore at most 24 processors can be implemented within a processor array if we want to avoid I/O conflicts on the score output pipeline.

Figure 2.12.: Filtering and sorting blocks for the ReMIX architecture

This continuous stream of results also poses additional challenges to the filtering and sorting steps, which now also need to be performed on-the-fly. For this purpose, we have designed a custom component described in Figure 2.12. This component holds (and updates) a list of 24 thresholds to filter out the results of the distance component. It is also in charge of updating the sorted list of nearest neighbors for each of the 24 descriptors handled by the processor array. Thanks to the highly selective nature of the filtering process, this sequential sorting component is able to sustain the average throughput from the distance computation component, and does not cause any stall in the pipeline.

| Bitwidth            | 24 bits | 16 bits | 12 bits | 8 bits | 3 bits |

|---------------------|---------|---------|---------|--------|--------|

| Query Time (sec)    | 50      | 40      | 28.5    | 20     | 12.5   |

| Speed-up factor     | 18      | 22      | 31      | 45     | 72     |

| Number of pipelines | 4       | 5       | 7       | 10     | 16     |

Table 2.1.: Search time and speed-up for varying bitwidth

The observed speed-up factor over the original software implementation (with the early exit

optimization) was 45. In other words a single ReMIX system is as efficient as a cluster of 45 PCs. While this acceleration factor only holds for descriptors encoded as 8 bit integers, we estimated the corresponding results for different bitwidth by implementing as many processor lines as possible on the FPGA and use this result to estimate the corresponding speed-up. These performance projections are summarized in Table 2.1.

## 2.3. Discussion

In this section, we briefly discuss, in retrospect, the contributions and results presented in this chapter, starting by our work on reconfigurable platforms.

Discussing the RDISK and ReMIX projects six years after their end turned out to be instructive and a bit disappointing at the same time. One observation is that, as we speculated, Flash memory would replace magnetic drives sooner or later. While this prediction is not completely realized, it is definitely in its way, as the SSD market is literally booming. Still, only few attempts have actually been made to fully take advantage of the opportunities they offer as very high-performance custom mass storage, by fully utilizing the aggregate bandwidth of several chips, rather than staying tied to a standard hard-disk interface such as SATA. A notable exception is the Fusion-IO company <sup>6</sup>, which provides high performance PCI-express solutions based on flash memory.

Another observation is that, in spite of all its potential benefits, the idea of coupling processing power to storage device (and to use FPGA for database processing) is still not mainstream. Although FPGAs are commonly used in high performance storage systems, their role is still restricted to low-layer error correction and/or arbitration. However, the idea of attaching a FPGA to a hard disk drive for coprocessing was successfully demonstrated by the Netezza company [33] in 2006 (now owned by IBM), with their SPU blade, which is strikingly similar to our RDISK prototype.

Nevertheless the impact of our work remained limited, and seems to have been ignored (in spite of its obvious relevance and similarity) by almost all recent contributions advocating the use of reconfigurable technologies for database processing platforms [141, 101, 49, 113]. This is however not so surprising and actually shed the light on a questionable habit in the custom computing community to often too quickly claiming for (re)inventing the wheel.

The work that we carried in these two projects required a huge investment in development effort, and one may conclude that designing and proposing original and innovative custom hardware architectures is not a viable research topic. Such as statement however need to be nuanced. This remains an important research topic, which currently suffers from one big issue: building real hardware prototypes for such systems is now out of reach for academic research. In the mean time, providing quantitative evidence on a prototype to backup the relevance of a new type of machine is mandatory. In my opinion, rather than trying to build real machines, custom computer architects should follow the way processor architects have been doing for more than a decade, and what supercomputer designers now also do: basing their experimentation on accurate simulators and/or models. These simulations could be carried at several different levels of abstraction of the machine (for example VPR for modeling the FPGA circuit [106], SocLib [155] for gathering cycle accurate platform level performance metrics, Orion [160] for modeling complex interconnect, etc).

Regarding our work on CBIR, it turns out to be of little practical interest today, as there is no more need for hardware accelerators in CBIR systems. Over the last few years, the *curse of dimensionality* was partially warded off and there now exist methods that reduce search time

<sup>6.</sup> http://www.fusionio.com

by orders of magnitude (to a few ten of milliseconds) while enabling very accurate results [99]. As a matter of fact, the only place where the use of FPGAs could still make a lot of sense is in the extraction of such descriptors, that requires a lot of processing power and relies on well known image processing algorithms that would be a good match for hardware acceleration [81].

| Supervision: Auguste Noumsi, graduated in 2010, 20 %, now assistant professor at University |

|---------------------------------------------------------------------------------------------|

| of Douala, Cameroon                                                                         |

| Journal: Parallel Computing 2006 [20]                                                       |

| International Journal of Electronics 2007 [29]                                              |

| Conferences: Engineering of Reconfigurable Systems and Algorithms 2003 [21]                 |

| 26th IEEE International Parallel & Distributed Processing Symposium 2006 [23]               |

| International Workshop on Applied Reconfigurable Computing 2007 [3]                         |

|                                                                                             |

## Massively Parallel Accelerator for HMM Profile Base Sequence search

The following chapter discusses contributions on the design of hardware accelerators for Hidden Markov Models (HMM) profile based sequence search, a widely used application in bioinformatics. The work presented below started in late 2006 in the context of the ReMIX and RDISK projects, while we were looking for new bioinformatics target applications. HMM based profile search, and more particularly the HMMER suite, turned out to be a challenging problem in terms of parallelization. I started working on the problem on my own (with support from Patrice Quinton), and the results lead to an initial contribution [9, 10] presented in Section 3.2. The results were later extended by Naeem Abbas (supervised by Patrice Quinton) in the context of his PhD [1]. This later work was carried in close collaboration with Sanjay Rajopadhye from Colorado State University.

This chapter is organized as follows, we will first start with a short presentation of the application (namely HMM Profile Bases similarity search), by explaining its role in bioinformatics and by detailing one of its most compute intensive kernel. In Section 3.2, we show how it is possible to derive an efficient processor array architecture for this application, even though the kernel does not admit any parallel schedule. The following section focuses on the kernel itself, and proposes a rewriting of the algorithm to make it amenable to an efficient parallel execution scheme based on *prefix-scan* operations. The chapter is closed by a survey of contributions related to ours, followed by a discussion on the relevance of FPGA based hardware accelerators in high performance biocomputing infrastructures.

## 3.1. Profile based sequence comparison

Sequence homology search tools are one of the most important kind of applications in computational molecular biology. In such applications, the protein sequences of unknown characteristics are compared against database of known sequences in order to predict protein functions and to classify protein families.

For this problem, techniques based on profile Hidden Markov Models (HMMs) [127, 62, 93] have shown to give very good results. Their strength stems from the fact that multiple sequence alignments concentrate on the features or key residues conserved by the family of sequences. As a consequence a profile based search can find a remote sequence homology that could not be detected through a pairwise alignment using simpler sequence matching algorithms such as BLAST [36] and/or Smith & Waterman [140].

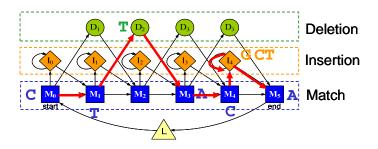

A profile HMM is a regular HMM consisting of a sequence of columns. In each column, a *match* state models the allowed residue, an *insert* state models the insertion of one or more residues, and *delete* the deletion of a residue. An example of such a profile is given in Figure 3.1, in which bold arrows represent a possible path for the target Amino acid sequence (CTTACGCTA). Each path leads to a similarity score, the goal being the retrieval of the path with the highest score using a modified Viterbi algorithm.

Figure 3.1.: Structure of a Plan7 profile HMM, as used in HMMER.

#### 3.1.1. The HMMER software suite

One of the most commonly used program for profile based sequence analysis is the open source software suite HMMER, developed at Washington University, St. Louis by Sean Eddy [61]. Two versions of the tool are currently used by the community, HMMER 2.0 and a recent (March 2010) HMMER 3.0.

In HMMER 2.0, performance profiling shows that the program spends more than 97% of the execution time in the P7Viterbi kernel. This kernel computes a similarity score between the profile HMM and the sequence at hand using a Viterbi dynamic programming algorithm. Matching a single HMM against a protein database is a very time consuming process, which is repeated many times during intensive comparisons.

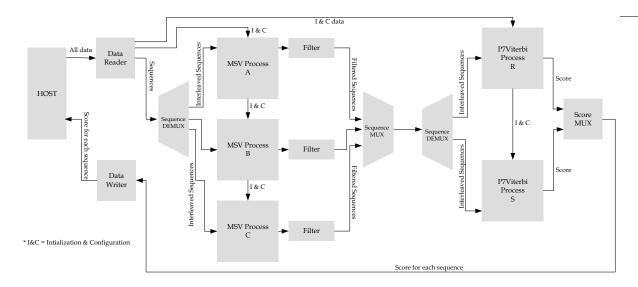

HMMER 3.0 is a complete redesign of the program and of its algorithms. Among other optimizations, it introduces a new heuristic routine called MSV, that is used as a pre-filtering step to the more costly P7Viterbi algorithm. This new execution pipeline is described in Figure 3.2. It is important to understand that this new version (and their corresponding algorithms) has been carefully redesigned to benefit from an efficient implementation on recent x86 multi-cores (this is discussed in more detail in Subsection 3.3.3).

Figure 3.2.: The HMMER3.0 pipeline, showing the effect of the MSV filter, with %95 of the sequences being filtered out by the heuristic.

Performance figure in sequence comparison algorithms are generally measured in Giga Cells Updates per Second (GCUP/s), where a cell update corresponds to one update of the equations of the algorithm. Table 3.1 shows performance figures for HMMER 2.0 and HMMER 3.0 with and without the use of Intel SSE - SIMD extensions. The reader may find that the impact of SIMD extension on performance to be striking, as it alone brings more than ten fold improvement over the non-SIMD version.

| HMMER    | globin.hmm (M=143), | Pkinase.hmm (M=255), | rrm.hmm (M=77), | fn3.hmm (M=84) |

|----------|---------------------|----------------------|-----------------|----------------|

| V2       | $\approx 0.03$      | $\approx 0.03$       | $\approx 0.03$  | $\approx 0.03$ |

| V3-noSSE | 0.3                 | 0.37                 | 0.3             | 0.26           |

| V3-SSE   | 5.2                 | 7.16                 | 2.83            | 2.65           |

Table 3.1.: Performance in GCUPS for Pfam-B.fasta

$$M_{i,k} = \max \begin{cases} e_{M}(\text{seq}_{i,k}) + \max \begin{cases} M_{i-1,k-1} + \text{TMM}_{k} \\ I_{i-1,k-1} + \text{TIM}_{k} \\ D_{i-1,k-1} + \text{TDM}_{k} \\ B_{i-1} + \text{trB}_{k} \end{cases}$$

$$I_{i,k} = \max \begin{cases} e_{I}(\text{seq}_{i,k}) + \max \begin{cases} M_{i-1,k} + \text{TMI}_{k} \\ I_{i-1,k} + \text{TII}_{k} \\ -\infty \end{cases}$$

(3.1)

$$I_{i,k} = \max \begin{cases} e_I(\text{seq}_{i,k}) + \max \begin{cases} M_{i-1,k} + \text{TMI}_k \\ I_{i-1,k} + \text{TII}_k \end{cases}$$

$$(3.2)$$

$$D_{i,k} = \max \begin{cases} M_{i,k-1} + \text{TMD}_k \\ D_{i,k-1} + \text{TDD}_k \\ -\infty \end{cases}$$

(3.3)

$$E_i = \max \begin{cases} \max_{k \in [0,K]} (M_{i,k}) + \text{trM}_k \\ -\infty \end{cases}$$

$$N_{i} = \max \begin{cases} N_{i-1} + \operatorname{trCnst}_{0}[N] \\ -\infty \end{cases}$$

$$(3.5) \qquad J_{i} = \max \begin{cases} E_{i} + \operatorname{trCnst}_{0}[E] \\ J_{i-1} + \operatorname{trCnst}_{0}[J] \\ -\infty \end{cases}$$

$$(3.6)$$

$$B_{i} = \max \begin{cases} N_{i} + \text{trCnst}_{1}[N] \\ J_{i} + \text{trCnst}_{1}[J] \\ -\infty \end{cases}$$

$$(3.7) \qquad C_{i} = \max \begin{cases} C_{i-1} + \text{trCnst}_{0}[C] \\ E_{i} + \text{trCnst}_{1}[E] \\ -\infty \end{cases}$$

$$(3.8)$$

Figure 3.3.: The system of recurrence equations defining the P7Viterbikernel

Figure 3.3 shows the system of recurrence equations defining the dynamic programming algorithm used for comparing a sequence against a profile (known as P7Viterbi kernel), where Ldenotes the protein sequence length and M the length of the profile HMM. The key observations of the equations (3.1-3.8) are that

- there is a chain of dependences in the increasing order of k in computing the values of D in any column;

- to compute the E for any column, we need all the values of M of that column, each of which needs a D from the previous column; and

- the value of E of a column is needed to compute any M in the next column.

Because of this, there seems to be an inherent sequentiality to the algorithm, preventing its parallelization. The same holds for the MSV routine, even though the use of reduction operations <sup>1</sup> is a simple way for exposing more parallelism. The remainder of this chapter describes two contributions, which target the same problem: How to accelerate the HMMER application in spite of its apparent lack of parallelism?

## 3.2. Design space exploration for parallel HMMER

In this section, we will show how to use well known results from the automatic parallelization community, to derive an efficient parallel architecture for the P7Viterbikernel. This derivation is done incrementally, by successive refinements of the initial parallelization.

#### 3.2.1. Exploring scheduling/mappings

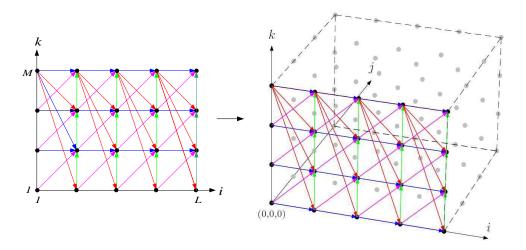

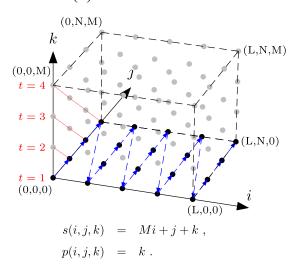

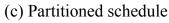

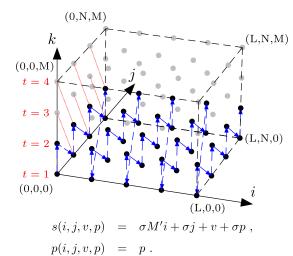

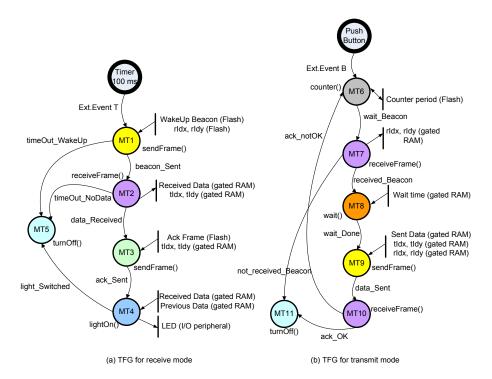

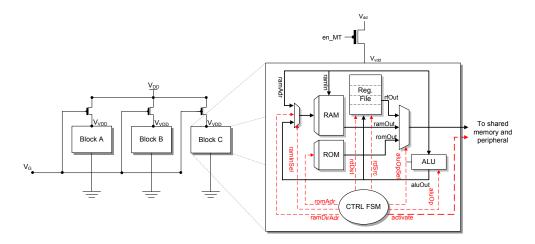

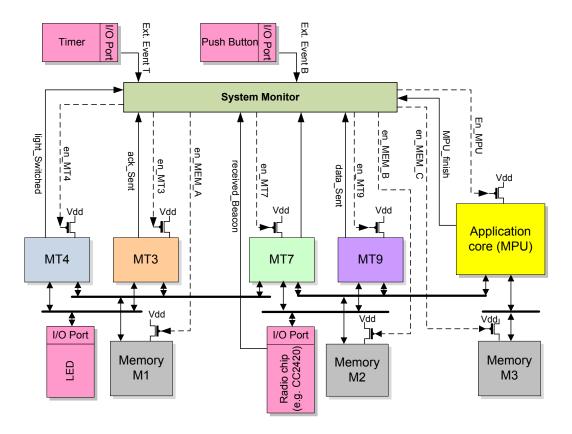

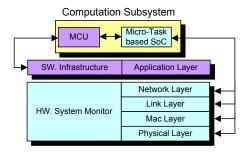

Deriving a regular parallel architecture from a System of Affine Recurrent Equation (SARE) is a well studied problem, for which many techniques have been proposed. The derivation

<sup>1.</sup> A reduction corresponds to a min/max/sum operation on all elements of a collection.

generally uses affine (or quasi affine) space-time mappings. Space-time mappings associate to every indexed variable of the SARE:

A logical execution time instant that we call schedule. In the scope of this work, we target

one dimensional schedules, that take the form of an affine function of the indices written

as

$$s(i_0,\ldots,i_m)=s_0i_0+\ldots+s_mi_m.$$

- A physical location, i.e, coordinates in a processor space. This location is also expressed in the form of an affine function of the indices (that we call allocation function). In our case, we are only interested in one-dimensional (i.e linear) arrays. We therefore have

$$p(i_0,\ldots,i_m)=\alpha_0i_0+\ldots+\alpha_mi_m.$$

Of course, this space-time mapping must satisfy several conditions.

- The chosen schedule must enforce all data dependencies present in the SARE. For  $u, v \in \mathcal{D}$  with v depending on u, the schedule function must guarantee that s(v) > s(u).

- The space-time mapping must be conflict-free, i.e, there must be no u and v in  $\mathcal{D}$  such that  $v \neq u$ , s(u) = s(v) and p(u) = p(v).

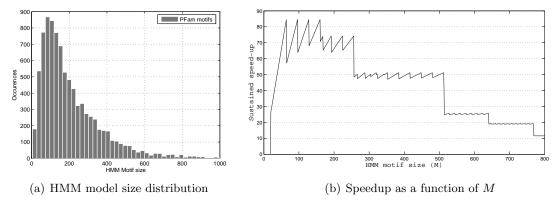

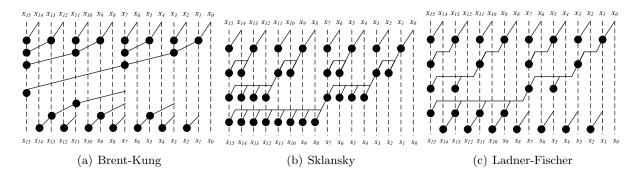

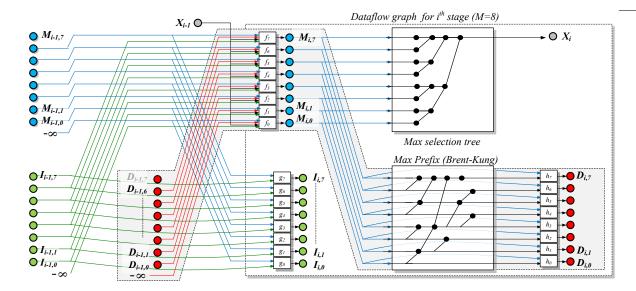

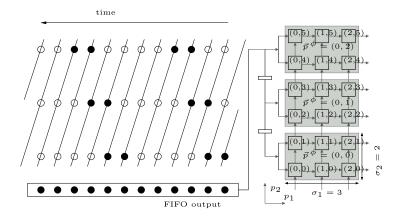

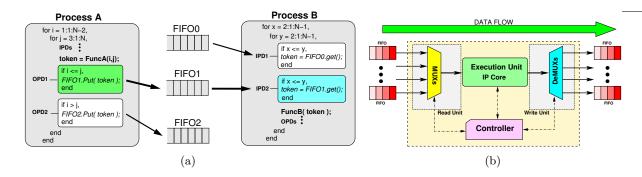

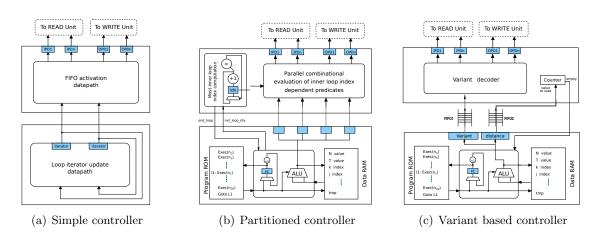

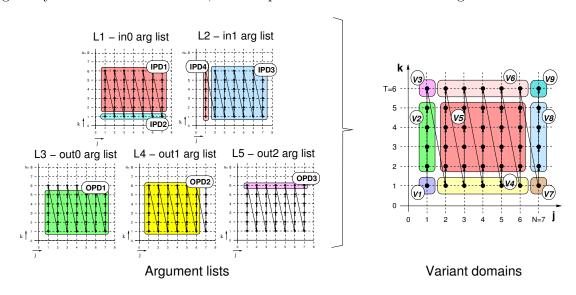

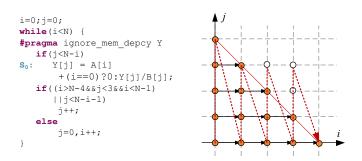

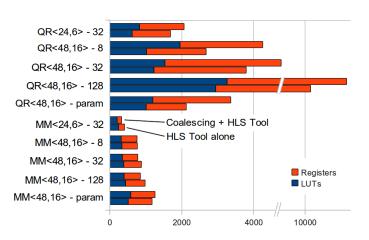

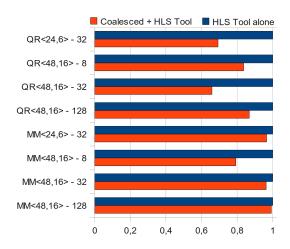

- The space-time mapping must be *dense*, which means that processors on the array are active every cycle in steady state.