## Custom Operator Identification for High-level Synthesis Chenglong Xiao

### ▶ To cite this version:

Chenglong Xiao. Custom Operator Identification for High-level Synthesis. Electronics. Université Rennes 1, 2012. English. NNT: 2012REN1E005 . tel-00759040

## HAL Id: tel-00759040 https://theses.hal.science/tel-00759040

Submitted on 29 Nov 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE / UNIVERSITÉ DE RENNES 1

sous le sceau de l'Université Européenne de Bretagne

pour le grade de

### DOCTEUR DE L'UNIVERSITÉ DE RENNES 1

Mention: Traitement du Signal et Télécommunications

Ecole doctorale MATISSE

présentée par

# Chenglong XIAO

préparée à l'unité de recherche UMR6074 IRISA Institut de recherche en informatique et systèmes aléatoires - CAIRN École Nationale Supérieure des Sciences Appliquées et de Technologie

Custom Operator Identification for High-Level Synthesis

# Thèse soutenue à LANNION le 8 Novembre, 2012

devant le jury composé de :

### Christophe JEGO

Professeur des Universités, IPB/ENSEIRB-MATMECA / rapporteur

## Philippe COUSSY

Maître de Conférences, Université de Bretagne Sud/rapporteur

### Daniel MÉNARD

Professeur des Universités, INSA Rennes / examinateur

## Thierry MICHEL

$STM icroelectronics \,/\, examinateur$

#### Olivier SENTIEYS

Professeur des Universités, Université de Rennes 1 - ENSSAT / examinateur

### Emmanuel CASSEAU

Professeur des Universités,

Université de Rennes 1 - ENSSAT / directeur de thèse

### Acknowledgments

First of all, I would like to thank my advisor professor Emmanuel Casseau for his invaluable guidance. His rigorous attitude towards scientific research and his patience to students have always impressed me. Without his constructive comments and suggestions, this thesis would not have been possible.

I wish to thank the members of my thesis committee for spending their precious time to read and evaluate my dissertation: Christophe Jego (professor at IPB/ENSEIRB-MATMECA), Philippe Coussy (associate professor at Université de Bretagne Sud, Daniel Ménard(professor at INSA Rennes, Thierry Michel (engineer at STMicroelectronics Crolles), Olivier Sentieys (professor at Université de Rennes 1).

I also would like to thank all the members of the IRISA/CAIRN team. In particular, I would like to thank Dr. Kevin Martin and Dr. Antoine Floch for their help during my PhD. With their high-quality implementation work, my PhD work goes on faster and more smoothly.

Most importantly I would like to thank my mother Jinfeng Cai and my wife Shanshan Wang. Without their never ending support and encourage, this thesis would not be possible. This thesis is dedicated to my son Yao Xiao who is always the source of my happiness.

### Custom Operator Identification for High-level Synthesis

**Abstract:** It is increasingly common to see custom operators appear in various fields of circuit design. Custom operators that can be implemented in special hardware units make it possible to reduce code size, improve performance and reduce area. In this thesis, we propose a custom operator based high-level synthesis design flow. The key issues involved in the design flow are: automatic enumeration and selection of custom operators from a given high-level application code and re-generation of the source code incorporating the selected custom operators.

However, automatic enumerating all the subgraphs is computationally difficult problem. In this thesis, we propose three enumeration algorithms for exact enumeration of subgraphs under various constraints. Compared to a previously proposed well-known algorithm, the proposed enumeration algorithms can achieve orders of magnitude speedup.

Selecting a most profitable subset from the enumerated subgraphs is also a time-consuming job. In this thesis, we present three different selection heuristics targeting different objectives. In addition, a branch-and-bound approach and a genetic algorithm are introduced to select the minimal number of matches that fully cover the data flow graph of a given application code. The greedy approaches are very efficient, but they may produce results that are sub-optimal. While the exact algorithms guarantee the optimum of solutions, but they fail to give solution in an affordable time in most situations. The proposed genetic algorithm makes trade-off between the two. The runtime and the quality of solutions can be controlled by some user-specified parameters.

During the code re-generation step, a graph isomorphism is required to group the structurally and functionally equivalent subgraphs that can be implemented with the same custom operator. An extended graph isomorphism algorithm that captures the characteristics of data-flow graph is proposed to determine the similarity between graphs after selection. Some specific problems existing in the graphs isomorphism check for data-flow graph are depicted in this thesis. Corresponding solutions for those specific problems are provided. To our knowledge, these were never mentioned in the previous literature.

We have developed and implemented a complete design flow for pattern based high-level synthesis. Unlike the previously proposed approaches, our design flow is quite adaptable and is independent of high-level synthesis tools (i.e., without modifying the scheduling and binding algorithms in high-level synthesis tools). Experimental results show that our approach achieves on average 19%, and up to 37% area reduction, compared to a traditional high-level synthesis. Meanwhile, the latency is reduced on average by 22%, and up to 59%. Furthermore, on average 74% and up to 81% code size reduction can be achieved. **Keywords:** custom operator, subgraph enumeration algorithm, subgraph selection algorithm, code transformation, high-level synthesis

### Identification d'opérateurs spécifiques pour la synthèse de haut niveau

La complexité croissante des applications à intégrer a conduit à concevoir les circuits à un haut niveau d'abstraction. A ce titre, par rapport à une synthèse classique de niveau dit " transfert de registres " (RTL), la synthèse de haut niveau (HLS) permet d'envisager une meilleure productivité. Par ailleurs, il est de plus en plus fréquent dans les différents domaines de la conception de circuits de faire appel à des opérateurs spécifiques, opérateurs qui permettent de réduire la taille du code, d'améliorer les performances ou de réduire la surface d'un circuit. Dans cette thèse, nous proposons un flot de conception basé sur l'identification d'opérateurs spécifiques pour la synthèse de haut niveau.

#### Synthèse de haut niveau

On constate depuis une vingtaine d'années que les applications à mettre en œuvre sont de plus en plus complexes. Elever le niveau d'abstraction permet de réduire considérablement le temps de conception. Aussi, la synthèse de haut niveau s'avère être de plus en plus utilisée dans les flots de conception de systèmes électroniques De nombreux outils commerciaux de synthèse de haut niveau ont été proposés par plusieurs fournisseurs. On trouve par exemple Autopilote, CatapultC, CTOS, Cynthesizer, SynphonyC et Cyber-Workbench. En outre, beaucoup d'outils de synthèse de haut niveau ont également été proposés par des universitaires (par exemple, Legup, GAUT, Trident et SPARK).

La synthèse de haut niveau, parfois appelée synthèse comportementale, est un processus de conception automatisée permettant de transformer des spécifications (par exemple, décrite en C, C + + ou SystemC) en des spécifications de bas niveau (transfert de registre) qui implémentent le comportement spécifié tout en satisfaisant les contraintes de conception. Les outils HLS acceptent des spécifications de haut niveau comme entrée. En général, la plupart des outils actuels de HLS commerciaux utilisent le langage C en entrée. Nous pouvons également trouver des outils HLS utilisant les langages tels Blue-Spec, Esterel and MATLAB. En plus des spécifications de haut niveau, une bibliothèque de ressources contenant les informations détaillées sur les composants matériels ainsi que les contraintes de conception spécifiques sont fournies à l'outil HLS. A partir de ces points d'entrées, l'outil HLS effectue les tâches suivantes et produit en sortie une description de matérielle qui permet d'implémenter la spécification:

"Front End " de compilation: Les spécifications sont analysés et traduites en représentations intermédiaires. Plusieurs transformations préliminaires ou des optimisations de code, telles que l'élimination de " code mort ", l'élimination de fausses dépendances de données, l'équilibrage de branches, la propagation de constantes, des transformations de boucles, et l'élimination de sous-expressions communes sont réalisées au plus tôt de cette étape. Après ces optimisations, les spécifications sont transformées en une représentation intermédiaire appropriée. Afin de capturer à la fois les dépendances de données et les dépendances de contrôle entre les opérations de la spécification, les représentations intermédiaires (IR) qui conservent les informations présentées dans la spécification d'entrée sont utilisées. Le graphe de flot de contrôle et de données (CDFG) est considéré comme l'une des plus populaires IR. Le CDFG est un graphe orienté dans lequel un nœud peut être soit une opération soit un bloc de base. Les arcs dans un CDFG représentent le

transfert d'une valeur ou une commande d'un nœud à un autre. A l'intérieur de chaque nœud, un graphe flot de données est utilisé pour capturer les dépendances de données entre opérations. En outre, les dépendances de données entre les blocs de base peuvent être exprimées à l'aide des graphes de tâches hiérarchiques.

Allocation: Ce processus détermine les types de composants matériels nécessaires pour la mise en œuvre du matériel ainsi que leur quantité. Les composants matériels peuvent être des unités fonctionnelles pour les opérations, des registres pour stocker des valeurs, des bus et des multiplexeurs pour interconnections.

Ordonnancement: L'ordonnancement est le processus qui attribue des cycles d'horloge ou des pas de temps aux opérations afin que les contraintes temporelles soient satisfaites. Chaque opération est ordonnancée en fonction des dépendances de données et de contrôle entre opérations. Il existe plusieurs algorithmes d'ordonnancement: dès que possible (AS-AP), le plus tard possible (ALAP), l'ordonnancement par liste, force dirigée et la programmation linéaire entière. L'ordonnancement et l'allocation des ressources sont généralement interdépendants. L'ordonnancement est effectué par rapport à des contraintes de ressources (celles qui sont affectées à l'étape d'allocation), tandis que l'allocation des ressources peut être améliorée si les opérations qui peuvent être exécutées en parallèle sont connus à l'avance (ces informations peuvent être obtenues à partir de l'ordonnancement).

Projection: Le processus de projection affecte les unités fonctionnelles aux opérations afin de pouvoir les exécuter, des registres pour stocker des valeurs qui circulent à travers les bus / multiplexeurs qui eux implémentent les transferts de données / contrôle. L'algorithme de projection décide de quelle unité fonctionnelle doit être utilisée pour effectuer une opération spécifique quand il y a plus d'une unité fonctionnelle capable d'exécuter l'opération au cycle en question. Les opérations et les données de durée de vie mutuellement exclusives peuvent partager le même composant matériel.

Génération de code: À la fin du processus de synthèse, la génération de code permet de produire une description de niveau RTL, qui inclus un chemin de données et une unité de commande. Le chemin de données se réfère aux unités fonctionnelles tels que des additionneurs, des multiplieurs, des unités arithmétiques et logiques (UAL) etc., des unités de mémorisation tels que des mémoires et des registres ainsi que les composants de communication/interconnexion tels que les bus et les multiplexeurs. L'unité de commande est une machine à états finis (FSM) qui génère des signaux de commande et contrôle du flot de données.

#### Opérateurs spécifiques

Il est fréquent de faire usage d'opérateurs spécifiques dans divers domaines de la conception de circuits. A titre d'exemple, l'usage d'opérateurs spécifiques permet de faire des compromis entre flexibilité et efficacité avec les processeurs extensibles. Un opérateur spécifique est composé d'un ensemble d'opérations de base (par exemple, des opérations arithmétiques de base telles que les additions, soustractions et multiplications). Une unité fonctionnelle spécifique implémente un opérateur spécifique.

Le premier avantage apporté par l'utilisation d'opérateurs spécifiques est la réduction importante du code source. En règle générale, l'opérateur spécifique encapsule plusieurs opérations de base et les assemble en un seul opérateur plus complexe. Ainsi, la taille du

code source peut être réduite, et le niveau de granularité du code source est augmenté. Les outils de synthèse de haut niveau peuvent alors produire des solutions plus rapidement avec le code réduit.

Avec les opérateurs spécifiques, des améliorations en terme de performances peuvent être obtenues. Les opérateurs spécifiques améliorent les performances de quatre façons possibles. Tout d'abord, les opérations de base à l'intérieur de l'opérateur spécifique sont chaînées selon les dépendances de données (chaînage d'opération). Deuxièmement, les opérations de base sans dépendance des données peuvent être parallélisées. Troisièmement, certaines techniques d'optimisation peuvent être appliquées pour réduire le chemin critique. Enfin, la mise en œuvre matérielle d'un opérateur spécifique est généralement plus rapide (chemin critique) que si on utilise des opérateurs de base (par exemple, le temps de latence d'une multiplication-accumulation (MAC) est inférieur à la somme de la latence d'un multiplieur et de la latence d'un additionneur).

En outre, les opérateurs spécifiques peuvent conduire à des gains en surface à travers les deux aspects suivants. Tout d'abord, en général, les flots de données internes d'un opérateur spécifique sont exempts de multiplexeurs. Deuxièmement, la mise en œuvre matérielle d'un opérateur spécifique conduit à une surface plus faible (par exemple, la surface d'un MAC est inférieure à la somme de la surface d'un multiplieur et la surface d'un additionneur). Il est à noter cependant que, en utilisant les opérateurs spécifiques, on peut parfois aboutir à un partage moins efficace des ressources: on trouve en effet plus d'instances d'opérations élémentaires dans un graphe d'origine que d'instances d'opérations spécifiques dans un graphe réduit.

Nous proposons un flot de conception tirant partie d'opérateurs spécifiques en amont de la synthèse de haut niveau et permettant de transformer le code source en lui incorporant des opérateurs spécifiques, afin d'améliorer les résultats des outils de synthèse de haut niveau. Contrairement aux approches précédentes de la littérature qui nécessitent de modifier les algorithmes d'ordonnancement et d'allocation des outils de synthèse de haut niveau, notre flot de conception est totalement indépendant de ces outils. Notre flot de conception peut ainsi être adapté à de nombreux outils de synthèse de haut niveau commerciaux.

Le flot de conception est composé de quatre étapes principales. Le point de départ est le code source de haut niveau (langage C par exemple). Dans la première étape, le code source est transformé en un graphe de flot de contrôle et de données (CDFG) en utilisant un compilateur open source GECOS. Ensuite, les sous-graphes possibles sont identifiés par un algorithme d'énumération à partir des graphes DFG (graphe flot de données) qui correspondent chacun à un bloc de base du CDFG. Puis un sous-ensemble des sous-graphes identifiés est sélectionné en fonction de différentes stratégies (nombre minimum d'opérateurs spécifiques, taille minimum de code, etc.). Enfin, le code source d'origine est transformé en un nouveau code source en intégrant les sous-graphes sélectionnés (les sous-graphes sélectionnés seront mis en œuvre en tant qu'opérateurs spécifiques). Le nouveau code source faisant appel aux opérateurs spécifiques est alors fourni en entrée de l'outil de synthèse de haut niveau ciblé.

Représentation intermédiaire: La spécification comportementale d'entrée de la synthèse de haut niveau est généralement composée d'une liste de déclarations séquentielles.

Les déclarations peuvent être des expressions de type opération, des structures conditionnelles et des boucles. Pour exprimer les dépendances de données dans la description d'entrée, le graphe flot de données est un bon candidat. Comme le graphe flot de données ne contient que des dépendances de données explicites, on peut faire appel à un graphe de flot de contrôle pour exprimer le contrôle d'une spécification d'entrée. Afin d'exprimer ces deux informations à la fois, les graphes de flot de données et de contrôle sont souvent utilisés et constituent une bonne représentation intermédiaire pour la synthèse de haut niveau.

Énumération de sous-graphes: L'efficacité de l'énumération de sous-graphes est meilleure si l'identification multiple d'un même sous-graphe peut être évitée. La plupart des travaux antérieurs conduisent à identifier plusieurs fois un même sous-graphe. Le temps d'exécution est alors inutilement augmenté. Dans cette thèse, nous présentons une approche efficace qui évite les identifications multiples de sous-graphes par une technique de suppression de nœuds lors de l'énumération des sous-graphes sous contrainte de taille. Dans cette thèse, nous présentons également un algorithme très flexible pour l'énumération exacte des sous-graphes sous contrainte d'entrées/sorties. L'algorithme est basé sur notre algorithme d'énumération sous contrainte de taille. L'algorithme peut être spécialisé pour générer tous les sous-graphes possibles ou seulement les sous-graphes connectés. Dans cette thèse, nous proposons également un nouvel algorithme pour l'énumération de sous-graphes sous contrainte d'entrées/sorties. Notre algorithme permet de résoudre le problème de manière efficace en profitant de la propriété topologique d'un graphe flot de données (DFG).

Sélection de sous-graphes: Diverses stratégies peuvent être utilisées pour guider la sélection sous-graphes. Dans cette thèse, nous nous concentrons sur trois stratégies différentes. Tout d'abord, la taille du code peut être un objectif d'optimisation important. En conception de systèmes embarqués, seule une petite quantité de mémoire est en général disponible pour stocker les instructions. Dans le contexte de la synthèse de haut niveau, la sélection du plus petit ensemble de sous-graphes conduit au code le plus compact. L'espace de conception est ainsi réduit, l'outil de synthèse de haut niveau peut alors produire des résultats en moins de temps. Ensuite, la fréquence d'occurrences d'un motif renseigne sur le partage possible des ressources. Une méthode de sélection basée sur la fréquence d'occurrences de motifs est présentée (basée sur le nombre d'instances de motifs). Enfin, la sélection de sous-graphes peut conduire à augmenter la longueur des chemins critiques. Ainsi, une sélection de sous-graphes qui prend en compte le surcoût en terme de latence est très important. Une méthode de sélection basée sur le chemin critique est également proposée dans cette thèse.

Les algorithmes de résolution exacte sont fortement consommateurs en temps d'exécution et échouent généralement à donner un résultat en raison d'un temps d'exécution trop long ou d'un débordement mémoire. Par exemple, un algorithme de type "branch-and-bound "requiert 20 secondes pour trouver le nombre minimum d'instances de motifs qui recouvrent entièrement le graphe d'un produit de vecteurs lorsque le graphe correspondant est un "petit graphe "qui contient seulement 8 nœuds. Lorsqu'on augmente la taille des vecteurs, cet algorithme exact ne parvient pas à produire de résultats en moins d'une heure lorsque le graphe contient 12 nœuds. Aussi, une approche heuristique efficace est nécessaire. Dans cette thèse, trois algorithmes de type heuristique visant des

objectifs différents sont représentés. Bien que l'algorithme exact est grand consommateur en temps comparé aux algorithmes heuristiques ou algorithmes gloutons, nous présentons cependant aussi un algorithme " branch-and-bound " pour connaître le nombre minimum d'instances de motifs dans un but de comparaison.

Le problème de sélection de motifs peut être transformé en un problème de couverture. Le problème de couverture est un problème d'optimisation combinatoire classique, problème pour lequel les algorithmes génétiques sont bien adaptés, en particulier lorsque le problème est un problème NP-complet. Par conséquent, nous avons également essayé d'appliquer un algorithme génétique pour résoudre le problème de sélection de motifs dans cette thèse.

Transformation de code: Après l'obtention d'un ensemble de sous-graphes produits par l'étape d'énumération de sous-graphes, l'étape de sélection sous-graphes nous délivre un ensemble des sous-graphes sélectionnés. Il est nécessaire de déterminer si deux sous-graphes sélectionnés peuvent être exécutés par une même unité fonctionnelle spécifique (cela se fait en pratique avant la sélection). Cette tâche peut être considérée comme un problème d'isomorphisme de graphes. Nous avons développé un algorithme d'isomorphisme de graphes. Notre algorithme est en fait une extension de l'algorithme d'isomorphisme de graphes VF2. Nous avons étendu l'algorithme VF2 en analysant certaines caractéristiques du graphe flot de données. L'algorithme VF2 trouve la correspondance entre deux graphes en comparant graduellement des paires de nœuds. En général, les correspondances partielles sont étendues à des correspondances partielles plus grandes en ajoutant une paire de nœuds voisins compatibles. Une paire de nœud est dite compatible uniquement lorsque les deux nœuds satisfont un ensemble de règles de faisabilité. L'ensemble des règles de faisabilité permet de réduire efficacement l'espace de recherche. Nous avons amélioré l'algorithme VF2 en ajoutant une vérification de cardinalité sur les sommets, les arêtes et le nœud de départ afin de rejeter rapidement des graphes différents. De plus, l'algorithme propose résout le problème causé par les opérations non commutatives.

Après avoir réalisé la projection des sous-graphes fonctionnellement équivalents sur des opérateurs spécifiques identiques, l'ensemble des nœuds à l'intérieur d'un sous-graphe est remplacé par un super nœud. Le super nœud correspond donc au sous-graphe sélectionné. Afin de ne pas perdre la sémantique du code d'origine, les super nœuds contiennent toutes les informations correspondant aux sous-graphes remplacés. phase de régénération de code a pour rôle de traduire correctement ce super nœud en code équivalent.

Une fois les sous-graphes remplacés par des super nœuds, un pragma spécifique peut être inclus dans le nouveau code source généré pour chaque opérateur spécifique. L'opérateur est alors présenté comme une fonction. Avec ce pragma spécifique, les outils de synthèse de haut niveau (par exemple, CatapultC (Mentor Graphics)) ordonnancera et projettera les opérateurs spécifiques exactement comme ils le font pour les opérateurs de base. Pour l'outil de synthèse de haut niveau toutes les fonctions non-inlinées sont considérées comme des opérateurs spécifiques par défaut (le pragma n'est donc pas nécessaire).

#### Contributions:

Dans cette thèse, nous développons un flot de synthèse de haut niveau basé sur l'utilisation d'opérateurs spécifiques. Les points clés de ce flot de conception sont les

suivants: énumération automatique et sélection des opérateurs spécifiques à partir d'une application spécifiée à haut niveau, et régénération d'un code source intégrant les opérateurs spécifiques sélectionnés. Cette thèse apporte les contributions suivantes:

Énumération de sous-graphes: Comme le nombre de sous-graphes dans un DFG est une fonction exponentielle du nombre de nœuds du DFG, l'énumération de sous-graphes est un problème difficile. Par exemple, dans un DFG provenant du benchmark de spécification GSM qui comporte 490 nœuds, le nombre de sous-graphes possibles vaut 341.641 lorsque les contraintes d'entrées et de sorties (E/S) sont 4 et 2 (au plus) respectivement. Lorsque les contraintes d'E/S sont 6/2, le nombre de sous-graphes passe à 1.454.539. Nous présentons trois algorithmes évolutifs d'énumération de sous-graphes qui permettent d'énumérer tous les sous-graphes de manière très efficace sous des contraintes de conception différentes. Pour énumérer les sous-graphes sous contrainte de taille, nous proposons un nouvel algorithme qui permet d'éviter les identifications multiples de sous-graphes. Sur la base de l'algorithme proposé sous contrainte de taille, un algorithme étendu qui vise à énumérer tous les sous-graphes possibles ou seulement sous-graphes connectés est ensuite présenté. En outre, nous présentons un algorithme au temps de calcul polynomial qui consiste en une amélioration d'un algorithme de référence pour énumérer tous les sous-graphes possibles, à savoir les sous-graphes disjoints et les sous-graphes connectés. Les expériences montrent que nos algorithmes permettent de gagner jusqu'à 2 décades en terme de temps de calcul par rapport à l'algorithme de référence.

Sélection de sous-graphes: La sélection d'un sous-ensemble de l'ensemble des sous-graphes générés par l'énumération de sous-graphes est également un problème coûteux en temps. Notre objectif est donc de proposer des algorithmes efficaces en temps. Trois approches heuristiques différentes de sélection de sous-graphes visant des objectifs différents sont présentées et une comparaison de ces algorithmes est faite dans la partie expériences. En outre, nous présentons un algorithme exact ainsi qu'un algorithme génétique pour la sélection d'un nombre minimum d'instances de motifs qui couvrent le graphe de l'application. L'algorithme génétique proposé est un compromis entre l'approche gloutonne et l'approche exacte. En d'autres termes, il réalise un compromis entre le temps d'exécution de la sélection et la qualité des résultats de la sélection.

Transformation de code: Nous avons étendu un algorithme existant d'isomorphisme de graphes afin de rejeter rapidement des graphes différents en tirant partie de certaines caractéristiques des graphes flots de données. Certains problèmes spécifiques que pose la vérification d'isomorphisme de graphes et de sous-graphes sont d'abord exposés. À notre connaissance, les problèmes mentionnés n'ont jamais été considérés dans la littérature. Les solutions correspondantes pour répondre aux problèmes soulevés sont fournies dans cette thèse. En outre, une présentation du code généré utilisant les opérateurs spécifiques est également faite.

Flot de conception automatisé: un flot de conception automatisé et adaptable basé sur l'utilisation d'opérateurs spécifiques pour la synthèse de haut niveau a ainsi pu être mis en œuvre. Les résultats pour un ensemble d'applications de référence montrent que la solution proposée permet d'obtenir une réduction significative la taille du code, une réduction de la surface et une diminution de la latence du circuit généré.

# Contents

| $\mathbf{A}$     | bstra | ct     |                                                   | iii  |

|------------------|-------|--------|---------------------------------------------------|------|

| $\mathbf{R}_{0}$ | esum  | é      |                                                   | v    |

| Li               | st of | Acron  | nyms                                              | xix  |

| Li               | st of | Notat  | cions                                             | 1    |

| 1                | Intr  | oduct  | ion                                               | 1    |

|                  | 1.1   | High-l | Level Synthesis                                   | . 1  |

|                  | 1.2   | Custo  | m Operators                                       | . 3  |

|                  | 1.3   | An O   | verview of the Design Flow                        | . 5  |

|                  | 1.4   | Contri | ibutions of this Thesis                           | . 7  |

|                  | 1.5   | Organ  | nization of this Thesis                           | . 9  |

| 2                | Rela  | ated V | Vork                                              | 11   |

|                  | 2.1   | Intern | nediate Representation                            | . 11 |

|                  |       | 2.1.1  | Data-Flow Graph                                   | . 12 |

|                  |       | 2.1.2  | Control-Flow Graph                                | . 14 |

|                  |       | 2.1.3  | Control Data-Flow Graph                           | . 15 |

|                  | 2.2   | Defini | tions                                             | . 16 |

|                  | 2.3   | Relate | ed Work on Subgraph Enumeration                   | . 18 |

|                  | 2.4   | Relate | ed Work on Subgraph/Pattern Selection             | . 25 |

|                  | 2.5   | Relate | ed Work on (Sub)Graph Isomorphism                 | . 29 |

|                  | 2.6   | Summ   | nary                                              | . 31 |

| 3                | Sub   | graph  | Enumeration                                       | 33   |

|                  | 3.1   | Proble | em Formulation                                    | . 33 |

|                  | 3.2   | An Al  | gorithm for Size Constrained Enumeration          | . 35 |

|                  | 3.3   | An Ex  | ktended Algorithm for I/O Constrained Enumeration | . 37 |

|                  |       | 3.3.1  | Overview                                          | . 37 |

|                  |       | 3.3.2  | Convexity                                         | . 39 |

|                  |       | 3 3 3  | I/O Constraints                                   | 41   |

xii Contents

|   |     | 3.3.4   | Data Structures and Calculations                        | 43 |

|---|-----|---------|---------------------------------------------------------|----|

|   | 3.4 | A Top   | ology Based Algorithm for I/O Constrained Enumeration   | 45 |

|   |     | 3.4.1   | Motivation                                              | 45 |

|   |     | 3.4.2   | Overview                                                | 47 |

|   |     | 3.4.3   | Search Space Pruning and Convexity                      | 49 |

|   |     | 3.4.4   | Data Structure and Calculations                         | 50 |

|   |     | 3.4.5   | Complexity Analysis                                     | 52 |

|   |     | 3.4.6   | Further Improvement                                     | 53 |

|   | 3.5 | Summ    | nary                                                    | 53 |

| 4 | Sub | graph   | Selection Algorithms                                    | 57 |

|   | 4.1 | Proble  | em Formulation                                          | 57 |

|   | 4.2 | Heuris  | stic Algorithms                                         | 59 |

|   |     | 4.2.1   | Minimal Number of Matches Selection                     | 60 |

|   |     | 4.2.2   | Frequency of Occurrences Based Pattern Selection        | 61 |

|   |     | 4.2.3   | Critical Path Based Match Selection                     | 62 |

|   | 4.3 | An Ex   | xact Algorithm for Minimal Number of Matches Selection  | 63 |

|   |     | 4.3.1   | Set Covering Problem                                    | 64 |

|   |     | 4.3.2   | A Branch-and-Bound Algorithm                            | 65 |

|   | 4.4 | A Ger   | netic Algorithm for Minimal Number of Matches Selection | 66 |

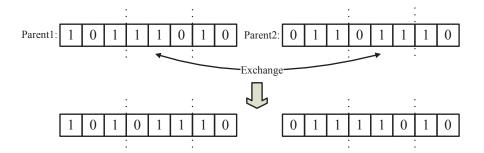

|   |     | 4.4.1   | Encoding                                                | 67 |

|   |     | 4.4.2   | Generating the Initial Solution                         | 68 |

|   |     | 4.4.3   | Fitness Function                                        | 69 |

|   |     | 4.4.4   | Selection                                               | 69 |

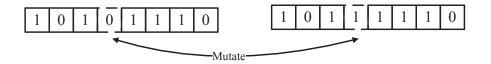

|   |     | 4.4.5   | Reproducing                                             | 70 |

|   |     | 4.4.6   | Replacement                                             | 73 |

|   | 4.5 | Summ    | nary                                                    | 73 |

| 5 | Cod | le Trai | nsformation                                             | 75 |

|   | 5.1 | A Gra   | ph Isomorphism Algorithm                                | 75 |

|   | 5.2 | Code    | Representation of Custom Operator                       | 79 |

|   | 5.3 | An Ex   | cample of Using the Complete Design Flow                | 80 |

|   | 5.4 | Summ    | nary                                                    | 80 |

| 6 | Exp | erime   | nts and Results                                         | 83 |

| C t t    |      |

|----------|------|

| Contents | XIII |

|              | 6.1  | Exper   | imental Setup                                                       | 84  |  |

|--------------|------|---------|---------------------------------------------------------------------|-----|--|

|              | 6.2  | Runtin  | me of the Enumeration Algorithms                                    | 84  |  |

|              |      | 6.2.1   | Runtime of the Size Constrained Enumeration Algorithm               | 86  |  |

|              |      | 6.2.2   | Runtime of the I/O Constrained Enumeration Algorithms               | 87  |  |

|              | 6.3  | Evalua  | ation of the Selection Approaches                                   | 94  |  |

|              |      | 6.3.1   | Area and Performance Evaluation                                     | 94  |  |

|              |      | 6.3.2   | Code Size Reduction                                                 | 98  |  |

|              |      | 6.3.3   | Comparison of the MS Algorithm and the Genetic Algorithm $$         | 99  |  |

|              | 6.4  | Discus  | sion and Summary                                                    | 101 |  |

| 7            | Con  | clusio  | ns                                                                  | 105 |  |

|              | 7.1  | Conclu  | ısion                                                               | 105 |  |

|              | 7.2  | Future  | e Work                                                              | 107 |  |

| $\mathbf{A}$ | Rur  | ntime o | of the Subgraph Enumeration Step                                    | 109 |  |

|              | A.1  |         | intime performance of the subgraph enumeration step under size con- | 109 |  |

| p:           | 1. 1 | 1       |                                                                     | 111 |  |

| ום           | DIIO | graphy  |                                                                     | 111 |  |

# List of Figures

| 1.1  | High-level synthesis flow                                                                                                                | 4  |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | (a) A selected custom operator (b) A custom operator with reduced critical path                                                          | 5  |

| 1.3  | Custom operator Identification for high-level synthesis                                                                                  | 6  |

| 1.4  | Summary of our approach to custom operator based high-level synthesis flow                                                               | 7  |

| 2.1  | (a) Fragment of C code without condition or loop (b) Corresponding data flow graph                                                       | 12 |

| 2.2  | (a) Fragment of C code with condition (b) Corresponding data flow graph (with loss of consistency)                                       | 13 |

| 2.3  | C code without condition or loop and its corresponding CFG                                                                               | 15 |

| 2.4  | (a) Fragment of C code (b) Corresponding control flow graph                                                                              | 16 |

| 2.5  | (a) Fragment of C code (b) Corresponding control data-flow graph                                                                         | 17 |

| 2.6  | A pattern with its matches                                                                                                               | 17 |

| 2.7  | Custom operator based high-level synthesis flow                                                                                          | 19 |

| 2.8  | A DFG and its corresponding binary search tree                                                                                           | 22 |

| 2.9  | A conflict graph                                                                                                                         | 27 |

| 2.10 | (a) Two graphs $G_1$ and $G_2$ , (b) a partial mapping solution, (c) the corresponding graphic state, (d) the only full mapping solution | 30 |

| 3.1  | An example of data-flow graph                                                                                                            | 34 |

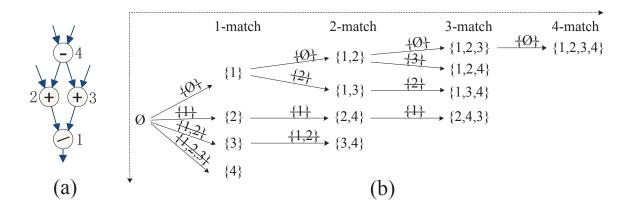

| 3.2  | The subgraph enumeration process for a simple DFG                                                                                        | 37 |

| 3.3  | Resolve I/O constraints violation $\ldots \ldots \ldots \ldots \ldots \ldots$                                                            | 43 |

| 3.4  | A topologically sorted data-flow graph                                                                                                   | 46 |

| 3.5  | Illustration of the search tree for the generation of all feasible subgraphs involving node 1 in Fig. 3.4                                | 52 |

| 4.1  | Overlapping between subgraphs                                                                                                            | 58 |

| 4.2  | Cyclic subgraphs                                                                                                                         | 58 |

| 4.3  | Select the subgraph with less overlapping                                                                                                | 60 |

| 4.4  | Select the pattern with more nodes                                                                                                       | 61 |

| 4.5  | (a) The original data-flow graph (b) A selection that results in the increase of the length of the critical path                         | 63 |

xvi List of Figures

| 4.6  | Binary representation of a solution                                                                                                                            | 68  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.7  | Two point crossover operator                                                                                                                                   | 72  |

| 4.8  | An example of mutation operator                                                                                                                                | 73  |

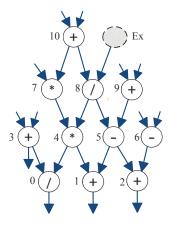

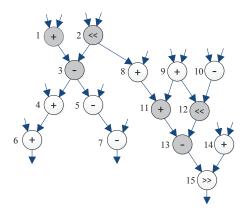

| 5.1  | DFG from the JPEG benchmark                                                                                                                                    | 77  |

| 5.2  | Two graphs with a non-commutative operation                                                                                                                    | 78  |

| 5.3  | Finding the matches of a symmetrical pattern                                                                                                                   | 79  |

| 5.4  | The code representation for a custom operator                                                                                                                  | 80  |

| 5.5  | An simple example of using the design flow                                                                                                                     | 82  |

| 6.1  | Custom operator based high-level synthesis flow                                                                                                                | 83  |

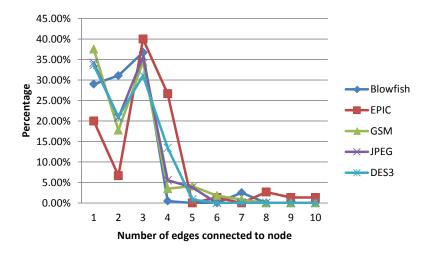

| 6.2  | The shape profile of the benchmarks $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                | 85  |

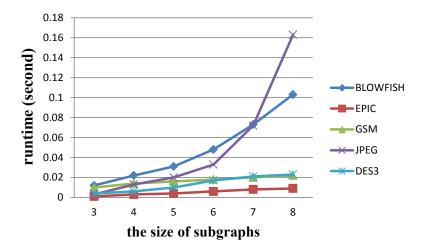

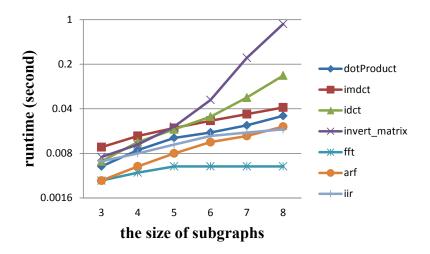

| 6.3  | The runtime performance of the size constrained enumeration algorithm when enumerating connected subgraphs                                                     | 86  |

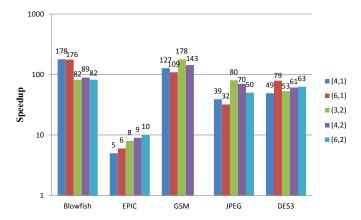

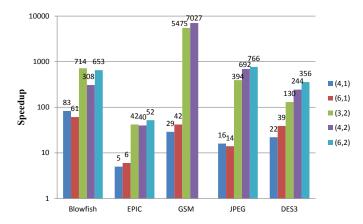

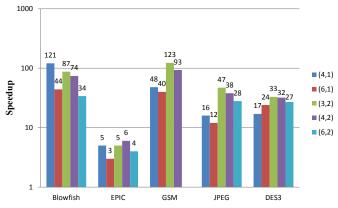

| 6.4  | Runtime speedup achieved by the algorithm $b$ over the algorithm $a$ for enumerating all feasible subgraphs $\dots \dots \dots \dots \dots \dots \dots$        | 88  |

| 6.5  | Runtime speedup achieved by the algorithm $c$ over the algorithm $a$ for enumerating all feasible subgraphs $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 90  |

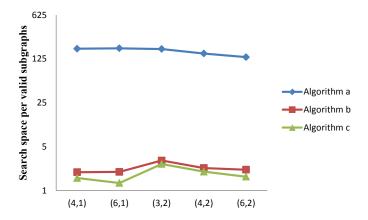

| 6.6  | Search space per feasible subgraph for the benchmark DES3 under different I/O constraints                                                                      | 90  |

| 6.7  | Runtime speedup achieved by the algorithm $b$ over the algorithm $a$ for enumerating connected subgraphs                                                       | 91  |

| 6.8  | Runtime speedup achieved by the algorithm $c$ over the algorithm $a$ for enumerating connected subgraphs                                                       | 91  |

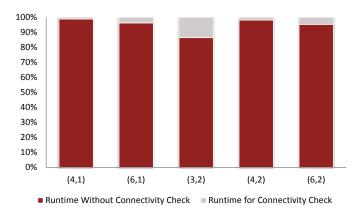

| 6.9  | Runtime for connectivity check and runtime for subgraph enumeration for the benchmark DES3 using the algorithm $a$                                             | 92  |

| 6.10 | Runtime for connectivity check and runtime for subgraph enumeration for the benchmark DES3 using the algorithm $c$                                             | 92  |

| 6.11 | Code size reduction rate achieved by the three selection approaches (maximum size of subgraphs is 6)                                                           | 98  |

| 6.12 | Code size reduction rate achieved by the MS algorithm and the Genetic algorithm (maximum size of subgraphs is 6)                                               | 100 |

| 6.13 | Runtime of the MS algorithm and the Genetic algorithm (maximum size of subgraphs is 6)                                                                         | 101 |

| A.1  | The runtime performance of the subgraph enumeration step under size constraint (connected subgraphs)                                                           | 109 |

# List of Tables

| 0.1 | rithms                                                                                                                                                                                                                           | 85  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.2 | Number of connected subgraphs and patterns under the size constraint $ . $ .                                                                                                                                                     | 87  |

| 6.3 | Comparison of the subgraph enumeration algorithms - all feasible subgraphs (a: the algorithm proposed in [Pozzi 2006], b: our algorithm presented in section 3.3, c: our algorithm based on topology presented in section 3.4) . | 89  |

| 6.4 | Comparison of the subgraph enumeration algorithms - connected subgraphs (a: the algorithm proposed in [Pozzi 2006], b: our algorithm presented in section 3.3, c: our algorithm based on topology presented in section 3.4) .    | 93  |

| 6.5 | Characteristics of the benchmarks for the evaluation of selection results $$ .                                                                                                                                                   | 95  |

| 6.6 | Area Reduction and Performance Improvement with Connected Subgraphs (maximum size of subgraphs is 6)                                                                                                                             | 96  |

| 6.7 | Area Reduction and Performance Improvement with Connected Subgraphs under I/O Constraints $(6/2)$                                                                                                                                | 97  |

| 6.8 | Area Reduction and Performance Improvement with All Feasible Subgraphs under I/O Constraints $(6/2)$                                                                                                                             | 98  |

| 6.9 | A set of parameters chosen for the genetic algorithm                                                                                                                                                                             | 100 |

# List of Acronyms

## Acronyms

| ALAP    | As Late As Possible                             |  |  |

|---------|-------------------------------------------------|--|--|

| ALU     | Arithmetic Logic Unit                           |  |  |

| ASAP    | As Soon As Possible                             |  |  |

| ASIC    | Application-Specific Integrated Circuit         |  |  |

| ASIP    | Application-Specific Instruction Set Processor  |  |  |

| CDFG    | Control Data Flow Graph                         |  |  |

| CSE     | Common Sub-expression Elimination               |  |  |

| DAG     | Directed Acyclic Graph                          |  |  |

| DFG     | Data Flow Graph                                 |  |  |

| EDA     | Electronic Design Automation                    |  |  |

| FPGA    | Field-Programmable Gate Array                   |  |  |

| FSM     | Finite State Machine                            |  |  |

| GA      | Genetic Algorithm                               |  |  |

| GPP     | General Purpose Processor                       |  |  |

| HLS     | High-Level Synthesis                            |  |  |

| HTG     | Hierarchical Task Graph                         |  |  |

| ILP     | Integer Linear Programming                      |  |  |

| IR      | Intermediate Representation                     |  |  |

| MAC     | Multiply-Accumulate                             |  |  |

| MAXMIMO | ${\bf Maximum\ Multiple-Input-Multiple-Output}$ |  |  |

| MIMO    | Multiple-Input-Multiple-Output                  |  |  |

| MISO    | Multiple-Input-Single-Output                    |  |  |

| RTL     | Register-Transfer Level                         |  |  |

| SCP     | Set Covering Problem                            |  |  |

# List of Notations

## Notations

| IN(G,M)                                  | The Number of Inputs of a Subgraph      |

|------------------------------------------|-----------------------------------------|

| PerInput(G,M)                            | Permanent Inputs of a Subgraph          |

| OUT(G,M)                                 | The Number of Outputs of a Subgraph     |

| $PerOutput(G,\!M)$                       | Permanent Outputs of a Subgraph         |

| $IN_{max}$                               | Maximal Number of Inputs                |

| $OUT_{max}$                              | Maximal Number of Outputs               |

| Succ(G,n)                                | All the Successors of a Node            |

| Succ(G,M)                                | All the Successors of a Subgraph        |

| $\operatorname{ISucc}(G,n)$              | Immediate Successors of a Node          |

| ISucc(G,M)                               | Immediate Successors of a Subgraph      |

| Pred(G,n)                                | All the Predecessors of a Node          |

| Pred(G,M)                                | All the Predecessors of a Subgraph      |

| $\mathrm{IPred}(G,\!n)$                  | Immediate Predecessors of a Node        |

| IPred(G,M)                               | Immediate Predecessors of a Subgraph    |

| Btw(n, M)                                | The Nodes between a Node and a Subgraph |

| $\operatorname{Disc}(G,n)$               | Disconnected Nodes of a Node            |

| $\mathrm{Disc}(\mathrm{G},\!\mathrm{M})$ | Disconnected Nodes of a Subgraph        |

## Introduction

The rapid growing size and complexity of the applications to be implemented has led to performing designing at a higher-level abstraction. Compared to register-transfer level (RTL) synthesis, high-level synthesis (HLS) may achieve better productivity. In recent years, it is increasingly common to see custom operators, which make it possible to reduce code size, improve performance and reduce area, appear in various fields of circuit design. In this thesis, we develop a custom operator based high-level synthesis flow in benefit of the advantages of custom operators.

First of all, we give a brief introduction on high-level synthesis. Then, we discuss the advantages achieved by using custom operators. Next, we present the proposed custom operator based high-level synthesis flow. Finally, the contributions and organizations of this thesis are presented.

## 1.1 High-Level Synthesis

In the past decades, the applications to be implemented are becoming more and more complex. As raising the design abstraction level allows to reduce the design time substantially, the use of high-level synthesis [McFarland 1988] has been increased in the electronic design automation (EDA) community. Many commercial high-level synthesis tools have been proposed by several vendors. Autopilot[Zhang 2008, Cong 2006], CatapultC [Bollaert 2008], CtoS [Bailey 2010, Cadence], Cynthesizer [Meredith 2008], Synphony-C [Synopsys, Kathail 2002] and CyberWorkbench [Kazutoshi 2008, Wakabayashi 2006] are only some of the existing high-level synthesis tools. In addition, plenty of academic high-level synthesis tools have also been introduced in recent years (e.g., Legup[Canis 2011], GAUT[Coussy 2008], Trident[Tripp 2007, Tri 2005] and

### SPARK[Gupta 2003, Gupta 2004]).

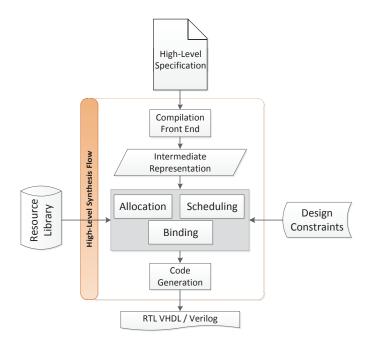

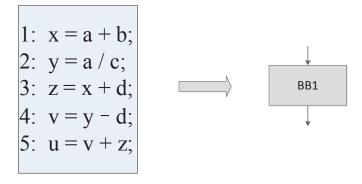

The high-level synthesis, sometimes referred to behavior synthesis, is an automated design process of transforming untimed or partially timed specifications (e.g., C, C++ or SystemC) to low-level cycle-accurate register-transfer level specifications that implements the specified behavior while satisfying the design constraints. Fig. 1.1 shows an overview of high synthesis flow. The HLS tools accept high-level specifications as inputs. In general, most of current commercial HLS tools take C-based specification as design entry [Cong 2011a]. We can also find some HLS tools using other input languages such as BlueSpec [BlueSpec ], Esterel[Edwards 2002] and MATLAB[Malay 2001]. In addition to the high-level specifications, the resource library containing the detail information of hardware components and specific design constraints are provided to HLS tool at the beginning [Coussy 2009]. With the provided inputs, the HLS tool carries out the following tasks and produces a hardware description language that implements the specification:

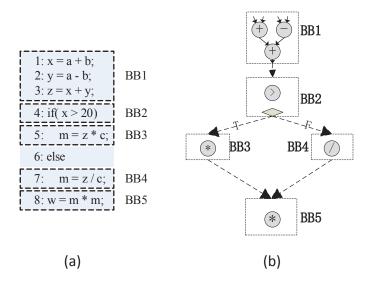

- Compilation Front End: The specifications are parsed into intermediate representations. Several preliminary transformations or code optimizations [Muchnick 1997, Gupta 2004] such as dead-code elimination, false data dependency elimination, branch balancing, constant propagation, loop transformations, speculative code motion and common subexpression elimination are performed at the earlier stage of this step [Coussy 2009]. After the optimizations, the specifications are transformed to an appropriate intermediate representation. In order to capture both the data dependencies and control dependencies between the operations in the specifications, different intermediate representations (IR) that retain all the information presented in the input specification are used. Control data flow graph (CDFG) is considered as one of the most popular IR. The CDFG is a directed graph in which a node can be either an operation or a basic block. The directed edges in a CDFG represent the transfer of a value or control from one node to another. Inside each node, a data flow graph is used to capture the data dependencies between operations. In addition, the data dependencies between basic blocks can be captured by using the hierarchical task graphs (HTGs) representation proposed in [Gupta 2003, Gupta 2004].

- Allocation: This process determines the types of hardware components and the number for each type to be included in the hardware implementation. The hardware components refer to the function units (such as adders, multipliers) for operations, the registers for storing values, the buses and the multiplexors for interconnections between

operators.

- Scheduling: Scheduling is the process of assigning operations to clock cycles or time steps so that the design constraints are satisfied. Each operation is scheduled according to the data dependencies and control dependencies between the operations. There are several commonly preferred scheduling algorithms: as soon as possible (ASAP) scheduling, as late as possible (ALSP) scheduling, list scheduling, force directed scheduling and integer linear programming formulation. The scheduling and resource allocation are usually interdependent. Scheduling is performed with respect to the resources constraints that are assigned in the allocation step, while the resource allocation can be improved if the operations that can be executed parallel are known in advance (these information can be obtained from scheduling) [McFarland 1988].

- Binding: The binding process assigns the function units to perform operations, registers to store values that pass across cycles and buses/multiplexors to realize the data/control transfers. The binding algorithm decides which function unit should be used to perform a specific operation when there are more than one functional units capable of executing the operation. The operations and the values with mutually exclusive lifetime can share the same hardware component.

- Code Transformation: At the end, the code transformation produces a RTL implementation including a data path and a control unit. The data path refers to function units such as adders, multipliers and arithmetic logic units (ALUs), storage units such as memories and registers, and connectivity components such as buses and multiplexors. The control unit is a finite state machine (FSM) that generates control signals and controls the data flow into the data logic path.

## 1.2 Custom Operators

Nowadays, it is common to find custom operators in various fields of circuit design. As an example, custom operator is a vital component to make trade-offs between flexibility and efficiency in extensible processors [Gonzalez 2000]. A custom operator is composed of a cluster of basic operations (e.g., primitive arithmetic operations such as add, subtract and multiply). A custom function unit is the hardwired implementation of a custom operator.

Figure 1.1: High-level synthesis flow

The first benefit brought by using custom operators is the significant compactness of the source code. Generally, the custom operator encapsulates several basic operations and compacts them into one complex operator. Thus, the size of the source code can be reduced and the granularity level of the source code is increased. Consequently, the high-level synthesis tools may give solutions in a shorter time with the compacted code.

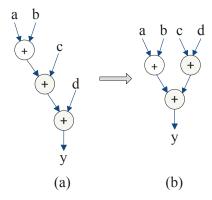

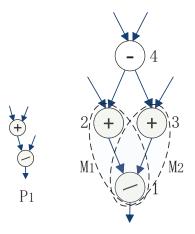

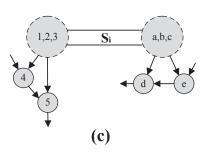

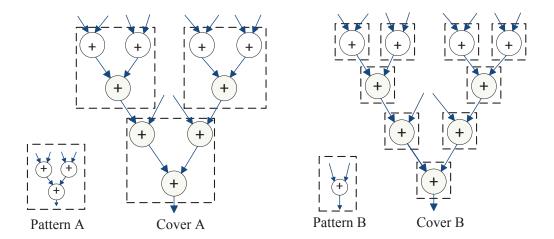

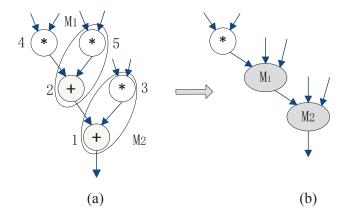

With custom operators, considerable performance improvement can be achieved. The custom operators improve performance through four possible ways. First, the basic operations inside the custom operator are automatically chained according to the data dependencies (operation chaining). Second, the basic operations without data dependencies between each other may be parallelized (parallelization). Third, some optimization techniques can be applied to reduce the critical path of custom operators (Fig. 1.2 shows an example of reducing the critical path of a selected custom operator. Let assume each addition takes 1 clock cycle to execute. The custom operator in Fig. 1.2 (a) requires 3 clock cycles to execute, while the custom operator with reduced critical path in Fig. 1.2 (b) only takes 2 clock cycles to execute. The critical path is reduced by imposing parallelism between the two sequential additions). Finally, the dedicated hardware implementation of a custom operator is usually faster than the basic operators (e.g., the latency of a

Figure 1.2: (a) A selected custom operator (b) A custom operator with reduced critical path

multiply-accumulate (MAC) is less than the sum of the latency of a multiplier and the latency of an adder [Yadav 1999]).

Moreover, the custom operators can reduce the area through the following two aspects. First, in general, the internal data flows of a custom operator are free of multiplexors [Cong 2008, Cong 2010, Cong 2011b]. Second, the dedicated hardware implementation of a custom operator leads to less area cost (e.g., the area of a MAC is less than the sum of the area of a multiplier and the area of an adder [Yadav 1999]). It is noteworthy that, using custom operators may lead to less resource sharing: more basic operations are found in a graph compared to custom operations.

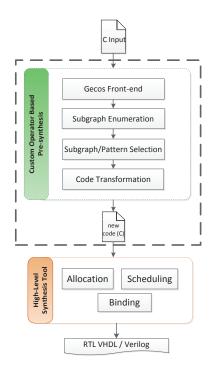

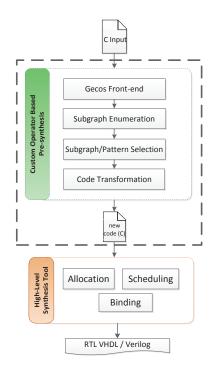

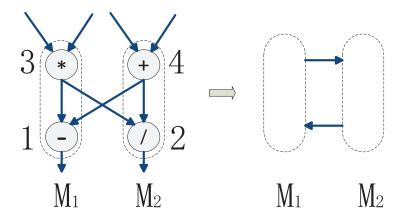

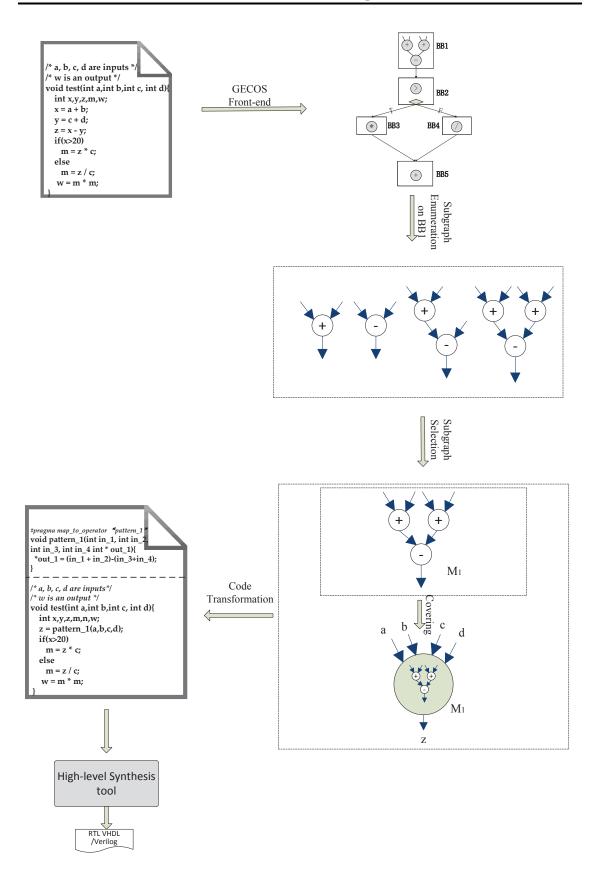

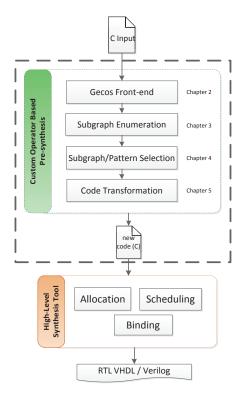

## 1.3 An Overview of the Design Flow

With the benefits of using custom operators in circuit designs, we propose an automated custom operator based pre-synthesis design flow to transform the source code by incorporating custom operators, such that better synthesis results can be obtained with high-level synthesis tools. Fig. 1.3 illustrates our proposed framework of the custom operator based pre-synthesis design flow. Unlike the previous frameworks in the literature that require to modify the scheduling and binding algorithms of high-level synthesis tools [Cong 2008, Cong 2010, Cong 2011b], our design flow is fully independent of high-level synthesis tools. The design flow can be adapted to many commercial high-level synthesis tools.

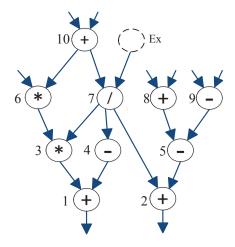

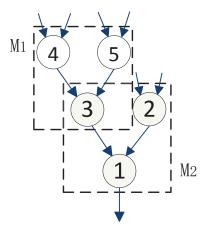

The design flow consists of four major steps. The starting point is the high-level

Figure 1.3: Custom operator Identification for high-level synthesis

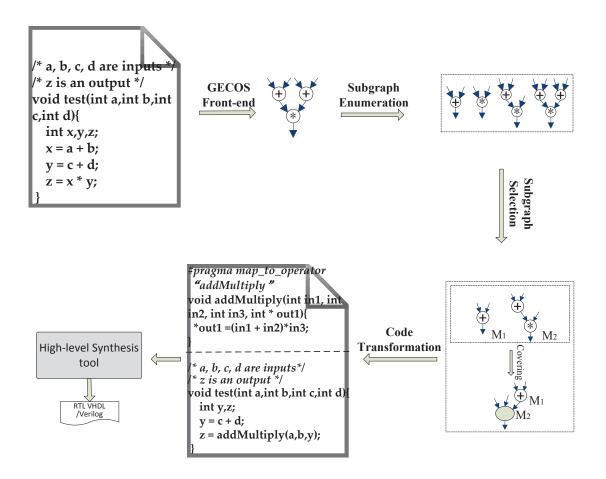

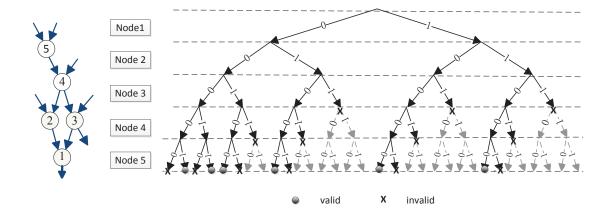

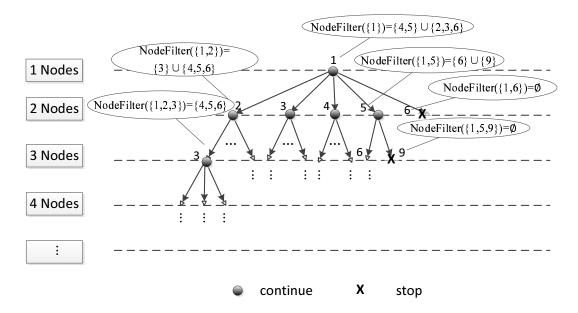

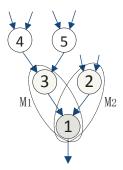

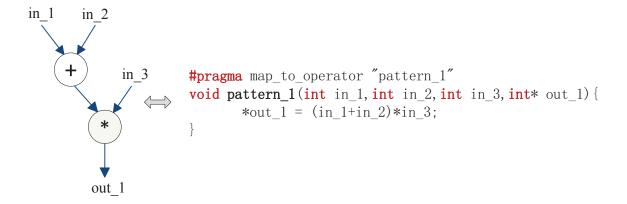

source code (C language). In the first step, the source code is translated to a control data flow graph (CDFG) using an open source compiler GECOS [GECOS]. A CDFG is a graph that represents the data dependencies between a number of basic blocks. Next, the potential subgraphs are identified by the subgraph enumeration algorithm from the DFG corresponding to a basic block of the CDFG. Then a subset of the identified subgraphs are selected according to different strategies (minimum number of custom operators, minimum code size etc.). Finally, the original source code is transformed to a new source code by incorporating the selected subgraphs (the selected subgraphs will be implemented as custom operators). The new source code with custom operators is then provided as input for high-level synthesis tool. More straightforwardly, a summary of our approach with a simple example to custom operator based high-level synthesis design flow is shown in Fig. 1.4. In the figure, a piece of C code is provided as input. It is transformed to a DFG by GECOS. All the subgraphs (connected subgraphs) in the DFG are enumerated. After subgraph enumeration, two subgraphs are selected (we assume  $M_1$  and  $M_2$  are selected). Based on the graph with selected subgraphs, a piece of new source code is generated. The new source code is then provided as input to the high-level synthesis tool.

Figure 1.4: Summary of our approach to custom operator based high-level synthesis flow

#### 1.4 Contributions of this Thesis

In this thesis, we develop a new custom operator (pattern) based high-level synthesis design flow. The key issues involved in the design flow are: automatic enumeration and selection of custom operators from a given high-level application and regeneration of source code incorporating the selected custom operators. This thesis makes the following contributions:

• Subgraph Enumeration: As the number of subgraphs in a DFG is exponential to the number of nodes of the DFG, subgraph enumeration is a computationally difficult problem. For example, in a DFG from a real world benchmark GSM that has 490 nodes, the number of subgraphs can be 341641 when input and output constraints (I/O constraints) are 4 and 2. When the I/O constraints are relaxed to 6/2, the number of subgraphs is augmented to 1454539. We present three scalable subgraph enumeration algorithms which can enumer-

ate all the subgraphs very efficiently under various design constraints. To enumerate all feasible subgraphs under size constraint, we propose a new algorithm that avoids multiple identifications of any subgraph. Based on the proposed size constrained subgraph enumeration algorithm, an extended algorithm that aims to enumerate all feasible subgraphs or only connected subgraphs is then presented. In addition, we present a polynomial-time algorithm that improves the previously proposed well-known algorithm [Pozzi 2006] for enumerating all feasible subgraphs including disjoint subgraphs and connected subgraphs. Experiments show that our algorithms can achieve orders of magnitude speedup over the well-known algorithm [Pozzi 2006].

- Subgraph Selection: Selecting a subset from the set of subgraphs generated by subgraph enumeration is also time costly, so our goal is to propose algorithms that are time efficient. Three different heuristic subgraph selection approaches targeting to different objectives are depicted and a complete comparison of them is shown in experiments. Furthermore, we present an exact algorithm and a genetic algorithm for selecting minimal number of matches to cover the data-flow graph of given application program. The proposed genetic algorithm makes trade-off between the greedy approach and the exact approach. In other words, it makes trade-off between the run-time of selection and the quality of selection results.

- Code Transformation: we extend an existing graph isomorphism algorithm to quickly reject dissimilar graphs by using some characteristics of data-flow graph. Some specific problems involved in the graph isomorphism check and subgraph isomorphism are first exposed. To our knowledge, the aforementioned problems were never considered in previous literature. The corresponding solution for the exposed problems are provided in this thesis. Moreover, a brief introduction to the code representation for custom operator in the generated code is also given.

- The Design Flow: an automated and adaptable custom operator-based pre-synthesis design flow is presented; results for a set of benchmarks show that significant code size reduction, area reduction and speedup can be achieved by our proposed design flow.

### 1.5 Organization of this Thesis

The rest of the thesis is organized as follows. The thesis starts with a survey of related work (Chapter 2). In chapter 2, for the sake of clarity, the intermediate representation of code used in the design flow and some important definitions are introduced. As the design flow involves three major problems: subgraph enumeration, subgraph selection and graph isomorphism, we then review the three problems respectively.

In chapter 3, the problem formulation of the subgraph enumeration is depicted. Particularly, the proof that gives a tighter upper bound of valid subgraphs under input and output constraints is presented. To efficiently solve the problem under various design constraints, three enumeration algorithms are presented in detail.

We formally formulate the subgraph selection problem and present some algorithms for this problem in chapter 4: three heuristics targeting different objectives, an exact algorithm and a genetic algorithm that select the minimal number of matches resulting in the most compacting code size.

After that, an extended graph isomorphism algorithm used to check the functional equivalence between subgraphs is introduced in chapter 5. In the same chapter, some specific problems like non-commutative problem and symmetrical problem residing in the isomorphism check are discussed and corresponding solutions are also provided.

Chapter 6 evaluates the efficiency of the proposed algorithms and the quality of results of the whole design flow. Finally, conclusions and future works are presented in chapter 7.

## Related Work

In this chapter, to clarify, we first present the intermediate representation used in our design flow. As there are three major problems involved in the proposed design flow, we begin the survey from the subgraph enumeration problem, which enumerates all feasible subgraphs under various constraints. Then, we review the subgraph selection problem, which try to select a subset of most profitable subgraphs in terms of different motivations. Finally, we survey the graph isomorphism problem, which aims to find the functional equivalence between subgraphs. In the survey of related works, we mainly focus on the algorithms dedicated to hardware design.

## 2.1 Intermediate Representation

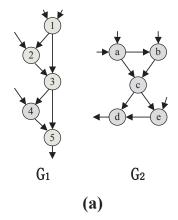

The behavioral specification to high-level synthesis is usually composed of a sequential list of statements. The statements could be operation expressions, conditional constructs and loop constructs. To capture the data-flow dependencies in the input description, data-flow graph is a good candidate for designers. As the data-flow graph only contains the explicit data dependencies, we could use control flow graph to capture the control flow through the input description. In order to capture the both information in design description, control data-flow graphs are a well known and good intermediate representation for high-level synthesis. In this section different intermediate representations for high-level synthesis are presented. The definition, semantics and an example of construction for DFG, CFG and CDFG are shown respectively.

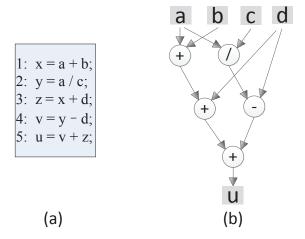

Figure 2.1: (a) Fragment of C code without condition or loop (b) Corresponding data flow graph

# 2.1.1 Data-Flow Graph

# 2.1.1.1 Definition

A data-flow graph (DFG) is a directed acyclic graph (DAG) which represents data dependencies between a number of operations. It is a graph G = (V, E), where the vertex set  $V = \{v_1, ..., v_n\}$  represents primitive operations and the edge set  $E = \{e_1, ..., e_m\} \in V \times V$  represents the data-flow dependencies.

#### 2.1.1.2 Semantics

A node receives data generated by its predecessor nodes and produces new data needed by its successors. The operation of the node is performed on the data of the incoming edges only when all the incoming data are ready. The resulting data is then put on the outgoing edges. Therefore, the execution order of the operations in the graph is thus constrained by the partial ordering of the nodes as defined by the directed edges. It is clear that data-flows through the graph and each time data encounters a node, an operation is performed on it.

Operation nodes can be primitive arithmetic operations, like +, -, \*, ++, or Boolean like >, <, or can be more complex custom operations. The timing constraints imposed by data dependencies can be denoted as follows: Let  $T = \{t_i; i = 0, 1, ..., n - 1\}$  be the execution start times of the operations and  $D = \{d_i; i = 0, 1, ..., n - 1\}$  be the execution

Figure 2.2: (a) Fragment of C code with condition (b) Corresponding data flow graph (with loss of consistency)

delays of each operations. Assume that an operation l reads the result of its predecessor k, then the operation l can start execution only after the predecessor k has finished execution. This can be expressed as:

$$t_l \ge t_k + d_k, \forall k, l : (v_k, v_l) \in E \tag{2.1}$$

#### 2.1.1.3 Examples

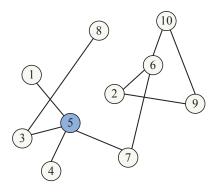

Any algorithmic behavioral description of a system consists of ordered operations. To demonstrate the data-flow graph construction, the fragment of C description in Fig.2.1(a) is used as an example. To simplify the construction, we use the segment of C code without condition or loop in it. The example of a data-flow graph for the fragment of C description is given in Fig.2.1(b). Operations in the data-flow graph are denoted by circular nodes with the operator sign within. The input nodes are represented by squares.

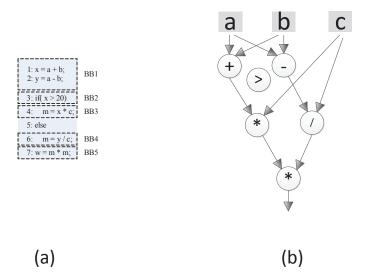

The segment of C code listed in Fig.2.2(a) has condition in it. The corresponding data flow graph for the above fragment of C description is given in Fig.2.2(b). Obviously, the control information is lost during the construction of data flow graph according to the definition of data flow graph. As shown in Fig.2.2(b), the node labeled with ">" has no input or output edge. Consequently, when we regenerate the new description code

from the incrementally refined DFG which has passed through various stages of a high-level synthesis system, the new generated description code is not functionally consistent with the original source code. Thus, to support conditional constructs, loops and procedure calls, we may use control flow graph directly, besides CFG. The authors [van Eijndhoven 1992] has proposed a new form of data flow graph which moves conditional constructs into the data flow graph.

# 2.1.2 Control-Flow Graph

#### 2.1.2.1 Definition

A control-flow graph represents the control dependencies among basic blocks (A basic block is a sequence of statements from the input description with no conditionals or loops between them). It is a graph G = (V,E), where  $V = \{v_1,...,v_n\}$  is the set of basic blocks which are treated as different sequences of statements in the design and  $E = \{e_1,...,e_m\} \in V \times V$  is the set of directed edges which represents the control flow between basic blocks.

### 2.1.2.2 Semantic

As we know, during the execution of program, each time the condition operation is executed, the control flow partitions into two control flows, one for the evaluation with value of true, the other for the evaluation value of false. As the program be executed continually, the control flows merge into a single control flow at the end of the conditional or loop construct [Gupta 2004]. Hence, in control flow graph, node can be identified as an operation node, branch node or merge node.

Operation node is a basic block which contains a sequence of operations and has one incoming edge and one outgoing edge, having no conditional check in them and having only a default output true path.

**Branch node** has two or more outgoing edges and one incoming edge, signifying the point at which a condition causes the control flow to branch into multiple control paths. Obviously, it also determines the control flow passes through which outgoing edges.

Merge node that has two or more incoming edges and one outgoing edge is opposite

Figure 2.3: C code without condition or loop and its corresponding CFG

to the branch node. In general, branch and merge nodes are used to model algorithmic constructs like if...then...else, case, and loop constructs like while...do, for...do. A feedback edge between the branch and merge nodes can represent the loop construct [de Jong 1991]. The last basic block in the design, which does not have any output control flow, is called as end node. The first basic block in the design, which does not have any input control flow, is called as first node [Gupta 2004].

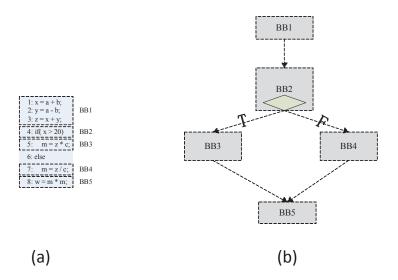

### 2.1.2.3 Example

As shown in Fig.2.3, the sequential operations in the fragment C code without condition or loop are aggregated into one basic block that represents these sequential operations. To understand more about CFG, we use the fragment of C code with condition 2.4(a) to construct the CFG. Fig.2.4(b) shows the control flow graph of the source code depicted in Fig.2.4(a). Each basic block aggregates a sequence of operations in the source code with no control flow between them (shown by shaded boxes in Fig. 2.4(a)). The arrow between basic blocks denotes the control flow as shown in the corresponding control flow graph in Fig.2.4 (b). The basic blocks are labeled from  $BB_1$  to  $BB_5$ . A diamond represents a Boolean conditional check or a fork in control flow with a true path and a false path.

#### 2.1.3 Control Data-Flow Graph

Data flow graph and control flow graph captures only explicit data dependencies and dataflow in the input description respectively. To represent the both information in the input description, we use control data-flow graphs. CDFG has been considered as one of the

Figure 2.4: (a) Fragment of C code (b) Corresponding control flow graph

most popular intermediate representation for high level synthesis.

The control data-flow graph is a graph G = (V,E), where  $V = \{v_1, ..., v_n\}$  is the set of basic blocks which are composed of a list of statements and  $E = \{e_1, ..., e_m\} \in V \times V$  is the set of directed edges which represents the control flow between basic blocks. Inside each basic block, a data-flow graph is used to represent the data-flow dependencies between the operations. A directed edge connecting the basic blocks represents a condition of statements such as if/case or loop constructs.

To model the CDFG construction, we use previous piece of c code (Fig.2.5(a)). The corresponding CDFG is shown in Figure 2.5(b). In the example, each basic block has a data-flow graph which represent a list of operations. The only entry of the data-flow graph is through the first operation and the only exit is the last instruction. The dash line represents the control flows between blocks. The real line denotes the data dependencies between operations.

# 2.2 Definitions

In this section, for the sake of clarity, we first give some important definitions that are utilized throughout the thesis. Then several notations that are used for calculation are introduced.

Formally, a match is defined as, for a directed acyclic graph G = (V, E), a sub-graph

2.2. Definitions 17

Figure 2.5: (a) Fragment of C code (b) Corresponding control data-flow graph

Figure 2.6: A pattern with its matches

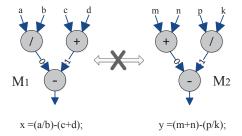

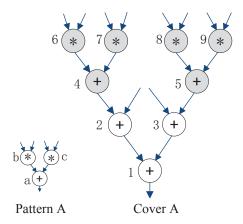

$M = (V_m, E_m)$  of graph G, where  $V_m \subseteq V$  and  $E_m \subseteq E^{-1}$ . A pattern or a template is an induced graph of isomorphic subgraphs. A pattern or a template is a graph representation of a custom operator. In other words, a match is an instance of a pattern or a template. As an example, in Fig. 2.6,  $P_1$  is a pattern and  $M_1$  and  $M_2$  are two matches of  $P_1$ . The term custom instruction is a code representation of a custom operator.

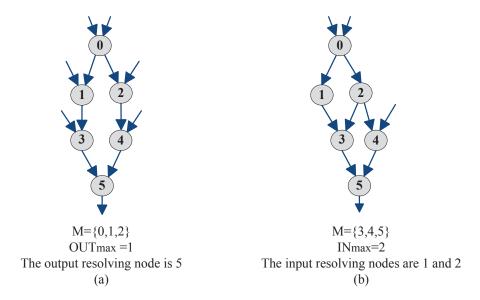

The input node set of a match (subgraph) M is denoted as IN(G, M). An input node is a node in G but not in M that has at least one edge entering the match M. Similarly, we use OUT(G, M) to denote the output node set of M. An output node is a node in M that has at least one edge exiting the match M and connecting to a node in G but not in

<sup>&</sup>lt;sup>1</sup>we will use the term match to represent subgraph alternatively in this thesis

M.

Given a DFG G(V,E) and a node u, some subsets can be defined according to their relationships with u.

- 1. Immediate predecessors of  $u: IPred(G, u) = \{v | v \in V, (v, u) \in E\}$ .

- 2. Immediate successors of  $u: ISucc(G, u) = \{v | v \in V, (u, v) \in E\}$ .

- 3. All predecessors of  $u: Pred(G, u) = \{v \in Pred(G, v) | v \in IPred(G, u)\}.$

- 4. All successors of  $u: Succ(G, u) = \{v \in Succ(G, v) | v \in ISucc(G, u)\}.$

- 5. Disconnected nodes of u: Disc(G, u) = G (Pred(G, u) Succ(G, u) u).

Similarly, given a graph G(V,E) and a subgraph (match)  $M \subseteq G$ , some subsets can also be defined according to their relationships with M.

- 1. Immediate predecessors of the subgraph  $M: IPred(G, M) = \bigcup_{u \in M} IPred(G, u) M$ .

- 2. Immediate successors of the subgraph M:  $ISucc(G, M) = \bigcup_{u \in M} ISucc(G, u) M$ .

- 3. All predecessors of the subgraph  $M: Pred(G, M) = \bigcup_{u \in M} Pred(G, u) M$ .

- 4. All successors of the subgraph  $M: Succ(G, M) = \bigcup_{u \in M} Succ(G, u) M$ .

- 5. Disconnected nodes of the subgraph M:  $Disc(G, M) = \{u | u \in V, \forall v \in M \text{ , there is neither a path from } u \text{ to } v \text{ or from } v \text{ to } u\}.$

# 2.3 Related Work on Subgraph Enumeration

As the key issues involved in our design flow are subgraph enumeration, subgraph selection and code transformation (see Fig. 2.7), we present the related works for subgraph enumeration, subgraph selection and graph isomorphism (graph isomorphism algorithm is used during code transformation to identify the functionally equivalent subgraphs) respectively. A lot of related researches on subgraph enumeration, subgraph selection and graph isomorphism have been done in recent years. The survey is restricted to algorithms that can take into account constraints related to hardware design. In this section, we start

Figure 2.7: Custom operator based high-level synthesis flow

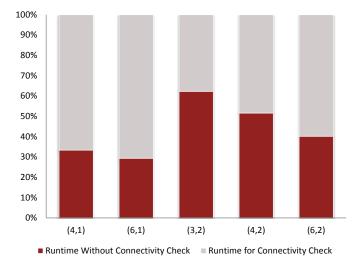

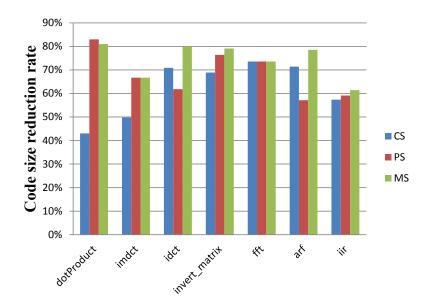

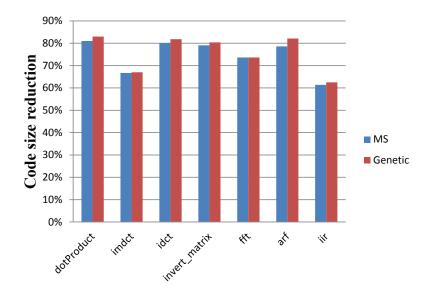

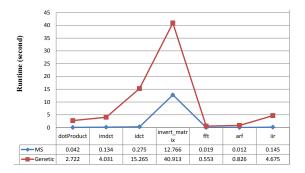

our review from subgraph enumeration and then discuss subgraph selection and graph isomorphism in the following sections.