# Transport properties and low-frequency noise in low-dimensional structures

Do Young Jang

#### ▶ To cite this version:

Do Young Jang. Transport properties and low-frequency noise in low-dimensional structures. Autre. Université de Grenoble; 239 - Korea University, 2011. Français. NNT: 2011GRENT096. tel-00767284

#### HAL Id: tel-00767284 https://theses.hal.science/tel-00767284

Submitted on 19 Dec 2012

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### UNIVERSITÉ DE GRENOBLE

#### **THÈSE**

Pour obtenir le grade de

#### DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Micro et Nano Électronique

Arrêté ministériel : 7 août 2006

Présentée par

#### **Do Young JANG**

Thèse dirigée par Laurent MONTÈS et Gérard GHIBAUDO

préparée au sein du Laboratoire IMEP-LAHC dans l'École Doctorale EEATS

# Propriétés de transport et de bruit à basse fréquence dans les structures à faible dimensionnalité

Thèse soutenue publiquement le 5 décembre 2011 devant le jury composé de :

Mme. Mireille MOUIS

DR CNRS Alpes-IMEP/INPG, Président

M. Jong-Tae PARK

Dr Incheon University, Rapporteur

M. Jongwan JUNG

Dr Sejong University, Rapporteur

M. Gyu Tae KIM

Dr Korea Univeristy, Co-directeur de thèse

M. Gérard GHIBAUDO

DR CNRS Alpes-IMEP/INPG, Co-directeur de thèse

M. Laurent MONTES

MCF INP Grenoble-IMEP, Directeur de thèse

# Transport properties and low-frequency noise in low-dimensional structures

| By | <b>Doyoung JANG</b>     |

|----|-------------------------|

|    | - J - 1 - 1 - 1 - 1 - 1 |

December 2011

International co-supervising program between Korea University and Grenoble INP

#### **Thesis Advisors:**

#### Gye Tae Kim

School of Electrical Engineering, Korea University, Seoul 136-701, Republic of Korea

#### Laurent Montès and Gérard Ghibaudo

IMEP-LAHC, Grenoble INP-MINATEC, 3 Parvis Louis Néel, 38016 Grenoble, France

### There's Plenty of Room at the Bottom.

Richard Feynman

... and still

#### **Contents**

| Abstra     | ct    | •••••••••••••••••••••••••••••••••••••••         | 7  |

|------------|-------|-------------------------------------------------|----|

| Chant      | or 1  | Introduction to low-dimensional structures      | 13 |

| -          |       |                                                 |    |

| 1.1<br>1.2 |       | Scaling overview                                |    |

|            |       | Top-down vs. Bottom-up approaches               |    |

| 1.3<br>1.4 |       | Electrical issues in low-dimensional structures |    |

| 1.5        |       | Outline of the thesis                           |    |

| Chapt      | er 2  | Electrical properties for FET structures        | 22 |

| 2.1        |       | Introduction                                    | 22 |

| 2.2        |       | Threshold voltage                               | 23 |

|            | 2.2.1 | Linear extrapolation method                     | 24 |

|            | 2.2.2 | Second derivative method                        | 25 |

|            | 2.2.3 | Y-function method                               | 26 |

| 2.3        |       | Carrier Mobility                                | 27 |

|            | 2.3.1 | Conductivity (or drift) carrier mobility        | 29 |

|            | 2.3.2 | Hall carrier mobility                           | 29 |

|            | 2.3.3 | MOSFET carrier mobility                         | 30 |

| 2.4        |       | Series and contact resistances                  | 32 |

| 2.5        |       | Subthreshold swing                              | 34 |

| 2.6        |       | Capacitance                                     | 35 |

| 2.7        |       | Summary                                         | 37 |

| Chapte     | er 3  | Low-frequency noise characterization            | 40 |

| 3.1        |       | Background: Definition and concepts             | 40 |

| 3.2        |       | Fundamental noise sources                       | 42 |

|            | 3.2.1 | Thermal noise                                   | 42 |

|            | 3.2.2 | Shot noise                                      | 43 |

|            | 3.2.3 | Generation-Recombination (g-r) noise            | 43 |

|            | 3.2.4 | Random-Telegraph-Signal noise                   | 44 |

|      | 3.2.5 | 1/ <i>f</i> noise                                                     | 45  |

|------|-------|-----------------------------------------------------------------------|-----|

| 3.3  | ;     | 1/f noise models for FET structures                                   | 47  |

|      | 3.3.1 | Hooge mobility fluctuation model                                      | 47  |

|      | 3.3.2 | Carrier number fluctuation model                                      | 48  |

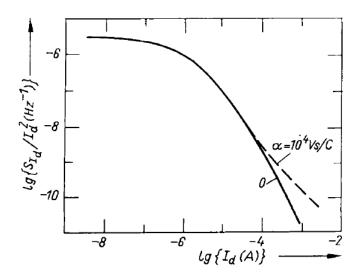

|      | 3.3.3 | Carrier number fluctuation with correlated mobility fluctuation model | 52  |

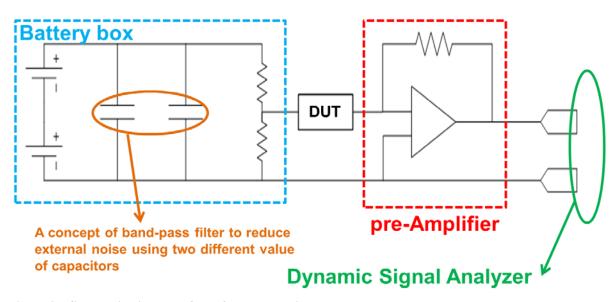

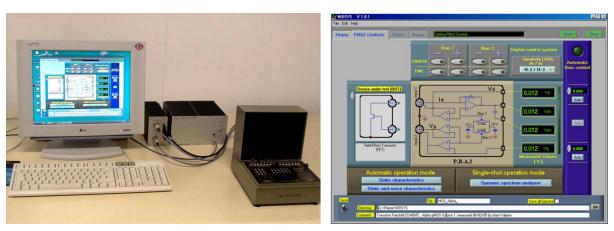

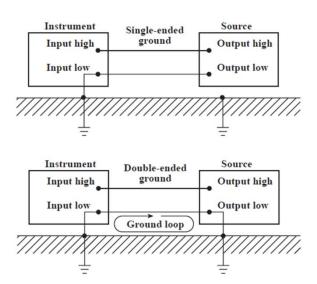

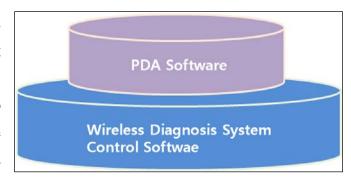

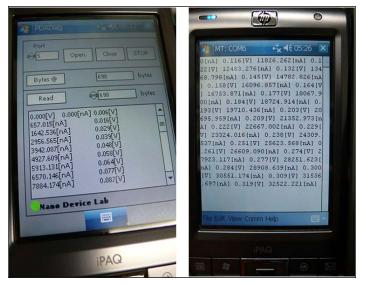

| 3.4  |       | Noise measurement system configuration                                | 53  |

| 3.5  | ,     | Summary                                                               | 56  |

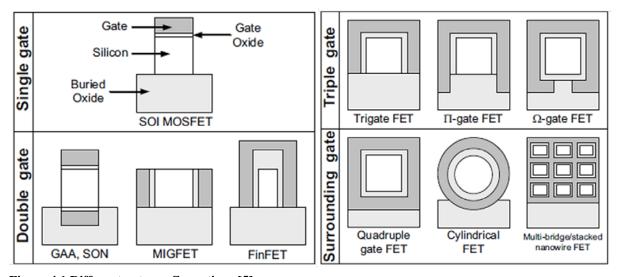

| Chap | ter 4 | Multi-Gate MOSFET                                                     | 61  |

| 4.1  |       | Background: From planar to 3-D structure                              | 61  |

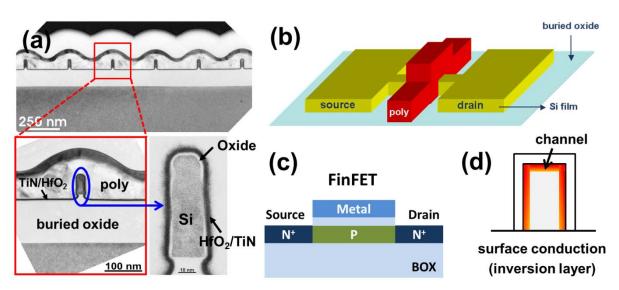

| 4.2  | ,     | FinFETs                                                               | 62  |

|      | 4.2.1 | Device structure                                                      | 62  |

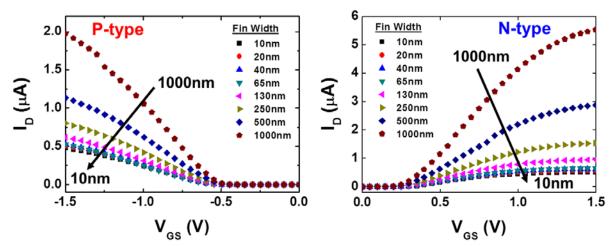

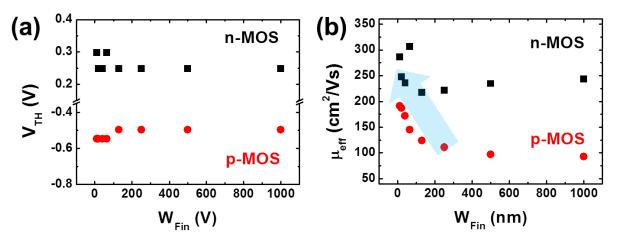

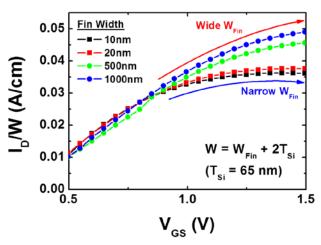

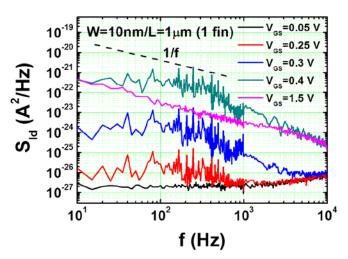

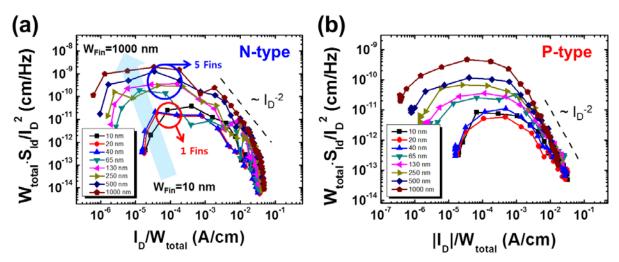

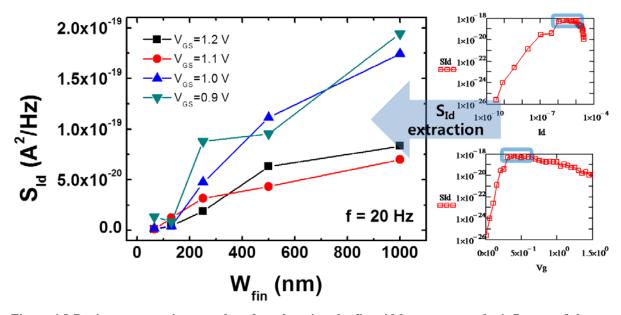

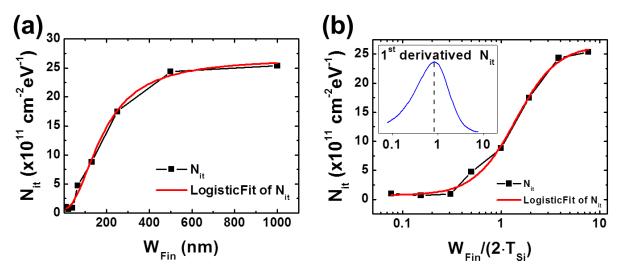

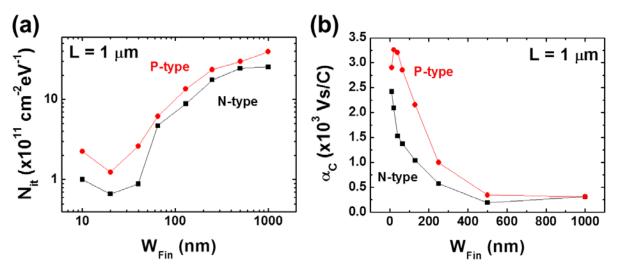

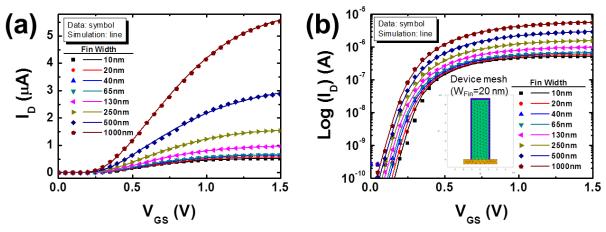

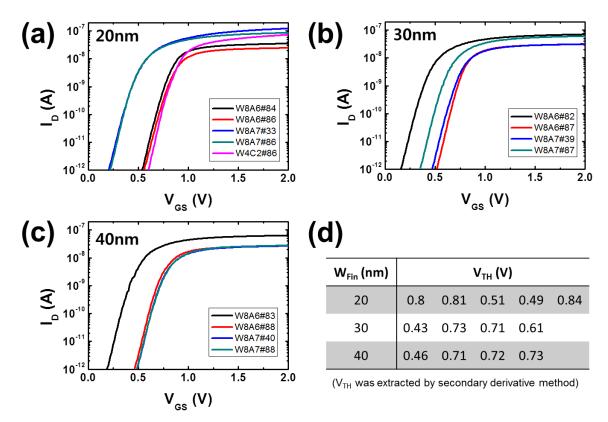

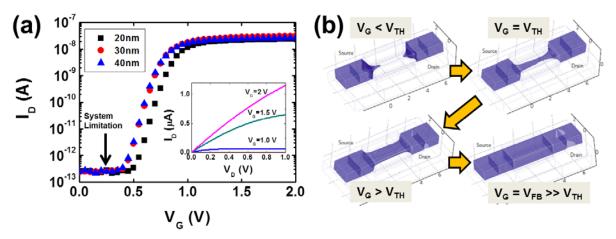

|      | 4.2.2 | Electrical characterization at the fin width variation                | 63  |

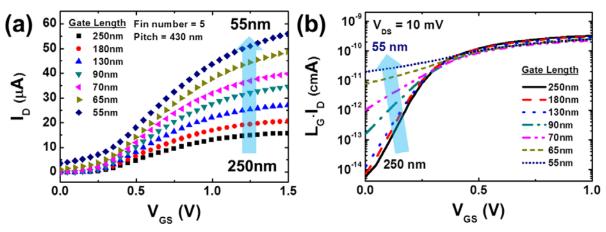

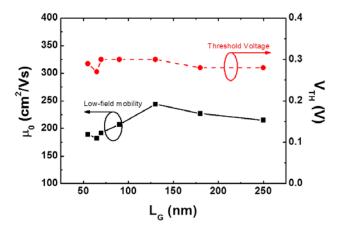

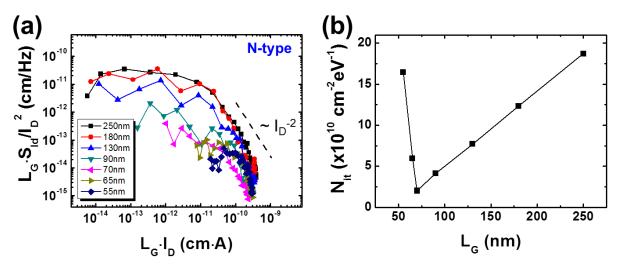

|      | 4.2.3 | Electrical characterization of the length dependence                  | 69  |

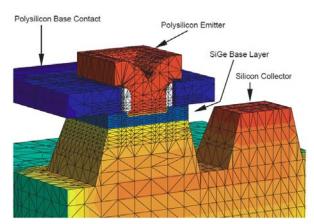

|      | 4.2.4 | Device simulation for the fin width dependence                        | 71  |

| 4.3  | ;     | Junctionless FETs                                                     | 74  |

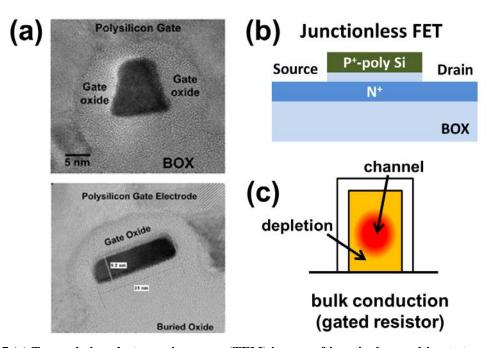

|      | 4.3.1 | Device structure                                                      | 74  |

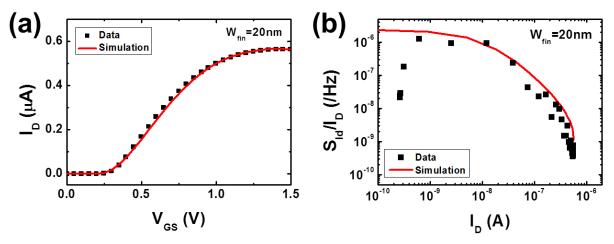

|      | 4.3.2 | DC characteristics                                                    | 75  |

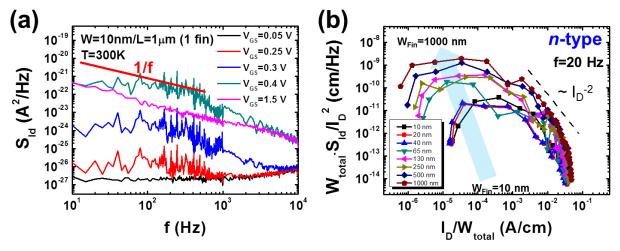

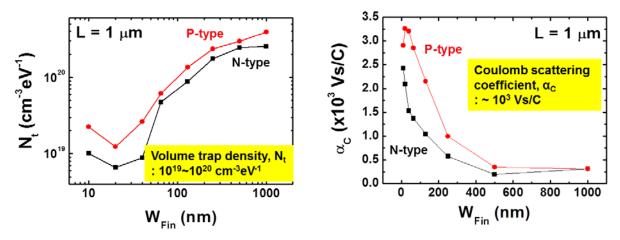

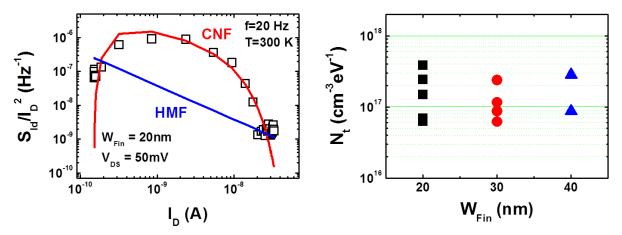

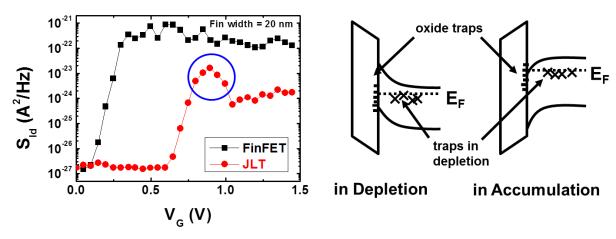

|      | 4.3.3 | LF noise characteristics                                              | 78  |

| 4.4  |       | Summary: Surface vs. Bulk conduction                                  | 83  |

| Chap | ter 5 | Nanowire and Nanotube                                                 | 86  |

| 5.1  |       | Background: Toward 1-D structures                                     | 86  |

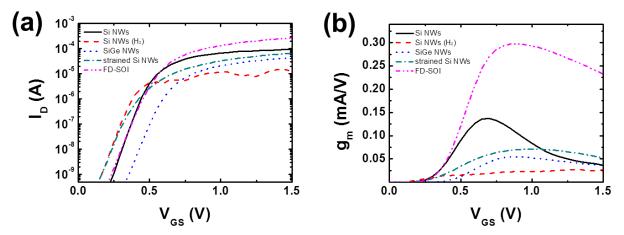

| 5.2  | ,     | 3-D stacked Si and SiGe nanowires                                     | 86  |

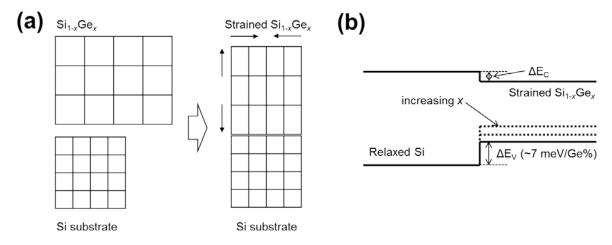

|      | 5.2.1 | Mobility enhancement – strain effect                                  | 87  |

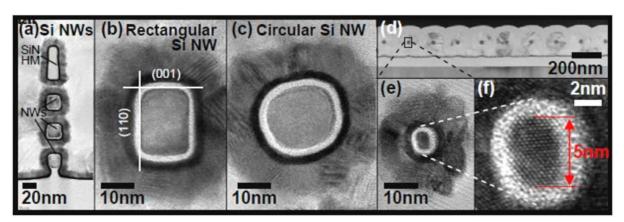

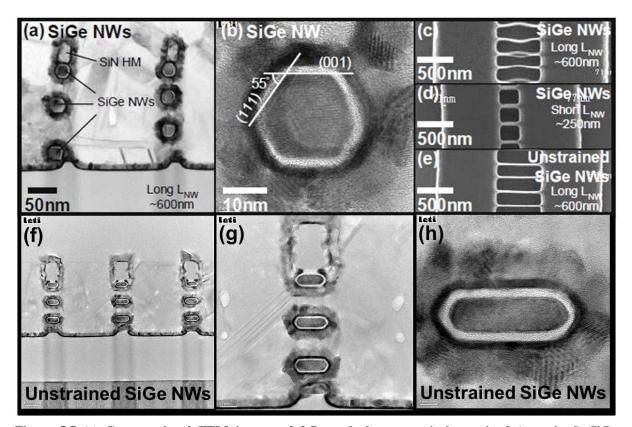

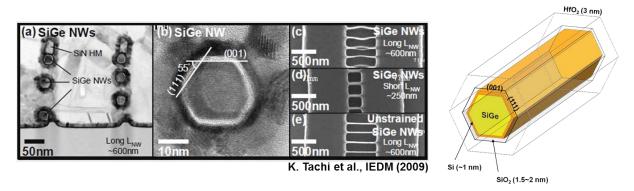

|      | 5.2.2 | Device structure                                                      | 89  |

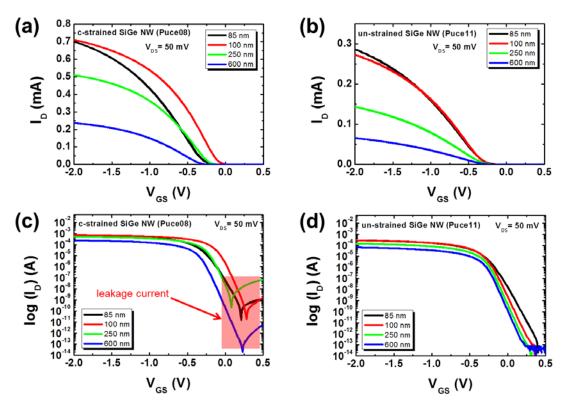

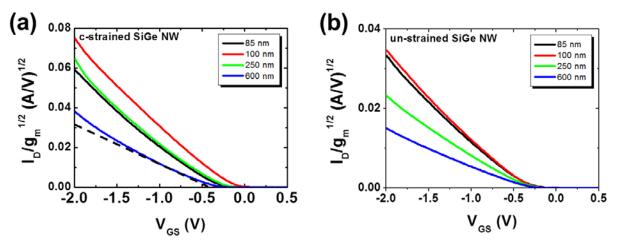

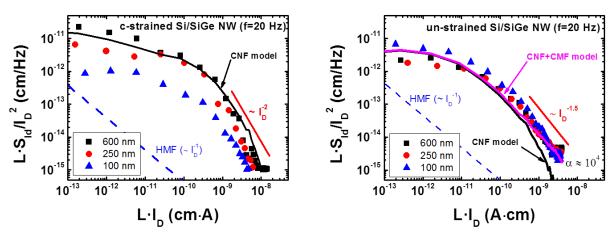

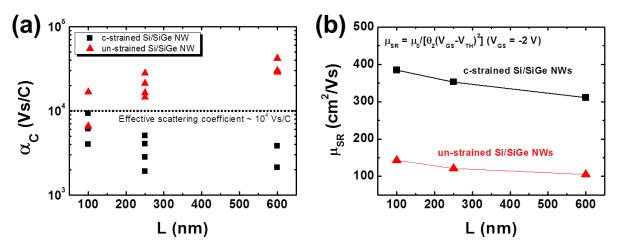

|      | 5.2.3 | C-strained and un-strained SiGe nanowire <i>p</i> -type FETs          | 91  |

|      | 5.2.4 | Noise comparison between Si and SiGe nanowire <i>n</i> -type FETs     | 101 |

| 5.3  | ;     | Nanotubes and nanowires based on Bottom-up approach                   | 103 |

|      | 5.3.1 | Metal-semiconductor junctions in multi-walled carbon nanotubes        | 103 |

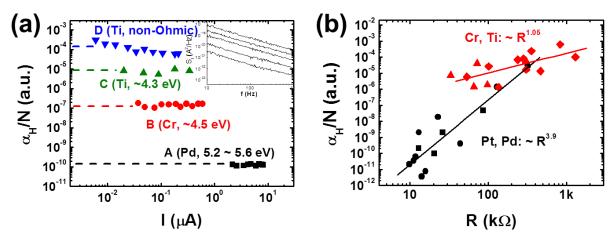

|      | 5.3.2 | Quality index for metal contacts – GaN nanowire                       | 106 |

| 5.4  |       | Summary: Impact of channel strain and metal contact                   | 110 |

|      |       |                                                                       |     |

| Chap | ter 6 | Graphene                                                              | 112 |

| 6.1                                    | Ph      | ysical Backgrounds                                     | 112 |  |

|----------------------------------------|---------|--------------------------------------------------------|-----|--|

|                                        | 6.1.1   | Electronic structure and carrier transport             | 112 |  |

|                                        | 6.1.2   | Research trends of graphene                            | 114 |  |

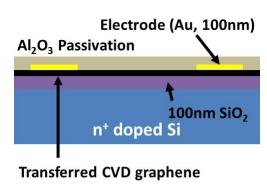

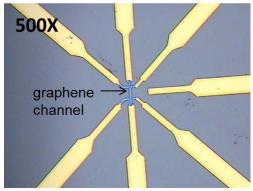

| 6.2                                    | De      | evice structure of graphene field effect transistors   | 116 |  |

| 6.3                                    | El      | ectrical properties and low-frequency noise in G-FETs  | 118 |  |

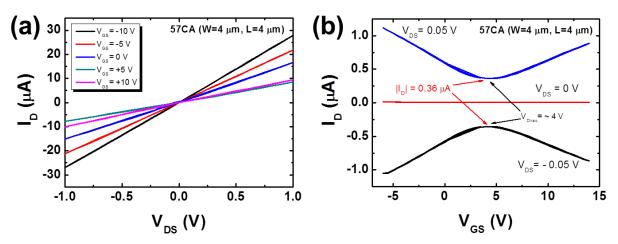

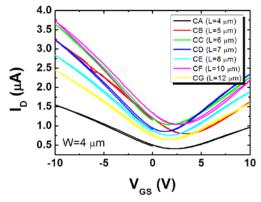

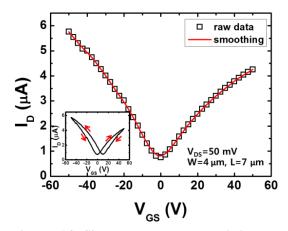

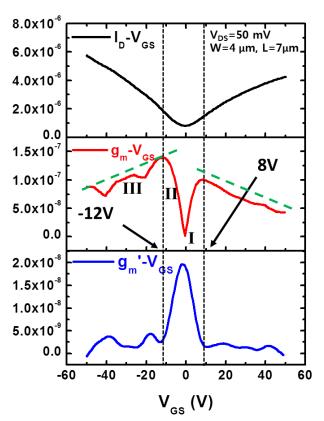

|                                        | 6.3.1   | Typical I-V characteristics & Length dependence        | 118 |  |

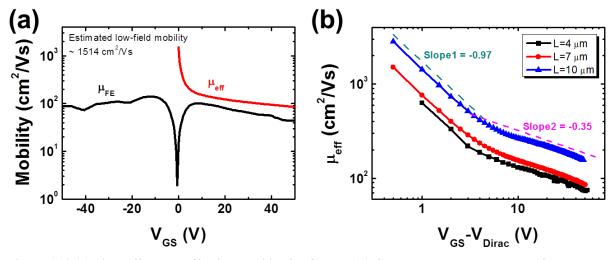

|                                        | 6.3.2   | Mobility scatterings on the SiO <sub>2</sub> substrate | 119 |  |

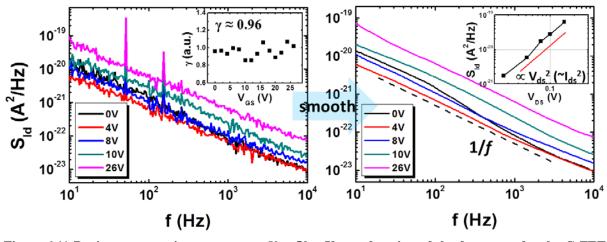

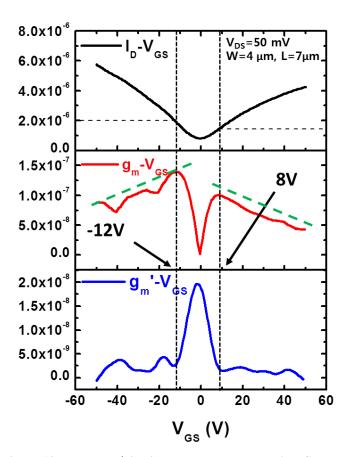

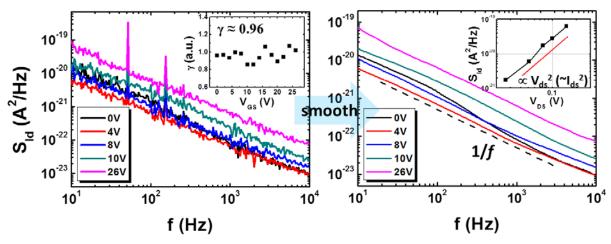

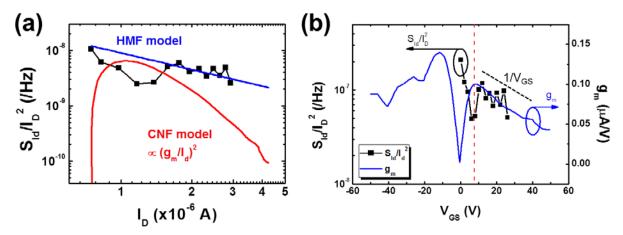

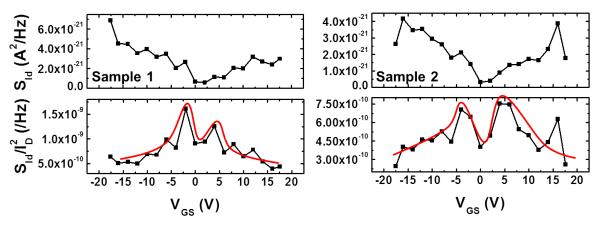

|                                        | 6.3.3   | LF noise characteristics                               | 122 |  |

| 6.4                                    | Su      | ımmary                                                 | 124 |  |

|                                        |         |                                                        |     |  |

| Appendix I – Physical constants        |         |                                                        |     |  |

| Appendix II – Glossary & abbreviations |         |                                                        |     |  |

| Apper                                  | ndix II | I – FlexPDE simulation script                          | 158 |  |

| Apper                                  | ndix IV | – Wireless diagnosis system for nano-bio sensors       | 160 |  |

| Résun                                  | né du t | ravail de thèse en Français                            | 165 |  |

| Ackno                                  | owledg  | ements                                                 | 186 |  |

| Public                                 | _       |                                                        |     |  |

#### **Abstract**

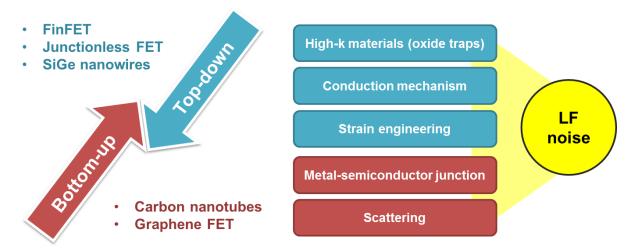

Recently, a keyword of complementary metal-oxide-semiconductor (CMOS) technology for the higher performance, lower power consumption, larger device integration, and cost reduction is "down-scaling" leading low-dimensional structures. For the various applications with low-dimensional structures, a great deal of research is being carried out to understand their electrical and physical properties. Particularly, low-frequency noise in conventional metal-oxide-semiconductor field-effect transistors (MOSFETs) has been well known to relate the signal fluctuations by the carrier trapping and de-trapping at the oxide-semiconductor interface. However, for low-dimensional structures, the noise properties are not sufficiently investigated. In this dissertation, the carrier transport and low-frequency noise properties in low-dimensional FET structures, which are fabricated by top-down or bottom-up approach, are investigated depending on high-k materials, conduction mechanism, strain engineering, metal-semiconductor junctions, and scatterings.

At the beginning of the dissertation, in chapter 1, the current issues of the device scaling in CMOS technology are reviewed and the low-dimensional structures are introduced with two representative approaches (i.e. top-down and bottom-up approaches). The electrical transport and low-frequency noise properties in low-dimensional structures are also discussed for the applications. In chapter 2, important device parameters of conventional FET structures such as threshold voltage, mobility, series resistance, subthreshold swing, and capacitance are defined and their practical extraction methods are presented. In chapter 3, the fundamental noise and representative low-frequency noise models for FET structures are introduced. One is the mobility fluctuation model (HMF) due to the carrier scattering and the other is the carrier number fluctuation model (CNF) considering the correlated mobility fluctuations (CMF) mainly affected by the trapping/release of charge carriers. In addition, the system configuration and helpful advices for the noise measurement are also discussed.

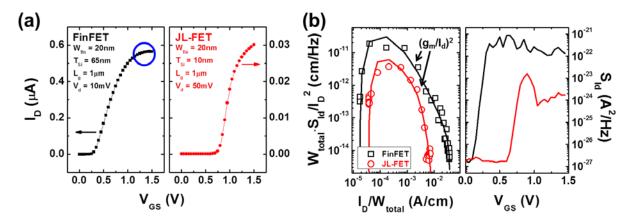

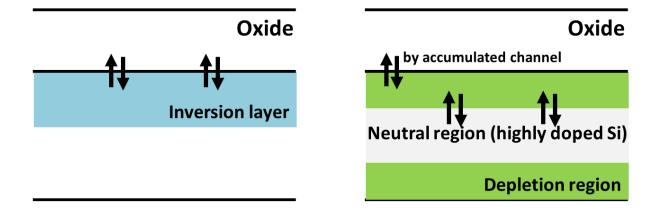

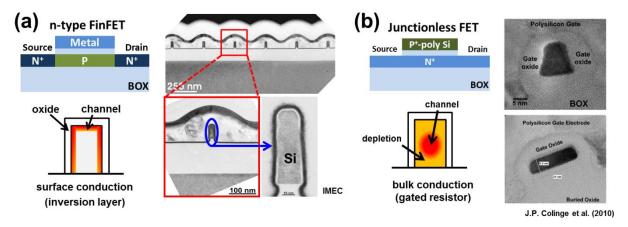

Experimental results of the transport properties and low-frequency noise in multi-gate FETs (FinFET and junctionless FET), Si and SiGe core-shell nanowire gate-all-around FETs, multi-walled carbon nanotube devices, and graphene FET are presented from chapter 4 to chapter 6. First, the multi-gate FET is a noticeable device recently introduced to reduce the short-channel effects. In this study, two kinds of multi-gate FETs are investigated: a FinFET is well-known as a multi-gate FET having a surface conduction by channel inversion whereas

a junctionless FET is operated by the highly doped channel i.e. bulk conduction. The bulk conduction is expected that the noise comes from the mobility fluctuations. But, interestingly, the low-frequency noise in junctionless FET is also explained by the carrier number fluctuation model same as the FinFET. The noise origin is estimated to have different mechanisms. For the FinFET, it is due to the carrier trapping and de-trapping at the oxide-semiconductor interface while the noise in junctionless FET is affected by carrier trapping at the boundary between the channel and depletion region (i.e. Schottky-Read-Hall generation-recombination).

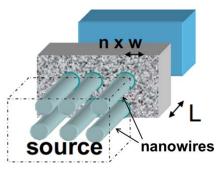

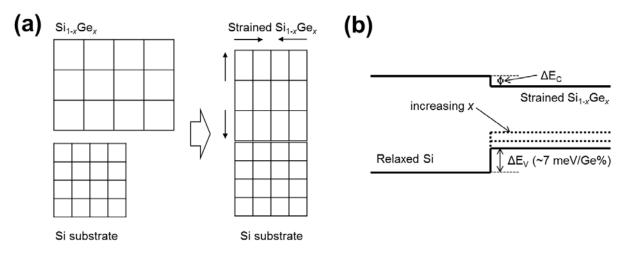

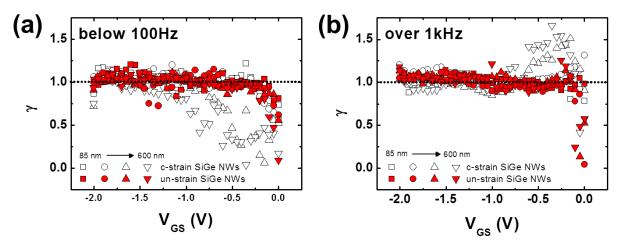

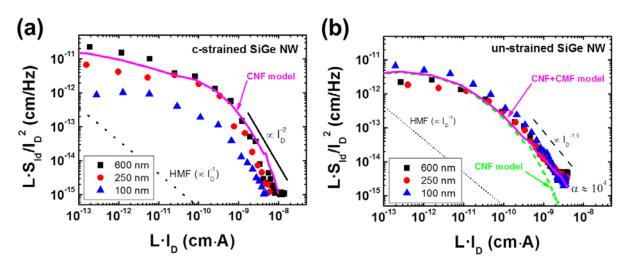

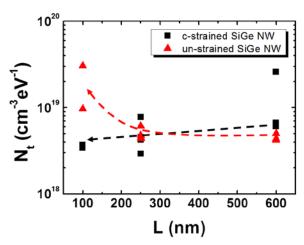

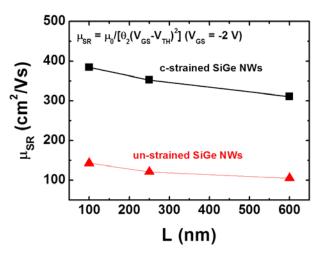

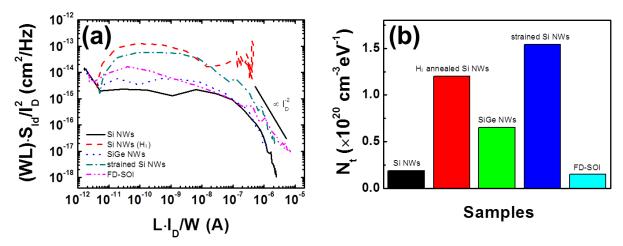

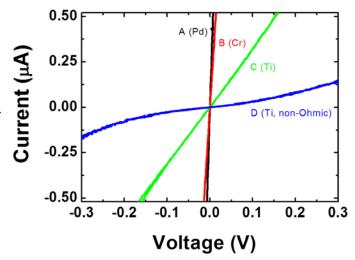

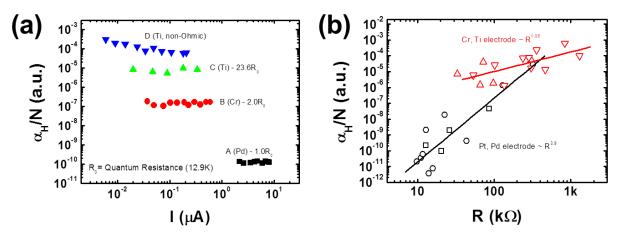

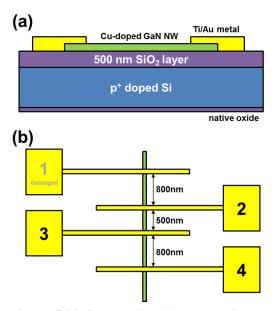

For the nanowire and nanotube structures, the impact of channel strain and metal contact on the low-frequency noise is observed. Three-dimensional (3-D) stacked Si and SiGe coreshell nanowire gate-all-around FETs were compared with compressively strained and unstrained devices. Even though the c-strained devices have inhomogeneous trap distribution in long channel devices, the trap densities of both devices are similar. However, the c-strained ones effectively reduce the influence of correlated mobility fluctuations by the carrier confinement far from the oxide/Si cap interface. Next, the influence of metal-semiconductor junction is studied with different metal contacts based on the noise analysis. The existence of Schottky barrier due to the work function difference shows different relationship for the low-frequency noise and the device resistance. It indicates that contact metal for nanowire can strongly affect the noise properties of low-dimensional structures. Using low-frequency noise measurement, the quality of metal contact on the GaN nanowire is analyzed and it shows that the noise measurement can be a useful tool to assessment the device quality and reliability.

As a perfect 2-D structure, Graphene is an interesting material having surprising high carrier mobility, massless electrons, and a zero band gap. However, graphene FETs fabricated on the substrate exhibit strongly degraded mobility due to the significant impact of carrier scattering. Considering the influence of substrate for the graphene channel, low-frequency noise in graphene FETs is investigated. The noise in single layer graphene FETs exhibits M-shaped behavior as a function of the gate voltage and its behavior is similar to the transconductance variation partially limited by the scattering from the substrate.

In conclusion, it is confirmed that low-frequency noise in FET structures are severely affected by the quality of gate dielectric irrespective of conduction mechanism. Nevertheless, it shows that the noise can be controlled and reduced by applying channel strain or using appropriate metal contact electrode. In the case of graphene transistors, it exhibits quite different noise behavior that is estimated by the carrier scattering on the substrate. Such

results will be helpful for the study of the carrier dynamics fundamental in low-dimensional structures and intense related research. Especially, the noise limits the performance of low-noise devices or sensor applications as decreasing the device size so that the noise should be considered for the future study of low-dimensional structures and their applications.

Keywords: low-frequency noise, 1/f noise, fluctuation, field-effect transistor, trap density, scattering, low-dimensional structure, top-down, bottom-up, FinFET, junctionless FET, SiGe nanowire, multi-walled carbon nanotube, graphene

## Theoretical Background

Chapter 1 Introduction to low-dimensional structures

Chapter 2 Electrical properties for FET structures

Chapter 3 Low-frequency noise characterization

#### **Chapter 1** Introduction to low-dimensional structures

#### 1.1 Scaling overview

The semiconductor technology has achieved a remarkable growth over the past half-century since the development of "transistor" by W. Shockley, J. Bardeen, and W. Brattain in 1947 [1] and the invention of integrated circuit (IC) by J. Kilby (1958) accelerated the growth of semiconductor industry and technology based on silicon. The number of transistors integrated on the same area dramatically increased from several tens to billions and the high-integrated semiconductor devices lead to the miniaturization of electronic products such as TV/VCR, computer, mobile phone, and other e-portable products. Finally, most products use semiconductor devices. For the high-performance of electronic applications, transistors were scaled down continuously and the efforts opened the era of nano devices. Nano devices have many advantages over than microscale counterpart for the performance, the power consumption, the integration and the application. Especially, the quantum transport by the channel confinement and the ballistic transport in which electrons cannot be scattered owing to low-dimensional structures are also noteworthy [2].

However, the device scaling also brought new challenges to overcome in terms of materials, device structures, fabrication technologies, performances, noise, reliability, and so on. For example, the conventional planar complementary metal-oxide-semiconductor (CMOS) technology appeared additional problems usually called "short-channel effects" as decreasing the channel size. The short-channel effects are secondary effects which refer to typically the source/drain charge sharing, the drain-induced barrier lowering, and the subsurface punchthrough [3]. The impact of short-channel effects is to reduce the threshold voltage of the devices so that it interferes with the normal operation of the devices. The limitation of optical lithography technology in wavelength and the alternatives of channel and gate oxide materials must be considered as well.

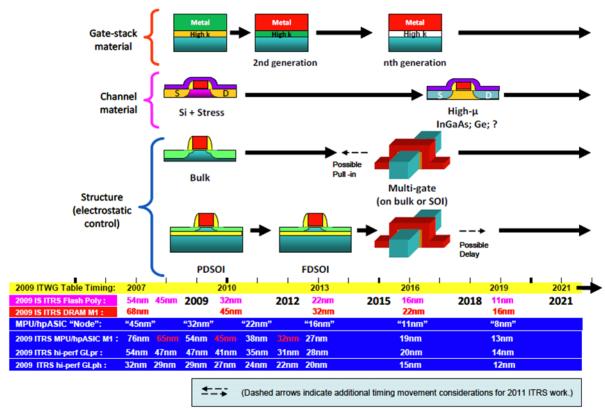

Figure 1.1 shows the graphical trends for the device scaling of International Technology Roadmap for Semiconductors (ITRS) 2010 reports [4]. The gate length of transistors should be sub 10 nm scales within 10 years. The gate-stack materials will maintain the use of high-k

Figure 1.1 ITRS Overall Roadmap Technology Characteristics (ORTC) graphical trends including overlay of 2009 industry logic "nodes" and ITRS trends for comparison [4].

materials instead of silicon oxide for better gate control and lower gate leakage current. For the high-speed devices, the channel has also been studied applying channel strain on silicon or supplanting the materials with Ge or III-V compound semiconductors that have higher mobility than silicon. To reduce the short-channel effects and obtain improved electrostatic control of devices, multi-gate structures have been proposed for the scaling away from the conventional planar technology [5]. Even if early multi-gate structures have been fabricated on the silicon on insulator (SOI) substrate, many studies are also in progress on bulk substrate [6], [7]. Besides studies based on silicon, there are many attempts and studies with nanowires and nanotubes for the next-generation semiconductor device.

As decreasing the channel structure close to quasi one-dimensional (1-D) structures, their physical and electrical properties are represented based on quantum mechanics. It is also complicated due to the structural features such as coupling effect, electrostatic control and surface effect. Therefore, for the successful device scaling, low-dimensional structures should be understood and studied.

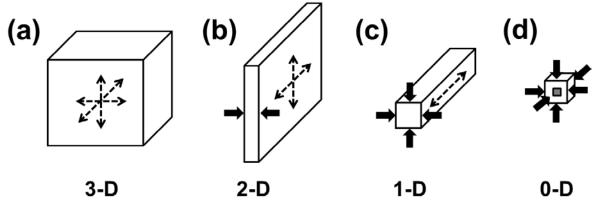

#### 1.2 1-D and 2-D structures

Low-dimensional structures came to the notice of the scientific community in the early 1970s when L. Esaki and R. Tsu suggested the fabrication of superlattices by epitaxial growth to realize negative-differential-conductivity devices appearing Bloch oscillations [8]. In the case of electronic transport, low-dimensional structure refers to a system in which the charge carriers (e.g. electron) are constrained by potential barriers so that their motion will be suppressed [9]. It can be classified into two-, one- or zero-dimensional structures depending on whether the potential barriers confine the electrons in one-, two-, or three- dimensions, respectively. Figure 1.2 represents illustrations of low-dimensional structures. It is noted that there is no absolute value of length to define the dimensionality and the length is just related to determine the physical properties of dimensionality in semiconductors such as Debye length, scattering length and so on [9].

Figure 1.2 Illustrations of low-dimensional structures: (a) bulk semiconductors (b) thin films, quantum wells (c) linear chain structures, quantum wires (d) quantum dots. A dotted line displays the freedom degree of carrier transport.

In CMOS technology, the conventional planar devices gradually changes to low-dimensional structured devices with the downscaling of the gate length. Contrary to bulk structured devices, 1-D and 2-D structures have novel physical and electrical properties. Electrons in materials show different electrical behavior such as the insulator, the semiconductor, and the metal depending on the materials size because they have different energy spacing of the eigenstates. For this reason, low-dimensional structures have been concerned by many scientists for a long time. In 1991, the discovery of carbon nanotubes as a 1-D nanostructure by S. Iigima [10] inaugurated an era of nanotechnology and accelerated it. In addition, metal oxide 1-D nanostructures such as ZnO, SnO<sub>2</sub>, Cu<sub>2</sub>O, Fe<sub>2</sub>O<sub>3</sub>, and CeO<sub>2</sub> have

investigated for the size and dimensionality dependence of nanostructure properties for their applications [11]. In 2004, the electrical property of monocrystalline graphitic films, so called

Figure 1.3 Mother of all graphitic forms [13].

"graphene" as a 2-D nanostructure reported by K. S. Novoselov and A. K. Geim [12]. Graphene is a flat monolayer of carbon atoms tightly packed into a 2-D honeycomb lattice, and it is a basic building block for graphitic materials of all other dimensionalities (Figure 1.3) [13]. More than 70 years ago, L. D. Landau and R. E. Peierls discussed that strictly 2-D crystals were thermodynamically unstable and could not exist owing to a divergent contribution of thermal fluctuations in low-dimensional crystal lattices [14-16].

Due to the difficulty of being 2-D crystals in ambient conditions, the study of 2-D structures was limited as a two-dimensional electron gas (2DEG) which is a gas of electrons free to move in two-dimensions [17]. However, various 2-D nanostructures can also be studied together with the successful exfoliation of graphene [18]. Recently, many studies of low-dimensional structures such as nanowires, nanotubes, and graphene have been carried out in various view points for the synthesis, device fabrication, characterization, and their applications.

#### 1.3 Top-down vs. Bottom-up approaches

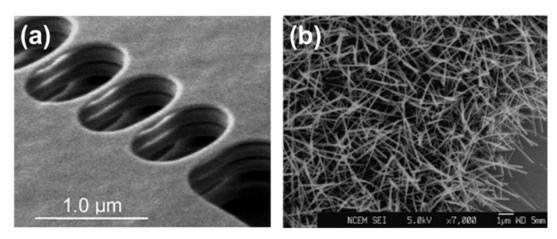

To fabricate 1-D and 2-D nanostructures such as nanowires, nanotubes and graphene (or other 2-D metal films), there are two representative approaches: one is the 'top-down' approach and the other is the 'bottom-up' approach. The top-down approach stands for the geometrical shaping and carving of solid materials from outside to inside whereas the bottom-up approach represents the structure growth by the increase of anisotropy from the atomic scale. Figure 1.4 shows the SEM images for SiGe [19] and ZnO nanowires [20] by top-down and bottom-up approach.

In detail, the top-down approach is based on the conventional semiconductor manufacturing processes consisting of film formation, impurity doping, lithography and

Figure 1.4 Scanning electron microscopy (SEM) images of (a) top-down processed stacked SiGe nanowires [19] and (b) ZnO nanowires grown on Si (100) substrate [20].

etching with various mask sets on the silicon substrate and most of semiconductor devices have been fabricated by this approach. For the realization of 1-D and 2-D nanostructures, the advanced lithography techniques that can be possible to make a pattern for narrow feature size (i.e. nanometer scale) and improved etching methods for the various dimensional structures are also required in the top-down approach. For this, electron-beam (e-beam) lithography, X-ray lithography, or immersion lithography systems were developed for drawing the nm-scale pattern [21-23]. In recent years, improved lithography systems and etching techniques have been applied for the next-generation metal-oxide-semiconductor field-effect transistors (MOSFETs) such as Double-Gate (DG) MOSFETs, FinFETs, and Gate-All-Around (GAA) FETs equivalent to 1-D or 2-D nanostructures. The top-down approach for nanostructures still guarantees the mass production and the reproducibility without many changes of existing fabrication processes. However, it needs high processing cost and well-defined large space for the equipment.

In the different point of view, the bottom-up approach generally indicates the chemically

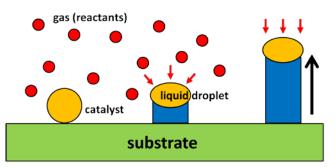

anisotropical growth of nanostructures from the atomic size. For anisotropical growth of crystal, the most well-known method in the bottom-up approach is the Vapor-Liquid-Solid (VLS) [24]. The VLS method is used for the crystal growth with direct adsorption of a gas phase on the substrate with slow chemical process

Figure 1.5 Schematic illustration of bottom-up grown nanowire by Vapor-Liquid-Solid (VLS) process.

as shown in Figure 1.5. The various size and length of nanowires can be grown by VLS method having a single crystal structure depending on the growth conditions.

After growth of nanowires on the substrate, the nanowire separation, purification, and post-growth techniques are required to select the proper size of nanowires and transfer to the substrate for the device fabrication through the dispersion process. And then metal electrodes are deposited to investigate their electrical properties. One of the difficulties for the device fabrication with an individual nanowire is the nanowire manipulation and accurate patterning for metallization because of their small size. There are some typical methods such as photo lithography, e-beam lithography or self-assembly technique for selective patterning [25]. E-beam lithography is typically used for metallization even if there are some difficulties to make selective patterns on the nanowire precisely. But a simple selective e-beam patterning technique with an optical microscope or a Scanning Electron Microscope (SEM) images enables it easy single nanowire pattern [26]. The bottom-up approach cannot guarantee the mass-production and the reproducibility due to the difficulties above-mentioned. But this approach is favorable to study intrinsic properties of nanostructures that are more close to 1-D or 2-D structures than ones made by a top-down technique.

#### 1.4 Electrical issues in low-dimensional structures

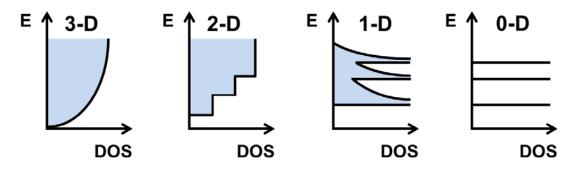

Low-dimensional structures have some interesting electrical phenomena such as an electron tunneling and a quantization of electronic states. The electron tunneling is a quantum mechanical phenomenon where a particle (e.g. an electron) can tunnel through a potential barrier at the quantum scale. It is used for the tunneling diode applications. On the other hand, the electron and its energy state are limited and quantized by the dimensionality. Electronic behaviors in a solid are determined by the density of state at the Fermi energy. The energy

Figure 1.6 Density of states (DOS) in low-dimensional (2-D, 1-D, 0-D) semiconductor structures.

dispersion in a bulk and low-dimensional structures are illustrated in Figure 1.6 [27]. Many electrical and physical properties in low-dimensional structures are expected to have better performances for nano electronics. To achieve low-dimensional structures by top-down or bottom-up approaches, there are some practical issues which should be considered.

For low-dimensional structure devices with conventional CMOS technology, an important issue is short-channel effects. The short-channel effects induced a leakage current in the offstate thereby increase the power consumption for the idle state. To reduce the short-channel effects and obtain the better gate control, nanowire channels with a gate-all-around structure are seen as an ideal transistor channel [28]. According to the device scaling, the channel is approaching 1-D structures which have large surface/volume ratio. The large surface/volume ratio is advantageous for sensor applications but it can also affects the electronic transport due to surface effects. The surface roughness control is one of the difficulties for nanostructures with top-down process and it can be a source of trapping center of charge carriers or mobility degradation by scatterings. The electrical noise, especially 1/f noise, is another issue for device scaling. As decreasing the device size, the 1/f noise is expected to increase because the relative noise spectral density is inversely proportional to the effective size of devices [29], [30]. The 1/f noise in the drain current or gate voltage of a MOSFET has been an important role for analog circuits and RF applications which are related to the signal to noise ratio (SNR) and the phase noise of oscillators, respectively [31]. Many studies for nanotubes and nanowires have been reported to exhibit significant current fluctuations in the low-frequency regime [32-39].

On the other hand, a Schottky barrier between the metal and semiconductor is a notable issue when we make a device with bottom-up growth nanowires. In general, metal electrodes are commonly used in a nanowire device unlike conventional MOSFETs having source/drain contacts with degenerated doped silicon. It is due to the difference of preferred fabrication process with nanowires [40]. For this reason, the existence of Schottky barrier in nanowire devices is inevitable. These contacts can be improved after thermal annealing process but it still limits the device performance and disturbs the intrinsic properties of the nanostructures.

#### 1.5 Outline of the thesis

In this thesis, the electrical properties of low-dimensional FET structures are investigated in the view point of top-down and bottom up approaches. Especially, low-frequency noise is

intensively characterized along with the electrical analysis of devices. Using the low-frequency noise characterization, the carrier dynamics that cannot be observed with normal electrical characterization is understood. Moreover, the low-frequency noise characterization is examined as a tool to determine the device quality. According to these objectives, the manuscript is structured as follows;

We have introduced the recent trends of CMOS technology and the device scaling issues are browsed roughly. To overcome the current limits of device scaling, the low-dimensional FET structures are discussed for their fabrication and electrical issues. Chapter 2 introduces some important parameters such as the threshold voltage, the mobility, the series resistance, the subthreshold swing, and the capacitance to understand the transport properties of nanowire and nanotube devices. The low-frequency noise is introduced in chapter 3 together with the history, the mathematical concept, the fundamentals, and the noise measurement system configuration. The well-known 1/f noise models for FET structures which are the carrier number fluctuation and the mobility fluctuation model are presented.

From chapter 4 to chapter 6, experimental results of static and 1/f noise properties are discussed for 1-D and 2-D nanostructures; Multi-gate MOSFETs (Chapter 4), Si and SiGe nanowire FETs and carbon nanotube devices (Chapter 5), and graphene FETs (Chapter 6). In chapter 4, FinFETs and junctionless FETs are examined with different channel length and width. The 1/f noise origin is compared between the FinFET and the junctionless FET which have the surface conduction and the bulk conduction, respectively. In chapter 5, the 1/f and RTS noise properties in Si and SiGe gate-all-around (GAA) FETs depending on the channel strain effect and the influence of junctions in GaN nanowire and carbon nanotubes are described. In chapter 6, the basic physics and 1/f noise analysis of graphene FETs are arranged separately because the graphene exhibits significantly different physical behaviors compared with other semiconductors. Finally, the summary of all experiment results is concluded in chapter 7.

#### **Chapter 2** Electrical properties for FET structures

#### 2.1 Introduction

The electrical measurement is the most-common method to understand the physical and electrical properties in semiconductors and their applications. Fundamentally, it has been understood with Ohm's law, giving the relationship between the voltage and the current in an electrical conductor. In detail, the electrical behavior depends on the conductivity (or resistivity) which is an intrinsic property determined by electrons in a solid. So, the electrical measurement will be helpful to understand the carrier dynamics in solid-states and to provide useful information for the applications. In general, it is classified as two different standpoints: one is a DC (direct current) measurement directly correlated to the resistance. It is mainly obtained with the current-voltage (*I-V*) measurement. The other is an AC (alternating current) measurement for the electrical impedance which can be understood as a kind of the resistance for the AC signal. The capacitance-voltage (C-V) measurement is normally used. Based on Ohms' law, the I-V measurement reveals a driving current, a conductance, a carrier mobility and so forth which are directly related to the device performance. On the other hand, the C-V measurement refers to one of the impedance spectroscopy and it can give more accurate information of charge carrier concentrations at the interface as well as in the bulk semiconductor.

In conventional MOSFETs, the electrical characterization has been used to extract device parameters to confirm the device performance and to apply to the logic devices. Such parameters as threshold voltage, mobility, carrier concentration, interface charge, series resistance can be extracted. In an era of nanotechnology, the electrical characterization is still important and relevant even though the device dimension is decreased approaching an atomic scale and the electronic transport is approaching to the quantum mechanics. Moreover, the improved model for nano-scale devices is needed considering additional effects as reducing the device size. In this chapter, several important parameters for the characterization of MOSFET structure devices such as threshold voltage, mobility, series resistance, capacitance, subthreshold swing and their detailed method will be summarized.

#### 2.2 Threshold voltage

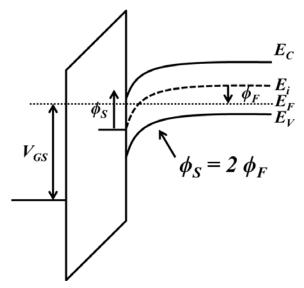

For understanding the MOSFET operation, threshold voltage ( $V_{TH}$ ) is the most important and fundamental device parameter and the precisely controlling of threshold voltage is a major issue in most CMOS integrated-circuit applications [3]. The definition of threshold voltage, firstly suggested in 1953 [41], is commonly understood as the gate voltage when the energy band bending at the Si-SiO<sub>2</sub> interface is equal to twice the potential in bulk semiconductors [42] as shown in Figure 2.1. The surface potential  $\phi_S$  on the p-type substrate (i.e. an n-channel MOSFET) for the threshold voltage is given by

$$\phi_S = 2\phi_F = \frac{2kT}{q} \ln\left(\frac{p}{n_i}\right) \approx \frac{2kT}{q} \ln\left(\frac{N_A}{n_i}\right)$$

(2.1)

where  $\phi_F$  is the bulk potential,  $n_i$  the intrinsic carrier density, p the hole density, and  $N_A$  the acceptor doping density. It corresponds to the gate voltage for which the channel is opened to the current flow.

Figure 2.1 Band diagram for threshold voltage in enhancement-mode *n*-channel MOSFET.

In detail, the conventional enhancement-mode n-channel MOSFET is comprised of a p-type silicon substrate. As increasing the gate voltage  $V_{GS}$ , the electrons start to be drawn at oxide-semiconductor interface by the electric field against the holes that are away from the interface. As a result, the n-type channel in p-type silicon substrate is formed if the electric field is sufficient. The channel region is called an inversion layer. Before the formation of sufficient inversion layer, the current cannot flow (i.e. turn-off) even though the current that is called the subthreshold current still

exists by diffusion. Therefore, the threshold voltage determines the device operation which means the formation of the channel layer for the conduction. An expression for the threshold voltage in the n-channel MOSFET on uniformly doped substrate without any short channel or other effects can be derived as

$$V_{TH} = V_{FB} + 2\phi_F + \frac{\sqrt{2q\varepsilon_S\varepsilon_0N_A(2\phi_F - V_{BS})}}{C_{OY}}$$

(2.2)

where  $V_{FB}$  is the flat-band voltage,  $\varepsilon_S$  the relative permittivity of silicon,  $\varepsilon_0$  the vacuum permittivity,  $C_{OX}$  the oxide capacitance, and  $V_{BS}$  the substrate-source voltage. For an ideal MOS system (i.e. no charges at the oxide and Si-SiO<sub>2</sub> interface), the flat-band voltage can be determined as

$$V_{FB} = \Phi_M - \Phi_S = \Phi_{MS} \tag{2.3}$$

where  $\Phi_M$  is the metal work function and  $\Phi_S$  the semiconductor work function. However, for a real MOS system, the flat-band voltage is further affected by several charges at the oxide and interface. Therefore, Equation 2.3 becomes

$$V_{FB} = \Phi_{MS} - \frac{Q_f}{C_{OX}} - \frac{Q_{it}(\phi_S)}{C_{OX}} - \frac{1}{C_{OX}} \int_0^{t_{OX}} \frac{x}{t_{OX}} \rho_m(x) dx - \frac{1}{C_{OX}} \int_0^{t_{OX}} \frac{x}{t_{OX}} \rho_{ot}(x) dx$$

(2.4)

where  $Q_f$  is the fixed charge at the Si-SiO<sub>2</sub> interface,  $Q_{it}$  the interface trapped charge depends on the surface potential  $\phi_S$ ,  $\rho_m(x)$  and  $p_{ot}(x)$  are the mobile and oxide trapped charges distributed along the oxide. These additional charges from the oxide and the interface are important for the threshold voltage. In practice, the threshold voltage can be derived from the MOSFET characteristics through  $I_D$ - $V_{GS}$  measurement. There are numerous methods for the threshold voltage extraction [42-46] and some well-known extraction methods are introduced in here. However, it is noted that each method is not always good for all kinds of transistors, particularly nano-scale transistors. Hence, to obtain more accurate value of threshold voltage, the threshold voltages from several methods should be compared considering the transport mechanism depending on the device structures and materials.

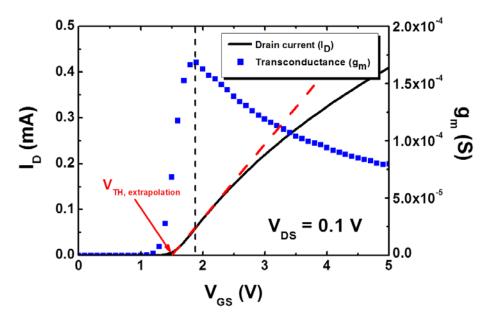

#### 2.2.1 Linear extrapolation method

The most classical method is a linear extrapolation method, which is an old style but well-known, using a linear fit at the maximum transconductance,  $g_{m, max}$  from  $I_D$ - $V_{GS}$  characteristics at the linear region. At strong inversion, the drain current can be expressed as

$$I_{D} = \frac{W}{L} \mu_{eff} C_{OX} \left[ \left( V_{GS} - V_{TH} \right) V_{DS} - \frac{1}{2} V_{DS}^{2} \right]$$

(2.5)

where W is the channel width, L the channel length, and  $\mu_{eff}$  the effective mobility. If  $V_{DS}$  is small enough, Equation 2.5 can be simplified to

Figure 2.2 Illustration of the linear extrapolation method for a commercial n-channel MOS transistor (HCF4007UB, a dual complementary pair plus inverter comprised of three n-channel and three p-channel enhancement type MOS transistors) at  $V_{DS} = 0.1$  V.

$$I_{D} = \frac{W}{I_{L}} \mu_{eff} C_{OX} (V_{GS} - V_{TH}) V_{DS}$$

(2.6)

At a constant of  $V_{DS}$ , based on Equation 2.6, the current expects to appear a linear curve for  $I_D$ - $V_{GS}$  characteristic but the actual curve is not linear because the effective mobility will be degraded at higher gate voltage. Therefore, a point to fit Equation 2.6 is the point where the transconductance  $g_m$  (= $dI_D/dV_{GS}$ ) reaches its maximum value. The threshold voltage can be found at the point of zero current in the linear fit drawn with the  $I_D$ - $V_{GS}$  curves focusing on the gate voltage at the  $g_{m,max}$  as illustrated in Figure 2.2. However, the linear extrapolation method is sensitive to the series resistance and mobility degradation.

#### 2.2.2 Second derivative method

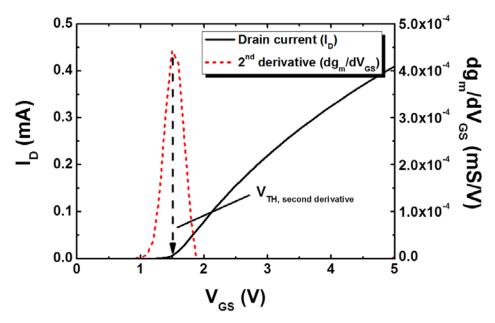

The second derivative method (also named transconductance change or transconductance derivative) defines the threshold voltage with a secondly derivative curve (= $d^2I_D/dV_{GS}^2$ ) of the transconductance at small drain voltage ( $V_{DS} < kT/q$ ) [47]. In this method, the gate voltage at the maximum value of the second derivative transconductance indicates the threshold voltage. The maximum point is related to the classical threshold band-bending of  $\phi_S = \phi_F + V_{SB}$  that is the surface inversion layer being equal to the substrate doping (where  $V_{SB}$  is the source-substrate voltage) [48]. The transconductance derivative method is rather simple and more

Figure 2.3 Illustration of second derivative method for a commercial n-channel MOS transistor (HCF4007UB) at  $V_{DS} = 0.1$  V.

precise compared with linear extrapolation technique and less affected by the series resistance and mobility degradation.

#### 2.2.3 Y-function method

The Y-function method (also called "drain current ratio" or "square root transconductance" method) was proposed by G. Ghibaudo in 1988 by combining the model of  $I_D$ - $V_{GS}$  and  $g_m$ - $V_{GS}$  characteristics to avoid the mobility degradation and the parasitic series resistance [46]. The model starts to consider the device in the linear operation at low drain voltage and the drain current can be expressed as Equation 2.6. Considering the dependence of the mobility on the gate voltage, it is represented as

$$I_{D} = \frac{WC_{OX}}{L} \frac{\mu_{0}}{\left[1 + \theta_{1}(V_{GS} - V_{TH})\right]} (V_{GS} - V_{TH}) V_{DS}$$

(2.7)

where  $\mu_0$  is the low field mobility, and  $\theta_1$  the mobility attenuation coefficient. Therefore, the transconductance of Equation 2.7 is

$$g_{m} = \frac{\partial I_{D}}{\partial V_{GS}} = \frac{W}{L} C_{OX} \frac{\mu_{0}}{\left[1 + \theta_{1} (V_{GS} - V_{TH})\right]^{2}} V_{DS}$$

(2.8)

The idea of Y-function method is the cancelation of the mobility attenuation coefficient  $\theta_I$  by dividing the current  $I_D$  with the square root of the transconductance  $g_m$  so that it results in

$$\frac{I_D}{g_m^{1/2}} = \left(\frac{W}{L} C_{OX} \mu_0 V_{DS}\right)^{1/2} (V_{GS} - V_{TH})$$

(2.9)

In Equation 2.9,  $I_D/g_m^{1/2}$  should be linear as increasing gate voltage with the intercept and slope which indicate the threshold voltage  $V_{TH}$  and low field mobility  $\mu_0$ , respectively (Figure 2.4 (a)). After  $V_{TH}$  extraction, the mobility attenuation coefficient  $\theta_I$  can be also presented as shown in Figure 2.4 (b) using an expression which is given by

$$\theta_1 = [I_D / (g_m (V_{GS} - V_{TH})) - 1] / (V_{GS} - V_{TH})$$

(2.10)

or it can be simplified as

$$\theta_1 = \frac{G_m}{I_D} - \frac{1}{V_{GS} - V_{TH}} \tag{2.11}$$

where  $G_m$  is defined as  $W/L(C_{OX}:\mu_0\cdot V_{DS})$ .

Figure 2.4 (a)  $I_D/g_m^{-1/2} - V_{GS}$  characteristic in a commercial n-channel MOS transistor (HCF4007UB) with an excellent straight fitting line (red solid line) and (b) extracted mobility attenuation coefficient  $\theta_I$  from Y-function method.

#### 2.3 Carrier Mobility

In solid-state physics, the term 'carrier mobility' refers in general to the property of the carrier (electron or hole) to move in semiconductor (or metal) under an electric field E. It can be also called an electron or hole mobility according to the carrier type but the term 'mobility' is more popular for all cases. When an electric field E is applied across the conductor, electrons (or holes) begin to move with an average velocity which is named the drift velocity  $v_d$ . So, the electron mobility  $\mu$  is defined as

$$\mathbf{v_d} = \mu \mathbf{E} \tag{2.12}$$

and it is specified in unit of cm<sup>2</sup>/Vs. In an intrinsic semiconductor, the mobility is dependent on carrier scatterings by phonons, impurities, defects, or alloy disorder which affects the drift velocity. The approximate relationship between the mobility and scattering time is

$$\mu = \frac{q\tau}{m^*} \tag{2.13}$$

where q is the electronic charge,  $m^*$  the effective mass of a carrier in the semiconductor, and  $\tau$  the average carrier scattering time. If the average scattering time  $\tau_i$  for each scattering mechanism is independent, the total mobility due to several scatterings can be expressed using the Mathiessen rule given by [49]

$$\frac{1}{\mu} = \sum_{i} \frac{1}{\mu_{i}} \tag{2.14}$$

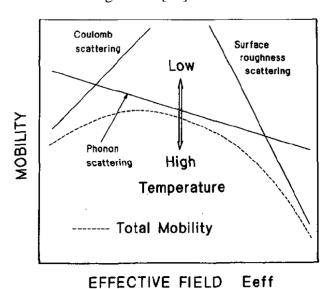

where  $\mu_i$  (= $q\tau_i/m^*$ ) is the limited mobility with the different scattering time. The Matthiessen rule has been used to study the influence of various scattering on the mobility in MOSFETs as shown in Figure 2.5 [50].

Figure 2.5 Schematic diagram of the effective field dependence of mobility in inversion layer by three dominant scattering mechanisms [50].

In semiconductors, the most common scattering mechanisms are ionized impurity scattering and phonon scattering (precisely, acoustic phonon scattering). The ionized impurity scattering is especially important for highly doped semiconductors and it stands for the carrier scattering by influencing the electric field of the ionized impurities coming from donors and/or acceptors in semiconductors. The scattering potential of ionized impurity scattering is assumed similar to Coulombic scattering but the ionized impurity scattering attracts mobile carriers which screen the potential.

For the phonon (or lattice) scattering, the semiconductor's band structure is influenced by changes in lattice spacing at any temperature above 0 K. The vibration of atoms causing the lattice spacing creates pressure (acoustic) waves in crystal, which are called phonons inducing the carrier scattering. There are two kinds of phonons: one is the acoustic phonons

and the other is optical phonons. The acoustic phonons are the lattice spacing due to the displacement of neighboring atoms in the same direction whereas the optical phonons coming from the opposite directions [51]. Apart from these major scattering mechanisms in semiconductors, there are also other important scatterings such as neutral impurity scattering, surface roughness scattering, and defect scattering depending on materials, structures, and process.

There are several mobilities in use depending on the extraction method. Representatively, they are conductivity mobility, Hall mobility, and MOSFET mobility for the characterization of semiconducting materials and devices.

#### 2.3.1 Conductivity (or drift) carrier mobility

The conductivity mobility ( $\mu_{drift}$ ) is derived from the simple relation between mobility and electrical conductivity  $\sigma$  that is the proportional to the product of the mobility and carrier concentration in semiconductor materials. The conductivity is given by

$$\sigma = q(n\mu_{drift,e} + p\mu_{drift,h}) \tag{2.15}$$

where n is the electron density,  $\mu_{drift,e}$  the electron mobility, p the hole density, and  $\mu_{drift,h}$  the hole mobility. The conductivity mobility is simple and easy to find but the majority carrier density is needed to obtain the accurate conductivity mobility. It is useful to characterize for the intrinsic property of materials.

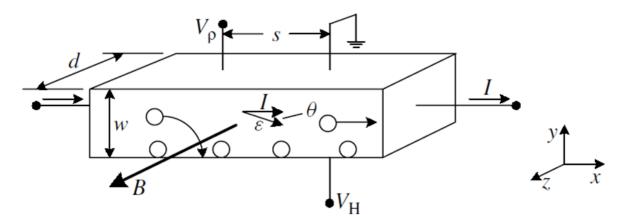

#### 2.3.2 Hall carrier mobility

The Hall measurement is a well-common method based on Hall Effect to obtain the mobility, carrier type, and carrier concentration in material. The Hall Effect is a phenomenon to produce a potential difference (Hall voltage,  $V_H$ ) perpendicular to the magnetic field and current when the magnetic field applied to the electrical conductor perpendicular to the current flow direction. As shown in Figure 2.6, it shows a schematic illustration of Hall Effect in a p-type conductor and the force causing Hall voltage is given by the vector expression

$$\mathbf{F} = q(\mathbf{E} + \mathbf{v} \times \mathbf{B}) \tag{2.16}$$

and Hall mobility  $\mu_H$  is defined by

Figure 2.6 Schematic illustration of the Hall Effect in a p-type conductor [47].

$$\mu_H = \frac{\left| R_H \right|}{\rho} = \frac{dV_H}{\rho BI} \tag{2.17}$$

where  $R_H$  is the Hall coefficient, B the magnetic field, I the current, and  $\rho$  the resistivity. The Hall mobility is trustworthy compared with the conductivity mobility but the method requires the sample having appropriate geometries for Hall measurement.

#### 2.3.3 MOSFET carrier mobility

In general, the conductivity and Hall mobilities are for bulk. In the case of MOSFETs, the surface is relatively important and the mobility is easily affected by various scatterings such as ionized impurity scattering, phonon scattering, and so on. Considering these scatterings, the total mobility is limited by the lowest mobility according to Mathiessen's rule. Therefore the method to extract the mobility only for MOSFET structures has been used. Effective mobility and Field-effect mobility are well-known terminology widely used for various material devices as well as silicon MOSFETs. Let consider an n-channel MOSFET of gate length *L* and width *W*. The drain current is simplified for the basic MOSFET operation as

$$I_{D} = g_{d} \cdot V_{DS} = \frac{W}{L} \mu_{eff} Q_{i} V_{DS}$$

(2.18)

where  $g_d$  is the drain conductance,  $\mu_{eff}$  the effective mobility and  $Q_i$  the inversion channel charge density (C/cm<sup>2</sup>). To extract the exact value of effective mobility, the inversion charge density  $Q_i$  is important and it can be determined in two different ways. One is a simple approximation with

$$Q_i = C_{OX}(V_{GS} - V_{TH}) (2.19)$$

and the other is a direct measurement of  $Q_i$  from the capacitance measurement (refer Chapter 2.6). The direct measurement of charge carriers is better than the approximation to extract the value of effective mobility. However, it is not convenient in many ways such as a necessity of additional C-V measurement and several capacitance effects (e.g. an overlap capacitance) depending on the device structure. For this reason, the approximation method is well used for the comparison for the number of devices and the capacitance measurement is recommended to obtain the more precise value of mobility.

For the effective mobility, the drain voltage is typically recommended about 50~100 mV as small as possible considering the uniformity of inversion charge carriers from source to drain. The definition of effective mobility is given by

$$\mu_{eff} = \frac{g_d L}{WQ_i} \tag{2.20}$$

and the drain conductance  $g_d$  is defined as

$$g_d = \frac{\partial I_D}{\partial V_{DS}} \bigg|_{V_{GS} = cons \tan t} \tag{2.21}$$

The ionized impurity scattering and surface roughness scattering that mainly affects the effective mobility depends on the substrate doping concentration and the electric field. The relation between the effective mobility and the surface electric field can be expressed as

$$\mu_{eff} = \frac{\mu_0}{1 + \left(\alpha E_{eff}\right)^{\gamma}} \tag{2.22}$$

where  $\alpha$  and  $\gamma$  are constants. In Equation 2.22, the "universal" mobility curves for the electric field which can be expressed as the electric field due to the space-charge region and the inversion layer charges [52-54]. But, the universal mobility is not good for understanding the device operation because the gate voltage can be measured experimentally, not the electric field. Therefore, the empirical relationship for the effective mobility degradation for the gate voltage is [55]

$$\mu_{eff} = \frac{\mu_0}{1 + \theta_1 (V_{GS} - V_{TH}) + \theta_2 (V_{GS} - V_{TH})^2}$$

(2.23)

where  $\theta_1$  and  $\theta_2$  are mobility attenuation factors which are related to the series resistance and surface roughness, respectively [56]. In the long channel devices, the value of  $\theta_2$  is negligible but, in the case of short channel, it may significantly affect to the mobility.

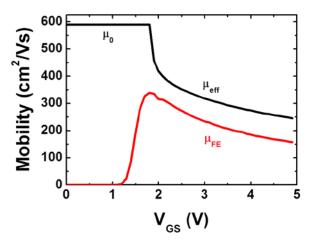

On the other hands, the field-effect mobility is determined using the transconductance  $g_m$  contrary to the effective mobility for the drain conductance  $g_d$  which is given by

$$g_{m} = \frac{\partial I_{D}}{\partial V_{GS}} \bigg|_{V_{DS} = cons \tan t}$$

(2.24)

and the field-effect mobility is defined as

$$\mu_{FE} = \frac{Lg_m}{WC_{OX}V_{DS}} \tag{2.25}$$

The effective and field-effect mobility are widely used with little consideration for nano

devices analysis. However, it is noted that there is mathematically a distinct difference for considering electric field dependence on the mobility. Figure 2.7 shows for the effective and field-effect mobility as a function of the gate voltage. The effective mobility is much larger than the field-effect mobility. It is due to the disregard of the electric field dependence for the mobility in the derivation of Equation 2.25 [57].

Figure 2.7 Comparison of the effective and field-effect mobilities (HCF4007UB).

#### 2.4 Series and contact resistances

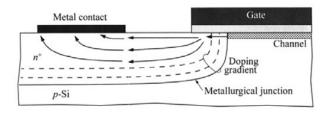

Figure 2.8 Different components of parasitic S/D series resistance. ( $R_{ac}$  is the accumulated-layer resistance due to doping gradient,  $R_{sp}$  the spreading resistance,  $R_{sh}$  the sheet resistance, and  $R_{co}$  the contact resistance) [59].

The term "series resistance" refers to the additional resistance which contributes to the total resistance of the device. It comes from the electrical connections from leads and contacts. It could be called "contact resistance" but it has been used for the metal-semiconductor junction as a main contribution [58]. Firstly, the series resistance in CMOS technology stands for the parasitic source/drain (S/D) resistance

connected to the channel in series when the device size is decreased. Therefore, the series resistance has been often understood the parasitic resistance. Figure 2.8 illustrates the detailed

schematic and the circuit model for different parasitic series resistances [59]. However, the resistance between source and drain is mostly classified as the source resistance  $R_S$ , the drain resistance  $R_D$ , the channel resistance  $R_{ch}$ , and the contact resistance  $R_C$  for the analysis. For MOSFETs, the total resistance  $R_{total}$  can be expressed a summation of  $R_{ch}$  and  $R_{SD}$  (= $R_S$ + $R_D$ ) as

$$R_{total} = R_{ch}(V_{GS} - V_{TH}) + R_{SD}$$

$$= \frac{L}{W} \rho_{ch}(V_{GS} - V_{TH}) + R_{SD}$$

(2.26)

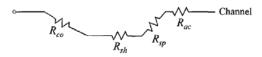

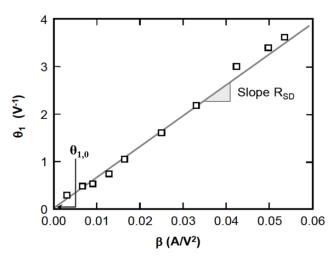

where  $\rho_{ch}$  is the resistivity of the channel. The series resistance  $R_{SD}$  can be extracted from the mobility attenuation factor  $\theta_1$  based on Y-function method [60],

$$\theta_{1} = \frac{G_{m}}{I_{D}} - \frac{1}{(V_{GS} - V_{TH})} = \theta_{1,0} + \beta (R_{S} + R_{D})$$

(2.27)

$$\beta = \frac{W}{L_{eff}} C_{OX} \mu_0 \tag{2.28}$$

Using Equation 2.27 and 2.28,  $\theta_1$  can be drawn as a linear function of  $\beta$  which is shown in Figure 2.9. The slope and the intercept with y axis of the plot gives the values of the total series resistance  $R_{SD}$  and the intrinsic mobility attenuation factor  $\theta_{1,0}$ , respectively. Interestingly,  $R_{SD}$  extraction is not affected by  $L_{eff}$  variations or  $L_{eff}$ -dependent  $\mu_0$  variations.

There is another resistance which Figure 2.9 Extraction of the series resistance  $R_{SD}$  and mobility attenuation factor  $\theta_I$  [60].

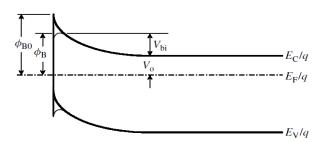

There is another resistance which called contact resistance mainly observed in the metal-semiconductor junctions. In

1874, F. Braun firstly reported the asymmetrical conduction between metal points and crystals [61]. The rectifying properties of the metal-semiconductor contact arise from the existence of an electrostatic barrier so called "Schottky barrier" at the interface between the metal and semiconductor. Theoretically, the electrostatic barrier is due to the difference in work functions of two materials (Figure 2.10). If the barrier height is small, the junction makes an "Ohmic" contact that presents a linear curve in current-voltage relationship. However, for the large barrier height, it is called "Schottky" contact due to the rectifying

Figure 2.10 Energy band diagram of the Schottky barrier [47].

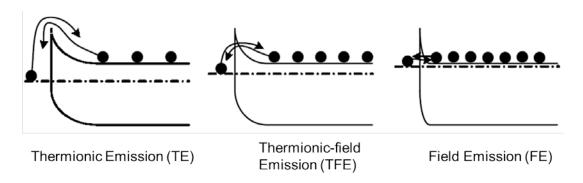

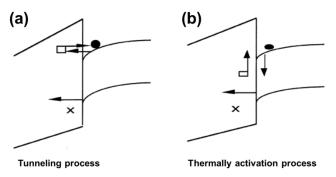

behaviors. The Schottky barrier is frequently observed in nanowire or nanotube devices with bottom-up grown nanostructures and it is one of the important issues for nanowire applications. The conduction mechanisms in metal-semiconductor are illustrated in Figure 2.11: thermionic emission (TE), thermionic-field emission (TFE), and field emission (FE)

[59]. For the evaluation of contact resistance, several methods are employed presently, such as transmission-line method (TLM), gated four-prove measurement, modified time-of-flight method, Kelvin probe force microscopy (KFM) and electric-field induced second harmonic generation (SHG) method [62-66].

Figure 2.11 Different conduction mechanisms in metal-semiconductor contacts: thermionic emission (TE), thermionic-field emission (TFE), and field emission (FE) [47].

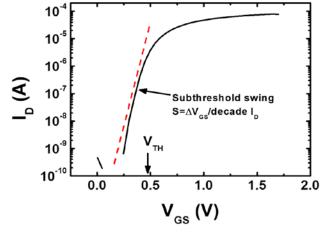

#### 2.5 Subthreshold swing

In a MOSFET, a small current exists between the source and the drain when the gate bias is below threshold voltage and the semiconductor surface is in weak inversion (i.e. subthreshold region). The current in the subthreshold region is named subthreshold current or a subthreshold leakage. Its behavior is similar to the exponentially increasing current of a forward biased diode because the subthreshold current is dominated by the diffusion current and not the drift current owing to lower electron charge in the channel [59]. In the subthreshold region (below threshold), the drain current of a MOSFET in all region can be expressed [67]

$$I_D = I_{D1} \exp\left(\frac{q(V_{GS} - V_{TH})}{nkT}\right) \left(1 - \exp\left(-\frac{qV_{DS}}{kT}\right)\right)$$

(2.29)

where  $I_{D1}$  depends on temperature, device dimensions, and substrate doping density and n is given by  $n=1+(C_b+C_{it})/C_{OX}$  where  $C_b$ ,  $C_{it}$ , and  $C_{OX}$  are respectively bulk, interface trap, and oxide capacitance per unit area. The subthreshold swing can be obtained from the plot of log  $(I_D)$  versus  $V_{GS}$  when  $V_{DS}$  is much larger than thermal voltage (i.e.  $V_{DS} >> kT/q$ ). As shown in Figure 2.12, the subthreshold swing is expressed as the reciprocal of slope in linear region. It corresponds to the gate voltage necessary to increase the drain current by one decade. Therefore, the subthreshold swing is given by

$$S = \frac{1}{Slope} = \frac{\ln(10)nkT}{q} \approx \frac{60nT}{300} \, mV \, / \, decade \tag{2.30}$$

The subthreshold swing is known to have minimum theoretical limit of 59.6 mV/decade  $(S=\ln(10)kT/q)$  in the case of very thin Si-SiO<sub>2</sub> interface having no traps at room temperature

[68]. It is one of the fundamental issues for silicon based MOSFET scaling since the subthreshold swing is increased as decreasing the channel length. The subthreshold swing is related to logic circuits for low-power, high-speed applications and it is an important parameter to determine the device performance for the MOSFET miniaturization [69].

Figure 2.12 Log  $(I_D)$  versus  $V_{GS}$  of 3-D stacked gate-all-around (GAA) silicon nanowire transistor.

## 2.6 Capacitance

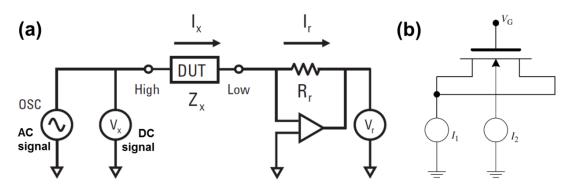

The capacitance-voltage (*C-V*) measurement is one of the most useful and common method to characterize electrical properties of materials and their interfaces. The *C-V* measurement is a specific technique for the impedance spectroscopy that has been used to investigate charge carriers in the bulk or interfacial region of any kind of solid or liquid material: ionic, semiconductor, mixed electronic-ionic, and dielectrics [70]. In MOSFETs, it has been mainly used to characterize oxide thickness, doping concentration, flat-band voltage, oxide charge, work function, and interface state density in MOS devices [47]. The

Figure 2.13 (a) Schematic diagram of an impedance measurement method named auto-balancing bridge method [73] and (b) Split C-V measurement arrangement [47].

capacitance is determined with the width of space-charge (i.e. depletion) region in a semiconductor junction applying small amplitude of AC voltage (or current) on a DC voltage. Typically, the frequency of AC signal is used with 10 kHz to 1 MHz and the amplitude is recommended as small as possible for accurate measurements or near the thermal voltage (≈ 25 mV) [71], [72]. But, the amplitude is used from 10 to 50 mV practically and it is adjustable depending on the devices.

Figure 2.13 (a) shows a schematic of the impedance measurement method called an autobalancing bridge method which is adapted to conventional equipment systems [73]. To measure capacitance in MOSFETs, the most widely used C-V measurement technique is called "split C-V" technique and consists in measuring the capacitance of the gate to channel (source/drain) and the gate to substrate as illustrated in Figure 2.13 (b) [74]. A time-varying gate voltage gives rise to currents  $I_I$  and  $I_2$ . With the substrate grounded, the channel inversion charge density  $C_i$  and the substrate depletion charge density  $C_b$  can be derived from  $I_I$  and  $I_2$  which is given by

$$I_{1} = \frac{dQ_{i}}{dV_{GS}} \frac{dV_{GS}}{dt} = C_{i} \frac{dV_{GS}}{dt} = C_{GC} \frac{dV_{GS}}{dt}$$

(2.31)

$$I_{2} = \frac{dQ_{b}}{dV_{GS}} \frac{dV_{GS}}{dt} = C_{b} \frac{dV_{GS}}{dt} = C_{GB} \frac{dV_{GS}}{dt}$$

(2.32)

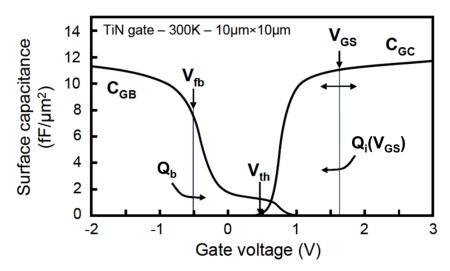

where  $C_{GC}$  is the gate-to-channel and  $C_{GB}$  the gate-to-bulk capacitance per unit area. Figure 2.14 shows the capacitance behavior of  $C_{GC}$  and  $C_{GB}$  from the split C-V measurements. The inversion charge  $Q_i$  and the substrate depletion charge  $Q_b$  can be obtained by the integration of  $C_{GC}$  from the accumulation to the gate voltage and  $C_{GB}$  from the flat band voltage to the inversion, respectively. The expressions for  $Q_i$  and  $Q_b$  are given by

Figure 2.14  $C_{GC}$  and  $C_{GB}$  behaviors as changing the gate voltage and principle of  $Q_i$  and  $Q_b$  with split C-V measurements [60].

$$Q_i = \int_{V_{acc}}^{V_{GS}} C_{GC} dV_{GS} \tag{2.33}$$

$$Q_b = \int_{V_{ER}}^{V_{inv}} C_{GB} dV_{GS} \tag{2.34}$$

With the results of Equation 2.33 and 2.34, the effective mobility and effective field can be calculated as [60]

$$\mu_{eff}(V_{GS}) = \frac{L}{W} \frac{I_D(V_{GS})/V_{DS}}{Q_i(V_{GS})}$$

(2.35)

$$E_{eff}(V_{GS}) = \frac{|Q_b| + \eta |Q_i(V_{GS})|}{\varepsilon_{ch}}$$

(2.36)

where  $\varepsilon_{ch}$  is the permittivity of channel material and  $\eta$  the empirical weighting parameter, which is varying with device type, doping concentration and temperature [75], [76].

# 2.7 Summary

In this chapter, the major device parameters to understand the transport properties based on the classical MOS transistor model were summarized together with the practical extraction methods. These parameters such as threshold voltage, mobility, series resistance, subthreshold swing, and capacitance are also useful to describe the electrical operation of nano-scale devices considering some fitting procedures. The parameter extractions and their

physical meanings can help to understand the physical phenomena and optimize the materials and fabrication processes correlated to the efficiency of carrier transport.

# **Chapter 3** Low-frequency noise characterization

#### 3.1 Background: Definition and concepts

In general, noise refers to any unwanted signal that is commonly observed in signals such as sounds, electronics, images, communications, and so on. For example, in communication systems, the noise signal blocks, changes, interferes or distorts the original messages and thereby the message may not deliver its meaning accurately. Similarly, noise also exists in all electronic devices and circuits as a result of the randomly spontaneous perturbation in the current (or voltage) due to the random movement of charge carriers and carrier fluctuations in the semiconductors by several reasons such as temperature, defects, and etc. The noise in electronic systems has been called "electronic noise".

The electronic noise can be briefly classified into two types: one is an external noise which is defined as a noise from other outer noise sources such as light, sound, and vibration and not from the electronic device itself. The external noise which is easy to observe in electrical measurements is the hindrance for understanding the inherent noise in electronic devices. However, it can be reduced or removed by some appropriate shielding techniques. In spite of the minimization of the external noise, on the other hand, there is still a noise due to an electronic device or rather a material itself like a semiconductor. It is named an internal

Figure 3.1 Drain current signal fluctuations in time domain [77].

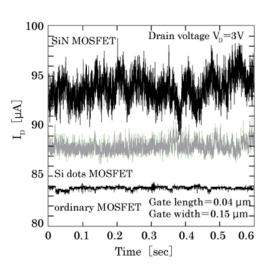

noise as a unique property of the electronic device. Accordingly, the internal noise cannot be entirely eliminated unlike the external noise but it can be effectively reduced by proper manufacturing process and design for the devices and circuits. In general, the study of electronic noise in solid-state devices reveals internal noise which explains the phenomena of current fluctuations following in the semiconductor. Figure 3.1 shows an example of drain current signal fluctuations with different structures of MOSFETs [77].

In detail, the time varying current I(t) in the semiconductor, considering the electronic noise, can be expressed as

$$I(t) = I_0 + i(t) (3.1)$$

where  $I_0$  is the average value of current for a certain applied voltage and i(t) is the small-signal variables of the randomly fluctuated currents in time variation. Since i(t) is a random variable, it cannot be predicted at any point in time. To characterize the noise in current signal I(t), one typical way is the averaging of random signals. By definition, however, the noise is non-deterministic as previously mentioned so that it is difficult to obtain a proper mean value and cannot be represented by any mathematical function. Indeed, the average of current I(t) which is measured for a certain time period will be always zero. For this reason, another mathematical quantity is required to properly represent the random noise behaviors in the current. In general, there are several squared quantities and one of them named the power spectral density (PSD) S(f) is generally used which is given by a Fourier transform method. A Fourier transform method is a well-known and powerful technique for the effective noise analysis which converts the random variables in the time domain to the frequency domain and it is defined as

$$X(f) = \int_{-\infty}^{\infty} x(t)e^{-j2\pi ft}dt \iff x(t) = \int_{-\infty}^{\infty} X(f)e^{j2\pi ft}df$$

(3.2)

where X(f) is the Fourier transform and x(t) is the inverse Fourier transform. If the Fourier transform decomposes the random signal into its constituent frequencies, the noise can be written as the sum of simple waves mathematically represented by sine and cosine. However, the Fourier transform is not desirable for all kinds of random signal because there is no inverse Fourier transforms for the conversion. To solve such mathematical problem in the Fourier transform, the autocorrelation function R(s), which is same process compared to the Fourier transform according to the Winer-Khintchine theorem, has been used [78], [79]. So, the PSD is given by

$$S(f) = 4 \int_0^\infty R(s) \cos(2\pi f s) ds \tag{3.3}$$

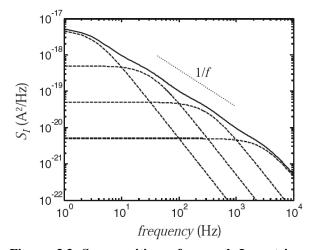

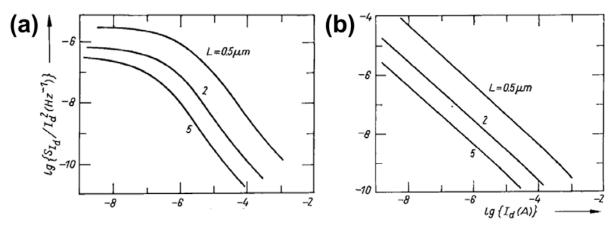

and it reflects how the noise power is distributed with frequency. The PSD can be obtained with a spectrum analyzer and the unit of PSD generally used in  $A^2/Hz$  and  $V^2/Hz$  for the noise current ( $S_I$ ) and noise voltage ( $S_V$ ), respectively.

Noise characterization has been one of the useful techniques to characterize the device reliability and the failure analysis for typical microelectronic devices because the noise forms an intrinsic lower noise limit and depends on material and fabrication processing [47].

Moreover, the noise spectroscopy has been applied to the study of deep levels in MOSFET like a deep-level transient spectroscopy (DLTS) [80]. Even the noise spectroscopy can be applied to very small area devices whereas the DLTS is impossible. Especially, for nano scale devices, the noise should be considered because it increases relatively as decreasing the current level due to the smaller size of device. Therefore the noise is getting important for low-dimensional structures. Why the electronic noise is important for nano scale devices? Basically, the resolution limit of an electronic device (e.g. a sensor) for the signal detection is determined by the signal to noise ratio (SNR). If the device has high signal level (i.e. high current), the resolution for the signal detection is generally limited by the electronic circuits whereas it becomes more sensitive to noise when the device has smaller current level. As a result, the noise restricts the minimum value of the input signal that determines the output signal of electronic circuits.

### 3.2 Fundamental noise sources

In the view point of physics, the electronic noise is one of carrier dynamics which is correlated to the scattering process in a solid-state. The scattering process is due to some collisions of charge carriers because of lattice vibrations during the transport or trapping/detrapping of charge carriers on the trap sites. It has been known that the scattering elements are channel defects, interface states, oxide traps or contacts. There are various kinds of noise sources and it represents different behaviors in the frequency domain depending on the noise source. In this chapter, the representative fundamental noise sources are discussed and described.

#### 3.2.1 Thermal noise

Thermal noise (also called Johnson, Nyquist, or white noise) is caused by the random thermal motion of current carriers (i.e. electrons or holes) in a semiconductor. In 1906, A. Einstein predicted that Brownian motion of charge carriers would lead to fluctuations in the potential across a resistor in thermal equilibrium [81]. Later on, in 1928, J. Johnson firstly measured [82] and H. Nyquist theoretically explained it [83]. Thermal noise is always presented for every semiconductor in the absence of an electrical field to be applied. The PSD of thermal noise is constant over a frequency range, which is why it is called white noise. The

voltage PSD of thermal noise due to the Brownian motion of carriers can be expressed as

$$S_V = 4kTR \tag{3.4}$$

where k is the Boltzmann constant, T the absolute temperature, and R the resistance. The corresponding current PSD of thermal noise is given by

$$S_I = \frac{S_V}{R^2} = \frac{4kT}{R} \tag{3.5}$$

Thermal noise always exist (except T=0 K) thereby it is frequently used for comparison between other noise types and thermometry purposes which provides the resistance R. For example, thermal noise is often used to calibrate a noise measurement system because it can give some value for the limits of the noise measurement system with temperature [84].

#### 3.2.2 Shot noise

Shot noise has been known as the discrete nature of charge transport. It is generally observed in devices having a potential barrier such as pn junctions, and Schottky diodes. In 1918, W. Schottky firstly discovered in vacuum tubes and derived an equation shown as the Schottky formula [85]. The PSD of shot noise is proportional to the electronic charge q of the carriers and the mean current I,

$$S_{I} = 2qI \tag{3.6}$$

There is no expression for the voltage PSD in shot noise because the current is necessary for the generation of shot noise. The shot noise is also called a white noise like thermal noise because its frequency dependence is the same as thermal noise. Thus, it cannot be distinguished simply due to the existence of the thermal noise. But the shot noise is generally much smaller than the thermal noise. Recently, shot noise becomes important in mesoscopic systems because the size of a mesoscopic system is comparable to some typical lengths which determine the level of electron correlations and the shot noise is correlated to the system length [86].

#### 3.2.3 Generation-Recombination (g-r) noise

Generation-recombination (g-r) noise is due to generation and recombination of charge carriers (i.e. electrons or holes) by trap sites which induce the conductance (or resistance) fluctuations. In semiconductors, the localized state cannot participate to the conduction

whereas the delocalized states contribute to the electron conduction. These localize states also named "traps" exist due to the presence of various defects or impurities in the semiconductor or at the interface. The PSD of g-r noise is given by a Lorentzian behavior

$$\frac{S_I}{I^2} = \frac{S_R}{R^2} = \frac{S_N}{N^2} = \frac{\overline{\Delta N^2}}{N^2} \left[ \frac{4\tau}{1 + (2\pi f \tau)^2} \right]$$

(3.7)

where N is the averaging number of free carriers,  $\overline{\Delta N^2}$  the variance of the fluctuating number of charge carriers, and  $\tau$  the carrier relaxation time. The relaxation time  $\tau$  is in the range of  $10^{-6}$  s to  $10^{-3}$  s as a characteristic of traps. The g-r noise is only valid when the Fermi energy level is near, within a few kT, to the trap energy level [87]. In general, the trap characteristics depend on the trap energy level and spatial position.

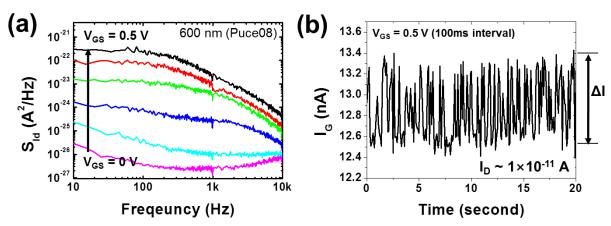

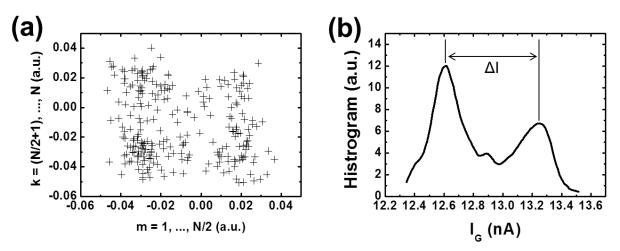

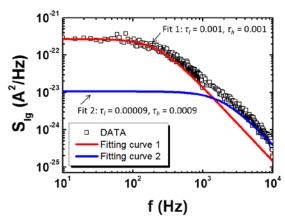

#### 3.2.4 Random-Telegraph-Signal noise

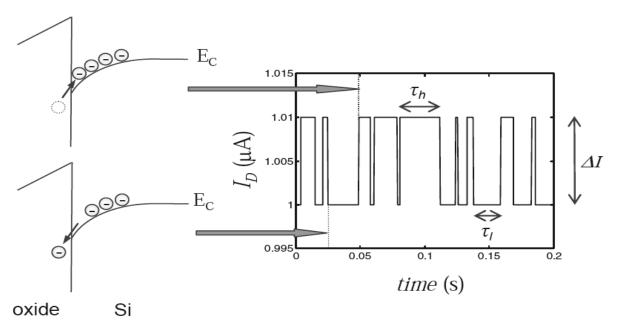

Figure 3.2 illustrates a schematic description of RTS noise in a MOS structure and the current waveform in time domain. Random-Telegraph-Signal (RTS) noise (also called burst noise, popcorn noise, impulse noise, and bi-stable noise) is an unusual case of g-r noise involving only few traps. The level of current will be between two or more states due to the random trapping and de-trapping of charge carriers. A simple two-level RTS noise can be observed in various types of semiconductor devices. Especially, RTS noise is common in

Figure 3.2 Schematic description of RTS noise in a MOS structure and a waveform of current in time domain [87].

small area MOS transistors and is correlated to individual carrier trapping at the silicon-oxide interface [88-90]. Likewise g-r noise, the PSD of RTS noise is a Lorentzian type and derived as

$$S_I(f) = \frac{4(\Delta I)^2}{(\tau_I + \tau_h)[(1/\tau_I + 1/\tau_h)^2 + (2\pi f)^2]}$$

(3.8)

where  $\tau_l$  and  $\tau_h$  are the time constant in the lower state and higher state, respectively and  $\Delta I$  is the difference of current between those two states (Figure 3.2). This type of noise is a good for study of a single trap activity in a system with few free carriers.

#### 3.2.5 1/f noise

1/f noise is generally also named flicker or excess noise with a PSD inversely proportional to the frequency f. It has been sometimes called low-frequency noise but it is not true strictly because other types of noise such as g-r or RTS noise can be observed in low-frequency region. Nevertheless, it is accepted since most of noise type is 1/f noise. In 1925, the 1/f noise was firstly found by J. Johnson in vacuum tubes and Schottky gave the first interpretation [91]. Since then, Christensen & Pearson found it for carbon microphones in 1936 and then the 1/f noise was also found in various semiconductor and semiconductor devices [92]. Up to now, a huge number of current noise spectra were measured with various materials such as semiconductors, semimetals, metals, superconductors, tunnel junctions, strongly disordered conductors, and etc. thereby the results, in practically all cases, appeared in a shape of an increase of current noise power spectrum as decreasing the frequency, 1/f. In general, 1/f noise is difficult to find at high frequency since it is finally hidden by thermal noise.

Even if 1/f noise is universal for various materials, there are still some controversies for the origin since many decades. Some major issues are as follows [93]: 1) Mobility vs. Number fluctuations, 2) Superposition of RTS noise for 1/f noise, and 3) Surface vs. Bulk origin.

1) Mobility vs. Number fluctuations: It is a well-known issue to understand the origin of 1/f noise. The current fluctuation in materials can be understood with the conductivity fluctuations since the conductivity is an inherent property which determines the device conductance. So, the conductivity  $\sigma$  is defined as

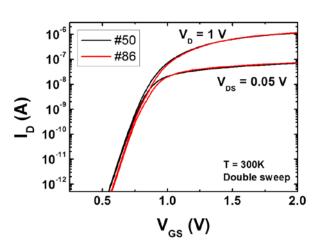

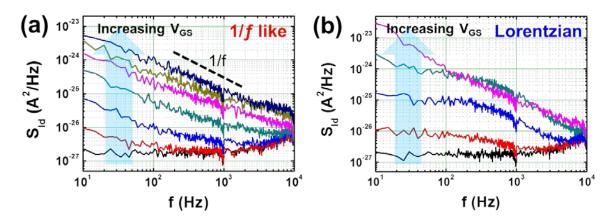

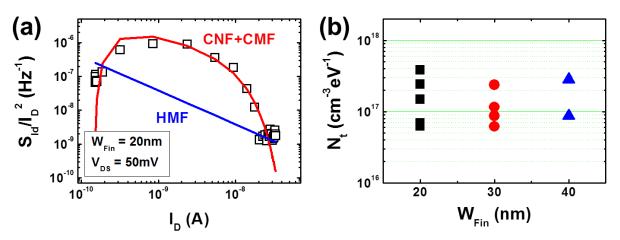

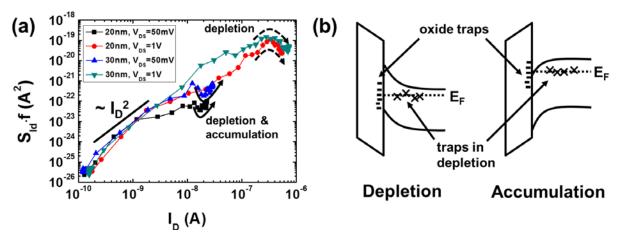

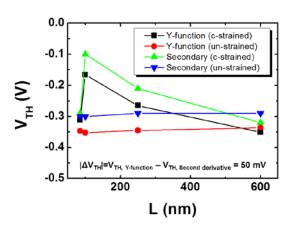

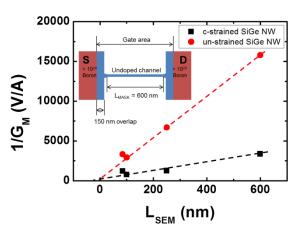

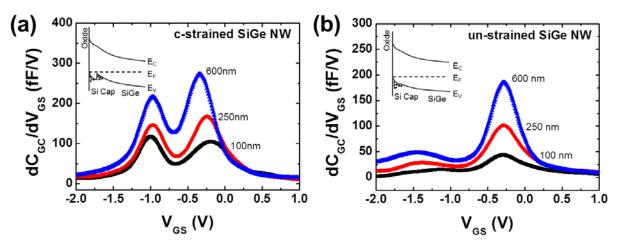

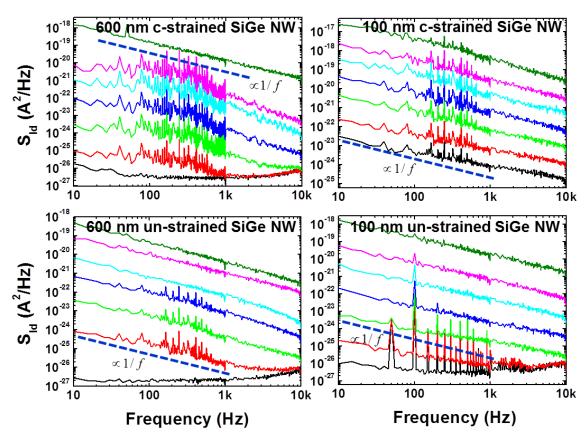

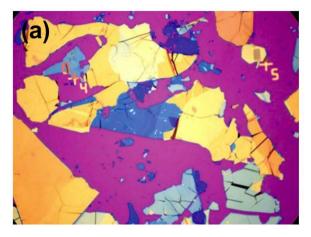

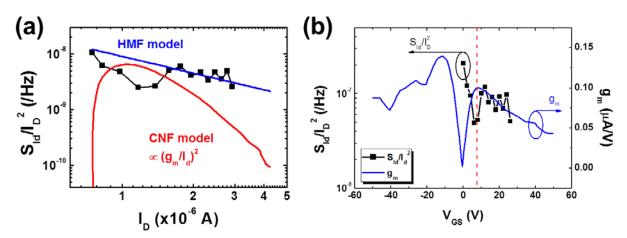

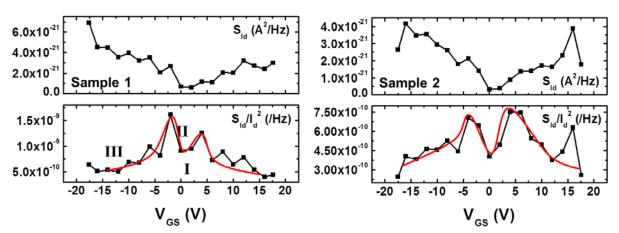

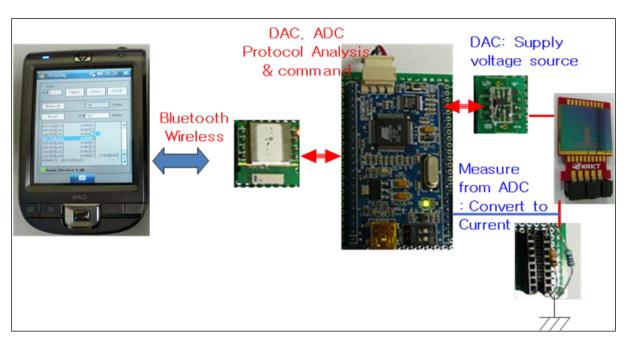

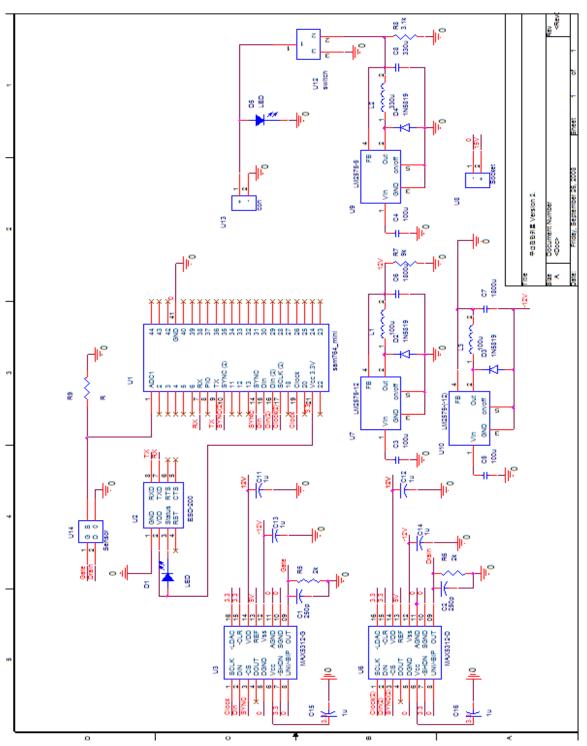

$$\sigma = qn\mu_{drift} \tag{3.9}$$