## Decoupled approaches to register and software controlled memory allocations

Boubacar Diouf

### ► To cite this version:

Boubacar Diouf. Decoupled approaches to register and software controlled memory allocations. Other [cs.OH]. Université Paris Sud - Paris XI, 2011. English. NNT: 2011PA112349 . tel-00769403

## HAL Id: tel-00769403 https://theses.hal.science/tel-00769403v1

Submitted on 1 Jan 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Decoupled Approaches to Register and Software-Controlled Memory Allocations

## THÈSE

présentée et soutenue publiquement le 15 Décembre 2011

pour l'obtention du

### Doctorat de l'Université de Paris-Sud

### Spécialité : informatique

par

M. Boubacar Diouf

### Composition du jury

| Président :    | Pr. Yannis MANOUSSAKIS                                            |

|----------------|-------------------------------------------------------------------|

| Rapporteurs :  | Pr. Pierre BOULET<br>Pr. Jingling XUE                             |

| Examinateurs : | Dr. Fabrice RASTELLO<br>Pr. Sebastian HACK<br>Dr. Florent BOUCHEZ |

Directeur de thèse : Pr. Albert Cohen

Mis en page avec la classe thloria.

### Remerciements

L'heure est venue de dire merci à tous ceux qui de près ou de loin m'ont soutenu, aidé ou encouragé durant ces années de thèse ou durant la redaction de ce manuscrit. Je suis conscient qu'il me faudrait sans doute l'équivalent d'un autre manuscrit pour remercier tout le monde monde et n'oublier personne. De ce fait, je tiens à remercier tous ceux dont les noms n'apparaissent pas dans ce document et qui m'ont, ne serait ce qu'une fois, aidé dans ma vie, même si ce fût par un petit sourire.

La première personne que je tiens à remercier est *Albert Cohen*, mon directeur de thèse, pour avoir accepté de diriger cette thèse. Je tiens aussi a le remercier pour toute la confiance qu'il m'a accordé, sa gentillesse et ses conseils.

Mes remerciements vont conjointement et tout particulièrement à M. Pierre Boulet, professeur à l'université Lille 1 et M. Xingling Xue, professeur à l'université de New South Wales en Australie, qui m'ont fait l'honneur d'être les rapporteurs de cette thèse. Le fait d'avoir des professeurs de leur qualité comme rapporteurs constitue pour moi une motivation et une satisfaction supplémentaire.

Je voudrais également remercier doublement M. Fabrice Rastello, chargé de recherche  $\tilde{A}$  l'ENS de Lyon, pour tous les conseils et critiques objectives qu'il m'a prodigué durant cette thèse, mais aussi pour avoir accepté d'examiner mon rapport de thèse.

Je voudrais également remercier M. Yannis Manoussakis, professeur à l'université Paris-Sud, M. Sebastian Hack, Professeur à l'université de Saarland et M. Florent Bouchez, Docteur-ingénieur à Kalray, pour avoir accepté d'examiner mon rapport de thèse et de faire partie de mon jury de thèse.

J'adresse mes remerciements les plus sincères à Taj et Arame pour les maux de tête que je leur ai causé lors de la relecture et de la correction de mon rapport de thèse.

Je voudrais remercier l'ensemble du personnel de l'INRIA et plus particulièrement Valèrie, Christine et Cédric pour leur apport positif lors des difficultés administratives ou logistiques que j'ai rencontrées.

Un grand merci à tous les membres de l'équipe Alchemy avec qui j'ai partagés des moments inoubliables durant toutes ces années de thèse : *Mounira*, *Taj*, *Mouad*, *Michael*, *Ryiadh*, *Sofiane*, *Zheng*, *Walid*, *Ramakrishna*, *Cédric*, *Luidnel*, *Konrad*, *Grigori Phillipe*, *Louis Noel*, *Olivier* et *Piotr*.

Je tiens aussi à remercier le club des veilleurs avec qui j'ai passé des moments sympatiques sur le parc club et au PCRI : *Lina* la veilleuse de nuit, *Rania* son adjointe et *Vincent* le matinal.

Je remercie toute ma famille, notamment Mon père Alioune, ma mère Fatoumata et

Ta Ba, mes frères Mao, Big Boss, Oussou, Moussa et Abib, ma soeur Fifi, mon cousin Seydina et ma belle soeur Fatou Diallo, pour leur irremplaçable et inconditionnel soutien. Il ne faudrait pas non plus que j'oublie mon voisin de colocation Mathieu, pour sa compréhension durant la rédaction et la préparation de la soutenance, et Zorro, pour son aide et son assistance en vue de la préparation de ma soutenance de thèse. Votre présence m'a permis de faire face aux difficultés, aux doutes et aux obstacles que j'ai pu rencontré.

J'aimerais à remercier toutes les personnes qui m'ont assisté durant mes travaux de recherche et d'écriture de cette thèse.

## $\bigcirc$

Merci à vous tous!

Je dédie cette thèse à ma mère Fatoumata Traoré, à mon père Alioune Diouf, à ma marraine Ta Ba, à mes nièces et neuveux, à qui j'ai donné le surnom de : The next generation, et à mon ami Cheikh Ada, notre voyage ensemble n'a pas duré bien longtemps. Puisse Dieu nous unir de nouveau dans ses hauts jardins iv

## Sommaire

| 1                | Allocation de Registres      |                                                                                                                      |  |  |  |

|------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

|                  | 1.1                          | Allocation de Registres Optimale Itérée                                                                              |  |  |  |

|                  | 1.2                          | Allocation de Registres Fractionnée                                                                                  |  |  |  |

| 2                | Allocation de Mémoire Locale |                                                                                                                      |  |  |  |

|                  | 2.1                          | Validation expérimentale                                                                                             |  |  |  |

|                  | 2.2                          | Etude théorique                                                                                                      |  |  |  |

| 3                | Allocat                      | tion par Clustering                                                                                                  |  |  |  |

|                  |                              |                                                                                                                      |  |  |  |

| Introduction xxi |                              |                                                                                                                      |  |  |  |

| 1                | Register Allocation          |                                                                                                                      |  |  |  |

|                  | 1.1                          | Spill Minimization                                                                                                   |  |  |  |

|                  | 1.2                          | Improvements of JIT Register Allocation                                                                              |  |  |  |

| 2                | 2 Local Memory Allocation    |                                                                                                                      |  |  |  |

|                  | 2.1                          | Link between Register and Local Memory Allocations                                                                   |  |  |  |

|                  | 2.2                          | The Local Memory Allocation Optimization Problem                                                                     |  |  |  |

| 3                | Outline                      |                                                                                                                      |  |  |  |

|                  | 3.1                          | Register Allocation $\ldots \ldots xxv$ |  |  |  |

|                  | 3.2                          | Local Memory Allocation                                                                                              |  |  |  |

|                  | 3.3                          | Reconciling Register and Local Memory Allocations 1                                                                  |  |  |  |

## I Register Allocation

\_

\_

| 0   |     |    |

|-----|-----|----|

| Som | mai | re |

| 1                           | Register Allocation5                   |                                                                                                   |    |  |

|-----------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------|----|--|

|                             | 1.1                                    | Introduction                                                                                      |    |  |

|                             | 1.2 Terminology                        |                                                                                                   |    |  |

|                             | 1.3                                    | 1.3 Aspects of the Optimization Problem                                                           |    |  |

|                             |                                        | 1.3.1 Complexity $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 11 |  |

|                             |                                        | 1.3.2 Register Allocation with Fixed Scheduling                                                   | 13 |  |

|                             | 1.4                                    | Graph Coloring                                                                                    | 13 |  |

|                             | 1.5                                    | Linear Scan                                                                                       | 17 |  |

|                             | 1.6                                    | Decoupled Register Allocation                                                                     | 20 |  |

|                             |                                        | 1.6.1 A first two-phase approach                                                                  | 20 |  |

|                             |                                        | 1.6.2 SSA-based Register Allocation                                                               | 20 |  |

|                             |                                        | 1.6.3 A Decoupled Linear Scan                                                                     | 22 |  |

|                             | 1.7                                    | Conclusion                                                                                        | 23 |  |

| <b>2</b>                    | Spli                                   | it Compilation 2                                                                                  | 25 |  |

|                             | 2.1                                    | Just-In-Time Compilation                                                                          | 26 |  |

|                             | 2.2 Annotations-Enhanced JIT Compilers |                                                                                                   |    |  |

|                             | 2.3                                    | Split Compilation                                                                                 | 28 |  |

|                             | 2.4                                    | Conclusion                                                                                        | 29 |  |

| 3 Split Register Allocation |                                        | it Register Allocation 3                                                                          | 81 |  |

|                             | 3.1                                    |                                                                                                   |    |  |

|                             |                                        | 3.1.1 A Case for Split Compilation                                                                | 31 |  |

|                             |                                        | 3.1.2 Outline of the chapter                                                                      | 32 |  |

|                             | 3.2                                    |                                                                                                   | 32 |  |

|                             |                                        | 3.2.1 Optimization Problem and Baseline Algorithm                                                 | 33 |  |

|                             |                                        | 3.2.2 The ILP Model                                                                               | 33 |  |

|                             |                                        | 3.2.3 Annotation Semantics                                                                        | 35 |  |

|                             |                                        | 3.2.4 The Offline Procedure                                                                       | 36 |  |

|                             |                                        | 3.2.5 The Online Procedure                                                                        | 38 |  |

|                             | 3.3                                    | Experimental Evaluation                                                                           | 39 |  |

|                             |                                        |                                                                                                   | 39 |  |

|                             |                                        |                                                                                                   | 10 |  |

|                             |                                        | 3.3.3 Portability Across Variations of the Register Count                                         | 12 |  |

|                             | 3.4                                    |                                                                                                   |    |  |

|   |      | 3.4.1 Portability of the Annotation                                                                                             |  |  |  |  |

|---|------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|   |      | 3.4.2 Separate Compilation                                                                                                      |  |  |  |  |

|   | 3.5  | Related Work                                                                                                                    |  |  |  |  |

|   | 3.6  | Conclusion                                                                                                                      |  |  |  |  |

|   |      |                                                                                                                                 |  |  |  |  |

| 4 | Iter | rated-Optimal Register Allocation 49                                                                                            |  |  |  |  |

|   | 4.1  | The Approach                                                                                                                    |  |  |  |  |

|   | 4.2  | Experimental Evaluation                                                                                                         |  |  |  |  |

|   |      | 4.2.1 Methodology $\ldots \ldots 51$ |  |  |  |  |

|   |      | 4.2.2 Results                                                                                                                   |  |  |  |  |

|   | 4.3  | Related Work                                                                                                                    |  |  |  |  |

|   | 4.4  | Conclusion                                                                                                                      |  |  |  |  |

|   |      |                                                                                                                                 |  |  |  |  |

## II Local Memory Allocation

57

| <b>5</b> | Loc                       | al Memories and Allocation Techniques            | 59 |

|----------|---------------------------|--------------------------------------------------|----|

|          | 5.1                       | Introduction                                     | 59 |

|          | 5.2                       | Static Allocation Methods                        | 61 |

|          | 5.3                       | Dynamic Allocation Methods                       | 62 |

|          | 5.4                       | Conclusion                                       | 64 |

| 6        | Mo                        | tivation and Approach to Local Memory Allocation | 65 |

|          | 6.1                       | Motivation                                       | 65 |

|          |                           | 6.1.1 Decoupled Allocation                       | 65 |

|          |                           | 6.1.2 Example                                    | 67 |

|          | 6.2                       | Our Approach to the Problem                      | 68 |

|          |                           | 6.2.1 Preliminary Analyses and Transformations   | 68 |

|          |                           | 6.2.2 Allocation Schemes                         | 70 |

|          | 6.3                       | .3 Related Work                                  |    |

|          | 6.4                       | Conclusion                                       | 72 |

| 7        | 7 Experimental Validation |                                                  | 73 |

|          | 7.1                       | Allocation                                       | 73 |

|          | 7.2                       | Assignment                                       | 77 |

|          | 7.3                       | Experimental Results                             | 79 |

### Sommaire

|     |                       | 7.3.1   | Setup                                                | 80 |

|-----|-----------------------|---------|------------------------------------------------------|----|

|     |                       | 7.3.2   | Results                                              | 80 |

|     | 7.4                   | Concl   | usion                                                | 81 |

| 8   | Dec                   | oupled  | l Local Memory Allocation for Linearized Programs    | 83 |

|     | 8.1                   | Weigh   | ted Graph Coloring and Local Memory Allocation       | 83 |

|     |                       | 8.1.1   | Weighted Graphs                                      | 83 |

|     |                       | 8.1.2   | Linearized Programs                                  | 84 |

|     |                       | 8.1.3   | Two Equivalent Classes                               | 85 |

|     | 8.2                   | Weigh   | ted Graph Coloring                                   | 86 |

|     |                       | 8.2.1   | The Ship-Building Problem                            | 86 |

|     |                       | 8.2.2   | The Submarine-Building Problem                       | 87 |

|     | 8.3                   | Weigh   | ted Proper Interval Graph Coloring                   | 89 |

|     |                       | 8.3.1   | Proper Interval Graph                                | 89 |

|     |                       | 8.3.2   | Proper Ordering                                      | 89 |

|     |                       | 8.3.3   | Decoupled Submarine-Building Problem                 | 90 |

|     | 8.4                   | Weigh   | ted Not-So-Proper Interval Graphs                    | 92 |

|     | 8.5                   | Exten   | sion to Weighted Interval Graphs                     | 94 |

|     | 8.6                   | Concl   | usion                                                | 94 |

| III | Rec                   | oncili  | ing Register and Local Memory Allocations            | 97 |

| 9   | $\mathbf{Th}\epsilon$ | e Clust | ering Allocator                                      | 99 |

|     |                       |         | Clustering Register Allocator                        | 99 |

|     |                       | 9.1.1   | Clustering of Variables                              |    |

|     |                       | 9.1.2   | Allocation and Assignment                            |    |

|     | 9.2                   | The C   | Clustering Local Memory Allocator                    |    |

|     |                       | 9.2.1   | Clustering of Array Blocks                           |    |

|     |                       | 9.2.2   | Allocation and Assignment                            |    |

|     | 9.3                   | Exper   | imental Evaluation                                   |    |

|     |                       | 9.3.1   | Register Allocation                                  |    |

|     |                       | 9.3.2   | Local Memory Allocation                              |    |

|     | 9.4                   |         | ssions about the Algorithm                           |    |

|     |                       | 9.4.1   | Practicability in the context of Register Allocation |    |

|                     | 9.4.2 Using the Clustering Allocator for Allocation only | 109 |  |

|---------------------|----------------------------------------------------------|-----|--|

| 9.5                 | Conclusion                                               | 10  |  |

| Conclu              | sion and Perspectives 1                                  | 11  |  |

| 1                   | Contributions                                            | 11  |  |

| 2                   | Perspectives                                             | 12  |  |

| List of Figures 114 |                                                          |     |  |

| List of Tables 116  |                                                          |     |  |

| Bibliography 117    |                                                          |     |  |

Sommaire

### Abstract

Register and local memory allocation are two important optimizations performed during compilation. The former optimization maps the variables of a program to either machine registers or main memory locations. The latter one maps arrays to either local memory or main memory locations. Recent work in register allocation leverages the complexity and performance benefits of decoupling its allocation and assignment phases.

In this thesis, we exploit the decoupled approach to propose a split register allocator, showing that linear complexity does not imply reduced code quality in just-in-time compilation, and to address the spill minimization problem. Considering the similarities between the register and local memory allocation problems, we study how a decoupled approach could be applied to the local memory allocation problem. We propose theoretical basis of such an approach, validate it experimentally and reset a bridge between the register and local memory allocation problems.

### Résumé

Les programmes informatiques sont souvent écrits dans des langages de haut niveau et puis traduit en code machine, une forme dans laquelle ils pourront être exécutés par les ordinateurs. Cette traduction est effectuée par un logiciel appelé, *compilateur*. Globalement le rôle d'un compilateur est de traduire un programme source en un programme cible sans en modifier la sémantique; il doit aussi signaler toutes les erreurs qu'il détecte durant le processus de traduction et essayer d'optimiser le code généré. Le programme cible peut être traduit en code machine ou dans un autre langage de programmation. Les optimisations effectuées, par le compilateur, cherchent à minimiser le temps d'execution, et ou, la taille du programme cible.

Le temps d'exécution d'un programme dépend du nombre d'instructions à exécuter mais aussi de la durée que prend chacune de ces instructions à s'exécuter. La durée d'exécution d'une instruction quant à elle peut varier d'une nanoseconde à plusieurs millisecondes selon le temps pris pour accéder aux données stockées dans la mémoire.

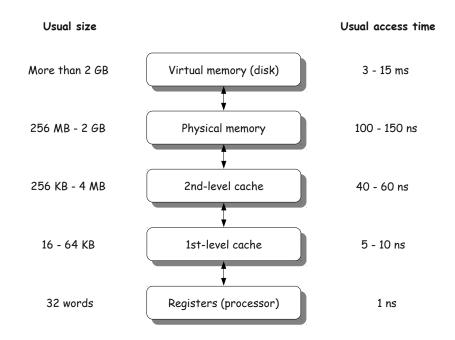

La variance dans les temps d'accès à la mémoire est due à une limitation technologique fondamentale: il est possible de concevoir des mémoires de petites capacités à accès rapide, il est aussi possible de concevoir des mémoires de grandes capacités à accès lent, mais il est impossible de concevoir des mémoires de grandes capacités à accès rapide. Il est impossible de fabriquer une mémoire de plusieurs giga-octets accessible en une nanoseconde, ce qui est la performance des processeurs hautes performances actuels. Pour réduire cette différence de performance entre le processeur et la mémoire, les ordinateurs modernes utilisent une *hierarchie mémoire*. Cela correspond à une organisation de la mémoire en plusieurs niveaux. Les mémoires rapides et de petites capacités sont placées à coté du processeurs, ce qui accèlére les accès, alors que celles de grandes capacités et lentes en sont éloignées.

La figure 1 est un exemple de hierarchie mémoire typique utilisée dans les ordinateurs modernes. Les unités mémoires les plus proches du processeurs sont les registres (situés dans le processeur) qui sont les plus rapides d'accès dans un ordinateur. Ensuite, nous avons une mémoire RAM statique (SRAM) de petite capacité, souvent configurée en un ou plusieurs niveaux de mémoire-cache, allant de quelques kilo-octets à plusieurs mega-octets. La mémoire physique ou mémoire principale allant de quelques centaines de mega-octets à plusieurs giga-octets, faite de mémoire RAM dynamique (DRAM) représente le niveau suivant. Enfin, le dernier niveau est formé par la mémoire virtuelle avec une capacité de plusieurs gigaoctets. Lorsqu'un accès mémoire survient, l'ordinateur cherche la donnée dans la mémoire la plus proche du processeur, et si la donnée ne s'y trouve pas, elle

Figure 1: La hierarchie mémoire

cherche dans le niveau supérieur et ainsi de suite.

Les mémoires SRAM sont généralement configurées comme des mémoires caches gérées par le matériel. Une seconde configuration possible est de les gérer de manière logicielle. Dans le cas d'une gestion logicielle les mémoires SRAM,  $mémoire(s) \ locale(s)$ , le développeur ou le compilateur insère explicitement des intructions pour transfèrer les données de la mémoire locale vers la mémoire principale. Les registres aussi, comme les mémoires locales, sont gérés de manière logicielle. Tous les autres niveaux de la mémoire sont gérés automatiquement.

Les registres sont les mémoires plus rapides d'accès, mais ils existent en trés petite quantité. Généralement toutes les variables d'un programme ne peuvent pas être stokées dans des registres. Les variables pour lesquelles il n'ya pas de registres disponibles sont stokées dans les couches supérieures de la mémoire qui sont plus éloignées du processeur, donc plus lentes. Pour réduire les accès à ces niveaux supérieurs, il convient donc d'utiliser au mieux les registres de la machine. Dans les compilateurs actuels, ce rôle est dédié à une optimisation appelée: *allocation de registres*. L'allocateur de registres attribue à chacune des variables du programme, soit un registre, soit un emplacement en mémoire. L'allocation de registres se décompose en deux étapes: *l'allocation* qui détermine à chaque point du programme l'ensemble des variables (variables allouées) qui seront stockées en registres et *l'assignation* qui choisit un registre spécifique pour chaque variable allouée.

De même que pour les registres, Il est important d'optimiser l'utilisation de la mémoire locale pour éviter d'accéder aux niveaux supérieurs de la mémoire, qui sont plus lents. Dans les compilateurs, l'optimisation en charge de la gestion de la mémoire locale est appelée *allocation de mémoire locale*. L'allocateur de mémoire locale selectionne l'ensemble des variables qui seront stockées dans la mémoire locale à chaque point du programme. Il choisit aussi pour chaque variable l'emplacement spécifique qu'il va occuper, soit en mémoire locale, soit en mémoire principale.

L'allocation de registres et l'allocation de mémoire locale sont deux problèmes qui sont NP-complets auxquels nous nous intéréssons dans cette thèse, qui est structurée en trois parties.

Dans la première partie de la thèse, nous nous penchons sur le problème de l'allocation de registres. Tout d'abord, nous proposons dans le contexte des compilateurs-juste-àtemps, une allocation de registres fractionnées, appelée *split register allocation*. Avec cette approche l'allocation de registres est effectuée en deux étapes: une faite durant la phase de compilation statique et l'autre pendant la phase de compilation dynamique. Ce qui permet de réduire le temps d'exécution des programmes avec un impact négligeable sur le temps de compilation. Ensuite Nous introduisons une allocation de registres incrémentale qui permet de résoudre d'une manière quasi-optimale le problème d'allocation. Cette méthode est pseudo-polynomiale alors que le problème d'allocation est NP- complet même à l'intérieur d'un "basic block".

Dans la deuxième partie de la thèse nous nous intéressons au problème de l'allocation de mémoire locale. Au vu des dernières avancées dans le domaine de l'allocation de registres, nous étudions dans quelle mesure le problème d'allocation pourrait être séparé de celui de l'assignation dans le contexte des mémoires locales. Dans un premier temps nous validons expérimentalement que les problèmes d'allocation et d'assignation peuvent être résolus séparément. Ensuite, nous procédons à une étude plus théorique d'une approche découplée de l'allocation de mémoire locale. Cela permet d'introduire de nouveaux résultats sur le "submarine-building problem", une variante du "ship-building problem", que nous avons défini. L'un de ces résultats met en évidence pour la première fois une différence de complexité (P vs. NP-complet) entre les graphes d'intervalles et les graphes d'intervalles unitaires.

Dans la troisième partie de la thèse nous proposons une nouvelle heuristique, appelée "clustering allocator" fondée sur la construction de sous-graphes stables d'un graphe d'interférence, permettant de découpler aussi bien le problème d'allocation pour les registres que pour les mémoires locales. Cette nouvelle heuristique se veut le pont qui permettra de réconcilier les problèmes d'allocations de registres et de mémoire locale.

## 1 Allocation de Registres

L'allocation de registres est un problème NP-complet. En effet, Chaitin et al. ont montré que le problème de l'existence d'une allocation sans spills (*sill-free*) est équivalent au problème de la coloration de graphe [CAC<sup>+</sup>81]. En plus, le problème de l'allocation de registres ne se limite pas uniquement au problème du "spill-free"; si la réponse au problème du "spill-free" est non, alors le but de l'allocation de registres est aussi de réduire l'impact des variables spillées sur le temps d'exécution du programme. Ce problème est connu sous le nom de, *minimisation des coûts de spills* ou *minimisation de spills*. Plusieurs heuristiques et techniques d'approximation au problème d'allocation de registres ont été proposé dans la litterature [CAC<sup>+</sup>81, BCT94, PS99, THS98, HGG06, PP08].

Dans cette première partie, nous proposons deux nouvelles techniques à savoir l'allocation de registres fractionnées, qui cherche à améliorer l'allocation de registres dans le contexte de la compilation *juste-à-temps* (JIT) et *l'allocation de registres optimale itérée* qui s'attaque au problème de la spill minimization.

### 1.1 Allocation de Registres Optimale Itérée

Les travaux en allocation de registres ont montré que lorsque les live ranges des variables sont assez finement découpés alors le problème de l'assignation devient quadratique dés lors qu'une allocation est possible. Il suffit juste que le nombre maximal de variable en vie en un point du programme soit inférieur au nombre de registres disponibles. Cependant le problème de la minimisation de spills demeure NP-complet même à l'intérieur d'un basic block [FCL00]. Les solutions proposées pour la résolution sont loin d'être optimales. Ce problème est d'autant plus important sur les machines CISC, où le nombre de registres est trés limité.

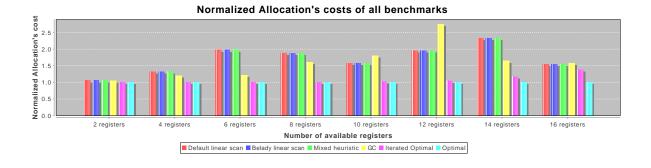

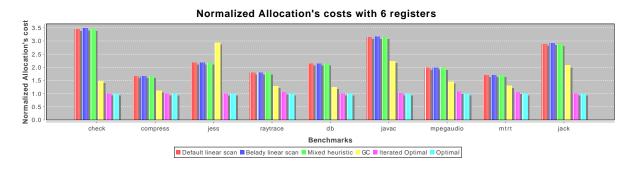

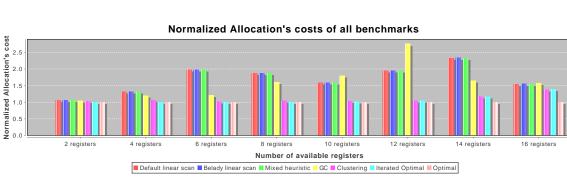

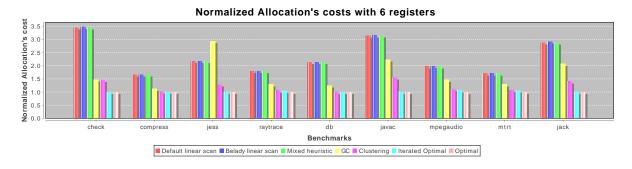

Nous nous sommes attaqués au problème de la minimisation de spills. Notre approche, appelée *allocation de registres optimale itérée*, permet de résoudre le problème d'allocation de manière quasi-optimale et ceci rapidement. Notre solution peut être utilisée dans un contexte découplé ou non. Nous avons comparé notre approche avec la coloration de graphe, le "linear scan", une nouvelle heuristique que nous avons conçu et appelé *heuristique mixte* et une allocation de registres optimale par programmation linéaire. Les résultats montrent que L'allocation de registres optimale itérée est souvent proche de l'allocation de registres optimale et produit de bien meilleurs résultats que les autres heuristiques. Un résultat trés intéréssant de notre approche est que, pour les programmes sous SSA, nous avons une garantie de pseudo-polynomialité.

### 1.2 Allocation de Registres Fractionnée

Dans le contexte de la compilation JIT, la compilation fait partie du processus global d'exécution des programmes. Ceci implique un compromis entre le temps de compilation, donc des optimisations et celui du temps d'exécution du code généré. En pratique, l'utilisation d'algorithmes de compléxité linéaire reste la régle pour la compilation JIT.

Notre approche de l'allocation de registres fractionnée montre qu'une compléxité linéaire n'implique pas forcément une réduction de la qualité du code généré. Notre approche est un exemple de compilation fractionnée, ou les analyses couteûses sont effectuées en avance pour guider des optimisations quasi-linéaires. Les informations collectées dans la phase hors-ligne de compilation statique, sont transmises à la phase en ligne, de compilation juste-à-temps, au moyen d'annotations de bytecode.

Notre allocateur de registres fractionnée garantie quatre propriétés: des annotations avec un impact minimal sur la taille du code, un traitement des annotations en temps linéaire, une perte minimale en qualité de code et la portabilité des annotations lorsque le nombre de registres disponibles varient. Nous avons implanté notre technique d'allocation de registres fractionnée dans JIkesRVM, la machine virtuelle de recherche d'IBM.

## 2 Allocation de Mémoire Locale

Dans la majorité des systèmes embarqués, les mémoires locales sont préférées au caches, du fait des garanties qu'elles offrent en prédictibilité, en adaptabilité (passage à l'échelle), en efficience énergétique, en rapidité d'accès aux données et du faible espace occupé sur la puce [BSL+02]. La predictibilité et une bonne consommation d'energie sont souvent essentielles aux applications temps réél et embarqués. D'autres processeurs plus spécialisés, tels que les "stream-processors et les processeurs graphiques, utilisent aussi les mémoires locales [NVI08, BPMR03].

Pour bien exploiter tout le potentiel des mémoires locales, il est essentiel de les utiliser de manière efficiente. Dans les compilateurs, cette tâche est à la charge d'une optimisation appelée allocation de mémoire locale. L'allocateur de mémoire locale selectionne l'ensemble des variables qui seront stockées dans la mémoire locale à chaque point du programme. Il choisit aussi pour chaque variable l'emplacement spécifique qu'il va occuper, soit en mémoire locale, soit en mémoire principale.

L'allocation de mémoire locale est un problème NP-complet [VWM04]. Les travaux précédants ont porté sur différents angles, ciblant aussi bien une allocation du code et des données du programme. Plusieurs heuristiques ont été proposées à la résolution du problème d'allocation de mémoire locale. [MFA01, VWM04, UDB06, LFX09, LXK11].

L'allocation de mémoire locale est connectée à l'allocation de registres depuis au moins 30 ans. En effet, dans son papier phare [Fab79], Fabri a démontré l'existence de liens forts entre les allocations de registres et de mémoire locale. Ces liens ont été sous-exploités depuis lors et par conséquant, les nouvelles avancées, réformant le design des "backend" des compilateurs, dans le domaine de l'allocation de registres ont été complétement ignorées en allocation de mémoire locale. Notre travail sur l'allocation de registres a été motivé par les récéntes avancées en allocation de registres et par la volonté de mieux comprendre le probléme d'optimisation.

#### 2.1 Validation expérimentale

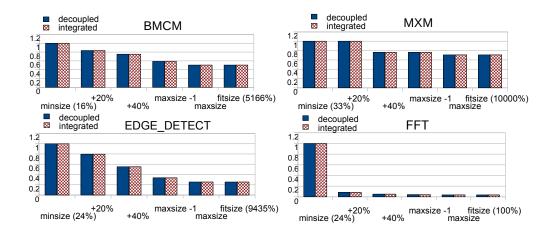

Pour valider notre intuition d'une approche découplée de l'allocation de mémoire locale, similairement à l'approche découplée en allocation de registres, nous avons exprimé l'allocation des tableaux en programmation linéaire pour résoudre le problème optimalement (en minimisant le coût des latences d'accès) en utilisant MAXSIZE comme critère. MAXSIZE est la taille maximale occupé par les tableaux en vie au même moment. Une fois le problème d'allocation résolu, la phase d'assignation se charge d'assigner aux tableaux alloués des emplacements dans la mémoire locale. Cependant, due à la possible fragmentation que la phase d'assignation peut entrainer, une solution du probléme d'allocation ne garantie pas forcément une solution au problème d'assignation. Néanmoins, nous avons expérimentalement montré, sur une série de benchmarks, que dés lors que le problème d'allocation admettait une solution alors le problème d'assignation aussi en admettait une sans spills supplémentaires.

### 2.2 Etude théorique

Aprés avoir expérimentalement validé une approche découplée de l'allocation de registres, nous avons pris une approche plus théorique qui a aboutit à des résultats fondamentaux dans le domaine de la gestion des mémoires locales par les compilateurs. Nous avons montré que la gestion des mémoires locales peut se modéliser comme un problème de coloration de graphes pondérés et nous avons étudié plusieurs variantes de ce problème. Ce qui a mené aux contributions suivantes:

- 1. L'introduction d'une nouvelle forme de coloration par intervalle que nous avons appelé "submarine-building".

- 2. Un nouvel algorithme linéaire et optimal résolvant le problème du "submarinebuilding" pour tout graphe d'intervalle propre et une preuve de NP-complétude de ce problème pour les graphes d'intervalle.

- 3. L'introduction d'un critère permettant de décider de la faisabilité ou non d'un problème de "submarine-building" sur les graphes d'intervalle propre. Lorsque le critère est satisfait, l'algorithme linéaire et optimal de résolution des problèmes "submarinebuilding" permet de résoudre le ship-building problème pour les graphes d'intervalle propre.

- 4. Nous exhibons pour la première fois un problème NP-complet pour les graphes d'intervalle et polynomial pour les graphes d'intervalle propre (qui sont équivalents aux graphes d'intervalle unitaire).

Les évaluations effectuées ont montré que l'approximation des graphes d'intervalle par des graphes d'intervalle propre ne fournit pas de très bons résultats. Ces résultats décevants nous ont poussé à la conception d'une nouvelle méthode heuristique de résolution du problème de la gestion des mémoire locale.

## 3 Allocation par Clustering

Notre étude théorique d'une approche découplée de l'allocation de mémoire locale a aboutit à des résultats encourageants. Cependant cette approche n'est pas encore assez mature pour qu'on puisse l'utiliser dans la pratique. De ce fait nous avons considéré une méthode heuristique que nous avons appelée, *clustering allocator*. Cette approche, bien qu'elle ait été conçue pour l'allocation de mémoire locale, fournit de trés bons résultats en allocation de registres. Donc après plusieurs année de séparation, le "clustering allocator" semble rétablir un pont entre les problèmes d'allocations de mémoire locale et de registres.

Le "clustering allocator" decouple les problème d'allocation et d'assignation et cherche à minimiser le coût de l'allocation par la construction de sous-graphes stables d'un graphe d'interférence. Durant la phase d'allocation, notre algorithme regroupe les variables par "clusters" qui seront alloués, ou spillés globalement.

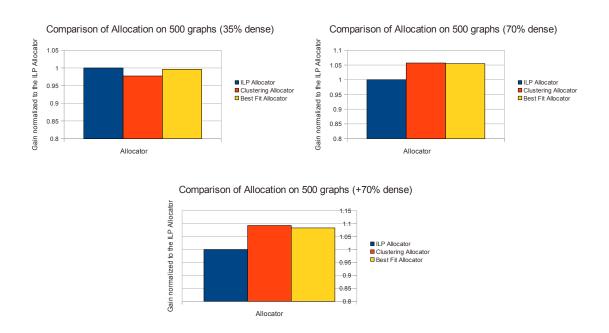

Pour les problèmes d'allocation de registres, le "clustering allocator fournit des résultats presques optimaux et est beaucoup plus performant que les autres heuristiques Pour les problèmes d'allocation de mèmoire locale, sur des graphes générés de manière aléatoire, nous obtenons de meilleurs résultats que l'algorithme du best-fit sur des graphes de densité moyenne à forte.

## Introduction

Programs running on computers are often written in high-level programming languages and then translated into an executable code, a form in which they can be executed by these computers. This translation is done by a software program, called a *compiler*. Globally, the role of a compiler is to translate a source program into a target program without changing the semantics of the source code; it must also report any errors that it detects during the translation and try to optimize the generated target code. The target program can be an executable code or a program written in another programming language. The optimizations, done by a compiler, try to minimize the execution time, and or, the size of the target program.

When a programmer compiles a program from a source language to an executable code, he wants the compiled one to conserve the source code's semantics. He also wants the code to run in an acceptable time. The execution time depends on the number of instructions to compute, and also on the computation time of each of these instructions. The computation time of an instruction can vary significantly, from nanoseconds to milliseconds, depending on the time taken to access data in memory.

The variance in memory access times is due to technological limitations: we can make small storage with fast access-time, we also can make large storage with slow access-time, but we cannot make large storage with fast access-time. It is impossible to make gigabytes of memory to be accessed in a nanosecond, the speed of high-performance processors. To reduce this performance gap between the processor and the memory, modern computers use a *memory hierarchy*. It corresponds to an organization of the memory into different levels of hierarchy. The faster and smaller levels of memory are placed closer to the processor, this speeds up access, and the slower and larger ones are placed farther from the processor.

Figure 1, taken from the "Dragon Book" [ALSU06], shows an example of a typical memory hierarchy in a modern computer. The closest memory level to the processor is composed of a few registers (located in the processor) that are accessed faster than any other kind of memory. Then, we have a small amount of on-chip *static RAM* (SRAM),

usually configured as one or many levels of hardware-managed cache, going from some kilobytes to many megabytes in size. The next level is the physical (main) memory, made of *dynamic RAM* (DRAM), going from hundreds of megabytes to many gigabytes. Finally, the last level in the hierarchy is the virtual memory with a size of many gigabytes. When a memory access occurs, the computer tries to find the data in the closest memory, and then if the data is not there, it tries in the higher level, and so on.

Figure 1: A typical memory hierarchy configuration, from the Dragon book [ALSU06]

The alternative approach to manage the SRAM is to configure it as a *software-controlled local memory*. In such an approach, the developer or the compiler must insert explicit instructions to transfer data between the local memory and the main memory. Like software-controlled local memories, registers also are managed by software. All the other levels of memory are managed automatically.

### **1** Register Allocation

Registers are the fastest type of memory within a computer. Registers are quickly accessed, but they exist in a very limited number. Usually, all the values of the executed code cannot reside in registers. The values not held in registers should reside in memory, which is farther from the processor and therefore slower to access. To reduce access to slower memory, it is essential to have an efficient usage of registers.

In all modern compilers, there is a phase called *register allocation* which optimizes the use of registers. The register allocator, in a phase called allocation, decides at each program point which variables will be held in registers (allocated variables) and which variables will be stored in memory; it also assigns each allocated variable to a register and maps to other variables a location in memory.

The register allocation is NP-complete. Indeed, Chaitin et al. have shown that the *spill-free* problem is equivalent to the graph coloring problem [CAC<sup>+</sup>81]. Moreover, register allocation is not bound to the spill-free problem; if the answer to the spill-free problem is no, the goal of register allocation is also to reduce the impact of the spilled variables on the execution time of the program (*spill cost minimization*). Many heuristics and approximation techniques have been proposed to solve register allocation [CAC<sup>+</sup>81, BCT94, PS99, THS98, HGG06, PP08].

In this thesis we are interested in two topics: the spill minimization problem and the improvement of the register allocation in the context of Just-in-time (JIT) compilation.

#### 1.1 Spill Minimization

Recent works in register allocation have shown that when enough live range splitting is allowed, the assignment problem can be solved in quadratic time as soon as the maximum number of simultaneously living variables is lower than the number of available registers. But unfortunately, the spill minimization problem (an allocation that minimizes the access latency) is still NP-complete even when enough live range splitting is allowed [FCL00]. The proposed solutions are far from being optimal. Thus, our aim is to propose good heuristics to solve this problem especially on systems like CISC machines where only few registers are available.

#### **1.2** Improvements of JIT Register Allocation

In the context of *Just-in-time* compilation, the compilation time is part of the global execution process. This implies a trade-off between the time spent for compilation (op-timizations) and the execution time of the produced code. In practice, (quasi-)linear complexity is the rule for JIT compilation. This severely impacts the aggressiveness of optimizations, like register allocation. We are interested in solutions that improve register allocation without lengthening the JIT compilation.

### 2 Local Memory Allocation

In most embedded systems, local memories are often preferred to caches due to their better performance and predictability, their power efficiency, and their smaller area cost [BSL+02]. Predictability of data access and power consumption efficiency are often essential to realtime and embedded applications. More specialized processors also utilize local memories, including stream-processing architectures such as graphical processors (GPUs) and network processors [NVI08, BPMR03].

To take advantage of all the potentials provided by local memories, it is essential to use them efficiently. Within a compiler, the optimization which performs this task is called *local memory allocation*. It selects the set of variables that will reside in the local memory at each point of the program. It also finds the specified place in the local memory or in the main memory where a variable will reside in.

The local memory allocation problem is NP-complete [VWM04]. Previous studies addressed local memory allocation from different angles, targeting both application/code and data. Many heuristics-based approaches to the problem have been proposed [MFA01, VWM04, UDB06, LFX09, LXK11].

Our work on local memory allocation is motivated by the recent advances in register allocation and the desire for a better understanding of the local memory optimization problem.

### 2.1 Link between Register and Local Memory Allocations

Compilation-time local memory allocation has been connected to register allocation for at least 30 years. Indeed, in her seminal paper [Fab79], Fabri reported strong links between register allocation and local memory allocation. This have been overlooked until very recently. As a result, the series of, fundamental and applied advances impacting the design of compiler backends have also been ignored in the field of local memory allocation [AG01, BDGR06a, HGG06, BDR07c, PP08].

### 2.2 The Local Memory Allocation Optimization Problem

While there exist many heuristics to the local memory allocation problem, theoretical foundations of the proposed heuristics are missing. More recently, Li et al. [LXK11] seriously improved the state of the art by proposing an approach to the problem, that has strong theoretical foundations. Nonetheless, little is known about the optimization problem, its complexity, and its interplay with other optimizations.

## 3 Outline

This dissertation is divided into three parts. The first part is devoted to register allocation, the second one tries to see in which context the fundamental advances in register allocation could be extended to local memory allocation, and the third one aims to rebuild a bridge between the domains of register and local memory allocations.

### 3.1 Register Allocation

In Chapter 1, we present the state of the art in register allocation. We introduce the terminology and the essential notions needed to understand register allocation. We describe the graph coloring and the linear scan approaches to register allocation and we show how separating the allocation phase from the assignment helps to ease and improve the register allocation.

In Chapter 2, we recall the approaches used to process programming languages: static compilation, interpretation, and JIT-compilation. We also introduce *split compilation* and show how it improves the quality of the code generated by JIT compilers.

In Chapter 3, we introduce the *split register allocation* which leverages the decoupled approach to improve register allocation in the context of JIT compilation. We experimentally validate the effectiveness of split register allocation and its portability with respect to register count variations, relying on annotations whose impact on the bytecode size is negligible.

Chapter 4 introduces a new decoupled approach, called *iterated-optimal allocation*, to register allocation. The iterated-optimal allocation algorithm achieves results close to optimal while offering pseudo-polynomial guarantees for SSA programs and fast allocations on general programs.

### 3.2 Local Memory Allocation

Chapter 5 sets the state of the art in local memory allocation. We introduce in this chapter static and dynamic methods for local memory allocation.

In Chapter 6, we explain the motivation of our work on local memory allocation. We also expose our approach to the problem, the preliminary assumptions we have made and our methodology to evaluate and compare our work.

Chapter 7 validates our intuition for decoupled approach to local memory allocation. It shows experimentally that after an optimal allocation phase relying on a generic and scalable integer linear program, the assignment phase could be achieved without any

#### 3. Outline

fragmentation-induced spills.

In Chapter 8, reinforced by results of Chapter 7, we study the local memory allocation in a more theoretical way setting the junction between local memory allocation for linearized programs and weighted interval graph coloring. We design and analyze a new variant of the *ship-building* problem called the *submarine-building* problem. We show that this problem is NP-complete on interval graphs, while it is solvable in linear time for proper interval graphs. We also give a criterion to guarantee the feasibility of the submarine-building problems for proper interval graphs and then we extend it to an extension of the class of proper interval graphs interval graphs. Our results show that while our approach represents an improvement over state of the art methods, it is limited so far in its practical application.

### 3.3 Reconciling Register and Local Memory Allocations

In Chapter 9, we propose a heuristic-based solution, the *clustering allocator*, which decouples the local memory allocation problem and aims to minimize the allocation cost. The clustering allocator while devised for local memory allocation, appears to be a very good solution to the register allocation problem. For register allocation, the results show that the clustering allocator outperforms both graph coloring and linear scan and is often close to the optimal solution. For local memory allocation the results are not as good as those for register allocation, but we do believe that the clustering allocator can be improved.

Introduction

# Part I

# **Register** Allocation

## Chapter 1

## **Register Allocation**

## 1.1 Introduction

When a programmer compiles a program from a source language to an executable code, he wants the compiled one to conserve the source code's semantics. He also wants the code to run in an acceptable time. The execution time depends on the number of instructions to compute, and also on the computation time of each of these instructions. The computation time of an instruction can vary significantly, from nanoseconds to milliseconds, depending on the time taken to access data in memory.

In a modern computer, it does not take more than one cycle of the CPU clock to read or write data into a register, while reading the data, from the cache or the main memory, is an order of magnitude slower. Registers are quickly accessed, but they exist in a very limited number. A 32-bit x86 architecture has only 8 general-purpose registers, ARM and PowerPC processors typically have 32 registers. Usually, all the values of the executed code cannot reside in registers. The values not held in registers should reside in memory. To reduce accesses to higher levels of memory it is essential to have an efficient usage of registers. Registers are software managed whereas all the other levels of the hierarchy are managed automatically. The management of the registers is done by the programmer, the application, or the compiler.

In all modern compilers, there is a phase called *register allocation* which optimizes the use of registers. The *register allocation* is usually one of the last phases of the compilation. It happens when all the candidate variables to register allocation are known. These candidate variables are composed of the variables already present in the source code and of the temporaries generated during preceding phases of compilation. The register allocation is defined [ALSU06] as the problem which is often subdivided into two sub-problems:

- 1. the *allocation* which selects the set of variables that will reside in registers at each point of the program.

- 2. the *assignment* which picks the specified register where a variable will reside in.

The variables mapped to registers are called *allocated variables* and the rest, stored in memory, are called *spilled variables*.

| a := 2                         | r1 := 2                       |

|--------------------------------|-------------------------------|

| b :=10                         | r2 := 10                      |

| a := a * b                     | r1 := r1 * r2                 |

| c := a - b                     | r3 := r1 - r2                 |

|                                |                               |

| (a) Before register allocation | (b) After register allocation |

Figure 1.1: An example of register allocation

Figure 1.1 (b) gives an example of register allocation for the code shown in Figure 1.1 (a). Assuming that three registers, r1, r2 and r3 are available, the variables a, b and c are assigned respectively to registers r1, r2, and r3.

In this chapter, we intend to present the state of the art in register allocation. Section 1.2 introduces the terms and notions necessary to understand register allocation. Section 1.3 presents some aspects of the register allocation problem, with a sub-section on its complexity. Then, Sections 1.4 and 1.5 present respectively graph coloring and linear scan as two approaches to register allocation; the former is the dominant approach, and the latter is an alternative mostly implemented in just-in-time compilers. Finally, Section 1.6 presents a new approach to register allocation which decouples its allocation and assignment phases.

### 1.2 Terminology

We set here the meaning of some terms and notions needed or used in register allocation.

**Basic Block.** A basic block is a maximal sequence of instructions with the following properties:

• it has a unique entry point as its first instruction. Any instruction within the basic block but this entry point cannot be a destination of a jump instruction.

#### 1.2. Terminology

• it has a unique exit point as its last instruction, meaning that no instruction but the last one can cause to leave the block.

Within a basic block, when the first instruction is executed all the other instructions of the basic block are executed.

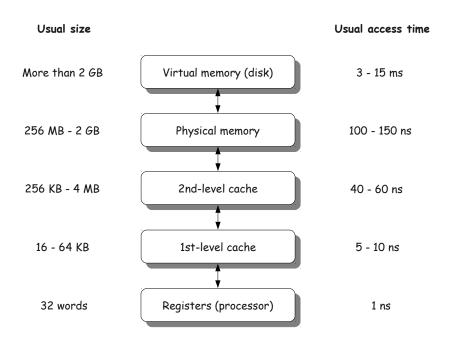

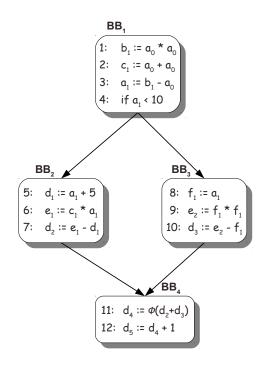

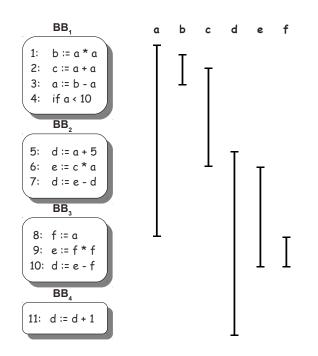

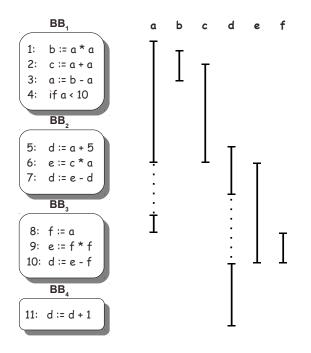

Figure 1.2(b) shows an example of four basic blocks:  $BB_1$ ,  $BB_2$ ,  $BB_3$  and  $BB_4$ .

**Control-flow graph.** A control-flow graph is an intermediate representation describing all the possible sequencing of instructions that may occur during the execution of the program. It is a directed graph where each node is a basic block. There is an edge from the basic block B to the basic block C, if the first instruction of C can follow immediately the last instruction of B. B is called a predecessor of C and C is called a successor of B. A control-flow graph must have a unique entry point and a unique exit point. That is why often an *entry block* and an *exit block* are added to the control-flow graph.

Figure 1.2: The control-flow graph of an example program.

Figure 1.2(b) shows the control-flow graph of the portion of code given in Figure 1.2(a).

**Dominators.** A node d of a control-flow graph dominates a node n if every path of directed edges from  $s_0$ , the entry point, to n must go through d [AP02]. Every node dominates itself. An *immediate dominator idom*(n) of n is a basic block that dominates

n and that is also dominated by any other basic block d that dominates n. A basic block cannot be its own immediate dominator. The graph containing every node of the control-flow graph, and for every node n and edge from idom(n) to n is called the *dominator tree*. It is a tree because each node has exactly one immediate dominator.

**Liveness.** We say that a variable v is *defined* by an instruction if it is a result of that instruction. We also say that it is *used* by an instruction if it is read by that instruction. Notice that a variable can be defined and used by the same instruction. For instance, the variable b in Figure 1.2(b) is defined by the first instruction. The variable d is re-defined and used by the instruction number 7. A variable v is said to be *live* at the point p if there exists a path in the control-flow graph from p to the exit point where v is used without being re-defined.

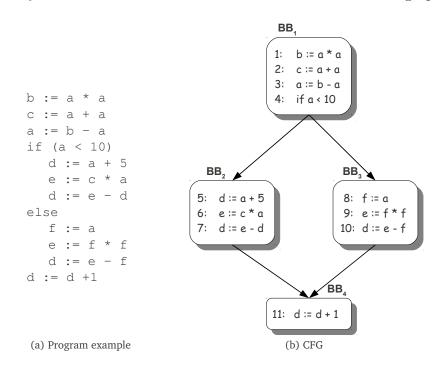

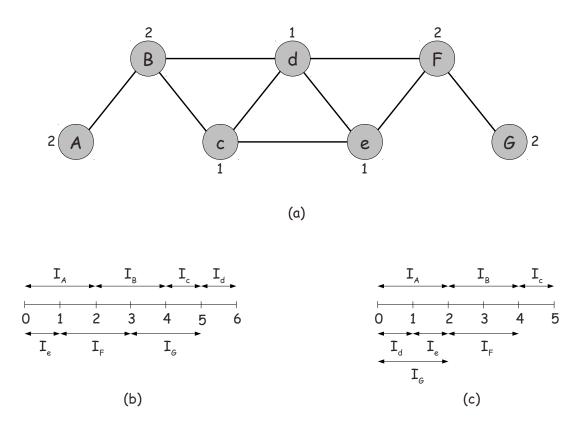

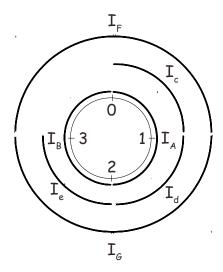

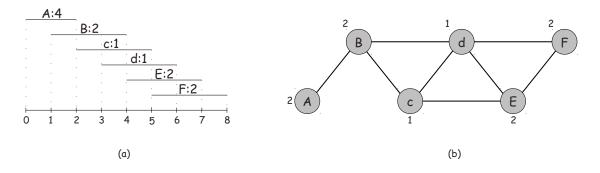

Live range. The *live range* of a variable v is the list of program points where it is live. Figure 1.3 shows the live ranges of the variables of the example program given in Figure 1.2(a). The variable a is supposed to be live in, which means it is live at the beginning of the basic block, it stays live until it is read, by the instruction 6 if the left branch is taken, and the instruction 8 if the right branch is taken. By abuse of terminology in this dissertation, as it is common in the literature, we sometimes use the term live range to designate the variable it refers to.

**Interference.** Two variables *interfere* if the intersection of their live ranges is nonempty. Two interfering variables cannot share the same register because this will cause one of them to overwrite the content of the other. The variables a and b interfere because their live ranges represented in Figure 1.3 intersect, whereas the variables d and f do not.

**Spilling.** An essential notion to register allocation is *spilling*. It is frequent that the number of available registers in an architecture cannot map all the variables of a program. Therefore, it is sometimes necessary to have some variables that remain in the memory. We say that these variables are spilled. In certain architectures, e.g., RISC architecture, memory can only be accessed through load and store instructions. This means that to use a variable v at address a, we need to load the value at address a (which is the value of v) into a register and then use this register as an operand. Thus, even if a variable is spilled, it must be loaded into a register from memory before each of its use, and stored from a register after each of its definition, and the added instructions are called *spill code*. In architectures like x86, an instruction's operand can be directly accessed from

#### 1.2. Terminology

Figure 1.3: The variables's live ranges in Figure 1.2(a).

memory. It means that to manipulate a variable v at address a in the memory, we can use a as an operand to directly use or define v. Such a kind of operand is called a *memory operand*. But even for these architectures, some restrictions may exist, for instance on IA-32 architectures, move instructions cannot have more than one memory operand.

**Coalescing.** Two variables related by a copy instruction and which do not interfere can be assigned to the same register. That is, the copy instruction becomes useless and can be safely removed. We say that these two variables are *coalesced*. A good register allocator will also strive as most as possible to coalesce variables that can be coalesced, because it will improve the quality of the generated code. For illustration, the variables a and f in Figure 1.3 should be coalesced, by looking at instruction 8.

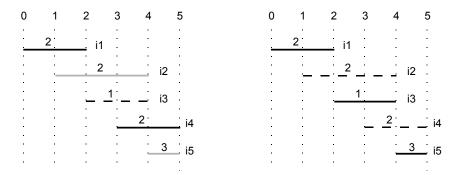

Live range splitting. A variable v live at two different instructions i1 and i2 can be split into two separate variables renamed  $v_1$  live at instruction  $i_1$  and  $v_2$  live  $i_2$ . To avoid changing the semantics of the program, sometimes it is necessary to join instructions  $v_1$ and  $v_2$ , with a copy instruction from  $v_1$  to  $v_2$ . This process of splitting the variable vis called *live range splitting*. The live range of a variable v can be very long and can have a non-empty intersection with many other variables's live ranges. Splitting the live range of such kind of variables tends to reduce the interference between variables and thus minimizes the number of registers required by a program.

Static Single-Assignment (SSA) Form. The SSA form is an intermediate representation in which each variable has only one definition in the program text [AP02, CFR<sup>+</sup>91, RWZ88]. The SSA form facilitates many other optimizations like constant propagation, dead code elimination, and register allocation, as we will see later. In straight line code (e.g. in a basic block), which is a code without control-flow, each definition of a variable v is given a new name such as  $(v_1, v_2, ...)$ , and each use of a variable v is renamed to the most recently defined version of the variable. In programs with control-flows, With two control-flow paths merging together, a special form of variable's definition called  $\phi$ -function, is inserted.

Figure 1.4: The program in 1.2(a) in SSA form.

In Figure 1.4, a  $\phi$ -function is inserted at the beginning of the basic block  $BB_4$ . The variable  $d_2$  and  $d_3$  used as the operands of the  $\phi$ -function indicate which definitions of d reach the join node. Subsequent uses of the variable d are replaced with uses of the variable  $d_4$ . The  $\phi$ -functions do not correspond to hardware instructions and after the optimizations have been done upon it, a program in SSA form must be translated into an executable representation without  $\phi$ -functions.

## 1.3 Aspects of the Optimization Problem

The scope of register allocation can be local, global, or interprocedural. It is *local* when it is restricted to a basic block, *global* when it is performed over a procedure or a method, and *interprocedural* when it is performed across multiple procedures. Register allocation has been performed since the first compiler for FORTRAN. It has been widely studied and shown to be NP-complete. It has also been shown to have strong interactions with the instruction scheduling optimization.

Depending on the trade-off between the difficulty of the register allocation problem and the quality of the solution of the problem (memory-access-latency minimization). We can identify at least three types of problems that can be considered:

- **Spill everywhere.** It corresponds to the coarser grain of the register allocation problem, where the live range of each variable is viewed as an atom [PS99], there is no live range splitting. In this context, a variable cannot be spilled at some part of the code and allocated at some other part: it is spilled everywhere. This approach does not give best results but it is simple and when compile time is in concern like in JIT compilers, it can be well suited.

- **Register allocation with live range splitting.** This approach is finer than the first one. The live range of a variable can be split at some points, for instance, at points where variables are redefined or spilled (to avoid loosing previous assignment). In this context, a variable can be assigned to a register  $r_1$  sometimes and spilled or allocated to another register  $r_2$  at a different moment. This second approach is harder but superior to the first one and SSA-based techniques and recent work on register allocation focus on it[THS98, HGG06, BDR07a].

- Load-store optimization. The third approach of the finest granularity. The goal is to optimize each load and store separately in order to minimize the memory access time. In this context, the variables's live ranges can be split between every two instructions that can be consecutive [AG01]. This approach gives much better results than the two preceding level of granularity, but it is also harder to solve.

## 1.3.1 Complexity

Register allocation is a NP-hard problem. Indeed, Chaitin et al. have shown that the *spill-free* problem is equivalent to the graph coloring problem [CAC+81]. Moreover, register allocation is not only bounded to the spill-free problem; if the answer to the spill-free

problem is no, the goal of register allocation is also to reduce the impact of the spilled variables on the execution time of the program (*spill minimization*). In addition to this, register allocation usually removes useless copy instructions in order to minimize the execution time of the program (coalescing problem). Register allocation also needs to handle some irregularities in the underlying architecture, like register *aliasing* and variable's *pre-coloring*.

**Spill-free problem.** Given k available registers and n variables that are candidates to register allocation, the spill-free problem answers the question of whether or not it is possible to assign the n variables to registers without any spilling. For general programs, this problem is equivalent to the graph coloring problem and is hence NP-complete [CAC<sup>+</sup>81].

Spill-cost (or spill) minimization problem. When all or part of a variable v in a program is spilled, it may impact on the execution time of the program because of the spill code insertion. If we assume that a store has a cost and a load has a cost too, then it is possible to compute the cost of the spilled variables. The spill minimization is the problem of minimizing the cost of the spilled variables for a register allocation problem. This problem becomes NP-complete even for local register allocation as soon as stores have positive cost [FCL00, LFCK99].

**Coalescing problem.** The coalescing reduces the cost of move instructions between variables that do not interfere. The problem of looking for an allocation of minimal cost (where each pair of coalescable variables has been assigned a cost) is NP-complete [BDR07b].

Aliasing problem. When an assignment to a register name can affect the content of another register name, such register names are said to alias. As shown in Figure 1.5, in the IA-32 architecture, the two lower bytes of the 32-bit general-purpose registers EAX and EBX can be referenced with names AX and BX. The first byte of AX and BX can be respectively referenced with AH and BL (high bytes) and their last bytes can be referenced with AL and BL (low bytes). In this example the register names EAX and AX, EAX and AH, or AX and AL alias. Lee et al. [LPP08] show that aliased register allocation is NP-complete even for straight-line programs, which are very simple programs without control-flows.

**Pre-coloring problem.** We say that a variable is pre-colored if it must be assigned to a register due to some architectural constraints. For instance, in many architectures,

Figure 1.5: An example of aliasing registers's names

registers are used to pass parameters during function and procedure calls. Such kind of conventions force the first k arguments of the called function to be assigned to the k registers reserved for that purpose. Register allocation with pre-colored variables is equivalent to the coloring extension problem. Biro et al. [BHT92] demonstrate that the coloring extension problem is NP-complete for interval graphs, and thus, for register allocation with pre-colored variables.

## 1.3.2 Register Allocation with Fixed Scheduling

Register allocation is not the only optimization performed by the compiler. It is part of a flow of optimizations which may impact on each other. In particular, it has strong interactions with *instruction scheduling* optimization. The instruction scheduling is used to increase the *Instruction Level-Parallelism* (the number of simultaneously executed instructions during a computer cycle). It looks for an ordering capable of improving the instruction level-parallelism.

Instruction scheduling can be done before or after register allocation. If it is done before register allocation, it can increase the number of needed registers and make the code harder to color. If it is done after register allocation, some ordering opportunities may then turn impossible due to the performed register allocation. The interplay between these two problems have been studied and many approaches that consider both of these two problems have been proposed in the literature [TE04b, BEH91, NP95]. Register allocation with instruction scheduling considerations is beyond the scope of this dissertation: we assume that we have a fixed scheduling.

## 1.4 Graph Coloring

The graph coloring is the dominant approach to register allocation. The idea of abstracting the register allocation problem to a graph coloring problem dates from the early 1960s [SL62]. The first graph coloring framework for register allocation has been implemented by Chaitin et al. [Cha82, CAC<sup>+</sup>81]. We need first to introduce some terms about graphs before presenting the graph coloring approach to register allocation.

A graph G = (V, E) consists of two sets, V the set of vertices or nodes, and E the set of edges. Every edge  $(v_1, v_2)$  of E has two end points  $v_1 \in V$  and  $v_2 \in V$ . We say that  $v_1$  and  $v_2$  are adjacent(s) or are neighbor(s) if  $(v_1, v_2) \in E$ . The number of neighbors of a vertex v is called the *degree* of v. Here, We only consider *undirected* graphs, i.e., we do not make difference between the edges  $(v_1, v_2)$  and  $(v_2, v_1)$ .

A clique is a set of vertices, where every pair of distinct vertices is adjacent. A clique is maximum if there is no clique of G of larger cardinality. The number of vertices in a maximum clique of G is denoted  $\omega(G)$  and is called the clique number of G.

A vertex coloring (or coloring) of a graph G is a function C that maps each vertex v of G into a color  $c_v$  such that adjacent vertices are mapped to different colors. We say that I is a k-coloring of G, if the number of colors used to color G is equal to k. The chromatic number  $\chi(G)$  is the smallest k for which it is possible to find a k-coloring of G. A proper coloring of a maximum clique A of G requires at least  $\omega(G)$  colors, because otherwise there will be at least two vertices of A having the same color. Hence, for any graph G we always have:  $\omega(G) \leq \chi(G)$ .

The technique presented here abstracts the register allocation to an *interference graph* coloring problem. The interference graph G of a given program is the intersection graph of the variables's live ranges in that program. Each variable is represented by a vertex in G and the vertices of two interfering variables are adjacent in G. If we consider each register as a color, thus for a given program, the register allocation problem corresponds to a graph coloring problem.

Chaitin et al. use the Kempe's heuristic to color the interference graph. Given a graph G and k available colors, the heuristic tries to find a k-coloring of G. Assume that there exists a node n in G of low degree, that is, a node which has less than k neighbors. From a k-coloring of  $G - \{n\}$ , it is easy to find a k-coloring of G, it suffices to assign to n a color that differs from the colors of its neighbors. Thus, n is always colorable and G is k-colorable if  $G - \{n\}$  is k-colorable. The node n can be removed (with its edges) from G and placed on a stack. When n is removed from G, the dregrees of its neighbors are lowered and this may turn some of its neighbors into low degree nodes in the new graph and prove that they are colorable. If this procedure can be iterated until the graph becomes empty, then G is showed to be k-colorable. To color G, it suffices to pop nodes from the stack, to insert them back into the graph and to map them to colors (the reverse order of their removal). A node n popped from the stack is inserted into the graph and the edges removed at the moment of its removal are restored. It is mapped to a color

different from all its current neighbors, though it can have some other neighbors not yet re-inserted into the graph.

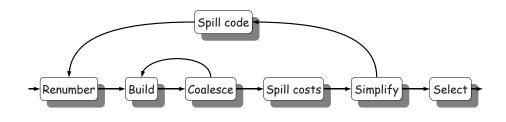

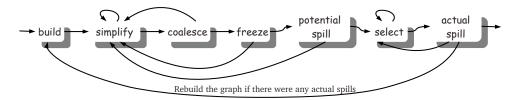

The allocator proposed by Chaitin et al. handles both spill code insertion and coalescing. The principal phases of this allocator are:

- **Renumber** performs live ranges splitting. Each variable v is renamed every time it is defined. It creates a new sub-variable  $v_i$  for each definition of v. At each use point of v, it merges together the  $v_i$  of v that reach the use. At the end of this process, each variable v is represented by a set of sub-variables called *names*.

- Build constructs the interference graph where each node represents a name.

- **Coalesce** removes unnecessary move instructions. Two names that do not interfere and that are related by a move instruction are coalesced into one node adjacent to the neighbors of the nodes being replaced. When no more coalescing is possible, the graph is re-build to trigger new opportunities for coalescing. The *Build* and *Coalesce* phases are repeated until no more coalescing is possible.

- **Spill costs** computes the cost of spilling each name. The cost of spilling a name is an estimation of the impact of spilling it on the execution time of the program.

- **Simplify** finds the set of nodes to be colored and order them. It first constructs an empty stack and looks repeatedly for a low degree node:

- 1. if such a node exists, it removes it from the graph and pushes it on the stack.

- 2. otherwise, all nodes are of significant degree  $(degree \ge k)$  and it chooses according to the spill costs a node to spill and removes it from the graph.

This procedure is repeated until the graph becomes empty.

**Spill Code** inserts loads and stores instructions if some nodes have been spilled during the simplification phase. For each spilled name n, it adds a load instruction before every use of n and a store instruction after every definition of n. Thus, n will be replaced into a collection of new names with tiny live ranges. Hopefully, due to their tiny live ranges, these new names will not interfere with several other names. After this step, the whole procedure is restarted from *Renumber*. These iterations from *Renumber* to *Simplify* are repeated until no node is spilled. But, in practice one or two iterations often suffice.