# Development of algorithms and architectures for driving assistance in adverse weather conditions using FPGAs

Diego Andres Botero Galeano

# ▶ To cite this version:

Diego Andres Botero Galeano. Development of algorithms and architectures for driving assistance in adverse weather conditions using FPGAs. Automatic. INSA de Toulouse, 2012. English. NNT: 2012ISAT0062. tel-00771869v2

# HAL Id: tel-00771869 https://theses.hal.science/tel-00771869v2

Submitted on 8 Apr 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### En vue de l'obtention du

# **DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE**

**Délivré par** *Institute National de Sciences Appliquées (INSA)* Discipline ou spécialité : Systèmes Embarqués et Robotique

Présentée et soutenue par Diego Andrés BOTERO GALEANO Le 5 décembre 2012

**Titre:** Development of algorithms and architectures for driving assistance in adverse weather conditions using FPGAs

#### Directeurs de Thèse :

Michel DEVY Jean-Louis BOIZARD

#### **JURY** Président :

Jean-Yves FOURNIOLS

## Rapporteurs:

François BERRY Ricardo CARMONA

# **Examinateurs:**

Johel MITERAN Jonathan PIAT Richard KLEIHORST

**Ecole doctorale :** Ecole Doctorale Systèmes (EDSYS)

Unité de recherche : Laboratoire d'Analyse et d'Architecture de Systèmes (LAAS)

# Résumé

En raison de l'augmentation du volume et de la complexité des systèmes de transport, de nouveaux systèmes avancés d'assistance à la conduite (ADAS) sont étudiés dans de nombreuses entreprises, laboratoires et universités. Ces systèmes comprennent des algorithmes avec des techniques qui ont été étudiés au cours des dernières décennies, comme la localisation et cartographie simultanées (SLAM), détection d'obstacles, la vision stéréoscopique, etc. Grâce aux progrès de l'électronique, de la robotique et de plusieurs autres domaines, de nouveaux systèmes embarqués sont développés pour garantir la sécurité des utilisateurs de ces systèmes critiques.

Pour la plupart de ces systèmes, une faible consommation d'énergie ainsi qu'une taille réduite sont nécessaires. Cela crée la contrainte d'exécuter les algorithmes sur les systèmes embarqués avec des ressources limitées. Dans la plupart des algorithmes, en particulier pour la vision par ordinateur, une grande quantité de données doivent être traitées à des fréquences élevées, ce qui exige des ressources informatiques importantes. Un FPGA satisfait cette exigence, son architecture parallèle combinée à sa faible consommation d'énergie et la souplesse pour les programmer permet de développer et d'exécuter des algorithmes plus efficacement que sur d'autres plateformes de traitement.

Les composants virtuels développés dans cette thèse ont été utilisés dans trois différents projets: PICASSO (vision stéréoscopique), COMMROB (détection d'obstacles à partir d'une système multicaméra) et SART (Système d'Aide au Roulage tous Temps).

# Abstract

Due to the increase of traffic volume and complexity of new transport systems, new Advanced Driver Assistance Systems (ADAS) are a subject of research of many companies, laboratories and universities. These systems include algorithms with techniques that have been studied during the last decades like Simultaneous Localization and Mapping (SLAM), obstacle detection, stereo vision, etc. Thanks to the advances in electronics, robotics and other domains, new embedded systems are being developed to guarantee the safety of the users of these critical systems.

For most of these systems a low power consumption as well as reduced size is required. It creates the constraint of execute the algorithms in embedded devices with limited resources. In most of algorithms, moreover for computer vision ones, a big amount of data must be processed at high frequencies, this amount of data demands strong computing resources. FPGAs satisfy this requirement; its parallel architecture combined with its low power consumption and flexibility allows developing and executing some algorithms more efficiently than any other processing platforms.

In this thesis different embedded computer vision architectures intended to be used in ADAS using FPGAs are presented such as:

- We present the implementation of a distortion correction architecture operating at 100 Hz in two cameras simultaneously. The correction module allows also to rectify two images for implementation of stereo vision.

- Obstacle detection algorithms based on Inverse Perspective Mapping (IPM) and classification based on Color/Texture attributes are presented. The IPM transform is based in the perspective effect of a scene perceived from two different points of view. Moreover results of the detection algorithms from color/texture attributes applied on a multi-cameras system, are fused in an occupancy grid.

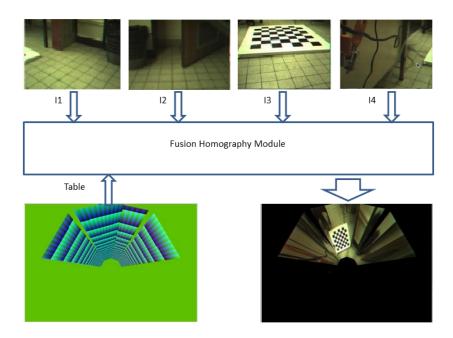

- An accelerator to apply homographies on images, is presented; this accelerator

can be used for different applications like the generation of Bird's eye view or

Side view.

- Multispectral vision is studied using both infrared images and color ones. Synthetic images are generated from information acquired from visible and infrared sources to provide a visual aid to the driver. Image enhancement specific for infrared images is also implemented and evaluated, based on the Contrast Limited Adaptive Histogram Equalization (CLAHE).

- An embedded SLAM algorithm is presented with different hardware accelerators (point detection, landmark tracking, active search, correlation, matrix operations).

All the algorithms were simulated, implemented and verified using as target FPGAs. The validation was done using development kits. A custom board integrating all the presented algorithms is presented.

Virtual components developed in this thesis were used in three different projects: PICASSO (stereo vision), COMMROB (obstacle detection from a multi-cameras system) and SART (multispectral vision).

# Contents

| List of Figures v                                                                                                                                                                                                                                       |                                              |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|--|

| List of Tables                                                                                                                                                                                                                                          | ix                                           |  |  |  |  |

| Glossary                                                                                                                                                                                                                                                | xi                                           |  |  |  |  |

| 1 Introduction 1.1 State of the art for Advanced Driver Assistance Systems on cars 1.2 State of the art for Driver Assistance on aircrafts 1.3 Context of the thesis 1.4 Thesis objectives 1.5 Contributions 1.6 Publications 1.7 Document organization | 3<br>6<br>7<br>8                             |  |  |  |  |

| 2 Theoretical background on driving assistance 2.1 Introduction                                                                                                                                                                                         | 11 12 14 16 17 19 20 22 23 24 25 26 27 29 29 |  |  |  |  |

| 2.12 Simultaneous Localization and Mapping (SLAM)                                                                                                                                                                                                       |                                              |  |  |  |  |

#### CONTENTS

|   |      | 2.12.1 EKF SLAM                                         | 31 |

|---|------|---------------------------------------------------------|----|

|   |      | 2.12.2 RT-SLAM                                          | 32 |

|   | 2.13 | Conclusion                                              | 32 |

|   |      |                                                         |    |

| 3 | Met  | chodology and design of embedded systems based on FPGAs | 35 |

|   | 3.1  | Introduction                                            | 35 |

|   | 3.2  | Parallel Processing Platforms                           | 36 |

|   | 0.2  | 3.2.1 Digital Signal Processor (DSP)                    | 36 |

|   |      |                                                         | 37 |

|   |      | 3.2.2 Graphic Processing Unit (GPU)                     |    |

|   |      | 3.2.3 Application-Specific Integrated Circuit (ASIC)    | 37 |

|   |      | 3.2.4 Field Programmable Gate Array (FPGA)              | 37 |

|   |      | 3.2.5 Parallel Processing Platforms comparison          | 42 |

|   | 3.3  | Designing with FPGAs                                    | 43 |

|   |      | 3.3.1 Hardware Description Language (HDL)               | 43 |

|   |      | 3.3.2 Setup and Hold                                    | 44 |

|   |      | 3.3.3 Pipelining                                        | 44 |

|   |      | 3.3.4 Floating Point Operations in FPGA                 | 45 |

|   |      | 9 -                                                     |    |

|   |      | 3.3.5 FPGA Memory management                            | 47 |

|   |      | 3.3.5.1 Multi-Port Memory Controller (MPMC)             | 48 |

|   |      | 3.3.5.2 Memory Interface Generator (MIG)                | 50 |

|   | 3.4  | FPGA embedded Processors                                | 50 |

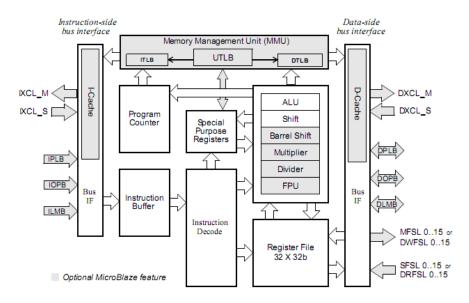

|   |      | 3.4.1 MicroBlaze and PicoBlaze                          | 51 |

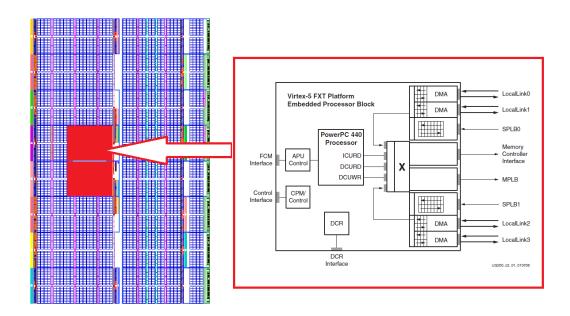

|   |      | 3.4.2 PowerPC                                           | 51 |

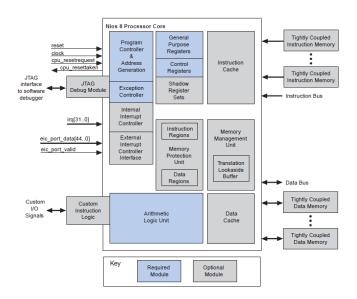

|   |      |                                                         | 52 |

|   |      | 3.4.4 Real Time Operating System (RTOS)                 | 52 |

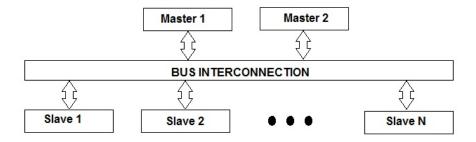

|   | 3.5  | FPGA Bus architectures                                  | 53 |

|   | 5.5  |                                                         |    |

|   |      | 3.5.1 Avalon Switch Fabric                              | 54 |

|   |      | 3.5.2 Processor Local Bus (PLB)                         | 55 |

|   |      | 3.5.3 AMBA-AXI4                                         | 55 |

|   | 3.6  | FPGA Development Flow                                   | 55 |

|   |      | 3.6.1 HLS Flow                                          | 55 |

|   |      | 3.6.2 Hand code RTL design Flow                         | 56 |

|   |      | 3.6.3 System simulation                                 | 60 |

|   | 3.7  | Conclusion                                              | 61 |

|   | 0.1  | Conclusion                                              | 01 |

| 1 | Har  | dware Integration                                       | 63 |

| 4 |      | Introduction                                            | 63 |

|   |      |                                                         |    |

|   | 4.2  | Image preprocessing                                     | 63 |

|   |      | 4.2.1 Distortion Correction implementation              | 64 |

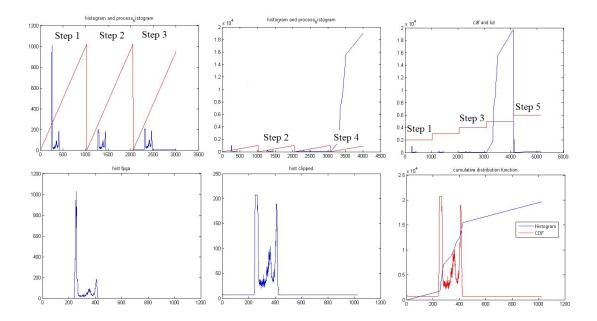

|   |      | 4.2.2 Histogram Equalization implementation             | 68 |

|   |      | 4.2.2.1 Pre-histogram                                   | 68 |

|   |      | 4.2.2.2 CLAHE                                           | 68 |

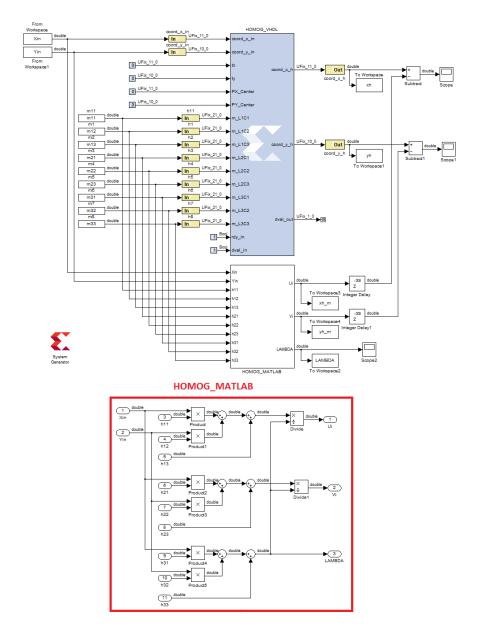

|   | 4.3  | Perspective transformation implementation               | 70 |

|   |      | 4.3.1 Homography without Cache memory                   | 73 |

|   |      | 4.3.2 Homography with Cache memory                      | 75 |

|   | 4.4  | Multispectral Vision implementation                     | 76 |

|   |      |                                                         |    |

|   | 4.5  | Obstacle detection implementation                       | 77 |

|   |      | 4.5.1 IPM                                               | 77 |

|   |      | 4.5.1.1 Monocular IPM                                   | 77 |

# CONTENTS

|              |       | 4.5.1.2 Stereo IPM                                     |

|--------------|-------|--------------------------------------------------------|

|              |       | 4.5.2 Texture Classification                           |

|              | 4.6   | Stereo vision implementation                           |

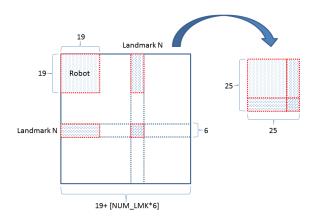

|              | 4.7   | Embedded SLAM                                          |

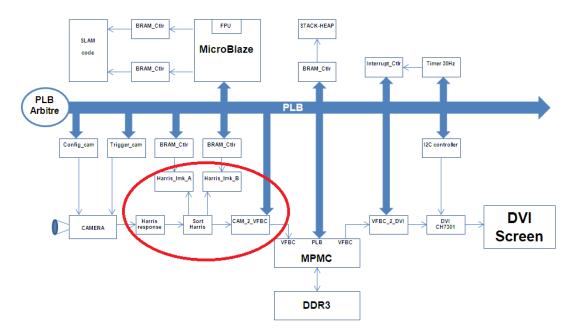

|              |       | 4.7.1 System prototyping                               |

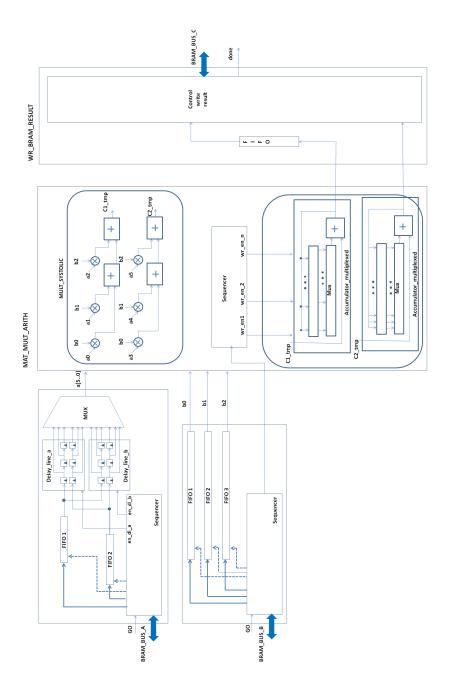

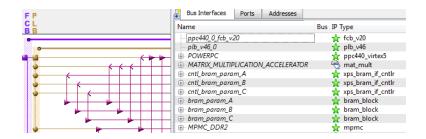

|              |       | 4.7.2 Matrix operations accelerators implementation 89 |

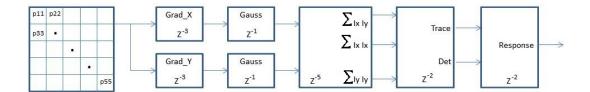

|              |       | 4.7.3 Harris point detector implementation             |

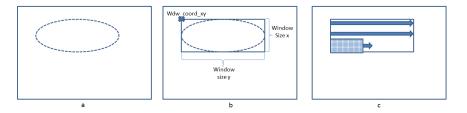

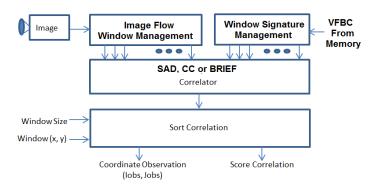

|              |       | 4.7.4 Active search implementation                     |

|              | 4.8   | Contour detection implementation                       |

|              | 4.9   | Conclusion                                             |

| 5            | Res   | ults and Projects 101                                  |

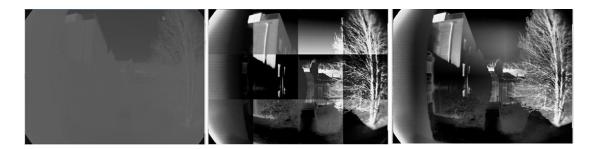

|              | 5.1   | Distortion correction results                          |

|              | 5.2   | CLAHE results                                          |

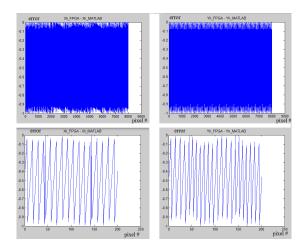

|              | 5.3   | Perspective transformation results                     |

|              | 5.4   | Multispectral vision results                           |

|              | 5.5   | Obstacle detection                                     |

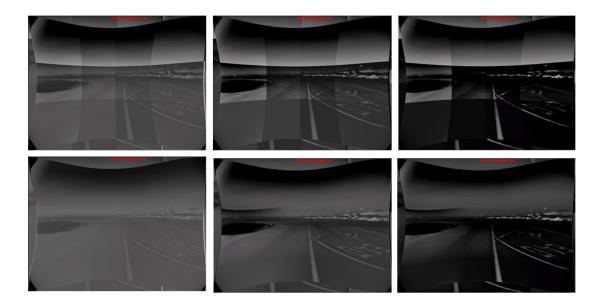

|              |       | 5.5.1 IPM results                                      |

|              |       | 5.5.2 Textures Obstacle detection - Camera belt        |

|              | 5.6   | Stereo-vision results                                  |

|              | 5.7   | Harris point detector results                          |

|              | 5.8   | Contour detection results                              |

|              | 5.9   | Timing and Resource utilization                        |

|              |       | 5.9.1 SART                                             |

|              |       | 5.9.1.1 SART Cameras                                   |

|              |       | 5.9.1.2 SART Architecture                              |

|              |       | 5.9.1.3 Parallel Processing                            |

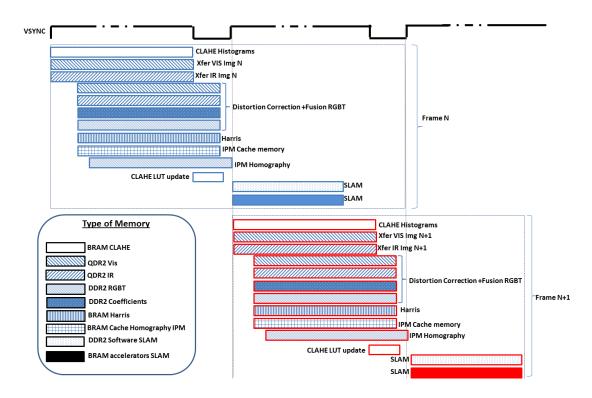

|              |       | 5.9.1.4 Memory accesses                                |

|              |       | 5.9.1.5 Hardware prototyping                           |

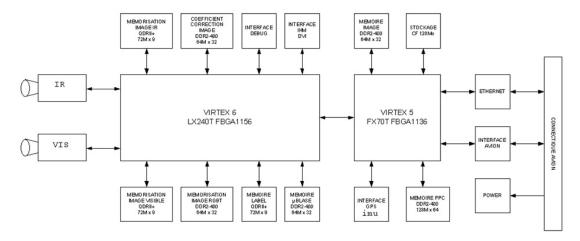

|              |       | 5.9.1.6 Board design                                   |

|              |       | 5.9.1.7 System Validation                              |

|              | 5.10  | Platforms used                                         |

| 6            | Con   | clusion 137                                            |

|              | 6.1   | Developed Algorithms and Architectures                 |

|              | 6.2   | Some future works                                      |

| $\mathbf{R}$ | efere | nces 143                                               |

# CONTENTS

# List of Figures

| 1.1<br>1.2 | Follow me vehicle                                                                       |    |

|------------|-----------------------------------------------------------------------------------------|----|

| 1.3        | Block diagram of modules and projects                                                   | 8  |

| 2.1        | Pinhole Camera Model                                                                    |    |

| 2.2        | Bilinear interpolation                                                                  |    |

| 2.3        | Infrared Cheesboard for calibration                                                     |    |

| 2.4        | Bird's eye view transformation                                                          |    |

| 2.5        | Xylon demo test vehicle                                                                 |    |

| 2.6        | Electromagnetic Spectrum                                                                |    |

| 2.7        | Relative response curves for different IR sensor materials                              |    |

| 2.8        | Infrared and visible view of a day and night scene                                      |    |

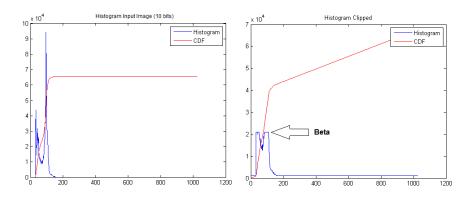

| 2.9        | CLAHE histograms                                                                        |    |

| 2.10       | Infrared and visible image of the stop bar in an airport context                        | 21 |

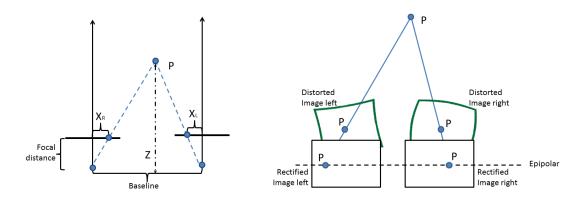

| 2.11       | Stereo vision principles                                                                | 23 |

| 2.12       | Configurable mechanic base for stereo vision                                            | 23 |

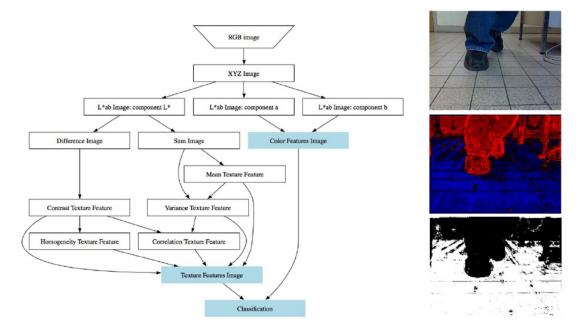

|            | Texture object detection algorithm                                                      |    |

| 2.14       | IPM coordinate notation                                                                 | 25 |

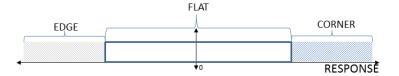

| 2.15       | Harris response feature classification                                                  | 28 |

| 2.16       | Brief comparison patterns                                                               | 29 |

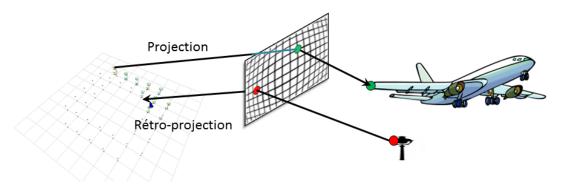

| 2.17       | Calibration necessity for SLAM projection, illustrates the projection, retro-projection | n  |

|            | operations done during the SLAM algorithm                                               |    |

| 2.18       | RT-SLAM decomposition of $P$ before implementing $HPH^t$                                | 33 |

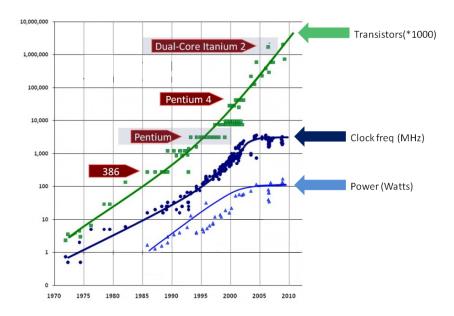

| 3.1        | Moore's Law                                                                             | 36 |

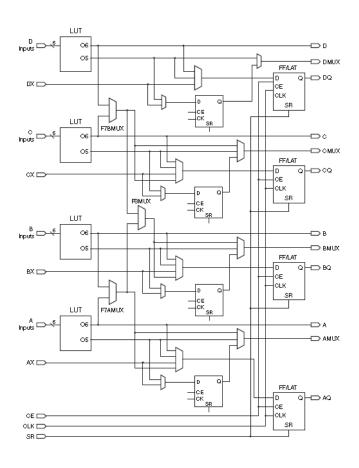

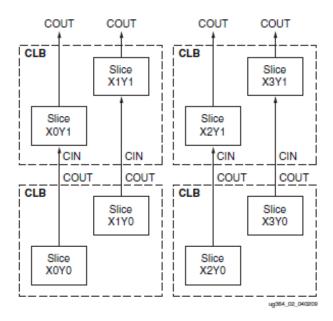

| 3.2        | SLICE Virtex 6 simplified block diagram                                                 | 38 |

| 3.3        | CLB block diagram                                                                       | 39 |

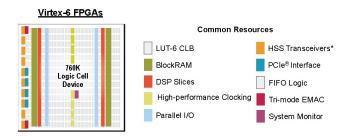

| 3.4        | Virtex 6 column architecture                                                            | 39 |

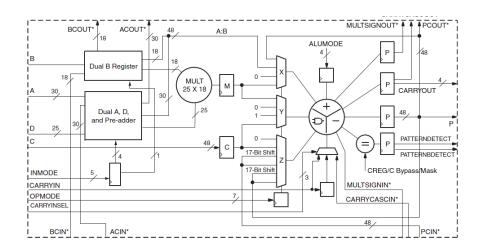

| 3.5        | DSP48 block diagram                                                                     | 40 |

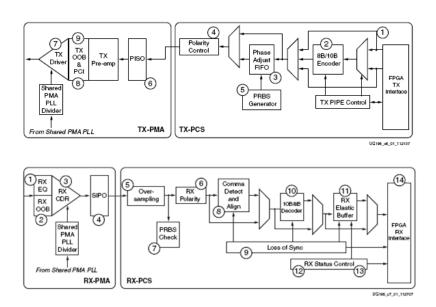

| 3.6        | GTP block diagrams                                                                      | 41 |

| 3.7        | FPGA devices comparison                                                                 | 41 |

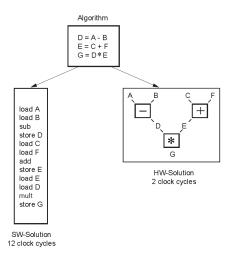

| 3.8        | Comparison between hardware and software execution                                      | 42 |

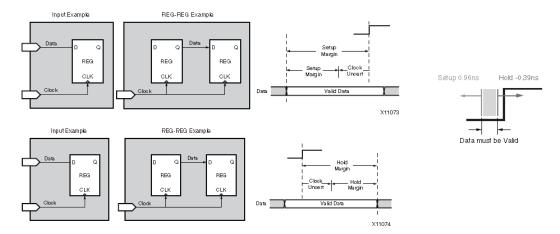

| 3.9        | Setup and Hold                                                                          | 44 |

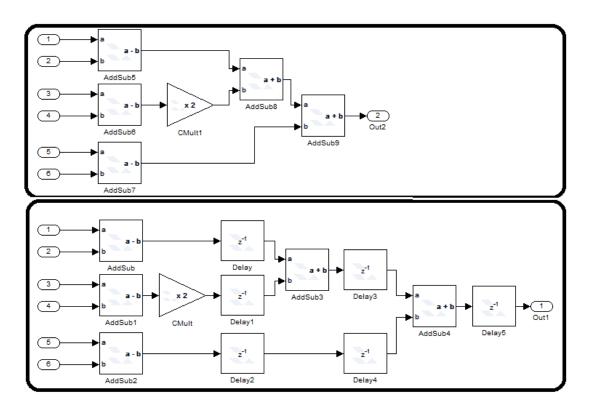

| 3.10       | Pipelined vs. not pipelined implementation                                              | 45 |

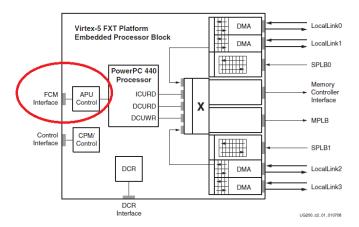

| 3.11       | PowerPC interfaces                                                                      | 46 |

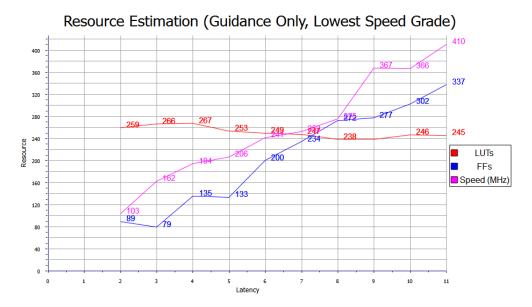

| 3.12       | Floating point addition latency, operation frequency and resources                      | 47 |

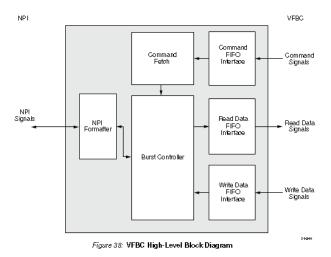

| 3 13       | VFRC block diagram                                                                      | 48 |

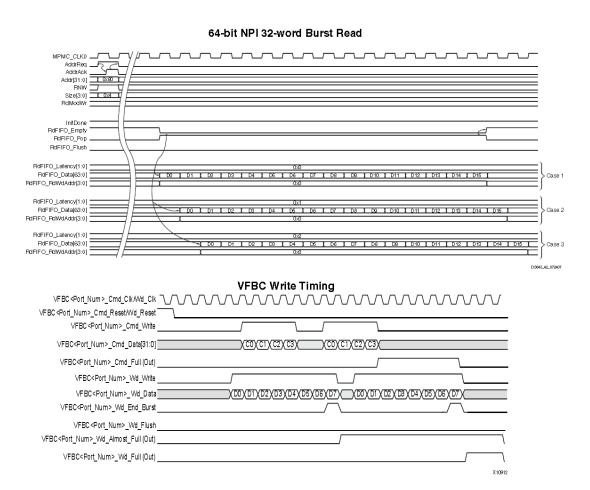

# LIST OF FIGURES

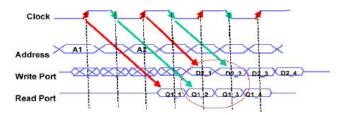

| 3.14 | MPMC transaction timing diagrams                                          | 49 |

|------|---------------------------------------------------------------------------|----|

|      | MicroBlaze block diagram                                                  |    |

|      | PowerPC in the die of a VFX70t                                            |    |

|      | NIOS II block diagram                                                     |    |

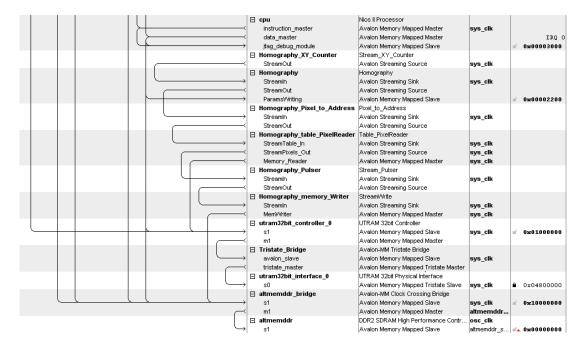

|      | Interconnection Bus                                                       |    |

|      | Avalon Switch Fabric                                                      |    |

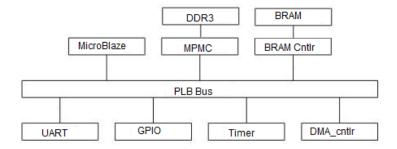

|      | PLB Bus example                                                           |    |

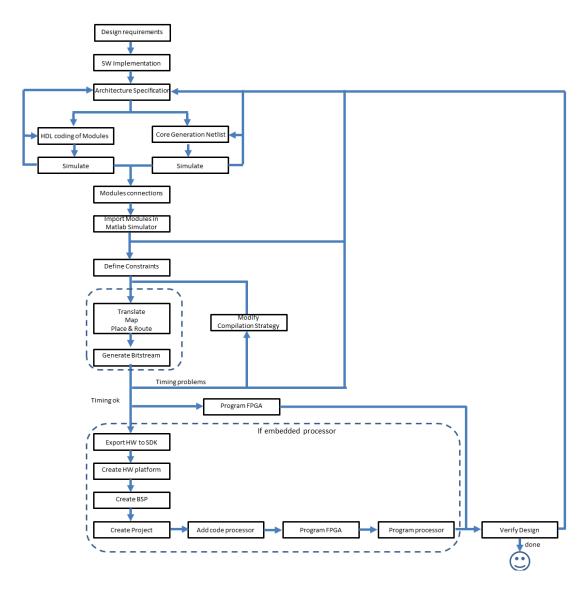

|      | Development flow followed in this thesis                                  |    |

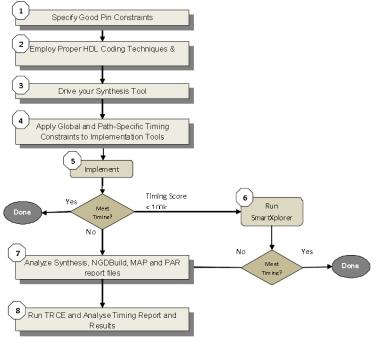

|      | Timing closure flowchart                                                  |    |

|      | 0                                                                         |    |

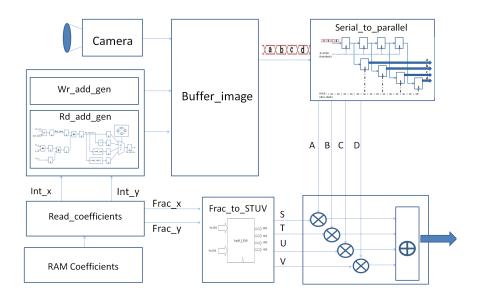

| 4.1  | Distortion correction pixel interpolation                                 | 64 |

| 4.2  | Coefficient codification                                                  | 64 |

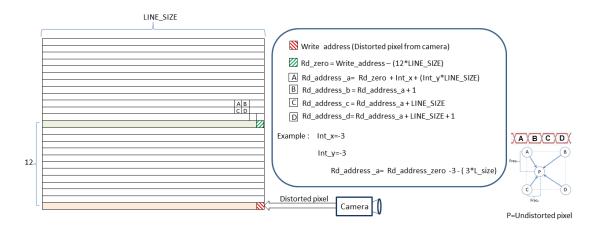

| 4.3  | Distortion Correction architecture                                        | 65 |

| 4.4  | Internal Memory Management                                                | 66 |

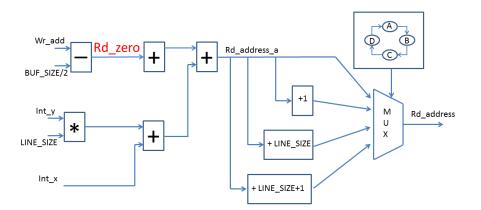

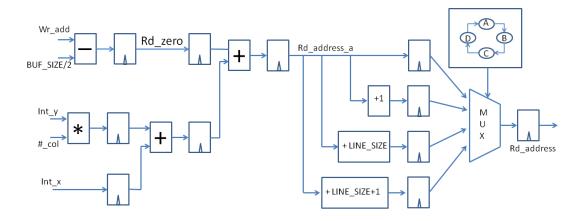

| 4.5  | Read Address generator                                                    |    |

| 4.6  | Read Address generator fully pipelined                                    |    |

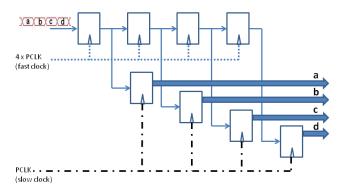

| 4.7  | Serial to parallel Distortion Correction module                           |    |

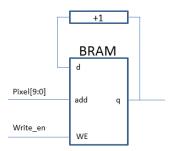

| 4.8  | Histogram tile block diagram                                              |    |

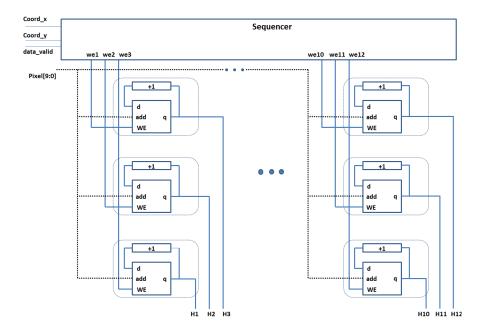

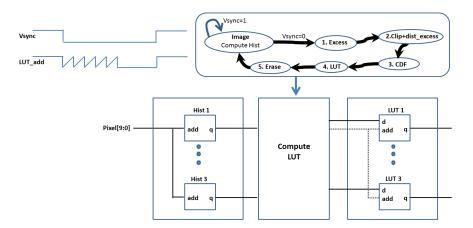

| 4.9  | CLAHE histogram array architecture                                        |    |

| 4.10 | CLAHE histogram processing architecture                                   |    |

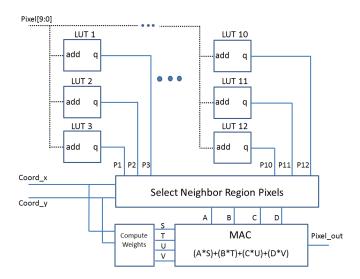

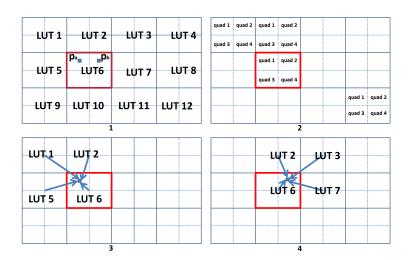

|      | CLAHE LUT interpolation                                                   |    |

|      | CLAHE quadrant interpolation                                              |    |

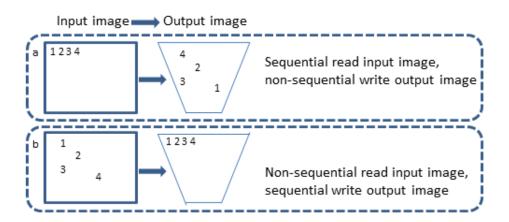

|      | Homography accesses sequential and random approaches                      |    |

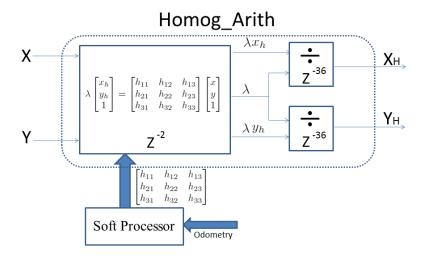

|      | Homography Arithmetic Unit block diagram                                  |    |

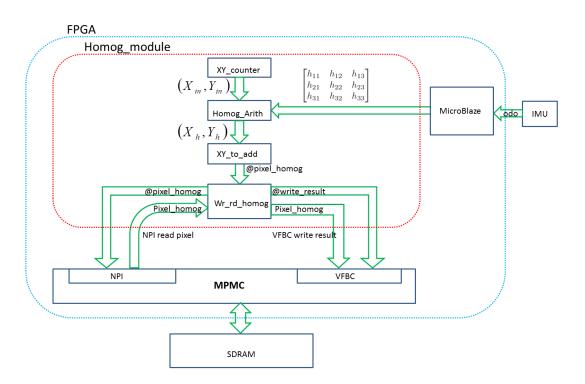

|      | Homography module without Cache memory                                    |    |

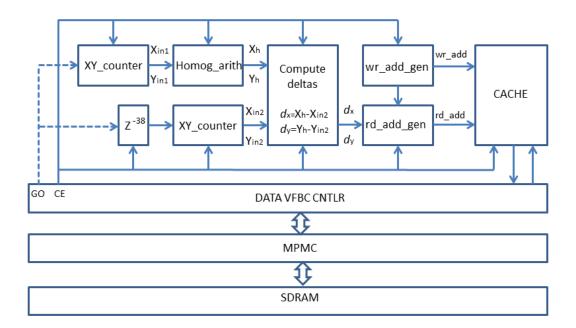

|      | Homography module with Cache memory                                       |    |

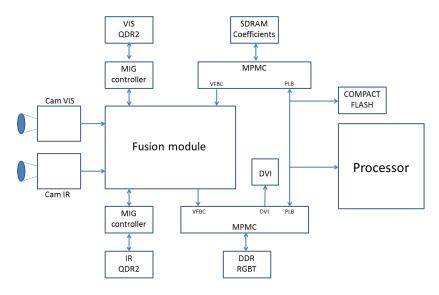

|      | Fusion IR and VIS using QDR2 memory                                       |    |

|      | QDR2 timing diagrams                                                      |    |

|      | IPM block diagrams                                                        |    |

|      | Gantt chart to compare latency of both MIPM methods                       |    |

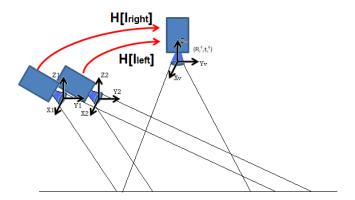

|      | Stereo IPM representation                                                 |    |

|      | Stereo IPM Bird's eye view approach                                       |    |

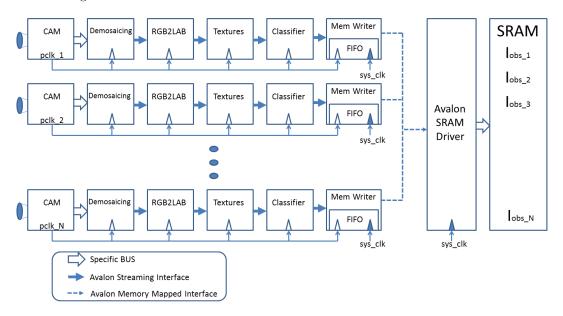

|      | Obstacle detection pipelines                                              |    |

|      | Multiple camera accesses to Avalon Bus                                    |    |

|      | Occupancy grid with different frame references                            |    |

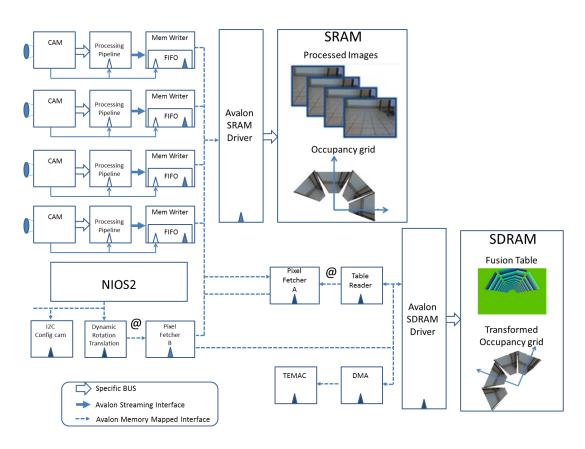

|      | Commrob block diagram                                                     |    |

|      | Picasso Hardware                                                          |    |

|      |                                                                           |    |

|      | Distortion coefficients upload mechanism                                  | 85 |

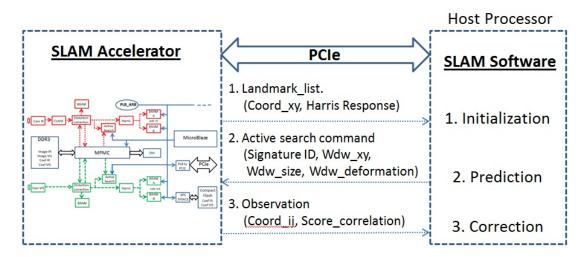

|      | SLAM accelerator block diagram                                            |    |

|      | Gant diagram representing SLAM speed-up given by the co-design            | 86 |

| 4.31 | Communication through PCIe between the host processor and the SLAM accel- | 0. |

| 4 00 | erator                                                                    | 87 |

|      | SLAM Prototyping                                                          | 88 |

|      | Block diagram matrix multiplication module                                | 90 |

|      | Multiplication Accelerator PLB connections                                | 91 |

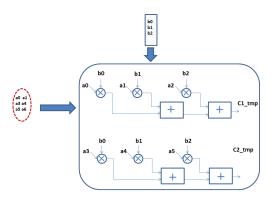

|      | Multiplication Systolic Array                                             | 91 |

|      | Multiplication descomposition of the matrix to feed the Systolic Array    | 92 |

|      | Matrix multiplication accelerator FIFO's interface                        | 93 |

| 4.38 | Harris detection block diagram                                            | 94 |

# LIST OF FIGURES

|              | Harris memory unit                                                     |     |

|--------------|------------------------------------------------------------------------|-----|

|              | Harris Arithmetic Unit                                                 |     |

|              | Harris unit integrated to the PLB system                               |     |

|              | Active Search                                                          |     |

|              | Block diagram of the Active Search module                              |     |

|              | Block diagram of the BRIEF module                                      |     |

| 4.45         | Sobel basic element architecture                                       | 99  |

| F 1          | D: 4 4' 14                                                             | 100 |

| 5.1          | Distortion correction result                                           |     |

| 5.2          | Matlab comparison distortion images                                    |     |

| $5.3 \\ 5.4$ | Comparison Distortion correction with and without Interpolation        |     |

| -            | Histogram and CDF after and before truncate bits                       |     |

| $5.5 \\ 5.6$ | CLAHE System generator simulation                                      |     |

| 5.0 - 5.7    | CLAHE system generator simulation                                      |     |

| 5.1<br>5.8   | CLAHE intermediary images                                              |     |

| 5.9          | Simulink homography verification diagram                               |     |

|              | Graphic of quantization error of the homography module                 |     |

|              | Homography effects of interpolation absence.                           |     |

|              | Homography necessity of pipelining.                                    |     |

|              | Fusion IR and VIS in different color spaces                            |     |

|              | IPM output image                                                       |     |

|              | SIPM calibration procedure                                             |     |

|              | SIPM tables encode homography and distortion correction simultaneously |     |

|              | SIPM results                                                           |     |

|              | Shadow effects in SIPM                                                 |     |

|              | Camera-belt disposition                                                |     |

|              | COMMROB Multicamera fusion image                                       |     |

|              | Occupancy grid                                                         |     |

|              | Micro camera developed at LAAS for the camera Belt                     |     |

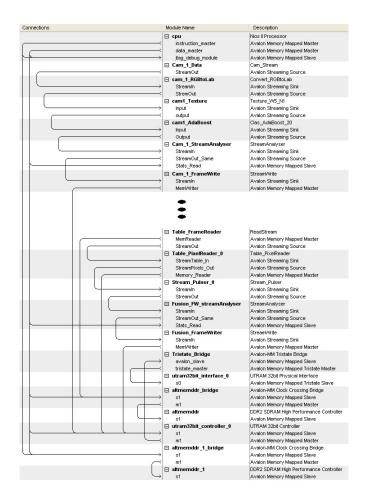

|              | Cammera Belt architecture in SOPC Builder                              |     |

|              | Disparity map after distortion correction                              |     |

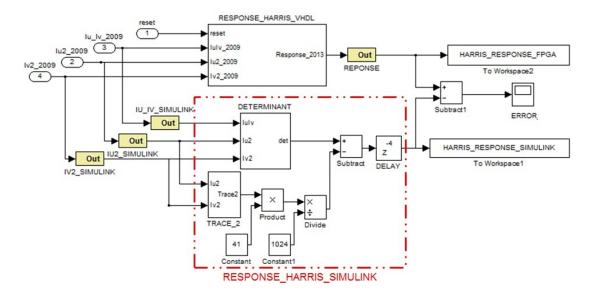

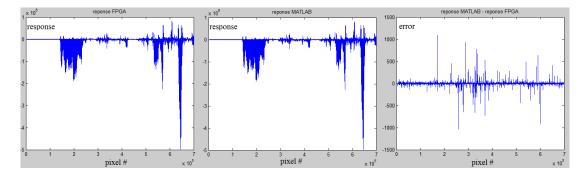

|              | Harris module in system generator and the Simulink model               |     |

|              | Response quantization error                                            |     |

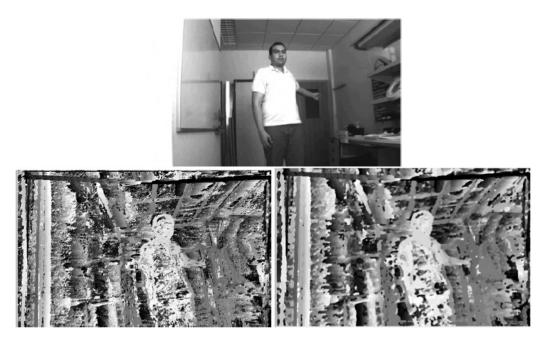

|              | Harris point detector output in System Generator                       |     |

|              | Harris point detector output                                           |     |

| 5.29         | Superposition input images and gradients                               | 120 |

| 5.30         | Gradient applied to undistorted images                                 | 121 |

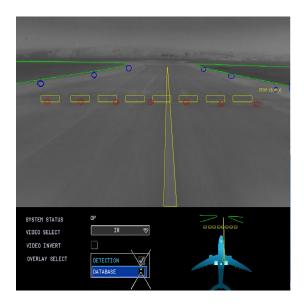

|              | SART HMI displayed image                                               |     |

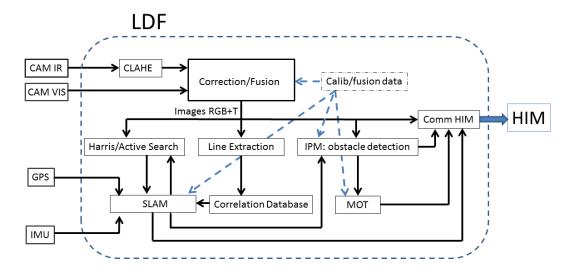

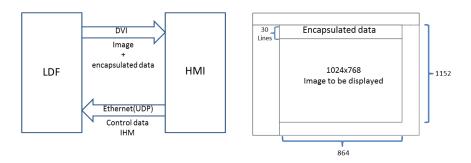

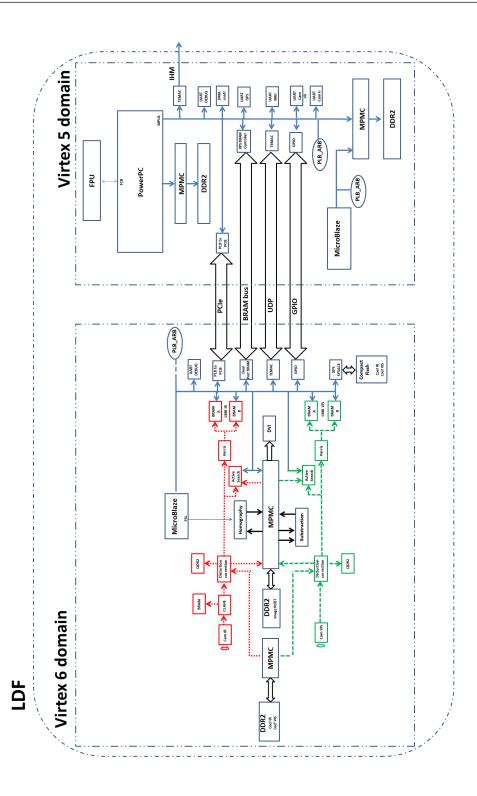

| 5.32         | Simplified block diagram SART algorithms                               | 123 |

|              | Interface HMI and LDF                                                  |     |

| 5.34         | SART cameras                                                           | 125 |

|              | Visible Image SART Camera                                              |     |

|              | Infrared Image SART Camera                                             |     |

|              | Block diagram of the SART System                                       |     |

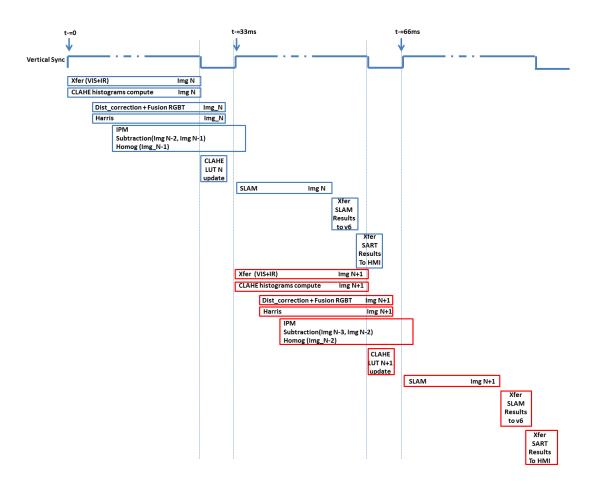

|              | Timing representation of SART processing algorithms                    |     |

|              | Timing representation of Memory accesses SART                          |     |

|              | Block diagram SART System                                              |     |

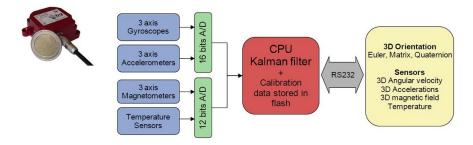

| 5.41         | SART Inertial Measurement Unit block diagram                           | 130 |

# LIST OF FIGURES

| 5.42 | LDF SART Board                                     | 132 |

|------|----------------------------------------------------|-----|

| 5.43 | SART demonstration Car                             | 133 |

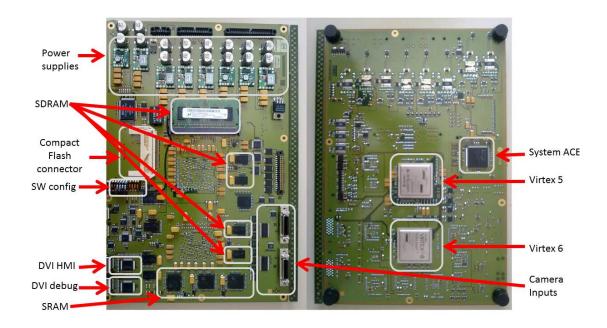

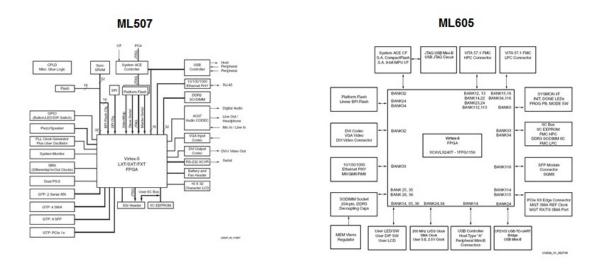

| 5.44 | ML507 and ML605 Block diagrams                     | 134 |

| 5.45 | Hardware Platform used to develop SLAM Accelerator | 134 |

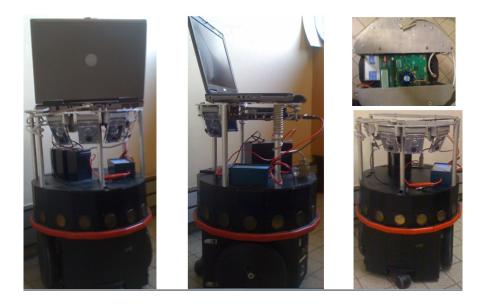

| 5.46 | Commrob platform                                   | 135 |

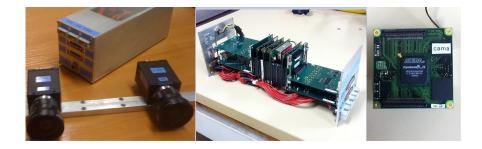

| 5.47 | Picasso Hardware                                   | 135 |

| 5.48 | Camera Belt hardware platform                      | 135 |

# List of Tables

| 3.1 | Parallel Processing Platforms comparison                                                                                                                   |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2 | Throughput of floating point multiplications depends of the architecture 46                                                                                |

| 5.1 | Resources required by our accelerator                                                                                                                      |

| 5.2 | Resources required for IPM                                                                                                                                 |

| 5.3 | Execution time required to compute equation 2.25 in Microblaze, taking into account the 3 euler angles and the x-y-z coordinates. Matrix inversion was im- |

|     | plemented using Gauss-Jordan Method                                                                                                                        |

| 5.4 | Execution time required to compute equation 2.25 in Microblaze, just using the                                                                             |

|     | yaw angle and x-y-z coordinates                                                                                                                            |

|                |                                                     | FOV            | Field Of View                                       |

|----------------|-----------------------------------------------------|----------------|-----------------------------------------------------|

|                |                                                     | FIFO           | First In First Out                                  |

| <b>~</b> 4.7   |                                                     | $\mathbf{FMC}$ | FPGA Mezzanine Connector                            |

| Glo            | ssary                                               | FOV            | Field Of View                                       |

|                | ·                                                   | FPGA           | Field Programmable Gate Array                       |

|                |                                                     | FPS            | Frames Per Second                                   |

| AHEBM          | Adaptive Histogram Equalization Based               | $\mathbf{FPU}$ | Floating Point Unit                                 |

|                | Method                                              | GPP            | General Purpose Processor                           |

| ACC            | Adaptive Cruise Control                             | GPS            | Global Positioning System                           |

| ADAS           | Advanced Driver Assistance Systems                  | GPOS           | General Purpose Operating System                    |

| AMBA           | Advanced Microcontroller Bus Architec-              | $\mathbf{GPU}$ | Graphic Processing Unit                             |

|                | ture                                                | HDL            | Hardware Description Language                       |

| $\mathbf{APU}$ | Auxiliary Processor Unit                            | HIL            | Hardware In the Loop                                |

| ASIC           | Application-Specific Integrated Circuit             | HDR            | High Dynamic Range                                  |

| AXI            | Advanced eXtensible Interface                       | HE             | Histogram Equalization                              |

| $\mathbf{BFM}$ | Bus Functional Model                                | HEBM           | Histogram Equalization Based Method                 |

| BRIEF          | Binary Robust Independent Elementary                | HLS            | High Level Synthesis                                |

|                | Features                                            | HPC            | High Performance Connector                          |

| BSP            | Board Support Package                               | IDP            | Inverse Depth Parametrization                       |

| $\mathbf{CC}$  | Cross-Correlation                                   | IHM            | Interface Human Machine                             |

| $\mathbf{CDF}$ | Cumulative Distribution Function                    | IMAPCA         | R Integrated Memory Array Processor<br>CAR          |

| CLAHE          | Contrast Limited Adaptive Histogram<br>Equalization | $\mathbf{IMU}$ | Inertial Measurement Unit                           |

| CLB            | Configurable Logic Blocks                           | IPM            | Inverse Perspective Mapping                         |

| COMMRO         | OB COMMunication with and among                     | IR             | Infrared                                            |

| 0011111110     | ROBots                                              | LAAS           | Laboratoire d'Analyse et d'Architecture des Systmes |

| DA             | Driving Assistance                                  | LDF            | Logique De Fusion                                   |

| $\mathbf{DMA}$ | Direct Memory Access                                | LIDAR          | Light Detection And Ranging                         |

| DDR            | Double Data Rate                                    | $_{ m LPC}$    | Low Performance Connector                           |

| DRC            | Dynamic Range Compression                           | LUT            | Look Up Table                                       |

| DSP            | Digital Signal Processor                            | lwIP           | Light Weight IP                                     |

| DUT            | Device Under Test                                   | LWIR           | Long-Wavelength Infrared                            |

| EDK            | Embedded Development Kit                            | MIPM           | Mono Inverse Perspective Mapping                    |

| EKF            | Extended Kalman Filter                              | MIG            | Memory Interface Generator                          |

|                |                                                     |                |                                                     |

$\mathbf{ELF}$

**ETACS**

Executable Loader File

External and Taxi Aid Camera System

# GLOSSARY

| MPMC    | Multi-Port Memory Controller           | SART            | Systme d' Aide au Roulage Tout temps         |

|---------|----------------------------------------|-----------------|----------------------------------------------|

| MWIR    | Mid-Wavelength Infrared                | $\mathbf{SDK}$  | Software Development Kit                     |

| NIR     | Near Infrared                          | SDRAM           | Synchronous Dynamic Random Access            |

| NTSB    | National Transportation Safety Board   |                 | Memory                                       |

| NUC     | Non-Uniformity Correction              | SIPM            | Stereo Inverse Perspective Mapping           |

| NPI     | Native Port Interface                  | SLAM            | Simultaneous Localization and Mapping        |

| os      | Operating System                       | SNR             | Signal to Noise Ratio                        |

| PC      | Personal Computer                      | $\mathbf{SRAM}$ | Static Random Access Memory                  |

| PCB     | Printed Circuit Board                  | SWIR            | Short-Wavelength Infrared                    |

| PICASSO | Plateforme dIntgration de Cameras mul- | TCP             | ${\it Transmission \ Control \ Protocol}\ ;$ |

|         | tiSenOrielles                          | TCAS            | Traffic Colision Allerting System            |

| PLB     | Processor Local Bus                    | UCF             | User Constraint File                         |

| PPC     | PowerPC                                | UDP             | User Datagram Protocol                       |

| QDR     | Quad Data Rate                         | UMBM            | Unsharp-Masking Based Methods                |

| RADAR   | RAdio Detection And Ranging            | VIS             | Visible                                      |

| RAP     | Robotique, Action et Perception        | VFBC            | Video Frame Buffer Controller                |

| RGBT    | Red, Green, Blue, Thermal              |                 |                                              |

| ROI     | Region Of Interest                     | VHDL            | VHSIC hardware description language          |

| RTOS    | Real Time Operating System             | VHSIC           | Very High Speed Integrated Circuit           |

| RT-SLAM | Real Time-Simultaneous Localization    | VLWIR           | Very Long-Wavelength Infrared                |

|         | and Mapping                            | ZNCC            | Zero-mean Normalized Cross Correla-          |

| SAD     | Sum Absolute Differences               |                 | tion                                         |

# 1

# Introduction

Embedded systems are everywhere and are part of our life. Thanks to the fast progress in technology, more complex systems have been developed to satisfy many needs of human beings. Some mass markets make the technology on embedded systems progress faster and faster, like smart phones, video games or Internet devices. It is well known that the greater number of computers are now integrated in embedded systems, comparing to laptops or desktops.

Some convergences make new technologies developed for one specific market, adopted for another one. Let us cite the Kinect product, introduced on the mass market as a device for video games, but which is more and more used in robotics applications as a low-cost 3D camera. The Kinect massive distribution illustrates also the importance of sensing, and moreover vision applications, which impulse technology transfers from research laboratories to companies: let us cite also the spectacular diffusion on smart phones or on cameras, of algorithms developed in vision labs some years ago, like the Viola&Jones face detection algorithm or the stitching methods, used now by everybody in the world.

One domain where technological improvements are now a survival conditions for many companies, concerns automotive or transportation industry. Advanced Driver Assistance Systems (ADAS) have been studied from twenty years in different applications involving vehicles, trains, aircrafts, helicopters...; these developments are justified by safety considerations, not only for marketing ones!!

Nowadays, numerous ADAS exist in the marketplace; many of them make use of advanced sensing technologies, like cameras, GPS, IMU, active sensors (Radar and LIDARs), etc. The processing of sensory data acquired by these devices, requires powerful, but cheap and low-energy computation systems. The use of these embedded systems on transportation applications, has improved the efficiency of all kind of vehicles and reduced the number of accidents and fatalities.

Our contributions concern an ADAS designed for aircraft pilots, but they could be adapted to be used on other vehicles. It is the reason why we present in the next section, a short state of the art on Driver Assistance, before describing our objectives and contributions.

# 1.1 State of the art for Advanced Driver Assistance Systems on cars

Driver Assistance on cars has known a very fast development since twenty years: the European EUREKA Prometheus program in the nineties, various other European member states programs involving collaborative researches between labs and automotive companies, made different technological improvements, which are now integrated on sensors or devices used on many cars. The involved technologies are numerous, from motor control, communications (between vehicles and/or road infrastructures), sensing, data processing... Moreover, the joint use of GPS and of knowledge data base on the road maps, made available accurate enough localization methods, so that a driver could be warned when arriving to a dangerous turn or crossroad. Systems devoted to the driver or passenger monitoring inside the car cockpit (smart airbags or drowsiness detection) are not considered here.

Our contributions only concern an embedded system integrating sensors and computation units, devoted to obstacle detection and the estimation of the vehicle motions. So hereafter, only works on these applications will be considered, to cope with either sensing or integration issues.

Radar tools have been used for many years now, mostly for military and commercial use, and today we find more and more of them showing up in new vehicles in order to provide ADAS, especially for obstacle detection on highways. One of the main disadvantages of the radar system comes from undesired reflections which generate false alarms. Radar techniques also present some drawbacks for lateral-position measurements [1].

In the last two decades the automotive industry has done a significant amount of research in ADAS. The most well known ADAS is the Back-up aid system, already installed on millions of cars. Automatic parking systems have also been installed by carmakers of upmarket models like the Lexus LS-series vehicle. Another very useful and popular system is cruise control, often limited to the speed control when driving on highways.

The ACC (Adaptive Cruise Control) already integrated in the Sedan BMW, is based on a dual core computer platform. This system provides an ADAS based on information coming from a GPS, radar, and a set of pre-calibrated cameras. The ACC implements perspective transformation of the images in order to provide a Bird's eye view and a side view. The system also provides a tool called a driving tube, which corresponds to an augmented reality methods, in order to superpose a driving virtual lane in the image to indicate the estimated trajectory to the driver. This system includes even automatic maneuvers for controlling acceleration of the vehicle.

Night Vision systems using cameras with infrared illumination or infrared cameras are included on the highest-end vehicles like Mercedes S-class and BMW 7 series. The high cost of this kind of cameras has limited the use in only highest-end vehicles; it could be developed for high-cost professional vehicles like trucks.

Lane changing systems assist drivers when changing lanes. This system is included in the Audi Q7 luxury SUV. These systems warn the driver if a lane change occurs without a previous activation of the turn indicator.

Sign recognition systems are being studied by many companies. If the driver does not see an important sign such as a stop sign, the system will alert the driver.

Toyota includes a safety system, based in the IMAPCAR (Integrated Memory Array Processor for CAR) [2] developed by NEC, in the Lexus LS460. This processor has a special architecture including 128 Processing Elements, providing the processor with a peak performance of 12.8 MMAC/s or 100 GOP/s. Different ADAS algorithms are included: Lane departure

warning, Pedestrian protection, Collision avoidance, Blind spot detection, high beam assistant, etc.

Finally let us cite some embedded systems involving vision. First the Mobil Eye company in Israel, proposes a product for obstacle detection using vision: this device implements in real time, pedestrian or car detection, using a learning/classification approach based on region descriptors like HOG (Histogram of Oriented Gradients): it is another example of a very fast transfer from research results (the initial Dalal/Triggs works appeared in 2005) to a product ready to be integrated on the mass market. More locally LAAS has some cooperations with companies in Toulouse involved in transportation applications; the Continental unit has developed for many years embedded systems based on vision, while the SME Delta Technologies Sud Ouest provides smart cameras used to assist the driver of buses in urban environment.

# 1.2 State of the art for Driver Assistance on aircrafts

In the aircraft industry different ADAS exist and are now mandatory for the safety of the ground operations of these critical systems. A large percentage of aircrafts operation time is devoted to actions on the ground; in Europe it corresponds to 10 to 30 percent of the aircrafts activities.

Bad weather conditions presented in some places throughout the year represent a significant loss for an airline company and are a risk for the passengers.

Improving airport traffic is becoming a big necessity for airline companies. Most of the worst accidents in the airplane domain have been on the ground and are generally caused by environmental conditions or human failures.

Since 1993 a total of 12 accidents have been reported by [3]. In the last year, there were 3 accidents involving big airplanes, which occurred during navigation on taxiways or parking areas. All of these accidents involved contacts of the winglets of the airplanes with other objects; the main cause of these accidents was the absence of systems to help pilots determine the space occupied by his aircraft. Because of these accidents, the National Transportation Safety Board (NTSB) is evaluating where or not to impose the installation of anti-collision systems, based on vision or radar sensors, in order to help pilots.

Large airplanes (Boeing 747, 757, 767, and 777; the Airbus A380; and the McDonnell Douglas MD-10 and MD-11) need an ADAS tool for maneuvering throughout the airport during the day, but it is particularly required during the night. There are many blind spots in these big machines, especially because the pilot is very high with respect to the ground plane, so that the blind area in front of the nose is very large; the pilot has no visibility. Moreover, the wing tips are not easily visible by the pilot, so that it constitutes a risk during the taxiway navigation of the parking approach; in these aircrafts, the pilot needs to open the cockpit window to have a clear view of the wing tips.

Nowadays, most of the help provided to the pilot is done using signs between the pilot and human operators with a series of signals called Marshaling Signals. These signals include commands like move ahead, slow down, turn, and stop. During this procedure, the pilot follows the orders of the operator without the option to react to a possible operator failure.

Some special airport procedures have been established when there are hazard conditions. One of them corresponds to the "follow me" vehicle shown in the figure 1.1. For this procedure, a vehicle with large panels and illuminations drives in front of the airplane in order to indicate the correct path for the pilot. It is very useful in very large airports (Francfort, London, Paris in Europe), where a pilot can be lost during the navigation on taxiways, especially in bad weather conditions. But the use of these "follow me" vehicles involves important delays in operations,

so delays also for passengers.

Figure 1.1: Follow me vehicle - Safety procedure used in many airports to guide the aircrafts. Taken from [4]

When doing a simple maneuver such as turning, different strategies must be followed because of the different dimensions and rotation axis of the airplanes; it is not sufficient to follow a marking on the ground. The pilot must execute an oversteering maneuver, making not visible markings and taxiways during the turn. Using an image with synthetic objects like taxiways boundaries inserted in the image, can make easier the execution of these maneuvers; it could reduce the human failure probability

Many of the existing ADAS used in aircraft today use localization systems based solely on GPS systems. Some systems have already been developed by companies like Thales. The OANS (Onboard Airport Navigation System) can be installed as an option on an Airbus A380; it dynamically displays the aircraft position over a high-resolution geo-referenced airport map. But the aircraft position is only computed from the GPS and IMU (Inertial Measurement Unit embedded on the aircraft) data; the confidence region is about 8 m. The OANS system makes use of an airport map to generate the synthetic images, but these databases themselves are not accurate enough and do not reference important visual landmarks like signs and beacons. So these systems are not accurate enough to guarantee that the wheels of a large aircraft remain on the taxiways and moreover, in some cases the aircraft is localized on an incorrect taxiway.

In [5] a real-time system combining infrared and visible cameras is presented. This system is intended to assist pilots during adverse weather conditions. Currently, a new European project called Alicia, which uses infrared and visible cameras combined with Radar and Lidar, is being developed.

Some last generation airplanes (a380, a340-500/600) include a system called ETACS (External and Taxi Aid Camera System) [6]. ETACS uses two cameras, which display the nose and the main landing gear in the cockpit. This system allows the pilot to detect possible collision of the airplane wing tips. The left side of the figure 1.2 shows the image displayed by this system.

The Ground maneuvering camera system [7] manages up to 6 cameras, this is a standard equipment for the Boeing 777-300, providing an automatic or manual viewing angle adjustment. The cameras are usually mounted behind the nose gear and in the horizontal stabilizers. On the right side of the figure 1.2 is shown the image displayed by this system.

Another system called TCAS (Traffic Collision Alerting System) [9] provides collision avoidance based on a communication link established automatically between the TCAS systems of the concerned aircrafts. This system warns the pilot if there is a collision risk, and indicates to the crew of each involved aircrafts actions that must be taken. To compute the maneuver, the TCAS system takes into account the dynamic models of the involved aircrafts. If there is a difference between the instructions done by the TCAS system and the control tower, the TCAS has always the priority. This system is designed to assist the pilot just for air operations;

Figure 1.2: Camera navigation systems - On the left, ETACS display appearance (taken from [8]). On the right, GMCS display appearance (taken from [7])

for the ground operations the presence of multiple TCAS units could degrade safety. For this reason, the system is usually placed in standby mode when the aircraft is on the ground.

Some of the existing systems are limited by a small field of view. In [5] is presented an ADAS that uses multispectral sources with just around 40 degrees of Field Of View. For the maneuvers done in the airports, this is still not enough.

Even if there are many systems that have been developed for ADAS, none of them satisfy the operational needs in terms of field of view, nor when there are low visibility conditions such as rain, snow, dust, fog, haze, or poor illumination. In order to help pilots in these situations, airports are equipped with visual aids like Ground Lighting, surface markings and Signs. Ground lighting provide taxiway edge lights, taxiway center lines, and runway edge lights. Surface markings provide stop bars, taxi indicators, edge lanes ...

In many of the current ADAS, DSPs or DSPs plus FPGAs have been used. A DSP only solution does not have enough compute horsepower to implement all of the processing needed for ADAS. An ASIC might be useful, but because the algorithms and techniques are evolving very quickly, an ASIC does not offer the option to easily upgrade the system.

ADAS must give information to the driver in real time and the decision must be taken immediately since only a few milliseconds can represent a big improvement for the safety of the users. A study realized in France in 2002 about about the required frequency of an obstacle avoidance system for highway navigation, concluded that such a system must process sensory data at 100Hz, taking into account delays required to confirm an alarm, and also, the reaction time of the driver once an alarm is generated.

An FPGA can execute the job of several DSPs to implement all of the algorithms needed for ADAS in real-time. An FPGA provides the developer, with a two-dimensional array of configurable resources that can implement a wide range of arithmetic and logic functions. A FPGA includes complex resources such as dedicated DSP or processor blocks, multipliers, dual port memories, lookup tables (LUTs), registers, tri-state buffers, multiplexers, digital clock managers and more.

In contrast, with a microprocessor or DSP processor, where performance is tied to the clock rate at which the processor can run, FPGA performance is tied to the amount of parallelism that can be implemented in the algorithms, making the FPGA a very strong signal processing

#### 1. INTRODUCTION

platform with the advantages of low power consumption, small size, easy installation, reliability, and flexibility.

In critical systems the software implementation represents more risk than a hardware implementation. In software there is a compiler that translates thousands of line code, resulting in a super complex system; a system too complex to be able to guarantee any sort of reliability. Software, for example, can experience electromagnetic noise resulting in the corruption of the program counter register and the system can completely crash.

In a hardware implementation, we can have better control of the available resources and of the implementation. For this reason we also justify the use of HDL language and FPGA design for these kinds of systems.

In this thesis, we need to process data for a human operator. For the development of an ADAS on aircraft, images will be displayed at 30 Hz in order to satisfy the visual comfort of the pilot. Real-time constraints push us to use high performance hardware like FPGAs.

## 1.3 Context of the thesis

This thesis was developed in the context of three projects: PICASSO (Plateforme d'Intgration de CameraS multiSenOrielles), COMMROB (Communication with and among Robots) and SART (Systme d' Aide au Roulage Tout temps).

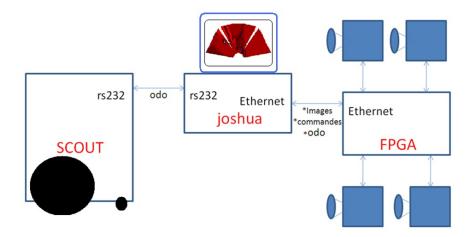

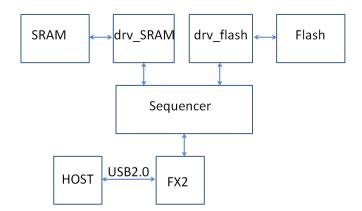

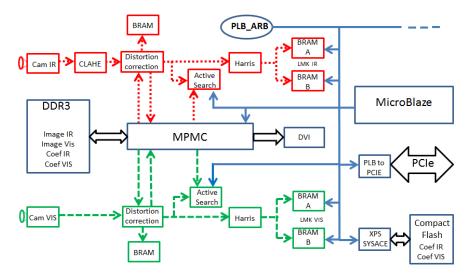

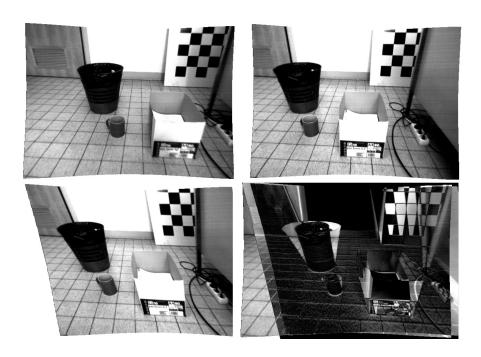

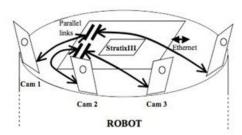

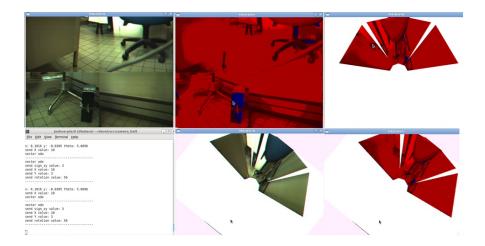

The project PICASSO aimed at developing a real-time stereo vision algorithm to be executed either for transportation applications, but also for a surgery application using stereo endoscopic images. A FPGA-based implementation of a passive stereo vision algorithm was developed in the PhD of A.Naoulou [10], assuming that the stereo images were undistorted and perfectly aligned. Our contribution was the integration of the image distortion correction and the rectification algorithm, executed in real-time at the pixel clock. Finally all modules have been integrated on a multi-FPGAs platform, made with three Altera Cyclone 2 boards. Initially, the PICASSO project had to cope also with multispectral vision, fusing data acquired by a stereo camera pair and an infrared camera; but the infrared camera was a prototype developed at LAAS, and it has been found that the infrared images were not stable enough to be processed. In the project COMMROB, the objective was to implement a companion robot, able to assist a human in an indoor dynamic environment with the presence of other persons or robots. LAAS participated to a work package devoted to indoor navigation; the main LAAS contribution concerned an integrated system designed for obstacle detection from a belt of micro-cameras, mounted around a robot. This system presented in [11], was developed in the PhD of M.Ibarra Manzano [12]. It was implemented only one method for obstacle detection, using pixel classification from color and texture descriptors. Our contribution has been first to develop and integrate a second method, using the Inverse Perspective Mapping transform, and then the system was extended to fuse the classification results obtained in parallel from images acquired by 4 cameras, in a single robot-centered or environment-centered occupancy grid. All methods were implemented and evaluated on a Altera Stratix 3 development kit, mounted on a robot equipped with four cameras.

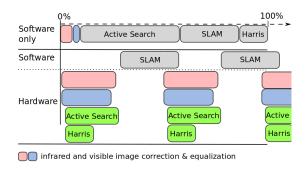

We have been mainly involved in the third project SART, an industrial project lead by the LATECOERE company in Toulouse. In this SART context, several functions required for a navigation system to help aircraft pilots have been developed. Different algorithms were first tested in software. Then, according to the estimation of resources and the needs of the algorithms, target FPGAs were chosen. Then, most of the algorithms were implemented on Xilinx Virtex6 and Virtex5 development kits. Finally, a custom board was developed to implement the final prototype. In this project, the constraint of VHDL use was imposed, because of the

high reliability of Hardware implementations using VHDL.

# 1.4 Thesis objectives

The objective of this thesis is the development of algorithms and architectures, integrated in an system embedded on vehicles, and devoted to obstacle detection and driver assistance for navigation under any weather conditions.

In this thesis, we will generate specifications and develop virtual components for: image transforms (rectification, correction, homography), maps construction, fusion, SLAM, contour detection, obstacle detection, and image enhancement. These virtual components will be developed and validated in real embedded systems, connected to real cameras.

Moreover, we want to evaluate the development of ADAS based on multispectral camera sources.

For Localization and Mapping of the robot, we have cooperated with other PhD students, which started from a C++ open source code called RT-SLAM, created at LAAS. Our objective consists in developing optimizations to the SLAM algorithm using hard coded accelerators taking advantage of the architecture of an FPGA.

Due to the certification constraints for equipments to be mounted on commercial aircrafts, we had (1) to use C instead of C++, and (2) to use VHDL for the development of modules on FPGAs. This is the reason why methodologies based on high level synthesis, i.e. taking advantage of C to VHDL compilers, have not been evaluated during this thesis. Nevertheless, during the development of this thesis we used a High Level Tool based on Matlab for verfication of the different modules.

## 1.5 Contributions

In this thesis we will study the development of algorithms and architectures to be used on embedded Advanced Driver Assistance Systems. We will study how to migrate the different and existing algorithms to limited resource platforms. Different algorithms were adapted in order to be implemented into embedded architectures with strong real time constraints.

We are interested in the use of Co-design to share the processing between processors and hardware accelerators developed using FPGAs. We want to use the parallel horsepower available in the FPGAs.

We have been mainly involved in the SART project; so our main motivations are to perform obstacle detection and to develop algorithms for localization and mapping using embedded multispectral cameras, in order to provide visual aids to the pilot.

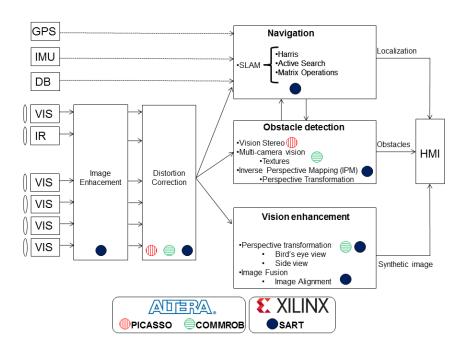

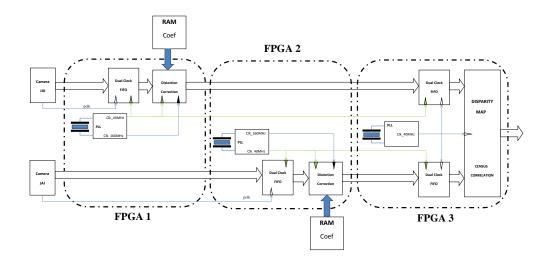

The figure 1.3 shows a block diagram of the different modules developed in this thesis, different target FPGAs from Xilinx and Altera were used in the development of the projects (PICASSO, COMMROB and SART) concerned in this work.

As a summary, our contribution aims at demonstrating the viability to use FPGAs to implement different vision algorithms to be integrated on ADAS, but also on autonomous robots; our results were used in three different projects: PICASSO (ADAS on vehicles), COMMROB (Robotics), and SART (ADAS for aircrafts).

In the research team RAP at LAAS-CNRS, the integration activity is becoming stronger; with this thesis we contribute to strengthen and make more visible this research activity.

Figure 1.3: Block diagram of modules and projects - In this thesis we show different architectures for tasks involved in ADAS. Architectures for Navigation, Obstacle detection and Vision enhancement are described.

# 1.6 Publications

- 1. D.BOTERO, J.PIAT, M.DEVY, J.L.BOIZARD "An FPGA accelerator for multispectral vision-based EKF-SLAM" IEEE IROS'12 Workshop on Smart CAmeras for roBOtic applications. October 2012.

- 2. D.BOTERO GALEANO, J.PIAT, P.CHALIMBAUD, M.DEVY, J.L.BOIZARD "FPGA implementation of mono and stereo inverse perspective mapping for obstacle detection" Design and Architectures for Signal and Image Processing. October 2012.

- 3. D.BOTERO GALEANO, M.DEVY, J.L.BOIZARD, W.FILALI "Real-time architecture on FPGA for obstacle detection using inverse perspective mapping" International Conference on Electronics Circuits and Systems, December 2011.

- 4. D.BOTERO GALEANO, A.GONZALEZ, M.DEVY "Architecture embarque pour le SLAM monoculaire". Reconnaissance des Formes et Intelligence Artificielle. January 2012.

- 5. W.FILALI, D.BOTERO GALEANO, M.DEVY, J.L.BOIZARD "SOPC components for real time image processing: rectification, distortion correction and homography" IEEE Workshop on Electronics, Control, Measurement and Signals. Juin 2011.

- 6. M.DEVY, J.L.BOIZARD, D.BOTERO GALEANO, H.D.CARILLO LINDADO, M.IBARRA MANZANO, Z.IRKI, A.NAOULOU, P.LACROIX, P.FILLATREAU, J.Y.FOURNIOLS, C.PARRA "Stereovision algorithm to be executed at 100Hz on a FPGA-based architecture". Advances in Theory and Applications of Stereo Vision, N978-953-307-516-7, Janvier 2011, Chapter 17, pp.327-352

# 1.7 Document organization

This thesis is composed of four main chapters.

Chapter 2 presents the theoretical foundations for the different algorithms evaluated during this thesis. This chapter explains some image processing algorithms using vision; some algorithms have been extended to be used with infrared cameras. An introduction to the infrared technology and preprocessing algorithms to efficiently exploit its information are presented. An introduction to multispectral vision is given. Vision algorithms are used for obstacle detection and for SLAM. The obstacle detection is explained using two different approaches, one geometric approach based in projective geometry, and a second approach based in textures.

Chapter 3 presents different embedded systems and their advantages. After a description of multiple platforms, the FPGA architecture is described in detail. The methodology followed during this thesis to work using FPGA is presented as well as the new emergent technologies used today and how they work with the new FPGAs.

Chapter 4 presents the integration of the algorithms described in chapter 2 on FPGA-based architectures. This chapter describes the accelerators coded in VHDL, using co-design techniques.

Chapter 5 presents the results of the implemented algorithms and architectures. This chapter describes more of the projects (PICASSO, COMMROB and SART) involved during the development of this thesis.

Finally we present the conclusion and the perspectives.

# 1. INTRODUCTION

# Theoretical background on driving assistance

## 2.1 Introduction

Driving assistance is a very extensive field of research, widely studied specially during the last 10 years. In this thesis, we studied some of the algorithms used; we present in this chapter just those used during the development of this thesis. The algorithms presented here were chosen according to the needs imposed during the projects involved during this thesis.

In this chapter we will first present a brief introduction to image processing algorithms used in this thesis. A description of the Distortion Correction problem will be presented. Then, the Perspective Transformation is described as well as real applications now being used in different research fields. In the next section, we present the infrared, its principal properties, and some algorithms used to extract the information from an infrared High Dynamic Range (HDR) sensor. We present the state of the art of Multi-spectral vision, which corresponds to simultaneously use infrared and visible cameras. Then, we will present two main obstacle detection algorithms; the first of which is based in perspective effects (Inverse Perspective Mapping-IPM), while the second is based in an adaboost classifier that uses Textures properties in images. In the last section, we present the SLAM algorithm widely used in robotics for localization and mapping.

# 2.2 Pinhole Camera Model

An image corresponds to a representation of a three dimensional scene onto a two dimensional surface. Different camera models [13] are used to represent the mapping between a point in the space and the point where it will be projected in a 2d-image acquired with a camera. One of the most used models is the Pinhole.

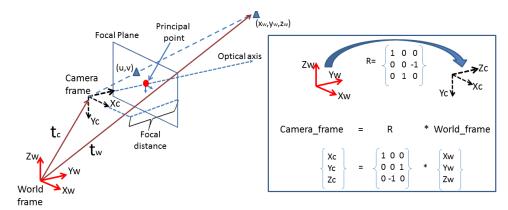

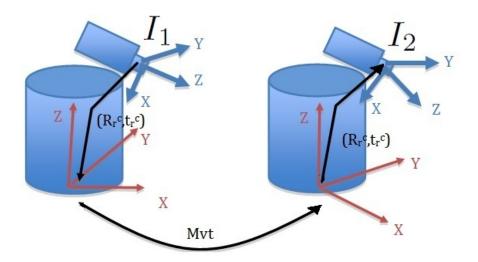

The Pinhole model shown in figure 2.1 expresses the relationship between an image coordinate (u, v) and a world coordinate  $(X_w, Y_w)$  in function of the intrinsic (K) and extrinsic  $(R, t_c)$  camera parameters. The model is given by equation 2.1.

$$\begin{bmatrix} su \\ sv \\ s \end{bmatrix} = KR \begin{bmatrix} X_w \\ Y_w \\ Z_w \end{bmatrix} + Kt_c \tag{2.1}$$

The intrinsic parameters (K) depend on the internal parameters of the camera and are represented with the matrix K given by the equation 2.2. The extrinsic parameters  $(R, t_c)$  depend of the orientation and the position of the camera respect to the world frame.

**Figure 2.1: Pinhole Camera Model** - In the figure, the camera frame is parallel to the world frame. For this reason, in this ideal example, the components of the rotation Matrix R are just 1, 0 and -1. Physically, it corresponds to have the camera parallel to the ground plane and the optical axis aligned with the Y-axis of the world frame.

$$K = \begin{bmatrix} \alpha_u & s & u_0 \\ 0 & \alpha_v & v_0 \\ 0 & 0 & 1 \end{bmatrix}$$

(2.2)

where,

s = skew

$\alpha_u = k_u f$

$\alpha_v = k_v f$

$k_u, k_v = \text{pixel size in (pixel/m)}$

f = focal distance

$(u_0, v_0) = \text{principal point coordinates}$

Generally, in a CCD camera the skew factor is equal to zero, which means that the x-axis and y-axis are perpendicular.

# 2.3 Distortion Correction

One of the main problems of long field of view cameras in image processing is the Distortion. The Distortion is a phenomenon caused by the optics properties of the camera. Typically, there are two types of distortion: radial and tangential. Radial distortion is due to the lens properties while tangential distortion is due to the imperfect centering of the lens with respect to the sensor.

The distortion effect is a phenomenon that is more important in cameras with wide angle lenses. In some Pinhole cameras with small field of view the distortion is almost null, while in cameras with longer field of view it is very important.

Working with a distorted image increases the complexity of the algorithms. In an undistorted image, a straight line can appear like a curve. Distortion correction is needed in many image processing algorithms.

Different camera models exist to model the distortion, some applications can use a simple cuadratic model to undistort the images, however, a higher order model can be used to improve the distortion correction results. The next equation shows a sixth order model, this model is used in different Matlab toolboxes (California Tech). In this equation the normalized (pinhole) image projection  $x_n = (x, y)$  is used to compute a new normalized coordinate  $x_d = (x_d(1), x_d(2))$ .

$$x_d = (x_d(1), x_d(2)).$$

$$x_d = \begin{bmatrix} x_d(1) \\ x_d(2) \end{bmatrix} = (1 + k_c(1)r^2 + k_c(2)r^4 + k_c(5)r^6)x_n + dx$$

$k_c$  is a vector containing the distortion information, and dx corresponds to the tangential distortion given by the next equation:

to tion given by the next equation:

$$dx = \begin{bmatrix} 2k_c(3)xy + k_c(4)(r^2 + 2x^2) \\ kc(3)(r^2 + 2y^2) + 2k_c(4)xy \end{bmatrix}$$

and,

$$r^2 = x^2 + y^2$$

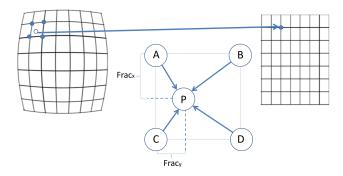

When building an undistorted image, the distortion correction algorithm remaps the pixels of an image in new coordinates according to a distortion model. This remap can cause non-integer coordinates as shown in the figure 2.2.

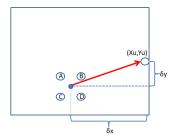

Figure 2.2: Bilinear interpolation -  $Frac_x$  and  $Frac_y$  are values between 0 and 1. They are used to assign the weights of the vicinity pixels (A, B, C and D) for the interpolation

The undistorted pixel can be replaced by the closest neighbor, however this can create artifacts in the reconstructed images that can affect the post-processing algorithms of the images. For example, in a corner detection algorithm, false corners can be detected.

Another approach to rebuild the unknown pixels is to implement a bilinear interpolation of the four pixels in the vicinity (A, B, C and D). When implementing a bilinear interpolation, weights are assigned to each one of the four neighbor pixels. For example, in the case that the unknown pixel is exactly in the middle of the four pixels ( $Frac_x = 0.5$  and  $Frac_y = 0.5$ ), the unknown pixel corresponds to the average of the four vicinity pixels.

The bilinear interpolation is done using the weighted sum given by the equation 2.3.

#### 2. THEORETICAL BACKGROUND ON DRIVING ASSISTANCE

$$P = A.S + B.T + C.U + D.V (2.3)$$

where,

$$S = (1 - Frac_x)(1 - Frac_y) \tag{2.4}$$

$$T = (1 - Frac_x)Frac_y (2.5)$$

$$U = Frac_x(1 - Frac_y) \tag{2.6}$$

$$V = Frac_x Frac_y \tag{2.7}$$

$$P = A(1 - Frac_x)(1 - Frac_y) + B(1 - Frac_x)Frac_y + CFrac_x(1 - Frac_y) + DFrac_xFrac_y$$

(2.8)

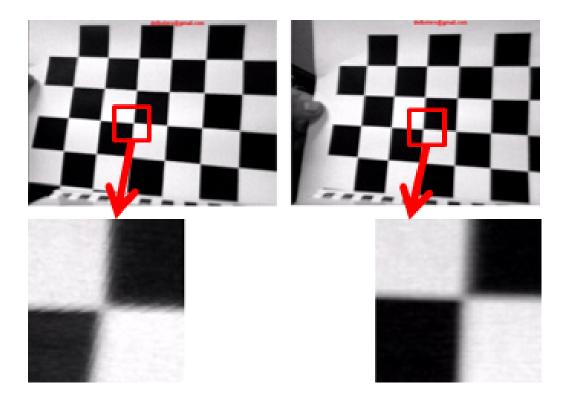

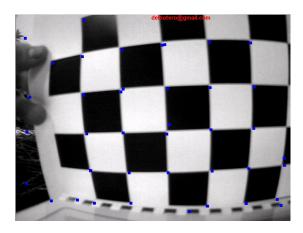

Distortion correction is usually implemented detecting the corners of a pattern chessboard image. Then, using an optimization algorithm the distortion parameters are computed. Different software toolboxes and applications exist to implement distortion correction.

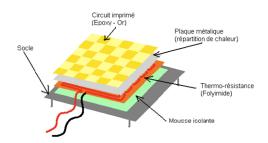

In the case of IR images, for calibration a simple chessboard cannot be used because the chesspatern will not be visible. Figure 2.3 shows a special chesspattern designed like a Printed Circuit Board (PCB) with an electric resistance in order to heat the cooper regions.

Figure 2.3: Infrared Cheesboard for calibration - This pattern has a small dimension

# 2.4 Perspective transformation

Homography is an important algorithm in computer vision widely used in many applications. When applying a homography to an image, the coordinates of the pixels of the image (x,y) are modified using an affine transformation. An homography results in the transformation of a plane. The rotation is particular case of a homography with H represented in the equation 2.9.

$$H_{rotation}(\theta) = \begin{bmatrix} cos(\theta) & -sin(\theta) & 0\\ sin(\theta) & cos(\theta) & 0\\ 0 & 0 & 1 \end{bmatrix}$$

(2.9)

The homography is implemented using the equation 2.10

$$\lambda \begin{bmatrix} x_h \\ y_h \\ 1 \end{bmatrix} = \begin{bmatrix} h_{11} & h_{12} & h_{13} \\ h_{21} & h_{22} & h_{23} \\ h_{31} & h_{32} & h_{33} \end{bmatrix} \begin{bmatrix} x \\ y \\ 1 \end{bmatrix}$$

(2.10)

A value  $\lambda$  done by equation 2.11 appears like a scale value for all the coordinates of the output image.

$$\lambda = xh_{31} + yh_{32} + h_{33} \tag{2.11}$$

From the equations 2.10 and 2.11, the values of  $x_h$  and  $y_h$  are done by the equations 2.12 and 2.13 respectively.

$$x_h = (xh_{11} + yh_{12} + h_{13})/(xh_{31} + yh_{32} + h_{33})$$

(2.12)

$$y_h = (xh_{21} + yh_{22} + h_{23})/(xh_{31} + yh_{32} + h_{33})$$

(2.13)

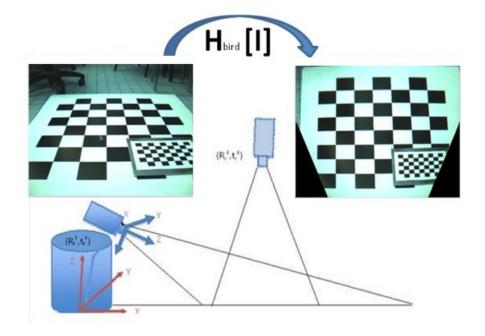

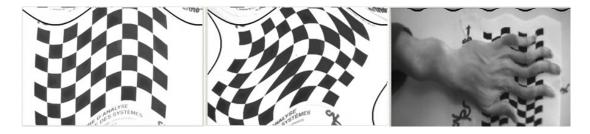

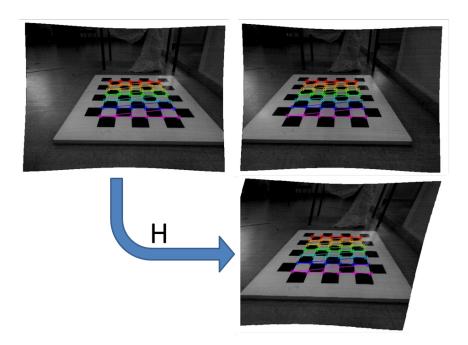

A homography can be used to build a Bird's eye view using a perspective transformation of an image, in this case a homography is used to build the Bird's eye view. The Bird's eye view corresponds to a virtual camera placed above the scene. See figure 2.4.

Figure 2.4: Bird's eye view transformation - Bird's eye view transformation.

In [14], homography is used to estimate the trajectory of a vehicle using a single camera placed on the roof of a car. In [15] and [16], it is used to generate X-ray panoramic images of bones using different views. In [17], detection and reconstruction of obstacles structures located over a ground plane is presented using homography.

#### 2. THEORETICAL BACKGROUND ON DRIVING ASSISTANCE

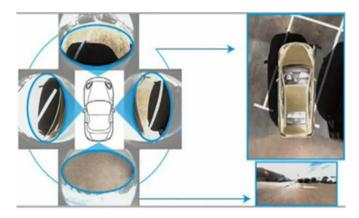

For drive assistance, some vehicle fabricants have developed systems based in perspective transformations to rebuild a Bird's Eye view and a Side view of the car. The company Xylon has developed a multi-camera system which uses four fish-eye cameras and an FPGA to rebuild a synthetic image in real-time that corresponds to the different perspective views of the vehicle, including the Bird's eye view. See figure 2.5. A similar system is beginning to be commercialized by the company BMW.

**Figure 2.5: Xylon demo test vehicle** - The system correct the lens distortions of the fish eye views, implements perspective transformations, and then displays a synthetic image. Taken from Xylon

The hardware acceleration of homography is useful for many applications included IPM. In [18] and [19], FPGA implementations of homography are presented; in both cases a SRAM memory is used.

## 2.5 Infrared

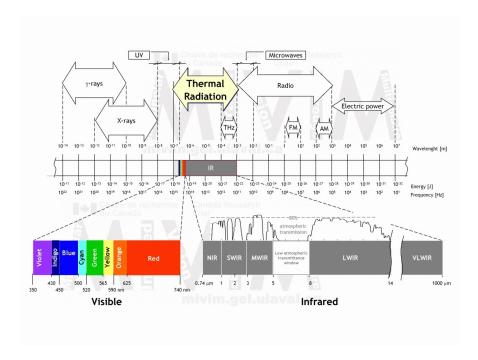

The human eye is sensible to wavelengths between 350 nm and 740 nm, this band of wavelengths is called visible spectrum. The infrared wavelengths are longer than that of visible light and includes wavelength that are between 740 nm and 14 um. Image 2.6 shows the electromagnetic spectrum (represented in function of the wavelength).

The infrared spectrum is subdivided into five gaps:

- 1. NIR (Near Infrared)

- 2. SWIR(Short-wavelength infrared)

- 3. MWIR(Mid-wavelength infrared)

- 4. LWIR(Long-wavelength infrared)

- 5. VLWIR(Very Long-wavelength infrared)

Using special cameras, wavelengths other than visible, can be observed by a human. Visible cameras capture the reflective light properties of the objects in the scene, while IR cameras are sensitive to the thermal emissivity properties of the objects.

The radiation measured by a IR camera comes from three sources:

- 1. Object's inherent temperature 2. Surroundings that was reflected onto the object's surface

- 3. Radiation that passed through the object from behind.

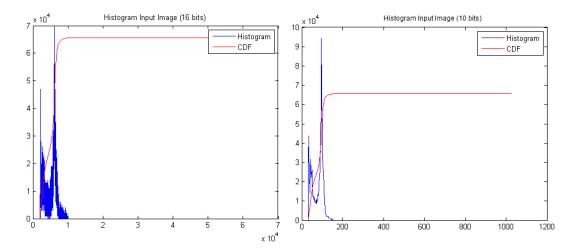

Thanks to the advances in infrared imagery, nowadays, we have High Dynamic Range (HDR) infrared cameras with a sensitivity of 16 bits. Usually the useful information in an IR image

Figure 2.6: Electromagnetic Spectrum - Taken from http://mivim.gel.ulaval.ca

is concentrated in a little portion of this dynamic range; IR images have extremely low SNR (signal to noise ratio).

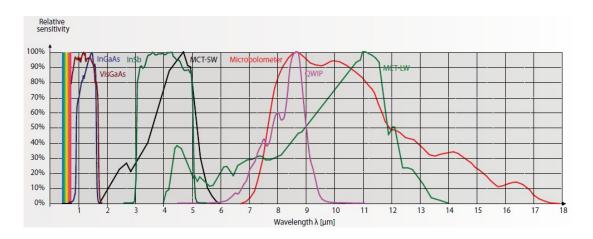

Different kind of IR sensor exists, with different spectral response according to their technology. See figure 2.7. IR cameras detect radiation in the electromagnetic spectrum with wavelengths from roughly 900 nm to 14,000 nm and produce images from that radiation. Common silicon detectors are sensitive to about 1050 nm, while InGaAs sensitivity starts around 950nm and ends between 1700 and 2600 nm, depending on the specific configuration.

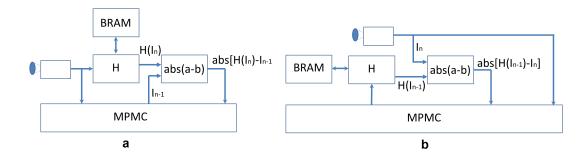

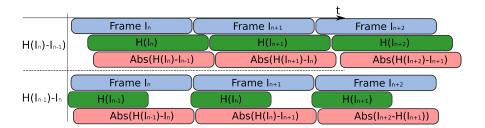

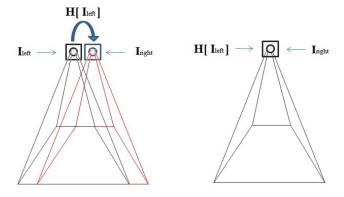

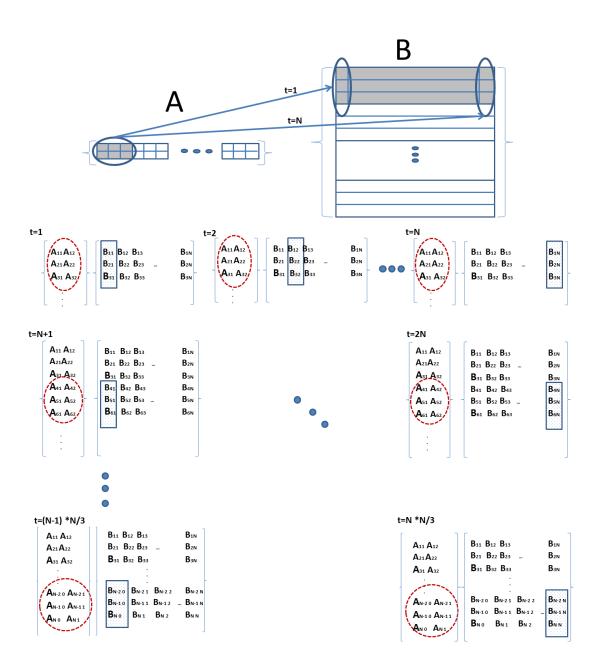

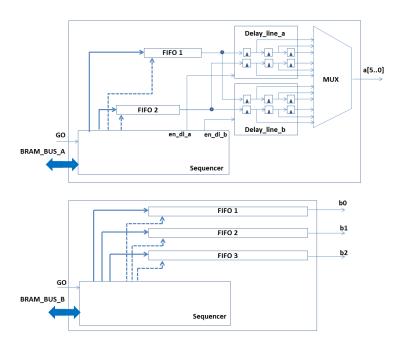

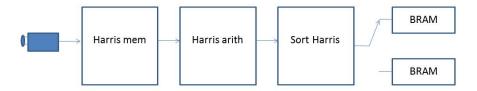

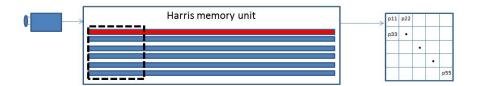

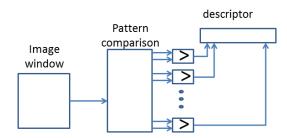

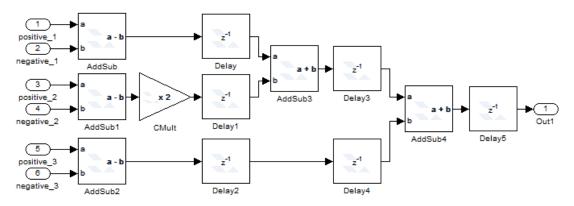

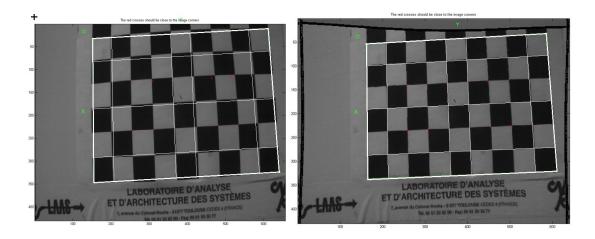

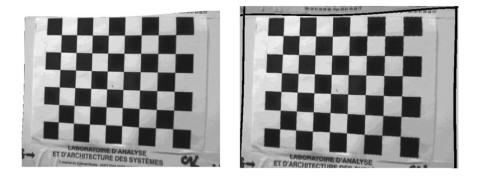

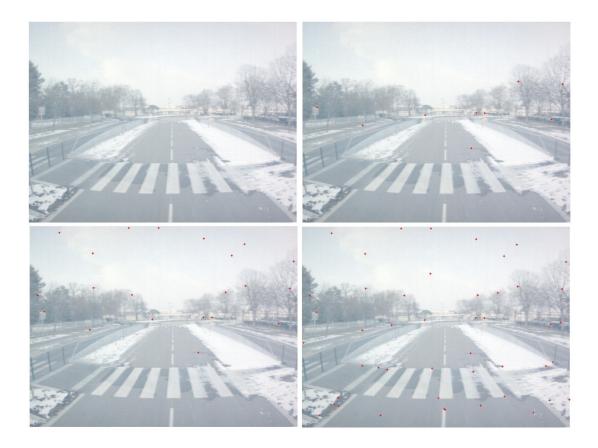

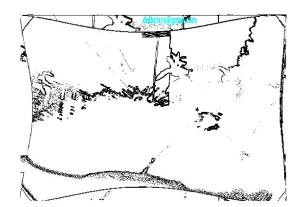

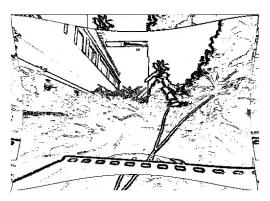

The most common technology used in infrared cameras is the Microbolometer, which allows for the fabrication of uncooled cameras.