# TIREX: une représentation textuelle intermédiaire pour un environnement d'exécution virtuel, échanger des informations du compilateur et d'analyse du programme

Artur Pietrek

#### ▶ To cite this version:

Artur Pietrek. TIREX: une représentation textuelle intermédiaire pour un environnement d'exécution virtuel, échanger des informations du compilateur et d'analyse du programme. Autre [cs.OH]. Université de Grenoble, 2012. Français. NNT: 2012GRENM046. tel-00780232

# HAL Id: tel-00780232 https://theses.hal.science/tel-00780232

Submitted on 23 Jan 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### UNIVERSITÉ DE GRENOBLE

### **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : **Informatique** Arrêté ministérial : 7 août 2006

Présentée par

#### **Artur Pietrek**

Thèse dirigée par **Jean-Claude Fernandez** et codirigée par **Benoît Dupont de Dinechin**

préparée au sein VERIMAG et de l'Ecole Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

# TIREX: a textual target-level intermediate representation

for virtual execution environment, compiler information exchange and program analysis

Thèse soutenue publiquement le **2 octobre 2012**, devant le jury composé de :

#### Mr. Philippe Clauss

Professeur, Université de Strasbourg, Rapporteur

#### Mr. Albert Cohen

Directeur de Recherche, INRIA, Rapporteur

#### Mr. Benoît Dupont de Dinechin

Directeur du Développement Logiciel, Kalray, Co-Directeur de thèse

#### Mr. Jean-Claude Fernandez

Professeur, Université Joseph Fourier, Directeur de thèse

#### Mr. Jean-Francois Méhaut

Professeur, Université Joseph Fourier, Président

#### Mr. Fabrice Rastello

Chargé de recherche, INRIA, Examinateur

# Acknowledgements

Foremost, I would like to express my gratitude to my both advisors: Jean-Claude Fernandez from Verimag, and Benoît Dupont de Dinechin from Kalray; first for the opportunity to work on the subject, and for their patience and knowledge, as well as motivation and encouragement in the tough moments.

I would also like to thank Philippe Clauss, Albert Cohen, Jean-François Méhaut and Fabrice Rastello, the members of my thesis committee, for their interest in my work and insightful comments. Special thanks go to Albert Cohen for his attempt to change my focus on engineering problems into a deeper, research view; and to Fabrice Rastello for interesting discussions on loops, data dependencies and traces.

Also, I thank to all my colleagues from Kalray and my fellow labmates from Verimag, for support during that three and a half years, and helpful comments. Especially to Florent Bouchez and Marc Poulhiès for their help.

I also have to mention my friends who helped me in many different things and spent their time with me on many activities: Vasso, Paris, Jean, Eduardo, Kasia, Piciu, Asia, Gosia, Karo, Justyna, Maciek, Radek, Michał, and others. Thank you! Especially I would like to thank to my parents for encouragement and to Oyuna for supporting me.

#### **Abstract**

Some environments require several compilers, for instance one for the operating system, supporting the full C/C++ norm, and one for the applications, potentially supporting less but able to derive more performance. Maintaining different compilers for a target requires considerable effort, thus it is easier to implement and maintain target-dependent optimizations in a single, external tool. This requires a way of connecting these compilers with the target-dependent optimizer, preferably passing along some internal compiler data structures that would be time-consuming, difficult or even impossible to reconstruct from assembly language for instance.

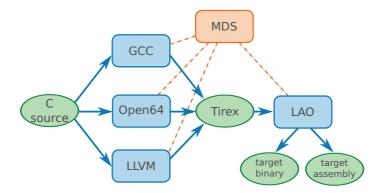

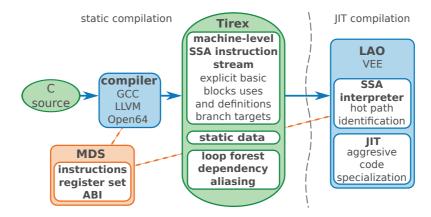

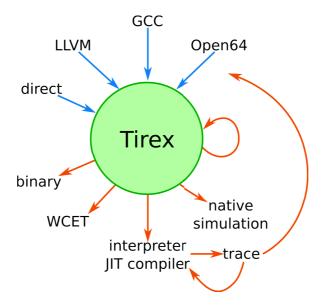

In this thesis we introduce Tirex, a Textual Intermediate Representation for EXchanging target-level information between compilers, optimizers an different tools in the compilation toolchain. Our intermediate representation contains an instruction stream of the target processor, but still keeps the explicit program structure and supports the SSA form(*Static Single Assignment*). It is easily extensible and highly flexible, which allows any data to be passed for the purpose of the optimizer.

We build Tirex by extending the existing Minimalist Intermediate Representation (MinIR), itself expressed as a YAML textual encoding of compiler structures. Our extensions in Tirex include: lowering the representation to a target level, conserving the program data stream, adding loop scoped information and data dependencies. Tirex is currently produced by the Open64 and the LLVM compilers, with a GCC producer under work. It is consumed by the Linear Assembly Optimizer (LAO), a specialized, target-specific, code optimizer.

We show that Tirex is versatile and can be used in a variety of different applications, such as a virtual execution environment (VEE), and provides strong basis for a program analysis framework. As part of the VEE, we present an interpreter for a Static Single Assignment (SSA) form and a *just-in-time* (JIT) compiler. We show how interpreting a target-level representation eliminates most of the complexities of mixed-mode execution. We also explore the issues related to efficiently interpreting a SSA form program representation.

#### Résumé

Certains environnements ont besoin de plusieurs compilateurs, par exemple un pour le système d'exploitation, supportant la norme C/C++ complète, et l'autre pour les applications, qui supporte éventuellement un sous-ensemble de la norme, mais capable de fournir plus de performance. Le maintien de plusieurs compilateurs pour une plateforme cible représente un effort considérable. Il est donc plus facile d'implémenter et de maintenir un seul outil responsable des optimisations particulières au processeur ciblé. Il nous faut alors un moyen de relier ces compilateurs à l'optimiseur, de préférence, en gardant au passage certaines structures de données internes aux compilateurs qui, soit prendraient du temps, soit seraient impossible à reconstruire à partir du code assembleur par exemple.

Dans cette thèse, nous introduisons Tirex, une représentation textuelle intermédiaire pour échanger des informations de bas niveau, déjà dépendantes de la cible, entre les compilateurs, les optimiseurs et les autres outils de la chaîne de compilation. Notre représentation contient un flot d'instructions du processeur cible, mais garde également la structure explicite du programme et supporte la forme SSA (*Static Single Assignment*). Elle est facilement extensible et très flexible, ce qui permet de transmettre toute donnée jugée importante à l'optimiseur.

Nous construisons Tirex par extension de MinIR, une représentation intermédiaire elle-même basée sur un encodage YAML des structures du compilateur. Nos extensions de Tirex comprennent : l'abaissement de la représentation au niveau du processeur cible, la conservation du flot de données du programme, ainsi que l'ajout d'informations sur les structures de boucles et les dépendances de données.

Nous montrons que Tirex est polyvalent et peut être utilisé dans une variété d'applications différentes, comme par exemple un environnement d'exécution virtuel (VEE), et fournit une base forte pour un environnement d'analyse du programme. Dans le cadre d'un VEE, nous présentons un interprèteur de la forme SSA et un compilateur *just-in-time* (JIT). Nous montrons comment l'interprétation d'une représentation au niveau du processeur cible élimine la plupart des problèmes liés à l'exécution en mode mixte. Nous explorons également les questions liées à l'interprétation efficace d'une représentation de programme sous la forme SSA.

# **Contents**

| Co | Contents 7 |                                                  |    |  |

|----|------------|--------------------------------------------------|----|--|

| 1  | Intr       | roduction                                        | 3  |  |

|    | 1.1        | Program compilation                              | 3  |  |

|    |            | 1.1.1 Just-In-Time                               | 5  |  |

|    |            | 1.1.2 Dynamic optimization                       | 8  |  |

|    | 1.2        | A third approach                                 | 9  |  |

|    | 1.3        | Contributions                                    | 10 |  |

|    | 1.4        | Outline of this thesis                           | 11 |  |

| 2  | Bac        | kground                                          | 13 |  |

|    | 2.1        | Program and control-flow graph                   | 13 |  |

|    |            | 2.1.1 Program structure                          | 14 |  |

|    |            | 2.1.2 Control-flow graph and its dominator tree  | 15 |  |

|    | 2.2        | Intermediate representation                      | 16 |  |

|    | 2.3        | Static Single Assignment form                    | 16 |  |

|    | 2.4        | On data, data dependence and loop nesting forest | 18 |  |

|    |            | 2.4.1 Data dependence definition and types       | 18 |  |

|    |            | 2.4.1.1 Data dependence graph                    | 19 |  |

|    |            | 2.4.2 On loops and loop nesting forests          | 19 |  |

|    | 2.5        | Summary                                          | 21 |  |

| 3  | Prio       | or Work                                          | 23 |  |

|    | 3.1        | Interpretation of the SSA form                   | 23 |  |

|    | 3.2        | Compilation Just-In-Time                         | 24 |  |

|    |            | 3.2.1 The beginning                              | 24 |  |

|    |            | 3.2.2 Java                                       | 25 |  |

|    |            | 3.2.3 Common Language Infrastructure             | 26 |  |

|    |            | 3.2.4 Staged dynamic compilation                 | 27 |  |

|    | 3.3        | Static Binary optimizers                         | 27 |  |

|    | 3.4        | Dynamic Optimizers and Binary Translators        | 28 |  |

|    | 3.5        | Binary instrumentation                           | 29 |  |

8 CONTENTS

|   |      | 3.5.1                 | Static binary instrumentation               | 29 |  |  |  |  |  |

|---|------|-----------------------|---------------------------------------------|----|--|--|--|--|--|

|   |      | 3.5.2                 | Dynamic binary instrumentation              | 29 |  |  |  |  |  |

|   |      | 3.5.3                 | Hybrid approach                             | 30 |  |  |  |  |  |

|   | 3.6  | Code                  | • • • • • • • • • • • • • • • • • • • •     | 30 |  |  |  |  |  |

|   | 3.7  |                       |                                             | 31 |  |  |  |  |  |

| 4 | C to | to CIL compilation 33 |                                             |    |  |  |  |  |  |

|   | 4.1  | Comm                  | non Intermediate Language                   | 34 |  |  |  |  |  |

|   | 4.2  | The Co                | ommunity                                    | 36 |  |  |  |  |  |

|   |      | 4.2.1                 | LCC.NET                                     | 36 |  |  |  |  |  |

|   |      | 4.2.2                 | The DotGNU Portable.NET and ILDJIT Projects | 37 |  |  |  |  |  |

|   |      | 4.2.3                 | The GCC4NET                                 | 37 |  |  |  |  |  |

|   |      | 4.2.4                 | The Mono Project                            | 38 |  |  |  |  |  |

|   |      | 4.2.5                 | The LLVM-MSIL code generator                | 38 |  |  |  |  |  |

|   | 4.3  | C to C                | IL compilation: study of issues             | 38 |  |  |  |  |  |

|   |      | 4.3.1                 | Example                                     | 39 |  |  |  |  |  |

|   | 4.4  | The G                 | CC-CIL Compiler                             | 42 |  |  |  |  |  |

|   |      | 4.4.1                 | <u>.</u>                                    | 42 |  |  |  |  |  |

|   |      | 4.4.2                 | The Compiler                                | 42 |  |  |  |  |  |

|   |      | 4.4.3                 | -                                           | 44 |  |  |  |  |  |

|   |      | 4.4.4                 | Improvements                                | 45 |  |  |  |  |  |

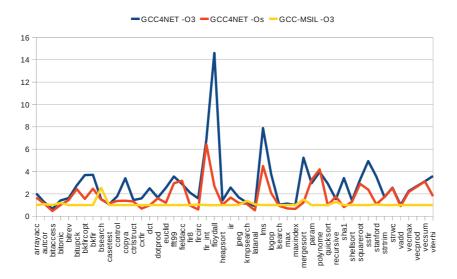

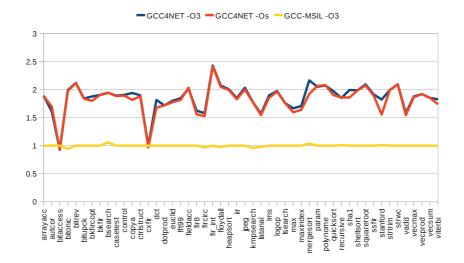

|   | 4.5  | Result                | -                                           | 46 |  |  |  |  |  |

|   | 4.6  |                       |                                             | 48 |  |  |  |  |  |

| 5 | The  | Frame                 | work                                        | 49 |  |  |  |  |  |

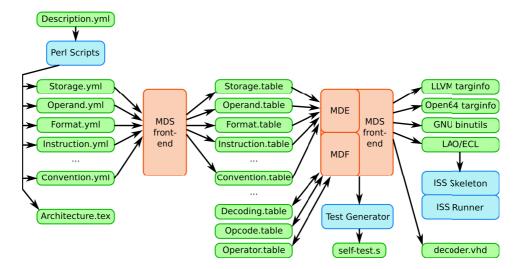

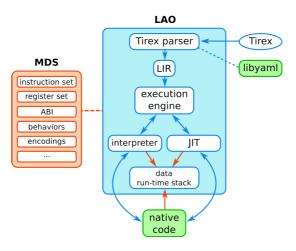

|   | 5.1  | Machi                 | ne Description System                       | 50 |  |  |  |  |  |

|   |      | 5.1.1                 | SSA Form on Target-Level Code               | 51 |  |  |  |  |  |

|   |      |                       | 5.1.1.1 MDS Support for SSA Form            | 51 |  |  |  |  |  |

|   |      |                       | 5.1.1.2 Operand Constraints in SSA Form     | 53 |  |  |  |  |  |

|   |      |                       | 5.1.1.3 Predicated Instructions in SSA Form | 53 |  |  |  |  |  |

|   | 5.2  | Low L                 | evel Virtual Machine                        | 54 |  |  |  |  |  |

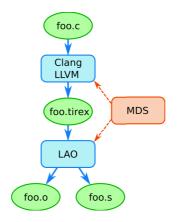

|   |      | 5.2.1                 | LLVM in our toolchain                       | 54 |  |  |  |  |  |

|   |      | 5.2.2                 | The Tirex Code Generator                    | 55 |  |  |  |  |  |

|   |      | 5.2.3                 | Current state and limitations               | 56 |  |  |  |  |  |

|   | 5.3  | Linear                | Assembly Optimizer                          | 56 |  |  |  |  |  |

|   |      | 5.3.1                 | Program processing                          | 57 |  |  |  |  |  |

|   | 5.4  | Summ                  |                                             | 58 |  |  |  |  |  |

| 6 | Tire | x                     |                                             | 59 |  |  |  |  |  |

|   | 6.1  | The M                 | inIR project                                | 61 |  |  |  |  |  |

|   | 6.2  |                       |                                             | 62 |  |  |  |  |  |

|   | 63   |                       | <del>-</del>                                | 64 |  |  |  |  |  |

| CONTENTS  | 1 |

|-----------|---|

| CONTLINIS |   |

|                 |              | 6.3.1   | Code Stream Representation            | 67 |  |  |

|-----------------|--------------|---------|---------------------------------------|----|--|--|

|                 |              | 6.3.2   | Sections                              | 68 |  |  |

|                 |              | 6.3.3   | Data Stream Representation            | 70 |  |  |

|                 | 6.4          | Loop S  | Scoped Information                    | 71 |  |  |

|                 | 6.5          | The us  | se cases                              | 74 |  |  |

|                 | 6.6          | Summ    | ary                                   | 75 |  |  |

| 7               | The          | Tirex F | Runtime                               | 77 |  |  |

|                 | 7.1          | Overv   | iew                                   | 79 |  |  |

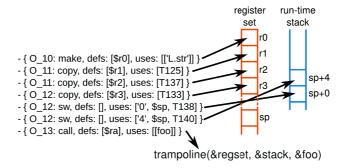

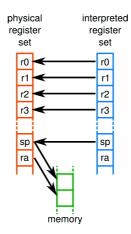

|                 | 7.2          | Interp  | reter                                 | 81 |  |  |

|                 |              | 7.2.1   | Interpreting Instructions             | 82 |  |  |

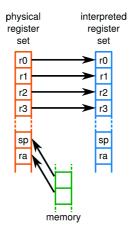

|                 |              | 7.2.2   | Calling Native Code                   | 82 |  |  |

|                 |              | 7.2.3   | Interpreting the SSA Form             | 84 |  |  |

|                 | 7.3          | The JI  | Г Compiler                            | 86 |  |  |

|                 |              | 7.3.1   | Code generation                       | 87 |  |  |

|                 |              | 7.3.2   | Code cache                            | 88 |  |  |

|                 | 7.4          | Summ    | ary                                   | 90 |  |  |

| 8               | Con          | clusion | ı                                     | 91 |  |  |

|                 | 8.1          | Future  | ework                                 | 91 |  |  |

|                 |              | 8.1.1   | Intermediate representation           | 91 |  |  |

|                 |              | 8.1.2   | The runtime                           | 92 |  |  |

|                 | 8.2          | Perspe  | ectives                               | 93 |  |  |

|                 |              | 8.2.1   | Execution traces and program analysis | 93 |  |  |

|                 |              | 8.2.2   | WCET                                  | 95 |  |  |

|                 |              | 8.2.3   | Native software simulation            | 96 |  |  |

|                 | 8.3          | Summ    | ary                                   | 97 |  |  |

| List of Figures |              |         |                                       |    |  |  |

| Listings        |              |         |                                       |    |  |  |

| Bi              | Bibliography |         |                                       |    |  |  |

2 CONTENTS

# Chapter 1

# Introduction

#### 1.1 Program compilation

Software development evolved drastically since first computers. Starting from programs written directly in the machine binary code, through assembly languages that made the process easier, up to many different kinds of high-level languages with different levels of abstraction. Depending on the needs, programmer can choose the language that makes it easier and less time-consuming to express the algorithms, provides portability among several different architectures, and allows to reuse some parts of the code, as well as provides easier ways of debugging.

Programs written in high-level languages depend on an other special program, a compiler, to transform them into binary code that can be executed on a given machine. The most important task of the compiler is to preserve the semantics of a source program in the resulting code. However, the higher abstraction of the source language, the more complicated it is for the compiler to generate optimal code, that is, code that would have performance similar to code written directly in the assembly language by an experienced programmer.

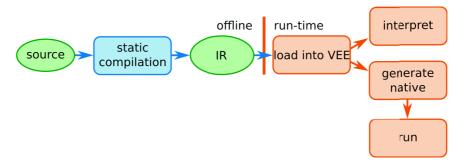

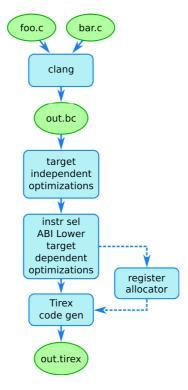

Of course, modern compilers deal with optimization problems quite well, assuming they do not have constraint resources in terms of time and memory. This is usually the case when a whole program is compiled into a given processor binary code prior to execution. Figure 1.1 shows a simplified compilation model, which includes in the

Figure 1.1: Static compilation

Figure 1.2: Dynamic compilation

compilation box phases such as assembling<sup>1</sup> and linking<sup>2</sup>. In such a case it does not matter how long the process will take, with, obviously, some reasonable limits, as it would be difficult to develop an application when a compiler processes one compilation unit for several hours or days. This compilation model is known as *static compilation*, where a complete, directly executable, native code is generated statically before execution of the program.

A static compiler, can produce fairly well optimized code, however, it does not have the knowledge about program execution like given parameters, size of processed data, or even the fact that not the whole program is run but rather some specific parts of it, for instance, not all conditional branches might be taken. The compiler can only speculate on the program execution behavior and misses some optimization opportunities.

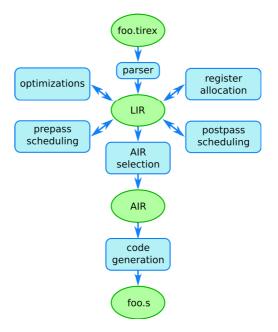

Opposite to static compilation, which is terminated prior to program execution, the dynamic compilation model as shown on Figure 1.2 employs a *virtual execution environment* (VEE) or *virtual machine*<sup>3</sup> (VM) where the program is in some kind of intermediate form (generated statically from a high-level language) and is loaded and executed either by interpretation or after being compiled to native code on demand, prior to execution (hence the name *dynamic compilation*). Such a model adds to program execution time, thus the VEE should spend as little time as possible managing the interpretation and the compilation processes. Also, the dynamic compiler should perform only transformations that would not exceed the time gained by applying these transformations in the first place.

The dynamic compilation techniques have been known for several decades. Although at the beginning perceived too expensive in terms of time and resources to be used as an alternative to static compilation, they evolved in the last two decades be-

<sup>&</sup>lt;sup>1</sup>The process of binary encoding the assembler language, resulting with so called *object files*.

<sup>&</sup>lt;sup>2</sup>Combining several object files into single executable.

<sup>&</sup>lt;sup>3</sup>A Virtual Execution Environment or Virtual Machine is a software that implements a machine capable of executing a program or a whole operating system. It hides the physical machine or/and the host operating system from the executed program.

coming more and more popular with the increasing performance and memory space of modern machines. They were also popularized due to the widespread of Java and .Net environments. Nowadays they could be found even in embedded, resource-constraint devices such as mobile phones and other portable devices.

These techniques, even though aiming lots of different goals, have one thing in common, that is the ability to inspect and alter a program during its execution and make use of obtained information. This could be useful not only for gaining additional performance, but also for detecting and preventing faulty or malicious program behaviors.

Among many different dynamic compilation systems, two main branches can be distinguished: Just-In-Time (JIT) and dynamic optimization.

#### 1.1.1 Just-In-Time

Just-In-Time divides the compilation process into two stages. First the program written in a high-level language is translated into a target-independent intermediate representation with the instruction set and the ABI<sup>4</sup> of a given Virtual Machine. Then, the intermediate representation can be partially interpreted, as well as compiled to target-processor code during execution, or in other words compiled *just-in-time* for execution.

The main goal of this approach is to provide a way to abstract any program from the underlying operating system and processor. A program can be written and statically compiled only once into a redistributable package, without any knowledge or assumptions about the host machine, targeting a Virtual Machine instead.

JIT also aims to improve performance of programs versus their statically compiled versions. For instance, a static compiler has to assume that the smallest subset of instructions of a given architecture can be used, otherwise a program could be executed only on the specific versions of a processor that provide the particular functionality. A JIT compiler, in contrary, can generate code that use all the capabilities of the version of the processor that the Virtual Machine runs on.

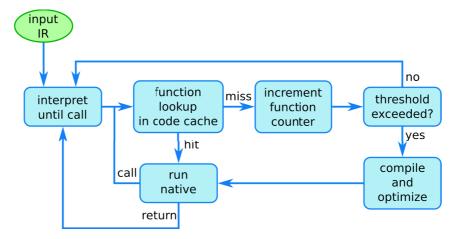

A simplified JIT structure is depicted on 1.3. Usually the execution starts in interpretation mode. Opposite to compilation, and although less efficient than running native code, this process does not introduce overhead. During interpretation, program execution is observed and frequently executed fragments of the given program are identified. Then, instead of translating the whole program to the native instruction stream, the compilation and optimization processes are limited only to these "hot" fragments.

<sup>&</sup>lt;sup>4</sup>Application Binary Interface – describes the interface between functions and a program with the operating system. It defines details such as data types with theirs sizes and alignments, the calling conventions (how the arguments are passed and results returned), stack-frame organization and register usage.

Figure 1.3: Simplified JIT structure

As an alternative, some JIT environments do not implement an interpreter at all, but rather employ two or three different compilation schemes, such as:

- fast non-optimizing compiler that produces instrumented code,

- non-optimizing compiler,

- optimizing compiler.

JIT can also benefit from the knowledge about the program execution gathered during interpretation, e.g., specializing the code to favor the paths of a program that are taken more often, or by observing that some variables in fact have constant or predictable values it can benefit from value-based optimizations. All these improvements are limited just to most frequently executed fragments, while the rest of the program, depending on the JIT constructions, is interpreted or compiled on demand with a fast, non-optimizing compiler. The hot fragments used by JIT environment as compilation and optimization units are either *hot functions* or *hot traces*.

**Hot Functions** In classical JIT a unit of compilation and optimization is a function. Each time a call to a function occurs a counter associated to it is incremented. When a threshold is exceeded, a function is considered to be *hot* and its (optimized) compilation is triggered. From that moment every call to this function results in calling the native code from the code cache instead of interpreting.

Operating on whole functions makes the management of compiled code relatively easy (its recompilation with more optimizations or eviction). However, obviously some paths within a function could be never or not frequently taken, thus the native code would take more space in the code cache than it is really required.

**Hot Traces** Some recent JIT compilers operate not on functions, but rather on traces of instructions. These *hot traces*, or *hot paths*, are usually gathered with a resolution of basic blocks during the interpretation of a program and correspond to the path taken in the control-flow graph. The scope of such a trace is not limited to a function boundary, but can capture several function calls or even recursive calls to the same function.

The difficulty of such approach is to handle the non-frequently taken, conditional paths which could be not captured into the trace. If the result of some conditional branch is different than expected, there is a need for special stub that will exit from the trace and execute the correct code. Also, some parts of different traces can overlap when capturing a recursive call, leading to code duplication in the code cache. However, the code locality in the code cache is much better in comparison to the function compilation approach.

Mixed-mode execution in JIT Although there exists JIT environments that do not rely on interpretation but rather on a few different JIT compilers instead (e.g., fast non-optimizing and slower optimizing), the process is still employed as a cheap and easy way for gathering profile, identification of hot functions or hot traces, as well as some other information. It is much easier to add profiling mechanisms along with interpretation routines than to dynamically insert special code inside a compiled program.

This, however, results in *mixed-mode execution*, a situation where both interpreted and native code are executed together. The difficulty lies in the differences between the Application Binary Interface (ABI) of the Virtual Machine and the target platform. These differences, especially *endianess* and *calling conventions* complicates the process of calling a native function from within the interpreted code and getting back the result. The same situation occurs when the native code calls a function that is not yet compiled, which results in falling back to the interpreter. These calls have to be handled through a special interface that ensures the arguments, results and the global data are compatible on both sides. This becomes more complicated when using non basic data types but complex structures and when accessing global data.

**A few words on JIT compilation** Before starting optimizing the code, a JIT compiler has to perform a lot of tasks, including among others:

- interpretation,

- ABI lowering,

- instruction selection,

- data layout and stack frames formation,

Figure 1.4: Simplified dynamic optimizer structure

- · register allocation,

- instruction scheduling.

Most of these tasks are the result of target-independent intermediate representation and do not profit much from information gained at run-time. Thus even before starting optimizations, a JIT compiler introduces overhead, limiting the time that can be spent on optimizations to gain more performance.

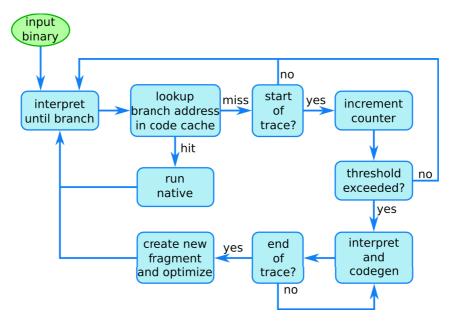

#### 1.1.2 Dynamic optimization

Dynamic optimization focuses mainly on improving performance of existing target-dependent binaries by exploiting run-time information that was not previously available for the static compiler prior to program execution. Figure 1.4 shows the structure of a simplified dynamic optimizer. First, the input native instruction stream is disassembled, then the program execution is observed by interpreting that disassembled instruction stream. When a branch occurs, the branch address is looked up in the trace cache. If found, the trace is executed from the cache, otherwise interpretation is continued until a trace of instructions for code generation and optimization is selected.

**Hot Traces** Similarly to trace JIT, only the hot traces are subject to optimization and specialization. A trace of blocks of instructions is gathered during interpretation, and is not limited to function boundaries, but can cover several function calls (including recursive calls) and can contain the same portions of code as other traces.

**Limitations** The target-dependent binary does not contain as much information as higher-level intermediate representation. For instance, there is no explicit program structure inside a binary. Because of that, during interpretation dynamic optimizer has to rebuild, often limited, program view and identify functions, basic blocks and loops. Identification of variables can be more complicated and sometimes even impossible, as it requires tracking memory accesses and operations on registers.

**Mixed-mode execution in dynamic optimizer** In contrast to JIT, dynamic optimizers interpret a native instruction stream of a given machine. Thanks to that there is only one ABI, in particular the *endianess* and *calling conventions* used for interpretation and compiled code are the same. This drastically simplifies the interoperability between interpreted and directly executed native code as there is no need to convert parameters and global data.

**A few words on dynamic optimizers** Before starting optimizing the code, dynamic optimizers also have to perform some time consuming tasks:

- · disassembly,

- interpretation,

- instruction scheduling,

- reassembly.

The task of rebuilding the program structure, including identification of variables needed to optimize the code, is time consuming, difficult and sometimes even impossible. This limits both the time spent for optimizing the code and possible optimizations.

### 1.2 A third approach

The two approaches presented above (JIT and dynamic optimizers) have one goal in common: gain more performance. In many ways being similar to each other, by using interpretation, the same code cache management concepts and optimization techniques, they approach the problem from opposite directions: high-level and target-level program representation, resulting in different problems they have to struggle with.

A closer look on the two aforementioned dynamic environments leads us to a conclusion that both of them have, among others, one important need in common: information not explicitly provided with the input program representation. This need requires considerable effort to construct or retrieve that information, or even guess it from the execution context, and both of these environments spend the resources for this task at the expense of the time that could be used for their main purposes.

Interestingly, both of them rely on the static compilation phase, and the static compiler already has to construct the same information for its internal use, just to discard it before even emitting the IR or target binary.

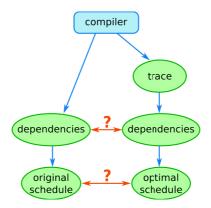

The problem of the need for reconstruction of information (i.e., program structure, loop information, data dependencies, Static Single Assignment form and others which we discuss later) that has been already created but discarded after its use (which at some point can lead to an irretrievable loss) is not limited only to the virtual execution environments. As we will show later in this work, it occurs also in complex static compilation toolchains, where the compilation process can be divided into several phases implemented in different tools, as well as for the purpose of static and dynamic program analysis that have to be performed in the context of the underlying machine, thus on a very-low level representation.

Following these observations, we raise and provide answers for the question whether it is useful to pass previously mentioned information through an intermediate representation as an input for a virtual execution environment which combines the advantages of JIT and dynamic optimizers and tries to avoid their problems. Finally, we ask whether additional information would be advantageous in complex toolchains and as a base for low-level program analysis frameworks.

#### 1.3 Contributions

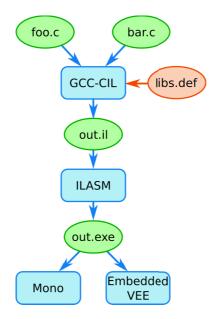

The CIL compilation toolchain Motivated by the opportunities given by the JIT compilation, that is gaining performance while keeping the redistributable form of the program target-independent, we have studied the possibilities of compilation of the C language into the Common Intermediate Language (CIL), followed by its JIT compilation and execution using the existing open-source tools. This led us to the investigation of the CIL backend in the Low Level Virtual Machine (LLVM) compilation framework and identification of the issues related to the execution of the generated CIL code on the open-source Mono platform. We have completed the backend and corrected the issues found in the backend as well as provided a working set of tools allowing to compile programs (with the focus on C language) and execute them correctly on the Mono platform, with the intention to use that code in our own Virtual Machine.

We have noticed, however, that the JIT compiler was spending time and resources on compilation phases that do not benefit much from information gained during execution of a program. Moreover, the target-independent intermediate representation (IR) was making the interoperability between interpretation of the CIL code and execution of native code complicated, especially when operating on a complex, non-basic data structures. Also, the fact that the frontend C language allows for direct memory access and pointer arithmetic, it is difficult and in can be impossible to guarantee the target-independence of the IR.

This execution model does not leave much time for the compiler to perform opti-

mizations and limits the possibilities only to optimizations that will not consume too much time and resources, otherwise they would slow down the execution instead of improving performance.

A universal IR The need for connecting several tools in a single compilation toolchain lead us to development of Tirex, a hybrid, linear SSA intermediate representation with instructions very close to the underlying processors, an explicit program description and additional information, including loop nesting forest and memory dependencies. Its purpose is also to provide a way for writing tests for optimizer passes, as well as a strong foundation of program analysis framework and virtual execution environments.

**Virtual Execution Environment** The experience with JIT and the study of dynamic optimization pushed us to explore a new path of dynamic code manipulation, placed between the two aforementioned. We have decided to give up the portability in favor of gaining more time for optimizations. We have come to a clear realization that Tirex can be perfectly suitable for this task.

As interpretation is a vital part of any virtual execution environment, which provides easy way of gathering program execution traces, in this thesis we present study on SSA interpretation of Tirex. Although interpreting SSA form is challenging, we are showing that it is feasible. Also, the interoperability between interpreted and native code (mixed-mode execution) proved to be much more simplified with Tirex in comparison with classical JIT approach.

We were able to generate native code from the Tirex IR dynamically, showing that this process is simplified with regard to classical JIT, and again confirming the ease of interoperability between interpreted and native code, leaving more time for optimizations.

#### 1.4 Outline of this thesis

In Chapter 1 we have presented a brief introduction to the world of dynamic compilation and optimization, as well as the problems related to it. Additionally, Chapter 1 summarizes the contributions of this thesis. Next, in Chapter 2 we introduce definitions and descriptions of basic concepts and terms used in this work. After that in Chapter 3 we discuss existing dynamic execution and optimization environments, as well as other concepts that made the foundations of our work. Chapter 4 shows issues related with C to CIL compilation and our contributions in this matter. After that in Chapter 5 we describe the framework used for the purpose of this thesis. In Chapter 6 we introduce and describe in details Tirex intermediate representation following by its virtual execution environment consisting of a interpreter SSA and JIT compiler, both

described in Chapter 7. Finally we conclude our work and discuss perspectives in Chapter 8.

# Chapter 2

# Background

In this chapter we define the terminology for the next chapters. First, we define the vocabulary related to the program itself and its structure from the compilers point of view and provide overview of intermediate representations. Then, we introduce the Static Single Assignment form. After that, we describe loop forests and their relation with data dependencies.

#### 2.1 Program and control-flow graph

A computer program is a sequence of instructions that executed would perform the task intended by a programmer. Or more formally, a **program** is a set of instructions connected by control-flow edges. An edge from instruction s to instruction s to instruction s to the order in which the instructions are executed, and can be represented by a graph, described in Section 2.1.2.

An **instruction** is a smallest, single operation that possibly uses some variables and possibly defines other variables. It can, but does not have to, take some input values, and also can return a result of some computation. Examples of some instructions are shown on the Figure 2.1.

| Instruction         | Definitions | Uses      |

|---------------------|-------------|-----------|

| add \$r0, \$r1, 123 | \$r0        | \$r1, 123 |

| goto BB4            | Ø           | BB4       |

| nop                 | Ø           | Ø         |

Figure 2.1: Instructions with the defined values and used parameters.

We also consider a group of instructions that will be executed in parallel, and call it

<sup>&</sup>lt;sup>1</sup>Or flow of control.

a **bundle**. Bundles are specific for VLIW processors that have the capability of executing multiple instructions in the same clock cycle, depending on the resources available (logical units). For instance, a load from memory and some arithmetic operations on registers can be performed simultaneously. Of course, the exact number of instructions in one bundle is constrained by architecture of the processor, availability of resources and mutual dependencies between the instructions. All the instructions in a bundle are encoded in a binary form together resulting in a *very long instruction word*, hence the name *VLIW*.

#### 2.1.1 Program structure

For the convenience of the programmer, and for the purpose of the compiler as well, a program can be divided into more units than simple instructions (or bundles of instructions). What we call a **structured model of programming** was initiated in 1960s by work of Bohm and Jacopini, and Edsger Dijkstra. As a contrast to an older, previously used model, where some condition test and goto instructions were used, this one introduced the use of procedures<sup>2</sup>, blocks of instructions, and loops. Although this model can slightly differ within different programming languages, internal low-level representation (independent from the used programming language) from the compiler point of view is structured in a similar fashion. This structure evolved during the years to have granularity suitable for different kind of optimizations.

In this thesis we will refer to this structure hierarchically: a **program** contains **procedures** build of **basic blocks** made of **instructions** (or **bundles**). Also, some basic blocks within a procedure can form a **loop** (we talk about loops in Section 2.4.2).

A **basic block** is a maximal sequence of instructions in a given program, in which flow of control enters at the beginning and leaves at the end without branch or call in the middle. In other words, a basic block is a portion of code that would be executed sequentially from its beginning (*entry point*) to the end (*exit point*). No entering or leaving path is allowed in the middle. Usually the last instruction in a basic block is a branch, call or return instruction, however it is not mandatory – in that case the control flow falls to the following basic block in the program.

Grouping the instructions that are executed sequentially without any control change in between allows for using blocks of instructions as optimization unit, e.g., in *basic-block reordering* which is used to reduce branch cost and the number of mispredicted branches.

A **procedure** is a way of abstraction and encapsulation of a part of a program that usually performs a specific task. In many environments it serves as a unit for separate compilation. At the same time it is also a unit of some optimizations that could not

<sup>&</sup>lt;sup>2</sup>Also called functions, or subroutines.

be performed more locally (i.e., cannot be done on a single basic block). In more formal way, a **procedure** is a portion of code build from one or more basic blocks, that possibly takes some *arguments* and possibly returns a *result*.

#### 2.1.2 Control-flow graph and its dominator tree

A procedure can be represented by the **control-flow graph** (CFG), a directed graph G = (N, E, r, t), with set of nodes N, set of edges E, the **entry** node r with no incoming edge, and the **exit** node t with no outgoing edge.

The CFG models the flow of control in that procedure and provides a graphical representation of all possible run-time paths. Usually the nodes represent basic blocks. In static analysis, the CFG is a basic tool used in several phases of compilation, including instruction scheduling and register allocation.

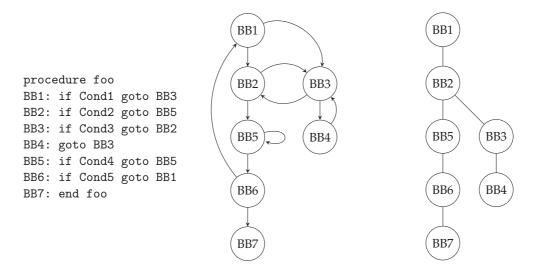

Figure 2.2: Example procedure, its control-flow graph and a dominator tree.

Figure 2.2 shows an example procedure, its CFG and a *dominator tree* (defined below) for that CFG. The basic block BB1 is the entry node, and BB7 – the exit node.

**Dominance property and the dominator tree** A node a in a CFG **dominates** a node b, denoted a dom b, if every path from the entry node r to b contains a. If a dom b and  $a \neq b$  then a **strictly dominates** b, or a sdom b. The node a is an **immediate dominator** of the node b, a idom b, if a sdom b and there is no node c such that a sdom c and c sdom b.

A **dominator tree** rooted at *r* is a directed graph whose nodes are the nodes of the given CFG and where each node other than *r* is pointed to by its immediate dominator.

#### 2.2 Intermediate representation

Intermediate representation (IR), is a language of an abstract machine used to represent a program independently from a programming language used to write that program and often independently from the target processor. Modern compilers usually convert the original program into such IR, and perform analysis and optimizations on it. In some compiler implementations there could be more than one IR involved, however in such cases one of the representations is the main IR.

From the view of structural organization IRs can fall into three categories: graphical, linear, and hybrid.

**Graphical IRs** represent the code as **trees** or **graphs** and consist of **nodes** and **edges**. Trees are a natural representation for the grammatical structure of the source code. Graphs, however, are more useful for representing other properties of a program, such as the control flow.

The graphical IRs are usually not the only IR in the compilation process. The data dependence graphs are generally used for a specific task, created just before the use, and destroyed afterwards. The control-flow graph (CFG) also comes with another IR for representing the operations inside basic blocks.

**Linear IRs** share a resemblance to assembly code in the sense that they both are a simple sequence of instructions, executed in order of their appearance. In that form, in contrast to graphical IRs, there is a need to encode transfer of control, hence generally each basic block ends with a branch, call or return instruction.

The two, most common linear IRs are **bytecode** and **three-address code**. Bytecode is also called stack-machine code or one-address code, as each instruction has at most one parameter (one address) which is placed on the evaluation stack before its execution. The result of the instruction is also placed on the stack, thus it has to be explicitly stored in memory if required. The bytecode is used in applications where size is essential, as it is very compact. Three-address code resembles more the code of modern processors, were most of the instructions get two operands and produce one result (thus making it *three*-address). Of course, some of the instructions will need fewer arguments and in some cases more than three.

**Hybrid IRs** try to combine properties of both aforementioned. A common practice is keeping linear code within basic blocks, and use graphs to represent the flow of control between these blocks. An example of commonly used hybrid IR is a linear IR in the Static Single Assignment form, which we describe in the following section.

## 2.3 Static Single Assignment form

The **Static Single Assignment** form is a naming convention for variables, which was the result of work on data-flow analysis, in particular on the identification and elimination of redundant computations published by Alpern et al. [1988]; Rosen et al. [1988].

Later, the foundations of SSA were presented in more details in a journal paper by Cytron et al. [1991].

A program is in SSA form if each variable is defined exactly once in the program text. In other words, a variable can occur on the left hand side of an assignment expression only once in a given program, hence there is one unique **static** definition. It is possible, however, to get multiple **dynamic** definitions – for example, as a result of the definition inside a loop. Usually, in SSA all definitions should occur before its use, i.e. it is considered with **dominance property**.

We have already defined the dominance property while talking about the CFG in Section 2.1.2. SSA is said to be **with dominance property** if, for every variable a, def(a) dom use(a), where def(a) is the instruction that defines a and use(a) is a set of the instructions that use a.

Since some variables have multiple definitions, to convert a program to SSA unique names have to be given to each definition of the same variable. However, simple renaming is not enough. At points where different control-flow paths merge (e.g., after an if else condition), the correct value has to be chosen depending on the path. For that purpose so-called virtual  $\phi$ -functions were introduced.

A  $\phi$ -function is a virtual operation placed at the beginning of a basic block, which takes as many arguments as the number of this block's incoming flow edges, and returns the  $n^{th}$  argument, when the execution path comes from the  $n^{th}$  incoming flow edge.

```

\begin{array}{lll} \text{if(b)} & & \text{if(b)} \\ & a = 2; & & \text{else} \\ & \text{else} & & a_2 = 3; \\ & c = a + 1; & & c = a_3 + 1; \end{array}

```

Figure 2.3: Example of C code and its representation in SSA.

The  $\phi$ -functions need a particular treatment for multiple reasons. First, they act as multiplexers that choose a value depending on which control-flow path the program comes from, hence their behavior depends on past execution.

For instance, as shown on Figure 2.3 suppose a conditional branch in the original program with assignment a=2 in the *true* branch and a=3 in the *false* one. Since SSA allows only one static assignment, this would be transformed into  $a_1=2$  and  $a_2=3$  in the branches, and the  $\phi$ -function  $a_3=\phi(a_1, a_2)$  at the join, meaning that  $a_3$  takes the value of  $a_1$  if the path comes from the *true* branch, and  $a_2$  if it comes from the *false* branch.

Moreover, multiple  $\phi$ -procedures at the beginning of a block need to be executed concurrently as their semantics is that the selection of values is done in parallel. Failure to do so may produce wrong results, the classical example (see Figure 2.4) being the

```

a = \phi(b, ...);

b = \phi(a, ...);

```

Figure 2.4: Swapping of two variables in SSA form using  $\phi$ -procedures.

"swap problem" was identified by Briggs et al. [1998] where  $\phi$ -procedures are used to swap values in variables. Executing them sequentially would result in the overwriting of variable a before its use in the second  $\phi$ .

### 2.4 On data, data dependence and loop nesting forest

A complete program, besides the instruction stream, has to contain **data** used for the computations. While talking about the **data stream** in our intermediate representation, we will use the term **object**. Data objects correspond to definition of **variables** and **constants** referenced in a program. They describe how much storage has to be assigned for the variables and constants, and how should they be placed in memory in order to correctly perform operations on them. Some of the variables and all constants have to be set to some initial values before program execution. We will refer to that value as **initializer**.

In more general view data is an **input** (**operand**) of some program statements<sup>3</sup>, and can be its **product** (result of computation). The compiler, in order to perform some optimizations has to keep track of data dependencies between the program statements. Otherwise it could for example move a definition of a variable after it use, resulting in a faulty computation. To perform so-called *aggressive optimizations*, the compiler needs memory dependencies annotated by the type of relation and discriminated by loop level.

#### 2.4.1 Data dependence definition and types

A statement  $S_w$  **depends** on statement  $S_v$  if and only if both of these statements access the same memory location and at least one of them stores into that memory location, and there exists a path of execution from  $S_v$  to  $S_w$ .

There are three types of dependencies (see Figure 2.5 for examples):

**Flow dependence** Statement  $S_w$  is data flow-dependent on  $S_v$  (denoted as  $S_v \delta S_w$ ), if a value computed in statement  $S_v$  is used in statement  $S_w$ .

**Anti dependence** Statement  $S_w$  is data anti-dependent on  $S_v$  if a variable is used in statement  $S_v$  before it is reassigned in statement  $S_w$  ( $S_v \bar{\delta} S_w$ ).

<sup>&</sup>lt;sup>3</sup>Or instructions in case of low-level program representation

**Output dependence** Statement  $S_w$  is data output-dependent on  $S_v$  when a variable is assigned in statement  $S_v$  and later reassigned in statement  $S_w$  ( $S_v\delta^{\circ}S_w$ ).

$$S_v: x=5$$

$S_v: y=x$   $S_w: x=2$  (a) Flow dependence  $S_v: x=5$   $S_w: x=2$  (c) Output dependence

Figure 2.5: Example of data dependencies between statements.

#### 2.4.1.1 Data dependence graph

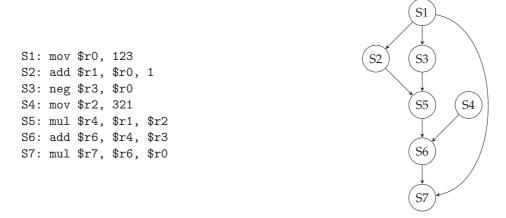

The data dependence graph is a directed graph G = (N, E), where each node  $n \in N$  corresponds to one of s program statements  $S_x(1 \le x \le s)$ , and each edge  $e = (S_v, S_w) \in E$ , is a dependence relation between statements  $S_v$  and  $S_w$ .

Figure 2.6: Example of data dependence graph.

Figure 2.6 shows a simple program in a three-address form and its data dependence graph. Statements *S*1 and *S*4 have no incoming dependency, while the other statements are flow-dependent on other statements in the program.

#### 2.4.2 On loops and loop nesting forests

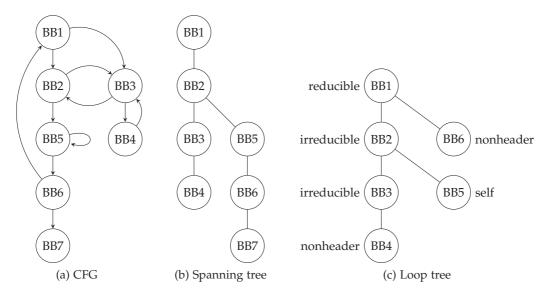

When discriminating dependencies by loop nesting level, all the producers and consumers of the intermediate representation have to agree on what loop they are talking about. A loop nesting forest is a data structure representing loops and relations

between them in a control-flow graph. There are several definitions (with different properties) of what a loop nesting forest is, e.g., Sreedhar et al. [1996]; Steensgaard [1993]; Havlak [1997].

Ramalingam [2002] proposed the axiomatic definition of loop nesting forests. In his definition, the header of a loop can be any node not dominated by other in the SCC (strongly connected collection) that defines the loop body. So in case of irreducible loops, there is an ambiguity.

In his PhD thesis, Boissinot [2010] defines the notion of a minimal connected loop nesting forest, which has applications to find live sets and perform liveness checks under the SSA form. A minimal loop nesting forest is a loop nesting forest such that no loop body from the forest is covered by another loop, and it is connected if the loop headers are selected from the set of entry nodes of the loop. In practice, loop forests proposed by Havlak [1997] are the best choice of minimal connected loop nesting forests.

**Havlak's loops** A *loop* is a sequence of statements that can be executed repeatedly. A loop consists of a *header* basic block and loop body that contains one or more basic blocks. The body of a loop can be executed a specified number of times, until some condition is satisfied, or indefinitely.

For a compiler, a loop is one of the most important scopes for some optimizations, as this is usually where the most time is spent during execution. These optimizations aim to improve cache performance and speed of loop execution, making use of parallel execution of some statements in the loop.

In this work we use definitions as provided by Havlak [1997], because only one basic block can be the header, hence there is no ambiguity as in Ramalingam's axiomatic definition and others. A more formal definition of loops comes from the notion of a *strongly connected component*.

In a given graph G(N, E), a **strongly connected component** (SCC) is a nonempty set of nodes  $S \subset N$  such that for any nodes  $a, b \in S$ , there exists a path from a to b and a path from b to a. A *maximal strongly connected component* is a SCC to which no more node can be added.

A **loop** in a graph G(N, E) is a pair (B, H) of non-empty sets of nodes  $B \subset N$  and  $H \subset N$ , such that  $H \subseteq B$ , where B is a strongly connected component, the body of the loop, and H is the set of headers of the loop. An **outermost loop** is a maximal SCC with at least one internal edge.

When traversing a graph with the classical depth-first search algorithm, a spanning tree is created as a by-product, which is then used for numbering the visited nodes. A header node of the loop is the first visited node of the SCC. A loop **nested** inside a loop L with header h is an outermost loop in the subgraph with node set (L-h).

This definition allows us to represent the loop nesting with a tree, where for each node its parent is a header of the smallest loop containing that node. A loop with

2.5. *SUMMARY* 21

Figure 2.7: An example of a loop tree for given CFG and its spanning tree.

a single entry is a **reducible loop**, while loop with multiple entries – an **irreducible loop**.

We give an example of a loop tree on Figure 2.7 with a corresponding CFG and a spanning tree. Havlak gives additional labels to the nodes in a loop tree. Nodes with descendants are headers and are marked **reducible** or **irreducible**. Nodes that do not have any descendant are marked either as *nonheader* or **self**, where **self** is a special case of a reducible loop with a single node, hence the header in itself is the loop.

### 2.5 Summary

In this chapter, we defined the main notions used in this thesis. We provided the notions about program structure and data stream, defined the control-flow graphs and discussed the intermediate representations. We introduced the SSA form, which is supported by our intermediate representation and used by the framework, both of which are presented in the following chapters. Finally, we provided background information on data dependencies and loop nesting forests, also supported by the proposed IR, to be used in the future by our framework.

# Chapter 3

# **Prior Work**

The main motivation of this thesis is to fill the gap between the execution environments that employ the classical *Just-In-Time* execution model with the *Dynamic optimizers*, and combine the advantages of both of them. These virtual execution environments seem to be the two major approaches in the wide family of dynamic code modification systems. The work done in this thesis rely however also on other technologies, that we describe in this chapter.

#### 3.1 Interpretation of the SSA form

Interpretation, although providing much less performance than execution of native code, is nonetheless very important tool in a virtual execution environment, as it allows for fast start-up of execution without the overhead of a compiler. It is also a cheap and easy implementation base for gathering traces and other useful information about the program execution. The interpretation techniques themselves being not new are well known, however not many interpreters of SSA form exist.

One of the interpreter operating on the SSA form could be found as a part of the Low Level Virtual Machine (described in more details in Chapter 5). It is written in C++ and designed for executing LLVM's bitcode, a target-independent intermediate representation which is in the SSA form by design. However, no work on measuring its performance or describing its implementation could be found. The authors state themselves in the source code, that it was designed "to be very simple, portable and inefficient."

Another work on interpretation of the SSA form was done by von Ronne et al. [2004]. Von Ronne proposes an "Interpretable SSA intermediate representation", which introduces some extensions to a classical SSA flavor in order to enable direct imperative interpretation of SSA. These extensions include a dedicated virtual register containing the edge number used by  $\phi$ -functions and a special instruction marking explicitly the end of  $\phi$ -functions in a basic block.

Although Von Ronne mentions that recursive calls would require storing the variables, probably on the stack, the discussion ends on that point.

#### 3.2 Compilation Just-In-Time

#### 3.2.1 The beginning

The idea of the classical JIT compilation can be traced to Rau [1978] who was considering a *universal host machine* (UHM). Rau classified program representations into three groups (see Section 2.2) according to their level of abstraction and usability for the execution on a virtual machine. The UHM was targeting multiple source languages, called by Rau *high-level representations* (or HRLs). He postulated the introduction of an intermediate representation (DIR) that the different HLRs would be statically compiled to. This DIR was suitable for interpretation and dynamic translation to the host machine code (DER).

Rau in his work also discussed the different design criteria of DIRs, such us code compaction versus semantic level of instructions and their impact on the UHM. He proposed also the use of dynamic translation instead of interpretation, as well as the organization of *dynamic translation buffer* (what would be called now a *code cache*) and its similarities to processors' cache memory.

The work of Rau inspired Deutsch and Schiffman [1984] for improving the Smalltalk [Goldberg and Robson, 1983] system. Smalltalk is a purely object-oriented language used in an interactive, exploratory programming model. Its source code is compiled statically to a bytecode representation. This bytecode was originally executed in a virtual machine by a stack-oriented interpreter. Deutsh and Schiffman in their implementation of Smalltalk as one of the optimizations used dynamic translation of the bytecode to native code. The procedures were compiled in a lazy scheme, i.e. just before the call, and the native version was cached for later use.

Smalltalk influenced another purely object-oriented system that uses dynamic translation techniques, Self Ungar and Smith [1987]. Rather than interpreter, Self used a fast, non-optimizing compiler for lazy compilation of procedures. Hölzle and Ungar [1994] credited this idea to work of Deutsch and Schiffman in Smalltalk. Three generations of Self's implementation provided lots of important observations used later in other systems.

Hölzle proposed the use of second, optimizing compiler and its application to *hot spots*. When a method was executed often, it was recompiled with that optimizing compiler. It was also Hölzle who noticed, that it is more important for the performance to carefully choose *what* to compile rather than *when* to compile, i.e., that instead of compiling a method whose counter triggered the compilation it could be better to compile its caller and inline the frequently called method.

#### 3.2.2 Java

One of the best known environments using dynamic translation is Java [Gosling et al., 1996] released by Sun Microsystems in 1995. It was designed as an alternative to C++, that would provide facilities for security, threading, distributed programming, as well as automatic memory management, and above all – target architecture independence that would allow programmers to write and compile their software only once but deploy on any environment where a Java Virtual Machine is available. As a result of lot of invested time and money, nowadays it could be found everywhere from desktop computers to embedded devices, even in mobile phones; in fact it is Java that brought the term *just-in-time* (or simply JIT) into use in computing.

Java, as other JIT environments, separates the compilation process into two phases. First the source code is compiled statically into a bytecode representation, next the bytecode is executed on the Java Virtual Machine (JVM). This bytecode was designed for a stack-based (virtual) machine and in the first releases was simply interpreted which resulted in very poor performance.

This problem was addressed by Cramer et al. [1997] with, once more, use of the techniques proposed by Rau and pioneered by Deutsch and Shiffman: dynamic translation of bytecode to native code. The compiler used for runtime code generation has to be much faster than static compiler. Cramer and his colleagues stated, that even though the bytecode, as being designed for stack-based interpretation, is not perfect for JITing, there is no time and resources for constructing different intermediate representation as in static compilers. They advocated the use of bytecode as the intermediate representation of the JIT compiler. Although the compiler was very simple, the results showed increase of performance, depending on benchmark, from 2 to 9 times versus the interpreted code.

Cramer also noticed, that although there obviously is lot of place for improvement in the JIT compiler, the performance of whole virtual execution environment depends not only on the native code generation and optimizations. According to him, the interpretation process took in average only 68% of execution time, while the rest was spent by the virtual machine on synchronization and garbage collection, and surprisingly only 1% on calling native code.

The following years, in particular with the work of Cierniak and Li [1997]; Adl-Tabatabai et al. [1998]; Burke et al. [1999]; Suganuma et al. [2000] and others, resulted in new ideas in Sun's JIT compiler as well as in different research JIT compilers for Java that improved the performance significantly. Important conclusion of this work is that simply generating native code instead of interpreting is not enough, bringing focus on optimization techniques suitable for JIT compilation.

Interesting implementation of Java Virtual Machine is Java HotSpot [Oracle, 2010]. It addressed also other issues related to execution of Java bytecode, i.e., synchronization and garbage collection, however we will focus only on the JIT compilation.

From the very beginning [Microsystems, 2001], instead of the lazy compilation model, i.e., compiling one method on demand, the execution started in the interpretation mode. The interpretation process was used not only to avoid the compilation overhead, but also to detect the frequently executed parts of the program (i.e., hot spots). Java HotSpot provides two JIT compilers: client and server. The client compiler is tuned to be used with a typical client applications that require fast response and does not perform any optimization except minimal inlining. The server compiler is tuned to optimize long-running server application. It perform all classical optimizations, such as dead code elimination, loop invariant hoisting, common subexpression elimination and constant propagation.

The stack-based IR considered previously by Cramer as suitable for the JIT process have been replaced for compiler's internal purpose by a register-based IRs, and the server compiler started to exploit the properties of the SSA form. Later versions of the client compiler use two intermediate representations, one of which is SSA-based, and the server compiler has been improved versus the older one to gain more performance and has been equipped with Java-specific optimizations, such us null-check and range-check elimination and exception throwing optimizations.

#### 3.2.3 Common Language Infrastructure

In early 2000 Microsoft introduced his .Net Framework, which was later partially published under the name of Common Language Infrastructure (CLI) as ECMA International [2006] standard. Its goal was to unify other Microsoft technologies under one API, thus allowing the programmers to develop and debug GUI, console, web and other applications in the same fashion. CLI in many ways is similar to Java, however it was designed later, thus its creators could make use of lessons learned by the creators of Java. In contrast to Java, which was designed to support only the Java language, CLI's philosophy is to provide support for multiple frontend languages and the interoperability between the code written in these languages, hence giving the possibility to choose the best suitable language to perform a given task.

Programs written in high-level frontend languages are compiled to stack-based bytecodes called Common Intermediate Language (CIL) previously known as Microsoft Intermediate Language, which is part of the Ecma standard and was described in details by Lidin [2006]. CIL is independent of the frontend language and from the underlying hardware, and although is suitable for interpretation, the .NET framework does not use an interpreter, but directly calls a JIT compiler [Gough, 2001] whenever a function is called for the very first time.

The .NET framework relies on two JIT compilers [Microsoft, 2006]: Standard-JIT and Econo-JIT. The latter is a fast, non-optimizing compiler, while the former produces better code.

A shared source, research implementation of CLI, named Shared Source CLI (SSCL

or Rotor) was also released by Microsoft. It was equipped with a one, very simple JIT compiler that did not perform any optimization, nor register allocation. It was designed to generate native code very fast in one pass and simulate the stack in a dedicated register. Vaswani and Srikant [2003] proposed a profile guided JIT compiler for Rotor with two level optimizations. Again, as it happened in Java, this JIT compiler internally was operating on a register-based intermediate representation.

The Mono project<sup>1</sup> provides an open-source implementation of the Common Language Infrastructure. Mono has its own JIT compiler. For its internal purpose starting from version 2.0 it converts the CIL bytecodes into a register-based linear intermediate representation [Mono, 2012]. It performs all the usual optimizations, such as copy and constant propagation, branch optimizations, dead code elimination. It performs the SSA optimizations as well, however the internal linear IR is not in SSA, thus requires its construction and destruction.

#### 3.2.4 Staged dynamic compilation

Other methods are used in staged dynamic compilation [Auslander et al., 1996; Consel and Noël, 1996; Grant et al., 1999]. The compilation process of a program is also divided into two parts: static and dynamic. The static compiler chooses only portions of code, typically previously annotated by user and generates templates, which are used at runtime by a dynamic compiler to specialize these parts of code without introduction of any intermediate representations.

Leone and Dybvig [1997] proposed even to statically compile the regions of code into three forms for different kind of optimizations: high-level IR for heavyweight optimizations, mid- or low-level IR for simple optimizations, and native code for regions that cannot benefit from dynamic optimizations.

# 3.3 Static Binary optimizers

Srivastava and Wall [1992] developed OM for link-time optimizations. OM takes object files and converts them into RTL language. This representation is optimized profiting from inter-modular optimizations not possible during compilation of each unit, and converted back to object form.

Spike [Cohn et al., 1997] is a profile-driven Alpha binaries optimizer for Windows NT. It automatically instruments binaries and collect profile data during execution. The collected data is used for static optimizations of the entire images of programs, including dynamic libraries.

<sup>&</sup>lt;sup>1</sup>http://www.mono-project.com/

## 3.4 Dynamic Optimizers and Binary Translators

We classify the dynamic optimizers and binary translators together, as they are similar in the way they operate on existing, target-dependent binaries rather than dedicated intermediate representations. Usually they observe the execution by interpreting the instruction stream, gather hot traces of instructions, and generate (optimized) native code.

One of such systems is Dynamo introduced by Bala et al. [2000]. It is designed for to transparently improve performance of statically generated binaries for PA-RISC processor. While interpreting the program, it gathers the hot-traces and generates optimized code for them. In case of performing worse than original binary it has a bailout mechanism to fallback to the original program. Dynamo converts the traces into a low-level IR, very close to underlying architecture and performs simple branch optimizations, redundancy removal, constant and copy propagation, strength reduction, loop invariant code motion and loop unrolling. Bala reported performance gain up to 22% in some cases, and an averages speedup of 9%.

Bruening et al. [2003] proposed a direct descendant of Dynamo called DynamoRIO, which provides a dynamic binary inspection and modification framework with an API exposed to higher-level applications, allowing to construct tools that can perform several different tasks. Its goal is not only to dynamically optimize existing programs, but rather to provide a framework for implementing such dynamic optimizations and analyses. It also uses interpretation for gathering traces, however to avoid overhead it caches translations of frequently executed code for direct execution.

Chen et al. [2000] worked on Mojo, a dynamic optimization system targeting Windows running on IA-32 architecture. Its goal is to run not only research benchmarks but also real-world, large applications with multithread support. As it is designed for a CISC processor, the authors, instead of using the interpreter as in Dynamo or DynamoRIO, proposed direct execution of native basic-blocks identified through disassembling and placed in a *basic-block cache*. Control instructions in such basic-blocks are patched to go back to a dispatcher. After identifying a hot-path, corresponding basic-blocks are optimized and placed in the *path cache*. The optimizations focus on code layout and branches, as well as loop unrolling. Mojo was also equipped with bailout mechanism in case of performing worse than native version of a given program.

DELI is a binary translation framework developed by Desoli et al. [2002], meant for near-native performance emulation with an API exposed to clients. It allows to build code manipulation, observation and emulation tools by providing some basic functionalities, such as code caches and fragment linking mechanisms. However, interpreter or JIT compiler of one ISA to native has to be provided by the client tools.

Strata [Scott and Davidson, 2001] is yet another framework for developing dynamic translation clients. Its goal is to provide a retargetable platform that has some common

services, such as memory management, code cache and dynamic linking. The authors show a use case for inspecting applications during execution and protect the system from malicious behaviors, as well as an dynamic instruction scheduler.

# 3.5 Binary instrumentation

## 3.5.1 Static binary instrumentation

A framework for writing program analysis tools for the Alpha platform, through a high-level API was implemented in ATOM [Srivastava and Eustace, 1994]. It is based on the OM project and contains instrumenting services and requires the user to specify only the tool detail. It inserts function calls to analysis framework at the user-specified points. User's tool compiled with the ATOM services results in the profiling tool which is further combined with the application resulting in a self-profiling and analyzing executable. Atom, however does not allow for modifying existing instructions, but only allows to call instrumentation functions.

EEL is a very similar toolkit to ATOM. Although released for SPARC, was designed with a platform-independent interface for "exutable editing" that would require only minimal knowledge about the target platform.

Another instrumentation toolkit, PEBIL Laurenzano et al. [2010], was influenced by a dynamic toolkit DynInst (described later), but instruments program statically by replacing some instructions with calls to instrumentation routines at specified points. To acquire enough space for this reason in case of variable-length instructions, it performs function relocation. Also, it supports insertion of *instrumentation snippets* – hand written assembly code, to avoid instrumentation functions.

#### 3.5.2 Dynamic binary instrumentation

DynInst [Buck and Hollingsworth, 2000] is a C++ class library that provides an API for dynamic program instrumentation and modification. The API also allows for changing function calls and removing them from the application. It uses machine independent representation to describe the instrumentations that allows to use the same instrumentation code across different platforms. The inserted code is translated to machine language and emitted into array in the application address space. Than, in order to call this code, one or more instructions in the point of instrumentation is replaced with a branch to a *trampoline*. Next another, *mini-trampoline* is called that saves the machine state (registers and condition codes), executes a *snippet* of the instrumentation code, restores the machine state and branches back to the main trampoline. Here another *snippets* can be called. When the process is finished, the replaced original instructions are executed, and the trampoline branches back to the point of insertion.

Another library that provides API for building dynamic instrumentation tools is implemented in Pin [Luk et al., 2005]. Similar to DynInst it provides the possibility to

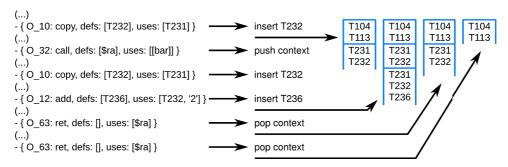

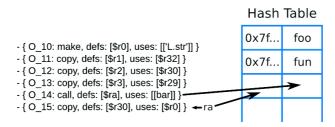

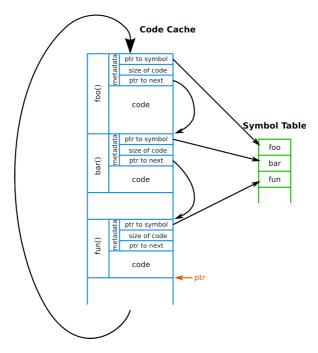

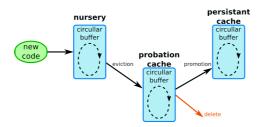

write target-independent instrumentations. However, instead of trampolines, it uses dynamic compilation techniques to instrument executables while they are running. It has capabilities to optimize the instrumentations and uses code caching and trace linking.