# Design and test of digitally-controlled power management IPs in advanced CMOS technologies

Bo Li

#### ▶ To cite this version:

Bo Li. Design and test of digitally-controlled power management IPs in advanced CMOS technologies. Other. INSA de Lyon, 2012. English. NNT: 2012ISAL0036. tel-00782429

### HAL Id: tel-00782429 https://theses.hal.science/tel-00782429

Submitted on 29 Jan 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Numéro d'ordre : 2012-ISAL-0036 Année 2012

### **THÈSE**

présentée devant

#### L'Institut National des Sciences Appliquées de Lyon

pour obtenir

#### LE GRADE DE DOCTEUR

ÉCOLE DOCTORALE : ÉLECTRONIQUE, ÉLECTROTECHNIQUE, AUTOMATIQUE SPÉCIALITÉ : GÉNIE ÉLECTRIQUE

par

#### LI Bo

### Conception et test de cellules de gestion d'énergie à commande numérique en technologies CMOS avancées

Design and Test of Digitally-Controlled Power Management IPs in Advanced CMOS Technologies

Soutenue le 7 Mai 2012 devant la Commission d'examen

Jury:

**ALLARD Bruno** Directeur de Thèse Professeur-INSA de Lyon **CIRSTEA Marcian** Professeur-Anglia Ruskin University Rapporteur **HEBRARD Luc** Professeur-Université Louis Pasteur Président LI Zheying Professeur-Beijing Union University Examinateur **LIN-SHI Xuefang** Professeur-INSA de Lyon Directeur de Thèse **MONMASSON Eric** Professeur-Université de Cergy-Pontoise Rapporteur **TROCHUT Séverin** Ingénieur-ST-Microelectronics Examinateur

#### INSA Direction de la Recherche - Ecoles Doctorales - Quinquennal 2011-2015

| SIGLE     | ECOLE DOCTORALE                                                                                                                        | NOM ET COORDONNEES DU RESPONSABLE                                                                                                                                                                        |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СНІМІЕ    | CHIMIE DE LYON http://www.edchimie-lyon.fr  Insa: R. GOURDON                                                                           | M. Jean Marc LANCELIN Université de Lyon – Collège Doctoral Bât ESCPE 43 bd du 11 novembre 1918 69622 VILLEURBANNE Cedex Tél: 04.72.43 13 95 directeur@edchimie-lyon.fr                                  |

| E.E.A.    | ELECTRONIOUE,<br>ELECTROTECHNIQUE, AUTOMATIQUE<br>http://edeea.ec-lyon.fr<br>Secrétariat : M.C. HAVGOUDOUKIAN<br>eea@ec-lyon.fr        | M. Gérard SCORLETTI Ecole Centrale de Lyon 36 avenue Guy de Collongue 69134 ECULLY Tél: 04.72.18 60 97 Fax: 04 78 43 37 17 Gerard.scorletti@ec-lyon.fr                                                   |

| E2M2      | EVOLUTION, ECOSYSTEME, MICROBIOLOGIE, MODELISATION http://e2m2.universite-lyon.fr                                                      | Mme Gudrun BORNETTE CNRS UMR 5023 LEHNA Université Claude Bernard Lyon 1 Bât Forel 43 bd du 11 novembre 1918 69622 VILLEURBANNE Cédex Tél: 04.72.43.12.94 e2m2@biomserv.univ-lyon1.fr                    |

| EDISS     | INTERDISCIPLINAIRE SCIENCES-<br>SANTE<br>http://ww2.ibcp.fr/ediss<br>Sec : Safia AIT CHALAL<br>Insa : M. LAGARDE                       | M. Didier REVEL Hôpital Louis Pradel Bâtiment Central 28 Avenue Doyen Lépine 69677 BRON Tél: 04.72.68 49 09 Fax :04 72 35 49 16 Didier.revel@creatis.uni-lyon1.fr                                        |

| INFOMATHS | INFORMATIQUE ET MATHEMATIQUES http://infomaths.univ-lyon1.fr                                                                           | M. Johannes KELLENDONK Université Claude Bernard Lyon 1 INFOMATHS Bâtiment Braconnier 43 bd du 11 novembre 1918 69622 VILLEURBANNE Cedex Tél: 04.72. 44.82.94 Fax 04 72 43 16 87 infomaths@univ-lyon1.fr |

| Matériaux | MATERIAUX DE LYON  Secrétariat : M. LABOUNE PM : 71.70 -Fax : 87.12 Bat. Saint Exupéry Ed.materiaux@insa-lyon.fr                       | M. Jean-Yves BUFFIERE INSA de Lyon MATEIS Bâtiment Saint Exupéry 7 avenue Jean Capelle 69621 VILLEURBANNE Cédex Tél: 04.72.43 83 18 Fax 04 72 43 85 28 Jean-yves.buffiere@insa-lyon.fr                   |

| MEGA      | MECANIOUE, ENERGETIQUE, GENIE CIVIL. ACOUSTIQUE  Secrétariat : M. LABOUNE PM : 71.70 -Fax : 87.12 Bat. Saint Exupéry mega@insa-lyon.fr | M. Philippe BOISSE INSA de Lyon Laboratoire LAMCOS Bâtiment Jacquard 25 bis avenue Jean Capelle 69621 VILLEURBANNE Cedex Tél:04.72.43.71.70 Fax: 04 72 43 72 37 Philippe.boisse@insa-lyon.fr             |

| ScSo      | ScSo*  M. OBADIA Lionel  Sec : Viviane POLSINELLI Insa : J.Y. TOUSSAINT                                                                | M. OBADIA Lionel<br>Université Lyon 2<br>86 rue Pasteur<br>69365 LYON Cedex 07<br>Tél: 04.78.69.72.76 Fax: 04.37.28.04.48<br>Lionel.Obadia@univ-lyon2.fr                                                 |

<sup>\*</sup>ScSo : Histoire, Geographie, Aménagement, Urbanisme, Archéologie, Science politique, Sociologie, Anthropologie

### **Abstract**

Owing to the development of modern semiconductor technology, it is possible to implement a digital controller for low-power high switching frequency DC-DC power converter in FPGA and ASIC. This thesis is intended to propose digital controllers with high performance, low power consumption and simple implementation architecture.

Besides existing digital control-laws, such as PID, RST, tri-mode and sliding-mode (SM), a novel digital control-law, direct control with dual-state-variable prediction (DDP control), for the buck converter is proposed based on the principle of predictive control. Compared to traditional current-mode predictive control, the predictions of the inductor current and the output voltage are performed at the same time by adding a control variable to the DPWM signal. DDP control exhibits very high dynamic transient performances under both load variations and reference changes. Experimental results in FPGA verify the performances at switching frequency up to 4MHz. Considering the implementation complexity and performances, DDP control is therefore a better candidate compared to PID, RST and SM controls.

For the boost converter exhibiting more serious nonlinearity, linear PID and nonlinear SM controllers are designed and implemented in FPGA to verify the performances.

A digital control requires a DPWM.  $\Sigma$ - $\Delta$  DPWM is therefore a good candidate regarding the implementation complexity and performances. An idle-tone free condition for  $\Sigma$ - $\Delta$  DPWM is considered to reduce the inherent tone-noise under DC-excitation compared to the classic approach. A guideline for  $\Sigma$ - $\Delta$  DPWM helps to satisfy proposed condition. In addition, an 1-1 MASH  $\Sigma$ - $\Delta$  DPWM with a feasible dither generation module is proposed to further restrain the idle-tone effect without deteriorating the closed-loop stability as well as to preserve a reasonable cost in hardware resources. The FPGA-based experimental results verify the performances of proposed DPWM in steady-state and transient-state.

Two ASICs in  $0.35\mu m$  CMOS process are implemented including the tri-mode controller for buck converter and the PID and SM controllers for the buck and boost converters respectively.

vi Abstract

The lab-scale tests are designed to lead to a power assessment model suggesting feasible applications. For the tri-mode controller, the measured power consumption is only 24.56mW/MHz when the time ratio of stand-by operation mode is 0.7. As specific power optimization strategies in RTL and system-level are applied to the latter chip, the measured power consumptions of the SM controllers for buck converter and boost converter are 4.46mW/MHz and 4.79mW/MHz respectively. The power consumption is foreseen as less than 1mW/MHz when the process scales down to nanometer technologies based on the power-scaling model. Compared to the state-of-theart analog counterpart, the prototype ICs are proven to achieve comparable or even higher power efficiency for low-to-medium power applications with the benefit of better accuracy and better flexibility.

### Résumé

Les technologies avancées de semi-conducteur permettent de mettre en œuvre un contrôleur numérique dédié aux convertisseurs à découpage, de faible puissance et de fréquence de découpage élevée sur FPGA et ASIC. Cette thèse vise à proposer des contrôleurs numériques des performances élevées, de faible consommation énergétique et qui peuvent être implémentés facilement.

En plus des contrôleurs numériques existants comme PID, RST, tri-mode et par mode de glissement, un nouveau contrôleur numérique (DDP) pour le convertisseur abaisseur de tension est proposé sur le principe de la commande prédictive: il introduit une nouvelle variable de contrôle qui est la position de la largeur d'impulsion permettant de contrôler de façon simultanée le courant dans l'inductance et la tension de sortie. La solution permet une dynamique très rapide en transitoire, aussi bien pour la variation de la charge que pour les changements de tension de référence. Les résultats expérimentaux sur FPGA vérifient les performances de ce contrôleur jusqu'à la fréquence de découpage de 4MHz. Les comparaisons avec les commandes PID, RST et par mode de glissement montrent que le contrôleur DDP présente un meilleur compromis entre la complexité algorithmique et les performances.

Pour le convertisseur élévateur de tension où la présence de non linéarité est importante, un contrôleur PID linéaire et un contrôleur par mode de glissement non linéaire sont conçus et mis en œuvre sur FPGA afin de vérifier leur performance.

Un contrôleur numérique nécessite une modulation numérique de largeur d'impulsion (DPWM). L'approche  $\Sigma$ - $\Delta$  de la DPWM est un bon candidat en ce qui concerne le compromis entre la complexité et les performances. Un guide de conception d'étage  $\Sigma$ - $\Delta$  pour le DPWM est présenté. Une architecture améliorée de architectures traditionnelles 1-1 MASH  $\Sigma$ - $\Delta$  DPWM est synthétisée sans détérioration de la stabilité en boucle fermée ainsi qu'en préservant un coût raisonnable en ressources matérielles. Les résultats expérimentaux sur FPGA vérifient les performances des DPWM proposées en régimes stationnaire et transitoire.

Deux ASICs sont portés en CMOS  $0.35\mu m$ : le contrôleur en tri-mode pour le convertisseur

viii Résumé

abaisseur de tension et la commande par mode de glissement pour les convertisseurs abaisseur et élévateur de tension. Les bancs de test sont conçus pour conduire à un modèle d'évaluation de consommation énergétique. Pour le contrôleur en tri-mode, la consommation de puissance mesurée est seulement de 24,56mW/MHz lorsque le ratio de temps en régime de repos (stand-by) est 0,7. Les consommations de puissance de commande par mode de glissement pour les convertisseurs abaisseur et élévateur de tension sont respectivement de 4,46mW/MHz et 4,79mW/MHz. En utilisant le modèle de puissance, une consommation de la puissance estimée inférieure à 1mW/MHz est envisageable dans des technologies CMOS plus avancées. Comparé aux contrôlés homologues analogiques de l'état de l'art, les prototypes ASICs illustrent la possibilité d'atteindre un rendement comparable pour les applications de faible et de moyen puissance mais avec l'avantage d'une meilleure précision et une meilleure flexibilité.

## Acknowledgement

The research presented in this thesis was performed at AMPERE laboratory, INSA de Lyon.

I extend my appreciation and gratitude to many people who made this thesis possible. In particular special thanks to my advisor Professor Bruno Allard, for his advice, rigor, encouragement, and patience. Working with Professor Bruno Allard has been one of the most memorable experiences and the best fortunes in my life.

I am deeply indebted to my co-advisor Professor Xuefang Lin-shi for her guidance and support professionally as well as academically. The opportunities to work with and learn from Professor Xuefang Lin-shi have greatly shaped my professional views and provided many experiences that will ongoing assets in my professional career.

Along with Professor Bruno Allard and Professor Xuefang Lin-shi, I would like to thank Professors HEBRARD Luc, LI Zheying, CIRSTEA Marcian, MONMASSON Eric and Mr. TROCHUT Séverin for serving on my qualifying exam committee, and for asking questions which have periodically resurfaced in my mind and conduced me to sharper thinking.

I would like to express my gratitude to other faculty members of Ampère laboratory, Dominique Tournier, Abderrahime Zaoui, Pascal Bevilacqua, Sandrine Vallet and Marie-Guy Mercier.

I would also like to express my thanks to my colleagues, Shuibao Guo, Nan Li, Huang Runhua, Yanyan Zhuang and Khalil El Falahi as well as Jiawei Zhang, Ting Li, Senbin Chen and other friends enrolled by the program UT-INSA in 2008. Their companion and friendship helped me a lot.

I also appreciate China Scholarship Council (CSC) for financial support. Finally, I dedicated this thesis to my parents.

Bo

# Contents

| Li | st of I | ligures                                                         | xix |

|----|---------|-----------------------------------------------------------------|-----|

| Li | st of T | Cables                                                          | xxi |

| Al | bbrevi  | ation                                                           | XXV |

| Fr | ench    | Part                                                            | 1   |

| In | trodu   | ction                                                           | 1   |

| 1  | Stat    | e of the Art                                                    | 7   |

|    | 1.1     | Digital Control-law                                             | 9   |

|    |         | 1.1.1 Linear Control                                            | 9   |

|    |         | 1.1.2 Nonlinear Control                                         | 11  |

|    |         | 1.1.3 Predictive Dead-beat Control                              | 12  |

|    |         | 1.1.4 Summary of Control-law                                    | 14  |

|    | 1.2     | Digital Pulse-width-modulator                                   | 14  |

|    |         | 1.2.1 Delay-cell-based Methods                                  | 15  |

|    |         | 1.2.2 Dither-based Methods                                      | 17  |

|    |         | 1.2.3 Hardware-assisted Methods                                 | 18  |

|    |         | 1.2.4 Summary of DPWM                                           | 19  |

|    | 1.3     | Available Products and Performances                             | 20  |

|    | 1.4     | Summary                                                         | 20  |

| 2  | Con     | trol-laws for the Buck and Boost Converters                     | 23  |

|    | 2.1     | Review of PID and RST Controls for the Buck Converter           | 23  |

|    |         | 2.1.1 PID Control for the Buck Converter                        | 25  |

|    |         | 2.1.2 Robust RST Control for the Buck Converter                 | 26  |

|    |         | 2.1.3 Comparative Study of PID and RST Control-laws             | 27  |

|    | 2.2     | Improved Power-aware Tri-mode Control                           | 30  |

|    |         | 2.2.1 Review of Tri-mode Control for the Buck Converter         | 30  |

|    |         | 2.2.2 An Improved Version of Tri-mode Control Dedicated to ASIC | 32  |

xii CONTENTS

|   | 2.3  | Review of SM Control                                          |

|---|------|---------------------------------------------------------------|

|   |      | 2.3.1 Design Methodology of a SM Control for Power Converters |

|   |      | 2.3.2 SM Control for the Buck Converter                       |

|   | 2.4  | Design and Test of Control-laws for the Boost Converter       |

|   |      | 2.4.1 PID Control for the Boost Converter                     |

|   |      | 2.4.2 SM Control for the Boost Converter                      |

|   |      | 2.4.3 Simulation Results                                      |

|   | 2.5  | Summary                                                       |

| 3 | Dire | ct Control with Dual-state-variable Prediction 45             |

|   | 3.1  | Discrete Model of the Buck Converter                          |

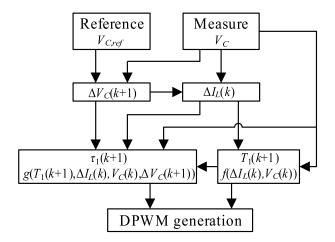

|   | 3.2  | DDP Control Pattern                                           |

|   | 3.3  | Calculation of the Current Variation                          |

|   | 3.4  | Calculation of the Voltage Variation                          |

|   | 3.5  | Operation of the Proposed Controller                          |

|   | 3.6  | Dynamic Range of $\tau_1$ and $T_1$                           |

|   | 3.7  | System Analysis and Simulation Results                        |

|   | 3.8  | Summary                                                       |

| 4 | Qua  | ntizers and Peripheral Building Blocks 57                     |

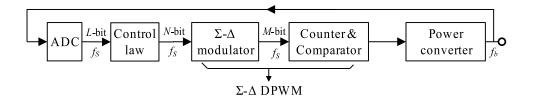

|   | 4.1  | $\Sigma$ - $\Delta$ Modulation for PWM                        |

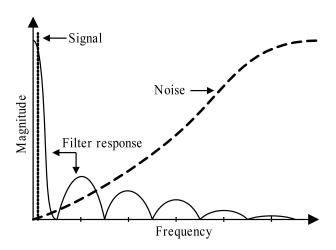

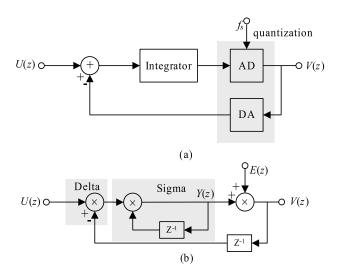

|   |      | 4.1.1 Design of the $\Sigma$ - $\Delta$ Modulation            |

|   |      | 4.1.2 $\Sigma$ - $\Delta$ Modulator under DC Excitation 61    |

|   | 4.2  | 1-1 DMASH $\Sigma$ - $\Delta$ DPWM                            |

|   | 4.3  | Phase-locked Loop for Clock Generation                        |

|   | 4.4  | Summary                                                       |

| 5 | Exp  | erimental Results in FPGA 75                                  |

|   | 5.1  | Testbench for the Buck and Boost Converters                   |

|   | 5.2  | Test of DPWM                                                  |

|   | 5.3  | Test of DDP Controller                                        |

|   | 5.4  | Test of PID and SM Controllers for the Boost Converter        |

|   | 5.5  | Summary                                                       |

| 6 | ASI  | C Integration 85                                              |

|   | 6.1  | Design Flow                                                   |

|   | 6.2  | VHDL-AMS Based Testbench and the Parameter Read-in Module 87  |

|   |      | 6.2.1 VHDL-AMS Based Testbench                                |

|   |      | 6.2.2 Parameter Read-in Module                                |

|   | 6.3  | Realized ICs                                                  |

|   |      | 6.3.1 The First Chip and Testbench                            |

|   |      | 6.3.2 The Second Chip and Testbench                           |

|   | 6.4  | Experimental Results with the First IC                        |

|   | 6.5  | Experimental Results with the Second IC                       |

|   | 6.6  | Summary                                                       |

CONTENTS xiii

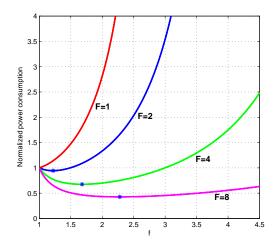

| 7  | Pow    | er Consumption Evaluation of Digital Controllers                          | 103        |

|----|--------|---------------------------------------------------------------------------|------------|

|    | 7.1    | Effective Power Estimation Model                                          | 104        |

|    | 7.2    | Feasible Evaluation of Power Consumption                                  | 108        |

|    |        | 7.2.1 Power Consumption Analysis of the Power-aware Tri-mode Controller . | 109        |

|    |        | 7.2.2 Power Consumption Analysis of the Second Chip                       | 110        |

|    |        | 7.2.3 Power Estimation in Advanced Technologies                           | 112        |

|    |        | 7.2.4 A Discussion about the Power Consumptions of ADC and Necessary Pe-  | 110        |

|    | 7.3    | ripherals                                                                 | 119<br>119 |

|    | 1.5    | Summary                                                                   | 119        |

| Co | nclus  | sion and perspective                                                      | 121        |

| Bi | bliogi | raphy                                                                     | 127        |

| Ar | nexe   | s                                                                         | 134        |

| A  | State  | e-space Models Dedicated to the Buck and Boost Converters                 | 135        |

|    | A.1    | Hybrid, State-space Averaging, and Small Signal Models                    | 135        |

|    | A.2    | State-space Averaging for the Buck and Boost Converters                   | 137        |

|    |        | A.2.1 Derivations for the Buck Converter                                  | 137        |

|    |        | A.2.2 Derivations for the Boost Converter                                 | 138        |

| В  | ASI    | C Testbench                                                               | 141        |

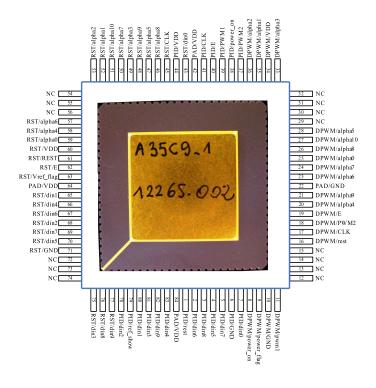

|    | B.1    | Packaged Chip and Pin Configuration                                       | 141        |

|    | B.2    | Testbech of the First Chip                                                | 144        |

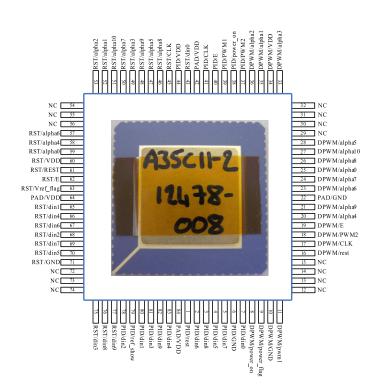

|    | B.3    | Testbech of the Second Chip                                               | 146        |

| C  | Con    | plementary Experimental Results                                           | 149        |

| D  | An I   | Example of RTL to Layout Design Flow                                      | 151        |

|    | D.1    | • 0                                                                       | 152        |

|    | D.2    | Place & Route Using Encounter                                             | 154        |

XiV

# List of Figures

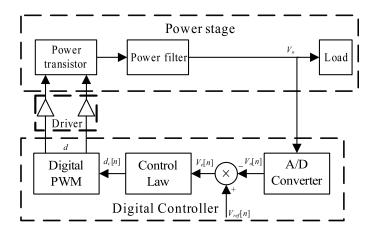

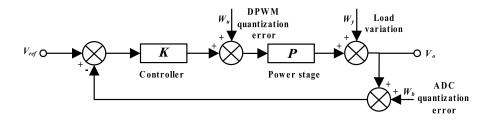

| 1    | Block diagram of a digitally controlled buck converter                                     | 2  |

|------|--------------------------------------------------------------------------------------------|----|

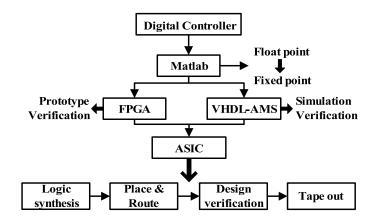

| 2    | General design flow for the digital controller                                             | 3  |

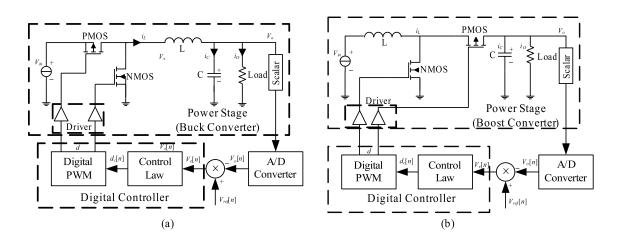

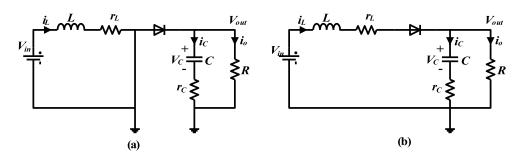

| 1.1  | Digitally controlled synchronous buck converter (a) and boost converter (b) re-            |    |

|      | spectively                                                                                 | 7  |

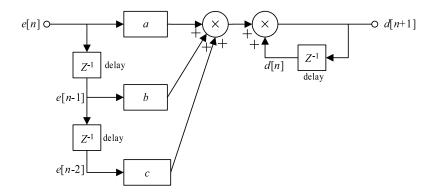

| 1.2  | Block diagram of the digital PID control [Prodic 02]                                       | 10 |

| 1.3  | Block diagram of the nonuniform ADC-based nonlinear control [Hu 08]                        | 11 |

| 1.4  | Quantizer characteristics of nonuniform ADC [Hu 08]                                        | 12 |

| 1.5  | Block diagram of the digital current-mode control                                          | 13 |

| 1.6  | Inductor current during one switching period for dead-beat control                         | 13 |

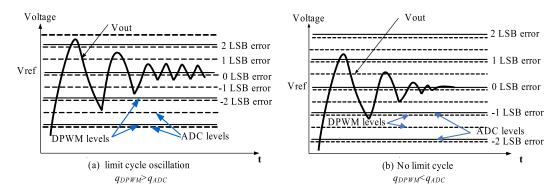

| 1.7  | Behavior of the output tracking with (a) DPWM resolution lower than ADC reso-              |    |

|      | lution, (b) DPWM resolution higher than ADC resolution                                     | 15 |

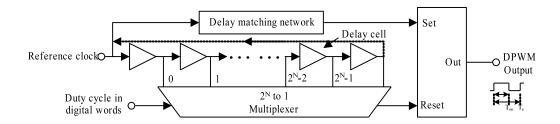

| 1.8  | Delay-line DPWM [Dancy 97, Patella 03, Lukic 07]                                           | 16 |

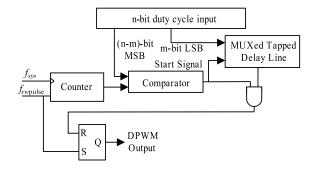

| 1.9  | Block diagram of hybrid DPWM [Yousefzadeh 06a]                                             | 16 |

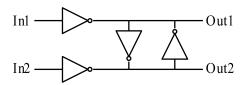

| 1.10 | Ring oscillator delay-cell [Peterchev 03b]                                                 | 16 |

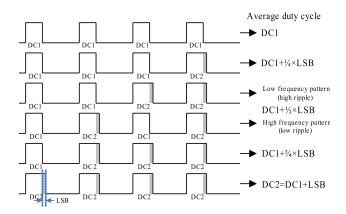

| 1.11 | Dither pattern realizing 2-bit DPWM [Peterchev 03a]                                        | 17 |

| 1.12 | Block diagram of dithered duty-cycle generator [Peterchev 03a]                             | 18 |

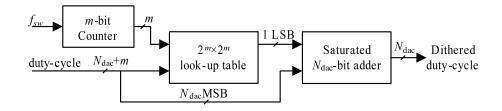

| 1.13 | Timing sequence of dual-clock DPWM with division parameter $M$ =7, $N$ =6 [Qiu 07]         | 18 |

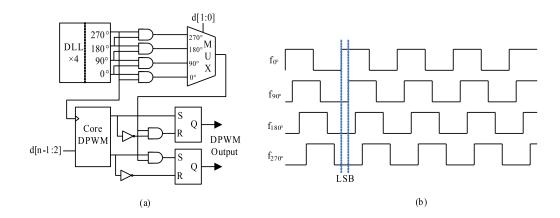

| 1.14 | (a) Block diagram of the phase-shift DPWM, (b) its timing sequence [Huerta 08,             |    |

|      | Quintero 09]                                                                               | 19 |

| 2.1  | Block diagram of a typical SMPS with disturbances                                          | 24 |

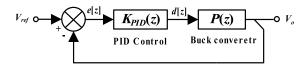

| 2.2  | Block diagram of a PID-controlled buck converter                                           | 25 |

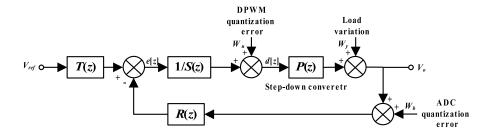

| 2.3  | Block diagram of the RST controlled buck converter                                         | 26 |

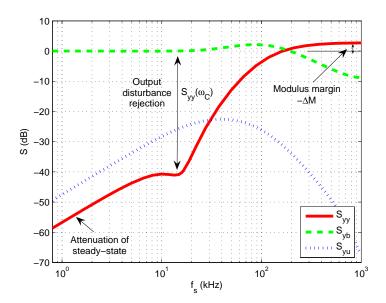

| 2.4  | Sensitivity functions for a robust RST controller                                          | 27 |

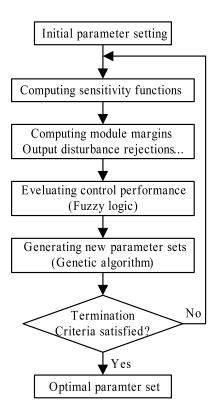

| 2.5  | Offline approach to determine the control parameters                                       | 28 |

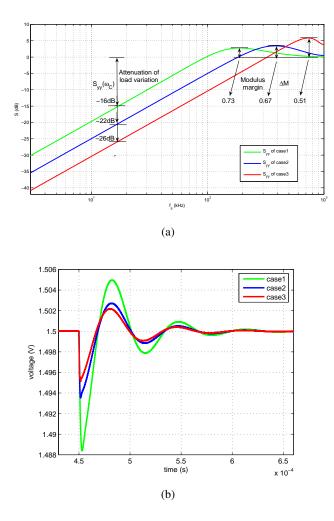

| 2.6  | (a) $S_{yy}$ sensitivity function for three PID controllers with different parameters, (b) |    |

|      | simulation of three PID controllers with different parameters under load change            |    |

|      | from 0.3A to 0.45A                                                                         | 29 |

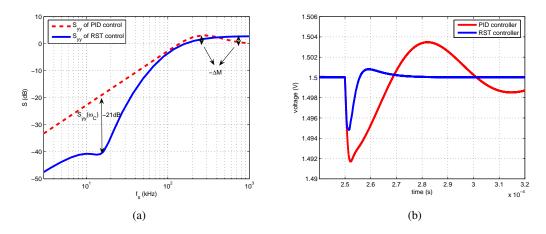

| 2.7  | (a) $S_{yy}$ sensitivity function for PID and RST controls, (b) simulation of PID and      |    |

|      | RST controls under load change from 0.3A to 0.45A                                          | 29 |

| 2.8  | Improved tri-mode controller dedicated to ASIC                                             | 30 |

xvi LIST OF FIGURES

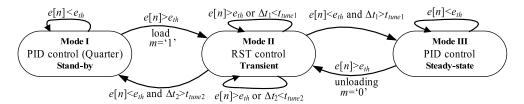

| 2.9  | State-switch diagram of mode arbitration block                                                                                                                                       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

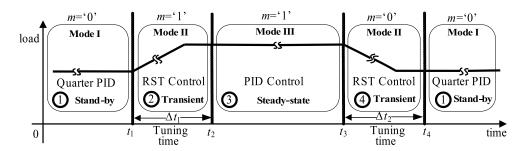

| 2.10 | Mode change procedure of tri-mode controller                                                                                                                                         |

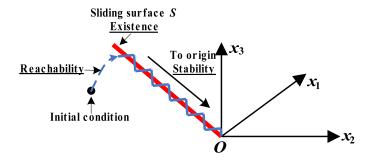

| 2.11 | Graphical representation of the convergence process of SM control satisfying ma-                                                                                                     |

|      | nipulation conditions                                                                                                                                                                |

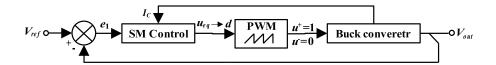

| 2.12 | Block diagram of SM controlled buck converter                                                                                                                                        |

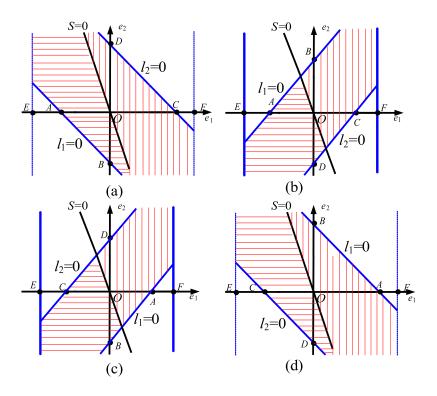

| 2.13 | Existence range of SM control mapped on $(e_1, e_2)$ phase plane                                                                                                                     |

|      | Dynamic response of the SM control under load change from 0.3A to 0.45A (a)                                                                                                          |

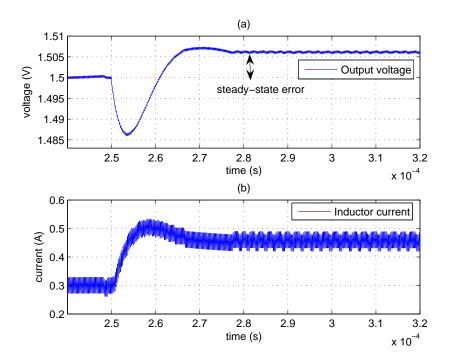

|      | output voltage, (b) inductor current                                                                                                                                                 |

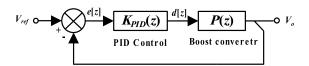

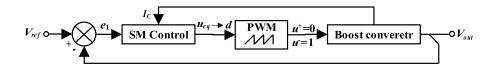

| 2.15 | Block diagram of a PID controlled boost converter                                                                                                                                    |

| 2.16 | Block diagram of SM controlled boost converter                                                                                                                                       |

| 2.17 | Dynamic responses under load change from 0.33A to 0.5A using (a) PID control-                                                                                                        |

|      | law, (b) SM control-law                                                                                                                                                              |

|      |                                                                                                                                                                                      |

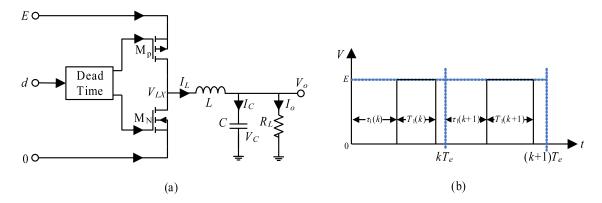

| 3.1  | (a) Block diagram of the buck converter, (b) a sample of corresponding current                                                                                                       |

|      | and voltage predictive control waveform                                                                                                                                              |

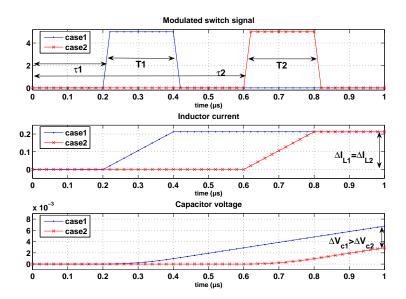

| 3.2  | System variables in one switching period with different voltage events 4                                                                                                             |

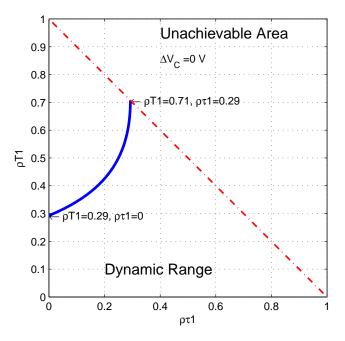

| 3.3  | Dynamic range and the corresponding tracking curve                                                                                                                                   |

| 3.4  | Operation of the DDP controller                                                                                                                                                      |

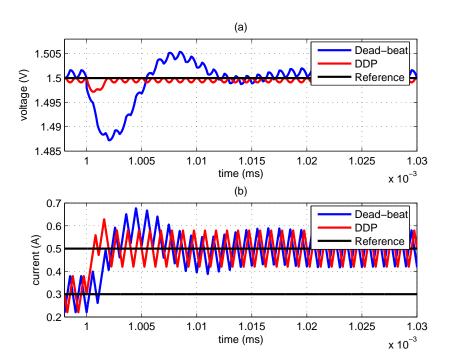

| 3.5  | Dynamic performances of the DDP and dead-beat controllers operating at 1MHz                                                                                                          |

|      | switching frequency respectively (a) voltage responses, (b) inductor current regu-                                                                                                   |

|      | lations                                                                                                                                                                              |

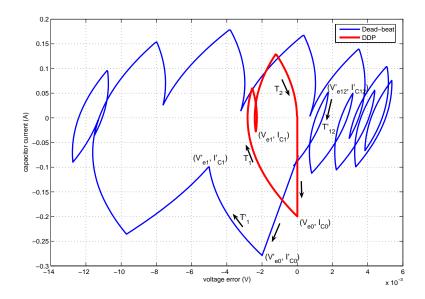

| 3.6  | State-space representation $(V_e, I_C)$ to describe the transient-state performances of                                                                                              |

|      | the DDP and deadbeat controllers respectively                                                                                                                                        |

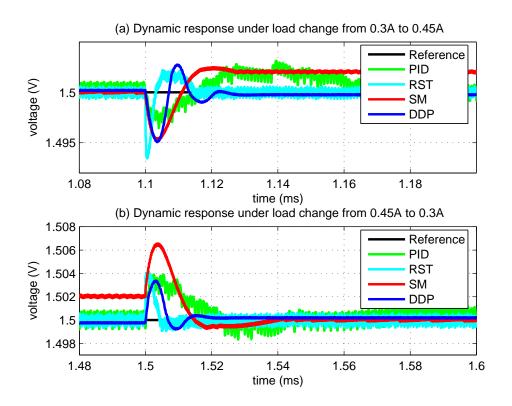

| 3.7  | Dynamic responses under load current change (0.3A $\rightarrow$ 0.45A $\rightarrow$ 0.3A) using                                                                                      |

|      | DDP, PID, RST and SM control-laws operating at 4MHz switching frequency 5                                                                                                            |

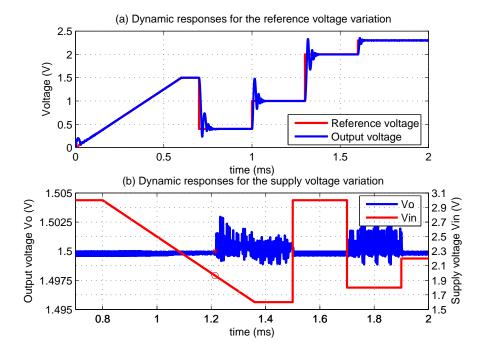

| 3.8  | (a) Dynamic responses for the reference voltage variation as well as the slope                                                                                                       |

|      | trajectory tracking, (b) dynamic responses for the supply voltage variation in slope                                                                                                 |

|      | mode and transition mode                                                                                                                                                             |

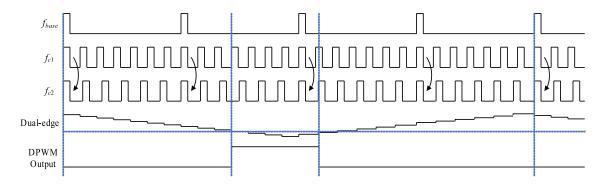

| 4.1  | Block diagram of the $\Sigma$ - $\Delta$ DPWM                                                                                                                                        |

| 4.2  | Amplitude frequency characteristic of oversampling modulator                                                                                                                         |

| 4.3  | Block diagram of the first-order (a) $\Sigma$ - $\Delta$ quantizer, (b) z-domain linear model 6                                                                                      |

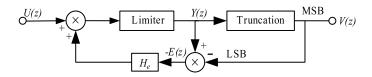

| 4.4  | Error-feedback structure                                                                                                                                                             |

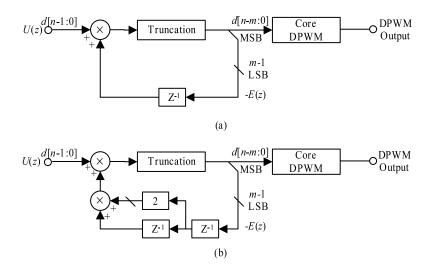

| 4.5  | Block diagram of (a) the first-order DPWM, (b) the second-order DPWM 6                                                                                                               |

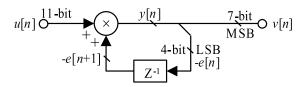

| 4.6  | An implementation example of the first-order $\Sigma$ - $\Delta$ modulator 6                                                                                                         |

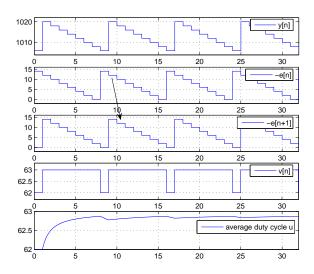

| 4.7  | A simulation example of the first-order $\Sigma$ - $\Delta$ modulator                                                                                                                |

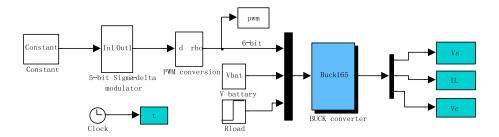

| 4.8  | Matlab simulink model to interpret the behavior of a $\Sigma$ - $\Delta$ modulator                                                                                                   |

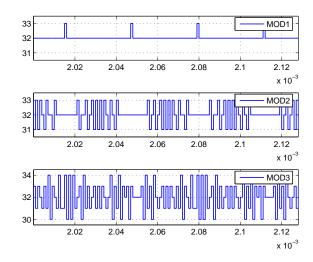

| 4.9  | Outputs of the $\Sigma$ - $\Delta$ modulators with different orders                                                                                                                  |

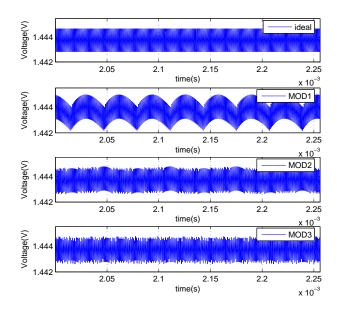

| 4.10 | Regulated power converter outputs by the $\Sigma$ - $\Delta$ DPWMs with different orders 6                                                                                           |

|      | (a) In-band quantization noise power versus input binary word of the first-order                                                                                                     |

| 7,11 | and second-order modulators in the buck converter, (b) the periodic peak noise                                                                                                       |

|      | around a specific input binary word                                                                                                                                                  |

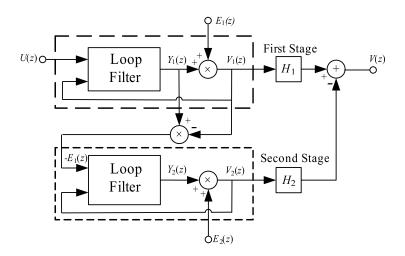

| 4 12 | Block diagram of a two stage MASH $\Sigma$ - $\Delta$ modulator [R. Schreier 05] 6                                                                                                   |

|      | Noise-shaping comparison between three 1-1 MASH $\Sigma$ - $\Delta$ modulations with dif-                                                                                            |

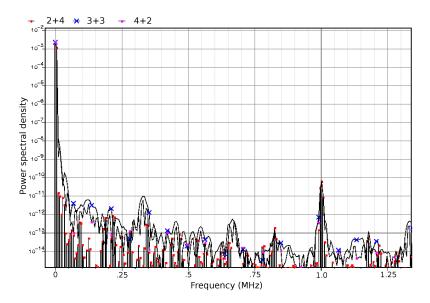

| 1.13 | ferent bit distributions                                                                                                                                                             |

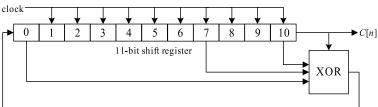

| 4 14 | Proposed 11-bit PN dither generator                                                                                                                                                  |

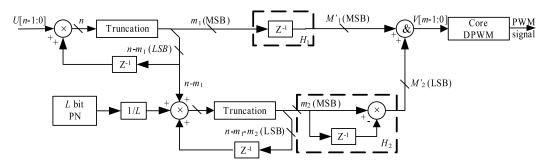

|      | Proposed 1-1 DMASH $\Sigma$ - $\Delta$ DPWM                                                                                                                                          |

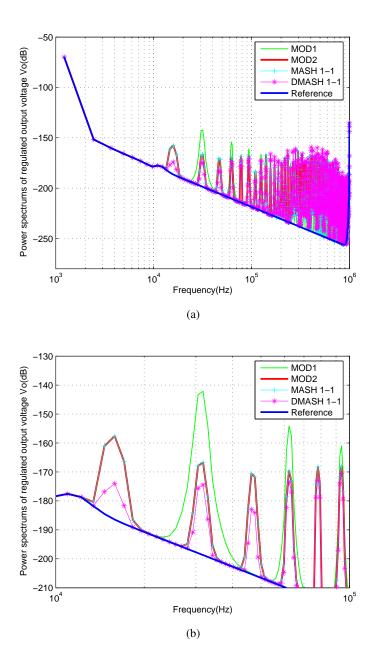

|      | (a) Power spectrums of output voltage $V_o$ using 1-1 DMASH and existing DP-                                                                                                         |

| 7.10 | WMs, (b) Power spectrums in the vicinity of the corner frequency $\dots \dots \dots$ |

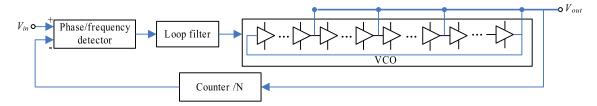

| 4 17 | Block diagram of a PLL                                                                                                                                                               |

| /    |                                                                                                                                                                                      |

LIST OF FIGURES xvii

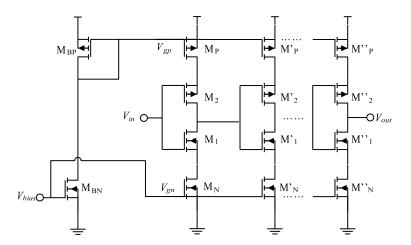

| 4.18 | Typical current-starved delay-cell with biasing circuit                                                                                                                        |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

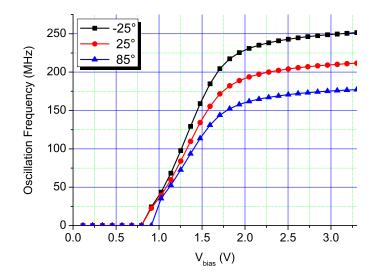

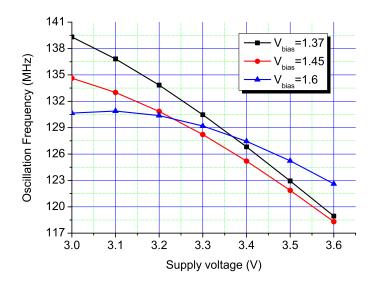

| 4.19 | Oscillation frequency of the current-starved VCO with the bias voltage 72                                                                                                      |

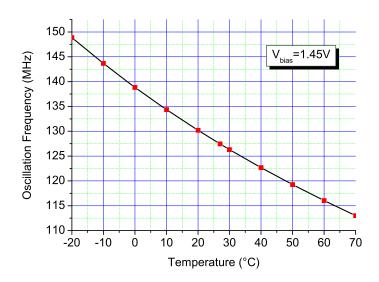

| 4.20 | Oscillation frequency of the current-starved VCO with the temperature                                                                                                          |

| 4.21 | Oscillation frequency of the current-starved VCO with the supply voltage 73                                                                                                    |

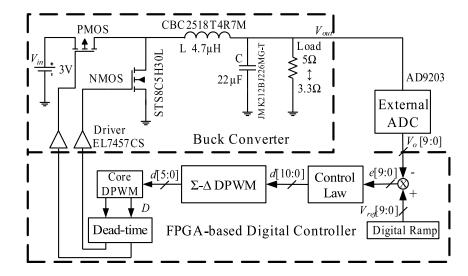

| 5.1  | Circuit configuration of the FPGA-based digital controller for the buck converter 76                                                                                           |

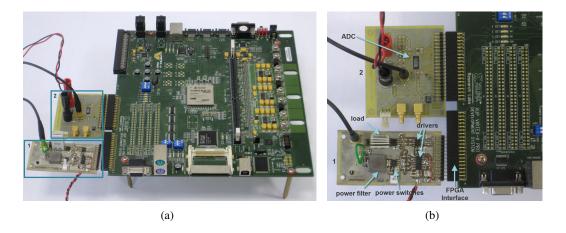

| 5.2  | The FPGA-based experimental platform of the buck converter (a) a system view,                                                                                                  |

|      | (b) a closed view of buck converter and ADC                                                                                                                                    |

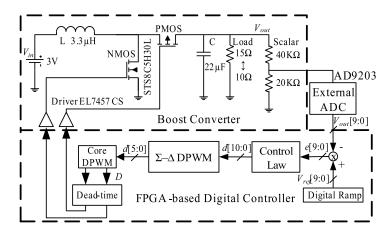

| 5.3  | Circuit configuration of the FPGA-based digital controller for the boost converter 77                                                                                          |

| 5.4  | The FPGA-based experimental platform for the boost converter (a) a system view, (b) a closed view of boost converter and ADCs                                                  |

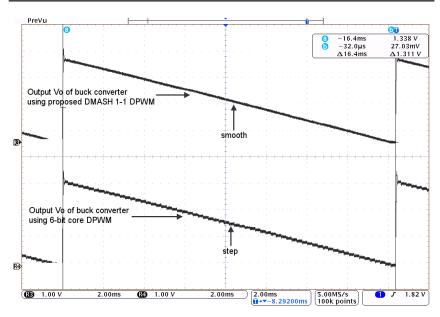

| 5.5  | Regulated output voltage $V_o$ of the experimental converter for a digital ramp from 2047 to 0                                                                                 |

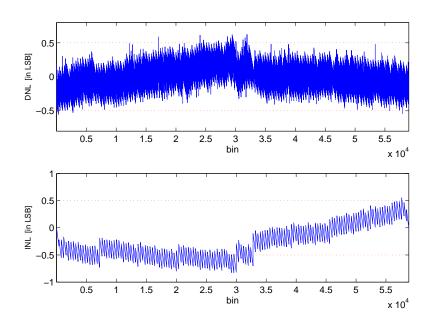

| 5.6  | Measured DNL and INL of the proposed 1-1 DMASH DPWM                                                                                                                            |

| 5.7  | Comparison of the regulated output voltage $V_o$ in transient state using the first                                                                                            |

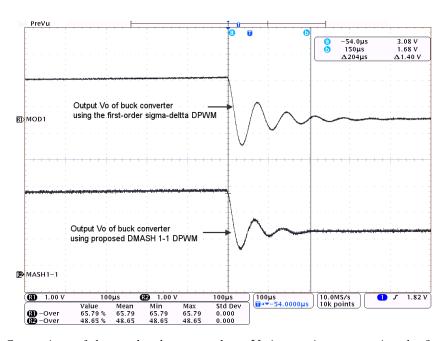

|      | order $\Sigma$ - $\Delta$ DPWM and the proposed 1-1 DMASH DPWM                                                                                                                 |

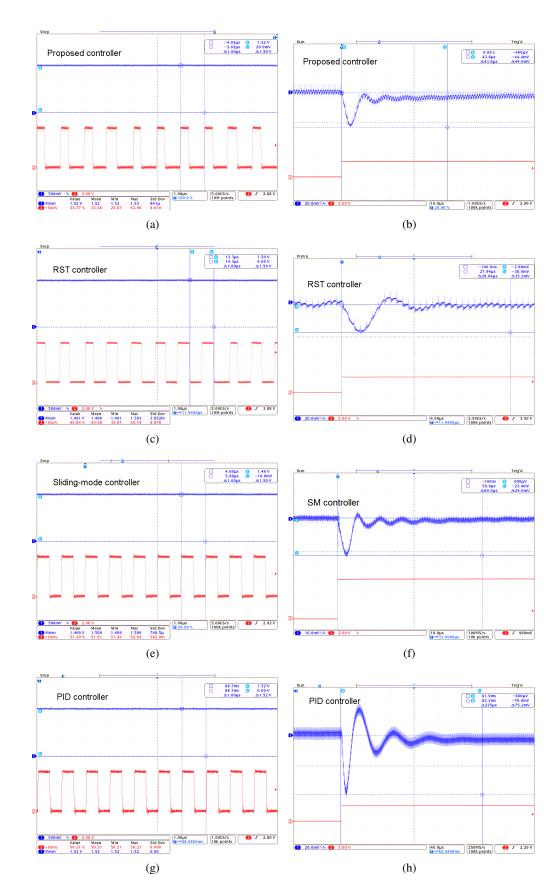

| 5.8  | Transient output voltages at 1MHz switching frequency during load change from 0.3A to 0.45A ( $R$ : from $5\Omega$ to $3.3\Omega$ ) as well as the steady-states using (a) DDP |

|      | controller in steady-state, (b) DDP controller in transient-state, (c) RST controller                                                                                          |

|      | in steady-state, (d) RST controller in transient-state, (e) SM controller in steady-                                                                                           |

|      | state, (f) SM controller in transient-state, (g) PID controller in steady-state, (h)                                                                                           |

|      | PID controller in transient-state                                                                                                                                              |

| 5.9  | Transient output voltage during load change from $0.45A$ to $0.3A$ (R: from $3.3\Omega$ to                                                                                     |

|      | $5\Omega$ ) using DDP controller (a) operating at 2MHz switching frequency, (b) operat-                                                                                        |

|      | ing at 4MHz switching frequency                                                                                                                                                |

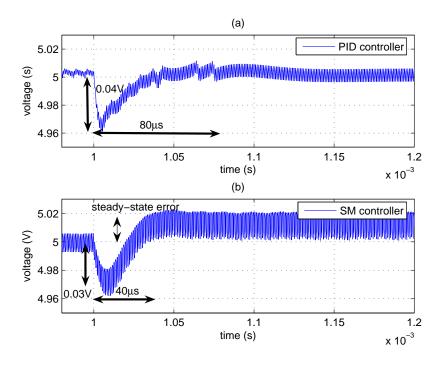

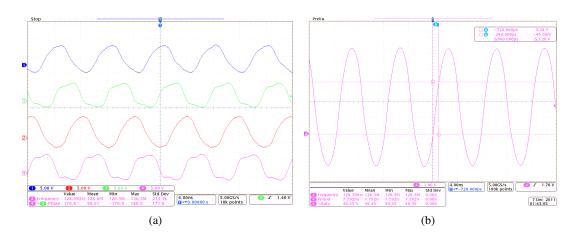

| 5.10 | PID controller: (a) steady-state operation at 1MHz, (b) load change from 0.33A to                                                                                              |

|      | $0.5A$ (R: from $15\Omega$ to $10\Omega$ )                                                                                                                                     |

| 5.11 | SM controller: (a) steady-state operation at 1MHz, (b) load change from 0.33A to                                                                                               |

|      | $0.5A$ (R: from $15\Omega$ to $10\Omega$ )                                                                                                                                     |

| 6.1  | Common digital IC design flow                                                                                                                                                  |

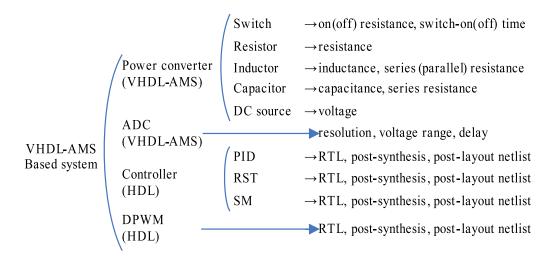

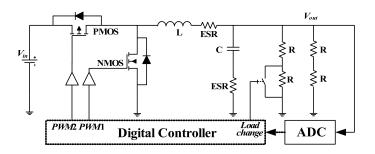

| 6.2  | Organization of a digitally controlled DC-DC power converter using VHDL-AMS 88                                                                                                 |

| 6.3  | Buck converter testbench using VHDL-AMS                                                                                                                                        |

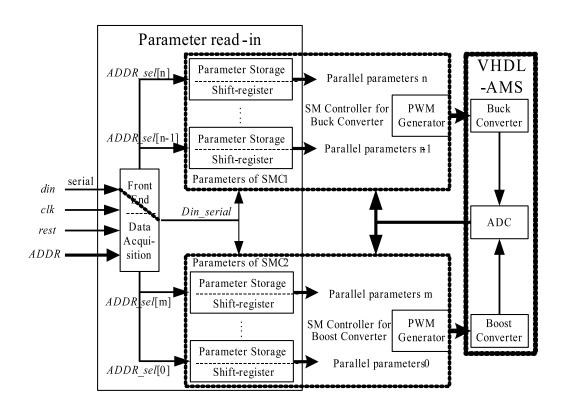

| 6.4  | Block diagram of the parameter read-in module                                                                                                                                  |

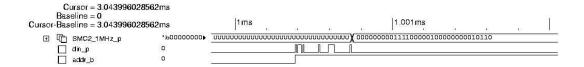

| 6.5  | Serial data receiver for dedicated controller                                                                                                                                  |

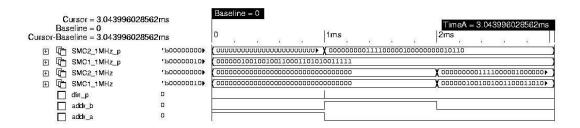

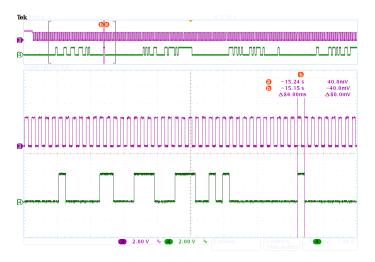

| 6.6  | Timing sequence of the parameter read-in module                                                                                                                                |

| 6.7  | Timing details of the parameter read-in module                                                                                                                                 |

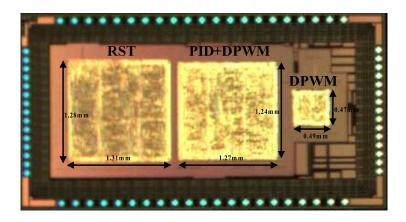

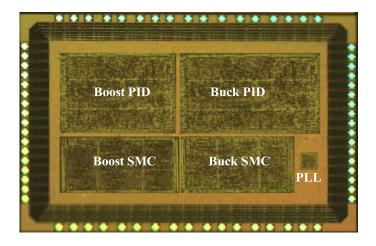

| 6.8  | Die micrograph of the first chip                                                                                                                                               |

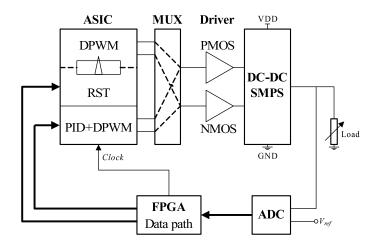

| 6.9  | Block diagram of the first chip testbench                                                                                                                                      |

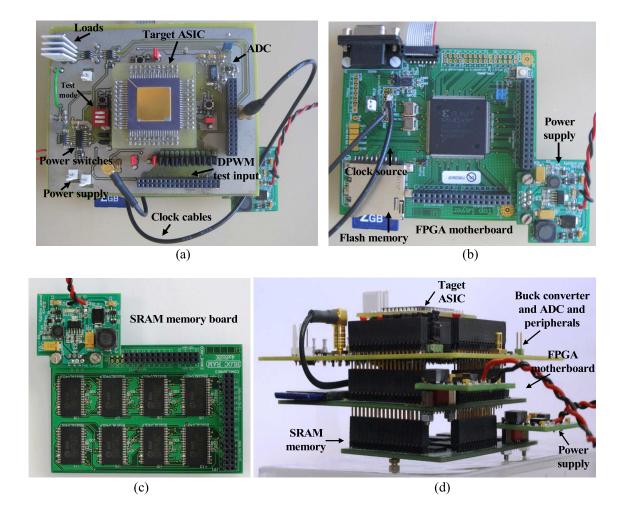

| 6.10 | Experimental test platform for the first chip (a) buck converter controlled by im-                                                                                             |

|      | plemented ASIC, (b) FPGA motherboard, (c) SRAM memory board, (d) a lateral view                                                                                                |

| 6.11 | Die micrograph of the second chip                                                                                                                                              |

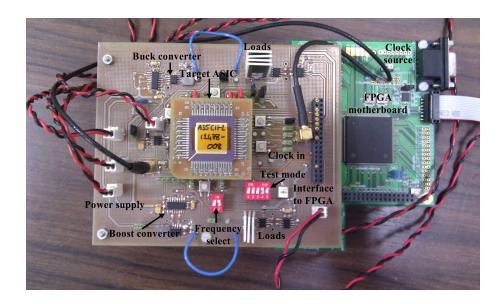

| 6.12 | Experimental test platform for the second chip                                                                                                                                 |

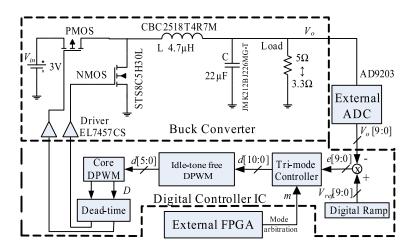

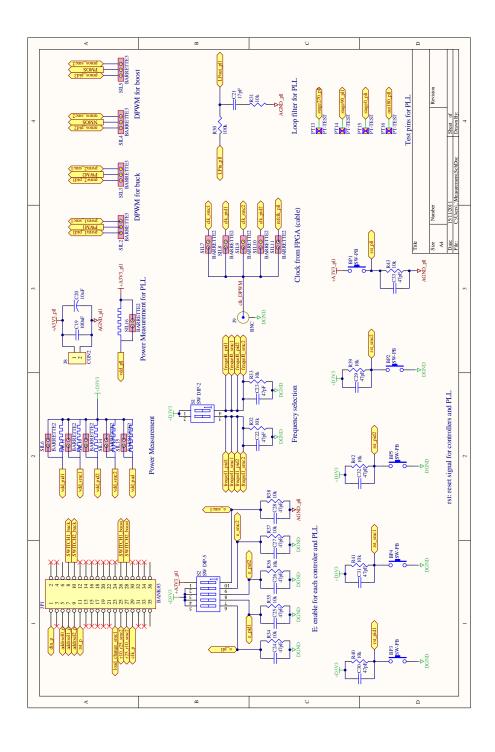

| 6.13 | Experimental platform schematic of the improved power-aware tri-mode controller                                                                                                |

|      | IC                                                                                                                                                                             |

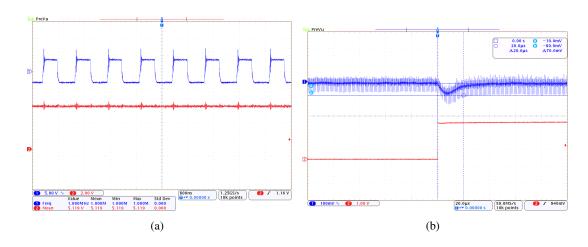

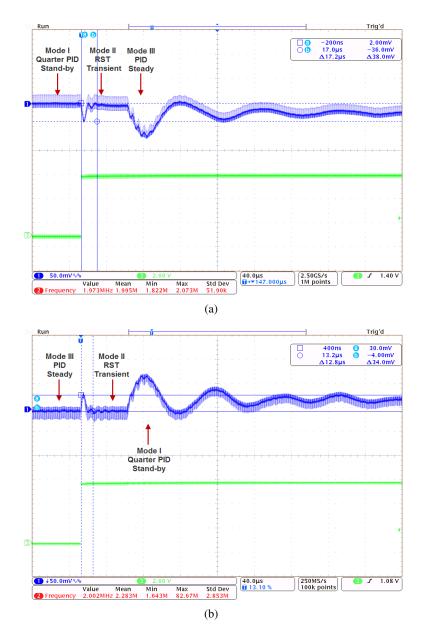

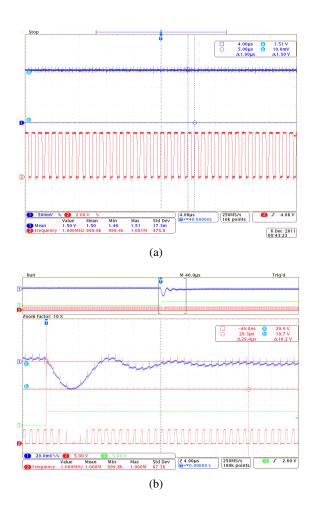

| 6.14 | Output voltage of improved tri-mode controller operating at 2MHz switching fre-                                                                                                |

|      | quency when load varies (a) from 0.3A to 0.45A, (b) from 0.45A to 0.3A 98                                                                                                      |

| 6.15 | A timing sequence example of the parameter read-in module                                                                                                                      |

xviii LIST OF FIGURES

| 6.16 | Experimental waveform of the PLL at 128MHz (a) with 4 phase shifts, (b) one phase details                                                                                                                                         | 99   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

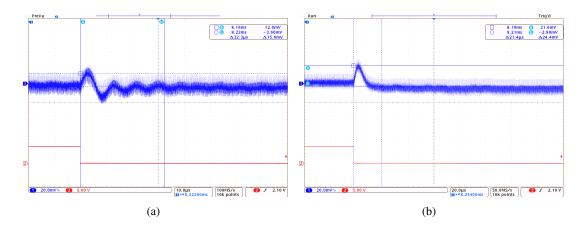

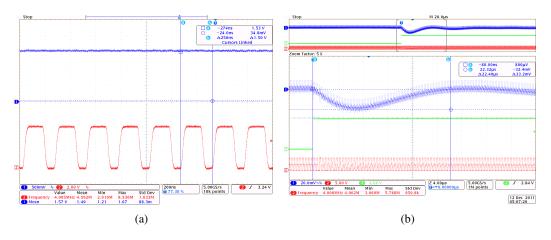

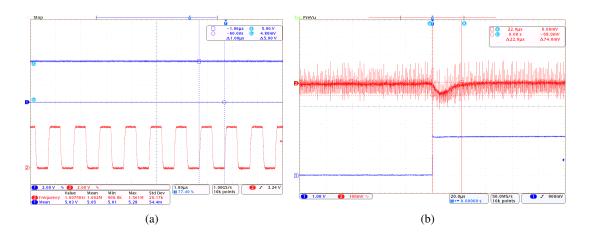

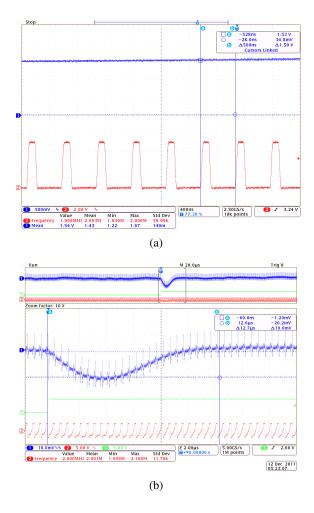

| 6.17 | SM controller for the buck converter: (a) steady-state operation at 4MHz, (b) load current change from $0.3A$ to $0.45A$ (R: from $5\Omega$ to $3.3\Omega$ )                                                                      | 99   |

| 6.18 | PID controller for the buck converter: (a) steady-state operation at 1MHz, (b) load current change from $0.3A$ to $0.45A$ (R: from $5\Omega$ to $3.3\Omega$ )                                                                     | 100  |

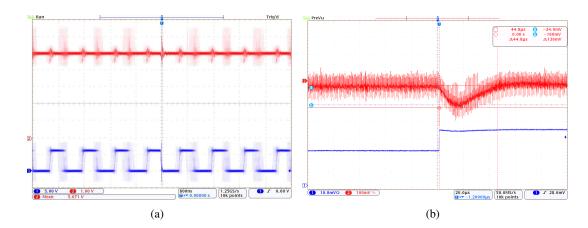

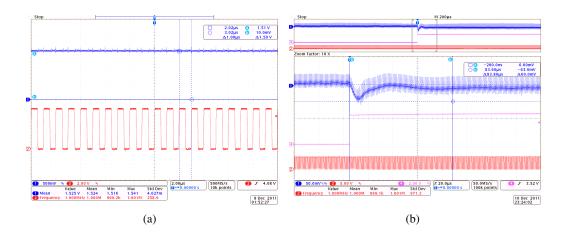

| 6.19 | SM controller for the boost controller: (a) steady-state operation at 1MHz, (b) load                                                                                                                                              |      |

| 6.20 | current change from 0.33A to 0.5A (R: from $15\Omega$ to $10\Omega$ ) PID controller for the boost controller: (a) steady-state operation at 1MHz, (b) load current change from 0.33A to 0.5A (R: from $15\Omega$ to $10\Omega$ ) | 100  |

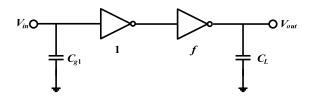

| 7.1  | Schematic to determine the minimum sized inverter                                                                                                                                                                                 | 104  |

| 7.2  | Normalized power consumption with respect to adopted process                                                                                                                                                                      | 105  |

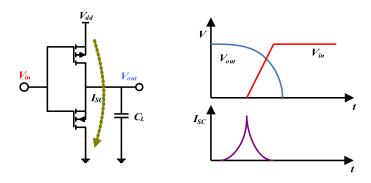

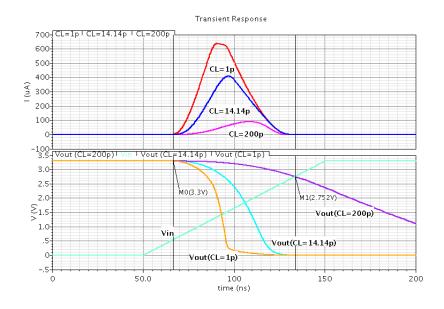

| 7.3  | Direct path caused by short current during switching                                                                                                                                                                              | 106  |

| 7.4  | Short current through inverter as a function of load capacitance                                                                                                                                                                  | 106  |

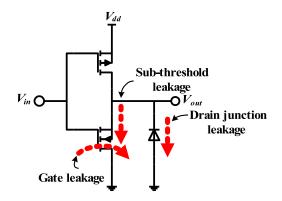

| 7.5  | Sources of leakage power consumption                                                                                                                                                                                              | 107  |

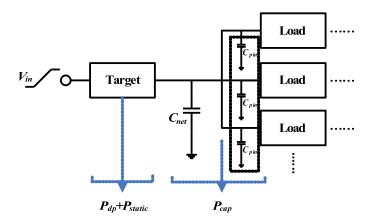

| 7.6  | Modeling of a power dissipation module by EDA tools [from Cadence RTL                                                                                                                                                             | 1.05 |

|      | Compiler manual]                                                                                                                                                                                                                  | 107  |

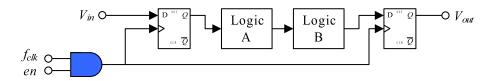

| 7.7  | Basic clock gating principal                                                                                                                                                                                                      | 108  |

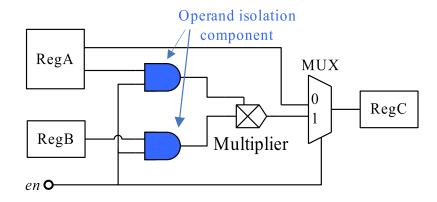

| 7.8  | Basic operand isolation principal                                                                                                                                                                                                 | 108  |

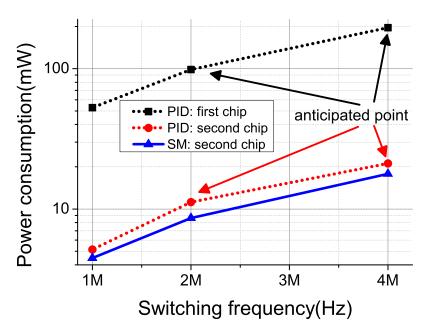

| 7.9  | Power consumption of the proposed tri-mode controller compared to stand-alone PID and RST controllers with respect to the SMPS switching frequency                                                                                | 109  |

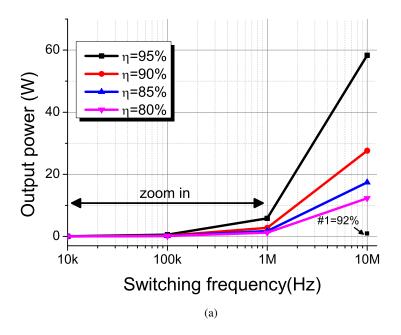

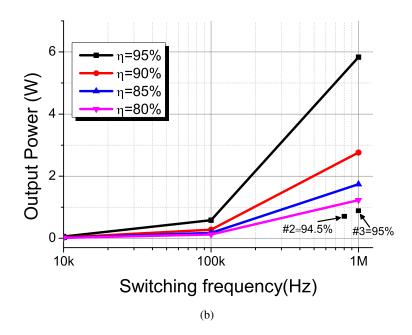

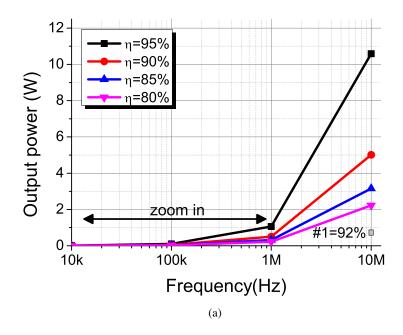

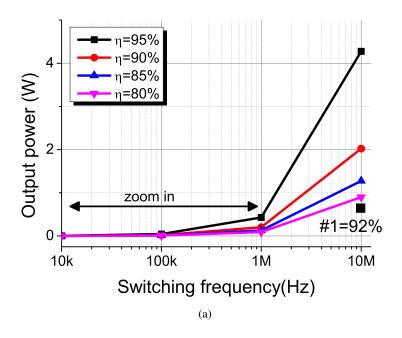

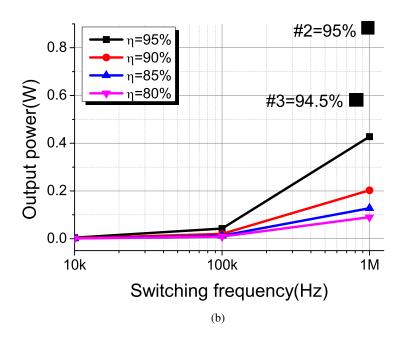

| 7.10 | Anticipated output power versus switching frequency of a buck converter con-                                                                                                                                                      | 105  |

| 7.10 | trolled by the improved power-aware tri-mode controller (a) with switching fre-                                                                                                                                                   |      |

|      | quency from 10kHz to 10MHz, (b) zoom for switching frequency from 10kHz to                                                                                                                                                        |      |

|      | 1MHz                                                                                                                                                                                                                              | 111  |

| 7 11 | Power consumption versus switching frequency of the PID and SM controllers in                                                                                                                                                     | 111  |

| 7.11 | the second chip compared to the PID controller in the first one                                                                                                                                                                   | 112  |

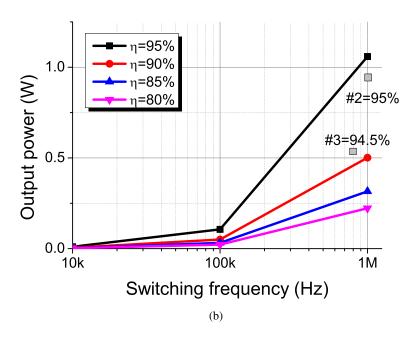

| 7 12 | Anticipated output power versus switching frequency of a buck converter con-                                                                                                                                                      |      |

| ,.12 | trolled by the SM controller (a) with switching frequency from 10kHz to 10MHz,                                                                                                                                                    |      |

|      | (b) zoom for switching frequency from 10kHz to 1MHz                                                                                                                                                                               | 113  |

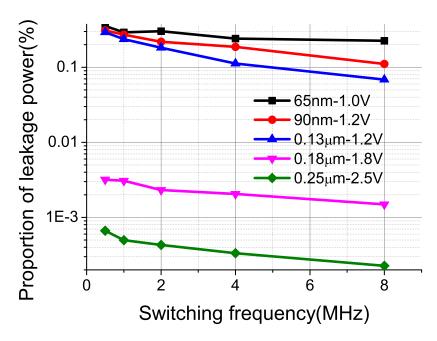

| 7.13 | Proportion of leakage power losses from the stand-alone PID controller in the first                                                                                                                                               |      |

|      | chip with $0.25\mu m$ , $0.18\mu m$ , $0.13\mu m$ , $90nm$ and $65nm$ CMOS processes respec-                                                                                                                                      |      |

|      | tively                                                                                                                                                                                                                            | 114  |

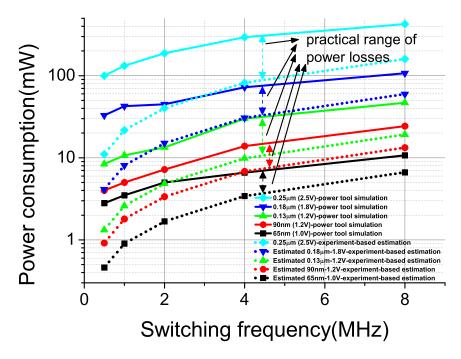

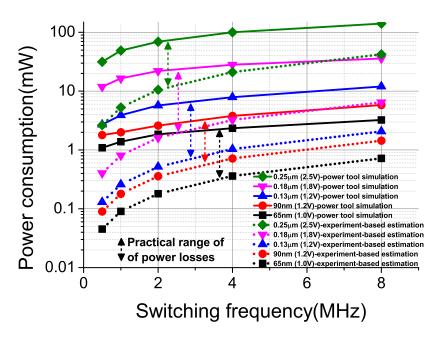

| 7.14 | Practical range of power losses for the stand-alone PID controller in $0.25\mu m$ ,                                                                                                                                               |      |

|      | $0.18\mu m$ , $0.13\mu m$ , $90nm$ and $65nm$ CMOS process respectively using a dedicated                                                                                                                                         |      |

|      | power simulation tool and extrapolation from experimental data                                                                                                                                                                    | 115  |

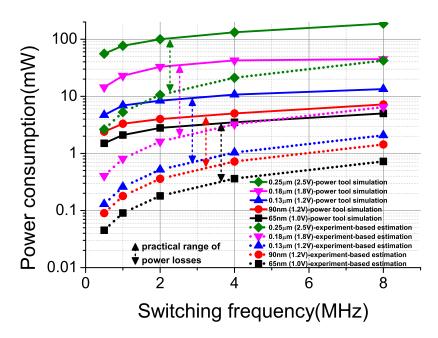

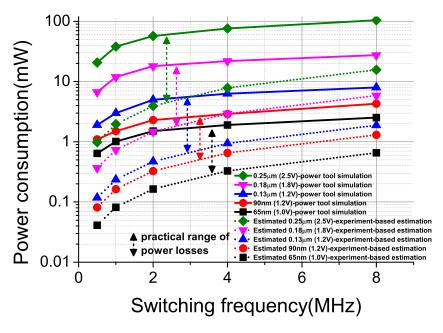

| 7.15 | Practical range of power losses for the optimized PID controller in $0.25\mu m$ , $0.18\mu m$ ,                                                                                                                                   |      |

|      | $0.13\mu m$ , $90nm$ and $65nm$ CMOS process respectively using a dedicated power                                                                                                                                                 |      |

|      | simulation tool and extrapolation from experimental data                                                                                                                                                                          | 116  |

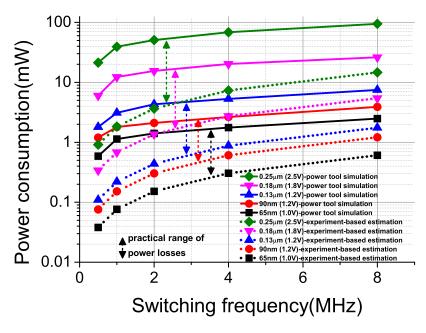

| 7.16 | Practical range of power losses for the optimized SM controller in $0.25\mu m$ , $0.18\mu m$ ,                                                                                                                                    |      |

|      | $0.13\mu m$ , $90nm$ and $65nm$ CMOS process respectively using a dedicated power                                                                                                                                                 |      |

|      | simulation tool and extrapolation from experimental data                                                                                                                                                                          | 116  |

| 7.17 |                                                                                                                                                                                                                                   |      |

|      | trolled by the SM controller in 90nm CMOS process (a) with switching frequency                                                                                                                                                    | 115  |

| 7.10 | from 10kHz to 10MHz, (b) Zoom for switching frequency from 10kHz to 1MHz                                                                                                                                                          | 117  |

| 7.18 | Practical range of power losses for the optimized PID controller for the boost con-                                                                                                                                               |      |

|      | verter in $0.25\mu m$ , $0.18\mu m$ , $0.13\mu m$ , $90nm$ and $65nm$ CMOS process respectively                                                                                                                                   | 110  |

|      | using a dedicated power simulation tool and extrapolation from experimental data                                                                                                                                                  | 118  |

LIST OF FIGURES xix

| 7.19        | Practical range of power losses for the optimized SM controller for boost converter in $0.25\mu m$ , $0.18\mu m$ , $0.13\mu m$ , $90nm$ and $65nm$ CMOS process respectively using a dedicated power simulation tool and extrapolation from experimental data | 118 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

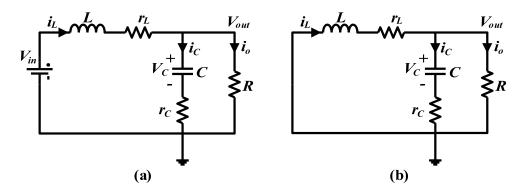

| A.1         | Buck converter topologies in CCM to derive the corresponding state equations (a) closed-switch, (b) open-switch                                                                                                                                               | 137 |

| A.2         | Boost converter topologies in CCM to derive the corresponding state equations (a)                                                                                                                                                                             |     |

|             | closed-switch, (b) open-switch                                                                                                                                                                                                                                | 139 |

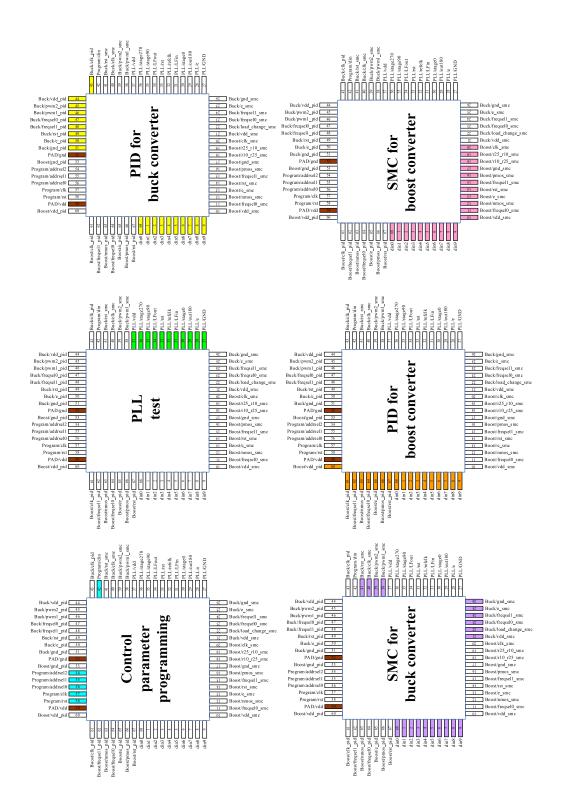

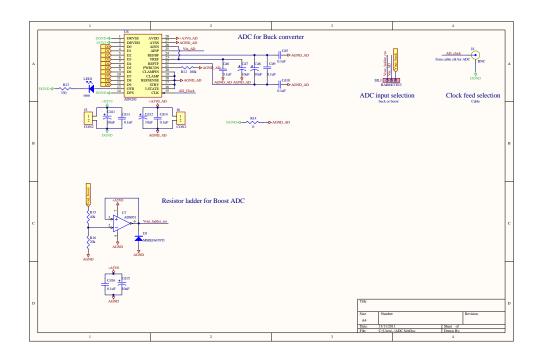

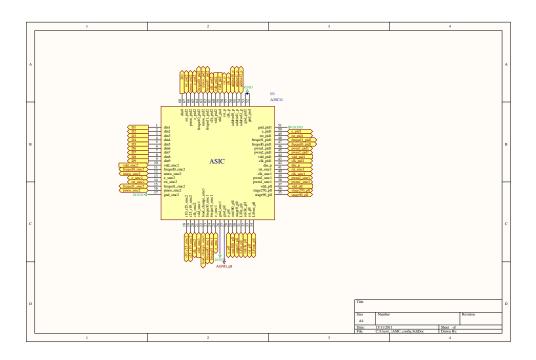

| B.1         | Pin definition and packaged chip of the first chip                                                                                                                                                                                                            | 141 |

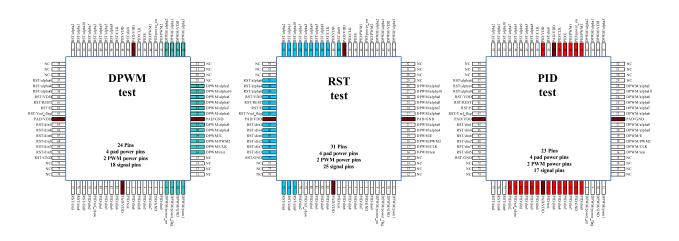

| B.2         | Pin configuration of each test                                                                                                                                                                                                                                | 142 |

| B.3         | Pin definition and packaged chip of the second chip                                                                                                                                                                                                           | 142 |

| B.4         | Pin configuration of the second ASIC test                                                                                                                                                                                                                     | 143 |

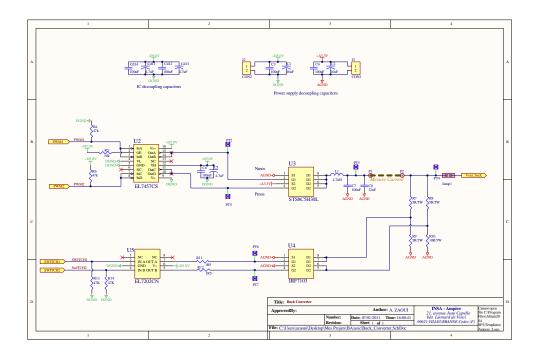

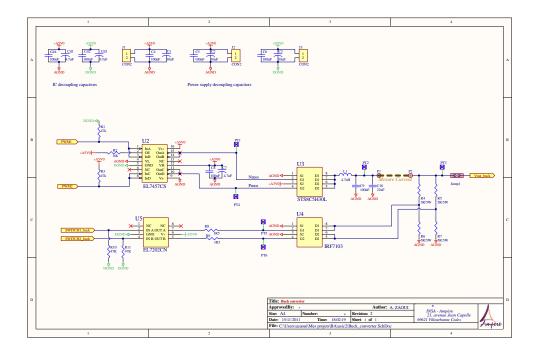

| B.5         | Buck converter under test                                                                                                                                                                                                                                     | 144 |

| B.6         | ADC as output quantizer                                                                                                                                                                                                                                       | 144 |

| B.7         | Target controller ASIC and its configurations                                                                                                                                                                                                                 | 145 |

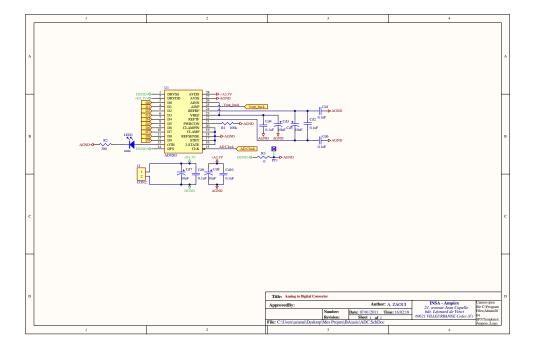

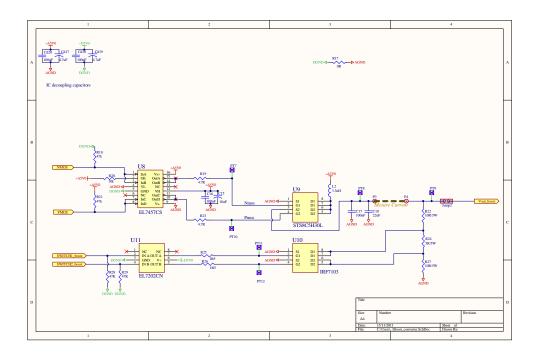

| B.8         | Buck converter under test                                                                                                                                                                                                                                     | 146 |

| B.9         | Boost converter under test                                                                                                                                                                                                                                    | 146 |

| B.10        | ADC as output quantizer                                                                                                                                                                                                                                       | 147 |

| B.11        | Target controller ASIC                                                                                                                                                                                                                                        | 147 |

| B.12        | Test configurations                                                                                                                                                                                                                                           | 148 |

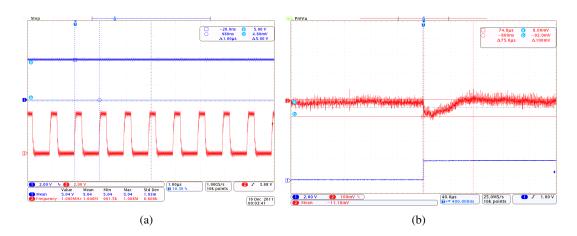

| <b>C</b> .1 | SM controller for the buck converter: (a) steady state operating at 1MHz, (b) load                                                                                                                                                                            |     |

|             | transients from 0.3A to 0.45A (R: from $5\Omega$ to $3.3\Omega$ )                                                                                                                                                                                             | 149 |

| C.2         | SM control for the buck converter: (a) steady state operating at 2MHz, (b) load                                                                                                                                                                               |     |

|             | transients from 0.3A to 0.45A (R: from $5\Omega$ to $3.3\Omega$ )                                                                                                                                                                                             | 150 |

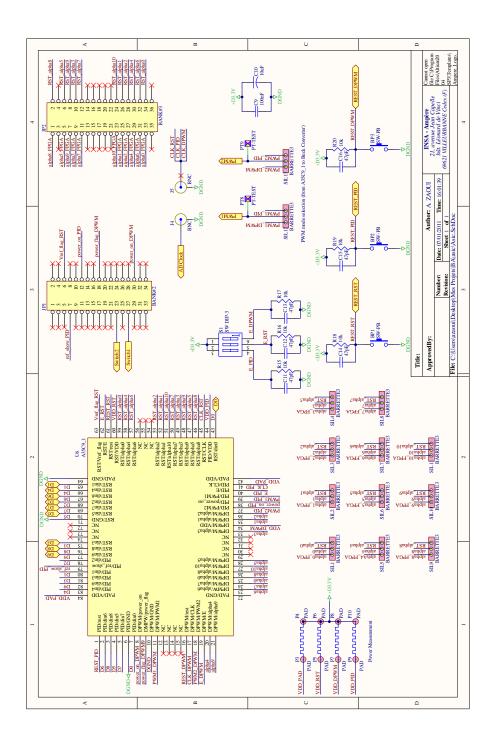

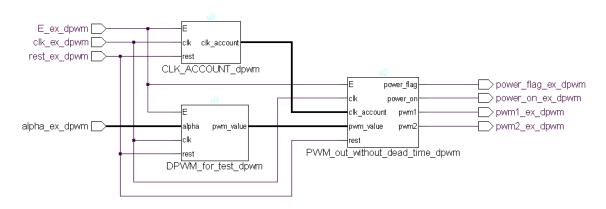

| D.1         | Building blocks of the dedicated DPWM                                                                                                                                                                                                                         | 151 |

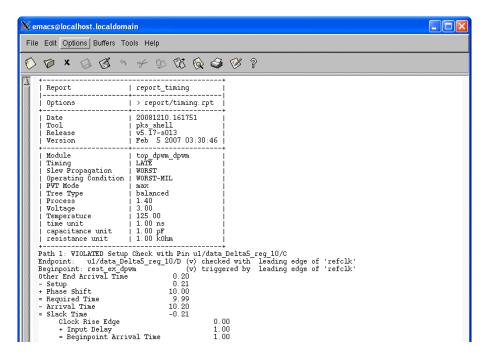

| D.2         | Timing report after synthesis                                                                                                                                                                                                                                 | 154 |

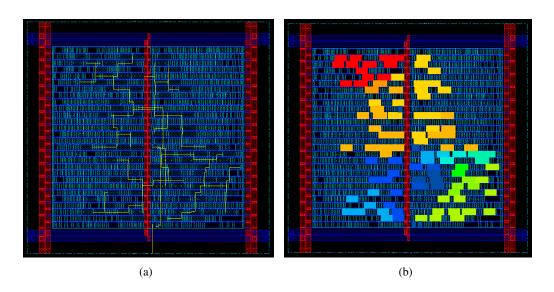

| D.3         | (a) Display clock tree after CTS, (b) Display clock phase delay after CTS                                                                                                                                                                                     | 155 |

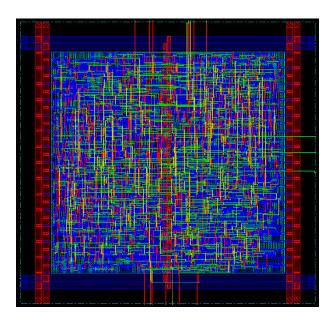

| D.4         | Post-place-and-route layout view                                                                                                                                                                                                                              | 155 |

XX LIST OF FIGURES

# List of Tables

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Summary of important ADCs                                                                                                                | 20<br>20 |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1                             | Dynamic performances of the DDP controller compared to other popular controllers based on simulation results at 4MHz switching frequency | 55       |

| 4.1                             | A variable and average duty-cycle example of the first-order $\Sigma\text{-}\Delta$ modulator                                            | 62       |

| 4.2                             | An example of maximum length sequence (MLS) with the shift register length from 5 to 11                                                  | 69       |

| 5.1                             | Parameters of the digitally controlled buck converter                                                                                    | 76       |

| 5.2                             | Parameters of the digitally controlled boost converter                                                                                   | 78       |

| 5.3                             | A comparison to reviewed controllers with respect to hardware resources                                                                  | 80       |

| 5.4                             | A comparison to reviewed controllers operating at 1MHz switching frequency with                                                          |          |

|                                 | respect to dynamic performances                                                                                                          | 82       |

| 5.5                             | Dynamic performances of the DDP controller under a load perturbation between                                                             |          |

|                                 | 0.3A and 0.45A                                                                                                                           | 83       |

| 5.6                             | Performance summary of SM and PID controllers for the boost converter                                                                    | 84       |

| 6.1                             | A parameter summary for the buck converter and ADC                                                                                       | 89       |

| 6.2                             | Referred devices and the parameters in the testbench                                                                                     | 94       |

| 6.3                             | Design specification of buck converter and ADC                                                                                           | 94       |

| 6.4                             | Chip areas of each functional block                                                                                                      | 95       |

| 6.5                             | Design specification for the boost converter and PLL                                                                                     | 95       |

| 6.6                             | Performances of the SM and PID controllers for the buck converter                                                                        | 97       |

| 6.7                             | Performances of the SM and PID controllers for the boost converter operating at                                                          |          |

|                                 | 1MHz                                                                                                                                     | 97       |

xxii LIST OF TABLES

### Abbreviation

**ADC** Analog-to-digital converter

ALU Arithmetic logic unit

**ASIC** Application-specific integrated circuit

**CCM** Continuous conduction mode

**CMOS** Complementary metal-oxide-semiconductor

**DAC** Digital-to-analog converter

**DCM** Discontinuous conduction Mode

**DLL** Delay-locked loop

**DMASH** Dithered multistage noise shaping

**DNL** Differential nonlinearity

**DPWM** Digital pulse-width modulation (modulator)

**DRC** Design rule check

**DSP** Digital signal processor

EDA Electronic design automation

ESR Equivalent series resistance

FPGA Field-programmable gate array

HDL Hardware description language

IC Integrated circuit

INL Integral nonlinearity

IP Intellectual property

LCO Limit-cycle oscillation

LDO Low-dropout regulator

xxiv Abbreviation

**LP** Loop filter

LSB Least significant bit

LUT Look-up table

LVS Layout versus schematic

MASH MultistAge-noise-SHaping

MLS Maximum length sequence

MOSFET Metal-oxide-semiconductor field-effect transistor

MSB Most significant bit

NTF Noise transfer function

PD Phase detector

PLL Phase-locked loop

PN Pseudo-noise

**PSD** Power spectral density

**PVT** Process-voltage-temperature

PwrSoC Power supply-on-chip RTL Register-transfer level

**SAR** Successive approximation register

**SDF** Standard delay format

SM Sliding-mode

**SMPS** Switched-mode power supply

**STF** Signal transfer function

**TTM** Time to market

VCO Voltage-controlled oscillatorVLSI Very-large-scale integrationVSS Variable structure system

**ZOH** Zero order hold

### French Part

### Chapitre 1 Etat de L'art

Afin de bénéficier de la technologie avancée CMOS, beaucoup d'idées sont proposées visà-vis de la commande numérique des convertisseurs de puissance. Contrairement au contrôleur analogique, l'implémentation du contrôleur numérique requiert un convertisseur analogique numérique (CAN) et une modulation de largeur d'impulsion (MLI) pour laquelle une attention particulière doit être accordée (pour éviter les cycles limites par exemple). La question cruciale du CAN est de parvenir à une résolution suffisante tout en maintenant la consommation d'énergie la plus faible possible. La ligne à retard ou les architectures hybrides sont des solutions possibles. Tous les CAN proposés ne mesurent que le voisinage de la tension de référence (notion de structure à fenêtres). La conception de CAN ne tombe pas dans le cadre de cette thèse.

Grâce à l'approche basée sur des "look-up tables", l'implémentation du régulateur linéaire, notamment le régulateur PID en mode tension, bénéficie d'avantage en termes de coût de ressources matérielles. Cependant, leurs performances dépendent généralement du point de fonctionnement, tel que la présence d'éléments parasites, la variation de la charge en fonction du temps ou la variation de la tension d'alimentation peuvent détériorer le comportement de la régulation. La commande non linéaire par mode de glissement offre de bonnes performances de régulation et présente des algorithmes relativement simples. Elle fera l'objet du Chapitre 2. Avec la connaissance du courant dans l'inductance, une structure de commande multi-boucles peut être adaptée : une boucle interne en courant et une boucle externe en tension. Cette méthode augmente l'efficacité du régulateur avec les avantages inhérents comme la protection contre les surintensités. La commande dite *dead-beat* et le contrôle en courant programmable sont largement utilisés pour la boucle de

xxvi French Part

courant interne. Cet algorithme de contrôle calcule, à chaque période d'échantillonnage, le rapport cyclique à l'aide d'un modèle discret du convertisseur, pour s'assurer que le courant dans l'inductance atteint la référence à la période suivante.

Une modulation numérique à largeur d'impulsion (MNLI) à haute résolution est une condition nécessaire pour éviter les oscillations de cycles limites (OCL). Les lignes-à-retard ou les compteurs associés à des comparateurs font parties des architectures classiques mais nécessitent des fréquences d'horloge d'autant plus élevée que la fréquence de découpage du convertisseur augmente. Différentes solutions sont proposées dans la littérature : les méthodes basée sur les cellules de retard, les méthodes utilisant le moyennage multi-cycle ou les méthodes assistées par des ressources matérielles. Nous nous focalisons sur la modulation  $\Sigma$ - $\Delta$  qui sera analysée du point de vue temporelle et fréquentielle dans le Chapitre 4.

A la fin de ce chapitre, les produits les plus importants reflétant l'état de l'art de la conception de régulateurs sont présentés comme références.

French Part xxvii

### Chapitre 2 Commandes pour des Convertisseurs Abaisseur et Elévateur de Tension

Ce chapitre se concentre sur la conception des commandes à haute efficacité énergétique, consacrée aux convertisseurs abaisseur et élévateur de tension. Les performances de la commande dédiée est critique pour l'efficacité de conversion. La commande adoptée doit fonctionner correctement dans l'état dynamique et l'état statique. L'implémentation physique doit être relativement simple. Par ailleurs les fréquences de découpage élevées (>100MHz) présentent un verrou fort pour la commande numérique.

Ce chapitre commence par une revue des commandes existantes pour un convertisseur abaisseur de tension comme les PID, RST et la commande par mode de glissement.

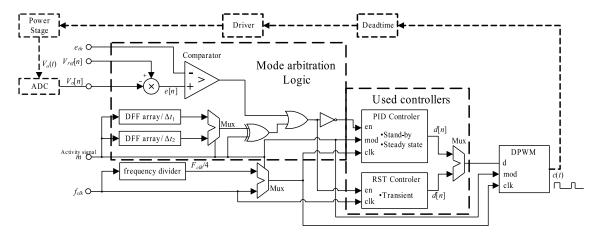

Une commande numérique dite tri-mode contenant un PID, un PID sous échantillonné et un RST a été étudiée. Une amélioration au niveau des transitions des états du contrôleur tri-mode est apportée en s'accordant avec les conditions des opérations du convertisseur abaisseur durant l'état stable, l'état repos (stand-by) et l'état transitoire.

Pour un convertisseur élévateur de tension où la non linéarité est plus importante, une commande linéaire PID et une commande non linéaire par mode de glissement sont synthétisées.

Une partie importante de notre travail s'intéresse à la consommation énergétique du contrôleur. L'objectif est de lier cette consommation aux performances de la commande. Toutes les commandes présentées dans ce chapitre sont intégrée au sein d'un ASIC afin de vérifier l'éligibilité d'une commande numérique donnée dans le cadre d'un système de gestion d'énergie intégré ou Power System-on-Chip - PwrSoC (l'objet du Chapitre 6 et Chapitre 7).

FRENCH PART

### **Chapitre 3** Commande Directe avec Deux Etats de Prédiction

Un nouveau contrôleur numérique basé sur le principe de la commande prédictive est proposée pour le convertisseur abaisseur de tension à haute fréquence de découpage. Par rapport à la commande prédictive traditionnelle en mode courant, la prédiction du courant de l'inductance et de la tension de sortie ont effectuées en même temps, en ajoutant une variable de contrôle au signal MNLI (modulation numérique de largeur d'impulsion ou DPWM). Ceci accélère la vitesse de convergence pendant les états transitoires, tandis que la rejection des perturbations de la charge et le suivi de référence sont conservées avec d'excellentes performances.

Cette commande nécessite des informations sur la tension aux bornes de la capacité de sortie et la variation du courant de l'inductance en entrée. Un algorithme d'estimation est proposé afin de réaliser cette commande sans ajouter des capteurs physiques.

L'analyse du fonctionnement de ce contrôleur illustre des performances meilleurs comparant aux celles des contrôleurs PID, RST ou par mode de glissement.

French Part xxix

### Chapitre 4 Quantificateurs et des Blocs Périphériques

Pour la commande numérique, les deux quantificateurs, MNLI et CAN, sont utilisées comme les interfaces entre le contrôleur et l'étage de puissance. Des quantificateurs de résolution insuffisante peuvent provoquer des oscillations de cycles limites ou OCL. Le défi pour la conception d'une approche de MNLI dépend non seulement de l'exigence de sa résolution, mais aussi de la faisabilité de l'implémentation en termes de consommation acceptable d'énergie. Les deux techniques possibles comportent la génération de petits intervalles par les techniques dérivées des lignes à retard et les techniques de moyenne dans le domaine temporel par la modulation  $\Sigma$ - $\Delta$  ou la décimation. En effet, les méthodes ci-dessous peuvent être considérées respectivement comme deux approches de génération pour la haute fréquence dans les domaines temporel et fréquentiel.

Le modulateur  $\Sigma$ - $\Delta$  pour MNLI consomme moins d'énergie que les lignes à retard. Une analyse en boucle fermée est donnée afin de démontrer l'effet du modulateur  $\Sigma$ - $\Delta$ . Le modulateur introduit des ordres d'excitation continue dans le spectre de la tension de sortie du convertisseur DC-DC, qu'il faut rejeter.

La structure dite 1-1 MASH  $\Sigma$ - $\Delta$  de MNLI est considérée dans ce chapitre. Conformément à l'analyse, il n'y a pas d'amélioration de la réduction du bruit, comparée à une MNLI  $\Sigma$ - $\Delta$  de second-ordre, bien que la performance dynamique soit prévue pour être améliorée. Alors un bloc de décimation est ajouté à la structure 1-1 MASH  $\Sigma$ - $\Delta$  si bien qu'il puisse effectivement réduire l'effet des marques lentes sans trop de ressources matérielles supplémentaires. Toutes les analyses durant des états stationnaire et transitoire seront données avec les résultats expérimentaux.

Le détail qui concerne l'implémentation du CAN concerne l'architecture de la ligne en retard et la fenêtre de capture. Comme le CAN n'est pas l'objet principal de ce travail, il ne sera pas élaboré dans ce chapitre. La boucle à verrouillage de phase (PLL: Phase Locked Loop) est un autre bloc nécessaire pour implémenter un ASIC. Ce chapitre donne une approche synthétique, adoptant la cellule à retard qui est insérée dans un oscillateur contrôlé en tension assisté par un convertisseur à pompe de charge comme détecteur de phase.

XXX FRENCH PART

### Chapitre 5 Résultats Expérimentaux sur FPGA

Ce chapitre présente les résultats expérimentaux des contrôleurs et MNLI discutés dans les chapitres précédents. Tout d'abord, les platesformes expérimentales pour les convertisseurs abaisseurs et élévateurs de tension sont introduites. Ensuite, les résultats expérimentaux vérifient les améliorations de la MNLI proposé. Les résultats expérimentaux de la commande directe avec deux états de prédiction pour le fonctionnement convertisseur abaisseur de tension à la fréquence de découpage de 1MHz, sont donnés en comparaison avec des PID, RST et par mode de glissement. Les essais avec une fréquence de découpage de 4MHz sont également réalisés pour montrer les meilleures performances du contrôleur proposé. Enfin, les performances du convertisseur élévateur de tension sous les contrôleurs PID et par mode de glissement sont fournies. La fréquence de découpage de 4MHz n'est limitée que par les éléments discrets du convertisseur DC-DC. Les simulations de l'ASIC montreront un fonctionnement correct vis-à-vis de fréquence de découpage supérieur à 50 MHz.

FRENCH PART XXXI

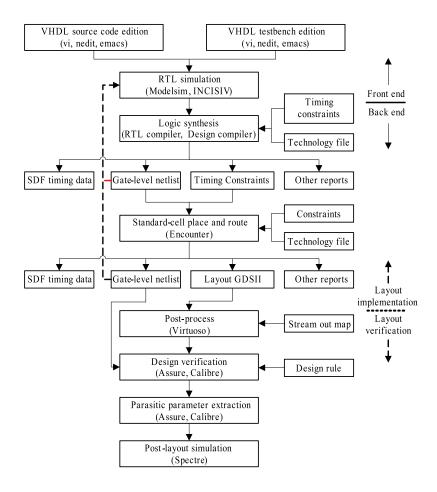

### **Chapitre 6** Intégration sur ASIC

Ce chapitre reprend d'abord le flot de conception *top-down* des circuits intégrés numériques et mixtes analogiques-numériques. Basé sur ce flot, deux ASICs ont été élaborés pour permettre une évaluation de la performance et l'efficacité des contrôleurs numériques, plus poussée que sur FPGA. Nous avons implémenté trois commandes dans une première puce (contrôleurs PID, RST et par mode de glissement). Certains circuits périphériques nécessaires sont aussi intégrés comme les MNLI, BVP (boucle à verrouillage de phase) et une interface série-parallèle.

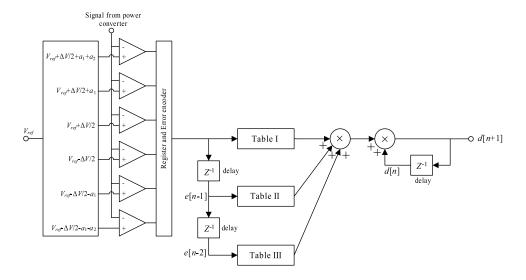

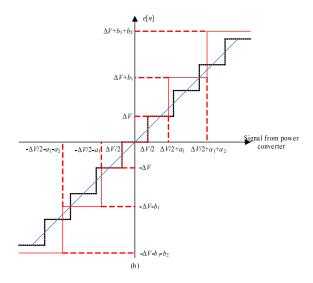

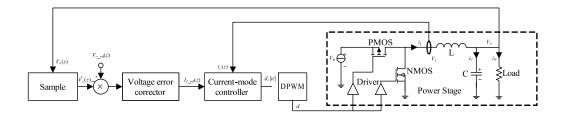

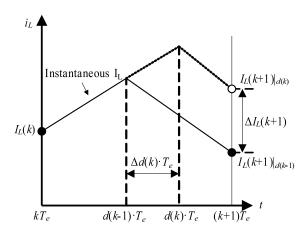

Le langage VHDL-AMS est utilisé pour construire le système de signaux mixtes. Il est possible d'évaluer les performances dynamiques et statiques durant la phase de conception de ASIC. C'est aussi la meilleure méthode pour estimer la performance des commandes avant l'implémentation actuelle sur FPGA ou ASIC.