### Memory and performance issues in parallel multifrontal factorizations and triangular solutions with sparse right-hand sides

François-Henry Rouet

#### ▶ To cite this version:

François-Henry Rouet. Memory and performance issues in parallel multifrontal factorizations and triangular solutions with sparse right-hand sides. Distributed, Parallel, and Cluster Computing [cs.DC]. Institut National Polytechnique de Toulouse - INPT, 2012. English. NNT: 2012INPT0070. tel-00785748v2

### HAL Id: tel-00785748 https://theses.hal.science/tel-00785748v2

Submitted on 10 Nov 2023

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Université de Toulouse

# THÈSE

En vue de l'obtention du

### DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

**Délivré par :** L'Institut National Polytechnique de Toulouse (INP Toulouse)

#### Présentée et soutenue par :

François-Henry Rouet

Le 17 Octobre 2012

Titre :

Memory and performance issues in parallel multifrontal factorizations and triangular solutions with sparse right-hand sides

Problèmes de mémoire et de performance de la factorisation multifrontale parallèle et de la résolution triangulaire à seconds membres creux

**Ecole doctorale et discipline ou spécialité :** ED MITT : Domaine STIC : Sûreté du logiciel et calcul haute performance

> Unité de recherche : IRIT - UMR 5505

**Directeurs de Thèse :** Patrick Amestoy (INPT-ENSEEIHT-IRIT) Alfredo Buttari (CNRS-IRIT)

Rapporteurs : Esmond Ng (Lawrence Berkeley National Laboratory) Sivan Toledo (Tel-Aviv University)

#### Autres membres du jury :

Iain Duff (Rutherford Appleton Laboratory) François Pellegrini (Laboratoire Bordelais de Recherche en Informatique)

## Résumé

Nous nous intéressons à la résolution de systèmes linéaires creux de très grande taille sur des machines parallèles. Dans ce contexte, la mémoire est un facteur qui limite voire empêche souvent l'utilisation de solveurs directs, notamment ceux basés sur la méthode multifrontale. Cette étude se concentre sur les problèmes de mémoire et de performance des deux phases des méthodes directes les plus coûteuses en mémoire et en temps : la factorisation numérique et la résolution triangulaire. Dans une première partie nous nous intéressons à la phase de résolution à seconds membres creux, puis, dans une seconde partie, nous nous intéressons à la scalabilité mémoire de la factorisation multifrontale.

La première partie de cette étude se concentre sur la résolution triangulaire à seconds membres creux, qui apparaissent dans de nombreuses applications. En particulier, nous nous intéressons au calcul d'entrées de l'inverse d'une matrice creuse, où les seconds membres et les vecteurs solutions sont tous deux creux. Nous présentons d'abord plusieurs schémas de stockage qui permettent de réduire significativement l'espace mémoire utilisé lors de la résolution, dans le cadre d'exécutions séquentielles et parallèles. Nous montrons ensuite que la façon dont les seconds membres sont regroupés peut fortement influencer la performance et nous considérons deux cadres différents : le cas hors-mémoire (*out-ofcore*) où le but est de réduire le nombre d'accès aux facteurs stockés sur disque, et le cas en mémoire (*in-core*) où le but est de réduire le nombre d'opérations. Finalement, nous montrons comment améliorer le parallélisme.

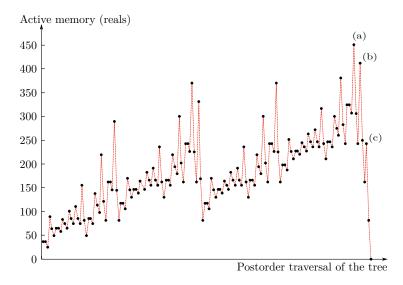

Dans la seconde partie, nous nous intéressons à la factorisation multifrontale parallèle. Nous montrons tout d'abord que contrôler la mémoire active spécifique à la méthode multifrontale est crucial, et que les techniques de répartition (mapping) classiques ne peuvent fournir une bonne scalabilité mémoire : le coût mémoire de la factorisation augmente fortement avec le nombre de processeurs. Nous proposons une classe d'algorithmes de répartition et d'ordonnancement conscients de la mémoire (memory-aware) qui cherchent à maximiser la performance tout en respectant une contrainte mémoire fournie par l'utilisateur. Ces techniques ont révélé des problèmes de performances dans certains des noyaux parallèles denses utilisés à chaque étape de la factorisation, et nous avons proposé plusieurs améliorations algorithmiques.

Les idées présentées tout au long de cette étude ont été implantées dans le solveur MUMPS (Solveur MUltifrontal Massivement Parallèle) et expérimentées sur des matrices de grande taille (plusieurs dizaines de millions d'inconnues) et sur des machines massivement parallèles (jusqu'à quelques milliers de coeurs). Elles ont permis d'améliorer les performances et la robustesse du code et seront disponibles dans une prochaine version. Certaines des idées présentées dans la première partie ont également été implantées dans le solveur PDSLin (solveur linéaire hybride basé sur une méthode de complément de Schur).

**Mots-clés :** matrices creuses, méthodes directes de résolution de systèmes linéaires, méthode multifrontale, graphes et hypergraphes, calcul haute performance, calcul parallèle, ordonnancement.

### Abstract

We consider the solution of very large sparse systems of linear equations on parallel architectures. In this context, memory is often a bottleneck that prevents or limits the use of direct solvers, especially those based on the multifrontal method. This work focuses on memory and performance issues of the two memory and computationally intensive phases of direct methods, namely, the numerical factorization and the solution phase. In the first part we consider the solution phase with sparse right-hand sides, and in the second part we consider the memory scalability of the multifrontal factorization.

In the first part, we focus on the triangular solution phase with multiple sparse righthand sides, that appear in numerous applications. We especially emphasize the computation of entries of the inverse, where both the right-hand sides and the solution are sparse. We first present several storage schemes that enable a significant compression of the solution space, both in a sequential and a parallel context. We then show that the way the right-hand sides are partitioned into blocks strongly influences the performance and we consider two different settings: the out-of-core case, where the aim is to reduce the number of accesses to the factors, that are stored on disk, and the in-core case, where the aim is to reduce the computational cost. Finally, we show how to enhance the parallel efficiency.

In the second part, we consider the parallel multifrontal factorization. We show that controlling the active memory specific to the multifrontal method is critical, and that commonly used mapping techniques usually fail to do so: they cannot achieve a high memory scalability, i.e., they dramatically increase the amount of memory needed by the factorization when the number of processors increases. We propose a class of memoryaware mapping and scheduling algorithms that aim at maximizing performance while enforcing a user-given memory constraint and provide robust memory estimates before the factorization. These techniques have raised performance issues in the parallel dense kernels used at each step of the factorization, and we have proposed some algorithmic improvements.

The ideas presented throughout this study have been implemented within the MUMPS (MUltifrontal Massively Parallel Solver) solver and experimented on large matrices (up to a few tens of millions unknowns) and massively parallel architectures (up to a few thousand cores). They have demonstrated to improve the performance and the robustness of the code, and will be available in a future release. Some of the ideas presented in the first part have also been implemented within the PDSLin (Parallel Domain decomposition Schur complement based Linear solver) package.

**Keywords:** sparse matrices, direct methods for linear systems, multifrontal method, graphs and hypergraphs, high-performance computing, parallel computing, scheduling.

# Acknowledgements

First of all, I would like to express my sincere gratitude to my advisors, Patrick Amestoy and Alfredo Buttari, as well as Jean-Yves L'Excellent and Bora Uçar who followed my work very closely. Thank you for encouraging and guiding my research, and for the tremendous amount of work that you put into this thesis. Collaborating with people like you is priceless for a student, and it was a privilege for me to work and learn from you. Again, *merci*!

I am grateful to all the people with whom I have collaborated during these three years. Firstly, I want to thank Abdou Guermouche and Emmanuel Agullo who revealed some of the magic behind scheduling algorithms. I want to thank Iain Duff for his help on many aspects of my work and for perfecting my English. I am also grateful to Sherry Li and Esmond Ng for working with me and hosting me twice at the Berkeley Lab. I also thank Ichitaro Yamazaki, Laurent Bouchet, Kamer Kaya, Yves Robert, Erik Boman, Siva Rajamanickam, and Nicolas Renon.

I would like to thank the referees of this dissertation, Esmond Ng and Sivan Toledo, for reviewing and commenting the manuscript, and for travelling overseas to attend the defense. I also thank the other members of the committee, Iain Duff and François Pellegrini.

I certainly owe many thanks to the people who populated my work environment, starting with the young folks, especially my office mates Clément Climoune Weisbecker, Mohamed Zen Zenadi and Florent La Flop Lopez, as well as Gaëtan La Gat André. Thank you for your support, you never-failing good humor and the (countless...) games of Blobby Volley and foosball! Many thanks to Guillaume La Josse Joslin and Mohamed La Wiss Sid-Lakhdar as well. I am grateful to many people at the IRIT Lab, including Chiara Puglisi, Daniel Ruiz, Serge Gratton, and the invaluable Sylvie Armengaud and Sylvie Eichen. I also thank many of my friends in Toulouse and elsewhere for their support; in a random order: Geoffroy, Thibault, Andra, Vivian, Benoît, Robert, Fred, Paul, David, Pascal, Erwan, Jean-Christophe and many others...

Finally, I am deeply grateful to my parents, my sister and my brother for their support during all these years of studies, that may have seem long to them!

# Contents

| R | Résumé ii            |                                                                                               |     |  |  |  |  |  |  |

|---|----------------------|-----------------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|

| A | bstra                | act                                                                                           |     |  |  |  |  |  |  |

| A | ckno                 | wledgements                                                                                   | v   |  |  |  |  |  |  |

| 1 | General introduction |                                                                                               |     |  |  |  |  |  |  |

|   | 1.1                  | General context                                                                               |     |  |  |  |  |  |  |

|   |                      | 1.1.1 Sparse linear systems and direct methods                                                |     |  |  |  |  |  |  |

|   |                      | 1.1.2 Distributed-memory sparse direct solvers                                                |     |  |  |  |  |  |  |

|   | 1.2                  | Background on multifrontal methods                                                            |     |  |  |  |  |  |  |

|   |                      | 1.2.1 The symmetric case                                                                      |     |  |  |  |  |  |  |

|   |                      | 1.2.2 The general case                                                                        |     |  |  |  |  |  |  |

|   |                      | 1.2.3 The three phases                                                                        |     |  |  |  |  |  |  |

|   | 1.3                  | Experimental environment                                                                      | 1   |  |  |  |  |  |  |

|   |                      | 1.3.1 The MUMPS solver                                                                        | 1   |  |  |  |  |  |  |

|   |                      | 1.3.2 The PDSLin solver                                                                       | 1   |  |  |  |  |  |  |

|   |                      | 1.3.3 Test problems                                                                           | ]   |  |  |  |  |  |  |

|   |                      | 1.3.4 Computational systems                                                                   | 1   |  |  |  |  |  |  |

| Ι | me                   | ution phase with sparse right-hand sides:<br>mory and performance issues                      | 1   |  |  |  |  |  |  |

| 2 |                      | roduction                                                                                     | 1   |  |  |  |  |  |  |

|   | 2.1                  | 2.1 Applications and motivations                                                              |     |  |  |  |  |  |  |

|   |                      | 2.1.1 Applications with sparse right-hand sides and/or sparse solution .                      | 1   |  |  |  |  |  |  |

|   |                      | 2.1.2 Applications involving the computation of inverse entries                               | 2   |  |  |  |  |  |  |

|   | 2.2                  | Exploiting sparsity in the solution phase                                                     | 2   |  |  |  |  |  |  |

|   |                      | 2.2.1 General case                                                                            | 2   |  |  |  |  |  |  |

|   |                      | 2.2.2 Application to the computation of inverse entries                                       | 2   |  |  |  |  |  |  |

|   | 2.3                  | Contributions                                                                                 | 2   |  |  |  |  |  |  |

|   | 2.4                  | The multifrontal solution phase                                                               | 2   |  |  |  |  |  |  |

|   |                      | 2.4.1 The forward phase                                                                       | 2   |  |  |  |  |  |  |

|   |                      | 2.4.2 The backward phase                                                                      | ę   |  |  |  |  |  |  |

| 3 | Cor                  | mpressing the solution space                                                                  | 3   |  |  |  |  |  |  |

|   | 3.1                  | Dense storage scheme                                                                          | 3   |  |  |  |  |  |  |

|   |                      |                                                                                               | - 3 |  |  |  |  |  |  |

|   |                      | 3.1.1       Idea       Idea       Idea         3.1.2       Construction       Idea       Idea | 3   |  |  |  |  |  |  |

|   | 3.2 | A stor | age scheme based on a union of paths                                                                                                    | 3 |

|---|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------|---|

|   |     | 3.2.1  | Idea                                                                                                                                    | 3 |

|   |     | 3.2.2  | Construction                                                                                                                            | ) |

|   | 3.3 | A stor | age scheme based on the height of the elimination tree 43                                                                               | 3 |

|   |     | 3.3.1  | Assumptions                                                                                                                             | 3 |

|   |     | 3.3.2  | Construction                                                                                                                            | 3 |

|   | 3.4 | Exper  | iments                                                                                                                                  | 5 |

|   |     | 3.4.1  | Dense right-hand sides: compression and locality effects 4                                                                              | 5 |

|   |     | 3.4.2  | Sparse right-hand sides                                                                                                                 | 6 |

|   |     |        |                                                                                                                                         |   |

| 4 |     |        | g accesses to the factors in an out-of-core execution 49                                                                                |   |

|   | 4.1 |        | -partitioning problem                                                                                                                   |   |

|   |     | 4.1.1  | Formulation                                                                                                                             |   |

|   |     | 4.1.2  | A lower bound                                                                                                                           |   |

|   |     | 4.1.3  | NP-completeness                                                                                                                         |   |

|   |     | 4.1.4  | The off-diagonal case                                                                                                                   | 4 |

|   | 4.2 | Heuris | tics                                                                                                                                    | 5 |

|   |     | 4.2.1  | A partitioning based on a postorder of the tree                                                                                         | 5 |

|   |     | 4.2.2  | A matching algorithm                                                                                                                    | 6 |

|   | 4.3 | Hyper  | graph models                                                                                                                            | 3 |

|   |     | 4.3.1  | The hypergraph partitioning problem                                                                                                     | 3 |

|   |     | 4.3.2  | Hypergraph model diagonal case                                                                                                          | 9 |

|   |     | 4.3.3  | Hypergraph model general case                                                                                                           | ) |

|   | 4.4 | Exper  | iments                                                                                                                                  | 1 |

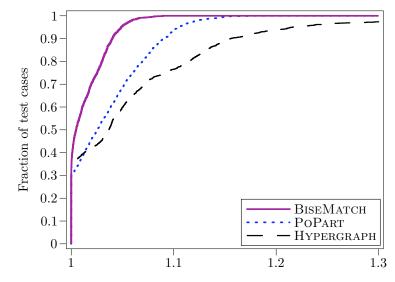

|   |     | 4.4.1  | Assessing the heuristics                                                                                                                | 2 |

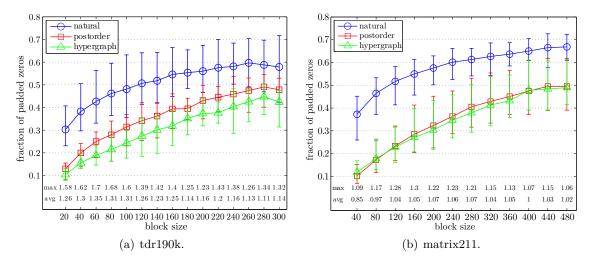

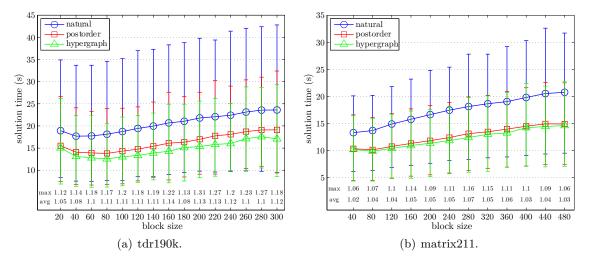

|   |     | 4.4.2  | Large-scale experiments diagonal entries                                                                                                | 3 |

|   |     | 4.4.3  | Large-scale experiments off-diagonal entries                                                                                            | 4 |

| _ |     |        |                                                                                                                                         |   |

| 5 |     |        | g computational cost in an in-core execution 6'                                                                                         |   |

|   | 5.1 |        | ming operations on a union of paths                                                                                                     |   |

|   |     | 5.1.1  | A partitioning based on a postorder of the tree                                                                                         |   |

|   |     | 5.1.2  | Hypergraph model                                                                                                                        |   |

|   |     | 5.1.3  | Experiments                                                                                                                             |   |

|   | 5.2 | -      | ting sparsity within blocks                                                                                                             |   |

|   |     | 5.2.1  | Core idea and construction                                                                                                              |   |

|   |     | 5.2.2  | Experiments                                                                                                                             | 3 |

| 6 | Enh | ancino | g parallelism 79                                                                                                                        | a |

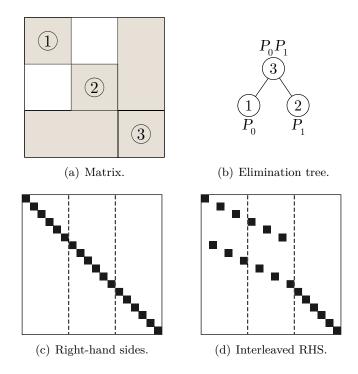

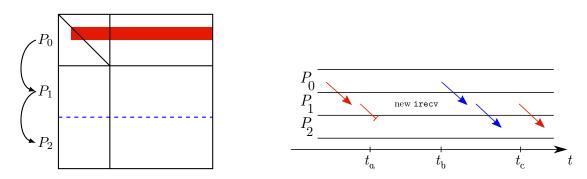

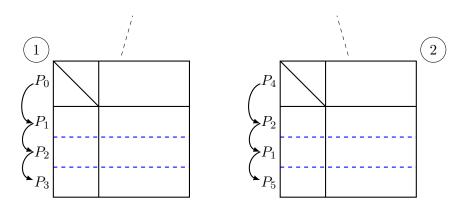

| Ŭ | 6.1 |        | sing multiple right-hand sides in a parallel context                                                                                    |   |

|   | 6.2 |        | ining tree parallelism and tree pruning                                                                                                 |   |

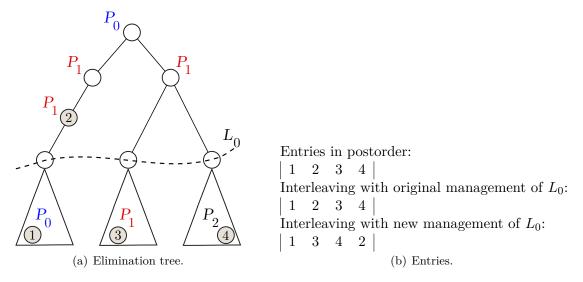

|   | 0.4 | 6.2.1  | An interleaving strategy                                                                                                                |   |

|   |     | 6.2.1  | Combining interleaving and sparsity within blocks                                                                                       |   |

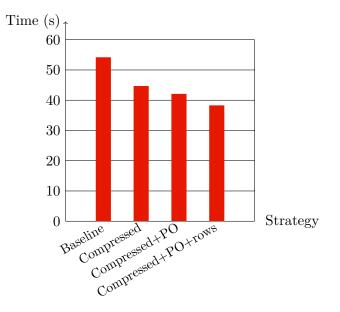

|   | 6.3 |        | iments $\ldots$                                        |   |

|   | 0.0 | 6.3.1  | Influence of the different strategies                                                                                                   |   |

|   |     | 6.3.2  | Influence of the block size                                                                                                             |   |

|   |     | 0.3.2  | $ \qquad \qquad$ | ) |

|    |      | ntrolling active memory in the<br>allel multifrontal factorization | 87  |

|----|------|--------------------------------------------------------------------|-----|

| 7  | Intr | coduction                                                          | 89  |

|    | 7.1  | The parallel multifrontal factorization                            | 90  |

|    |      | 7.1.1 An asynchronous scheme                                       | 90  |

|    |      | 7.1.2 Common mapping techniques                                    | 91  |

|    |      | 7.1.3 Mapping and scheduling techniques in MUMPS                   | 96  |

|    | 7.2  | Controlling the active memory                                      | 98  |

|    |      | 7.2.1 The sequential case                                          | 98  |

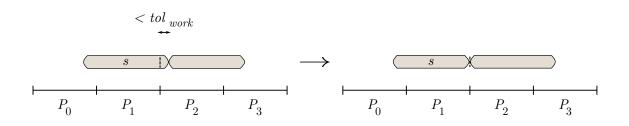

|    |      | 7.2.2 The parallel case                                            | 102 |

|    |      | 7.2.3 Relation to the tree pebble game                             | 105 |

| 8  | Mei  | mory scalability issues                                            | 109 |

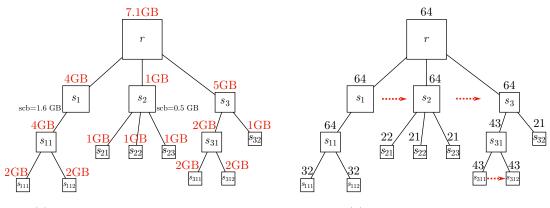

|    | 8.1  | A simple example                                                   | 109 |

|    | 8.2  | Theoretical study on regular grids                                 | 111 |

|    |      | 8.2.1 Main result                                                  | 111 |

|    |      | 8.2.2 Proof context                                                | 112 |

|    |      | 8.2.3 Proof computation of the memory efficiency                   | 116 |

|    | 8.3  | Experimental results                                               | 124 |

| 9  | A c  | lass of memory-aware algorithms                                    | 127 |

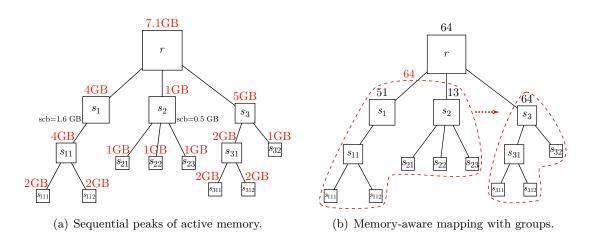

|    | 9.1  | A simple memory-aware mapping                                      | 127 |

|    |      | 9.1.1 Idea and algorithm                                           | 127 |

|    |      | 9.1.2 Example                                                      | 129 |

|    |      | 9.1.3 Difficulties                                                 | 131 |

|    | 9.2  | Detecting groups of siblings                                       | 132 |

|    |      | 9.2.1 A motivating example                                         | 132 |

|    |      | 9.2.2 Algorithm                                                    | 133 |

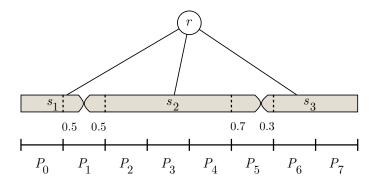

|    | 9.3  | Decimal mapping, granularities and relaxations                     | 135 |

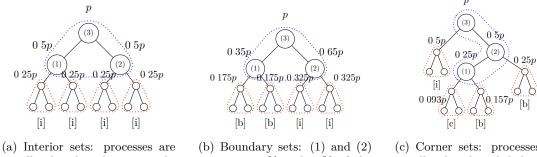

|    |      | 9.3.1 Handling decimal number of processes                         | 135 |

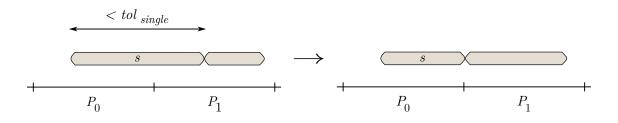

|    |      | 9.3.2 Granularities                                                | 137 |

|    |      | 9.3.3 Other relaxations                                            | 138 |

| 10 | Per  | formance aspects                                                   | 141 |

|    |      | Enforcing serializations                                           | 141 |

|    |      | 10.1.1 Simple case                                                 | 141 |

|    |      | 10.1.2 Group dependencies                                          | 142 |

|    | 10.2 | Communication patterns in parallel nodes                           | 143 |

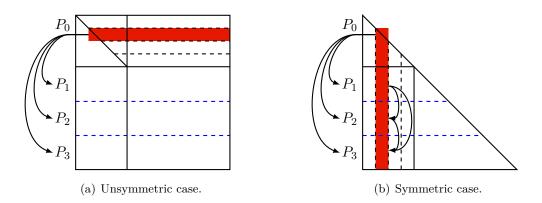

|    |      | 10.2.1 Baseline scheme                                             | 143 |

|    |      | 10.2.2 A tree-based asynchronous broadcast                         | 146 |

|    |      | 10.2.3 Implementation issues                                       | 149 |

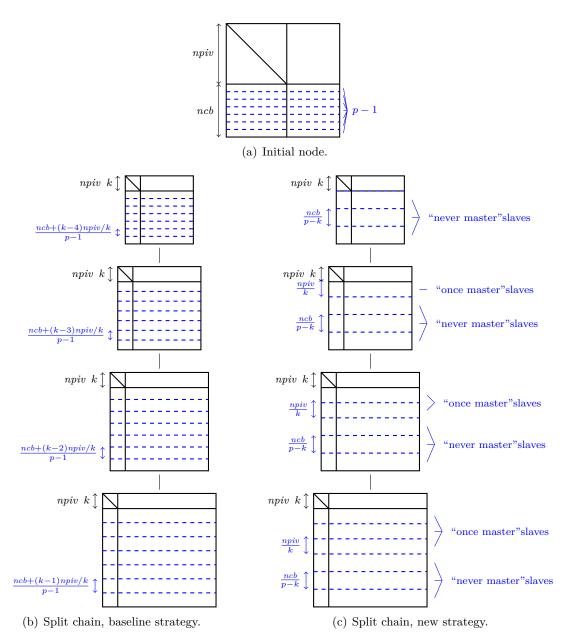

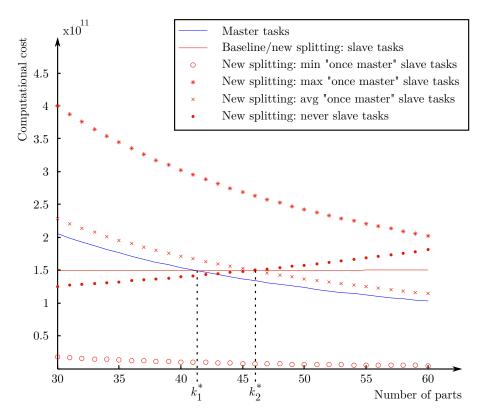

|    | 10.3 | Splitting nodes                                                    | 152 |

|    | 10.0 | 10.3.1 Idea and strategies                                         | 152 |

|    |      | 10.3.2 Performance models                                          | 155 |

| 11 | Exn  | periments on large problems                                        | 159 |

|    |      | Experimental settings                                              | 159 |

|    |      | Assessing the different strategies                                 | 160 |

|    |      | Towards very large problems                                        | 164 |

| 12 | General conclusion                |       |  |  |  |  |

|----|-----------------------------------|-------|--|--|--|--|

|    | 12.1 General results              | . 165 |  |  |  |  |

|    | 12.2 Software improvements        | . 166 |  |  |  |  |

|    | 12.3 Perspectives and future work | . 167 |  |  |  |  |

| Α  | Publications                      | 169   |  |  |  |  |

|    | A.1 Submitted publications        | . 169 |  |  |  |  |

|    | A.2 Articles                      | . 169 |  |  |  |  |

|    | A.3 Proceedings                   | . 169 |  |  |  |  |

|    | A.4 Conferences                   | . 169 |  |  |  |  |

|    | A.5 Reports                       | . 170 |  |  |  |  |

| Bi | bliography                        | 171   |  |  |  |  |

### Chapter 1

### General introduction

#### **1.1** General context

#### 1.1.1 Sparse linear systems and direct methods

We consider the solution of linear systems of the form

Ax = b

where A is a large square sparse matrix, b is the right-hand side (possibly with several columns) and x is the unknown. In Wilkinson's definition, a sparse matrix is any matrix with enough zeros that it pays to take advantage of them . Sparse matrices appear in numerous scientific applications (mechanics, fluid dynamics, quantum chemistry, data analysis, optimization...). In physical applications, sparsity is often due to the fact that the matrix represents loosely coupled data or a discretized physical domain where a limited-range interaction takes place; this implies that some unknowns of the linear system do not interact with each other, resulting in structural zeros in the matrix. Solving sparse linear systems is often a keystone in numerical simulations; nowadays, sparse linear systems from practical applications commonly have millions of unknowns, sometimes billions.

There are two main classes of methods for the solution of sparse linear systems: direct methods, that are based on a factorization of A (e.g., LU or QR), and iterative methods, that build a sequence of iterates that hopefully converges to the solution. Direct methods are acknowledged for their numerical stability but often have large memory and computational requirements, while iterative methods are less memory demanding and often faster but less robust in general; the choice of a method is usually complicated since it depends on many parameters such as the properties of the matrix and the application. Hybrid methods, that aim at combining the strengths of both classes, are increasingly popular.

In this dissertation, we focus on direct methods that rely on Gaussian elimination, i.e., algorithms that compute a factorization of the matrix A under the form LU (in the general case),  $LDL^T$  (in the symmetric case) or  $LL^T$  (in the symmetric positive definite case, *Cholesky factorization*). We provide in Algorithm 1.1 a simplistic sketch of LUfactorization in the dense case, i.e., the nonzero pattern of the matrix is not taken into account. We ignore pivoting and numerical issues as it is not our point in this section and we assume that any entry found on the diagonal is nonzero. Each step *i* in the factorization consists of *eliminating* a pivot (the diagonal entry  $a_{ii}$ ), which yields a new column in Land a new row in U, and in modifying the trailing part of the matrix by performing a rankone update. These two operations are denoted by **Factor** and **Update** in the algorithm. The approach presented in Algorithm 1.1 is a *right-looking* approach, which means that as soon as a column of the L factors is computed (**Factor**), an update of the trailing part (columns on the right of column i) is performed (**Update**). The computations can be reorganized to obtain a *left-looking* approach, in which, at every step, **Update** is performed before **Factor**; in this case, **Update** is performed using the columns that are already computed, that lie on the left of column i.

| Algorithm 1.1 Dense $LU$ factorization.                                                                                                                                            |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| /* Input: a square matrix A of size n; $A = [a_{ij}]_{i=1:n,j=1:n}$                                                                                                                | */ |

| /* <b>Output:</b> A is replaced with its $LU$ factors                                                                                                                              | */ |

| 1: for $k = 1$ to $n$ do<br>2: Factor: $a_{k+1:n k} = \frac{a_{k+1:n,k}}{a_{kk}}$<br>3: Update: $a_{k+1:n k+1:n} = a_{k+1:n k+1:n} = a_{k+1:n k} \times a_{k k+1:n}$<br>4: end for |    |

In *sparse* direct methods, a key issue is the *ll-in* phenomenon; the **Update** operation can be written as

$$i j > k a_{ij} \quad a_{ij} \quad a_{ik} \quad a_{kj}$$

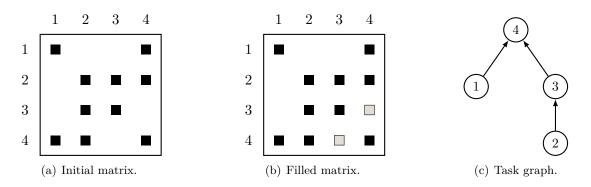

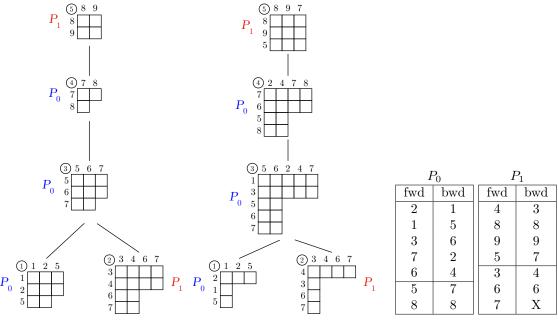

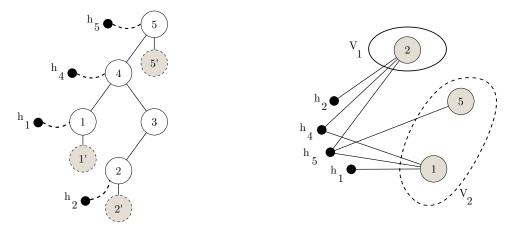

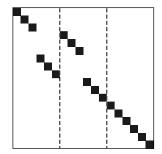

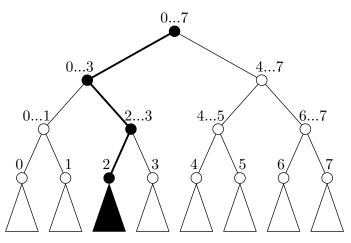

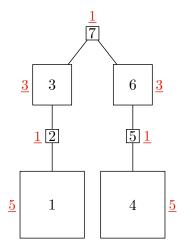

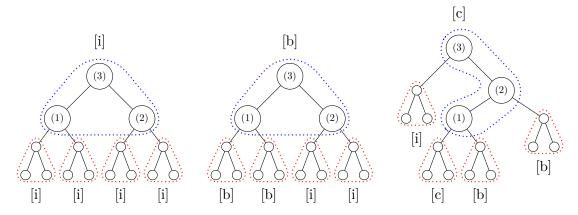

If  $a_{ij} = 0$  but  $a_{ik} = 0$  and  $a_{kj} = 0$ , then a zero entry in the initial matrix becomes nonzero in the factors; in the end, the nonzero pattern of the factors is a superset of the nonzero pattern of the initial matrix. We illustrate this phenomenon in Figure 1.1, where we show the pattern of an initial matrix (a) and the pattern of its factors (b); elements (4–3) and (3–4) are created when eliminating the second pivot. Sparse direct methods exploit the nonzero pattern of the matrix to compute a graph that represents the nonzero structure of the factors and is used as a task graph during the factorization.

We give a formal presentation of this idea in the context of the multifrontal method in Section 1.2. Here, we provide a very simple example that we use to highlight the different variants of sparse Gaussian elimination. Consider the example in Figure 1.1. One can see that since  $a_{12} = 0$  and  $a_{13} = 0$ , the **Update** operation performed when eliminating the first pivot  $(a_{11})$  does not modify columns 2 and 3. Symmetrically, since  $a_{21} = 0$  and  $a_{31} = 0$ , the elimination of  $a_{11}$  does not modify rows 2 and 3; therefore, one is free to eliminate pivots  $a_{22}$  and  $a_{33}$  before or after pivot  $a_{11}$ , without any incidence on the result. On the contrary, the second pivot must be eliminated before the third pivot (because  $a_{23} = 0$  and  $a_{32} = 0$ ). Similarly, the fourth pivot must be eliminated after all the other variables. This yields a dependency graph that we show in Figure 1.1(c).

Figure 1.1: Nonzero pattern of a sparse matrix (a), nonzero pattern of its factors where the *ll-in entries* are shaded (b), and task graph of the factorization (c).

Two main classes of sparse direct methods exist. Supernodal methods are the natural extension of the left-looking and right-looking methods to sparse matrices; at each node in the graph, some rows and columns of the factors are computed and stored, and are used at some other nodes in the graph to perform updates. In a right-looking approach, once the rows and columns of the factors associated with a given node are computed, they are immediately used at some other nodes in the graph to perform some updates; in the leftlooking approach, this is the opposite: the updates are delayed as much as possible. From this perspective, the *multifrontal method* can be considered as a variant of the right-looking approach where every node has a temporary zone where partial updates are computed; the updates associated with a node are carried throughout the task graph and accumulated with some partial updates before they reach their final destination. We illustrate this in the example in Figure 1.1. Consider the elimination of pivot 2. In the right-looking method, once pivot 2 is eliminated, updates are applied to the rows and columns associated with nodes 3 and 4. In particular, at node 4, the update  $a_{44}$  $a_{44}$  $a_{42}$   $a_{24}$  is applied. In the multifrontal method, the partial update  $a_{42} a_{24}$  is passed from node 2 to node 3. Node 3 adds this partial update to its own partial update  $(a_{43} a_{34})$  and passes the whole update to node 4. The drawback of the method is that some temporary memory has to be used to store and accumulate partial updates; however in practice the method delivers high performance because it allows for large matrix-matrix operations and limits the use of indirect addressing. The notion of *aggregates* was introduced in right-looking methods to capture this advantage of the multifrontal methods. In this dissertation, we focus on the multifrontal method (although many ideas can be applied to supernodal methods), that we describe in detail in the next section.

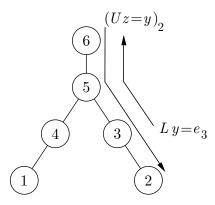

Once the factorization is completed, the solution x of the system is computed in two steps:

The forward elimination consists of solving Ly = b for y, where b is the right-hand side of the system.

The backward substitution consists of solving Ux = y, where x is the solution of the initial system.

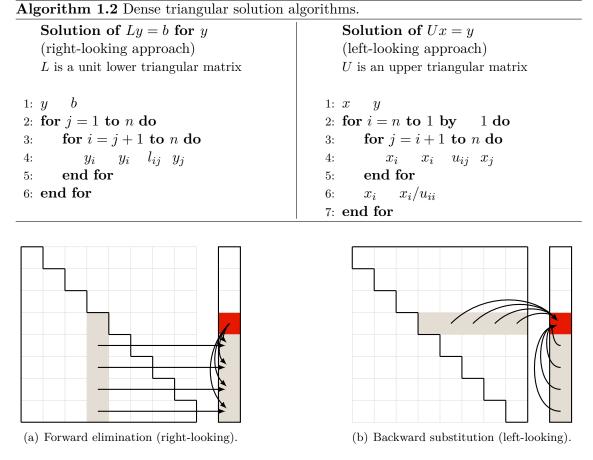

We describe the two steps of triangular solution in Algorithm 1.2 in the dense case and illustrate them in Figure 1.2. Note that we illustrate a right-looking approach for the forward elimination (i.e., at each step, the trailing part of the solution vector is updated), and a left-looking approach for the backward phase (i.e., each step begins with aggregating contributions from the components of the solution that are already computed); this corresponds to a natural storage scheme where the L and U factors are stored by columns and rows respectively. We describe in detail the multifrontal triangular solution phase in Chapter 2.

#### 1.1.2 Distributed-memory sparse direct solvers

A large part of this thesis is dedicated to the study of sparse direct methods in a parallel context. We are particularly interested in distributed-memory architectures, in which each one of the *processes* that execute a given code has its own memory address space. Processes need to explicitly communicate using messages in order to exchange data; MPI is by far the most widespread library for doing so. Note than since *processors* now have several cores and can run several *processes* at the same time, we try to use these two terms accurately; in particular, when describing parallel algorithms, the relevant metric will most of the time be the number of *processes*.

Figure 1.2: Dense triangular solution algorithms.

Parallel, distributed-memory sparse direct methods consist of distributing the abovementioned task graph over a set of processes. The second part of this thesis is dedicated to these aspects. Among publicly available and active distributed-memory sparse direct solvers, one can cite PasTiX [52] and SuperLU\_DIST [63], that implement different variants of supernodal methods, and MUMPS [9, 11], that implements a multifrontal method. We describe MUMPS in detail in Section 1.3.1.

#### **1.2** Background on multifrontal methods

The *multifrontal method* by Duff & Reid [32, 33] heavily relies on the notion of *elimination* tree. The elimination tree was introduced by Schreiber [82] for symmetric matrices. The unsymmetric case is much more complex; different structures that represent the elimination process and various strategies appear in the literature. The definition of elimination trees for the unsymmetric case is recently introduced by Eisenstat & Liu [34, 36]. Firstly, we describe the symmetric case in detail, then we briefly review the unsymmetric case.

#### 1.2.1 The symmetric case

We start with the symmetric positive definite case; let A be a square symmetric positive definite matrix of order n, and L the Cholesky factor of A ( $A = L L^{T}$ ). Firstly, we define the *adjacency graph* of A:

De nition 1.1 - Adjacency graph.

The adjacency graph of A is a graph G(A) = (V E) with n vertices such that:

There is a vertex  $v_j = V$  for each row (or column) j of A.

There is an edge  $v_i v_j$  E if and only if  $a_{ij} = 0$ .

Similarly, the *lled graph* of A is the adjacency graph G(F) of  $F = L + L^T$ , the *lled matrix* of A. Note that, because of the fill-in entries, the graph of A is a subgraph of the filled graph (with the same vertices).

Many equivalent definitions exist for the (symmetric) elimination tree; we recommend the survey by Liu [70] where many definitions, results and construction algorithms are provided. The simplest definition is probably the following:

**De nition 1.2** - Elimination tree (symmetric case); from [70]. The elimination tree of A is a graph with n vertices such that p is the parent of a node j if and only if

$$p = \min i > j : l_{ij} = 0$$

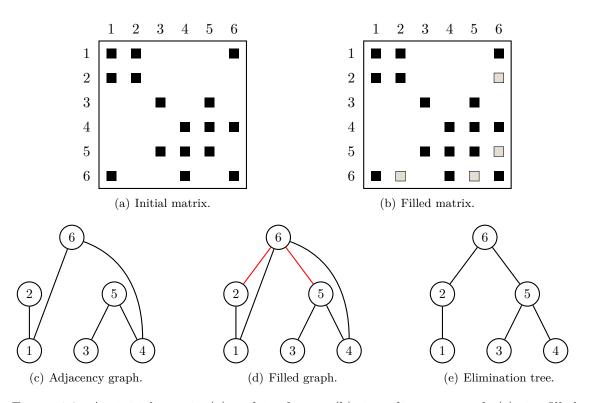

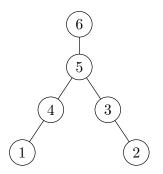

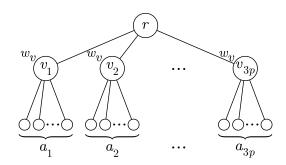

If A is irreducible, this structure is a tree; otherwise it is a forest. Throughout this study, we will always assume that A is irreducible, unless stated otherwise. Another definition is that the elimination tree is the transitive reduction of the filled graph<sup>1</sup>. We illustrate the notions of adjacency graph, filled graph and elimination tree in Figure 1.3.

Figure 1.3: An initial matrix (a) and its factors (b), its adjacency graph (c), its filled graph (d), and its elimination tree (e).

<sup>&</sup>lt;sup>1</sup>More precisely, it is the transitive reduction of the *directed filled graph*, which is the same graph as the lled graph, except that every edge  $\{v_i, v_j\}$  with i < j is directed from i to j.

The multifrontal method is based on the elimination tree. We strongly recommend the survey by Liu [71] that provides a comprehensive and instructive presentation of the multifrontal method. Here we recall the main ingredients that will be useful in the following (we follow the proof and the notation from the above-mentioned survey). We begin with two fundamental results:

**Theorem 1.1** - [71, Theorem 3.1]. If node k is a descendant of j in the elimination tree, then the structure of the vector  $(l_{jk} \quad l_{nk})^T$  is contained in the structure of  $(l_{jj} \quad l_{nj})^T$ .

**Theorem 1.2** - [71, Theorem 3.2]. If  $l_{jk} = 0$  and k < j, then the node k is a descendant of j in the elimination tree.

Consider the *j*-th column of the *L* factor; let  $j i_1 i_r$  be the row indices of the nonzeros in  $L_{j:n j}$  and  $\mathcal{T}(j)$  the subtree rooted at *j*. In the multifrontal method, every node *j* in the elimination tree is associated with a dense *frontal matrix*  $F_j$ , defined as

$$F_{j} = \begin{array}{cccc} a_{jj} & a_{ji_{1}} & a_{ji_{r}} \\ a_{i_{1}j} & & \\ \vdots & 0 & \\ a_{i_{r}j} & & \end{array} + \overline{U}_{j} \text{ with } \overline{U}_{j} = \sum_{\substack{k \in \mathcal{T}(j) \ j}} \begin{array}{c} l_{jk} \\ l_{i1 \ k} \\ \vdots \\ l_{irk} \end{array} \quad l_{jk} \quad l_{i1 \ k} \\ \vdots \\ l_{i_{r}k} \end{array}$$

The first term in the two-term sum that defines  $F_j$  is called the *arrowhead matrix* and consists of nonzero elements of the initial matrix. Note that the entries that correspond to fill-in entries are zeros. The second term is the *subtree update matrix* and is the sum of all the rank-one updates from the columns that are descendant of j in the tree. It follows from Theorem 1.1 and Theorem 1.2 that when  $F_j$  is computed, the first column (and the first row by symmetry) is fully updated; the variable j is said to be *fully-summed*. Therefore, one can apply a step of Gaussian elimination to  $F_j$  to eliminate the j-th pivot, yielding the factor column  $L_{j:n j}$ :

$$F_{j} = \begin{array}{ccccccccc} l_{jj} & 0 & & \\ l_{i_{1}j} & & 1 & 0 & l_{jj} & l_{i_{1}j} & & l_{i_{r}j} \\ \vdots & I & 0 & U_{j} & 0 & I \\ l_{i_{r}j} & & & \end{array}$$

$U_j$ , the  $r \times r$  Schur complement that results from the step of elimination, is also called the *contribution block* associated with  $F_j$ . The following result holds:

**Theorem 1.3** - [71, Theorem 3.3].

$$U_j = \sum_{k \in \mathcal{T}(j)} \begin{array}{c} l_{i1\ k} \\ \vdots \\ l_{i_rk} \end{array} \qquad l_{i1\ k} \qquad l_{i_rk}$$

This shows that once a step of elimination is applied to  $F_j$ ,  $U_j$ , the (2,2) block of  $F_j$ contains the sum of all the rank-one updates of the subtree rooted at j; those are the updates that are needed to update the subsequent columns. Therefore, the frontal matrix  $F_j$  contains all the information needed for the subsequent steps of the factorization, and the information from the frontal matrices corresponding to descendants of j is no longer needed. This is what the following result states by showing how to compute a frontal matrix  $F_j$  using only the information coming from the children of j in the tree; denote  $s_{j1} \qquad s_{j\,nc_j}$  the children of j:

**Theorem 1.4** - [71, Theorem 4.1].

$$F_{j} = \begin{array}{cccc} a_{jj} & a_{ji_{1}} & & a_{ji_{r}} \\ a_{i_{1}j} & & & & \\ \vdots & & 0 & & & \\ a_{i_{r}j} & & & & U_{s_{j1}} & & & U_{s_{jnc_{j}}} \end{array}$$

The frontal matrix at a given node j is *assembled* (computed) by summing the arrowhead matrix with the contribution blocks from the children of j; note that this is not a regular sum, the contribution blocks have to be extended by introducing zero rows and columns to conform with the indices of  $F_j$ . The operator is referred to as the *extend-add* operator. Therefore, the multifrontal method consists of, at every node j in tree:

- 1. Assembling the nonzeros from the original matrix (the arrowhead matrix) together with the contribution blocks from the children nodes of j into the frontal matrix.

- 2. Eliminating the fully-summed variable j; this produces the j-th column in the factors and a Schur complement (the contribution block) that will be assembled into the parent node at a subsequent step in the factorization.

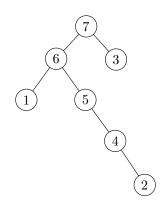

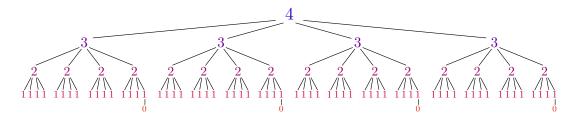

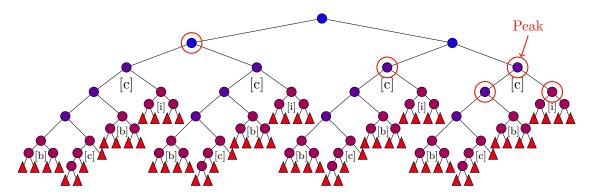

This process implies a *topological traversal* of the tree, i.e., a parent node must be processed after its children. In practice, a *postorder traversal* is used; a postordering of the tree is such that all the nodes in a given subtree are number consecutively. This allows the use of a stack mechanism to store the contribution blocks. We discuss in detail the choice of a postorder versus a topological traversal in Section 7.2.1.

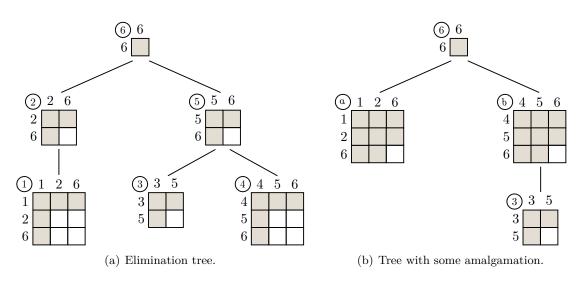

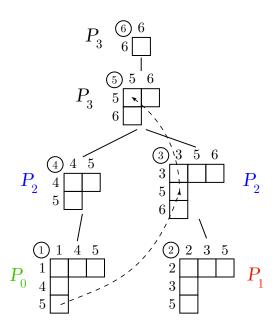

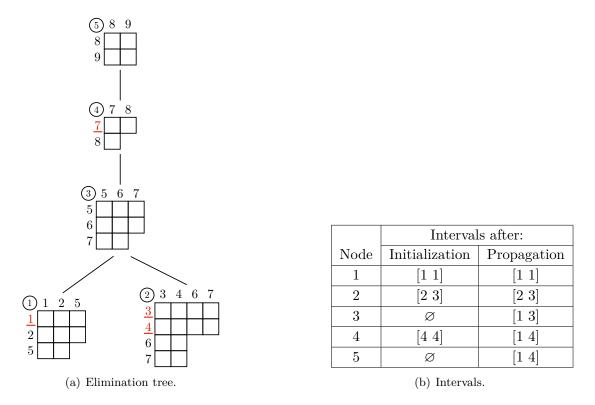

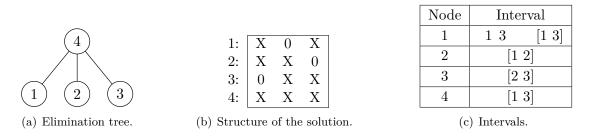

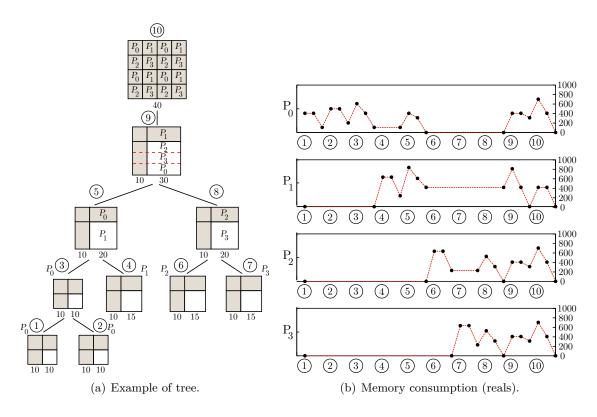

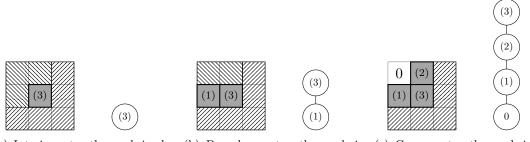

The elimination tree and the associated frontal matrices are often referred to as the *assembly tree* (although we will often use the generic term *elimination tree* in this thesis). We illustrate in Figure 1.4(a) the assembly tree of the matrix from Figure 1.3(a). Note that, when assembling node 5, the contribution block from 3 (a  $1 \times 1$  matrix) needs to be extended to a  $2 \times 2$  matrix (in practice, other techniques are used).

The use of *supernodes* is a major practical improvement to the multifrontal method; a supernode is a range of columns of the factors with the same lower diagonal nonzero structure. They correspond to nodes that form a clique in the filled graph and are connected to the same nodes. For example, in Figure 1.3(d), nodes 3 and 4, as well as nodes 1 and 2, form supernodes. The corresponding frontal matrices can be merged without introducing any fill-in in the factors; this is referred to as *no- ll* amalgamation. This yields the tree in Figure 1.4(b). The interest is that this enables the use of matrix-matrix dense kernels; each front has a  $2 \times 2$  block structure where several variables are eliminated at the same time, enabling the use of dense matrix-matrix kernels. The criterion for forming supernodes can be relaxed: columns whose structures are not exactly the same can be grouped together. This generates some fill-in but also provides more efficiency.

#### 1.2.2 The general case

Generalizing the elimination tree and the multifrontal method to the unsymmetric case is not straightforward. The difficulty is that the structure of the factors cannot be repre-

Figure 1.4: Elimination tree (a) and tree with some amalgamation (b) associated with the matrix in Figure 1.3(a), with the frontal matrices shown at each node. The shaded entries correspond to the factors and the empty entries correspond to contribution blocks.

sented using a tree. Indeed, the transitive reductions of the directed graphs of L and U are directed acyclic graphs (dags for short), that Gilbert & Liu call *elimination dags* [45]. These structures are for example used in the supernodal code SuperLU\_DIST.

In their initial approach, Duff & Reid choose to rely on the elimination tree of the symmetrized matrix  $A + A^T$  [33], and many codes, such as MUMPS, follow this idea. This works well for problems that are structurally symmetric or nearly so, but this can dramatically increase the memory and computational requirements for very unsymmetric problems (in the structural sense). Other structures and approaches exist. We recommend the survey by Pothen & Toledo [76, Section 5] and a discussion in one of Eisenstat & Liu's papers [35, Section 3]. Eisenstat & Liu define elimination trees for unsymmetric matrices as follows:

**De nition 1.3** - Elimination tree (general case); from [34].

The elimination tree of A is a graph with n vertices such that p is the parent of a node j if and only if

$$p = \min \quad i > j : i \stackrel{L}{=} j \stackrel{U}{=} i$$

where  $i \stackrel{L}{=} j$  (respectively  $i \stackrel{U}{=} j$ ) if and only there is a path from i to j in the directed graph of L (respectively U).

Then they show that the two following properties are incompatible [35, Section 3]:

- (a) The rows (respectively columns) of every frontal matrix  $F_k$  correspond to the rows i such that  $l_{ik} = 0$  (respectively, columns such that  $u_{kj} = 0$ ). Note that this means that frontal matrices are possibly rectangular.

- (b) Every update (contribution block) can be sent and assembled into a single frontal matrix.

In the usual approach where the elimination tree of the symmetrized matrix  $A + A^T$  is used, (b) is satisfied: the contribution block of a front is sent to its parent only. However (a) is violated because some fronts have nonzero entries in rows (respectively columns) whose entries in the factor part are zero. Amestoy & Puglisi suggested an approach where they remove on the fly, when a front is assembled, rows and columns that are structurally zero  $[12]^2$ ; property (a) is still not ensured but this allows to reduce the computational requirements and the effects are very interesting in practice.

The incompatibility between (a) and (b) shows that the unsymmetric elimination tree cannot be used as a dataflow graph since contribution blocks might have to be sent to multiple nodes, that can lie on different branches. Eisenstat & Liu propose an approach where the tree is used as a task graph and a dag, which is for instance a supergraph of the elimination tree, is used to enforce data dependencies. This idea appears in Gupta's work on the WSMP code [50] where he uses a variant of elimination dags as a task graph and others dags as dataflow graphs; similarly, the UMFPACK code by Davis [29] relies on the column elimination tree (elimination tree of the symmetric matrix  $A^T A$ ) as a task graph and some structures relying on biclique covers as dataflow graphs.

In this study, we always consider the symmetric elimination tree, i.e., the elimination tree of  $A + A^T$ . In the first part, where we address problems related to sparse right-hand sides, we heavily rely on the elimination tree as a representation of the structure of the factors; in the second part where we tackle memory scalability problems, we view the elimination more as a task graph. We believe that generalizing the ideas we present in this thesis to unsymmetric elimination trees is not straightforward (although probably feasible).

#### 1.2.3 The three phases

Multifrontal codes often follow a three phase approach: analysis, numerical factorization, triangular solution.

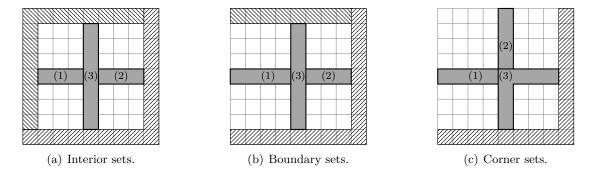

The *analysis* phase applies numerical and structural pretreatments to the matrix, in order to optimize the subsequent phases. One of the main preprocessings, called *reorder*ing, aims at reducing the fill-in; it consists of permuting the rows and columns of the initial matrix so that less fill-in will occur in the factorization of the permuted matrix. Minimizing the fill-in is NP-complete [92]. Numerous heuristics have been studied to obtain efficient techniques that significantly decrease the fill-in. They fall into two main classes: *local methods* choose the pivot order by traversing the adjacency graph following a local heuristic (e.g., nodes with lowest degree first). The Approximate Minimum Degree algorithm (AMD) is one of the most popular techniques [6]. Global methods try to partition the adjacency graph and usually provide solvers with a tree of separators (sets of nodes or edges whose removal disconnect the graph). SCOTCH [74] and METIS [55] are probably the two most popular graph partitioning software packages. Once the ordering is computed, the symbolic factorization computes the structure of the factors (in practice, part of the work can be done during the ordering phase). The analysis phase also involves numerical pretreatments that aim at avoiding problems during the factorization. Scaling is a typical example of such a preprocessing: it computes two diagonal matrices  $D_r$  and  $D_c$  such that  $D_r A D_c$  has better numerical properties, that is, less pivoting and numerical fill-in will occur during the factorization.

The numerical factorization computes the factors, relying on the pivot order and the elimination tree computed during the analysis. A keystone issue is the *numerical pivoting*, that aims at ensuring a good numerical accuracy by avoiding divisions by small pivots (diagonal elements). In case a bad pivot is found, the associated row is swapped with

<sup>&</sup>lt;sup>2</sup>This implies that fronts can be rectangular.

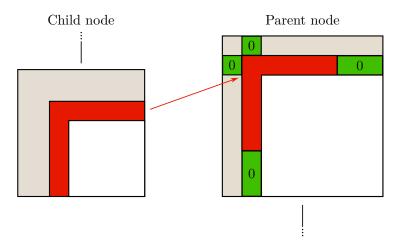

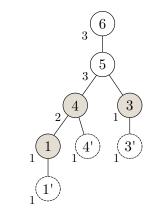

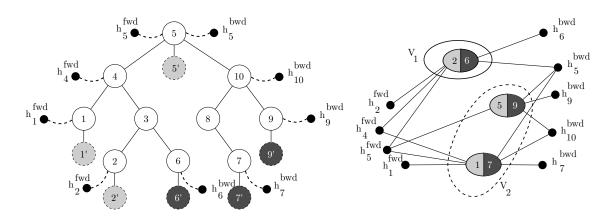

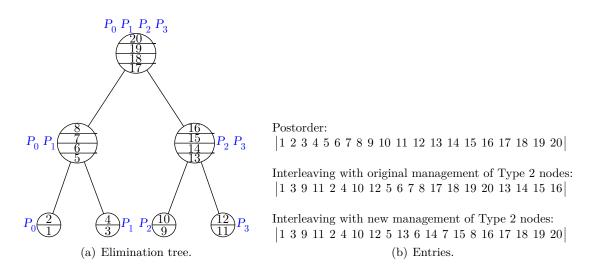

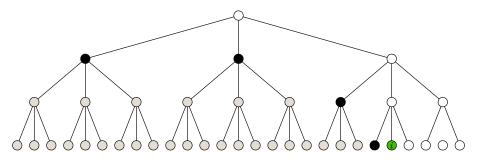

another unfactored row so that the new diagonal element has better properties. In this dissertation we do not focus at all on numerical issues, therefore we do not describe in detail the different existing pivoting strategies. We simply highlight a specific property of the multifrontal method. Within a frontal matrix (corresponding to a supernode), pivots can only be chosen inside the (1,1) block, because the rows and columns that touch the contribution block are not fully summed; when a pivot cannot be eliminated without jeopardizing the numerical accuracy, the corresponding rows and columns are swapped with other columns and pushed to the border of the (1,1) block. They remain unfactored and are delayed to the frontal matrix of the parent, where they appear as fully-summed variables and are placed at the border of the (1,1) block; this is referred to as *delayed pivoting.* We illustrate this in Figure 1.5. The frontal matrix of the parent becomes larger and some fill-in occurs because of the variables that appear in the parent node but not in the child. A variable might be delayed several times if needed. Therefore, the elimination tree is a dynamic structure that can change during the factorization; in a parallel context, this implies that some dynamic scheduling should be used in order to compensate for the imbalance in workloads and memory loads that might arise because of delayed pivots and that cannot be forecast. We highlight these aspects in the second part of this thesis.

Figure 1.5: Delayed pivoting: some pivots that cannot be eliminated (dark rows and columns in the figure) are delayed to the parent node. Note that this introduces some numerical fill-in (explicit zero entries in the parent node).

An interesting feature of the multifrontal method (as well as right-looking methods) is that it can efficiently run *out-of-core*; this consists of using storage disks as an extension of the main memory, which is useful when the memory requirements for the factorization are larger than the main memory. In the multifrontal method, once the contribution block of a frontal matrix is computed, the rows and columns of factors for this frontal matrix are no longer needed (see Theorem 1.3 and 1.4); therefore, factors can be written to disk as soon as they are computed (and removed from the main memory) without being read in the rest of the factorization. This limits the volume of accesses to storage disks, that are usually much slower than the main memory. In Chapter 4, we address a problem related to the triangular solution phase in an out-of-core context.

The last step is the solution phase that computes the solution of the system in two steps: forward elimination and backward substitution, as in the dense case. They consist of a bottom-up and a top-down traversal of the tree, respectively. We describe these two algorithms in detail in Section 2.4. Finally, we provide some notation that will be useful in the following; for a given node i (sometimes  $\mathcal{N}_i$ ):

$nfront_i$  is the order of the frontal matrix associated with *i*.

$sfront_i$  is the surface of the front.

$npiv_i$  is the number of fully-summed variables in the front.

$ncb_i$  is the size of the contribution block.

$scb_i$  is the surface of the contribution block.

$nc_i$  is the number of children of i.

sib(i) is the set of siblings of *i*.

#### **1.3** Experimental environment

#### 1.3.1 The MUMPS solver

The main motivation for this work was to study and experiment algorithmic ideas in order to improve the MUMPS solver. The MUMPS solver [9, 11] is a parallel direct solver that implements the multifrontal method. MUMPS started in 1996 with the European project PARASOL; it was inspired by the shared-memory code MA41 by Amestoy and Duff [7, 3], which itself relies on the earlier HSL code MA37 by Duff and Reid. MUMPS primarily targets at distributed-memory architectures; at the moment, multithreading is achieved only using a multithreaded BLAS, but work is in progress to exploit shared-memory parallelism using OpenMP [5].

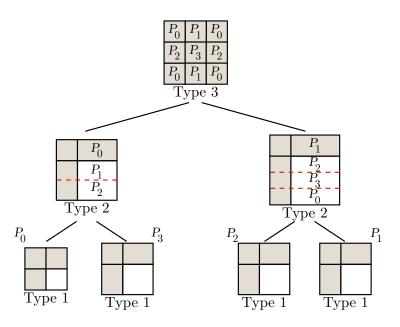

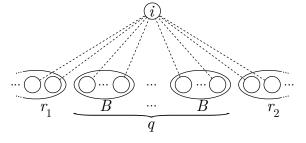

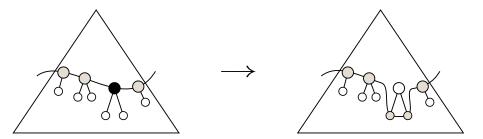

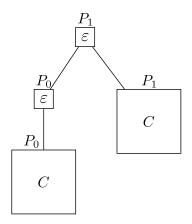

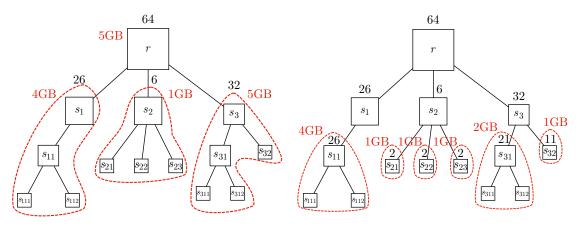

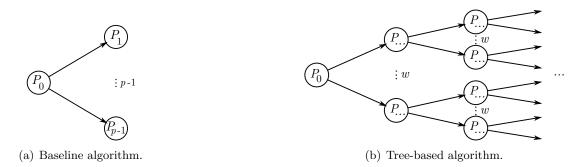

MUMPS relies heavily on the elimination tree of the matrix A to be factored; if A is unsymmetric, MUMPS uses the sparsity pattern of  $A + A^T$ . Both tree parallelism and node parallelism are exploited. We refer to sequential nodes and parallel nodes as *Type 1* nodes and *Type 2* nodes respectively. Type 2 nodes are distributed following a 1D rowwise partitioning: the so-called *master process* holds the (1,1) block and the (1,2) block (rows of the U factor) and is in charge of organizing the computations; *slave processes* are in charge of the (2,1) block (columns of L) and the (2,2) block (the contribution block). The root node can optionally be processed using a two-dimensional partitioning relying on ScaLAPACK, in which case we call it a *Type 3 root*. We illustrate this in Figure 1.6. Contrary to most codes that rely on static approaches where tasks are assigned to processes in advance, MUMPS relies on a dynamic scheduling of the tasks, using a completely asynchronous approach; this increases the complexity of the code but makes it able to perform dynamic pivoting, which guarantees the numerical stability. We will describe all these aspects in detail in Chapter 7.

MUMPS provides a large range of numerical features that make it a very robust code, and it also provides many functionalities:

**Input:** MUMPS provides Fortran, C and MATLAB interfaces. The input matrix can be unsymmetric or symmetric; it can be centralized or distributed, assembled or in elemental format (i.e., represented as an expended sum of dense matrices). Real and complex, single and double precision arithmetic are supported.

Figure 1.6: Node types used within MUMPS: the Type 3 root node is distributed following a 2D block cyclic partitioning, Type 2 nodes follow a 1D row-wise partitioning where the master process holds the rows of the U factor while slave processes share off-diagonal columns of the L factor and the contribution block. Type 1 nodes are processed by a single process.

- Analysis: many structural and numerical pretreatments (scalings) can be applied and different ordering strategies and packages can be used, in particular AMD [6] and some other local heuristics, PORD [83], METIS [55], SCOTCH [74] and their parallel versions PARMETIS [56] and PT-SCOTCH [28].

- **Factorization:** LU,  $LDL^T$  and Cholesky factorizations can be performed, depending on the matrix. Many pivoting strategies (two-by-two pivots, delayed pivoting...) are implemented and guarantee the numerical robustness of the code. The factorization can be performed in an *out-of-core* mode, where partial factors are saved on disks as soon as they are no longer needed; using asynchronous I/O operations, this has a relatively small impact on the performance but significantly reduces the memory usage [1, 84].

- **Solve step:** dense and sparse right-hand sides are supported; the solution can be either centralized or distributed.

- **Postprocessing:** iterative refinement can be applied to the solution vector, and a numerical analysis can be performed to return more information to the user (backward error, etc.).

- **Miscellaneous:** many features are available beyond the classical analysis-factorizationsolution scheme: partial factorization and computation of the Schur complement (see the next section), computation of the inertia and the determinant of the matrix, computation of a nullspace basis for rank-deficient matrices...

The aim of this study is to tackle two difficulties that arise in MUMPS as well as in many other sparse direct solvers:

- 1. The triangular solve step of direct solvers is known to be less efficient than the factorization: while many sparse factorization codes are able to reach reasonable flop rates and speed-ups, the triangular solution often lags behind, which is critical especially in applications where several solve steps (often thousands) are performed after a factorization. This was confirmed in the last MUMPS Users' Group Meeting in 2010, where many users put a more efficient solution phase on their wish list. In this study, we have been interested in improving the solution phase especially in the case where sparse right-hand sides and/or sparse solution vectors are involved: this is described in the first part of this dissertation, where we suggest different ideas to improve the performance and the memory usage of the solution phase.

- 2. Memory is known to be a limitation to the use of direct solvers. In MUMPS, the memory estimates computed prior to the factorization are often not very reliable because of the dynamic nature of the code, where tasks are not assigned in advance. Furthermore, MUMPS relies on the multifrontal factorization, which makes use of a (parallel) stack to store contribution blocks: the behavior of this stack is difficult to predict in a parallel environment. Thus users quite often face the error code -9, which means that the workspace allocated before the factorization is too small, because memory estimates were too optimistic. In this study we are interested in developing mapping and scheduling algorithms that enforce some memory constraints and provide reliable memory estimates prior to the factorization: this is described in the second part of this dissertation.

#### 1.3.2 The PDSLin solver

Hybrid methods attempt to combine the strengths of direct and iterative methods in order to obtain solvers that are able to tackle larger problems. Among these, the Schur complement methods [85] have gained popularity in recent years and have demonstrated to be scalable on large numbers of processors. In this method, the original linear system Ax = b is first reordered into a system with the following block structure:

where D is referred to as the -th *interior subdomain*, C consists of *separators*, and E and F are the *interfaces* between D and C. To compute the solution of the linear system (1.1), we first compute the solution vector y on the interface by solving the Schur complement system,

$$Sy = g \tag{1.2}$$

where the Schur complement S is defined as

$$S = C \qquad \sum_{k=1}^{k} F D^{-1} E$$

and  $g = g \sum_{i=1}^{k} F D^{-1} f$ . Then, to compute the solution vector u on the -th subdomain, we solve the -th subdomain system

$$D \ u = f \qquad E \ y \tag{1.3}$$

#### 1. General introduction

Many software packages implement this method: one can cite HIPS [38], MaPHyS [47], ShyLU [78] and PDSLin [64]. We focus on the last, as some of the ideas presented in Chapter 5 have been implemented and experimented within this solver. PDSLin uses the parallel direct solver SuperLU\_DIST [63] on each one of the interior domains D (1.3). PDSLin does not explicitly form the Schur complement S: its solves the Schur complement system (1.2) using a preconditioned iterative method, the preconditioner being the LU factorization of an approximate Schur complement S obtained with SuperLU\_DIST.

The approximate Schur complement S is obtained through the following process: first, a *local matrix* A is associated with each subdomain D:

$$A = \begin{array}{cc} D & E \\ F & 0 \end{array}$$

where E and F are the nonzero columns of E and nonzero rows of F respectively. Then D is factorized using SuperLU\_DIST, yielding  $P D \overline{P} = L U$  where P and  $\overline{P}$  are row and column permutations respectively. Then the update matrix T is computed as

$$T = F D^{-1}E$$

=  $F \overline{P} U^{-1} \quad L^{-1}P E$

=  $W G$

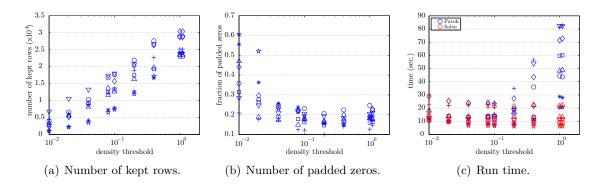

where  $W = F \overline{P} U^{-1}$  and  $G = L^{-1}P E$  are computed using the parallel triangular solver of SuperLU\_DIST. A large amount of fill might occur in W and G. Thus, in order to reduce the memory and computational cost, they are approximated by discarding entries with magnitude less than a prescribed threshold, yielding their approximations W and G and the approximate update matrix T = W G. Therefore, using the interpolation matrices  $R_{E_{\ell}}$  and  $R_{F_{\ell}}$  that map the columns and rows of E and F respectively, the approximate Schur complement is formed as

$$S = C \qquad \sum_{k=1}^{k} R_{F_{\ell}} T R_{E_{\ell}}^{T}$$

Finally, in order to further reduce the cost of the preconditioner, small nonzero elements are discarded from S, yielding the final approximate Schur complement S.

Two combinatorial problems are of interest in the framework of the PDSLin solver:

- 1. Computing the doubly-bordered form (1.1) so that multiple constraints are satisfied: balancing the workload between the different subdomains (i.e., the cost of the factorizations), balancing the workload between the different interfaces (i.e., the cost of triangular solves) and reducing the size of the Schur complement. We have used different graph and hypergraph partitioning formulations, and have developed a recursive hypergraph bisection method. We have tackled this problem but it is out of the scope of this dissertation, and we refer the reader to [57] and [91].

- 2. Partitioning the right-hand sides columns  $F^T$  and E in order to speed up the computation of  $W = F \overline{P} U^{-1}$  and  $G = L^{-1}P E$ . This is described in Chapter 5, where we have examined different heuristics and a hypergraph model.

#### 1.3.3 Test problems

We describe in Table 1.1 the matrices that were used in the experiments carried out during this study. They arise from various industrial and academic applications from our partners; they all correspond to physical problems taking place in three-dimensional domains with the exception of matrix211. This kind of matrices is often challenging for direct solvers as they exhibit large amount of fill. The matrices we have selected exhibit different properties in terms of symmetry, fill-in, etc., but they are not very demanding numerically, as this was not the point of this study. We indicate in the table the size of the factors obtained by ordering the matrices with METIS [55].

| Matrix name             | Order   | Entries    | Factors | Sym | Arithmetic   | Description; origin                             |

|-------------------------|---------|------------|---------|-----|--------------|-------------------------------------------------|

|                         | N       | (millions) | (GB)    |     |              |                                                 |

| NICE20MC <sup>()</sup>  | 715923  | 28.1       | 8.3     | sym | double real  | Seismic processing; BRGM lab                    |

| matrix211               | 801378  | 55.8       | 3.9     | uns | double real  | Fusion, M3D-C <sup>1</sup> code; Center for Ex- |

|                         |         |            |         |     |              | tended MHD Modeling                             |

| AUDI <sup>()</sup>      | 943695  | 39.3       | 9.9     | sym | double real  | Automotive crankshaft model; Para-              |

|                         |         |            |         |     |              | sol collection                                  |

| bone010 <sup>()</sup>   | 986703  | 36.3       | 8.6     | sym | double real  | 3D trabecular bone; Mathematical                |

|                         |         |            |         |     |              | Research Institute of Oberwolfach               |

| pancake2_3              | 1004060 | 49.1       | 39.8    | uns | single cmplx | 3D electromagnetism; Padova Univer-             |

|                         |         |            |         |     |              | sity                                            |

| tdr190k                 | 1110242 | 43.3       | 5.7     | sym | double real  | Accelerator; Omega3P code, SLAC                 |

|                         |         |            |         |     |              | National Accelerator Laboratory                 |

| CONESHL <sup>()</sup>   | 1262212 | 43.0       | 5.5     | sym | double real  | 3D finite element, SAMCEF code;                 |

|                         |         |            |         |     |              | SAMTECH                                         |

| Hook_1498 <sup>()</sup> | 1498023 | 31.2       | 12.3    | sym | double real  | 3D model of a steel hook; Padova Uni-           |

|                         |         |            |         |     |              | versity                                         |

| FLUX-2M <sup>()</sup>   | 2001728 | 212.9      | 34.8    | uns | single cmplx | 3D finite element, FLUX code; CE-               |

|                         |         |            |         |     |              | DRAT                                            |

| CAS4R_LR15              | 2423135 | 19.6       | 4.5     | sym | single cmplx | 3D electromagnetism; EADS Innova-               |

|                         |         |            |         |     |              | tion Works                                      |

| meca_raff6              | 3269763 | 130.1      | 63.5    | sym | double real  | Thermo-mechanical coupling, Code                |

|                         |         |            |         |     |              | Aster; EDF                                      |

Table 1.1: Set of matrices used for the experiments. Those marked with <sup>()</sup> are publicly available on gridtlse.org. We indicate the symmetry either using sym (symmetric) or uns (unsymmetric).

We have also used two generators that are able to create matrices with prescribed size, corresponding to an  $nx \times ny \times nz$  physical domain: the d11 generator produces symmetric real matrices corresponding to an eleven-point stencil, and the Geoazur generator, provided by Stéphane Operto and Jean Virieux (Geoazur consortium), produces unsymmetric complex matrices corresponding to a 27-point stencil. This generator is used in Geophysics (modeling of acoustic wave propagation in the frequency domain), and the matrices it generates are challenging for direct solvers as they are very memory demanding. For example, with nx = ny = nz = 192, the size of the matrix is N = 7077888, the number of entries in the matrix is 189 1 millions, and the size of the LU factors is 144 GB (in single precision arithmetic).

#### 1.3.4 Computational systems

We describe the different systems on which we have carried out our experiments:

Pret, desktop machine at ENSEEIHT: one quad-core Intel Xeon W3350 processor

$@3~\mathrm{GHz},\,4~\mathrm{GB}$  of memory and a 7200 RPM hard drive. Used for the experiments in Chapter 4.

Franklin, Cray XT4 machine at the National Energy Research Scientific Computing Center (NERSC): 9572 nodes with one quad-core AMD Opteron 1356 processor @2.3 GHz and 8 GB memory per node. Used for the experiments in Section 5.1.

Hyperion, Altix ICE 8200 machine at the Calcul en Midi-Pyrénées resource center (CALMIP): 352 nodes with two quad-core Intel Xeon 5560 processors @2.8 GHz and 32 GB memory per node. Used for the experiments in Section 5.2, Chapter 10 and Chapter 11.

Hopper, Cray XE6 machine at the National Energy Research Scientific Computing Center (NERSC): 6384 nodes with two twelve-core AMD Opteron 6172 processors @2.1 GHz and 32 GB memory per node. Used for some of the experiments in Chapter 10.

# Part I

# Solution phase with sparse right-hand sides: memory and performance issues

### Chapter 2

### Introduction

The first part of this thesis focuses on memory and performance aspects of the multifrontal solution phase with sparse right-hand sides and/or sparse solution vectors. While much effort has been dedicated to exploiting the sparsity of the matrix in the factorization phase, few studies have considered exploiting sparsity of the right-hand side(s) in the solution phase. However, the main result was established in the 80's by Gilbert [44]<sup>1</sup>, who showed that the structure of the solution of Ax = b (with A non singular) is the *closure* of the structure of *b* (see Section 2.2 for details). Interestingly, Gilbert and Liu used this theorem to compute the structure of the *LU* factors by formulating the sparse *LU* factorization as a sequence of sparse triangular solves [45], but paradoxically, few studies or codes have used this result in the solution phase. Furthermore, little has been done about multiple right-hand sides. In this work, we are interested in computations that involve multiple sparse right-hand sides and sparse solution vectors; we focus on compressing the memory space used by the solution phase, reducing the computational cost in different contexts (in-core and out-of-core settings), and enhancing parallelism.

In this introductory chapter, we first mention in Section 2.1 various applications that involve sparse right-hand sides and sparse solutions, and we especially highlight applications that involve computation of a set of entries of the inverse of a sparse matrix (that we refer to as *inverse entries*); as we will see, this amounts to solving linear systems where both the right-hand sides and the solution vectors are sparse. We also give a brief survey of the existing methods for computing inverse entries. In Section 2.2, we describe how to exploit sparsity of the right-hand sides and/or the solution vectors; we show how this can be applied to the computation of inverse entries. We then describe the problems we have focused on and our contributions in Section 2.3. Finally, we describe in Section 2.4 the general parallel multifrontal solution algorithm, as it will be useful for the subsequent chapters.

#### 2.1 Applications and motivations

#### 2.1.1 Applications with sparse right-hand sides and/or sparse solution

Many physical applications involve solving linear systems with sparse right-hand sides that correspond to data that is nonzero at only a few points of the physical domain. Similarly, it is also often required to compute the solution of a problem at only a few points of the domain, which corresponds to computing only a few entries of the solution vectors (we

<sup>&</sup>lt;sup>1</sup>The publication is dated 1994 but the associated technical report is actually from 1986.

refer this to as *selected solution* or *selected entries*). These situations are for example described in [16] in the context of Poisson's equations.

Solving linear programming problems with the simplex algorithm often exhibits highlyreducible matrices, sparse right-hand sides and sparse solution vectors. This situation is referred to as hyper-sparsity [51].

Several methods for solving sparse linear systems involve intermediate steps that rely on sparse right-hand sides, even if the initial right-hand side is not necessarily sparse. This is the case in the Schur complement method where the update of the Schur complement requires the solution of triangular systems with sparse right-hand sides (see Section 1.3.2). This is also the case in the block-Cimmino method [13]; in this iterative method, several augmented systems of the form

$$\begin{array}{cccc} G & A^{iT} & u^i \\ A^i & 0 & v^i \end{array} = \begin{array}{c} 0 \\ r^i \end{array}$$

need to be solved at each iteration (the  $A^i$ 's correspond to a row-wise partition of the initial matrix A). In these augmented systems, the right-hand side is sparse and only the upper part,  $u^i$ , of the solution is needed in the iterative process.

Nullspace computations in the context of rank revealing L U factorization for general unsymmetric matrices also require the solution of linear systems with sparse right-hand sides. In order to compute a basis of the nullspace of a rank-deficient matrix, one has to solve Ax = 0. First, a rank-revealing factorization is performed, which provides A = LU with det(L) = 0 and U containing zero rows, due to the detection of null pivots. Therefore, one has to solve Ux = 0. Assume for example that pivot j is a null pivot. We write Ux = 0 in the following form:

$$\begin{array}{cccccccc} U_{1:j-1 \ 1:j-1} & U_{1:j-1 \ j} & U_{1:j-1 \ j+1:n} & & x_{1:j-1} & 0 \\ & 0 & 0 & & x_j & = 0 \\ & & U_{j+1:n \ j+1:n} & & x_{j+1:n} & 0 \end{array}$$

Assuming  $U_{j+1:n \ j+1:n}$  is not rank deficient, we have  $x_{j+1:n} = 0$ , and  $x_j$  can be set to 1. We thus have to solve:

$$U_{1:j-1\;1:j-1} x_{1:j-1} = U_{1:j-1\;j}$$

and the final nullspace vector is  $x = (x_{1:j-1}; 1; 0)$ . Note that the same set of equations can be obtained by setting  $u_{jj}$  to 1 during the factorization and the right-hand side to  $e_j$ . Therefore, the nullspace vector can be computed by solving  $Ux = e_j$ . In the general case, U has several zero rows, and one has to solve UX = E, where each column of E is a vector  $e_j$  associated with a null pivot j, and the columns of E are sorted in the order in which the null pivots have been detected. This scheme is explained in detail in [84].

#### 2.1.2 Applications involving the computation of inverse entries