## Protection des architectures hétérogènes multiprocesseurs dans les systèmes embarqués: Une approche décentralisée basée sur des pare-feux matériels

Pascal Cotret

#### ▶ To cite this version:

Pascal Cotret. Protection des architectures hétérogènes multiprocesseurs dans les systèmes embarqués : Une approche décentralisée basée sur des pare-feux matériels. Electronique. Université de Bretagne Sud, 2012. Français. NNT : . tel-00789541v2

### HAL Id: tel-00789541 https://theses.hal.science/tel-00789541v2

Submitted on 30 Oct 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THESE / UNIVERSITÉ DE BRETAGNE-SUD

sous le sceau de l'Université européenne de Bretagne

pour obtenir le titre de

**Ecole doctorale SICMA**

DOCTEUR DE L'UNIVERSITÉ DE BRETAGNE-SUD

Mention : STIC

présentée par

#### **Pascal Cotret**

Préparée à l'Unité Mixte de Recherche 6285 Lab-STICC, Laboratoire des Sciences et Techniques de l'Information, de la Communication et de la Connaissance (Lorient)

Protection des architectures hétérogènes multiprocesseurs dans les systèmes embarqués : Une approche décentralisée basée sur des pare-feux matériels

Thèse soutenue le 11 décembre 2012 devant le jury composé de :

#### **Viktor Fischer**

Professeur des universités, Laboratoire Hubert-Curien Université Jean-Monnet, Saint-Etienne / président

#### **Daniel Chillet**

Maître de conférences HDR, Laboratoire IRISA (équipe CAIRN) Université de Rennes 1, Lannion / rapporteur

#### **Bruno Rouzeyre**

Professeur des universités, Laboratoire LIRMM Université de Montpellier 2 / rapporteur

#### Jean-Philippe Diguet

Directeur de recherche CNRS, Laboratoire Lab-STICC Université de Bretagne-Sud, Lorient / examinateur

#### **Guy Gogniat**

Professeur des universités, Laboratoire Lab-STICC Université de Bretagne-Sud, Lorient / examinateur

# Protection des architectures hétérogènes multiprocesseurs dans les systèmes embarqués : une approche décentralisée basée sur des pare-feux matériels

Thèse

présentée le 11 Décembre 2012 À l'Université de Bretagne-Sud Laboratoire Lab-STICC École doctorale SICMA pour l'obtention du grade de Docteur - Mention STIC par Pascal Cotret

#### Jury:

Professeur des universités, Université Jean-Monnet Daniel CHILLET, rapporteur

Maître de conférences HDR, Université de Rennes 1

Bruno ROUZEYRE, rapporteur

Professeur des universités, Université de Montpellier 2

Jean-Philippe DIGUET, examinateur

Directeur de recherche, Université de Bretagne-Sud

Guy GOGNIAT, directeur de thèse

Professeur des universités, Université de Bretagne-Sud

Lorient, Université de Bretagne-Sud, 2012

Viktor FISCHER, président du jury

### **Abstract**

Embedded systems are used in several domains and are parts of our daily life: we use them when we use our smartphones or when we drive our modern cars embedding GPS, light/rain sensors and other electronic assistance mechanisms. These systems process sensitive data (such as credit card numbers, critical information about the host system and so on) which must be protected against external attacks as these data are transmitted through a communication link where the attacker can connect to extract sensitive information or inject malicious code within the system. Unfortunately, embedded systems contain more and more components which make more and more security breaches that can be exploited to provoke attacks.

One of the goals of this thesis is to propose a method to protect communications and memories in a multiprocessor architecture implemented in a FPGA reconfigurable chip. The method is based on the implementation of hardware mechanisms offering monitoring and cryptographic features in order to give a secured execution environment according to a given threat model. The main goal of the solution proposed in this work is to minimize perturbations in the data traffic; it is considered that it can be accomplished by focusing on the latency impact of our security mechanisms. Our solution is also sensible to attack events: as soon as an attack is detected, an update process of security policies can be enabled.

Following an analysis of implementation results, two extensions of the basic solution are described: a fully-secured flow for startup/maintenance of FPGA-based multiprocessor systems and a method to improve attacks detection in order to take into account software parameters in multitasks applications.

### Résumé

Les systèmes embarqués sont présents dans de nombreux domaines et font même partie de notre quotidien à travers les smartphones ou l'électronique embarquée dans les voitures par exemple. Ces systèmes manipulent des données sensibles (codes de carte bleue, informations techniques sur le système hôte...) qui doivent être protégées contre les attaques extérieures d'autant plus que ces données sont transmises sur un canal de communication sur lequel l'attaquant peut se greffer pour extraire des données ou injecter du code malveillant. Le fait que ces systèmes contiennent de plus en plus de composants dans une seule et même puce augmente le nombre de failles qui peuvent être exploitées pour provoquer des attaques.

Les travaux menés dans ce manuscrit s'attachent à proposer une méthode de sécurisation des communications et des mémoires dans une architecture multiprocesseur embarquée dans un composant reconfigurable FPGA par l'implantation de mécanismes matériels qui proposent des fonctions de surveillance et de cryptographie afin de protéger le système contre un modèle de menaces prédéfini tout en minimisant l'impact en latence pour éviter de perturber le trafic des données dans le système. Afin de répondre au mieux aux tentatives d'attaques, le protocole de mise à jour est également défini.

Après une analyse des résultats obtenus par différentes implémentations, deux extensions sont proposées : un flot de sécurité complet dédié à la mise en route et la maintenance d'un système multiprocesseur sur FPGA ainsi qu'une amélioration des techniques de détection afin de prendre en compte des paramètres logiciels dans les applications multi-tâches.

## Remerciements

En premier lieu, je tiens à remercier Guy Gogniat, directeur du Lab-STICC et mon directeur de thèse, de m'avoir encadré pendant ces trois années. Il a toujours été de bon conseil dans les décisions à prendre et a su être un soutien important dans les phases de rédaction d'articles et de ce manuscrit. Merci encore Guy pour ces trois ans.

Je remercie également le professeur Viktor Fischer du Laboratoire Hubert-Curien à Saint-Etienne d'avoir accepté d'être le président du jury.

Je remercie Mr Daniel Chillet (Laboratoire IRISA-CAIRN à Lannion) et Mr Bruno Rouzeyre du Laboratoire LIRMM de Montpellier d'être les rapporteurs de cette thèse.

Je remercie enfin Jean-Philippe Diguet (Lab-STICC) d'avoir endossé le rôle d'examinateur.

Je remercie également les personnes du laboratoire Lab-STICC qui ont fait de ces 3 années une thèse pas totalement banale. Je pense notamment à Cédric ×2, Dominique, Florence, Ghizlane, Jean-Christophe, Romain, Sébastien, Vianney, Virginie, Willy, Youenn, Yvan. J'en oublie sûrement, désolé pour eux. . .

Un p'tit merci au passage (on arrête avec les anaphores) à l'équipe CAIRN du laboratoire IRISA qui m'accueille depuis septembre à Lannion en qualité d'ATER pour m'avoir permis de terminer cette thèse dans de bonnes conditions.

Et enfin, un grand grand merci à Patrick et Martine (plus connus sous les pseudonymes de Papa et Maman) de me « supporter » dans tous les sens du terme (!) depuis quelques années maintenant, même à distance.

Lorient, Décembre 2012

P.C.

## Liste des publications

[Cotret *et al.* 2010] Pascal Cotret, Jérémie Crenne et Guy Gogniat. *Sécurisation des communications dans une architecture multiprocesseur.* In MajecSTIC (MAnifestation des JEunes Chercheurs en Sciences et Technologies de l'Information et de la Communication), pages 163-170, Bordeaux, France, Octobre 2010.

[Gaspar *et al.* 2010] Lubos Gaspar, Viktor Fischer, Florent Bernard, Lilian Bossuet et Pascal Cotret. *HCrypt: A Novel Concept of Crypto-processor with Secured Key Management.* In ReConFig (International Conference on ReConFigurable Computing and FPGAs), pages 280-285, Cancùn, Mexique, Décembre 2010. IEEE.

[Cotret *et al.* 2011] Pascal Cotret, Jérémie Crenne, Guy Gogniat, Jean-Philippe Diguet, Lubos Gaspar et Guillaume Duc. *Distributed security for communications and memories in a multiprocessor architecture*. In RAW (18th Reconfigurable Architectures Workshop), pages 326-329, Anchorage, AK, Etats-Unis, Mai 2011. IEEE.

[Crenne *et al.* 2011a] Jérémie Crenne, Pascal Cotret, Guy Gogniat, Russell Tessier et Jean-Philippe Diguet. *Efficient key-dependent message authentication in reconfigurable hardware*. In FPT (International Conference on Field-Programmable Technology), pages 1-6, New Delhi, Décembre 2011. IEEE.

[Cotret et al. 2012a] Pascal Cotret, Jérémie Crenne, Guy Gogniat et Jean-Philippe Diguet. Bus-based MPSoC security through communication protection: A latency-efficient alternative. In FCCM (20th Annual IEEE International Symposium on Field-Programmable Custom Computing Machines), pages 200-207, Toronto, ON, Canada, Avril 2012. IEEE. [Cotret et al. 2012b] Pascal Cotret, Florian Devic, Guy Gogniat, Benoît Badrignans et Lionel Torres. Security enhancements for FPGA-based MPSoCs: a boot-to-runtime protection flow for an embedded Linux-based system. In ReCoSoC (7th International Workshop on Reconfigurable Communication-centric Systems-on-Chip), York, Angleterre, Juillet 2012. IEEE.

[Cotret *et al.* 2012c] Pascal Cotret, Guy Gogniat, Jean-Philippe Diguet et Jérémie Crenne. *Lightweight reconfiguration security services for AXI-based MPSoCs.* In FPL (International Conference on Field Programmable Logic and Applications), Oslo, Norvège, Août 2012. IEEE.

# Table des matières

| Ał | ostra  | ct       |                                                               | 7   |

|----|--------|----------|---------------------------------------------------------------|-----|

| Ré | ésum   | é        |                                                               | vi  |

| Re | emer   | ciemer   | nts                                                           | ix  |

| Li | ste d  | es publ  | ications                                                      | xi  |

| Ta | ıble d | les figu | res                                                           | xix |

| Li | ste d  | es table | eaux                                                          | xxi |

| In | trod   | uction   |                                                               | 1   |

| 1  | Con    | texte    |                                                               | 5   |

|    | 1.1    | Systèr   | nes embarqués : généralités                                   | 6   |

|    | 1.2    | Taxon    | omie non exhaustive des attaques sur les systèmes embarqués . | 8   |

|    | 1.3    | Sécur    | ité : généralités                                             | 9   |

|    |        | 1.3.1    | Confidentialité                                               | 9   |

|    |        | 1.3.2    | Intégrité                                                     | 11  |

|    |        | 1.3.3    | Authentification                                              | 12  |

|    |        | 1.3.4    | Combinaisons alternatives                                     | 13  |

|    | 1.4    | Concl    | usion                                                         | 13  |

| 2  | État   | de l'ar  | t                                                             | 15  |

|    | 2.1    | Comn     | nunications dans les architectures multiprocesseurs           | 17  |

|    |        | 2.1.1    | Bus : topologies et protocoles                                | 17  |

|    |        | 2.1.2    | NoC                                                           | 22  |

|    | 2.2    | Trava    | ux existants                                                  | 23  |

|    |        | 2.2.1    | NoC                                                           | 24  |

|    |        | 2.2.2    | Bus                                                           | 28  |

|    |        | 2.2.3    | Codesign logiciel-matériel                                    | 30  |

|    |        | 2.2.4    | Protection de la mémoire externe                              | 32  |

|    |        |          |                                                               |     |

#### Table des matières

|   | 2.3 | Positionnement                                            | 33 |

|---|-----|-----------------------------------------------------------|----|

|   |     | 2.3.1 Cahier des charges                                  | 33 |

|   |     | 2.3.2 Modèle de menaces                                   | 34 |

|   |     | 2.3.3 Comparatif                                          | 35 |

|   | 2.4 | Conclusion                                                | 36 |

| 3 | Pro | tection statique des communications 3                     | 37 |

|   | 3.1 | Cadre de la solution                                      | 38 |

|   |     | 3.1.1 Contraintes sur la plateforme                       | 38 |

|   |     | 3.1.2 Modèle de menaces                                   | 39 |

|   |     | 3.1.2.1 Transactions internes                             | 39 |

|   |     | 3.1.2.2 Transactions externes                             | 10 |

|   |     | 3.1.2.3 Vecteurs d'attaques                               | 10 |

|   |     | 3.1.2.4 Synthèse                                          | 11 |

|   |     | 3.1.3 Vue haut-niveau de la solution proposée             | 11 |

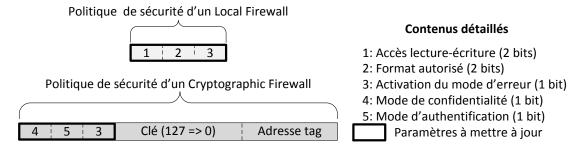

|   |     | 3.1.4 Politiques de sécurité                              | 13 |

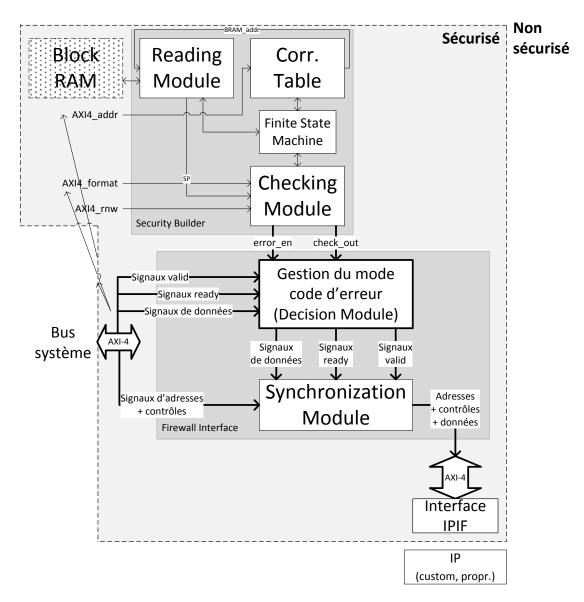

|   | 3.2 | Local Firewall                                            | 17 |

|   |     | 3.2.1 Firewall Interface                                  | 18 |

|   |     | 3.2.2 Security Builder                                    | 19 |

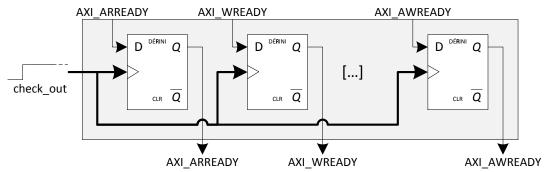

|   | 3.3 | Cryptographic Firewall                                    | 53 |

|   |     | 3.3.1 Fonctionnalités communes                            | 54 |

|   |     | 3.3.2 Choix des modes de confidentialité et d'intégrité 5 | 55 |

|   | 3.4 | Politiques de sécurité : formulation et choix matériels   | 59 |

|   | 3.5 | Conclusion                                                | 31 |

| 4 | Mis | es à jour en temps réel                                   | 3  |

|   | 4.1 | Problèmes liés à la solution proposée                     | 34 |

|   |     | 4.1.1 Mise à jour du système                              | 34 |

|   |     | 4.1.2 Cahier des charges pour la flexibilité              | 64 |

|   | 4.2 | Évolution des modes de sécurité                           | 35 |

|   |     | 4.2.1 Description                                         | 35 |

|   |     | 4.2.1.1 Situation initiale 6                              | 35 |

|   |     | 4.2.1.2 Lecture seule                                     | 66 |

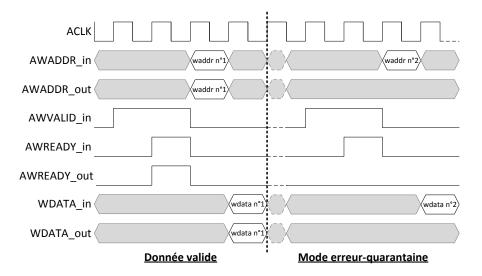

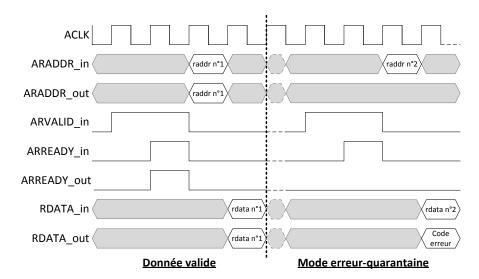

|   |     | 4.2.1.3 Erreur-quarantaine 6                              | 37 |

|   |     | 4.2.1.4 Flux de mise à jour                               | 68 |

|   |     | 4.2.1.5 Réinitialisation du système 6                     | 69 |

|   |     | o .                                                       | 69 |

|   |     | 4.2.3 Implémentation du code d'erreur                     | 71 |

|   | 4.3 | Solution flexible                                         | 75 |

|   |     | 4.3.1 Vue générale de la solution                         | 75 |

|   |     | 4.3.2  | Surveillance des attaques                                        | 76  |

|---|-----|--------|------------------------------------------------------------------|-----|

|   |     | 4.3.3  | Mise à jour des politiques de sécurité                           | 79  |

|   |     |        | 4.3.3.1 Modifications architecturales sur la protection statique | 79  |

|   |     |        | 4.3.3.2 Propriétés du protocole de communication AXI             | 80  |

|   |     |        | 4.3.3.3 Description du protocole de mise à jour                  | 81  |

|   |     | 4.3.4  | Interfaces utilisateur                                           | 84  |

|   | 4.4 | Concl  | usion                                                            | 85  |

| 5 | Imp | lémen  | tations et analyse de la solution                                | 87  |

|   | 5.1 | Cas d' | étude                                                            | 88  |

|   |     | 5.1.1  | Architecture                                                     | 88  |

|   |     | 5.1.2  | Politiques de sécurité                                           | 89  |

|   |     | 5.1.3  | Logiciel                                                         | 90  |

|   |     |        | 5.1.3.1 Applications                                             | 90  |

|   |     |        | 5.1.3.2 Système d'exploitation                                   | 92  |

|   | 5.2 | Résult | tats                                                             | 93  |

|   |     | 5.2.1  | Surface                                                          | 93  |

|   |     |        | 5.2.1.1 Pare-feux seuls                                          | 93  |

|   |     |        | 5.2.1.2 Surcoûts sur le cas d'étude                              | 97  |

|   |     |        | 5.2.1.3 Résultats sur des plateformes comemrciales               | 98  |

|   |     |        | 5.2.1.4 Comparatif avec les travaux existants                    | 99  |

|   |     | 5.2.2  | Latence                                                          | 101 |

|   |     | 5.2.3  | Occupation mémoire                                               | 105 |

|   | 5.3 | Gestic | on et stockage des clés                                          | 110 |

|   | 5.4 | Synth  | èse                                                              | 112 |

|   | 5.5 | Concl  | usion                                                            | 113 |

| 6 |     |        | 1                                                                | 115 |

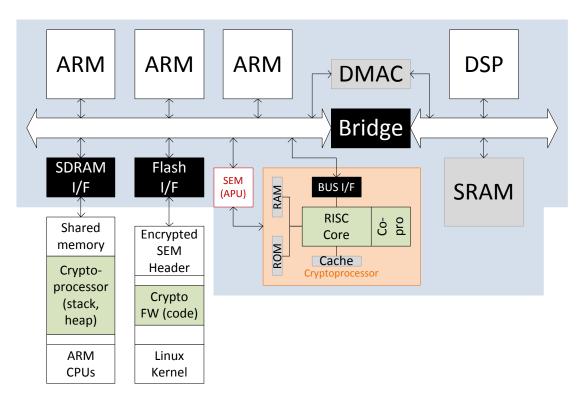

|   | 6.1 | Du bit | tstream à l'exécution de l'application                           | 116 |

|   |     | 6.1.1  | Problématique                                                    | 116 |

|   |     | 6.1.2  | Travaux existants                                                | 118 |

|   |     | 6.1.3  | Boot flexible d'un Linux embarqué                                | 119 |

|   |     | 6.1.4  | Contribution personnelle                                         | 121 |

|   |     | 6.1.5  | Résultats et analyse                                             | 124 |

|   |     |        | 6.1.5.1 Surface                                                  | 124 |

|   |     |        | 6.1.5.2 Latence                                                  | 126 |

|   |     |        | 6.1.5.3 Résultats de benchmarks                                  | 127 |

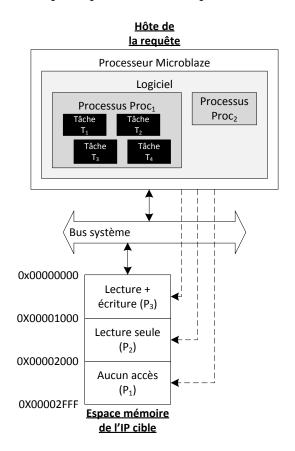

|   | 6.2 | Améli  | oration de la granularité de protection                          | 129 |

|   |     | 6.2.1  | Problématique                                                    | 129 |

|   |     | 6.2.2  | Contexte                                                         | 131 |

#### Table des matières

|    |       | 6.2.3  | Solution    | ns et analyse  |            |        | <br> | <br> | <br> |  | 131 |

|----|-------|--------|-------------|----------------|------------|--------|------|------|------|--|-----|

|    |       |        | 6.2.3.1     | Solution log   | gicielle . |        | <br> | <br> | <br> |  | 132 |

|    |       |        | 6.2.3.2     | Solution ma    | térielle . |        | <br> | <br> | <br> |  | 134 |

|    |       |        | 6.2.3.3     | Analyse des    | deux sol   | utions | <br> | <br> | <br> |  | 136 |

|    | 6.3   | Concl  | usion       |                |            |        | <br> | <br> | <br> |  | 137 |

| 7  | Con   | clusio | ns          |                |            |        |      |      |      |  | 139 |

|    | 7.1   | Persp  | ective : to | olérance aux : | fautes     |        | <br> | <br> | <br> |  | 140 |

|    | 7.2   | Synth  | èse des c   | ontributions   |            |        | <br> | <br> | <br> |  | 142 |

| Bi | bliog | raphie | •           |                |            |        |      |      |      |  | 151 |

# Table des figures

| 1.1  | Exemple de système embarqué sécurisé                                     | 7          |

|------|--------------------------------------------------------------------------|------------|

| 1.2  | Confidentialité - Mécanisme de chiffrement par clé privée                | 10         |

| 1.3  | Mécanisme d'intégrité                                                    | 11         |

| 1.4  | Mécanisme d'authentification                                             | 12         |

| 2.1  | Loi de Moore - Nombre de transistors pour divers modèles de processeur   | 16         |

| 2.2  | Nombre de liens dans une architecture avec liaisons point-à-point        | 18         |

| 2.3  | Topologies de bus                                                        | 19         |

| 2.4  | Évolution du nombre de liens en fonction du nombre d'éléments            | 20         |

| 2.5  | Bus hiérarchiques                                                        | 21         |

| 2.6  | Exemple d'architecture d'un réseau sur puce                              | 22         |

| 2.7  | Solution de [Diguet <i>et al.</i> 2007]                                  | 24         |

| 2.8  | Solution de [Fiorin <i>et al.</i> 2007a]                                 | 26         |

| 2.9  | Solution de [Sepulveda <i>et al.</i> 2012b]                              | 27         |

| 2.10 | Solution de Coburn et al. sur une architecture multiprocesseur générique | 29         |

| 2.11 | Architecture de la solution Trustzone                                    | 31         |

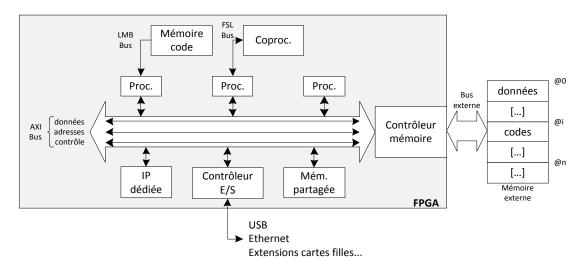

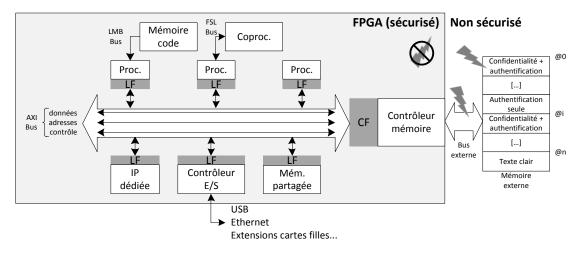

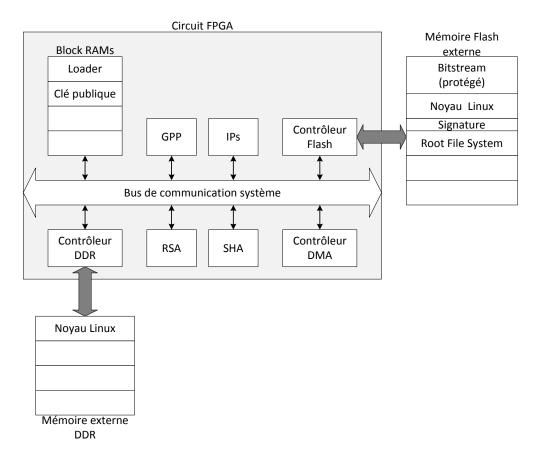

| 3.1  | MPSoC générique sur puce FPGA                                            | 39         |

| 3.2  | Zones de confiance sur une architecture multiprocesseur                  | 41         |

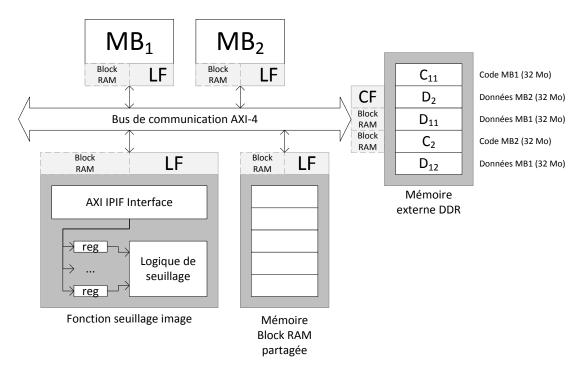

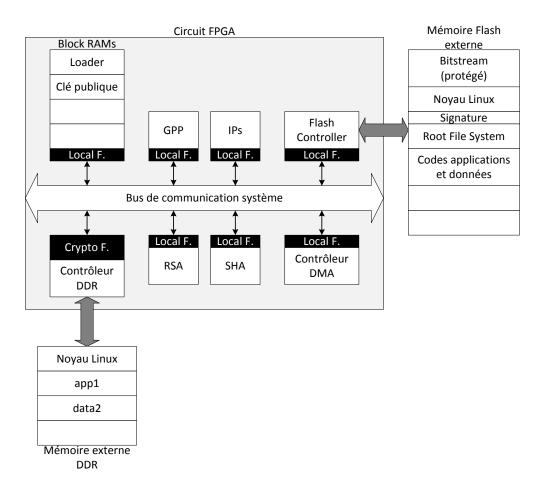

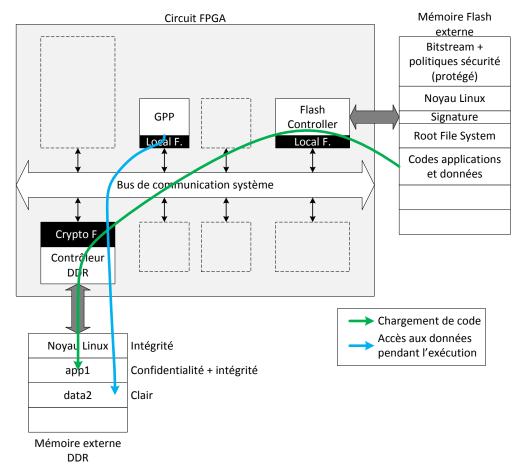

| 3.3  | Solution proposée implantée sur un MPSoC générique                       | 42         |

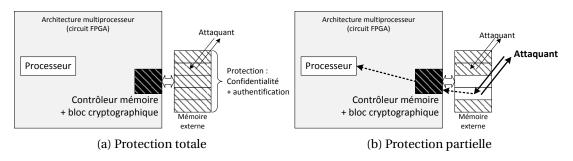

| 3.4  | Protection d'une mémoire externe en confidentialité et authentification  | 44         |

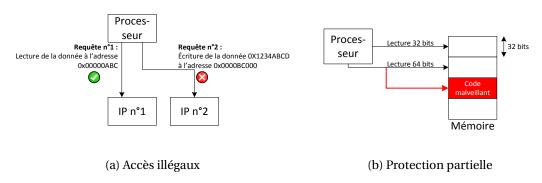

| 3.5  | Protection des droits en lecture-écriture et du format                   | 45         |

| 3.6  | Spoofing, rejeu et réallocation                                          | 46         |

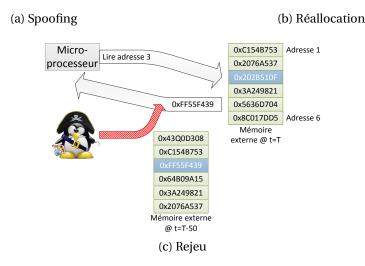

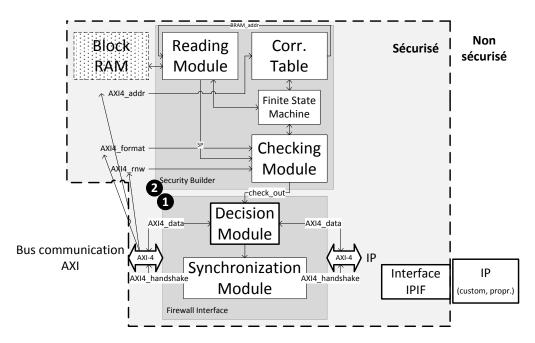

| 3.7  | Structure d'un Local Firewall                                            | 47         |

| 3.8  | Structure d'un Synchronization Module                                    | 48         |

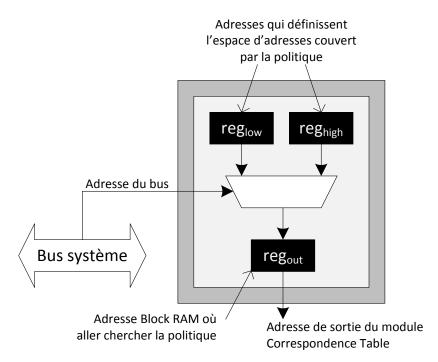

| 3.9  | Implémentation de la Correspondence Table                                | 50         |

| 3.10 | Implémentation du Checking Module                                        | 51         |

| 3.11 | Machine à états associée au module Security Builder                      | 52         |

| 3.12 | Structure d'un Cryptographic Firewall                                    | 53         |

| 3.13 | Chemins de données dans un Cryptographic Firewall                        | <b>5</b> 4 |

| 3.14 | Cryptographic Module : AES-GCM                                           | 57         |

#### Table des figures

| 3.15 | Organisation des politiques de sécurité dans les mémoires Block RAM      | 59  |

|------|--------------------------------------------------------------------------|-----|

| 4.1  | Modes de sécurité en situation initiale                                  | 66  |

| 4.2  | Modes de sécurité en lecture seule                                       | 67  |

| 4.3  | Modes de sécurité en erreur-quarantaine                                  | 67  |

| 4.4  | Évolution des modes de sécurité                                          | 68  |

| 4.5  | Agencement des politiques de sécurité dans les Block RAM pour Local      |     |

|      | et Cryptographic Firewall                                                | 70  |

| 4.6  | Structure interne d'un Local Firewall                                    | 72  |

| 4.7  | Mode erreur pour les canaux d'écriture                                   | 73  |

| 4.8  | Mode erreur pour les canaux de lecture                                   | 74  |

| 4.9  | Implémentation du mode erreur-quarantaine dans le module Firewall        |     |

|      | Interface                                                                | 75  |

| 4.10 | Architecture globale de la zone de surveillance et de mise à jour des    |     |

|      | politiques de sécurité                                                   | 76  |

| 4.11 | Structure générique d'un pare-feu (LF-CF) avec détection des attaques    |     |

|      | par flags                                                                | 77  |

| 4.12 | Architecture de l'IP de surveillance et routine d'interruption           | 78  |

| 4.13 | Architecture de l'IP de surveillance avec 2 registres principaux         | 79  |

| 4.14 | Modifications sur la protection statique                                 | 80  |

|      | Chronogramme du mécanisme poignée de main                                | 80  |

| 4.16 | Diagramme de la machine à états finis pour la mise à jour des politiques |     |

|      | de sécurité                                                              | 81  |

| 4.17 | Architecture partielle d'un pare-feu avec éléments de mise à jour        | 82  |

| 5.1  | Architecture du cas d'étude                                              | 88  |

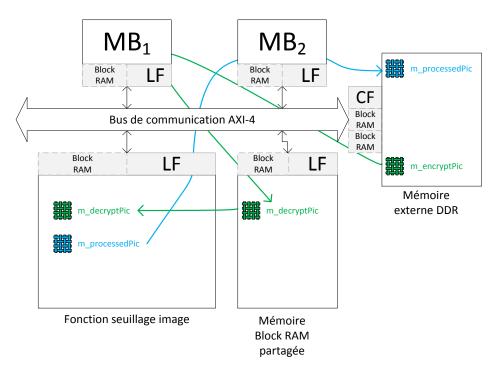

| 5.2  | Diagramme de séquence de l'application picProc                           | 90  |

| 5.3  | Illustration du déroulement de picProc sur le cas d'étude                | 91  |

| 5.4  | Structure du module Correspondence Table pour 1 politique de sécurité    | 93  |

| 5.5  | Architecture simplifiée du NEC MP21x                                     | 98  |

| 5.6  | Histogramme - Latence de simulations de scenarii                         | 102 |

| 5.7  | Schémas de fonctionnement des mécanismes de sécurité                     | 104 |

| 5.8  | Occupation mémoire en fonction du nombre de politiques de sécurité       | 107 |

| 5.9  | Occupation mémoire en fonction du nombre de pare-feux                    | 109 |

| 5.10 | Gestion d'une mémoire chiffrée avec plusieurs clés                       | 110 |

| 5.11 | Gestion d'une mémoire chiffrée avec 2 clés                               | 111 |

| 5.12 | Occupation mémoire avec prise en compte ou non des registres clés .      | 112 |

| 6.1  | Amorçage d'un système embarqué sur un FPGA                               | 116 |

| 6.2  | Boot flexible d'un Linux embarqué                                        | 120 |

#### Table des figures

| 6.3 | Boot flexible avec protection de la mémoire externe                  | 122 |

|-----|----------------------------------------------------------------------|-----|

| 6.4 | Chemin de données et stockage des politiques dans une implémentation |     |

|     | avec le boot flexible                                                | 123 |

| 6.5 | Filtrage en fonction des adresses                                    | 129 |

| 6.6 | Filtrage en fonction des tâches                                      | 130 |

| 6.7 | Identification par solution logicielle                               | 133 |

| 6.8 | Structure des politiques dans les Block RAM                          | 133 |

| 6.9 | Identification par solution matérielle                               | 135 |

| 7.1 | Implémentation de la tolérance aux fautes dans l'IP de surveillance  | 141 |

# Liste des tableaux

| 2.1 | Resultats individuels                                                     | 35  |

|-----|---------------------------------------------------------------------------|-----|

| 3.1 | Comparatif des modes disponibles pour le bloc cryptographique             | 56  |

| 3.2 | Description des paramètres en Block RAM                                   | 60  |

| 3.3 | Description des paramètres cryptographiques                               | 60  |

| 5.1 | Droits d'accès pour le cas d'étude                                        | 89  |

| 5.2 | Évolution de la surface du module Correspondence Table en fonction        |     |

|     | du nombre de politiques                                                   | 94  |

| 5.3 | Résultats de synthèse des pare-feux seuls                                 | 95  |

| 5.4 | Résultats de synthèse des éléments dédiés à la mise à jour de la sécurité | 96  |

| 5.5 | Résultats en surface des différentes configurations                       | 97  |

| 5.6 | Implémentation des pare-feux sur des plateformes commerciales             | 99  |

| 5.7 | Comparatif avec les travaux existants                                     | 100 |

| 5.8 | Implémentations distribuée et centralisée                                 | 101 |

| 5.9 | Surcoûts de la sécurité sur des applications logicielles                  | 104 |

| 6.1 | Surcoûts en surface                                                       | 125 |

| 6.2 | Surcoût des blocs dédiés au boot                                          | 126 |

| 6.3 | Surcoûts des options de chiffrement                                       | 127 |

| 6.4 | Surcoûts des applications benchmarks                                      | 128 |

| 6.5 | Comparatif entre les solutions logicielle et matérielle                   | 136 |

### Introduction

Les systèmes embarqués font désormais partie de la vie quotidienne : les smartphones, l'électronique dans les automobiles, l'électronique dédiée à la navigation marine, etc. Les systèmes embarqués sont également utilisés dans des domaines spécifiques tels que l'aérospatial ou le domaine militaire. En ce qui concerne les applications militaires, on peut citer par exemple le robot BigDog développé par Boston Dynamics  $^1$ .

Ce robot a pour tâche principale d'effectuer le transport de lourdes charges sur des opérations militaires. Ce type de robot possède différentes fonctions :

- Un GPS lui permet de se repérer.

- Il est également capable d'effectuer des communications radio pour communiquer des informations techniques et stratégiques.

- Une batterie de capteurs et de caméras permettent au robot de pouvoir analyser son environnement.

Ce type de systèmes est capable de transmettre et de recevoir des données de différentes natures. Le robot peut récupérer les valeurs de capteurs (gestion du mouvement, images des caméras...) mais manipule également des informations plus critiques telles que le code associé au système embarqué qui gère le fonctionnement du robot ou des données plus critiques qui doivent rester confidentielles (messages stratégiques à chiffrer, communications entre les différentes unités militaires...). Ces données sont éventuellement transmises par liaison et doivent être stockées dans des espaces sécurisés du système embarqué dans le robot afin que ces données ne soient pas accessibles à de potentiels attaquants.

<sup>1.</sup> http://www.bostondynamics.com/robot\_bigdog.html

#### Introduction

Ce robot est basé sur un système embarqué avec des processeurs et un système d'exploitation basé sur Unix nommé QNX<sup>2</sup>. Le micro-ordinateur doit être capable de récupérer les informations des différents capteurs (position GPS, caméras, pression, force) et également de commander les composants du robot (par exemple, actionner le système hydraulique qui permet au robot d'avancer ou transmettre des données par liaison radio).

Il faut donc que ces systèmes embarqués possèdent des mécanismes de sécurité qui leur permettent de pouvoir s'exécuter dans un environnement sécurisé : c'est-à-dire que, dans le cas idéal, le système sécurisé doit être capable de filtrer les attaques provenant de l'extérieur mais également de détecter une attaque qui surviendrait à l'intérieur même de l'architecture (au cas où un attaquant ait pu trouver une faille dans le système).

Les mécanismes de sécurité appliqués à ces architectures hétérogènes doivent respecter, au-delà du cahier des charges en termes de sécurité (algorithme cryptographique, modèle de menace...), des contraintes physiques liées à l'implantation sur des systèmes embarqués : contraintes de consommation, de temps de traitement, etc.

Pour le prototypage des systèmes embarqués, l'utilisation d'une technologie reconfigurable telle que les FPGA est une solution intéressante (en comparaison avec les circuits utilisant la technologie ASIC) : elle permet d'implémenter un système embarqué dans un temps de développement court tout en ayant la possibilité d'être reconfiguré afin de tester une version mise à jour du système embarqué (contrairement aux circuits ASIC dont la structure est définitive une fois qu'ils ont été produits).

Dans ce manuscrit, on s'intéresse plus particulièrement à la protection des architectures hétérogènes multiprocesseurs au niveau des communications et des mémoires : on considère qu'il s'agit de points névralgiques à prendre en compte dans le développement de systèmes embarqués sécurisés, en particulier sur des technologies FPGA. En effet, les espaces de stockage de données et les canaux de communication sont des supports pour déployer des attaques compromettant le fonctionnement du système.

<sup>2.</sup> http://www.qnx.com/

Afin d'adresser cette problématique, je propose un manuscrit organisé en 7 chapitres. Le chapitre 1 de ce manuscrit donne des éléments de contexte sur ce qu'est la sécurité et sur les différentes fonctions cryptographiques que l'on peut utiliser.

Le chapitre 2 est un état de l'art sur le sujet qui se focalise essentiellement sur la protection des communications. La protection des mémoires est également évoquée dans une seconde partie.

Les chapitres 3 et 4 décrivent en détail l'implémentation d'une solution à base de pare-feux matériels sur un composant FPGA pour protéger les communications et les mémoires selon un modèle de menaces prédéfini. Les mécanismes qui permettent de mettre à jour les contextes de sécurité en cas d'attaque sont décrits dans le chapitre 4.

Le chapitre 5 est une analyse complète des résultats obtenus par des implémentations des mécanismes de sécurité proposés dans ce manuscrit.

Le chapitre 6 propose des extensions à la solution proposée dans les chapitres 3 et 4. La première concerne l'intégration des pare-feux matériels proposés dans ce manuscrit dans un flot de protection du boot d'un système d'exploitation embarqué préexistant; la deuxième concerne l'amélioration de la finesse de détection des pare-feux au niveau logiciel (plus précisément au niveau tâche).

Enfin, le chapitre 7 présente les conclusions ainsi que les perspectives sur l'approche proposée dans ce manuscrit.

# 1 Contexte

Dans ce chapitre, quelques notions sur les systèmes embarqués sont décrites. Dans une seconde partie, on explique les motivations en termes de sécurité ainsi qu'un inventaire non exhaustif des attaques existantes. Enfin, quelques éléments sur la cryptographie sont donnés dans la dernière partie du chapitre.

#### **Sommaire**

| 1.1 | Systèmes embarqués : généralités 6                                 |

|-----|--------------------------------------------------------------------|

| 1.2 | Taxonomie non exhaustive des attaques sur les systèmes embarqués 8 |

| 1.3 | Sécurité: généralités                                              |

|     | 1.3.1 Confidentialité                                              |

|     | 1.3.2 Intégrité                                                    |

|     | 1.3.3 Authentification                                             |

|     | 1.3.4 Combinaisons alternatives                                    |

| 1.4 | Conclusion                                                         |

#### 1.1 Systèmes embarqués : généralités

De nos jours, les systèmes embarqués sont utilisés dans la vie de tous les jours : électronique grand public, automobile, télécommunications - réseaux, etc. Que ce soit dans les voitures ou les smartphones, ces systèmes sont capables de réaliser des fonctions complexes et sont fabriqués dans des technologies de pointe pour respecter des cahiers des charges de plus en plus contraignants : la miniaturisation des systèmes embarqués ainsi que les contraintes en termes de performance (vitesse d'exécution, puissance consommée...) sont des paramètres qui doivent être pris en compte dans le développement de ce type de circuits.

De plus, les systèmes embarqués tentent d'implémenter de plus en plus de composants matériels dans une seule et même carte, le tout étant généralement géré par une couche logicielle composée d'un système d'exploitation ainsi que de plusieurs applications. Dans le cycle de développement des systèmes embarqués, plusieurs paramètres sont à étudier : les performances à atteindre par rapport à l'application visée, la durée de vie que l'on souhaite, etc. Depuis quelques temps, les problématiques de sécurité deviennent une étape essentielle dans le développement des systèmes embarqués ([Kocher *et al.* 2004]) : le nombre de failles augmente avec le nombre de composants et ceux-ci sont en mesure de manipuler et de transmettre des données de différentes natures qui doivent être traitées dans un environnement d'exécution sécurisé afin d'éviter les fuites de données.

Dans le domaine de la sécurité des systèmes embarqués, on peut définir différents axes d'étude pour un seul et même système. D'après [Ravi *et al.* 2004], les critères de sécurité généraux à observer sont les suivants : la sécurisation des communications, la sécurisation des espaces de stockage, la sécurisation des entrées-sorties ainsi que l'authentification des utilisateurs. Pour répondre à ces différents points, les développeurs de systèmes embarqués peuvent proposer des mécanismes ayant pour but de réaliser ces différents critères de sécurité.

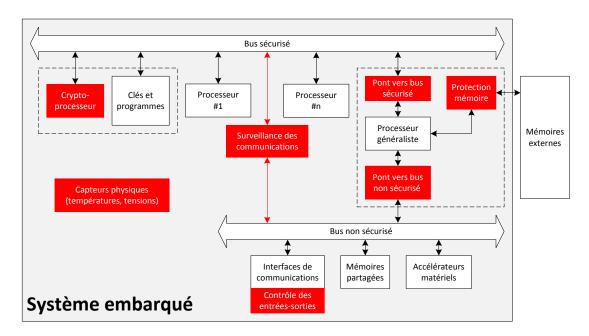

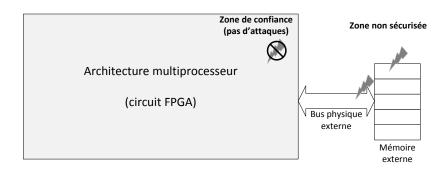

FIGURE 1.1 – Exemple de système embarqué sécurisé

Le système proposé dans la figure 1.1 est une représentation d'un système avec des mécanismes de protection qui permettent de définir des zones sécurisées et non sécurisées afin de distribuer correctement le flux de données entre les différents composants. Par exemple dans la figure 1.1, un cryptoprocesseur permet de chiffrer les communications sur le bus sécurisé et les communications avec le milieu extérieur sont contrôlées par les interfaces de communications tandis que les données stockées dans les mémoires externes sont également protégées au niveau du contrôleur mémoire. Un processeur généraliste est également présent afin de faire la transition entre l'espace sécurisé et l'espace non sécurisé.

Les travaux proposés dans cette thèse s'intéressent plus particulièrement à la protection des communications : on considère qu'il s'agit d'un aspect primordial dans le développement des systèmes embarqués car les canaux de communications voient défiler des données de différentes natures (applications, données confidentielles, éléments cryptographiques) qui n'ont pas toujours les mêmes besoins en termes de sécurité (certaines données ne doivent en aucun cas être révélées à un attaquant potentiel tandis que d'autres, comme des signaux de contrôles, ne nécessitent pas autant d'attention). Par extension, le stockage des données est également un point qui sera abordé dans ce manuscrit : les mémoires constituent un autre point névralgique de la sécurité des systèmes embarqués.

# 1.2 Taxonomie non exhaustive des attaques sur les systèmes embarqués

Lorsqu'un système embarqué est attaqué, on distingue généralement deux catégories : les attaques matérielles et les attaques logicielles. En ce qui concerne les attaques matérielles, l'objectif de l'attaquant est d'utiliser des propriétés physiques du circuit pour neutraliser le système ou en extraire des informations (données confidentielles sur l'utilisateur, clés cryptographiques, codes de processeur). Une des possibilités consiste à utiliser les attaques par canaux cachés [Guilley & Pacalet 2004] : par une bonne connaissance des caractéristiques physiques du système en mesurant la puissance du système par une attaque de type DPA (Differential Power Analysis) ou en analysant les émanations électromagnétiques par une EMA (ElectroMagnetic Analysis), on peut extraire des informations telle que la clé secrète d'un algorithme de chiffrement [Peeters et al. 2007]. L'autre catégorie concerne les attaques dites logicielles. Dans le monde informatique, cela revient aux virus, chevaux de Troie et autres vers ([Dagon et al. 2004] propose des exemples de ces attaques appliquées aux téléphones portables). Pour les systèmes embarqués, il va s'agir de modifier le contenu de mémoires ou d'injecter du code contenant des instructions malveillantes qui vont modifier le comportement du système.

Toutes ces attaques ont pour objectif d'altérer, d'une manière ou d'une autre, le comportement d'un système embarqué donné. Un des scenarii possible est de provoquer des dénis de services : le but est d'envoyer un grand nombre de requêtes au système cible afin de faire en sorte qu'il ne réponde plus ou de diminuer sa durée de vie ([Nash *et al.* 2005]). Il est également possible d'attaquer le système en provoquant un *buffer overflow* (scenario déroulé par exemple dans [Coburn *et al.* 2005]) : dans ce cas, le système va aller lire des données modifiées par l'attaquant afin de modifier le code associé à un processeur par exemple. Enfin, on peut citer plusieurs attaques s'intéressant aux liens entre les mémoires et le coeur du système embarqué :

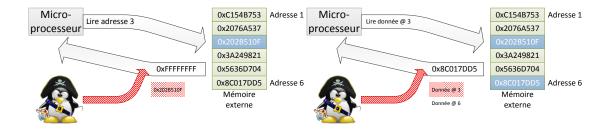

- Replay: sauvegarder l'état de la mémoire à un instant t et réutiliser cette sauvegarde à un instant  $t + \Delta t$ . Dans ce cas, l'organisation de la mémoire aura toujours la même structure

- Spoofing : injecter des données personnelles au niveau du lien de communication entre la mémoire externe et le système embarqué.

- Relocation: modifier l'organisation des différentes pages mémoires. Dans ce cas, le système qui veut aller lire les données de la page n°3 va, par exemple, récupérer les données de la page n°4 sans le savoir.

Globalement, toutes les attaques décrites dans cette partie sont des exemples de techniques qui montrent que la sécurité doit être prise en compte dans le développement de systèmes embarqués afin qu'ils ne soient pas détournés de leur fonction première.

#### 1.3 Sécurité: généralités

Comme cela a été dit dans le paragraphe précédent, il existe différents vecteurs d'attaques et donc différentes techniques de protection pour chacun. Si on se réfère à l'architecture présentée dans la figure 1.1, on peut dire que les mécanismes de protection peuvent être représentés sous la forme de capteurs de données physiques (températures, tensions ou courant pour contrer les attaques physiques), des capteurs de données systèmes (surveillance des communications pour limiter les dénis de service ou les attaques de type *buffer overflow*) ou encore des fonctions cryptographiques (pour la protection des données dans les blocs mémoires ou le chiffrement des données par un cryptoprocesseur).

Les travaux présentés dans cette thèse s'intéressent aux deux dernières métriques. L'essentiel des travaux sur la protection des communications est décrit dans la suite du manuscrit pour un cahier des charges donné. La suite de ce chapitre s'attache à donner quelques notions sur les paramètres cryptographiques que sont la confidentialité, l'intégrité et l'authentification.

#### 1.3.1 Confidentialité

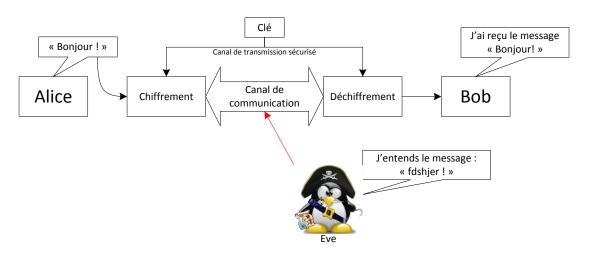

La confidentialité consiste à remplacer un texte par un autre grâce à un mécanisme de chiffrement pour que la donnée soit illisible par un attaquant.

Dans la figure 1.2, Alice veut transmettre un message (*"Bonjour"*) à Bob. Le problème est que ce message ne doit pas être compréhensible pour Eve (qui symbolise un attaquant). Par conséquent, un mécanisme de chiffrement par *clé secrète* est implémenté afin que le message transmis sur le canal de communication soit différent. Dans la figure 1.2, Alice va chiffrer le message avec la clé avant de le transmettre à Bob qui pourra le déchiffrer avec la même clé (ceci suppose que la clé a été transmise entre les deux protagonistes par l'intermédiaire d'un lien sécurisé). Alors, l'attaquant n'est capable de récupérer qu'une version modifiée du message original. Il existe deux types de chiffrement : le chiffrement dit *symétrique* et le chiffrement *asymétrique*.

FIGURE 1.2 – Confidentialité - Mécanisme de chiffrement par clé privée

Le chiffrement symétrique correspond à celui représenté dans la figure 1.2 : il n'y a qu'une seule clé (dite secrète) partagée entre l'expéditeur et le destinataire du message. Un exemple d'algorithme de chiffrement symétrique est l'AES (Advanced Encryption Standard) : cet algorithme a été formalisé en 2000 suite à un concours lancé par le NIST <sup>1</sup> et a été approuvé par la NSA <sup>2</sup>. Cet algorithme existe sous différents modes de fonctionnements qui ont chacun leurs avantages et inconvénients en termes de performances (latence, quantité de données nécessaires en amont du chiffrement) et en termes de sécurité; [Crenne 2011] propose une description détaillée de ces différents modes. L'autre type de chiffrement est dit asymétrique. La principale différence réside dans le fait que celui-ci repose sur un fonctionnement avec deux clés (une clé publique et une clé privée) : sur la base du mécanisme proposé dans la figure 1.2, Alice va chiffrer le message avec la clé publique et Bob le déchiffre avec sa clé privée. Même si la clé publique est diffusée (contrairement à la clé secrète), l'attaquant ne peut pas déchiffrer le message. Un exemple d'algorithme de chiffrement asymétrique est l'algorithme RSA (Rivest, Shamir, Adleman du nom des trois auteurs de ce standard) décrit dans les années 1970<sup>3</sup>.

<sup>1.</sup> National Institute of Standards and Technologies

<sup>2.</sup> National Security Agency

$<sup>3.\</sup> http://worldwide.espacenet.com/publicationDetails/biblio?CC=US\&NR=4405829\&KC=\&FT=E\&locale=en\_EP$

#### 1.3.2 Intégrité

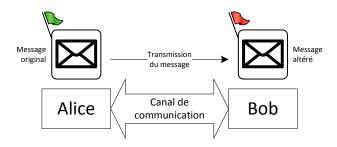

L'intégrité consiste à vérifier que le message n'a pas été altéré pendant la transmission.

FIGURE 1.3 – Mécanisme d'intégrité

Dans la figure 1.3, le message qu'envoie Alice à Bob a été modifié soit par une perturbation du canal de communication, soit par une injection d'une donnée contrefaite. Pour vérifier l'intégrité, on peut associer à la donnée une valeur témoin qui permet de détecter si la donnée a été modifiée (dès que la donnée change, la valeur témoin change).

L'intégrité peut être réalisée par l'implémentation d'une fonction de hachage : ces fonctions produisent des données de taille fixe à partir de données arbitraires de telle sorte qu'une modification de la donnée en entrée de la fonction de hachage change la valeur de sortie (qu'on appelle *hash*). Parmi les fonctions de hachage les plus connues, on peut citer MD5 (*Message Digest 5*, inventé par Rivest en 1991) ou la famille des SHA (*Secure Hash Algorithm*, dont la troisième version devrait sortir d'ici la fin de l'année 2012 par un concours organisé par la NIST <sup>4</sup>. D'autres structures plus complexes, telles que les arbres de Merkle [Merkle 1987], existent : la donnée est divisée en sous-blocs de taille égale et chacun à sa propre valeur de hachage, ces valeurs sont ensuite compressées jusqu'à obtenir un hash global de la donnée. On peut l'utiliser pour vérifier l'intégrité d'un message sans en connaître la totalité (il suffit de connaître le hash d'une partie de la donnée que l'on souhaite vérifier).

<sup>4.</sup> http://csrc.nist.gov/groups/ST/hash/sha-3/index.html

#### 1.3.3 Authentification

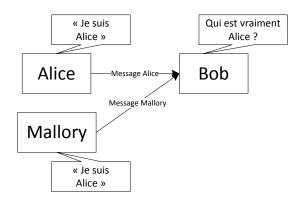

L'authentification consiste à vérifier que l'initiateur de la requête est bien celui attendu.

FIGURE 1.4 – Mécanisme d'authentification

Dans la figure 1.4, la situation est telle que le destinataire de la communication (Bob dans ce cas) reçoit deux informations provenant de sources différentes (Alice et Mallory) mais se proclamant tous les deux comme étant le seul et unique initiateur de la transaction (tous les deux disent être Alice). Par conséquent, il faut un mécanisme qui permet d'authentifier l'initiateur de la transaction (un certificat qui permet de dire quels sont les initiateurs autorisés). On trouve ce type de mécanisme dans le protocole SSL (*Secure Socket Layer*, dont une implémentation libre existe <sup>5</sup>).

<sup>5.</sup> http://www.openssl.org/

#### 1.3.4 Combinaisons alternatives

Plutôt que d'utiliser deux fonctions séparément pour réaliser deux des propriétés énoncées ci-dessus (confidentialité, intégrité et authentification), il existe des fonctions qui combinent plusieurs propriétés en un seul module.

- MAC (Message Authentication Code<sup>6</sup>), permet de vérifier l'intégrité et l'authentification d'un message.

- CBC-MAC est un dérivé du chiffrement DES qui permet aussi de vérifier l'authentification d'un message <sup>7</sup>.

- AES-GCM [McGrew & Viega 2004, Crenne et al. 2011b] est une fonction qui permet de réaliser la confidentialité et l'authentification (éventuellement l'intégrité) en utilisant le chiffrement AES (des détails sur cet algorithme sont donnés ultérieurement dans le manuscrit étant donné qu'il s'agit de l'algorithme choisi dans ces travaux).

# 1.4 Conclusion

Ce chapitre présente succinctement les propriétés qui seront utilisées dans la suite de ce manuscrit. Concrètement, lorsqu'on évoque la sécurité des systèmes embarqués, on s'intéresse donc à la protection des communications dans les systèmes multiprocesseurs en utilisant des mécanismes qui font office de capteurs du trafic de données ainsi qu'à la protection des mémoires par l'utilisation de ces capteurs combinée à l'utilisation de propriétés cryptographiques que sont la confidentialité et l'intégrité. Dans la suite de ce manuscrit, on étudiera les performances et les contraintes d'une implémentation de ces propriétés sur un système multiprocesseur embarqué sur un composant reconfigurable de type FPGA.

<sup>6.</sup> http://en.wikipedia.org/wiki/Message\_authentication\_code

<sup>7.</sup> http://www.itl.nist.gov/fipspubs/fip113.htm

# 2 État de l'art

Ce chapitre a pour but de faire une présentation des travaux existants dans le domaine ainsi que de positionner les travaux présentés dans cette thèse et d'en décrire les principales caractéristiques.

# **Sommaire**

| 2.1 | Comn   | nunications dans les architectures multiprocesseurs 17 |

|-----|--------|--------------------------------------------------------|

|     | 2.1.1  | Bus: topologies et protocoles                          |

|     | 2.1.2  | NoC                                                    |

| 2.2 | Trava  | ux existants                                           |

|     | 2.2.1  | NoC                                                    |

|     | 2.2.2  | Bus                                                    |

|     | 2.2.3  | Codesign logiciel-matériel                             |

|     | 2.2.4  | Protection de la mémoire externe                       |

| 2.3 | Positi | onnement                                               |

|     | 2.3.1  | Cahier des charges                                     |

|     | 2.3.2  | Modèle de menaces                                      |

|     | 2.3.3  | Comparatif                                             |

| 2.4 | Concl  | usion                                                  |

En amont à l'état de l'art, il faut bien prendre conscience que les systèmes embarqués sont de plus en plus complexes. En effet, les systèmes embarqués (qu'ils soient basés sur des technologies reconfigurables telles que les FPGAs ou pas) contiennent de plus en plus de composants au sein d'une seule et même puce.

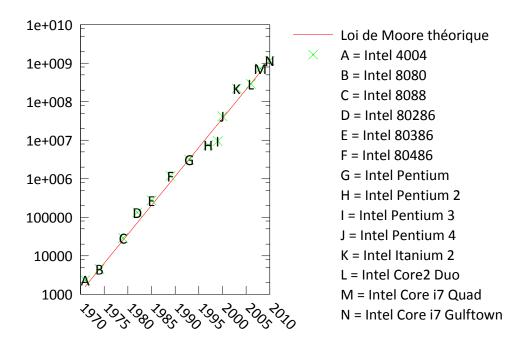

FIGURE 2.1 – Loi de Moore - Nombre de transistors pour divers modèles de processeur

D'après la loi de Moore <sup>1</sup> (voir figure 2.1), le nombre de transistors dans les processeurs des ordinateurs double tous les 18 mois : elle confirme le fait qu'avec l'avancement des hautes technologies, les processeurs (et par extension les systèmes embarqués) ont tendance à contenir de plus en plus de composants dans une seule et même puce. Malgré tout, cette hypothèse n'est pas valable à long terme : la finesse de gravure ne pourra pas diminuer indéfiniment et les constructeurs s'intéressent déjà aux puces multi-coeurs et aux transistors en trois dimensions (par exemple, dans les processeurs Ivy Bridge d'Intel <sup>2</sup>).

<sup>1.</sup> Les données sont issues de la page http://fr.wikipedia.org/wiki/Microprocesseur

<sup>2.</sup> http://www.bbc.co.uk/news/technology-17785464

Dans le fonctionnement des systèmes embarqués, il y a différentes phases : des temps de calcul (par exemple, une compression d'images ou un traitement du signal par un processeur), des transmissions de données entre les composants ou encore des lectures-écritures dans des mémoires. De notre point de vue, l'aspect le plus important est au niveau des communications au sein du système embarqué : les données qui circulent sur le moyen de communication du système sont de différentes natures (données, codes processeur ou informations confidentielles sur l'utilisateur) et n'ont pas non plus les mêmes besoins en termes de sécurité. Par extension, on s'intéressera également à la protection des mémoires : il s'agit d'une brèche qui peut être exploitée pour perturber les communications.

La suite de ce chapitre présente tout d'abord les architectures de communications qui sont susceptibles de nous intéresser. Ensuite, un état de l'art sur les mécanismes de protection existants permet de montrer le positionnement choisi pour les travaux présentés dans cette thèse par rapport aux travaux existants dans le domaine.

# 2.1 Communications dans les architectures multiprocesseurs

# 2.1.1 Bus: topologies et protocoles

Dans les systèmes embarqués, il faut que les composants de l'architecture puissent communiquer entre eux. Il existe plusieurs manières d'implémenter un réseau de communication entre les éléments du système multiprocesseur. La solution la plus simple consiste à implémenter des connexions point-à-point entre les composants.

Cette approche facilite le protocole de communication : étant donné que les liens sont individuels, il n'y a pas besoin de mécanisme d'arbitrage et la latence de communication est minimale. Par contre, son inconvénient majeur se situe au niveau architectural : plus il y a de composants dans le système à implémenter, plus il faut de liens de communication pour les relier entre eux. On propose de déterminer la « taille » de l'architecture (autrement dit, le nombre de liens nécessaire en fonction du nombre de composants).

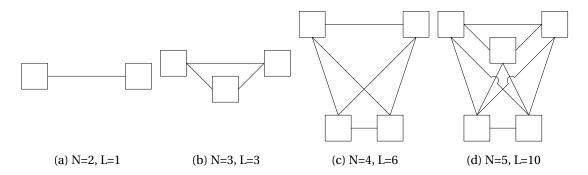

Soit N le nombre de composants et L le nombre de liens nécessaires. On suppose également que les liens de communication sont bidirectionnels (half-duplex ou full-duplex, la communication peut avoir lieu dans les deux sens mais pas forcément simultanément). Enfin, on suppose que les mécanismes de sécurité ne sont pas mutualisés (1 mécanisme par lien). Les figures 2.2a à 2.2d illustrent les architectures pour les 4 premiers cas (jusqu'à N=5).

FIGURE 2.2 – Nombre de liens dans une architecture avec liaisons point-à-point

On remarque également que :

Pour N=2,

$$L=N\times\frac{1}{2}$$

Pour N=3,  $L=N$

Pour N=4,  $L=N\times\frac{3}{2}$

Pour N=5,  $L=N\times2$

On peut en déduire que l'évolution du nombre de liens L en fonction du nombre d'éléments N suit l'équation :

$$L = \binom{N}{2} = \frac{N!}{2! \times (N-2)!} = N \times \frac{N-1}{2}$$

(2.2)

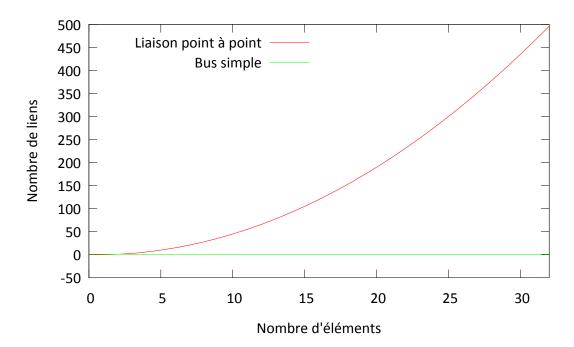

Cette fonction est représentée dans la figure 2.4 : l'évolution du nombre de liens suit une fonction en parabole, le nombre de liens augmente rapidement avec le nombre d'éléments dans l'architecture. D'un point de vue sécurité, la tendance est la même tant que les mécanismes de sécurité restent individuels (s'ils étaient mutualisés, on perdrait de l'intérêt de la liaison point-à-point).

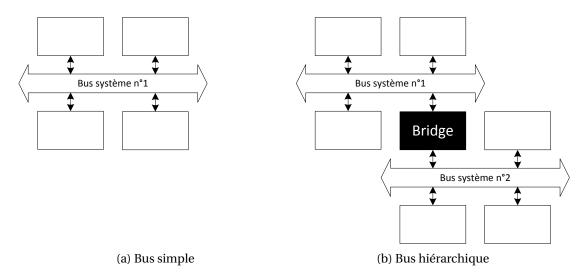

Dans un second temps, il existe des approches où le lien de communication est partagé entre les différents composants du système embarqué (voir figure 2.3a). Dans ce cas, la gestion des communications est réalisée par un arbitre [Poletti *et al.* 2003] qui est capable de choisir dans quel ordre les transactions doivent se dérouler en fonction d'une politique définie par le protocole choisi ou par l'utilisateur (par exemple : round-robin, priorité fixe...). Dans ces bus, il n'y a qu'une seule transaction à la fois. D'un point de vue architectural, les bus ont des limites quant au nombre de composants admis par chaque médium de communication (c'est-à-dire, le maximum qu'un arbitre est capable de gérer en même temps) qui dépendent du protocole choisi (PLB, AXI ...), on considère généralement que ces limites sont de l'ordre de 32 éléments par bus (d'après [Xilinx 2011a], on peut connecter jusqu'à 16 maîtres à 16 esclaves sur un bus AXI).

FIGURE 2.3 – Topologies de bus

Comme précédemment, on propose de calculer le nombre de liens L nécessaires pour connecter N éléments grâce à des bus AXI. On suppose qu'on travaille sur un bus simple : d'après [Xilinx 2011a], le nombre d'éléments maximum sur un lien est de 32. On a donc :

$$L = 1, \forall N \le 32 \tag{2.3}$$

La figure 2.4 présente l'évolution du nombre de liens en fonction du nombre d'éléments pour les liaisons point-à-point et bus AXI simple.

FIGURE 2.4 - Évolution du nombre de liens en fonction du nombre d'éléments

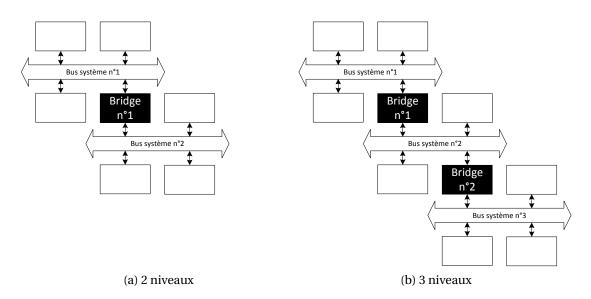

En termes de nombre de liens (par extension, en termes de surface), la solution par bus simple est beaucoup plus avantageuse. Pour des systèmes où le bus simple ne suffit plus, on peut utiliser des bus hiérarchiques qui sont une succession de bus simples interconnectés par des bridges (voir figure 2.5).

Le raisonnement pour connaître le nombre d'éléments maximum N sur un bus hiérarchique à L niveaux (c'est-à-dire à L bus simples) est le suivant. D'après la figure 2.5a, le bridge compte comme 1 élément sur chaque bus simple. Pour la structure à 3 niveaux (figure 2.5b), le bus n°2 possède 2 bridges. Par conséquent :

$$N=31+31+1=63 \quad \text{éléments dont 1 bridge pour} \quad L=2$$

$$N=31+30+31+2=94 \quad \text{éléments dont 2 bridges pour} \quad L=3$$

(2.4)

#### 2.1. Communications dans les architectures multiprocesseurs

FIGURE 2.5 – Bus hiérarchiques

Dans tous les cas, le coût en surface est moindre par rapport à une solution point-àpoint (voir figure 2.4) étant donné que les ressources pour transmettre les données

sont mutualisées. Par contre, on augmente la pénalité en termes de latence car les

transactions sur ce type de système doivent généralement être supervisées par un

arbitre de bus qui décide la priorité à donner à telle ou telle transaction. Pour les

technologies reconfigurables telles que les FPGAs, certains fabricants ont leur standard

(Avalon pour Altera...), d'autres utilisent un protocole open-source (Wishbone <sup>3</sup>),

d'autres exemples de protocoles sont donnés par [Mitic & Stojcev 2006] qui propose

une description et un comparatif des caractéristiques de chaque standard.

Chacun a ses avantages et ses inconvénients mais de part l'utilisation d'une plateforme Xilinx pour les implémentations ultérieures, le protocole de bus utilisé sera celui proposé par le fondeur Xilinx. En réalité, il en existe deux : PLB, un standard en phase de devenir obsolète implémenté dans les outils de développement du fabricant de FPGA Xilinx (et fourni par IBM).

<sup>3.</sup> Projet géré par Opencores: http://opencores.org/opencores, wishbone

Ce protocole dispose de deux bus:

- PLB (Processor Local Bus <sup>4</sup>), pour les transactions à haut-débit (processeurs, mémoires).

- OPB (On-chip Peripheral Bus), pour les transactions plus lentes (entrées, sorties).

AXI, la version actuelle sur la base d'un standard de ARM (c'est celui qu'on choisira dans la suite de ce manuscrit) se base également sur deux bus :

- AXI ([Xilinx 2011a, ARM 2012]), analogue à PLB.

- AXI-Lite, analogue à OPB.

#### 2.1.2 NoC

Pour des architectures manycores (contenant de nombreux éléments), on peut faire appel à des techniques s'inspirant des réseaux informatiques <sup>5</sup>.

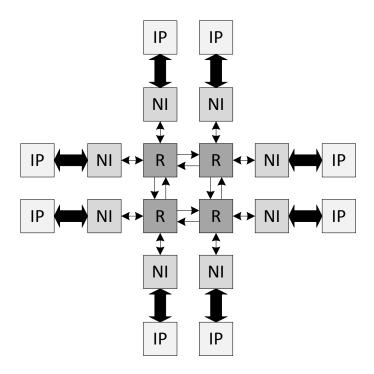

FIGURE 2.6 – Exemple d'architecture d'un réseau sur puce

<sup>4.</sup> http://www.xilinx.com/support/documentation/ip\_documentation/plb\_v46.pdf

<sup>5.</sup> http://en.wikipedia.org/wiki/Network\_On\_Chip

Les réseaux sur puce (NoC, *Network-on-Chip*) sont constitués de *routeurs* (R) et d'*interfaces réseaux* (NI) à la manière d'un réseau informatique avec ses routeurs et ses ordinateurs (qui représentent donc les différentes IP du système implanté sur le FPGA). Cette technologie est facilement extensible si un élément est rajouté dans l'architecture. Contrairement aux technologies de type bus, il n'y a pas de standard très répandu pour les systèmes embarqués dont l'architecture de communication est basée sur des réseaux sur puce. Généralement, ces réseaux sont souvent personnalisés pour satisfaire un besoin particulier : sécurité des transactions, adaptation du réseau aux modifications de l'environnement extérieur, architectures adaptées au haut-débit. Parmi celles-ci, on peut citer :

- SPIN [Adriahantenaina *et al.* 2003] : les précurseurs du NoC en 2003 au laboratoire LIP6.

- $-\mu$ Spider [Evain 2006] : un exemple du laboratoire Lab-STICC, pour des problématiques de contraintes de temps réel (un flot de conception est proposé dans cette optique).

- xPipes [Bertozzi & Benini 2006] : développé conjointement par les universités de Stanford et de Bologne, spécialisée dans les architectures gigacores (c'est-à-dire contenant de très nombreux éléments).

# 2.2 Travaux existants

Dans la littérature, plusieurs études se sont intéressées à la sécurité pour les systèmes embarqués [Ravi *et al.* 2004, Kocher *et al.* 2004]. Il en ressort que les mécanismes de sécurité peuvent se matérialiser sous deux formes : des blocs matériels ou des fonctions logicielles. Les solutions logicielles ne nécessitent généralement pas de modules matériels supplémentaires mais offrent des performances moindres en termes de latence par rapport à une solution purement matérielle. Par exemple, les auteurs de [Mencer *et al.* 1998] se sont intéressés à l'implémentation d'un algorithme de chiffrement pour les communications mobiles sur différentes technologies (DSP, FPGA, ASIC...) : il en ressort qu'une implémentation matérielle sur FPGA du chiffrement est environ 10 fois plus rapide qu'une implémentation sur DSP. La réactivité des mécanismes (c'est-à-dire le fait de bloquer l'attaque avant qu'elle ait le temps de se répandre dans le système) est essentielle pour garantir au système embarqué une protection efficace.

Les travaux existants dans le domaine de la protection des communications sont nombreux. Tout d'abord, on s'intéresse aux travaux sur les NoCs puis les bus. Dans un second temps, on exposera quelques solutions hybrides mélangeant des éléments matériels et logiciels. Enfin, comme la protection des mémoires fait aussi partie des points à observer, une vue d'ensemble de quelques solutions est donnée dans la dernière partie de cette section.

#### 2.2.1 NoC

Pour les architectures à grande échelle (c'est-à-dire contenant de nombreux éléments) avec une architecture basée sur un réseau sur puce, on considère l'étude de trois solutions existantes. Premièrement, Diguet et al. [Diguet et al. 2007] proposent une solution où les contrôles de sécurité sont effectués dans chaque interface de manière distribuée (figure 2.7).

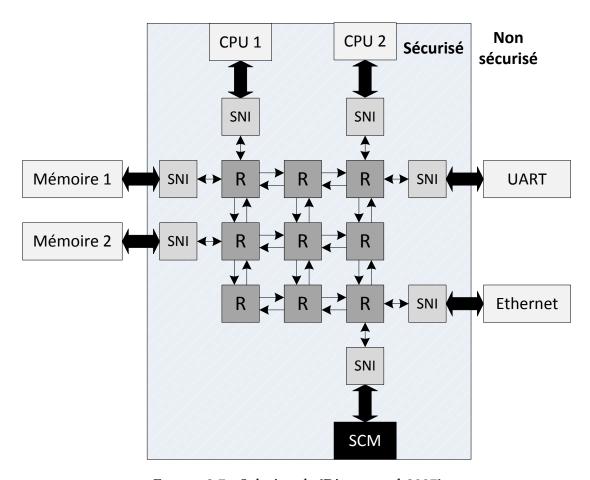

FIGURE 2.7 – Solution de [Diguet et al. 2007]

Les interfaces réseau SNI (Secured Network Interface) renvoient ensuite des informations à une unité de gestion SCM (Security and Configuration Manager) qui s'occupe des différentes configurations et des éventuelles contre-attaques; la mise à jour des mécanismes de sécurité est réalisée par des reconfigurations dynamiques partielles des mécanismes de sécurité. Les travaux proposés par [Diguet et al. 2007] s'intéressent à des scenarii tels que le détournement de processeur ou de méthodes de déni de service. Globalement, le modèle de menace comprend tout ce qui génère ces scenarii mais ne propose pas de chiffrement (par contre, il y a de l'authentification et de l'intégrité) et le modèle ne prend pas en compte les attaques physiques (injections de fautes, attaques par canaux cachés...). De plus, il est possible de mettre à jour les mécanismes de sécurité par une reconfiguration dynamique partielle des éléments concernés. Un des inconvénients de cette solution est qu'elle ne gère pas le chiffrement des mémoires : toutes les données stockées sont lisibles par un attaquant. A priori, les transmissions d'informations entre les interfaces SNI et le gestionnaire SCM se font par le NoC où transite également les données : il s'agit d'informations de natures différentes, il faudrait mieux qu'elles utilisent des canaux dédiés.

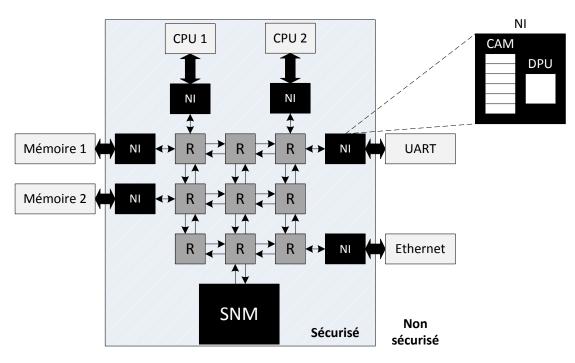

Fiorin et al. [Fiorin *et al.* 2007b, Fiorin *et al.* 2008b, Fiorin *et al.* 2008a] proposent une alternative à cette contribution en ajoutant des « capteurs » à l'intérieur de l'interface sécurisée pour améliorer la finesse des contrôles. Chaque interface sécurisée, considérée comme étant de confiance, est constituée d'un ensemble de sondes, d'unités de protection et d'un noyau dédié à la gestion du réseau de communication.

Ces sondes peuvent bloquer les transactions entrantes selon des paramètres stockés dans une mémoire addressable par contenu (CAM, Content-Adressable Memory) considérée de confiance. Un gestionnaire de la sécurité du système (Network Security Manager dans la figure 2.8) collecte les informations provenant des interfaces pour détecter les collisions et les erreurs dans le trafic de données. Contrairement à la solution proposée dans [Diguet et al. 2007], les mécanismes de la solution de Fiorin et al. peuvent être mis à jour sans reconfiguration partielle (ils sont mis à jour par une modification des règles contenues dans les mémoires CAM) mais ne contiennent pas de services cryptographiques qui permettent de chiffrer d'une manière ou d'une autre les données qui transitent par les interfaces sécurisées. Tout comme la solution précédente, les travaux de Fiorin et al. ont pour objectif de détecter les attaques qui provoquent des dénis de services et qui visent à extraire des informations confidentielles du système. Pour ce faire, des mécanismes sont implantés aux interfaces et permettent de filtrer les accès selon des règles prédéfinies.

FIGURE 2.8 – Solution de [Fiorin et al. 2007a]

La solution proposée par Fiorin et al. est basée sur une interface sécurisée avec un mécanisme nommé DPU (pour *Data Protection Unit*, voir figure 2.8). Ce mécanisme autorise ou non une transaction en fonction des paramètres stockés dans les mémoires de confiance. Dans cette implémentation, le module DPU ne suffit pas à protéger le système dans le cas où l'IP source de la transaction a été modifiée par un attaquant par l'une des deux méthodes suivantes :

- Modification du comportement de l'IP initiatrice de la transaction par modification de son code source ou une reconfiguration dynamique partielle. Par exemple, il peut s'agir d'un cas où un processeur veut effectuer des transactions qui ne respectent pas les règles imposées par la DPU. Le modèle de Fiorin et al. ne couvre pas la protection des mémoires contenant les codes et applications liées aux processeurs ainsi que la protection du canal de reconfiguration dynamique partielle par un port dédié (sous réserve que l'attaquant soit capable de faire un bitstream valide).

- Modification du contenu des mémoires CAM contenant les règles de sécurité. Si un attaquant est capable de modifier les valeurs des paramètres de sécurité liés aux interfaces DPU (écriture sur un autre port ou attaque matérielle provoquant des événements de type bitflip qui modifient la valeur d'un ou plusieurs bits de la mémoire).

Compte tenu du cahier des charges proposé dans leurs travaux, Fiorin et al. sont capables de détecter des attaques de type déni de service mais ne peuvent pas anticiper la modification d'une IP en amont par un attaquant.

Enfin, concernant les travaux relatifs à la sécurité dans les NoC, on peut également citer les travaux de Sepulveda et al. ([Sepulveda et al. 2012b, Sepulveda et al. 2012a]).

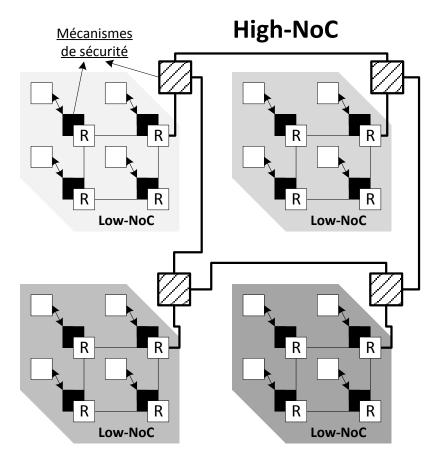

FIGURE 2.9 – Solution de [Sepulveda et al. 2012b]

Là où les travaux cités précédemment s'attachaient à la protection d'un seul NoC, la structure proposée par Sepulveda et al. permet de définir une certaine hiérarchie de la sécurité appliquée au système. Concrètement, sur la figure 2.9, on distingue deux catégories de NoC : les *low-NoC* et les *high-NoC*, chacun *low-NoC* a sa propre politique de sécurité. Par conséquent, le NoC hiérarchique proposé ici permet de définir un ensemble de NoCs plus simples, chacun pouvant être régi par des paramètres de sécurité différents : le NoC principal (ou *high-NoC*) permet alors de gérer le trafic qui vient de ses différents clusters.

#### Chapitre 2. État de l'art

Le panel d'attaques qui peut être couvert par la solution de [Sepulveda *et al.* 2012b] est assez large : les mécanismes de sécurité proposés permettent de vérifier les droits d'accès et également d'avoir un contrôle de l'authentification des données ; on pourrait donc détecter les scenarii de type *hijacking* où les processeurs sont détournés de leur fonction première ou tout ce qui relève de l'extraction d'informations confidentielles. Comme dans les solutions précédentes, comme le NoC hiérarchique et ses mécanismes de protection sont considérés comme étant de confiance, les attaques proviennent de l'extérieur (entrées-sorties ou mémoires). Par contre, cette solution ne possède pas non plus de fonction de chiffrement des données. Enfin, les attaques par déni de service (dans le sens de production de données à des fréquences surélevées) ne sont a priori pas détectées : des séries de paquets sont insérées sur le réseau mais avec des droits d'accès corrects (par exemple, en modifiant le contenu d'une mémoire contenant du code processeur).

#### 2.2.2 Bus

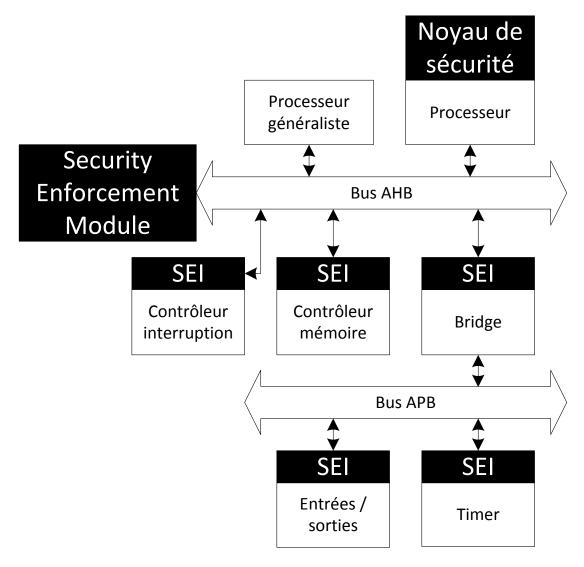

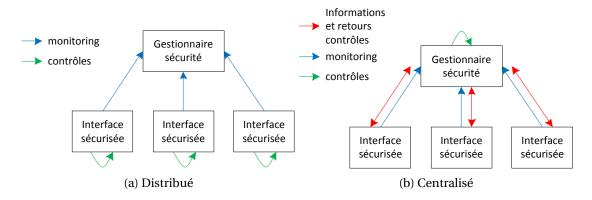

Pour les systèmes multiprocesseurs ayant une architecture de communication à base de bus, la contribution majeure a été publiée par Coburn[Coburn *et al.* 2005] (voir figure 2.10). Cette approche est similaire aux travaux de Fiorin[Fiorin *et al.* 2007a, Fiorin *et al.* 2007b, Fiorin *et al.* 2008b, Fiorin *et al.* 2008a], elle est basée sur des interfaces réseaux avec des mécanismes de sécurité additionnels nommés SEI (*Security Enforcement Module*) implémentés entre chaque IP et le bus système. Chaque SEI va extraire des informations de l'IP et du bus qui permettent de définir ou non si la transaction courante est valide (c'est-à-dire si elle respecte les contraintes de sécurité du système). La principale contrainte de cette solution est que ces informations sont renvoyées à un gestionnaire centralisé qui est lui seul responsable de faire les opérations qui permettront finalement de bloquer ou non une transaction. Le surcoût en latence va donc forcément être augmenté, et donc provoquer des perturbations dans les communications au sein du système multiprocesseur (voir la comparaison sur les approches distribuée et centralisée dans le chapitre 5).

$\label{eq:figure 2.10-Solution} Figure \ 2.10-Solution \ de \ Coburn \ et \ al. \ sur \ une \ architecture \ multiprocesseur \ générique$

Cette solution ne propose pas la mise à jour des règles de sécurité ni de fonction cryptographique. Par contre, elle paraît la plus complète sur le modèle de menace pris en compte (même s'il n'est pas clairement exposé dans l'article) : les accès ainsi que la valeur de données spécifiées par le concepteur peuvent être contrôlés, enfin le module de contrôle de séquence SPU (*Sequence Protection Unit*) permet quant à lui de détecter des séquences d'attaques non désirées : le terme est assez large, il permet d'englober les attaques de type déni de services ou détournement du fonctionnement de processeurs.

L'approche proposée par Coburn et al. suggère de centraliser les contrôles au sein d'un gestionnaire de la sécurité du système (SEM, *Security Enforcement Manager*). Autrement dit, dès lors que ce gestionnaire est corrompu, il est possible de mettre hors d'usage le système : le SEM est un bloc matériel qui, sous certaines conditions peut être remplacé par une version corrompue grâce à une reconfiguration dynamique partielle (sous réserve que l'attaquant soit capable de produire un bitstream valide). Tout comme la solution proposée par Fiorin et al. [Fiorin *et al.* 2008b], les paramètres qui permettent de définir telle ou telle règle de sécurité sont stockés dans des mémoires qui peuvent être attaquées soit par une attaque matérielle (par exemple, une attaque électromagnétique) soit par un port non utilisé de la mémoire contenant les paramètres de sécurité.

# 2.2.3 Codesign logiciel-matériel

Pour protéger le système contre un modèle d'attaque prédéfini, d'autres solutions proposent une séparation physique des composants afin de définir des zones sécurisées et non sécurisées. Par exemple, les auteurs de [Huffmire *et al.* 2008] utilisent une séparation physique de certains blocs (nommés *moats*) durant le placement-routage où le routage est interdit, ce qui permet d'isoler certaines zones du FPGA; d'autres modules (nommés *drawbridges*) permettent alors de réaliser des ponts sécurisés entre les différentes zones isolées du FPGA.

D'autres contributions proposent de combiner des éléments matériels à des éléments logiciels pour fournir des procédures de sécurité au système cible. Les travaux de Porquet [Porquet 2010] et de Plouviez [Plouviez 2011] se sont concentrés sur une solution de ce type : les auteurs proposent un mécanisme pour gérer plusieurs logiciels de manière sécurisée sur une architecture hétérogène où l'espace mémoire est partagé et protégé.

Le module logiciel *Global Trusted Agent* est en charge de définir les droits d'accès de chaque logiciel à l'espace mémoire alors que la partie matérielle est distribuée autour du réseau d'interconnexion afin d'analyser les différentes transactions et de vérifier qu'elles soient bien en accord avec les droits d'accès logiciels.

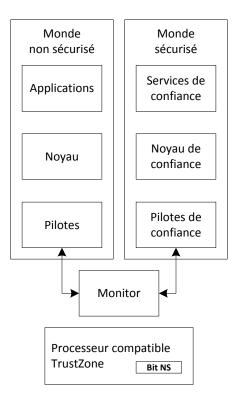

ARM a proposé son propre protocole, Trustzone [Xu *et al.* 2008], qui permet deux zones dont l'une est plus « privilégiée » que l'autre : cela peut être par exemple, une zone dédiée au noyau du système d'exploitation et une autre pour les applications sensibles telles que les problématiques d'authentification ou d'allocation mémoire. Un module matériel est en charge de surveiller que les données ne passent pas d'une zone à l'autre (le module *Monitor* dans la figure 2.11) et que, si nécessaire, les communications soient protégées (différenciation des deux modes par un bit de décision, le bit NS pour *Non-Secure bit* stocké dans un registre d'un coprocesseur).

FIGURE 2.11 – Architecture de la solution Trustzone

#### 2.2.4 Protection de la mémoire externe

D'après les travaux précédemment décrits, la protection des mémoires est un autre point sensible du développement de système à microprocesseurs. Ces systèmes sont soumis à de nombreuses attaques [Elbaz *et al.* 2006b]. La protection des mémoires en termes de confidentialité n'est pas suffisante : les attaques de type rejeu, relocation et spoofing (voir chapitre 3) peuvent malgré tout permettre d'interagir avec le système lorsqu'un processeur effectue des requêtes vers la mémoire. Par conséquent, il faut utiliser d'autres propriétés telles que l'intégrité et l'authentification afin de protéger les mémoires contre un panel d'attaques plus large.

XOM ([Lie *et al.* 2003]) est une solution qui permet de combiner la confidentialité et l'intégrité dans un système multiprocesseur où la mémoire externe n'est pas sécurisée : par conséquent, si le système d'exploitation est stocké en externe, il n'est pas de confiance. L'implémentation d'un tel système suppose que la structure du processeur soit modifiée en plus d'y ajouter des fonctions matérielles : l'impact en performances est assez important puisque les auteurs de [Lie *et al.* 2003] énoncent une perte de 50%.

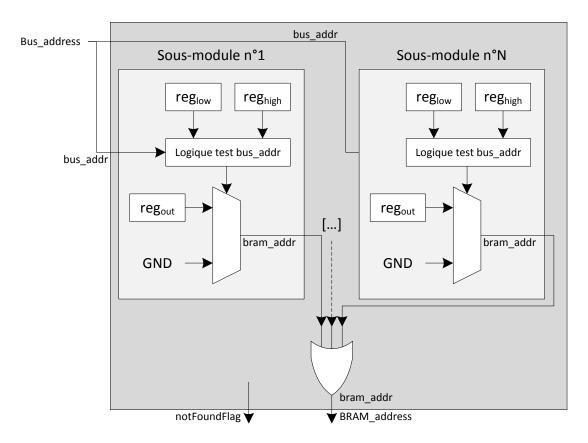

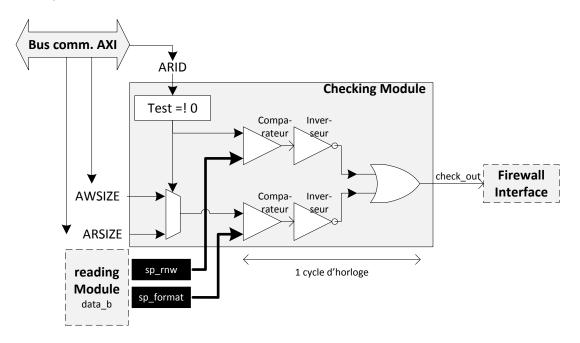

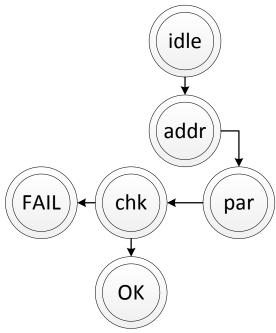

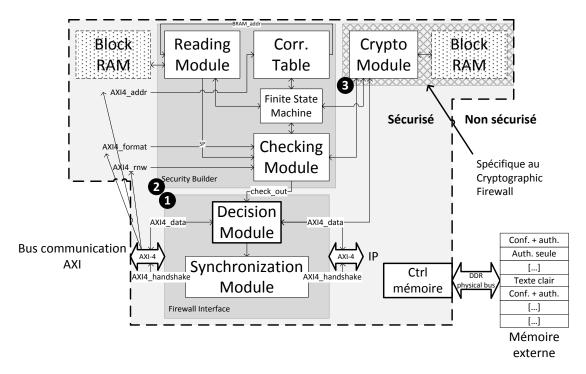

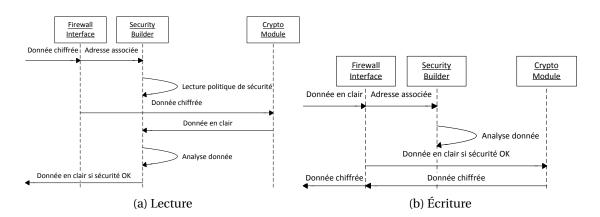

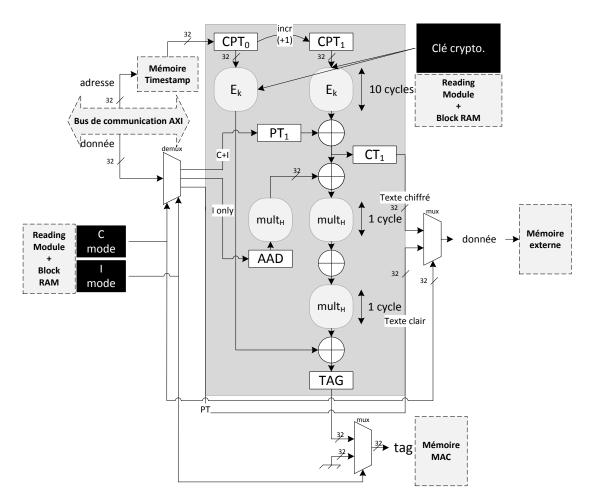

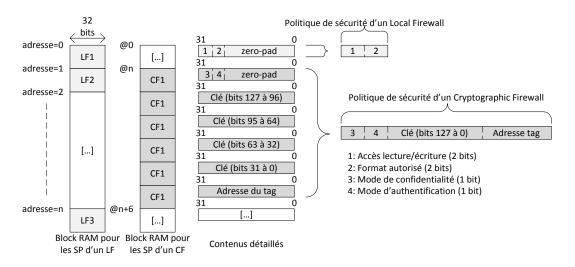

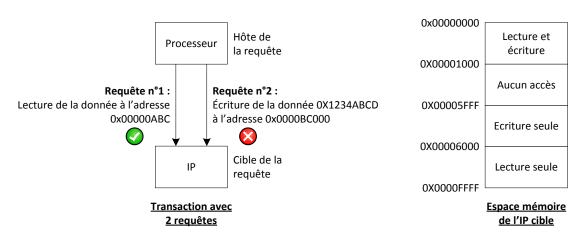

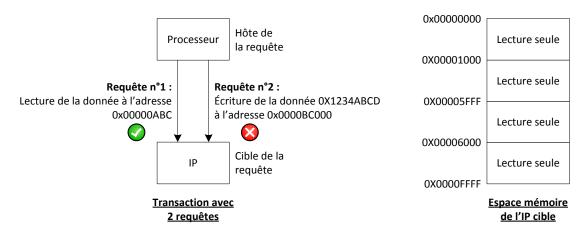

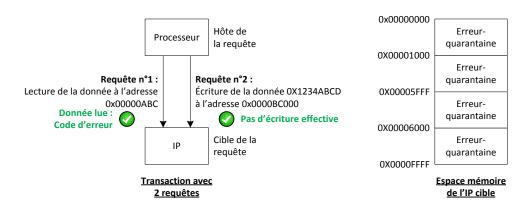

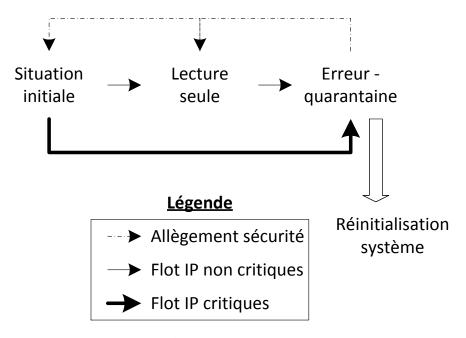

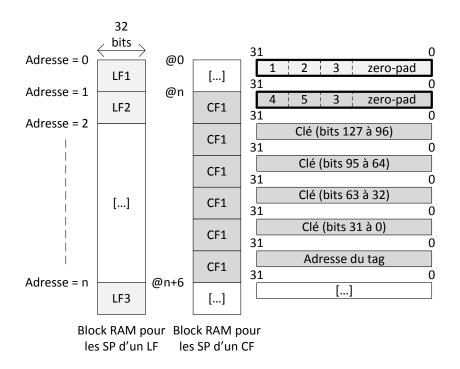

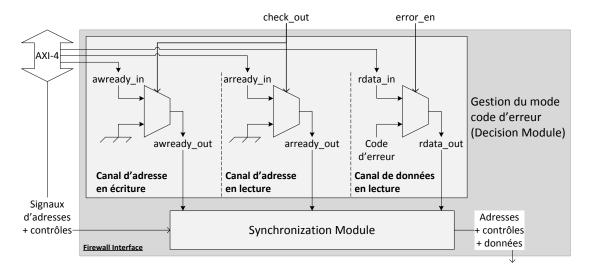

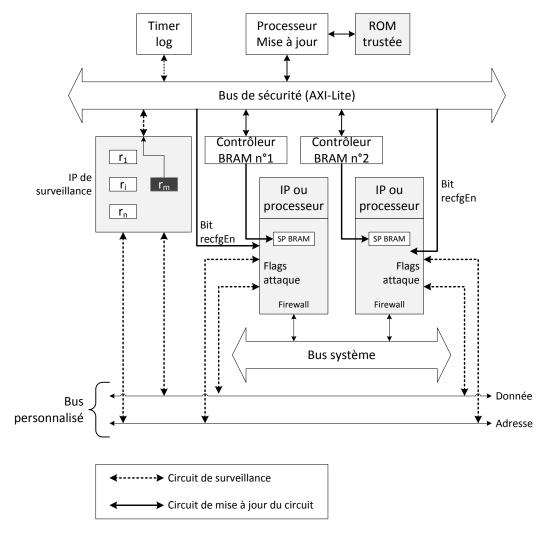

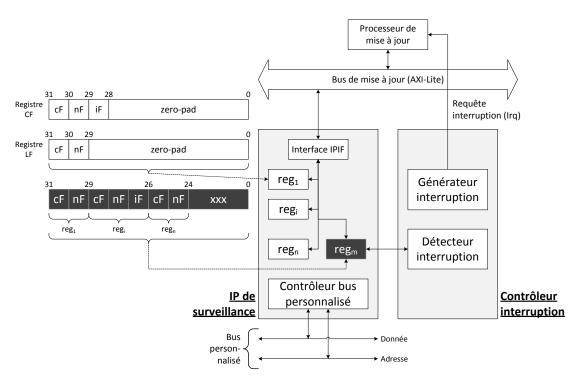

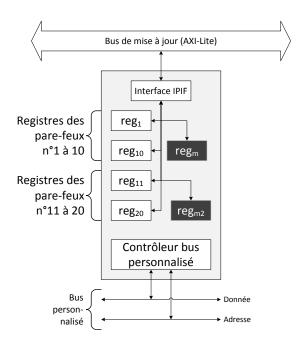

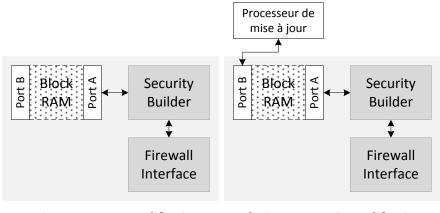

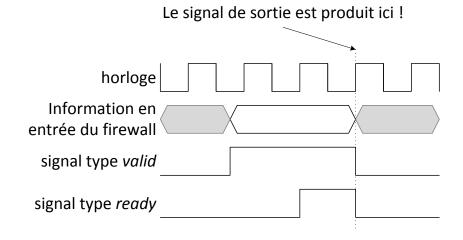

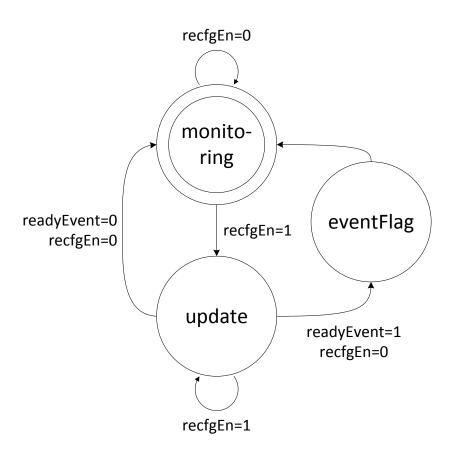

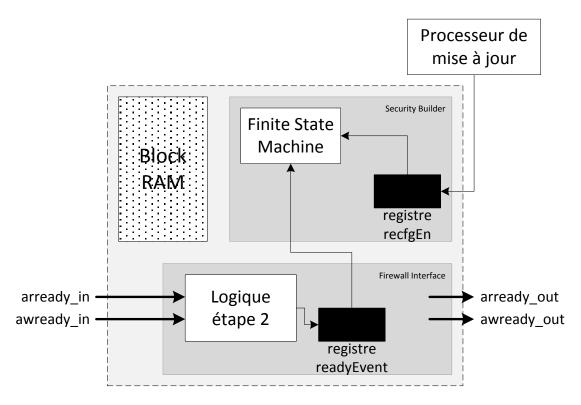

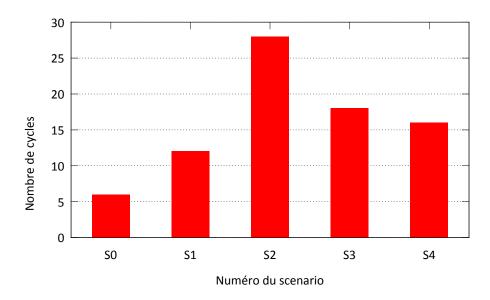

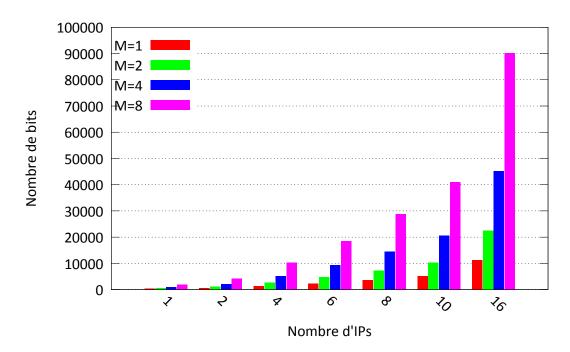

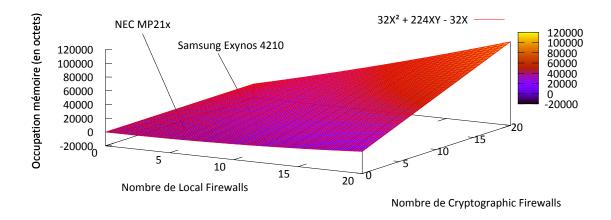

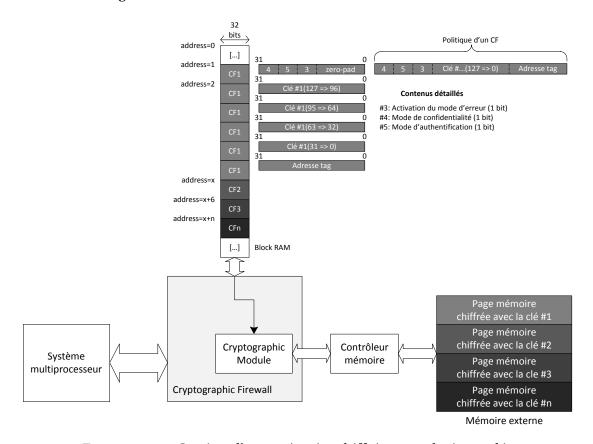

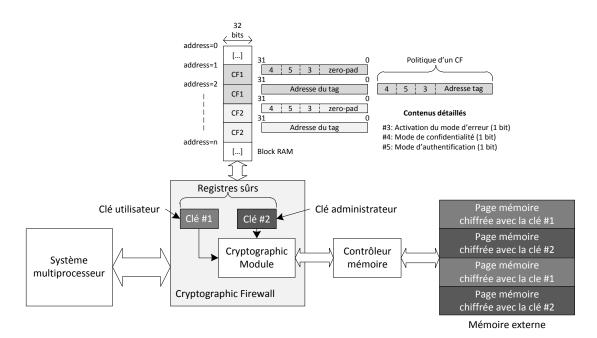

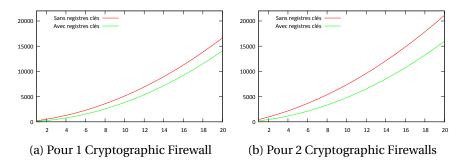

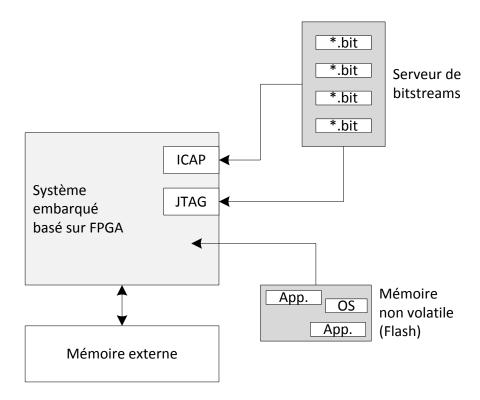

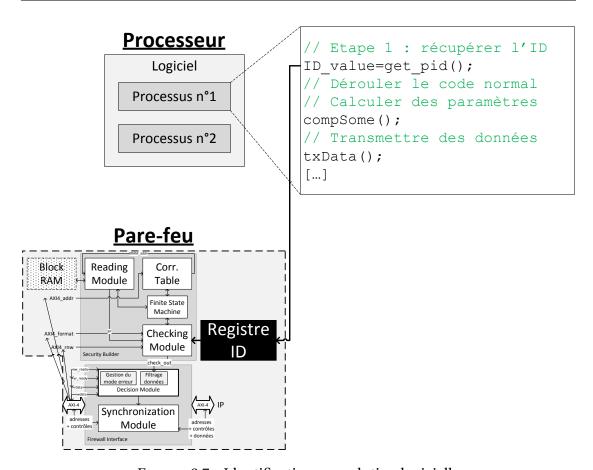

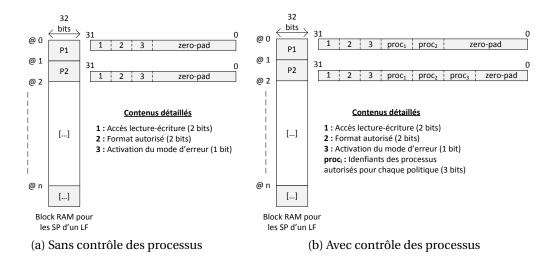

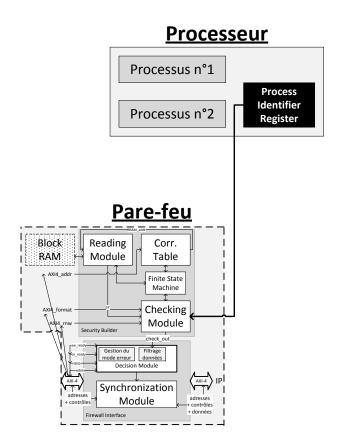

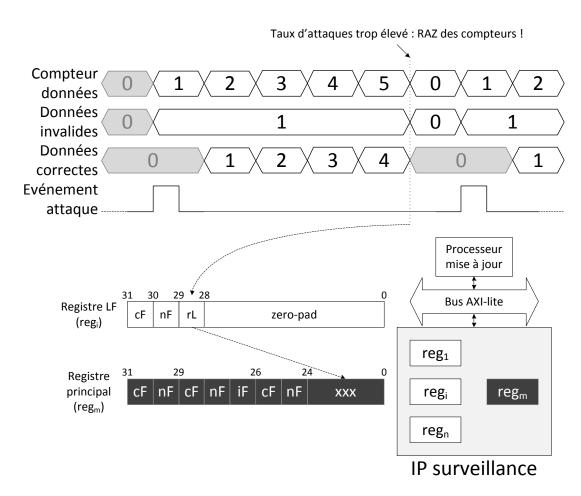

L'architecture AEGIS ([Suh 2005]) est basée sur un processeur sécurisé qui contient également des fonctions de confidentialité et d'intégrité : tout ce qui sort ou rentre dans le processeur est sécurisé. En dehors du processeur, tout est considéré comme n'étant pas de confiance (et donc soumis à des attaques physiques et logicielles) : les mémoires, les entrées-sorties... Selon les configurations (taille des caches du processeur), la perte en performances va de 3,8% (taux de cache miss pour les données de 6,25%) à 130% (implémentation du processeur sans caches).