## Towards Optimized Flexible Multi-ASIP Architectures for LDPC/Turbo Decoding

Purushotham Murugappa Velayuthan

#### ▶ To cite this version:

Purushotham Murugappa Velayuthan. Towards Optimized Flexible Multi-ASIP Architectures for LDPC/Turbo Decoding. Electronics. Télécom Bretagne, Université de Bretagne-Sud, 2012. English. NNT: . tel-00811941

#### HAL Id: tel-00811941 https://theses.hal.science/tel-00811941v1

Submitted on 11 Apr 2013

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

$N^o$  d'ordre : 2012telb0260

Sous le sceau de l'Université européenne de Bretagne

#### TÉLÉCOM BRETAGNE

#### EN HABILITATION CONJOINTE AVEC L'UNIVERSITÉ DE BRETAGNE-SUD

#### ECOLE DOCTORALE -SICMA

Mention: STIC (Sciences et Technologies de l'Information et de la Communication)

par

#### Purushotham Murugappa Velayuthan

# Towards Optimized Flexible Multi-ASIP Architectures for LDPC/Turbo Decoding

soutenue le 17 décembre 2012 devant la commission d'examen :

#### Composition du Jury :

Président : M. Guy Gogniat, Professeur à l'Université de Bretagne-Sud

Rapporteurs: M. Gerd Ascheid, Professeur à l'Université RWTH Aachen

M. François Verdier, Professeur à l'Université de Nice

Examinateurs: M. Gilles Sassatelli, Directeur de Recherche CNRS au LIRMM

M. Fabien Clermidy, Ingénieur chercheur (HDR) au CEA-LETI

Directeur : M. Michel Jézéquel, Professeur à Télécom Bretagne

Encadrant: M. Amer Baghdadi, Professeur à Télécom Bretagne

To life and its infinite possibilities.

## Acknowledgements

First, I would like to express my gratitude to my supervisor Amer Baghdadi, for his constant motivation and patience during this entire thesis work. I also thank him for both personal and technical help that he graciously offered irrespective of the time of the day it was needed. I always will cherish the freedom he offered (as well as the pressure he exerted at times) in bringing out the best in me. I also thank him for the kindness that he showed during those endless arguments, discussions and obvious misunderstandings that we have had.

I would also like to thank Michel Jézéquel, the director of my thesis for his support during this period.

I extend my gratitude to my collegues Atif, Rachid, Camilo, Jean-Noel and many others to have supported me and made me feel welcomed every day at work. A special thanks also goes to my dear friends Ashwani and Tarini (and many more from/in various parts of the world) to have tirelessly counselled me to uplift my spirits whenever I felt down.

Lastly, it's a pleasure to thank my family in India for having stood by me through thick and thin. They have always encouraged me to pursue my dreams no matter how weird it seemed.

## **Contents**

| A  | cknow | vledgem | nents                                             | iii |

|----|-------|---------|---------------------------------------------------|-----|

| In | trodu | ction   |                                                   | 1   |

| 1  | Bac   | kgroun  | d: Channel Codes and Decoding Algorithms          | 7   |

|    | 1.1   | Comm    | nunication system overview                        | 8   |

|    | 1.2   | Turbo   | codes                                             | 10  |

|    |       | 1.2.1   | Recursive Systematic Convolutional codes          | 11  |

|    |       | 1.2.2   | Turbo Code Interleaver                            | 14  |

|    |       |         | 1.2.2.1 Almost regular permutation (ARP)          | 14  |

|    |       |         | 1.2.2.2 Quadratic polynomial permutation (QPP)    | 15  |

|    | 1.3   | Turbo   | decoding                                          | 15  |

|    |       | 1.3.1   | Maximum Aposteriori Probability (MAP) algorithm   | 17  |

|    |       | 1.3.2   | Max-Log-MAP approximation                         | 18  |

|    |       | 1.3.3   | Max-Log-MAP for Turbo decoding                    | 19  |

|    |       | 1.3.4   | Parallelism in Turbo decoding                     | 20  |

|    |       |         | 1.3.4.1 Metric level parallelism                  | 21  |

|    |       |         | 1.3.4.2 SISO decoder level parallelism            | 23  |

|    |       |         | 1.3.4.3 Turbo decoder level parallelism           | 25  |

|    | 1.4   | Low D   | Density Parity Check codes                        | 25  |

|    |       | 1.4.1   | Linear block codes                                | 26  |

|    |       | 1.4.2   | QC-LDPC codes                                     | 27  |

|    |       | 1.4.3   | LDPC in WiFi and WiMAX standard                   | 29  |

|    | 1.5   | Low D   | Density Parity Check decoding                     | 29  |

|    |       | 1.5.1   | LDPC decoding algorithm: Normalized Min-Sum (NMS) | 30  |

|    |       | 1.5.2   | Scheduling                                        | 31  |

|    |       | 1.5.3   | Modified NMS formulation for implementation       | 32  |

|    | 1.6   | Summ    | arv                                               | 33  |

vi CONTENTS

| 2 | ASI | P Desig | n Methodo           | logy and State of the Art in Channel Decoder Design                                      | 35 |

|---|-----|---------|---------------------|------------------------------------------------------------------------------------------|----|

|   | 2.1 | Custor  | nizable emb         | pedded processors                                                                        | 36 |

|   |     | 2.1.1   | Application         | on-Specific Instruction-set Processors                                                   | 37 |

|   |     | 2.1.2   | ADL-bas             | ed design tool: Processor designer                                                       | 37 |

|   |     | 2.1.3   | Classical A         | ASIP design flow                                                                         | 40 |

|   | 2.2 | State o | of the art in       | channel decoder design                                                                   | 41 |

|   |     | 2.2.1   | Turbo dec           | oding architectures                                                                      | 41 |

|   |     | 2.2.2   | LDPC dec            | coding architectures                                                                     | 42 |

|   |     | 2.2.3   | Multi-cod           | e channel decoding architectures                                                         | 44 |

|   | 2.3 | Initial | ASIP archit         | tecture for flexible Turbo decoding                                                      | 46 |

|   |     | 2.3.1   | Overview            | of the TurbASIP architecture                                                             | 46 |

|   |     | 2.3.2   | TurbASIP            | pipeline                                                                                 | 47 |

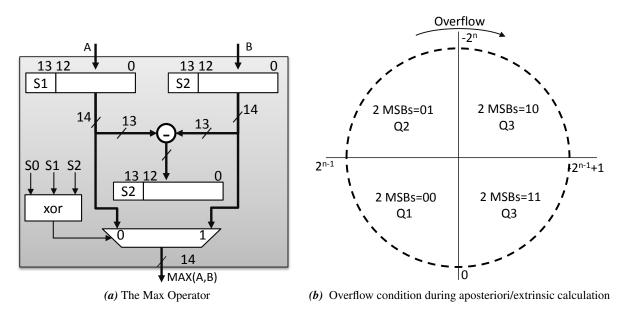

|   |     | 2.3.3   | Max and 1           | modulo operators                                                                         | 49 |

|   |     | 2.3.4   | TurbASII            | P: sample assembly code                                                                  | 50 |

|   |     | 2.3.5   | Memory p            | partitions                                                                               | 53 |

|   |     | 2.3.6   | ASIC syn            | thesis results                                                                           | 53 |

|   | 2.4 | Summ    | ary                 |                                                                                          | 55 |

| 3 | Dec | ASIP: F | lexible Tur         | rbo/LDPC Decoder                                                                         | 57 |

|   | 3.1 | Design  | n motivation        | ns                                                                                       | 58 |

|   |     | 3.1.1   | Architectu          | re Efficiency                                                                            | 59 |

|   |     | 3.1.2   | Quantizati          | ion analysis                                                                             | 60 |

|   | 3.2 | DecAS   | $\mathrm{SIP}_{v1}$ |                                                                                          | 62 |

|   |     | 3.2.1   | System ar           | chitecture                                                                               | 62 |

|   |     | 3.2.2   | Turbo mo            | de                                                                                       | 63 |

|   |     |         | 3.2.2.1             | Memory architecture                                                                      | 63 |

|   |     |         | 3.2.2.2             | Processing schedule                                                                      | 64 |

|   |     |         | 3.2.2.3             | Pipeline architecture                                                                    | 64 |

|   |     |         | 3.2.2.4             | Interleave/deinterleave address generation                                               | 65 |

|   |     |         | 3.2.2.5             | NoC messages                                                                             | 67 |

|   |     |         | 3.2.2.6             | Assembly code                                                                            | 68 |

|   |     | 3.2.3   | LDPC mo             | ode                                                                                      | 71 |

|   |     |         |                     | Proposed scheduling illustrated with simple example using 2-DecASIP $_{v1}$ architecture | 71 |

|   |     |         |                     | Proposed scheduling with 8-DecASIP $_{v1}$ architecture                                  | 73 |

|   |     |         |                     | Memory architecture                                                                      | 80 |

|   |     |         | 3.2.3.4             | NoC messages                                                                             | 82 |

|   |     |         | 3.2.3.5             | Pipeline architecture and assembly Code                                                  | 82 |

CONTENTS

|   |     | 3.2.4  | ASIC synthesis results                                        |

|---|-----|--------|---------------------------------------------------------------|

|   | 3.3 | DecAS  | $SIP_{v2}$                                                    |

|   |     | 3.3.1  | System architecture                                           |

|   |     | 3.3.2  | Turbo mode                                                    |

|   |     | 3.3.3  | LDPC mode                                                     |

|   |     |        | 3.3.3.1 NoC messages and NoC schedule                         |

|   |     |        | 3.3.3.2 LDPC assembly code                                    |

|   |     | 3.3.4  | Configuration memory                                          |

|   |     | 3.3.5  | ASIC synthesis results                                        |

|   |     | 3.3.6  | Discussions and analysis of recent related implementations    |

|   | 3.4 | Summ   | ary                                                           |

|   | EDC |        | AGICD 4.4 . CD AGID                                           |

| 4 |     |        | ASIC Prototyping of DecASIP 101                               |

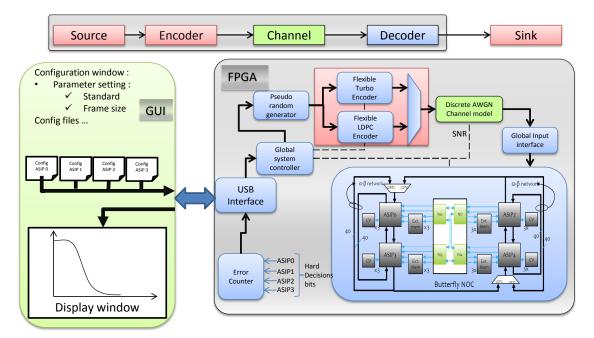

|   | 4.1 |        | lew of the proposed FPGA 4-DecASIP system prototype           |

|   | 4.2 |        | le channel encoder                                            |

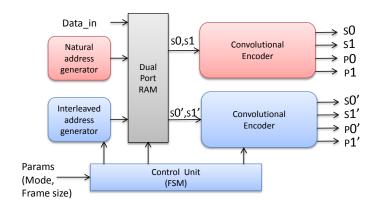

|   |     | 4.2.1  | Flexible Turbo encoder                                        |

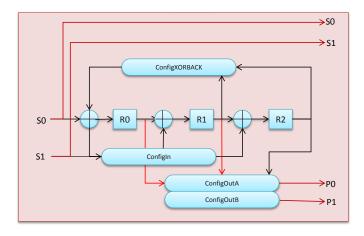

|   | 4.0 | 4.2.2  | Flexible LDPC encoder                                         |

|   | 4.3 |        | le Turbo/LDPC decoder                                         |

|   | 4.4 |        | blocks of the system prototype                                |

|   |     | 4.4.1  | Pseudo random generator                                       |

|   |     | 4.4.2  | Flexible channel model                                        |

|   |     | 4.4.3  | Global input interface                                        |

|   |     | 4.4.4  | Error counter                                                 |

|   |     | 4.4.5  | Configuration module                                          |

|   |     | 4.4.6  | Global system controller                                      |

|   |     | 4.4.7  | Graphical User Interface (GUI)                                |

|   |     | 4.4.8  | USB interface                                                 |

|   | 4.5 |        | s of the FPGA prototype                                       |

|   |     | 4.5.1  | FPGA synthesis results                                        |

|   |     | 4.5.2  | Speed of reconfiguration between different decoding modes 110 |

|   |     | 4.5.3  | Scalability and throughput                                    |

|   |     | 4.5.4  | Performance results                                           |

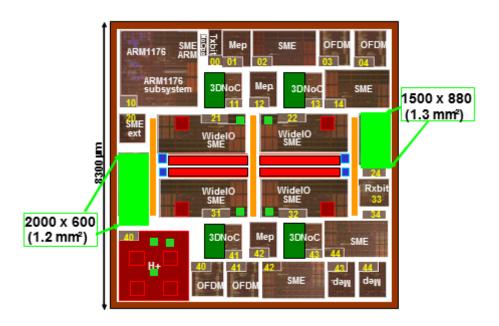

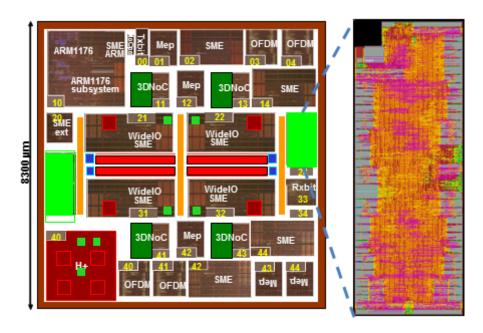

|   | 4.6 | ASIC i | integration of DecASIP                                        |

|   |     | 4.6.1  | MAG3D chip from CEA-LETI                                      |

|   |     | 4.6.2  | Integration constraints                                       |

|   |     | 4.6.3  | ASIC integration results                                      |

|   | 4.7 | Summ   | ary                                                           |

VIII

| 5  | TDe                     | ecASIP: Parameterized Turbo Decoder                  | 117 |

|----|-------------------------|------------------------------------------------------|-----|

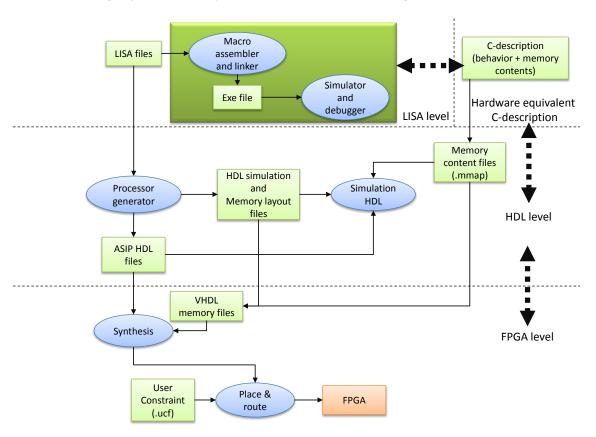

|    | 5.1                     | Proposed design flow for parameterized cores         | 118 |

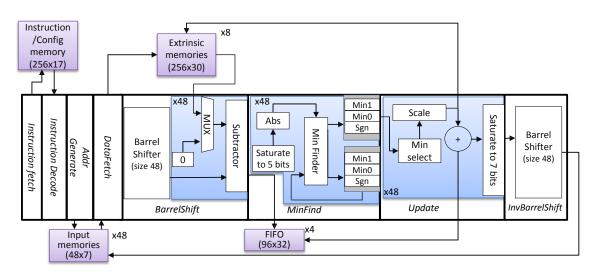

|    | 5.2                     | Design choices and TDecASIP decoder architecture     | 119 |

|    |                         | 5.2.1 Design choices                                 | 119 |

|    |                         | 5.2.2 TDecASIP decoder architecture                  | 121 |

|    |                         | 5.2.2.1 Pipeline control finite state machine        | 123 |

|    |                         | 5.2.2.2 Pipeline architecture                        | 124 |

|    |                         | 5.2.3 Memory organization                            | 124 |

|    | 5.3                     | FPGA prototype and synthesis results                 | 125 |

|    | 5.4                     | ASIC synthesis results                               | 126 |

|    | 5.5                     | Summary                                              | 128 |

| 6  | LDe                     | ecASIP: LDPC Decoder                                 | 129 |

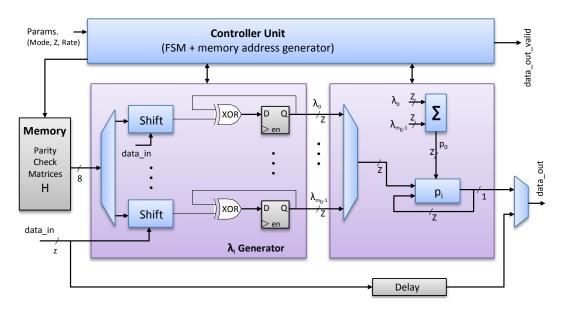

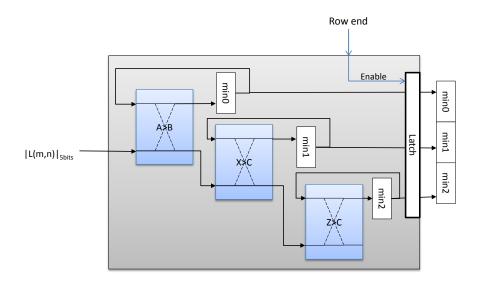

|    | 6.1                     | Design motivations and LDecASIP decoder architecture | 130 |

|    | 6.2                     | Prototype and incremental feature addition           | 132 |

|    | 6.3                     | FPGA and ASIC synthesis results                      | 133 |

|    | 6.4                     | Summary                                              | 135 |

| Co | onclus                  | sions and Perspectives                               | 137 |

| Ré | sumé                    | en Français                                          | 141 |

| Gl | ossar                   | $\mathbf{y}$                                         | 147 |

| No | tatio                   | ns                                                   | 151 |

| Bi | bliogi                  | raphy                                                | 153 |

| Li | List of publications 16 |                                                      |     |

## **List of Figures**

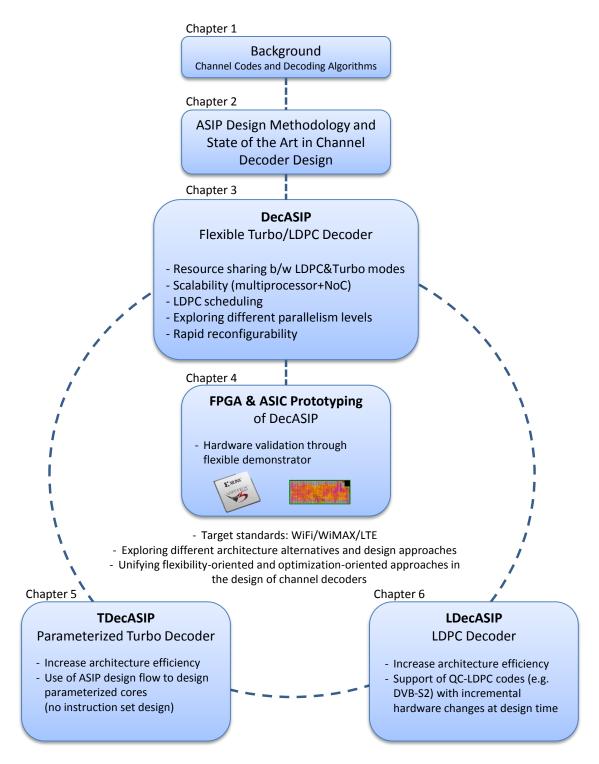

| 1    | Overview of the thesis outline and contributions                                                | 4  |

|------|-------------------------------------------------------------------------------------------------|----|

| 1.1  | Digital communication system model                                                              | 8  |

| 1.2  | Bit error rate performance of a Turbo code w.r.t. channel capacity and other conventional codes | 9  |

| 1.3  | Serial concatenated code structure                                                              | 10 |

| 1.4  | Parallel RSC Turbo encoder structure                                                            | 10 |

| 1.5  | Examples of Non systematic and Systematic convolutional codes                                   | 11 |

| 1.6  | Recursive systematic codes (RSC)                                                                | 13 |

| 1.7  | Trellis diagram of encoder of Figure 1.6b                                                       | 13 |

| 1.8  | Classical Turbo decoder structure                                                               | 16 |

| 1.9  | Turbo decoding: Forward-Backward schedule                                                       | 21 |

| 1.10 | Turbo decoding: Butterfly schedule                                                              | 22 |

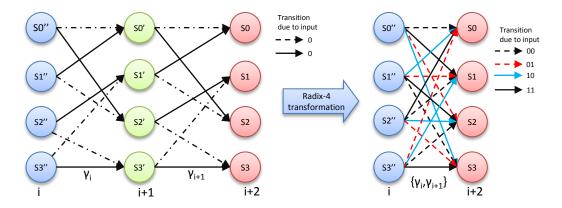

| 1.11 | Radix-4 trellis compression                                                                     | 22 |

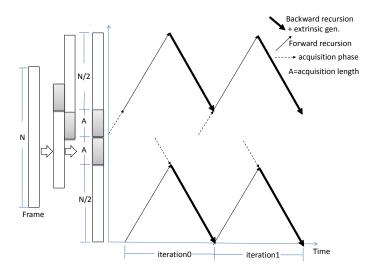

| 1.12 | Sub-blocking with initialization through acquistion                                             | 23 |

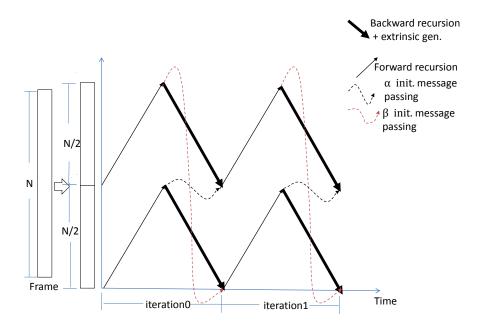

| 1.13 | Sub-blocking with initialization through message passing                                        | 24 |

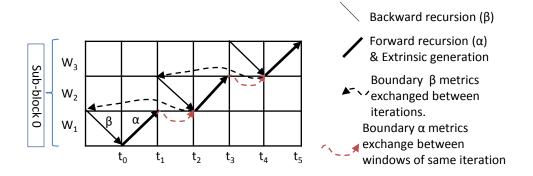

| 1.14 | Sub-blocking and windowing with initialization through message passing                          | 25 |

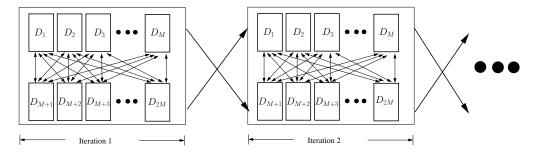

| 1.15 | Turbo decoding: Shuffled decoding strategy, where $D_x$ = SISO decoders x=1,2,                  | 25 |

| 1.16 | Linear block code mapping example for (n=3, k=2) $\dots \dots \dots$                            | 26 |

| 1.17 | Linear block code generator matrix $G$ and parity check matrix $H$ for (n=7,k=4)                | 27 |

| 1.18 | Tanner graph of H matrix in 1.17                                                                | 27 |

| 1.19 | LDPC check matrix representations: $H_{base}$                                                   | 28 |

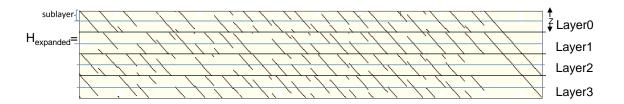

| 1.20 | LDPC check matrix representations: $H_{expanded}$ form of 1.19                                  | 28 |

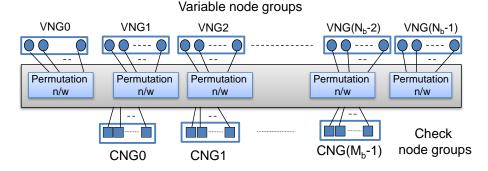

| 1.21 | LDPC check matrix representations: Generalised Tanner graph representation of LDPC H-matrix     | 28 |

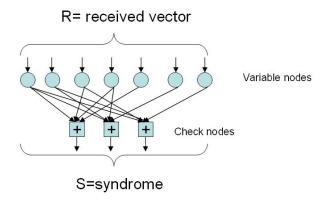

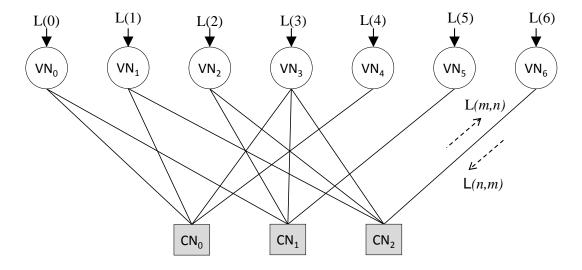

| 1.22 | Tanner graph example showing the two-phase message passing decoding                             | 30 |

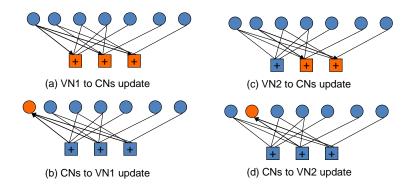

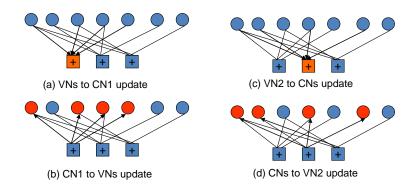

| 1.23 | LDPC decoding using vertical schedule                                                           | 32 |

| 1 24 | I DPC decoding using horizontal schedule                                                        | 32 |

X LIST OF FIGURES

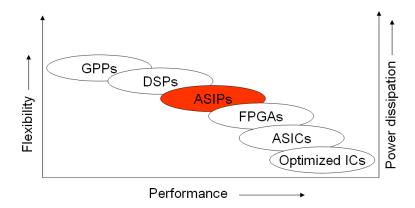

| 2.1  | Comparison of performance, flexibility and power dissipation trade-off of implementation methods                                                                                                                                                                              |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

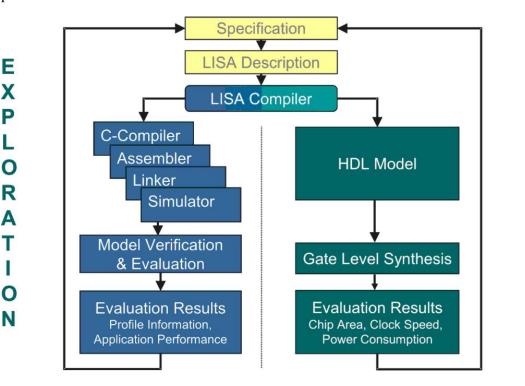

| 2.2  | LISA-based ASIP architecture exploration flow                                                                                                                                                                                                                                 |

| 2.3  | LISA-based ASIP architecture design flow                                                                                                                                                                                                                                      |

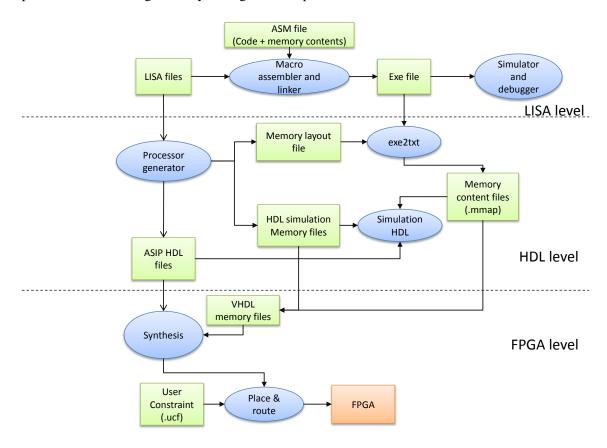

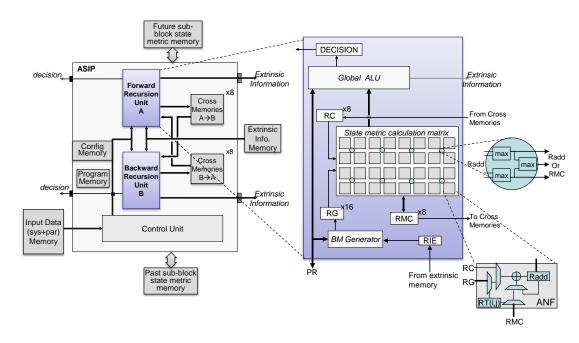

| 2.4  | TurbASIP architecture                                                                                                                                                                                                                                                         |

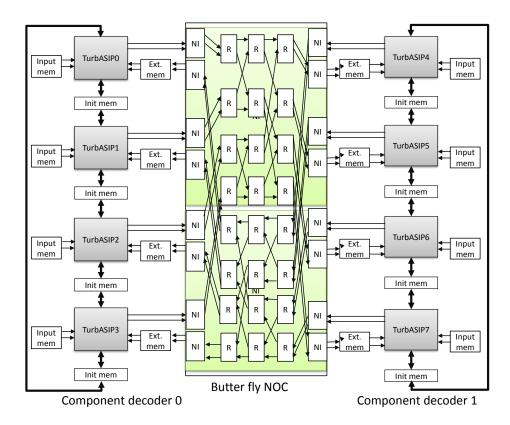

| 2.5  | Multi-TurbASIP architecture                                                                                                                                                                                                                                                   |

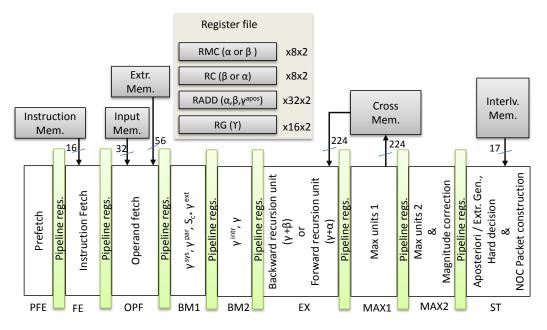

| 2.6  | Overview of the TurbASIP pipeline stages along with its register file and memory banks                                                                                                                                                                                        |

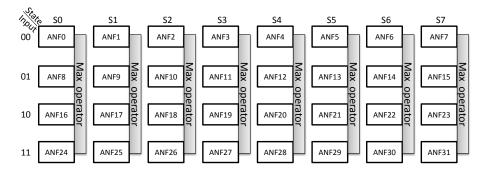

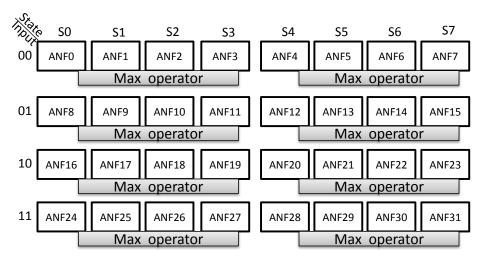

| 2.7  | Four input max operator modes                                                                                                                                                                                                                                                 |

| 2.8  | Max operator unit and over flow condition                                                                                                                                                                                                                                     |

| 2.9  | TurbASIP: LLRs storage in memory banks                                                                                                                                                                                                                                        |

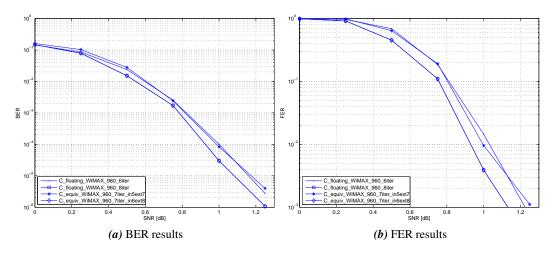

| 3.1  | C-simulations BER and FER results for WiMAX frame size 1920 bits and code rate of 1/3                                                                                                                                                                                         |

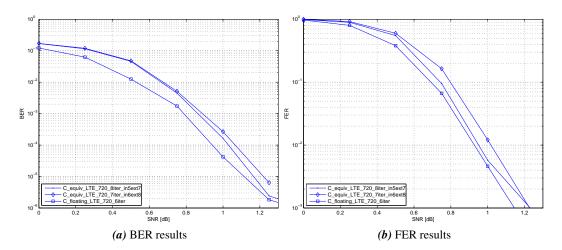

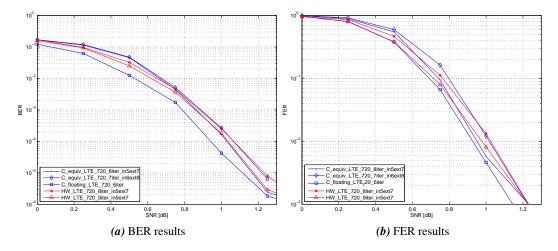

| 3.2  | C-simulation BER and FER results for LTE frame size 1440 bits and code rate of 1/3                                                                                                                                                                                            |

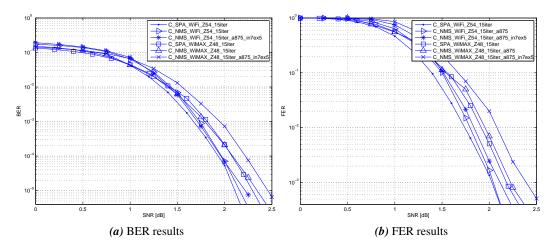

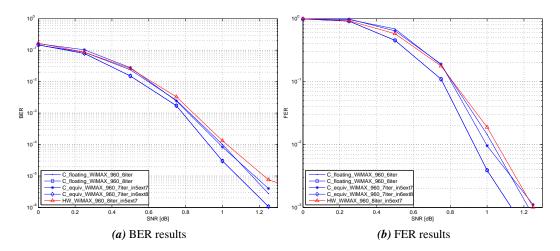

| 3.3  | C-simulation BER and FER results for LDPC WiMAX Z=48 and WiFi Z=54 and code rate of 1/2                                                                                                                                                                                       |

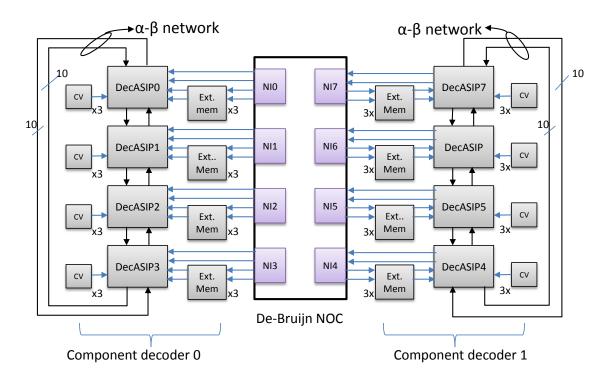

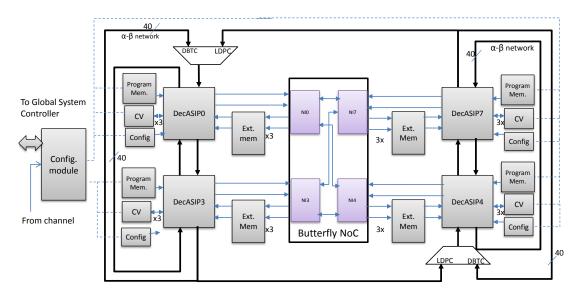

| 3.4  | $DecASIP_{v1}$ System Architecture                                                                                                                                                                                                                                            |

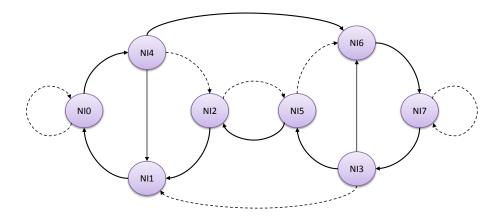

| 3.5  | Binary de-Bruijn NoC topology for 8 nodes                                                                                                                                                                                                                                     |

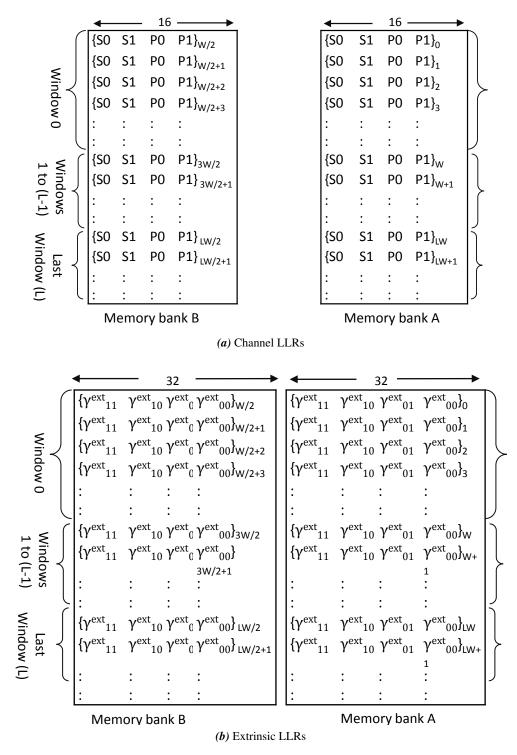

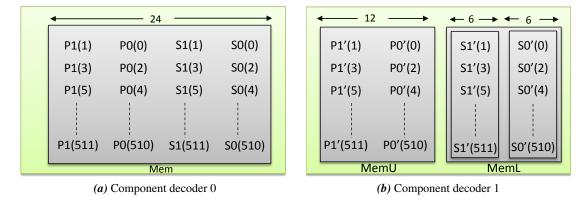

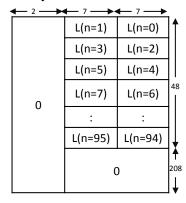

| 3.6  | DecASIP $_{v1}$ : Input memory (CV) bank0 organization in Turbo mode                                                                                                                                                                                                          |

| 3.7  | DecASIP $_{v1}$ : Extrinsic memory bank0 organization in Turbo mode                                                                                                                                                                                                           |

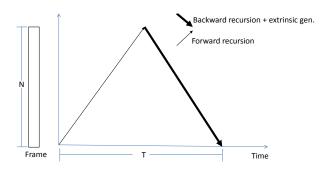

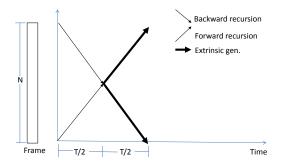

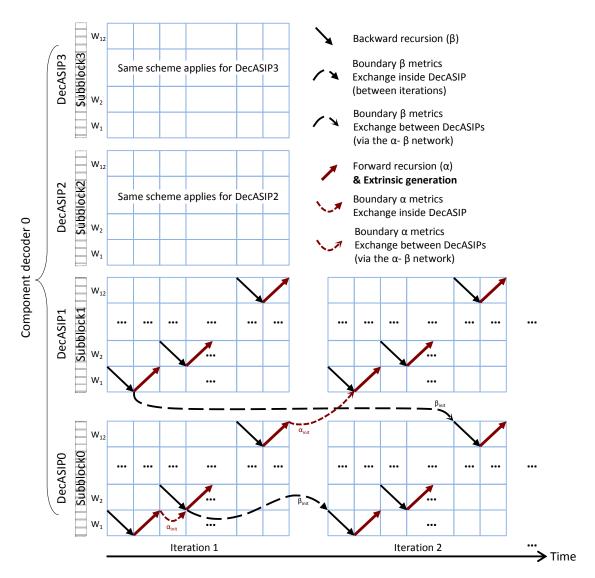

| 3.8  | DecASIP $_{v1}$ : Backward-Forward schedule adopted in Turbo mode. The number of processed windows per DecASIP depends on the frame size, the maximum number of windows per DecASIP is 12                                                                                     |

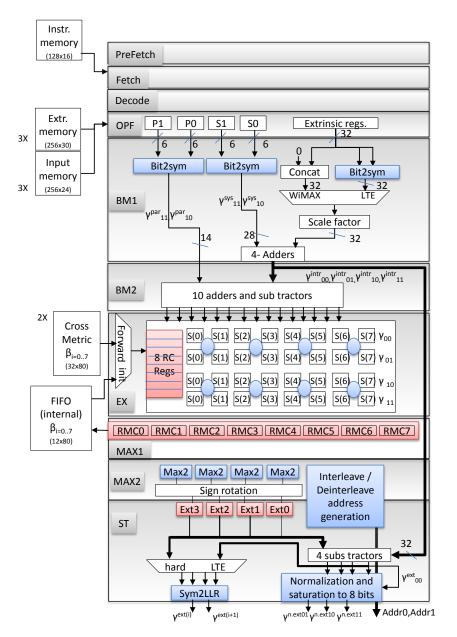

| 3.9  | $DecASIP_{v1}$ : Pipeline architecture in Turbo mode                                                                                                                                                                                                                          |

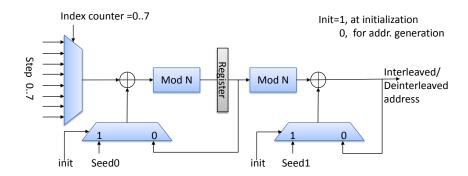

| 3.10 | DecASIP $_{v1}$ : ARP and QPP interleaved/deinterleaved address generation in Turbo mode                                                                                                                                                                                      |

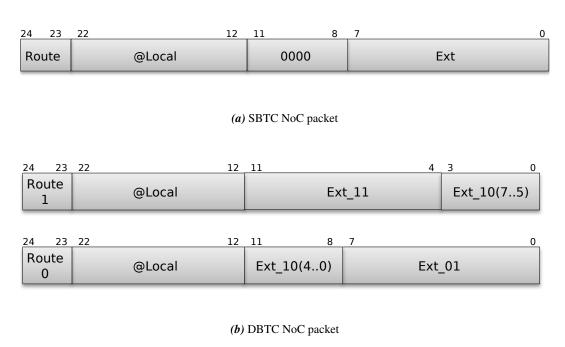

| 3.11 | $DecASIP_{v1}$ : NoC packets format in Turbo mode                                                                                                                                                                                                                             |

| 3.12 | Simple LDPC $H_{base}$ matrix example with $N_b$ =6, $M_b$ =2, and $Z$ =6                                                                                                                                                                                                     |

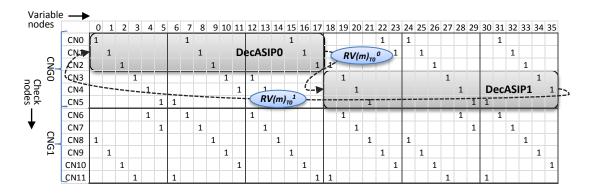

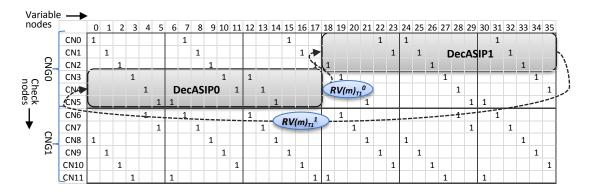

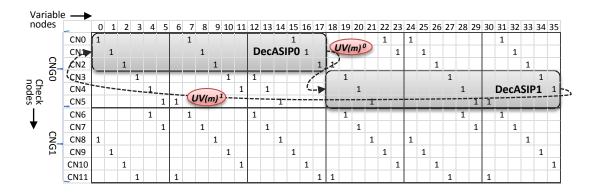

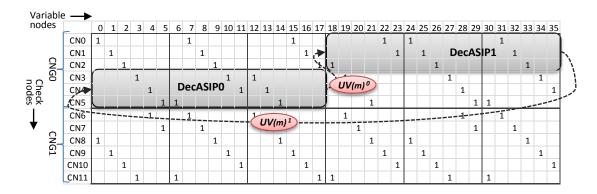

| 3.13 | DecASIP $_{v1}$ : Proposed LDPC decoding schedule with 2-DecASIP architecture at time step t= $T_0$                                                                                                                                                                           |

| 3.14 | DecASIP $_{v1}$ : Proposed LDPC decoding schedule with 2-DecASIP architecture at time step t= $T_1$                                                                                                                                                                           |

| 3.15 | DecASIP $_{v1}$ : Proposed LDPC decoding schedule with 2-DecASIP architecture at time step t= $T_2$                                                                                                                                                                           |

| 3.16 | DecASIP $_{v1}$ : Proposed LDPC decoding schedule with 2-DecASIP architecture at time step t= $T_3$                                                                                                                                                                           |

| 3.17 | LDPC check matrix $H_{base}$ from the WiFi standard with code rate 1/2, sub-matrix size $Z$ =81, and frame length of 1944 bits. This $H_{base}$ matrix consists of $M_b \times N_b$ permutation sub-matrices of size $Z_1(M_b=12, N_b=24, \text{ and } Z=81$ in this example) |

LIST OF FIGURES Xi

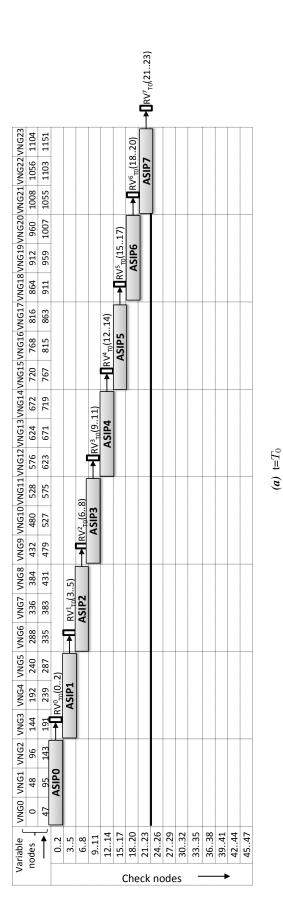

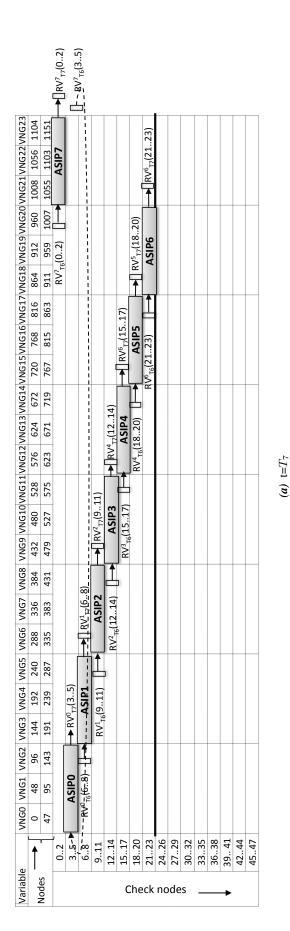

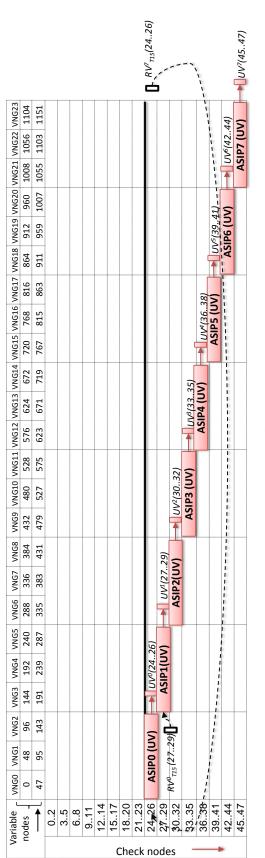

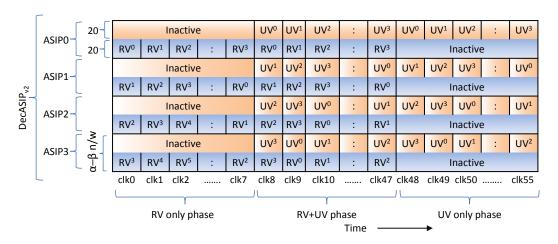

| 3.18 | DecASIP $_{v1}$ : Proposed LDPC decoding schedule with 8-DecASIP architecture — RV phase                                                                                                                             |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.19 | $ \begin{array}{l} {\rm DecASIP}_{v1} \hbox{: Proposed LDPC decoding schedule with 8-DecASIP architecture} \\ {\rm — RV~phase~@t=} \\ T_7 \hbox{ and RV+UV~phase @t=} \\ T_8 \end{array} . \ldots . \ldots . \ldots$ |

| 3.20 | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                 |

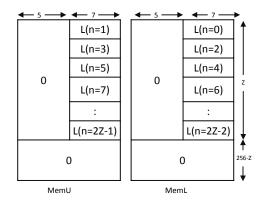

| 3.21 | $DecASIP_{v1}$ : Input memory bank 0 organization in LDPC mode                                                                                                                                                       |

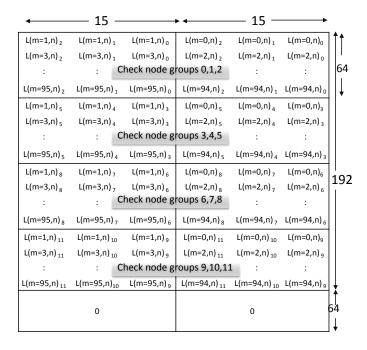

| 3.22 | $\operatorname{DecASIP}_{v1}$ : Extrinsic memory bank 0 organization in LDPC mode                                                                                                                                    |

| 3.23 | $DecASIP_{v1}$ : Pseudo code for $CV$ address generation of the input memory bank storing $VNG_y$ in $LDPC$ mode                                                                                                     |

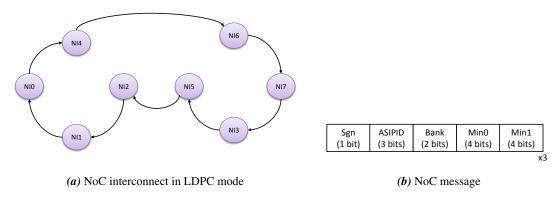

| 3.24 | $DecASIP_{v1}$ : NoC interconnect and payload in LDPC mode                                                                                                                                                           |

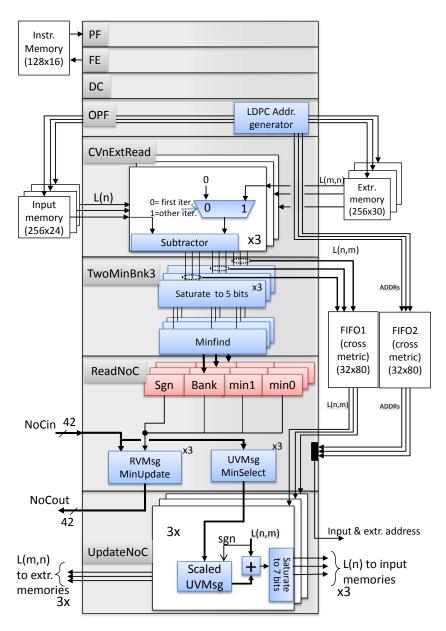

| 3.25 | $DecASIP_{v1}$ : Pipeline architecture in LDPC mode                                                                                                                                                                  |

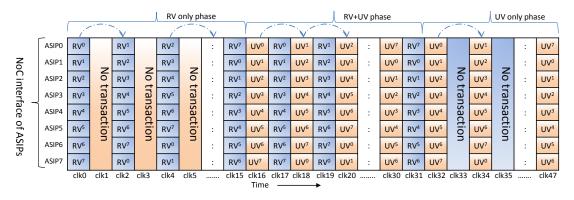

| 3.26 | $DecASIP_{v1}$ : RV and UV messages scheduling with the 8-DecASIP architecture in LDPC mode                                                                                                                          |

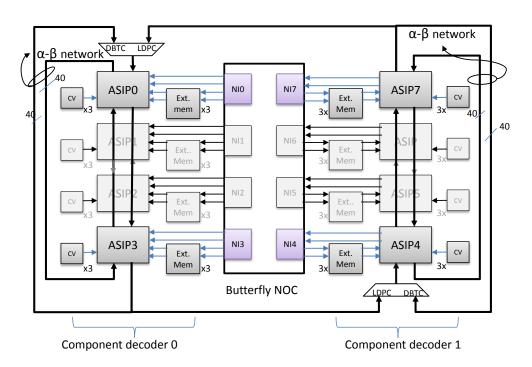

| 3.27 | $DecASIP_{v2}$ System Architecture                                                                                                                                                                                   |

|      | $DecASIP_{v2}$ : NoC packets format using the Butterfly NoC                                                                                                                                                          |

| 3.29 | $\operatorname{DecASIP}_{v2}$ : Input memory bank 0 organization in LDPC mode                                                                                                                                        |

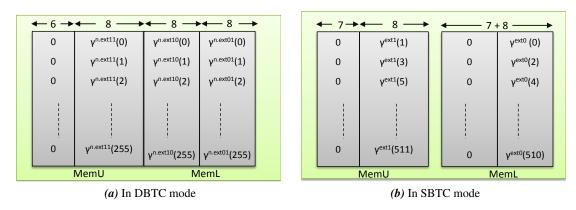

| 3.30 | $\operatorname{DecASIP}_{v2}$ : Extrinsic memory bank 0 organization in LDPC mode                                                                                                                                    |

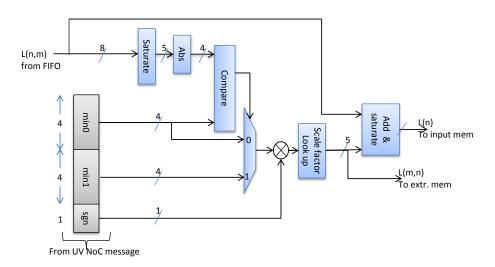

| 3.31 | $DecASIP_{v2}$ : Variable node update unit in LDPC mode                                                                                                                                                              |

| 3.32 | $\operatorname{DecASIP}_{v2}$ : NoC message format in LDPC mode                                                                                                                                                      |

| 3.33 | $DecASIP_{v2}$ : NoC message passing in LDPC mode. Example for CNG0 processing with $Z$ =48                                                                                                                          |

| 3.34 | $DecASIP_{v2}$ : Pseudo code for CV address generation in LDPC mode                                                                                                                                                  |

| 4.1  | Global FPGA platform architecture overview                                                                                                                                                                           |

| 4.2  | Flexible Turbo Encoder                                                                                                                                                                                               |

| 4.3  | Flexible convolutional Encoder                                                                                                                                                                                       |

| 4.4  | Flexible LDPC Encoder                                                                                                                                                                                                |

| 4.5  | DecASIP decoder system architecture                                                                                                                                                                                  |

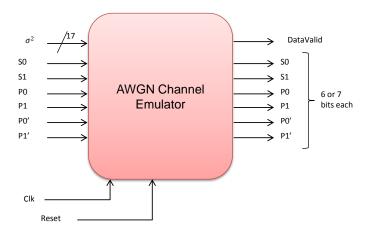

| 4.6  | AWGN channel input and output ports                                                                                                                                                                                  |

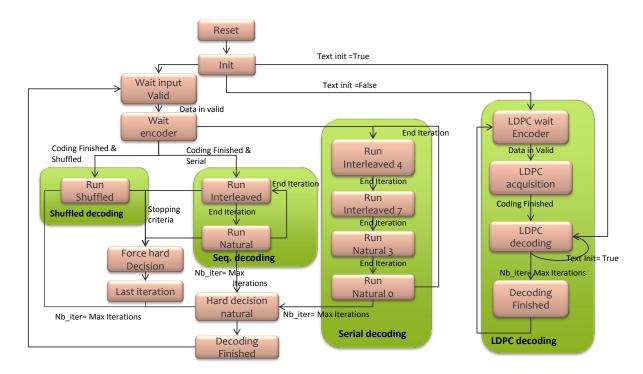

| 4.7  | FSM of the global system controller                                                                                                                                                                                  |

| 4.8  | Graphical User Interface (GUI) for the DecASIP FPGA prototype                                                                                                                                                        |

| 4.9  | FPGA prototype BER and FER results in SBTC mode for LTE frame size of 1440 bits and code rate of 1/3                                                                                                                 |

| 4.10 | FPGA prototype BER and FER results in DBTC mode for WiMAX frame size of 1920 bits and code rate of 1/3                                                                                                               |

| 4.11 | FPGA prototype BER and FER results in LDPC mode for WiMAX Z=48 and WiFi Z=54 and code rate of 1/2                                                                                                                    |

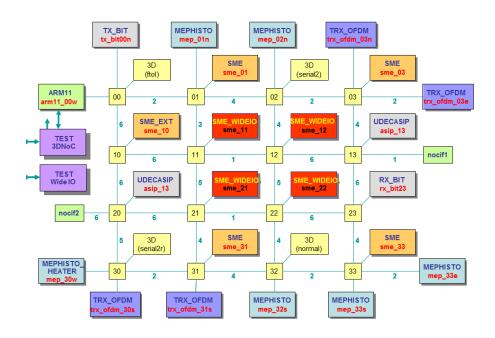

| 4.12 | MAG3D system architecture                                                                                                                                                                                            |

|      | Placement of DecASIP $_{v2}$ system on MAG3D                                                                                                                                                                         |

Xİİ LIST OF FIGURES

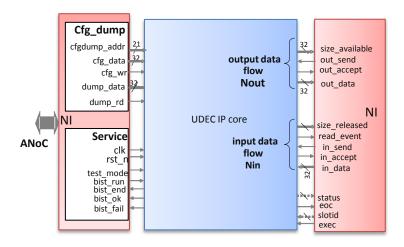

| 4.14 | 4 DecASIP system: Network interface to GALS on MAG3D                                   | 115 |

|------|----------------------------------------------------------------------------------------|-----|

| 4.15 | Post-route DecASIP chip diagram on MAG3D                                               | 115 |

| 5.1  | Proposed design flow for parameterized ASIP                                            | 118 |

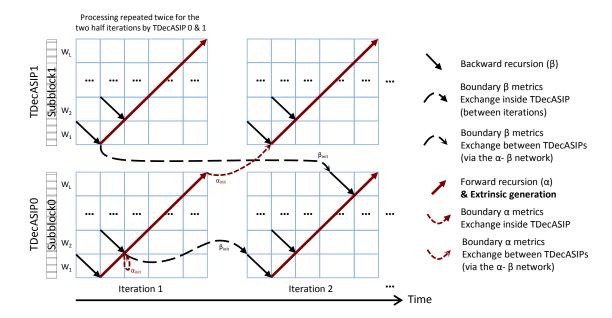

| 5.2  | TDecASIP: Windowing and backward-forward schedule                                      | 120 |

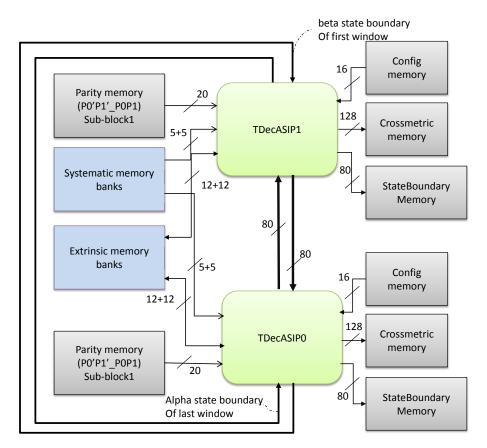

| 5.3  | Overview and memory organization of the proposed 2-TDecASIP Turbo decoder architecture | 121 |

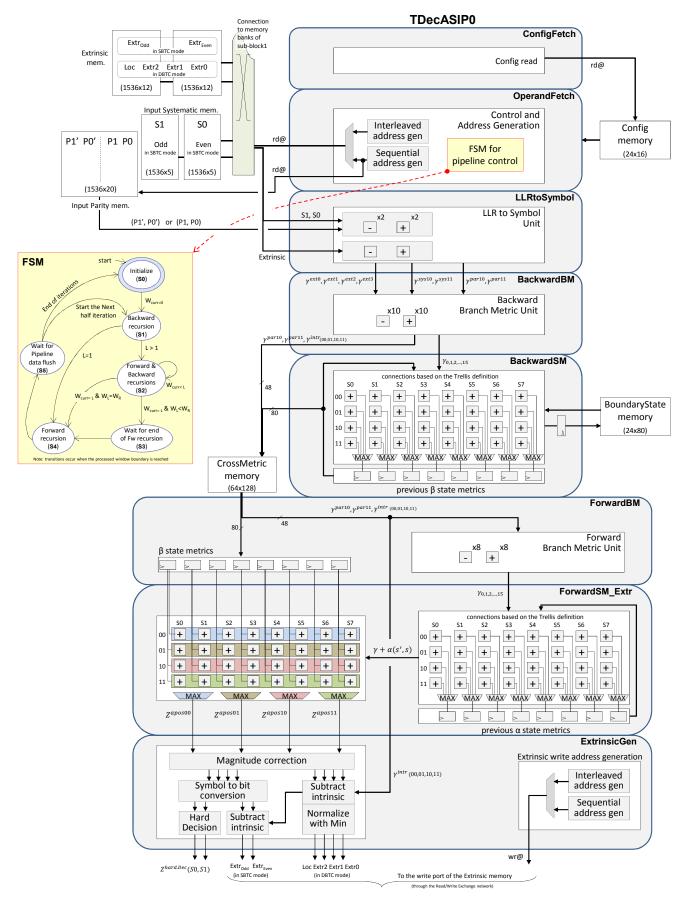

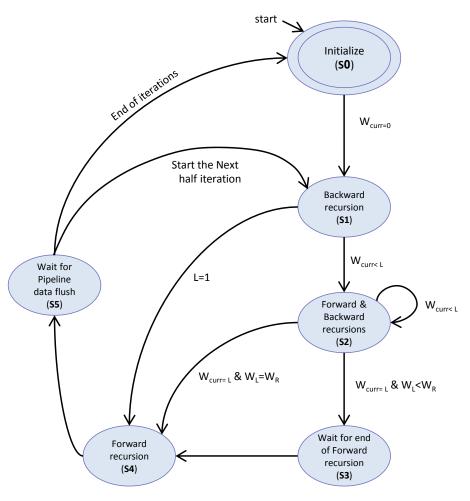

| 5.4  | Detailed pipeline architecture and FSM of the proposed TDecASIP parametrized core      | 122 |

| 5.5  | TDecASIP: Finite state machine for decoder execution control                           | 123 |

| 5.6  | TDecASIP: Prototyping environment                                                      | 125 |

| 6.1  | LDecASIP pipeline architecture                                                         | 130 |

| 6.2  | LDecASIP: Instruction/config memory                                                    | 131 |

| 6.3  | LDecASIP: FPGA prototyping environment                                                 | 132 |

| 6.4  | LDecASIP: Min calculator unit for DVB-S2                                               | 133 |

## **List of Tables**

| 1   | Representative set of mobile wireless standards and related channel codes and parameters                                                                 | 1   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.1 | Characteristics of WiFi and WiMAX LDPC check matrices                                                                                                    | 29  |

| 2.1 | Memory bank partitions for a single TurbASIP in 4x4 mode                                                                                                 | 55  |

| 2.2 | ASIC synthesis results for complete 4x4 TurbASIP system using 65nm general purpose CMOS technology (worst case 0.9v, 125C)                               | 55  |

| 3.1 | $\operatorname{DecASIP}_{v1}$ : Interleaved/deinterleaved address generation step and seed values in Turbo mode                                          | 67  |

| 3.2 | DecASIP $_{v1}$ : ASIC synthesis results for the complete 8-DecASIP $_{v1}$ system decoder using $65nm$ CMOS technology @510 MHz (worst case 0.9v, 125C) | 86  |

| 3.3 | DecASIP $_{v1}$ : Summary of the memory bank partitions for a single ASIP in the 8-DecASIP system decoder                                                | 86  |

| 3.4 | DecASIP $_{v1}$ : Throughput results and achieved architecture efficiency for an 8-DecASIP $_{v1}$ system decoder                                        | 86  |

| 3.5 | $DecASIP_{v2}$ : Configuration memory contents for $DecASIP\ 0$                                                                                          | 96  |

| 3.6 | DecASIP $_{v2}$ : ASIC synthesis results for the complete 4-DecASIP $_{v2}$ system decoder using $65nm$ CMOS technology @510 MHz (worst case 0.9v, 125C) | 97  |

| 3.7 | DecASIP $_{v2}$ : Summary of the memory bank partitions for a single ASIP in the 4-DecASIP system decoder                                                | 97  |

| 3.8 | $\operatorname{DecASIP}_{v2}$ : Results comparison with few recent state-of-the-art implementations                                                      | 98  |

| 4.1 | FPGA platform 2x2 DecASIP memory requirements of the banks                                                                                               | 106 |

| 4.2 | FPGA prototype synthesis on Xilinx Virtex-5 LX330 FPGA                                                                                                   | 110 |

| 4.3 | Required number of cycles to change the decoding mode for the 4-DecASIP system                                                                           | 110 |

| 4.4 | Scalability and throughput achieved for FPGA prototype implementation and operating frequency of 80 MHz                                                  | 111 |

| 5.1 | TDecASIP: FPGA (Xilinx Virtex-5 (xc5vlx330-1ff1760)) resource utilization for 1 processor                                                                | 126 |

XİV LIST OF TABLES

| 5.2 | TDecASIP: Memory partitions                                                                                                                  | 126 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.3 | TDecASIP: Post synthesis area utilization per processor for 2 processor architecture with general purpose CMOS 65nm, (worst case 0.9v, 125C) | 127 |

| 5.4 | Results and comparison with with few recent related works                                                                                    | 127 |

| 6.1 | LDecASIP: Memory bank partition for WiFi and WiMAX standard                                                                                  | 133 |

| 6.2 | LDecASIP: ASIC and FPGA synthesis results                                                                                                    | 134 |

| 6.3 | LDecASIP: Throughput (in Mbps) and latency L (in clock cycles per iteration) for WiMAX and WiFi mode @500MHz                                 | 134 |

| 6.4 | LDecASIP: Expected DVB-S2 latency L (in clock cycles per iteration) and throughputs (in Mbps) at 25 iterations @500MHz                       | 134 |

| 6.5 | LDecASIP: Comparison with the state of the art                                                                                               | 135 |

### Introduction

OBILE wireless connectivity is a key feature of a growing number of devices, which will count soon in tens of billions, from laptops, tablets, cell phones, cameras and other portable devices. The variety of applications and traffic types will be significantly larger than today and will result in more diverse requirements. These applications are driving the creation of new transmission techniques and design architectures that push the boundaries to achieve high throughput, low latency, area and power efficient implementations.

Channel coding is one of the key techniques that enable reliable high throughput data transfer through unreliable wireless channels. However, as a large variety of channel coding options and flavors are specified in existing and emerging digital communication standards, there is an increasing need for flexible implementations. In fact, several powerful error correction techniques exist today, each suitable for specific application parameters (frame size, transmission channel, signal-to-noise ratio, bandwidth, etc). Considering the emerging multi-mode and multi-standard applications, as well as the increasing interest for Software Defined Radio (SDR) and Cognitive Radio (CR) applications, combination of multiple error correction techniques becomes mandatory. Table 1 shows a representative set of mobile wireless standards to highlight their differences in data rates and channel encoding schemes. The most commonly used error correcting codes in these standards are Convolutional Codes (CC), Turbo codes (SBTC: Single Binary Turbo Codes and DBTC: Double Binary Turbo Codes), and Low-Density Parity-Check (LDPC) codes.

| Standard             | Codes | Rates      | States | info. bits | Channel Throughput |

|----------------------|-------|------------|--------|------------|--------------------|

| EDGE                 | CC    | 1/41/3     | 64     | 870        | 384 kbps           |

| UMTS                 | CC    | 1/41/2     | 256    | 504        | 32 kbps            |

| UNITS                | SBTC  | 1/3        | 8      | 5114       | 2 Mbps             |

| HSDPA                | SBTC  | 1/2 - 3/4  | 8      | 5114       | 14.4 Mbps          |

| CDMA-2k              | CC    | 1/6 1/2    | 256    | 744        | 28 kbps            |

| CDIVIA-2K            | SBTC  | 1/5 - 1/2  | 8      | 20730      | 2 Mbps             |

| IEEE-802.11n (WiFi)  | CC    | 1/23/4     | 64     | 4095       | 450Mbps            |

| IEEE-002.1111 (WIF1) | LDPC  | 1/2 - 5/6  | -      | 1620       | 450Mbps            |

|                      | CC    | 1/2 - 5/6  | 64     | 864        | 75 Mbps            |

| IEEE802.16e (WiMAX)  | DBTC  | 1/2 - 3/4  | 8      | 4800       | 75 Mbps            |

|                      | LDPC  | 1/2 - 5/6  | -      | 1920       | 75 Mbps            |

| DVB-S2               | LDPC  | 1/4 - 9/10 | -      | 64800      | 90 Mbps            |

| DVB-RCS              | DBTC  | 1/3 - 6/7  | 8      | 1728       | 2 Mbps             |

| 3GPP-LTE             | SBTC  | 0.33-0.95  | 8      | 6144       | 150 Mbps           |

Table 1 — Representative set of mobile wireless standards and related channel codes and parameters

2 INTRODUCTION

#### **Problems**

In this context, and at the receiver side, it is well known that channel decoding is one of the most computation, communication, and memory intensive, and thus, power-consuming component. Channel decoder design has been extensively investigated during the last few years and several implementations have been proposed. Some of these implementations succeeded in achieving high throughput for specific standards through the adoption of highly dedicated architectures that work as hardware accelerators. However, these implementations do not take into account flexibility and scalability issues. Particularly, this approach implies the allocation of multiple separated hardware accelerators to realize multi-standard systems, which often result in poor hardware efficiency. Furthermore, it implies long design time which is no more compatible with the severe time-to-market constraints and the continuous development of new standards and applications.

More recently, several contributions have been proposed targeting flexible, yet high throughput, implementations of channel decoders. The flexibility varies from supporting different modes of a single communication standard to the support of multi-standards multi-modes applications. Other implementations have even proposed to increase the target flexibility to the support of different channel coding techniques. As a matter of fact, a knowledge gap is growing quickly in the last few years between the need for flexibility in the digital base-band processing segment of modern communication systems, and the actual availability of flexible while efficient hardware support to the quest for reconfigurability. The main reason that determines this growing gap is related to the poor area and energy efficiency of flexible solutions proposed till now and the huge increase of non-recurrent engineering (NRE) costs in the production of dedicated integrated circuits for specific applications (ASIC) with new semiconductor technologies.

#### Objectives and scope of the thesis

Towards the target of filling the above mentioned gap, this thesis work aims at defining and developing an efficient and high performance flexible channel decoder architecture model for emerging and future digital communication systems. The need of optimal solutions in terms of performance, area, and power consumption is increasing and cannot be neglected against flexibility. In common understanding, a "blind" approach towards flexibility results in some loss in optimality. The objective of this work is related to unifying flexibility-oriented and optimization-oriented approaches. The main goal is to deliver enablers and building block solutions in order to derive, for a specific application need, the best balance between a highly flexible solution and a specifically optimized one.

Towards this objective, the thesis work investigates multiprocessing and Application-Specific Instruction-set Processor models (ASIP) which enable the designer to scale and freely tune the flexibility/performance trade-off as required by the considered application requirements. Related contributions are emerging rapidly seeking to improve the resulting architecture efficiency in terms of performance/area and in addition to increase the flexibility support.

By considering mainly the challenging Turbo and LDPC decoding applications, multi-ASIP channel decoder architectures are proposed targeting high flexibility combined with high Architecture Efficiency (AE) in terms of bits/cycle/iteration/mm<sup>2</sup>. Different architecture alternatives and design approaches are explored. Furthermore, in order to be relevant to existing and emerging standards we limit the supported flexibility targeting LDPC and Turbo codes specified in

INTRODUCTION 3

WiFi, WiMAX, and LTE. This also enables to compare with existing state-of-the-art implementations.

#### Thesis contributions

Towards the above mentioned objectives, the results of this thesis work can be summarized in the following 4 main contributions (which are also illustrated in Figure 1 corresponding to chapters 3, 4, 5, and 6):

- Design of a scalable and flexible high throughput multi-ASIP LDPC/Turbo decoder:

- Proposal and design of a flexible and optimized ASIP architecture, namely **DecASIP**, supporting Turbo and LDPC decoding.

- Proposal of an efficient resource sharing between LDPC and Turbo decoding modes.

- Proposal of a scalable high throughput multi-ASIP channel decoder with efficient mapping of the target standards.

- Proposal of a new LDPC decoding schedule adapted to the target multi-ASIP channel decoder.

- Exploring possible parallelism techniques for efficient decoding of SBTC, DBTC, and LDPC codes.

- Optimization of the dynamic configuration speed between the different supported decoding modes.

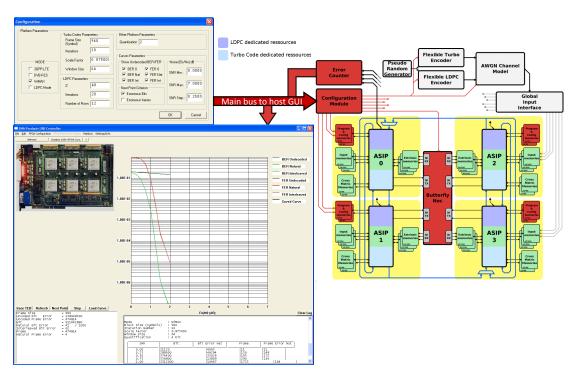

- FPGA and ASIC prototyping of the proposed multi-ASIP LDPC/Turbo decoder:

- Proposal and design of a complete FPGA-based prototype of the proposed multi-ASIP LD-PC/Turbo decoder.

- ASIC integration of a 4-DecASIP channel decoder in the latest Telecom chip (namely MAG3D) designed by the CEA-LETI targeting 4G communication applications

- Design of a parameterized ASIP for Turbo decoding, **TDecASIP**:

- Increasing the architecture efficiency in terms of bit/cycle/iteration/mm<sup>2</sup>.

- Enabling the design of application-specific parameterized cores using an ASIP design flow.

- Design of an optimized ASIP for LDPC decoding, namely **LDecASIP**:

- Increasing the architecture efficiency in terms of bit/cycle/iteration/mm<sup>2</sup>.

- Enhancing the ASIP-based LDPC decoder with a design-time feature enabling incremental changes for future support of other QC-LDPC codes (e.g. DVB-S2 with high expansion factor Z = 360).

#### **Thesis Outline**

The thesis manuscript is composed of six chapters as illustrated in Figure 1 and described below:

**Chapter 1** introduces the basic concepts related to convolutional Turbo codes and LDPC codes along with their decoding algorithms. First, an overview of the fundamental concepts of channel coding and the basics for error-correcting codes are introduced. The second section presents the Turbo codes and details their basic components. This is followed, in the third section, by the presentation of the corresponding decoding algorithms, namely Maximum Aposteriori Probability (MAP) and the low complexity Max-Log-MAP. This section also briefs a note

4 Introduction

Figure 1 — Overview of the thesis outline and contributions

on possible parallelism levels exploited for implementation. The last two sections focus on the presentation of the LDPC codes and their most commonly used algorithm, namely Normalized Min-Sum (NMS), in a reformulated manner as used in this thesis work.

**Chapter 2** introduces the ASIP-based design approach and the considered Processor Designer tool from Synopsys (ex. CoWare tools). It further gives an overview on state-of-the-art

INTRODUCTION 5

efforts in channel decoder design in order to clarify the position of the proposed contributions in this thesis work. Based on the ASIP design approach, the chapter presents an initial ASIP architecture, namely TurbASIP, which constitutes the starting point of this thesis work.

Chapter 3 presents our first contributions in the design of flexible and optimized channel decoder supporting Turbo and LDPC codes. Starting with the initial TurbASIP architecture presented in the previous chapter, several objectives have been specified for this work, which can be summarized in the following points: (1) efficient resource sharing between the LDPC and Turbo decoding modes, (2) scalability to enable the accommodation of current and future high throughput requirements, (3) new LDPC decoding schedule adapted to the base TurbASIP architecture, (4) exploring possible parallelism techniques for efficient decoding of SBTC, DBTC, and LDPC codes, and (5) rapid configurability between the different supported decoding modes.

Towards fulfilling these objectives, an ASIP-based multiprocessor architecture is proposed and designed in two phases. The first phase achieves the targeted objectives through the design of a novel ASIP architecture, namely  $DecASIP_{v1}$ , and the efficient mapping of the target standards on an 8-DecASIP system decoder. The second phase ( $DecASIP_{v2}$ ) mainly enhances the throughput in LDPC mode by increasing the supported parallelism degree. It also modifies the proposed LDPC scheduling to support 4-DecASIP or 2-DecASIP decoder architectures.

The first section of this chapter presents the design motivations and architectural choices made for the  $DecASIP_{v1}$  along with the analysis on quantization and reference curves for the implemented modes, namely SBTC (LTE), DBTC (WiMAX) and LDPC (WiFi, WiMAX) modes. The second and third sections present the two design phases of the proposed DecASIP channel decoder.

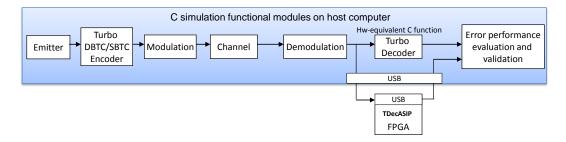

Chapter 4 is dedicated to the presentation of the conducted efforts towards FPGA and ASIC prototyping of the proposed flexible channel decoder. A complete FPGA-based prototype of the proposed multi-standard Turbo/LDPC decoder is demonstrated. The functional prototype implements a full communication system including encoder, channel model, ASIP-based decoder and performance counters. All components are flexible and are dynamically configurable through a dedicated GUI (Graphical User Interface). The proposed prototype supports all communication modes defined in LTE, WiFi and WiMAX wireless communication standards. Furthermore, as a joint effort with another PhD student at the CEA-LETI (Pallavi Reddy), an ASIC integration of the proposed flexible channel decoder has been elaborated. A 4-DecASIP channel decoder is integrated in the latest Telecom chip (namely MAG3D) designed by the CEA-LETI targeting 4G communication applications. The chapter is organised as follows. The first section reiterates the communication system model presented in the first chapter drawing parallels to the implemented design units on the target FPGA prototype. Two blocks are illustrated in detail in the second section of this chapter: the flexible Turbo and LDPC encoders.

Chapter 5 presents a new optimized flexible standalone Turbo decoder, namely TDecASIP. The objective behind this new design is twofold: (1) investigate the maximum attainable architecture efficiency for ASIP-based Turbo decoding, and related to this first objective (2) investigate the possibility to design application-specific parameterized cores using the available ASIP design flow. The idea of this last objective is to evaluate the benefits from removing the need of a program memory and the related instruction decoder. Towards fulfilling these objectives, TDecASIP architecture is proposed and designed as a parameterized Turbo decoder. The proposed architecture exhibits a very high architecture efficiency and supports all SBTC and DBTC modes of 3GPP LTE and WiMAX standards respectively.

This chapter is organized as follows. The first section presents the proposed design flow using Synopsys Processor Designer tool to describe application-specific parameterized cores.

6 INTRODUCTION

The second section illustrates the motivations behind the architectural choices and describes the proposed architecture of TDecASIP. Finally, the last two sections of the chapter presents the FPGA and ASIC synthesis results highlighting the attained architecture efficiency of this new flexible Turbo decoder design.

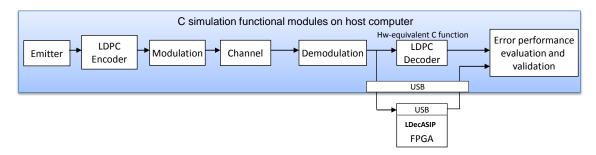

Chapter 6 presents a new optimized flexible standalone LDPC decoder, namely LDecASIP. The objective behind this new design is twofold: (1) investigate the maximum attainable architecture efficiency for ASIP-based LDPC decoding and (2) explore the possibility of realizing a flexible decoder allowing to implement and validate new/incremental algorithm changes with fast turnaround time in design. The idea of this last objective is to enhance the ASIP-based LDPC decoder with a design-time feature enabling incremental changes for future support of other QC-LDPC codes (e.g. DVB-S2 with high expansion factor Z=360). Towards fulfilling these objectives, LDecASIP architecture is proposed and designed. The proposed architecture exhibits a very high architecture efficiency, supports all QC-LDPC codes and related parameters of WiFi and WiMAX standards (with expansion factors ranging from Z=24 to Z=96), and enables the support other QC-LDPC codes with structured incremental hardware changes at design time.

The chapter is organized as follows. The first section describes the design motivations along with the proposed LDPC decoder architecture. The second section presents the added design-time flexibility feature and illustrates the proposed way of upgrading the design to support other QC-LDPC codes through the example of DVB-S2 LDPC decoding. Finally, the third section presents the FPGA and ASIC synthesis results with architecture efficiency evaluation and related discussions.

**CHAPTER**

# **Background: Channel Codes** and Decoding Algorithms

THIS chapter presents an overview of a typical communication system with special emphasis on channel coding and decoding algorithms. As this thesis work targets LDPC and Turbo codes, the chapter focuses mainly on detailing the decoding algorithms of these codes.

The first section introduces the need for channel coding and the notion of channel capacity. The second section presents the Turbo codes and details their basic components. This is followed, in the third section, by the presentation of the corresponding decoding algorithms, namely Maximum Aposteriori Probability (MAP) and the low complexity Max-Log-MAP. This section also briefs a note on possible parallelism levels that should be exploited for high throughput implementations. The last two sections focus on the presentation of the LDPC codes and their most commonly used decoding algorithm, namely Normalized Min-Sum (NMS), in a reformulated manner as used in this thesis work.

#### 1.1 Communication system overview

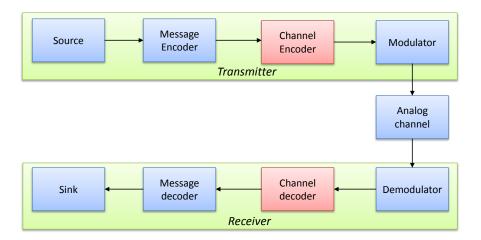

A simplified block digram of a communication system which emphasis the role of the error-correction (control) coding (ECC) is shown in Figure 1.1. It consists of a *source*, a channel encoder, a transmission channel, a channel decoder and a *sink*. The *source* abstracts the information data to be transmitted, e.g. audio, video, text data, etc., while the *sink* block abstracts the actual recipient of this data, e.g. television, radio, cell phone, etc. The *source* output, if analog, has to be converted to digital form by a message encoder which may additionally remove redundancy in the information bits (source coding) before sending them to the channel encoder. The channel encoder introduces redundancy in a controlled manner so that at the receiving end, the redundant bits can be used for error detection or error correction. The modulator maps the encoded digital sequences into signal waveforms suitable for propagation. Modulation can be performed by varying the amplitude, the phase or the frequency of a sinusoidal waveform called the *carrier*. The channel block abstracts

Figure 1.1 — Digital communication system model

the communication medium over which the data is transmitted, e.g. air, wire-line, fiber optic channels, etc. Two major limitations of real channels are thermal noise and finite bandwidth. Hence in the receiver, the demodulator typically generates a digital sequence at its output as the best estimates of the transmitted codeword. In other words, the demodulator demaps the modulated signal received from the channel into soft values that represent the received signal. From these values, the channel decoder estimates the transmitted message based on the encoding rule and the characteristics of the channel with a goal to minimize the effect of the channel noise.

The Shannon limit: The aim of every digital communication system is to transmit as much data as possible with little or no error utilizing minimum amount of power. Signal bandwidth is the measure of the speed of transmission. High speed transmission waveforms would need rapid changes in time and hence high transmission bandwidth. However, the capacitive and inductive properties of the channel prevents instantaneous change of signals, depending on the frequency range, environment and medium of the channel. Various probabilistic models have been proposed for simplicity of mathematical analysis like, Additive White Gaussian Noise (AWGN) channel, Rayleigh channel, etc. In this thesis, we consider the simple AWGN channel model. As the name suggests, the added noise to the transmitted signal has a Gaussian distribution.

For a given channel bandwidth B, there is an upper limit on the data rate related to the Energy

per bit to noise ratio  $\frac{E_b}{N0}$  of the channel [1]. This maximum limit is called *Channel capacity* and for an AWGN channel is given by (as shown by Claude Shannon [1]):

$$C = B \times log_2(1 + \frac{E_b}{N0}) \ bits/sec$$

(1.1)

Shannon's channel coding theorem guarantees that data can be transmitted reliably at very low probability of error over a noisy communication channel if the transmission rate R is less than the threshold C. The probability of errors can be made to decrease exponentially as the frame length of the coding scheme goes to infinity. The gain or power saved w.r.t. to a uncoded system achieved due to the use of channel coding is called *Coding gain*.

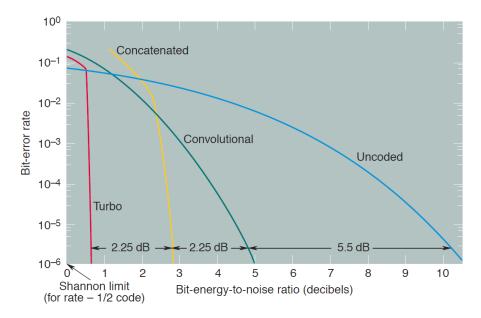

Figure 1.2 — Bit error rate performance of a Turbo code w.r.t. channel capacity and other conventional codes

This theorem only guarantees the existence of such codes but does not define these codes. Thus, ever since its first publication in 1948, the scientific community is trying to find error correction codes of finite length with reasonable complexity and approaching as close as possible to the channel capacity. In this context, different channel codes have been proposed aiming to achieve this channel capacity such as: convolutional codes, Hamming codes, Reed Solomon codes, convolutional Turbo codes, Block Turbo codes, LDPC codes, etc. Among these codes, Turbo and LDPC codes are shown to be capacity approaching. Figure 1.2 [2] illustrates how for a target bit-error rate of  $10^{-6}$ , the use of convolutional and concatenated codes provides a 5.5-decibel and 7.75-decibel improvement respectively compared with the uncoded system. The use of a Turbo code imparts an additional 2.25-decibel improvement compared with the concatenated code, resulting in a total coding gain of 10 decibels compared with the uncoded system. With the use of a rate-1/2 Turbo code, system error performance can approach levels within about 1 decibel of the Shannon limit. Similar performance curves can be obtained for LDPC codes too. Due to such excellent error correction properties, LDPC and Turbo codes are widely used in recent and emerging wireless communication standards. The following sections introduce these two families of codes with their commonly used decoding algorithms.

#### 1.2 Turbo codes

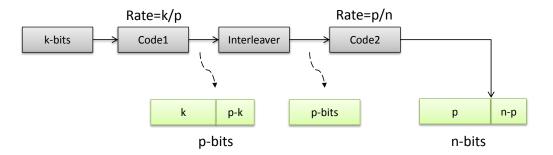

As mentioned earlier, the probability of errors can be made to decrease exponentially as the coded frame length (N) goes to infinity. However, for such long codes the optimum decoding scheme that simply computes the likelihood of every possible transmitted codeword presents a complexity which increases exponentially with N, hence practical implementation of such decoders becomes infeasible. As an alternative, David Forney proposed a divide and conquer approach to the problem by designing codes that are concatenation of simpler codes [3]. Two possible methods of concatenation exist, namely:

Serial concatenation (Figure 1.3) where the output of outer code is the input of the inner code. Subsequently, it was observed that the addition of a function of interleaving between the two codes increases robustness of the concatenated codes significantly. Figure 1.3 shows an example of such serially concatenated codes with a global code rate of k/n with two component encoders (Code1, Code2). The encoders Code1 and Code2 encode the data at rates of k/p and p/n respectively.

Figure 1.3 — Serial concatenated code structure

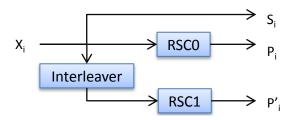

Parallel concatenation (Figure 1.4) which consists of two systematic encoders, where the

first encoder receives the source data X<sub>i</sub> in natural order and at the same time the second

encoder receives the same data but in interleaved order. The output is composed of the

source data and the associated redundant bits produced by the natural and the interleaved

domain encoders.

In fact, many existing and emerging wireless communication standards specify parallel concatenated convolutional Turbo codes. In this context, a typical Turbo encoder consists of parallel concatenation of two Recursive Systematic Convolutional (RSC) encoders separated by an interleaver as shown in Figure 1.4. The input bit stream  $X_i$  is encoded into 3 output streams namely the systematic S as well as two parities  $P_i$  and  $P'_i$  from the encoders that encode the natural and interleaved bit streams respectively. Generally, two types of RSC encoders are specified in

Figure 1.4 — Parallel RSC Turbo encoder structure

1.2. TURBO CODES

current standards:

• Double Binary Turbo Code (DBTC) encoder (specified in DVB-RCS and WiMAX standards) uses a RSC that encodes bit pairs (double binary symbols) of the incoming payload of size N bits to a stream of parity bit pairs.

• Single Binary Turbo Code (SBTC) encoder (specified in LTE standard) which uses a RSC that encodes bitwise the incoming payload of size N bits to a stream of parity bits.

The rest of this section presents the concepts of convolutional codes and interleaving rules as specified in the target wireless communication standards.

#### 1.2.1 Recursive Systematic Convolutional codes

Convolutional codes have been widely used in applications such as space and satellite communications, cellular mobile, digital broadcasting, etc. Their popularity is due to their simple structure and easily implementable maximum likelihood soft decision decoding methods.

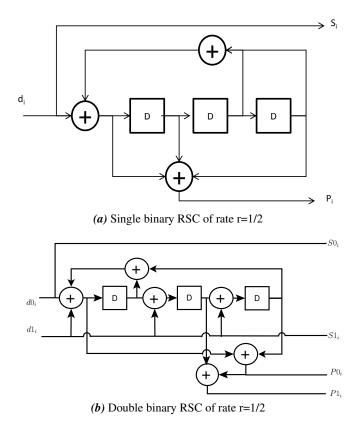

A convolutional code of rate r=k/n is a linear function which, at every instant i, transforms an input symbol  $d_i$  of k bits into an output coded symbol  $c_i$  of n bits (k>n). A code is called *Systematic* if a part of the output is made up of systematic bits  $s_i=d_i$  and the rest of the bits (n-k) are made up of parity bits. The output bits are the linear combination of the current and the previous input bits. The linear function is usually given by generator polynomials. There

(a) Non-systematic convolutional code

(b) Systematic convolutional code

Figure 1.5 — Examples of Non systematic and Systematic convolutional codes

are three main types of convolutional codes namely Non-Systematic (NSC), Systematic (SC) and Recursive Systematic (RSC) convolutional codes. The only difference in the encoding of the SC and NSC is that, in NSC the output does not contain input systematic bits as shown in Figure 1.5a. This figure illustrates too how a convolutional encoder can be described using shift registers and modulo two adders. The generator polynomials of the convolutional codes examples of Figure 1.5 are given as:

$$S_i = d_i$$

$P1_i = g1(x) = 1 + x^1 + x^2$

$P2_i = g2(x) = 1 + x^2$

$C_i \equiv (S_i, P1_i, P2_i)$

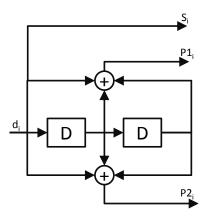

These generator polynomials represent the connections between the outputs of the shift register and the modulo two adders. They are generally represented by their coefficients in binary: (111) for  $P1_i$  and (101) for  $P2_i$ . If the encoder shift register has feedback and includes input data as part of the output then it is called Recursive systematic encoder (RSC) (Figure 1.6a). The encoder shown Figure 1.6a is a single binary Recursive Systematic Convolutional (RSC) code (from LTE standard [4]) which encodes one bit at a time. The parity bits are generated by the polynomial given by:

$$P(D) = \frac{1 + D + D^3}{1 + D^2 + D^3}$$

$$C_i \equiv (S_i, P_i)$$

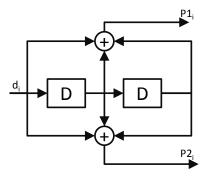

Similar representation is used for a RSC which encodes 2 bits at a time as shown in Figure 1.6b. The encoder shown is called Double Binary Recursive Systematic Convolutional code (as used in WiMAX standard [5]) and the parity bits are generated by the polynomial given by:

$$S0_{i} = d0_{i}$$

$$S1_{i} = d1_{i}$$

$$P_{1} = \frac{1 + D^{2} + D^{3}}{1 + D + D^{3}}$$

$$P_{2} = \frac{1 + D^{3}}{1 + D + D^{3}}$$

$$C_{i} \equiv (S0_{i}, S1_{i}, P0_{i}, P1_{i})$$

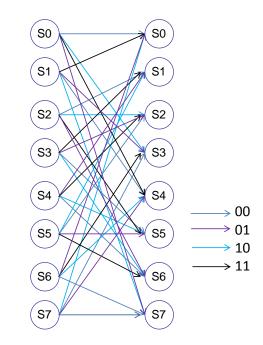

Convolutional codes are characterized by a parameter called constraint length, given as K = M+1, where M is number of flip-flops of the encoder shift register. The number of flip-flops also indicated that the encoder has  $2^M$  states. Another commonly used representation of convolutional encoding is the trellis diagram [6] which is made up of nodes and branches. A node represents the state S of the code. A branch represents a transition from one state  $(S_{i-1}(m'))$  to another state  $(S_i(m))$  due to an input bit pair (in case of a double binary convolutional code). Each transition is associated to input and output vector of the encoder. Figure 1.7 shows the trellis representation of the double binary encoder of Figure 1.6b that has K=4, i.e. with M=3 (8 states). It has to be noted that each state has  $2^b=4$  possible transitions, where b=2 is the number of bits at the input of the encoder.

1.2. TURBO CODES 13

Figure 1.6 — Recursive systematic codes (RSC)

Figure 1.7 — Trellis diagram of encoder of Figure 1.6b

**Trellis termination:** During the encoding process the shift register of the encoder starts typically with the state zero. Towards the end of the encoding process M zeros are inserted in

order to bring back the encoder state to zero. Thus, the transmitted codeword has extra parity bits that are the result of the zero insertion, known in the literature as *zero padding*. Such technique ensures that the encoder starts and ends in a known state, however it results in minor loss of transmission bandwidth.

As an alternative, *Tail biting* scheme is used in some standards like DVB-RCS and WiMAX which adopt circular recursive systematic convolutional (CRSC) codes. For this type of circular codes, the encoder is initialized for each frame of data in a certain state called the circulation state  $S_c$  that leads the encoder to return to the same state at the end of the encoding process of the frame. The existence of such a state is ensured when the size of the encoded data frame is not a multiple of the period of the encoding recursive generator [7]. The value of the circulation state  $S_c$  depends on the contents of the sequence to encode and determining  $S_c$  requires a preencoding operation. First, the encoder is initialized to the "all zero" state and the data sequence is encoded once, leading to a final encoder state  $S_k^0$ . From this final state  $S_k^0$ , the circulation state  $S_c$  can be calculated using simple combinational operators or a corresponding lookup table as described in [7].

Viterbi algorithm is commonly used to decode convolutional codes [8]. Viterbi decoding is done via estimating the most likely sequence of states by observing the received bit sequence.

#### 1.2.2 Turbo Code Interleaver

Interleavers in a digital communication system are used to temporally disperse the data. The primary interest of them in concatenated codes is to put two copies of same symbol (coming to two encoders) at different interval of time. This enables to retrieve at least one copy of a symbol in a situation where the other one has been destroyed by the channel. An interleaver  $(\prod)$  satisfying this property can be verified by studying the dispersion factor S given by the minimum distance between two symbols in natural order and interleaved order:

$$S = \min_{i,j} (|i - j| + |\Pi(i) - \Pi(j)|)$$

(1.2)

The design of interleavers respecting a dispersion factor can be reasonably achieved through the S-random algorithm proposed in [9]. However, even if this kind of interleaver can be sufficient to validate the performance in the convergence zone of a code, it does not achieve a good asymptotic performance. Therefore to improve the latter, the design of the interleaver must also take into account the nature of component encoders. Complexity of the hardware implementation should, in addition, be taken into account. In fact, the recent wireless standards specify performance and hardware aware interleavling laws for each supported frame length.

In following sections the interleaving functions associated to Turbo codes for WiMAX and LTE standards are described.

#### 1.2.2.1 Almost regular permutation (ARP)

The ARP interleaver is used in double binary Turbo codes for both standards IEEE 802.16e WiMAX . It can be described by the function  $\prod(j)$  which provides the interleaved address of each double-binary symbol of index j, where j=0,1,...N-1 and N is the number of symbols in the frame.

$$\prod(j) = (P_0 \times j + P + 1) \bmod N$$

(1.3)

1.3. TURBO DECODING

where

$$P = 0$$

if  $j \mod 4 = 0$

$P = \frac{N}{2} + P_1$  if  $j \mod 4 = 1$

$P = P_2$  if  $j \mod 4 = 2$

$P = \frac{N}{2} + P_3$  if  $j \mod 4 = 3$  (1.4)

where the parameters  $P_0$ ,  $P_1$ ,  $P_2$  and  $P_3$  depend on the frame size and are specified in the corresponding standard [5].

Another step of interleaving is specified in these standards which consists of swapping the two bits of alternate couples, i.e  $(a_j, b_j) = (b_j, a_j)$  if  $j \mod 2 = 0$ .

It is worth to note that this interleaver structure is well suited for hardware implementation and presents a collision-free property for certain level of parallelism.

#### 1.2.2.2 Quadratic polynomial permutation (QPP)

The interleaver specified in single binary Turbo codes for the LTE standard [4] is called quadratic polynomial permutation (QPP) interleaver. It is given by the following expression:

$$\prod(j) = (f_1 j + f_2 j^2) \bmod N$$

(1.5)

where the parameters  $f_1$  and  $f_2$  are integers, depend on the frame size N ( $0 \le j, f_1, f_2 < N$ ), and specified in the standard. In this standard, all the frame sizes are even numbers and are divisible by 4 and 8. Moreover, by definition, the parameter  $f_1$  is always an odd number whereas  $f_2$  is always an even number. Through further inspection, we can mention one of the several algebraic properties of the QPP interleaver:

$\prod(j)$  has the same even/odd parity as j as shown in 1.6 and 1.7:

$$\prod (2 \times k) \bmod 2 = 0 \tag{1.6}$$

$$\prod (2 \times k + 1) \bmod 2 = 1 \tag{1.7}$$

This property will be used later for the hardware implementation in order to design an extrinsic exchange module to avoid memory collisions when using particular parallelism techniques (butterfly schedule and trellis compression). More information on the other properties for the QPP interleavers are given in [10, 11]. Moreover, the frame size N is always divisible by 16, 32, and 64 when  $N \ge 512$ ,  $N \ge 1024$ , and  $N \ge 2048$ , respectively. The specific structure of the QPP interleaver equation enables sub-block parallelism degrees (see Sub-section 1.3.4.2) that range from 1, 2, ... to 64.

#### 1.3 Turbo decoding

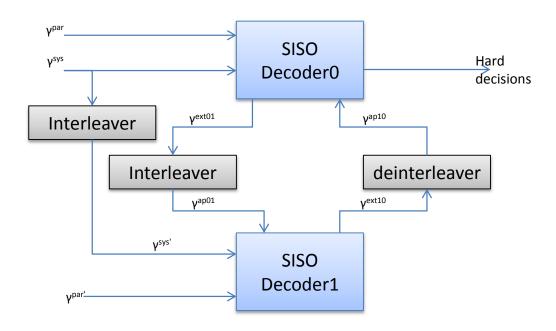

This section presents the principle of Turbo decoding with a brief overview of the Maximum Aposteriori Probability (MAP) algorithm. The Turbo decoding principle relies on the iterative exchange of probabilistic messages between two (or more) decoders dealing with the same

received data [12]. In a typical Turbo decoding system (Figure 1.8), two decoders operate iteratively on the received frame (one in natural domain and the other in interleaved domain) and pass probabilistic messages, the so-called *extrinsic information*, to each other after each iteration. The decoders, namely Soft-Input Soft- Output (SISO) decoders, operate on soft information to improve the decoding performance. Thus, each SISO decoder takes into consideration, besides its own channel input data, the received extrinsic information from the other SISO decoder in order to improve its estimation over the iterations. Usually, but not necessarily, the computations are

Figure 1.8 — Classical Turbo decoder structure

done in the logarithmic domain. Each decoder calculates the Log-Likelihood Ratio (LLR) for the  $\mathbf{i}^{th}$  data bit  $d_i$ , as

$$\gamma(d_i) = \ln \frac{Pr(d_i = +1|y)}{Pr(d_i = -1|y)}$$

(1.8)

Input LLRs causing trellis transition can be decomposed into 3 independent terms, as

$$\gamma(d_i) = \gamma^{ap}(d_i) + \gamma^{sys}(d_i) + \gamma^{par}(d_i)$$

(1.9)

where  $\gamma^{ap}(d_i)$  is the a-priori information of  $d_i$ ,  $\gamma^{sys}(d_i)$  and  $\gamma^{par}(d_i)$  are the channel measurement of the systematic and parity parts respectively.  $\gamma^{ext}(d_i)$  is the extrinsic information that is sent by the SISO decoder to the other decoder (as shown in Figure 1.8). Extrinsic information  $\gamma^{ext}$  from one decoder becomes the a-priori information  $\gamma^{ap}$  for the other decoder at the next decoding stage. In Figure 1.8,  $\gamma^{ext01}$  represents the extrinsic information sent from SISO decoder0 to SISO decoder1, while  $\gamma^{ext10}$  denotes the extrinsic information sent from SISO decoder1 to SISO decoder0. Although different kinds of algorithms are proposed in the literature for this SISO decoding, Soft Output Viterbi Algorithm (SOVA) and Maximum Aposteriori Probability (MAP) algorithms are the most commonly used. The SOVA algorithm is a soft output variant of the classical Viterbi algorithm that aims to find the most likely sequence of the transmitted codeword [13]. This algorithm targets to minimize the frame error rate (FER). The MAP algorithm [14] on the other hand, which also referred to in the literature as Bahl-Cock-Jelinek-Raviv (BCJR) or forward-backward algorithm, targets to minimize the bit error rate (BER). This last

1.3. TURBO DECODING

algorithm, which is considered in this thesis work, is the optimal decoding algorithm which calculates the probability of each symbol from the probability of all possible paths in the trellis between initial and final states.

#### 1.3.1 Maximum Aposteriori Probability (MAP) algorithm

For each source symbol  $d_i^{sym}$  comprised of m bits, encoded in n output bits by an encoder having M memory elements (i.e  $2^M$  states) at rate r=k/n, a MAP decoder provides  $2^m$  a posteriori probabilities given the channel output y received by the decoder. The hard decision on the corresponding value j, i.e.  $d_i^{sym}=j$ , that maximizes the a posteriori probability is expressed in terms of joint probabilities as:

$$Pr(d_i^{sym} = j|y) = \frac{p(d_i^{sym} = j, y)}{\sum_{l=0}^{2^m - 1} p(d_i^{sym} = l, y)}$$

(1.10)