# Exploration and optimization of tree-based FPGA architectures

Zied Marrakchi

#### ▶ To cite this version:

Zied Marrakchi. Exploration and optimization of tree-based FPGA architectures. Hardware Architecture [cs.AR]. Université Pierre et Marie Curie - Paris VI, 2008. English. NNT: 2008PA066478. tel-00813115

#### HAL Id: tel-00813115 https://theses.hal.science/tel-00813115

Submitted on 15 Apr 2013  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE L'UNIVERSITÉ PIERRE ET MARIE CURIE

#### Spécialité : INFORMATIQUE ET MICRO-ÉLECTRONIQUE

Présentée par : Zied Marrakchi

## Pour obtenir le grade de DOCTEUR DE L'UNIVERSITÉ PIERRE ET MARIE CURIE

## EXPLORATION ET OPTIMISATION D'ARCHITECTURES FPGA ARBORESCENTES

#### Soutenue le : 25 Novembre 2008

Devant le jury composé de :

| M. | Habib Mehrez      | Paris 6      | Directeur de thèse |

|----|-------------------|--------------|--------------------|

| M. | Lionnel Torres    | LIRMM        | Rapporteur         |

| M. | Jean-Luc Danger   | ENST         | Rapporteur         |

| M. | Michel Minoux     | Paris 6      | Examinateur        |

| M. | Olivier Lepape    | Abound Logic | Examinateur        |

| M. | Christian Masson  | LIP6/BULL    | Examinateur        |

| M. | Jean-Luc Rebourg  | CEA-DAM      | Examinateur        |

| M. | Joachim Pistorius | Altera       | Examinateur        |

|    |                   |              |                    |

# Ph.D. THESIS OF THE UNIVERSITY OF PIERRE ET MARIE CURIE

#### Department : COMPUTER SCIENCE AND MICRO-ELECTRONICS

Presented by : Zied Marrakchi

### Thesis submitted to obtain the degree of DOCTOR OF THE UNIVERSITY PIERRE ET MARIE CURIE

# EXPLORATION AND OPTIMIZATION OF TREE-BASED FPGA ARCHITECTURES

Defended in :  $25^{th}$  November 2008

Commitee in charge :

| M. | Habib Mehrez      | Paris 6         |

|----|-------------------|-----------------|

| M. | Lionnel Torres    | LIRMM, Reviewer |

| M. | Jean-Luc Danger   | ENST, Reviewer  |

| M. | Michel Minoux     | Paris 6         |

| M. | Olivier Lepape    | Abound Logic    |

| M. | Christian Masson  | LIP6/BULL       |

| M. | Jean-Luc Rebourg  | CEA-DAM         |

| M. | Joachim Pistorius | Altera          |

#### Résumé

Les circuits FPGAs (Field Programmable Gate Arrays) sont devenus des acteurs importants dans le domaine du traitement numérique qui a été dominé auparavant par les microprocesseurs et les circuits intégrés spécifiques. Le plus grand défi pour les FP-GAs aujourd'hui est de présenter un bon compromis entre une grande souplesse et de bonnes performances (vitesse, surface et consommation). La combinaison de trois facteurs définit les caractéristiques d'un circuit FPGA: la qualité de l'architecture, la qualité des outils CAO de configuration et la conception électrique du FPGA. L'objet de cette thèse est l'exploration de nouvelles architectures et de structures d'interconnexion qui pourront améliorer les performances de ces circuits. En effet, les ressources d'interconnexion occupent 90% de la surface totale et occasionnent 60% de la consommation électrique. Les architectures étudiées présentent des structures matricielles et arborescentes. Les principaux résultats sont les suivants:

• Au départ nous explorons différentes topologies arborescentes et nous comparons leurs surfaces à celles des architectures matricielles. Pour cela, nous développons une plateforme d'outils logiciels permettant d'implanter différents circuits logiques sur l'architecture cible. En se basant sur cette étude expérimentale, nous définissons une nouvelle architecture arborescente. Nous montrons, en nous appuyant sur un modèle d'estimation de surface, que cette architecture permet de réduire la surface totale de 56% par rapport à une architecture matricielle. Ceci est dû essentiellement à une meilleure utilisation des ressources d'interconnexion.

• Nous explorons les effets des différents paramètres de l'architecture proposée: le coefficient de Rent, la taille des groupes logiques et le nombre d'entrées par bloc logique. Ceci permet de régler l'architecture pour l'adapter à des domaines d'applications qui ont des contraintes spécifiques en terme de surface, vitesse et consommation.

• Enfin, nous proposons une architecture qui rassemble les avantages des structures arborescentes et matricielles. Nous unifions les deux structures en construisant des groupes de blocs logiques qui ont localement un réseau d'interconnexion arborescent et qui sont connectés entre eux via un réseau matriciel. Nous montrons que l'architecture obtenue présente un bon compromis entre l'évolutivité de la vue physique et la densité de la surface.

**Mots-clés:** FPGA, Réseau d'interconnexion, Loi de Rent, Structure arborescente, Structure matricielle, Optimisation, Partitionnement, Placement, Routage, Analyse de timing

#### Abstract

Today, FPGAs (Field Programmable Gate Arrays) become important actors in the computational devices domain that was originally dominated by microprocessors and ASICs. FPGA design big challenge is to find a good tradeoff between flexibility and performances. Three factors combine to determine the characteristics of an FPGA: quality of its architecture, quality of the CAD tools used to map circuits into the FPGA, and its electrical design. The subject of this dissertation is the exploration of new interconnect topologies and architectures that may play important roles in FPGA performances improvement. In fact interconnect is the dominant factor in terms of area (90%) and power dissipation (60%). The main architectures under exploration have Tree-based or Mesh-Based topology. The main results are the following:

• We first explore different Tree-based architectures and we compare them to Meshbased architecture in terms of area. For this purpose we develop an exploration tools platform allowing to implement various benchmark circuits on the target architecture. Using experimental evaluation, we define a new Tree-based FPGA architecture and we show that it has good performances and density characteristics. We show, based on total cells area evaluation, that using the proposed topology we achieve a gain of 56% compared to the common Mesh-based FPGA architecture. This is due essentially to the high interconnect utilization achieved by this architecture.

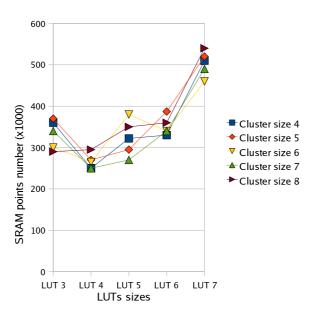

• We explore the effect of different architecture parameters: Rent's ratio, cluster sizes, and LUTs sizes. We show how they interact and the way to tune them to satisfy different specific applicative constraints (density, performance and power).

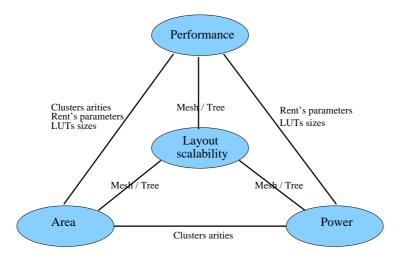

• Finally, we propose an architecture that takes advantage of both Mesh and Tree strongest points. We unify both structures by building clusters with a Tree-based local interconnect and we connect these clusters by a Mesh-based interconnect. We show that the resulting architecture presents a good tradeoff between layout scalability and area density.

**Keywords:** FPGA, Interconnect, Rent's rule, Tree-based architecture, Mesh-based architecture, Optimization, Partitioning, Placement, Routing, Timing analysis.

À mes parents.

#### Remerciements

Je tiens à remercier vivement monsieur Alain Greiner pour m'avoir accueilli dans son laboratoire et pour l'énergie qu'il a dépensée afin de maintenir de bonnes conditions de travail.

Je tiens également à remercier mon directeur de thèse monsieur Habib Mehrez pour sa grande disponibilité et ses conseils qui m'ont été très utiles dans la préparation de ce travail.

J'adresse mes remerciments à messieurs Jean-Luc Danger, directeur d'études à Telecom ParisTech (ENST Paris), et Lionnel Torres, professeur à l'université Montpellier II, qui m'ont fait l'honneur d'être rapporteurs de cette thèse.

Je tiens également à remercier messieurs Michel Minoux, Professeur à Paris 6, Christian masson, collaborateur bénévole au LIP6 et ex-chef service CAD/VLSI chez BULL, Olivier Lepape, vice président de Abound Logic, Jean-Luc Rebourg, ingénieur électronicien au CEA-DAM, et Joachim Pistorius, ingénieur logiciel chez Altera, qui ont bien voulu accepter de juger ce travail en participant à mon jury de thèse.

Une mention toute particulière revient à monsieur Christian Masson qui a très vite perçu l'intérêt de mes recherches préliminaires et a su au bon moment guider les développements réalisés au cours de ce travail. Qu'il trouve ici l'expression de toute ma gratitude pour son dynamisme et son enthousiasme pour mon sujet de recherche.

J'ai particulièrement apprécié la collaboration avec madame Alix Munier Kordon qui m'a engagé à étudier à fond les architectures proposées et identifier leurs potentiels et limites. Je tiens à la remercier et lui exprimer ma sincère gratitude de m'avoir fait bénéficier de son expérience dans le domaine de l'optimisation combinatoire.

C'est aussi pour moi l'occasion d'exprimer ma profonde reconnaissance à monsieur François Durbin pour sa gentillesse et ses talents linguistiques. De nombreux documents et en particulier ce manuscrit auraient été bien mal écrits sans ses aides.

Cette thèse est le résultat d'un travail d'équipe et je salut tous mes collègues Hayder Mrabet, Hussain Pavez, Emna Amouri, Umer Farooq de l'équipe "Arith" et Christophe Alexandre de l'équipe "Coriolis". Je tiens également à remercier Arnaud Caron, ancien doctorant au LIP6 pour ses conseils, ses remarques pertinentes et ses encouragements. Je remercie aussi tous les étudiants du Master 2 ACSI, ayant contribué à ce travail. Je tiens également à remercier tous les respensables de l'équipe EIM du CEA qui ont soutenu et encouragé ce travail, de près ou de loin, et en particulier monsieur André Tissot pour ses collaborations et l'interêt continu qu'il a accordé à mes recherches.

# Contents

| Ré | ésum                        | é                                          | v  |  |  |

|----|-----------------------------|--------------------------------------------|----|--|--|

| In | trodu                       | letion                                     | 1  |  |  |

|    | 1                           | Research goals and contributions           | 2  |  |  |

|    | 2                           | Outline                                    |    |  |  |

| 1  | FPG                         | A Architectures                            | 7  |  |  |

|    | 1.1                         | Introduction                               | 7  |  |  |

|    | 1.2                         | Configurable Logic Blocks                  | 8  |  |  |

|    | 1.3                         | Interconnect topologies                    | 9  |  |  |

|    |                             | 1.3.1 VPR-based Mesh interconnect          | 9  |  |  |

|    |                             | 1.3.2 Altera's Stratix II architecture     | 12 |  |  |

|    |                             | 1.3.3 Multilevel Hierarchical Interconnect | 15 |  |  |

|    | 1.4                         | Conclusion                                 | 20 |  |  |

| 2  | FPGA Configuration CAD Flow |                                            |    |  |  |

|    | 2.1                         | Synthesis                                  | 21 |  |  |

|    | 2.2                         | Technology Mapping                         | 23 |  |  |

|    | 2.3                         | Clustering                                 | 24 |  |  |

|    |                             | 2.3.1 Bottom-up approaches                 | 25 |  |  |

|    |                             | 2.3.2 Top-down approaches                  | 26 |  |  |

|    | 2.4                         | Placement                                  | 29 |  |  |

|    |                             | 2.4.1 Simulated annealing based approach   | 30 |  |  |

|    |                             | 2.4.2 Partitioning based approach          | 32 |  |  |

|    | 2.5                         | Routing                                    | 33 |  |  |

|    | 2.6                         | Timing Analysis                            | 35 |  |  |

#### xiv Contents

|   | 2.7  | Concl   | usion                                         | 36 |

|---|------|---------|-----------------------------------------------|----|

| 3 | Arcl | hitectu | res Exploration Environment                   | 37 |

|   | 3.1  | Explo   | ration Methodologies                          | 37 |

|   |      | 3.1.1   | Analytical comparison                         | 37 |

|   |      | 3.1.2   | Experimental comparison                       | 38 |

|   |      | 3.1.3   | Reference architecture                        | 39 |

|   | 3.2  | Explo   | ration Platform                               | 40 |

|   |      | 3.2.1   | Synthesis and Mapping                         | 40 |

|   |      | 3.2.2   | Clustering and Partitioning                   | 41 |

|   |      | 3.2.3   | Placement                                     | 43 |

|   |      | 3.2.4   | Routing                                       | 44 |

|   |      | 3.2.5   | Timing Analysis                               | 44 |

|   | 3.3  | Area a  | and Delay Models                              | 45 |

|   |      | 3.3.1   | Switches requirement                          | 45 |

|   |      | 3.3.2   | Wiring requirement                            | 46 |

|   |      | 3.3.3   | Delay Model                                   | 47 |

|   | 3.4  | Bench   | mark circuits                                 | 47 |

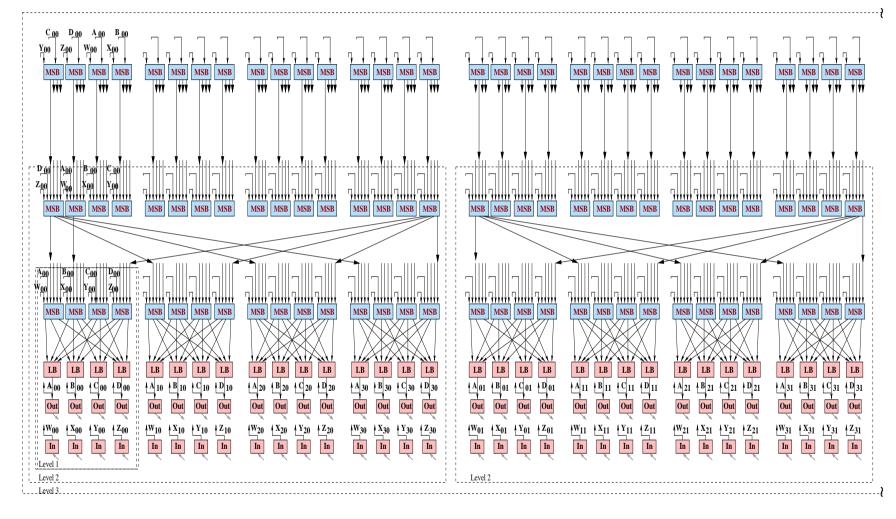

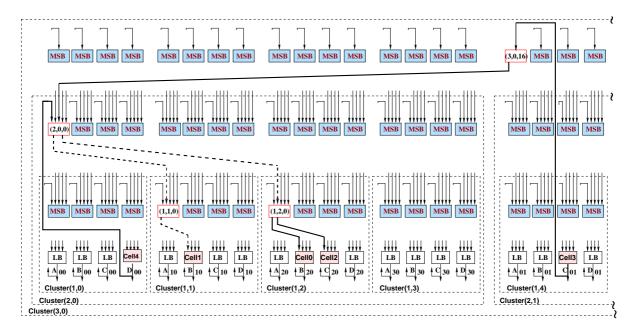

|   | 3.5  | Archit  | tecture Example                               | 48 |

|   | 3.6  | Concl   | usion                                         | 52 |

| 4 | Tree | e-based | FPGA with optimized cluster signals bandwidth | 57 |

|   | 4.1  | Propo   | sed Architecture                              | 57 |

|   |      | 4.1.1   | Wire growth model                             | 58 |

|   |      | 4.1.2   | Switch growth model                           | 59 |

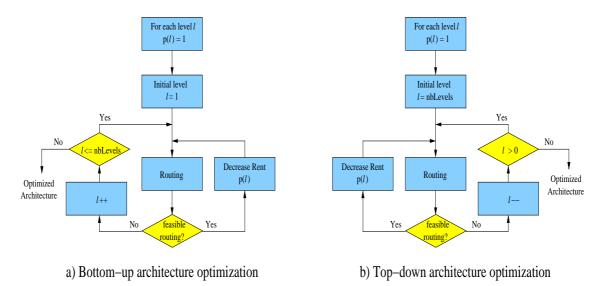

|   | 4.2  | Partiti | oning methodologies                           | 60 |

|   |      | 4.2.1   | Top-down partitioning                         | 61 |

|   |      | 4.2.2   | Bottom-up partitioning                        | 61 |

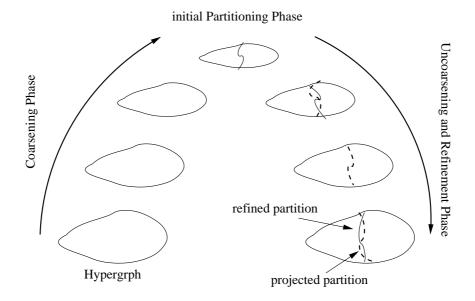

|   |      | 4.2.3   | Multilevel refinement                         | 64 |

|   | 4.3  | Exper   | imental Results                               | 65 |

|   |      | 4.3.1   | Partitioning methodologies comparison         | 65 |

|   |      | 4.3.2   | Architectures comparison                      | 68 |

|   | 4.4  | Concl   | usion                                         | 69 |

| 5 | Tree | -based interconnect with depopulated switch boxes 7              | 1 |

|---|------|------------------------------------------------------------------|---|

|   | 5.1  | MFPGA routing interconnect                                       | 1 |

|   |      | 5.1.1 Downward Network                                           | 2 |

|   |      | 5.1.2 Upward Network                                             | 3 |

|   |      | 5.1.3 Connection with outside                                    | 4 |

|   |      | 5.1.4 Rent's Rule based MFPGA model                              | 6 |

|   | 5.2  | MFPGA placement                                                  | 7 |

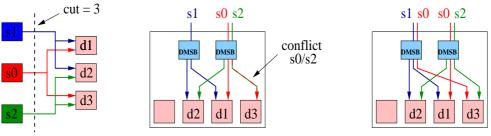

|   |      | 5.2.1 Conflict conditions                                        | 7 |

|   |      | 5.2.2 Placement example                                          | 8 |

|   |      | 5.2.3 Partitioning                                               | 0 |

|   |      | 5.2.4 Detailed placement                                         | 1 |

|   |      | 5.2.5 Logic replication                                          | 5 |

|   | 5.3  | MFPGA routing                                                    | 7 |

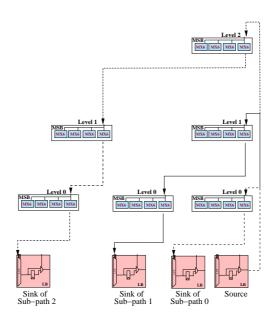

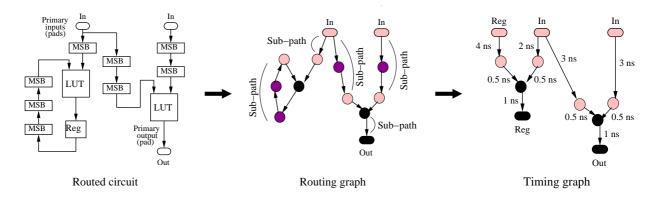

|   | 5.4  | Timing Analysis                                                  | 8 |

|   |      | 5.4.1 Sub-paths delays evaluation                                | 9 |

|   |      | 5.4.2 Critical path extraction                                   | 1 |

|   | 5.5  | Experimental results                                             | 2 |

|   |      | 5.5.1 Placement techniques evaluation                            | 2 |

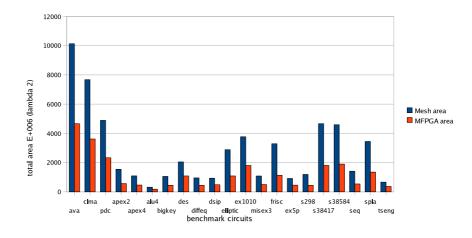

|   |      | 5.5.2 Density performances                                       | 4 |

|   |      | 5.5.3 Speed performances                                         | 4 |

|   | 5.6  | Conclusion                                                       | 5 |

| _ | _    |                                                                  | _ |

| 6 |      | e-based FPGA with optimized switch boxes and signals bandwidth 9 |   |

|   | 6.1  | Interconnect Improvement                                         |   |

|   | 6.2  | Interconnect Depopulation                                        |   |

|   | 6.3  | Connection with Outside                                          |   |

|   | 6.4  | Rent's Rule Based Model                                          |   |

|   |      | 6.4.1 Switches requirement                                       |   |

|   |      | 6.4.2 Wiring Requirements                                        |   |

|   |      | 6.4.3 Comparison with Mesh Model                                 |   |

|   | 6.5  | Configuration Flow                                               |   |

|   |      | 6.5.1 Multilevel Partitioning                                    |   |

|   |      | 6.5.2 Routing                                                    | 3 |

|   |      |                                                                  |   |

xv

|    | 6.6     | Exper   | imental Evaluation                   | . 105 |

|----|---------|---------|--------------------------------------|-------|

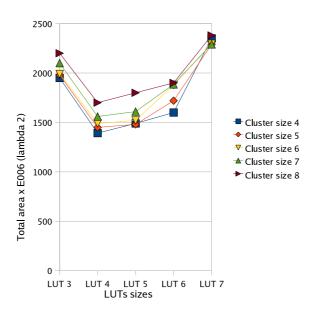

|    |         | 6.6.1   | Tree-based architecture optimization | . 106 |

|    |         | 6.6.2   | Area Efficiency                      | . 108 |

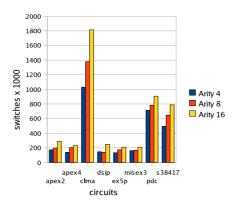

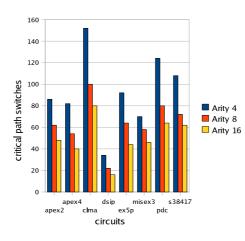

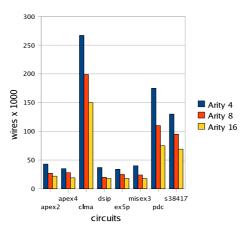

|    |         | 6.6.3   | Clusters Arity Effect                | . 112 |

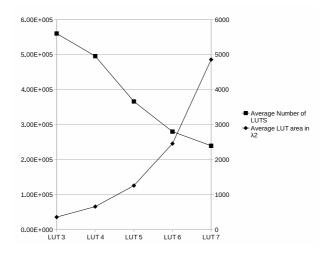

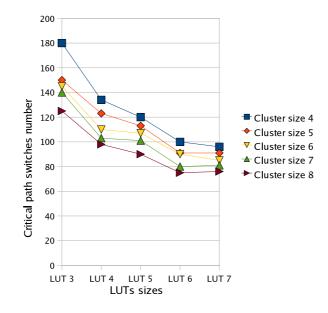

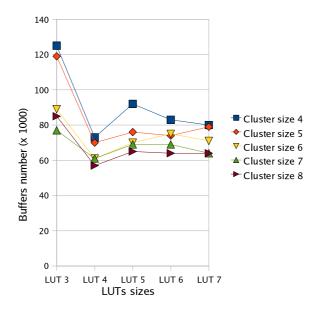

|    |         | 6.6.4   | LUT Size Effect                      | . 114 |

|    | 6.7     | Concl   | usion                                | . 118 |

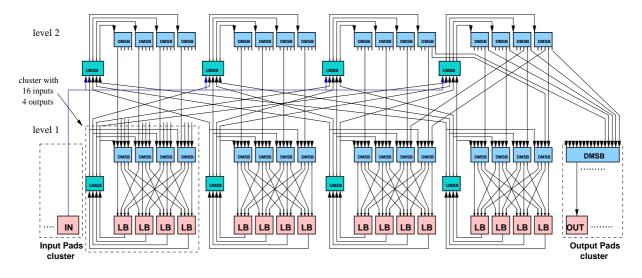

| 7  | Mes     | h of Tr | ee Architecture                      | 119   |

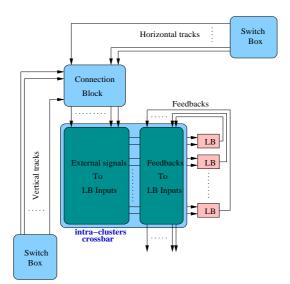

|    | 7.1     | Mesh    | of Tree architecture                 | . 119 |

|    |         | 7.1.1   | Cluster local interconnect           | . 121 |

|    |         | 7.1.2   | Mesh routing interconnect            | . 123 |

|    |         | 7.1.3   | Track length                         | . 126 |

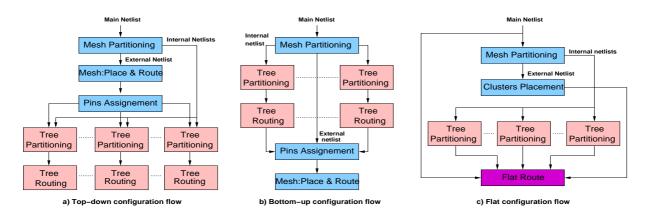

|    | 7.2     | Config  | guration flow                        | . 127 |

|    |         | 7.2.1   | Mesh partitioning                    | . 129 |

|    |         | 7.2.2   | Mesh placement                       | . 129 |

|    |         | 7.2.3   | Top-down pins assignment             | . 129 |

|    |         | 7.2.4   | Bottom-up pins assignment            | . 130 |

|    |         | 7.2.5   | Routing                              | . 131 |

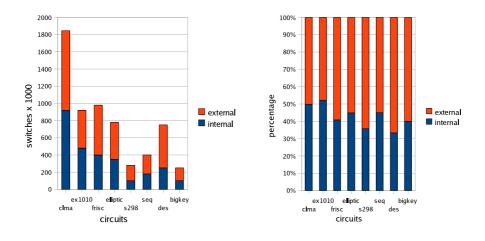

|    | 7.3     | Exper   | imental results                      | . 131 |

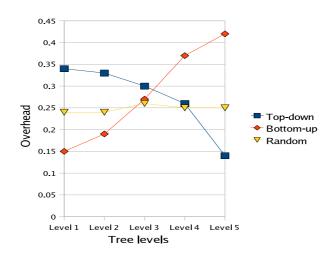

|    |         | 7.3.1   | Mesh of Tree: top-down vs. bottom-up | . 131 |

|    |         | 7.3.2   | Mesh of Tree vs. VPR-style Mesh      | . 133 |

|    | 7.4     | Concl   | usion                                | . 133 |

| Сс | onclu   | sion an | d Future Lines of Research           | 137   |

|    | 1       | Concl   | usion                                | . 137 |

|    | 2       | Future  | e work                               | . 140 |

| Li | st of ] | Publica | itions                               | 143   |

| Bi | bliog   | raphy   |                                      | 147   |

# List of Figures

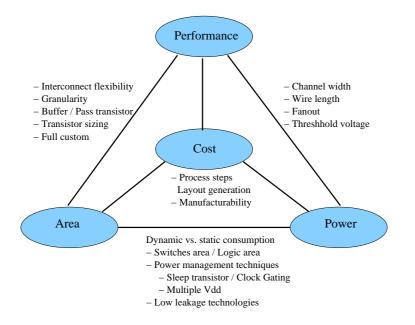

| 1    | Today's FPGA design challenges [M.Hutton, 2005]                              | 3   |

|------|------------------------------------------------------------------------------|-----|

| 1.1  | FPGA architecture model                                                      | 7   |

| 1.2  | LB and Logic clusters                                                        | 8   |

| 1.3  |                                                                              | 10  |

| 1.4  | Channel segmentation distribution                                            | 11  |

| 1.5  | Two types of programmable switches used in SRAM-based FPGAs                  | 11  |

| 1.6  | Altera's Stratix-II block diagram                                            | 13  |

| 1.7  | Stratix-II Logic Array Block (LAB) structure                                 | 14  |

| 1.8  | R4 interconnect connections                                                  | 14  |

| 1.9  | C4 interconnect connections                                                  | 16  |

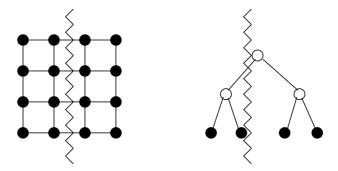

| 1.10 | Mesh vs. Tree structure                                                      | 17  |

| 1.11 | Hierarchical FPGA topology                                                   | 17  |

| 1.12 | HSRA interconnect structure                                                  | 18  |

| 1.13 | The APEX programmable logic devices [M.Hutton et al., 2001]                  | 19  |

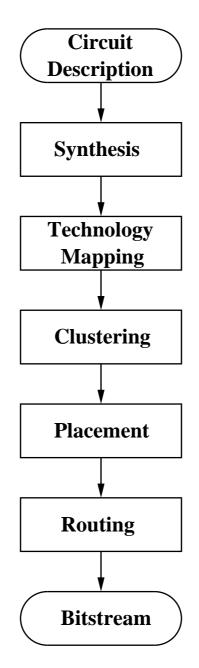

| 2.1  | FPGA CAD flow                                                                | 22  |

| 2.2  | Directed Acyclic Graph representation of a circuit                           | 23  |

| 2.3  | Example of Technology Mapping                                                | 23  |

| 2.4  |                                                                              | 24  |

| 2.5  | The gain bucket structure as illustrated in [C.M.Fiduccia and R.M.Mattheyese | es, |

|      | 1982]                                                                        | 28  |

| 2.6  | Multilevel Hypergraph Bisection                                              | 30  |

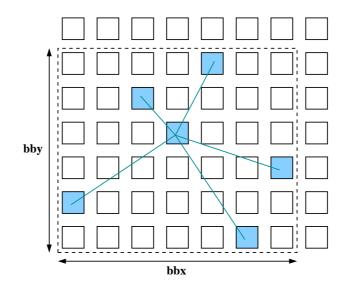

| 2.7  | Bounding Box of an hypothetical 6-terminals net [V.Betz et al., 1999]        | 32  |

| 2.8  | Modelling FPGA routing architecture as a directed graph [V.Betz et al.,      |     |

|      | 1999]                                                                        | 33  |

| 3.1  | Implication of local Rent exponent                                           | 38  |

| 3.2  | 0 $'$ $1$ $1$                                                                | 39  |

| 3.3  | Architectures exploration platform                                           | 40  |

#### xviii List of Figures

| 3.4  | Evaluation of several partitioning metrics                            | 41 |

|------|-----------------------------------------------------------------------|----|

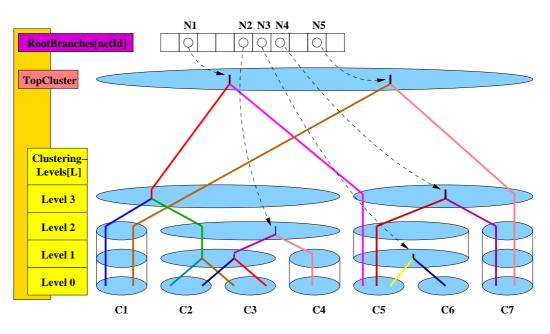

| 3.5  | Mangrove data structure: Multilevel clustered hypergraph              | 42 |

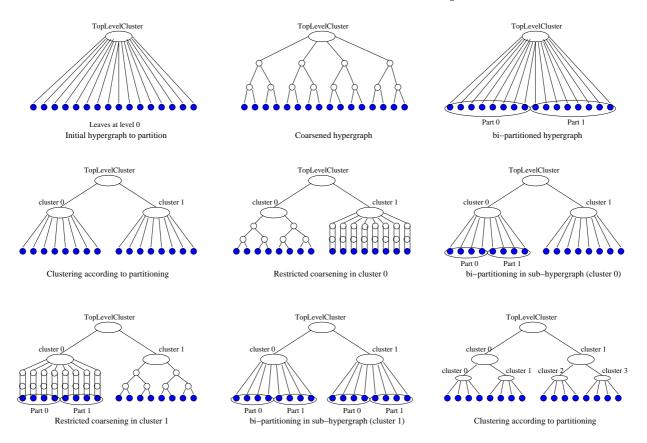

| 3.6  | 2-levels recursive bi-partitioning steps                              | 43 |

| 3.7  | Unidirectional vs. bidirectional wires                                | 45 |

| 3.8  | The minimal bisection width of a Mesh and a binary Tree               | 46 |

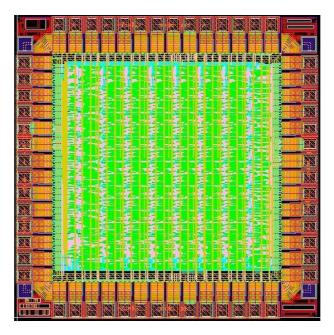

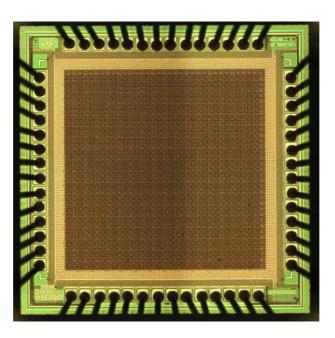

| 3.9  | Layout of a 8x8 Mesh architecture                                     | 48 |

| 3.10 | Microchip made on 130nm CMOS technology process                       | 50 |

| 3.11 | Single driver-based Mesh interconnect                                 | 51 |

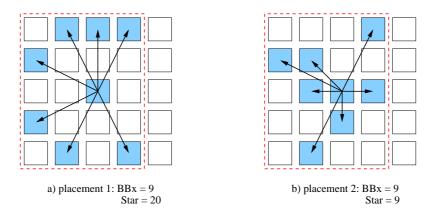

| 3.12 | Placements cost evaluation based on two different objective functions | 52 |

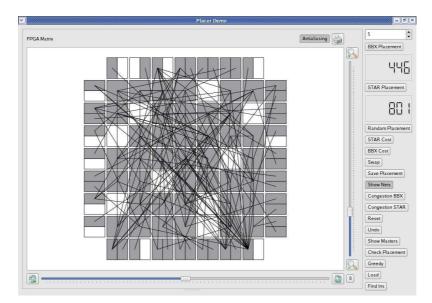

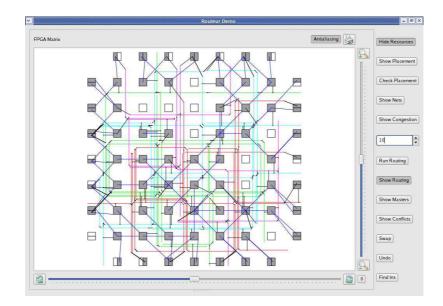

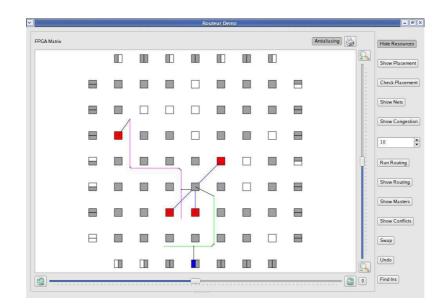

| 3.13 | Random netlist placement on CFPGA architecture                        | 53 |

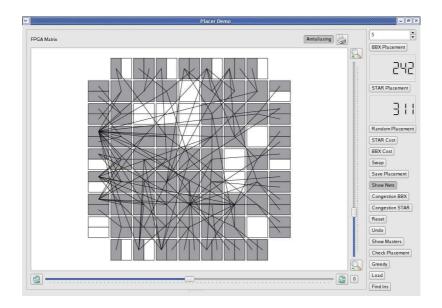

| 3.14 | Optimized netlist placement on CFPGA architecture                     | 54 |

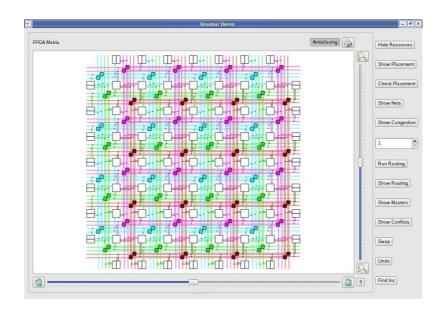

| 3.15 | CFPGA architecture routing resources                                  | 54 |

|      | Routed netlist on CFPGA architecture                                  | 55 |

| 3.17 | Routed signals connected to an LB                                     | 55 |

| 4.1  | General Tree-based architecture                                       | 58 |

| 4.2  | TFPGA: Tree based FPGA interconnect                                   | 59 |

| 4.3  | Switching node in 2-arity Hierarchical Interconnect [A.DeHon, 1996]   | 60 |

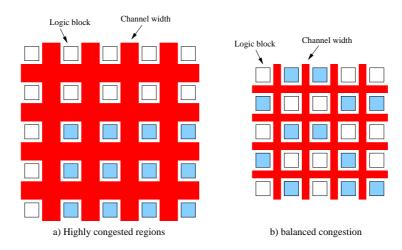

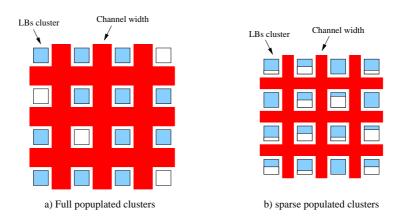

| 4.4  | Congestion-aware placement                                            | 61 |

| 4.5  | Congestion-aware clustering                                           | 62 |

| 4.6  | Reducing external routing demand [A.Singh and M.Marek-Sadowska,       | 02 |

| 1.0  | 2002]                                                                 | 63 |

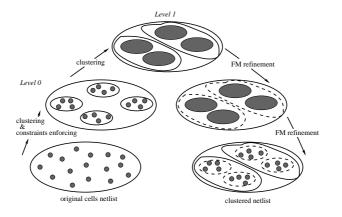

| 4.7  | Multilevel clustering & refinement                                    | 64 |

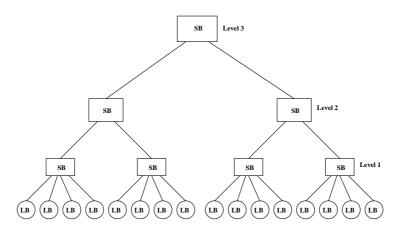

| 4.8  | 4x2x2 Tree architecture: clusters arity definition at every level     | 65 |

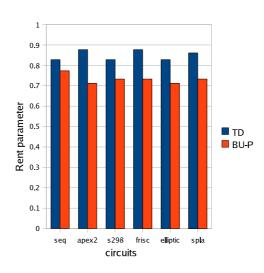

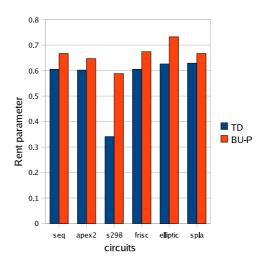

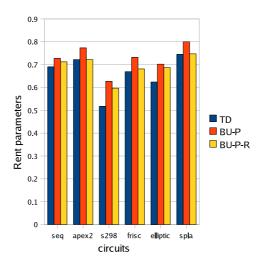

| 4.9  | Results for partitioning Rent's parameters at level 1                 | 66 |

| 4.10 | Results for partitioning Rent's parameters at level 3                 | 67 |

|      | Results for partitioning Rent's parameters at level 2                 | 67 |

|      |                                                                       |    |

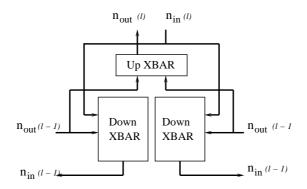

| 5.1  | MFPGA interconnect                                                    |    |

| 5.2  | Downward Network                                                      | 73 |

| 5.3  | Upward Network                                                        | 74 |

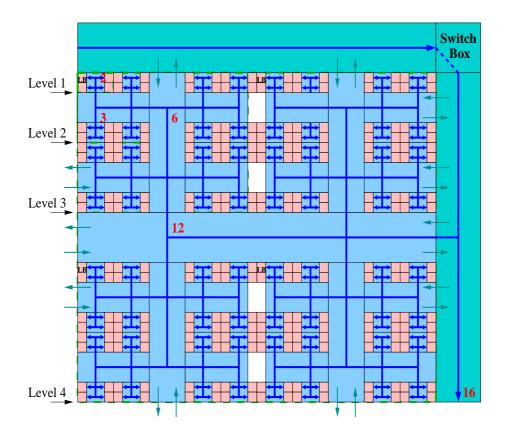

| 5.4  | 3-level MFPGA structure with $k = 4$ and $p = 1$                      | 75 |

| 5.5  | Netlist to route                                                      | 78 |

| 5.6  | Detailed placement example                                            | 79 |

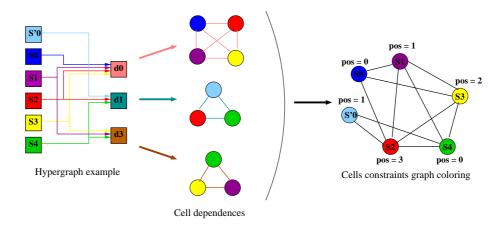

| 5.7  | CCH: Cell Constraints Hypergraph                                      | 80 |

| 5.8  | ACCG: Advanced Cell Constraints Graph                                 | 81 |

| 5.9  | Graph coloring problem                                                | 83 |

| 5.10 | Moves range limiters                                                  | 84 |

| 5.11 | Fanout reduction by means of replication                              | 86 |

|      | Routability improvement                                                    |

|------|----------------------------------------------------------------------------|

|      | Instances replication effect on graph coloring (detailed placement) 87     |

|      | Sub-paths timing caracterisation                                           |

|      | 4-levels symmetric MFPGA layout                                            |

| 5.16 | Timing graph modeling of a simple circuit                                  |

| 6.1  | Tree-based interconnect: upward and downward networks                      |

| 6.2  | Tree-based interconnect depopulation using Rent's rule (level 1 with $p =$ |

|      | 0.73)                                                                      |

| 6.3  | Interconnect switches distribution                                         |

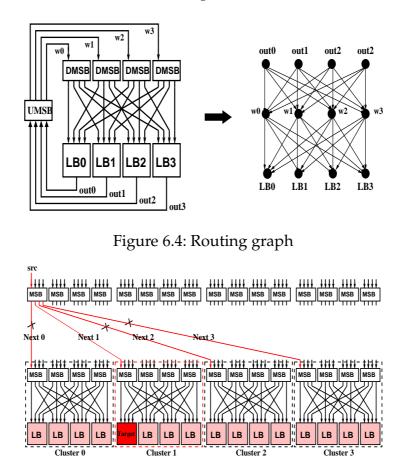

| 6.4  | Routing graph                                                              |

| 6.5  | Search space pruning                                                       |

| 6.6  | MFPGA architecture evaluation flow                                         |

| 6.7  | A netlist routing example                                                  |

| 6.8  | Overhead between Architecture and partitioned netlist Rent's parame-       |

|      | ters (21 benchmark avg.)                                                   |

| 6.9  | MFPGA area vs Mesh area (21 benchmark circuits)                            |

| 6.10 | Area distribution between interconnect resources and logic blocks 111      |

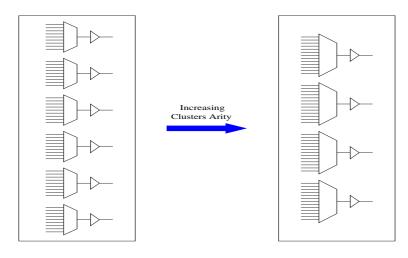

| 6.11 | MFPGA architectures with different arity factors                           |

| 6.12 | Varying multiplexers sizes and numbers                                     |

| 6.13 | Clusters arity effect on switches number                                   |

| 6.14 | Clusters arity effect on critical path crossed switches                    |

| 6.15 | Clusters arity effect on wires number (<=> Muxes number)                   |

| 6.16 | Total area for clusters sizes 4-8 (21 benchmark avg.)                      |

| 6.17 | LUTs number and LUT area versus LUT size (for cluster arity = 4) 115       |

| 6.18 | Critical path switches number clusters sizes 4-8 (21 benchmark avg.) 116   |

| 6.19 | Buffers number clusters sizes 4-8 (21 benchmark avg.)                      |

| 6.20 | SRAM points number clusters sizes 4-8 (21 benchmark avg.)                  |

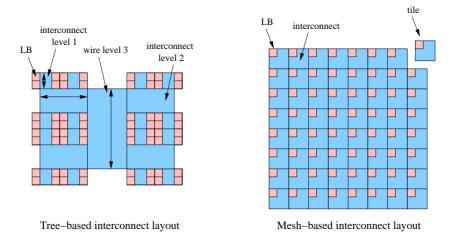

| 7.1  | Tree-based and Mesh-based layouts view                                     |

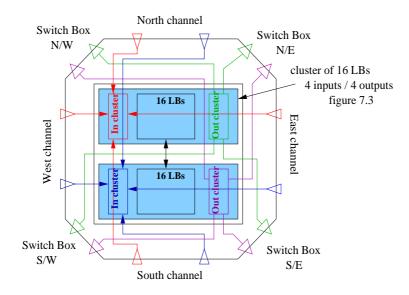

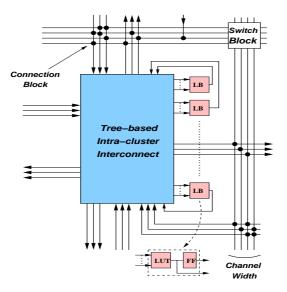

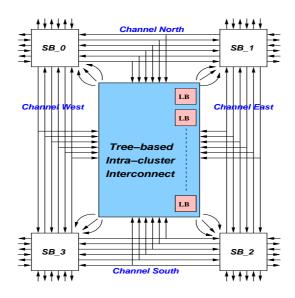

| 7.2  | cluster-based Mesh interconnect components                                 |

| 7.3  | 16-LBs cluster interface: External input and output connections            |

| 7.4  | Mesh clusters pins distribution                                            |

| 7.5  | Node of Mesh of Tree architecture with bidirectional wires                 |

| 7.6  | Connection block and switch box designs: bidirectional wires               |

| 7.7  | Mesh interconnect based on single-driver and unidirectional wires 125      |

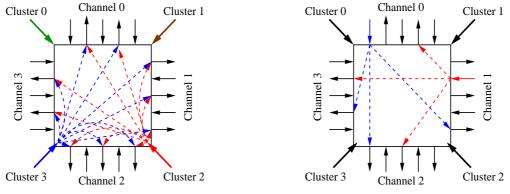

| 7.8  | Mesh switch box topology                                                   |

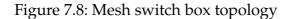

| 7.9  | Maximum wire lengths depending on Tree size (arity 4)                      |

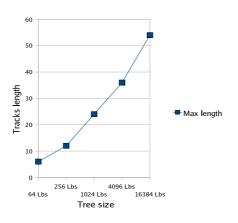

| 7.10 | Maximum wire lengths depending on Tree clusters arity (4096 LBs) 127       |

#### xx List of Figures

| 7.11   | Layout view of Mesh of Tree basic tile                                                    |

|--------|-------------------------------------------------------------------------------------------|

| 7.12   | Top-down Mesh of Tree configuration flow                                                  |

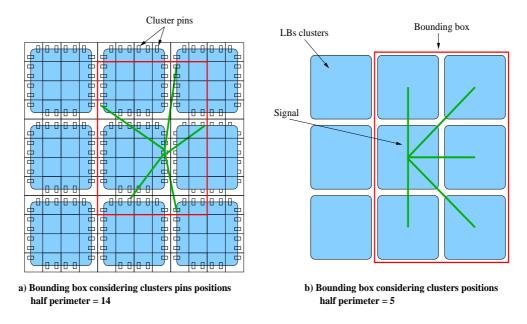

| 7.13   | Bounding box function evaluation                                                          |

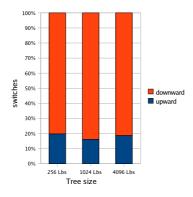

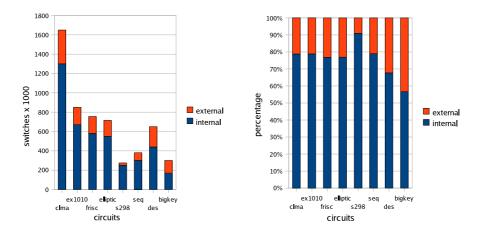

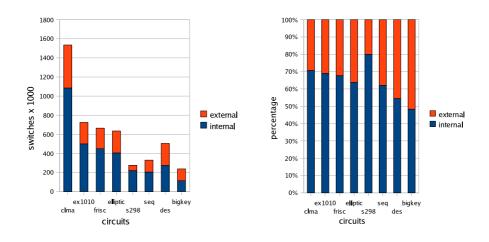

| 7.14   | Interconnect distribution in Mesh of Tree architecture: Bottom-up approach131             |

| 7.15   | Interconnect distribution in Mesh of Tree architecture: Top-down approach 132             |

| 7.16   | Interconnect distribution in Mesh of Tree architecture: Flat approach 132                 |

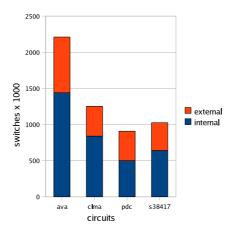

| 7.17   | Interconnect distribution in Mesh of Tree architecture                                    |

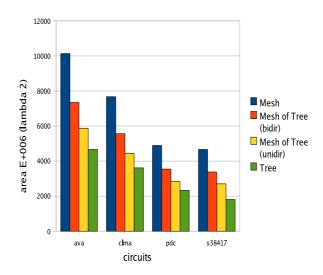

| 7.18   | Comparison of various FPGA architectures areas                                            |

| 1<br>2 | FPGA architectures tradeoffs139Tree-based architecture with heterogeneous logic blocks140 |

# List of Tables

| 3.1 | Standard cells characteristics                                        | 46  |

|-----|-----------------------------------------------------------------------|-----|

| 3.2 | Benchmarks characteristics                                            | 49  |

| 4.1 | Rent parameter partitioning results                                   | 66  |

| 4.2 | Switches comparison between Mesh-based FPGA architecture and TFPGA    | 69  |

| 5.1 | Detailed placement techniques evaluation                              | 93  |

| 5.2 | Clusters Moving effect                                                | 93  |

| 5.3 | Area Comparison: MFPGA vs Mesh                                        | 94  |

| 5.4 | Speed Comparison ( $0.13 \mu m$ CMOS, $1.2V$ )                        | 95  |

| 6.1 | Levels Rent's rule parameters                                         | 107 |

| 6.2 | Area and performance comparison between various optimizing approaches | 108 |

| 6.3 | Netlists and architectures characteristics                            | 109 |

| 6.4 | Tree vs. clustered VPR-style Mesh                                     | 110 |

| 6.5 | Levels Rent's parameters for 2 circuits                               | 112 |

| 7.1 | Mesh of Tree track length                                             | 127 |

| 7.2 | Mesh of Tree: switches requirement                                    | 134 |

# List of Algorithms

| 2.1 | Pseudo-code of the VPack algorithm [V.Betz et al., 1999]                    | 26   |

|-----|-----------------------------------------------------------------------------|------|

| 2.2 | Pseudo-code for FM heuristic [D.A.Papa and I.L.Markov, ]                    | 27   |

| 2.3 | Pseudo-code for the Multilevel Partitioning algorithm [D.A.Papa and I.L.Mar | kov, |

|     | ]                                                                           | 29   |

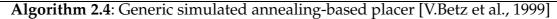

| 2.4 | Generic simulated annealing-based placer [V.Betz et al., 1999]              | 31   |

| 2.5 | Pseudo-code of the Path finder routing algorithm [L.McMurchie and C.Ebelin  | ۱g,  |

|     | 1995]                                                                       | 34   |

| 3.1 | pseudo-code to compute cost function variation after a single instance      |      |

|     | moving                                                                      | 51   |

| 5.1 | ACCG construction                                                           | 82   |

| 5.2 | Incremental cost computing                                                  | 84   |

| 5.3 | Constructed solution                                                        | 85   |

| 5.4 | Adapted <i>Pathfinder</i>                                                   | 88   |

# Introduction

Field-Programmable Gate Arrays are Integrated Circuits (ICs) whose functionality is programmed after manufacturing. They consist of configurable logic blocks and I/O blocks that are interconnected by a configurable routing. FPGAs are configured to implement user circuits by writing into the configuration memory that is embedded within the FPGA. Configuration memory is spread throughout the FPGA and defines the logical function of each configurable logic block and the connections within the configurable routing fabric. Although other methods exist, FPGA configuration memory is typically implemented using static RAM (SRAM). Other technologies used to implement configuration memory include antifuses [J.Greene et al., 1993] and floating gate transistors [S.Brown, 1994]. However, this thesis focuses on SRAM-based FPGA devices exclusively, since SRAM-based FPGAs are the most common commercial FPGAs.

Reconfigurability of FPGAs is fundamentally different from traditional general-purpose microprocessors. An application is implemented on a microprocessor by compiling the application to a stream of instructions that are sequentially decoded and executed by fixed, general-purpose logic resources. Unlike FPGAs, the functionality of a microprocessor's logic resources cannot be modified on a per-application basis. Instead, each application is compiled into a unique stream of instructions that are executed by the microprocessor. Since it is possible to express almost any application as a sequence of instructions, microprocessors are arguably the most flexible computational devices today. However, microprocessors often incur a performance penalty due to their very flexibility. To support flexibility, the fixed logic resources in a microprocessor are deliberately designed to execute certain basic computations efficiently. Consequently, applications that would benefit from customized, tailor-made logic resources often take a performance hit when executed on a general-purpose microprocessors.

While microprocessors are attractive for their flexibility, an Application Specific Integrated Circuit (ASIC) is a device that is customized to a specific application. Since the exact nature of the application is known beforehand, ASIC hardware resources are designed to provide the highest performance implementation for the application. The price paid by ASICs because of their superlative performance characteristics is flexibility. Once an ASIC has been manufactured, it is impossible to modify it to implement

#### 2 Introduction

another application, different from the one it was intended for. Further, since the Non-Recurring Engineering (NRE) costs involved in designing and manufacturing an ASIC are comparatively high, it is generally unfeasible to design and fabricate ASICs in low volumes.

Since their introduction in the mid eighties, FPGAs evolved from a simple, low-capacity gate array technology to devices [Stratix, II] [Virtex, 5] that provide a mix of coarsegrained data path units, microprocessor cores, on chip A/D conversion, and gate counts by millions. Today, FPGAs become important actors in the computational devices domain that was originally dominated by microprocessors and ASICs. Just like microprocessors, FPGA-based systems can be reprogrammed on a per-application basis. At the same time, FPGAs offer significant performance benefits over microprocessor implementations for a number of applications. Although these benefits are still generally an order of magnitude less than equivalent ASIC implementations, low NRE costs, fast time-to-market, and flexibility of FPGAs make them an attractive choice for low-tomedium volume applications.

In order to investigate the quality of different FPGA architectures, one needs CAD tools capable of implementing circuits automatically in each FPGA architecture of interest. Once a circuit has been implemented in an FPGA architecture, one needs next accurate area and delay models to evaluate the quality (speed achieved, area required) of the circuit implementation in the FPGA architecture under test.

Three factors combine to determine the characteristics of an FPGA: quality of the FPGA architecture, quality of the CAD tools used to map circuits into the FPGA, and electrical (i.e. transistor-level) design of the FPGA.

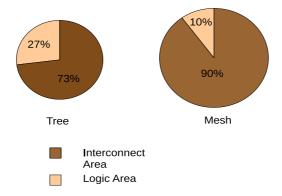

#### 1 Research goals and contributions

Despite their design cost advantage, FPGAs impose large area overheads when compared to custom silicon alternatives (ASICs). To illustrate the magnitude of this problem we refer to the work presented in [I.Kuon and J.Rose, 2007] where authors measure the gap between FPGAs and ASICs in terms of logic density, circuit speed and power consumption. It is shown that for circuits containing only look-up table-based logic and flip-flops, the ratio of silicon area required to implement them in FPGAs and ASICs is on average 35. The dynamic power consumption ratio is approximately 14 times. This is due essentially to the FPGA programmable interconnect which is the dominant area factor. In fact FPGAs have 90% routing and 10% logic occupancy. In addition interconnect is the major factor behind power dissipation. According to results shown in [L.Shang et al., 2002], the power dissipation share of routing, logic and clocking resources are 60%, 16% and 14%, respectively.

#### 1. Research goals and contributions 3

Figure 1: Today's FPGA design challenges [M.Hutton, 2005]

There is a considerable demand for FPGAs with less area, lower delay and power consumption. As illustrated in figure 1, the 4 features characterizing an FPGA are: Area, performance (achieved speed), power dissipation and cost (manufacturing). The tight interaction between these features can be explained by the following examples:

- Reducing total switches number may induce area and power dissipation reduction, however it can reduce flexibility and consequently increases path lengths (performance degradation).

- Using power management techniques reduces power at the cost of area increase, performances degradation and manufacturing cost increase.

Thus FPGA design big challenge is to find a good tradeoff between the 4 different features. A general method used to make FPGAs more efficient is to search for improvements to the numerous algorithmic steps which map a logic circuit into FPGA. Improvements to the logic synthesis step, for example, can reduce the amount and depth of needed logic. Also, improvements to the partitioning, placement, and clustering steps, such as those described in [V.Betz et al., 1999], can reduce interconnect use and delay by shortening connections. Similarly, improvements on the routing step can map critical delay paths to faster connections. Defining an FPGA architecture is a challenge of fixing logic and routing resources so that these algorithms produce the most efficient results possible. Since both algorithms and architectures can be simultaneously defined, there is a significant amount of interaction which can influence the final result.

#### 4 Introduction

The aim of this thesis is to present a new efficient way to design interconnection structures for programmable logic: the way in which the programmable wires are connected. We also propose a set of new CAD tools to map circuits on the proposed architecture and to explore its efficiency. The main characteristics of the proposed architecture topology are summarized in the following points:

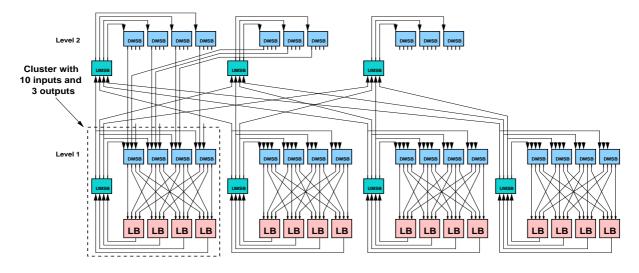

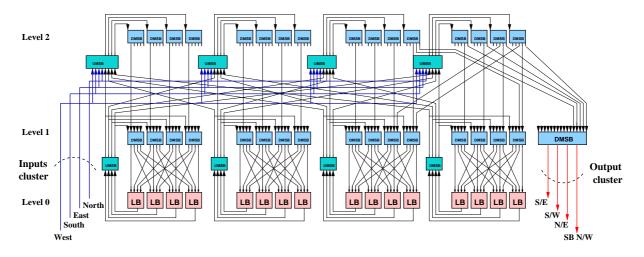

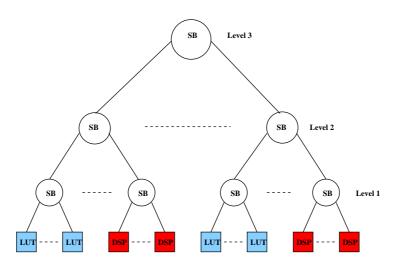

- Tree-based topology: Most logic designs exhibit locality of connections, which implies a hierarchy in the placement and routing of the connections between logic blocks. We propose a Tree-based FPGA (hierarchical) architecture which aims at exploiting this feature to provide smaller routing delays and more predictable timing behavior. This architecture is created by connecting logic blocks into clusters. Theses clusters are connected recursively to form a hierarchical structure.

- Interconnect depopulation: The interconnect structure in common FPGA architectures is designed generally to maximize logic utilization. Our philosophy is to design architectures with depopulated interconnect. Our purpose is to increase interconnect utilization at the expense of logic utilization. The philosophy behind depopulated routing architecture is to increase silicon utilization through efficient use of the interconnect structure, which accounts for 80-90% of the total area in common Mesh-based FPGA devices.

- Interconnect predictability: We use an interconnect topology based on the Butterfly fat Tree distribution. This structure offers a predictability feature since paths from sources to destinations are limited and predictable. This property is very interesting and can be exploited in the placement phase to improve routability.

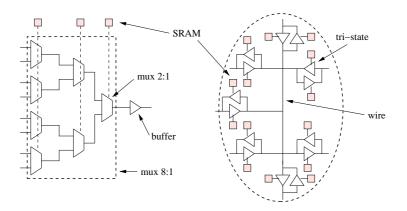

- Single driver interconnect: In early FPGA architectures, an interconnect wire was shared and could be driven by many possible resources. Although this made wires bidirectional, it required several large, tri-state buffers per wire and only one of which could be turned on for a specific configuration. Consequently numerous buffers were left unused, which added area, capacitance, power and delay. Modern Mesh FPGA architectures have shifted away from allowing multiple drivers to connect to each interconnect wire. It was shown in [G.Lemieux et al., 2004] that when single-driver wiring is used, area improves by 25% and delay improves by 9%. Common Tree-based FPGA architectures [A.DeHon, 1999] [Y.Lay and P.Wang, 1997] use bidirectional wires. In this thesis we propose a Tree-based interconnect having a single driver at starting point of each wire. Instead of tri-states, each driver has a multiplexer to select from many possible sources. This organization results in unidirectional wires. The benefit of using unidirectional wires is the elimination of bidirectional buffering and tri-states and consequently area reduction, performance improvement and power dissipation reduction.

#### 2 Outline

This section gives a brief overview of the contents of the following chapters:

The two first chapters give an overview of the current state-of-the-art FPGA architectures and configuration CAD tools. We start with describing some academic and industrial architectures with different interconnect topologies. The two most typical FPGA architectures are Mesh-based and Tree-based. Next, we describe the different steps of FPGA configuration flow. A survey of the most commonly used algorithms for each of these steps is provided.

Since the purpose of the thesis is to evaluate different FPGA architectures experimentally, we propose in the third chapter a generic exploration platform. In this environment we describe the different implemented tools and we explain their interaction with the target architecture. To evaluate each architecture we propose models and metrics to measure efficiencies in terms of area and speed performances.

In the three following chapters we present a progressive optimization of a Tree-based architecture. First, in chapter 4 we propose a basic architecture with fully populated switch boxes and optimized signals bandwidth. We conclude, based on a comparison with a common Mesh architecture, that optimizing only signals bandwidth is not sufficient. In chapter 5, we propose to optimize only switch boxes and to use large signals bandwidth. We conclude, based on the same comparison, that area density is much improved at the expense of routability degradation. Thus, in chapter 6 we propose an architecture combining a moderate optimization in terms of switch box population and signals bandwidth. We show experimentally, that this architecture has a good routability and interesting area density.

In the last chapter, we propose an architecture unifying both Mesh and Tree advantages, which are respectively: layout scalability and area efficiency. Finally, conclusions are provided along with possible directions for future research and development.

# FPGA Architectures

#### 1.1 Introduction

A field Programmable Gate Array (FPGA) is a prefabricated silicon device that can be reconfigured to implement various applications. Reconfigurability of an FPGA is derived from reprogrammable Static Random Access Memory (SRAM) cells. By program-

Figure 1.1: FPGA architecture model

#### 8 Chapter 1. FPGA Architectures

ming SRAM cells, the functionality of FPGA logic units can be tailored to implement a particular computation. Logic Blocks and interconnections (figure 1.1 are established by programming SRAM cells to connect prefabricated routing wires together. Thus, any given application can be mapped into an FPGA by programming functionality and connectivity of logic Blocks based on the specific characteristics of the application. The big challenge of FPGA is to provide the maximum flexibility with the minimum area cost. FPGA designers propose different architectures topologies to achieve this tradeoff. In this chapter we, first, describe the reconfigurable Logic Block which allows functional flexibility. Then, we describe different interconnect topologies which allow routing flexibility.

#### 1.2 Configurable Logic Blocks

Logic blocks implement the logical component of a user circuit. Since FPGAs must be flexible enough to implement any user circuit, FPGA logic blocks must be capable of implementing a wide range of logical functions. To achieve this flexibility, most commercial FPGAs use lookup-table (LUT) based logic blocks. A LUT with k inputs (k-LUT) contains  $2^k$  configuration bits and can implement any k-input function (or gate). Using LUTs with many inputs (large k) reduces the number of LUTs required to implement a user circuit and moreover reduces routing demands; however, it increases the area of the k-LUTs exponentially. By examining speed, area, and routability tradeoffs, previous works have shown that 4-input LUTs result in the fastest and the densest FPGAs [J.Rose et al., 1990] [E.Ahmed and J.Rose, 2000].

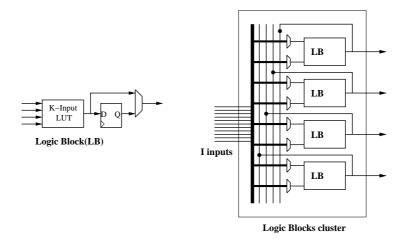

Figure 1.2: LB and Logic clusters

Early FPGAs had logic blocks that included a LUT, a flip-flop, and local interconnect.

This simple structure, called a logic block (LB), is illustrated in figure 1.2. To enhance their functionality, multiple LBs are combined into logic block with additional local interconnect. This larger structure, called a cluster, is also illustrated in figure 1.2. The advantages of clusters are similar to those of large LUTs: fewer logic blocks, less global routing, and better performance. However, the area penalty incurred by a cluster is much smaller than that of a large LUT. Modern FPGAs contain typically between 4 and 10 logic elements per cluster.

Most commercial FPGAs contain an increasingly larger number of hard macro blocks. As shown in figure 1.1, these macro blocks can include embedded memories, multipliers, or high speed I/Os. In this thesis we are interested to improve architecture performances based on interconnect topologies exploration. The FPGA model used in the following consists of programmable Logic Blocks (LBs) and programmable routing elements.

#### **1.3 Interconnect topologies**

FPGA routing interconnect connects internal FPGA components, such as logic blocks and I/O blocks. The performance and the density of an FPGA is largely determined by its routing architecture since routing accounts for most of the area, delay, and power of the FPGA.

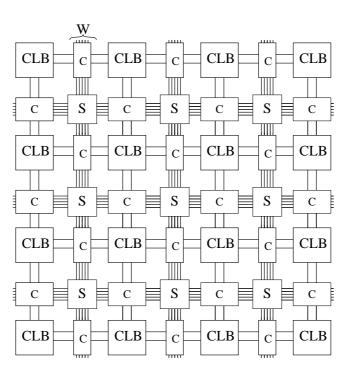

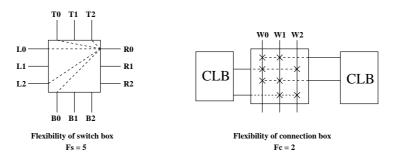

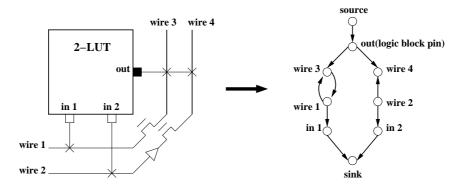

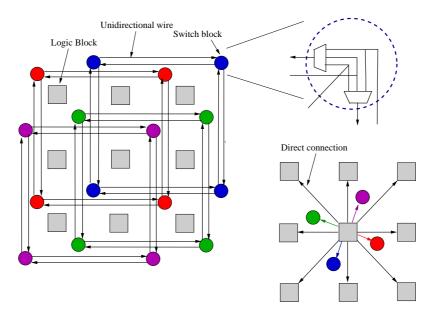

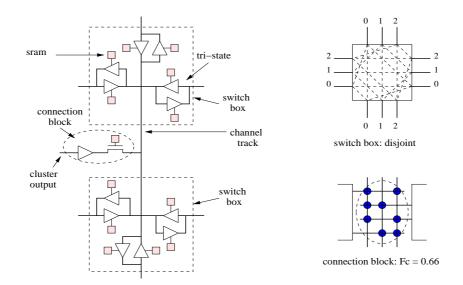

#### 1.3.1 VPR-based Mesh interconnect

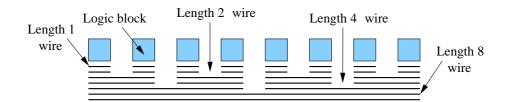

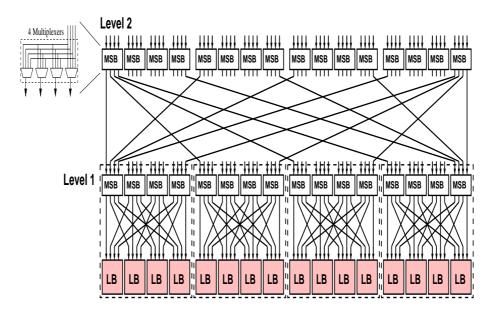

Mesh based FPGA are also called island-style FPGA, since, as illustrated in figure 1.3, logic blocks look like islands in a sea of configurable routing. Logic Blocks are typically arranged in a grid and are surrounded by horizontal and vertical routing channels. Mesh architectures are most common among academic and commercial FPGAs. The routing fabric consists of pre-fabricated wiring segments and programmable switches organized into rows and columns. The set of switches used to connect a logic block to an adjacent routing channel is called a connection block C. Similarly, the set of switches used to connect intersecting routing channels is called a switch block S. Every routing channel contains W parallel wire tracks, where W is called the channel width. The same width is used for all channels. Figure 1.3 illustrates these various routing structures. The structure of these individual routing components can be parametrized by routing channel width, segments distribution, connection block topology, and switch block topology. Segments distribution describes the lengths of the wire segments in the routing channels. Figure 1.4 shows an example of channel segmentation distribution. Longer wire segments span multiple blocks and require fewer switches, thereby reducing routing routing

#### 10 Chapter 1. FPGA Architectures

S : Switch Box

L : Logic Block

C : Connection Box

Figure 1.3: Mesh based FPGA architecture

Figure 1.4: Channel segmentation distribution

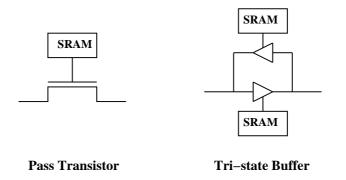

Figure 1.5: Two types of programmable switches used in SRAM-based FPGAs

area and delay. However, they also decrease routing flexibility, which reduces the probability that a user circuit can be routed successfully. Modern FPGAs commonly use a combination of long and short wires in order to balance this tradeoff.

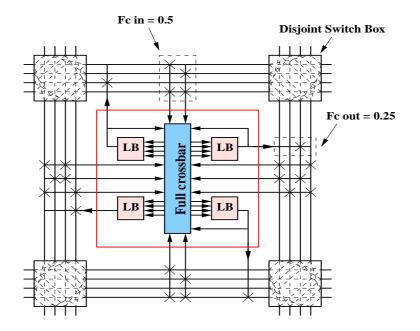

Connection and switch block topologies describe the interconnection pattern within these blocks. In terms of routability, fully populated blocks (that is, blocks for which any incident pin can be connected to any other incident pin) would be optimal. However, in terms of area, the cost would be prohibitive. Previous work [J.Rose et al., 1990, G.Lemieux and D.Lewis, 2002] has shown that connection and switch blocks still provide good routability even when only sparsely populated. Connection block population is defined by  $F_{c_{in}}$  and  $F_{c_{out}}$  parameters, where  $F_{c_{in}}$  is routing channel to cluster input switch density and  $F_{c_{out}}$  is cluster output to the routing channel density. Programmable SRAM-based switches within connection blocks and switch blocks can be implemented using either pass-transistors or tri-state buffers, as illustrated in Figure 1.5. Pass-transistor switches require less area and dissipate less power than tri-state buffer switches. However, tri-state buffer switches are faster for connections that span many segments. It is well known by VLSI designers [V.Adler and E.G.Friedman, 1997] that propagation delay through one pass transistor is smaller than corresponding delay through one buffer. However, it is also known that placing many pass transistors in series is much slower than a similar chain of buffers because delay grows quadratically with the former, but linearly with the latter. Routing architectures commonly use a combination of tri-state buffer and pass-transistor switches to reduce area and delay. Global networks, such as

### 12 Chapter 1. FPGA Architectures

clock and reset networks, are implemented with dedicated routing tracks which are separated from the configurable routing. Like other integrated circuits, FPGA clock distribution networks are designed to minimize skew in order to maximize system performance.

FPGA vendors do not offer FPGAs with different amounts of interconnects, for a given logic capacity. This is surprising since interconnect consumes nearly 90% of the chip area. Some reasons for not offering a variety of interconnect sizes are inventory control, the impact of marketing and sales of inferior or unroutable devices, and the large amount of engineering effort required to develop a single device. The LUT size, the number of LBs in every cluster and the number of inputs per cluster vary with each vendor. For all experiments performed in the main chapters of this thesis, those parameters are chosen to be consistent with previous work [E.Ahmed and J.Rose, 2000]. Note that the channel width of the FPGA is left as a variable. The CAD tools used in this thesis attempt to find the minimum possible channel width required to route a specific circuit. The amount of interconnect is tailored for the circuit to be implemented. This technique allows us to compare different interconnect topologies in terms of routability targeting different applications domains.

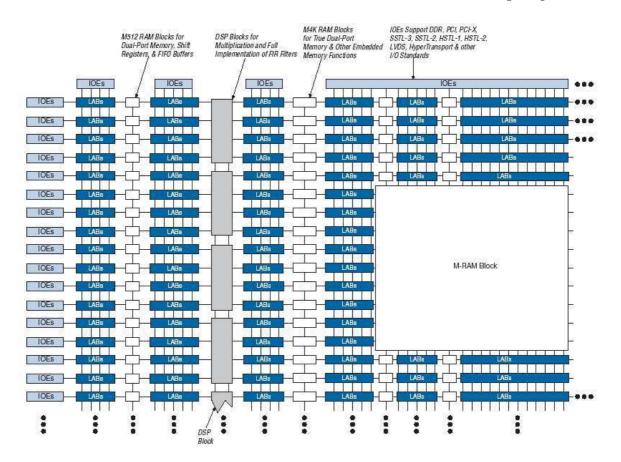

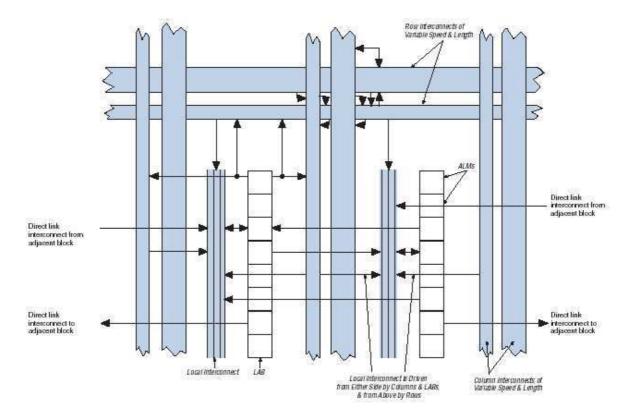

## 1.3.2 Altera's Stratix II architecture

Altera's Stratix II [Stratix, II] architecture is an industrial example of an island-style FPGA (Figure 1.6). The logic structure consists of LABs (Logic Array Blocks), memory blocks, and digital signal processing (DSP) blocks. LABs are used to implement general-purpose logic, and are symmetrically distributed in rows and columns throughout the device fabric. The DSP blocks are custom designed to implement full-precision multipliers of different granularities, and are grouped into columns. Input- and output-only elements (IOEs) represent the external interface of the device. IOEs are located along the periphery of the device.

Each Stratix II LAB consists of eight Adaptive Logic Modules (ALMs). An ALM consists of 2 adaptive LUTs (ALUTs) with eight inputs altogether. Construction of an ALM allows implementation of 2 separate 4-input Boolean functions. Further, an ALM can also be used to implement any six-input Boolean function, and some seven-input functions. In addition to lookup tables, an ALM provides 2 programmable registers, 2 dedicated full-adders, a carry chain, and a register-chain. Full-adders and carry chain can be used to implement arithmetic operations, and the register-chain is used to build shift registers. Outputs of an ALM drive all types of interconnect provided by the Stratix II device. Figure 1.7 illustrates a LAB interconnect interface.

Interconnections between LABs, RAM blocks, DSP blocks and the IOEs are established using the Multi-track interconnect structure. This interconnect structure consists of wire

Figure 1.6: Altera's Stratix-II block diagram

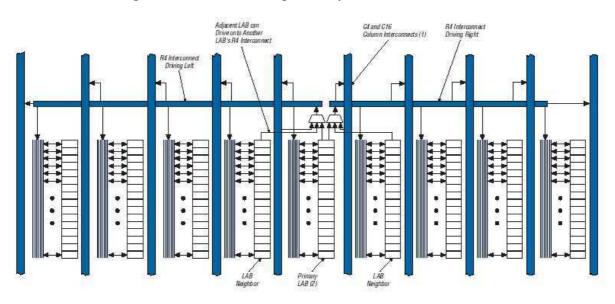

segments of different lengths and speeds. The interconnect wire-segments span fixed distances, and run in the horizontal (row interconnects) and vertical (column interconnects) directions. The row interconnects (Figure 1.8) can be used to route signals between LABs, DSP blocks, and memory blocks in the same row. Row interconnect resources are of the following types:

- Direct connections between LABs and adjacent blocks.

- R4 resources that span 4 blocks to the left or right.

- R24 resources that provide high-speed access across 24 columns.

Each LAB owns its set of R4 interconnects. A LAB has approximately equal numbers of driven-left and driven-right R4 interconnects. An R4 interconnect that is driven to the left can be driven by either the primary LAB (Figure 1.8) or the adjacent LAB to the left. Similarly, a driven-right R4 interconnect may be driven by the primary LAB or the LAB immediately to its right. Multiple R4 resources can be connected to each other to

### 14 Chapter 1. FPGA Architectures

Figure 1.7: Stratix-II Logic Array Block (LAB) structure

Figure 1.8: R4 interconnect connections

establish longer connections within the same row. R4 interconnects can also drive C4

and C16 column interconnects, and R24 high speed row resources.

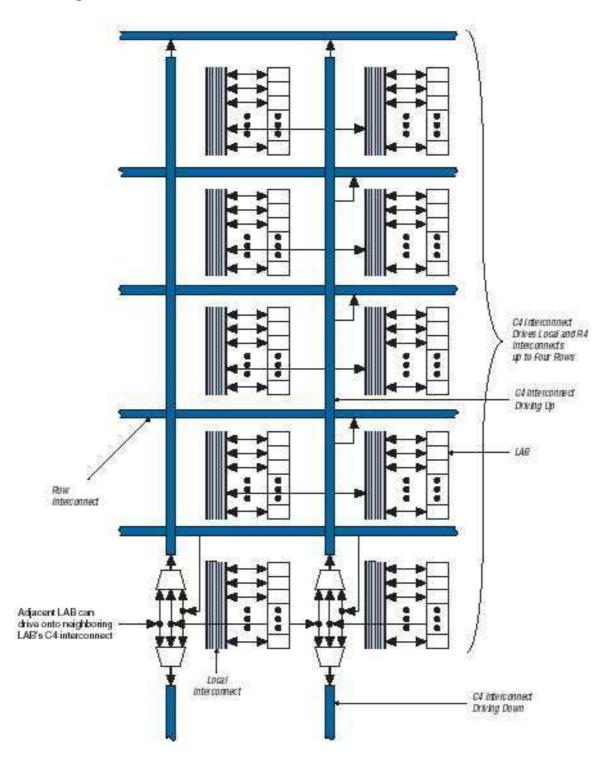

Column interconnect structure is similar to row interconnect structure. Column interconnects include:

- Carry chain interconnects within a LAB, and from LAB to LAB in the same column.

- Register chain interconnects.

- C4 resources that span 4 blocks in the up and down directions

- C16 resources for high-speed vertical routing across 16 rows.

Carry chain and register chain interconnects are separated from local interconnect (Figure 1.7) in a LAB. Each LAB has its own set of driven-up and driven-down C4 interconnects. C4 interconnects can also be driven by the LABs that are immediately adjacent to the primary LAB. Multiple C4 resources can be connected to each other to form longer connections within a column, and C4 interconnects can also drive row interconnects to establish column-to-column interconnections. C16 interconnects are high-speed vertical resources that span 16 LABs. A C16 interconnect can drive row and column interconnects at every fourth LAB. A LAB local interconnect structure cannot be directly driven by a C16 interconnect; only C4 and R4 interconnects can drive a LAB local interconnect structure. Figure 1.9 shows the C4 interconnect structure in the Stratix II device.

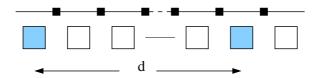

## 1.3.3 Multilevel Hierarchical Interconnect

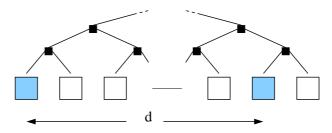

Most logic designs exhibit locality of connections implying a hierarchy in placement and routing of connections between logic blocks. The Hierarchical FPGA architecture attempts to exploit this feature to provide smaller routing delays and more predictable timing behavior. Multilevel hierarchical architecture is created by connecting logic blocks into clusters. These clusters are recursively connected to form a hierarchical structure. The speed of a net is determined by the number of routing switches it has to pass through and the length of wires. The relationship between switch delay and wire delay is explained in section 3.3.3. In a Mesh structure, the number of segments in series increases linearly with manhattan distance *d*, between the logic blocks to be connected. An advantage of a Tree connectivity is that the number of switches in series in a route connecting 2 logic blocks increases as a logarithmic function of the manhattan distance. This is illustrated on figure 1.10.

We assume that Multilevel hierarchical interconnect regroups architectures with more than 2 levels of hierarchy and Tree-based ones. For example VPR and APEX architectures are not included in this category since they have only 2 levels of hierarchy.

## 16 Chapter 1. FPGA Architectures

Figure 1.9: C4 interconnect connections

(a) Number of Series Switches in a Mesh Structure

(b) Number of Series Switches in a Tree Structure

Figure 1.10: Mesh vs. Tree structure

#### HFPGA: Hierarchical FPGA

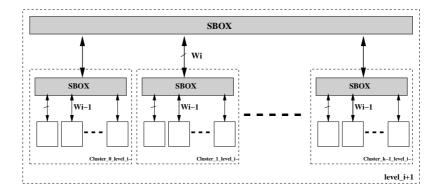

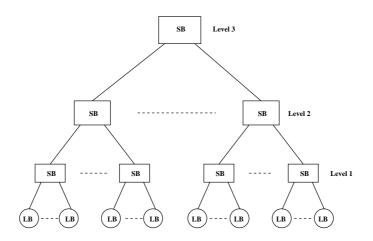

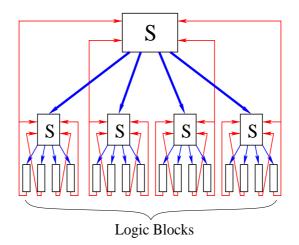

In the hierarchical FPGA called HFPGA, LBs are grouped into clusters. Clusters are then grouped

Figure 1.11: Hierarchical FPGA topology

recursively together (see figure 1.11). The clustered VPR mesh architecture has a Hierarchical topology with only two levels. Here we consider multilevel hierarchical architectures with more than 2 levels. In [A.Aggarwal and D.M.Lewis, 1994] and [Y.Lay and P.Wang, 1997] various hierarchical structures were discussed. The HFPGA routability depends on switch boxes topologies. HFPGAs comprising fully populated switch boxes ensure 100% routability but are very

#### 18 Chapter 1. FPGA Architectures

penalizing in terms of area. In [Y.Lay and P.Wang, 1997] authors explored the HFPGA architecture, investigating how the switch pattern can be partly depopulated while maintaining a good routability.

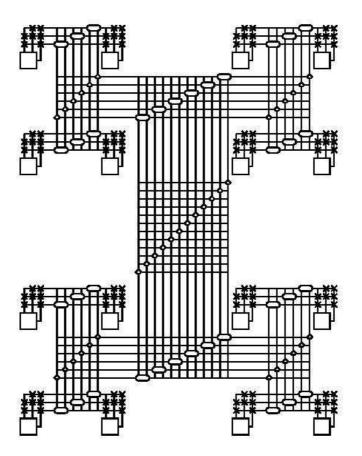

#### HSRA: Hierarchical Synchronous Reconfigurable Array

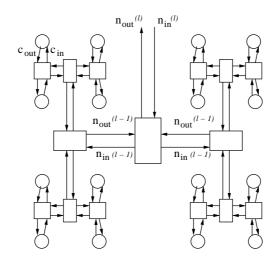

A well-known academic hierarchical FPGA is the Hierarchical Synchronous Reconfigurable

Figure 1.12: HSRA interconnect structure

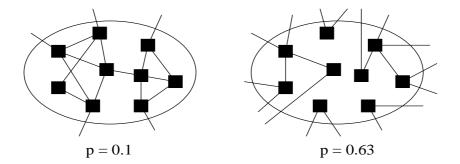

Array (HSRA) [A.DeHon, 1999]. HSRA has a strictly hierarchical, Tree-based interconnect structure (Figure 2-6). Consequently, HSRA logic and interconnect structures are not as closely coupled as the logic and interconnect structures of island-style FPGAs. Recall that every LAB in Altera's Stratix II device owns R4 and C4 interconnects. In HSRA, the only wire-segments that directly connect to the logic units are located at the leaves of the interconnect tree. All other wire-segments are decoupled from the logic structure. A HSRA logic unit consists of a single 4-LUT / D-FF pair. The input-pin connectivity is based on a choose- k strategy [A.DeHon, 1999], and the output pins are fully connected. The richness of HSRA interconnect structure is defined by its base channel width and interconnect growth rate. The base channel width c is the number of tracks at the leaves of the interconnect Tree (in figure 1.12, c = 3). Growth rate p is the rate at which the interconnect grows towards the root (in figure 1.12, p = 0.5). The growth rate is realized using the following types of switch-blocks:

- Non-compressing (2:1) switch blocks The number of root-going tracks is equal to the sum of the number of root-going tracks of the two children.

- Compressing (1:1) switch blocks The number of root-going tracks is equal to the number of root-going tracks of either child.

A repeating combination of non-compressing and compressing switch blocks can be used to realize any value of p less than one. For example, a repeating pattern of (2:1 1:1) switch blocks realizes p = 0.5, while the pattern (2:1 2:1 1:1) realizes p = 0.67. A HSRA that has only 2:1 switch blocks provides maximum interconnection bandwidth (i.e. a value of p = 1).

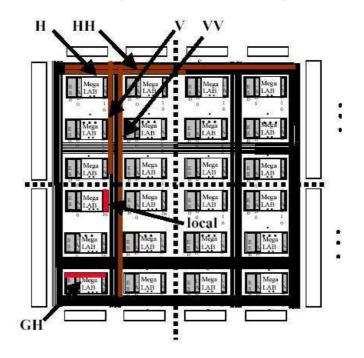

#### APEX Altera

APEX architecture is a commercial product from Altera Corporation which includes 3 lev-

Figure 1.13: The APEX programmable logic devices [M.Hutton et al., 2001]

els of interconnect hierarchy. Figure 1.13 shows a diagram of the APEX 20K400 programmable logic device. The basic logic-element (LE) is a 4-input LUT and DFF pair. Groups of 10 LEs are grouped into a logic-array-block or LAB. Interconnect within a LAB is complete, meaning that a connection from the output of any LE to the input of another LE in its LAB always exists, and any signal entering the input region can reach every LE.

#### 20 Chapter 1. FPGA Architectures

Groups of 16 LABs form a MegaLab. Interconnect within a MegaLab requires an LE to drive a GH (MegaLab global H) line, a horizontal line, which switches into the input region of any other LAB in the same MegaLab. Adjacent LABs have the ability to interleave their input regions, so an LE in  $LAB_i$  can usually drive  $LAB_{i+1}$  without using a GH line. A 20K400 MegaLab contains 279 GH lines.

The top-level architecture is a 4 by 26 array of MegaLabs. Communication between MegaLabs is accomplished by global H (horizontal) and V (vertical) wires, that switch at their intersection points. The H and V lines are segmented by a bidirectional segmentation buffer at the horizontal and vertical centers of the chip. In figure 1.13, We denote the use of a single (half-chip) line as H or V and a double or full-chip line through the segmentation buffer as HH or VV. The 20K400 contains 100 H lines per MegaLab row, and 80 V lines per LAB-column.

# 1.4 Conclusion

The interconnect structure of a Mesh-based FPGA is generally designed to maximize logic utilization. Hierarchical FPGAs belong to the class of routing-poor FPGA architectures that are designed to increase interconnect utilization at the expense of logic utilization. The philosophy behind routing-poor architectures is increased silicon utilization through efficient use of the interconnect structure (which may account for  $\sim 80-90\%$  of the total area in island-style FPGAs). The most used and studied architecture is the Mesh. In the following chapters we will focus on the Tree-based topology interconnect and we will try to combine it with the Mesh to take advantage of both architectures merits.

2

# FPGA Configuration CAD Flow

FPGA architectures have been intensely investigated over the past two decades. A major aspect of FPGA architecture research is the development of Computer Aided Design (CAD) tools for mapping applications to FPGAs. It is well established that the quality of an FPGA-based implementation is largely determined by the effectiveness of accompanying suite of CAD tools. Benefits of an otherwise well designed, feature rich FPGA architecture might be impaired if the CAD tools cannot take advantage of the features that the FPGA provides. Thus, CAD algorithm research is essential to the necessary architectural advancement to narrow the performance gaps between FPGAs and other computational devices like ASICs.

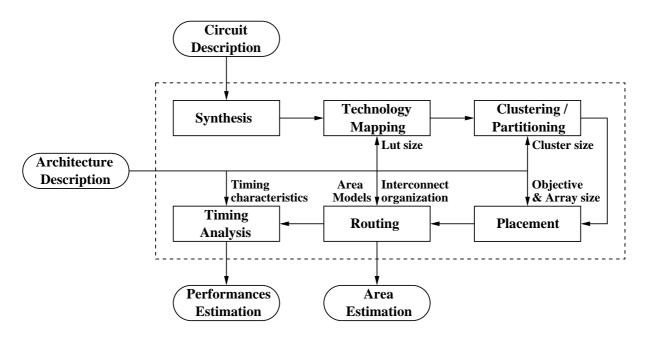

The process of converting a circuit description into a format that can be loaded into an FPGA can be roughly divided into five distinct steps, namely: synthesis, technology mapping, clustering, placement and routing. The final output of FPGA CAD tools is a bitstream that configures the state of the memory bits in an FPGA. The state of these bits determines the logical function that the FPGA implements. Figure 2.1 shows a flowchart of the FPGA CAD flow. In the following sections, we describe the typical algorithms used in each step of the CAD flow.

## 2.1 Synthesis

Synthesis involves translating a circuit description, traditionally written in a hardware description language (HDL) (e.g. VHDL or Verilog), into a gate-level representation. The gate-level representation is a network consisting of Boolean logic gates and flip-flops. There are no FPGAspecific optimizations performed during synthesis since this is normally a technology independent step. Further details concerning synthesis are omitted because they are beyond the scope

Figure 2.1: FPGA CAD flow

Figure 2.2: Directed Acyclic Graph representation of a circuit

Figure 2.3: Example of Technology Mapping

of this thesis.

# 2.2 Technology Mapping

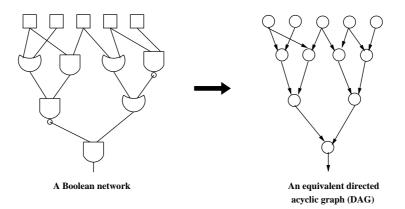

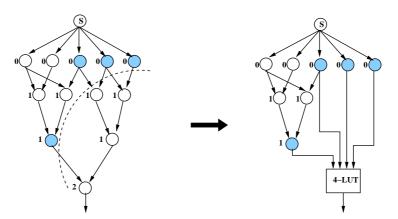

The output from synthesis tools is a circuit description of Boolean logic gates, flip-flops and wiring connections between these elements. The circuit can also be represented by a Directed Acyclic Graph (DAG). Each node in the graph represents a gate, flip-flop, primary input or primary output. Each edge in the graph represents a connection between two circuit elements. Figure 2.2 shows an example of a DAG representation of a circuit. Given a library of cells, the technology mapping problem can be expressed as finding a network of cells that implements the Boolean network. In the FPGA technology mapping problem, the library of cells is composed of k-input LUTs and flip-flops. Therefore, FPGA technology mapping involves transforming the Boolean network into k-bounded cells. Each cell can then be implemented as an independent k-LUT. Figure 2.3 shows an example of transforming a Boolean network into k-bounded cells. Technology mapping algorithms can optimize a design for a set of objectives including depth,

Figure 2.4: Example of clustering

area or power. The FlowMap algorithm [J.Cong and Y.Ding, 1994a] is the most widely used academic tool for FPGA technology mapping. FlowMap is a breakthrough in FPGA technology mapping because it is able to find a depth-optimal solution in polynomial time. FlowMap guarantees depth optimality at the expense of logic duplication. Since the introduction of FlowMap, numerous technology mappers have been designed that optimize for area and run-time while still maintaining the depth-optimality of the circuit [J.Cong and Y.Ding, 1994b] [J.Cong and Y.Hwang, 1995] [J.Cong and Y.Ding, 2000]. The result of the technology mapping step generates a network of k-bounded LUTs and flip-flops.

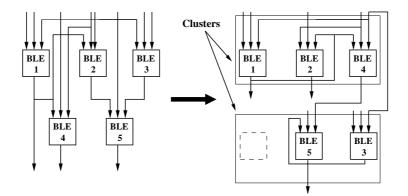

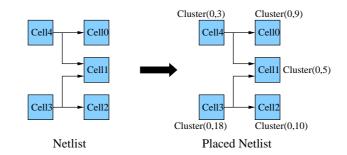

# 2.3 Clustering

The logic elements in a Mesh-based FPGA are typically arranged in two levels of hierarchy. The first level consists of logic blocks (LBs) which are k-input LUT and flip-flop pairs. The second level hierarchy groups *k* LBs together to form logic blocks clusters. The clustering phase of the FPGA CAD flow is the process of forming groups of *k* LBs. These clusters can then be mapped directly to a logic element on an FPGA. Figure 2.4 shows an example of the clustering process. Clustering algorithms can be broadly categorized into three general approaches, namely top-down [D.Huang and A.Kahng, 1995] [L.Hagen and A.Kahng, 1997], depth-optimal [R.Murgai et al., 1991] [M.Dehkordi and S.Brown, 2002] and bottom-up [A.Marquart et al., 1999] [E.Bozorgzadeh and al, 2004] [A.Singh and M.Marek-Sadowska, 2002]. Top-down approaches partition the LBs into clusters by successively subdividing the network or by iteratively moving LBs between parts. Depth-optimal solutions attempt to minimize delay at the expense of logic duplication. Bottom-up approaches are generally preferred for FPGA CAD tools due to their fast run times and reasonable timing delays. They only consider local connectivity information and can easily satisfy clusters pin constraints. Top-down approaches offer the best solutions; however, their computational complexity can be prohibitive.

#### 2.3.1 Bottom-up approaches

Bottom-up approaches build clusters sequentially one at a time. The process starts by choosing an LB which acts as a cluster seed. LBs are then greedily selected and added to the cluster, applying various attraction functions. The VPack [A.Marquart et al., 1999] attraction function is based on the number of shared nets between a candidate LB and the LBs that are already in the cluster. For each cluster, the attraction function is used to select a seed LB from the set of all LBs that have not already been packed. After packing a seed LB into the new cluster, a second attraction function selects new LBs to pack into the cluster. LBs are packed into the cluster until the cluster reaches full capacity or all cluster inputs have been used. If all cluster inputs become occupied before this cluster reaches full capacity, a hill-climbing technique is applied, searching for LBs that do not increase the number of inputs used by the cluster. The VPack pseudo-code is outlined in algorithm 2.1.

T-VPack [V.Betz et al., 1999] is a timing-driven version of VPack which gives added weight to grouping LBs on the critical path together. The algorithm is identical to VPack, however, the attraction functions which select the LBs to be packed into the clusters are different. The VPack seed function chooses LBs with the most used inputs, whereas the T-VPack seed function chooses LBs with the most used attraction function chooses LBs with the largest number of connections with the LBs already packed into the cluster. T-VPack's second attraction function has two components for a LB *B* being considered for cluster *C*:

$$Attraction(B,C) = \alpha.Crit(B) + (1-\alpha)\frac{|Nets(B) \cap Nets(C)|}{G}$$

(2.1)

where Crit(B) is a measure of how close LB *B* is to being on the critical path, Nets(B) is the set of nets connected to LB *B*, Nets(C) is the set of nets connected to the LBs already selected for cluster *C*,  $\alpha$  is a user-defined constant which determines the relative importance of the attraction components, and *G* is a normalizing factor. The first component of T-VPack's second attraction function chooses critical-path LBs, and the second chooses LBs that share many connections with the LBs already packed into the cluster. By initializing and then packing clusters with criticalpath LBs, the algorithm is able to absorb long sequences of critical-path LBs into clusters. This minimizes circuit delay since the local interconnect within the cluster is significantly faster than the global interconnect of the FPGA.

RPack [E.Bozorgzadeh and al, 2004] improves routability of a circuit by introducing a new set of routability metrics. RPack significantly reduced the channel widths required by circuits compared to VPack. T-RPack [E.Bozorgzadeh and al, 2004] is a timing driven version of RPack which is similar to T-VPack by giving added weight to grouping LBs on the critical path.

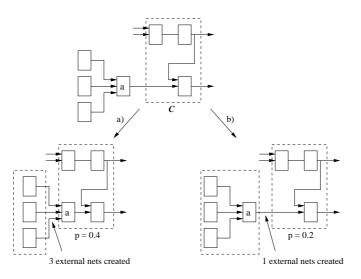

iRAC [A.Singh and M.Marek-Sadowska, 2002] improves the routability of circuits even further by using an attraction function that attempts to encapsulate as many low fanout nets as possible within a cluster. If a net can be completely encapsulated within a cluster, there is no need to route that net in the external routing network. By encapsulating as many nets as possible within clusters, routability is improved because there are less external nets to route in total.

```

UnclusteredLBs = PatternMatchToLBs(LUTs,Registers);

LogicClusters = NULL;

while UnclusteredLBs != NULL do

C = GetLBwithMostUsedInputs(UnclusteredLBs);

while |C| < k do

/*cluster is not full*/

BestLB = MaxAttractionLegalLB(C,UnclusteredLBs);

if BestLB == NULL then

/*No LB can be added to this cluster*/

break;

endif

UnclusteredLBs = UnclusteredLB - BestLB;

C = C \cup BestLB;

endw

if |C| < k then

/*Cluster is not full - try hill climbing*/

while |C| < k do

BestLB = MinClusterInputIncreaseLB(C,UnclusteredLBs);

C = C \cup BestLB;

UnclusteredLBs = UnclusteredLB - BestLB;

endw

if ClusterIsIllegal(C) then

RestoreToLastLegalState(C,UnclusteredLBs);

endif

endif

LogicClusters = LogicClusters \cup C;

endw

```

Algorithm 2.1: Pseudo-code of the VPack algorithm [V.Betz et al., 1999]

## 2.3.2 Top-down approaches

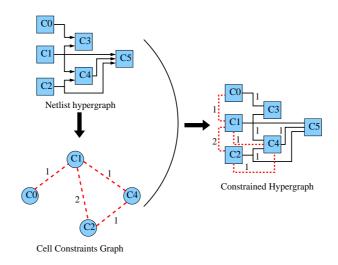

The K-way partitioning problem seeks to minimize a given cost function of such an assignment. A standard cost function is net cut, which is the number of hyperedges that span more than one partition, or more generally, the sum of weights of such hyperedges. Constraints are typically imposed on the solution, and make the problem difficult. For example some vertices can be fixed in their parts or the total vertex weight in each part must be limited (balance constraint and FPGA clusters size). With balance constraints, the problem of partitioning optimally a hypergraph is known to be NP-hard [M.Garey and D.Johnson, 1979]. However, since partitioning is critical in several practical applications, heuristic algorithms were developed with near-linear runtime. Such move-based heuristics for k-way hypergraph partitioning appear in [B.Kernighan

and S.Lin, 1970] [C.M.Fiduccia and R.M.Mattheyeses, 1982] [T.Bui et al., 1987].

#### Fiduccia-Mattheyses algorithm

The Fiduccia-Mattheyses (FM) heuristics [C.M.Fiduccia and R.M.Mattheyeses, 1982] work by prioritizing moves by gain. A move changes to which partition a particular vertex belongs, and the gain is the corresponding change of the cost function. After each vertex is moved, gains for connected modules are updated.

The Fiduccia-Mattheyses (FM) heuristic for partitioning hypergraphs is an iterative improve-

```

partitioning = initial_solution;

while solution quality improves do

Initialize gain_container from partitioning;

solution_cost = partitioning.get_cost();

while not all vertices locked do

move = choose_move();

solution_cost += gain_container.get_gain(move);

gain_container.lock_vertex(move.vertex());

gain_update(move);

partitioning.apply(move);

endw

roll back partitioning to best seen solution;

gain_container.unlock_all();

endw

```

#### Algorithm 2.2: Pseudo-code for FM heuristic [D.A.Papa and I.L.Markov, ]

ment algorithm. FM starts with a possibly random solution and changes the solution by a sequence of moves which are organized as passes. At the beginning of a pass, all vertices are free to move (unlocked), and each possible move is labeled with the immediate change to the cost it would cause; this is called the gain of the move (positive gains reduce solution cost, while negative gains increase it). Iteratively, a move with highest gain is selected and executed, and the moving vertex is locked, i.e., is not allowed to move again during that pass. Since moving a vertex can change gains of adjacent vertices, after a move is executed all affected gains are updated. Selection and execution of a best-gain move, followed by gain update, are repeated until every vertex is locked. Then, the best solution seen during the pass is adopted as the starting solution of the next pass. The algorithm terminates when a pass fails to improve solution quality. Pseudo-code for the FM heuristic is given in algorithm 2.2.

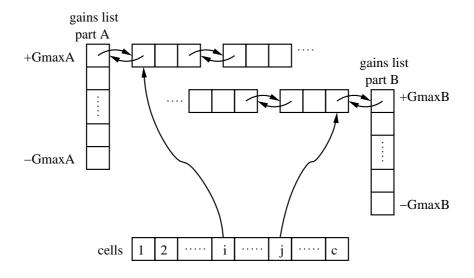

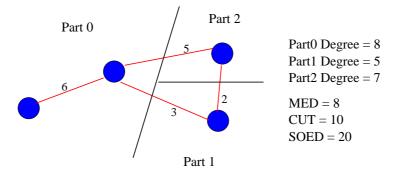

The FM algorithm has 3 main components (1) computation of initial gain values at the beginning of a pass; (2) the retrieval of the best-gain (feasible) move; and (3) the update of all affected gain values after a move is made. One contribution of Fiduccia and Mattheyses lies in observing that circuit hypergraphs are sparse, and any move's gain is bounded between plus and minus

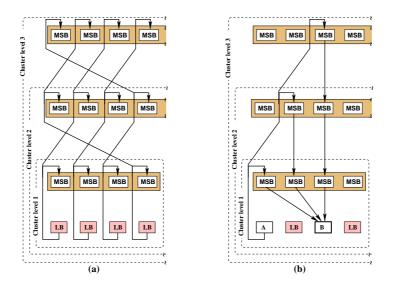

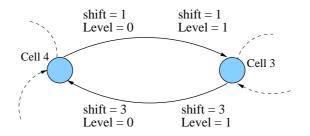

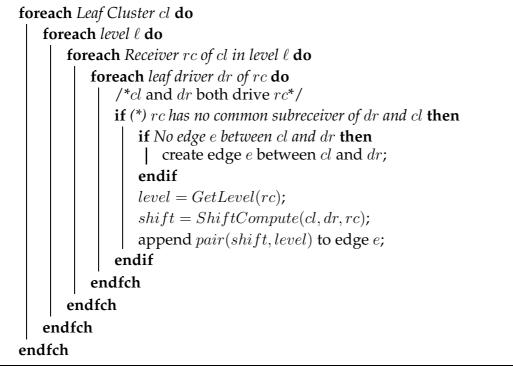

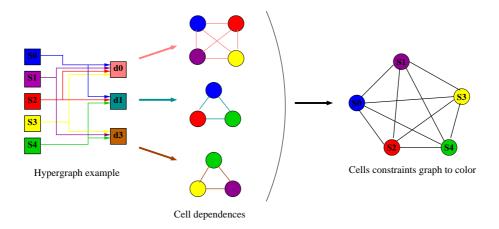

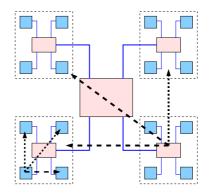

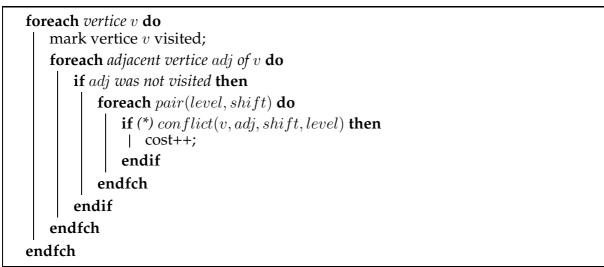

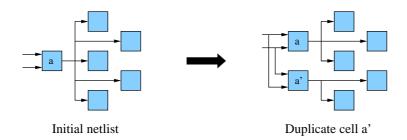

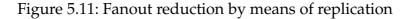

Figure 2.5: The gain bucket structure as illustrated in [C.M.Fiduccia and R.M.Mattheyeses, 1982]