# Iterative receivers: scheduling, convergence speed and complexity

Salim Haddad

### ▶ To cite this version:

Salim Haddad. Iterative receivers: scheduling, convergence speed and complexity. Electronics. Télécom Bretagne, Université de Bretagne-Sud, 2012. English. NNT: . tel-00821905

## HAL Id: tel-00821905 https://theses.hal.science/tel-00821905

Submitted on 13 May 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Sous le sceau de l'Université européenne de Bretagne

## **Télécom Bretagne**

En habilitation conjointe avec l'Université de Bretagne-Sud

Ecole Doctorale - SICMA

Récepteurs itératifs : ordonnancement, convergence et complexité

## Thèse de Doctorat

Mention : STIC (Sciences et Technologies de l'Information et de la Communication)

Présentée par Salim HADDAD

Département : Electronique

Laboratoire : Lab-STICC / Pôle CACS

Directeur de thèse : Michel Jézéquel

Soutenue le 16 novembre 2012

#### Jury :

| M. Fabrice Monteiro, | Professeur à l'Université de Lorraine                     | (Président)   |

|----------------------|-----------------------------------------------------------|---------------|

| M. Maryline Hélard,  | Professeure à l'INSA de Rennes                            | (Rapporteur)  |

| M. Guido Masera,     | Professeur à Politecnico di Torino                        | (Rapporteur)  |

| M. Smail Niar,       | Professeur à l'Université de Valenciennes                 | (Examinateur) |

| M. Philippe Coussy,  | Maître de conférences/HDR, à l'Université de Bretagne-Sud | (Examinateur) |

| M. Amer Baghdadi,    | Maître de conférences/HDR, à Télécom Bretagne             | (Encadrant)   |

| M. Michel Jézéquel,  | Professeur à Télécom Bretagne                             | (Directeur)   |

## Contents

| In | trodu | ction    |              |                                                       | 1  |

|----|-------|----------|--------------|-------------------------------------------------------|----|

| 1  | Wire  | eless Di | gital Com    | munication Systems and Iterative Processing           | 5  |

|    | 1.1   | Wirele   | ss Digital ( | Communication Systems                                 | 6  |

|    |       | 1.1.1    | Convolut     | ional Turbo Codes (CTC)                               | 7  |

|    |       |          | 1.1.1.1      | CTC Encoder                                           | 7  |

|    |       |          | 1.1.1.2      | CTC Interleaver                                       | 10 |

|    |       |          | 1.1.1.3      | CTC Puncturing                                        | 10 |

|    |       | 1.1.2    | Bit-Interl   | eaved Coded Modulation (BICM)                         | 11 |

|    |       | 1.1.3    | Mapping      |                                                       | 12 |

|    |       |          | 1.1.3.1      | Quadrature Amplitude Modulation (QAM)                 | 12 |

|    |       |          | 1.1.3.2      | Gray Mapping                                          | 13 |

|    |       |          | 1.1.3.3      | Signal Space Diversity (SSD)                          | 13 |

|    |       |          | 1.1.3.4      | Constellation Sub-Partitioning Technique              | 14 |

|    |       |          | 1.1.3.5      | Bits-to-Symbol Allocation Technique                   | 15 |

|    |       | 1.1.4    | MIMO To      | echniques                                             | 15 |

|    |       |          | 1.1.4.1      | Space-Time Coding (STC)                               | 15 |

|    |       |          | 1.1.4.2      | Spatial Multiplexing (SM)                             | 16 |

|    |       | 1.1.5    | Channel 1    | Models                                                | 16 |

|    |       |          | 1.1.5.1      | Frequency Selective Channel                           | 16 |

|    |       |          | 1.1.5.2      | Time Selective Channel                                | 17 |

|    |       |          | 1.1.5.3      | Double Selective Channel                              | 18 |

|    | 1.2   | Iterativ | ve (Turbo)   | Processing                                            | 18 |

|    |       | 1.2.1    | Turbo De     | coding                                                | 18 |

|    |       | 1.2.2    | Turbo De     | modulation with Turbo Decoding                        | 18 |

|    |       | 1.2.3    | Turbo Eq     | ualization with Turbo Decoding                        | 18 |

|    |       | 1.2.4    | Turbo Eq     | ualization with Turbo Demodulation and Turbo Decoding | 19 |

|    | 1.3   | Summ     | ary          | · · · · · · · · · · · · · · · · · · ·                 | 20 |

| 2 | Turł | oo Deco  | ding: Algorithms and Schedulings                                     | 21 |

|---|------|----------|----------------------------------------------------------------------|----|

|   | 2.1  | State o  | f the Art                                                            | 22 |

|   | 2.2  | SISO I   | Decoding Algorithms                                                  | 22 |

|   |      | 2.2.1    | MAP Decoding Algorithm                                               | 23 |

|   |      | 2.2.2    | Max-Log-MAP Decoding Algorithm                                       | 24 |

|   |      | 2.2.3    | Parallelism in Turbo Decoding                                        | 25 |

|   |      |          | 2.2.3.1 Metric Level Parallelism                                     | 25 |

|   |      |          | 2.2.3.2 SISO Decoder Level Parallelism                               | 26 |

|   |      |          | 2.2.3.3 Parallelism of Turbo Decoder                                 | 27 |

|   | 2.3  | SISO 7   | Furbo Decoding Schemes                                               | 28 |

|   | 2.4  | Turbo    | Decoding Schedulings                                                 | 29 |

|   |      | 2.4.1    | Classical Turbo Decoding Schedulings                                 | 29 |

|   |      | 2.4.2    | Shuffled Turbo Decoding scheduling with Overlapping                  | 30 |

|   |      |          | 2.4.2.1 <i>Overlapping 1</i> scheme                                  | 31 |

|   |      |          | 2.4.2.2 <i>Overlapping</i> 2 scheme                                  | 33 |

|   | 2.5  | Summa    | ary                                                                  | 34 |

| 3 | Opti | imized [ | Turbo Demodulation with Turbo Decoding: Algorithms, Schedulings, and |    |

|   | -    |          | Estimation                                                           | 35 |

|   | 3.1  | State o  | f the Art                                                            | 37 |

|   | 3.2  | SISO I   | Demapping Algorithms                                                 | 38 |

|   |      | 3.2.1    | MAP Demapping Algorithm                                              | 39 |

|   |      | 3.2.2    | Max-Log-MAP Demapping Algorithm                                      | 39 |

|   |      | 3.2.3    | Parallelism in Turbo Demodulation                                    | 40 |

|   |      |          | 3.2.3.1 Demapping Metric Level Parallelism                           | 40 |

|   |      |          | 3.2.3.2 Demapper Component Level Parallelism                         | 40 |

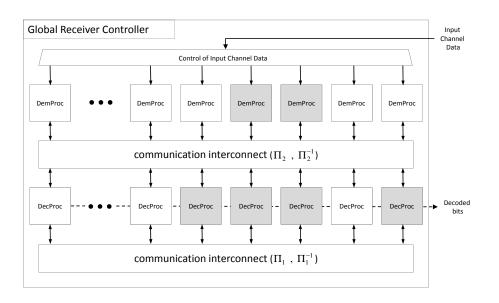

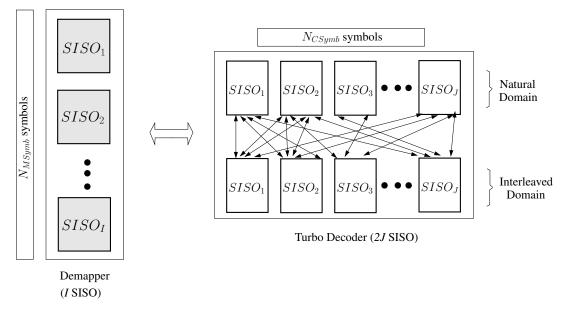

|   |      |          | 3.2.3.3 Turbo Demodulation Level Parallelism                         | 41 |

|   | 3.3  | Turbo    | Demodulation with Turbo Decoding Convergence Speed Analysis          | 41 |

|   |      | 3.3.1    | TBICM-SSD and TBICM-ID-SSD Error Correction Performance              | 42 |

|   |      | 3.3.2    | EXIT Chart Block Diagram                                             | 42 |

|   |      | 3.3.3    | Effects of Constellation Rotation                                    | 44 |

|   |      | 3.3.4    | Effects of Bits-to-Symbol Allocation Scheme                          | 46 |

|   |      | 3.3.5    | Effects of Max-Log-MAP Algorithm                                     | 47 |

|   | 3.4  | Reduci   | ing the Number of Demapping Iterations in TBICM-ID-SSD               | 48 |

|   |      | 3.4.1    | Proposed TBICM-ID-SSD Scheduling                                     | 49 |

|   |      | 3.4.2    | SISO Demapping and SISO Decoding Complexity Evaluation               | 50 |

|   |      |          | 3.4.2.1 SISO Demapping and SISO Decoding Typical Quantization Values | 50 |

|      |                                                                                                | 3.4.2.2 Complexity Evaluation of the SISO Demapper                                                                                                                                                                                                                                                                                                                                                                                      | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                                                                | 3.4.2.3 Complexity Evaluation of the SISO Decoder                                                                                                                                                                                                                                                                                                                                                                                       | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |                                                                                                | 3.4.2.4 Complexity Normalization                                                                                                                                                                                                                                                                                                                                                                                                        | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 3.4.3                                                                                          | Discussions and Achieved Improvements                                                                                                                                                                                                                                                                                                                                                                                                   | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |                                                                                                | 3.4.3.1 Complexity Reduction Ratio $G_1$                                                                                                                                                                                                                                                                                                                                                                                                | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |                                                                                                | 3.4.3.2 Achieved Improvements                                                                                                                                                                                                                                                                                                                                                                                                           | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.5  | Other                                                                                          | Schedulings for TBICM-ID-SSD                                                                                                                                                                                                                                                                                                                                                                                                            | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 3.5.1                                                                                          | Scheduling Strategy                                                                                                                                                                                                                                                                                                                                                                                                                     | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

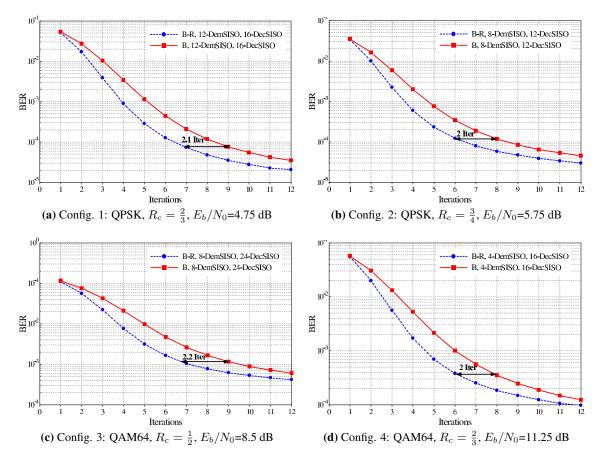

|      | 3.5.2                                                                                          | BER Performance Analysis                                                                                                                                                                                                                                                                                                                                                                                                                | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

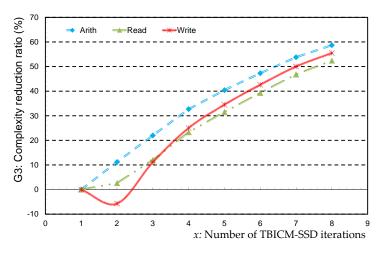

|      | 3.5.3                                                                                          | Complexity Analysis                                                                                                                                                                                                                                                                                                                                                                                                                     | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.6  | Compl                                                                                          | lexity Adaptive TBICM-ID-SSD Receiver                                                                                                                                                                                                                                                                                                                                                                                                   | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 3.6.1                                                                                          | TBICM-SSD and TBICM-ID-SSD Complexity Expressions                                                                                                                                                                                                                                                                                                                                                                                       | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 3.6.2                                                                                          | Number of Iterations Analysis for Identical Complexity                                                                                                                                                                                                                                                                                                                                                                                  | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 3.6.3                                                                                          | Complexity Analysis for Identical Performance and Achieved Improvements                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                         | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                         | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |                                                                                                | 1 5 5                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.7  |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 3.7.2                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                         | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 3.7.3                                                                                          | Area optimization                                                                                                                                                                                                                                                                                                                                                                                                                       | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.8  | Compl                                                                                          | lexity Reduction of Shuffled Parallel TBICM-ID-SSD                                                                                                                                                                                                                                                                                                                                                                                      | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 3.8.1                                                                                          | Parallel Full Shuffled TBICM-ID-SSD Strategy                                                                                                                                                                                                                                                                                                                                                                                            | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 3.8.2                                                                                          | Simulations and Achieved Improvements                                                                                                                                                                                                                                                                                                                                                                                                   | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |                                                                                                | 3.8.2.1 Performance Simulations for Different Shuffled Turbo Decoding                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                         | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| • •  | ~                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                         | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.9  | Summ                                                                                           | ary                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Opti | imized                                                                                         | Turbo Equalization with Turbo Decoding: Algorithms, Schedulings, and                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Con  | nplexity                                                                                       | Estimation                                                                                                                                                                                                                                                                                                                                                                                                                              | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.1  | State c                                                                                        | of the Art                                                                                                                                                                                                                                                                                                                                                                                                                              | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.2  | SISO I                                                                                         | Equalization Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                  | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

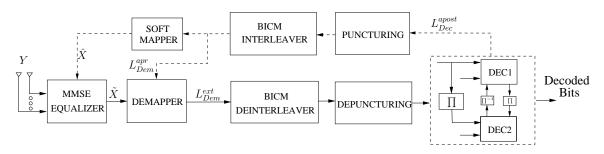

|      | 4.2.1                                                                                          | MMSE Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                          | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 4.2.2                                                                                          | Demapping                                                                                                                                                                                                                                                                                                                                                                                                                               | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 4.2.3                                                                                          | Soft Mapping                                                                                                                                                                                                                                                                                                                                                                                                                            | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 4.2.4                                                                                          | Parallelism in Turbo Equalization                                                                                                                                                                                                                                                                                                                                                                                                       | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |                                                                                                | 4.2.4.1 Symbol Estimation Level Parallelism                                                                                                                                                                                                                                                                                                                                                                                             | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | <ul> <li>3.6</li> <li>3.7</li> <li>3.8</li> <li>3.9</li> <li>Opti Cont</li> <li>4.1</li> </ul> | <ul> <li>3.5 Other 3</li> <li>3.5.1</li> <li>3.5.2</li> <li>3.5.3</li> <li>3.6 Complexity</li> <li>3.7 Efficie</li> <li>3.7.1</li> <li>3.6.2</li> <li>3.6.3</li> </ul> 3.7 Efficie <ul> <li>3.7.1</li> <li>3.7.2</li> <li>3.7.3</li> </ul> 3.8 Complexity <ul> <li>3.8</li> <li>3.8</li> </ul> 3.9 Summ Optimized <ul> <li>Complexity</li> <li>4.1 State of</li> <li>4.2 SISO I</li> <li>4.2.1</li> <li>4.2.2</li> <li>4.2.3</li> </ul> | 3.4.2.3       Complexity Evaluation of the SISO Decoder         3.4.2.4       Complexity Normalization         3.4.2.4       Complexity Normalization         3.4.3       Discussions and Achieved Improvements         3.4.3.1       Complexity Reduction Ratio G1         3.4.3.2       Achieved Improvements         3.5.1       Schedulings for TBICM-ID-SSD         3.5.2       BER Performance Analysis         3.5.3       Complexity Analysis         3.5.4       Complexity Analysis         3.5.3       Complexity Analysis         3.6.1       TBICM-ID-SSD Receiver         3.6.2       Number of Iterations Analysis for Identical Complexity         3.6.3       Complexity Analysis for Identical Performance and Achieved Improvements         G3 |

|           |          | 4.2.4.2 Equalizer Component Level Parallelism                     | 86  |

|-----------|----------|-------------------------------------------------------------------|-----|

|           |          | 4.2.4.3 Turbo Equalization Level Parallelism                      | 87  |

| 4.3       | Turbo    | Equalization with Turbo Decoding Convergence Speed Analysis       | 87  |

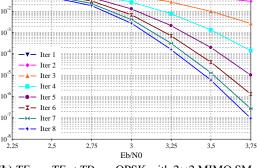

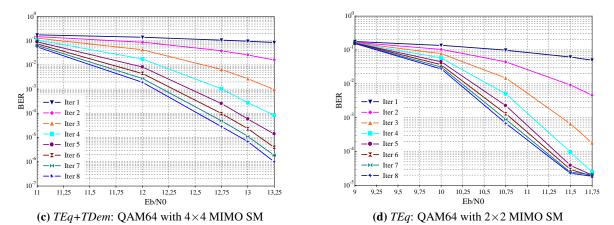

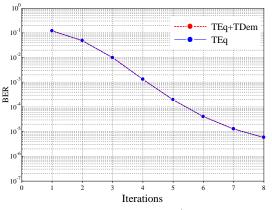

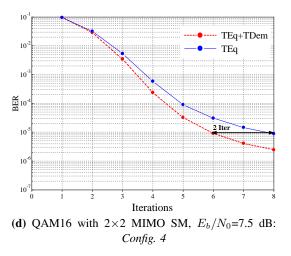

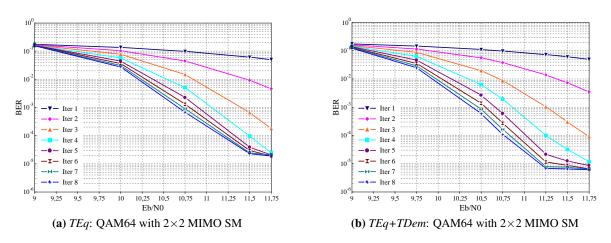

|           | 4.3.1    | <i>TEq</i> and <i>TEq+TDem</i> Error Correction Performance       | 87  |

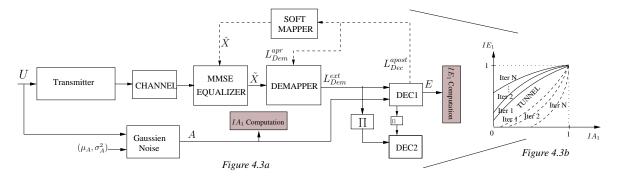

|           | 4.3.2    | EXIT Chart Block Diagram                                          | 87  |

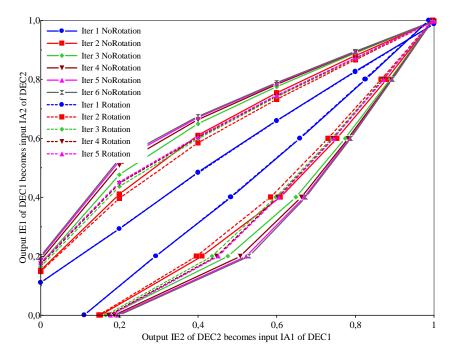

|           | 4.3.3    | Effects of Constellation Rotation                                 | 89  |

|           | 4.3.4    | Effects of Feedback to the Equalizer and to the Demapper          | 90  |

| 4.4       | Reduct   | ing the Number of Equalization Iterations in $TEq$ and $TEq+TDem$ | 91  |

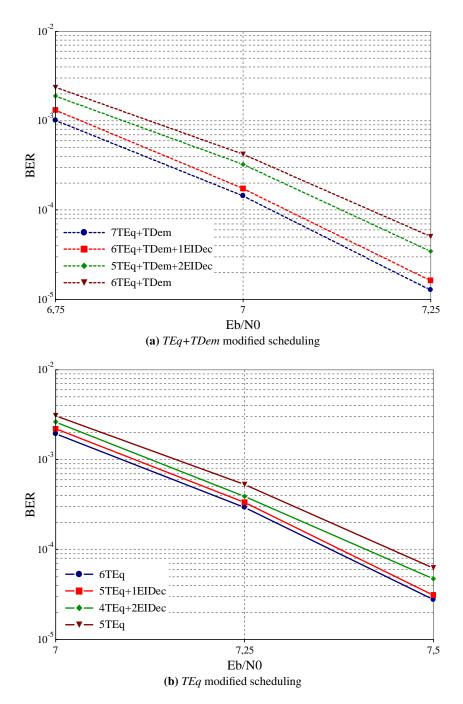

|           | 4.4.1    | Proposed <i>TEq</i> and <i>TEq+TDem</i> Schedulings               | 91  |

|           | 4.4.2    | SISO MMSE Equalizer Complexity Evaluation                         | 94  |

|           |          | 4.4.2.1 SISO Equalization Typical Quantization Values             | 94  |

|           |          | 4.4.2.2 Complexity Evaluation of SISO Equalizer                   | 95  |

|           |          | 4.4.2.3 Complexity Normalization                                  | 97  |

|           | 4.4.3    | Discussions and Achieved Improvements                             | 99  |

|           |          | 4.4.3.1 Complexity Reduction Ratio $G_5$                          | 99  |

|           |          | 4.4.3.2 Achieved Improvements                                     | 101 |

| 4.5       | Compl    | lexity Adaptive <i>TEq+TDem</i> Receiver                          | 101 |

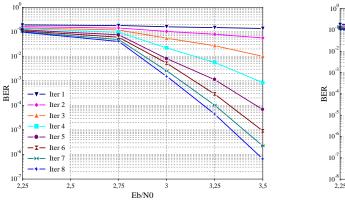

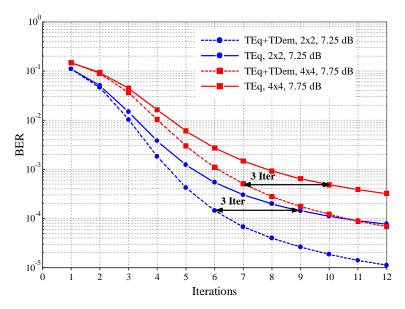

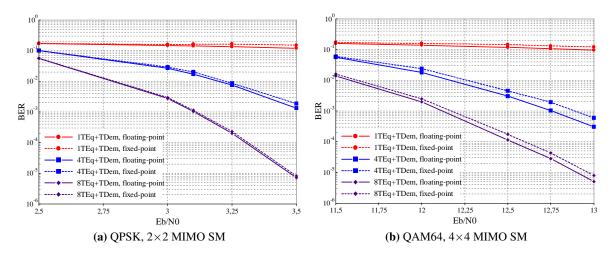

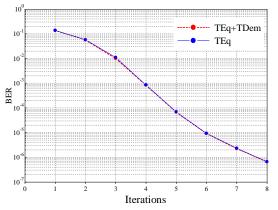

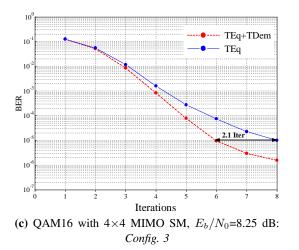

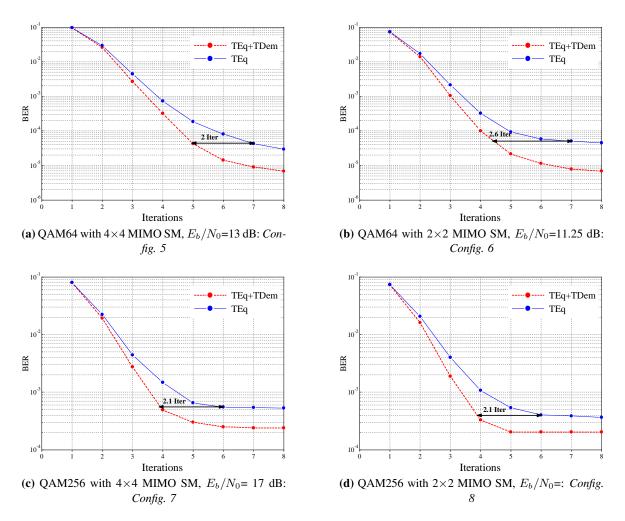

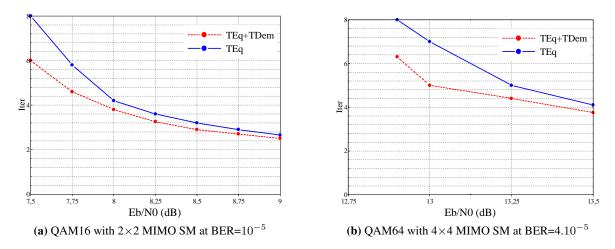

|           | 4.5.1    | <i>TEq+TDem</i> and <i>TEq</i> Performance Simulations            | 102 |

|           | 4.5.2    | Discussions and Achieved Improvements                             | 104 |

| 4.6       | Summ     | ary                                                               | 106 |

| Conclus   | sions an | d Perspectives                                                    | 109 |

| Résumé    | en Fra   | nçais                                                             | 111 |

| Glossar   | у        |                                                                   | 121 |

| Notation  | ns       |                                                                   | 123 |

| Bibliog   | aphy     |                                                                   | 127 |

| List of p | oublicat | tions                                                             | 135 |

\_\_\_\_\_

## **List of Figures**

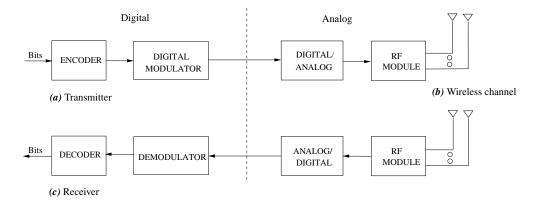

| 1.1  | Wireless digital communication system: (a) Transmitter (b) Wireless channel (c) Receiver.                                                                                                                                                                                                                                                                                                                                                    | 6  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

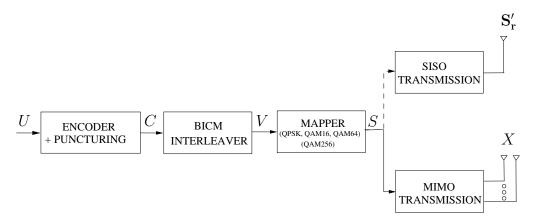

| 1.2  | SISO and MIMO transmitter system model for WiMAX standard.                                                                                                                                                                                                                                                                                                                                                                                   | 7  |

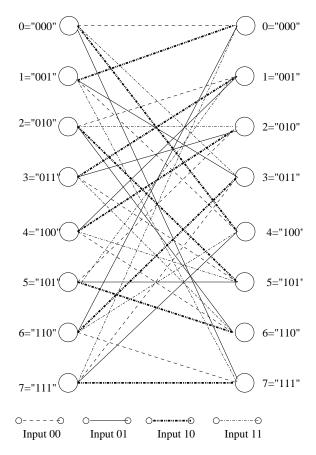

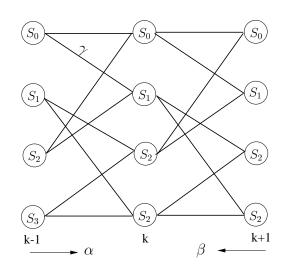

| 1.3  | CTC trellis associated with the double-binary CRSC constituent encoder used in WiMAX and DVB-RCS.                                                                                                                                                                                                                                                                                                                                            | 8  |

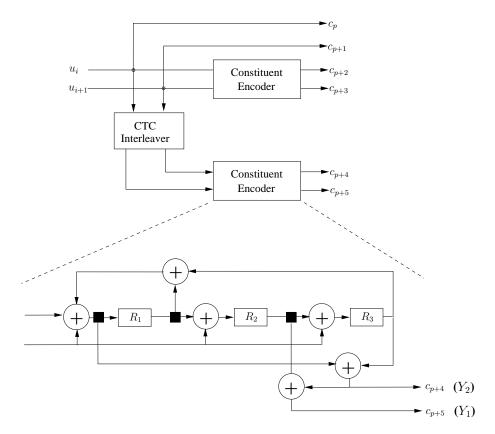

| 1.4  | CTC encoder used in WiMAX and DVB-RCS, 8-state double binary CRSC code                                                                                                                                                                                                                                                                                                                                                                       | 9  |

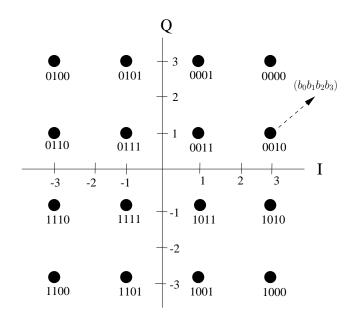

| 1.5  | Gray mapped QAM16 constellation.                                                                                                                                                                                                                                                                                                                                                                                                             | 13 |

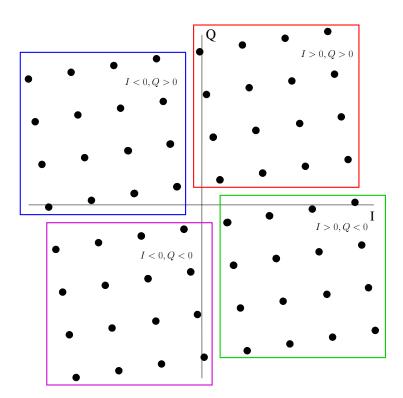

| 1.6  | Rotated QAM64 constellation of the DVB-T2 standard with the sub-partitioning technique.                                                                                                                                                                                                                                                                                                                                                      | 15 |

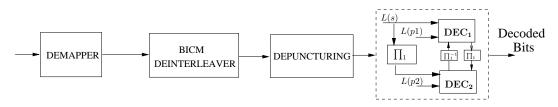

| 1.7  | System-level receiver: turbo decoding.                                                                                                                                                                                                                                                                                                                                                                                                       | 18 |

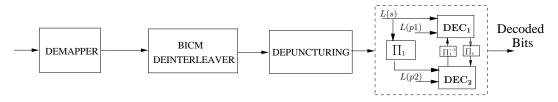

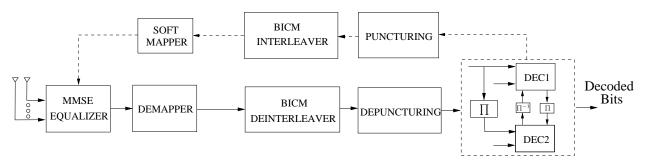

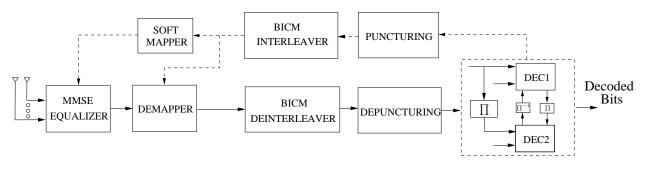

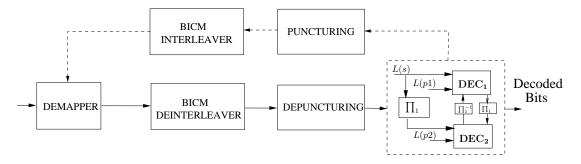

| 1.8  | System-level receiver: turbo demodulation with turbo decoding.                                                                                                                                                                                                                                                                                                                                                                               | 19 |

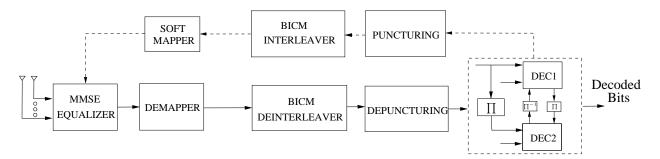

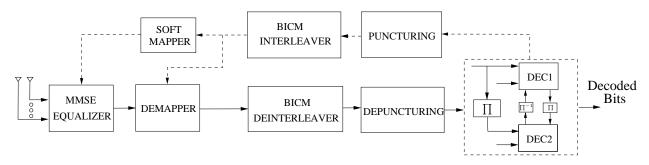

| 1.9  | System-level receiver: turbo equalization with turbo decoding                                                                                                                                                                                                                                                                                                                                                                                | 19 |

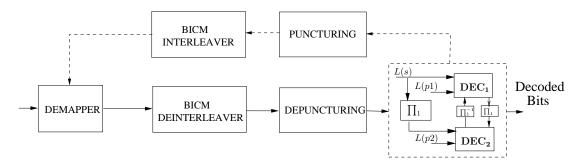

| 1.10 | System-level receiver: turbo equalization with turbo demodulation turbo decoding.                                                                                                                                                                                                                                                                                                                                                            | 19 |

| 2.1  | System model with TBICM-SSD.                                                                                                                                                                                                                                                                                                                                                                                                                 | 22 |

| 2.2  | BCJR metrics associated with trellis transitions                                                                                                                                                                                                                                                                                                                                                                                             | 26 |

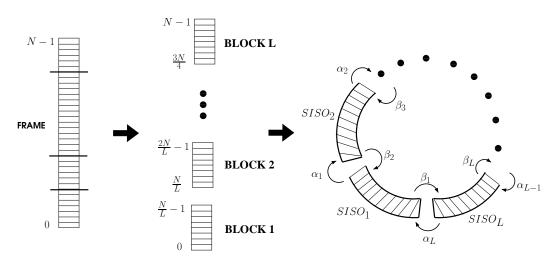

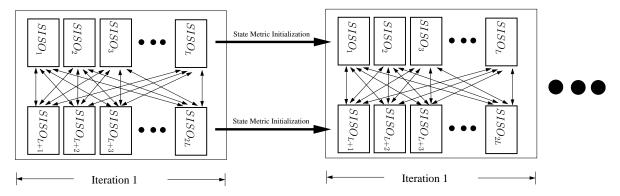

| 2.3  | Sub-block parallelism with message passing for metric initialization, circular code.                                                                                                                                                                                                                                                                                                                                                         | 26 |

| 2.4  | Shuffled turbo decoding.                                                                                                                                                                                                                                                                                                                                                                                                                     | 27 |

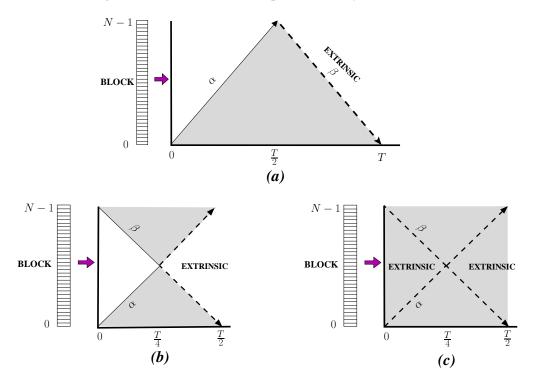

| 2.5  | SISO decoder schemes: (a) Forward-Backward (b) Butterfly (c) Butterfly-Replica                                                                                                                                                                                                                                                                                                                                                               | 28 |

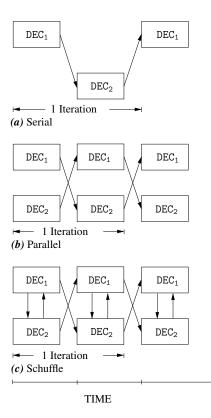

| 2.6  | Classical turbo decoding schedulings: (a) Serial (b) Parallel (c) Shuffled                                                                                                                                                                                                                                                                                                                                                                   | 30 |

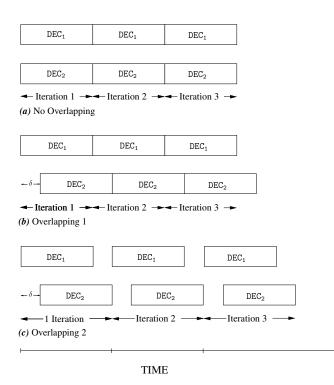

| 2.7  | Shuffled turbo decoding scheduling with overlapping: (a) No Overlapping (b) Overlapping 1 (c) Overlapping 2                                                                                                                                                                                                                                                                                                                                  | 31 |

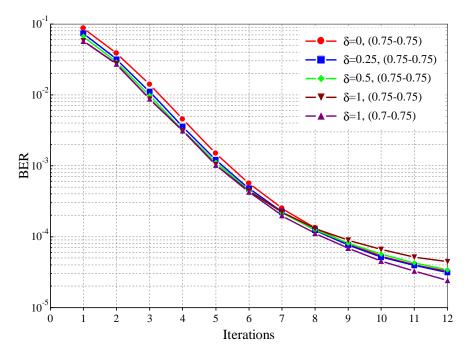

| 2.8  | BER performance at the output of DEC <sub>2</sub> in function of iterations for TBICM-SSD pro-<br>cessing in shuffled turbo decoding with butterfly scheme and <i>Overlapping 1</i> scheme<br>for different values of $\delta$ and scaling factors (2.2.2) for the transmission of 1536 infor-<br>mation bits frame over Rayleigh fading channel. QAM16 modulation scheme, $R_c = \frac{1}{2}$<br>and $E_b/N_0=6.25$ dB are considered.      | 32 |

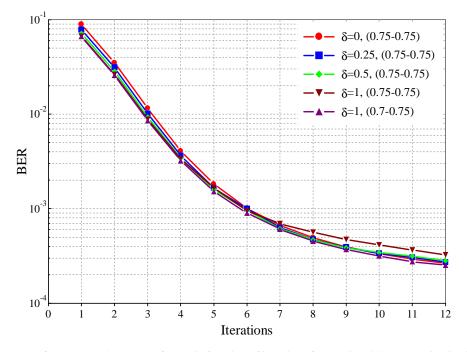

| 2.9  | BER performance at the output of DEC <sub>2</sub> in function of iterations for TBICM-SSD pro-<br>cessing in shuffled turbo decoding with butterfly-replica scheme and <i>Overlapping 1</i><br>scheme for different values of $\delta$ and scaling factors (2.2.2) for the transmission of<br>1536 information bits frame over Rayleigh fading channel. QAM16 modulation<br>scheme, $R_c = \frac{1}{2}$ and $E_b/N_0 = 6$ dB are considered. | 32 |

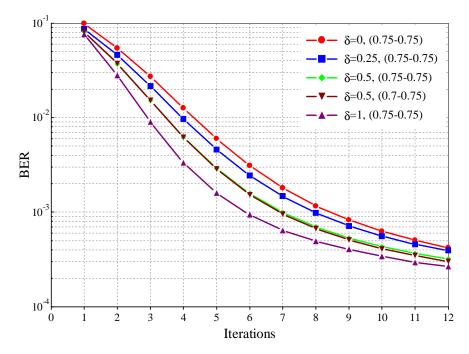

| 2.10 | BER performance at the output of DEC <sub>2</sub> in function of iterations for TBICM-SSD processing in shuffled turbo decoding with butterfly scheme and <i>Overlapping 2</i> scheme for different values of $\delta$ and scaling factors (2.2.2) for the transmission of 1536 information bits frame over Rayleigh fading channel. QAM16 modulation scheme, $R_c = \frac{1}{2}$ and $E_b/N_0=6$ dB are considered. | 33 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

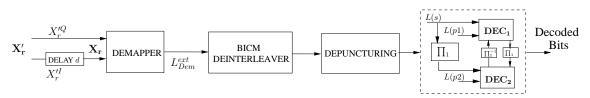

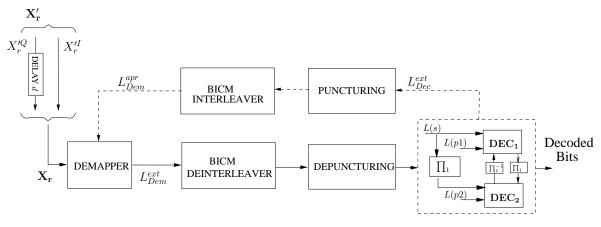

| 3.1  | Receiver model with TBICM-ID-SSD.                                                                                                                                                                                                                                                                                                                                                                                    | 38 |

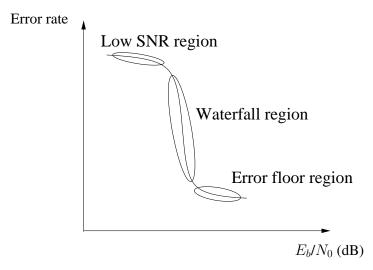

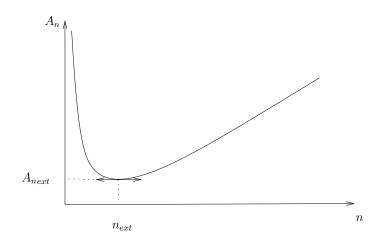

| 3.2  | The three typical distinct regions of error correction performance of an iterative process.                                                                                                                                                                                                                                                                                                                          | 42 |

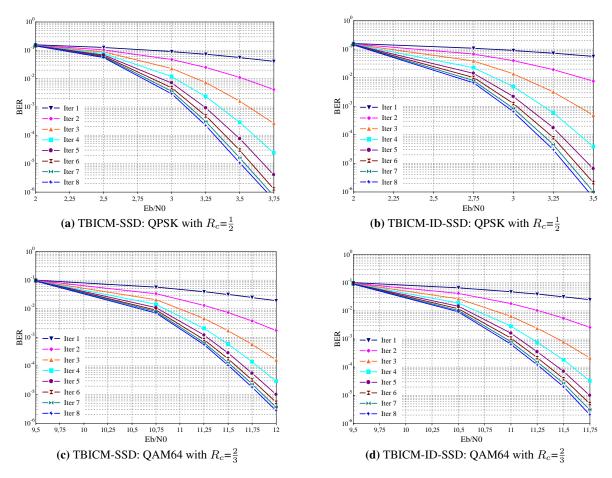

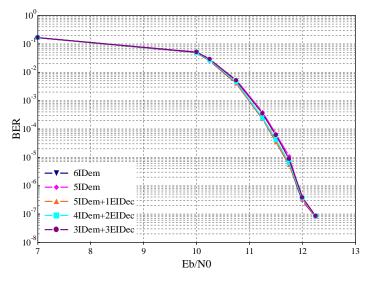

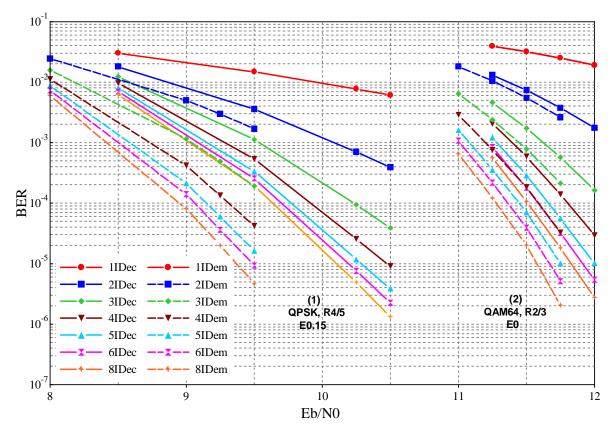

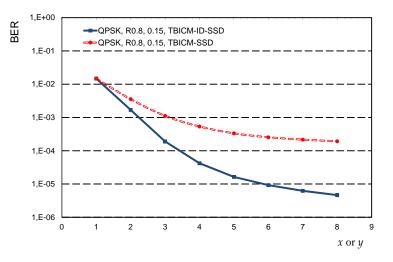

| 3.3  | BER performance simulations for TBICM-SSD and TBICM-ID-SSD for the trans-<br>mission of 1536 information bits frame over Rayleigh fast-fading channel without<br>erasure. Different system configurations (QPSK and QAM64 modulation schemes<br>with $R_c = \frac{1}{2}$ and $R_c = \frac{2}{3}$ ) are considered respectively.                                                                                      | 43 |

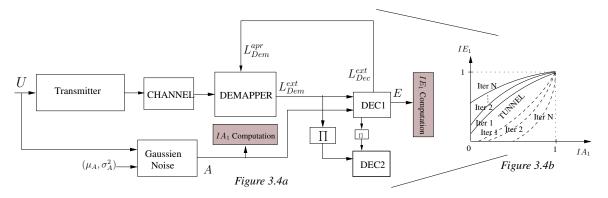

| 3.4  | EXIT chart block diagram for turbo demodulation with turbo decoding.                                                                                                                                                                                                                                                                                                                                                 | 43 |

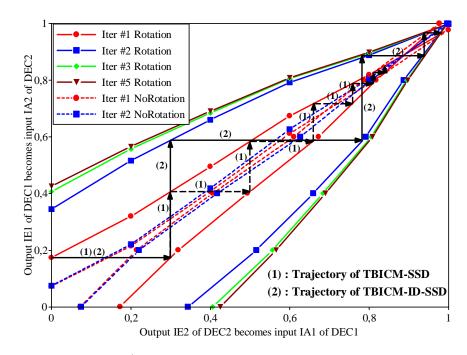

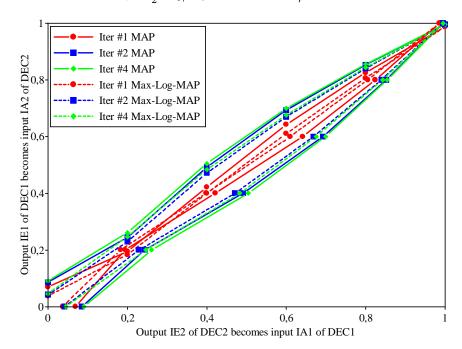

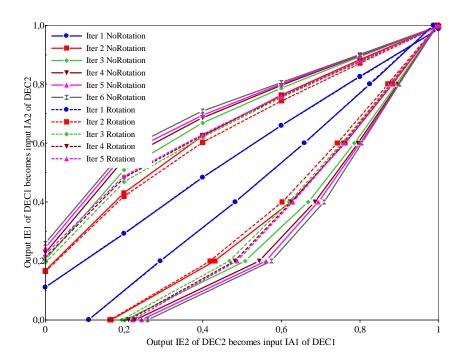

| 3.5  | EXIT chart analysis at $E_b/N_0=22$ dB of the double-binary turbo decoder for itera-<br>tions to the QAM64 demapper. $R_c = \frac{4}{5}$ is considered for transmission over Rayleigh<br>fast-fading channel with erasure probability $P_{\rho}=0.15$ .                                                                                                                                                              | 45 |

| 3.6  | EXIT chart analysis at $E_b/N_0$ = 7 dB of the double-binary turbo decoder for iterations<br>to the QPSK demapper. $R_c = \frac{6}{7}$ is considered for transmission over Rayleigh fast-<br>fading channel without erasure.                                                                                                                                                                                         | 45 |

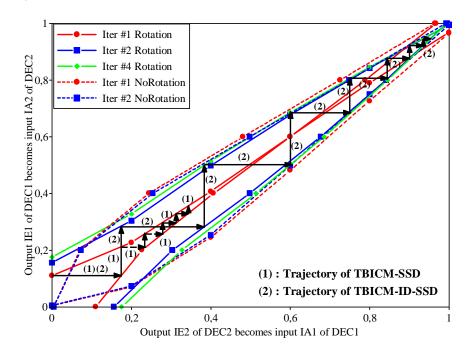

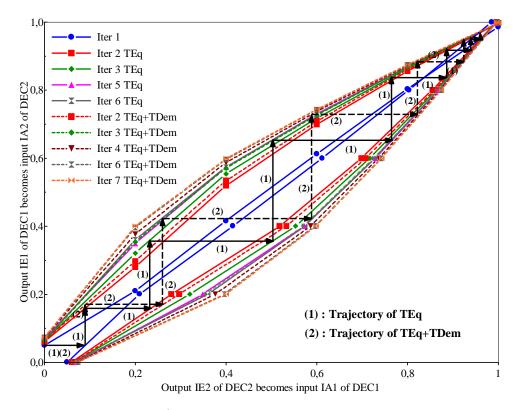

| 3.7  | EXIT chart analysis at $E_b/N_0$ = 14 dB of the double-binary turbo decoder for itera-<br>tions to the QAM16 demapper. $R_c = \frac{1}{2}$ and Rayleigh fast-fading channel with erasure<br>probability $P_{\rho}$ =0.15 are considered.                                                                                                                                                                             | 46 |

| 3.8  | EXIT chart analysis at $E_b/N_0$ = 5.5 dB of the double-binary turbo decoder for iter-<br>ations to the QAM16 demapper. $R_c = \frac{1}{2}$ and Rayleigh fast-fading channel without<br>erasure are considered.                                                                                                                                                                                                      | 47 |

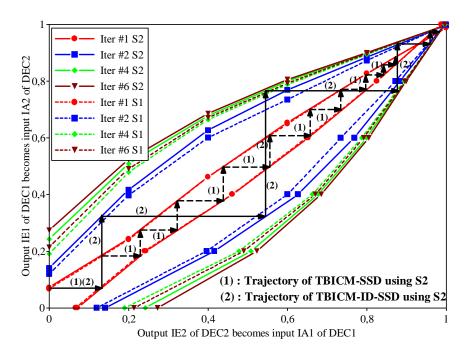

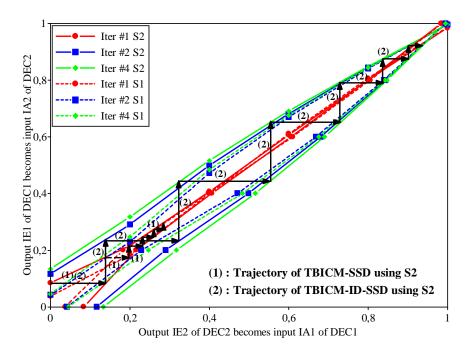

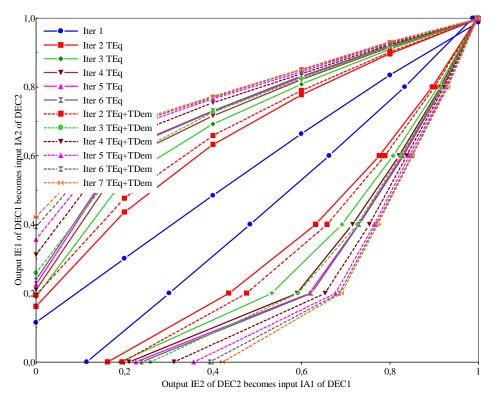

| 3.9  | EXIT chart analysis at $E_b/N_0$ = 5.5 dB of the double-binary turbo decoder for iter-<br>ations to the QAM16 demapper. $R_c = \frac{1}{2}$ and Rayleigh fast-fading channel without<br>erasure are considered.                                                                                                                                                                                                      | 47 |

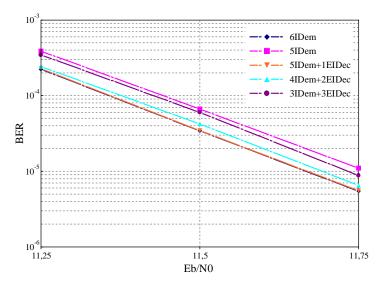

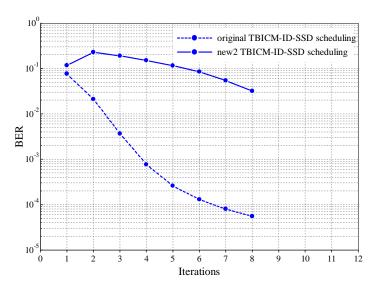

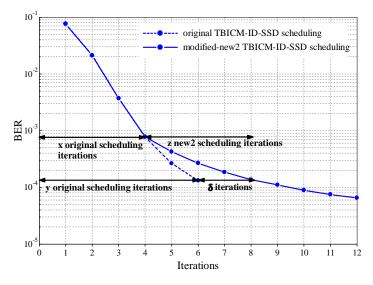

| 3.10 | BER performance comparison for TBICM-ID-SSD for the transmission of 1536 in-<br>formation bits frame over Rayleigh fast-fading channel without erasure. QAM64<br>modulation scheme and $R_c = \frac{2}{3}$ are considered.                                                                                                                                                                                           | 48 |

| 3.11 | BER performance comparison for TBICM-ID-SSD for the transmission of 1536 information bits frame over Rayleigh fast-fading channel with erasure probability $P_{\rho}$ =0.15. QAM16 modulation scheme and $R_c = \frac{4}{5}$ are considered                                                                                                                                                                          | 48 |

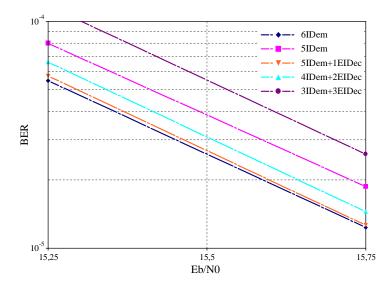

| 3.12 | BER performance comparison for TBICM-ID-SSD for the transmission of 1536 in-<br>formation bits frame over Rayleigh fast-fading channel without erasure. QAM64<br>modulation scheme and $R_c = \frac{2}{3}$ are considered.                                                                                                                                                                                           | 50 |

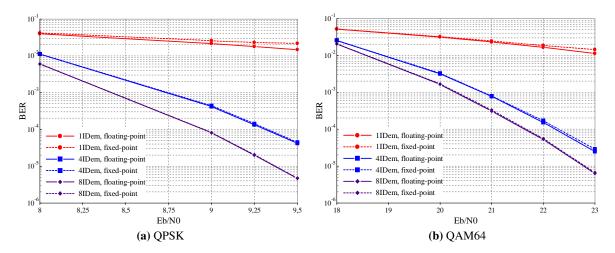

| 3.13 | Floating-point vs Fixed-point BER performance comparison for TBICM-ID-SSD for<br>the transmission of 1536 information bits frame over Rayleigh fast-fading channel<br>with erasure probability $P_{\rho}$ =0.15. QPSK and QAM64 modulation schemes are con-                                                                                                                                                          |    |

|      | sidered respectively for 1, 4, and 8 TBICM-ID-SSD iterations. $R_c = \frac{4}{5}$ .                                                                                                                                                                                                                                                                                                                                  | 51 |

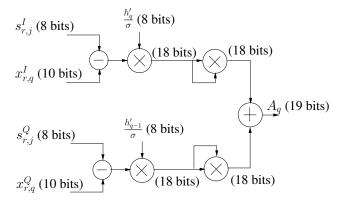

|      | Euclidean distance computation unit                                                                                                                                                                                                                                                                                                                                                                                  | 52 |

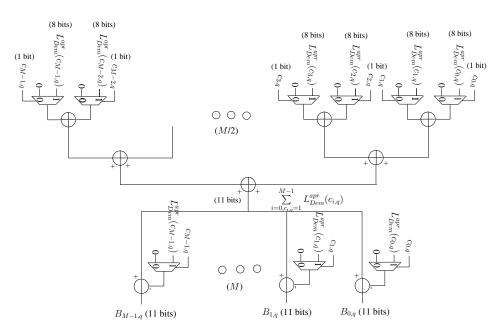

|      | A priori adder computation unit                                                                                                                                                                                                                                                                                                                                                                                      | 53 |

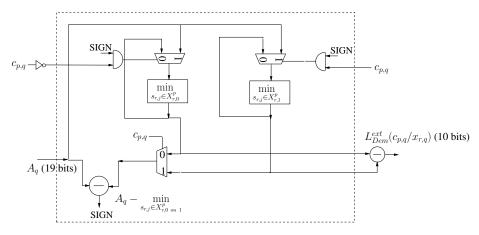

| 3.16 | Minimum Finder for One LLR                                                                                                                                                                                                                                                                                                                                                                                           | 54 |

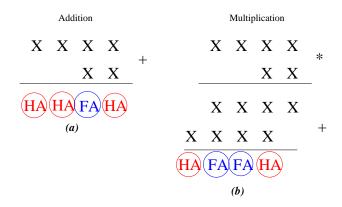

| 3.17 | Complexity normalization examples: (a) Addition operation (b) Multiplication oper-<br>ation.                                                                                                                                                                                                                             | 56 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|