# Programmation efficace et sécurisé d'applications à mémoire partagée

Emmanuel Sifakis

#### ▶ To cite this version:

Emmanuel Sifakis. Programmation efficace et sécurisé d'applications à mémoire partagée. Autre [cs.OH]. Université de Grenoble, 2013. Français. NNT: 2013GRENM004. tel-00823054v2

# HAL Id: tel-00823054 https://theses.hal.science/tel-00823054v2

Submitted on 24 May 2013

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ DE GRENOBLE

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : **Informatique** Arrêté ministérial : 7 août 2006

Présentée par

#### **Emmanuel Sifakis**

Thèse dirigée par **Saddek Bensalem** et codirigée par **Laurent Mounier**

préparée au sein Verimag et de l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique

# Towards efficient and secure shared memory applications

Thèse soutenue publiquement le 6 Mai 2013, devant le jury composé de :

Mr. Roland Groz

Professeur à Grenoble INP, Président

Mr. Klaus Havelund

Senior Research Scientist at NASA JPL LARS, Rapporteur

Mr. Gilles Muller

Directeur de Recherche à INRIA REGAL, LIP6, Rapporteur

Mr. Ahmed Bouajjani

Professeur à Paris Diderot, Examinateur

Mr. Saddek Bensalem

Professeur UJF, Directeur de thèse

Mr. Laurent Mounier

Maître de conférences UJF, Co-Directeur de thèse

#### ABSTRACT

The invasion of multi-core and multi-processor platforms on all aspects of computing makes shared memory parallel programming mainstream. Yet, the fundamental problems of exploiting parallelism efficiently and correctly have not been fully addressed. Moreover, the execution model of these platforms (notably the relaxed memory models they implement) introduces new challenges to static and dynamic program analysis. In this work we address 1) the optimization of pessimistic implementations of critical sections and 2) the dynamic information flow analysis for parallel executions of multi-threaded programs.

Critical sections are excerpts of code that must appear as executed atomically. Their pessimistic implementation reposes on synchronization mechanisms, such as mutexes, and consists into obtaining and releasing them at the beginning and end of the critical section respectively. We present a general algorithm for the acquisition/release of synchronization mechanisms and define on top of it several policies aiming to reduce contention by minimizing the possession time of synchronization mechanisms. We demonstrate the correctness of these policies (i.e., they preserve atomicity and guarantee deadlock freedom) and evaluate them experimentally.

The second issue tackled is dynamic information flow analysis of parallel executions. Precisely tracking information flow of a parallel execution is due to non-deterministic accesses to shared memory. Most existing solutions that address this problem enforce a serial execution of the target application. This allows to obtain an explicit serialization of memory accesses but incurs both an execution-time overhead and eliminates the effects of relaxed memory models. In contrast, the technique we propose allows to predict the plausible serializations of a parallel execution with respect to the memory model. We applied this approach in the context of taint analysis, a dynamic information flow analysis widely used in vulnerability detection. To improve precision of taint analysis we further take into account the semantics of synchronization mechanisms such as mutexes, which restricts the predicted serializations accordingly.

The solutions proposed have been implemented in proof of concept tools which allowed their evaluation on some hand-crafted examples.

### RÉSUMÉ

L'utilisation massive des plateformes multi-cœurs et multi-processeurs a pour effet de favoriser la programmation parallèle à mémoire partagée. Néanmoins, exploiter efficacement et de manière correcte le parallélisme sur ces plateformes reste un problème de recherche ouvert. De plus, leur modèle d'exécution sous-jacent, et notamment les modèles de mémoire "relâchés", posent de nouveaux défis pour les outils d'analyse statiques et dynamiques. Dans cette thèse nous abordons deux aspects importants dans le cadre de la programmation sur plateformes multi-cœurs et multi-processeurs: l'optimisation de sections critiques implémentées selon l'approche pessimiste, et l'analyse dynamique de flots d'informations.

Les sections critiques définissent un ensemble d'accès mémoire qui doivent être exécutées de façon atomique. Leur implémentation pessimiste repose sur l'acquisition et le relâchement de mécanismes de synchronisation, tels que les verrous, en début et en fin de sections critiques. Nous présentons un algorithme générique pour l'acquisition/relâchement des mécanismes de synchronisation, et nous définissons sur cet algorithme un ensemble de politiques particulières ayant pour objectif d'augmenter le parallélisme en réduisant le temps de possession des verrous par les différentes threads. Nous montrons alors la correction de ces politiques (respect de l'atomicité et absence de blocages), et nous validons expérimentalement leur intérêt.

Le deuxième point abordé est l'analyse dynamique de flot d'information pour des exécutions parallèles. Dans ce type d'analyse, l'enjeu est de définir précisément l'ordre dans lequel les accès à des mémoires partagées peuvent avoir lieu à l'exécution. La plupart des travaux existant sur ce thème se basent sur une exécution sérialisée du programme cible. Ceci permet d'obtenir une sérialisation explicite des accès mémoire mais entraîne un surcoût en temps d'exécution et ignore l'effet des modèles mémoire relâchées. A contrario, la technique que nous proposons permet de prédire l'ensemble des sérialisations possibles vis-a-vis de ce modèle mémoire à partir d'une seule exécution parallèle ("runtime prediction"). Nous avons développé cette approche dans le cadre de l'analyse de teinte, qui est largement utilisée en détection de vulnérabilités. Pour améliorer la précision de cette analyse nous prenons également en compte la sémantique des primitives de synchronisation qui réduisent le nombre de sérialisations valides.

Les travaux proposés ont été implémentés dans des outils prototypes qui ont permis leur évaluation sur des exemples représentatifs.

# Acknowledgements

Foremost, I would like to express my deepest gratitude to my co-advisor Laurent Mounier. His immense enthusiasm, support, availability and attention to details made it a real pleasure to work with him. I also sincerely thank my advisor Saddek Bensalem for his integrity and support.

I would like to thank all members of the jury for their implication in the evaluation of my thesis. A special thanks to Klaus Havelund and Gilles Muller for thoroughly examining my thesis but also for their enriching comments. I also thank Ahmed Bouajjani for his participation in the jury and Roland Gros who accepted to president the dissertation.

I also thank all my colleagues and officemates at Verimag for their support and encouragement over all these past years. A special thanks to my friends Paris, Vasso and Tesnim with which we shared many good moments but also went through a lot.

Last but not least I am deeply grateful to my family. My parents George and Marie-Claude to whom I dedicate this thesis. I thank them for raising me with good values, and making my education always a priority. I also thank my sisters Catherine and Sandra for their encouragement. Lastly I thank Manolya for all her support especially during the hard part of redacting this document.

# Contents

| 1        | Intr                 | Introduction                 |                                          |    |  |  |  |

|----------|----------------------|------------------------------|------------------------------------------|----|--|--|--|

|          | 1.1                  | Increasing computing power   |                                          |    |  |  |  |

|          | 1.2                  | .2 Exploiting computer power |                                          |    |  |  |  |

|          |                      | 1.2.1                        | Parallel programming models              | 4  |  |  |  |

|          |                      | 1.2.2                        | Shared memory architectures              | 4  |  |  |  |

|          |                      | 1.2.3                        | Caveats of shared memory                 | 5  |  |  |  |

|          | 1.3                  | Securi                       | ty and correctness                       | 5  |  |  |  |

|          |                      | 1.3.1                        | Information security                     | 5  |  |  |  |

|          |                      | 1.3.2                        | Program validation                       | 6  |  |  |  |

|          | 1.4                  | Our co                       | ontribution                              | 7  |  |  |  |

|          |                      | 1.4.1                        | Optimizing pessimistic critical sections | 7  |  |  |  |

|          |                      | 1.4.2                        | Predictive information flow analysis     | 8  |  |  |  |

|          | 1.5                  | Organ                        | ization of the thesis                    | 8  |  |  |  |

| <b>2</b> | $\operatorname{Thr}$ | ead pr                       | rogramming model                         | 11 |  |  |  |

|          | 2.1                  | What                         | are threads?                             | 11 |  |  |  |

|          |                      | 2.1.1                        | Description of a process                 | 11 |  |  |  |

|          |                      | 2.1.2                        | Description of threads                   | 12 |  |  |  |

|          | 2.2                  | Comm                         | non usage of threads                     | 13 |  |  |  |

|          | 2.3                  | Challe                       | enges of threads                         | 14 |  |  |  |

|          | 2.4                  | Data 1                       | race detection                           | 17 |  |  |  |

|          | 2.5                  | Synch                        | ronization mechanisms                    | 18 |  |  |  |

|          |                      | 2.5.1                        | Synchronization issues                   | 19 |  |  |  |

|          | 2.6                  | Execu                        | ting threads in parallel                 | 20 |  |  |  |

|          |                      | 2.6.1                        | Sequential consistency                   | 21 |  |  |  |

|          |                      | 2.6.2                        | Relaxing sequential consistency          | 22 |  |  |  |

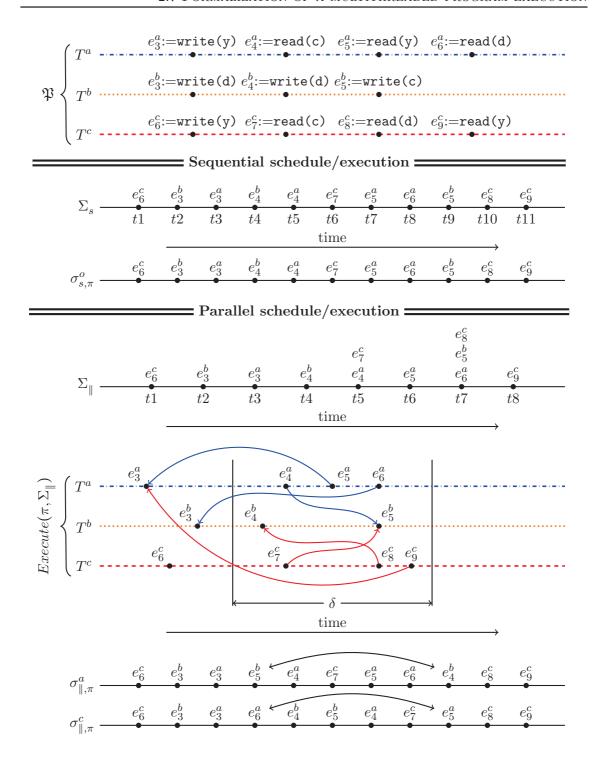

|   | 2.7 | Forma                   | alization of a multithreaded program execution                          | 23 |

|---|-----|-------------------------|-------------------------------------------------------------------------|----|

|   |     | 2.7.1                   | Sequential schedule and serialization                                   | 25 |

|   |     | 2.7.2                   | Parallel schedule and serialization                                     | 25 |

|   |     | 2.7.3                   | Constraining interleavings of a multithreaded execution $\dots$         | 28 |

|   | 2.8 | Summ                    | nary                                                                    | 29 |

| 3 | Opt | timizin                 | g critical sections                                                     | 31 |

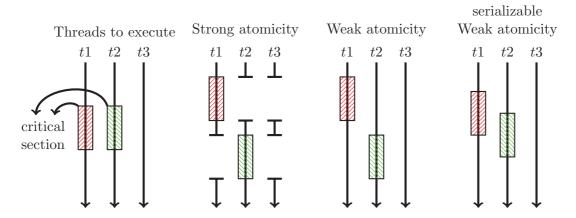

|   | 3.1 | Relaxi                  | ing atomicity of critical sections                                      | 32 |

|   | 3.2 | Imple                   | menting critical sections                                               | 33 |

|   |     | 3.2.1                   | Optimistic implementation of critical sections                          | 33 |

|   |     | 3.2.2                   | Pessimistic implementation of critical sections                         | 34 |

|   |     | 3.2.3                   | Optimistic versus pessimistic concurrency                               | 34 |

|   | 3.3 | Impro                   | ving pessimistic implementations of critical sections                   | 35 |

|   |     | 3.3.1                   | Positioning of our work                                                 | 36 |

|   | 3.4 | Mutua                   | al exclusion mechanisms                                                 | 36 |

|   | 3.5 | Policie                 | es for acquisition/release of protections                               | 41 |

|   |     | 3.5.1                   | General algorithm for managing protections                              | 41 |

|   |     | 3.5.2                   | Policies for acquisition/release of protections                         | 43 |

|   | 3.6 | Obser                   | vations on policies                                                     | 52 |

|   |     | 3.6.1                   | Equivalence of $Incremental/Eager$ and $Incremental\ priority\ release$ | 52 |

|   |     | 3.6.2                   | Optimizing critical sections implemented with $Incremental$ policies    | 53 |

|   |     | 3.6.3                   | Inferring optimal total order of variables                              | 54 |

|   | 3.7 | Exten                   | ding critical sections                                                  | 56 |

|   |     | 3.7.1                   | Loops and conditionals                                                  | 56 |

|   |     | 3.7.2                   | Function calls                                                          | 61 |

|   | 3.8 | Recap                   | itulation                                                               | 61 |

| 4 | Pre | $\operatorname{dictiv}$ | e information flow analysis                                             | 63 |

|   | 4.1 | Taint                   | analysis                                                                | 64 |

|   |     | 4.1.1                   | Explicit information flow                                               | 64 |

|   |     | 4.1.2                   | Implicit information flow                                               | 64 |

|   |     | 4.1.3                   | Application of taint analysis                                           | 65 |

|   | 4.2 | Tracin                  | ng taintness                                                            | 66 |

|   |     | 4.2.1                   | Dynamic binary instrumentation                                          | 66 |

|     | 4.2.2   | Sequential taint analysis                                              | 67  |

|-----|---------|------------------------------------------------------------------------|-----|

|     | 4.2.3   | Optimizing DIFT                                                        | 70  |

| 4.3 | Exten   | ding monitored traces                                                  | 71  |

|     | 4.3.1   | Runtime prediction for concurrency bugs                                | 71  |

|     | 4.3.2   | Runtime prediction applied to information flow                         | 72  |

|     | 4.3.3   | Positioning of our work                                                | 73  |

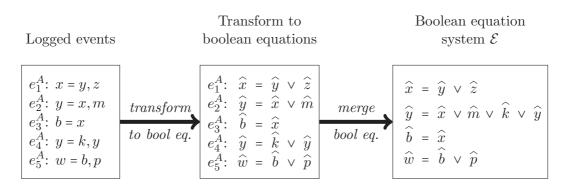

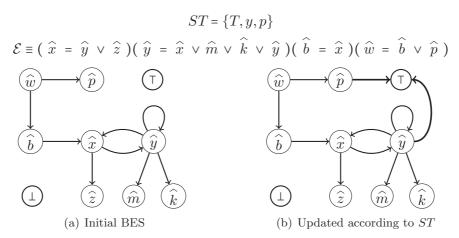

| 4.4 | Predic  | ctive explicit taint analysis                                          | 73  |

|     | 4.4.1   | Overview of our approach                                               | 73  |

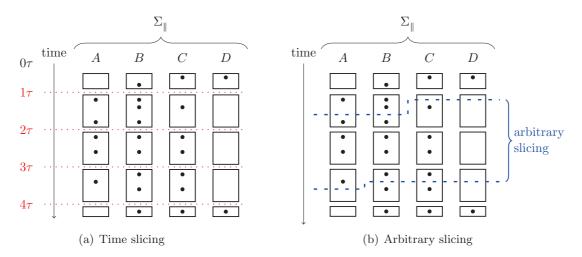

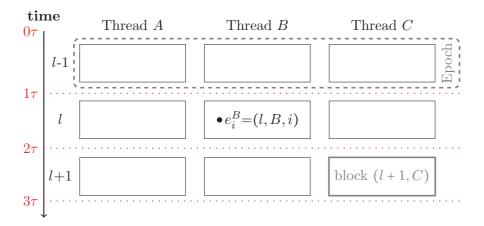

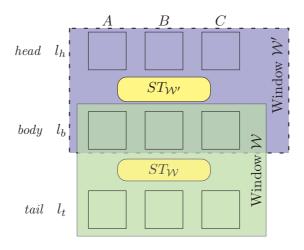

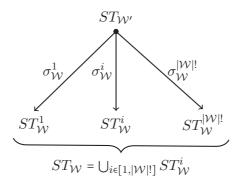

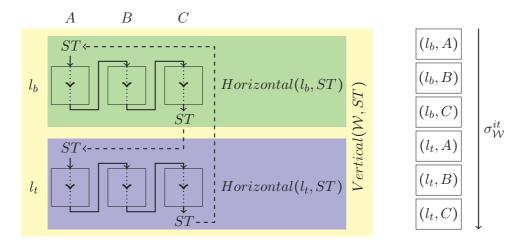

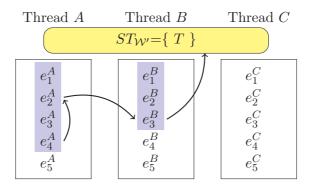

|     | 4.4.2   | Slicing the parallel schedule $\Sigma_{\parallel}(\log \mbox{ files})$ | 75  |

| 4.5 | Sliding | g window-based explicit taint prediction                               | 76  |

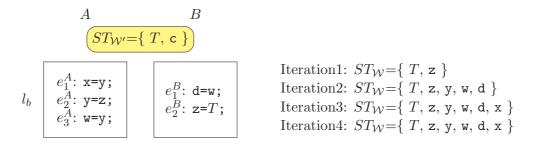

| 4.6 | Iterati | ve explicit taint prediction in a window                               | 79  |

|     | 4.6.1   | Enumerative approach                                                   | 80  |

|     | 4.6.2   | Iterative approach                                                     | 81  |

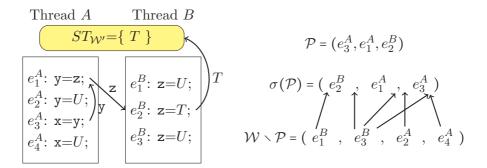

|     | 4.6.3   | Sliding windows - overlapping                                          | 84  |

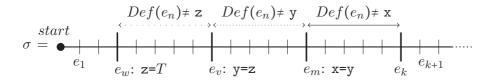

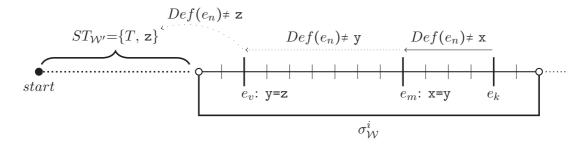

| 4.7 | Iterati | ve taint propagation under sequential consistency                      | 85  |

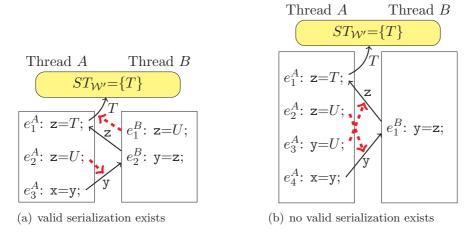

|     | 4.7.1   | Respecting program order without kills                                 | 85  |

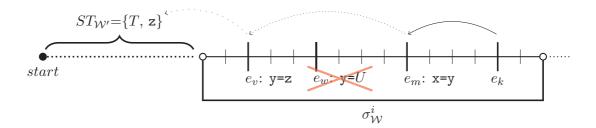

|     | 4.7.2   | Taking kills into account                                              | 90  |

|     | 4.7.3   | Effects of sliding window                                              | 96  |

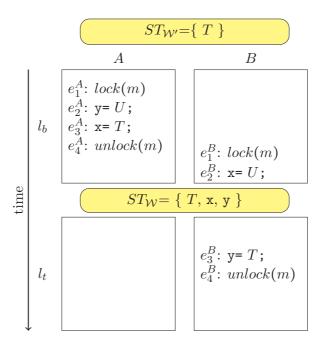

| 4.8 | Respe   | cting synchronization primitives                                       | 99  |

|     | 4.8.1   | Inferring order from mutexes                                           | 100 |

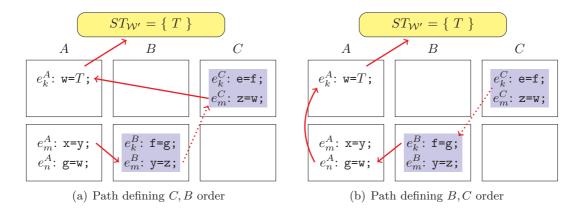

|     | 4.8.2   | Enforcing explicit mutex ordering in taint dependency paths $\dots$ .  | 102 |

|     | 4.8.3   | Enforcing implicit mutex ordering in taint dependency paths            | 102 |

| 4.9 | Recap   | itulation                                                              | 105 |

| Imp | olemen  | tation and experimentation                                             | 107 |

| 5.1 | Optim   | nizing critical sections                                               | 107 |

|     | 5.1.1   | Library for managing protections                                       | 107 |

|     | 5.1.2   | Experimentations                                                       | 110 |

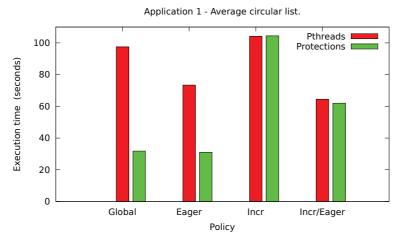

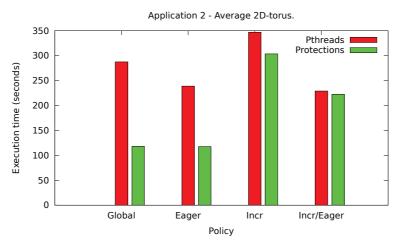

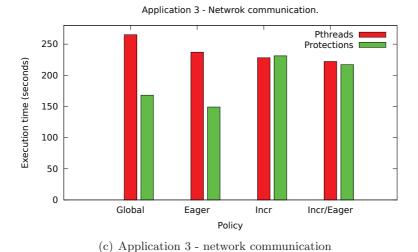

|     | 5.1.3   | Experimental results                                                   | 113 |

| 5.2 | Offline | e predictive information flow                                          | 118 |

|     | 5.2.1   | Proof of concept tool                                                  | 118 |

|     | 5.2.2   | Some experimental results                                              | 124 |

|     |         |                                                                        |     |

6 Conclusion and perspectives

| 6.1     | Optimizing critical sections         | 127 |

|---------|--------------------------------------|-----|

| 6.2     | Predictive information flow analysis | 128 |

| Appen   | dix A Boolean equation systems       | 131 |

| Bibliog | graphy                               | 144 |

# List of Figures

| 1.1  | Explicitly parallel computer systems                                 | 2  |

|------|----------------------------------------------------------------------|----|

| 1.2  | Data parallelism (loop parallelization)                              | 3  |

| 1.3  | Parallel systems abstraction                                         | 3  |

| 1.4  | Physically shared memory architectures                               | 4  |

| 2.1  | Address space and status of a process                                | 12 |

| 2.2  | Overview of processes and threads                                    | 14 |

| 2.3  | Deadlock                                                             | 19 |

| 2.4  | Execution of multithreaded application                               | 21 |

| 2.5  | $Dekkers$ algorithm broke under Write $\rightarrow$ Read relaxation  | 23 |

| 2.6  | Obtaining serializations for a multithreaded program ${\mathfrak P}$ | 27 |

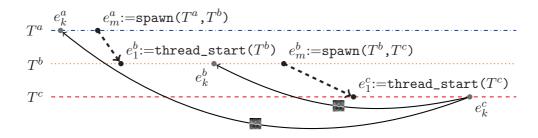

| 2.7  | Transitive happens before on thread create                           | 28 |

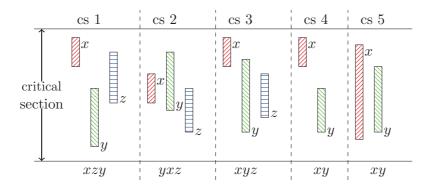

| 3.1  | Relaxing atomicity of critical sections                              | 33 |

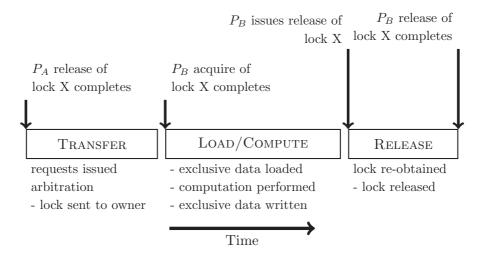

| 3.2  | Synchronization period for high contention lock. (from [KBG97])      | 35 |

| 3.3  | Deadlock by obtaining incrementally read/write protections           | 38 |

| 3.4  | Benefit of write intend protection                                   | 39 |

| 3.5  | Acquiring protections respecting order                               | 40 |

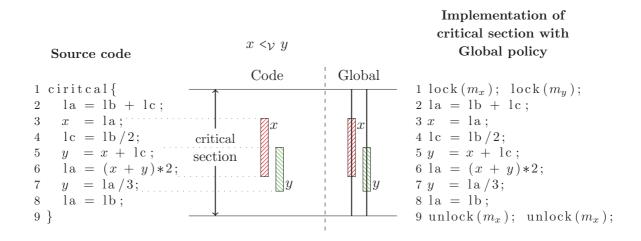

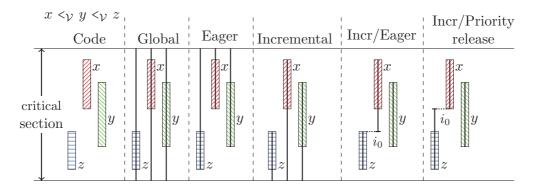

| 3.6  | Policies for acquiring/releasing protections                         | 43 |

| 3.7  | Global policy                                                        | 44 |

| 3.8  | Eager policy                                                         | 45 |

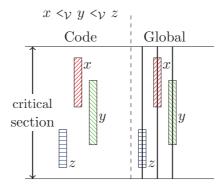

| 3.9  | Incremental policy                                                   | 47 |

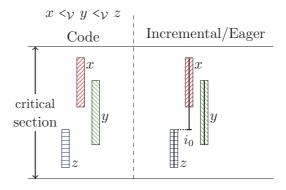

| 3.10 | Incremental/Eager policy                                             | 49 |

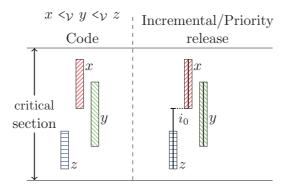

| 3.11 | Incremental/Priority release policy                                  | 50 |

| 3.12 | Policies for acquiring/releasing protections                         | 52 |

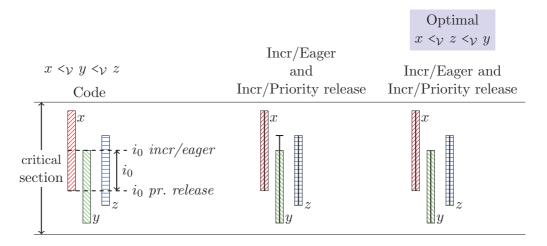

| 3.13 | Equivalence of Incremental/Eager and Incremental priority release    | 53 |

| 3.14 | Choosing arbitrary $i_0$                                             | 53 |

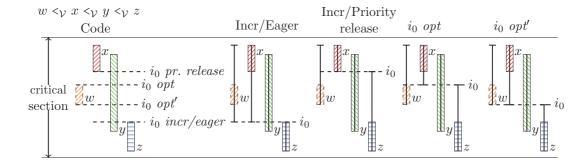

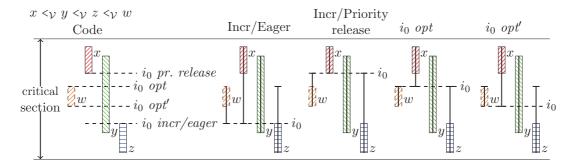

| 3.15 | Optimizing access to a variable                                                            | 54 |

|------|--------------------------------------------------------------------------------------------|----|

| 3.16 | Optimizing order for critical sections                                                     | 55 |

| 3.17 | Good vs bad ordering                                                                       | 55 |

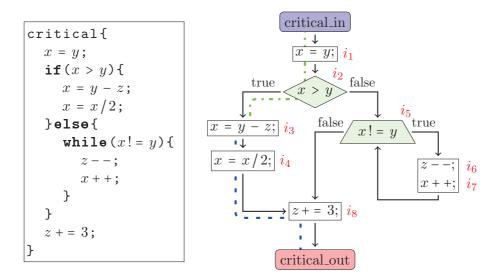

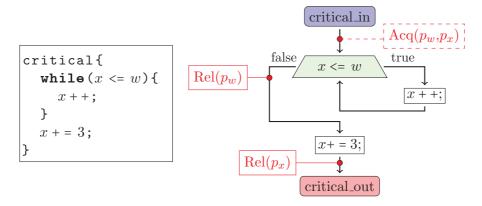

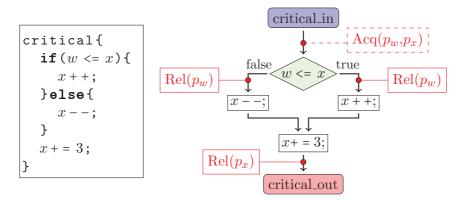

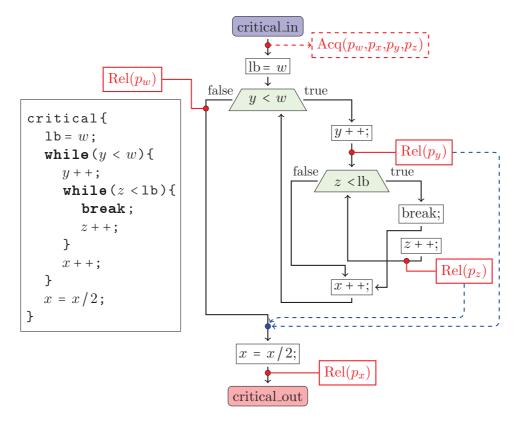

| 3.18 | Control Flow Graph (CFG) example                                                           | 57 |

| 3.19 | While loop conditional release protection                                                  | 58 |

| 3.20 | Branch loop conditional release protection                                                 | 58 |

| 3.21 | Nested loops in critical section                                                           | 59 |

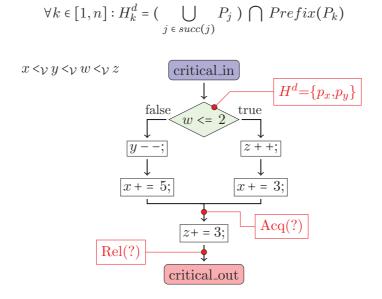

| 3.22 | Pessimistic $H_k^d$ computation                                                            | 60 |

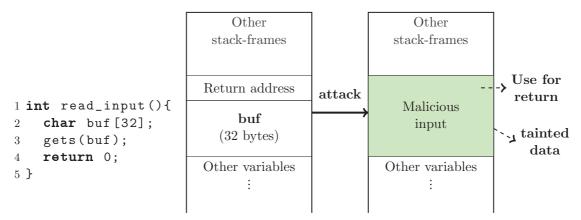

| 4.1  | Stack smashing by buffer overflow                                                          | 65 |

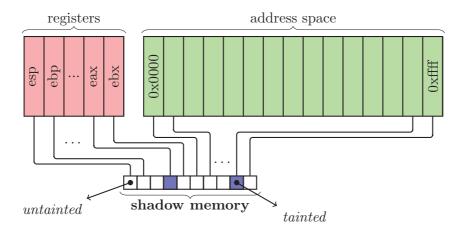

| 4.2  | Shadow memory mapping                                                                      | 68 |

| 4.3  | DIFT analysis using Dynamic Binary Instrumentation frameworks                              | 69 |

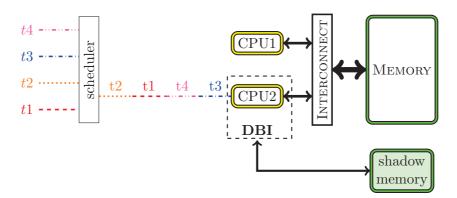

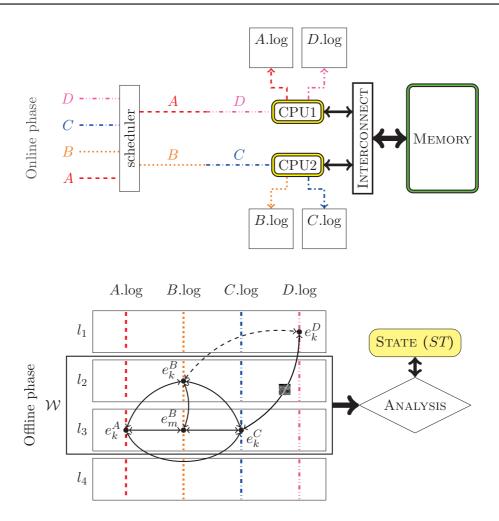

| 4.4  | Overview of our approach                                                                   | 74 |

| 4.5  | Slicing $\Sigma_{\parallel}$ into epochs                                                   | 75 |

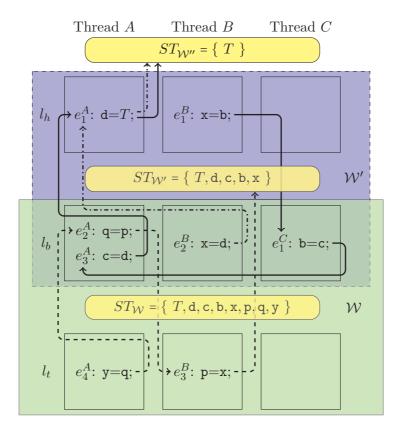

| 4.6  | Basic notations                                                                            | 76 |

| 4.7  | Sliding window based analysis                                                              | 77 |

| 4.8  | Taint definition for a concrete serialization                                              | 78 |

| 4.9  | Taint definition for a plausible serialization of events in a window $\mathcal{W}$         | 79 |

| 4.10 | Relaxed taint definition for a plausible serialization of events in a window $\mathcal{W}$ | 80 |

| 4.11 | Enumerative prediction of taint propagation                                                | 81 |

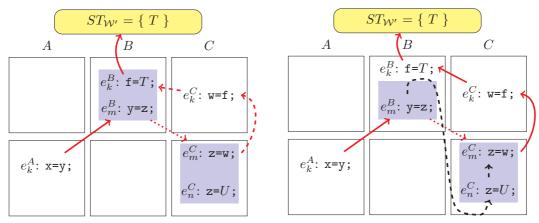

| 4.12 | Obtaining boolean equation system                                                          | 82 |

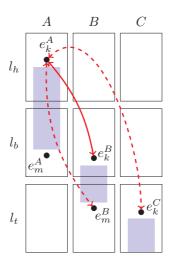

| 4.13 | Variable dependency graph of disjunctive boolean equation system. $\dots$                  | 82 |

| 4.14 | Equivalence between path in dependency graph and tainting serialization .                  | 83 |

| 4.15 | Iterating over the window                                                                  | 84 |

| 4.16 | Example, sequential consistency and iteration                                              | 86 |

| 4.17 | Composing a sequentially consistent serialization based on a $TDP$                         | 90 |

| 4.18 | Events contained in $\sigma^i_{\mathcal{P}}$                                               | 91 |

| 4.19 | Inferring a valid serialization for a path $\mathcal{P}$                                   | 91 |

| 4.20 | Events not belonging to $\mathcal P$ are considered kills                                  | 92 |

| 4.21 | Kill in $\mathcal{W}$ when not generated                                                   | 95 |

| 4.22 | All threads generating $x$ must eventually kill it                                         | 95 |

| 4.23 | Delay killing in tail                                                                      | 97 |

| 4.24 | Propagation through incompatible $TDPs$                                                    | 98 |

| 4.25 | Interleaving critical sections                                           | 101 |

|------|--------------------------------------------------------------------------|-----|

| 4.26 | Ordering critical sections using mutexes                                 | 102 |

| 4.27 | Taint paths define implicitly order of critical sections                 | 103 |

| 4.28 | Implicit precedence of critical sections                                 | 104 |

|      |                                                                          |     |

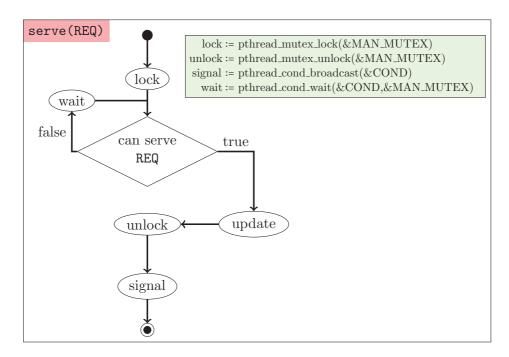

| 5.1  | Activity diagram for serve function                                      | 109 |

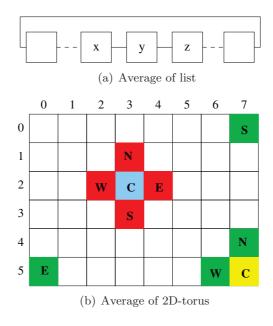

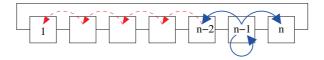

| 5.2  | Average computation, Applications 1 and 2 $\dots$                        | 111 |

| 5.3  | Communication in a network Application 3                                 | 112 |

| 5.4  | Comparison of policies and implementation of mutexes $\dots \dots \dots$ | 114 |

| 5.5  | Problem of <i>incremental</i> policy for application 1                   | 115 |

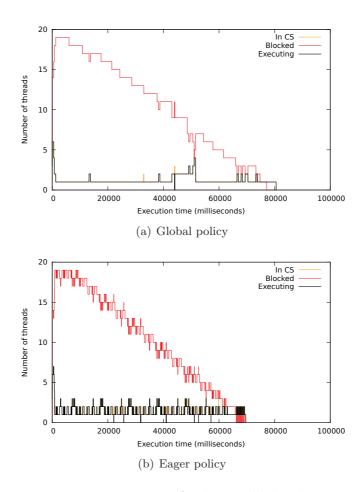

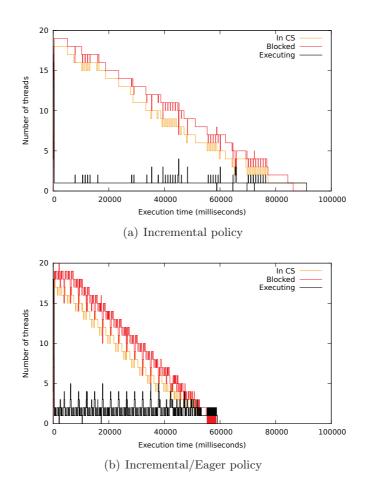

| 5.6  | Execution of policies $global$ and $eager$                               | 116 |

| 5.7  | Execution of policies $incremental$ and $incremental/priority\ release$  | 117 |

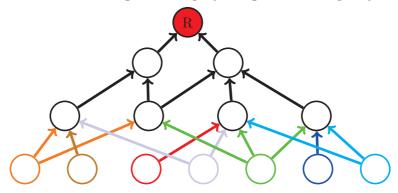

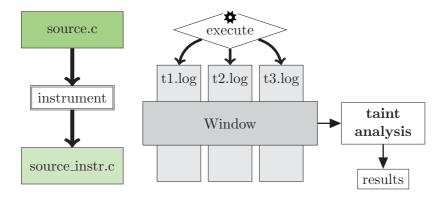

| 5.8  | Abstract analysis framework                                              | 118 |

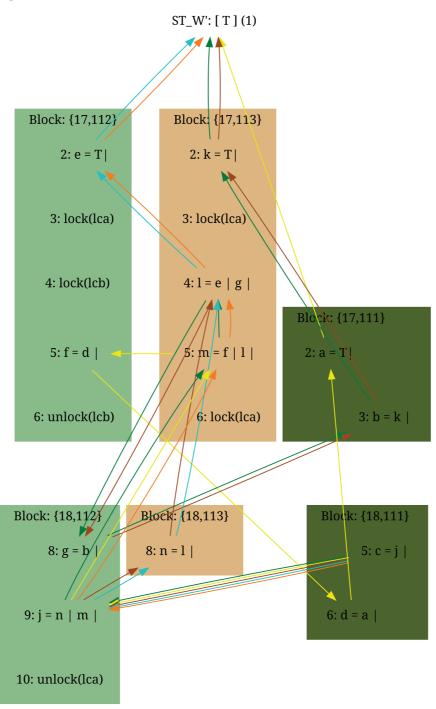

| 5.9  | Tainting paths for (18,111,5) under relaxed analysis                     | 121 |

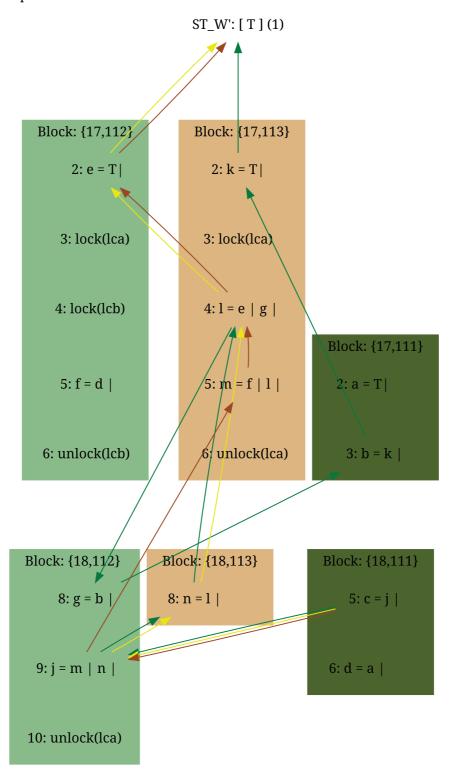

| 5.10 | Tainting paths for (18,111,5) under sequential analysis                  | 122 |

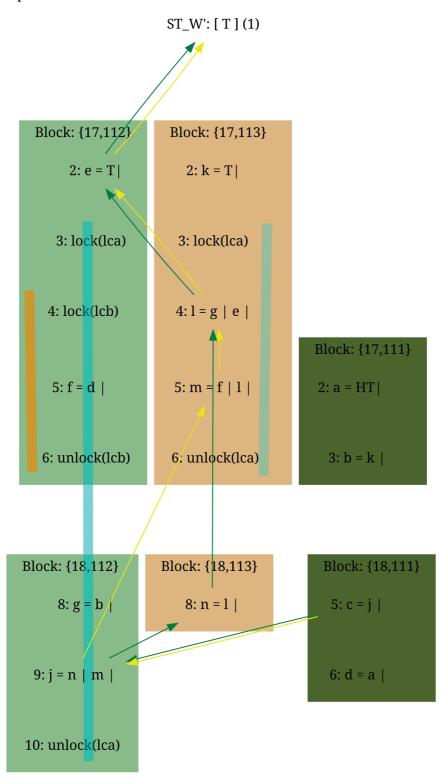

| 5.11 | Tainting paths for $(18,111,5)$ under <i>synchronization</i> analysis    | 123 |

| 5.12 | Cutting of epochs                                                        | 125 |

|      |                                                                          |     |

# Chapter 1

# Introduction

Computer systems are evolving with an astonishing rapid rate and are extensively used in various contexts, from scientific computations to critical systems, personal computers and consumer electronics. In all cases there is an insatiable demand for *performance*, since it allows to accomplish more complex tasks faster. Moreover, due to the importance of information manipulated by computer systems *correctness* and *security* are a major concern.

#### 1.1 Increasing computing power

A computer is a machine based on the *Von Neuman* architecture. It consists of a *central processing unit* (CPU) connected to a *memory* and some *input/output* (I/O) devices to communicate with the environment. The CPU is capable of performing a finite set of arithmetic and logic operations on data with a constant speed defined by the CPU clock. The sequence of operations to be performed by the CPU are specified in programs. Both programs and data reside in memory.

Increasing computing power implies performing more calculations in less time. For several decades the increase of performance in computer systems reposed mainly on the advance of hardware. According to *Moore's law* the cost effective density of transistors per chip should double approximately every two years. This implied that faster CPUs and larger memories could be fabricated all at reduced costs. Of course all this gain did not come for free. Faster CPUs need more electric power, and in combination with the reduced size heating of chips reaches critical levels.

Increasing the clock speed of a CPU was not sufficient itself for obtaining significant performance gains. The usage of CPUs had to be optimized (i.e., clock cycles should not be waisted). To that end several architectural changes have been applied such as: introduction of *cache memories* to hide latency for accessing main memory, or usage of dedicated buses for signals and data transfers. Another type of optimization was to add parallelism at the hardware level. It came in the form of *pipelining*, *instruction level parallelism* (*ILP*) and *simultaneous multi-threading*. This type of parallelism is implicit because it is transparent to the programmers.

Reaching physical limits and running out of coarse optimizations with significant benefits, hardware design was oriented towards explicit parallelism. That is, computers consisting of multiple processing units. This came in two flavors:

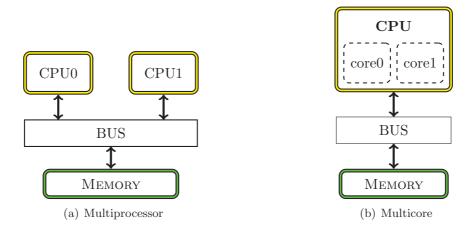

multiprocessor: multiple CPUs interconnected into some topology are placed inside a single computer system. Figure 1.1(a) illustrates a multiprocessor system consisting of two CPUs;

multicore: multiple processing units (called cores) are placed on a single CPU chip. Figure 1.1(b) presents a multicore CPU consisting of two cores.

Figure 1.1: Explicitly parallel computer systems.

Programmers must be aware of explicit parallelism in order to exploit it correctly and efficiently. This turns out to be an utterly challenging task. Parallelism adds non-determinism which makes it more difficult to reason about a programs correctness. Moreover, analyses and debugging tools that were used on sequential programs must be adapted to deal with parallelism.

## 1.2 Exploiting computer power

The switch from single processor to parallel architectures (multicores and multiprocessors) has a great impact on the way software is conceived. Better performance of a program no longer comes for free. To improve performance, programs must be parallelized. There are two sources of parallelism, data parallelism and task parallelism. Data (or loop-level) parallelism takes advantage of independent data to partition them into data sets and execute the same computation function on each partitioning concurrently. Figure 1.2 on the facing page illustrates an example of loop parallelization. The original loop on the left can be split and be executed in parallel as is the case on the right. Task parallelism focuses on executing different computation functions concurrently, and potentially on the same data sets.

Parallel computation is not a new concept in computer systems. In the early 70s already vector processing was developed to increase performance of mathematical computations.

```

1 int data[1000]

2 % CPU0

3 for(i=0; i<1000; i++){

data[i]++;

data[i]++;

4 }

6 % CPU1

7 for(i=500; i<1000; i++){

data[i]++;

data[i]++;

```

Figure 1.2: Data parallelism (loop parallelization).

Vector computers consist of a master processor which dispatches instructions to a number of processing units which execute them simultaneously on different memory locations. Such type of supercomputers were exclusively used for scientific and engineering purposes. A great break through to parallel computing came with the development of networks and the increased performance and reduced cost of personal computers. This allowed to build supercomputers by connecting custom of the shelf computers into *clusters* and *grids*.

A cluster is typically a set of homogeneous tightly connected computers, usually through a high speed local network (e.g., Myrinet). A grid is a collection of heterogeneous loosely connected computers, often through the Internet. Grids are mostly seen as a distributed system while clusters often appear as a single computational unit. Both clusters and grids are used in high performance computing (HPC) to solve complex problems. Two new trends in HPC are cloud computing and general purpose graphics processing unit (GPGPU) computing. Cloud computing offers access to remote computer resources through a service while GPGPU allows to exploit the computing power of graphics processing units, which consist of thousands of light cores specially designed for parallel performance.

Parallel computers independently of their scale (multi-core, multiprocessor, cluster, grid) can be abstracted using three building blocks: (i) processing units (ii) memory modules and (iii) interconnections. An interconnect links processing units between them or with memory modules. Figure 1.3 illustrates two common parallel architectures, the distributed memory on the left and the shared memory on the right. In the distributed memory architecture each processing unit has a private/local memory and can access the memory of other processing units through the network. In the shared memory case all processing units are directly connected to a globally visible shared memory.

Figure 1.3: Parallel systems abstraction

#### 1.2.1 Parallel programming models

Processing units of a parallel system need to exchange data and synchronize in order to accomplish a common task. Communication is done either using *message passing* or through *shared memory*. In *message passing*, as its name indicates, messages are sent between processing units. This communication model is well adapted for distributed parallel systems where messages are sent through a network. An interface known as MPI (Message Passing Interface) has been standardized for message passing communications, and several implementations of it exist. In the *shared memory* model data are transferred by placing them into designated locations of the globally visible address space. The synchronization is also done through shared memory, using synchronization primitives such as locks.

Both the *message passing* and *shared memory* communication mechanisms do not need to correspond directly to the underlaying platform. That is, message passing can be implemented through shared memory and dually shared memory can be simulated through distributed shared memories. In the rest of the document we focus to parallel computer systems with *physically shared memory*. That is, we consider multiprocessor and multicore architectures. In these architectures the shared memory model fits naturally.

#### 1.2.2 Shared memory architectures

Physically shared memory architectures can be devised into uniform memory access (UMA) and non-uniform memory accesses (NUMA) as illustrated in Figure 1.4. In UMA architectures accesses to the shared memory take the same time independently of which processor issued them. In NUMA architectures processors can still access any memory location, but the time required depends whether the memory location resides in its own local memory (immediate interconnection with memory, faster access) or to the local memory of other processors (non-immediate interconnection with memory, slower access). NUMA architectures have a structure similar to distributed memories.

Figure 1.4: Physically shared memory architectures.

The architectures can also be classified by the types of processors they are composed of. In *symmetric multiprocessor* (SMP) systems all processors have the same characteristics. Dually, in *asymmetric multiprocessor* (ASMP) systems the processors used can have different characteristics (e.g., CPU speed).

#### 1.2.3 Caveats of shared memory

In the shared memory model, independently of the underlaying architecture, concurrent modifications to common memory locations can cause data races. That is, the outcome of the program executed depends on the order in which memory updates took place. Data races can have disastrous results. Thus, precautions must be taken, when necessary, to eliminate them. In the shared memory model synchronization mechanisms that guarantee mutual exclusion are used to enforce an order among critical sections (portions of code containing that should be executed atomically). The mis-usage of synchronization mechanisms such as locks can introduce deadlocks i.e., disallow permanently the blocked parts to make any progress.

Mutual exclusion of critical sections implies they are serialized, which is necessary for the correctness of the programs. Serialization in parallel programs should be minimized in order to obtain significant performance gains. As formulated in *Amdahl's law*: the speedup of a program using multiple processors in parallel computing is limited by the time needed to execute the sequential fraction of the program.

The abstraction we used (processing units, memory, interconnection) to describe parallel computers provides an intuitive overview of the architectures but also hides many details such as *caches*. Caches are small and very fast memories which store copies of picked memory locations in order to hide the latency of main memory accesses. Maintaining caches coherent is a major issue because a processor may miss the update of a cached memory location residing on an other processor. To resolve those issues several *cache coherency* protocols exist.

Because shared memory parallel architectures can widely vary (UMA, NUMA, different levels of cache, cache coherence protocols used) the behavior of a program can also vary according to the platform it is executed on. It is hence necessary to define a memory consistency model which specifies the behavior of memory with respect to simultaneous accesses to the same location and issued by different processors. To gain in performance several relaxed consistency models have been proposed and applied to a vast majority of commercial architectures.

#### 1.3 Security and correctness

#### 1.3.1 Information security

The importance of information is invaluable and a number of security properties such as (i) confidentiality (ii) integrity and (iii) availability must be guaranteed. Nowadays information is stored, processed and transfered among a multitude of devices. Although encryption algorithms and communication protocols can ensure integrity and confidentiality, of data storage and transfer, they are not always used properly. Data are often stored un-encrypted and their security relies entirely on the operating system access control which is insufficient.

Benign software may unintentionally leak confidential data, or contain vulnerabilities

that could be exploited by malicious software (malware). Malwares come in many flavors, viruses, worms, trojan horses, spywares etc. and focus in disclosing confidential information, or causing denial of services (e.g., crash programs) or capture the host computer (zombie computer) in order to accomplish further malicious tasks. To protect against software vulnerabilities *information flow* analysis is mandatory.

Information flow analyses trace how data processed by a program transit inside memory at execution time. Two popular analyses focusing on preserving security are non-interference and taint analysis. Non-interference focuses on confidentiality. It ensures that high (confidential) data do not flow into low (public) data. A program is safe if the same outputs are observed for different values of high data. Taint analysis on the other hand tracks untrusted data such as user or network input and checks how they influence vulnerable statements (e.g., return address of functions). Taint analysis was originally implemented in the Perl language for identifying security risks on web sites such as SQL injections and buffer overflow attacks. The term taint analysis is now widely used as a synonym to dynamic information flow tracing (DIFT). Moreover, the type of information traced is not restricted to untrusted data and thus more general analyses can be implemented.

#### 1.3.2 Program validation

Further to the security aspects, correctness of applications is also crucial. To state a program is correct a formal specification (mathematical description) must be provided and formal verification techniques should be employed to demonstrate it. Intuitively, an application is correct when it exhibits the expected behavior. Formal methods give verdicts about all executions of a program. Though, to overcome the complexity and non-determinism of the analyzed systems they use abstractions which usually over-approximate the systems behavior. This leads to false positives, i.e., finding errors that could not occur in a real execution of the program. A somehow dual technique called testing is widely used to validate program executions.

Testing has become an indispensable part of software development. It is applied to validate if a program meets its functional and extra-functional requirements for a specific (specially guided) execution. Testing is applied dynamically, that is by executing a program or fragment of a program and observe the execution for the tested property. We must note that testing is not exhaustive and thus it cannot be used for verification. In order to increase the confidence of programs *stress testing* is applied to increase coverage of tested executions. If any functional errors (bugs) are found during testing they should be resolved through the debugging process.

Debugging of programs consists in finding errors (bugs) and correcting them accordingly. In order to debug an error it should be *reproducible* so that it can be replayed as many times necessary to detect its source. Several tools called debuggers help developers in this process. They allow a step-by-step execution of the program and inspection of memory at any point.

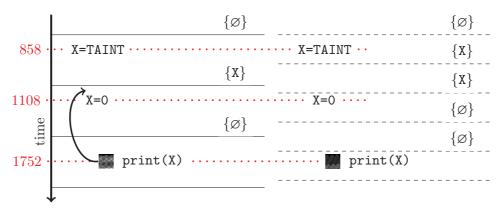

The non-determinism of concurrent program executions makes information flow track-

ing, testing and debugging more challenging. Concurrent modifications to shared memory affect the propagation of taintness and observations of testing. Taint propagation or verdict of tests can be different for repeated executions using the same inputs. The non-deterministic execution is affected by many factors such as scheduling decisions taken by the operating system or even the serialization of events by the execution platform. Reproducing a non-deterministic execution precisely is nearly impossible. Thus, we can no longer specify precisely the execution that was tested, nor can we easily reproduce bugs in order to fix them. A partial solution to checking non-deterministic executions is *runtime prediction*. The intuition behind it is to infer/predict plausible serializations based on a concrete execution of the observed application. Thus, upon a single test execution we predict several neighboring executions which would be hard to enforce.

#### 1.4 Our contribution

This thesis addresses two topics related to parallel executions of multi-threaded programs on shared memory architectures. The first problem addressed is the optimization of pessimistic implementations of critical sections. The second problem addressed is the taint analysis for parallel executions of multithreaded programs on multicore architectures.

#### 1.4.1 Optimizing pessimistic critical sections

Critical sections are widely used to enforce mutual exclusion between conflicting accesses to shared resources, e.g., shared memory locations. They are traditionally implemented using synchronization mechanisms such as locks. The locks necessary to protect a critical section are in most cases obtained prior to entering the critical section and released only once the critical section has been executed.

In this work we identify the properties on locks that must be respected such that the semantic of critical sections is preserved. We then propose several policies intending to minimize possession of locks and thus increase parallelism at execution time. The contributions of this work are summarized as follows:

- The definition of a generic lock acquisition/release algorithm for critical sections.

- The instantiation of five policies on top of our algorithm. Correctness of these policies with respect to deadlock freedom and absence of data races is provided.

- The definition of a new exclusion mechanism called *read write intend*.

- The development of a library implementing several exclusion mechanisms, including read write intend. The library also provides functionality for serving atomically the acquisition and release of sets of synchronization mechanisms.

#### Publications

Sifakis Emmanuel and Mounier Laurent. Politiques de gestion de protections pour l'implémentation

de sections critiques. RENPAR, 2011

Sifakis Emmanuel and Mounier Laurent. Politiques de gestion de protections pour l'implémentation de sections critiques. TSI special RENPAR, 2012

#### 1.4.2 Predictive information flow analysis

Information flow analysis is often applied at runtime since it is more precise. Performing information flow analysis on shared memory programs executing in parallel is utterly difficult. To overcome the difficulties introduced by parallel execution the majority of existing works impose the serialized execution of the analyzed applications. Note that in this case information flows inferred are restricted to the observed serialization.

In this work we propose a predictive information flow analysis for parallel programs. Our analysis allows the parallel execution of applications which is the input to our prediction algorithm. The prediction is applied to bounded portions of code that were executed "simultaneously". Predictions are inferred by the iterative algorithm we propose. The prediction focuses into capturing information flows produced by plausible serializations of the parallel execution observed. The predictions should take into account the characteristics of the execution platform. We use *taint* analysis as a representative information flow analysis and consider sequentially consistent platforms. A considerable effort has been done to reduce false predictions. The contributions of this work are summarized as follows:

- Proposition of a runtime prediction technique for parallel executions.

- Definition of an algorithm for precise predictive taint analysis. The precision of predictions comes from:

- (i) taking into account the underlaying memory model;

- (ii) safely un-tainting memory locations;

- (iii) respecting semantics of synchronization mechanisms (locks).

- The algorithm we propose avoids the enumeration of all serializations.

- Implementation of a proof of concept tool.

#### **Publications**

Sifakis Emmanuel and Mounier Laurent. Dynamic information-flow analysis for multithreaded applications. *ISOLA*, 2012

### 1.5 Organization of the thesis

The thesis is organized in six chapters. Chapter 2 provides background information on threads and formalizes their execution. In chapter 3 we present the contribution on *optimizing critical sections*, while in chapter 4 the contribution on *offline predictive taint*

analysis. Chapter 5 presents the proof of concept experimentations we conducted as well as some tools that were developed. Finally, chapter 6 provides some perspectives and concludes the thesis. Below, are some more detailed descriptions on the content of each chapter.

- Chapter 2 provides background information on thread programming model. We start with a detailed description of different types of threads (kernel, user level). Next, we about the challenges introduced by thread programming, races and synchronization. The chapter ends with a short presentation of weak memory models and the formalization of threads and their execution.

- Chapter 3 initially details critical sections and gives an overview on the two main implementation approaches *optimistic* and *pessimistic*. Next, it presents some literature on improving pessimistic implementations of critical sections. Then we present our algorithm for acquiring and releasing protections and how it is used to compute protections to be held by each instruction in the critical section according to our policies. In total, we define five polices and prove they respect the desired properties.

- Chapter 4 first presents taint analysis (both implicit and explicit). Then it provides background information on dynamic taint analysis. The framework for offline explicit taint prediction is detailed and applied to a completely relaxed memory model, as well as to a sequentially consistent one. For the sequentially consistent memory model we also provide details on the refinement of taint predictions by taking into account untainting of variables and the semantic of synchronization mechanisms (locks).

- Chapter 5 contains the experimentations conducted and the tools developed. The experiments on critical sections although hand-crafted tend to simulate computations commonly found in image processing, with high contention. The experiments on taint propagation are also on hand-crafted examples and the implemented tool is mostly a proof of concept.

- **Chapter 6** concludes with a summarization of the thesis and presents some perspectives for the works on *optimizing critical sections* and *predictive information flow*.

# Chapter 2

# Thread programming model

With SMP and multicore architectures becoming ubiquitous shared memory programming goes mainstream. The *thread programming model* which was widely used even on mono-processor architectures is suitable for exploiting the parallelism offered by the multicore and multiprocessor architectures. In this chapter we provide an overview of thread programming and the challenges programmers have to face.

#### 2.1 What are threads?

A thread or light weight process defines a separate stream of execution within a process. To make the definition more concrete we present hereafter some background information on operating systems (OS). We detail processes and threads and point out their differences. The information we provide is kept at a high level and is based on the *Unix* OS. More detailed information on operating systems is provided in [Tan01].

#### 2.1.1 Description of a process

A fundamental task of operating systems is to instrument the execution of several programs concurrently. This is called *multitasking*. Because the resources (most importantly the CPU) are limited the OS has to rapidly switch the execution of programs so that they appear as executing in parallel. The process abstraction:

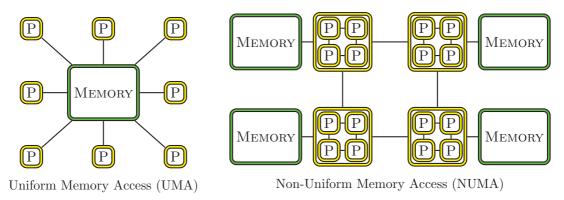

- provides isolation between running programs by assigning to each a virtual portion of main memory (RAM) called the *address space* in which the program can read and write. The address space is logically split into three parts as illustrated in Figure 2.1(a). The *text* segment contains the programs code while the *data* segment the global variables. The stack segment stores information on routines executed by the program. The free space between data and stack is used for dynamic memory allocation.

- stores at the OS level (e.g., in the process table) a multitude of attributes related to a programs execution such as:

Figure 2.1: Address space and status of a process

- general registers

- program counter

- stack pointer

- status, which can be either of:

- \* executing when the process uses a CPU;

- \* blocked when a process gets blocked by an event e.g., reading from hard disk:

- \* ready when it is waiting to be scheduled on a CPU.

Figure 2.1(b) illustrates in an automaton the transitions among the status of a process.

- file descriptors

- priority

- signals

#### 2.1.2 Description of threads

As mentioned earlier a thread defines a separate execution stream within a process. An execution stream consists of the following information which is necessary for resuming the execution on a CPU:

- program counter

- stack pointer

- register values

- status

Defining a thread implies storing the minimum information listed above for the thread. The rest of the information stored for a process is shared among threads. A process can hence be conceived as a mean of grouping resources (address space (memory), files, devices etc.) which are accessible by its threads. By default a process consists of a single thread.

#### Creation and scheduling of threads

There are two ways of creating a thread: manually (user-level threads) or through the OS (kernel threads). Each has its advantages and weak points. User-level threads were most popular when OS did not support threads (still some do not). In this case information on threads is entirely stored in the address space of the process. Moreover, the programmer is responsible of storing and resuming correctly threads. Kernel threads are created and managed by the OS so information on resuming a threads execution is stored at the OS level. Dually, the stack associated to the thread resides in the address space of the process. The number of threads the OS can manage may be limited. In any case, the creation of threads is much faster than that of processes because no resources need to be acquired (e.g., assign a new address space).

For user-level threads the OS assumes managing a regular process, thus in case of a multiprocessor it will always provide only one CPU to execute on. Moreover, scheduling of user-level threads is at the complete responsibility of the programmer. This can be advantageous because any scheduling policy can be applied according to the needs of the program. Kernel threads on the other hand are scheduled by the OS (multi-threading). Dually to user-level threads the OS can assign multiple CPUs to the process and thus execute threads in parallel. In both cases switching between threads is much faster than switching between processes. Finally, the two types of threads can be combined inside a process.

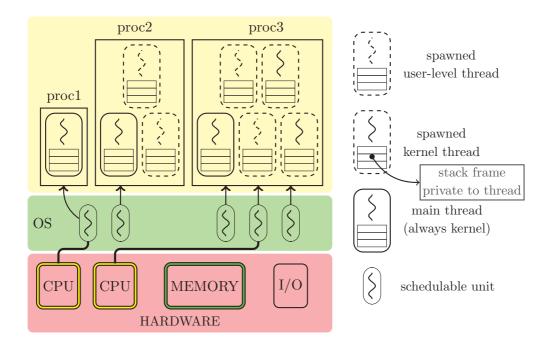

Figure 2.2 presents an instance of a computer system stacked into three layers. At the bottom is the *hardware* in the middle the OS, and at the top the *processes* being executed. The OS has a set of available scheduling units which are linked to a process. A schedulable unit is assigned to a process for each *kernel thread* it contains. A process always has at least one *kernel thread* (as in proc1) which executes it. Process three (proc3) for instance has three *kernel threads* one of which is the main thread and the other two were spawned, as well as two *user-level threads*. Finally, the lines connecting a schedulable unit to a CPU denote the scheduling at a given time.

## 2.2 Common usage of threads

In section 2.1 we gave an insight of threads implementation and how they are related to processes. Processes can be seen as a way of grouping resources while threads as entities to be scheduled for execution. Hereafter we present how the benefits of threads are most commonly exploited.

The main motivation behind threads is to allow a process to progress while waiting on a blocking instruction such as reading a file. A great example is a text editor which stores a backup of the current work while the user edits the text. Instead of blocking the text editor, a thread is spawned and performs the blocking I/O operation while an other thread keeps processing the text. Similarly, all programs with user interaction use threads to remain reactive to user input.

Another common case combines two properties of threads. Access to the same set of

Figure 2.2: Overview of processes and threads.

resources and cheap creation and destruction cost. A server which has to reply to a large number of requests can take advantage of these two characteristics of threads. First, it can rapidly create a thread per request, thus it can concurrently serve many clients. Secondly, by sharing the resources it can be more efficient. For example, a web server could read an *html page* once and forward it to a number of clients that requested it.

Finally, multicore and multiprocessor architectures allow the parallel execution of threads, at least for the number of kernel threads. This can be used to increase performance of applications by parallelizing loops or doing parallel sorting etc. Parallel algorithms are privileged because thread synchronization is much easier to achieve (compared to using inter process communication) and data are immediately shared.

## 2.3 Challenges of threads

The benefits of thread programming do not come for free. Concurrent modifications to the shared memory of a process can cause several bugs such as inconsistent data, memory leaks, program crashing, but can also have disastrous consequences [LT93, Pou04]. Concurrent implies both interleaving instructions of threads and executing them in parallel (i.e., simultaneously each on a CPU or core). In any case non-determinism creates races which can be categorized into *race conditions* and *data races*. The two types of races overlap and thus are often used interchangeably. We provide the definition of each and give an example to clear any ambiguity.

Race condition: occurs when the ordering of events affects the programs correctness.

The ordering may vary due to several reasons such as non-deterministic scheduling, interrupts, memory operations on multiprocessors etc.

**Data race:** is a special case of race condition where two (or more) threads attempt to access a memory address simultaneously, at least an operation is a write and no ordering of the events is enforced. We must note that a data race can be benign.

The overlapping of the definitions is due to the fact that data races are susceptible to turn into race conditions. Resolving data races by no means implies elimination of race conditions. Race conditions are more related to the semantic of what is executed and thus are harder to reason about, identify and resolve.

To disambiguate the definitions we use the example of a bank account withdraw (inspired from [Reg11]). It is intuitive that each withdrawal should be atomic. That is, concurrently withdrawing from an account should reduce the balance of the account by an amount equivalent to the sum of all concurrent withdraws. Listing 2.1 contains a naive implementation of function withdraw which removes the specified amount from the given account acc.

```

1 withdraw(Account acc, int amount){

2   bal = acc.balance;

3   if( bal >= amount ){

4    acc.balcance = bal-amount;

5  }

6 }

```

Listing 2.1: Naive withdraw example.

If two threads t1, t2 issued concurrently a withdraw from an account X then the effect of the withdraw issued by a thread could be suppressed. Such a case occurs if both threads read the same initial balance from account X and then race for writing the new balance of the account. The outcome depends on which thread will write last, since thats the value that will persist. In this naive implementation we have both race conditions because the outcome depends on the scheduling of the threads but also data races since no ordering on memory accesses is enforced.

To correct the implementation of withdraw we must eliminate both data races and race conditions. We use the mutex synchronization mechanism which, as its name denotes, provides mutual exclusion. We assume each account is attributed a mutex (accessible through acc.mutex). More details on synchronization mechanisms are provided in section 2.5.

The implementation of withdraw presented in Listing 2.2 is data race free because all accesses to attributes of the account are synchronized. This however does not prevent race conditions to occur.

```

1 withdraw (Account acc, int amount) {

lock (acc. mutex);

bal = acc.balance;

3

unlock (acc. mutex);

4

if( bal >= amount ){

5

lock (acc. mutex);

6

acc.balcance = bal-amount;

7

8

unlock (acc.mutex);

9

}

10 }

```

Listing 2.2: Withdraw without data races.

Eliminating race conditions necessitates to execute a set of instructions in mutual exclusion with all conflicting instructions of other threads. These portions of code are called *critical* or *atomic* sections. In our example we want to ensure the balance is updated correctly. Thus our critical section should ensure the balance has not been modified between the check and its update. The implementation of Listing 2.3 is both free of race conditions and data races, at least as long as it concerns concurrent withdraws.

```

1 withdraw(Account acc, int amount){

2  lock(acc.mutex);

3  bal = acc.balance;

4  if( bal >= amount ){

5  acc.balcance = bal-amount;

6  }

7  unlock(acc.mutex);

8 }

```

Listing 2.3: Withdraw without data races and race conditions.

We mentioned earlier that data races can be benign. We extend the withdraw example such that it contains a data race which is benign. For that we assume the accounts have a flag which denotes the account has been accessed. This information can be used for random checking of accounts for instance. Thus for performance it may be profitable not to protect accesses to it. The implementation of Listing 2.4 has no race conditions although it contains a data race.

```

1 withdraw(Account acc, int amount){

2  lock(acc.mutex);

3  bal = acc.balance;

4  if( bal >= amount ){

5  acc.balcance = bal-amount;

6  }

7  unlock(acc.mutex);

8  acc.flag = true;

9 }

```

Listing 2.4: Withdraw with data race but without race conditions.

#### 2.4 Data race detection

Data races exist in almost any multi-threaded application for a multitude of reasons: (i) programmers were unable to anticipate interleavings or (ii) left them voluntarily for performance reasons (iii) miss-use of synchronization mechanisms (iv) priority inversion or (v) erroneous assumptions on atomicity of instructions. Because data races can be the source of various bugs and race conditions, several works have focused on their detection. Static and dynamic techniques have been extensively used to that end. Even some special hardware has been designed [MSQT09, ZTZ07, MC91].

Several static analyses and type systems have been defined for race detection, targeting most commonly C and Java languages. Pratikakis et al. [PFH11] propose LOCKSMITH a data flow analysis tool for detecting data races in C programs using POSIX threads and mutexes. The principle of their tool is to deduce a correlation between locks and the memory locations they protect. A program is race-free if all accesses to a location are consistently protected by the same lock. RacerX [EA03] is another race detection tool which also reasons about deadlock freedom. Moreover, it provides a ranking of identified races according to (i) the likelihood of being a false positive and (ii) the difficulty of inspection.

Flanagan et al. [FF00, FLL<sup>+</sup>02, FFLQ08] have conducted a great amount of work on static race detection of Java programs. In [FF00] they propose a type system capable of capturing common synchronization patterns such as classes with internal synchronization and thread-local classes. The type system requires programmers to annotate fields with a locking expression that protects them. In [FLL<sup>+</sup>02] they present Extended Static Checker for Java (ESC/Java). Apart from detecting races it also finds common programming errors such as null dereferences. Most importantly though it uses an automatic theorem-prover to reason about the semantics of the program and which gives it the capability of detecting errors observable at runtime only. Finally, in [FFLQ08] they propose a type system for inferring atomicity of Java methods.

A drawback of static techniques is the excessive number of false positives they produce. The reason is most of them make pessimistic assumptions on feasible interleavings. Dynamic analyses on the other hand are more precise because they reason on feasible executions and all aliasing issues are eliminated. A plethora of such tools exist. Some of these tools such as [PK96, YRC05, JBPT09] are based on the *happens before* relation defined by Lamport in [Lam78]. In this approach accesses to a shared location by different threads should be ordered based on a synchronization. Another technique is the so called lockset analysis employed by Eraser [SBN+97]. It consists in monitoring every shared memory access and verify consistent locking behavior is observed. That is, all accesses to a memory location are protected by the same lock. Hybrid tools combining happens before and lockset technique have also been implemented [OC03, SI09]. Because dynamic methods incur great overheads at execution time [MMN09] proposes a sampling method for monitoring running applications. Data race detection analysis is only performed during selected portions of a programs execution.

Finally, although dynamic data race detection tools are precise a great number of races

detected are benign. Narayanasamy et al. [NWT<sup>+</sup>07] split their data races into potentially benign and harmful. To be able to triage they record the execution into logs and then perform all analyses offline during replay. To classify a data race two different schedules are replayed, if the outcome is the same for both schedules then it is considered as benign. Of course there is no guarantee that all schedules are also benign, but at least the tool cannot demonstrate a harmful execution. A more recent race detection classification tool is Portend [KZC12]. It is also based on replaying a concrete execution but does a finer classification into four categories and has improved accuracy.

#### 2.5 Synchronization mechanisms

Synchronization mechanisms allow to impose an order on the execution of threads and thus control access to shared resources. There exist several mechanisms to synchronize threads. We detail hereafter the most commonly used ones. The implementation and behavior of these mechanisms varies but always relies on special hardware instructions which guarantee atomic update of the information related to the synchronization mechanism.

lock: is a binary variable with two states locked and unlocked. Only one thread can obtain the lock at a time, all other threads are prevented from obtaining it until it is unlocked. Locks provide mutual exclusion and are thus used for protecting critical sections (sequences of instructions susceptible to create race conditions). There are typically two variations of locks:

spin lock a thread that was not able to obtain the lock will repeatedly try to obtain it, resulting into consuming CPU cycles without making any progress. This tactic is advantageous when the time spinning to acquire the lock is smaller than a context switch to another thread.

mutex threads that are not able to obtain the lock get blocked allowing other threads to execute. When the lock is released they are signaled and can try again to obtain the lock.

semaphores: are mostly used to control access to countable shared resources. A semaphore can be conceived as a counter with atomic increment (V) and decrement (P) interface. To obtain a resource a process has to decrement the semaphore. If the semaphores value becomes negative the thread is blocked and put in a waiting list. To release a resource a thread increments the semaphore. If the previous value was negative it unblocks the first thread in the waiting queue.

condition variable: allows to block a thread until a condition is true. A condition variable is always used in conjunction with a lock. The lock is needed for atomically checking the condition. If the condition is false then the lock is released (so other threads can update the condition) and the thread sleeps in a queue related to the condition variable. When another thread updates data of the condition it should signal a single or all threads waiting on the condition so they can test it again.

barriers: are used to synchronize a set of threads. All threads must reach to the state designated by the barrier prior to continuing. For example in a parallel sorting of a table all threads must finish sorting their sub-table prior to merging the sorted parts.

#### 2.5.1 Synchronization issues

Synchronization mechanisms affect the execution of a process by blocking threads when necessary. This brings to surface some well known problems that of *deadlock*, *livelock* or *starvation* and *priority inversion*.

#### Deadlock

A deadlock (or deadly embrace) occurs when two threads mutually wait on a resource held by the other thread to be released. For a deadlock to occur several conditions known as Coffman conditions [CES71] must hold.

- i) mutual exclusion: a resource is either held by a thread else it is available.

- ii) hold and wait: threads can hold some resources while waiting for others

- iii) no preemption: resources obtained by a thread cannot be forcibly released. The thread must release them voluntarily.

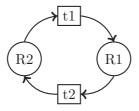

- iv) circular wait: there exists a circular chain between two or more threads each waiting on a resource obtained by the next in the chain. Figure 2.3 illustrates such a case, where circles represent the resources (locks for instance) and squares the threads. Edges exiting threads represent resources obtained while incoming edges represent the requested resources.

Figure 2.3: Deadlock.

#### Deadlock handling

If deadlocks are ignored, then most probably at some point the entire process will get blocked. To avoid this undesired event several solutions can be used. They are categorized into: (i) detection and recovery (ii) avoidance (iii) prevention. detection and recovery: In this approach action is taken after a deadlock is detected. To detect deadlocks a graph of resources must be kept up to date. Then, an algorithm for detecting cycles can be used to detect deadlocks. Recovery occurs by forcibly removing a resource from a thread, that is braking Coffman condition iii.

**avoidance:** Dynamically decides whether allowing a thread to obtain a resource can lead to a deadlock. For this approach to work knowledge of all resources a thread will need is required. The *bankers algorithm* proposed by Dijkstra solves this problem.

**prevention:** To prevent deadlocks it suffices to eliminate one of the Coffman conditions.

- i mutual exclusion can be eliminated by using lock free algorithms

- ii to lift the hold and wait condition, all threads must obtain the resources they require prior to starting their execution. Because resources are usually obtained one by one backing of is necessary i.e., if a resource is not immediately available all resources previously acquired must be released and try again.

- iii removing the no preemption condition correctly necessitates a roll-back of all actions executed by a thread before releasing the resource. This can be too expensive to implement or even impossible (in the case of I/O for instance).

- iv to eliminate circular waits Dijkstra originally proposed defining a partial order over the resources and then enforce they are acquired respecting that ordering.

#### Livelock or starvation

This problem occurs when a thread which is not blocked does not manage to progress. This can happen due to unfair scheduling for instance. Another case is when higher priority threads monopolize a resource thus excluding lower priority threads from accessing it.

# **Priority inversion**

Priority inversion occurs when a low priority thread surpasses a higher priority thread. Here is a typical case of priority inversion as presented in [MSD10]. To demonstrate it three threads are required: t1 with low priority, t2 with medium and t3 with high priority. Initially t2,t3 are blocked and thus t1 manages to acquire a resource to be shared with t3. While t1 has not yet released the resource t2 preempts it because it has a higher priority. Eventually t2 will run to completion surpassing t3 which will resume only after t2 finishes and t1 releases the shared resource. To avoid such circumstances priority inheritance is often used.

# 2.6 Executing threads in parallel

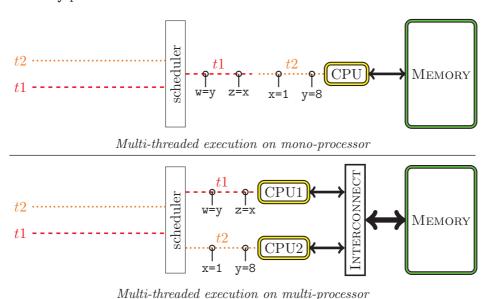

Threads are executed *concurrently*, which incurs their execution can be arbitrarily *inter-leaved* or occur in *parallel* (i.e., at the same time). Figure 2.4 illustrates the scheduling of a multi-threaded application consisting of two threads on a mono-processor and on a

multi-processor system. When executing on the mono-processor, threads are interleaved according to the schedule and memory accesses are serialized respecting program order of executed threads. When executing on a multi-processor (or multicore) system real parallelism can be obtained, and memory accesses may not appear in the same order to all threads. In the example of Figure 2.4 we assume all variables are initialized to zero. For the mono-processor execution the values of z and w will always be 1 and 8 respectively, which is the expected result. For the parallel execution though the values corresponding to z and w can be 1 and 0 respectively, which is a rather unexpected result since the assignment to y precedes that to x and thus should have taken effect too.

Figure 2.4: Execution of multithreaded application.

The memory inconsistencies that can be observed by a multi-processor system are specified in its weak/consistency memory model. The memory model specifies how the memory system behaves. That is, it correlates the values read by load operations with the value written by store operations to the same memory location in a parallel execution of a program. The inconsistencies are caused by several optimizations introduced by compilers and the executing platform. Compiler optimizations are correct for single-threaded applications while hardware optimizations for mono-processor systems. Adve et al [AG96] provide more details on shared memory consistency models and the effect of various optimizations.

### 2.6.1 Sequential consistency

Prior to introducing relaxations of weak memory models, we present *sequential consistency* (SC) which is the memory model programmers are used to reason about. *Sequential consistency* is defined by Lamport in [Lam79] and focuses on:

**program order:** a processor must issue memory operations in the same order as they appear in the program, and prior to issuing a memory operation it must ensure that

its previous memory operation is complete.

write atomicity: writes to the same memory location are made visible in the same order to all processors.

# 2.6.2 Relaxing sequential consistency

For performance reasons most architectures break sequential consistency by using out-oforder execution, non strict cache coherency protocols, and complex memory interconnections (e.g., switch-based). Various memory models can be defined by relaxing the *program* order and write atomicity which are necessary for SC. The relaxations are bounded within a time interval  $\delta$ . We enumerate hereafter some relaxations and present in Table 2.1 how they are incorporated in a number of relaxed memory models.

program order: in this case accesses are made to different locations

- write to read  $(W \to R)$ : a read operation completes before a preceding write

- write to write  $(W \to W)$ : the order of writes is inversed

- read to read or write (R → RW): a read or write operation completes before a preceding read

write atomicity: in this case accesses are to the same location

- read own write early: a processor reads the new values it wrote prior they are made visible to other processors.

- read others write early: a processor can read new values prior they are made visible to all processors.

| Relaxation | $W \to R$ | $W \to W$ | $R \to RW$ | Read Own<br>Write early | Read Others<br>Write early |

|------------|-----------|-----------|------------|-------------------------|----------------------------|

| SC         |           |           |            |                         |                            |

| IMB370     |           |           |            |                         |                            |

| PC         |           |           |            |                         |                            |

| TSO        |           |           |            |                         |                            |

| PSO        |           |           |            |                         |                            |

| RMO        |           |           | 32         |                         |                            |

| WO         |           |           | 12         |                         |                            |

| PowerPC    |           |           |            |                         |                            |

Table 2.1: Relaxations accepted by most common memory models

As we can note in Table 2.1 one of the most common relaxations is the *write to read*  $(W\rightarrow R)$ . Because writes are more costly operations they are often placed in a write buffer while waiting their completion. Subsequent reads can be served as long as there is no pending write to the same address in the buffer. We use the example presented in [AG96] which demonstrates how this relaxation breaks Dekkers algorithm for mutual exclusion.

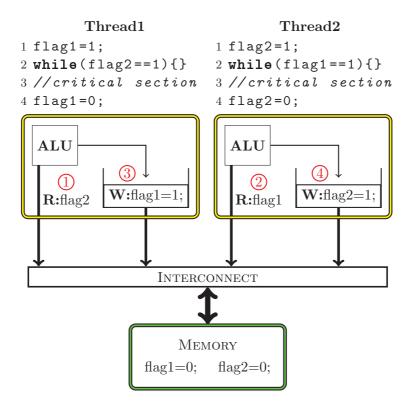

Figure 2.5 illustrates the pseudo-code to be executed by each thread, and a possible execution on an architecture which relaxes  $W\rightarrow R$ . Under sequential consistency Dekkers algorithm guarantees mutual exclusion between two threads. Each thread notifies (by updating its flag) the other it attempts to access the critical section and then checks (reads the other flag) if the competing thread has accessed its critical section first. In the illustrated execution, the circled numbers define the order in which the accesses are served by the memory. As we can note, both threads update their flag, which goes in the respective write buffer and subsequently test the competing threads flag which in both cases returns 0. Thus, both threads assume they can proceed with the execution of their critical section which breaks mutual exclusion.

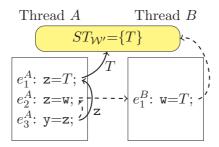

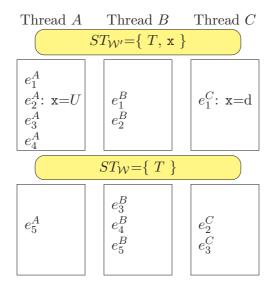

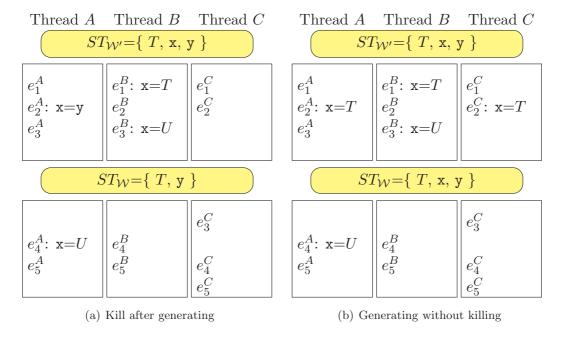

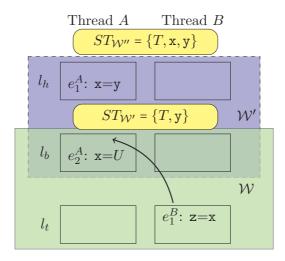

Figure 2.5: Dekkers algorithm broke under Write  $\rightarrow$  Read relaxation