# Model-based design for on-chip systems using and extending Marte and IP-XACT

Aamir Mehmood Khan

## ▶ To cite this version:

Aamir Mehmood Khan. Model-based design for on-chip systems using and extending Marte and IP-XACT. Embedded Systems. Université Nice Sophia Antipolis, 2010. English. NNT: 2010NICE4002 . tel-00834283

## HAL Id: tel-00834283 https://theses.hal.science/tel-00834283

Submitted on 14 Jun2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ DE NICE-SOPHIA ANTIPOLIS

## ÉCOLE DOCTORALE STIC SCIENCES ET TECHNOLOGIES DE L'INFORMATION ET DE LA COMMUNICATION

# THÈSE

pour obtenir le titre de

## **Docteur en Sciences**

de l'Université de Nice-Sophia Antipolis

Mention : Informatique

présentée et soutenue par

Aamir MEHMOOD KHAN

## MODEL-BASED DESIGN FOR ON-CHIP SYSTEMS

USING AND EXTENDING MARTE AND IP-XACT

Thèse dirigée par Charles ANDRÉ et Frédéric MALLET

soutenue le 11 mars 2010

### Jury :

| M. Jean-Luc DEKEYSER | Professeur             | Rapporteur, examinateur |

|----------------------|------------------------|-------------------------|

| M. François TERRIER  | Directeur de Recherche | Rapporteur, examinateur |

| M. Charles ANDRÉ     | Professeur             | Examinateur             |

| M. Frédéric MALLET   | Maître de conférences  | Examinateur             |

| M. Pierre BRICAUD    | Directeur R&D SYNOPSYS | Invité                  |

To Mufti Saeed Khan Sahab and the Family Front.

## Acknowledgments

Firstly, I would like to thank Mufti Saeed Khan for all his help and guidance and especially my cousins 'The Family Front' for keeping the fun part of my life alive. I say thanks to HEC (Higher Education Commission) Pakistan for providing me an opportunity to excel in life and serve better my homeland. I also thank SFERE (Société Française d'Exploration des Ressource Educatives) for guiding me and making my stay in France easier. I am thankful to the University of Nice, Sophia-Antipolis for the management of my studies and for the training by the CED (College des Études Doctoral) in which I participated. I pay my gratitude to the members of CIMPACA (Centre Intégré de Microélectronique Provence-Alpes-Côte d'Azur) design platform for providing an access to the DesignWare IP Room and all other relevant tools. Especially I would like to thank Mr. Pierre Bricaud for kindly arranging special lectures on Synopsys Tools.

I say thanks to INRIA Sophia-Antipolis for welcoming me and for having provided me with all its resources. Thanks to our project assistant, Patricia Lachaume for her help and advice in administrative and daily life. I express gratitude to each member of the AOSTE project for the time spent with them and for their support. I thank Benoît Ferrero for helping me on the technical aspects of my work. I thank Jean-Francois Le Tallec for the discussions and suggestions regarding SystemC and TLM. I thank Julien Boucaron, Anthony Coadou and Luc Hogie for having lively discussions. I thank Julien DeAntoni and Marie-Agnès Peraldi Frati for giving me their valuable suggestions at the meetings. I say thanks to my friends Uzair Khan, Sheheryar Malik and Shafqatur-Rehman for having valuable discussions during the coffee breaks. I thank Najam-ul-Islam for helping me in every aspect of my life and keeping a warm company with his jolly nature.

And especially, I would like to thank Charles André, Frédéric Mallet and Robert de Simone, my thesis supervisors, for helping, guiding and supervising my work. They are my best mentors in all aspects of my studies and research work. I am grateful to Jean-Luc Dekeyser and François Terrier for being my thesis reviewers. Thank you both for your feedback and the corrections you suggested. Your constructive criticism was really helpful.

## Abstract

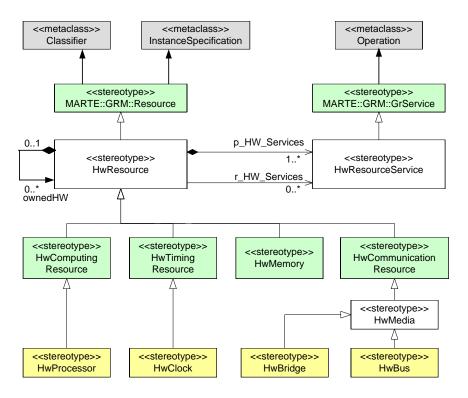

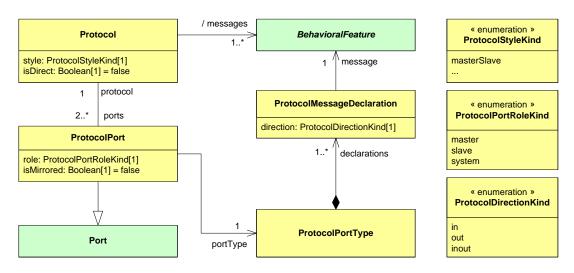

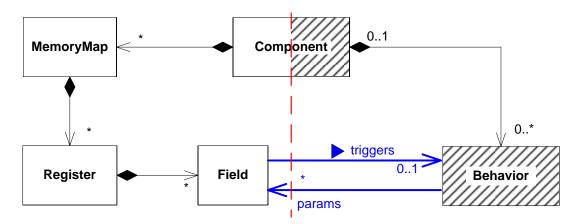

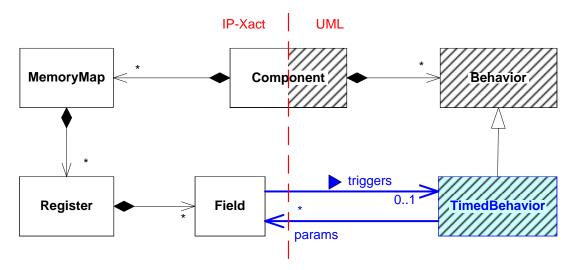

On-chip systems (also known as System-on-chip or SoC) are more and more complex. Soc design heavily relies on reuse of building blocks, called IPs (Intellectual Property). These IPs are built by different designers working with different tools. So, there is an urgent demand for interoperability of IPs, that is, ensuring format compatibility and unique interpretation of the descriptions. IP-Xact is a *de facto* standard defined in the context of electronic system design to provide portable representations of (electronic) components and IPs. It succeeds in syntactic compatibility but neglects the behavioral aspects. UML is a classical modeling language for software engineering. It provides several model elements to cover all aspects of a design (structural and behavioral). We advocate a conjoint use of UML and IP-Xact to achieve the required interoperability. More specifically, we reuse the UML Profile for MARTE to extend UML elements with specific features for embedded and real-time systems. MARTE Generic Resource Modeling (GRM) package is extended to add IP-Xact structural features. MARTE Time Model extends the untimed UML with an abstract concept of time, adequate to model at the Electronic System Level.

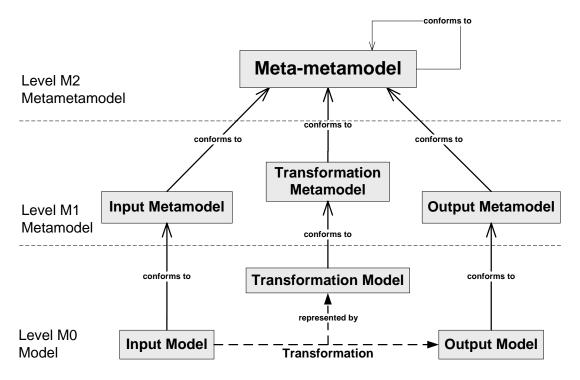

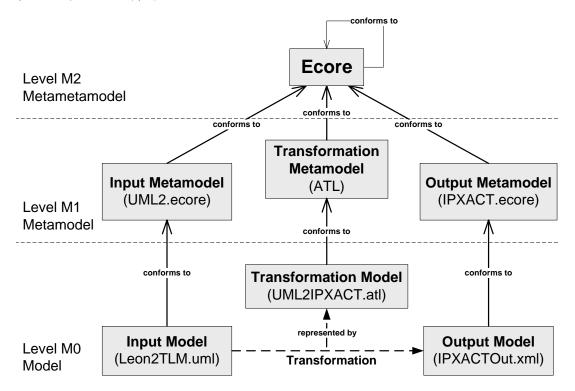

The first contribution of this thesis is the definition of an IP-Xact domain model. This domain model is used to build a UML Profile for IP-Xact that reuses, as much as possible, MARTE stereotypes and defines new ones only when required. A model transformation has been implemented in ATL to use UML graphical editors as front-ends for the specification of IPs and to generate IP-Xact code.

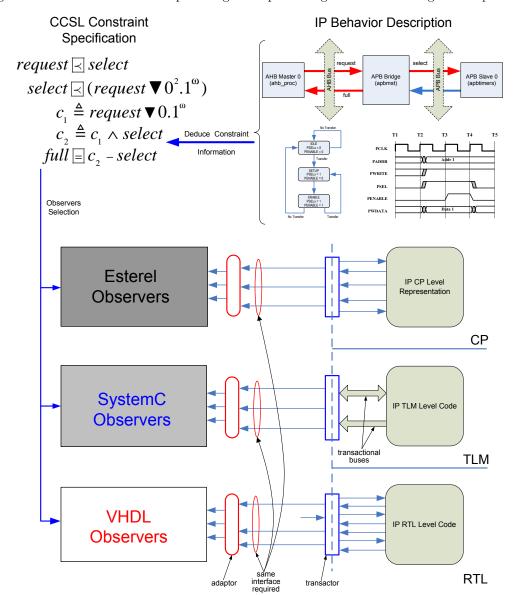

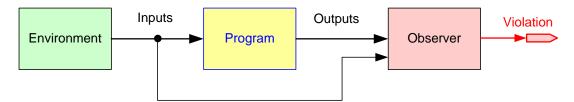

The second contribution addresses the modeling of the IP time properties and constraints. UML behavioral diagrams are enriched with logical clocks and clock constraints using the MARTE Clock Constraint Specification Language (CCSL). The CCSL specification can serve as a "golden model" for the expected time behavior and the verification of candidate implementations at different abstraction levels (RTL or TLM). Time properties are verified through the use of a dedicated library of observers.

## Résumé

Les Systèmes sur puce (SoC) sont de plus en plus complexes. Leur conception repose largement sur la réutilisation des blocs, appelés IP (Intellectual Property). Ces IP sont construites par des concepteurs différents travaillant avec des outils différents. Aussi existe-t-il une demande pressante concernant l'interopérabilité des IP, c'est-à-dire d'assurer la compatibilité des formats et l'unicité d'interprétation de leurs descriptions. IP-xact constitue un standard de facto défini dans le cadre de la conception de systèmes électroniques pour fournir des représentations portables de composants (électroniques) et d'IP. IP-Xact a réussi à assurer la compatibilité syntaxique, mais il a négligé les aspects comportementaux. UML est un langage de modélisation classique pour le génie logiciel. Il fournit des éléments de modèle propres à couvrir tous les aspects structurels et comportementaux d'une conception. Nous prônons une utilisation conjointe d'UML et d'IP-xact pour réaliser la nécessaire interopérabilité. Plus précisément, nous réutilisons le profil UML pour MARTE pour étendre UML avec des caractéristiques temps réel embarquées. Le paquetage Modélisation Générique de Ressources de MARTE est étendu pour prendre en compte des spécificités structurelles d'IPxact. Le Modèle de temps de MARTE étend le modèle atemporel d'UML avec le concept de temps logique bien adapté à la modélisation au niveau système électronique.

La première contribution de cette thèse est la définition d'un modèle de domaine pour IP-Xact. Ce modèle de domaine est utilisé pour construire un profil UML pour IP-Xact qui réutilise autant que possible les stéréotypes de MARTE et en définit de nouveaux uniquement en cas de besoin. Une transformation de modèle a été mise en œuvre dans ATL permettant d'utiliser des éditeurs graphiques UML comme front-end pour la spécification d'IP et la génération des spécifications IP-Xact correspondantes. Inversement, des fichiers IP-Xact peuvent être importés dans un outil UML par une autre transformation de modèles.

La deuxième contribution porte sur la modélisation de propriétés et de contraintes temporelles portant sur des IP. Les diagrammes comportementaux d'UML sont enrichis avec des horloges logiques et des contraintes d'horloge exprimées dans le langage de specification de contraintes d'horloge (CCSL) de MARTE. La spécification CCSL peut alors servir de « modèle de référence » pour le comportement temporel attendu et la vérification des implémentations à différents niveaux d'abstraction (RTL ou TLM). Les propriétés temporelles sont vérifiées en utilisant une bibliothèque spécialisée d'observateurs.

# Contents

| 1        | Intr | roduction 1                                          |

|----------|------|------------------------------------------------------|

|          | 1.1  | Issues Addressed 1                                   |

|          | 1.2  | Proposed Approach                                    |

|          | 1.3  | Document Organization                                |

| <b>2</b> | Ele  | ctronic Systems Design 5                             |

|          | 2.1  | New trends in Electronic Systems Design              |

|          | 2.2  | Systems on Chip (SoCs) Design Flow                   |

|          |      | 2.2.1 Traditional/Classical Design Flow Approaches 6 |

|          |      | 2.2.2 Stages of SoC Design Flow                      |

|          | 2.3  | Synchronous Languages                                |

|          |      | 2.3.1 Reactive and real-time systems                 |

|          |      | 2.3.2 Esterel Language                               |

|          | 2.4  | Transactional Level Modeling                         |

|          | 2.5  | Register Transfer Level                              |

|          | 2.6  | Conclusion                                           |

| 3        | Mo   | del Driven Engineering 21                            |

|          | 3.1  | Introduction                                         |

|          | 3.2  | Models and metamodels                                |

|          | 3.3  | UML                                                  |

|          |      | 3.3.1 UML Classifiers                                |

|          |      | 3.3.2 UML Structured Classes                         |

|          |      | <b>3.3.3</b> UML Profiles                            |

|          |      | 3.3.4 Example of UML modeling of a Timer             |

|          | 3.4  | The UML Profile for MARTE                            |

|          |      | 3.4.1 Overview                                       |

|          |      | 3.4.2 Resources and Allocation                       |

|          |      | 3.4.3 Time in MARTE                                  |

|          | 3.5  | Model to model transformation                        |

|          | 3.6  | Conclusion                                           |

|          |      |                                                      |

| 4 | Illus | strative Example                                                                          |                    | <b>37</b> |

|---|-------|-------------------------------------------------------------------------------------------|--------------------|-----------|

|   | 4.1   | Communications and interactions                                                           |                    | 38        |

|   |       | $4.1.1  \text{Protocol}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |                    | 38        |

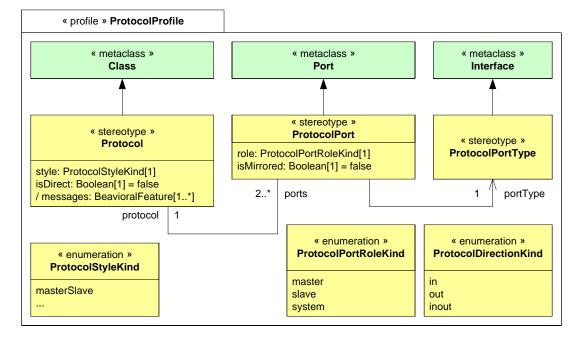

|   |       | 4.1.2 Protocol metamodel                                                                  |                    | 38        |

|   |       | 4.1.3 Protocol profile                                                                    |                    | 39        |

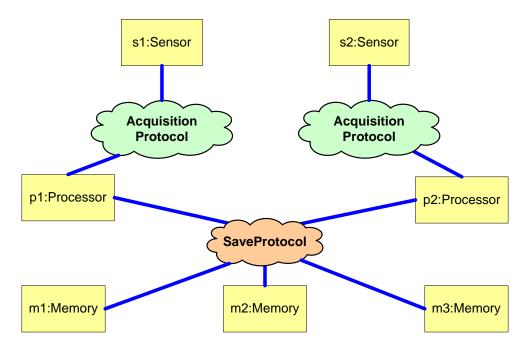

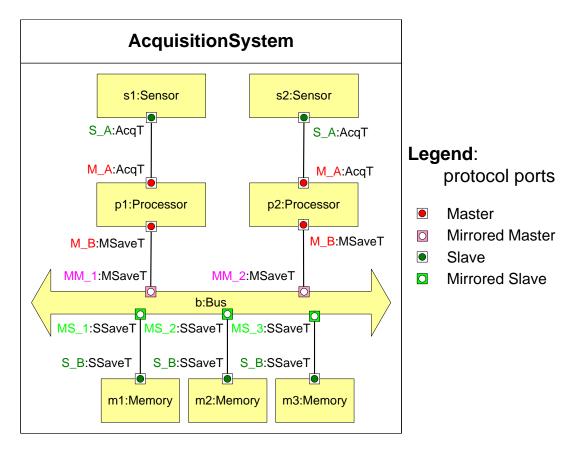

|   | 4.2   | Acquisition system                                                                        |                    | 39        |

|   |       | 4.2.1 System overview                                                                     |                    | 39        |

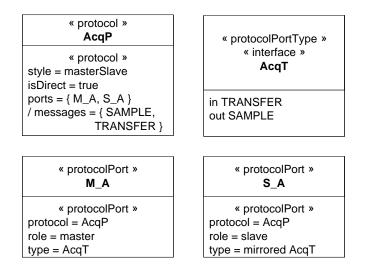

|   |       | 4.2.2 Specification of the protocols of                                                   | of the application | 41        |

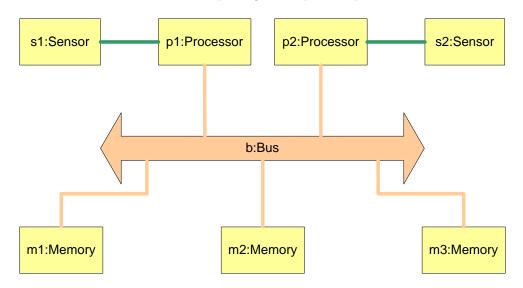

|   |       | 4.2.3 Architecture model                                                                  |                    | 42        |

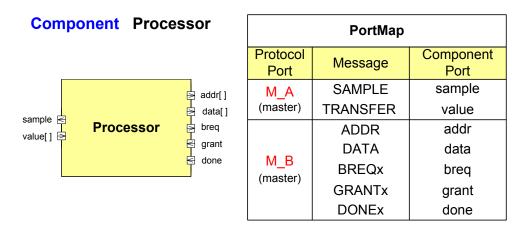

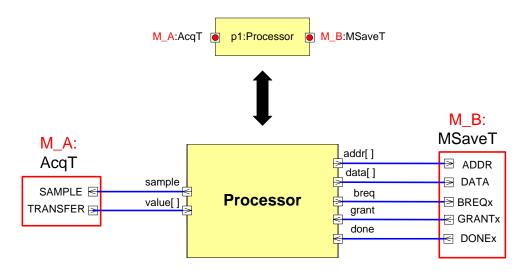

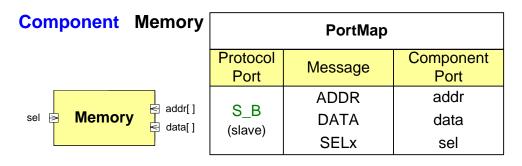

|   |       | 4.2.4 Components                                                                          |                    | 42        |

|   | 4.3   | Esterel modeling                                                                          |                    | 47        |

|   |       | 4.3.1 Data units                                                                          |                    | 47        |

|   |       | 4.3.2 Interfaces specifications                                                           |                    | 47        |

|   |       | 4.3.3 Modules                                                                             |                    | 48        |

|   | 4.4   | VHDL modeling                                                                             |                    | 50        |

|   |       | 4.4.1 Application types                                                                   |                    | 50        |

|   |       | 4.4.2 Component specifications                                                            |                    | 50        |

|   |       | 4.4.3 Architecture                                                                        |                    | 51        |

|   | 4.5   | SystemC modeling                                                                          |                    | 52        |

|   |       | 4.5.1 Transaction level modeling                                                          |                    | 53        |

|   |       | 4.5.2 Modules                                                                             |                    | 54        |

|   | 4.6   | Conclusion                                                                                |                    | 57        |

| 5 | SPI   | IRIT IP-XACT Metamodel                                                                    |                    | <b>59</b> |

|   | 5.1   | Introduction                                                                              |                    | 60        |

|   |       | 5.1.1 Design Environment                                                                  |                    | 60        |

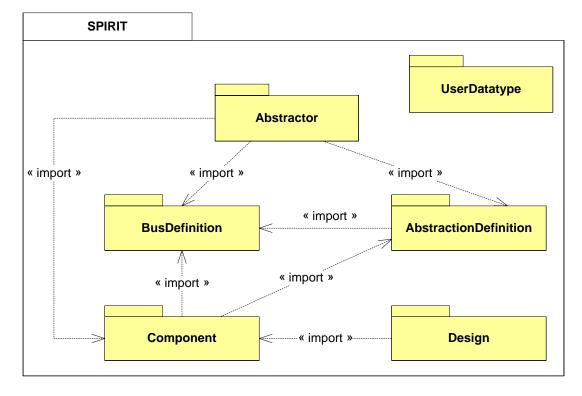

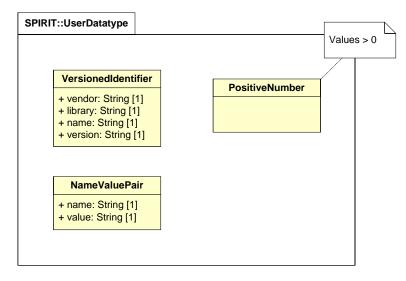

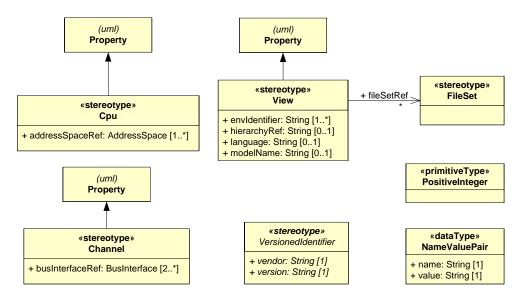

|   |       | 5.1.2 IP-XACT Metamodel Overvie                                                           | w                  | 61        |

|   |       | 5.1.3 The Acquisition system in IP-                                                       | Xact               | 63        |

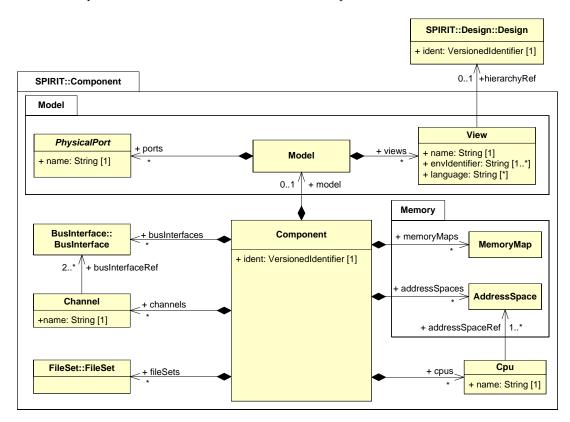

|   | 5.2   | Component                                                                                 |                    | 63        |

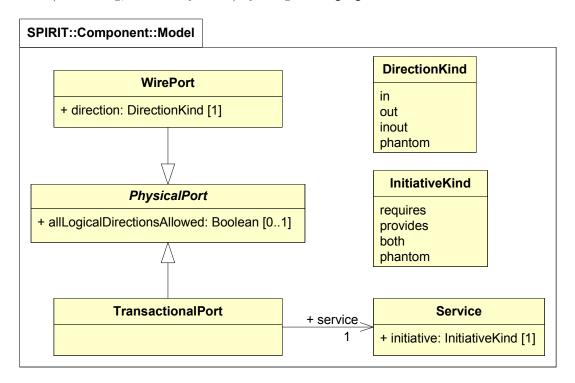

|   |       | 5.2.1 Model                                                                               |                    | 64        |

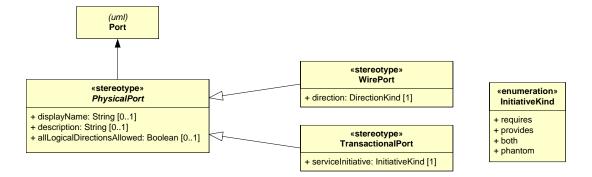

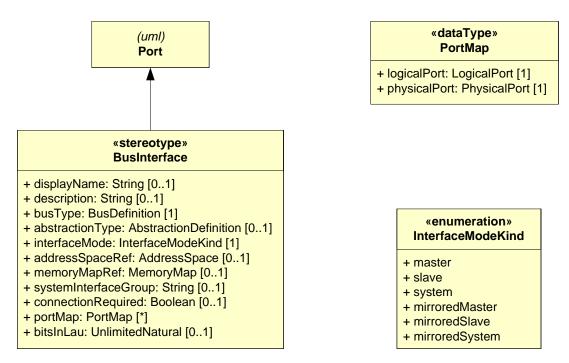

|   |       | 5.2.2 Bus Interface                                                                       |                    | 66        |

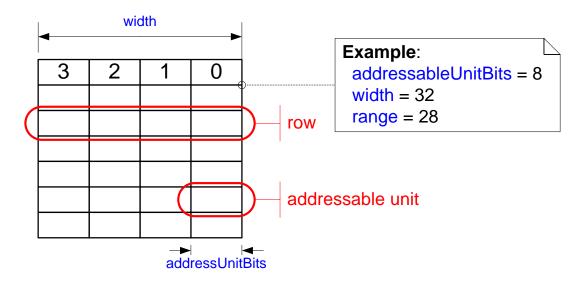

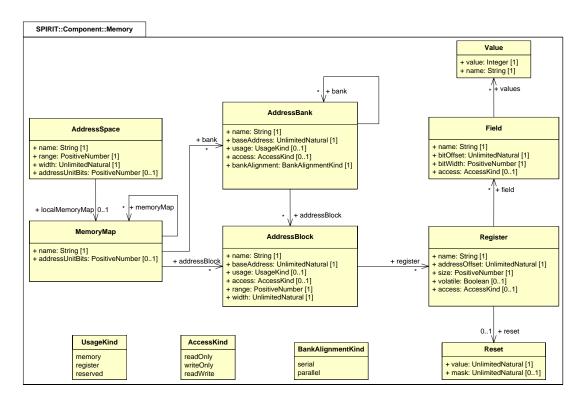

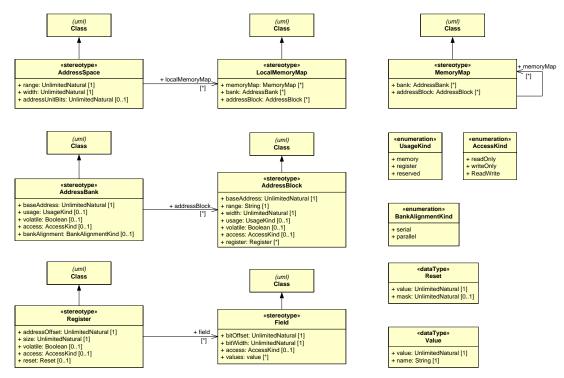

|   |       | 5.2.3 Memory                                                                              |                    | 68        |

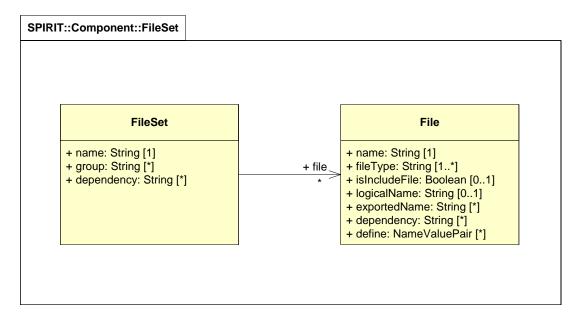

|   |       | 5.2.4 Other Elements                                                                      |                    | 70        |

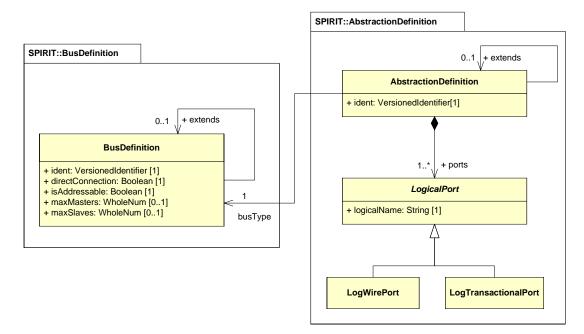

|   | 5.3   | Interface Definitions                                                                     |                    | 71        |

|   |       | 5.3.1 Bus Definition                                                                      |                    | 71        |

|   |       | 5.3.2 Abstraction Definition                                                              |                    | 72        |

|   | 5.4   | Design                                                                                    |                    | 75        |

|   | 5.5   | Abstractor                                                                                |                    | 76        |

|   | 5.6   | Conclusion                                                                                |                    | 78        |

| 6 | Mo  | deling IP-XACT in UML                                                                      | 79       |

|---|-----|--------------------------------------------------------------------------------------------|----------|

|   | 6.1 | Introduction                                                                               | 80       |

|   | 6.2 | Mapping IP-XACT Concepts                                                                   | 80       |

|   | 6.3 | UML Profile for IP-XACT                                                                    | 81       |

|   |     | 6.3.1 UML and MARTE Profile                                                                | 81       |

|   |     | 6.3.2 UML and IP-XACT Profile                                                              | 83       |

|   | 6.4 | IP-XACT Models in UML                                                                      | 91       |

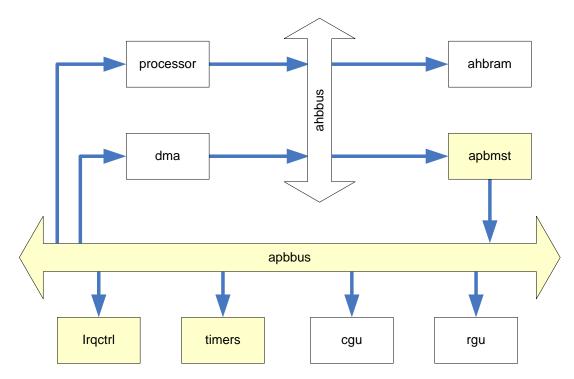

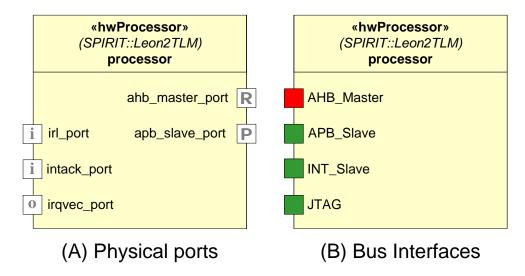

|   |     | 6.4.1 Leon II Architecture based Example                                                   | 91       |

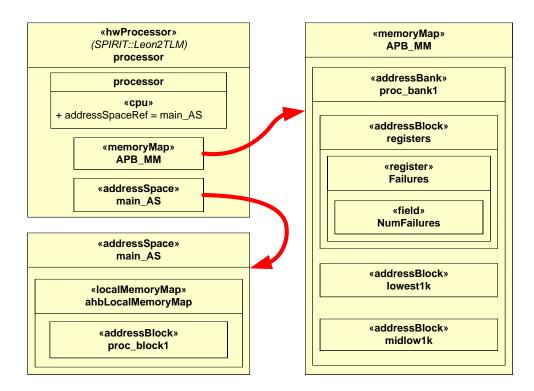

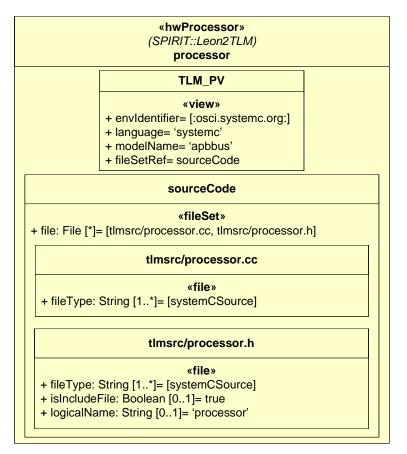

|   |     | $6.4.2  \text{Component}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 93       |

|   |     | 6.4.3 Design and Hierarchical Components                                                   | 97       |

|   |     | 6.4.4 Abstractor                                                                           | 02       |

|   |     | 6.4.5 Interface Definitions                                                                | 03       |

|   | 6.5 | Conclusion                                                                                 | 04       |

| 7 | Beł | navior Modeling 1                                                                          | 07       |

| • | 7.1 | Introduction                                                                               |          |

|   | 7.2 | Reactive behaviors                                                                         |          |

|   |     | 7.2.1 Synchronous languages                                                                |          |

|   |     | 7.2.2 Formalisms with microstep simulation semantics 1                                     |          |

|   |     | 7.2.3 Transaction Level Modeling                                                           |          |

|   | 7.3 | Modeling with logical clocks                                                               |          |

|   |     | 7.3.1 Multiform logical time                                                               |          |

|   |     | 7.3.2 Clock Constraints                                                                    |          |

|   |     | 7.3.3 CCSL in the Acquisition system                                                       |          |

|   | 7.4 | IP-XACT and Behavior                                                                       |          |

|   |     | 7.4.1 Specification of the behavior                                                        |          |

|   |     | 7.4.2 Behavior triggering                                                                  |          |

|   | 7.5 | Conclusion                                                                                 |          |

| 8 | Vor | ification and Testbenches                                                                  | 35       |

| 0 |     |                                                                                            | 36<br>36 |

|   | 8.2 | Property checking                                                                          |          |

|   | 0.2 | 8.2.1 Principle                                                                            |          |

|   |     | 8.2.2 Observers                                                                            |          |

|   | 8.3 | Observer implementation                                                                    |          |

|   | 0.0 | 8.3.1 Esterel observers of the Acquisition system                                          |          |

|   |     | 8.3.2 VHDL observer library                                                                |          |

|   | 8.4 | Observers Example                                                                          |          |

|   | 0.4 | 8.4.1 APB Bridge Specification                                                             |          |

|   |     | 8.4.2 Applying CCSL Constraints                                                            |          |

|   | 8.5 | Conclusion                                                                                 |          |

VIII

| 9  | Conclusion9.1Contributions9.2Future works |     |

|----|-------------------------------------------|-----|

| AĮ | opendices                                 | 169 |

| A  | Acronyms, abbreviations and definitions   | 169 |

|    | A.1 Electronic systems                    | 169 |

|    | A.2 CCSL symbols                          |     |

| в  | Acquisition System Codes                  | 173 |

|    | B.1 Esterel code                          | 173 |

|    | B.2 SystemC code                          |     |

| С  | CCSL and VHDL Observers                   | 185 |

|    | C.1 Adaptors                              | 185 |

|    | C.2 Observers                             |     |

|    | C.3 Generators                            |     |

| Bi | bliography                                | 195 |

# Chapter 1 Introduction

In our daily lives, miniaturization and the growing complexity of electronic systems has resulted in a generalization of the use of on-chip systems. This growing complexity is driven by the consumer demands and the ability of the modern techniques to address complex physical hardware. On-chip system (also called system-on-a-chip or SoC) refers to integrating all components of an electronic system into a single integrated circuit (an IC chip). It is a blend of software and silicon hardware components intended to perform predefined functions in order to serve a given market. The distinctive feature of these systems is to be concentrated on a single block, the chip, to provide the maximum functionality. These SoC designs are very diverse, consisting of multiple design domains (hardware, software, analog), multiple source components (Core IPs, DSPs, ASICs, etc.) and have diverse constraint limitations (real-time, low power, cost efficiency, etc.). All these things make the SoCs very complex. This growth of complexity has been made possible by the unrelenting progress of technology integration of transistors on a chip. In short, a SoC is a complete system which would have been assembled on a circuit board just a few years back, but now can fit entirely in a single chip.

With the exponential growth of system complexity, designing systems at lower levels has become more difficult. So the focus of SoC designers has shifted to more abstract representations. The traditional approach of designing chips, their functionalities, implementation, and verification techniques does not follow the same innovative techniques to match the growth of the SoC complexity. This complexity can only be addressed by modeling at higher level and relying on greater component reuse. Many research initiatives are destined to address these issues to increase productivity techniques and innovations to meet the economic and technical constraints in demand.

### 1.1 Issues Addressed

soc designs heavily rely on the reuse of building blocks, called IPs (Intellectual Property). These IPs are built by different designers working with different tools. Reuse and integration of these heterogeneous IPs from multiple vendors is a major issue of Soc design. The attempt to validate assembled designs by global co-simulation at the implementation level is doomed to failure because of the increasing complexity and size of actual Socs. Thus, there is a clear demand for a multi-level description of Soc with verification, analysis, and optimization possibly conducted at the various modeling levels. In particular, analysis of general platform partitioning, based on a coarse abstraction of IP components, is highly looked after. This requires interoperability of IP components described at the corresponding stages, and the use of trace-

ability to switch between different abstraction layers. Although this is partially promoted by emerging specifications (or standards), it is still insufficiently supported by current methodologies. Such specifications include SystemC [IEE05], IP-Xact [SPI08], OpenAccess API [GL06], and also Unified Modeling Language (UML [OMG07]) based specifications like the UML Profile for Modeling and Analysis of Real-Time and Embedded systems (MARTE [OMG08c]) that specifically targets real-time and embedded systems.

System Modeling requires representation of both structural aspects at different levels of abstraction as well as functional aspects possibly considering time-related viewpoints such as untimed, logical synchronous, or timed models. So the focus areas of our work are both architectural and behavioral aspects of IPs.

For system architecture representation, UML uses class, component, and composite structure diagrams, while SysML [Wei08] (a UML profile for systems engineering) uses block diagrams. UML is a classical modeling language for software engineering. It provides several model elements to cover all structural as well as behavioral aspects of a design but it contains no specific constructs for modeling IPs. Tools like Esterel Studio, and virtual platforms like CoWare, Synopsys CoreAssembler and ARM RealView, introduce their own architecture diagrams, resulting in non-interoperable models. On the other side, IP-Xact relies on XML schemas for specification of IP meta-data and tool interfaces. It has become a *de facto* standard in the context of ESL design. It presents some ADL (Architecture Description Language) features for the declaration of externally visible design interfaces and the component interconnections. It provides portable representations of electronic components and IPs, thus ensuring a kind of syntactic compatibility. It also describes book-keeping information (ownership, versioning, tool chain used, etc.) and memory mappings, useful in deployment and simulation. However, IP-xact scatters information, with data duplication sometimes over various locations. This makes IP-xact difficult to handle manually. Moreover, it also lacks abstract representation of IPs, like the Communication Processes (CP) level. To sum up, we are still looking for a standard, covering all the aspects of the structural description of IPs.

For component behavior representation, we consider various abstraction levels discussed by Gajski [CG03] like CP (Communicating Processes), TLM (Transaction Level Modeling) with its sub-levels PV (Programmers View) and PVT (Programmer View with Time), CC (Cycle Callable), CA (Cycle Accurate), and RTL (Register Transfer Level). IP-Xact provides support for the behavior representation at low abstraction level (RTL), and medium level (TLM/PV, TLM/PVT, CC) through SystemC and VHDL files. These languages provide support for the timed modeling but are not used for abstract levels (CP). On the other hand, UML statemachines, sequence and activity diagrams can be used for modeling at abstract levels like CP (Communicating Processes). But UML lacks the notion of time required to model timed abstract systems. MARTE could be seen as introducing the relevant *timed* version at this level through logical time and abstract user-defined logical clocks.

### 1.2 Proposed Approach

In this thesis, we are addressing the issues of integration and interoperability between the various building blocks (IPs) of a SoC both at structural and functional levels.

The first contribution of this thesis is the definition of an IP-Xact domain model (metamodel). We propose a joint use of UML and IP-Xact, targeting a better integration of both specifications. By this effort, we are able to utilize the graphical and tool capabilities of UML (graphical modular designing, component reuse, different representation views, etc.), jointly with IP-Xact. For this purpose, we partially extend the UML profile for MARTE with IP-Xactspecific stereotypes. Relying on a profiling approach allows easy creation and extension of

#### 1.3. DOCUMENT ORGANIZATION

model editors for IP-Xact based on existing UML graphical editors (*e.g.*,Eclipse UML, Magic-Draw by NoMagic, Rational Software Architect by IBM, Artisan, Papyrus, ...). Selected UML structural models are extended with IP-Xact capabilities and UML behavior models complement the current IP-Xact/SystemC specifications. MARTE time model adds the necessary abilities to specify time requirements. This combined approach allows us the use of IP-Xact in a more abstract-level modeling environment. A transformation engine is built to export models to IP-Xact-dedicated tools. We chose to do this by specializing the MARTE profile, which already provides a number of modeling features for extra-functional aspects and for introducing logical time in the UML. We only define new stereotypes when nothing equivalent exist either in standard UML or in MARTE.

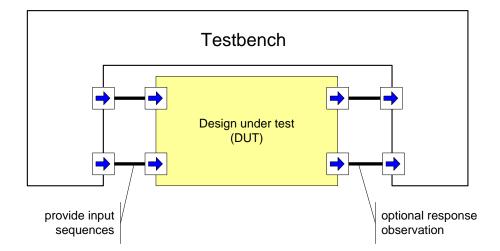

The second contribution of our research work addresses the modeling of time properties and constraints for the IPs. For *component behavior* representation, we enrich the UML behavioral diagrams with the MARTE time model and its associated clock constraint specification language (CCSL) to attach time/behavioral information to an IP structural representation. Our effort related to time information does not attempt to represent the behavior in its entirety but focuses on the IP timing properties extracted directly from the IP specification (datasheets). Expected time properties are expressed in CCSL. Such CCSL specifications then serve as the reference model for the expected time behavior and drive the verification of IPs. These properties are verified with CCSL observers for different implementations of the IP at various abstraction levels, to give some functional equivalence. As an example, we include the time information extracted from the IP datasheets and show how this information can be used to generate test-benches tailored for the different abstraction levels to test the desired IP properties.

#### **1.3** Document Organization

This document is organized into three main parts. The first part consists of chapters 2, 3, and 4. It introduces the basic concepts involved in SoC design flow and model driven engineering (MDE). This introduction prepares a ground for discussing the more advanced issues. Thus, in chapter 2 we compare the traditional and a current approach for the design of SoCs. Later on, we review some of the languages used at the various abstraction levels for SoC designs. Readers from the EDA community can comfortably skip this chapter. In chapter 3, we focus on the classical model-driven approach. This includes a view on the use of models and metamodels in general, and the UML in particular. We introduce the profiling mechanism of UML and a discussion follows on the popular UML profiles related to this work. We then propose a transformation of UML models into IP-Xact models empowering us with the automation of design process. Readers familiar with model-driven engineering can skip these details. Finally in chapter 4, we introduce a simplified computer system example starting from high-level models and refining it to more concrete implementations. This example covers almost all the aspects of our research work. It functions as a running example for this contribution and is often referred to in the following chapters.

Second part of the thesis relates to our contribution regarding the description, integration and interoperability of structural building blocks of socs. It consists of chapters 5 and 6. Chapter 5 introduces our representation of the domain view of IP-Xact specification. This representation is then utilized in chapter 6 for creating the UML profile for IP-Xact based on the existing UML profile for MARTE. Later we model the Leon II system architecture in UML using this newly introduced profile.

In the last part of the thesis, we present our contribution to time behavioral aspects of IPs. This part consists of chapters 7 and 8. In chapter 7, we discuss the behavioral representation of our running example at various abstraction levels. This is followed by an introduction to the clock constraint specification language (CCSL) and on suggestions to integrate this information into the IP-Xact specification. In chapter 8, we introduce the implementation of CCSL constraints in VHDL language which are then used to test and verify the selective properties of Leon II-based embedded system architecture.

The last chapter of this work concludes by recalling the main points of our contribution, the results of using our models with the tools from Synopsys coreAssembler and Innovator, and by providing some perspectives for future works.

# Chapter 2

# **Electronic Systems Design**

#### Contents

| <b>2.1</b> | New            | v trends in Electronic Systems Design 6      |

|------------|----------------|----------------------------------------------|

| <b>2.2</b> | Syst           | ems on Chip (SoCs) Design Flow 6             |

|            | 2.2.1          | Traditional/Classical Design Flow Approaches |

|            | 2.2.2          | Stages of SoC Design Flow 8                  |

| <b>2.3</b> | $\mathbf{Syn}$ | chronous Languages                           |

|            | 2.3.1          | Reactive and real-time systems               |

|            | 2.3.2          | Esterel Language                             |

| <b>2.4</b> | Tra            | nsactional Level Modeling 16                 |

| <b>2.5</b> | $\mathbf{Reg}$ | ister Transfer Level                         |

| 2.6        | Con            | clusion                                      |

Electronic System-Level (ESL) design is the use of appropriate abstraction layers to maximize the understanding of the system while reducing the development time and cost to the system. On the one hand this approach focuses the concurrent development of software/hardware design while on the other hand it introduces abstract modeling layers like transaction level modeling (TLM).

In this chapter we explore the different concepts related to the ESL design including SoC design flow and different abstraction layers. These concepts are then utilized in the structural and behavioral modeling of embedded systems. In the last part, we explore three families of languages (synchronous languages, system-level languages, and hardware description languages) that are used in the other chapters of this thesis for architectural and behavioral descriptions.

## 2.1 New trends in Electronic Systems Design

Electronic systems are increasingly present in our daily lives. Advances in miniaturization allow chip design carrying a continually increasing number of features. Simple mobile phones of the past are now increasing having multiple features like advanced communications like GSM and 3G, camera, video recording, touch sensitive menus, Internet and wireless access, or GPS navigation system, all integrated into a single chip. These all features are associated with a processing chip lying at the center of any electronic device. This chip is an equivalent of the old designs of dispersed devices connected through the buses on the motherboard. Such a chip known as *System-on-a-Chip* or SoC is the brain of most the embedded devices designed these days.

The doubling of the complexing of systems on chips, approximately every two years as predicted by Moore's Law, has given us systems that are increasingly sophisticated, and are at the same time more and more difficult to conceive. On the other hand, the productivity of a system designer/developer was comparatively slow. Thus, there is a growing gap between the evolution of the physical chip designs and the software support for them, termed as the *design gap*. This problem gave way into finding the new trends focused on system design methodology.

Daniel D. Gajski has discussed, in his paper [Gaj07] and a panel discussion [SSS+03], about the strategies for dealing with the rising Systems-on-Chip (SoCs) complexity by using the higher abstraction levels. An abstraction level is a means of addressing the inability of the human mind to totally comprehend a complex system at a very detailed level [BMP07]. Thus we increase the size of the basic building blocks that are used in our designs. Presently used complex SoCs cannot be properly represented in the traditional register transfer level based methodologies.

In this chapter, we firstly present the design flow for the realization of Systems on Chips. Later, we explore in detail the major stages of this design flow including Register Transfer Level (RTL) and Transaction Level Modeling (TLM). Finally we try identify their shortcomings and the areas of possible improvement.

## 2.2 Systems on Chip (SoCs) Design Flow

#### 2.2.1 Traditional/Classical Design Flow Approaches

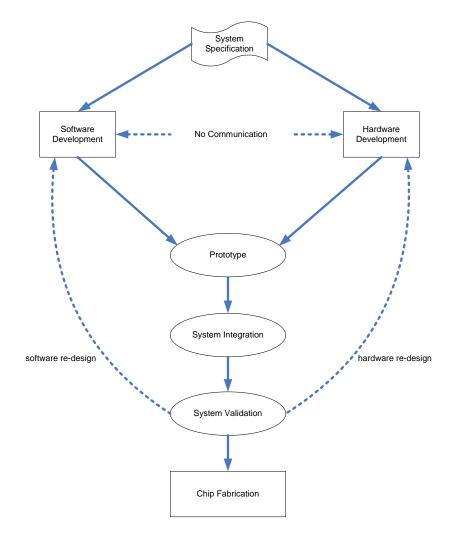

Frank Ghenassia in his book [Ghe05] states that the design flow is a rigorous engineering methodology or process for conceiving, verifying, validating, and delivering a final integrated circuit design to production, at a precisely controlled level of quality. Moreover, he gives also a look into the traditional design flow of an embedded system as shown in figure 2.1. This design flow starts with the design specification given by the client. Based on this specification two separate developments of the hardware and software begins independently. Note that the two developments take place totally independently without any regard of others' existence. The two designs are kept separate until the prototype of the system-under-design is ready to be tested.

In a traditional design flow, the hardware design development usually begins with the creation of hardware models using hardware description languages (HDLs) like VHDL or Verilog. These models are then simulated for functional verification or correctness of the behavior of the module. Finally, synthesis is performed to obtain the code netlist. Later this design is laid on the chip to build our basic prototype. On the other hand, the software development goes independently without any knowledge about the hardware design. Although the software

Figure 2.1: Traditional SoC Design Flow.

coding starts quite early in this way, but the testing of this code can only happen when the hardware design prototype is available.

One of the biggest disadvantages of the traditional design flow approach is the system validation at quite late stages of the design. Until the system prototype is ready and simulated along with the software design, we cannot validate the system. This problem is augmented with the fact that the software and hardware designs are modeled independently and without co-ordination. Hence, when at the later design stages a problem evolves, it costs more to correct it and re-design the system prototype. Moreover, the simulation speed for the designs at this level is very slow making the task of validating huge designs to be very long.

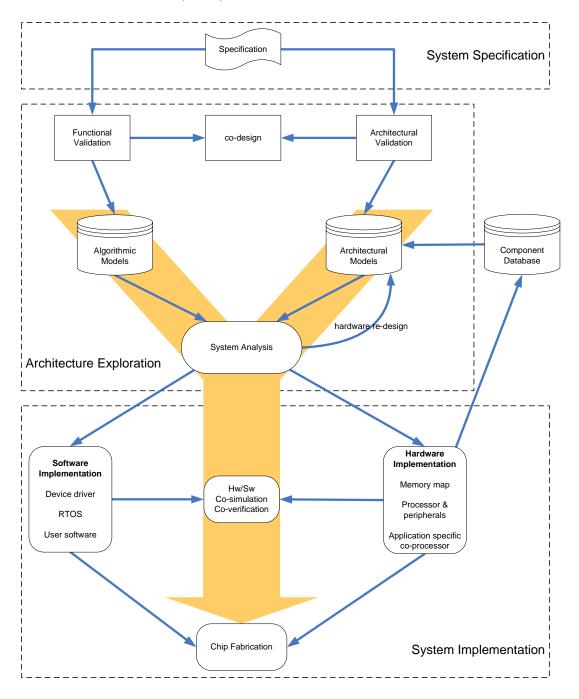

A new and classical system level design flow approach is shown in the figure 2.2. This classical design flow differs from the traditional system design flow in many ways. The traditional design flow uses a single system specification to describe both hardware and software. On the other hand, classical design flow models use the Y-chart methodology [Erb06] for the

hardware/software partitioning. This methodology uses a clear separation between an algorithmic/application model, an architecture model and an explicit mapping step to relate the algorithmic model to the architecture model. The application model describes the functional behavior of an application independent of architectural specification whereas the architecture model defines the system architecture characteristics. Thus, unlike the traditional approach in which hardware and software simulation are regarded as the co-operating parts, the Ychart approach distinguishes algorithm/application and architecture simulation where the latter involves simulation of programmable as well as reconfigurable/dedicated parts [Erb06]. Moreover, in the traditional design flow, the system validation is not possible until the design prototype is ready whereas in the present time classical modeling approaches, the system can be hardware/software co-simulated just after the initial design specification phase. This cosimulation [Sch03] is absolutely necessary for the software development such that the software design teams can have an idea of the underlying hardware resources to be utilized efficiently. In the traditional approach, the software development can only proceed when the hardware development phase has completed whereas in the current practice, hardware and software are partitioned to co-simulate at the same time. Partitioning is the process of choosing what algorithms (or parts thereof) defined in the specification to implement in software components running on processors, what to implement in hardware components, and the division of algorithms within the software and hardware components [BMP07]. There are limitations for this as the developed code depends on the underlying hardware used. For this purpose, techniques have been developed to enable the software to run on virtual hardware models or virtual platforms like the ones using transaction models (discussed in detail later). This approach dramatically reduces the Time-to-Market (TTM) duration due to reduced number of errors and early system validation. *Time-to-Market* is the time duration that it takes for a system chip design to be materialized and introduced to the market and is an important index to judge the performance of design techniques used.

#### 2.2.2 Stages of SoC Design Flow

A classical system level design flow (shown in the figure 2.2) can be divided into three main phases: system specification phase, architecture exploration phase and the system implementation phase, all discussed next.

#### System specification

In the system specification phase, we identify the requirements that the chip has to fulfill. SoC provides a variety of features on a single chip including interaction with the other component modules and with the user, which makes it quite complex. The SoC specification includes the desired requirements from the end-user and the specific constraints being enforced by the surrounding environment. These constraints can be of a vast variety. For instance, for a multimedia application, the loss of data is not as important as the jitters and the delay in the communication whereas for critical embedded applications like in avionics, the systems have to be real-time as well as accurate in data. All such constraints are taken into account while designing a chip.

#### Architecture exploration

System specification phase leads to the *architecture exploration phase* during which the system architect determines the hardware configuration that will be necessary to meet the needs

Figure 2.2: Classical System Level Design Flow.

expressed before. This step is broken down into two parts: functional modeling phase and system analysis phase.

During the *functional modeling phase*, different executable models for the hardware and

the software of the system are designed. Usually hardware modeling deals with the resource allocation while software modeling includes the definition of key functions, programs and routines. These models identify the key building blocks of the system and their interconnections. They provide the possibility of an early functional and architectural validation of the system, co-designing hardware and software models. These models also give us a big picture about the requirements and interdependence of system modules leading to early detection of logical system errors. The algorithmic and architectural models used for the creation of functional model are rarely rebuilt from scratch in each new chip but are usually reused from an IP library. Here, a standard like IP-Xact [SPI08], which is at the heart of this thesis, plays a key role by providing component IP databases. In fact the blocks which constitute a system on chip are generally created to be reused and usually a new system design architecture reuses and integrates these components, leading us to the concept of *platform based systems* [SVCDBS04].

System analysis phase decides the low level details about the system design. This step crucially determines the remaining design flow as by this time the system architect must determine how the chip will be incorporated to meet the requirements specified in the previous phase. A key parameter for this determination is the hardware/software partitioning. At the end of this phase we obtain a hardware/software partitioned system that has an adequately allocated proportion of design functionality between the hardware and the software. After this phase our system architecture is finalized and we can proceed with the system implementation phase. As an example we consider a functional model of a system running some specific programs. There are several ways to execute this specific program on the given model. In one approach, we can assign the task to a processor and hence algorithm is implemented in the software. This approach is quite easy and offers great flexibility as we can alter the program (to a limit) even after the hardware fabrication. However, if the executed program is too complex, the processors are not an efficient choice in terms of time and power consumption. This leads us to the second approach of creating ASICs (Application Specific Integrated Circuits) which costs us the flexibility to modify but are very efficient in terms of energy and time consumption leading to shorter time-to-market durations. A third approach placed in between these two is of the use of FPGAs. FPGAs are fully customizable hardware units and give more flexibility for hardware design as compared to ASICs. The system analysis process finally leads us to the determination of a system whose software has been specified as well as components that will execute it. This gives way to the development of respective software or hardware implementations in the next phase.

#### System implementation

Following the system analysis, we have the *system implementation phase* after which we have the software and hardware implementation models of the system.

In the present times, the *software implementation* for a SoC design has become a pivotal part for the overall system development. Software development includes variety of programming including the low level device drivers coding, the operating system development and management, and finally the problem specific end-user application. With the current trends of evolution of system-on-chip architectures, having generalized multiprocessor system designs, the importance of implementation software augments. The device drivers and operating systems are the softwares that are directly dependent on the underlying hardware and make the application programming simple and hardware independent. Software programming heavily depends on the system requirements specification. On one side a simple SoC design can have a naive software implementation whereas on the other side if the software is implemented for the critical embedded applications like in avionics or life saving devices, its correctness and proper functioning matters a lot. Various design techniques have emerged in the EDA industry

to deal with the verification and validation of such software implementations.

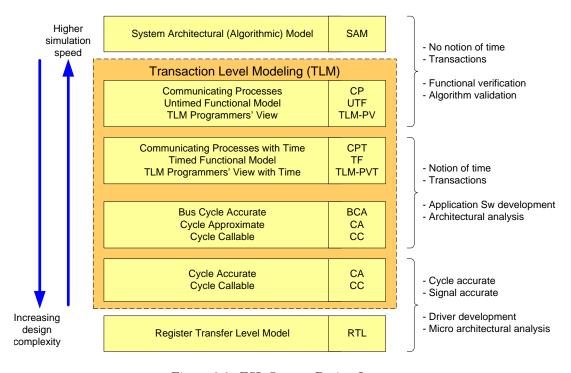

Figure 2.3: ESL System Design Layers.

The hardware implementation is the process of creating models that may be synthesized into gate-level models. These models of a system design can be represented at different modeling levels. Every design engineer can have his own view of the abstraction level of system design. There can be potentially hundreds of abstraction levels for an electronic system design, but mainly we focus on three commonly used abstraction levels [Rev08] namely System Architectural Model (SAM), Transactional Level Modeling (TLM), and Register Transfer Level (RTL) (as shown in figure 2.3). From a system designer's view point, the design starts from a model specification. System Architectural Model comprises of design specification and its algorithmic model. The design specification is the system requirement usually documented in a textual language. Then this requirement specification is converted into a simple model comprising of functions. Both these representations give the broad picture of the system representation and are usually not meant for simulation purposes. These representations are characterized by untimed transactions and can be used for high level system validation purposes. At the higher levels of abstraction, the range of modeling levels is coarsely defined and overlaps with the adjacent levels. Transaction Level Modeling (TLM) is an abstract modeling level providing the initial executable model of the system, hence leading to early system simulation and validation. While most of these levels are optional and are only there to facilitate the design flow, the last RTL model is mandatory. RTL models give the most precise way to represent the components present on the chip, and which can be automatically synthesized into a logical combination of elementary operations (logic gates) whose implementation is materialized through the transistors and integrated circuits (ICs) engraved on the circuit chips. These different modeling levels demand different models and languages. We present three families of languages addressing the various levels.

### 2.3 Synchronous Languages

Most electronic systems are *reactive* and present to some extent *real-time* features. Synchronous languages have been developed to deal with reactive systems. We present them in this chapter on electronic systems for three main reasons:

- the importance of electronic systems in real-time and embedded applications;

- the intrinsic interest of the synchronous paradigm and its relationship with synchronous circuits;

- the recent evolution of some synchronous languages, like Esterel, to electronic system design.

#### 2.3.1 Reactive and real-time systems

Reactive systems interact with the real-world environment by reading the sensors or receiving interrupts and produce the output commands/information. For correct functionality they have to produce valid data under strict time constraints (deadlines) hence leading to both logical and temporal correctness of real-time systems [BB91]. Safety is a critical issue for many realtime systems with numerous human lives at stake. The behavior programming in general and especially of such systems can be done using combination of finite state machines (FSMs). StateCharts [Har87], which are hierarchical and concurrent state-transition models, can be used instead of a collection of FSMs. Both FSMs and StateCharts are normally implemented in HDLs or C language. Such low-level languages do not help much to deal with the complexity of the systems and have limited component reuse, difficult to debug, and error-prone (with error detection at late design stages). Moreover, these languages are not adequate for high level design for which system-level design languages like SystemC [IEE05] and SpecC [DGG02] were introduced lately. These system-level languages facilitated the hardware/software co-design and co-simulation leading to early system validation. However they lack a formal semantics and hence are not a good choice for the formal verification and the correct-by-construction [Ber07] implementation of systems.

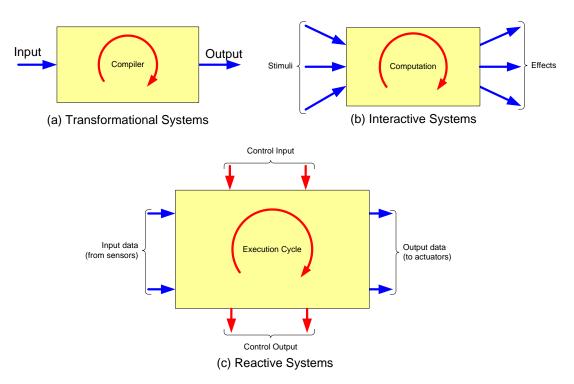

Computer systems broadly fall into three categories based on their behavior; transformational systems, interactive systems, and reactive/reflex systems [Hal92, chapter 1]. Example of *transformational systems* is the compiler which takes input code and generates an output targeted for a specific architecture. The *interactive systems* are the ones which intake several input stimuli and produce various output signals according to the input signals, without any regard for the time taken to process this information. This means that the environment/client does not know when the output will be available. On the other side, the *reactive systems* are the ones in which correct functioning of the system not only depends on processing the input but also on the timely response of the system (just like our reflexes). Hence the interactive systems are non-deterministic while the reactive systems are predictable. In another way, we can say that the interactive systems have got their own pace of execution while interacting with the environment whereas the reactive systems theoretically react instantly to the inputs and their pace of execution is dictated by the environment. All these types of computer systems are shown graphically in the figure 2.4.

The behavior of a reactive system is usually described as a sequence of reactions, resulting from *execution cycles* in which (sequentially) it reads inputs from the sensors, processes that

Figure 2.4: Types of Computer Systems.

input data based on the control commands, and finally generates output to manipulate the actuators. The reactive systems are generally implemented by finite state machines (FSMs). Traditionally, the tools to design reactive systems forced the users to choose between the determinism and concurrency for a system. Contrary to the traditional programming languages, synchronous languages prove to be the good candidate for the programming of reactive/realtime systems. These languages provided the system designers with the ideal primitives to deal with the issues related to reactive systems design. Synchronous Languages were initially introduced in the beginning of 1980s  $^{1}$ . They are based on the *perfect synchrony hypothe*sis [Ber00b], in which concurrent processes are able to perform computation and exchange information in zero time. Such a synchronous model has a great appeal in the real-time modeling domain including embedded systems (avionics, SoC design), communication systems and hardware design. These languages can be classified as declarative languages and imperative languages, based on their programming style. Declarative synchronous languages adopt a dataflow style. They express the logic of a computation without explicitly describing its control flow. They focus on 'what' the program should accomplish. Synchronous programming languages like *Lustre* [HCRP91] and *Signal* [LGLBLM91] represent this category. The former is a synchronous flow language that relies on equations; the latter is more general and considers relations. Both can be efficiently used for steady-process control and signal processing applications. In the contrast, *imperative synchronous languages* describe (reactive) behavior in terms of statements that change a program state; they focus on the 'how'. Esterel [BdS91, Ber00b] and SyncCharts [And96] represent such languages. They are better used in control-intensive

<sup>&</sup>lt;sup>1</sup>http://www.esterel-technologies.com/technology/history/

applications. Recently, developments in the synchronous language tools have made this classification a bit vague. For instance SCADE, a Lustre-based industrial synchronous methodology and tool-set  $^2$ , has integrated SSMs (Safe State Machines, a variant of SyncCharts) which are control-oriented, and Esterel (version 7) now supports Lustre-like equations.

The synchronous languages provide the formal semantics as well as the abstract representation of designs at system level which makes them a good choice for behavior representation. The imperative programming languages like Esterel also facilitate the designing of FSMs, discussed in the next subsection.

#### 2.3.2 Esterel Language

In our work, to program the reactive applications and FSMS, we have used Esterel Language along with SyncCharts. These applications can be represented using textual (Esterel) as well as graphical (SyncCharts) forms. *SyncCharts* is a graphical language expressing hierarchical and concurrent state machines. SyncCharts is a model akin to StateCharts. However, they differ on their semantics: SyncCharts adheres to the perfect synchrony hypothesis while State-Charts has many synchronous but not perfect synchronous semantics [vdB94, HN96]. Because SyncCharts and Esterel share a common semantics, they can be freely mixed in a specification. In the Esterel Studio Suite, a syncChart is first translated into a semantically equivalent Esterel program, and then treated as an ordinary Esterel program. In the following, an Esterel rogram stands for its textual as well its graphical format. The compilation chain of Esterel can generate program codes in languages like C, VHDL, or SystemC. These programs have a behavior equivalent to the one specified by the Esterel program, but concurrency has been compiled out.

The early versions of the Esterel language [BdS91] (in the 80's and 90's) targeted reactive systems and safety-critical systems without special consideration for electronic systems. Since 1999, within an industrial context, the Esterel compiler has undergone broad syntactic extensions, leading to Esterel v7 [Est05], and its main application domain has become electronic system design. To understand this evolution we have to briefly describe the basics of Esterel and bring out the main changes in the language.

#### Esterel v5

The syntax and an informal semantics of Esterel v5 are presented in a language primer [Ber00a]. A book [PBEB07] describes formal semantics of the language and different compilers. An Esterel program can be seen as specifying a collection of communicating threads running concurrently. Here, concurrency should be understood as cooperation, not competition as it is often the case in interactive systems. Note that most of the Esterel compilers generate a sequential executable code; thus the threads we consider are logical or conceptual, not physical (run-time threads).

The simplest way to understand the behavior of a synchronous program is to consider that each thread performs a cycle-based computation in which environment actions strictly alternates with thread actions. The many threads that constitute the program communicate and interact during their active phase. These concurrent/cooperative evolutions define an *instant*. All the actions and the information exchanges are *simultaneous* (*i.e.*, at the same instant).

In Esterel, *signals* are the only means of communication and provide the unique support for communication between threads. When a thread *emits* a signal, this signal is instantly broadcast and thus can be seen by any thread that may be concerned. A signal is either

<sup>&</sup>lt;sup>2</sup>http://www.esterel-technologies.com/products/scade-suite/

#### 2.3. SYNCHRONOUS LANGUAGES

present or absent at a given instant. *Pure* signals carry only this presence information. *Valued* signals also convey a typed value.

To emit or test a signal is a reactive statement in Esterel. Preemptions are other typical reactive statements. *Preemption* is the capability for a thread to block the execution of another thread. The preemption can be temporary (*suspension*) or definitive (*abortion*). The simplest form of abortion is the **await** statement which makes a thread wait for the next presence of a signal.

Syntactically, an Esterel program consists of one or several modules. A *module* is a program unit that has a declarative part (*header*) and an imperative part (*body*). The header specifies the interface of the module: it declares signals with their direction (input, output, inputoutput) and their type. The body contains executable statements and structured blocks of statements that can be nested and composed in parallel or in sequence. Modules can also be instantiated in a module, allowing hierarchical specifications. *Local signals* declared within the body of a module serve as communication medium for its concurrent threads.

The semantics of Esterel guarantees that preemptions at any depth and any degree of concurrency are always deterministic. The unicity of each signal status (presence and value, if any) is also assured at each instant. This makes Esterel an outstanding language for programming complex control-dominated systems that require fully predictable behavior.

Note that Esterel, like the other synchronous languages [Hal92], relies on a *logical time* rather than *physical time*. Only the ordering of event occurrences is meaningful, not the "physical" duration between them. An event can occur before or after another one, but it is also possible for them to occur simultaneously. In contrast to non-synchronous models, the notion of simultaneity is precisely defined in synchronous languages and characterizes things occurring at the same instant.

The compilation of an Esterel program is a hard task [Ber00b, PBEB07]. Each signal must respect two *coherence rules*:

- 1. a signal is only present or absent in an instant, never both;

- 2. during a reaction, for any output or local signal, all the emit actions must precede any test action.

The latter rule is a form of causality relationship not easy to check on complex programs. The *constructive semantics* has defined simple correctness criteria for causality. A second difficulty came from the size of the generated code when FSMs were taken as target representation. In the mid 90's appeared the *circuit semantics* of Esterel. This semantics translates Esterel programs into sequential circuits, or equivalently into logical equations, similar to the ones found in Lustre programs. This logical representation is amenable to powerful optimizations that have been extensively studied in the hardware community. Direct implementations in hardware and software can be generated from the optimized circuits. The close relationship between the Esterel semantics and the circuits is probably one of the main reasons why Esterel has successfully evolved to Esterel v7 which is equipped to address electronic design.

#### Esterel v7

Esterel v5 failed at modeling/programming large-scale system-level or hardware designs. It lacked prominent features [BKS03] in its ability to describe data paths, to deal with bit-vectors, to directly support Moore machines, etc. Esterel v7 has corrected these deficiencies by syntactic improvements that have left the semantics of the language mostly unchanged.

For our usage of Esterel in this thesis, the most interesting changes are in the declarative part. Three types of program units are now available:

- *Data unit* which declares data types, constants, functions, or procedures. It can *extend* one or several other data units by importing all the objects they declare.

- Interface unit which primarily declares input/output signals and can also extend other data and interface units by importing all their data and signal declarations. Interface units can also be declared as mirror of some other interface which means that the interface type is the same, but the interface signal directions are reversed.

- *Module unit* that defines the reactive behavior of the system. The header of the module can extend data and interface units by importing the objects they declare.

Units can be generic, which allows better reuse. Also of interest is the introduction of *port*. A port is a group of signals typed by an interface. A port allows renaming of signals in interface instantiations. Esterel v7 supports *arrays*. Ports and signals can be declared as arrays. The array mechanism facilitates the specification and the handling of large structures like buses in computer architecture.

Modern hardware designs usually have more than one clock. Moreover, for power saving, these clocks can be turned on and off. To address these new design challenges, Esterel v7 supports *multi-clocking* and adopts the GALS (Globally Asynchronous Locally Synchronous) design paradigm. A new kind of signal (clock) and a new kind of unit (multi-clock) have been added to the language. A multi-clock unit is similar to a module unit but it declares one or many clocks in its header. It can also define local signals and clocks. Several module and multi-clock units can be instantiated in a multi-clock unit. The classic module instances perform computations, usually driven by an explicit clock, while the enclosing multi-clock unit only deals with clocks and signals.

All the correct Esterel programs are synthesizable in hardware and software, including multi-clock designs. Moreover, the programming structure of Esterel v7 resembles more to the HDLs. So, the advent of Esterel v7 has greatly improved the capabilities of the language for use in EDA (Electronic Design Automation) applications. Besides all these language improvements, Esterel Studio now supports *architecture diagrams*, a graphical notation similar to hardware block-diagrams and representing the Esterel design structure.

### 2.4 Transactional Level Modeling

Transaction Level Modeling (TLM) is a high level approach to modeling digital systems where details of communication among modules are separated from the details of the implementation of the functional units or of the communication architecture [Gro02]. Low simulation speeds and complex SoC designs turn the system designers towards the more abstract level system representations. Transaction Level Modeling (TLM) is one such abstract system representation which can be regarded as the first representation of the implemented components after hardware/software partitioning. Because of its high level of abstraction, TLM gives us high simulation speeds for a complete system on chip design representation as compared to respective RTL models. Figure 2.3 shows the TLM abstraction layer. The transactional level itself is not a particularly defined modeling level but is a collective logical name for four model layers communicating processes (CP), communicating processes with time (CPT), bus cycle accurate (BCA), and cycle accurate (CA).

The communicating processes (CP) models are also called as untimed functional models (UTF). They are the architectural models targeted at early functional modeling and verification of systems where timing annotations are not required. They consist of asynchronous concurrent message-passing elements as there is no notion of time at this level just as for

system architectural models. As they do not contain unnecessary implementation details, they can be developed, optimized and rapidly modified to the designers' needs. These models are characterized by high simulation speeds and less complex design models. On the other hand, the *communicating processes with time* (CPT) model is a micro-architectural model containing essential time annotations for behavioral and communication specifications [Ghe05]. Compared to CP models, these CPT models are closer to RTL models. These models focus on the simulation accuracy, architecture analysis and real-time software development. The Open SystemC Initiative (OSCI) <sup>3</sup> has defined the above given modeling levels from the software engineering point of view. CP level is also called as the programmers' view (PV) and CPT level is called as programmers' view with time (PVT).

The bus cycle accurate (BCA) models consider the temporal granularity at the bus transaction levels. The message passing is usually atomic. At bus cycle accurate levels also known as cycle-approximate levels, the actual operations of the bus or IP accesses are present, but the timing between them is not known precisely. In cycle accurate models, the communication information is passed at clock boundaries and exact cycle counts are known. Gate propagation level is the most detailed hardware implementation model at which the timing within the clock period is also known precisely.

Electronic System Level being an established approach for System-on-a-chip (SoC) design can be accomplished through the use of SystemC as an abstract modeling language. SystemC language was developed by OSCI, a not-for-profit organization [SystemC], in 1999. It is a actually a collection library of C++ routines, macros and classes that can be compiled with any conventional C++ compiler. Its working and capabilities are similar to HDLs (VHDL and Verilog) like the simulation of concurrent processes, events, and signals but provides more flexibility, greater expressiveness, different templates, and data types, as well as the full power of the C++ language. It can be considered as a language for high level structure modeling and behavior representation using constructs like communication channels, buses, interfaces, modules and threads. Due to these features, SystemC is often duly associated with ESL design and TLM. It has got a wide variety of application like software development, system-level modeling, architectural exploration, functional verification, high-level synthesis, and performance modeling.

Modules are the basic building blocks of a SystemC design structure. A SystemC model usually consists of several modules that communicate through ports. Modules are represented using two types of C++ functions, methods and threads. Threads are the function calls that can be paused using the wait statement whereas methods run till the end of their execution once triggered or called. SystemC models execute in discrete events of time. Channels are the main communication of SystemC connecting module interfaces. They can be either simple wires or complex communication mechanisms like FIFOs. Modules, ports, interfaces, and Channels together form interface-based design style, where computation and communication can be modeled separately. SystemC also introduces a number of different data types.

### 2.5 Register Transfer Level

Register transfer level (RTL) refers to that level of abstraction at which a circuit is described as synchronous transfers between functional units, such as multipliers and arithmetic-logic units, and register files [Gro02]. The *basic building blocks* of an RTL design are modules constructed from simple gates. These building blocks are comprised of functional units, such as adders and comparators, storage components, such as registers, and data routing components, such as multiplexers. This abstraction level is also referred to as module-level abstraction [Chu06].

<sup>&</sup>lt;sup>3</sup>http://www.systemc.org/home/

Contrary to the gate level representation, RT level *data representation* is more abstract. Ports and data types are used to represent groups of hardware connections and signals respectively. Similarly, the *behavioral description* of a system, to specify the functional operations at this level, generally uses finite state machines (FSMs) to express the data flow. The system state of the FSM describes the internal behavior state of the system at any specific instance of time. The *timing representation* at the RT level is shown by a clock signal input to the storage components like register blocks. These clock signals act as a trigger for the actions in the synchronous modules. Data is manipulated (latched, sampled, read, written *etc.*) on the edge (rising or falling) of these clock signals. In this way, these clocks act as the synchronizing pulse for the system. The clock pulses have frequency limitations by the hardware implementation. Clock signals have to be of long enough durations that they account for the system propagation delays. Thus due to the use of clocks, we do not usually consider the system changes occurring within the clock cycle and the system timing is considered in terms of number of clock cycles.

A digital system design can be described at different levels of abstraction and with variety of view points, depending on the background and knowledge of the designer and requirements of the system. Here comes the role of the hardware description languages (HDLs) which let the designers to accurately model the designs from the structural and behavioral view points, at a desired level of abstraction. This thing gives the system designers an opportunity to focus their efforts on the design and do not mix up the different view points of a design also. This effort also gives a standardized approach to the system design and make various designs compatible with each other. Traditional programming languages are not adequate for modeling digital hardware which also increases the necessity of the role of hardware description languages. The traditional general purpose languages like C follow the sequential process paradigm which helps the programmers to easily formulate a step by step design approach. On the other hand the digital hardware consists of concurrently operating small modules of sequential or combinational circuits. Such sort of design modeling is not possible with general purpose languages.

One of the popular hardware description language that we focus on in our work is VHDL. VHDL stands for VHSIC (Very High Speed Integrated Circuit) HDL. It is used to describe the structure and behavior of a system. It can describe a system at various levels like behavior, data flow, and structure. VHDL system design and programming is usually a top-down design methodology where a system design is modeled at a higher level. Later this model is tested using simulation techniques and then refined to low level synthesizable hardware implementations. A typical VHDL module consists of two major parts: an entity declaration and an architecture description. The entity declaration defines the interface of the module. This interface is visible and available to the other components. The *architecture body* specifies the internal operation or organization of the circuit. VHDL supports "hardware" types (bit, bit\_vector,...), and multi-valued logic types (sd\_logic) through its IEEE library. The statements inside the architecture body are executed as concurrent building blocks (in parallel). An *after* keyword is used to trigger the statement blocks at a particular instance of time relative to the input clock. These VHDL modules (also known as components) once declared and defined, can be instantiated in the architecture body of other modules. Hence, we can have a library of defined components which can be used in our designs as needed. Common VHDL editors/simulators come with a set of such libraries having commonly used digital design components. When instantiating a component in our design, the port map keyword is used to bind the interfaces of the instantiated component to the ports of the component specification. Such a structural description of our design facilitates the hierarchical design of complex systems. VHDL also facilitates us to program sequential statements. Such a code is sometimes also referred to as *behavioral description*. These features are considered as an exception to the VHDL semantics [Chu06]. These statements are encapsulated in a special construct known as

a process. A process can have a sensitivity list, a set of signals, which trigger its execution.

One of the major advantages of programming at the RTL level in languages like VHDL is of program simulation. This helps us to study the functioning of our program (and eventually the hardware) or its functional verification. Testing and verification are studied in chapter 8.

## 2.6 Conclusion

In this chapter we have described the general concepts of ESL design especially in context of different levels of abstraction. We have initially presented the traditional view of design-flow approach used, followed by the focus on new trends like co-simulation and hardware/software partitioning. In the end, we have introduced programming languages for modeling at different abstraction levels. These languages are later utilized while dealing with the behavioral representation of electronic systems (chapter 7).

# Chapter 3

# Model Driven Engineering

#### Contents

| <b>3.1</b> | Intro | oduction                           |

|------------|-------|------------------------------------|

| <b>3.2</b> | Mod   | els and metamodels 22              |

| 3.3        | UM    | L                                  |

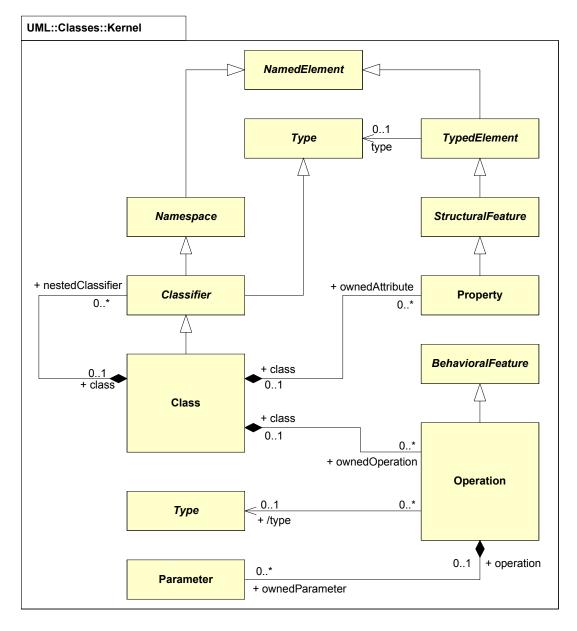

|            | 3.3.1 | UML Classifiers                    |

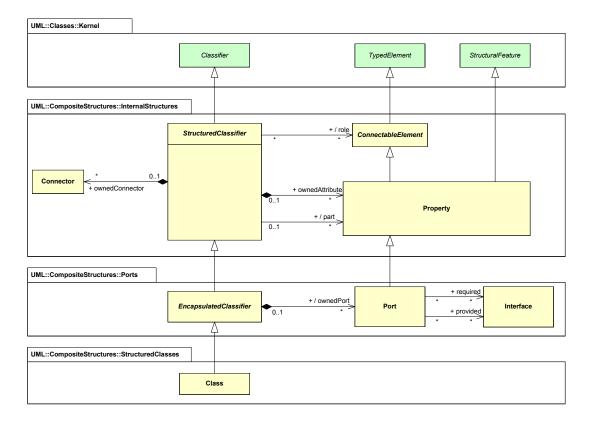

|            | 3.3.2 | UML Structured Classes             |

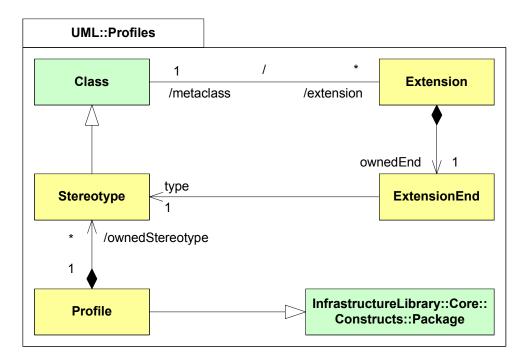

|            | 3.3.3 | UML Profiles                       |

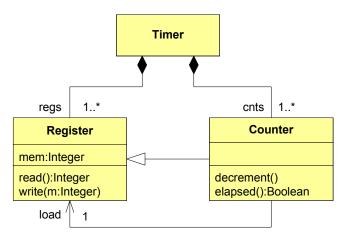

|            | 3.3.4 | Example of UML modeling of a Timer |

| 3.4        | The   | UML Profile for MARTE              |

|            | 3.4.1 | <b>Overview</b>                    |

|            | 3.4.2 | Resources and Allocation           |

|            | 3.4.3 | Time in MARTE                      |

| <b>3.5</b> | Mod   | el to model transformation         |

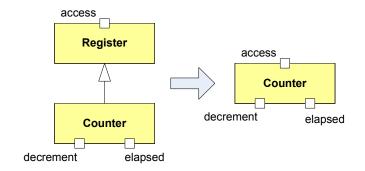

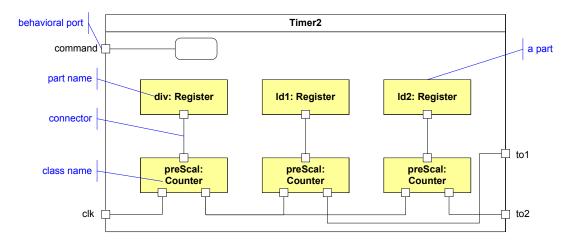

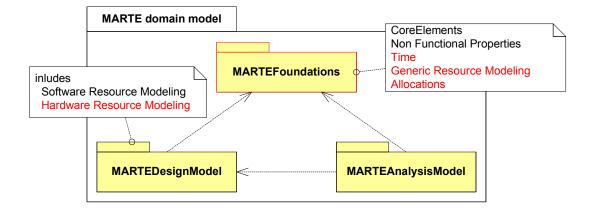

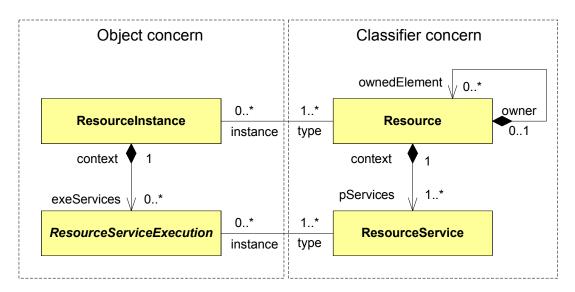

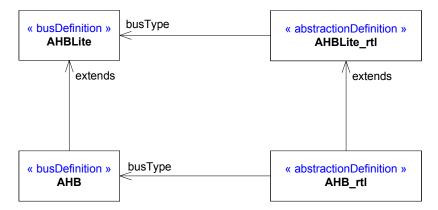

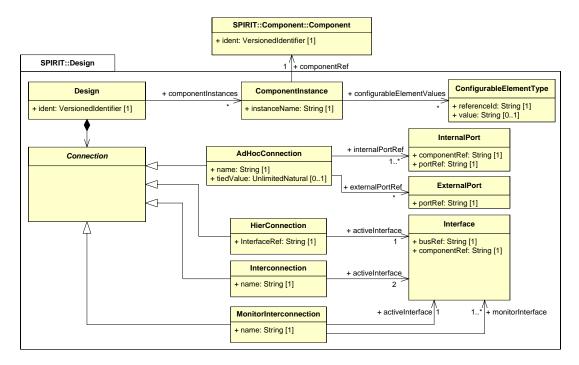

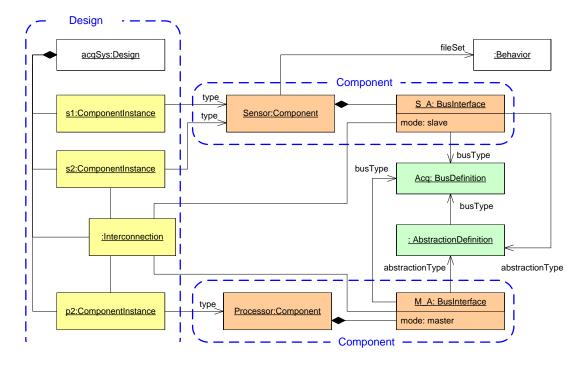

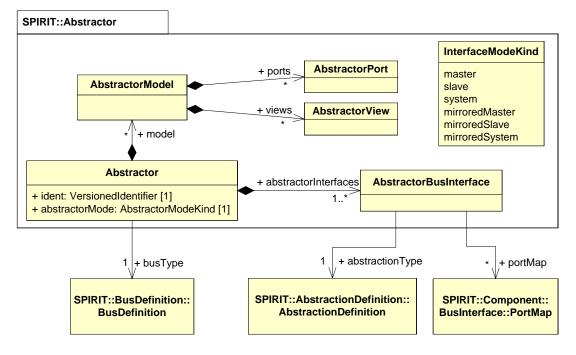

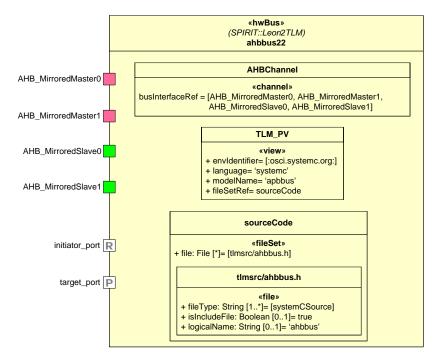

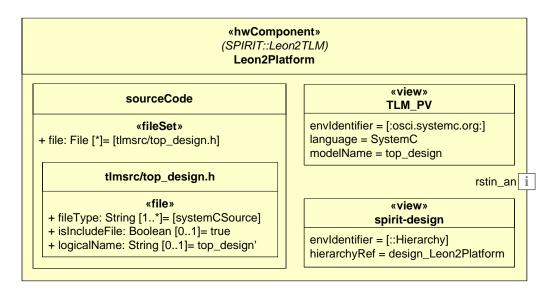

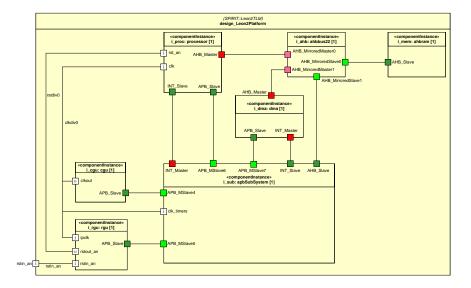

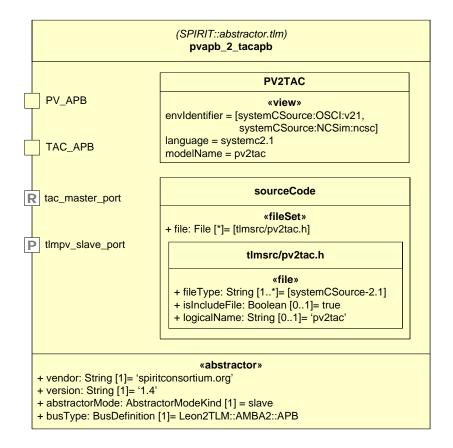

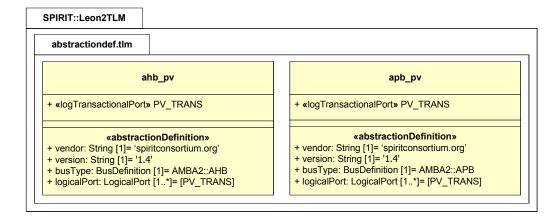

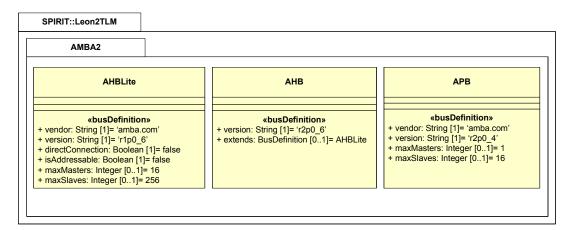

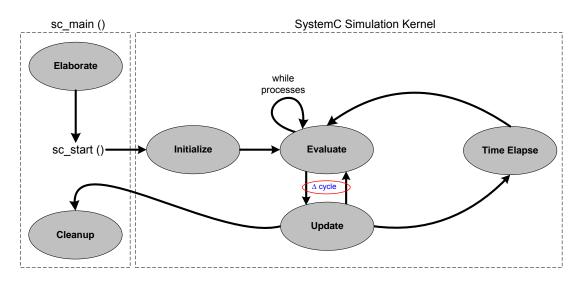

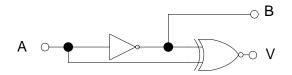

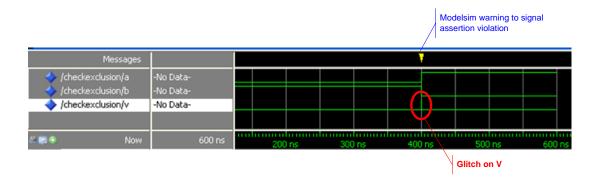

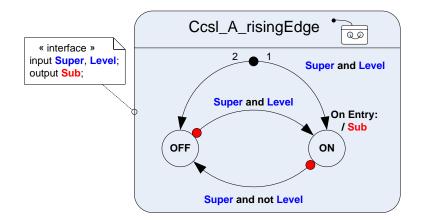

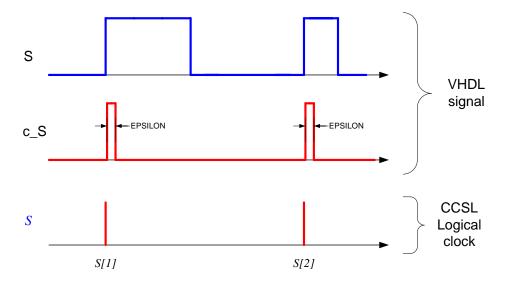

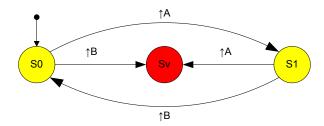

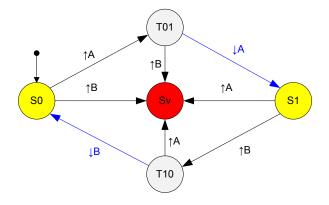

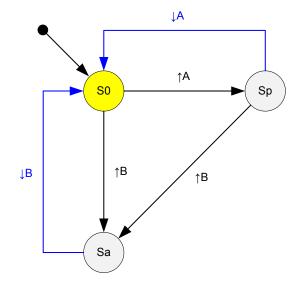

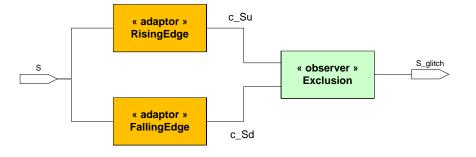

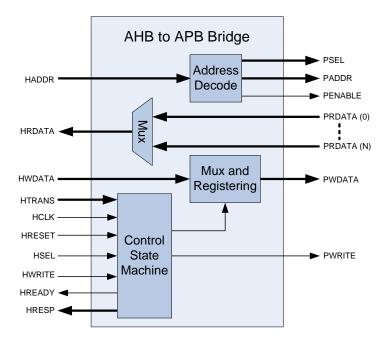

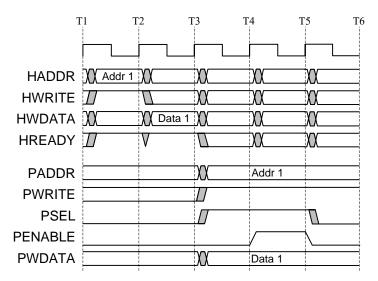

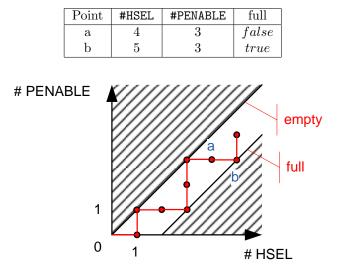

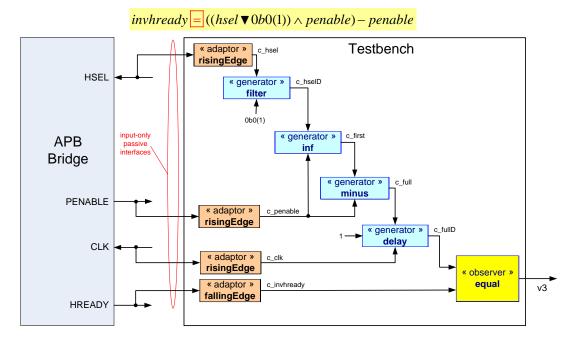

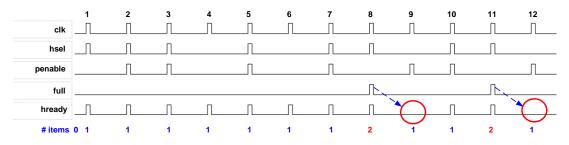

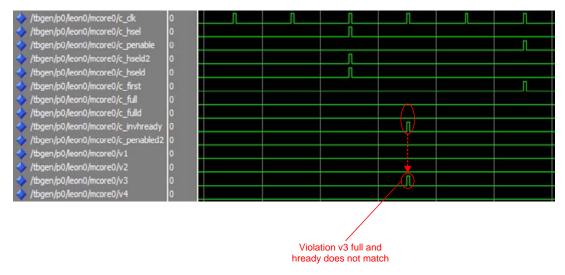

| 3.6        | Con   | clusion                            |