# Développement d'architectures HW/SW tolérantes aux fautes et auto-calibrantes pour les technologies Intégrées 3D

Vladimir Pasca

#### ► To cite this version:

Vladimir Pasca. Développement d'architectures HW/SW tolérantes aux fautes et auto-calibrantes pour les technologies Intégrées 3D. Autre. Université de Grenoble, 2013. Français. NNT: 2013GRENT001. tel-00838677v2

### HAL Id: tel-00838677 https://theses.hal.science/tel-00838677v2

Submitted on 22 Jan 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ DE GRENOBLE

# THÈSE

Pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité: Nanoélectronique et Nanotechnologies Arrêté ministériel: 7 août 2006

Numéro ISBN 978-2-11-129172-0

Présentée par

## Vladimir PASCA

Thèse dirigée par Mme. Lorena ANGHEL et Codirigée par M. Mounir BENABDENBI

Préparée au sein du Laboratoire TIMA Dans l'École Doctorale d'Electronique, Electrotechnique, Automatique et Traitement du Signal

# Développement d'Architectures HW / SW Tolérantes aux Fautes et Auto-calibrantes pour les Technologies Intégrées 3D

Thèse soutenue publiquement le **11 Janvier 2013**, devant le jury composé de:

#### M. Ian O'CONNOR

Professeur, Ecole Centrale Lyon (Président) **M. Patrick GIRARD** Directeur de Recherche CNRS (Rapporteur) **M. Andreas STEININGER** Professeur, TU Wien (Rapporteur) **M. Pascal VIVET** Chercheur CEA-Leti (Examinateur) **Mme. Lorena ANGHEL** Professeur, INP Grenoble (Directeur) **M. Mounir BENABDENBI** Maître de Conférence, INP Grenoble (Co-encadrant)

# Acknowledgements

It is always difficult to express your gratitude and acknowledgement to many great people that have provided me valuable advices during my PhD. My first thoughts go to my supervisor Professor Lorena Anghel, whose guidance from the first internships in 2006 until the last days of my PhD helped me both at a professional and personal level. I would like to thank her for the excellent guidance, great suggestions, neverending patience, support and encouragement. My deepest gratitude also goes to my co-supervisor, Professor Mounir Benabdenbi. His suggestions, patience and guidance made my work easier and helped it come to completion. My gratitude also goes to Dr. Michael Nicolaidis, the leader of the ARIS group in TIMA. I cannot even find the words to properly express the great impact his wonderful advices and guidance had on my work.

I thank Professor Ian O'Connor for accepting to be the president of the jury and for the numerous scientific exchanges we had during our collaboration in the 3DIM3 project. I would like to acknowledge the great work of Dr. Patrick Girard and Professor Andreas Steininger in reviewing my work. Their great researcher experience, patience and understanding provided great suggestions that helped improve the quality of this manuscript. I also thank Dr. Pascal Vivet for accepting to be part of the jury. I value his comments on my work and his deep understanding on difference challenges of 3D integration, which pointed me to very interesting directions.

I would also like to express my gratitude to M. Marcello Coppolla from ST Grenoble for allowing me to validate most of my work in a realistic environment using the Spidergon STNoC platform. I thank Dr. Riccardo Locatelli and M. Giuseppe Maruccia for their helpful support during the time I spent in the ST group.

My work would have been very difficult without the constant help and support from my colleagues in TIMA. First, I would like to acknowledge Claudia Rusu for her help and suggestions in the first part of my thesis. No work on NoCs would have been possible without the many fruitful discussions I had with Fabien Chaix, Saif-Ur Rheman and Gilles Bizot. I also thank Hai Yu, Diarga Fall, Wassim Mansour, Thieri Bonnoît, Yi Gang, and Panagiota Papavramidou for their help, support and suggestions. Finally, I would like to acknowledge Salma Bergaoui for her help and advices, and for taking the awful task of correcting the French summary of my thesis.

Finally, I thank my family and fiancée for their support during these years away from them. None of this would have been possible without their invaluable advices.

# Table of Contents

| INTRODUCTION                                                          |    |

|-----------------------------------------------------------------------|----|

| 3D INTEGRATION AND NETWORKS-ON-CHIP                                   |    |

| 2.1 3D INTEGRATION USING TSVs                                         |    |

| 2.2 CHALLENGES OF TSV-BASED 3D INTEGRATED SYSTEMS                     |    |

| 2.2.1 Testing TSV-based 3D ICs                                        |    |

| 2.2.2 Testing Through-Silicon-Vias                                    |    |

| 2.2.2.1 Boundary Scan                                                 |    |

| 2.2.2.2 Interconnect Built-In Self-Test                               |    |

| 2.2.3 Reliability and Yield                                           |    |

| 2.2.3.1 Faults classification                                         |    |

| 2.2.3.2 Manufacturing defects in 3D ICs                               |    |

| 2.2.3.3 Reliability in 3D ICs<br>2.3 NETWORKS-ON-CHIP IN 3D SYSTEMS   |    |

| 2.3.1 From 2D NoCs to 3D NoCs                                         |    |

| 2.3.2 3D NoC Design                                                   |    |

| 2.3.3 NoC Testing                                                     |    |

| 2.3.4 Reliability and Yield                                           |    |

| 2.3.4.1 Fault-tolerant routing                                        |    |

| 2.3.4.2 Link repair                                                   |    |

| 2.3.4.3 Signal encoding                                               |    |

| 2.3.4.4 Robust router architectures                                   |    |

| 2.3.4.5 Extensions to 3D NoCs                                         |    |

| 2.4 CONCLUSION                                                        |    |

| TESTING THROUGH-SILICON-VIAS IN 3D NOC LINKS                          |    |

| 3.1 3D NOC INTER-DIE INTERCONNECT BIST                                | 39 |

| 3.1.1 Testing TSV faults and defects                                  |    |

| 3.1.2 Interconnect BIST architecture                                  |    |

| 3.2 K <sup>TH</sup> -AGGRESSOR FAULT MODEL FOR TSVs                   |    |

| 3.2.1 Defining aggressor orders                                       |    |

| 3.2.2 TSV partitioning in victim sets                                 |    |

| 3.3 IMPLEMENTATION OF KAF-BASED IBIST                                 |    |

| 3.3.1 Generating KAF Test Patterns                                    |    |

| 3.3.2 Configurable KAF-based Test Patterns                            |    |

| 3.4 EXPERIMENTAL RESULTS                                              |    |

| <i>3.4.1 Test duration</i>                                            |    |

| 3.4.2 KAF-based IBIST area evaluations                                |    |

| 3.4.2.1 IBIST                                                         |    |

| 3.4.2.2 Configurable IBIST                                            |    |

| 3.5 CONCLUSION                                                        |    |

| ERROR RESILIENCE IN 3D NETWORKS-ON-CHIP                               |    |

| 4.1 DATA LINK ERROR RESILIENCE FOR TRANSIENT FAULTS                   |    |

| 4.1.1 Forward Error Correction                                        |    |

| 4.1.2 Automatic Retransmission Query                                  |    |

| 4.1.3 Hybrid Error Correction with Retransmission                     |    |

| 4.1.4 Link protection strategies in 3D NoCs                           |    |

| 4.2 DATA LINK ERROR RESILIENCE FOR PERMANENT FAULTS                   |    |

| 4.2.1 TSV Spare-and-Replace (TSV-SnR)                                 |    |

| 4.2.1.1 TSV-SnR Architecture                                          |    |

| 4.2.1.2 Optimization of TSV-SnR costs                                 |    |

| 4.2.2 Configurable Serial Fault-Tolerant Links (CSL)                  |    |

| 4.2.2.1 CSL Architecture                                              |    |

| 4.2.2.2 Off-chip repair signal computation                            |    |

| 4.2.2.3 Signal Grouping                                               |    |

| 4.2.3 Interconnect Built-In Self-Test, Self-Repair and Adaptive Self- |    |

| 4.2.3.1 IBIRAS Architecture                                           |    |

| 4.2.3.2 Self-repair circuitry                                         |    |

| 4.2.3.3 Adaptive serialization circuitry                              |    |

| Vladimir Pasca                                                                               | 6  |

|----------------------------------------------------------------------------------------------|----|

| 4.3 NETWORK ERROR RESILIENCE FOR TRANSIENT FAULTS                                            | 75 |

| 4.3.1 Network-level Forward Error Correction                                                 |    |

| 4.4 NETWORK ERROR RESILIENCE FOR TSV PERMANENT FAULTS                                        | 77 |

| 4.4.1 TSV-Fault Tolerant Routing in 3D NoCs                                                  |    |

| 4.4.2 Master Node Selection                                                                  |    |

| 4.5 MULTY-LAYER ERROR RESILIENCE FOR 3D NOCS                                                 |    |

| 4.5.1 Multi-layer TSV yield improvement                                                      |    |

| 4.5.2 Multi-layer reliability improvement                                                    |    |

| 4.6 CONCLUSION                                                                               |    |

| EXPERIMENTAL EVALUATIONS OF ERROR RESILIENCE STRATEGIES                                      |    |

| 5.1 TSV Permanent Faults in 3D NoCs                                                          | 87 |

| 5.1.1 Data link yield improvement strategies                                                 |    |

| 5.1.1.1 TSV Spare-and-Repair                                                                 |    |

| 5.1.1.2 Configurable Serial Links                                                            |    |

| 5.1.1.3 Inter-die link repair trade-offs                                                     |    |

| 5.1.2 Network-level fault-tolerant routing algorithm                                         |    |

| 5.1.3 Multi-layer TSV yield improvement                                                      |    |

| 5.1.3.1 Area overheads                                                                       |    |

| 5.1.3.2 Impact on network latency                                                            |    |

| 5.1.4 In-field TSV failures                                                                  |    |

| 5.1.5 Remarks on mitigating TSV permanent faults                                             |    |

| 5.2 TRANSIENT TSV FAULTS IN 3D NOCS                                                          |    |

| 5.2.1 Data link error resilience                                                             |    |

| 5.2.1.1 Reliability assessments                                                              |    |

| 5.2.1.2 Selective inter-die link protection                                                  |    |

| <ul><li>5.2.1.3 Area and power overheads</li><li>5.2.1.4 Impact on network latency</li></ul> |    |

| 5.2.1.4 Impact on network latency         5.2.2 Network-level error resilience               |    |

| 5.2.2 Network-tevel error restlience                                                         |    |

| 5.2.2.1 Kendolity assessments                                                                |    |

| 5.2.3 Multi-layer error resilience                                                           |    |

| 5.2.3.1 Reliability assessments                                                              |    |

| 5.2.3.2 Area and power overheads                                                             |    |

| 5.2.3.3 Impact on network latency                                                            |    |

| 5.2.4 Remarks on mitigating transient faults                                                 |    |

| 5.3 CONCLUSIONS                                                                              |    |

| 3D NOC ERROR RESILIENCE EXPLORATION                                                          |    |

| 6.1 ERROR RESILIENCE EXPLORATION FOR 3D NOCS                                                 |    |

| 6.2 THE ERX TOOL                                                                             |    |

| 6.2.1 Error resilience scheme selection                                                      |    |

| 6.2.2 ERX network average latency analytic evaluation                                        |    |

| 6.2.3 ERX area evaluation                                                                    |    |

| 6.3 System-level evaluation                                                                  |    |

| 6.3.1 3D System Architecture                                                                 |    |

| 6.3.2 Error resilient configurations                                                         |    |

| 6.3.2.1 First 3D MPSoC configuration                                                         |    |

| 6.3.2.2 Second 3D MPSoC configuration                                                        |    |

| 6.3.3 Performance evaluations                                                                |    |

| 6.4 LIMITATIONS OF ERROR RESILIENCE EXPLORATION                                              |    |

| 6.5 CONCLUSION                                                                               |    |

| CONCLUSION AND FUTURE WORK                                                                   |    |

| APPENDIX                                                                                     |    |

|                                                                                              |    |

# List of Figures

| FIGURE I-1                 | MANY-CORE SYSTEM COMPLEXITY TRENDS [ITRS07]                                                                                | 13         |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------|------------|

| FIGURE I-2                 | TRENDS OF INTERCONNECT AND TRANSISTOR DELAYS FOR SUB-MICRON TECHNOLOGIES [ITRS05]                                          |            |

| FIGURE I-3                 | ABSTRACTION LAYERS OF NOC-BASED MPSOCS [BDM02]                                                                             |            |

| FIGURE II-1                | TSV-BASED STACKED 3D INTEGRATION (A) [LU03] REDUCES THE AVERAGE GLOBAL INTERCONNECT                                        |            |

|                            | в)                                                                                                                         | 20         |

| FIGURE II-2                | SUMMARY OF 3D CHIP MANUFACTURING STEPS (SOURCE: YOLE DEVELOPMENT)                                                          |            |

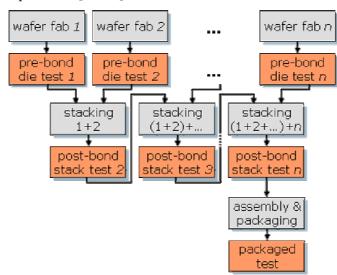

| FIGURE II-3                | STACKED 3D CHIP TEST FLOW [MZ09]                                                                                           |            |

| FIGURE II-4                | EXAMPLE OF A SIMPLE 3D TEST ACESS MECHANISM [MCK12]                                                                        | 23         |

| FIGURE II-5                | BOUNDARY SCAN TEST FOR REGULAR TSVs TSV <sub>1</sub> -TSV <sub>N</sub>                                                     |            |

| FIGURE II-6                | INTERCONNECT BUILT-IN SELF-TEST FOR N REGULAR TSVs                                                                         |            |

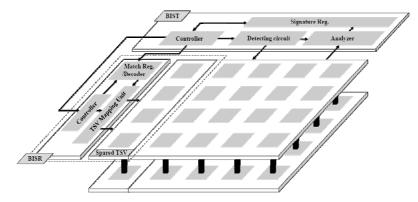

| FIGURE II-7                | BUILT-IN SELF-TEST AND REPAIR FOR THROUGH-SILICON-VIAS [HHH10]                                                             | 26         |

| FIGURE II-8                | POST-BOND TSV BIST FOR BIDIRECTIONAL TSVS SET AS INBOUD AND OUTBOUND FOR A GIVEN DIE                                       |            |

| [HLC11]                    |                                                                                                                            |            |

| FIGURE II-9                | TSV CHECK AND REPAIR STRATEGY FOR 4 SIGNALS A,B, C, D [KCH10]                                                              | 29         |

| FIGURE II-10               | IP BLOCKS WITH INITIATOR AND TARGET INTERFACES CONNECTED BY A NOC                                                          | 31         |

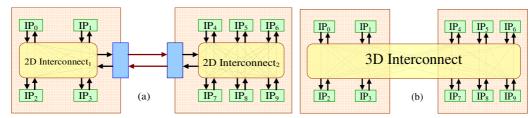

| FIGURE II-11               | INTERCONNECT FABRIC STRATEGIES FOR STACKED 3D SOCS                                                                         |            |

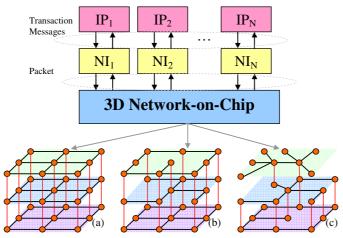

| FIGURE II-12               | MPSoC IMPLEMENTED USING 3D NoCs                                                                                            |            |

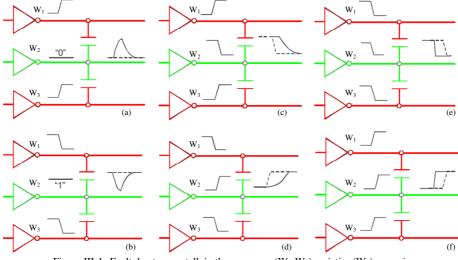

| FIGURE III-1               | FAULT DUE TO CROSSTALK IN THE AGGRESSOR $(W_1-W_3)$ – VECTIM $(W_2)$ SCENARIO                                              | 40         |

| FIGURE III-2               | INTER-DIE LINK INTERCONNECT BUILT-IN SELF-TEST (IBIST)                                                                     |            |

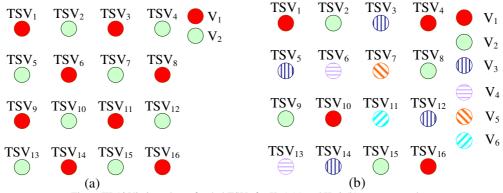

| FIGURE III-3               | 1 <sup>st</sup> , 2 <sup>nd</sup> and 3 <sup>rd</sup> aggressor sets for regular (A) and non-uniform (B) TSV distributions |            |

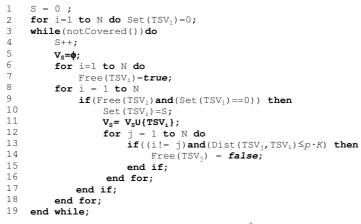

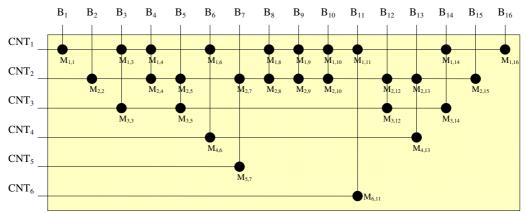

| FIGURE III-4               | TSV partitioning algorithm using the $K^{\text{th}}$ order aggressors for N TSVs                                           | 43         |

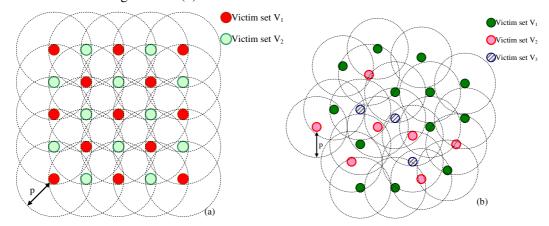

| FIGURE III-5               | The victim sets for $1^{st}$ order aggressors in regular (a) and non-uniform (b) $\mathrm{TSV}$                            |            |

| DISTRIBU                   | TIONS                                                                                                                      |            |

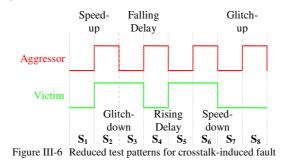

| FIGURE III-6               | REDUCED TEST PATTERNS FOR CROSSTALK-INDUCED FAULT                                                                          |            |

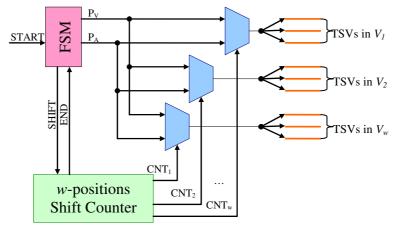

| FIGURE III-7               | TRAFFIC PATTERN GENERATOR FOR KAF-BASED BIST                                                                               |            |

| FIGURE III-8               | FSM FOR GENERATING AGGRESSOR / VICTIM TEST SIGNALS                                                                         |            |

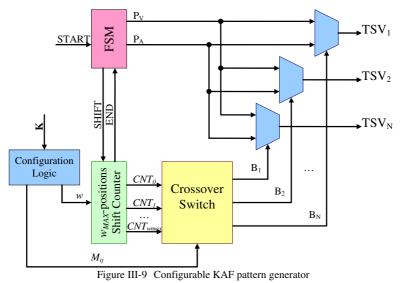

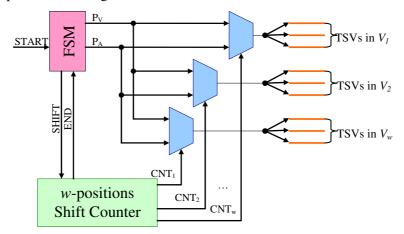

| FIGURE III-9               | CONFIGURABLE KAF PATTERN GENERATOR                                                                                         |            |

| FIGURE III-10              | VICTIM SUBSETS FOR $4x4$ TSVs for K=1 (A) and K=2 (B) aggressor orders                                                     | 47         |

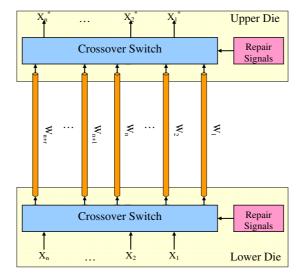

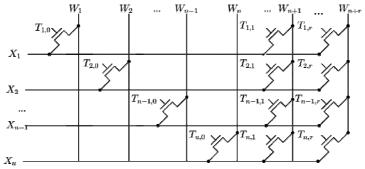

| FIGURE III-11              | CROSSOVER SWITCH STRUCTURE FOR 4X4 TSVS HAVING K=1 (W=2) AND K=2 (W=6) AGGRESSOR                                           |            |

| ORDERS                     | 48                                                                                                                         |            |

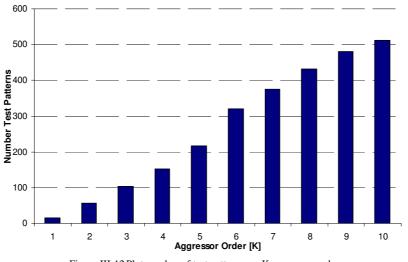

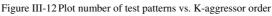

| FIGURE III-12              | PLOT NUMBER OF TEST PATTERNS VS. K-AGGRESSOR ORDER                                                                         |            |

| FIGURE III-13              | NUMBER OF TEST PATTERNS VS. K-AGGRESSOR ORDER                                                                              | 50         |

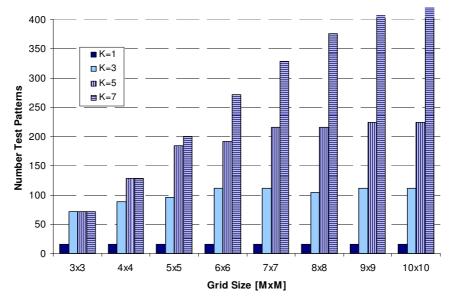

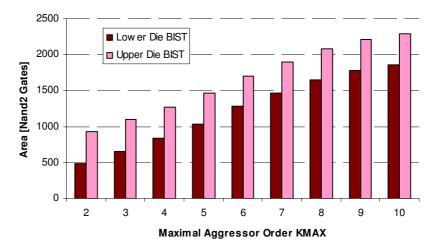

| FIGURE III-14              | AREA OF TSV INTERCONNECT BIST COMPONENTS FOR AN 8x8 TSV ARRAY WHEN DIFFERENT K-                                            | <b>~</b> 1 |

|                            | OR ORDERS ARE CONSIDERED                                                                                                   | 51         |

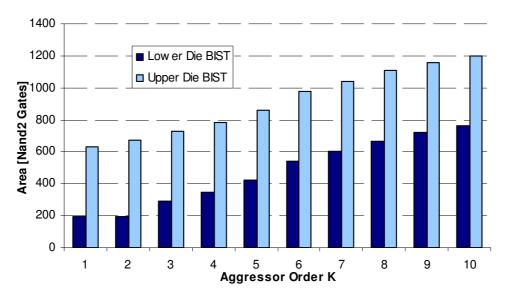

| FIGURE III-15              | THE KAF-BASED TSV BIST AREA OF THE LOWER AND UPPER DIE COMPONENTS FOR DIFFERET TSV                                         | 51         |

|                            | ZES AND AGGRESSOR ORDERS                                                                                                   |            |

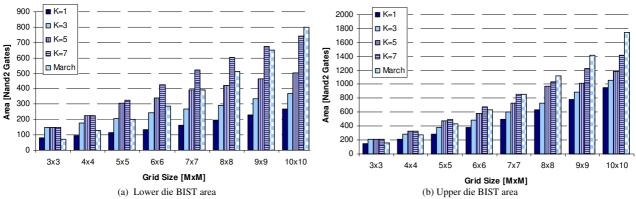

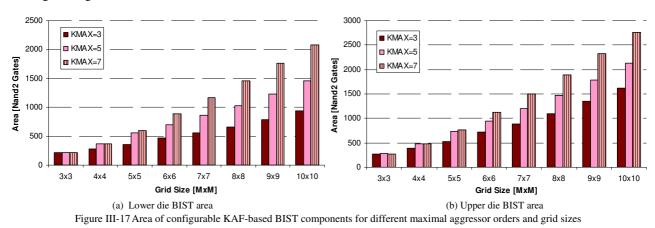

| FIGURE III-16              | AREA OF THE CONFIGURABLE KAF-BASED BIST COMPONENT FOR DIFFERENT MAXIMAL AGGRESSOF                                          |            |

| FIGURE III-17              | MAX<br>Area of configurable KAF-based BIST components for different maximal aggressor                                      | 32         |

|                            | AREA OF CONFIGURABLE KAF-BASED DIST COMPONENTS FOR DIFFERENT MAXIMAL AGGRESSOR                                             | 52         |

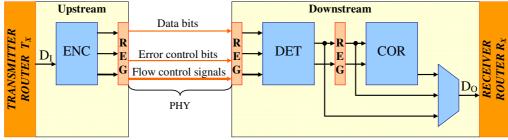

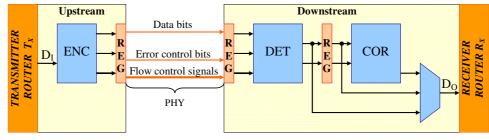

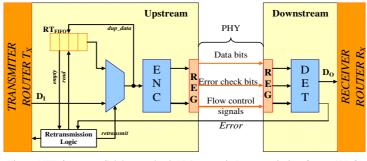

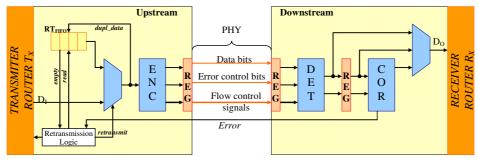

| FIGURE IV-1                | FORWARD ERROR CORRECTION (FEC) SCHEME                                                                                      |            |

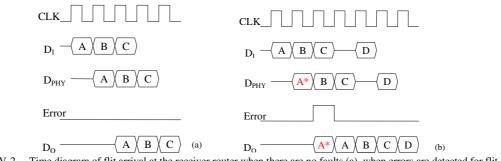

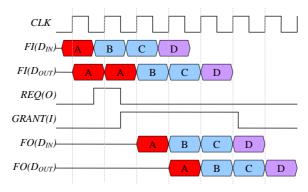

| FIGURE IV-1<br>FIGURE IV-2 | TIME DIAGRAM OF FLIT ARRIVAL AT THE RECEIVER ROUTER WHEN THERE ARE NO FAULTS (A), WHEN                                     |            |

|                            | RE DETECTED FOR FLIT A (B)                                                                                                 |            |

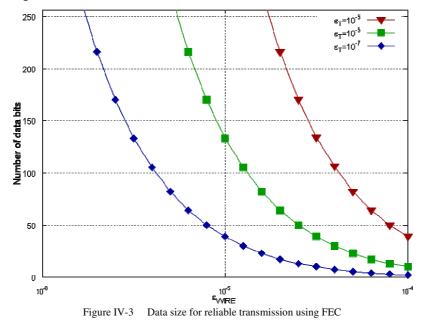

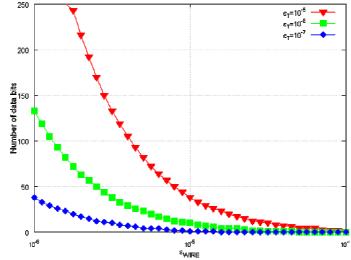

| FIGURE IV-3                | DATA SIZE FOR RELIABLE TRANSMISSION USING FEC                                                                              | 50         |

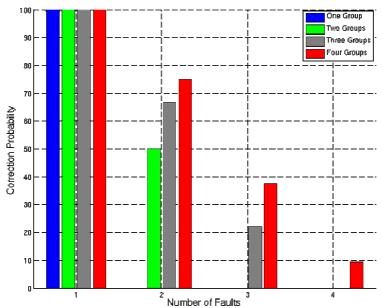

| FIGURE IV-5                | CORRECTION PROBABILITIES OF INTERLEAVED HAMMING SEC CODES FOR 32 DATA BITS                                                 |            |

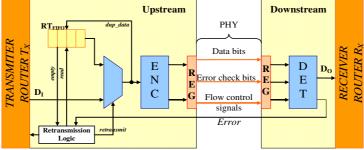

| FIGURE IV-5                | GO-BACK-N AUTOMATIC RETRANSMISSION QUERY (ARQ) SCHEME                                                                      |            |

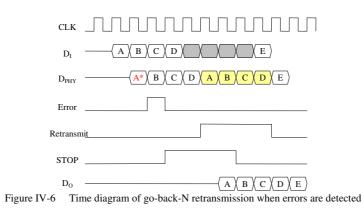

| FIGURE IV-5                | TIME DIAGRAM OF GO-BACK-N RETRANSMISSION WHEN ERRORS ARE DETECTED                                                          |            |

| FIGURE IV-7                | HYBRID ERROR CORRECTION AND RETRASSISSION WHEN ERRORS ARE DETECTED                                                         |            |

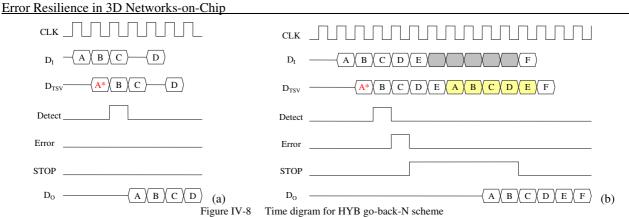

| FIGURE IV-8                | TIME DIGRAM FOR HYB GO-BACK-N SCHEME                                                                                       |            |

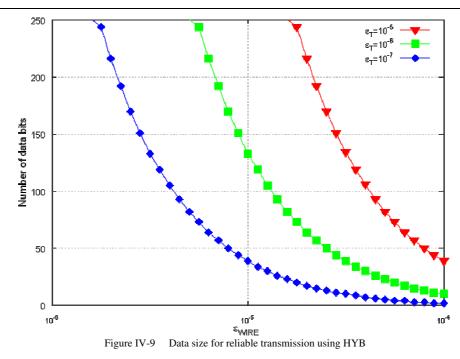

| FIGURE IV-9                | DATA SIZE FOR RELIABLE TRANSMISSION USING HYB                                                                              |            |

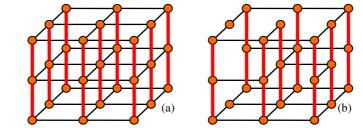

| FIGURE IV-10               | 3D NOCS WITH REGULAR (A) AND QUASI-REGULAR (B) TOPOLOGIES USING INTER-DIE PROTECTED LI                                     |            |

| 1.001217 10                | 63                                                                                                                         |            |

| FIGURE IV-11               | REPAIR FABRIC FOR <i>N</i> REGULAR TSVS AND <i>R</i> SPARES                                                                | 64         |

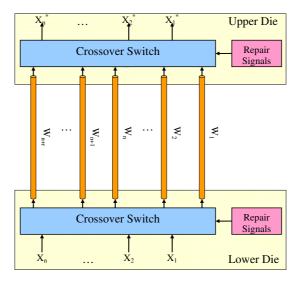

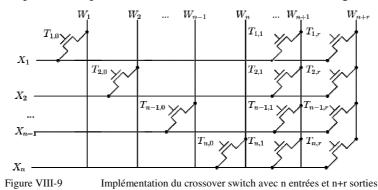

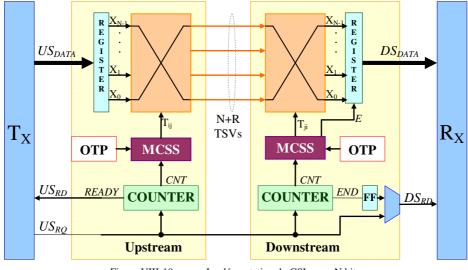

| FIGURE IV-12               | SPARE-AND-REPLACE CROSSOVER SWITCH WITH <i>N</i> INPUTS AND <i>N</i> + <i>R</i> OUTPUTS                                    |            |

| FIGURE IV-13               | OPTIMAL SPARE-AND-REPLACE CONFIGURATION PROCESS                                                                            |            |

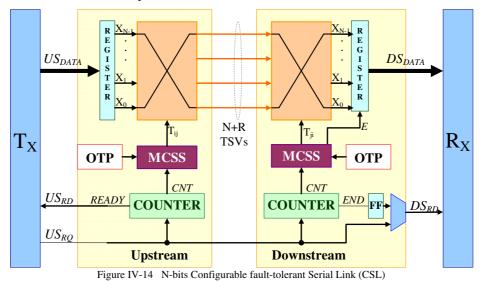

| FIGURE IV-14               | N-BITS CONFIGURABLE FAULT-TOLERANT SERIAL LINK (CSL)                                                                       |            |

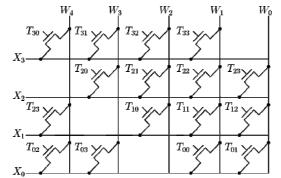

| FIGURE IV-15                 | 4-INPUTS AND 5-OUTPUTS UPSTREAM CROSSOVER SWITCH WITH THE CORRESPONDING CONTROL                                                             |     |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

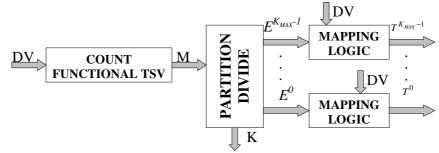

| SIGNALS<br>FIGURE IV-16      | 68 Computational deocks used to determine the number of transmission over $K$ the matrix                                                    | υw  |

|                              | COMPUTATIONAL BLOCKS USED TO DETERMINE THE NUMBER OF TRANSMISSION CYCLE K, THE MATE SIGNALS T, AND THE DOWNSTREAM REGISTER ENABLE SIGNALS E |     |

| FIGURE IV-17                 | CSL CONTROL SIGNALS FOR THE TWO-CYCLE TRANSMISSION OF 4 DATA BITS ON 3 FUNCTIONAL TSV                                                       |     |

|                              | ROSSOVER SWITCH AND FF ENABLE SIGNALS $T_0$ and $E_0$ for the first cycle and (b) the crossover                                             | 5.  |

|                              | ND FF ENABLE SIGNALS $T_1$ and $E_1$ for the second transition cycle                                                                        | 70  |

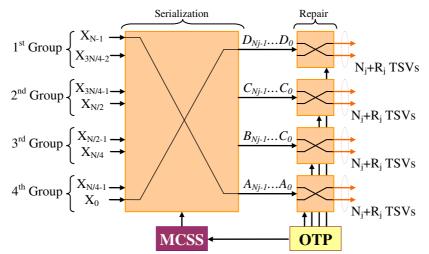

| FIGURE IV-18                 | LOGICAL DECOMPOSITION OF THE UPSTREAM CROSSOVER SWITCH FOR CSLS WITH 4 GROUPS                                                               |     |

| FIGURE IV-19                 | AREA OPTIMIZATION PROCESS FOR CSLS                                                                                                          |     |

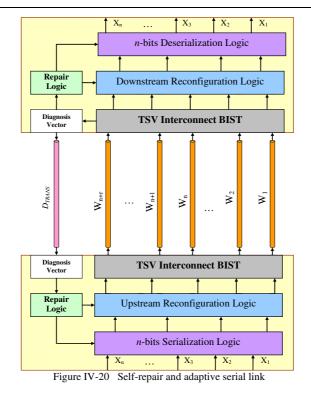

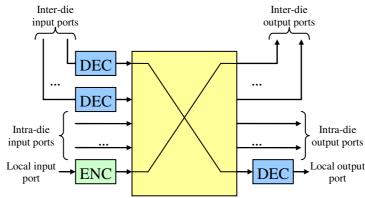

| FIGURE IV-20                 | Self-repair and adaptive serial link                                                                                                        | 72  |

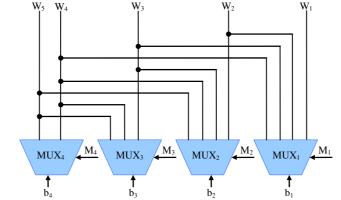

| FIGURE IV-21                 | MUX IMPLEMENTATION OF THE CROSSOVER SWITCH IN THE RECONFIGURATION LOGIC                                                                     | 73  |

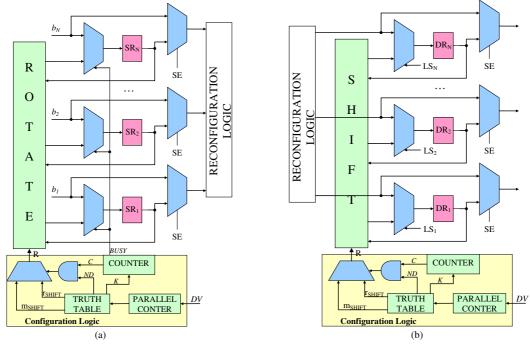

| FIGURE IV-22                 | <i>N</i> -BIT SERIALIZATION (A) AND DESERIALIZATION (B) MODULES WITHOUT EXTRA ROTATE CYCLE                                                  |     |

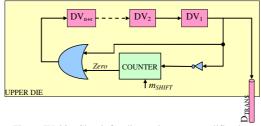

| FIGURE IV-23                 | CIRCUIT FOR DIAGNOSIS VECTOR MODIFICATION                                                                                                   |     |

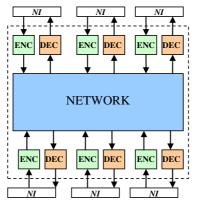

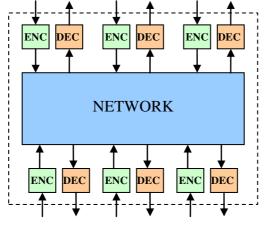

| FIGURE IV-24                 | NETWORK-LEVEL FORWARD ERROR CORRECTION                                                                                                      |     |

| FIGURE IV-25                 | NUMBER OF DATA BITS THAT CAN BE RELIABLY TRANSMITTED OVER A 10-HOPS PATH WITH A ROUTE                                                       |     |

|                              | $ATE E_{ROUTER} = 10^{-4} \dots$                                                                                                            |     |

| FIGURE IV-26                 | TSV-FAULT-TOLERANT ROUTING ALGORITHM IN 3D MESHES                                                                                           |     |

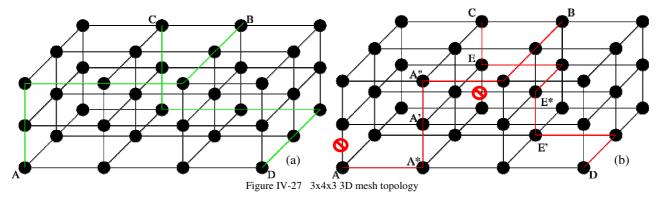

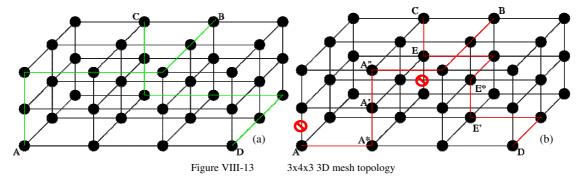

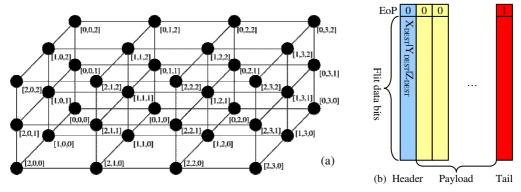

| FIGURE IV-27                 | 3x4x3 3D MESH TOPOLOGY                                                                                                                      |     |

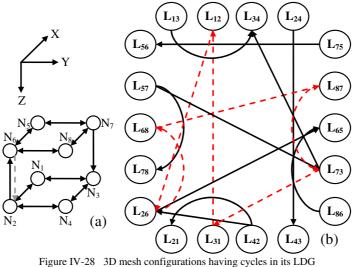

| FIGURE IV-28                 | 3D MESH CONFIGURATIONS HAVING CYCLES IN ITS LDG                                                                                             |     |

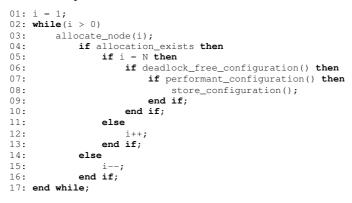

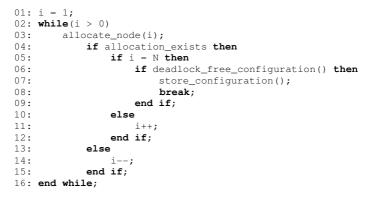

| FIGURE IV-29                 | MASTER NODE SELECTION ALGORITHM<br>FAST MASTER NODE SELECTION ALGORITHM                                                                     |     |

| FIGURE IV-30<br>FIGURE IV-31 | NOC-BASED 3D MPSoC CONFIGURATION PROCESS                                                                                                    |     |

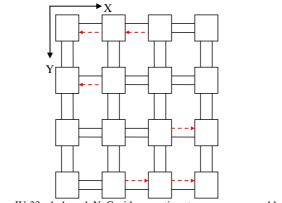

| FIGURE IV-31<br>FIGURE IV-32 | NOC-BASED 5D WIF SOC CONFIGURATION PROCESS                                                                                                  |     |

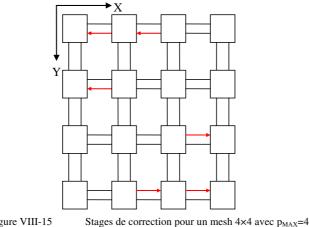

| FIGURE IV-32<br>FIGURE IV-33 | 4×4 MESH NOC WITH CORRECTION STAGES EVERY P <sub>MAX</sub> =4 HOP                                                                           |     |

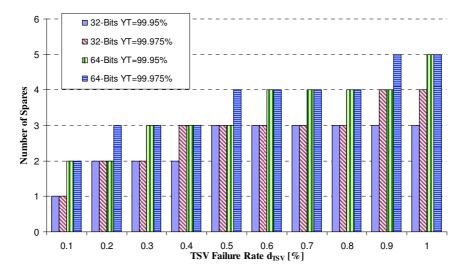

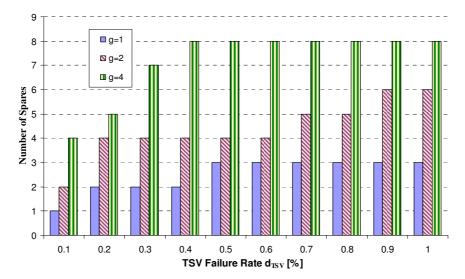

| FIGURE V-1                   | NUMBER OF SPARES FOR 32-BITS AND 64-BITS INTER-DIE LINKS                                                                                    |     |

| FIGURE V-1                   | NUMBER OF STARES FOR 32-BITS AND 04-BITS INTER-DIE EINKS                                                                                    |     |

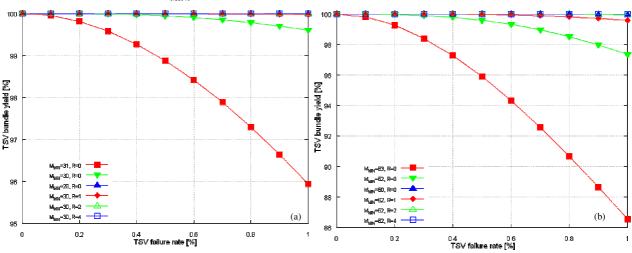

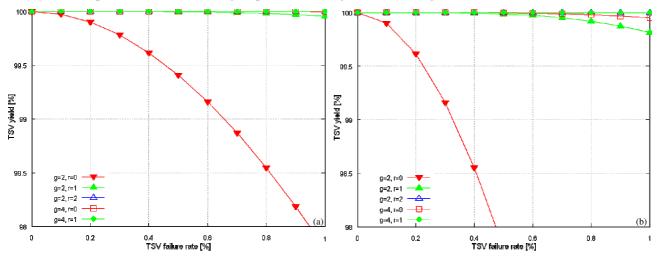

| FIGURE V-3                   | TSV YIELD FOR 32-BITS (A) AND 64-BITS (B) LINKS USING CSL.                                                                                  |     |

| FIGURE V-4                   | TSV YIELD FOR 32-BITS (A) AND 64-BITS (B) GROUPED CSLS                                                                                      |     |

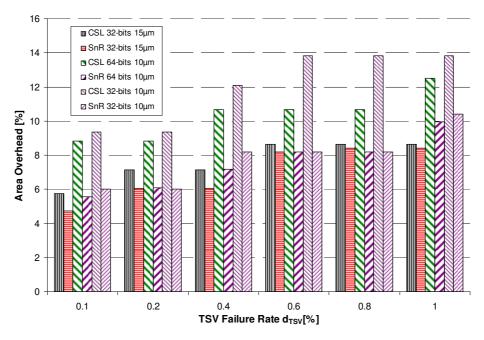

| FIGURE V-5                   | SEVEN-PORT ROUTER AREA OVERHEADS FOR DIFFERENT TSV-SNR AND CSL CONFIGURATIONS                                                               |     |

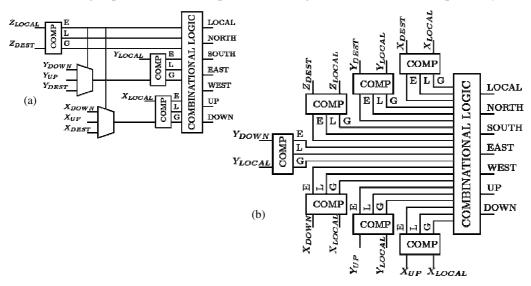

| FIGURE V-6                   | LOW-AREA (A) AND HIGH-SPEED(B) IMPLEMENTATIONS OF ZYX-BASED TSV-FTR                                                                         |     |

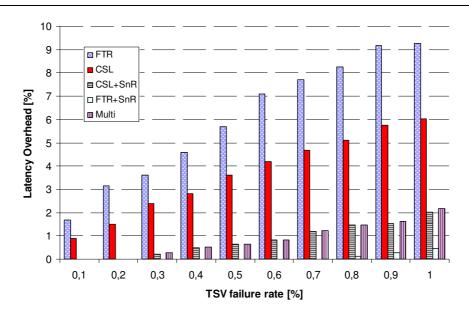

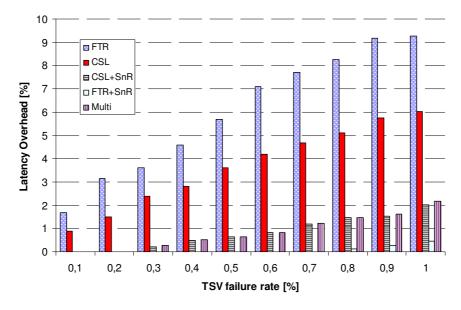

| FIGURE V-7                   | LATENCY OVERHEAD FOR 5x5x4 MESH TOPOLOGY USING DIFFERENT STRATEGIES                                                                         |     |

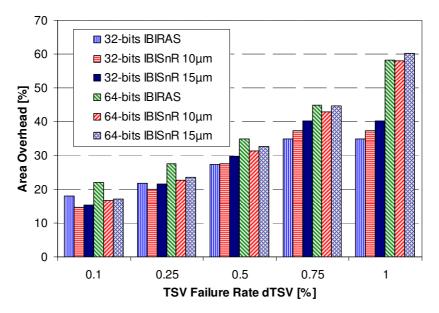

| FIGURE V-8                   | AREA OVERHEADS FOR ON-CHIP SPARE-BASED (IBISNR) AND SERIALIZATION-BASED (IBIRAS) REPAIR                                                     |     |

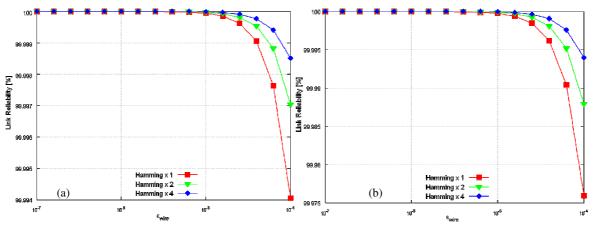

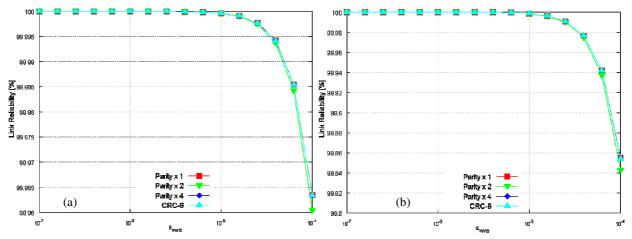

| FIGURE V-9                   | Link-component of 12-hops path reliability for $32$ (a) and $64$ (b) bits FEC-protected links .                                             | 103 |

| FIGURE V-10                  | LINK-COMPONENT OF 12-HOPS PATH RELIABILITY FOR $32$ (A) and $64$ (b) bits ARQ-protected line 105                                            | ٢S  |

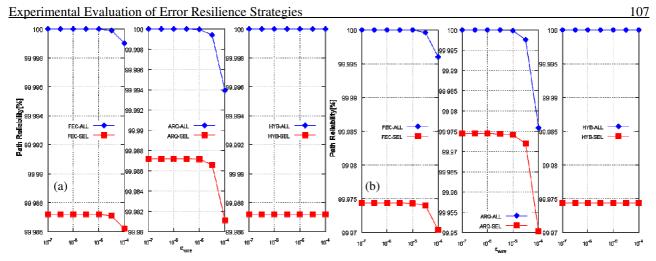

| FIGURE V-11                  | PATH RELIABILITY WITH ERROR RESILIENT INTER-DIE LINKS (I.E. SELECTIVE INTER-DIE PROTECTION                                                  |     |

| ,                            | D FULL-LINK PROTECTION (ALL) FOR AN INTRA-DIE WIRE FAILURE RATE OF $E_{WIRE} = 10^{-6}$                                                     |     |

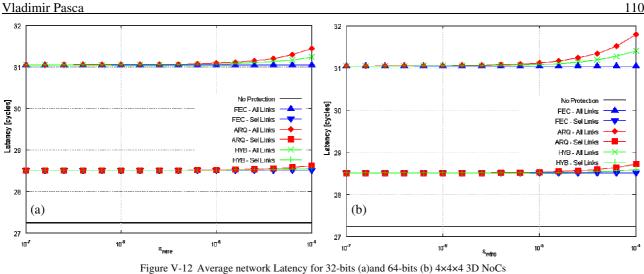

| FIGURE V-12                  | AVERAGE NETWORK LATENCY FOR 32-BITS (A)AND 64-BITS (B) 4×4×4 3D NoCs                                                                        |     |

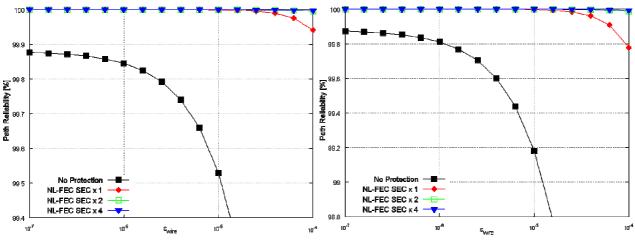

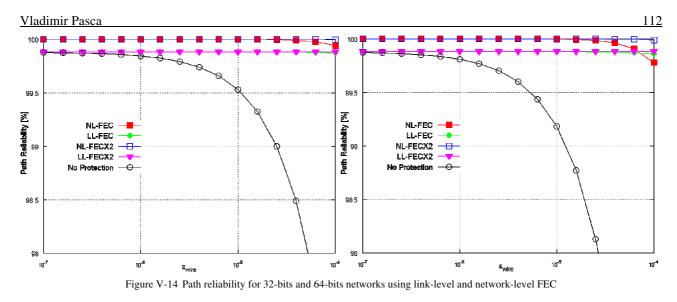

| FIGURE V-13                  | PATH RELIABILITY FOR 32-BITS AND 64-BITS NETWORKS USING NL-FEC WITH INTERLEAVED HAMM 111                                                    |     |

| FIGURE V-14                  | PATH RELIABILITY FOR 32-BITS AND 64-BITS NETWORKS USING LINK-LEVEL AND NETWORK-LEVEL F 112                                                  | EC  |

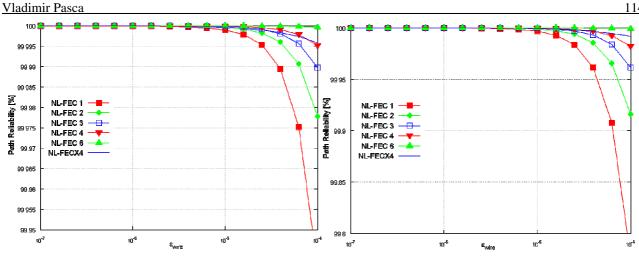

| FIGURE V-15                  | COMPARISON OF LINK-LEVEL AND NETWORK-LEVEL FEC FOR 32 BITS ROUTERS                                                                          |     |

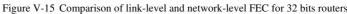

| FIGURE V-16                  | IMPACT OF INTERMEDIATE CORRECTION STAGES ON NETWORK LATENCY                                                                                 |     |

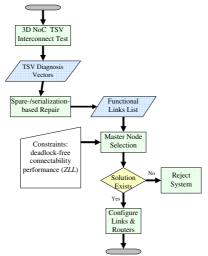

| FIGURE VI-1                  | ERROR-RESILIENCE EXPLORATION (ERX) DIAGRAM FOR 3D NOCS                                                                                      |     |

| FIGURE VI-2                  | SELECTION PROCESS FOR TSV PERMANENT FAULTS                                                                                                  |     |

| FIGURE VI-3                  | ERROR RESILIENCE 3D NOC EVALUATION FLOW                                                                                                     |     |

| FIGURE VI-4                  | 3D MPSoC ARCHITECTURE WITH PHYSICALLY SEPARATED REQUEST AND RESPONSE NETWORKS                                                               |     |

| FIGURE VI-5                  | TRANSACTION EXECUTION TIME IN THE (A) UNPROTECTED AND (B) ERROR-RESILIENCE PLATFORM                                                         |     |

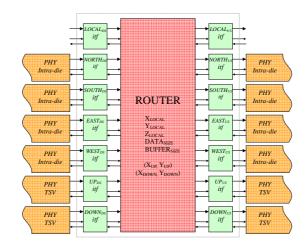

| FIGURE A-1                   | 3D 3×4×3 MESH TOPOLOGY (A) AND THE PACKET FORMAT FOR THE 3D FULLY-SYNCHRONOUS 3D NOC 169                                                    | (B) |

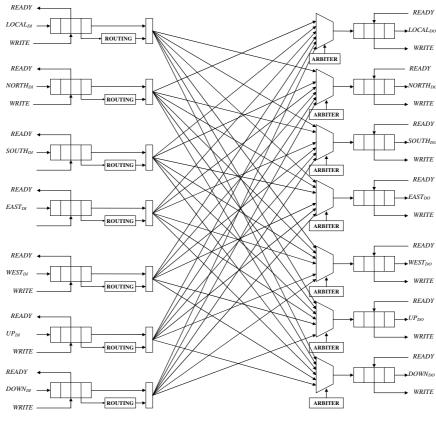

| FIGURE A-2                   | SEVEN-PORT ROUTER MICRO-ARCHITECTURE                                                                                                        | 170 |

| FIGURE A-3                   | TIME DIAGRAM OF CONTENTION-FREE ROUTER TRAVERSAL FROM INPUT I TO OUTPUT O                                                                   |     |

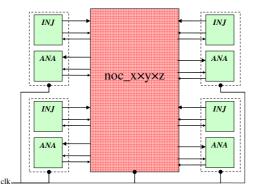

| FIGURE A-4                   | SIMULATION PLATFORM FOR NOC_XYZ MODULE                                                                                                      | 172 |

| FIGURE A-5                   | INSTANTIATED SEVEN-PORT ROUTER WITH ERROR RESILIENCE INTERFACES                                                                             | 173 |

| FIGURE A-6                   | LINK INSTANTIATION BEWEEN TWO CONNECTED ROUTER PORTS USING TWO LINK MODULES                                                                 |     |

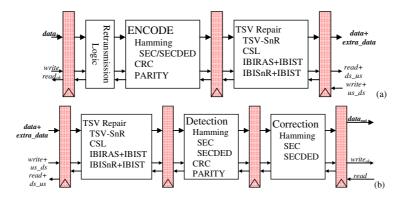

| FIGURE A-7                   | UPSTREAM~(A)~AND~DOWNSTREAM~(B)~INTERFACES~WITH~OPTIONAL~MODULES~AND~REGISTER~STAGES~.                                                      | 174 |

| FIGURE A-8                   | SIMULATION PLATFORM FOR ERROR RESILIENT NOC_XYZ MODULE WITH ERROR INJECTION FOR INTRA-                                                      |     |

|                              | E WIRES                                                                                                                                     |     |

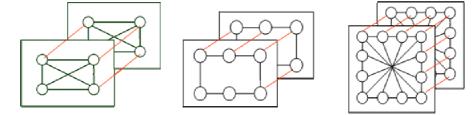

| FIGURE A-9                   | SPIDERGON STNOC TOPOLOGIES                                                                                                                  | 175 |

| List of Figures |                                                                        | 9   |

|-----------------|------------------------------------------------------------------------|-----|

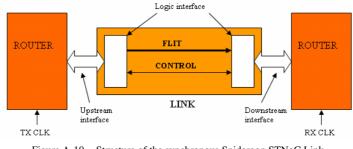

| FIGURE A-10     | STRUCTURE OF THE SYNCHRONOUS SPIDERGON STNOC LINK.                     | 176 |

| FIGURE A-11     | SPIDERGON STNOC-BASED 3D MPSoC ARCHITECTURE                            | 177 |

| FIGURE A-12     | ERROR RESILIENCE SCHEME FOR REQUEST AND RESPONSE LINKS IN THE 3D MPSoC | 178 |

# Glossary

| TSV         | Through-Silicon-Vias                              |

|-------------|---------------------------------------------------|

| VDSM / UDSM | Very-/Ultra-Deep Submicron                        |

| GSI         | Giga-Scale Integration                            |

| TSI         | Tera-Scale Integration                            |

| KGD         | Known Good Die                                    |

| NoC         | Network-on-Chip                                   |

| SoC         | System-on-Chip                                    |

| MPSoC       | Multi-Processor System-on-Chip                    |

| MP2SoC      | Massively-Parallel Multi-Processor System-on-Chip |

| TAM         | Test Access Mechanism                             |

| BIST        | Built-In Self-Test                                |

| BISR        | Built-In Self-Repair                              |

| ECC         | Error Correction Code                             |

| TMR         | Triple Modular Redundancy                         |

| FEC         | Forward Error-Correction                          |

| D2D         | Die-to-Die                                        |

| D2W         | Die-to-Wafer                                      |

| W2W         | Wafer-to-Wafer                                    |

#### INTRODUCTION

For more than five decades, electrical engineers, computer and material scientist have built integrated circuits with increasing complexity and capabilities. In the early days of silicon semiconductor industry, it was predicted that the integration density (i.e. number of transistors per chip) would double every 18 months (*Moore's Law*) [Moo65]. Nowadays, all system functionalities (i.e. processing, memory, I/O, analog) are integrated on a single chip (or package) with more than one billion transistors / chip (i.e. Giga-Scale Integration GSI). The  $10^{12}$  transistors / chip (i.e. Tera-Scale Integration TSI) milestone should be reached by the end of this decade. In the System-on-Chip (SoC) integration paradigm, hardware and software designers work together to offer systems with high computational power that satisfy the performance, energy-efficiency and reliability requirements.

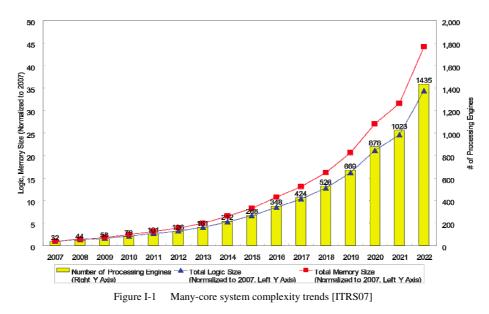

However, improvements of computing performance and energy-efficiency by technological scaling lead to high development cost. Multi-processing became a powerful strategy to increase system performance by leveraging data-level and instruction-level parallelism. User applications are divided in tasks that run in parallel on one or more processing elements (i.e. Multi-/Many-Processor System-on-Chip MPSoC). Figure I-1 represents the ITRS trends in many-core system complexity.

The logic and memory size increases such that today chips comprise  $\sim 5 \times$  more logic elements and memory arrays than in 2007. By 2020, chips are expected to have up to 20× more logic and 27× more memory components. The increase of logic size is mainly due to the increasing number of processing elements. As shown above, today we have just entered the hundreds-cores era, but within a decade chips are expected to have more than one thousand cores (many-core SoCs).

Unfortunately, the increased complexity of chips cannot be efficiently managed by traditional design paradigms. Technological scaling raises a serious issue that was overlooked in older technology nodes: *wires do not scale the same way as transistors*. In the last decade this problem gained a lot of attention since, in

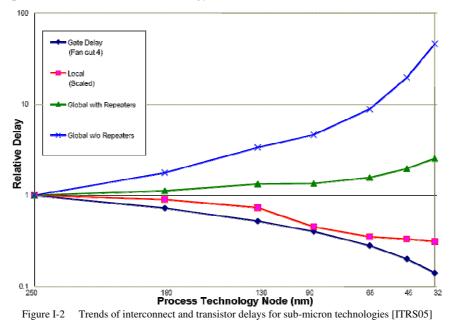

very-deep sub-micron (*VDSM*) technologies, wire delays begin to dominate the delays of logic gates. Despite well-known reliability issues (i.e. electro-migration, diffusion in silicon), the high conductivity of copper made it the suitable candidate to replace aluminum in chip wiring since 1998. Developments in copper interconnect technologies and *low-K* dielectrics reduced signal propagation delays and improved signal integrity. However, the delays of copper wires increase in advanced technology nodes while the gate delays decrease. For aluminum, the breakeven point was for the 250 nm technology node (i.e. around year 2000), while for copper it was at the 150 nm technology node (i.e. around year 2005). In Figure I-2, the wire and gate delay trends are represented for different technology nodes.

The trends above show that, relative to 250 nm technology node, the gate and local wire (i.e. first metal layers  $M_1$ - $M_3$ ) delays decrease from generation to generation, while the global interconnect (i.e. top-most metal layers) relative delay increases. In the 32 nm technology node, gates are up to 5× faster than in 250 nm technologies, while signal propagation on global wires is up to 50× slower. The delay challenge of global wires can be partially alleviated by inserting repeaters. In this case, the relative delays of global wires are 5× larger. However, the delay gain is paid in extra area and power for the repeaters. In [ML04], it was shown that the dynamic power dissipated on interconnects accounts for ~50% of the total chip power consumption and about 90% of this power is dissipated on global wires. For advanced technology nodes (i.e. below 32 nm) that study also predicted that the dissipated on wires will account for 65% of the total chip power. Therefore, interconnects are the performance bottleneck in GSI / TSI technologies.

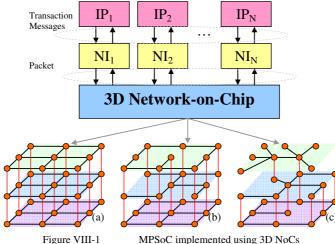

Technology scaling poses another challenge: traditional bus-like interconnect fabrics are not scalable for SoCs comprising hundreds or thousands of Intellectual Property (IP) blocks. Communication contention due to arbitration reduces the overall system performance. In embedded MPSoCs, a widely accepted solution to this problem is the packet-switched interconnection fabric: the *Network-on-Chip (NoC)*. Similarly to the ISO/OSI model in computer networks, NoCs also have abstraction layers, which are shown in Figure I-3.

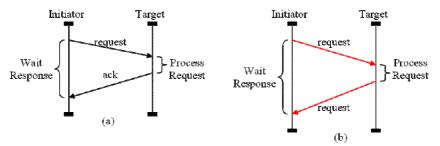

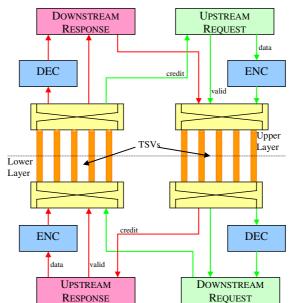

Figure I-3 Abstraction layers of NoC-based MPSoCs [BdM02]

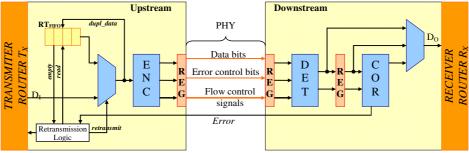

In most communication-centric systems, on-chip communication is performed by load / store transactions (i.e. transaction-based communication), using a specific protocols (e.g. AMBA-AXI, VCI/OCP). Initiator (or master) nodes (e.g. CPU), begin transactions by making load / store requests to targets (or slaves) modules (e.g. memory). In software, application-level read / write operations to memory are translated into system-level load / store transactions. At transport-level, these transactions are split in request / response messages that are packetized and forwarded to the network. Packets are processed at network-level and they are transmitted from source to destination in a pipelined way. At data link-level, routers exchange flow control units (flits) over the physical communication environment *PHY*.

The interconnect problems can be solved at technological level using 3D integration. In 3D chips, silicon layers are stacked and connected by shorter vertical wires called Through-Silicon-Vias (TSVs). The power and timing improvements promises of stacked 3D integration are mainly due to the reduced average interconnect length. At system-level, the joint use of 3D integration and NoC-centric design paradigms open the way to novel energy-efficient architectures with significant performance improvements.

Despite recent technological progress, TSV-based 3D chips are not considered mature enough for largescale production. Interconnect test, manufacturing costs, yield and reliability, thermal management and heat removal are among the greatest challenges of this technology. In 3D MPSoCs using NoCs as system-level interconnect fabric, testing and ensuring high reliability / yield becomes increasingly difficult. Intra-/inter-die communication reliability is paramount for communication-centric MPSoCs. Faults that occur during network traversal may lead to system failures. Hence, efficient interconnect test strategies and error resilience techniques are no longer a *nice-to-have*, but a *must-have* feature. In this thesis, three main issues of NoCcentric 3D MPSoCs are addressed: interconnect TSV test, yield and reliability.

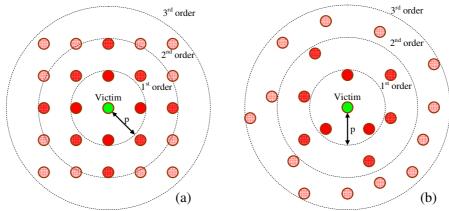

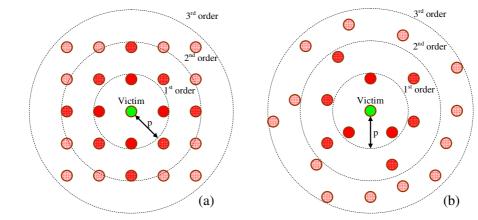

Interconnect Built-In Self-Test (*IBIST*) strategies have proven to be efficient in testing on-chip and boardlevel interconnects for structural and functional faults. If inter-die synchronization can be guaranteed in stacked 3D chips, then similar *IBIST* methodologies can also be used for TSV tests. Although existing test pattern generators can be used for TSV tests, they have poor fault coverage (e.g. only structural faults like opens and shorts are detected) or they are too conservative, leading to high test costs. Using the victimaggressor scenario, where signal transitions on victim wires are affected by signal transitions on aggressor wires, the  $K^{th}$ -Aggressor-Fault (KAF) model is proposed. For KAF-based TSV tests, depending on their distance to the victim TSV, neighboring aggressors are organized in classes called *aggressor orders*. The novelty of this approach is that, depending on the TSV technology, higher order aggressors may not be considered for tests. The major advantages of this strategy are simpler test circuitry and fewer test patterns, which translates into shorter test duration.

Error resilience of 3D NoCs against TSV permanent and transient faults can be efficiently improved by different single-/multi-layer strategies. In multi-layer schemes, the task of fault mitigation is shared across several abstraction layers (e.g. data link and network). In 3D NoCs, error resilience can be ensured at data link and / or network levels, on NoC components (i.e. links and routers). The main contributions of this thesis on error resilient strategies are summarized in the following.

In modern chips, transient faults are responsible for more than 80% of system failures [BdM02]. In 3D NoCs, transients can affect both wires (i.e. intra-die wires and TSVs) and different router components (e.g. buffers, arbitration logic). To leverage transient errors on NoC links, correct data transmission is ensured by implementing retransmission-/correction-based error control schemes on intra-/inter-die links. Reliable transmission through the entire network (i.e. links and routers) is ensured by network-level error resilience schemes on individual flits. In the multi-layer framework, link-level and network-level protection are jointly used in order to ensure reliable communication. Flits are individually encoded at the source, and correction stages are inserted on links along the path such that multiple errors do not cumulate.

Permanent TSV faults due to manufacturing defects have a dramatic impact on 3D chip yield. The proposed data link-level solutions to repair TSV failures in 3D NoCs are: *Spare-and-Replace (TSV-SnR)* and *Configurable fault-tolerant Serialization (CSL)*. At network-level, TSV permanent faults are mitigated by instructing routers to forward packets around faulty components (i.e. inter-die links). An important feature of the proposed TSV-fault tolerant routing algorithm (*TSV-FTR*) is that it does not use virtual channels to ensure deadlock freedom, a critical property for NoCs.

In aggressive 3D technologies, chips are expected to have *thousands* and *tens of thousands* TSVs. For such complex systems, in-field TSV failures may cause serious reliability issues. Therefore, a Built-In Self-Repair strategy based on spare TSVs and adaptive serialization (*IBIRAS*) has been developed. The main benefit of this approach is that no external intervention is required, as the repair signals are determined on-chip using the interconnect test diagnosis vector.

Although solutions to the TSV reliability / yield issues exist, it is difficult to determine which of these strategies is better suited for a given 3D NoC. Choosing the best error resilience configuration for a 3D NoC architecture, which must satisfy yield and reliability targets for a given failure rate, is very difficult. *One-fits-all* solutions do not exist, as each technique has its own advantages and limitations with respect to costs (i.e. area, power, TSV count) and impact on system performance. The area and power budget could be very limited and, depending on system requirements, the performance penalty due to error mitigation should be very low.

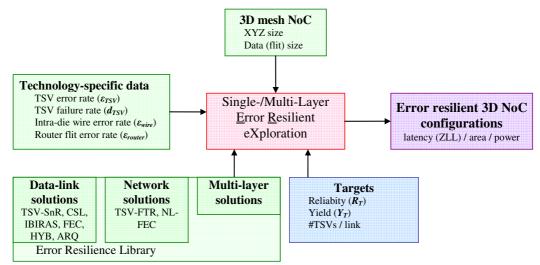

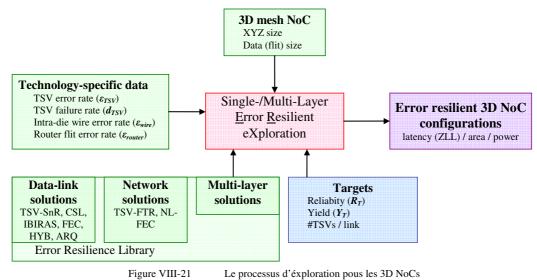

Moreover, the possibility to jointly use error resilience at different abstraction layers (i.e. data link and network) makes new costs-performance trade-offs possible. To address this challenge, an *error resilience exploration (ERX)* tool for 3D NoCs is proposed in this thesis. Hence, given a 3D NoC configuration, different error-resilient configurations (i.e. single-layer and multi-layer) are implemented and evaluated (i.e. area, power and network latency) such that designers can choose the optimal solution.

In the remaining of this manuscript, all above contributions are detailed as follows. Chapter 2 presents a state-of-the-art on 3D integration technologies and their implications on system architectures. Different 3D integration strategies and challenges, and (3D) NoC-related design, test and reliability issues with existing solutions are discussed. In Chapter 3, the novel KAF model used for TSV self-tests in NoC inter-die links is presented. The error resilience strategies and exploration tool for 3D NoCs is presented in Chapter 4. Data link and network-level fault tolerance solutions for transient and permanent faults are presented with different scenarios in which they can be jointly used in multi-layer error resilience schemes. Chapter 5 presents an assessment of the error resilience schemes in the context of 3D mesh NoCs. The objective of this study is to show the resilience capabilities of each solution and identify different trade-offs. The *error resilience exploration* concept with its application to 3D NoCs is presented in Chapter 6. Using the error resilience exploration tool (*ERX*), the impact of error resilience on system performance is assessed for a 64-tiles 3D MPSoCs which is implemented in SystemC using the SoCLib cycle-accurate bit-accurate (CABA) library [SL]. Finally, Chapter 7 concludes this thesis and discusses further research directions.

## Chapter Two

#### **3D INTEGRATION AND NETWORKS-ON-CHIP**

|        | DINTEGRATION USING TSVS                      |    |

|--------|----------------------------------------------|----|

| 2.2 CH | IALLENGES OF TSV-BASED 3D INTEGRATED SYSTEMS | 21 |

| 2.2.1  | Testing TSV-based 3D ICs                     | 21 |

| 2.2.2  | Testing Through-Silicon-Vias                 |    |

| 2.2.2. |                                              | 24 |

| 2.2.2. | 2 Interconnect Built-In Self-Test            | 24 |

| 2.2.3  | Reliability and Yield                        |    |

| 2.2.3. | 1 Faults classification                      |    |

| 2.2.3. | 2 Manufacturing defects in 3D ICs            |    |

| 2.2.3. | 3 Reliability in 3D ICs                      |    |

| 2.3 NE | TWORKS-ON-CHIP IN 3D SYSTEMS                 |    |

| 2.3.1  | From 2D NoCs to 3D NoCs                      | 31 |

| 2.3.2  | 3D NoC Design                                |    |

| 2.3.3  | NoC Testing                                  |    |

| 2.3.4  | Reliability and Yield                        |    |

| 2.3.4. |                                              |    |

| 2.3.4. | 2 Link repair                                | 35 |

| 2.3.4. | 3 Signal encoding                            |    |

| 2.3.4. | 4 Robust router architectures                |    |

| 2.3.4. |                                              |    |

| 2.4 Co | NCLUSION                                     |    |

|        |                                              |    |

Stacked 3D integration is an emerging technology that promises heterogeneous system integration with reduced power consumption and increased performance. Layers of active silicon are stacked and vertically connected by Through-Silicon-Vias (TSVs). Today, TSV-based 3D integration is not yet fully mature and new design and test concepts are being developed. While novel techniques are used to improve the 3D chip compound yield and reliability, several other techniques have been adapted from well-established fields. In this chapter, TSV-based 3D integration fundamental concepts and challenges are presented. As the main focus of this thesis are the test and reliability / yield issues of the 3D system interconnect fabric (i.e. Network-on-Chip), different solutions to the above mentioned challenges are presented in the context of (3D) NoCs.

#### 2.1 3D Integration using TSVs

The System-on-Chip (*SoC*) paradigm primarily addresses the complexity of off-chip interconnects by integrating all system components in a single package. From Multi-chip-Modules (*MCMs*) to Systems-in-Package (*SiPs*) and Systems-on-Package (*SoPs*), the number of components /  $cm^2$  has steadily increased in the last decades. Although systems become more complex and offer more functionality, integrating them in a single package becomes a great challenge. The key technology for more system-level integration is 3D stacking using Through-Silicon-Vias (*TSVs*).

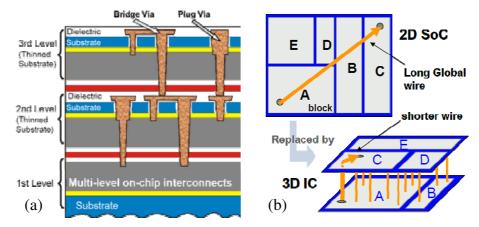

The benefits of TSV-based 3D integration are mainly achieved by stacking active silicon layers. These layers are connected using short (i.e. *tens* of  $\mu m$ ) inter-die wires called Through-Silicon-Vias (TSVs), as represented in Figure II-1 (a). In 3D Systems-on-Chip (3D SoC), performance improvements and power savings are achieved by replacing long global interconnects of 2D SoCs with shorter TSVs. Compared to 2D chips, the average interconnect length is reduced by a factor proportional to the square root of the number of layers in the stack [PF09]. In Figure II-1 (b), the connection between blocks *A* and *C* of a 2D SoC is replaced by TSVs, significantly reducing the wire length.

Figure II-1 TSV-based stacked 3D integration (a) [Lu03] reduces the average global interconnect length (b)

Unlike traditional chips, each layer of the 3D stack can be implemented in different technologies. The advantages of TSV-based 3D integration are not limited to integration heterogeneity. A power reduction of 40% was reported in [Pat11] for a stacked 3D chip. In the same paper, the chip footprint of 3D ICs is also reduced and more capabilities can be integrated in a single package (i.e. up to  $4\times$  density increase). Moreover, the flexibility of 3D system architectures enables an up to 400% performance improvement.

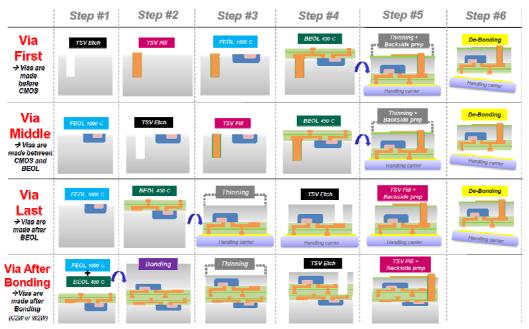

The manufacturing processes of 3D chips are more complex than in traditional CMOS. There are many different processing technologies to choose from. Each process has its advantages and disadvantages in terms of compatibility with existing CMOS manufacturing processes, manufacturing throughput and reliability. The main steps in manufacturing 3D chips are wafer thinning, TSV formation and bonding. The order in which these processes are performed can be different, leading to different trade-offs. In Figure II-2, the main manufacturing processes with respect to TSV formation are presented.

Figure II-2 Summary of 3D chip manufacturing steps (source: YOLE Development)

In the *via-first* approach, the TSVs are manufactured first by etching the bulk silicon and depositing the TSV metal (i.e. copper or tungsten). After the lithographic processes for transistors manufacturing and metal

layers deposition, the wafer is flipped and, while bonded to a carrier wafer, the bulk silicon is thinned down to tens of  $\mu m$  (i.e. until the TSV tips are visible). Before stacking the wafer, backside preparation processes and de-bonding from the handling carrier are performed. In the *via-middle* approach, TSVs are formed in intermediate steps between transistor manufacturing and metal layers deposition. In the *via-last* approach, after the lithographic processes for transistors and metal layer, the wafer is flipped. Then, the wafer is thinned while bonded to a carrier wafer and TSVs are formed. After backside preparation processes, the carrier wafer is removed and the thinned wafer is ready for bonding. In the *via-after-bonding* approach, TSVs are manufactured after the wafers bonding and thinning processes.

Depending on the die/wafer orientation, bonding can be made *face-to-face*, *back-to-back* and *face-to-back*. It is also possible to have *wafer-to-wafer* (w2w), *die-to-wafer* (d2w) and *die-to-die* (d2d) bonding. In the w2w approach, entire wafers are bonded. The advantage of this approach is high manufacturing throughput. Unfortunately, this strategy can result in poor compound yield, as faulty dies are likely to be stacked on functional ones. Another limitation of wafer-level processing is that dies must have the identical sizes, while in the d2w strategy dies with different sizes can be stacked. The d2w process also has the advantage of higher yield, but the manufacturing throughput is reduced, as individual dies are tested before bonding (i.e. *Known-Good-Die KGD*). The d2d approach has the potential of providing maximum yield, as only dies that pass prebond tests are stacked. However, similar to the d2w case, the throughput is significantly reduced and test / manufacturing costs are higher.

TSV-based stacked 3D integration is used in different applications such as CMOS Image Sensors (CIS) [HJN08], and memories [KCH10], *Memory-on-Logic (MoL)* [Loh08, HAG10, VG11], and *Logic-on-Logic (LoL)* [FDG12]. *MoL* systems comprise a single layer of interconnected processing cores (ASIC) which exchange data with memory layers. In *LoL* MPSoCs, two or more stacked dies of processing cores exchange messages. In this case, the global interconnect fabric, which connects these cores, spans across two or more layers, ensuring both intra-die and inter-die communication.

3D integration is an emerging and rapidly growing technology. Despite its promises, several challenges must be addressed before 3D stacking becomes main-stream. In the following section, the major challenges of TSV-based 3D integration and potential solutions are presented.

#### 2.2 Challenges of TSV-based 3D Integrated Systems

Testing, reliability and yield, thermal management and costs remain the major challenges of TSV-based 3D integration. In recent years, these issues have been addressed by the scientific community using novel solutions or re-implementing existing ones. In this section, a review of major contribution in solving these challenges is presented.

#### 2.2.1 Testing TSV-based 3D ICs

Among the most important challenges is how to efficiently test 3D system architectures. A common strategy is to test each die before bonding (i.e. *Known Good Die* bonding) and then perform final chip tests. It has been shown that this strategy pays-offs only when the die yield is not very high [Mar10]. For a 3D chip comprising many dies, it is also possible to perform partial stack dies testing. In other words, each time a die

is stacked, the existing partial stack is tested. In Figure II-3, a 3D chip test flow with intermediate pre-bond and post-bond test steps is represented [MZ09].

Figure II-3 Stacked 3D chip test flow [MZ09]

The manufacturing throughput of the *partial-stack test* strategy is very low, as tests are performed both *pre-* and *post-*bonding. In order to improve manufacturing throughput, it is possible to remove intermediate test steps. A challenge in *pre-*bond tests is that it requires access to the die using dedicated access pads. However, because these tests are often performed on thinned dies/wafers, reliability problems arise, as test pins could damage the die/wafer [MZ09].

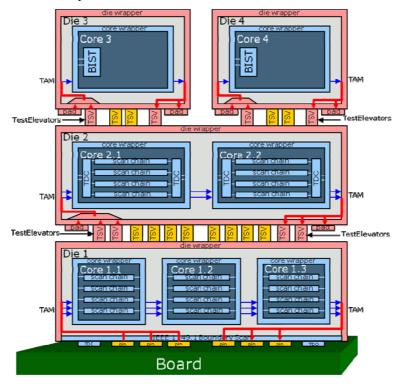

*Design-for-Test* (DfT) circuitry is required to ensure full controllability and observability of 3D system components (i.e. TSVs, cores, dies). In order to ensure efficient testing, there are several requirements that the Test Access Mechanism (3D TAM) should satisfy. The 3D DfT architecture must be scalable with respect to the number of dies. In order to have higher production testing, a parallel access mechanism, which provides a trade-off between implementation costs and test access bandwidth, should be considered [MZ09, Mar10, MCK12]. Another possible requirement of 3D test is modularity: cores and TSVs are tested as separate units. If this requirement is fulfilled then it is possible to optimize testing for specific fault models, enable test flow optimization optimize the number of test elevators (i.e. TSVs used for test data transmission in upper layers) [NGC10] or reduce test duration [NCG11]. In Figure II-4, an example of state-of-the-art 3D TAM based on the IEEE 1149.1 and IEEE 1500 standards is given [MCK12].

Figure II-4 Example of a Simple 3D Test Acess Mechanism [MCK12]

In this 3D DfT architecture, die-level test wrappers are considered for each die in the stack. The main features of the standardizable die wrapper are serial and parallel interfaces for wrapper instructions / low-bandwidth tests and high-bandwidth test data; *TestTurns* that feed data back to the bottom die; *Test Elevators* that propagate test data up and down the stack; optional test pads for pre-bond testing; and an optional inclusion / exclusion mechanisms for embedded IPs.

The most important feature of the 3D TAM is the possibility of inter-die wire testing. Interconnect tests can be performed similarly to boundary scan (IEEE 1149.1) and built-in self-test strategies in on-chip and board-level wires. In the following, interconnect failure modes and strategies to sensitize these faults are presented.

#### 2.2.2 Testing Through-Silicon-Vias

The TSV failure modes are not fundamentally different from on-chip and board-level interconnects. In all cases, interconnect manufacturing and aging/wear-out defects are modeled using the basic faults: *open, short, stuck-at,* and *delay* faults. In the *open fault model,* a wire is assumed broken and its terminals are electrically disconnected. In the *short fault model,* two ore more wires are electrically connected when they should not be. Depending on the technology, either *AND* or *OR* logic gates can be used to obtain the resulting value of the wires. For *stuck-at* faults, the signal sent on a wire is stuck at a '0' or '1' value, independently of the values sent on the wire. In the case of *delay faults,* the signal eventually assumes the correct value, but more slowly (or rarely, more quickly) than normal. Possible causes of delay faults are process variation, crosstalk, etc.

Sensitizing these faults requires dedicated test circuitry that ensures both interconnect controllability and observability. In the following it is shown how the boundary scan and interconnect built-in self-test strategies, which have been used for on-chip interconnect tests, are used for TSV tests.

#### 2.2.2.1 Boundary Scan

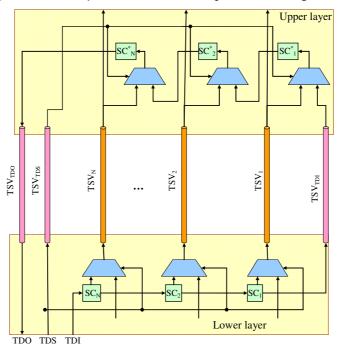

The main purpose of the commonly used IEEE 1149.1 (Boundary Scan) standard is Printed Circuit Board (PCB) wire testing. This standard can be adapted for 3D ICs such that TSV interconnect test can be performed in a similar way. The major advantages of *Boundary Scan* are a reduced number of test pins and a relatively small number of test patterns necessary to sensitize structural faults (e.g. open, shorts). To illustrate how TSVs can be tested, let us consider the two stacked dies such that the lower die is connected with the upper die through *N* TSVs. The simplified *boundary-scan* architecture is presented in Figure II-5.

Figure II-5 Boundary Scan Test for regular TSVs TSV<sub>1</sub>-TSV<sub>N</sub>

The *N*-bits test vector  $T_{I}$ - $T_{N}$  is serially shifted in the chip through the *TDI* port and transported to the lower scan cells  $SC_{I}$  to  $SC_{N}$ . Once the test vector is loaded in these cells, the control signal *TDS* is set and the scan cells contents is transmitted through the *N* TSVs and loaded in the  $SC_{I}^{*}$  to  $SC_{N}^{*}$  scan cells from the upper layer. Then, under the control of the external tester, the response vector  $T_{I}^{*}$ - $T_{N}^{*}$  (i.e. contents of  $SC_{I}^{*}$  to  $SC_{N}^{*}$ ) is shifted out on the *TDO* port. In order to reduce test times, while the response vector is shifted out, the next test vector may be loaded in  $SC_{I}$  to  $SC_{N}$ . After the test phase, the external tester compares the test and response vectors in order to identify faulty TSVs. Note that the  $TSV_{TDI}$ ,  $TSV_{TDO}$  and  $TSV_{TDS}$  vertical connections must be functional in order to guarantee test correctness.

Test vectors are generated off-chip using different algorithms based on counting sequences [Kau74], modified counting sequences [GM82], true/complement sequences [Wag87], marching ones, etc. Since tests are performed at the lower frequencies of external testers, only structural faults can be detected.

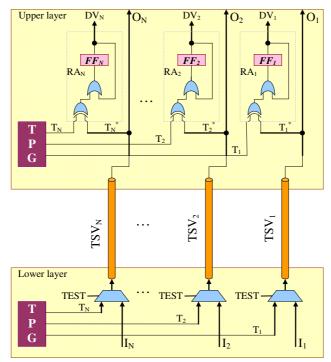

#### 2.2.2.2 Interconnect Built-In Self-Test

TSV interconnect delay faults testing can be performed by adopting at-speed test strategies similar to those developed for on-chip and board-level interconnects. However, it is necessary to have good inter-die synchronization, for such implementations to be possible.

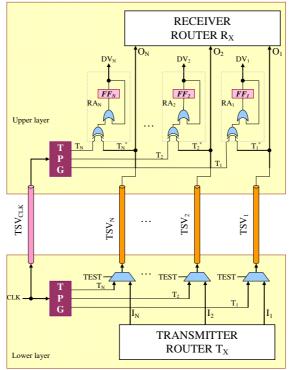

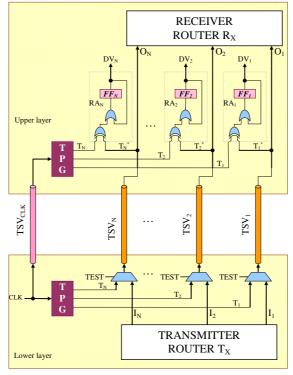

Interconnect Built-In Self-Test (*IBIST*) strategies are used for testing global on-chip and board-level interconnects. Implementing *IBIST* strategies in TSV-based 3D systems comes with some advantages: fewer test pins / test elevators and simplified external testers, as test vectors (or test stimuli) are generated on-chip. Because tests are performed at nominal clock rates (i.e. at-speed tests), delay faults (including delay faults due to crosstalk) can also be sensitized. Let us consider a TSV bundle with *N* wires that connect two stacked dies. In Figure II-6, a simplified *IBIST* test architecture adapted for 3D interconnects is represented.

Figure II-6 Interconnect Built-In Self-Test for N regular TSVs

During the test phase (i.e. TEST='1'), N bits test vectors  $T_I \cdot T_N$  are generated by Test Pattern Generators (TPGs) in the lower die and transmitted on TSVs. In the upper layer, the received vector  $T_I^* \cdot T_N^*$  is compared to the original transmitted vector locally generated by a second TPG identical to the one in the lower layer. The *response analysis* cells (*RA*) compare the response and test vectors, and iteratively build the diagnosis vector  $DV_I \cdot DV_N$ . In each response analysis cell *RA<sub>i</sub>*, a *XOR* gate compares the received test stimulus  $T_i^*$  with the expected one  $T_i$ . Using an *OR* gate, any mismatch of these signals is stored in *RA's* internal flip-flop  $F_i$ . At the end of the test phase, the diagnosis vector which identifies the faulty TSVs is stored in *RA*'s internal flip-flop  $FF_I \cdot FF_N$ .

The *IBIST* main component is the *TPG* block. Test patterns can be generated using different algorithms, depending on the targeted TSV fault models (e.g. open, short, delay). In the case of open and short faults, the *TPG* module generates test patterns using algorithms such as Counting Sequence, Modified Counting Sequence, or True/Complement Sequence. In order to detect delay faults, both '0'-'1' and '1'-'0' transitions have to be activated for every wire. The marching-'1'/'0' and rearranged True/Complement test sequences can be used for delay faults. Interconnect at-speed tests using Linear Feed-back Shift Registers (LFSRs) and Multiple-Input Shift Registers (MISRs) have been proposed for on-chip interconnect tests [SD02]. LFSR optimization techniques are also possible. For example, the authors of [PCZ01] have used Markov chains to

generate realistic switching activity. The disadvantage of *LFSR*-based solutions are high aliasing probability (i.e. multiple faults impact the MISR's capability to detect them), long test sequence for detecting all faults, and relatively low fault coverage.

In [Jut04], at-speed tests for delay faults are performed using *Interleaved True/Complement Counting* (*ITCC*) sequences where complemented vectors are transmitted right after their true valued counterparts. *ITCC* sequences sensitize some delay faults due to crosstalk, as the complemented values '0'/1' and '1'/'0' are transmitted on any two pair of wires. In [CDB99] a worst-case test strategy for delay faults due to crosstalk has been proposed for on-chip interconnects. This strategy can detect both structural / delay faults, but the test sequence is very long (i.e. for *N* wires a total of *8N* vectors are used, compared to the  $2 \cdot [log_2(N)]$  vectors of *ITCC*) and the hardware implementation costs are non-negligible. Using the aggressor-victim scenario, the *Maximum Aggressor Fault (MAF)* model proposed in [CDB99] takes into account the crosstalk effects between a set of aggressor wires and a victim wire. Signal transitions on the victim wire are affected by the crosstalk noise induced by transitions on *all* other wires.

Few of these delay faults strategies have been implemented in a 3D integration setting. For example, LFSR-MISR techniques have been implemented for TSV self-test [HHH10]. In this test strategy, which is represented in Figure II-7, TSVs are assumed are distributed on regular arrays.

Figure II-7 Built-In Self-test and Repair for Through-Silicon-Vias [HHH10]

In order to reduce test durations, TSVs are tested one row at a time and a single spare is allocated for every row. The number of dedicated TSVs required by this self-test and self-repair strategy is high: for each TSV row, a single TSV is necessary to indicate in the lower die that the functional spare replaces a faulty regular TSV.

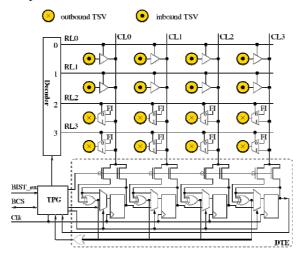

Another post-bond interconnect TSV *BIST* strategy was proposed in [HLC11]. In this scheme, it is also considered that TSVs are distributed on regular arrays. In Figure II-8, the BIST architecture for the TSVs of a die is represented. In this architecture, *outbound* TSVs are the TSVs that carry signals off the current die and *inbound* TSVs are those TSVs that carry signals from the neighboring die.

Figure II-8 Post-bond TSV BIST for bidirectional TSVs set as inboud and outbound for a given die [HLC11]

The *BIST* consists of a row decoder, a test pattern generator (*TPG*), and a test data transportation and evaluation (*DTE*) circuit. The BIST control signals (*BCS*) and enable signal (*BIST\_en*) manage the *BIST* operation. In order to reduce test and diagnosis duration, TSVs are tested one row at a time. The decoder selects a row for test pattern application or test response evaluation. The TPG generates control signals and test patterns for the decoder and the *DTE*. The *DTE* consists of shift registers and a comparator such that it can perform the test pattern/response transportation using the shift register and the test response evaluation using the comparator. TSVs in the same column are connected to a column line (*CL*) through a multiplexer or a tristate buffer. For an outbound TSV, a multiplexer is used to select a signal from the functional circuit (*FI*) or the CL. For an inbound TSV, a tri-state buffer is used to pass or block the signal to the test circuit. The benefit of this approach is that it requires less time and on-chip resources than IEEE 1500 test wrappers. However,  $l+c+2\cdot r$  cycles are needed to test the  $r \times c$  TSV array for a single test pattern.

Recent advances in testing 3D ICs and TSVs enable chip manufactures to adopt 3D integration. Moreover, the compatibility of 3D DfT with well-established IEEE standards such as IEEE 1149.1 and IEEE 1500 will facilitate the use of this technology in future designs. However, for products to be successful, testing is only part of the solution. The 3D chip reliability and yield challenges and potential solutions are discussed in the following section.

#### 2.2.3 Reliability and Yield

The key to any successful product, including 3D MPSoCs, is whether it is reliable (i.e. there are very few failures during its expected lifetime) and the manufacturing yield is high enough such that very few units are discarded due to manufacturing defects. In order to ensure high reliability and yield, faults that may occur during manufacturing processes and system lifetime must be mitigated. In this section, major fault tolerant solutions proposed for 3D ICs are discussed. However, in order to understand how fault tolerant solutions are used, a brief classification of faults is presented first.

#### 2.2.3.1 Faults classification

Depending on their nature, faults can be *permanent* or *temporary* (i.e. *transient* and *intermittent*). In general, a permanent fault always occurs when a particular set of conditions exists. In hardware, permanent

faults model physical defects and they affect the circuit behavior always in the same way. They usually include the faults due to manufacturing process defects. During normal operation, a number of aging / wearout mechanisms can occur in the long term. Such faults (e.g. electro-migration in wires) are initially revealed as intermittent faults until they finally provoke a permanent fault.

A *transient fault* disturbs the normal operation of an element in the system for a limited period of time. Outside this time period, the affected element operation is not influenced. Transients usually do not cause physical damage to the device, but the effects of a transient fault may last even after its duration ends. Transient faults in MPSoCs are mainly represented by the so-called *soft errors*. These are caused by interferences of any kind, but also by the impact of cosmic rays and radiation on silicon. Soft errors generated by radiation impact are mostly present in harsh environments with very high concentration of radiations or particles (e.g. space or nuclear power plants). However, with the advanced technology downscaling and the voltage and capability reduction, the circuit sensitivity to soft errors is significant even in normal environments [Nic05].

An *intermittent fault* is defined as a malfunction of a device or system that occurs periodically, either at regular or irregular intervals. Outside of these periods, the device or system functions normally. The cause of an intermittent fault is several contributing factors occurring simultaneously. Intermittent faults in interconnects typically cause burst errors.

*Single* or *multiple* faults can occur in the system. They can occur in one or several parts of the system: transmission lines and combinational logic wire values can be delayed or inverted, while register values and memory bits can be inversed.

Due to the increased complexity of 3D ICs, errors are more than a possibility. Moreover, intra-die and inter-die parametric variations and errors cumulate, leading to potentially low yield and reliability. In the following, different yield improvement strategies that mitigate permanent faults due to manufacturing defects are presented.

#### 2.2.3.2 Manufacturing defects in 3D ICs

Pre-bond die tests help improving the chip yield, as only functional dies are stacked (i.e. KGD bonding). In [THV10], a compound yield improvement strategy for wafer-level processing is proposed. Using a *wafer repository*, wafers are bonded such that faulty dies are on the same position. Using this strategy the probability that packages contain faulty dies can be significantly reduced. In [Sin11], the symmetry of wafer has been used for matching faulty dies and improving the overall chip yield.

Another yield improvement strategy consists in allocating spare layers. Unfortunately, this strategy can be efficiently implemented only for 3D memories, which have highly regular architectures. For example, the authors of [TH11] use redundant layers and dedicated layer replacement circuitry that alleviates the issues of electrical fusing by using a series of address comparators.

In the *KGD* paradigm, TSV defects are the main cause of yield loss. Void formation, lamination due to thermally induced stress, height variation, and XY misalignment are major TSV failure mechanisms [PCF07, KXM09, LCD09].

Inter-die wire failures due to manufacturing are often mitigated using *spare-and-replace* strategies (i.e. *hardware redundancy*) where functional spare TSVs replace faulty regular TSVs. Hardware redundancy is proposed in [HHC10] for ASIC applications where TSVs are packed in blocks with one spare per block. Signals are routed on TSVs through a chain of MUXes. When faulty TSVs are detected, the signals transmitted on that TSV and on all subsequent TSVs in the chain are shifted by one position. The MUXes are controlled by arrays of e-fuse memories that are programmed using scan chains. For TSV failure rates (i.e. probability that a single TSV is faulty) up to 0.01%, one spare is allocated for each TSV block such that the TSV yield is raised up to 99.99%. However, the fault recovery rates (i.e. the probability that the fault pattern can be repaired) drop to 90% and 95%, when there are 50 and 25 TSVs per block, respectively. Hence, for the same number of TSVs, higher yield can only be achieved by partitioning the TSVs in more groups and allocating more spares / chip.

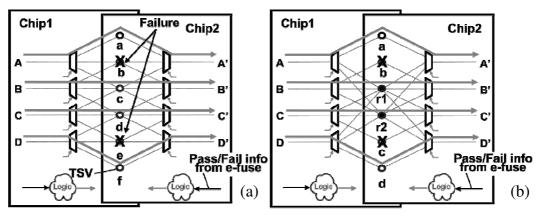

For 3D DDR3 DRAM memories [KCH10], TSV connectivity check and repair is used to improve the yield (>98%) of stacked chips comprising four layers connected by *300* TSVs. In the proposed schemes, which are represented in Figure II-9, one additional spare is considered for every pair of signals (2:1) or two additional spares are added for every four signals (4:2).

Figure II-9 TSV check and repair strategy for 4 signals A,B, C, D [KCH10]

TSVs are tested externally for open and short faults and using scan chains which output diagnosis vectors to external diagnosis circuitry. Faulty TSVs are repaired by their neighbors by programming arrays of e-fuses. Thus, detour paths decrease, reducing interconnect routing complexity and capacitive loads. For TSV technologies with  $80\mu m$  pitch, the authors report a  $\sim 2\%$  chip area overhead due to the total footprint of spare TSVs.

In [ZKA11], the grouping strategy was used within TSV bundles in order to efficiently use spare resources for different TSV defect distributions. Their experimental results showed that having fewer groups and more spares pays-off for high failure rates. The authors of [JXE12] use the *row/column repair* strategy for regular arrays of TSVs. Hence, for each  $N \times M$  TSV array an extra row / column of spares (i.e. N+M spares) is added such that faulty spares are replaced by their nearest neighbor. Using specific repair algorithms, they can achieve better yield with fewer spares than existing group-based solutions.

Although manufacturing defects remain the main source of faults in 3D ICs, in-field failures and transient errors during normal system operation could compromise the entire system. In the following, existing reliability enhancement solutions specific to 3D ICs are presented.

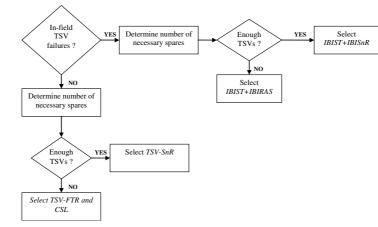

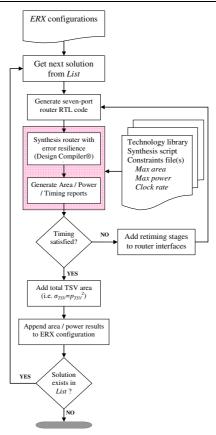

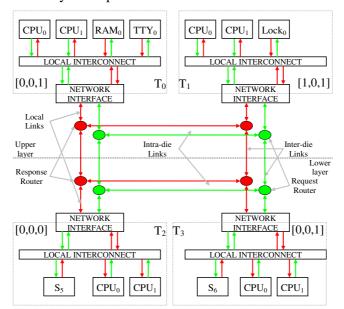

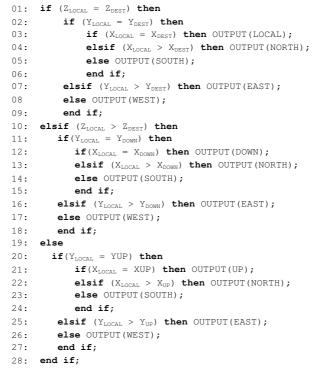

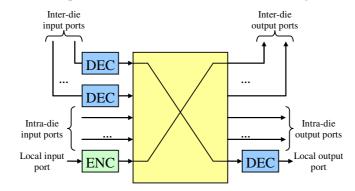

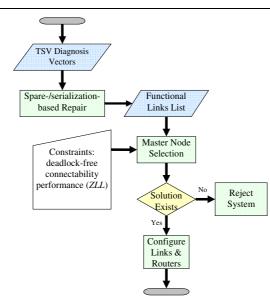

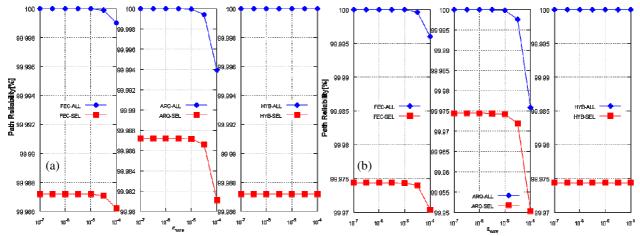

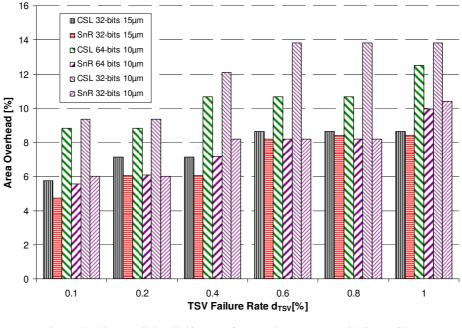

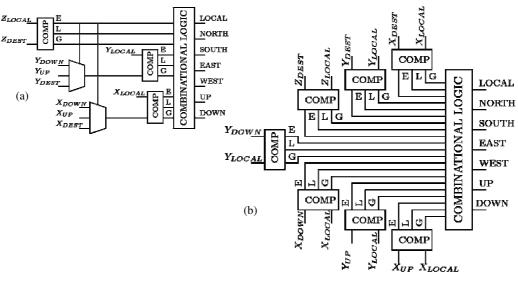

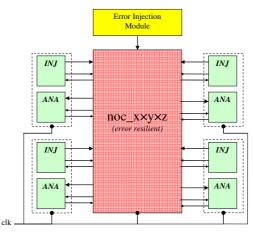

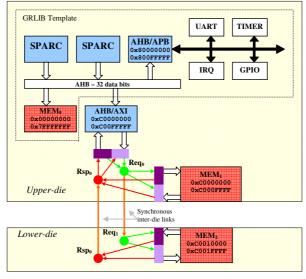

#### 2.2.3.3 Reliability in 3D ICs