# Parallel heterogeneous Branch and Bound algorithms for multi-core and multi-GPU environments

Imen Chakroun

### ▶ To cite this version:

Imen Chakroun. Parallel heterogeneous Branch and Bound algorithms for multi-core and multi-GPU environments. Distributed, Parallel, and Cluster Computing [cs.DC]. Université des Sciences et Technologie de Lille I, 2013. English. NNT: . tel-00841965

# HAL Id: tel-00841965 https://theses.hal.science/tel-00841965

Submitted on 8 Jul 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Ecole Doctorale Sciences Pour l'Ingénieur Université Lille 1 Nord-de-France Laboratoire d'Informatique Fondamentale de Lille (UMR CNRS 8022) Centre de Recherche INRIA Lille Nord Europe

Thèse présentée pour obtenir le grade de docteur Discipline : Informatique

# Parallel heterogeneous Branch and Bound algorithms for multi-core and multi-GPU environments

Défendue par :

## Imen Chakroun

Octobre 2010 - Juin 2013

Devant le jury composé de:

Rapporteur : Pierre Manneback, Professeur, Université de Mons, Belgique

Rapporteur: Catherine Roucairol, Professeur, Université de Versailles

Examinateur : Pierre Boulet, Professeur, Université Lille 1 Sciences et Technologies Examinateur : Stéphane Genaud, MCF HDR, ENSIIE Université de Strasbourg

Directeur de thèse: Nouredine Melab, Professeur, Université Lille 1 Sciences et Technologies

Numéro d'ordre : 41136 | Année : 2013

### Abstract:

Branch and Bound (B&B) algorithms are attractive for solving to optimality combinatorial optimization problems (COPs) by exploring a tree-based search space. Nevertheless, they are highly time-intensive when dealing with large problem instances (e.g. Taillard's FSP benchmarks) even using grid computing [Mezmaz et al., IEEE IPDPS'2007]. Massively parallel computing supplied through today's heterogeneous (GPU-enhanced multicore) platforms [TOP500] is required to tackle more efficiently those instances. The challenge is therefore to exploit all the underlying levels of parallelism and thus to rethink accordingly the parallel models of B&B. In this thesis, we revisit the design and implementation of B&B for solving large COPs on (large) multi-core and multi-GPU platforms. The Flow-Shop scheduling problem (FSP) is considered as a case study.

A preliminary experimental study on some large FSP instances has revealed that the search tree is highly irregular (in shape and size) and very large (billions of billions of nodes), and the bounding operator is time-exorbitant (about 97% of B&B). Therefore, our first contribution is to propose a (single CPU core) GPU-accelerated approach (GB&B) in which only the bounding operator is performed on the GPU device. The approach deals with two issues: thread divergence [Chakroun et al., Concurrency and Computation: Practice and Experience 2012 and device hierarchical memory optimization [Melab et al., IEEE Cluster 2012. Compared to a single CPU core-based implementation, speed-ups up to (×100) are obtained on Nvidia Tesla C2050. Although these good speed-ups, the performance analysis has shown that the overhead induced by the data transfer between CPU and GPU is high. Therefore, the aim of the second contribution [Chakroun et al., ICCS 2013 is to extend the approach (LL-GB&B) in order to minimize the CPU-GPU communication latency. Such objective is achieved through a GPU-based fine-grained parallelization of the branching and pruning operators in addition to the bounding one. The major and particularly challenging issue addressed here is thread divergence due to the strongly irregular nature of the explored tree mentioned above. Compared to a single CPU-based execution, LL-GB&B allows accelerations up to (×160) for large problem instances.

The third contribution [Chakroun et al., Journal of Parallel and Distributed Computing, 2013] consists in investigating the combination of GPU with multi-core processing. Two scenarios have been explored leading to two approaches: a concurrent (RLL-GB&B) and a cooperative one (PLL-GB&B). In the first one, the exploration process is performed concurrently by the GPU and the CPU cores. In the cooperative approach, the CPU cores

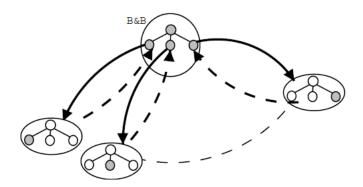

prepare and off-load to GPU pools of subproblems using data streaming while the GPU performs the exploration. When combining multi-core and GPU, we figure out that using RLL-GB&B is not beneficial while PLL-GB&B enables an improvement up to (36%) compared to LL-GB&B. Recently computational grids such as Grid5000 (on some sites) have been enhanced with GPU accelerators, therefore the fourth contribution of this thesis is to address the combination of GPU and multi-core computing with large scale distributed computing. To do that, the different revisited algorithms have been put together in a heterogeneous meta-algorithm which automatically selects the one to be deployed according to the target hardware configuration. The meta-algorithm is coupled with the B&B@Grid approach proposed in [Mezmaz et al., IEEE IPDPS'2007]. B&B@Grid distributes the work units (search subspaces coded by intervals) among the grid nodes while the meta-algorithm selects and applies locally a parallel B&B algorithm on the received intervals. The combined approach allowed us to solve to optimality and efficiently some Taillard's FSP instances (20 jobs on 20 machines).

### Keywords:

Parallel Branch-and-Bound, Heterogeneous computing, Graphics processing units, Multi-core computing, Grid'5000, Flowshop Scheduling Problem, Combinatorial Optimization, Exact Methods.

### Résumé:

Les algorithmes Branch and Bound (B&B) sont attractifs pour la résolution exacte de problèmes d'optimisation combinatoire (POC) par exploration d'un espace de recherche arborescent. Néanmoins, ces algorithmes sont très gourmands en temps de calcul pour des instances de problèmes de grande taille (exemple : benchmarks de Taillard pour FSP) même en utilisant le calcul sur grilles informatiques [Mezmaz et al., IEEE IPDPS'2007]. Le calcul massivement parallèle fourni à travers les plates-formes de calcul hétérogènes d'aujourd'hui [TOP500] est requis pour traiter efficacement de telles instances. Le défi est alors d'exploiter tous les niveaux de parallélisme sous-jacents et donc de repenser en conséquence les modèles parallèles des algorithmes B&B. Dans cette thèse, nous nous attachons à revisiter la conception et l'implémentation des ces algorithmes pour la résolution de POC de grande taille sur (larges) plates-formes de calcul multi-coeurs et multi-GPUs. Le problème d'ordonnancement Flow-Shop (FSP) est considéré comme étude de cas.

Une étude expérimentale préliminaire sur quelques grandes instances du FSP a révélé que l'arbre de recherche est hautement irrégulier (en forme et en taille) et très large (milliards de milliards de noeuds), et que l'opérateur d'évaluation des bornes est exorbitant en temps de calcul (environ 97% du temps de B&B). Par conséquent, notre première contribution est de proposer une approche GPU avec un seul coeur CPU (GB&B) dans laquelle seul l'opérateur d'évaluation est exécuté sur GPU. L'approche traite deux défis: la divergence de threads [Chakroun et al., Concurrency and Computation: Practice and Experience 2012] et l'optimisation de la gestion de la mémoire hiérarchique du GPU [Melab et al., IEEE Cluster 2012]. Comparée à une version séquentielle, des accélérations allant jusqu'à (×100) sont obtenues sur Nvidia Tesla C2050. L'analyse des performances de GB&B a montré que le surcoût induit par le transfert des données entre le CPU et le GPU est élevé. Par conséquent, l'objectif de la deuxième contribution [Chakroun et al., ICCS 2013 est d'étendre l'approche (LL-GB&B) afin de minimiser la latence de communication CPU-GPU. Cet objectif est réalisé grâce à une parallélisation à grain fin sur GPU des opérateurs de séparation et d'élagage. Le défi majeur relevé ici est la divergence de threads qui est due à la nature fortement irrégulière citée ci-dessus de l'arbre exploré. Comparée à une exécution séquentielle, LL-GB&B permet d'atteindre des accélérations allant jusqu'à  $(\times 160)$  pour les plus grandes instances.

La troisième contribution [Chakroun et al., Journal of Parallel and Distributed Computing, 2013] consiste à étudier l'utilisation combinée des GPUs avec les processeurs multi-coeurs. Deux scénarios ont été explorés conduisant à deux approches: une concurrente (RLL-GB&B) et une coopérative (PLL-GB&B). Dans le premier cas, le processus d'exploration est effectué simultanément par le GPU et les coeurs du CPU. Dans l'approche

coopérative, les coeurs du CPU préparent et transfèrent les sous-problèmes en utilisant le "streaming CUDA" tandis que le GPU effectue l'exploration. L'utilisation combinée du multi-coeur et du GPU a montré que l'utilisation de RLL-GB&B n'est pas bénéfique et que PLL-GB&B permet une amélioration allant jusqu'à (36%) par rapport à LL-GB&B. Sachant que récemment des grilles de calcul comme Grid5000 (certains sites) ont été équipées avec des GPU, la quatrième contribution de cette thèse traite de la combinaison du calcul sur GPU et multi-coeur avec le calcul distribué à grande échelle. Pour ce faire, les différentes approches proposées ont été réunies dans un méta-algorithme hétérogène qui sélectionne automatiquement l'algorithme à déployer en fonction de la configuration matérielle cible. Ce méta-algorithme est couplé avec l'approche B&B@Grid proposée dans [Mezmaz et al., IEEE IPDPS'2007]. B&B@Grid répartit les unités de travail (sous-espaces de recherche codés par des intervalles) entre les noeuds de la grille tandis que le méta-algorithme choisit et déploie localement un algorithme de B&B parallèle sur les intervalles reçus. L'approche combinée nous a permis de résoudre à l'optimalité et efficacement les instances (20 × 20) de Taillard.

### Mots clés:

Branch-and-Bound Parallèlle, Calcul hétérogène, Processeurs Graphiques, Machines multi-coeurs, Problème d'ordonnancement du Flowshop, Grid'5000, Optimisation Combinatoire, Méthodes exactes.

### Acknowledgments

During these three years of PhD, I have been receiving help, support and encouragement from many people I would like to thank through these lines.

First of all, I would like to express my deepest gratitude to my supervisor Pr. Nouredine Melab. I thank him for the effort he put into training me in the scientific field. Thanks to his experience and encouragement I was able to conduct my research in the right direction despite the times doubt. I learned a lot of him during these years both professionally and personally. It was a pleasure to work with him.

I am also very much grateful to Dr. Mohand Mezmaz and Dr. Ahcène Bendjoudi for their generous help. I would like to thank them for sharing their time very often with me and for the scientific discussions we have held.

I am pleased to thank the members of my thesis examination committee: Pr. Pierre Manneback and Pr. Catherine Roucairol for reviewing this work, for spending their time on careful reading and for their many valuable comments on how to improve the thesis manuscript. I also thanks Pr. Pierre Boulet and Dr. Stephane Genaud for agreeing to examine my thesis defense.

I shall not forget my colleagues and friends I have known during these three years of PhD, with whom I had exchanged so many useful tips and valuable ideas and nice and happy moments: Khedidja Seridi, Rahma Yengui, Hajer Sassi, Karima Boufaras, Sana Cherif, Hana Krichen, Chiraz Trabelsi, Nadia Dahmani, Ines Bahri.

It is also a pleasure to thank all the people working in the Dolphin Team: Katerina, Sezin, Sophie, Marie-Eléonore, Julie, Julie, Bayrem, Mostepha Redouane, Thé Van, Moustapha, Mathieu, Tuan, Yacine, Martin.

These acknowledgments would not be complete without thanking my family for their constant support and care. Today I feel that my parents hard work and dreams have been blossomed. I thank my father Abdelrazzek, my mother Jamila and my sister Olfa. I also wish to extend my thanks to my family-in-law for their kind support.

Finally, I would like to mention two other people who are very important in my life: My husband Mahmoud and my little coming son. A warm thanks to Mahmoud for everything, for making me so happy, for his comprehension and for his unconditional support and encouragement during these three years.

# List of Figures

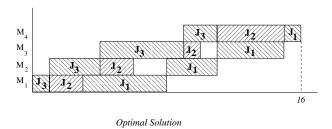

| 2.1 | Illustration of a permutation FSP with $n = 3$ and $m = 4$ . The table reports                                                 |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------|----|

|     | the processing times of the jobs on the machines. The Gantt diagram shows                                                      |    |

|     | the optimal solution to the problem instance                                                                                   | g  |

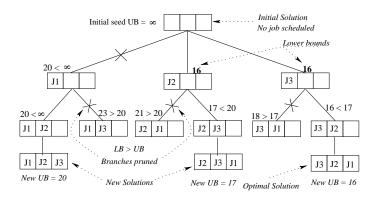

| 2.2 | The search tree generated and explored by a B&B algorithm for solving                                                          |    |

|     | an FSP with 3 jobs. Nodes with a lower bound (LB) greater (resp. lower                                                         |    |

|     | or equal) than the current best solution are pruned (resp. decomposed or                                                       |    |

|     | $branched). \dots \dots$ | 13 |

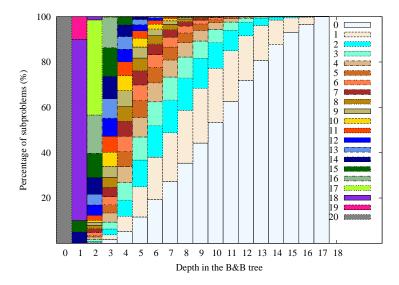

| 2.3 | Percentage of subproblems with corresponding number of children per depth                                                      |    |

|     | in the instance Ta023                                                                                                          | 15 |

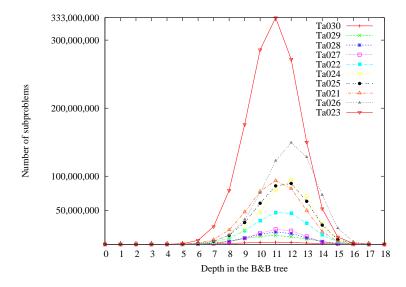

| 2.4 | Comparison of the structures of the 10 standard instances of FSP defined                                                       |    |

|     | with 20 jobs and 20 machines                                                                                                   | 16 |

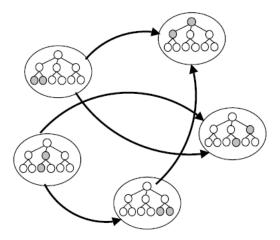

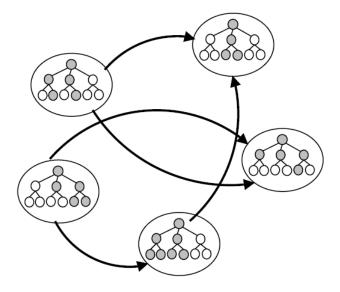

| 2.5 | Illustration of the parallel tree exploration model                                                                            | 17 |

| 2.6 | Illustration of the parallel multi-parametric model                                                                            | 18 |

| 2.7 | Illustration of the parallel evaluation of bounds model                                                                        | 19 |

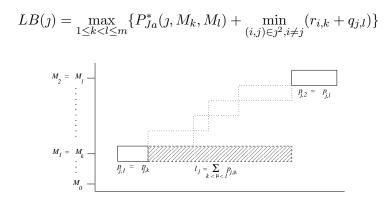

| 3.1 | The lag $l_j$ of a job $J_j$ for a couple $(k,l)$ of machines is the sum of the                                                |    |

|     | processing times of the job on all the machines between $k$ and $l$                                                            | 36 |

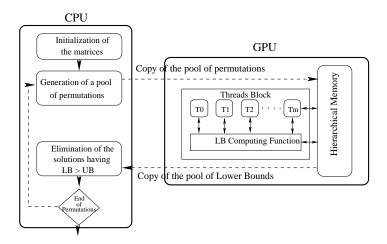

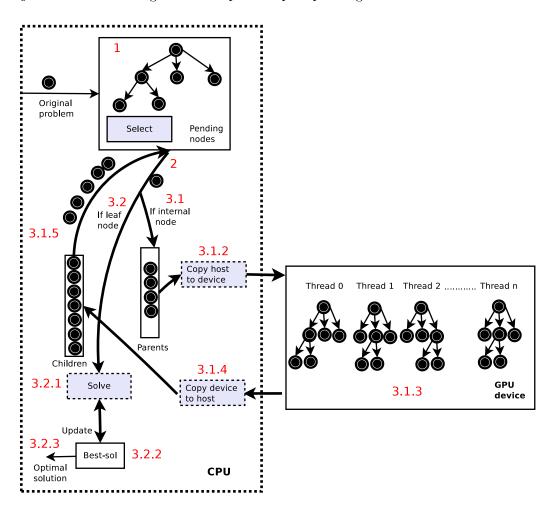

| 3.2 | The overall architecture of the GPU-accelerated algorithm based on the                                                         |    |

|     | parallel evaluation of bounds (GB&B)                                                                                           | 37 |

| 3.3 | Pseudo-code implementing the LB function                                                                                       | 45 |

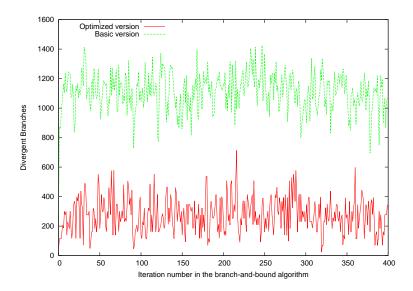

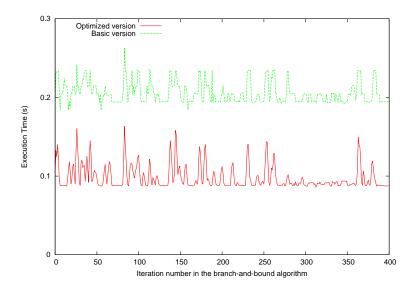

| 3.4 | Number of divergent branches with and without thread divergence reduction.                                                     | 56 |

| 3.5 | Elapsed time by the branches with and without thread divergence reduction.                                                     | 56 |

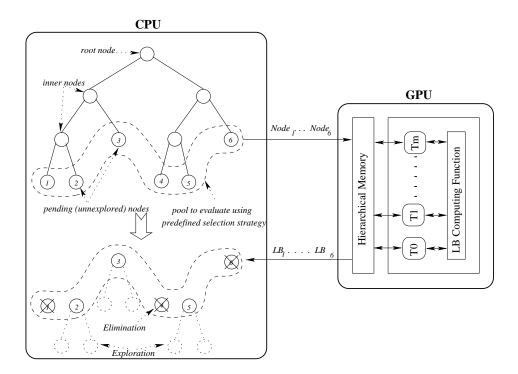

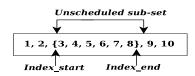

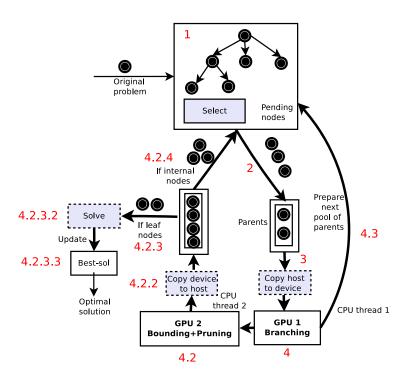

| 4.1 | The overall architecture of the GPU-accelerated B&B algorithm based on                                                         |    |

|     | the parallel evaluation of bounds. The approach introduces two main adap-                                                      |    |

|     | tations compared to a traditional $B\&B$ : selection of thousand of nodes and                                                  |    |

|     | evaluation in parallel                                                                                                         | 66 |

| 4.2 | The overall architecture of the multiple-nodes driven GPU-accelerated $B\&B$                                                   |    |

|     | algorithm.                                                                                                                     | 69 |

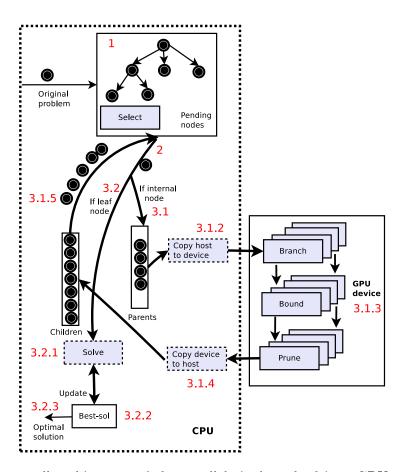

| 4.3 | Representation of a partial schedule associated with a subproblem. The                                                         |    |

|     | indexes between brackets correspond to unscheduled jobs                                                                        | 71 |

| 4.4 | The overall architecture of the parallel single-node driven GPU-accelerated                                                    |    |

|     | B&B algorithm                                                                                                                  | 73 |

viii List of Figures

| 4.5 | Comparison of memory location accesses in the multiple-nodes driven and single-node driven GPU-based branching operator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 76   |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

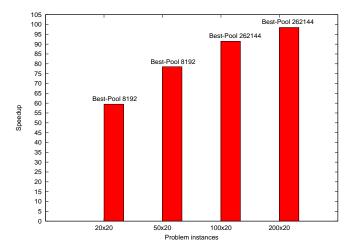

| 4.6 | The speedups and corresponding used pools obtained using the auto-tuned algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 78   |

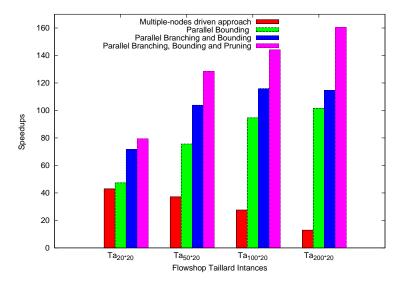

| 4.7 | Comparison of the speedups obtained with different GPU accelerated ver-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •    |

|     | sions of the B&B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 81   |

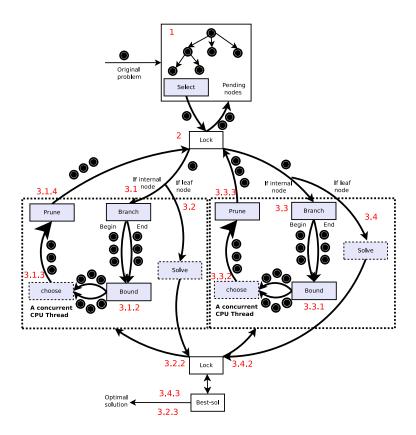

| 5.1 | Illustration of the multi-core B&B algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 88   |

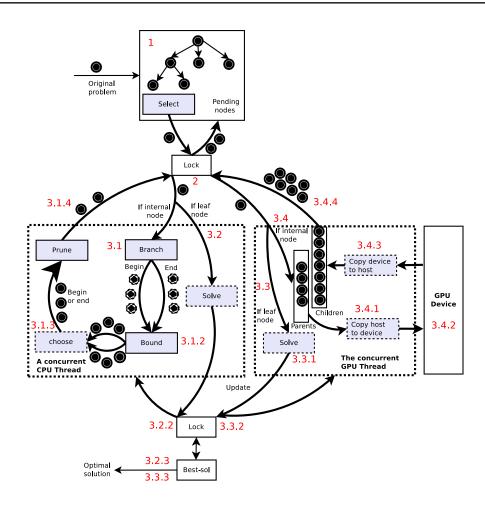

| 5.2 | Illustration of the ConcuRrent multi-core Low-Latency GPU-accelerated B&B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 90   |

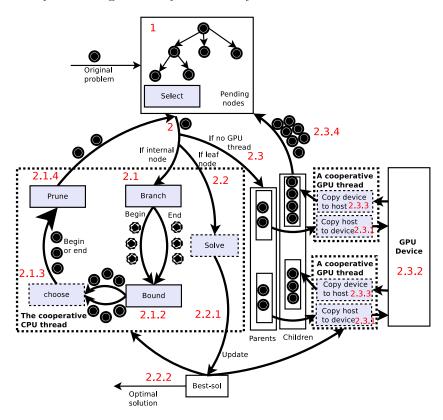

| 5.3 | Illustration of the cooperative multi-core low latency GPU-accelerated B&B $PLL$ - $GB$ $\mathcal{E}B$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 94   |

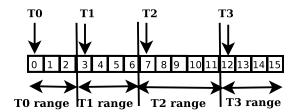

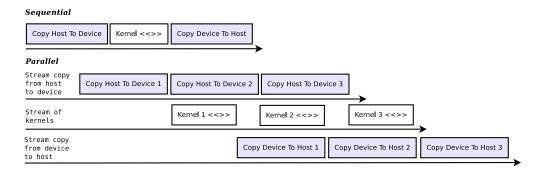

| 5.4 | Sequential and concurrent operations performed on GPU devices with compute capability 2.0. Two copy engine and a kernel engine enables concurrent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| 5.5 | transfer operations and kernel execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 95   |

|     | kernel is on GPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 98   |

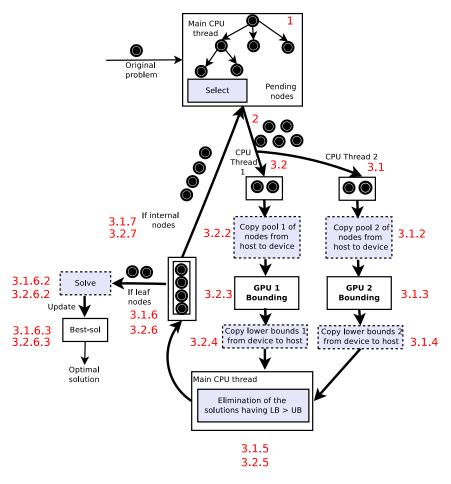

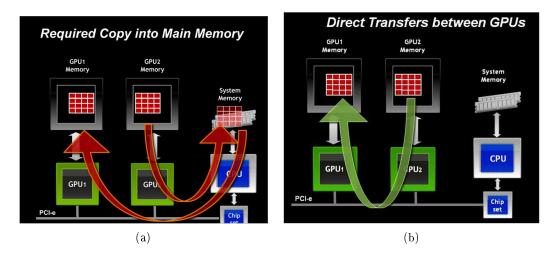

| 5.6 | Illustration of the Low Latency Multi-GPU B&B algorithm ( $LL$ - $MultiGB$ &B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .100 |

| 5.7 | Data transfer without Peer to Peer direct transfer memory (via CPU memory) (a) with Peer to Peer direct transfer memory (b) (direct between GPUs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|     | [NVIDIA Corporation 2011b]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 100  |

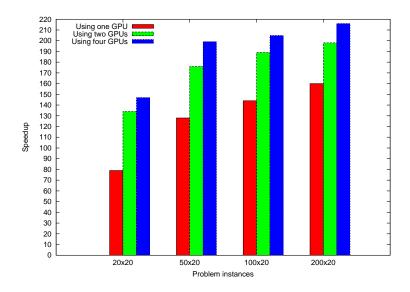

| 5.8 | Comparing the speedup for different problem instances using a single / multiple GPUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 106  |

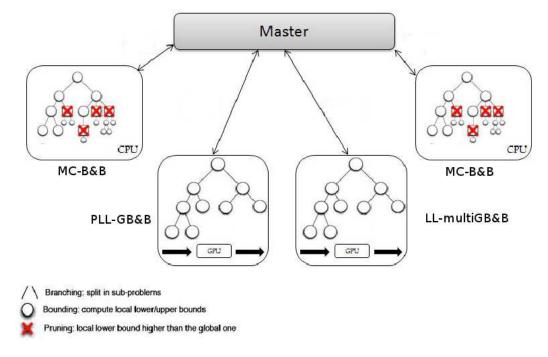

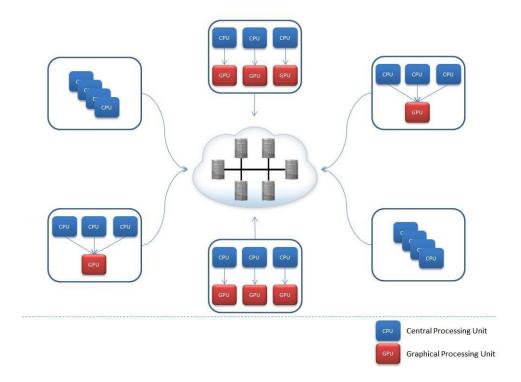

| 6.1 | Overview of the distributed heterogeneous B&B (HB&B@GRID)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 110  |

| 6.2 | A simplified representation of a cluster/grid that contains interconnected heterogeneous ressources with single/multiple CPUs and single/multiple                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|     | GPUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 111  |

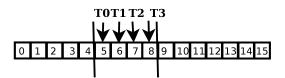

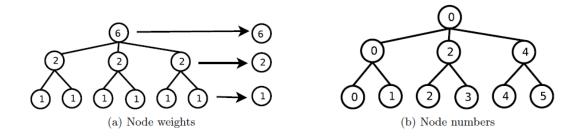

| 6.3 | The tree-based representation where each node has a unique number and contiguous nodes are represented by intervals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 114  |

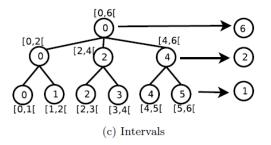

| 6.4 | The experimental computational grid Grid'5000 [Gri 2003]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 116  |

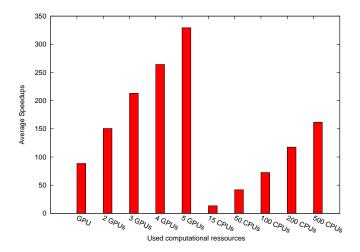

| 6.5 | Comparison between the GPU-based Branch and Bound and the CPU-based distributed version of the algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 121  |

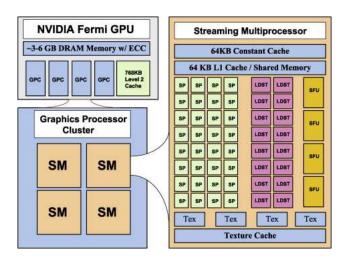

| A.1 | A simplified hardware block diagram for the NVIDIA Fermi GPU architectory (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Fermi GPU architectory (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Fermi GPU architectory (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Fermi GPU architectory (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Fermi GPU architectory (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Fermi GPU architectory (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Fermi GPU architectory (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Fermi GPU architectory (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Fermi GPU architectory (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Company (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Company (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Company (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Company (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Company (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Company (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Company (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Company (NVIDIA Company) and the simplified hardware block diagram for the NVIDIA Company (NVIDIA Co | 100  |

|     | ture [NVIDIA Corporation 2011b]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 138  |

List of Figures ix

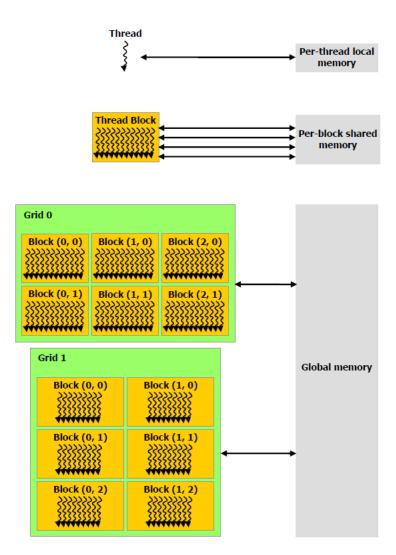

| A.2                        | CUDA hierarchy of threads, blocks and grids with corresponding per-       |  |  |  |

|----------------------------|---------------------------------------------------------------------------|--|--|--|

|                            | thread private, per-block shared and per-application global memory spaces |  |  |  |

| [NVIDIA Corporation 2011b] |                                                                           |  |  |  |

# List of Tables

| 3.1  | Execution time of the bounding operator compared to the execution time                                               |            |

|------|----------------------------------------------------------------------------------------------------------------------|------------|

|      | of the whole B&B algorithm.                                                                                          | 37         |

| 3.2  | The different data structures of the $LB$ algorithm and their associated                                             |            |

|      | complexities in memory size and numbers of accesses. The parameters $n$ ,                                            |            |

|      | m and $n'$ designate respectively the total number of jobs, the total number                                         |            |

|      | of machines and the number of remaining jobs to be scheduled for the                                                 |            |

|      | subproblems for which the lower bound is being computed                                                              | 46         |

| 3.3  | The sizes of each data structure for the different experimented problem                                              |            |

|      | instances. The sizes are given in number of elements and in bytes (between                                           |            |

|      | $brackets).  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $                               | 47         |

| 3.4  | Size of the data structures used the by each group of instance                                                       | 49         |

| 3.5  | Average normalized execution times as a function of the number of blocks                                             |            |

|      | and the number of threads per block                                                                                  | 50         |

| 3.6  | The serial resolution time of each instance according to its number of jobs                                          |            |

|      | and machines                                                                                                         | 52         |

| 3.7  | Speedups for different problem instances and pool sizes                                                              | 53         |

| 3.8  | Speedups for different problem instances and pool sizes using a sorted pool.                                         | 54         |

| 3.9  | Speedups for different instances and pool sizes using thread divergence man-                                         |            |

|      | agement                                                                                                              | 55         |

| 3.10 |                                                                                                                      |            |

|      | method.                                                                                                              | 57         |

| 3.11 | Speedups for different problem instances and pool sizes obtained with data                                           |            |

|      | access optimization. $PTM$ , $RM$ , $QM$ and $MM$ are placed in the GPU                                              | <b>-</b> - |

| 0.10 | shared memory. $JM$ and $LM$ are copied to the global memory                                                         | 58         |

| 3.12 | Speedups for different problem instances and pool sizes obtained with data                                           |            |

|      | access optimization. $JM$ , $RM$ , $QM$ and $MM$ are placed in the GPU                                               | ۲.         |

| 9 19 | shared memory. $PTM$ and $LM$ are copied to the global memory                                                        | 59         |

| 3.13 | Speedups for different problem instances and pool sizes obtained with data                                           |            |

|      | access optimization. $PTM$ and $JM$ are placed together in shared memory and all others are placed in global memory. | 60         |

| 2 11 |                                                                                                                      |            |

| J.14 | Percentage of time consumed by each step of the parallel bounding approach.                                          | υl         |

| 4.1  | Parallel speedup measured for different problem instances and pool sizes                                             |            |

|      | without using the ASH heuristic.                                                                                     | 79         |

xii List of Tables

| 4.2 | Speedups reported for the two approaches of the GPU-based B&B                                                            | 79  |

|-----|--------------------------------------------------------------------------------------------------------------------------|-----|

| 4.3 | Speedup calculated with the parallelization of each operator                                                             | 81  |

| 4.4 | Comparison of the amount of data transfer with the different parallelization                                             |     |

|     | approaches.                                                                                                              | 82  |

| 5.1 | Obtained speedups using the $(MC\text{-}B\mathcal{C}B)$ approach where no GPU is used.                                   | 103 |

| 5.2 | Obtained speedups using the $RLL\text{-}GB\ensuremath{\mathcal{C}B}\ensuremath{\mathcal{C}B}$ approach with a single GPU | 104 |

| 5.3 | Average normalized waiting times spent by the concurrent GPU thread                                                      |     |

|     | when accessing global data structures.                                                                                   | 104 |

| 5.4 | Obtained speedups using the $PLL$ - $GB \& B$ approach where the cooperative                                             |     |

|     | CPU thread does not perform the exploration of subproblems                                                               | 105 |

| 5.5 | Obtained speedups using the $PLL$ - $GB$ $\&B$ approach where the collaborative                                          |     |

|     | CPU threads explores nodes in parallel to the GPU execution                                                              | 105 |

| 6.1 | Configurations of the distributed machines used for the experiments on                                                   |     |

|     | Grid'5000                                                                                                                | 118 |

| 6.2 | Sequential resolution times (seconds) for the instances Ta021-Ta030 corre-                                               |     |

|     | sponding to the group of instances with 20 jobs and 20 machines                                                          | 119 |

| 6.3 | Execution times (seconds) for the instances Ta021 to Ta030 using different                                               |     |

|     | scales of the distributed CPU-based version of the B&B                                                                   | 120 |

| 6.4 | Execution times (seconds) for the instances Ta021 to Ta030 using different                                               |     |

|     | scales of the distributed GPU-accelerated version of the B&B                                                             | 121 |

# Contents

| 1 | Intr | ntroduction |                                                                     |  |  |

|---|------|-------------|---------------------------------------------------------------------|--|--|

| 2 | Par  | allel B     | ranch and Bound algorithms                                          |  |  |

|   | 2.1  | Introd      | luction to combinatorial optimization                               |  |  |

|   |      | 2.1.1       | The Permutation Flowshop Scheduling Problem                         |  |  |

|   |      | 2.1.2       | Resolution methods for combinatorial optimization problems          |  |  |

|   | 2.2  | Branc       | h and Bound algorithms                                              |  |  |

|   |      | 2.2.1       | Serial B&B                                                          |  |  |

|   |      | 2.2.2       | Illustration on the Permutation Flowshop Scheduling Problem         |  |  |

|   |      | 2.2.3       | Analysis of the irregularity of the B&B algorithm                   |  |  |

|   | 2.3  | Parall      | el Branch-and-Bound algorithms                                      |  |  |

|   |      | 2.3.1       | Parallel tree exploration model                                     |  |  |

|   |      | 2.3.2       | Parallel multi-parametric model                                     |  |  |

|   |      | 2.3.3       | Parallel evaluation of the bounds                                   |  |  |

|   |      | 2.3.4       | Parallel evaluation of a single bound/solution                      |  |  |

|   | 2.4  | Parall      | el B&B for Graphics Processing Units                                |  |  |

|   |      | 2.4.1       | Thread divergence                                                   |  |  |

|   |      | 2.4.2       | Memory access optimization                                          |  |  |

|   |      | 2.4.3       | CPU-GPU communication optimization                                  |  |  |

|   |      | 2.4.4       | Related works                                                       |  |  |

|   | 2.5  | Parall      | el B&B for multi-core shared memory machines                        |  |  |

|   |      | 2.5.1       | Synchronization and caching issues                                  |  |  |

|   |      | 2.5.2       | Related works                                                       |  |  |

|   | 2.6  | Parall      | el B&B for computational grids                                      |  |  |

|   |      | 2.6.1       | Challenging issues                                                  |  |  |

|   |      | 2.6.2       | Related works                                                       |  |  |

|   | 2.7  | Concl       | usion                                                               |  |  |

| 3 | GP   | U-acce      | elerated parallel bounding applied to FSP                           |  |  |

|   | 3.1  | Introd      | luction                                                             |  |  |

|   | 3.2  | Lower       | Bound for FSP                                                       |  |  |

|   | 3.3  | A GP        | U-accelerated B&B based on the parallel evaluation of bounds (GB&B) |  |  |

|   | 3.4  | Threa       | d divergence reduction                                              |  |  |

|   |      | 3 4 1       | Problem statement in the FSP lower bound                            |  |  |

xiv Contents

|   |      | 3.4.2 Mechanisms for reducing branch divergence                              | 40        |  |  |  |

|---|------|------------------------------------------------------------------------------|-----------|--|--|--|

|   | 3.5  | Data placement optimization for the FSP lower bound                          | 44        |  |  |  |

|   |      | 3.5.1 Complexity analysis and implementation                                 | 44        |  |  |  |

|   |      | 3.5.2 Data placement pattern of the lower bound on GPU                       | 46        |  |  |  |

|   | 3.6  | Experiments                                                                  | 48        |  |  |  |

|   |      | 3.6.1 Experimental settings and parameters tuning                            | 48        |  |  |  |

|   |      | 3.6.2 Experimental protocol                                                  | 51        |  |  |  |

|   |      | 3.6.3 Performance Evaluation of the GB&B                                     | 53        |  |  |  |

|   |      | 3.6.4 Performances of the thread reduction approaches                        | 54        |  |  |  |

|   |      | 3.6.5 Performances of the data access optimizations                          | 58        |  |  |  |

|   |      | 3.6.6 Overhead characterization of the GPU-accelerated parallel bounding     |           |  |  |  |

|   |      | operator                                                                     | 60        |  |  |  |

|   | 3.7  | Conclusion                                                                   | 61        |  |  |  |

| 4 | GP   | U-based parallel tree exploration                                            | 63        |  |  |  |

|   | 4.1  | Introduction                                                                 | 64        |  |  |  |

|   | 4.2  | An adaptive selection operator based on a dynamic parameter tuning heuristic | 66        |  |  |  |

|   | 4.3  | The multiple-nodes driven GPU-accelerated approach                           | 68        |  |  |  |

|   |      | 4.3.1 Branching Operator                                                     | 70        |  |  |  |

|   |      | 4.3.2 Pruning Operator                                                       | 70        |  |  |  |

|   |      | 4.3.3 Synthesis                                                              | 71        |  |  |  |

|   | 4.4  | The single-node driven GPU-accelerated B&B                                   | 73        |  |  |  |

|   |      | 4.4.1 Branching Operator                                                     | 75        |  |  |  |

|   |      | 4.4.2 Pruning operator                                                       | 76        |  |  |  |

|   |      | 4.4.3 Synthesis                                                              | 77        |  |  |  |