# Etude de la variabilité en technologie FDSOI: du transistor aux cellules mémoires SRAM

Jérôme Mazurier

#### ▶ To cite this version:

Jérôme Mazurier. Etude de la variabilité en technologie FDSOI: du transistor aux cellules mémoires SRAM. Autre. Université de Grenoble, 2012. Français. NNT: 2012GRENT058. tel-00845680

## HAL Id: tel-00845680 https://theses.hal.science/tel-00845680

Submitted on 17 Jul 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ DE GRENOBLE

### **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Nano Électronique et Nano Technologies Arrêté ministériel : 7 août 2006

Présentée par

#### Jérôme MAZURIER

Thèse dirigée par Marc BELLEVILLE et codirigée par Olivier WEBER

préparée au sein du CEA LETI dans l'École Doctorale Electronique, Electrotechnique, Automatique et Traitement du Signal

# Etude de la variabilité en technologie FDSOI : du transistor aux cellules mémoires SRAM

Thèse soutenue publiquement le 24 octobre 2012, devant le jury composé de :

Monsieur, Gérard, GHIBAUDO

Directeur de recherche à l'IMEP-LAHC (Président)

Monsieur, Amara, AMARA

Professeur à l'ISEP (Rapporteur)

Monsieur, Jean Luc, AUTRAN

Professeur à l'Université d'Aix Marseille (Rapporteur)

Monsieur, Marc, BELLEVILLE

Directeur de recherche au CEA LETI (Directeur de thèse)

Monsieur, Olivier, WEBER

Ingénieur de recherche au CEA LETI (Co-encadrant)

Monsieur, Michel, HAOND

Directeur technique à STMicroelectronics (Membre)

Monsieur, Liviu, MILITARU

Maître de conférences à l'INSA de Lyon (Membre)

Université Joseph Fourier / Université Pierre Mendès France / Université Stendhal / Université de Savoie / Grenoble INP

| « La statistique est moins une science qu'un art. Elle est la poésie des nombres.<br>Chacun y trouve ce qu'il y met. » |

|------------------------------------------------------------------------------------------------------------------------|

| Albert BRIE, Le mot du silencieux (L'hiver nous fait suer), Le Devoir                                                  |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

|                                                                                                                        |

## Remerciements

Cette thèse a été réalisée au Commissariat à l'Energie Atomique et aux Energies Alternatives (CEA) de Grenoble, au sein du Laboratoire d'Electronique de Technologie de l'Information (LETI), dans le Département des COmposants Silicium (DCOS) et dans le Laboratoire des Dispositifs Innovants (LDI), dirigé successivement par Olivier Faynot et Thierry Poiroux. Je les remercie tous les deux pour m'avoir accueilli au LDI.

Les résultats présentés dans ce manuscrit sont le fruit d'une étroite collaboration avec les entreprises de STMicrolectronics à Crolles, de SOITEC à Bernin et finalement de IBM à Albany (Etats-Unis).

J'adresse mes remerciements à l'ensemble des membres du jury pour avoir pris le temps d'évaluer ce travail. Merci à Gérard Ghibaudo, Directeur de l'IMEP-LAHC d'avoir présider mon jury. Merci à Jean-Luc Autran, Professeur à l'Université d'Aix-Marseille et à Amara Amara, Directeur de la recherche à l'ISEP, pour m'avoir fait l'honneur d'être les rapporteurs de cette étude. Merci enfin à Michel Haond et Liviu Militaru pour avoir accepté d'examiner mon travail.

J'exprime toute ma reconnaissance à mon directeur de thèse, Marc Belleville, pour sa disponibilité et son implication tout au long de ces trois années de thèse. Il a apporté à mes recherches le regard du concepteur, indispensable lors du développement d'une technologie en microélectronique, en plus du point de vue du technologue qui lui m'a été inculqué par mes collègues de laboratoire.

Je tiens à remercier Olivier Weber pour son aide et son soutien en tant qu'encadrent. Tes nombreuses connaissances scientifiques ont permis de me guider durant ces trois années, sans jamais montrer un signe de faiblesse. Je suis honoré d'avoir pu être ton premier thésard. Enfin, merci de m'avoir épaulé lors des deadlines, jusqu'à peaufiner les derniers détails à des heures relativement déraisonnables. J'en profite également pour témoigner ma reconnaissance envers François Andrieu qui aura toujours pris le temps pour m'aider, notamment suite au départ d'Olivier pour le site de Crolles. Tes conseils ont été extrêmement bénéfiques lors de l'accomplissement de cette thèse.

Je souhaite remercier Claude Tabone, maitre du SIAM 5 (après Georges, bien sûr), qui m'aura enseigné toutes les manipulations permettant de caractériser les transistors. Merci également pour m'avoir aidé de nombreuses fois dans l'analyse électrique des lots. Enfin, un grand merci pour ton optimisme inébranlable (le célèbre « Tout va bien ») et ton enthousiasme lors de l'analyse des courbes de rendement...

Je tiens maintenant à remercier tout particulièrement Fabienne Allain et Alain Toffoli pour tout le temps qu'ils m'ont consacré, ainsi que pour m'avoir donné l'opportunité de tester de manière automatisée une quantité astronomique de dispositifs, me permettant ainsi d'étudier en détail la variabilité en technologie FDSOI. Merci également à Rabah Kies et Giovanni Romano pour avoir eu l'occasion de lancer des tests pour moi. Voici quelques chiffres permettant d'illustrer ce travail de caractérisation électrique. Ces trois années de thèse se sont traduites par l'étude de 30 lots électriques (soit 212 plaques), représentant un total de 2.154.888 transistors mesurés, obtenus grâce à 4275 heures de test. Record battu!

Cependant, tous ces dispositifs n'auraient pas pu voir le jour sans le travail du personnel des salles blanches du LETI et de STMicroelectronics, ainsi que des techniciens filière responsables du

suivi quotidien des lots. Je remercie donc Lucie Tosti, Laurent Brevard et Pierre Perreau pour toute l'aide qu'ils m'ont apportée.

J'adresse également mes remerciements à Marie-Anne Jaud et Olivier Rozeau pour avoir toujours pris le temps de me conseiller lors des périodes de doute, ainsi que pour m'avoir formé respectivement en TCAD et en modélisation compacte.

Merci à Maryline Cordeau et Nicolas Chevalier pour le temps qu'ils m'ont consacré dans l'acquisition et l'analyse des mesures AFM.

Je souhaite remercier les différentes personnes du LETI avec qui j'ai eu l'occasion de travailler durant cette thèse (Thierry Poiroux, Georges Guegan, Bernard Previtali, Cyrille Le Royer, Krunoslav Romanjek, Mikaël Cassé, Xavier Garros, Maud Vinet, Perrine Batude, Sylvain Barraud, Thomas, Ernst, Romain Wacquez, Phuong Nguyen, Claire Fenouillet-Beranger, Yves Morand, Olivier Thomas, Laurent Grenouillet), celles de ST (Frédéric Bœuf, Nicolas Planes, Michel Haond, Franck Arnaud, Aurélie Bajolet, ...) et celles de SOITEC (Walter Schwarzenbach, Nicolas Daval, Bich-Yen Nguyen, Konstantin Bourdelle, Pablo-Eduardo Acosta-Alba ...).

Merci évidemment à tous les stagiaires et thésards que j'ai vu passer : Alexandre Hubert, Sophie Baudot, Kiichi Tachi, Lia Masero, Marine Gasulla, Siméon Morvan, Gabriele Navarro, Anthony Villalon, Heimanu Niebojewski, Cuiqin Xu, Veeresh Deshpande, Mylène Clavel, Louis Hutin, Jean-Paul Mazellier, Manan Suri, Matthieu Berthome, Jean-Philippe Noel, et bien d'autres.

Pour finir, merci à ma famille et à mes amis pour m'avoir soutenu durant ces trois années.

# Table des matières

| REMERCIEMENTS                                                                                                                                       | 4    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| TABLE DES MATIERES                                                                                                                                  | 6    |

| LISTE DES ACRONYMES                                                                                                                                 | 9    |

| INTRODUCTION GENERALE                                                                                                                               | .13  |

| CHAPITRE 1                                                                                                                                          | .16  |

| PRESENTATION DE LA TECHNOLOGIE METAL-OXYDE-SEMICONDUCTEUR ET DE<br>LA PROBLEMATIQUE DE LA VARIABILITE POUR LE NŒUD TECHNOLOGIQUE<br>32NM ET EN DEÇA | .16  |

| 1.1. Introduction                                                                                                                                   | . 17 |

| 1.2. Technologie des transistors MOS à effet de champ                                                                                               |      |

| 1.2.1. Le transistor MOS : principe et régimes de fonctionnement                                                                                    | . 17 |

| 1.2.1.a. Principe de fonctionnement et architecture                                                                                                 | . 17 |

| 1.2.1.b. Régimes de fonctionnement                                                                                                                  | . 19 |

| 1.2.2. Effets de canaux courts et abaissement de la barrière de conduction induite par le                                                           |      |

| drain                                                                                                                                               |      |

| 1.3. Amélioration des performances grâce à la technologie FDSOI                                                                                     |      |

| 1.3.1. Présentation de la technologie SOI                                                                                                           | . 22 |

| 1.3.2. Architecture et procédés de fabrication des transistors FDSOI                                                                                | 24   |

| 1.3.3. Améliorations obtenues grâce à l'utilisation d'un film de silicium et d'un oxyde enterré minces avec back-plane                              | 25   |

| 1.4. La problématique de la variabilité en microélectronique                                                                                        |      |

| 1.4.1. Variabilité systématique                                                                                                                     |      |

| 1.4.2. Variabilité stochastique                                                                                                                     |      |

| 1.4.3. Impact de la variabilité sur les circuits                                                                                                    | 31   |

| 1.4.3.a. Cellule mémoire SRAM                                                                                                                       |      |

| 1.4.3.b. Circuits analogiques                                                                                                                       |      |

| 1.4.4. Sources de variabilité stochastique du V <sub>T</sub> en technologie FDSOI                                                                   |      |

| 1.4.4.a. Influence des dopants dans le canal de conduction                                                                                          |      |

| 1.4.4.b. Sources liées aux effets de canaux courts                                                                                                  |      |

| 1.4.4.c. Contribution de l'empilement de grille                                                                                                     |      |

| 1.5. Conclusion                                                                                                                                     |      |

| 1.6. Références bibliographiques                                                                                                                    |      |

|                                                                                                                                                     |      |

| CHAPITRE 2                                                                                                                                          | 48   |

| ETUDE EXPERIMENTALE DE LA VARIABILITE DE LA TENSION DE SEUIL EN TECHNOLOGIE FDSOI                                                                   | 48   |

| 2.1. Introduction                                                                                                                                   | . 49 |

| 2.2. Variabilité de la tension de seuil en technologie UTBB                                                                                         | 50   |

| 2.2.1. Modulation de la tension de seuil par polarisation du BP                                                                                     | 50   |

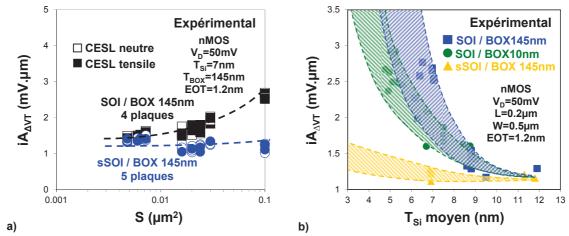

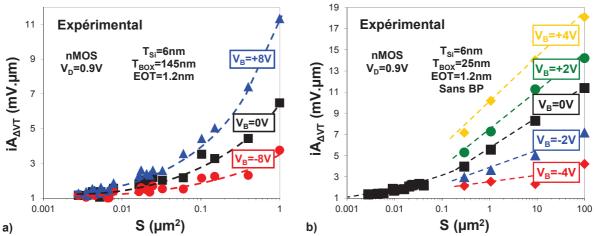

| 2.2.2. Influence de l'oxyde enterré mince et de l'implantation des BP sur l'appariement des transistors                                             | 50   |

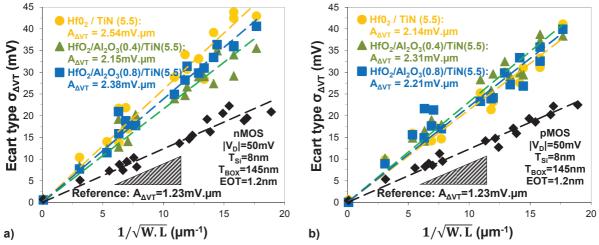

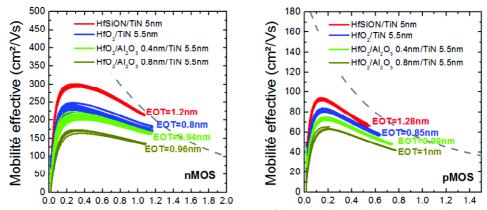

| 2.3. Modulation de la tension de seuil par l'empilement de grille et impact sur la variabilité                                                      |      |

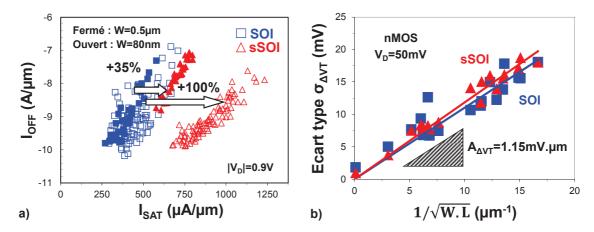

| 2.4. Utilisation de substrats sSOI à film mince contraint                                                                                           | . 54 |

| 2.5. Conclusion                                                                                                                                     |      |

| 2.6. Références bibliographiques                                                                                                                    |      |

|                                                                                                                                                     |      |

| CHAPITRE 3                                                                                                               | 59      |

|--------------------------------------------------------------------------------------------------------------------------|---------|

| ETUDE DE LA VARIABILITE DES CARACTERISTIQUES ELECTRIQUES SNM ET WM<br>DE CELLULES MEMOIRES SRAM EN TECHNOLOGIE FDSOI     | !<br>59 |

| 3.1. Introduction                                                                                                        | 60      |

| 3.2. Figures de mérite des cellules mémoires SRAM                                                                        |         |

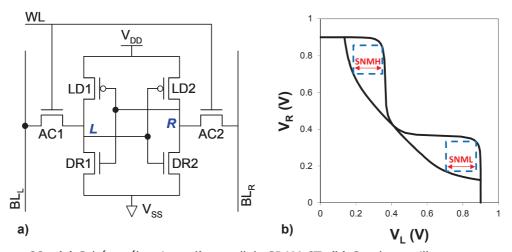

| 3.2.1. Fonctionnement de la cellule mémoire                                                                              | 60      |

| 3.2.2. Mesure de la variabilité de la stabilité en lecture et en écriture                                                | 63      |

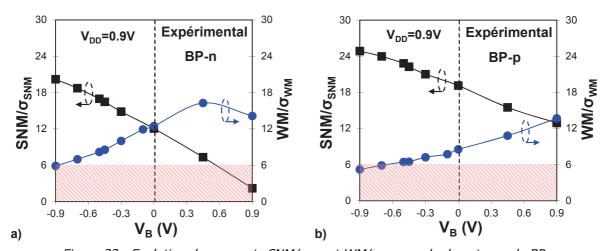

| 3.3. Impact de la polarisation des BP sur la variabilité des cellules SRAM                                               | 64      |

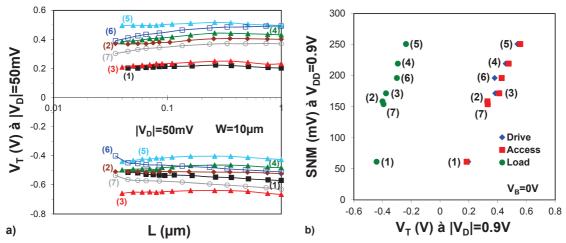

| 3.4. Corrélations entre les caractéristiques électriques de transistors MOS et de cellules                               |         |

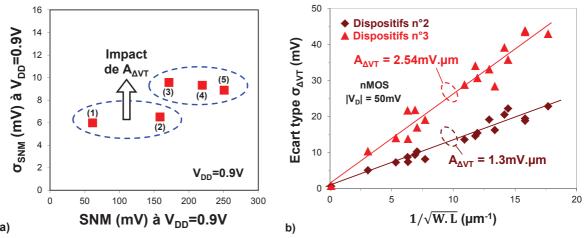

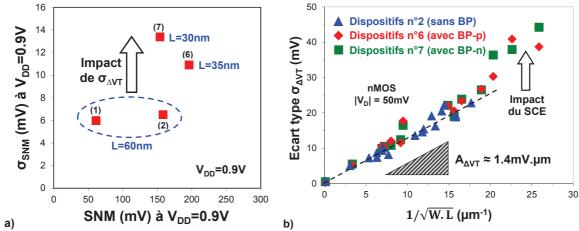

| mémoires SRAM                                                                                                            | 66      |

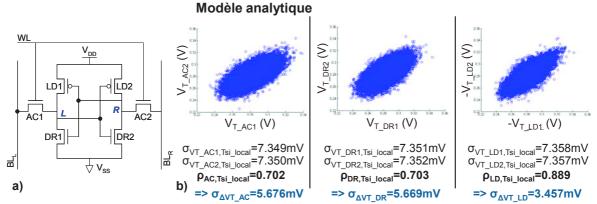

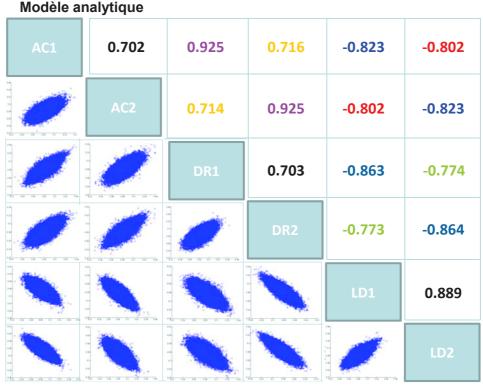

| 3.5. Modèle analytique de variabilité de la SNM                                                                          | 69      |

| 3.6. Modélisation compacte de cellules mémoires SRAM                                                                     |         |

| 3.7. Conclusion                                                                                                          |         |

| 3.8. Références bibliographiques                                                                                         |         |

| CHAPITRE 4                                                                                                               | 77      |

| ETUDE EXPERIMENTALE DE LA VARIABILITE DU COURANT DE DRAIN EN<br>TECHNOLOGIE FDSOI                                        | 77      |

| 4.1. Introduction                                                                                                        |         |

| 4.2. Mesures expérimentales de la variabilité du courant de drain                                                        | 78      |

| 4.3. Etude des corrélations existantes entre les différentes caractéristiques électriques du transistor MOS              |         |

| 4.4. Facteurs technologiques limitant la variabilité du courant de drain                                                 |         |

| 4.5. Conclusion                                                                                                          |         |

| 4.6. Références bibliographiques                                                                                         |         |

| CHAPITRE 5                                                                                                               |         |

| IMPACT DE L'UNIFORMITE DU FILM DE SILICIUM SUR LA VARIABILITE DES<br>TRANSISTORS MOS ET DES CIRCUITS SRAM                |         |

| 5.1. Introduction                                                                                                        | 87      |

| 5.2. Analyse expérimentale de la variabilité du V <sub>T</sub> sur des transistors FDSOI ayant un film de silicium mince | 87      |

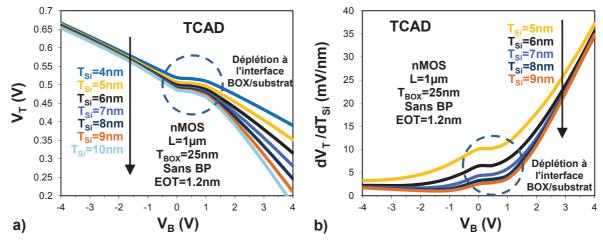

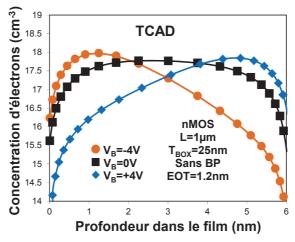

| 5.3. Etude TCAD de la dérivée dV <sub>T</sub> /dT <sub>Si</sub> : dépendance avec la position du barycentre de           |         |

| porteurs dans le canal                                                                                                   |         |

| 5.4. Développement d'un modèle analytique basé sur des mesures AFM                                                       | 95      |

| 5.5. Influence des fluctuations de T <sub>Si</sub> sur la variabilité globale des transistors et des circuits            | 100     |

| mémoires SRAM                                                                                                            |         |

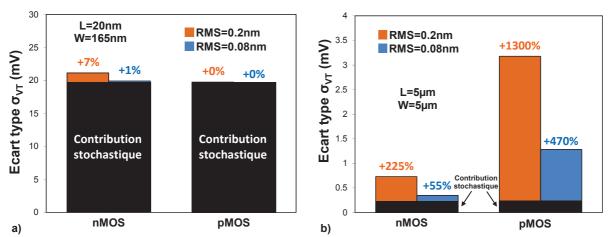

| 5.5.1. Transistors nMOS (canal Si) et pMOS (canal SiGe)                                                                  |         |

| 5.5.1.b. Dispositifs pour les circuits analogiques (L=W=5µm)                                                             |         |

| 5.5.1.c. Influence de la rugosité RMS sur la variabilité globale                                                         |         |

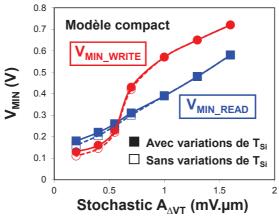

| 5.5.2. Circuit SRAM de 200Mb                                                                                             |         |

| 5.6. Conclusion                                                                                                          |         |

| 5.7. Références bibliographiques                                                                                         | 113     |

| CONCLUSION GENERALE                                                                                                      | 116     |

| ANNEXE A                                                                                                                 | 120     |

| A.1. Structures de test                                                                                                  |         |

| A.2. Distribution gaussienne                                                                                             |         |

| A.2.1. Moyenne et écart type                                                                                             |         |

| A.2.2. Test du khi-deux                                                                                                  |         |

| A.3. Filtrage de données                                                                                                 |         |

| A.4. Intervalle de confiance                                                                                             |         |

|                                                                                                                          | 1/4     |

| A.6. Méthodes d'extraction de la tension de seuil | 126 |

|---------------------------------------------------|-----|

| ANNEXE B                                          | 128 |

| BIBLIOGRAPHIE GENERALE                            |     |

| LISTE DES PUBLICATIONS                            | 145 |

| RESUME                                            | 148 |

| ABSTRACT                                          | 148 |

## Liste des acronymes

Α

AC Transistors nMOS d'accès (SRAM) AFM Microscopie à Force Atomique

$A_{\Delta VT}$  Paramètre d'appariement de la tension de seuil

В

Band-gap Largeur de la bande interdite (=1.11eV à 300K, c'est-à-dire environ 27°C)

BL<sub>L</sub>/BL<sub>R</sub> Lignes de bit dans les matrices SRAM (*Bit-Line*)

BOX Oxyde enterré

BP Plan de masse (*Back Plane*)

BP-n BP de type n BP-p BP de type p

Bulk Transistor sur silicium massif

C

C<sub>DEP</sub> Capacité de déplétion

CESL Couche d'arrêt à la gravure des contacts

CMOS Transistors Métal-Oxyde-Semiconducteur complémentaires

Cox Capacité de l'oxyde de grille

C<sub>SS</sub> Capacité liée à la qualité des états d'interfaces

cSiGeOI Compressive SiGe on Insulator

χ Affinité électronique du semiconducteur (=4.1eV pour le silicium)

**D**, Δ

DIBL Abaissement de la barrière de potentiel par polarisation du drain

DR Transistors nMOS de décharge (SRAM)

D° Position moyenne de la zone de transition à partir de laquelle le travail de sortie

évolue, dans les directions L et W

ΔD Distance séparant les zones actives de deux transistors adjacents

ΔDIBL Différence de DIBL entre deux transistors adjacents  $\Delta I_D$ Différence de I<sub>D</sub> entre deux transistors adjacents  $\Delta I_{LIN}$ Différence de I<sub>LIN</sub> entre deux transistors adjacents  $\Delta I_{OFF}$ Différence de I<sub>OFF</sub> entre deux transistors adjacents Différence de I<sub>SAT</sub> entre deux transistors adjacents  $\Delta I_{SAT}$ Différence de R<sub>ON</sub> entre deux transistors adjacents  $\Delta R_{ON}$ Différence de SS<sub>SAT</sub> entre deux transistors adjacents  $\Delta SS_{SAT}$  $\Delta V_T$ Différence de V<sub>T</sub> entre deux transistors adjacents  $\Delta V_{T\_LIN}$ Différence de V<sub>T\_LIN</sub> entre deux transistors adjacents  $\Delta V_{T\_SAT}$ Différence de V<sub>T\_SAT</sub> entre deux transistors adjacents

Ε, ε

E<sub>F</sub> Niveau de Fermi

E<sub>G</sub> Largeur de la bande interdite séparant la bande de conduction de la bande de valence

(1.12eV à 300K, c'est-à-dire environ 27°C)

$\begin{array}{ll} \text{EOT} & \text{Epaisseur de di\'electrique \'equivalente \`a du SiO}_2 \\ \epsilon_o & \text{Permittivit\'e\'e \'electrique du vide (=8.85x10^{-12} \text{ F/m})} \\ \epsilon_{OX} & \text{Permittivit\'e\'electrique d'un oxyde (=3.9x$\epsilon_o)} \\ \epsilon_{Si} & \text{Permittivit\'e\'electrique du silicium (=11.9x$\epsilon_o)} \end{array}$

F

FDSOI Transistor complétement déserté sur silicium sur isolant

G

G<sub>m</sub> Transconductance

$\gamma$  Facteur de couplage (=  $\Delta V_T / \Delta V_B$ )

$\gamma_{BC}$  Facteur de couplage correspondant à une conduction à l'interface arrière  $\gamma_{FC}$  Facteur de couplage correspondant à une conduction à l'interface avant

Н

High-k Diélectrique de grille ayant une haute permittivité

HVT  $High V_T$

h Constante de Planck réduite (=1.054x10<sup>-34</sup> J.s)

Ι

iA<sub>ΔVT</sub> Paramètre d'appariement individuel de la tension de seuil pour une géométrie L/W

I<sub>CELL</sub> Courant de lecture de la donnée (SRAM)

I<sub>D</sub> Courant de drain

I<sub>DB</sub> Courant entre le drain et le substrat

I<sub>G</sub> Courant de grille

$\begin{array}{ll} I_{\text{GB}} & \text{Courant tunnel entre la grille et le substrat} \\ I_{\text{GD}} & \text{Courant tunnel entre la grille et le drain} \\ I_{\text{GS}} & \text{Courant tunnel entre la grille et la source} \end{array}$

$\begin{array}{ll} I_{LIN} & \text{Courant de drain en régime ohmique } (V_G = V_{DD} \; ; \; V_D = 50 \text{mV}) \\ I_{OFF} & \text{Courant de fuite en régime de saturation } (V_G = 0V \; ; \; V_D = V_{DD}) \\ I_{SAT} & \text{Courant de drain en régime de saturation } (V_G = V_{DD} \; ; \; V_D = V_{DD}) \end{array}$

I<sub>SB</sub> Courant entre la source et le substrat (MOSFET) ou consommation de la cellule en

mode de rétention (SRAM)

ITRS International Technology Roadmap for Semiconductors

K

$k_B$  Constante de Boltzmann (=1.38x10<sup>-23</sup> J/K = 8.62x10<sup>-5</sup> eV/K)

k<sub>high-k</sub> Constante diélectrique du *high-k* k<sub>SiO2</sub> Constante diélectrique du SiO<sub>2</sub>

L

L Longueur de grille

LD Transistors pMOS de charge (SRAM)

Leff Leg Longueur effective du canal de conduction

Rugosité en bord de grille (*Line Edge Roughness*)

LVT Low  $V_T$

Μ, μ

m\* Masse effective de confinement des porteurs.

MOSFET Transistor Metal-Oxyde-Semiconductor à effet de champ

$\mu_{\text{EFF}}$  Mobilité effective des porteurs

N

N<sub>A</sub> Densité de dopants dans le film de silicium

N<sub>BP</sub> Densité de dopants dans le BP

n<sub>i</sub> Densité intrinsèque de porteurs dans le silicium (=1.137x10<sup>10</sup> cm<sup>-3</sup> à 300K)

Ρ, Φ, ψ

PDSOI Transistor partiellement déserté sur silicium sur isolant

$\phi_{BP}$  Travail de sortie du BP

$\phi_{\text{\tiny D}}$  Hauteur de barrière entre la source et le canal.

φ<sub>F</sub> Différence d'énergie entre le niveau de Fermi extrinsèque et le niveau de Fermi

intrinsèque

$\phi_m$  Travail de sortie de la grille

$\phi_{ms}$  Différence de travail de sortie entre la grille et le canal

φ<sub>s</sub> Travail de sortie du semiconducteur

Ψ<sub>s</sub> Potentiel de surface à l'interface diélectrique/silicium

$\Psi_{\text{S.th}}$  Potentiel de surface à l'interface diélectrique/silicium, au seuil de conduction

Q

q Charge élémentaire (= $1.6x10^{-19}$  C) Q<sub>DEP</sub> Charge de déplétion du canal Q<sub>INV</sub> Charge d'inversion du canal

Q<sub>INV,th</sub> Charge d'inversion du canal, au seuil de conduction

Q<sub>SS</sub> Charges positives piégées à l'interface oxyde/substrat et impuretés ionisées incluses

dans le volume de l'oxyde de grille.

**R**, ρ

R<sub>C</sub> Résistances de contact

R<sub>CANAL</sub> Résistance du canal de conduction

RDF Fluctuation du nombre de dopants dans le canal

R<sub>EXT</sub> Résistances d'extensions R<sub>J</sub> Résistances de jonctions RMS Rugosité du film de silicium RNM Stabilité en rétention (SRAM)

R<sub>ON</sub> Résistance totale entre la source et le drain

R<sub>OV</sub> Résistances de recouvrement R<sub>SD</sub> Résistances d'accès au canal

RVT Regular  $V_T$

ρ Coefficient de corrélation

S, σ

SCE Effets de canaux courts SNM Stabilité en lecture (SRAM)

SOI Silicium sur Isolant

SRAM Mémoire statique (Static Random Access Memory)

SS<sub>LIN</sub> Pente sous le seuil en régime ohmique SS<sub>SAT</sub> Pente sous le seuil en régime de saturation

sSOI Silicium contraint sur Isolant STI Shallow Trench Isolation

$\sigma_{\!\scriptscriptstyle L}$  Ecart type des fluctuations de la longueur effective du canal de conduction

$\sigma_{NBP}$  Ecart type des fluctuations de dopage du BP

$\sigma_{Qox}$  Ecart type des fluctuations de charges dans l'oxyde de grille

$\sigma_{SNM}$  Ecart type de la distribution de SNM

$\begin{array}{ll} \sigma_{TBOX} & \text{Ecart type des fluctuations d'épaisseur de l'oxyde enterr\'e} \\ \sigma_{Tox} & \text{Ecart type des fluctuations d'épaisseur de l'oxyde de grille} \\ \sigma_{Tsi} & \text{Ecart type des fluctuations d'épaisseur du film de silicium} \end{array}$

$\begin{array}{ll} \sigma_{VT} & \text{Ecart type de la distribution de $V_T$} \\ \sigma_{WM} & \text{Ecart type de la distribution de WM} \end{array}$

σ<sub>εοχ</sub> Ecart type des fluctuations de permittivité dans l'oxyde de grille

$\begin{array}{ll} \sigma_{(\Delta ID/ID)} & \text{Ecart type de la distribution de } \Delta I_D/I_D \\ \sigma_{(\Delta IOFF/IOFF)} & \text{Ecart type de la distribution de } \Delta I_{OFF}/I_{OFF} \\ \sigma_{(\Delta ISAT/ISAT)} & \text{Ecart type de la distribution de } \Delta I_{SAT}/I_{SAT} \end{array}$

$\sigma_{\Delta VT}$  Ecart type de la distribution de  $\Delta V_T$

$\begin{array}{ll} \sigma_{\Delta VT,SCE/DIBL} & \text{Ecart type de la distribution de } \Delta V_T \text{ induit par le SCE et le DIBL} \\ \sigma_{\Delta VT,TSi} & \text{Ecart type de la distribution de } \Delta V_T \text{ induit par les variations de } T_{Si} \end{array}$

$\sigma_{\!\scriptscriptstyle \phi BP}$  Ecart type des fluctuations du travail de sortie du BP

T

T Température

T<sub>BOX</sub> Epaisseur de l'oxyde enterré

T<sub>BOX FFE</sub> Epaisseur effective de l'oxyde enterré prenant en compte T<sub>DEP SUB</sub>

TCAD Technology Computer Aided Design

T<sub>DEP</sub> Epaisseur de la zone de déplétion sous la grille

T<sub>DEP SUB</sub> Epaisseur de la zone de déplétion dans le substrat (sous le BOX)

T<sub>DS</sub> Profondeur de *darkspace* induite par les effets de confinement quantique

T<sub>OX</sub> Epaisseur physique de l'oxyde de grille

T<sub>Si</sub> Epaisseur du film de silicium

$T_{SiO2}$  Epaisseur de la couche de SiO<sub>2</sub> (cSiGeOI par condensation)

$T_{SiO2\_piedestal}$  Epaisseur physique de l'oxyde piédestal

T<sub>SiGe\_final</sub> Epaisseur finale du film de SiGe (cSiGeOI par condensation)

T<sub>SiGe\_initial</sub> Epaisseur initiale du film de SiGe (cSiGeOI par condensation)

U

UTBOX Oxyde enterré ultra-mince

UTBB Film de silicium et oxyde enterré ultra-minces

V

$V_{\text{B}}$  Tension appliquée sur le substrat  $V_{\text{D}}$  Tension appliquée sur le drain

$V_{\text{DD}}$  Tension d'alimentation

V<sub>DD MIN</sub> Tension minimale d'alimentation

$\begin{array}{ll} V_{FB} & \quad \text{Tension de bande plate} \\ V_{G} & \quad \text{Tension appliquée sur la grille} \end{array}$

$V_{\text{MIN\_READ}}$  Tension minimale d'alimentation en mode de lecture  $V_{\text{MIN\_WRITE}}$  Tension minimale d'alimentation en mode d'écriture

V<sub>S</sub> Tension appliquée sur la source

V<sub>T</sub> Tension de seuil

V<sub>T CC</sub> Tension de seuil mesurée avec la méthode du courant constant

V<sub>T\_EXT</sub> Tension de seuil mesurée avec la méthode de l'extrapolation au maximum de la

transconductance

$\begin{array}{ll} V_{T\_LIN} & \quad & \text{Tension de seuil en régime ohmique} \\ V_{T\_SAT} & \quad & \text{Tension de seuil en régime de saturation} \end{array}$

$V_{Tn}$  Tension de seuil des transistors nMOS en régime ohmique (canal long)  $V_{Tp}$  Tension de seuil des transistors pMOS en régime ohmique (canal long)

W

$\begin{array}{ll} W & \quad \text{Largeur de la zone active du transistor} \\ W_{EFF} & \quad \text{Largeur effective du canal de conduction} \end{array}$

WL Ligne de mot dans les matrices SRAM (Word-Line)

WM Stabilité en écriture (SRAM)

X

$\begin{array}{ll} X_{EXT} & \text{Profondeur de diffusion des dopants dans les extensions source-drain} \\ X_{Ge\_final} & \text{Concentration finale de Ge dans le film de SiGe (cSiGeOI par condensation)} \\ X_{Ge\_initial} & \text{Concentration initiale de Ge dans le film de SiGe (cSiGeOI par condensation)} \end{array}$

$X_{SD}$  Profondeur de diffusion des dopants dans les jonctions source-drain

# Introduction générale

La microélectronique est un secteur industriel extrêmement concurrentiel représentant un chiffre d'affaire de 250 milliards d'euros en 2011. Cette industrie repose sur le transistor MOS (pour Métal-Oxyde-Semiconducteur) à effet de champ. Il sert de base pour le développement de circuits intégrés, qui sont eux-mêmes utilisés pour de nombreuses applications telles que l'informatique, la téléphonie mobile, la photographie numérique, les consoles de jeux, l'automobile, l'aérospatiale, et bien d'autres. Depuis sa première démonstration expérimentale en 1947, les dimensions caractéristiques du transistor sont sans cesse revues à la baisse pour chaque nouvelle génération, suivant la loi de Moore [Moore '65]. Ce concept de miniaturisation reposant sur une simple réduction d'échelle et de la tension d'alimentation a permis durant de nombreuses années d'atteindre les objectifs qui sont la réduction du coût de fabrication, l'amélioration des performances du circuit, tout en doublant le nombre de transistors sur une puce tous les 18 mois. A titre d'exemple, nous pouvons citer le premier microprocesseur commercialisé, développé par la société Intel en 1971, possédant 2300 transistors. De nos jours, la même société propose des microprocesseurs composés de 1.4 milliards de transistors répartis sur 160mm².

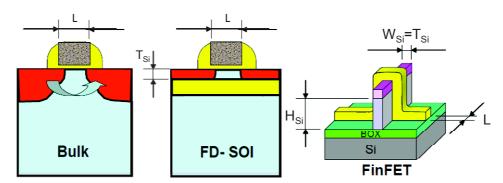

Cependant, depuis le début des années 2000, cette loi n'est plus suffisante pour garantir de meilleures performances tout en réduisant le coût entre deux générations. Les dimensions caractéristiques du transistor sont devenues si faibles que des phénomènes parasites ont commencé à impacter significativement ses performances électriques, notamment la dégradation du contrôle électrostatique de la grille sur le canal de conduction. Des solutions technologiques ont vu le jour afin de poursuivre la miniaturisation, mais des limitations intrinsèques au transistor sur silicium massif ne pourront plus longtemps être contournées dans ce monde désormais nanométrique.

De nouvelles architectures ont ainsi été développées afin de le remplacer, parmi lesquelles on trouve notamment les transistors FinFET [Hisamoto '89] [Huang '99] [Colinge '07] et les dispositifs à film mince sur diélectrique enterré (nommés communément FDSOI) [Young '89] [Choi '00] [Poiroux '10]. La technologie FinFET présente une architecture verticale qui autorise une forte densité d'intégration. En revanche les transistors FDSOI sont de type planaire, à l'instar des dispositifs usuels sur silicium massif, ce qui autorise un transfert de certaines étapes technologiques et facilite la conception des cellules standards, en comparaison aux dispositifs FinFET.

Le marché actuel de la microélectronique requiert à la fois des performances élevées et une faible consommation pour les applications mobiles (informatique, téléphonie, ...) afin d'augmenter l'autonomie. Il est également indispensable de pouvoir co-intégrer sur une même puce plusieurs

fonctionnalités (pour un minimum de place). On parle alors de SoC (pour *System-on-Chip*). Cela est possible en développant une plateforme technologique possédant plusieurs tensions de seuil (V<sub>T</sub>). Sur silicium massif, l'ajustement de la tension de seuil est réalisé par une modification du dopage du canal de conduction. Cependant, les architectures FDSOI et FinFET requièrent un canal non dopé afin de bénéficier de tous leurs avantages en termes de contrôle électrostatique. D'autres solutions sont par conséquent nécessaires, comme la modification du matériau de grille dont le travail de sortie a un impact direct sur la valeur du V<sub>T</sub>. La technologie FDSOI planaire possède également un puissant bras de levier permettant d'adresser cette problématique de multi-V<sub>T</sub>. L'utilisation d'un diélectrique enterré mince, couplé à un plan de masse implanté sous celui-ci, peut servir de seconde grille (de manière similaire aux transistors sur silicium massif), dont la polarisation appliquée sur le substrat peut être utilisée afin de moduler très précisément la tension de seuil.

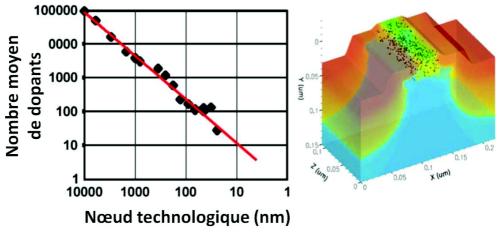

Une autre problématique majeure liée à la miniaturisation des dimensions des transistors est la difficulté croissante d'avoir des caractéristiques électriques qui soient les plus proches possibles d'un dispositif à l'autre. Depuis le nœud technologique 90nm, la contribution systématique liée au processus d'intégration n'est plus prédominante devant la contribution stochastique, induite quant à elle par des sources de fluctuations dont la longueur de corrélation est très faible devant les dimensions des transistors, telles que la variation statistique du nombre de dopants, la granularité de la grille métallique, la rugosité de flanc de la grille, etc. On assiste alors à des variations de la tension de seuil et du courant de drain entre deux transistors situés à la distance minimale autorisée par les règles de dessin. Cette source de variabilité est par ailleurs beaucoup plus complexe à minimiser car elle n'est pas directement liée à la qualité des équipements utilisés pour la fabrication des dispositifs. Elle a tout d'abord eu une importante influence sur les applications analogiques (paires différentielles, miroirs de courants, etc.) [Kinget '96] [Pelgrom '98], puis ces variations ont impacté significativement les applications numériques en terme de délai et de fuite [Burnett '94] [Bowman '00] [Malavasi '01], et plus particulièrement la stabilité en lecture et en écriture des circuits mémoires SRAM en raison des très petites dimensions des dispositifs utilisés [Bhavnagarwala '00] [Stolk '01]. C'est désormais une problématique majeure lors du développement d'une nouvelle filière technologique, au-delà des optimisations usuelles des performances.

C'est dans ce contexte que se situe ce mémoire de thèse traitant de la variabilité stochastique du transistor MOS en technologie FDSOI. L'objectif est d'appréhender les sources de fluctuations impactant les caractéristiques électriques du dispositif et leur influence sur les circuits mémoires SRAM.

Dans le premier chapitre, nous allons présenter le fonctionnement du transistor MOS sur silicium massif, ainsi que les principales problématiques liées à la miniaturisation des dimensions du dispositif. Nous verrons également les avantages de la technologie FDSOI, notamment en termes de contrôle

électrostatique et de réduction de la variabilité stochastique. Les différentes sources de fluctuations intrinsèques à cette architecture seront présentées, ainsi que la méthodologie permettant d'estimer la variabilité.

Dans le second chapitre, nous allons présenter les solutions permettant d'ajuster la tension de seuil des transistors FDSOI, ainsi que leur impact sur la variabilité stochastique du  $V_T$  grâce à des résultats expérimentaux.

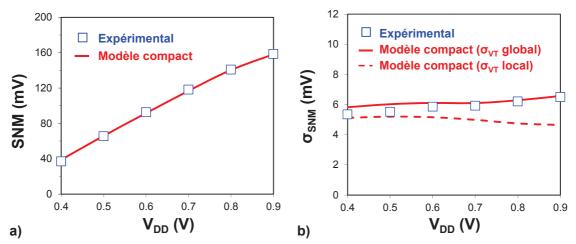

Le troisième chapitre sera consacré à l'analyse de la variabilité des caractéristiques électriques de cellules mémoires SRAM. Nous étudierons expérimentalement les corrélations existantes entre la variabilité des caractéristiques électriques des transistors et celles des SRAM. Un modèle compact sera utilisé afin de déterminer la contribution de la variabilité du  $V_T$  sur les fluctuations de la stabilité en lecture (nommée SNM). Nous verrons également quels sont les transistors de la cellule qui induisent le plus de fluctuations de la SNM grâce à un modèle analytique développé durant cette thèse.

Suite à cette étude exhaustive de la variabilité du  $V_T$ , nous allons analyser expérimentalement dans le quatrième chapitre la variabilité stochastique du courant de drain des transistors FDSOI réalisés. Ainsi, nous allons montrer quels sont les facteurs technologiques limitant et identifier les étapes critiques du processus d'intégration devant être optimisées.

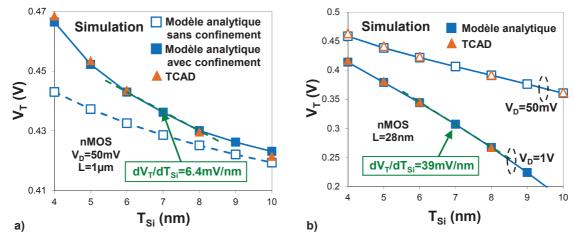

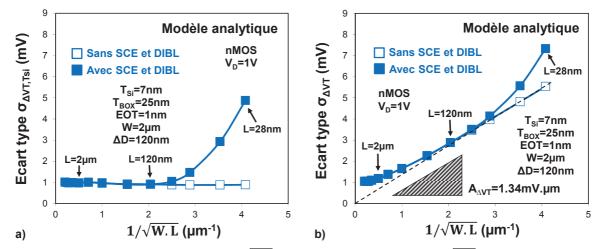

Enfin, dans le cinquième et dernier chapitre, nous allons analyser l'influence des fluctuations locales de l'épaisseur du film de silicium en technologie FDSOI sur la variabilité stochastique de la tension de seuil. Cette étude sera basée sur des mesures expérimentales, ainsi que sur les résultats d'un modèle analytique développé durant la thèse, préalablement calibré sur des simulations TCAD. Suite à cette quantification de l'impact des fluctuations de  $T_{Si}$ , une étude prédictive de la variabilité globale de la tension de seuil sera finalement présentée en technologie FDSOI 20nm, avec des transistors nMOS et pMOS ayant respectivement un canal de conduction Si et SiGe. L'impact de cette source de fluctuations sur un circuit SRAM de 200Mb sera également analysé grâce à un modèle compact.

## Chapitre 1

Présentation de la technologie Métal-Oxyde-Semiconducteur et de la problématique de la variabilité pour le nœud technologique 32nm et en deçà

#### 1.1. Introduction

Le transistor Métal-Oxyde-Semiconducteur à effet de champ (pour *Metal-Oxide-Semiconductor Field-Effect-Transistor*), également appelé MOSFET ou MOS, est utilisé comme élément de base des circuits intégrés. De nombreuses optimisations ont été apportées au fil des nœuds technologiques afin de surmonter les effets parasites induits par la miniaturisation des dimensions caractéristiques et par l'augmentation de la densité d'intégration. Ainsi, des dispositifs ayant des longueurs de grille très courtes ont vu le jour, nécessitant d'intégrer de nouveaux matériaux comme les oxydes à forte permittivité ou les grilles métalliques. Des matériaux présentant une forte contrainte mécanique ont été utilisés afin d'atteindre des performances toujours accrues, telles que les couches d'arrêt de gravure des contacts (appelées CESL pour *Contact Etch Stop Layer*) [Pidin '04] ou les source-drain SiGe [Yeo '05]. La reproductibilité des caractéristiques électriques des transistors est par conséquent devenue très sensible aux variations pouvant survenir dans l'ensemble des étapes du processus d'intégration.

L'objectif de ce chapitre est de présenter les transistors MOS sur silicium massif et de comprendre comment la technologie FDSOI (pour *Fully Depleted Silicon On Insulator*) permet de limiter l'influence des effets parasites liés à la miniaturisation des dimensions. Nous détaillerons ensuite les sources de fluctuations impactant les caractéristiques électriques des transistors FDSOI. Enfin, la méthodologie utilisée afin de caractériser expérimentalement la variabilité sera introduite.

#### 1.2. Technologie des transistors MOS à effet de champ

#### 1.2.1. Le transistor MOS : principe et régimes de fonctionnement

#### 1.2.1.a. Principe de fonctionnement et architecture

Le transistor MOS constitue l'élément de base des circuits intégrés utilisés dans le domaine de la microélectronique. Sa fonction est assez similaire à celle d'un interrupteur. En effet, il a pour rôle de laisser passer un courant ou de le bloquer. Afin de réaliser des fonctions logiques, deux types de transistors MOS sont utilisés : les nMOS, pour lesquels les porteurs du canal de conduction sont des électrons, et les pMOS, pour lesquels les porteurs sont des trous. La modulation de la concentration des porteurs dans le canal est obtenue par l'application d'un potentiel électrique sur l'électrode de grille qui crée un champ électrique vertical.

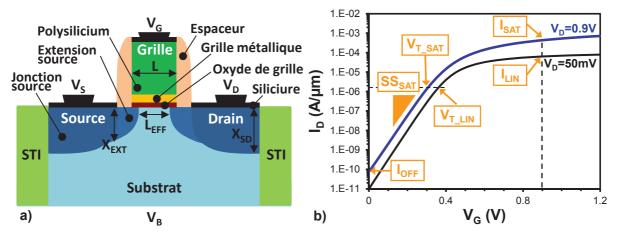

Un transistor MOS sur silicium massif (également appelé transistor *bulk*) est réalisé sur un substrat (de type p pour les nMOS et de type n pour les pMOS) dans lequel on trouve des zones fortement dopées (de type n pour les nMOS et de type p pour les pMOS) qui servent d'électrodes de source et de drain, comme le montre la Figure 1 (a). Ces deux jonctions jouent le rôle de réservoirs de porteurs et sont obtenues par implantation ionique de dopants. Le transistor est isolé électriquement par des tranchées d'oxyde appelées STI (pour *Shallow Trench Isolation*). La région de silicium située entre deux tranchées correspond à la zone active où est fabriqué le transistor. L'électrode de grille est

constituée d'un empilement de plusieurs matériaux, à savoir un oxyde, un métal de grille et une couche de polysilicium. Une siliciuration des jonctions source-drain et du sommet de la grille est effectuée dans le but d'optimiser le contact avec les vias métalliques servant de connexions vers différents niveaux de métaux, ainsi que pour diminuer les résistances d'accès. Les dimensions caractéristiques d'un transistor (Figure 1 (a)) sont la longueur de grille L, la longueur effective du canal de conduction ( $L_{\text{EFF}}$ ), la largeur de la zone active (W, non représentée sur ce schéma car perpendiculaire au plan), l'épaisseur de l'oxyde de grille ( $T_{\text{OX}}$ ), la profondeur de diffusion des dopants dans les extensions ( $X_{\text{EXT}}$ ) et la profondeur de diffusion des dopants dans les jonctions source-drain ( $X_{\text{SD}}$ ).

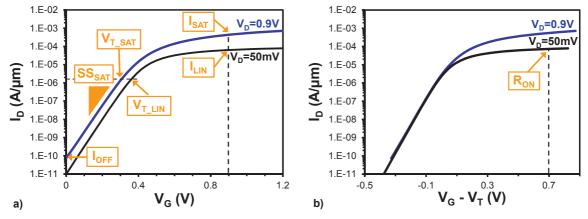

Figure 1 : (a) Représentation schématique d'un transistor nMOS sur silicium massif. (b) Courbe  $I_D(V_G)$  en régime ohmique  $(V_D=50 \text{mV})$  et en régime de saturation  $(V_D=0.9 \text{V})$  illustrant les caractéristiques électriques usuelles.

Quand un potentiel électrique (positif pour les nMOS et négatif pour les pMOS) est appliqué sur la grille, le transistor bascule de l'état bloqué à l'état passant, par la création d'un canal de conduction surfacique entre la source et le drain, à proximité de l'interface entre le substrat et l'oxyde de grille (Figure 1 (a)). Cela correspondant à un canal d'inversion de porteurs dans le canal : de type n (électrons) dans un substrat de type p pour les nMOS et de type p (trous) dans un substrat de type n pour les pMOS. L'application d'un potentiel sur l'électrode de drain permet aux porteurs de se déplacer de la source vers le drain, assurant la circulation d'un courant nommé  $I_D$ . L'électrode de substrat (notée  $V_B$  pour *bulk*) sera dans un premier temps polarisée à la masse ( $V_B$ =0V). Nous verrons par la suite l'intérêt que peut apporter la tension de substrat afin de moduler les caractéristiques électriques du transistor. La source est elle aussi polarisée à la masse ( $V_S$ =0V), autant pour les nMOS que pour les pMOS. Ceci restera valable pour l'analyse des transistors MOS individuels. Dans le cas des circuits intégrés, la source n'est pas polarisée de la même manière pour les nMOS et pour les pMOS.

Différentes caractéristiques électriques permettent de juger les performances du transistor. On s'intéresse notamment à la valeur du courant de drain dans les modes de fonctionnement bloqué  $(V_G=0V,\ V_D=V_{DD}\ en\ nMOS\ et\ V_D=-V_{DD}\ en\ pMOS)$  et passant  $(V_G=V_D=V_{DD}\ en\ nMOS\ et\ V_G=V_D=-V_{DD}\ en\ nMOS\ et\ v_G=V_D=-V_D$

pMOS), notés respectivement  $I_{OFF}$  et  $I_{SAT}$ . Le courant  $I_{OFF}$  dépend de la somme des courants tunnels entre la grille et le substrat ( $I_{GB}$ ) et entre la grille et les extensions du drain ( $I_{GD}$ ) et de la source ( $I_{GS}$ ), de la qualité des jonctions PN côté source et côté drain impactant les courants entre le drain et le substrat ( $I_{DB}$ ) et entre la source et le substrat ( $I_{SB}$ ), ainsi que de la hauteur de la barrière de potentiel entre le canal et les extensions (impactant le courant entre la source et le drain  $I_{SD}$ ). Le courant  $I_{SAT}$  évolue en fonction de la tension de drain appliquée et sera déterminé en général pour deux tensions  $V_D$  spécifiques, à savoir pour  $|V_D|=50$ mV (noté  $I_{LIN}$ ) et pour  $|V_D|=|V_{DD}|$  (noté  $I_{SAT}$ ). Typiquement, l'objectif d'un transistor est d'avoir un courant  $I_{OFF}$  aussi faible que possible (Équation 1), des courants  $I_{LIN}$  et  $I_{SAT}$  le plus fort possible et un passage entre ces deux états aussi abrupt que possible. Cette zone de transition est caractérisée par la valeur de la pente sous le seuil notée SS (SS<sub>LIN</sub> pour  $|V_D|=50$ mV et SS<sub>SAT</sub> pour  $|V_D|=|V_{DD}|$ ) (Équation 3), comme cela est illustré à la Figure 1 (b). La limite théorique de la pente sous le seuil est de 60mV/décade pour une température de 300K. Enfin, la tension de seuil  $V_T$  correspond à la frontière séparant l'état bloqué de l'état passant. Elle est notée  $V_{T_LIN}$  quand  $|V_D|=50$ mV et  $V_{T_LSAT}$  quand  $|V_D|=V_{DD}$  (Figure 1 (b)).

$$\log(I_{OFF}) = \log(I_{TH}) - \frac{V_{T\_LIN}}{SS_{LTN}}$$

(Équation 1)

$$I_{TH} = 10^{-7} \cdot \frac{W}{I}$$

(Équation 2)

$$SS = \left(\frac{\partial log I_D}{\partial V_G}\right) = \frac{k_B \cdot T}{q} \cdot ln(10) \left(1 + \frac{C_{DEP}}{C_{OX}} + \frac{C_{SS}}{C_{OX}}\right)$$

(Équation 3)

avec  $C_{DEP}$  la capacité de déplétion dans le substrat,  $C_{SS}$  la capacité liée à la qualité des états d'interface oxyde/substrat,  $C_{OX}$  la capacité de l'oxyde de grille,  $k_B$  la constante de Boltzmann, T la température et q la charge élémentaire.

Les caractéristiques  $I_{OFF}$  et  $I_{SAT}$  sont très couramment utilisées afin de juger les performances globales d'un transistor. Plus le rapport  $I_{SAT}/I_{OFF}$  est élevé, meilleur est le dispositif.

#### 1.2.1.b. Régimes de fonctionnement

La conduction dans un transistor MOS est modulée par le champ électrique de la grille qui agit à l'interface oxyde/substrat. Le potentiel de surface à cette interface est noté  $\Psi_S$ . La différence de type de dopants entre le canal de conduction et les jonctions source-drain crée une barrière de potentiel dont la hauteur varie en fonction de la polarisation appliquée sur l'électrode de grille. Nous introduisons la grandeur  $\phi_F$  correspondant au potentiel de Fermi. Elle représente l'écart entre le niveau de Fermi extrinsèque (pour un semiconducteur ayant une concentration  $N_A$  de dopants de type accepteur) et le niveau de Fermi intrinsèque (pour le même semiconducteur, cette fois non dopé) :

$$\phi_{F} = \frac{k_{B}.T}{q}.\ln\left(\frac{N_{A}}{n_{i}}\right)$$

(Équation 4)

avec  $n_i$  la densité intrinsèque de porteurs du matériau (1.137 $\times$ 10 $^{10}$  cm $^{-3}$  à 300K).

La tension de bande plate  $V_{FB}$  correspond à la tension qu'il faut appliquer sur la grille pour que le potentiel de surface  $\Psi_S$  soit nul :

$$V_{FB} = \phi_{m} - \phi_{s} - \frac{Q_{SS}}{C_{OV}}$$

(Équation 5)

avec  $\phi_m$  le travail de sortie de la grille,  $\phi_s$  le travail de sortie du semiconducteur du canal et  $Q_{SS}$  l'ensemble des charges positives piégées à l'interface oxyde/substrat et des impuretés ionisées incluses dans le volume de l'oxyde de grille.

Les différents régimes de fonctionnement du transistor dépendent donc du potentiel de surface  $\Psi_S$ . Prenons pour exemple le cas d'un nMOS :

#### $\triangleright$ Régime d'accumulation : $\Psi_S$ <0 c'est-à-dire $V_G$ < $V_{FB}$

Les porteurs majoritaires (trous) du substrat sont attirés à proximité de l'interface oxyde/substrat. La barrière de potentiel est trop haute pour être franchie par les porteurs minoritaires présents dans la source. Le transistor est par conséquent en régime d'accumulation.

ightharpoonup Régime de bandes plates :  $\Psi_S = 0$

La courbure des bandes est nulle.

ightharpoonup Régime de déplétion :  $0 < \Psi_S < \phi_F$  c'est-à-dire  $V_G > V_{FB}$

Les porteurs majoritaires (trous) sont repoussés de l'interface oxyde/substrat. Il se crée ainsi une zone dépourvue de porteurs libres. La barrière de potentiel entre le canal et les jonctions source-drain commence à s'abaisser mais ne laisse pas encore la possibilité aux électrons de la franchir. Le transistor est en régime de déplétion.

#### ightharpoonup Régime d'inversion faible : $\phi_F < \Psi_S < 2.\phi_F$ c'est-à-dire $V_{FB} < V_G < V_T$

Les porteurs minoritaires commencent à franchir la barrière de potentiel et forment une couche d'inversion à proximité de l'interface oxyde/substrat. La densité de porteurs minoritaires (électrons) reste inférieure à la concentration de porteurs majoritaires dans le substrat (trous). Le courant de drain évolue exponentiellement avec la tension  $V_G$  suivant un mécanisme de diffusion. Les porteurs se déplacent grâce à un gradient de charges de telle manière que les électrons vont de la zone de forte concentration (côté source) vers la zone de faible concentration (côté drain). La tension de seuil est atteinte lorsque la concentration de porteurs minoritaires à proximité de l'interface oxyde/substrat devient égale à la concentration des porteurs majoritaires dans le substrat, ce qui intervient quand  $\Psi_S = 2.\phi_F$ . Le transistor est en régime d'inversion faible. La tension de seuil est définie telle que :

$$V_{T} = V_{FB} + 2.\phi_{F} - \frac{Q_{DEP}}{C_{OX}}$$

(Équation 6)

avec  $Q_{DEP}$  la charge de déplétion dans le canal. Nous noterons que le travail de sortie  $\phi_m$  du métal intervient directement dans la valeur du  $V_T$  par l'intermédiaire de la tension  $V_{FB}$  (Equation 5).

#### ightharpoonup Régime d'inversion forte : $\Psi_S > 2.\phi_F$ c'est-à-dire $V_G > V_T$

La concentration de porteurs minoritaires (électrons) à proximité de l'interface oxyde/substrat est beaucoup plus grande que la concentration de porteurs majoritaires dans le substrat. Le courant de drain est déterminé par un mécanisme de dérive selon le champ longitudinal fixé par la tension V<sub>D</sub>. Le transistor est en régime d'inversion forte.

Quand  $V_D < V_G - V_T$ , le transistor fonctionne en régime ohmique. Le courant de drain dépend linéairement de la tension  $V_G$  et est donné par :

$$I_{LIN} = \frac{W_{EFF}}{L_{FFF}} \cdot \mu_{EFF} \cdot C_{OX} \cdot \left( V_{G} - V_{T} - \frac{V_{D}}{2} \right) \cdot V_{D}$$

(Équation 7)

avec  $W_{EFF}$  la largeur effective du canal ( $W_{EFF}$ =W en technologie FDSOI simple grille),  $L_{EFF}$  la longueur effective du canal et  $\mu_{EFF}$  la mobilité effective des porteurs.

Quand  $V_D \ge V_G - V_T$ , un pincement apparaît du côté du drain. Il tend à se rapprocher légèrement de la source quand  $V_D$  augmente. Le potentiel au point de pincement est constant et indépendant de la tension de drain. Le transistor est en régime de saturation.  $I_D$  n'évolue donc plus en fonction de  $V_D$ , ce qui donne :

$$I_{SAT} = \frac{1}{2} \cdot \frac{W_{EFF}}{L_{EFF}} \cdot \mu_{EFF} \cdot C_{OX} \cdot (V_G - V_T)^2$$

(Équation 8)

$$EOT = T_{high-k} \cdot \left( \frac{k_{SiO_2}}{k_{high-k}} \right) + T_{SiO_2 - piédestal}$$

(Équation 9)

avec  $k_{SiO2}$  la constante diélectrique du  $SiO_2$ ,  $k_{high-k}$  celle du diélectrique ayant une haute permittivité,  $T_{high-k}$  l'épaisseur physique du *high-k* et  $T_{SiO2\_piédestal}$  l'épaisseur physique de l'oxyde piédestal.

## 1.2.2. Effets de canaux courts et abaissement de la barrière de conduction induite par le drain

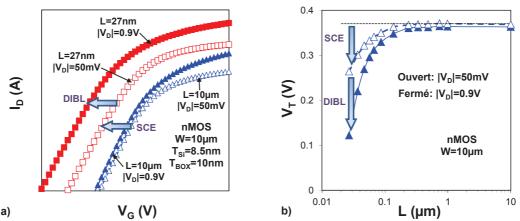

Les effets de canaux courts, nommés SCE (pour *Short Channel Effect*), désignent une perte du contrôle électrostatique du canal par la grille. Dans un transistor ayant un canal long, la composante verticale du champ électrique commence par déserter le canal, puis entraîne un phénomène d'inversion à plus forte polarisation sur la grille. Or, les jonctions n/p formées par les extensions source/drain créent des zones de déplétion de quelques nanomètres dans lesquelles le potentiel chute et empêche un contrôle par la grille. Ainsi, dans le cas de canaux courts, ces zones de déplétion vont finir par se superposer et induire une chute du potentiel. L'abaissement de la barrière de potentiel du canal qui en résulte va réduire le  $V_T$  du transistor (Figure 2), augmenter la pente sous le seuil, et finalement dégrader le courant de fuite  $I_{OFF}$ . En appliquant une tension de drain élevée, le DIBL (pour *Drain Induced Barrier Lowering*) va entraîner une perte additionnelle du contrôle électrostatique (abaissement de la barrière de potentiel du canal d'autant plus significative que  $V_D$  est important). Deux caractéristiques peuvent ainsi être extraîtes : les tensions de seuil  $V_{T_LIN}$  (en régime ohmique, à  $|V_D| = 50$ mV) et  $V_{T_LSAT}$  (en régime de saturation, à  $|V_D| = V_{DD}$ ). Le DIBL est calculé en soustrayant ces deux tensions de seuil. L'influence du SCE et du DIBL sur les courbes  $V_T(L)$  et  $I_D(V_G)$  est illustrée à la Fiqure 2.

Figure 2 : (a)  $I_D(V_G)$  mesurés sur des transistors ayant un canal long (L=10 $\mu$ m) ou un canal court (L=30nm), à  $V_D$ =50mV et 0.9V. (b) Tension de seuil  $V_T$  en fonction de la longueur de grille permettant de mettre en évidence le SCE et le DIBL.

#### 1.3. Amélioration des performances grâce à la technologie FDSOI

#### 1.3.1. Présentation de la technologie SOI

Comme nous l'avons vu précédemment, la miniaturisation des dimensions des transistors induit des effets parasites qui altèrent leurs performances. Cela se traduit par une complexification du processus d'intégration, indispensable afin de suivre les spécifications de l'ITRS (pour *International Technology Roadmap for Semiconductors*) [ITRS '11]. Le transistor *bulk* atteignant ses limites vis-à-vis du contrôle des effets de canaux courts pour les longueurs de grille inférieures à 30nm, d'autres architectures technologiques ont vu le jour. Parmi celles-ci, on trouve la technologie « Silicium sur

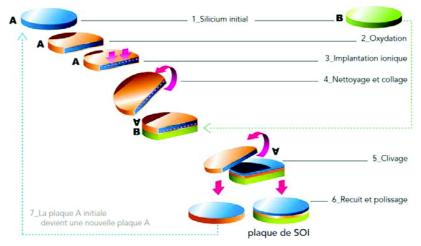

Isolant », également appelée SOI (pour *Silicon On Insulator*). Le substrat SOI est constitué d'un film de silicium monocristallin non dopé ( $N_A \approx 10^{15}$  at.cm<sup>-3</sup>), isolé du substrat de silicium par un oxyde enterré appelé BOX (pour *Buried OXide*). La zone active du transistor sera définie dans la couche de silicium supérieure. La société SOITEC est le premier fournisseur mondial de plaques SOI, utilisant le procédé Smart  $Cut^{TM}$  [Bruel '95] [Maleville '06]. Le principe est d'utiliser un substrat de silicium (appelé A sur la Figure 3) sur lequel une oxydation est réalisée. L'épaisseur de celle-ci correspondra au final à celle de l'oxyde enterré. Une implantation d'atomes d'hydrogène est effectuée à la profondeur désirée (correspondant approximativement à l'épaisseur finale du film de silicium). Un collage moléculaire est réalisé entre A et un second substrat préalablement nettoyé (appelé B sur la Figure 3), suivi d'un recuit à haute température afin d'obtenir une fracture au niveau des atomes d'hydrogène. Finalement, un procédé permettant d'uniformiser la surface du film de silicium actif est utilisé.

Figure 3 : Schéma de principe du procédé de fabrication des plaques SOI utilisant le procédé Smart Cut™ [Schwarzenbach '11]

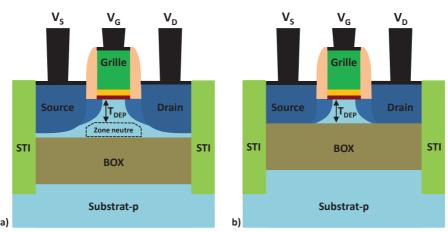

Ainsi, deux nouveaux paramètres physiques entrent en considération par rapport à des transistors sur silicium massif : l'épaisseur du film de silicium actif, notée  $T_{Si}$ , et l'épaisseur de l'oxyde enterré, notée  $T_{BOX}$ . Deux catégories de transistors MOSFET peuvent être réalisées grâce aux substrats SOI. Quand  $T_{Si}$  est important (supérieur à 50nm), la zone de déplétion n'atteint pas le BOX. On observe ainsi une zone neutre, comme le montre la Figure 4 (a). On parle dans ce cas de transistors « partiellement déplétés » ou PDSOI (*Partially Depleted SOI*). Cette zone est définie telle que :

$$T_{\text{DEP}} = \frac{Q_{\text{DEP}}}{q.N_{\text{A}}}$$

(Équation 10)

En revanche, quand l'épaisseur du film de silicium est suffisamment mince pour que la zone de déplétion atteigne le BOX (Figure 4 (b)), on parle de transistors « complètement déplétés » ou FDSOI (*Fully Depleted SOI*). C'est à cette architecture que nous allons nous intéresser dans ce manuscrit.

Figure 4 : Représentation schématique d'un transistor PDSOI (a) et d'un transistor FDSOI (b).

#### 1.3.2. Architecture et procédés de fabrication des transistors FDSOI

Historiquement, les substrats SOI ont été développés pour des applications spatiales [Leray '90] car ils présentent une meilleure résistance aux rayonnements ionisants par rapport au silicium massif. Cependant, il existe également de nombreux avantages qui font de la technologie FDSOI un candidat pertinent pour les prochains nœuds technologiques :

- ➤ Une isolation totale grâce à la présence du BOX. Il n'y a pas de circulation de courant dans le substrat entre des transistors voisins, comme cela est le cas pour les transistors sur silicium massif. Le déclenchement du thyristor parasite (phénomène de « latch-up ») est par conséquent supprimé.

- Un excellent contrôle électrostatique grâce à une plus faible profondeur des jonctions source/drain [Barral '07] [Fenouillet '09a] et à une plus faible profondeur de déplétion  $T_{DEP}$ . Celles-ci sont fixées par l'épaisseur  $T_{Si}$  du film de silicium, non par les procédés d'implantation du canal et de recuit comme c'est le cas sur silicium massif. De plus, en technologie FDSOI, le canal est non dopé, ce qui implique l'absence de réservoir de porteurs libres dans le film de silicium. Il n'existe donc pas de régime d'accumulation et le film reste déserté tant que le potentiel de surface est inférieur à  $\phi_F$ , assurant une pente sous le seuil et un courant  $I_{OFF}$  améliorés.

- Une réduction de la profondeur de déplétion, conduisant à un champ effectif transverse plus faible et par conséquent à une amélioration de la mobilité des porteurs. Le courant de drain en régime de saturation est amélioré.

Des substrats SOI de 300mm de diamètre ont été utilisés durant cette thèse afin de fabriquer les transistors FDSOI. Le film de silicium est aminci par oxydation et gravure humide afin d'atteindre l'épaisseur  $T_{Si}$  souhaitée. Cette étape est essentielle afin de bénéficier d'un bon contrôle électrostatique de la grille sur le canal de conduction. Une isolation STI est ensuite réalisée entre les transistors afin d'éviter la création de courants parasites. Il s'agit de tranchées d'oxyde situées à chaque extrémité de la zone active. Une zone fortement dopée est implantée sous le BOX. Celle-ci est

appelée BP (pour Back-Plane), et son pic de concentration maximale est ajusté afin de ne pas obtenir un dopage résiduel dans le canal de conduction. Le type de dopage va permettre d'ajuster la tension de seuil des transistors FDSOI par couplage électrostatique à travers le BOX, comme nous le verrons dans la section 1.3.3. Un empilement de grille est déposé (oxyde piédestal + oxyde à forte permittivité (high-k) + grille métallique). La grille métallique la plus utilisée sur cette architecture non dopée est le nitrure de titane TiN, dont le travail de sortie est proche du travail de sortie du silicium intrinsèque, c'est-à-dire 4.61eV [Sze '07]. On parle dans ce cas de matériaux mid-gap permettant d'obtenir des tensions de seuil équilibrées entre nMOS et pMOS (V<sub>Tn</sub>≈ -V<sub>Tp</sub>). L'ensemble est complété par un dépôt de polysilicium. Après gravure de cet empilement, un espaceur de nitrure (Si<sub>3</sub>N<sub>4</sub>) est réalisé de manière à isoler la grille des futures zones source et drain. Une épitaxie est effectuée afin d'augmenter l'épaisseur du film de silicium dans les jonctions source-drain, le but étant d'optimiser certaines composantes des résistances séries. Les extensions source-drain sont implantées afin de doper le film de silicium sous les espaceurs. Un second espaceur est réalisé juste avant l'implantation des jonctions source-drain. Le processus d'intégration se poursuit par une activation des dopants à forte température et une siliciuration des jonctions afin de réduire la résistance parasite de contact. Finalement, les vias et les niveaux de métaux supérieurs sont réalisés afin de rendre le transistor testable électriquement, ainsi que pour réaliser les interconnexions indispensables au fonctionnement des circuits intégrés complexes.

## 1.3.3. Améliorations obtenues grâce à l'utilisation d'un film de silicium et d'un oxyde enterré minces avec back-plane

Les travaux de [Skotnicki '88] sur la transformation « tension-dopage » permettent de modéliser analytiquement les effets de canaux courts, où le SCE et le DIBL sont définis en technologie FDSOI par les équations suivantes :

$$SCE = 0.64. \frac{\varepsilon_{Si}}{\varepsilon_{OX}} \cdot \left(1 + \frac{T_{Si}^{2}}{L_{EFF}^{2}}\right) \cdot \frac{EOT + T_{DS}}{L_{EFF}} \cdot \frac{T_{Si} + \lambda \cdot T_{BOX}}{L_{EFF}} \cdot \phi_{D}$$

(Équation 11)

$$DIBL = 0.8. \frac{\varepsilon_{Si}}{\varepsilon_{OX}} \left( 1 + \frac{T_{Si}^2}{L_{EFF}^2} \right) \cdot \frac{EOT + T_{DS}}{L_{EFF}} \cdot \frac{T_{Si} + \lambda \cdot T_{BOX}}{L_{EFF}} \cdot V_D$$

(Équation 12)

$$\lambda = 0.21 \left( 1 + \tanh \left( 1.5 \cdot \frac{T_{BOX}}{L_{EFF}} \right) - 1 \right) \left( 1 + 0.09 \cdot \left( \frac{T_{BOX}}{L_{EFF}} \right) \right) \left( \frac{L_{EFF}}{T_{BOX}} \right)$$

(Équation 13)

avec  $\epsilon_{Si}$  la permittivité électrique du silicium,  $\epsilon_{OX}$  la permittivité électrique de l'oxyde SiO<sub>2</sub>, L<sub>EFF</sub> la longueur effective définie par L<sub>EFF</sub>=0.8.X<sub>EXT</sub>, T<sub>DS</sub> la profondeur de *darkspace* induite par les effets de confinement quantique qui tendent à repousser les porteurs de l'interface SiO<sub>2</sub>/Si et  $\phi_D$  la hauteur de barrière entre la source et le canal.

Les équations 11 et 12 mettent ainsi en évidence que la réduction de l'épaisseur du film de silicium mince permet d'améliorer le contrôle des effets de canaux courts (réduction de la profondeur des jonctions source-drain et de la zone de déplétion  $T_{DEP}$ ). En réduisant l'épaisseur du film de silicium, les

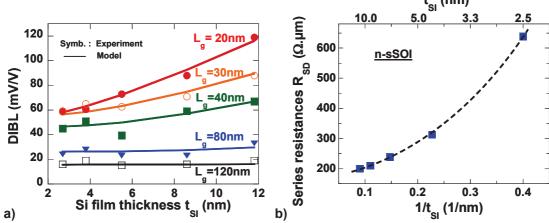

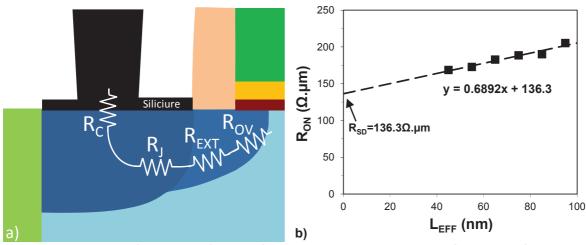

lignes de potentiel dans le canal s'aplanissent, se traduisant par une amélioration du contrôle de la grille sur le canal de conduction et donc à une réduction des effets de canaux courts. Un gain significatif est par conséquent obtenu sur le DIBL [Barral '07], comme illustré à la Figure 5 (a). En revanche, cela induit également une augmentation des résistances d'accès au canal (Figure 5 (b)), ce qui a pour conséquence de dégrader les performances du transistor. Une optimisation des jonctions source-drain est indispensable afin de maintenir R<sub>SD</sub> aussi faible que possible [Ponoth '11].

Figure 5 : (a) Evolution du DIBL en fonction de l'épaisseur du film de silicium pour différentes longueurs de grille de dispositifs FDSOI nMOS ( $T_{BOX}$ =145nm) et (b) des résistances d'accès au canal  $R_{SD}$  en fonction de  $T_{Si}$  [Barral '07].

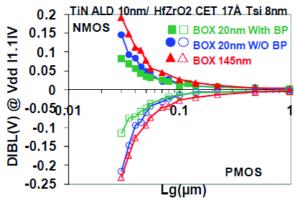

En plus de l'amincissement du film de silicium, il est également intéressant de réduire l'épaisseur du BOX afin d'améliorer le contrôle des effets de canaux courts, comme l'illustre les équations 11 et 12. En effet, il existe des lignes de champ qui se propagent dans le BOX, créant un couplage entre la source et le drain [Yeh '95], [Ernst '99], [Fenouillet '04]. Pour de petites longueurs de grille, le potentiel dans l'oxyde enterré prend une forme parabolique et sa variation n'est donc plus linéaire comme sur un canal long. Ceci induit une augmentation du potentiel dans le canal de conduction (à l'interface Si/BOX). L'amincissement de la couche d'oxyde enterré permet de diminuer le couplage entre la source et le drain. Les lignes de champ retrouvent ainsi une variation linéaire dans le BOX, ce qui améliore le contrôle électrostatique [Gallon '07]. La Figure 6 montre qu'en diminuant l'épaisseur du BOX de 145nm à 20nm, il est possible de réduire le DIBL de 25 % pour une longueur de grille de 30nm. Par la suite, en présence de T<sub>Si</sub> et de T<sub>BOX</sub> minces, nous parlerons de substrats UTBB (pour *Ultra-Thin Body and Buried Oxide*).

En l'absence de dopage sous l'oxyde enterré, les champs électriques induits par la grille et par les source-drain provoquent une déplétion sous le BOX (d'épaisseur  $T_{DEP\_SUB}$ ) ce qui augmente son épaisseur effective  $T_{BOX\_eff}$ . Lorsque  $T_{BOX}$  diminue, la zone de déplétion commence à prendre une importance significative par rapport à l'épaisseur physique de l'oxyde enterré. On obtient ainsi :

$$T_{BOX\_eff} = T_{BOX} + \frac{\varepsilon_{OX}}{\varepsilon_{S_i}}.T_{DEP\_SUB}$$

(Équation 14)

Figure 6 : Evolution du DIBL en fonction de la longueur de grille de dispositifs FDSOI nMOS et pMOS  $(T_{Si}=8nm, EOT=1.4nm)$ . Les résultats sont donnés pour des épaisseurs de BOX de 145nm et 20nm (avec ou sans BP) [Fenouillet '11].

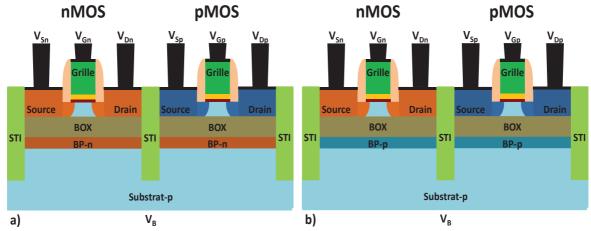

Cette zone de déplétion va par conséquent modifier le potentiel du canal de conduction et altérer le contrôle électrostatique. Une réduction de cette déplétion est possible en introduisant un dopage sous le BOX, appelé *back-plane* (BP) [Ernst '99] (voir la Figure 7). Celui-ci est réalisé avec des ions Indium ou Bore (BP de type p) et Arsenic ou Phosphore (BP de type n). Les conditions d'implantation (dose, énergie, type d'ions) sont définies de telle manière que le pic de concentration maximale soit situé juste en dessous du BOX, tout en évitant un dopage du film de silicium actif. L'utilisation d'un BP de type opposé à celui des jonctions source-drain permet par ailleurs d'améliorer encore plus le contrôle électrostatique [Gallon '07], le BP ayant pour rôle d'empêcher la pénétration du champ électrique dans le substrat.

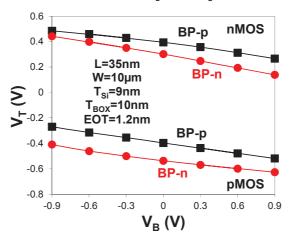

L'utilisation d'un oxyde enterré mince présente également un intérêt pour l'ajustement de la tension de seuil des transistors FDSOI. C'est un point clé de cette technologie, permettant de contrôler les fuites et/ou d'augmenter la vitesse d'un même dispositif avec une grande flexibilité. L'intégration d'un BP implanté sous le BOX peut être utilisée comme une seconde grille, dont la polarisation V<sub>B</sub> agit sur les caractéristiques électriques du dispositif [Noel '09] [Noel '11]. Cette méthode est basée sur les techniques de réduction du courant de fuite qui ont été développées en technologie MOS sur silicium massif. En appliquant une différence de potentiel entre le BP et la source du transistor (négatif pour les nMOS et positive pour les pMOS), la tension de seuil augmente et permet ainsi de réduire le courant I<sub>OFF</sub> [Kuroda '96a] [Kuroda '96b] [Oowaki '98]. Cette technique est communément appelée RBB (pour *Reverse Back Biasing*). Par opposition, quand la différence de potentiel est positive pour les nMOS et négative pour les pMOS, le courant de drain en régime d'inversion forte augmente ce qui permet d'accroître la vitesse du dispositif. Cette technique s'appelle FBB (pour *Forward Back Biasing*).

La Figure 7 montre un schéma d'intégration dans lequel la polarisation face arrière  $V_B$  va agir de manière commune (à travers le substrat) sur les nMOS et les pMOS. Cette architecture a été utilisée sur les dispositifs expérimentaux (transistors MOS et cellules mémoires SRAM) que nous étudierons dans les prochains chapitres. Par ailleurs, une seule grille métallique est utilisée pour tous les transistors, ainsi qu'un seul type de BP. Néanmoins, deux types de BP ont été testés (Figure 7) permettant d'adresser deux  $V_T$  pour chaque type de MOS. Un BP du même type que les source-drain donnera un transistor de type LVT (pour  $Low\ V_T$ ) alors qu'un BP de type opposé donnera un  $V_T$  plus élevé, de type RVT (pour  $Regular\ V_T$ ) (voir le paragraphe suivant). Une flexibilité additionnelle pour l'ajustement des tensions de seuil est possible en polarisant indépendamment les BP des nMOS et des pMOS (pouvant également être de types différents sur un même substrat) grâce à l'implantation de caissons sous les BP et à la réalisation de prises caissons avec ouverture du BOX [Noel '10].

Figure 7 : Vue schématique en coupe de transistors nMOS et pMOS fabriqués en technologie FDSOI ayant un film de silicium mince, ainsi qu'un oxyde enterré mince avec un BP unique (de type n dans (a) et de type p dans (b)). La polarisation du BP se fait par l'intermédiaire du substrat. La même grille métallique est utilisée pour les nMOS et les pMOS.

Nous allons maintenant décrire la capacité de la grille arrière à ajuster la tension de seuil du transistor. Le facteur de couplage entre la grille avant et la grille arrière est défini tel que  $\gamma = \Delta V_T / \Delta V_B$ . Ce facteur de couplage est dépendant du mode de conduction du dispositif. Pour commencer, nous allons considérer une architecture de transistor ayant un canal long et un BOX mince sans BP. L'épaisseur du film de silicium est suffisamment épaisse pour que le canal de conduction reste de type surfacique. En effet, dans le cas d'un film extrêmement mince, celui-ci peut devenir volumique [Colinge '97] en raison d'un couplage entre les populations de porteurs situées aux interfaces avant et arrière.

En appliquant une tension négative sur  $V_B$  (positive dans le cas des pMOS), le potentiel à l'interface Si/BOX chute. Un canal de conduction est créé à l'interface avant du film de silicium lorsque  $V_G=V_T$ . Le facteur de couplage est donné par l'équation suivante (cas d'un canal long) [Lim '83] :

$$\gamma_{FC} = \frac{EOT}{T_{BOX} + \frac{\varepsilon_{SiO2}}{\varepsilon_{Si}}.T_{Si}}$$

(Équation 15)

En appliquant une tension  $V_B$  comprise dans la gamme [0V, 1V] ([-1V, 0V] dans le cas des pMOS), l'interface BOX/substrat se situe en régime de déplétion [Mazellier '08] ce qui augmente l'épaisseur effective  $T_{BOX\_eff}$ . Lorsque l'épaisseur du BOX est faible, la zone de déplétion va prendre une importance significative par rapport à l'épaisseur physique de l'oxyde enterré (Equation 14).

De plus, quand  $V_B$  est supérieure à environ 1V (inférieure à -1V pour les pMOS), le potentiel à l'interface Si/BOX augmente et induit la création d'un canal de conduction à l'interface arrière du film de silicium à  $V_G=V_T$ . Le facteur de couplage se présente de la manière suivante [Lim '83] :

$$\gamma_{BC} = \frac{EOT + \frac{\varepsilon_{SiO2}}{\varepsilon_{Si}} . T_{Si}}{T_{BOX}}$$

(Équation 16)

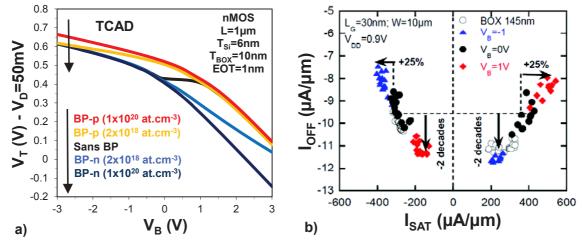

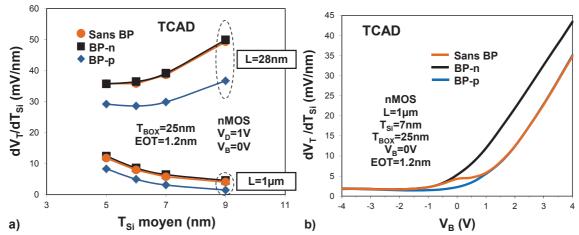

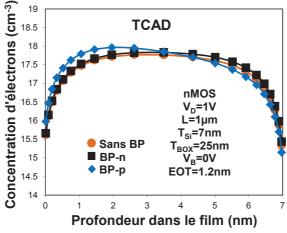

L'influence du BP sur la courbe  $V_T(V_B)$  est illustrée à la Figure 8 (a). Les trois régimes de fonctionnement du substrat sont très clairement visibles quand aucun BP n'est utilisé. En revanche, l'implantation d'un BP sous le BOX agit fortement sur le comportement électrique en fonction de V<sub>B</sub>. Tout d'abord, cela minimise fortement l'effet de déplétion à l'interface BOX/substrat intervenant dans la gamme [0V, 1V] pour les nMOS ([-1V, 0V] pour les pMOS) sans BP. La Figure 8 (a) montre également que pour une valeur V<sub>B</sub> négative (positive pour les pMOS), un BP-n n'a pas d'influence sur la courbe V<sub>T</sub>(V<sub>B</sub>) par rapport à l'architecture BOX mince sans BP. Les électrons naturellement présents (lié au type de BP) sont plaqués à proximité de l'interface BOX/substrat. Par opposition, dans le cas où un BP-p est utilisé, on observe une influence de la déplétion des porteurs majoritaires (trous) présents dans le silicium à proximité de l'interface BOX/substrat. Finalement, pour une valeur V<sub>B</sub> supérieure à environ 1V (inférieure à -1V dans le cas des pMOS), c'est la configuration ayant un BP-p (des trous sont naturellement présents à proximité de l'interface BOX/substrat) qui a le même comportement que le cas sans BP. L'utilisation d'un BP-n se traduit par une modification de la courbe  $V_T(V_B)$  en raison de la présence d'une zone de déplétion des porteurs majoritaires (électrons) présents dans le substrat. Le phénomène de déplétion est mis en avant grâce aux différentes conditions de simulations de BP (dopage à 2x10<sup>18</sup> ou 1x10<sup>20</sup> at.cm<sup>-3</sup>). En effet, quand ce dopage est fortement augmenté par rapport aux valeurs typiques égales à 2x10<sup>18</sup> at.cm<sup>-3</sup>, l'épaisseur de la zone de déplétion à l'interface BOX/substrat est atténuée, ce qui donne deux courbes V<sub>T</sub>(V<sub>B</sub>) identiques pour les deux types de BP, simplement décalées en V<sub>B</sub> de la valeur de la bande interdite (*band-gap*) du silicium. On notera ainsi que pour une même valeur de V<sub>B</sub>, un changement de type de BP permet de moduler le V<sub>T</sub> de xmV, x étant défini tel que :

$$x=band-gap \cdot \frac{dV_T}{dV_R}$$

(Équation 17)

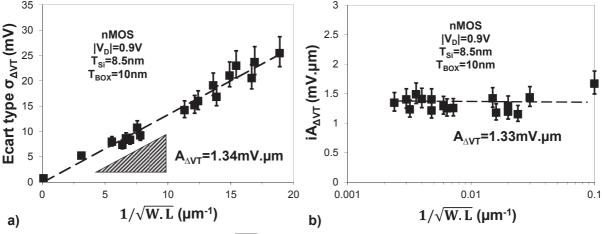

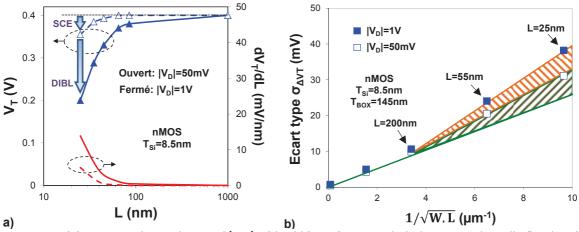

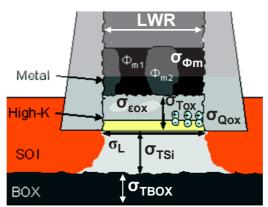

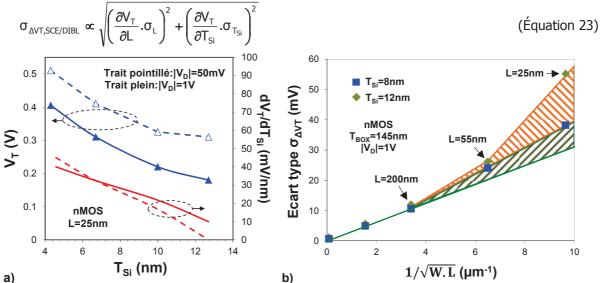

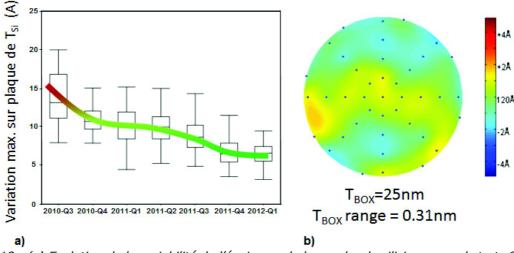

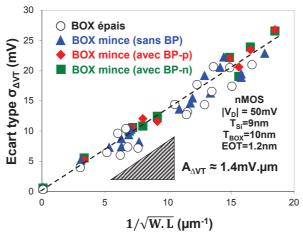

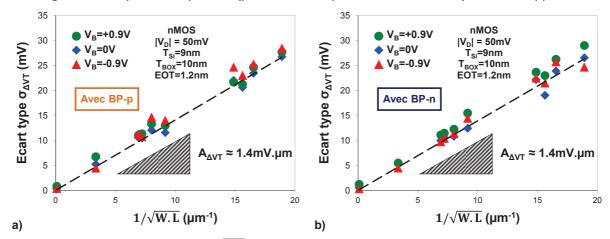

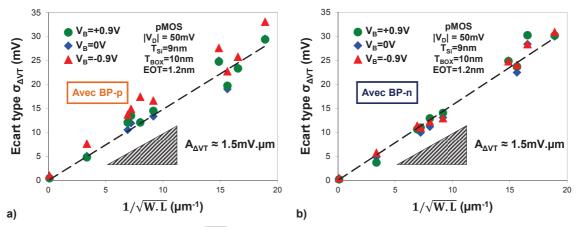

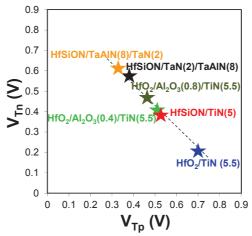

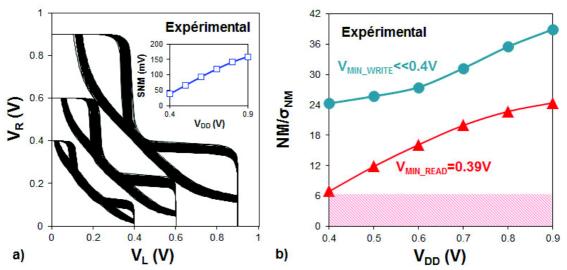

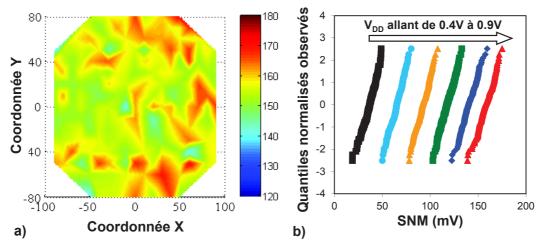

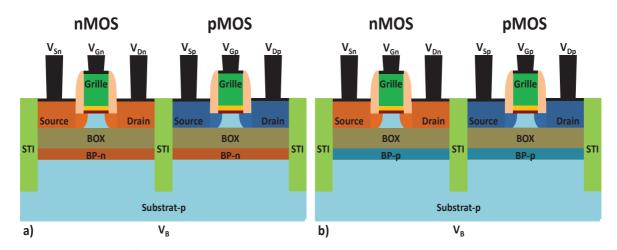

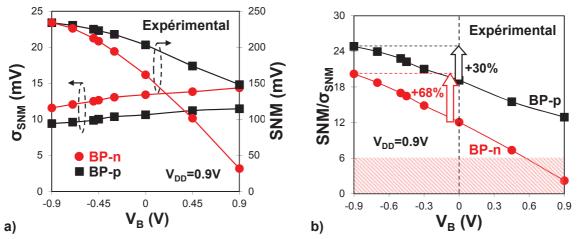

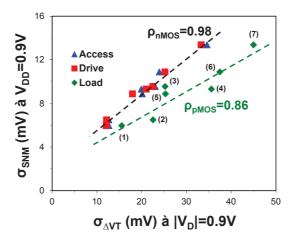

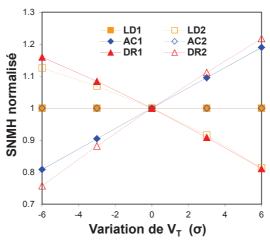

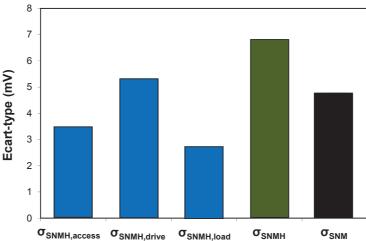

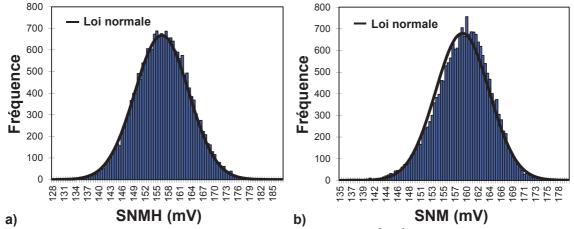

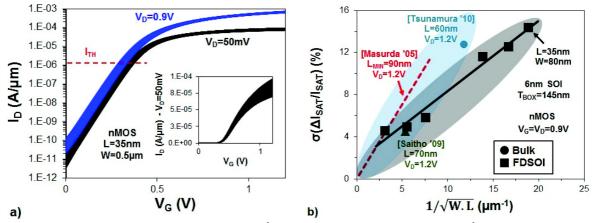

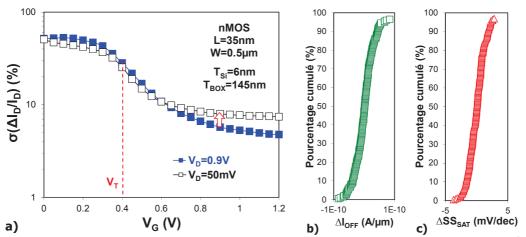

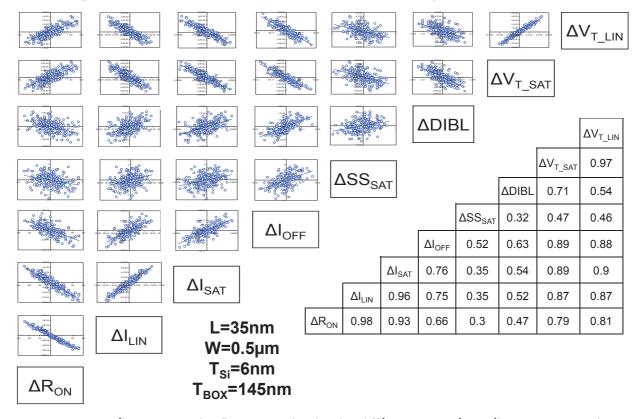

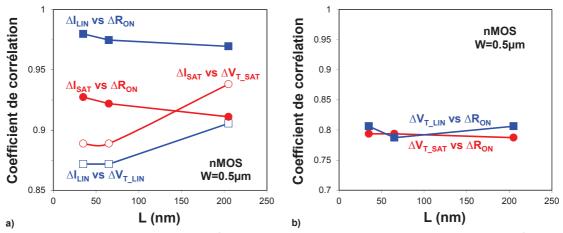

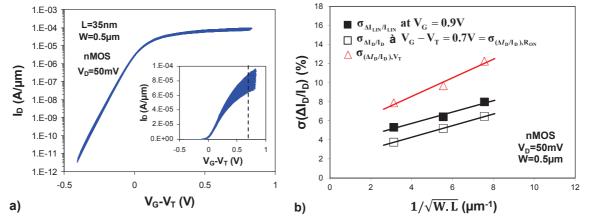

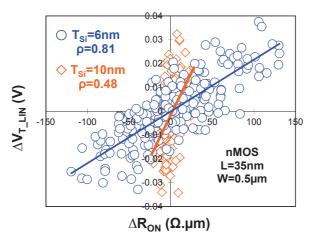

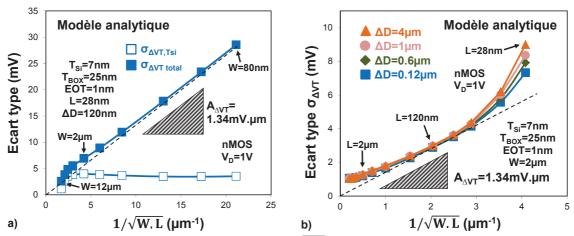

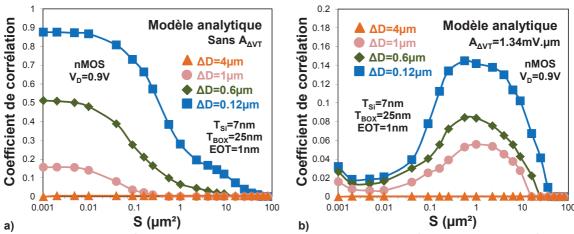

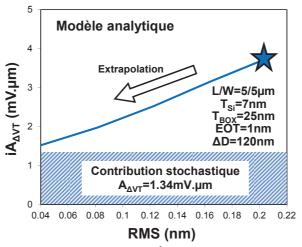

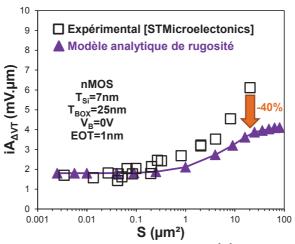

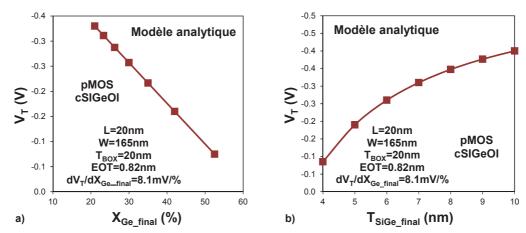

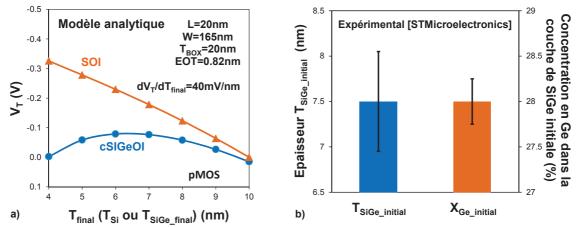

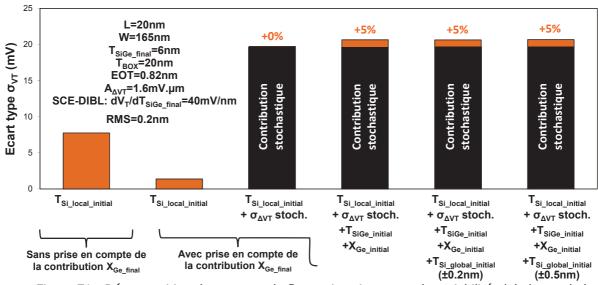

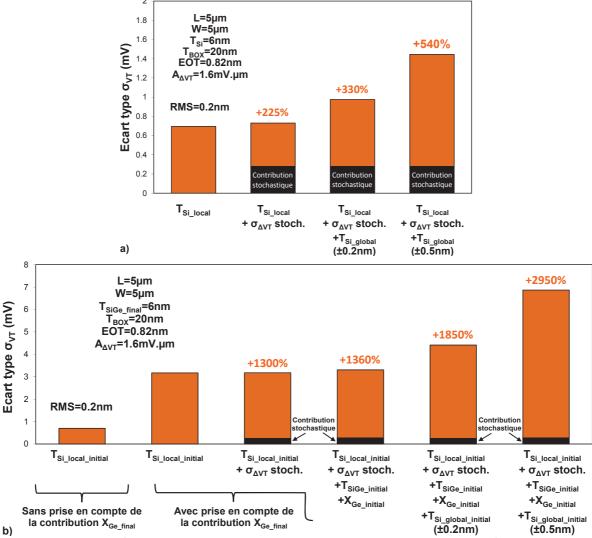

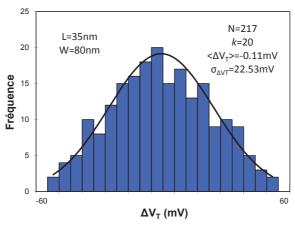

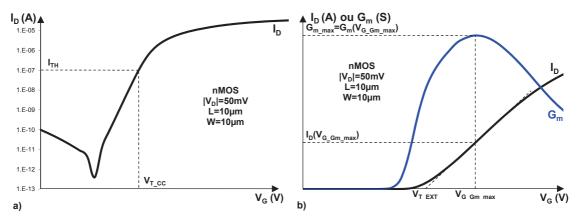

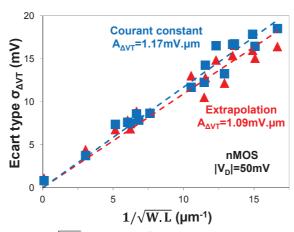

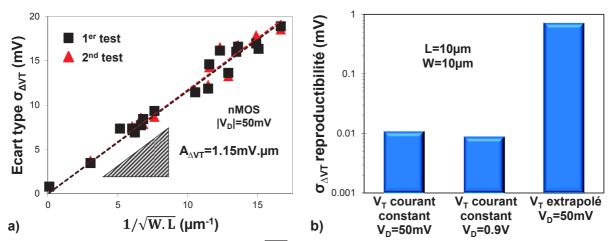

Cet écart peut être utilisé avantageusement pour faire évoluer un dispositif de type LVT en RVT, par exemple. Un BOX mince ( $T_{BOX}$ <50nm) est indispensable afin d'avoir une modulation efficace du  $V_T$ . L'entreprise SOITEC a déjà montré qu'il est possible de réduire  $T_{BOX}$  jusqu'à une épaisseur de 1.5nm [Delprat '09]. L'intégration de BP sous le BOX mince est requise, à laquelle est couplée une utilisation optimale de  $V_B$ . L'efficacité de cette architecture a par ailleurs été démontrée sur silicium