# Acceleration of a bioinformatics application using high-level synthesis

Naeem Abbas

# ► To cite this version:

Naeem Abbas. Acceleration of a bioinformatics application using high-level synthesis. Other [cs.OH]. École normale supérieure de Cachan - ENS Cachan, 2012. English. NNT: 2012DENS0019 . tel-00847076

# HAL Id: tel-00847076 https://theses.hal.science/tel-00847076

Submitted on 22 Jul 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE / ENS CACHAN - BRETAGNE

sous le sceau de l'Université européenne de Bretagne pour obtenir le titre de DOCTEUR DE L'ÉCOLE NORMALE SUPÉRIEURE DE CACHAN Mention : Informatique École doctorale MATISSE présentée par **Naeem Abbas** Préparée à l'Unité Mixte de Recherche 6074 Institut de recherche en informatique et systèmes aléatoires

Acceleration of a **Bioinformatics Application using High-Level** Synthesis

Thèse soutenue le 22 mai 2012 devant le jury composé de :

Philippe COUSSY, Maître de conférences - Université de Bretagne Sud / rapporteur Florent DE DINECHIN, Maître de conférences - ENS Lyon / rapporteur

#### Rumen ANDONOV,

Professeur des universités - Université de Rennes 1 / examinateur Tanguy RISSET, Professeur des universités - INSA de Lyon / examinateur

Steven DERRIEN, Maître de conférences - Université de Rennes 1 / directeur de thèse Patrice QUINTON,

Professeur des universités - ENS Cachan-Bretagne / directeur de thèse

#### Résumé

Les avancées dans le domaine de la bioinformatique ont ouvert de nouveaux horizons pour la recherche en biologie et en pharmacologie. Les machines comme les algorithmes utilisées aujourd'hui ne sont cependant plus en mesure de répondre à la demande exponentiellement croissante en puissance de calcul. Il existe donc un besoin pour des plate-formes de calculs spécialisées pour ce types de traitement, qui sauraient tirer partie de l'ensemble des technologie de calcul parallèle actuelles (Grilles, multi-coeurs, GPU, FPGA).

Dans cette thèse nous étudions comment l'utilisation d'outils de synthèse de haut niveau peut aider à la conception d'accélérateurs matériels spécialisés massivement parallèles. Ces outils permettent de réduire considérablement les temps de conception mais ne sont pas conçus pour produire des architectures matérielles massivement parallèles efficaces. Les travaux de cette thèse se sont attachés à dégager des techniques de parallélisation, ainsi que les moyens d'exprimer efficacement ce parallélisme, pour des outils de type HLS.

Nous avons appliqué ces résultats à une application de bioinformatique connue sous le nom de HMMER. Cet algorithme qui pourrait être un bon candidat à une accélération matérielle est très délicat à paralléliser. Nous avons proposé un schéma d'exécution parallèle original, basé sur une réécriture mathématique de l'algorithme, qui a été suivi par une exploration des schéma d'exécution matériels possible sur FPGA. Ce résultat à ensuite donnée lieu à une mise en œuvre sur un accélérateur matériel et a démontré des facteurs d'accélération encourageants.

Les travaux démontre également la pertinence des outils de HLS pour la conception d'accélérateur matériel pour le calcul haute performance en Bioinformatique, à la fois pour réduire les temps de conception, mais aussi pour obtenir des architectures plus efficaces et plus facilement reciblables d'un plateforme à une autre.

#### Abstract

The revolutionary advancements in the field of bioinformatics have opened new horizons in biological and pharmaceutical research. However, the existing bioinformatics tools are unable to meet the computational demands, due to the recent exponential growth in biological data. So there is a dire need to build future bioinformatics platforms incorporating modern parallel computation techniques.

In this work, we investigate FPGA based acceleration of these applications, using High-Level Synthesis. High-Level Synthesis tools enable automatic translation of abstract specifications to the hardware design, considerably reducing the design efforts. However, the generation of an efficient hardware using these tools is often a challenge for the designers. Our research effort encompasses an exploration of the techniques and practices, that can lead to the generation of an efficient design from these high-level synthesis tools.

We illustrate our methodology by accelerating a widely used application -- HMMER -- in bioinformatics community. HMMER is well-known for its compute-intensive kernels and data dependencies that lead to a sequential execution. We propose an original parallelization scheme based on rewriting of its mathematical formulation, followed by an indepth exploration of hardware mapping techniques of these kernels, and finally show on-board acceleration results.

Our research work demonstrates designing flexible hardware accelerators for bioinformatics applications, using design methodologies which are more efficient than the traditional ones, and where resulting designs are scalable enough to meet the future requirements.

Nº d'ordre :

École normale supérieure de Cachan - Antenne de Bretagne

Campus de Ker Lann - Avenue Robert Schuman - 35170 BRUZ Tél : +33(0)2 99 05 93 00 - Fax : +33(0)2 99 05 93 29

# Contents

| 1        | Introduction                                 |                                                                  |    |  |  |  |  |

|----------|----------------------------------------------|------------------------------------------------------------------|----|--|--|--|--|

|          | 1.1                                          | High Performance Computing for Bioinformatics                    | 1  |  |  |  |  |

|          | 1.2                                          | FPGA based Hardware Acceleration                                 | 3  |  |  |  |  |

|          | 1.3                                          | FPGA Design Flow                                                 | 3  |  |  |  |  |

|          |                                              | 1.3.1 Synthèse de haut niveau                                    | 5  |  |  |  |  |

|          | 1.4                                          | Parallélisation à l'aide de réductions et de préfixes parallèles | 6  |  |  |  |  |

|          | 1.5                                          | Contributions de cette thèse                                     |    |  |  |  |  |

| <b>2</b> | Intr                                         | oduction                                                         | 9  |  |  |  |  |

|          | 2.1                                          | High Performance Computing for Bioinformatics                    | 9  |  |  |  |  |

|          | 2.2                                          | FPGA based Hardware Acceleration                                 | 10 |  |  |  |  |

|          | 2.3                                          | FPGA Design Flow                                                 | 11 |  |  |  |  |

|          |                                              | 2.3.1 High-level Synthesis                                       | 13 |  |  |  |  |

|          | 2.4                                          | Exploiting Parallelism with Reductions and Prefixes              | 14 |  |  |  |  |

|          | 2.5                                          | Contributions of this work                                       |    |  |  |  |  |

| 3        | An Introduction to Bioinformatics Algorithms |                                                                  |    |  |  |  |  |

|          | 3.1                                          | DNA, RNA & Proteins:                                             |    |  |  |  |  |

|          | 3.2                                          | Sequence Alignment                                               |    |  |  |  |  |

|          |                                              | 3.2.1 Pairwise Sequence Alignment                                | 20 |  |  |  |  |

|          |                                              | 3.2.2 Multiple Sequence Alignment                                | 23 |  |  |  |  |

|          |                                              | 3.2.3 The HMMER tool suit                                        | 27 |  |  |  |  |

|          |                                              | 3.2.4 Computational Complexity                                   | 29 |  |  |  |  |

|          | 3.3                                          | RNA Structure Prediction                                         | 30 |  |  |  |  |

|          |                                              | 3.3.1 The Nussinov Algorithm                                     | 31 |  |  |  |  |

|          |                                              | 3.3.2 The Zuker Algorithm                                        | 32 |  |  |  |  |

|          | 3.4                                          | High Performance Bioinformatics                                  | 33 |  |  |  |  |

|          | 3.5                                          | Conclusion                                                       |    |  |  |  |  |

| 4        | HLS Based Acceleration: From C to Circuit    |                                                                  |    |  |  |  |  |

|          | 4.1                                          | Reconfigurable Computing                                         | 35 |  |  |  |  |

|          | 4.2                                          | Accelerators for Biocomputing 38                                 |    |  |  |  |  |

|          | 4.3                                          | High Level Synthesis                                             | 39 |  |  |  |  |

|          |                | 4.3.1                | Advantages of HLS over RTL coding                                                                                          |  |  |  |  |  |

|----------|----------------|----------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|          | 4.4            | HLS D                | Design Steps $\ldots \ldots 41$ |  |  |  |  |  |

|          |                | 4.4.1                | Compilation                                                                                                                |  |  |  |  |  |

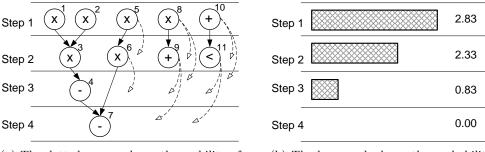

|          |                | 4.4.2                | Operation Scheduling 41                                                                                                    |  |  |  |  |  |

|          |                | 4.4.3                | Allocation & Binding 47                                                                                                    |  |  |  |  |  |

|          |                | 4.4.4                | Generation                                                                                                                 |  |  |  |  |  |

|          | 4.5            | High I               | evel Synthesis Tools: An Overview                                                                                          |  |  |  |  |  |

|          |                | 4.5.1                | Impulse C                                                                                                                  |  |  |  |  |  |

|          |                | 4.5.2                | Catapult C                                                                                                                 |  |  |  |  |  |

|          |                | 4.5.3                | MMAlpha                                                                                                                    |  |  |  |  |  |

|          |                | 4.5.4                | C2H                                                                                                                        |  |  |  |  |  |

|          | 4.6            | Conclu               | sion $\ldots \ldots 54$                              |  |  |  |  |  |

| <b>5</b> | Effi           | cient H              | lardware Generation with HLS 57                                                                                            |  |  |  |  |  |

|          | 5.1            | Bit-Le               | vel Transformations                                                                                                        |  |  |  |  |  |

|          |                | 5.1.1                | Bit-Width Narrowing 58                                                                                                     |  |  |  |  |  |

|          |                | 5.1.2                | Bit-level Optimization                                                                                                     |  |  |  |  |  |

|          | 5.2            | Instrue              | ction-level transformations                                                                                                |  |  |  |  |  |

|          |                | 5.2.1                | Operator Strength Reduction                                                                                                |  |  |  |  |  |

|          |                | 5.2.2                | Height Reduction                                                                                                           |  |  |  |  |  |

|          |                | 5.2.3                | Code Motion                                                                                                                |  |  |  |  |  |

|          | 5.3            | Loop Transformations |                                                                                                                            |  |  |  |  |  |

|          |                | 5.3.1                | Unrolling                                                                                                                  |  |  |  |  |  |

|          |                | 5.3.2                | Loop Interchange                                                                                                           |  |  |  |  |  |

|          |                | 5.3.3                | Loop Shifting                                                                                                              |  |  |  |  |  |

|          |                | 5.3.4                | Loop Peeling                                                                                                               |  |  |  |  |  |

|          |                | 5.3.5                | Loop Skewing                                                                                                               |  |  |  |  |  |

|          |                | 5.3.6                | Loop Fusion                                                                                                                |  |  |  |  |  |

|          |                | 5.3.7                | C-Slowing                                                                                                                  |  |  |  |  |  |

|          |                | 5.3.8                | Loop Tiling & Strip-mining                                                                                                 |  |  |  |  |  |

|          |                | 5.3.9                | Memory Splitting & Interleaving                                                                                            |  |  |  |  |  |

|          |                | 5.3.10               | Data Replication, Reuse and Scalar Replacement 71                                                                          |  |  |  |  |  |

|          |                | 5.3.11               | Array Contraction                                                                                                          |  |  |  |  |  |

|          |                | 5.3.12               | Data Prefetching                                                                                                           |  |  |  |  |  |

|          |                | 5.3.13               | Memory Duplication                                                                                                         |  |  |  |  |  |

|          | 5.4            | Conclu               | sion $\ldots \ldots 76$         |  |  |  |  |  |

| 6        | $\mathbf{Ext}$ | racting              | g Parallelism in HMMER 79                                                                                                  |  |  |  |  |  |

|          | 6.1            | I Introduction       |                                                                                                                            |  |  |  |  |  |

|          | 6.2            | 6.2 Background       |                                                                                                                            |  |  |  |  |  |

|          |                | 6.2.1                | Profile HMMs                                                                                                               |  |  |  |  |  |

|          |                | 6.2.2                | P7Viterbi Algorithm Description                                                                                            |  |  |  |  |  |

|   |                             | 6.2.3                                                                                                   | Look ahead Computations                           |  |  |  |  |  |

|---|-----------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|--|

|   | 6.3                         | Relate                                                                                                  | ed work                                           |  |  |  |  |  |

|   |                             | 6.3.1                                                                                                   | Early Implementations                             |  |  |  |  |  |

|   |                             | 6.3.2                                                                                                   | Speculative Execution of the Viterbi Algorithm    |  |  |  |  |  |

|   |                             | 6.3.3                                                                                                   | GPU Implementations of HMMER                      |  |  |  |  |  |

|   |                             | 6.3.4                                                                                                   | HMMER3 and the Multi Ungapped Segment Heuristic   |  |  |  |  |  |

|   |                             | 6.3.5                                                                                                   | Accelerating the Complete HMMER3 Pipeline         |  |  |  |  |  |

|   | 6.4                         | Rewri                                                                                                   | ting the MSV Kernel                               |  |  |  |  |  |

|   | 6.5                         | .5 Rewriting the P7Viterbi Kernel                                                                       |                                                   |  |  |  |  |  |

|   |                             | 6.5.1                                                                                                   | Finding Reductions                                |  |  |  |  |  |

|   |                             | 6.5.2                                                                                                   | Impact of the Data-Dependence Graph               |  |  |  |  |  |

|   | 6.6                         | Parall                                                                                                  | el Prefix Networks                                |  |  |  |  |  |

|   | 6.7                         | Concl                                                                                                   | usion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $$ 96   |  |  |  |  |  |

| 7 | 7 Hardware Mapping of HMMER |                                                                                                         |                                                   |  |  |  |  |  |

|   | 7.1                         | Hardw                                                                                                   | vare Mapping                                      |  |  |  |  |  |

|   |                             | 7.1.1                                                                                                   | Architecture with a Single Combinational Datapath |  |  |  |  |  |

|   |                             | 7.1.2                                                                                                   | A C-slowed Pipelined Datapath                     |  |  |  |  |  |

|   |                             | 7.1.3                                                                                                   | Implementing the Max-Prefix Operator              |  |  |  |  |  |

|   |                             | 7.1.4                                                                                                   | Managing Resource Constraints through Tiling      |  |  |  |  |  |

|   |                             | 7.1.5                                                                                                   | Accelerating the Full HMMER Pipeline              |  |  |  |  |  |

|   | 7.2                         | mentation through High-Level Synthesis                                                                  |                                                   |  |  |  |  |  |

|   |                             | 7.2.1                                                                                                   | Loop Transformations                              |  |  |  |  |  |

|   |                             | 7.2.2                                                                                                   | Loop Unroll & Memory Partitioning                 |  |  |  |  |  |

|   |                             | 7.2.3                                                                                                   | Ping-Pong Memories                                |  |  |  |  |  |

|   |                             | 7.2.4                                                                                                   | Scalar Replication                                |  |  |  |  |  |

|   |                             | 7.2.5                                                                                                   | Memory Duplication                                |  |  |  |  |  |

|   | 7.3 Experimental results    |                                                                                                         |                                                   |  |  |  |  |  |

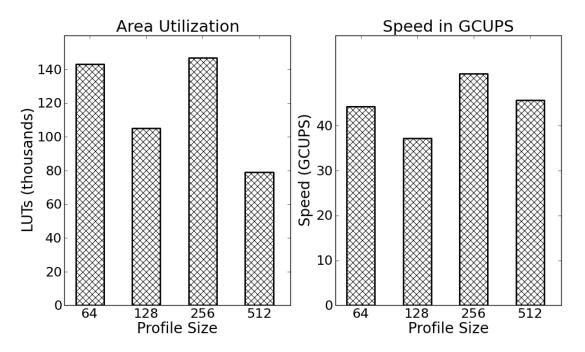

|   |                             | 7.3.1                                                                                                   | Area/Speed Results for the MSV Filter             |  |  |  |  |  |

|   |                             | 7.3.2                                                                                                   | Area/Speed Results for Max-Prefix Networks        |  |  |  |  |  |

|   |                             | 7.3.3                                                                                                   | Area/Speed Results for the P7Viterbi Filter       |  |  |  |  |  |

|   |                             | 7.3.4                                                                                                   | System level performance                          |  |  |  |  |  |

|   |                             | 7.3.5                                                                                                   | A Complete System-Level Redesign                  |  |  |  |  |  |

|   |                             | 7.3.6                                                                                                   | Discussion                                        |  |  |  |  |  |

|   | 7.4                         | .4 Conclusion $\ldots$ |                                                   |  |  |  |  |  |

| 8 | Cor                         | nclusio                                                                                                 | n & Future Perspectives 113                       |  |  |  |  |  |

|   | 8.1                         | 1 Conclusion                                                                                            |                                                   |  |  |  |  |  |

|   | 8.2                         | Future                                                                                                  | e Perspectives                                    |  |  |  |  |  |

1

# Introduction

## **1.1** High Performance Computing for Bioinformatics

La Bioinformatique est un domaine récent, mais qui suscite depuis une dizaine d'année de plus en plus d'intérêt dans la communauté scientifique. Ce domaine recouvre des champs disciplinaires très variés incluant la biologie, la génétique, l'informatique mais également les mathématiques. L'objectif premier de la bioinformatique est d'offrir aux biologistes des outils informatiques qui leur permettront d'analyser des données issues de séquences génétiques (par exemple de l'ADN, de l'ARN et/ou des protéines) afin d'essayer de découvrir ou de prédire les fonctions biologiques associées à ces séquences.

Les problématiques de la bio-informatique sont nombreuses, parmi celles-ci on peut citer la découverte de gènes dans des séquences d'ADN, la prédiction (et la classification) de la structure et des fonctions de protéines ainsi que la construction automatique d'arbres phylogéniques en vue de l'étude des relations évolutives.

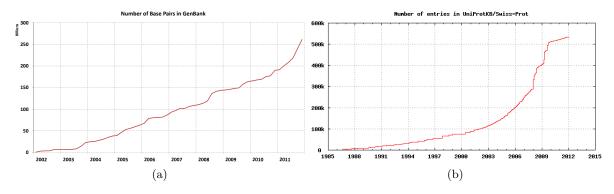

En outre, cette dernière décennie a vue l'apparition de techniques de séquençage d'ADN à haut débit, qui ont permises de grandes avancées (séquençage complet du génome humain [VAM<sup>+</sup>01], projet d'annotation du génome des plantes [SRV<sup>+</sup>07]). Ces progrès se sont à leur tour traduits par une explosion du volume de données génomiques (ADN, proteines) disponibles pour la communauté, comme l'illustre la figure 2.1, qui montre l'évolution des banques NCBI GenBank [NCB11] (ADN) UniProt [INT] (proteines).

Il est à noter que les nouvelles générations de technologies de séquençage, facilitent encore plus l'extraction d'énormes quantités de séquences, et vont certainement accentuer cette croissance exponentielle.

Les chercheurs sont de fait désormais confrontés à un défi majeur : extraire de ces volumes de données gigantesques des informations utiles à la compréhension de phénomènes biologiques. Les outils traditionnellement utilisés par la communauté bioinformatique ne sont en effet pas conçus pour fonctionner sur de telles masses de données, et les volumes de calculs mis en jeux dans ces outils d'analyses sont devenus trop importants au point de devenir un goulot d'étranglement.

Figure 1.1: The exponential growth of the (a) GenBank and (b) UniPortKB databases [NCB11, ?].

De nombreux travaux se sont donc intéressés à l'utilisation de machines parallèles pour réduire ces temps de calcul. Si les premier travaux ciblaient essentiellement des architectures de super-calculateurs classiques [SRG03, YHK09, CCSV04, GCBT10] (grilles, clusters), la démocratisation des architectures multi-cœurs [Edd, LBP<sup>+</sup>08] et l'émergence du GPGPU<sup>1</sup> ont rendu ces travaux plus populaires. Outre ces travaux portant sur des architecture généralistes programmables, il faut également mentionner l'utilisation d'accélérateur matériels spécialisés à base de logique programmable [HMS<sup>+</sup>07, SKD06, DQ07, LST] qui a démontré qu'il était possible de profiter de capacités d'accélération très élevées pour tout en restant à des niveaux de consommation électriques et donc des coûts de maintenance très raisonnables.

L'augmentation de la densité et de la vitesse des circuits FPGA a ainsi favorisé l'émergence d'accélérateurs matériels reconfigurables orientés vers le domaine du calcul haute performance (HPC), avec des applications en calculs financier [ZLH+05, WV08], simulations météorologiques [AT01], traitements vidéo [LSK+05] mais également en bioinformatique[DQ07, SKD06].

Les accélérateurs FPGAs se sont ainsi avérés être des architectures matérielles bien adaptées à la mise en œuvre de traitements de type bioinformatique. Ceux-ci offrent souvent la possibilité d'exposer un un niveau important de parallélisme à grain fin dans l'algorithme, lequel peut ensuite être exploité très efficacement par une mise en œuvre sur FPGA. Une part importante des algorithmes de bioinformatique repose en effet sur l'utilisation de techniques à base de programmation dynamique, en autre pour la comparaison de séquence (Smith-Waterman [SW81], Needleman-Wunsch [NW70] and BLAST [AGM<sup>+</sup>90]), l'alignement multiple de séquences (CLUSTALW [THG94]), la recherche sur profil (HMMER [Edd]), le repliage de séquences de RNA (MFOLD [Zuk03]) et même la construction d'arbres phylogéniques (PHYLIP [Fel93]). Le caractère régulier des traitements effectués dans ces algorithmes se prête ainsi facilement à une parallélisation sur un architecture de type réseau régulier disposant de communication locales.

<sup>&</sup>lt;sup>1</sup>Qui vise à utiliser les capacités de calculs très importantes des cartes graphiques pour accélérer des calculs scientifiques

### 1.2 FPGA based Hardware Acceleration

Les circuits FPGAs se présentent comme un gigantesque matrice de cellules logiques programmables, ils peuvent donc être configurés pour implémenter un nombre élevé de chemins de données matériels spécialisés et fonctionnant en parallèle. Les développeurs peuvent ainsi directement implémenter un accélérateur matériel dédié à l'application et tirer parti des gains en performance dus au parallélisme et à la spécialisation.

Dans un FPGA, l'expression de ce parallélisme peut prendre de nombreuses plusieurs formes : parallélisme de tâches en implantant plusieurs cœurs de calculs opérant en parallèle, parallélisme d'opérations au travers de l'utilisation de chemins de données pipelinés complexes. Parce que les FPGAs fonctionnent à des fréquences d'horloges bien plus faibles que les processeurs (en moyenne par un facteur 10), ils doivent compenser leur lenteur relative en exploitant un niveau de parallélisme massif au sein du circuit, tout en s'assurant de la possibilité d'alimenter le circuit en donnée à une cadence suffisante.

Une des techniques utilisées pour améliorer à la fois le degré de parallélisme et la fréquence de fonctionnement des circuits implantés sur le FPGA est d'utiliser des encodages de données à précision réduite (entiers à précision arbitraire, et codage virgule fixe en lieu et place des flottants).

Ici encore les algorithmes de bioinformatique se prêtent très bien à ce genre d'optimisations (par exemple, le codage d'un base ADN peut se faire sur 2 bits au lieu d'un octet complet). Ces caractéristiques en font donc de très bon candidats à une accélération matérielle sur FPGA, en particulier comparé à des machine de type GPUs plus orienté vers le calcul flottant. De nombreux travaux se sont donc intéressés à la mise en uvre, sur FPGA, daccélérateur matériels pour les algorithmes les plus couramment utilisés [HMS<sup>+</sup>07, SKD06, DQ07].

Ces implémentations, qui ont démontrés des facteurs daccélération très encourageant, se basent sur des spécifications du circuit écrites en VHDL ou Verilog, et très fortement optimisées pour une technologie FPGA donnée. Ce type dapproche pose de fait des problèmes de portabilité, et passer dun accélérateur FPGA à un autre nécessite souvent de reprendre la conception du circuit à zéro. Le section suivante aborde ce problème et discute de la pertinence des outils de synthèse de haut niveau dans ce contexte.

### 1.3 FPGA Design Flow

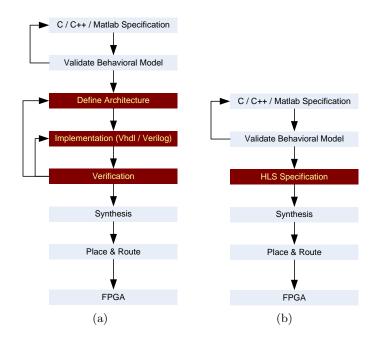

Le flot de conception standard pour circuit FPGA se base en grand partie sur celui d'un ASIC. Les principales étapes de ce flot sont représentées dans la Figure 2.2a, elles ne concernent cependant que la partie matérielle d'un co-design logiciel-matériel, le logiciel embarqué étant développé à l'aide de chaînes de compilation classiques.

La première étape de ce flot consiste à définir les spécifications fonctionnelles des composants dans des langages de haut niveau (C, C++, Matlab) afin de déterminer le comportement exact du système. Une fois validée, le concepteur doit définir une

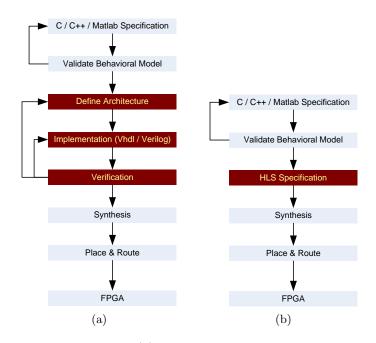

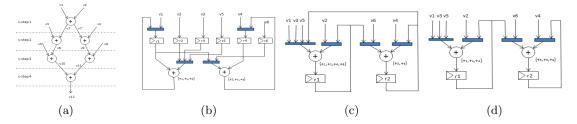

Figure 1.2: Flot de conception FPGA: (a) Flot de conception traditionnel basé sur l'utilisation de langages de description de matériel (HDLs). La description d'une application en HDL est délicate et nécessite un effeort de vérifictaion important. (b) Flot de synthèse basé sur l'utilisation d'outils de synthèse de haut niveau: l'étape de conception manuelle au niveau RTL est remplaée par une description comportementale de haut niveau, suivie d'un phase de généraion automatique de description RTL.

architecture matérielle qui sera en mesure de satisfaire les contraintes de performance, de coût et de consommation électrique imposés par le cahier des charges.

Une fois l'architecture définie, les concepteurs doivent décrire cette architecture au niveau RTL (Register to Logic) à l'aide de langages de description de matériel (Verilog ou VHDL) ou de spécifications schématiques. Cette description est ensuite validée à l'aide de simulations, afin de garantir sa correction.

Une fois vérifiée, la description du circuit est alors synthétisée, c'est-à-dire transformée en une représentation à base de primitives logiques du FPGA ciblé appelée *netlist*. Cette représentation est ensuite placée et routée sur le circuit FPGA ciblé, en permet de dériver un fichier *bitstream* qui servira à configurer le FPGA.

Ce flot de conception reste cependant très complexe et nécessite souvent de nombreuses itérations avant d'obtenir une configuration matérielle opérationnelle.

La première difficulté est de bien choisir la cible architecturale (type de FPGA, capacités de traitement, de mémorisation, etc.), car celle-ci va conditionner une grande partie des choix de conception ultérieurs. Un mauvais choix initial peut ainsi avoir un impact très important sur l'effort de conception global. Le seconde (et principale) difficulté est la spécification au niveau RTL (Register to Logic) de l'architecture de l'accélérateur, qui se fait à l'aide de langage de description matériel tels VHDL ou Verilog. Cette étape est très fastidieuse et nécessite une étape de débogage très longue, avec de nombreuses itérations entre les étapes de spécification et de validation.

La complexité toujours croissante des systèmes électroniques, qui s'illustre par une constante augmentation des fonctionnalités intégrées sur un seul circuit FPGA, rend cette étape de conception RTL de plus en plus critique [CD08]. De fait, les outils de conceptions utilisés pour la mise en œuvre de systèmes de communication sans-fils 4G sont les même que pour le standard GSM, et ce malgré l'énorme écart de complexité entre ces deux standards.

De nombreux travaux se sont donc intéressés à ce problème, en proposant de relever le niveau d'abstraction utilisé la spécification de composants. L'objectif est d'offrir des outils de génération automatique de description RTL à partir de spécification algorithmiques dans des langages de plus haut niveau tel C ou SystemC. On parle alors d'outils de *synthèse de haut niveau*.

#### 1.3.1 Synthèse de haut niveau

Les outils de synthèse de haut niveau (High Level Synthesis) visent principalement à réduire les délais de conception, en utilisant des spécifications de plus haut-niveau que celles offertes par les approches basés sur des descriptions RTL. En plus de réduire le temps de conception à proprement parler, les outils d'HLS permettent également de fortement réduire le temps de vérification, en diminuant le nombre d'itération nécessaire pour obtenir un composant fonctionnel. Par ailleurs en libérant le concepteur de la gestion des horloges, du partage de ressource et de l'interfaçage mémoire, ces outils réduisent également les risques d'erreurs.

Le portage de spécification RTL d'une technologie à une autre se fait souvent au prix d'une baisse des performances et d'une augmentation du coût en ressource et en consommation énergétique [Fin10].

Au contraire, parce que la spécification HLS se fait au niveau fonctionnel, le portage d'une IP matérielle d'une plate-forme à une autre est simplifié, puisque c'est l'outil d'HLS qui va se charger de réaliser le mapping technologique.

Pour autant, les architectures matérielles générées automatiquement à partir d'un niveau de spécification plus abstrait ne sont que rarement aussi efficaces que des implémentations manuelles. En conséquence, les faibles performances obtenues par une utilisation naïve de ces outils limitent l'intérêt des FPGAs dans un contexte de calcul « haute performance ».

Ces faibles performances s'expliquent par l'incapacité de ces outils à extraire un niveau de parallélisme suffisamment élevé. Les accélérateurs matériels issus de ces outils peinent de fait à rivaliser avec des architecture GPU et multi-cœurs, et ce d'autant plus qu'il doivent compter sur une fréquence de fonctionnement plus faible.

Il est possible de lever cette difficulté, en modifiant directement le code source de l'application de manière à faire apparaître un niveau de parallélisme qui sera exploitable par l'outil. Ce type de technique est très efficace dès lors que l'on cherche à accélérer des calculs réguliers, ayant la forme de nids de boucles. En effet, il est possible de d'appuyer sur la grande quantité de travaux issus de la communauté de parallélisation

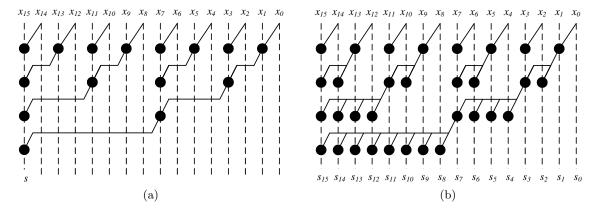

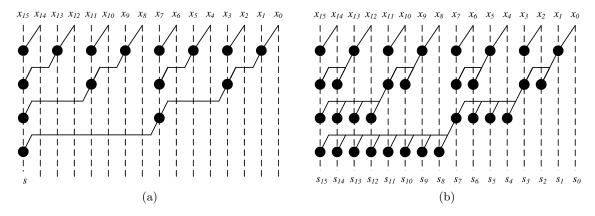

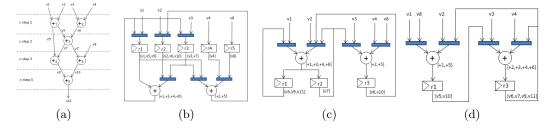

Figure 1.3: Examples of Reduction, (a), and Scan, (b), are shown here, with a possible order of computation.

#### automatique [Wol90, Wol96].

Outre les aspects liés à la parallélisation des calculs proprement dits, l'obtention de bonne performances nécessite également de prendre en compte de manière très fine la gestion des données dans les différents niveaux de hiérarchie mémoire du système (mémoire hôte, mémoire locale sur la carte, mémoire embarquée). Une des contributions de ce travail est de présenter une revue d'ensemble des transformations clés permettant d'obtenir, grâce à des outils de synthèse de haut niveau, des architectures matérielles spécialisées exploitant efficacement les possibilités des accélérateurs FPGAs actuels.

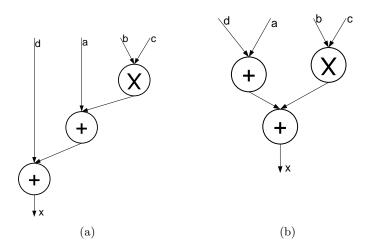

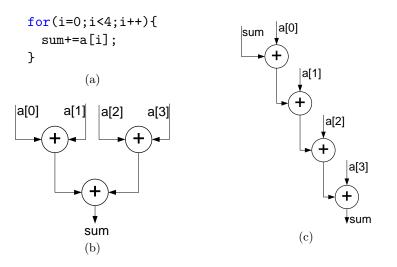

# 1.4 Parallélisation à l'aide de réductions et de préfixes parallèles

Les algorithmes élémentaires utilisés en algèbre linéaire peuvent être classés en deux catégories. Dans la première, la taille du résultat d'un calcul est du même ordre que la taille de ces opérandes; c'est par exemple le cas de l'addition de deux vecteurs. Dans la seconde la taille du résultat est plus beaucoup plus petite (en général une valeur scalaire), d'où le terme de réduction proposé par Iverson [Ive62], et qui correspond par exemple à l'opération de sommation des éléments d'un vecteur ou d'une matrice.

Dans ce travail, nous nous sommes intéressés à deux types de calculs : les opérations de *réduction* et les opérations de *préfixes*<sup>2</sup>. Ces opérations, qui opèrent sur des collections d'objets, sont basées sur l'utilisation d'un opérateur élémentaire disposant de propriétés de commutativité et d'associativité.

Soit  $\oplus$  le symbole identifiant cet opérateur élémentaire, une réduction sur un vecteur

<sup>&</sup>lt;sup>2</sup>également connus sous le terme de scan

opérande  $(x_1, x_2, \ldots, x_n)$  s'écrit comme:

$$s = \bigoplus_{i=0}^{n} x_i = x_0 \oplus x_1 \oplus \ldots \oplus x_n \tag{1.1}$$

Pour l'opération de préfixe, la taille du résultat est la même que celle de l'opérande, et se définit, pour vecteur opérande  $(x_1, x_2, \ldots, x_n)$  et pour un vecteur résultat  $(s_1, s_2, \ldots, s_n)$  comme:

$$s_k = \bigoplus_{i=0}^k x_i = x_0 \oplus x_1 \oplus \ldots \oplus x_k \tag{1.2}$$

Ces deux types d'opérations sont représentées sur la Figure 2.3 pour n = 16. Il est important de remarquer que ces opérations, a priori séquentielles dans leur définition, peuvent être réalisées de manière parallèle en réorganisant les calculs de manière plus ou moins complexe. En particulier, la mise en œuvre efficace d'opérations de type préfixes sur circuits VLSI est un sujet qui a reçu beaucoup d'attention <sup>3</sup>, et ce depuis le début des années 60. De nombreuses structures matérielles permettant d'explorer des compromis entre rapidité et coût en surface ont ainsi été proposées [LF80, BK82, KS73, HC87, Skl60].

La mise en œuvre matérielle d'un algorithme utilisant des opérations de préfixes peut profiter de ces résultats, en explorant les différentes possibilités de réaliser le traitement pour choisir la plus efficace. Cette exploration est d'autant plus facile lorsque la conception se fait à haut niveau d'abstraction, par exemple en utilisant des outils de synthèse de haut niveau.

Les algorithmes d'alignement de séquences utilisés en bioinformatique, sont basés sur des algorithmes de programmation dynamique, et exposent des schémas de calcul se prêtant justement assez bien à des reformulations mathématiques permettant de faire ressortir des opérations de réductions et/ou de préfixe.

Dans le chapitre ??, nous montrons comment certains des traitements mis en jeu dans l'outil HMMER [Edd] peuvent être reformulées comme des opérations de réductions et/ou de préfixes, lesquelles permettent une parallélisation plus efficace.

### 1.5 Contributions de cette thèse

Le chapitre 3 propose une courte introduction au domaine de la bioinformatique, et à ses enjeux. Nous détaillons en particulier les principaux algorithmes utilisés pour l'alignement la comparaison et le repliement de séquences, en mettant l'accent sur leur coût en termes de traitements et sur leur capacité à passer à l'échelle sur de gros volumes de données. Nous montrons en particulier que la plupart des approches utilisés ne passent pas à l'échelle, et nécessitent de recourir à des architectures matérielle exploitant des niveaux de parallélisme important.

$<sup>^{3}</sup>$ Cet intérêt s'explique par le fait que l'opération d'addition binaire est une opération de préfixe

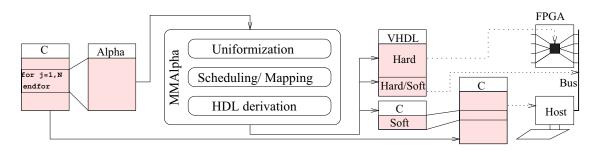

Le chapitre 4 présente ensuite un survol des techniques et outils de synthèse de haut niveau. Ces outils permettent de dériver une architecture matérielle spécialisée directement à partir d'une spécification algorithmique (par exemple en C). Ils permettent ainsi de réduire de manière drastique les temps de conception. Le chapitre présente les différentes étapes mises en jeu dans un flot de synthèse HLS, et propose un état de l'art des techniques utilisées dans ces outils. Le chapitre se termine par une revue des outils de HLS académiques et commerciaux actuellement disponibles.

Le chapitre 5 s'intéresse quant à lui aux techniques de transformation de code permettant d'améliorer les performances des architectures obtenues par synthèse HLS. Cette partie du manuscrit s'intéresse en particulier aux transformations de boucles pour la parallélisation et à l'optimisation des accès à la mémoire, qui sont des points cruciaux pour l'obtention d'accélérateurs efficaces.

Les chapitres 6 & 7 présentent quant à eux les contributions de ce travail, qui portent sur l'utilisation de transformations de programme complexes, en vue de l'accélération matériel du programme HMMER. Cet outil, très utilisé dans la communauté bioinformatique, repose sur deux noyaux de calculs (MSV et P7Viterbi) réputés difficiles à accélérer du fait de la présence de dépendances de données qui empêchent a priori toute parallélisation. Dans le chapitre 6, nous présentons l'état de l'art concernant la parallélisation de HMMER sur FPGA et proposons une reformulation des noyaux MSV et P7Viterbi qui permet de mettre en évidence un niveau important de parallélisme au travers d'opérations de réductions et de préfixes.

Le chapitre 7 s'intéresse quand à lui à la mise en œuvre, sur un accélérateur FPGA et à l'aide d'un outil HLS commercial, d'une architecture de co-processeur parallèle pour HMMER. L'originalité de l'approche vient de l'utilisation d'un schéma de calcul complexe, exploitant du parallélisme à grain fin (boucles vectorisées) et à gros grain (utilisation d'un macro-pipeline de tâche). Ces schémas ont donnés lieu à une mise en œuvre matérielle sur une carte FPGA (XtremeData), et nous a permis de démontrer des facteur d'accélération intéressant par rapport à une mise en œuvre optimisée exploitant de manière très fine les extension SIMD des processeurs multi-cœurs Intel.

2

# Introduction

### 2.1 High Performance Computing for Bioinformatics

Bioinformatics can be defined as an application of concepts from computer science, mathematics and statistics to analyze biological data (e.g. DNA, RNA and Proteins) and to predict their the functions and structures. The typical problems found in bioinformatics consist in finding genes in DNA sequences, analyzing new proteins, aligning similar proteins into families and generating phylogenetic trees to expose evolutionary relationships.

In the last decade, there has been a rapid growth in the amount of available digital biological data with the advancement in DNA sequencing techniques, and particularly the success of projects such as The Human Genome Project [VAM<sup>+</sup>01] and genome annotation projects for plants [SRV<sup>+</sup>07]. The noticeable examples are the growth of DNA sequence information in NCBI's GenBank [NCB11] database and the growth of protein sequences in the UniProt [?] database, as shown in Figure 2.1. Furthermore, the next-generation sequencing technologies have enabled the extraction of genome sequence data in huge quantities, and this will result in further growth of these databases.

Computer scientists and biomedical researchers are now facing a major challenge of transforming this enormous amount of genomic data into biological understanding. The traditional tools and algorithms in bioinformatics were designed to handle very small databases, hence a bottleneck in terms of computational time has arisen when scaled up to facilitate analyses of large data-sets and databases. Recently, a lot of research efforts have been done enabling modern bioinformatics tools to take advantage of parallel computing environments. The implementation of bioinformatic applications on modern multicore general-purpose processors [Edd, LBP<sup>+</sup>08], General Purpose Graphic Processors (GPGPU) [WBKC09b, VS11, MV08], grid technology [SRG03, YHK09, CCSV04, GCBT10] and reconfigurable platforms, such as field-programmable gate arrays (FPGAs) [HMS<sup>+</sup>07, SKD06, DQ07, LST] have shown promising acceleration and have significantly reduced the runtime of many biological algorithms while operating on the

Figure 2.1: The exponential growth of the (a) GenBank and (b) UniPortKB databases [NCB11, ?].

enormous databases.

The considerable increase in logic density and clock speed of FPGAs, in recent years, have in turn increased the trend of using FPGAs to implement compute intensive algorithms from various domains, including finance [ZLH<sup>+</sup>05, WV08], weather forecast [AT01], video encoding [LSK<sup>+</sup>05] and bioinformatics[DQ07, SKD06]. FPGAs are an attractive target architecture for bioinformatics applications, considering their cost-effectiveness as customized accelerators and their ability to exploit the fine-grain parallelism available in many bioinformatics applications. A large class of bioinformatics applications rely on dynamic programming algorithms or a fast approximation of one, including sequence database search programs (Smith-Waterman [SW81], Needleman-Wunsch [NW70] and BLAST [AGM<sup>+</sup>90]), multiple sequence alignment programs (CLUSTALW [THG94]), profile based search programs (HMMER [Edd]), RNA-folding programs (MFOLD [Zuk03]) and even phylogenetic inference programs (PHYLIP [Fel93]). The FPGA architecture is very well suited for such dynamic programming algorithms, since it has a regular structure, similar to the data dependencies in dynamic programming algorithms, with a communication network to close neighbors.

### 2.2 FPGA based Hardware Acceleration

FPGAs are simply large fields of programmable gates, so they can be programmed into many parallel hardware execution paths. Due to their parallel nature, different processing operations do not have to compete for the same resources. The designer can map any number of task-specific cores on an FPGA, that all run as simultaneous parallel circuits.

On an FPGA, a designer can exhibit parallelism with the help of a variety of computation granularities (i.e. fine and coarse-grain parallelism), pipelining the long computation paths and through data parallelism. The parallelism granularity may range from very fine-grain computations (e.g. bit-level operations), to fine-grain operations, as in a SIMD architecture (e.g. word- and instruction-level operations) and to coarse-grain computations (e.g. many independent instances of a highly compute intensive kernel, operating in parallel).

Since FPGAs operate on a very low frequency (about  $10 \times low$ ) in comparison with a CPU, so in order to outperform the CPU based performance, there should be enough computations to be computed in parallel. Hence compute intensive applications with massive inherent parallelism (e.g. converting each pixel of a color image to grayscale) are highly suitable for FPGA based implementation. Similarly applications with reduced bit-width data are appropriate for FPGAs, due to their ability to compute custom bitwidth operations. The majority of bioinformatics algorithms do not require even the full integer precision, thus floating point arithmetic on a modern CPUs will be not valuable. Therefore, FPGA based implementation of such applications can exploit the customizable precision and parallelism, and can result in improved speed and better utilization of the available resources.

The properties held by bioinformatic applications make them viable for FPGA based acceleration in comparison with other acceleration approaches, such as clusters and GPUs. And a lot of research work has been done to accelerate these applications on FPGAs using traditional hardware languages (VHDL and Verilog) [HMS<sup>+</sup>07, SKD06, DQ07]. The resulting implementations are very efficient and the obtained speedup is highly valuable. However, there are few issues with FPGA based implementations that hinders the designer to opt for an FPGA based implementation, e.g. the design flow is highly error prone and lengthy verification phase often becomes the bottleneck in design projects. In next section, we will highlight these issues by discussing the traditional FPGA design flow and a possible solution to these issues through high-level synthesis.

# 2.3 FPGA Design Flow

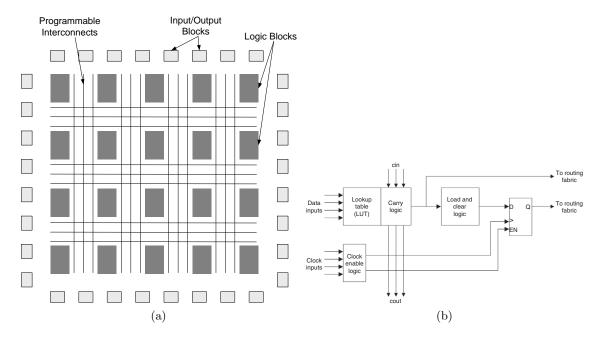

The standard design flow for FPGA designs is borrowed from ASICs, as shown in Figure 2.2a. In practice, a design is usually partitioned into hardware & software parts. The steps shown in Figure 2.2a are related only to the implementation of hardware blocks in such a design, while the software blocks will be implemented using standard software development techniques.

The first step in design flow is to define functional specifications in C, C++, Matlab or any other language in order to validate and fine-tune the desired behavior. Once tested, the designer needs to define an optimal architecture to implement the desired functionality. The architecture selection defines the performance, area and power consumption goals to be met. After the architecture is defined, the design team hand-codes these decisions in the form of a Hardware Description language (Verilog or Vhdl) or in the form of a schematic design. At this stage, functional simulation is carried out to verify the correctness of the described functionality.

After functional verification, the design can be synthesized, i.e. mapping boolean operators on lookup tables (LUTs) modules, shown in Figure 4.1b. The result of logic synthesis is called the *netlist*, a file describing the modules to be used for the

Figure 2.2: FPGA Design Flow: (a) Traditional FPGA design flow using Hardware Description languages (HDLs). The application description in HDL is very error prone and requires a lot of verification efforts. Similarly, it is not easy to port design to other FPGA architectures. (b) High-level Synthesis based FPGA design flow: The manual RTL based design steps are replaced with high-level behavioral description of design following by an automatic generation of RTL design.

implementation of the design and its interconnections. In next step, we place and route the design on FPGA, i.e. the operators (LUTs, Flip-Flops, Multiplexers, etc.) described in the netlist will be now placed on the FPGA fabric and will be connected together through routing. This step is normally done by the CAD tool provided by the FPGA vendor. The CAD tool generates a file called *bitstream*. The bitstream file contains the description of all the bits to be configured, in order to configure LUTs, the interconnect matrices, multiplexers and I/O of the FPGA. Now, by loading the bitstream file on the FPGA, the hardware will be configured according to the functional specifications of the application.

However, the design flow is not that straightforward and often involves a lot of iterative development steps. First problem is to find a suitable architecture, since the following design steps closely related to the selected architecture. An inadequate choice of underlying architecture will prolong the development cycle greatly. The biggest problem in the design flow is the manual RTL description, as when the design is tested after first implementation, bugs are reported and a lot of development time is usually spent in hunting down and fixing the bugs individually. The iterative process of fixing bugs, generating new bugs and fixing them again, prolongs the time-to-market.

One major issue with HDL based implementation is the ever-increasing complexity of electronic designs. The increase in device capacity only exacerbates this issue, as programmers seek to map increasingly complex computations to even larger devices [CD08]. The reality is that we are trying to develop 4G broadband modems and H264 decoders

with tools and methods inherited from era, when GSM and VGA controllers were popular technologies [Fin10]. Eventually, creating RTL design triggers bug and cause the verification phase to be the bottleneck of any ASIC project.

Many research efforts have been done to ameliorate this issue by offering higher-level programming abstractions combined with an automatic RTL generation from popular high-level languages such as C or Matlab, known as *High-level Synthesis* (HLS) tools.

#### 2.3.1 High-level Synthesis

High-level synthesis addresses the root cause of the problem, posed by HDL based design flow, by providing an error-free path from abstract specification to RTL. HLS reduces the implementation time, while also reduces the overall verification effort. The high-level of abstraction needs a lot less detail for the description, and the designer can only focus on describing the desired behavior. With fewer lines of code, when there are no such details as clocks, technology or micro-architecture specifications in side the sources, the risk of errors is greatly reduced. Similarly with fewer blocks to verify, the design can be exhaustively verified.

The abstract functional specifications in HLS, makes the design reuse more effective. Since the design sources are now the abstract specification of the design, retargeting to other architectures is easier. Similarly, the concepts of IP and reuse, which have been promoted to address the design complexity challenge with RTL design, are often unhelpful. The retargeting of legacy RTL is usually done at the expense of power, performance and area [Fin10]. However, in HLS, we are dealing with pure functional specifications and technology specific information is added later by HLS tool automatically. This makes the IP reuse and change in existing functionality, easy to implement and verify.

For biocomputing applications, HLS framework simplify the complex algorithmic description phase and also maximize the design portability. However, the abstract specification of a design may lack several design optimization details, which also expands the hardware mapping possibilities. This can lead to a less efficient design through automatic RTL design generation, in comparison with the efficiency of a highly detailed manual RTL design. Consequently, the resulting performance of HLS based design is often not good enough to justify the use of an FPGA based acceleration. Most of the research efforts in development of these HLS tools, are dedicated to an efficient translation of the given input C code into a hardware design, and this task has been accomplished quite effectively. However, there has been a very little focus on automatic parallelization extraction from the input C code. Therefore, the designer needs to pay a lot of attention on 'what' kind of C code will generate 'what' kind of circuit.

To tackle this problem, the HLS input needs to be reformed by exposing the hidden parallelism in the algorithm. This task can be accomplished with a prior dependency analysis of input design and based on this analysis parallelism can be expressed with the help of modern high performance compiler optimization techniques [Wol90, Wol96]. The input code should also manage memory resources in an efficient way ( i.e. minimizing

Figure 2.3: Examples of Reduction, (a), and Scan, (b), are shown here, with a possible order of computation.

data communication overhead and maximizing data reuse). Hence, there is a dire need to identify, analyze and layout the rules and guidelines, a designer should keep in mind, while designing for hardware using high-level synthesis tools.

The leitmotiv of this thesis consists in a critical analysis of state of the art HLS tools, identifying their capabilities and shortcomings, formalize techniques to craft an efficient hardware using these tools and exercise these strategies on a well-known, compute-intensive and naively sequential bioinformatic application (i.e. HMMER).

# 2.4 Exploiting Parallelism with Reductions and Prefixes

The basic algorithms of linear algebra and matrix computation fall into two broad classes. In the first one, the output of a computation is of the same size or bigger than the input data. This is the case, for instance, for vector operations. In the second class, the output is much smaller, typically only one value, than the input data, hence the name reduction which has been coined by Iverson [Ive62].

Here, we are interested in two special kind of such computations, namely *reduction* and *scans* or *prefix* computations, where operations hold associativity and commutative properties. Let say,  $\oplus$  represents such an operation, then a reduction can be defined, over a input vector  $(x_1, x_2, \ldots, x_n)$ , as:

$$s = \bigoplus_{i=0}^{n} x_i = x_0 \oplus x_1 \oplus \ldots \oplus x_n \tag{2.1}$$

A prefix operation belongs to the first class of computations, where output is exactly the same size as the input, and can be defined for an output vector  $(s_1, s_2, \ldots, s_n)$  as:

$$s_k = \bigoplus_{i=0}^k x_i = x_0 \oplus x_1 \oplus \ldots \oplus x_k$$

(2.2)

The operations can be visualized in Figure 2.3 for n = 16. The possibility to compute these operations in parallel and in numerous order of executions, has given significant importance to these computations. While targeting FPGA, a designer can easily devise a compromise between the speed and area.

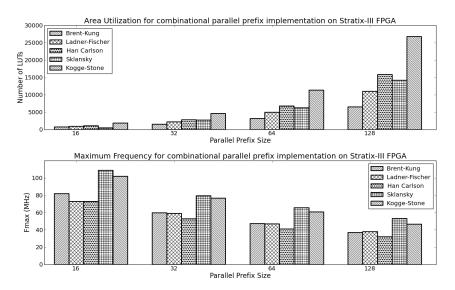

The parallel implementation of prefix networks (Parallel Prefix) has received a wealth of attention from VLSI community going back almost 50 years and various network topologies have been proposed [LF80, BK82, KS73, HC87, Skl60]. These network topologies allow a variety of hardware implementations of a prefix operation, managing various design trade-offs, such as speed, area, wiring and fan-out. Thus, expressing parallelism in the form of prefix operations allows to utilize these previously developed network topologies. Furthermore, the high-level synthesis based implementation of such networks simplifies the design exploration task.

Sequence alignment techniques, based on dynamic programming algorithms, in bioinformatic applications generally compute a best score for a comparison and the computations involved usually hold the above mentioned algebraic properties. So there is a strong tendency that reduction and prefix computations can be detected in these algorithms and it will lead to parallel implementation of the algorithms. In Chapter ??, we demonstrate how algorithmic dependencies in HMMER [Edd] can be transformed into reductions and prefixes through algorithmic rewriting and which ultimately help to accelerate the execution.

## 2.5 Contributions of this work

Chapter 3 provides an brief introduction to bioinformatics field and common practices in this field. We highlight some important algorithms for sequence alignment and RNA folding. A review of these algorithms provides a fair insight to the algorithmic complexities and also highlights the challenge being faced by biologists and computer scientists, i.e. exercising these algorithms on constantly growing size of genome databases in becoming time prohibitive. There is a pressing need to utilize the advancements in computation platforms and accelerate bioinformatics applications.

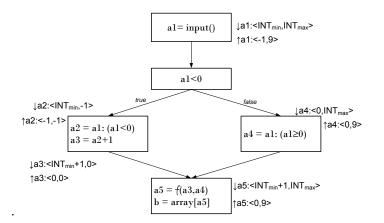

Chapter 4 discusses how bioinformatics applications are viable for FPGA based acceleration. It also reasons the importance of high-level synthesis in FPGA based implementation, in comparison with traditional RTL based designs. The chapter introduces to the design flow inside an HLS tool and discusses the state of the art techniques applied in each step of the design flow. It also provides an overview of few well-known HLS tools in market, investigates their handling of input code and identify the basis of performance degradation.

Chapter 5 is dedicated to design techniques and code transformations, a designer needs to bear in mind while designing hardware from high-level specifications (i.e. C code). The sole idea is to highlight that 'what' kind of C code will be translated to 'what' kind of hardware, and 'what' kind of transformations may help to accomplish design goals (Speed/Area).

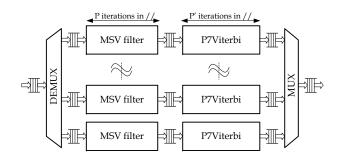

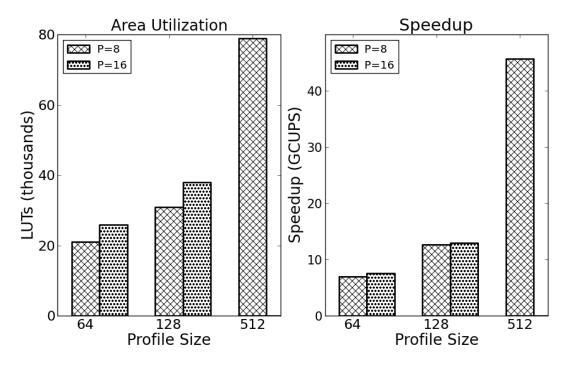

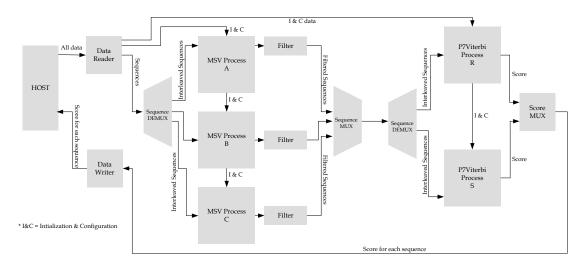

Chapter 6 & 7 presents the research work carried out to accelerate HMMER application by exercising the previously discussed techniques for efficient hardware design using HLS. HMMER is a widely usied tool in bioinformatics for sequence homology searching. The computation kernels of HMMER, namely MSV and P7Viterbi are very compute-intensive, and their data dependencies, if interpreted naively, lead to a purely sequential execution. We propose an original parallelization scheme for HMMER based on rewriting its mathematical formulation, in order to expose hidden potential parallelization opportunities by transforming computations into well-known architectures, i.e. parallel prefix networks & reduction trees. Besides exploring fine-grain parallelization possibilities, we employ and compare coarse-grain parallelization through different system-level implementations of the complete execution pipeline, based on either several independent pipelines or a large aggregated pipeline. We implement our parallelization scheme on FPGA, and then present and compare our speedup with the latest HMMER3 SSE version on a Quad-core Intel Xeon machine. Our results show that a careful HLS based implementation can fairly compete an RTL based design in terms of performance and holds a definite edge in terms of time-to-market and design efforts.

3

# An Introduction to Bioinformatics Algorithms

Bioinformatics can be defined as the science of developing computer systems and algorithms for the purpose of spreading up and enhancing biological research [Aga08]. To understand bioinformatics in a meaningful way, it is necessary for a computer scientist to understand some basic biology. This chapter provides a short introduction to those fundamental concepts in biology and highlights some common algorithms being used in bioinformatics.

# 3.1 DNA, RNA & Proteins:

Cells are the smallest structural unit of life that has all the basic characteristics of a living organism, such as maintaining life and reproducing it [SEQb]. A cell contains all the necessary *information* as well as the required *equipment* to not only produce a replica of itself, but also helps its offspring start functioning [JP04]. Each cell in a human body contains 23 pairs of chromosomes, consisting of 30,000 genes in each of them. There are around  $10^{12}$  cells in a body, which gives an estimate of approximately 3 billion pairs of DNA bases [oEGP08]. Similarly, the plant genome-sequencing project reports more than 40,000 genes in average plants [SRV<sup>+</sup>07].

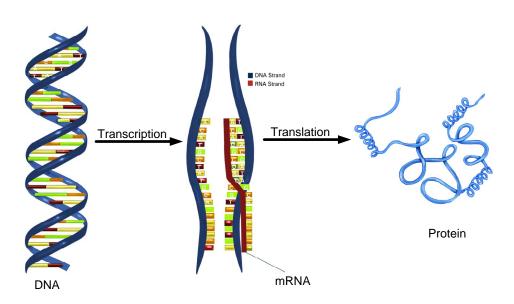

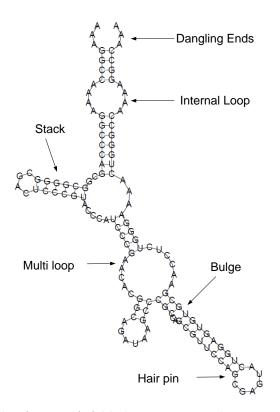

The three primary types of molecules studied by biologists are DNA, RNA and proteins. The relationship between these molecules is the transfer of information from DNA to proteins through RNA, as shown in Figure 3.1. DNA encodes RNA that produces the proteins, where proteins are responsible for managing and performing different biological processes inside the cell. A DNA within a cell holds the complete information describing the functionality of the cell. RNA transfers short pieces of this information to different places within the cell, where this information is used to produce proteins [JP04].

DNA is a long molecule forming a chain, where the links of the chain are pieces called

Figure 3.1: The relationship between DNA, RNA and Proteins is referred as the central dogma of life. [Courtesy of NIGMS Image Gallery [Gal]]

nucleotides, or 'bases', named 'A', 'C', 'G' and 'T'. DNA encodes the information necessary to build a cell. Most of the cell activities, e.g. breaking down the food as enzymes, building new cell fragments, cell signaling and signal transduction, are carried out by proteins. However, a DNA sequence must be decoded to make a protein and the decoding process requires the creations of an RNA template [Wil03]. The creation of "messenger RNA" or mRNA is called *transcription*, while the process of creating proteins from the mRNA is called *translation*.

The discovery of DNA is probably the most influential discovery of the 20th century, that led to extraordinary breakthroughs in the field of science and medicine. The discovery of DNA has enabled the identification of genes, diagnosing of diseases and developing treatments for them.

#### Why Bioinformatics?

The information that biologists have collected about gene sequences needs to be processed, in order to completely understand their function and roles, e.g. how a specific gene is related to a specific disease, or what are the functions of thousands of proteins and how proteins can be classified, in accordance to the functionalities. The field of *Bioinformatics* is a collection of such tools and methods that are used to collect, store, analyze and classify this huge amount of biological data.

As mentioned by Thampi [Tha09] regarding the history of bioninformatics, it began in the 1960s with the efforts of Margaret O. Dayhoff, Walter M. Fitch, Russell F. Doolittle and others. Since then it has evolved into a much developed discipline, having strong infulence on modern biology research. In 1970, Saul B. Needleman and Christian D. Wunsch [NW70], proposed the first DNA sequence matching algorithm. However, during the 1990s few major steps brought revolution in bioinformatics study, e.g. the start of

# AUUAACUUAUACAUUGAUAAC AAAAACUUAUACAU - GAUAAC GAACACUUAUAUAA - UCUAUC AGAAGCUUAUAUAA - UCUAUC

Figure 3.2: An example for multiple sequence alignment: The region of convergence is the shaded part where exact matches are found in all sequences.

Human Genome Project Bioinformatics, the availability of new analysis, services and the availability of data through Internet. Huge databases, such as GenBank and EMBL were designed to store, compare and analyze the biological sequence data that is being produced at an enormous rate. Today, bioinformatics field involves structural and functional analysis of proteins and genes, drug development and pre-clinical and clinical trials [Tha09].

The field of bioinformatic encompasses the use of tools and techniques from three separate disciplines; the source of the data to be analyzed is related to molecular biology, the platform and resources to analyze this data are borrowed from computer science, and the techniques and tools that analyze this data are based on data analysis algorithms [Ric]. The common activities in bioinformatics are hence storing DNA and protein sequences, analyzing, aligning or comparing, classifying protein families and finding new members, predicting structures of RNAs and constructing phylogenetic trees or evolutionary trees. In this chapter, we will focus on algorithms related to general sequence alignments [NW70, SW81, AGM<sup>+</sup>90, THG94, Edd11a] and RNA folding [NPGK78, ZS81].

# **3.2** Sequence Alignment

Sequence alignment is an arrangement of two sequences which shows where the two sequences are similar, and where they differ. Sequence alignment techniques are used to discover structural and functional properties of the biological data and characterizing evolutionary relationship in sequences. The identical characters are identified as matches, while nonidentical characters are mentioned as gaps. The regions with identical characters are known as *conserved region*, as shown in Figure 3.2. To discover this information it is important to obtain the "optimal" alignment, which is the one that exhibits the most significant similarities, and the fewer differences.

A similarity between two sequences suggests a similarity in the function or the structure of these sequences. Additionally, strong similarities between two sequences may also show the evolutionary relationship between them, assuming that there might be a common ancestor sequence. The alignment indicates the changes that could have occurred between the two homologous sequences w.r.t. a common ancestor sequence during evolution.

There are two types of sequence alignments: **global alignments** try to align the sequences from end to end for each sequence. Sequences that are similar and that are

approximately the same length are suitable candidates for global alignment. On the contrary **local alignments** search for segments of the two sequences that are similar. Local Alignment does not force the entire sequence into alignment, instead it only aligns the regions with the highest density of matches. It hence generates one or more subalignments in the aligned sequences. Local alignments are more suitable for aligning sequences which are different in length, or sequences that have a strong conserved region but not located at same position in both sequences.

In the following section we will show a comparison of both type of alignments and how for the same sequence pair, alignment result can differ.

Sequences are usually either aligned in pairwise manner, i.e. through a *Pairwise* sequence alignment, to compare and identify similarities in two sequences. In some other cases, three or more sequences are aligned, i.e. through a *Multiple sequence alignment*. The latter ones are used to show similarities conserved by most of the sequences and to construct families of these sequences. New members of such families can then be found by searching sequence databases for other sequences exhibiting these same conserved regions.

#### 3.2.1 Pairwise Sequence Alignment

Pairwise alignment methods are used to find optimal local or global alignment of two query sequences. The most common methods for pairwise alignment are *dot matrix*, *dynamic programming* and *word* or *k-tuple* methods. The most famous dynamic programming algorithms for pairwise alignment are Smith-Waterman [SW81] and Needleman-Wunsch [NW70] algorithms. BLAST [AGM<sup>+</sup>90], one of the most widely used bioinformatic tool, is based on a word method.

**Needleman-Wunsch:** Needleman-Wunsch algorithm performs global alignment for a pair of sequences. The algorithm was proposed in 1970 by Saul B. Needleman and Christian D. Wunsch [NW70], and was the first application of dynamic programming to biological sequence comparison. To find the alignment with the highest score, a two-dimensional array (or matrix) D is allocated. The entry in row i and column j is denoted by  $D_{i,j}$ . There is one column for each character in sequence A, and one row for each character in sequence B. Each cell of matrix D will be computed using following formula:

$$D_{i,j} = \max \begin{cases} D_{i-1,j-1} + \delta(A_i, B_j) \\ D_{i-1,j} + \delta(A_i, -) \\ D_{i,j-1} + \delta(-, B_j) \end{cases}$$

(3.1)

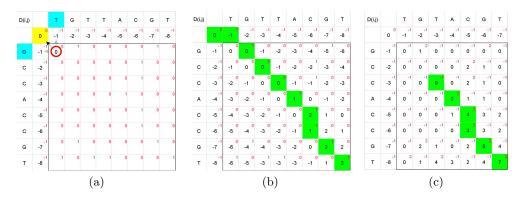

Figure 3.3a shows the initialized matrix and the data dependency, as depicted by the formula above. The numbers in small font, in first row and first column mentions the gap penalty while in rest of the matrix they shows the matching and penalty scores. The matching score,  $\delta(A_i, B_j)$  is equal to 1 when  $A_i$  and  $B_j$  are same characters. Otherwise, the penalty is set to 0 for any mismatch. Figre 3.3b shows the global alignment from

Figure 3.3: Pair-wise Sequence Alignment: (a) Matrix initialization & computation dependencies, (b) Global alignment with Needleman-Wunsch, (c) Local alignment with Smith-Waterman. The green trail in (b) and (c) shows the alignment. [Figures generated using Basic-Algorithms-of-Bioinformatics Applet [Cas]]

Needleman-Wunsch algorithm. The final alignment for this example:

| - | G            | $\mathbf{C}$ | $\mathbf{C}$ | Α | $\mathbf{C}$ | $\mathbf{C}$ | $\mathbf{G}$ | Т |

|---|--------------|--------------|--------------|---|--------------|--------------|--------------|---|

|   |              |              |              |   |              |              |              |   |

| Т | $\mathbf{G}$ | Т            | Т            | А | $\mathbf{C}$ | -            | $\mathbf{G}$ | Т |

**Smith-Waterman:** The Smith-Waterman algorithm, also based on dynamic programming techniques, computes the optimal local alignment of two sequences. Instead of looking at the entire sequence length, the Smith-Waterman algorithm compares only segments (for all possible lengths) of the input sequences and try to optimizes the similarity score. The main difference with Needleman-Wunsch is that Needleman-Wunsch allows negative scoring, whereas Smith-Waterman forces negative values to zero. This choice of positive scoring makes local alignment visible. The Smith-Waterman algorithm computes the matrix D as:

$$D_{i,j} = \max \begin{cases} D_{i-1,j-1} + \delta(A_i, B_j) \\ D_{i-1,j} + \delta(A_i, -) \\ D_{i,j-1} + \delta(-, B_j) \\ 0 \end{cases}$$

(3.2)

Figure 3.3c shows the local alignment, where matching score,  $\delta(A_i, B_j)$  is set to 2 and all penalties are set to -1. The final alignment in this case is:

$$\begin{array}{ccccccc} A & C & C & G & T \\ | & | & & | & | \\ A & C & - & G & T \end{array}$$

Local vs. Global Alignment: From the above two alignments, it can be seen that global alignment can align even less conserved regions in comparison with local alignment that only aligns the regions that are well conserved by the two sequences. Similarly, local Global Alignment CAG - TTATGTGGGCCCAAATTG

CAGTTATGTGGGCCCAAATTG

Local Alignment |||||||||||||||

GGGCCCAAATTGCAGTTATGT

Figure 3.4: Local Alignment aligns very significant regions, apart from the region location in two sequences, While global alignment aligns even small, not very significant, regions.

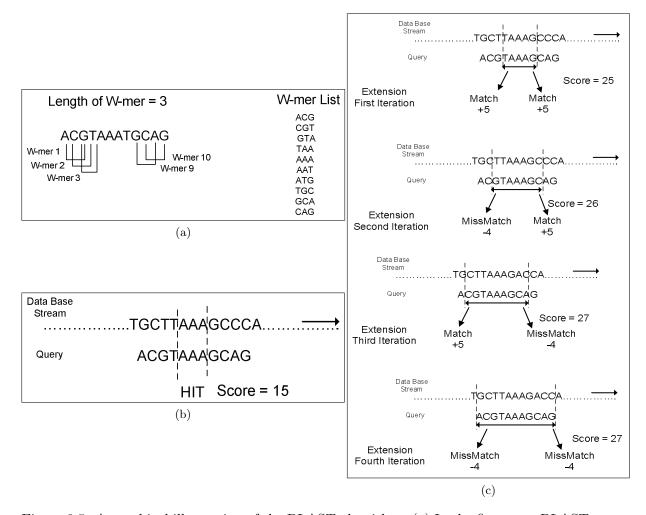

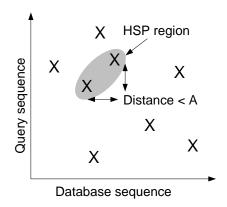

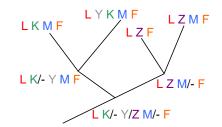

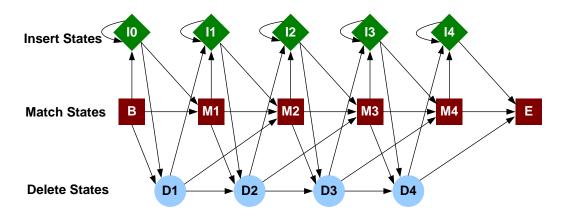

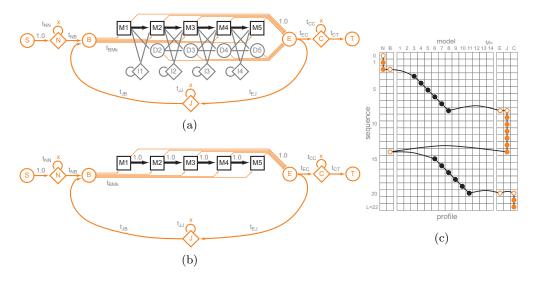

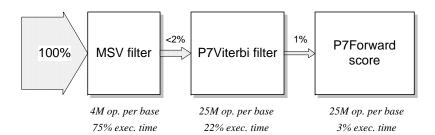

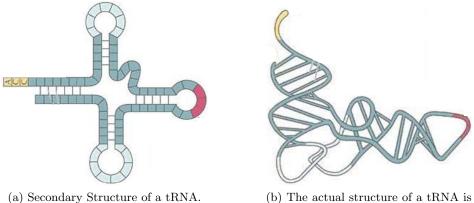

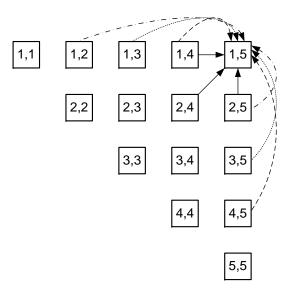

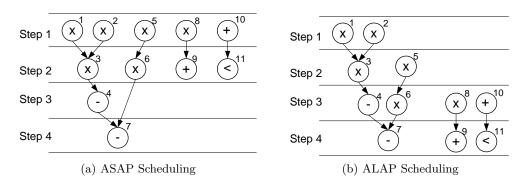

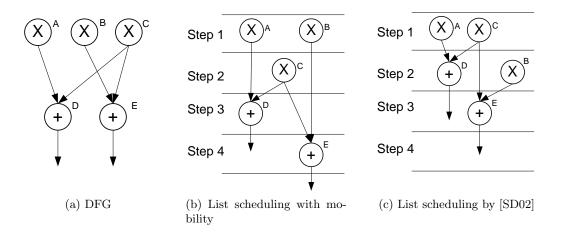

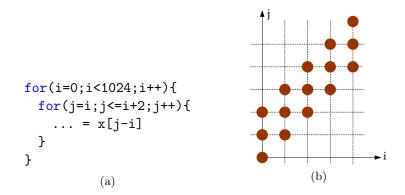

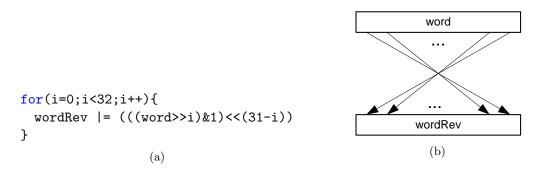

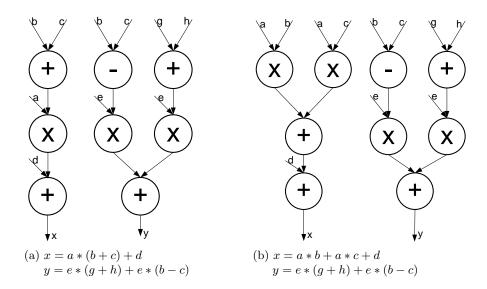

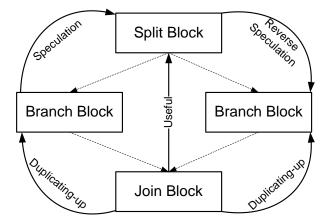

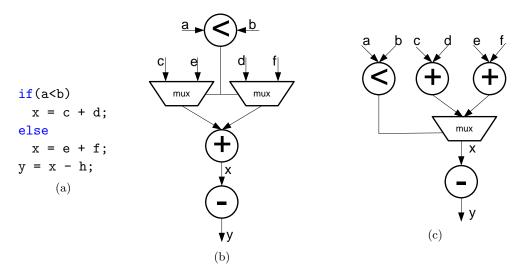

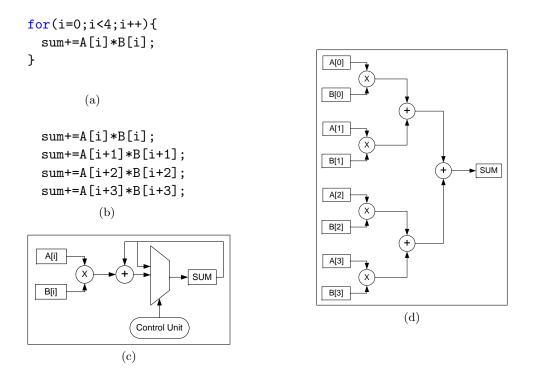

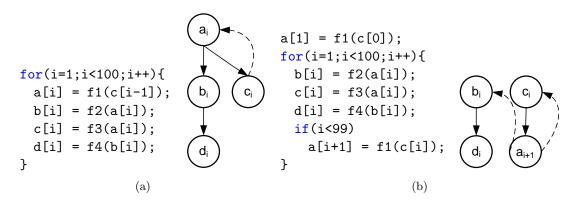

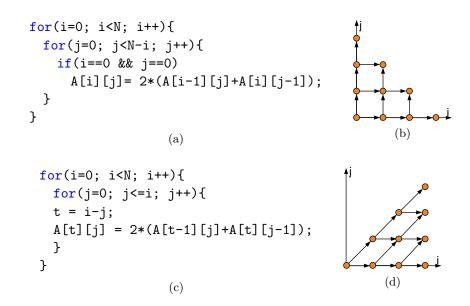

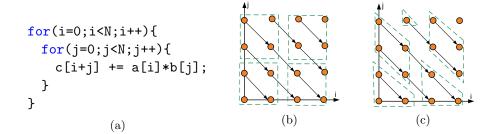

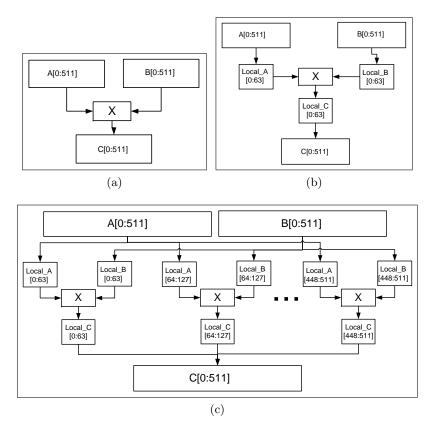

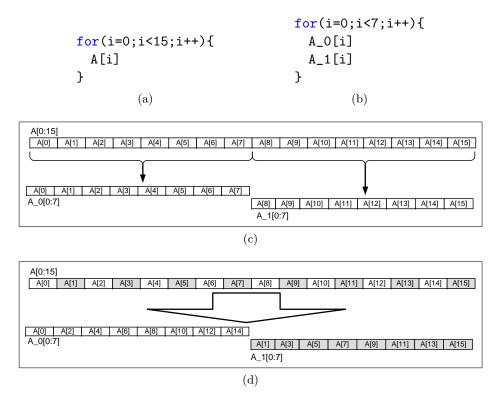

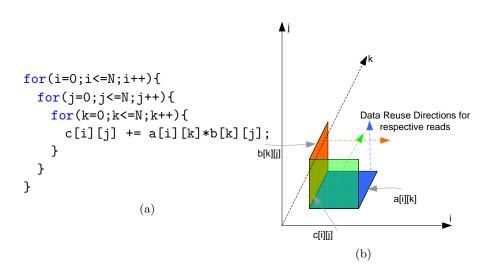

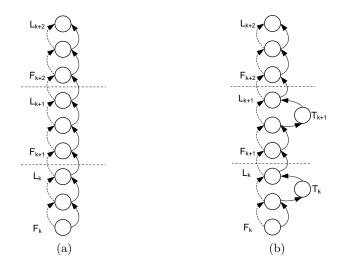

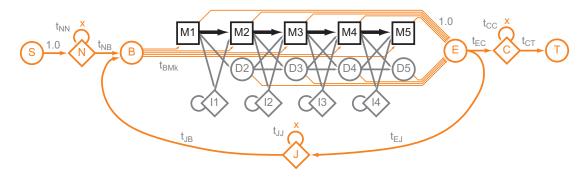

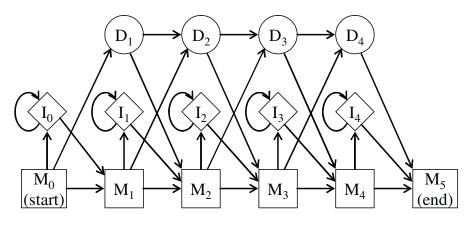

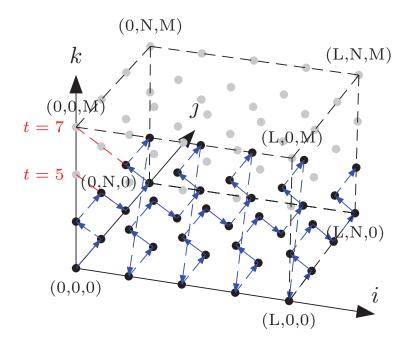

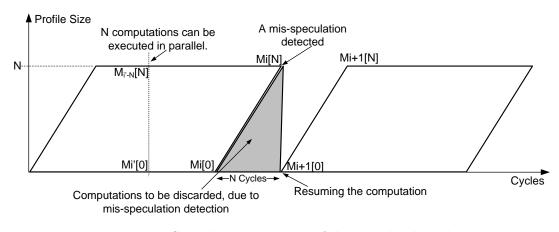

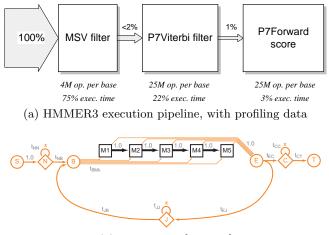

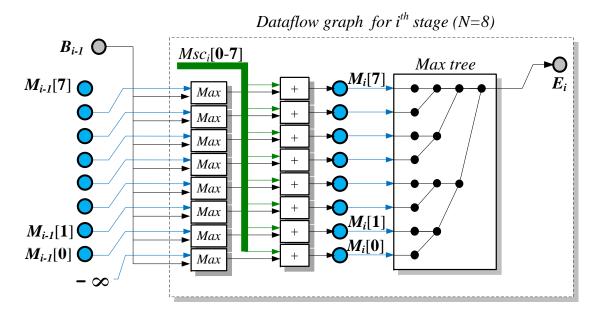

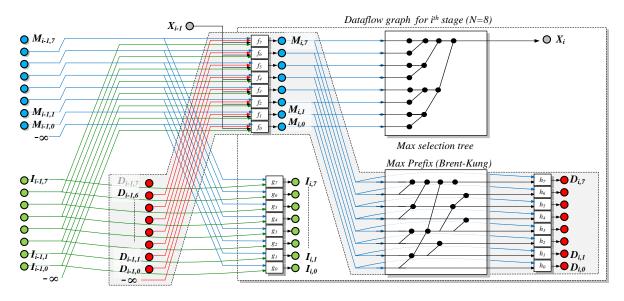

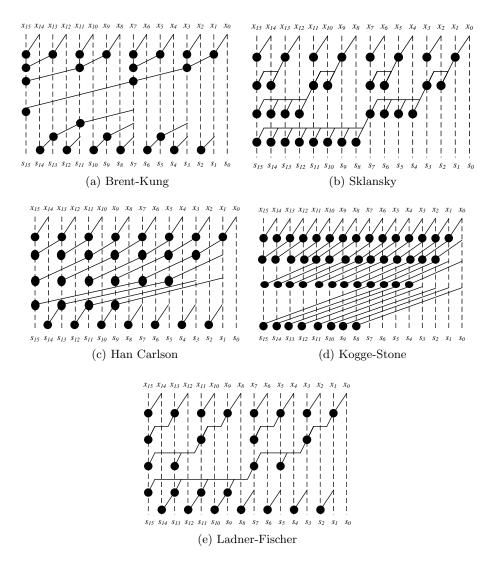

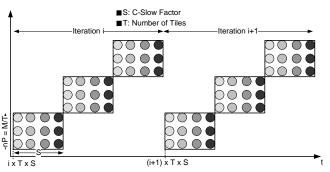

alignment can align well conserved regions, apart from their location in the two sequences. The example in Figure 3.4 shows how different results can be obtained from global and local alignments. In this example, local alignment aligns the starting region of the one sequence to the end region of the other sequence. On the other hand, global alignment aligns sequences from end to end and the example demonstrates the "gappy" nature of global alignment when sequences are insufficiently similar. Global alignments are most useful when query sequences are similar and of roughly equal size, e.g. protein sequences from the same protein family are often very conserved, and hence have almost the same length [JP04].